# 化合物半导体

CS COMPOUND SEMICONDUCTOR CHINA

2025年 10/11月

200mm 碳化硅衬底

厚度与外延厚度的多

维度影响

碳化硅结型势垒肖特

基二极管的高温挑战

为GaN加入超结结构

用无缝III-V族集成革

新硅基光子的竞争

## 溶液法生长碳化硅单晶的 位错研究

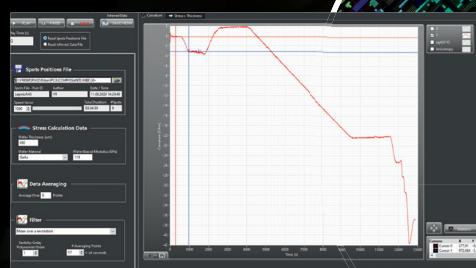

# 化合物半导体外延表面实时监测

原位实时

曲线跟踪

RIBER

**EZ-CURVE®**

过程监控工具：

良率增强

- 表面应力和曲率原位测量

- 实时探测

- 经典曲线对比

**RIBER**

info@riber.com

www.riber.com

INNOVATIVE SOLUTIONS FOR SEMICONDUCTOR INDUSTRY

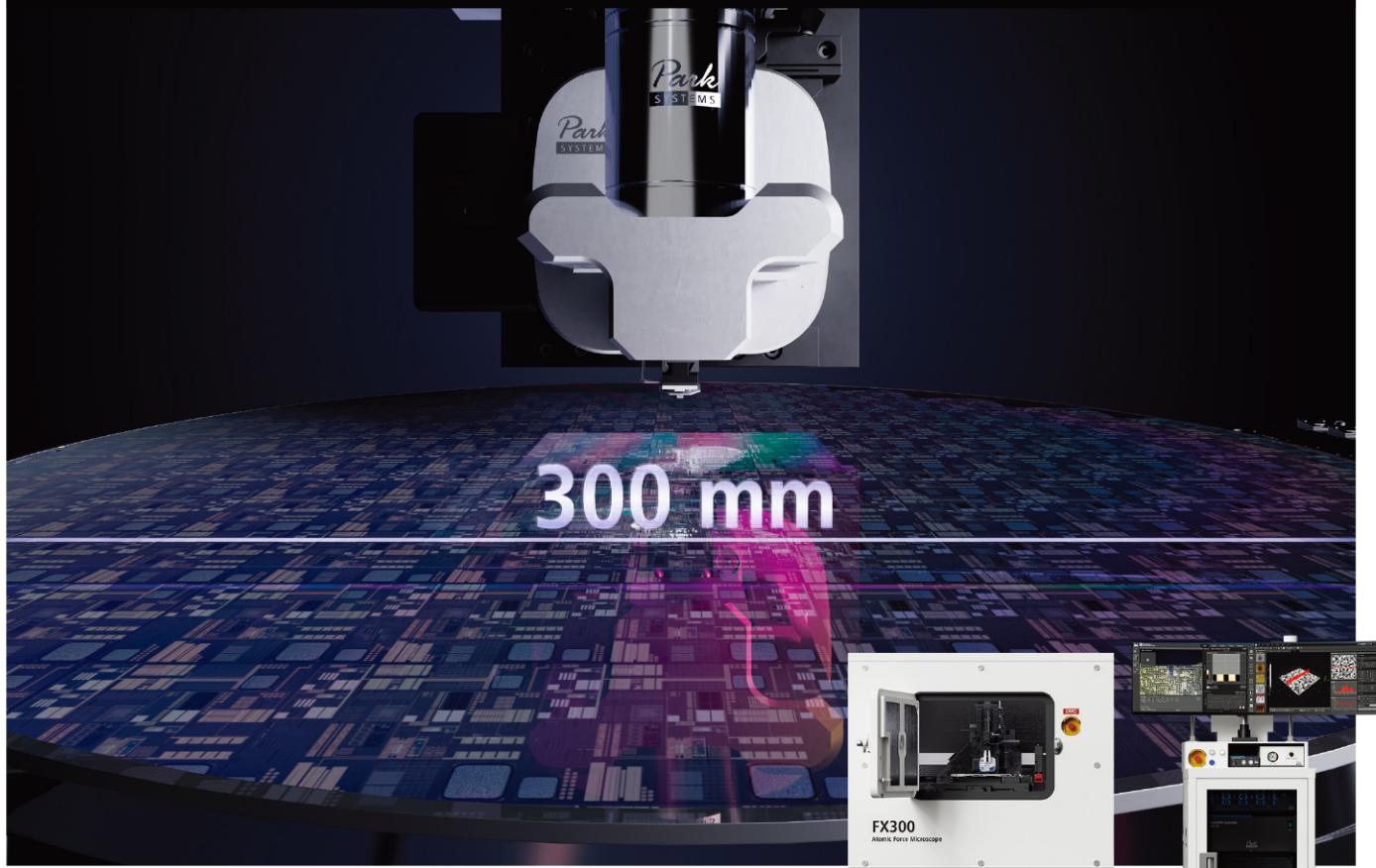

# 推动科研成果向 300毫米晶圆生产的转化

## Park FX300

### 助力从研发到生产的高效过渡

FX300可实现从实验室研究到生产环节的顺利衔接，能够测量从小样品到300mm晶圆的各种尺寸，支持广泛的原子力显微镜模式，适用于半导体检测及先进材料研究等多样化应用。

### 为创新而设计

配备自动探针识别与更换、快速激光对准功能，并结合SmartScan AI智能控制，实现从研发到质量管控的高效扩展。

### 值得信赖的精密表现

具备更清晰、更稳定的成像效果，更好的控制噪声与漂移，并通过优化的 SLD 光源，提供可靠的测量结果。

扫码了解更多

**FERMI** INSTRUMENTS

半导体薄膜物理沉积设备供应商

**费勉仪器**

创立于2017年，提供设计开发、集成测试、售后服务等一站式供应服务平台。

主营业务：半导体装备制造、精密零部件制造、不锈钢真空腔体焊接制造等。

MBE-800 cluster 分子束外延系统

MBE-1000 cluster 分子束外延系统

LFCP-600 真空解理和钝化系统

HLFP-800P 原子氢清洗钝化系统

PV-200C全自动磁控PZT薄膜生产线

**费勉仪器科技(南京)有限公司**

Fermion Instruments (Nanjing) Co., Ltd.

VIP HOTLINE +86-25-5888 3672

南京市江北新区智达路6号智城园区3号楼 info@fermi.com

费勉仪器公众号

费勉仪器官网

## 封面故事 Cover Story

13

### 溶液法生长碳化硅单晶的位错研究

#### Study on Dislocations in Solution-Grown Silicon Carbide Single Crystals

PVT法经过长时间运用，技术已经成熟，但是其晶体质量，生长成本仍是两大关键难题。HTCVD法同样存在生产成本更高的问题，同时其采用的易燃易爆气体不利于可持续发展。溶液法由于其生长温度低，位错密度小，原料成本低等天然优势成为目前大力发展的碳化硅单晶生长方法，并有望成为未来主流的产业化长晶技术。本研究表明，优化生长界面温度梯度、抑制气孔形成、实施扩径生长以及采用偏轴籽晶生长都可以显著降低晶体中的位错数量，提升单晶质量。

- 常州臻晶半导体有限公司

## 编者话 Editor's Note

04

### 液相法取代PVT只是时间问题

#### Just a matter of time: Replacing PVT with Solution Growth

- 陆敏

## 业界动态 Industry

05

### 芯联集成与理想汽车碳化硅产品量产交付

#### Sunic Integrated Circuit and Li Auto begin mass production and delivery of silicon carbide products.

05

### Imec推出300毫米GaN晶圆计划

#### Imec launches 300mm GaN program.

06

### 美国能源部拟资助其国内镓生产

#### US DoE to fund domestic gallium production.

06

### 英诺赛科为英伟达开发800V GaN电源方案

#### Innoscience develops 800V GaN power solution for NVIDIA.

07

### 牵引逆变器安装量增长19%

#### Traction inverter installations up 19%.

08

### Axcelis与Veeco宣布合并

#### Axcelis and Veeco announce merger.

08

### 格力电子×电子科技大学：碳化硅器件联合研究中心揭牌

#### Gree Electronics × University of Electronic Science and Technology of China: Joint Research Center for Silicon Carbide Devices officially inaugurated.

关于雅时国际商讯 (ACT International)

**ACT** INTERNATIONAL 产品系列，包括印刷和数字媒体以及会议和活动，雅时国际为国际营销公司和本地企业提供了进入中国市场的机会。雅时国际的媒体品牌为电子制造、机器视觉系统、激光/光子学、射频/微波系统设计、洁净室/污染控制和半导体制造，化合物半导体、工业AI等领域的20多万名专业读者和受众提供服务，雅时国际也是一些世界领先的技术出版社和活动组织者的销售代表。雅时国际的总部设在香港，在北京、上海、深圳和武汉设有分公司。[www.actintl.com.hk](http://www.actintl.com.hk)

关于《化合物半导体》

《化合物半导体》中国版(CSC)是全球最重要和最权威的杂志Compound Semiconductor的“姐妹”杂志，亦是中国唯一专注于化合物半导体产业的权威杂志，重点介绍国外先进技术和产业化经验，促进国内产业发展，为国内读者提供化合物半导体行业的专业知识。内容涵盖晶体的特性研究，器件结构的设计，生产中用到的材料、设备、软件、测量、厂房设施，以及有关市场分析和动态。

扫一扫

免费下载电子书

## Evatec专栏 Evatec Column

- 09 采用液态镓靶溅射制备的简并态 GaN 的低场传输特性与散射机制研究

Low-field transport properties and scattering mechanisms of degenerate n-GaN by sputtering from a liquid Ga-target**

- Philipp Doering 博士, 弗劳恩霍夫应用固体物理研究所IAF

- Thomas Tschirky, Evatec高级科学家

## 技术 Technology

- 19 200mm 碳化硅衬底厚度与外延厚度的多维度影响

Thick homoepitaxy on 200 mm SiCS**

- THOMAS KUHR, WOLFSPEED 公司工艺制程开发工程高级总监

- 23 碳化硅结型势垒肖特基二极管的高温挑战

Silicon Carbide Junction Barrier Schottky Diode to Challenge High Temperatures**

- 杨良<sup>1</sup>, 吉吟东<sup>2</sup>, 刘超超<sup>3</sup>, 宋亚东<sup>4</sup>, 曹建武<sup>5</sup>, 罗宁胜<sup>6</sup>

(1 深圳爱仕特科技有限公司, 2 清华大学信息科学技术学院, 3 江苏晶利恒半导体科技有限公司, 4 苏州安萨斯半导体有限公司, 5 深圳市慧亚科技有限公司, 6 合肥光电子半导体研究院特种封测技术实验室)

- 29 为 GaN 加入超结结构

Giving GaN a superjunction**

- 魏进、沈波; 北京大学

- 32 用无缝 III-V 族集成革新硅基光子的竞争

The race to revolutionise silicon photonics with seamless III-V integration**

- Bernardette Kunert 与 Joris Van Campenhout, imec

## 科技前沿 Research Review

- 37 无石英的 GaN-on-GaN 外延片的 HVPE 扩大生产

Scaling quartz-free HVPE of GaN-on-GaN epiwafers**

- 38 钝化  $\beta\text{-Ga}_2\text{O}_3$  器件

Passivating  $\beta\text{-Ga}_2\text{O}_3$  devices**

- 39 热壁 MOCVD 助力 GaN-on-AlN HEMTs

Hot-wall MOCVD helps GaN-on-AlN HEMTs**

## 40 广告索引 Advertisement Index

### 《化合物半导体》编委会 (排名不分先后)

- 张国义教授 北京大学东莞光电研究院荣誉院长, 中国有色金属学会宽禁带半导体专委会顾问委员会委员

王新强教授 北京大学博雅特聘教授, 博导

孙 钱博士 中国科学院苏州纳米技术与纳米仿生研究所研究院、博导、副主任

刘红超博士 安徽长飞先进半导体有限公司首席科学家

李哲洋博士 怀柔实验室资深技术专家 教授级高工, 博导

李顺峰博士 苏州半导体激光创新研究院执行院长

佟存柱教授 中科院长春光学精密机械与物理研究所常务副主任/研究

陈明祥教授 华中科技大学/武汉利之达科技 教授/首席专家

周贞宏博士 BelGaN CEO

张昭宇教授 香港中文大学(深圳)理工学院副教授 深圳半导体激光器重点实验室主任

孙海定博士 中国科学技术大学微电子学院研究员、博导

钮应喜博士 中国科学院半导体研究所, 教授级高工

郑中屏博士 台湾工业研究院光电所资深研究员, 台湾鹏正光电创建人, 佛山照明LED事业部创建人

北京华林嘉业科技有限公司 (CGB) 成立于2008年，主要从事半导体、泛半导体、新材料等领域的专业设备的研发、生产、销售及服务。公司研发总部位于北京亦庄经济技术开发区，拥有河北廊坊北方生产基地和无锡华东区域服务中心。同时在日本设有研发中心，专注于产品研发和海外市场服务。

产品应用领域包含：集成电路 (IC) 、微机电系统 (MEMS) 、硅材料 (Si) 、化合物半导体 (Compound Semiconductor) 、光通信器件 (Optical Communication Devices) 、功率器件 (Power Devices) 、半导体照明 (LED) 、先进封装 (Advanced Packaging) 、光伏电池 (Photovoltaic) 、平板显示 (FPD) 和科研 (R&D) 等。

作为国内深耕半导体湿法设备、全自动晶圆倒角机、全自动刷片机、干燥机、化学品供给系统等设备制造商, CGB始终严格按照国际质量管理体系标准进行全方位和全过程的质量控制, 同时注重持续改进及创新。近年来, 荣获北京市创新型中小企业、北京市知识产权试点单位、国家高新技术企业、北京市“专精特新”中小企业等称号。未来, 我们将不断提升自主创新能力及核心竞争力, 为客户提供更加优化完善的技术服务和专业定制化解决方案。

### 北京华林嘉业科技有限公司

Beijing CGB Technology Co.,Ltd

服 务 热 线 : 400-650-7658

官 网 网 址 : <http://www.cgbtek.com>

总 部 地 址 : 北京市经济开发区科创十三街18号院30号楼

华东服务中心: 无锡市新吴区IC设计大厦 B1003-1004

北方制造基地: 河北·廊坊市·香河机器人产业港·3期A栋

(华东/海外区) 负责人: 139 1127 1076

(华南区) 负责人: 130 5158 6635

(西南/西北区) 负责人: 193 2206 6460

(华中区) 负责人: 180 1536 7016

(京津冀) 负责人: 130 5158 6631

(大项目部) 负责人: 139 1029 7918

(MEMS专区/山陕区) 负责人: 180 1239 7806

(技术支持) 负责人: 139 1127 9276

# 液相法取代 PVT 只是时间问题

“成本”二字，像一把达摩克利斯之剑悬在整个碳化硅产业头顶。无论下游车企，还是AI数据中心厂商，以及AR眼镜及先进封装领域，都在等一个能把大尺寸碳化硅晶片价格快速降下来的技术方案。目前，碳化硅单晶生长主要有三种方法：物理气相传输(PVT)、液相法和高温化学气相沉积(HTCVD)。在这场技术竞赛中，液相法正逐渐崭露头角，而其取代PVT似乎只是时间问题。

## 一、PVT的现状与局限

PVT技术是目前碳化硅材料生长的主流方法。自20世纪80年代开始产业化以来，PVT已经走过了四十多年的发展历程。它的技术成熟度高，生产工艺相对稳定，是目前大多数碳化硅生产企业所采用的技术路线。然而，随着技术的发展，PVT的局限性也逐渐显现出来。

首先，PVT技术的核心问题是制造成本高。尽管经过多年的发展，PVT技术已经在一定程度上降低了生产成本，但其成本仍然较高。这主要是由于PVT技术在原材料利用率、良率和生长效率上的限制。PVT技术需要在2300度高温下进行，这导致了能源消耗大，生产成本难以进一步降低。此外，PVT技术在生长p型晶体时存在困难，这限制了碳化硅材料在更高电压、更高功率应用场景中的使用。

其次，PVT技术在生长高品质碳化硅晶体方面也面临挑战。尽管PVT技术已经取得了显著的进步，但在晶体质量上仍然存在很多问题，如晶体微管无法消除、位错及层错缺陷密度高、应力大等。这些问题直接影响了下游器件的性能和可靠性，限制了碳化硅材料在高端应用领域的进一步拓展。

## 二、液相法的优势与潜力

液相法作为一种新兴的碳化硅材料生长技术，近年来受到了越来越多的关注。液相法具有许多独特的优势，使其在未来的碳化硅材料生产中具有巨大的潜力。

首先，液相法在生长高品质碳化硅晶体方面具有显著优势。液相法通过在相对较低温度的溶液中进行晶体生长，能够更好地控制晶体生长的环境和条件（近平衡态），从而生长出高质量、低缺陷和低应力的碳化硅晶体。这对于提高下游器件的性能和可靠性具有重要意义。

其次，液相法在生长厚晶体方面具有独特的优势。液相法采用顶部籽晶提拉法，能够向上提拉生长晶体，因此没有PVT法生长空间受限的问题。目前，液相法已经能够生长出近30毫米厚的碳化硅晶体，未来有望进一步突破厚度限制，达到60毫米甚至更厚。

此外，液相法在生产P型碳化硅衬底方面具有独占性优势。低阻P型碳化硅衬底是传统PVT技术难以生产的，而液相法则能够轻松实现。这为液相法在碳化硅材料市场中开辟了一个独特的细分领域，为其未来的市场拓展奠定了基础。

## 三、液相法与PVT的合作与竞争

尽管液相法具有许多优势，但在现阶段，它与PVT仍然存在一定的合作空间。液相法可以通过提供高品质的籽晶来助力PVT生长更高品质的晶体。这对于PVT技术在短期内提升晶体质量及良率具有重要意义。然而，随着液相法技术的不断进步，其厚度生长能力的突破将使其逐渐具备取代PVT的潜力。

在未来三到五年内，液相法有望与PVT并存。在这段时间内，液相法将不断提升自身的技术水平，逐步扩大市场份额。而PVT技术则将通过优化生产工艺、提高生产效率等方式来保持其市场地位。然而，从长远来看，液相法取代PVT只是时间问题。随着液相法在厚度生长突破、晶体质量及落地产能提升等方面的优势逐渐显现，其在碳化硅材料市场中的份额将不断扩大，最终取代PVT成为主流技术。技术更替从不讲情怀，只算成本账。当液相法把“高品质”与“低成本”同时写进量产公式，PVT四十年的荣光便注定成为历史注脚。

### 社长 Publisher

麦协林 Adonis Mak

adonism@actintl.com.hk

### 荣誉顾问 Honorary advisor

郝跃院士 Academician Hao Yue

### 主编 Editor in Chief

陆敏 Min Lu

MinL@actintl.com.hk

### 出版社 Publishing House

雅时国际商讯 ACT International

香港九龙 B,13/F, Por Yen Bldg,

长沙湾青山道478号 478 Castle Peak Road,

百欣大厦 Cheung Sha Wan,

13楼B室 Kowloon, Hong Kong

Tel: (852) 2838 6298

Fax: (852) 2838 2766

### 北京 Beijing

Tel/Fax: 86 10 64187252

### 上海 Shanghai

Tel: 86 21 62511200

Fax: 86 21 52410030

### 深圳 Shenzhen

Tel: 86 755 25988573

Fax: 86 755 25988567

### 武汉 Wuhan

Tel: 86 27 82201291

### UK Office

Angel Business Communications Ltd.

6 Bow Court,

Fletchworth Gate,

Burnsall Road, Coventry,

CV56SP, UK

Tel: +44 (0)1923 690200

Chief Operating Officer

Stephen Whitehurst

stephen.whitehurst@angelbc.com

Tel: +44 (0)2476 718970

ISSN 2789-2735

© 2025 版权所有 翻印必究

# 芯联集成与理想汽车碳化硅产品量产交付

据芯联集成官微消息，近日，芯联集成与理想汽车举办合作伙伴交流会暨 BAREDIE 晶圆下线仪式，这标志着双方在碳化硅产品领域的深度合作取得了重大阶段性成果。

据悉，自 2024 年 3 月正式签署战略合作框架协议以来，两家公司在碳化硅技术上展开了全面且深入的合作。历经一年多的紧密协作，由理想汽车设计开发、芯联集成代工量产的碳化硅产品现已开启量产交付。

此次量产交付的碳化硅产品，标志着双方战略协同迈入新阶段，也是理想纯电战略落地的关键一环。未来，该产品

将在理想 i 系列纯电车型上搭载。该碳化硅产品在综合性能方面表现卓越，尤其是在导通电阻、应用结温等方面较市场主流产品展现出更大优势，有助于提升车辆补能效率及续航里程。

芯联集成董事长、总经理赵奇表示，双方共创出“用户需求牵引 + 技术针对研发”的合作模式，不仅助力双方研发团队联合攻关，突破高温 KGD 检测等关键技术瓶颈，也跑通了从需求定义到量产顺利落地的全链路环节，有效地提升了研发效率。

## Imec 推出 300 毫米 GaN 晶圆计划

AIXTRON、GlobalFoundries、KLA Corporation、Synopsys 和 Veeco 作为首批合作伙伴加入 imec 的 300mm 氮化镓晶圆电力电子项目

比利时研究和创新中心 Imec 宣布，AIXTRON、GlobalFoundries、KLA Corporation、Synopsys 和 Veeco 成为其 300 毫米 GaN 开放式创新计划的首批合作伙伴，该计划适用于低压和高压电力电子应用。该计划是 imec 关于 GaN 电力电子的工业联盟计划 (IIAP) 的一部分，旨在开发 300mm GaN 外延生长以及低压和高压 GaN HEMT 工艺流程。使用 300mm 衬底不仅可以降低 GaN 器件的制造成本，还可以开发更先进的电力电子器件，例如用于 CPU 和 GPU 的高效低压负载点转换器。

Imec 氮化镓电力电子项目研究员兼项目总监 Stefaan Decoutere 表示：“过渡到 300 毫米晶圆的好处不仅仅是扩大生产规模和降低成本。我们兼容 CMOS 的 GaN 技术现在可以使用 300 毫米最先进的器件，这将使我们能够开发更先进的基于 GaN 的功率器件。例如，用于负载点转换器的扩展低压 p-GaN 栅极 HEMT，支持 CPU 和 GPU 的节能配电。”

作为 300mm GaN 计划的一部分，将首先使用 300mm Si(111) 作为衬底，为低压应用 (100V 及以上) 建立横向 p-GaN HEMT 技术平台基准。为此，以 p-GaN 蚀刻和欧姆触点形成为中心的工艺模块工作正在进行中。后续，高压应用成为目标。对于 650V 及以上，开发使用 300mm 规格和 CMOS 兼容的 QST 工程基板（一种具有多晶 AlN 磁芯的材料）。在开发过程中，对 300 毫米晶圆弓形及其机械强度的控制是首要关注的问题。

300mm GaN 计划的推出是在成功的 300mm 晶圆处理测试和掩模组开发之后推出的。Imec 预计到 2025 年底，其

洁净室将安装完整的 300 毫米开发设备。Stefaan Decoutere 补充道：“300 毫米氮化镓开发的成功还取决于建立强大的生态系统并共同推动从 300 毫米氮化镓增长和工艺集成到封装解决方案的创新的能力。因此，我们很高兴地宣布 AIXTRON、GlobalFoundries、KLA Corporation、Synopsys 和 Veeco 成为我们 300 毫米氮化镓开放研发计划的首批合作伙伴，并希望尽快欢迎更多合作伙伴。因为开发先进的氮化镓电力电子器件需要设计、外延、工艺集成和应用之间的紧密耦合——事实证明，这种耦合对于我们在 200 毫米氮化镓方面的开创性工作至关重要。”

基于氮化镓的快速电池充电器的市场采用已经凸显了氮化镓技术在功率转换方面的颠覆性潜力。外延生长、器件和 IC 制造、可靠性和系统级优化方面的不断进步正在为新一代紧凑、轻质和节能的电力电子设备铺平道路，这些电力电子器件的性能优于传统的硅基解决方案。应用范围从电动汽车中的车载充电器和 DC/DC 转换器到电信基础设施和人工智能数据中心的太阳能逆变器和配电系统，氮化镓创新正在推动全球脱碳、电气化和数字化工作。

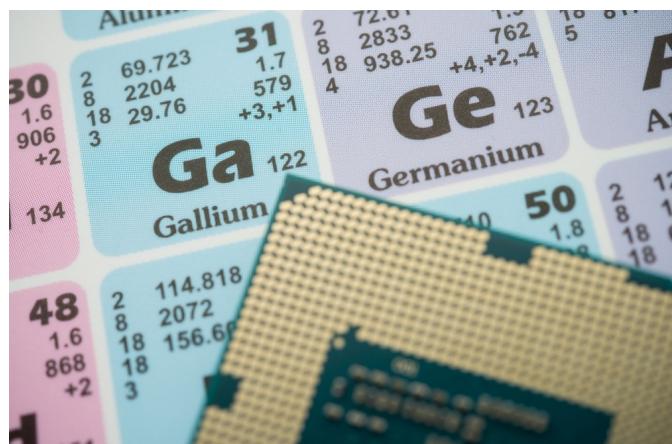

# 美国能源部拟资助其国内镓生产

TRACE-Ga 计划旨在协助建立安全、独立的美国镓供应链

美国能源部 (DOE) 化石能源和碳管理办公室宣布了关于镓回收和先进关键材料提取技术 (TRACE-Ga) 计划。

该计划旨在帮助美国建立安全独立的国内镓供应链。镓是用于军事、电力应用、通信等领域的化合物半导体关键材料。

该计划支持从美国金属加工原料中回收镓的经济可行的创新技术，以加强美国关键矿产供应链。

根据新闻公告，TRACE-Ga 将由 ENERGYWERX (DOE 的合作伙伴关系中介机构) 与美国能源部 (DOE) 合作管理，旨在“扩大 DOE 与创新组织和非传统合作伙伴的合作，促进能源解决方案的快速开发、扩展和部署”。

未来项目是关于测试和验证原型技术，计划目标是通过

至少 14 天的连续运行，在真实的金属工业加工流程中生产至少 50 公斤纯镓。项目目标是验证一个能够每年至少生产 1 公吨镓的原型。

## 英诺赛科为英伟达开发 800V GaN 电源方案

10 月 14 日，氮化镓 (GaN) 功率器件制造商英诺赛科在港交所公告，公司正与英伟达展开深度合作，共同开发支持 800V 直流 (800 VDC) 电源架构的全氮化镓 (GaN) 电源解决方案。这一合作旨在为新一代“人工智能工厂”(AI Factories) 提供更高能效、更高功率密度的供电系统，助力数据中心实现绿色低碳转型，应对 AI 算力爆发带来的能源挑战。

随着生成式 AI、大模型训练和推理应用的迅猛发展，全球数据中心正加速向“AI 工厂”演进。英伟达在其 GTC 大会上多次强调，AI 数据中心不再是传统服务器集群的简单扩展，而是集成了数万颗 GPU、高速互连网络与海量存储的超级计算中枢。然而，这种前所未有的算力密度也带来了巨大的能源压力。

据估算，一座大型 AI 数据中心的功耗可达数十甚至上百兆瓦，相当于一座中小型城市的用电量。在如此高负载下，传统基于硅 (Si) 基器件的 48V 或 54V 低压直流供电架构已显疲态：转换效率低、能量损耗大、散热需求高、占用空间多，严重制约了系统的整体能效与可扩展性。

英伟达 CEO 黄仁勋就曾指出，AI 的未来不仅取决于算力，更取决于能源效率。我们必须重新思考整个数据中心的架构，从芯片到系统，再到供电网络。

800VDC 机架电源架构将在人工智能数据中心领域实现了重大突破，它不仅能显著提升效率与功率密度，还能有效降低能耗需求，并减少二氧化碳的排放量。这一技术变革，

与电动汽车行业从 400V 向 800V 的跨越式升级颇为相似，可使电流降低 16 倍，从而大幅减少 I<sup>2</sup>R 损耗并最大限度降低对铜材的需求。

除了向 800V 机架电源过渡外，该架构还要求在 800V 到 1V 的电压转换中实现超高功率密度和超高效率。而只有氮化镓功率器件 (GaN) 能够同时满足这些严苛要求。

英诺赛科与英伟达的合作，正是针对这一痛点，提出了一套革命性的解决方案：采用 800V 高压直流 (800 VDC) 配电架构，结合全氮化镓 (GaN) 功率器件，构建新一代高效电源系统。该解决方案能够在提升效率、功率密度、可靠性和环保指标的同时，显著压缩系统体积和成本，是面对 AI 大算力、数据中心以及高压电动汽车充电等场景的关键技术路径。

其中，氮化镓作为第三代半导体材料，具备高频、高效率、低导通电阻和耐高温等特性，是实现高压高效转换的理想选择。全 GaN 电源系统可在 MHz 级高频下工作，显著缩小电感、变压器等无源元件体积，从而大幅提升功率密度——单位体积内可提供的电力输出。

英诺赛科凭借其全球领先的 8 英寸 GaN-on-Si 制造平台，已实现高性能 GaN 器件的规模化量产。此次合作中，英诺赛科将提供基于其 InnoGaN® 技术的高压 GaN FETs，为 800 VDC 电源架构提供全 GaN 电源解决方案，构建全链路高效转换系统。

受这一消息的影响，英诺赛科 (02577) 高开近 15%。

# 牵引逆变器安装量增长 19%

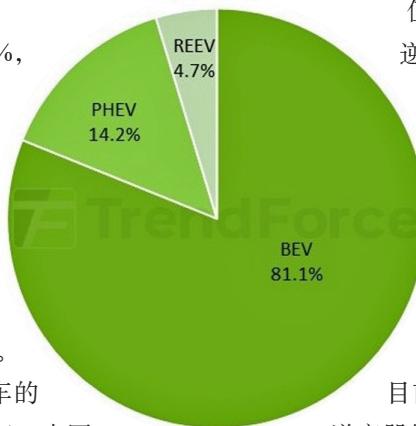

TrendForce 最新报告《全球电动汽车逆变器市场数据》显示，受纯电动汽车 (BEV) 销售强劲推动，2025 年第二季度全球电动汽车牵引逆变器安装量达到 766 万台，同比增长 19%。

纯电动汽车 (BEV) 占安装量的 52%，自 2024 年第一季度以来再次占据领先地位，并超过了混合动力汽车（包括混合动力电动汽车 (HEV)、插电式混合动力汽车 (HEV) 和增程式电动汽车 (REEV)）的总份额。

在一级供应商中，比亚迪和电装分别以 17% 和 14% 的市场份额领先市场。受益于纯电动汽车和可再生能源电动汽车的强劲销售，华为市场份额从 3% 提升至 4%。中国企业日益占据市场主导地位；除了比亚迪和华为之外，汇川技术也稳居前五大供应商之列。

2025 年第二季度，SiC 逆变器的渗透率达到了 17%。尽管目前仍主要集中在纯电动汽车 (BEV) 领域，但其应

用范围正在扩展至插电式混合动力汽车 (PHEV) 和纯电动 (REEV)，这两款车型合计占据了 SiC 逆变器安装量的近 19%，且全部由中国汽车制造商贡献。

值得注意的是，目前 20% 的 REEV 主驱动逆变器采用 SiC，仅次于 31% 的纯电动汽车 (BEV)。TrendForce 表示，不断增长的 REEV 需求并未取代其他动力系统类型，反而扩大了整体逆变器市场，这使得 REEV 成为 SiC 应用的关键催化剂。

TrendForce 指出，随着 REEV 的成熟，将有助于实现 SiC 逆变器市场的多元化，从而减少对纯电动汽车的过度依赖。目前中国仍然是 PHEV、REEV 和纯电动汽车逆变器的最大市场，英飞凌等公司正加大在中国的产量，以抓住增长机遇。总体而言，中国强劲的电动汽车生态系统正在改变整个供应链的影响力平衡，使中国外的汽车制造商更难缩小差距。

## 与Evatec携手， 净享新能源的蓝天白云

在功率器件中的镀膜技术领域，

Evatec助您开辟新径

从300毫米硅片加工到碳化硅(SiC)或氮化镓(GaN)宽禁带(WBG)应用，Evatec是您在功率器件中镀膜工艺的可靠伙伴。

凭借减薄/键合晶圆的无损安全传输，结合晶圆应力与温度管理，确保您的生产始终精准无误。

访问 [evatecnet.com/markets/power-devices](http://evatecnet.com/markets/power-devices)

了解如何提升您的生产效能，或通过

[evatecnet.com/about-us/sales-service](http://evatecnet.com/about-us/sales-service)

联系当地办事处

意发薄膜科技(上海)有限公司，

电话:+86 21 6019 1660

邮箱:infochina@evatecnet.com

Evatec — 半导体镀膜专家

先进封装、半导体、光电子、光子学

[www.evatecnet.com](http://www.evatecnet.com)

半导体镀膜设备和工艺

硅片, 碳化硅和氮化镓 ↑

增加产能一路向前 ↑

# Axcelis 与 Veeco 宣布合并

近期，Axcelis Technologies 股份有限公司和 Veeco Instruments 股份有限公司宣布，两家公司已达成最终协议，以全股合并的方式合并，合并后的公司预计企业价值约为 44 亿美元。

该交易预计将于 2026 年下半年完成，但须经两家公司股东批准，获得所需的监管批准，并满足其他惯例成交条件。

交易完成后，合并后的公司总部将设在马萨诸塞州贝弗利。

按收入计算，此次合并将创建美国第四大晶圆制造设备供应商，提供有意义的规模和资源，以更好地在全球半导体设备价值链中竞争。合并后的公司将提供差异化和全面的产品组合，涵盖离子注入、激光退火、离子束沉积、先进的封装解决方案和 MOCVD。

资料显示，Axcelis 总部位于马萨诸塞州贝弗利，致力于通过离子注入系统的设计、制造和完整生命周期支持来开发使能工艺应用，这是 IC 制造工艺中最关键和使能的步骤之一。Veeco 则是一家创新的半导体工艺设备制造商，业务包括激光退火、离子束、金属有机化学气相沉积 (MOCVD)、单晶片蚀刻和清洁以及光刻技术。

# 格力电子×电子科技大学：碳化硅器件联合研究中心揭牌

10 月上旬，“碳化硅功率半导体器件联合研究中心”揭牌仪式在珠海举行。珠海格力电器股份有限公司总裁助理、珠海格力电子元器件有限公司总经理冯尹，电子科技大学功率集成技术实验室（PITEL）负责人、集成电路研究中心主任张波，及双方多位专家、教授和技术管理人员出席仪式。此次中心的成立，标志着格力电子与电子科技大学在产学研融合与功率半导体技术创新领域迈出坚实一步。

## 校企携手，以创新应对“卡脖子”挑战

珠海格力电子元器件有限公司副总经理张鹏在致辞中指出，联合研究中心的成立，是高校与产业科研深度融合的重要举措。电子科技大学在集成电路与微电子领域拥有雄厚科研实力，而格力电子坚持自主投入，聚焦核心技术攻关，致力于解决“卡脖子”难题。双方将以优势互补为基础，共同在功率半导体领域实现技术突破。

电子科技大学张波教授强调，功率半导体是实现绿色智能化和“零碳”目标的关键支撑，而碳化硅作为下一代核心材料，已在成本、性能与应用领域取得显著进展。此次合作不仅聚焦技术创新，更着眼于国家与人类可持续发展的宏观目标。校方将为联合研究中心提供科研资源与人才支持，助力格力电子在功率半导体领域开辟新增长极。

活动现场，双方共同为“碳化硅功率半导体器件联合研究中心”揭牌。

电子科技大学张有润教授介绍，双方在过去两年的合作中，已在平面器件、沟槽技术与超结结构等方向取得阶段性成果。未来，研究中心将聚焦车规级可靠性、先进模块封装、IPM 驱动等关键技术，推动科研成果快速转化为产业生产力，助力中国功率半导体产业高质量发展。

格力电子技术代表罗博士表示，双方合作是“产业需求”与“学术优势”的深度融合，将围绕碳化硅全链条技术攻关，推动成果转化与应用拓展，并建立常态化交流、定期技术研讨和联合人才培养三大机制，携手开拓碳化硅器件蓝海市场。

冯尹在总结中表示，格力电器已形成多元化、科技型全球制造体系，在碳化硅功率芯片方面具备强劲内生需求。双方理念契合，可依托联合研究中心共同攻克技术瓶颈、拓展市场边界、共促科研成果落地。他强调，唯有以自主创新为驱动、以开放合作为动力，才能实现共创共赢，助力产业腾飞。

# 采用液态镓靶溅射制备的简并态 GaN 的低场传输特性与散射机制 研究

**Philipp Doering** 博士（弗劳恩霍夫应用固体物理研究所 IAF）与 **Thomas Tschirky**（Evatec 高级科学家）共同探讨了液态镓靶材溅射工艺的研究进展。

## 摘要

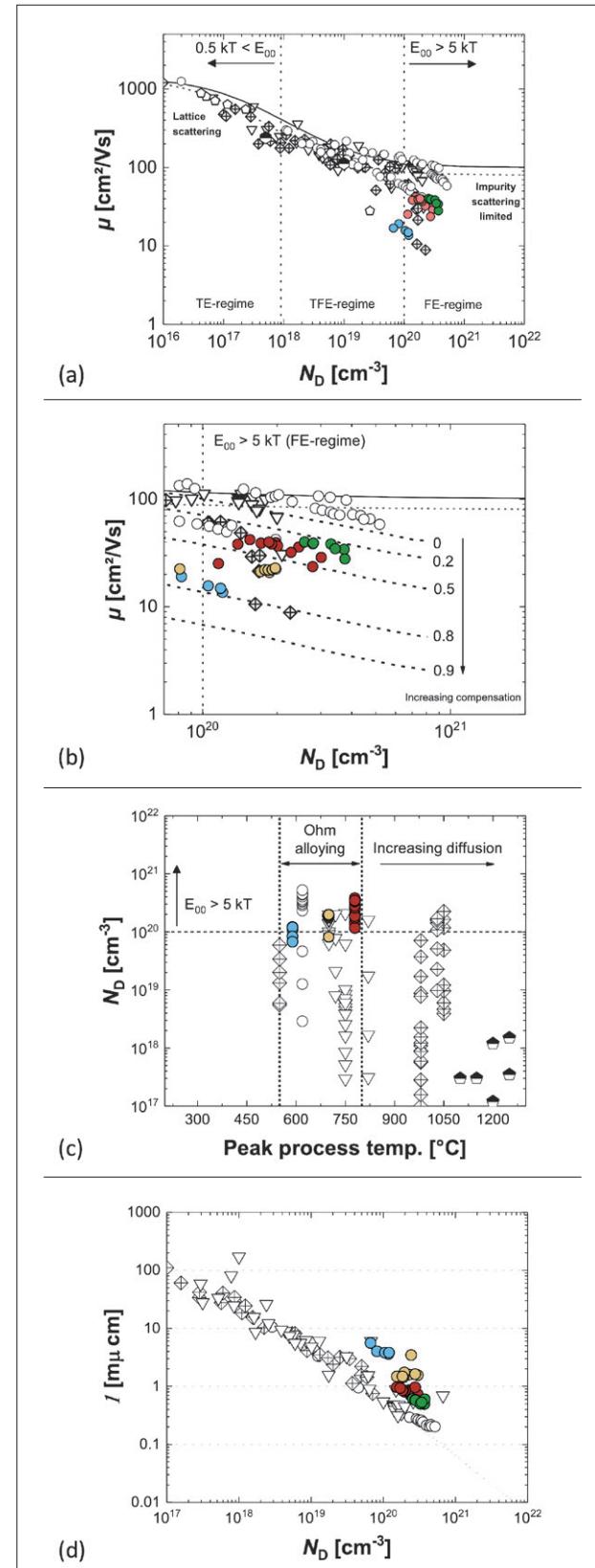

本工作采用液态镓靶共溅射方法制备了简并 n 型氮化镓（GaN）薄膜，并系统研究了其低场输运特性与散射机制。在低于 800°C 的工艺温度下，实现了高达  $3 \times 10^{20} \text{ cm}^{-3}$  以上的掺杂浓度，电阻率低于 0.5 mΩ·cm。变温霍尔测量（300–550 K）结果表明，薄膜表现出典型的简并半导体特征，电子迁移率与施主浓度在测试温区内变化微弱。进一步分析表明，电离杂质散射是限制载流子迁移率的主导机制，高温区域则存在一定程度的极性光学声子散射贡献。研究排除了位错与晶界散射对测量迁移率的显著影响。该结果证明，溅射法作为一种低温、高产量、可扩展的 n 型 GaN 制备路径，具有重要的应用潜力。

为满足下一代无线通信系统对数据速率日益增长的需求，采用更高频段以提升系统效率与带宽已成为必然趋势。基于氮化镓的低噪声高功率放大器及其与硅基 CMOS 工艺的先进异质集成技术，在这一发展中具有关键意义。然而，为实现更高截止频率而进一步缩小栅长（LG）时，必须有效降低器件中的寄生电阻。

对于采用高铝含量势垒层的高电子迁移率晶体

管（HEMT）及多沟道器件而言，其接触电阻主要受限于金属 - 半导体界面的固有势垒高度。为实现实金属 - 半导体界面处的最低电压降，理想的电流传输机制应完全由隧穿效应主导。通过移除 AlGaN 势垒层和 / 或将接触区下方区域转变为 n 型掺杂结构，是促使电子在高铝含量条件下从热离子发射转变为场发射、进而有效穿越势垒进入二维电子气（2DEG）通道的关键途径。

原型溅射模块中透过晶圆支架观察液态镓靶材

表1：共溅射n型GaN薄膜的结构特性： $t_{n\text{-GaN}}$ —硅掺杂GaN层厚度， $T_H$ —标称加热器温度，GR—生长速率，rms—均方根，FWHM—00.2衍射峰半高宽。

| 样品 | 基板      | n型氮化镓厚度 | 生长温度  | 生长速率     | 粗糙度Rms  | XRD (00.2)<br>FWHM |

|----|---------|---------|-------|----------|---------|--------------------|

| A  | 氮化镓/蓝宝石 | 150 nm  | 700°C | 0.9 nm/s | 0.58 nm | 0.188°             |

| B  | 氮化镓/蓝宝石 | 150 nm  | 590°C | 0.9 nm/s | 0.38 nm | —                  |

| C  | 氮化镓/蓝宝石 | 150 nm  | 800°C | 0.9 nm/s | 0.91 nm | 0.134°             |

| D  | 蓝宝石     | 1050 nm | 800°C | 0.6 nm/s | 21.6 nm | 0.437°             |

然而，实现完全基于场发射电流传输所需的高掺杂浓度( $ND > 1 \times 10^{20} \text{ cm}^{-3}$ )仍面临挑战，主要原因在于高掺杂易导致晶体质量下降。此外，在大尺寸晶圆上采用低温工艺不仅有助于保护HEMT结构中AlGaN/GaN界面的完整性，也在硅基平台上直接实现III族氮化物(光)电子器件的异质集成提供了可能。

本研究系统分析了通过硅与液态镓靶共溅射技术在4英寸蓝宝石衬底上制备的重掺硅氮化镓(GaN)薄膜的输运特性。实验结果表明，所制备薄膜具有极高的有效施主浓度( $ND > 3 \times 10^{20} \text{ cm}^{-3}$ )。在800°C与590°C的生长温度下，分别实现了低于0.5 mΩ·cm和3.5 mΩ·cm的电阻率。高硅掺杂条件下，载流子迁移率主要受电离杂质散射机制限制。在补偿比θ约低于0.2的条件下，即使溅射制备的GaN薄膜施主浓度 $ND > 1 \times 10^{20} \text{ cm}^{-3}$ ，其施主-受主补偿比仍能保持基本恒定。这一特性与金属有机化学气相沉积(MOCVD)和分子束外延(MBE)工艺中报道的变化规律存在明显差异。变温霍尔测量显示，载流子浓度与迁移率随温度升高无明显变化，表明材料发生了从半导体特性向金属特性的莫特转变。在较低生长温度( $\leq 800^\circ\text{C}$ )下获得的载流子浓度与电阻率数据，显著优于已报道的MOCVD工艺制备的薄膜性能。本研究证实了液态镓靶溅射氮化镓作为一种替代性制备路径的可行性。该工艺兼具高载流子密度与良好的工艺扩展性，适用于4英寸及以上尺寸晶圆制造，在未来射频及光电器件(如隧道结)的氮化镓基工艺集成中具有重要应用潜力。

当前先进接触工艺的研究重点，主要聚焦于开发CMOS兼容、无金化及低温欧姆接触技术，并满足高铝组分AlGaN及新型Al(Sc)N基HEMT器件对n型GaN外延再生长工艺的高度集成需求。目前，多种技术途径已成功实现高n型掺杂GaN薄膜的制备，包括硅离子注入、分子束外延(MBE)、金属有机化学气相沉积(MOCVD)掺杂(硅/锗)、脉冲激光沉积(PLD)，以及采用固态镓靶材(掺杂硅/锗/锡/氧)的反应脉冲溅射(PVD)等。其中，硅离子注入技术虽已应用于GaN器件，但其载流子浓度通常难以突破 $1 \times 10^{19} \text{ cm}^{-3}$ ，且需通过高温退火修复晶格损伤。MBE再生长欧姆接触层得益于较低的生长温度，目前被视为优选方案，但在大尺寸

扩展、量产效率与均匀性控制方面仍存在挑战。

采用流动调制外延技术虽可在低温下实现MOCVD再生长并降低生长速率，但在550°C条件下载流子密度难以突破 $5 \times 10^{19} \text{ cm}^{-2}$ ，且受限于非选择性生长模式的缺失，难以避免生长速率不均匀的问题。传统实现高生长速率的工艺通常需在更高温度( $> 950^\circ\text{C}$ )下进行。相比之下，反应溅射工艺在300至600纳米厚度薄膜中成功实现了高载流子密度与高迁移率的结合。然而，该工艺所使用的固态镓靶需依赖强力冷却以维持其固态特性，随着晶圆直径增大，冷却系统设计更趋复杂。此外，固态靶材(如陶瓷镓)中的杂质浓度也难以精确控制。采用液态镓靶则可有效避免上述问题：它不仅省去了维持固态所需的复杂冷却系统，还具备靶材填充简便、生长过程中无飞溅坑等优势。与陶瓷镓靶相比，液态靶材更易于扩展至2英寸以上大尺寸晶圆，同时能够显著降低非故意掺杂水平。

在4英寸蓝宝石衬底上进行了导电薄膜的沉积实验。首先采用金属有机化学气相沉积(MOCVD)制备了三个样品(A-C)，通过引入掺铁缓冲层使GaN层呈现半绝缘特性，并在顶层沉积200 nm非故意掺杂GaN层以补偿铁偏析效应。样品A、B和C的方块电阻经非接触涡流法测量显示，其阻值均高于100 kΩ/sq，达到该测量装置的上限。随后使用经工艺优化的Evatec CLUSTERLINER 200II设备，通过硅靶与液态镓靶共溅射工艺，在MOCVD生长的GaN基底上沉积了150 nm硅掺杂GaN薄膜，标称生长温度分别为590°C、700°C和800°C。另制备样品D作为对照，直接在蓝宝石衬底上溅射生长GaN:Si薄膜。通过X射线衍射测量(002)面摇摆曲线，并采用双伪Voigt函数拟合获得半高宽(FWHM)值。分析假定强度较低的衍射峰对应于溅射掺杂硅的GaN相。MOCVD缓冲层的FWHM测得为0.064°。对于最低生长温度(590°C)的样品，由于第二衍射峰强度过低无法实现有效拟合，但仍可确认降低加热器温度会导致晶体质量出现轻微下降。

采用原子力显微镜(AFM)对薄膜表面形貌进行表征，通过均方根粗糙度(rms)分析表明，在最低生长温度下获得了最为光滑的表面。详细结构特性参数汇总于表1。

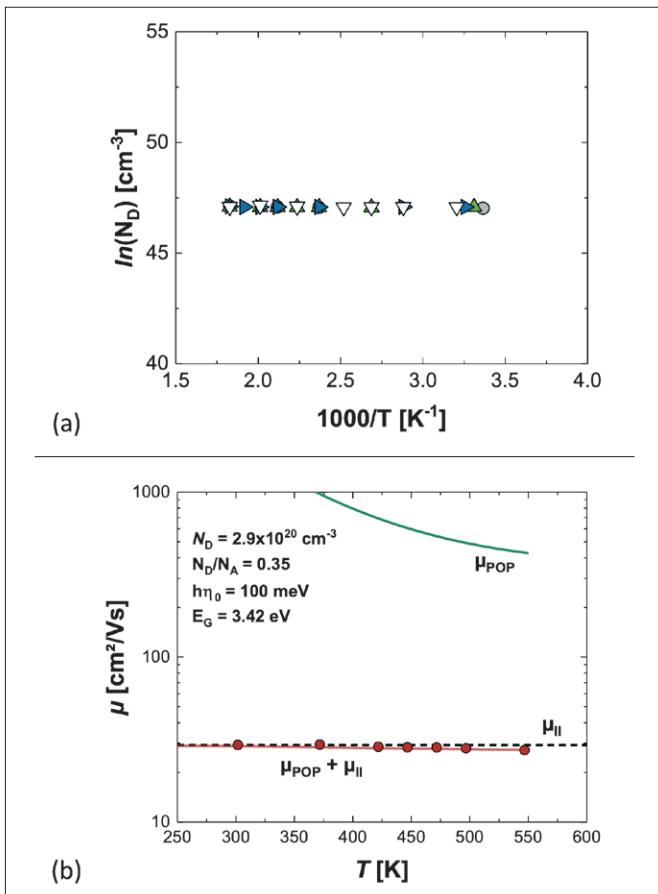

金属 - 半导体传输特性的理论模型——包括热电子发射(TE)、热场发射(TFE)与场发射(FE)——取决于特征能量 $E_{00}$ , 而该能量由接触区下方的载流子浓度决定, 其函数关系如下所示:

$$E_{00} = \frac{q\hbar}{4\pi} \sqrt{\frac{N_D}{\epsilon_r \left(\frac{m_{tun}^*}{m}\right)}}$$

其中,  $q$  为元电荷,  $\hbar$  为约化普朗克常数,  $\epsilon_r$  (9.5) 为氮化镓相对介电常数,  $m_{tun}$  为有效隧穿质量 ( $m_{tun}^*/m = 0.22$ )。我们采用简单的微分方法: 前端  $E_{00} \leq 0.5 \text{ kT}$ ; TFE:  $0.5 \text{ kT} \leq E_{00} \leq 5 \text{ kT}$  且  $E_{00} \geq 5 \text{ kT}$ 。为实现 FE 机制, 要求 GaN 施主浓度  $N_D > 1 \times 10^{20} \text{ cm}^{-3}$ 。采用室温霍尔测量表征低场输运特性。通过阴影掩模蒸发制备钛基欧姆接触, 并利用四端结构实现机械隔离。采用硅靶共溅射技术可在同一晶圆上实现硅浓度梯度, 具体取决于晶圆区域与硅靶的距离。因此, 可以在同一晶圆上测量多种载流子浓度及相应的载流子迁移率。所有样品的载流子密度范围为  $N_D = 6.7 \times 10^{19}$  至  $3.7 \times 10^{20} \text{ cm}^{-3}$ , 载流子迁移率  $\mu = 21$  至  $42 \text{ cm}^2/\text{Vs}$ 。实验结果显示(图 1), 随着加热器温度升高, 补偿比显著改善。所实现的载流子浓度不仅超越目前 MOCVD ( $N_D < 2.2 \times 10^{20} \text{ cm}^{-3}$ ) 和 MBE ( $N_D < 2 \times 10^{20} \text{ cm}^{-3}$ ) 工艺水平, 且生长温度更低(图 1c)。该浓度满足  $E_{00} \geq 5 \text{ kT}$  对应的  $N_D > 1 \times 10^{20} \text{ cm}^{-3}$  要求, 其高载流子浓度特性有助于解决微缩化 GaN HEMT 中因源极耗尽导致的线性度失真问题。

总体而言, 共溅射 GaN:Si 材料中可能存在多种散射机制共同作用, 但在高掺杂浓度条件下, 电离杂质散射预计占据主导地位。该散射过程与补偿比  $\theta = N_D/N_A$  的关系可由下式描述: 电离杂质散射与补偿比  $\theta = N_D/N_A$  的关系可表示为:

$$\mu_{II} = 3(\epsilon_0 \epsilon_r)^2 \left(\frac{h}{q}\right)^3 \left(\frac{n}{N_I}\right) \left(\frac{1}{m_F^*}\right) \left(\ln(1 + \beta_F^2) - \frac{\beta_F^2}{1 + \beta_F^2}\right)^{-1}$$

与:

$$\beta_F^2 = \frac{16 m_e^* \epsilon_0 \epsilon_r E_F^2}{3 q^2 h^2 n}$$

且  $N_I$  和  $m_F^*$  分别表示费米能级处的电离杂质浓度与有效质量, 其表达式为:

$$m_F^* = m_e^* \left(1 + \frac{6\alpha E_F}{E_g}\right)$$

随着

$$E_F = E_F^0 \left(1 + \frac{\alpha E_F^0}{E_G}\right)$$

和

$$E_F^0 = \left(\frac{h^2 (3\pi^2 n)^{2/3}}{2 m_e^*}\right)$$

图 1: (a) 不同制备方法中施主浓度与载流子迁移率的对比关系: 金属有机化学气相沉积(十字四分之一圆)、分子束外延(菱形)、氢化物气相外延(五边形)、反应溅射(灰色圆形)及硅离子注入(半填充六边形)。本研究中样本以彩色标识: A (黄色)、B (蓝色)、C (红色)、D (绿色)。实线与虚线表示基于 Schwierz 等人的 Caughey-Thomas 近似拟合结果; (b)  $E_{00} > 5 \text{ kT}$  条件下施主浓度  $N_D$  与迁移率  $\mu$  的对应关系; (c) 峰值工艺温度与实测施主浓度关系图, 图中同时标注了 AlGaN/GaN 欧姆接触合金化工艺的典型温度范围作为参考; (d) 载流子浓度与比电阻率的关联特性。

图2: (a) 样品C在三个不同测量位置的阿伦尼乌斯曲线; (b) 重掺杂GaN电子迁移率随温度的变化关系。图中同时给出了电离杂质散射( $\mu_{II}$ , 黑色曲线)与极性光学声子散射( $\mu_{POP}$ , 绿色曲线)的理论建模结果, 二者与实验数据(红色数据点)表现出良好的一致性。

此处,  $\alpha$  (0.64) 和  $m_e^*$  ( $0.22m_e$ ) 分别表示非抛物线导带系数 (满足  $\alpha = 1/(m_e^*/m_e)$ ) 2 和电子有效质量。如图 1b 所示, 当 MOCVD 与 MBE 制备的样品中施主浓度  $N_D > 1 \times 10^{20} \text{ cm}^{-3}$  时, 观测到较高的载流子补偿比  $\theta = N_D/N_A$ , 导致迁移率显著下降, 从而限制了可实现的载流子密度与比电阻率性能。本研究中, 共溅射薄膜在较高生长温度下, 即使  $N_D$  达到  $3.7 \times 10^{20} \text{ cm}^{-3}$ , 其补偿比仍保持相对稳定; 而在较低生长温度下 ( $\theta = 0.8$ ), 补偿比明显上升, 这可能源于晶体质量退化, 例如镓空位等点缺陷密度增加。该推测与 XRD 中观察到的第二 (002) 衍射峰半高宽增大及强度减弱相一致。目前, 仅见采用固态镓靶在 2 英寸衬底上反应溅射制备的薄膜报道, 其在相同载流子密度范围内具备更高迁移率。相关数据甚至高于  $\theta = 0$  时的理论杂质散射极限, 文献中将其归因于对电子有效质量的低估, 但未作深入探讨。经计算得到的比电阻率与文献数据对比如图 2 所示。本研究在最高生长温度 ( $800^\circ\text{C}$ ) 下获得最低电阻率  $\rho < 0.5 \text{ m}\Omega\cdot\text{cm}$ , 接近不同生长方法中的最优报道值。如前所述, 随着补偿比上升, 生长温度降低将导致电阻率升高, 样品 A 在  $590^\circ\text{C}$  时的最低电阻率为  $3.5 \text{ m}\Omega\cdot\text{cm}$ 。实验测得的载流子浓度远超理论预期, 达到了实现金属导电行为所需的掺杂水平。为验证溅射 GaN 薄膜是否发生莫特

转变, 在  $300\text{--}575 \text{ K}$  温度区间进行了变温霍尔测试。电子浓度与迁移率在整个温区内未见明显变化, 表明硅掺杂 GaN 薄膜呈现典型的简并半导体特性。温度相关的极性光学声子散射通过下式建模:

$$\mu_{POP} = \frac{\epsilon_0 \epsilon_r \hbar}{e N m_F^*} \sqrt{\frac{\hbar}{2 m_F^* \omega_0 (1 + \hbar \omega_0 / E_G)}} \left( 1 - 5 \frac{k_B T}{E_G} \right)$$

其中  $\hbar \omega_0$  为光学声子能量 ( $100 \text{ meV}$ )。由于位错密度低于  $1 \times 10^{11} \text{ cm}^{-2}$  时, 其对掺杂浓度高于  $1 \times 10^{20} \text{ cm}^{-3}$  的横向迁移率影响可忽略, 因此未考虑位错散射的贡献。

基于在蓝宝石衬底上采用 AlN 成核层 MOCVD 生长的 GaN 模板 (即本工作所用模板) 通常具备极低位错密度, 且在后续溅射 GaN 过程中界面处未引入新生位错。对于溅射制备的 GaN 薄膜, 虽可推测晶界处存在散射效应, 但相关势垒应导致载流子迁移率或浓度呈现热激活特性, 而实验中并未观测到该现象。此外, 在高掺杂水平下, 大部分与晶界相关的陷阱态被填满, 势垒的高度和宽度均会降低。基于图 2b 所示, 通过应用 Matthiessen 规则并结合公式 (2) 与 (7), 成功实现了载流子迁移率温度依赖特性的拟合。仅发现  $\mu_{POP}$  的微弱贡献, 而  $\mu_{II}$  明显主导了样品中的整体低场散射。

本研究表明, 采用液态镓靶共溅射技术可成功制备重掺杂 n 型 GaN 薄膜。在低于  $800^\circ\text{C}$  的工艺温度下, 实现了超过  $3 \times 10^{20} \text{ cm}^{-3}$  的载流子浓度, 电阻率低于  $0.5 \text{ m}\Omega\cdot\text{cm}$ 。变温霍尔测量 ( $300\text{--}550 \text{ K}$ ) 证实材料发生莫特转变, 载流子浓度与迁移率在测试温区内保持稳定, 未出现明显变化。分析表明, 低场迁移率主要受电离杂质散射主导, 高温区间仅存在微弱的极性光学声子散射贡献, 同时排除了位错与晶界散射的显著影响。该结果证明, 溅射技术作为一种低温、高通量且具备良好扩展性的 n 型 GaN 再生长工艺, 具有重要的应用前景。CS

刚完成填充的液态镓靶材坩埚。

插图: 液态镓填充过程示意

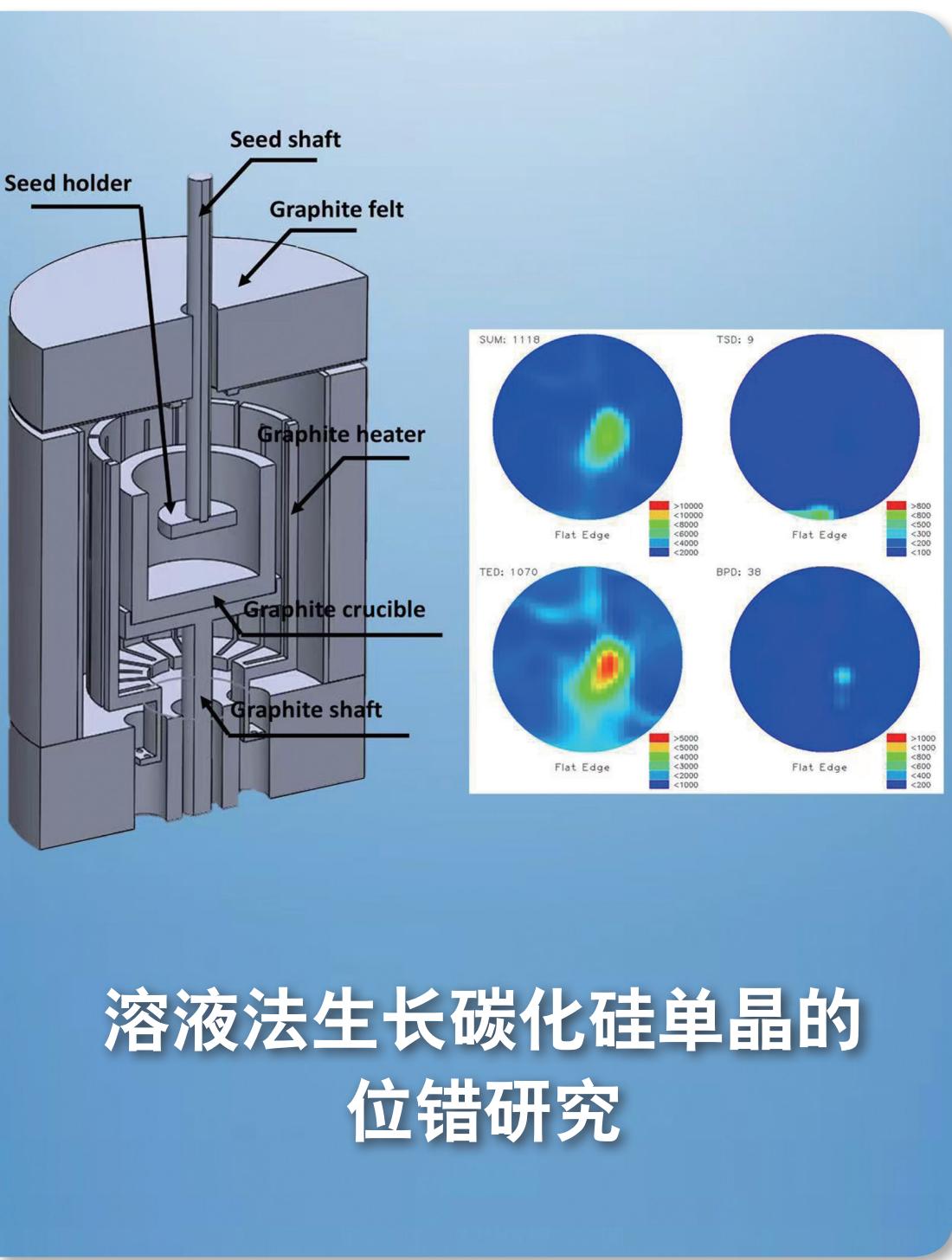

# 溶液法生长碳化硅单晶的位错研究

**摘要：**本文针对溶液法（SG）生长4H-SiC单晶过程中的位错增殖和转化问题展开研究，分析了贯穿螺位错（TSD）、贯穿刃位错（TED）、基面位错（BPD）等典型位错的形成与转化机制。通过实验研究了生长界面温度梯度大小、生长层有无气孔、扩径生长以及籽晶晶向等条件变化对晶体中位错数量的影响。结果表明，优化生长界面温度梯度、抑制气孔形成、实施扩径生长以及采用偏轴籽晶生长都可以显著降低晶体中的位错数量，提升单晶质量。

作者：常州臻晶半导体有限公司

## 引言

碳化硅是目前主流的第三代半导体材料，具有较高的热导率，击穿电场，电子漂移速率，可广泛应用于高压高功率电力电子器件。目前主流的碳化硅晶体生长方法主要物理气相传输法（PVT）、溶液法（SG）和高温化学气相沉积法（HTCVD）。PVT法经过长时间运用，技术已经成熟，但是其晶体质量，生长成本仍是二大关键难题。HTCVD法同样存在生产成本更高的问题，同时其采用的易燃易爆气体不利于可持续发展。SG法由于其生长温度低，位错密度小，原料成本低等天然优势成为目前大力发展的碳化硅单晶生长方法，并有望成为未来主流的产业化长晶技术。

目前4H-SiC的电力电子器件已在新能源汽车、数据中心、智能电网，轨道交通等领域得到广泛应用。尽管如此，商用6-8英寸4H-SiC单晶衬底中的位错密度仍然高达 $10^3\sim10^4\text{ cm}^{-2}$ <sup>[1]</sup>。衬底中如此高的位错密度会在外延过程中穿透或者部

分转变为其他类型的位错或是堆垛层错，并在外延表面形成不同形貌的表面缺陷，如三角形、胡萝卜缺陷等，从而影响器件的性能。表1是SiC位错对不同器件的影响情况汇总<sup>[2]</sup>。4H-SiC外延片中的位错作为载流子复合中心，增大漏电流，降低器件性能及使用寿命，该问题是目前限制4H-SiC应用的关键瓶颈之一。因此，理解4H-SiC中位错的基本性质，明确位错在碳化硅生长过程中的产生、增殖和转化机理，对于降低4H-SiC中位错密度从而提升4H-SiC单晶质量至关重要。

本文结合溶液法碳化硅单晶生长工艺，分析了生长过程中位错的增殖与转化规律，针对分析所得的关键问题，设计对比实验生长出晶体并获得晶片样品，对样品进行位错缺陷检测，研究了工艺条件及籽晶晶向选择等对晶体中位错数量的影响，提出液相法碳化硅单晶生长工艺优化方向以降低单晶中的位错数量。

表1：SiC位错对不同器件的影响<sup>[2]</sup>

| 器件类型   | BPDs                       | TEDs/TSDs          | MP                                   |

|--------|----------------------------|--------------------|--------------------------------------|

| MOSFET | $R_{on}\uparrow$<br>栅氧可靠性↓ | 栅氧可靠↓              | $I_{leak}\uparrow$<br>Limit $I_{op}$ |

| SBD    | $I_{leak}\uparrow$         | $I_{leak}\uparrow$ | $V_B\downarrow$                      |

| p-n二极管 | $R_{on}\uparrow$           | $V_B\downarrow$    | $I_{leak}\uparrow$<br>Limit $I_{op}$ |

| IGBT   | 栅氧可靠↓                      | $\tau\downarrow$   | Limit $I_{op}$                       |

备注： $V_B$ 击穿电压； $R_{on}$ 导通电阻； $I_{leak}$ 漏电流； $I_{op}$ 工作电流； $\tau$ 载流子寿命

## 1. 实验

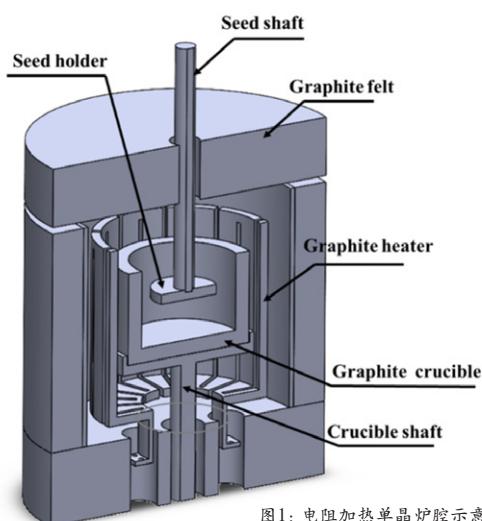

本实验使用本公司生产的商业化溶液法电阻炉 ZJ-R08 进行晶体生长实验，图 1 为该单晶炉热场示意图。将 Cr、Al 等助溶剂元素和硅料放入石墨坩埚中一同加热，经过多个学者研究证实 Cr 在提高溶液溶碳能力上有着显著作用<sup>[3-5]</sup>，而 Al 的添加可以很大程度降低晶体表面宏观台阶的高度<sup>[6-7]</sup>。该实验采用 6-8 英寸 4H-SiC 肾晶，实验过程中炉内充入氩气保护，加热助溶剂完全熔化形成溶液，达到温度后下降籽晶，籽晶表面接触溶液进行回溶，回溶结束开始单晶生长，生长时籽晶旋转速度 50rpm，生长温度 1800℃，生长 50h 后提拉单晶使其脱离溶液，随后缓慢降温冷却。对出炉晶体进行切片，经研磨和抛光后获得晶片，随后采用熔融的 KOH 和 Na<sub>2</sub>O<sub>2</sub> 混合物对晶片进行腐蚀处理，腐蚀温度 500℃，腐蚀时间 15min，清洗后得到检测样片。采用 Leica DM8000M 光学显微镜、谦视科技 LFMC-SiC 缺陷检测仪测试了样片的位错密度及分布。

图1：电阻加热单晶炉腔示意图

## 2. 溶液法生长碳化硅单晶过程中位错的转化和抑制

4H-SiC 晶体中有三种主要的位错：贯穿螺位错 (TSD)，贯穿刃位错 (TED) 和基面位错 (BPD)，此外 SiC 还有一种特有的微管 (MP) 缺陷，它是伯格氏矢量几倍于 TSD 的巨大螺位错。表 2 为 SiC 晶体中 TED, TSD, BPD 的方向及其伯格氏矢量方向<sup>[8]</sup>。TSDs 的伯氏矢量和位错方向平行，其通常沿着 <0001> 方向传播，当晶体中存在应力时，位错线会倾向于向能量更低的方向或是晶面弯曲。根据位错理论中伯格氏矢量守恒的基本原理，当位于 {0001} 基面的位错线发生弯曲时，其位错线方向与伯格氏矢量的关系会从原本的平行（对应螺型位错）转变为既不平行也不垂直的状态，位错随之转化为混合位错。此时，混合位错在基面上的滑移分量会导致原子偏离正常的堆垛序列，进而形成 Frank 型堆垛层错。

表2: SiC晶体中TED, TSD, BPD的方向及其伯格氏矢量方向<sup>[8]</sup>

| 位错类型 | 伯格氏矢量            | 位错线方向                            |

|------|------------------|----------------------------------|

| TSD  | $n<0001>(n=1,2)$ | <0001>                           |

| TED  | $<11\bar{2}0>/3$ | <0001>                           |

| BPD  | $<11\bar{2}0>/3$ | 在 {0001} 面内<br>(倾向于<11\bar{2}0>) |

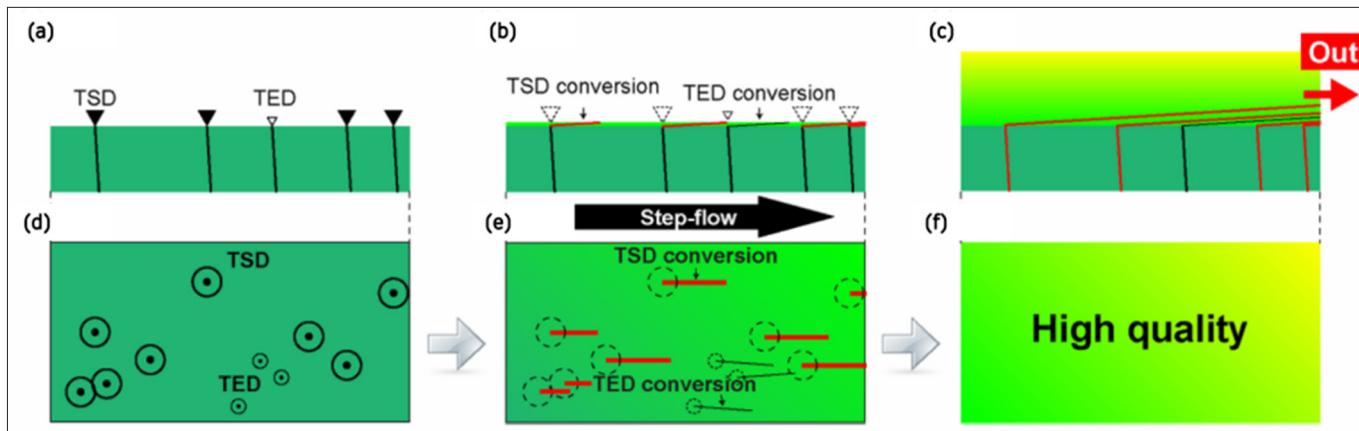

大量研究表明，溶液法生长 SiC 单晶的过程中不会产生微管，并且可以有效地闭合籽晶中固有的微管及一些其他宏观缺陷<sup>[9-10]</sup>，从而大幅提升晶体的质量，有利于获得更高质量的 SiC 单晶，除此之外如图 2 所示，选用偏角度籽晶，TSDs 和 TEDs 在宏观台阶的台阶流作用下，分别转化为堆垛层错和基面位错。随着生长的进行，这些转化后的缺陷发生横向扩展，最终移出晶体，进一步降低位错数量<sup>[11-13]</sup>。同样在生长过程中通过改

图2：溶液法中位错转换过程<sup>[11]</sup>

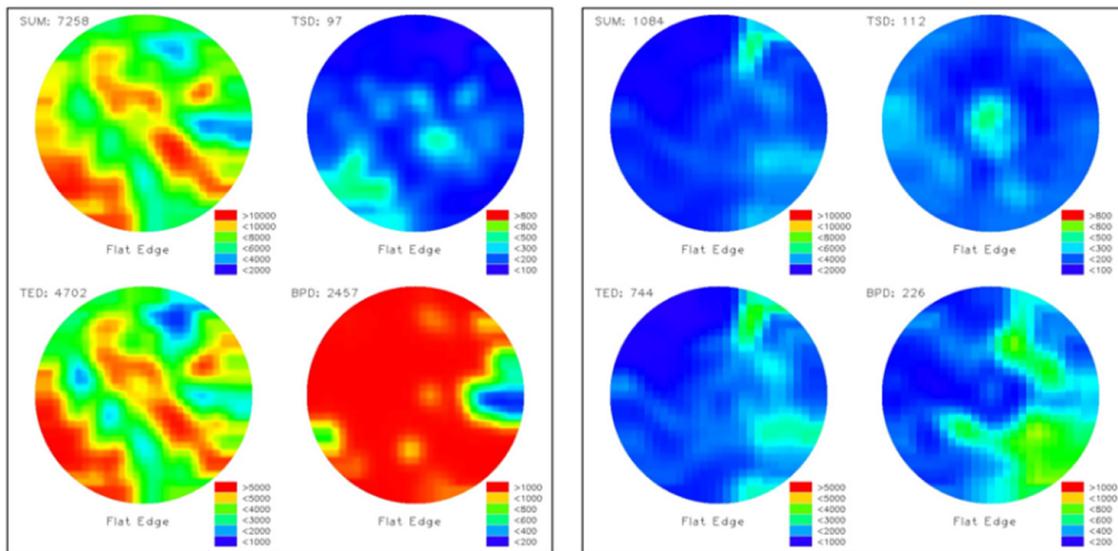

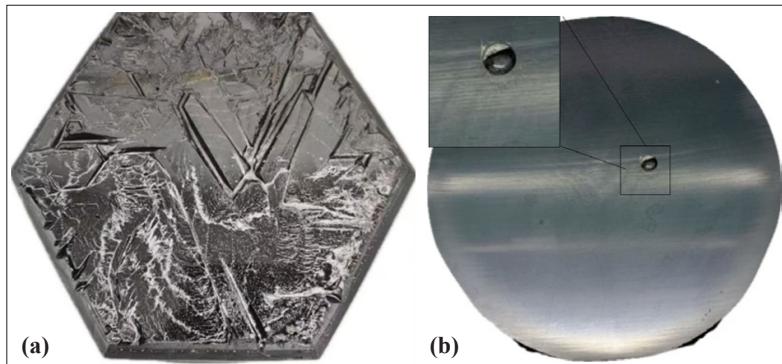

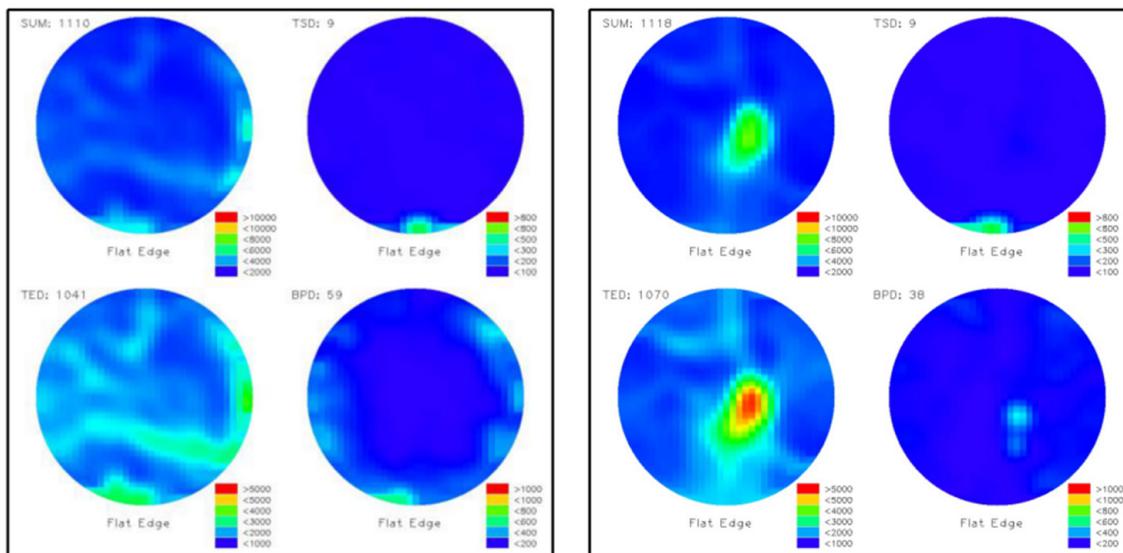

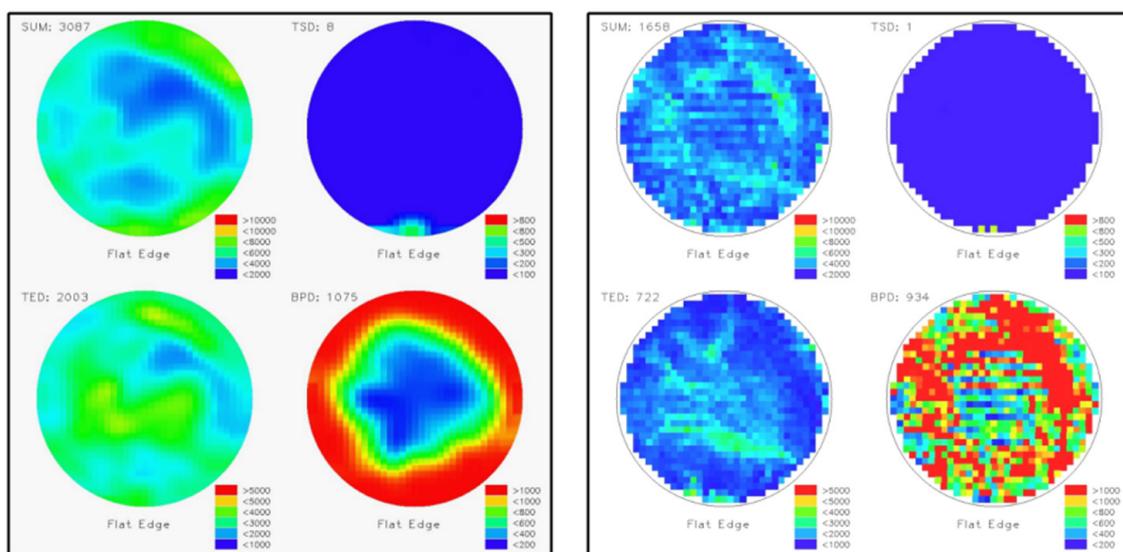

图3：晶片位错缺陷扫描图谱(图中数据单位： $\text{个}/\text{cm}^2$ )，(a)生长界面温度梯度 $5^\circ\text{C}\text{cm}^{-1}$ ；(b)生长界面温度梯度 $2^\circ\text{C}\text{cm}^{-1}$

进生长工艺也可以避免位错产生或增殖。本文通过多组实验验证分析，得出优化生长界面温度梯度、控制晶体内部气孔形成、选用偏角度籽晶以及实施扩径生长可显著降低晶体中的位错密度，提升晶体质量。

## 2.1 生长界面温度梯度对位错数量的影响

在溶液法生长碳化硅单晶时，生长界面处的低温与溶液中的高温形成的温度差导致的碳过饱和是晶体生长的驱动力。生长界面温度梯度大时，晶体生长速度快，若界面处没有充足的溶质供应则会导致晶体中出现溶剂包裹，即使有充足的溶质浓度，大的梯度也会导致晶体内部热应力加大，导致位错产生。如图3所示：(a) 中晶体生长过程的生长界面温度梯度为 $5^\circ\text{C cm}^{-1}$ ；(b) 中晶体生长界面温度梯度为 $2^\circ\text{C cm}^{-1}$ 。(b) 晶体的位错数量明显少于(a) 晶体。出现该影响的原因在于：尽管溶液法整体生长体系的温度梯度较小，通常不会产生破坏晶体完整性的应力，但热应力偏大仍会导致晶体内部出现点阵错配，而点阵错配进一步会诱发晶体内部产生螺位错(TSD)、刃位错(TED)等，最终表现为晶片缺陷数量多少与生长界面处温度梯度大小呈正相关性。

由以上可知，生长过程中生长界面温度梯度是导致位错数量变化的重要参数。此外，在籽晶接触液面瞬间，籽晶表面和溶液表面的温差也是导致位错产生的主要因素。

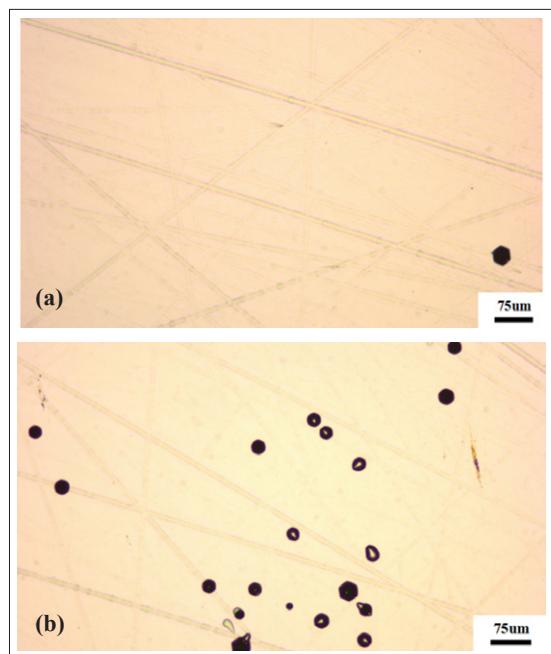

图4为籽晶在距离液面不同位置处烘烤后，接触溶液进行生长和加工腐蚀后获得样片的位错

缺陷扫描数据，不同位置烘烤时籽晶与液面的温差不同，籽晶距离液面越近，两者温差越小。(a) 将籽晶置于液面以上5mm烘烤，随后下降籽晶接触液面，接触瞬间籽晶背面温度升高 $3^\circ\text{C}$ ，(b) 将籽晶置于液面以上10mm烘烤，随后下降籽晶接触液面，接触瞬间籽晶背面温度升高 $6^\circ\text{C}$ 。从实验结果来看，采用(a) 工艺产生的位错缺陷数量要明显减小，这是因为在接触前，籽晶表面和溶液表面的传热方式以辐射传热为主，接触后以热传导为主，再加上籽晶表面和液面本身就存在温度差异，这种差异叠加传热方式的转变加剧了接触瞬间的热冲击，导致籽晶表面晶格出现失配而产生新位错。

## 2.2 气孔形成对位错数量的影响

溶液法生长碳化硅单晶时晶体内部气孔形成主要集中于两个阶段，一是籽晶接触液面的瞬间，二是籽晶接触液面后的回溶阶段。第一阶段接触

图4：晶片中的位错分布(图中数据为视场范围内位错缺陷个数)，(a)籽晶置于液面以上5 mm烘烤；(b)籽晶置于液面以上10 mm烘烤

图5: (a) 含有大尺寸气孔的晶体；(b) 切割晶片表面气孔形貌

瞬间，由于籽晶与液面存在不平行或者液面波动的状态下，籽晶表面与液面接触存在先后，接触时会出现空隙，空隙中包裹气体，这类气孔的尺寸可达2mm左右，其轮廓为标准圆形，通常位于晶体边缘。这类气孔将生长表面与溶液隔开，气孔内的籽晶表面没有任何溶剂夹杂和生长回溶痕迹。第二阶段的情况通过多组实验和国内外研究分析可能由以下情况导致<sup>[14-15]</sup>：1) 炉内惰性气体分压过大，导致溶液中溶解量明显增加；2) 接触时界面低温与溶液内部高温温差大，导致接触界面出现气体析出；3) 籽晶烘烤不充分，冷的籽晶表面与高温溶液接触瞬间的温度差导致气体析出；4) 籽晶在未接触液面之前，挥发出的溶剂吸附在籽晶表面，在籽晶表面形成少量微小腐蚀坑，

籽晶接触液面后回溶不充分导致腐蚀坑未完全消除，生长时低的腐蚀坑内压缩有气体形成气孔。以上问题导致的气孔尺寸通常小于1mm，将籽晶完全剥离或是通过切开研磨处理后可以观察。

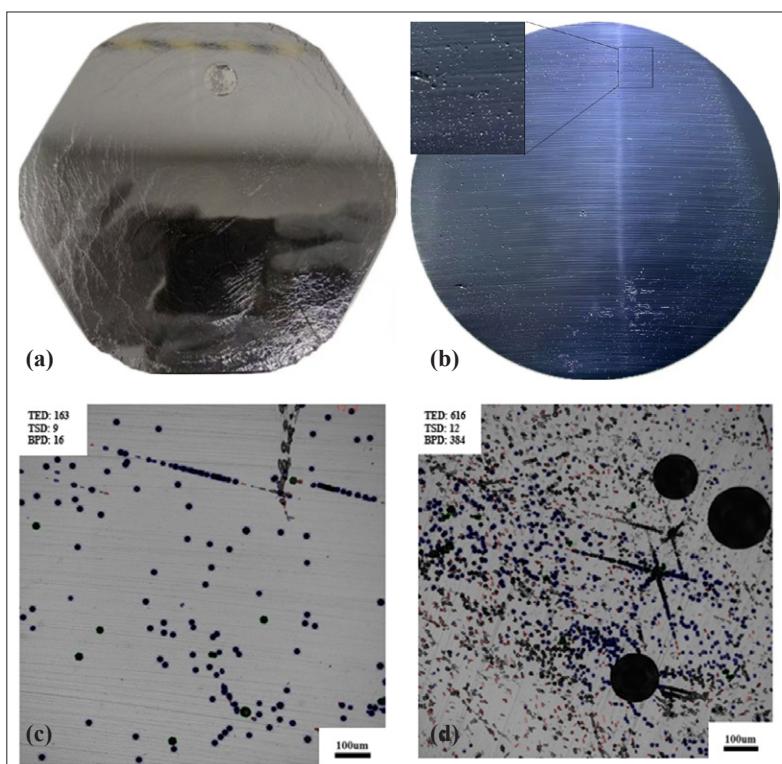

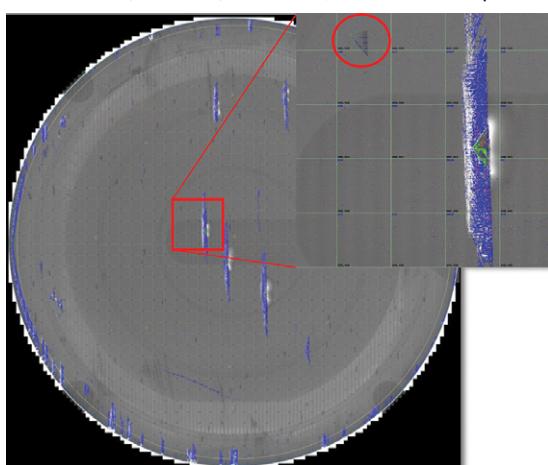

通过实验获得包含有两种气孔的晶体及切割晶片样品，图5(a)、图5(b)所示为含有大尺寸气孔的晶体及沿晶体生长厚度0.5mm处切割获得晶片表面气孔形貌，气孔区域与溶液隔离导致生长中断，其周围区域溶液流动受影响，晶体表面呈现明显条纹状溶剂包裹。图6(a)所示含有微小气孔的晶体，气孔较早闭合，晶体后期生长未受到明显影响，晶体表面仍光滑平整。图6(b)显示沿晶体生长厚度0.5mm处切割获得的晶片边缘存在大量微米级气孔。图6(c)和图6(d)分别对应图6(b)所示切割晶片表面正常区域和含气孔区域的位错缺陷扫描数据，含气孔区域TSD，TED位错数量明显增加，经过统计，视场内的TDs数量(TSD与TED数量之和)高达628个，正常区域视场内的TDs数量仅为172个。单晶中的气孔导致其周围晶格畸变变大，导致晶格失配，位错数量大幅增加。

### 2.3 扩径生长对位错数量的影响

溶液法相较于目前主流的物理气相传输法，其显著优势在于通过控制提拉速度和溶液中温差较容易实现晶体的扩径。采用0°籽晶进行生长，由于TDs的位错线与晶体生长方向平行，TDs位

图6: (a) 含有微小气孔晶体；(b) 切割晶片表面气孔形貌；(c) 晶片正常区域位错分布；(d) 晶片含有气孔区域位错分布 (图中数据为视场范围内位错缺陷个数)

图7: 晶片中 (a) 扩径区域和 (b) 原始生长区域位错分布

图8: (a) 原始籽晶和 (b) 生长晶体中位错缺陷扫描图谱 (图中数据单位: 个/cm<sup>2</sup>)

错较难转换。本文通过多组实验发现,采用小籽晶进行扩径生长,如图7所示,小籽晶扩径区域的缺陷数量要明显少于原始籽晶处的缺陷数量。这主要是因为籽晶扩径区域的生长方向与TDs的位错线存在夹角,该夹角可以帮助TDs在一定程度上转换成基面位错,最终移出晶体,扩径区域位错数量甚至降低至零。

#### 2.4 籽晶晶向对晶体中位错数量的影响

溶液法生长碳化硅单晶,常选用的籽晶可分为(0001)面正晶向和(0001)面沿<1120>方向4°偏轴籽晶。在使用正晶向籽晶进行生长的过程中,由于晶体生长方向垂直于BPDs,籽晶中的BPDs很难传播到生长晶体中,因此可以生长出基本不

含BPDs的晶体<sup>[16]</sup>。但是由于TDs的位错线与晶体生长方向平行,籽晶中的TDs很容易向生长晶体传播,因此TDs转化率较低。如图8所示,采用正晶向籽晶进行晶体生长,晶片中TDs数量几乎和原始籽晶中TDs数量一致甚至略有增加,但BPDs数量明显减小。

在使用4°偏轴籽晶生长过程中,整个生长面呈现台阶流生长模式,从而形成供位错转换的宏观台阶,随着晶体的生长,籽晶中的TSDs和TEDs在宏观台阶附近被转换为基面上的缺陷,随着晶体生长的持续进行,这些缺陷最终从晶体边缘移出,从而实现SiC的高质量生长。图9为采用4°偏轴籽晶生长后的位错缺陷扫描图,可以明显看到晶体中的TDs数量明显降低。

图9: (a) 原始籽晶和 (b) 生长晶体中位错缺陷扫描图谱 (图中数据单位: 个/cm<sup>2</sup>)

## 结论

本研究通过系统实验与表征分析，明确了溶液法生长4H-SiC单晶过程中位错缺陷的主要来源和控制方法。合适的生长界面温度梯度可以减少热应力与溶剂包裹，明显抑制位错的增殖；通过减小溶液温差并对籽晶充分回溶处理等调整可以有效抑制晶体内气孔的形成从而避免产生新位错；小籽晶扩径生长可在扩径区域实现位错的充分消除；选择偏轴籽晶进行单晶生长可实现TSD和TED向基面缺陷的转化后降低生长晶体的位错数量。综上所述，通过多参数协同优化，溶液法有望生长出低缺陷、高质量的4H-SiC单晶，推动其在高压高功率电力电子器件中的更广泛应用。

## 公司简介：

常州臻晶半导体有限公司成立于2020年10月，位于常州市武进国家高新区创新产业园内，是一家专业从事第三代半导体碳化硅（SiC）的溶液法长晶设备及技术开发的高新技术公司。

主营产品及服务包括：6-12英寸液相法碳化硅电阻长晶炉及其长晶工艺、液相法籽晶、低阻p型液相法衬底及晶体晶片加工服务。

地 址：江苏省常州市武进区武宜南路377号19号厂房东

联系人：蒋志强 19952805727

## 扩展阅读

- [1] T Narumi, D Chaussende, T Yoshikawa. 3C-, 4H-, and 6H-SiC crystal habitus and interfacial behaviours in high temperature Si-based solvents[J]. CrystEngComm, 2020, 22(20): 3489-3496.

- [2] P C Chen, W C Miao, T Ahmed, et al. Defect inspection techniques in SiC[J]. Nanoscale Research Letters, 2022, 17(1): 30.

- [3] S Kawanishi, Y Nagamatsu, T Yoshikawa, et al. Availability of Cr-rich Cr-Si solvent for rapid solution growth of 4H-SiC[J]. Journal of Crystal Growth, 2020, 549: 125877.

- [4] K Hyun, S J Kim, T Taishi. Effect of cobalt addition to Si-Cr solvent in top-seeded solution growth[J]. Applied Surface Science, 2020, 513: 145798.

- [5] H Daikoku, M Kado, A Seki, et al. Solution growth on concave surface of 4H-SiC crystal[J]. Crystal Growth & Design, 2016, 16(3): 1256-1260.

- [6] T Mitani, N Komatsu, T Takahashi, et al. Effect of aluminum addition on the surface step morphology of 4H-SiC grown from Si-Cr-C solution[J]. Journal of Crystal Growth, 2015, 423: 45-49.

- [7] N Komatsu, T Mitani, Y Hayashi, et al. Modification of the surface morphology of 4H-SiC by addition of Sn and Al in solution growth with Si-Cr solvents[J]. Journal of Crystal Growth, 2017, 458: 37-43.

- [8] M T Ha, S M Jeong. A review of the simulation studies on the bulk growth of silicon carbide single crystals[J]. Korean Ceram. Soc., 2022, 59(2): 153-179.

- [9] T Ujihara, S Munetoh, K Kusunoki, et al. Crystal quality evaluation of 6H-SiC layers grown by liquid phase epitaxy around micropipes using micro-Raman scattering spectroscopy[J]. Materials Science Forum, 2004, 457/458/459/460: 633-636.

- [10] T Ujihara, S Munetoh, K Kusunoki, et al. Crystal quality of a 6H-SiC layer grown over macrodefects by liquid-phase epitaxy: a Raman spectroscopic study[J]. Thin Solid Films, 2005, 476(1): 206-209.

- [11] S. Harada, Y. Yamamoto, K. Seki, et al. Current advances in SiC solution growth (<Special Issue>) Opening Up a New World of Crystal Growth on SiC[J]. Journal of the Japan Association for Crystal Growth, 2013, 40(1): 25-32.

- [12] T Ujihara, S Kozawa, K Seki, et al. Conversion mechanism of threading screw dislocation during SiC solution growth[J]. Materials Science Forum, 2012, 717/718/719/720: 351-354.

- [13] Y Yamamoto, S Harada, K Seki, et al. High-efficiency conversion of threading screw dislocations in 4H-SiC by solution growth[J]. Applied Physics Express, 2012, 5(11): 115501.

- [14] G Wang, D Sheng, Y Yang, et al. Wafer-scale p-type SiC single crystals with high crystalline quality[J]. Crystal Growth & Design, 2024, 24(13): 5686-5692.

- [15] Y Wang, P Gu, P Wang. Improvement of surface morphology by optimizing the growth conditions in solution growth of SiC single crystal[J]. Journal of Crystal Growth, 2023, 605: 127074.

- [16] K Seki, K Kusunoki, S Harada, et al. Evaluation of basal plane dislocation behavior in the epitaxial layer on a 4H-SiC wafer fabricated by the solution growth method. Mater. Sci. Forum, 2019, 963: 80-84.

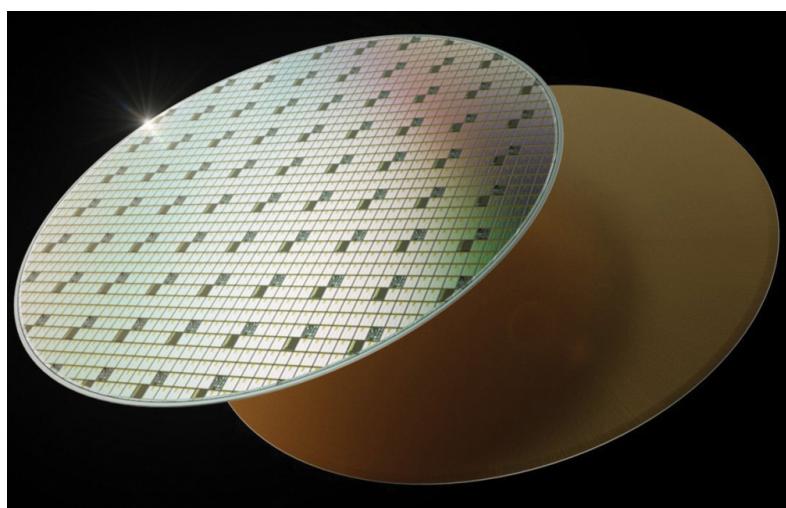

# 200mm 碳化硅衬底厚度与外延厚度的多维度影响

作者: THOMAS KUHR, WOLFSPEED 公司工艺制程开发工程高级总监

**我**们能将碳化硅 (SiC) 衬底厚度推进到多薄而不影响性能? 这是我们几十年来一直在追问的问题, 同时我们也在不断突破碳化硅 (SiC) 材料性能的极限——因为我们知道下一代碳化硅 (SiC) 器件技术正依赖于此。

这篇文章探讨了 Wolfspeed 在碳化硅 (SiC) 衬底的成本、可扩展性和质量等最严峻挑战方面的研究, 包括了碳化硅 (SiC) 外延和衬底厚度如何影响高压电器件。

碳化硅 (SiC) 衬底的成本需要降下来。但是, 如果我们对这种基础材料的厚度施加限制的话, 会阻碍这些努力吗?

碳化硅 (SiC) 正受益于电动汽车的蓬勃发展。基于这种宽禁带半导体的功率器件的采用, 使得更高效率的电子设备能够将系统损耗降低 80% 甚至更多。然而, 尽管这令人印象深刻, 但这只是其好处的冰山一角。和其他宽禁带材料一样, 碳化硅 (SiC) 还具有高热导率和优异的饱和漂移速度, 使得用这种材料制成的器件能够在高电场强度下工作, 并应用于许多技术领域, 包括高电压直流、脉冲功率和固态变压器。使用可处理高达 10 kV 的单个碳化硅 (SiC) MOSFET 芯片, 甚至更高电压的双极器件, 为设计人员提供了简化系统并在许多应用中降低电阻加热损耗的机会。

随着碳化硅 (SiC) 持续展现出优于现有技术的改进性能, 其较高的成本正受到重点关注。在半导体行业内, 应对这一挑战的常见解决方案是转向更大尺寸的晶圆, 从而将固定的加工成本分摊到更多的器件上。这一转变正在进行中, 碳化硅 (SiC) 衬底目前正经历从 150 mm 直径向 200 mm 直径的转型。然而, 与随着直径增加而增加晶圆厚度的硅 (Si) 行业不同, 碳化硅 (SiC) 行业正在考虑为 200 mm 直径晶圆保留现今 150 mm

直径晶圆所使用的 350  $\mu\text{m}$  厚度。

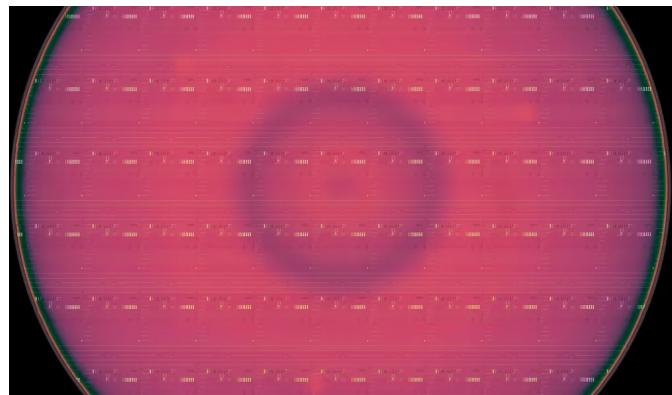

Wolfspeed 作为全球碳化硅 (SiC) 衬底和器件的领先企业, 我们一直在研究, 当采用 350  $\mu\text{m}$  厚度和 500  $\mu\text{m}$  厚度的晶圆时, 不同厚度条件下的外延层在质量上有何差异。用于制造 650 V 和 1200 V 器件的“薄”碳化硅 (SiC) 层的生长, 往往不会因温度情况或衬底与外延膜层之间掺杂差异而产生显著应力。然而, 当外延层更厚且掺杂浓度更低时——这是更高击穿电压器件的两个关键要求——应力会被放大, 产生新的缺陷并引发晶圆形状问题。

此外, 外延缺陷的尺寸和面积也会增加, 因为它们通常在衬底界面处或附近产生, 并随着薄膜的生长而相应增大。更大的应力和更大的缺陷, 加上高电压器件通常尺寸更大, 这些因素的复合效应导致晶圆的可使用面积大大降低, 从而导致芯片良率降低和每个器件的成本升高。

## 可能会出现什么问题?

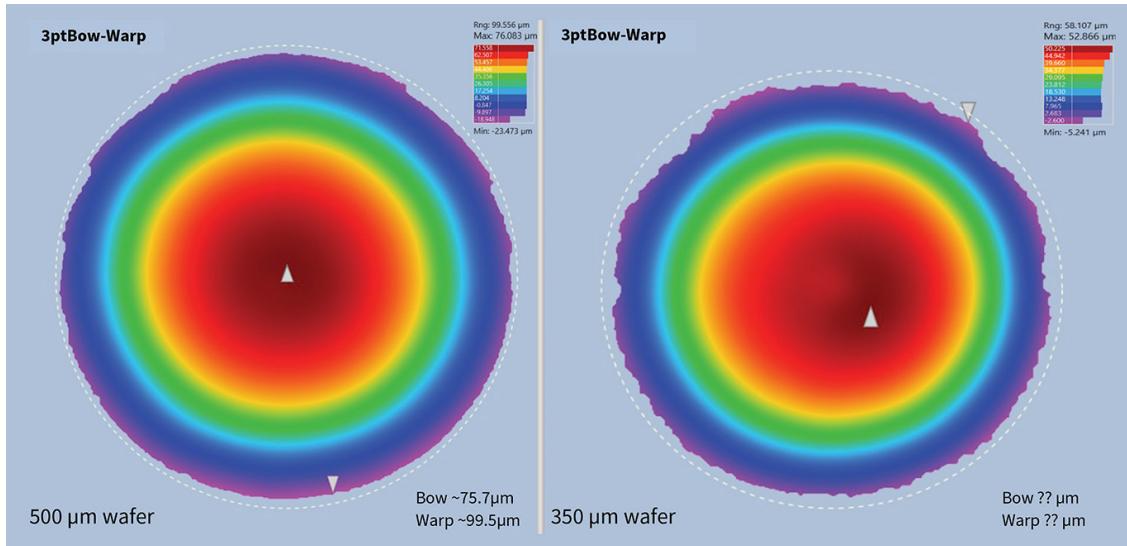

为了加深我们对更薄衬底和更厚外延层之间相互作用的理解, 我们研究了三种不同厚度的同

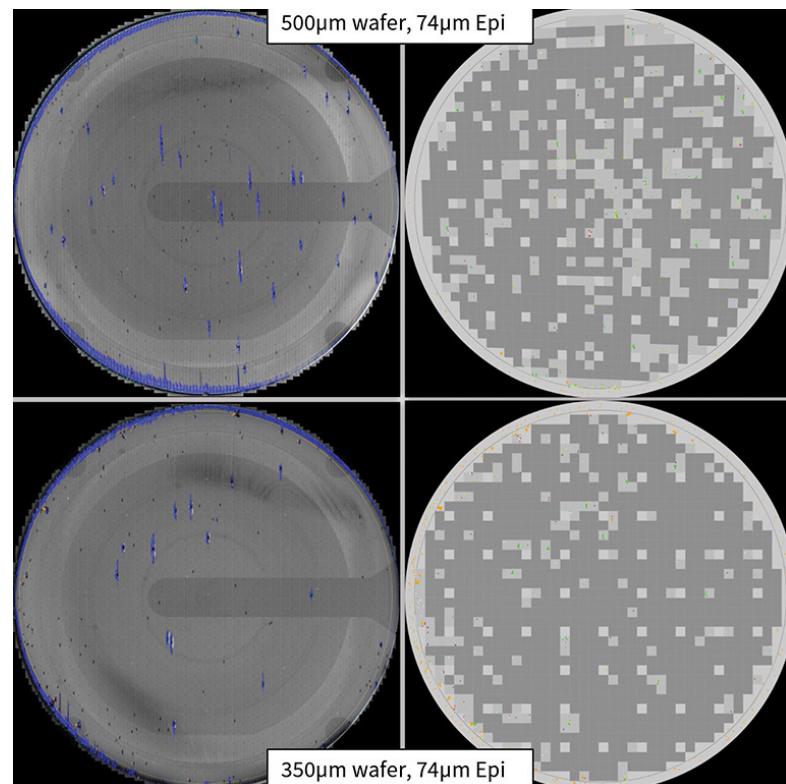

图1: 500 μm 厚度(左)和350 μm 厚度(右)的晶圆形状图比较。请注意，在这两种情况下都未生成完整的图谱，不过左侧的扫描更完整。350 μm 厚度晶圆的弯曲度(Bow)和翘曲度(Warp)明显更高，超出了当前工具配置的测量范围。

质外延层的性能对比。外延层在350 μm厚度和500 μm厚度的200 mm SiC衬底上进行生长，并采用了两种已商用的反应器平台。诚然，进行这种评估的最佳方法是将单个晶锭切割成多个不同厚度的衬底，因为这样可以标准化衬底缺陷的起始点。但在这项工作中，我们使用了内部生产的晶圆因为它们已经可获取的。我们根据特定的器件要求选择了掺杂和厚度目标，旨在达到所需击穿电压下的最低电阻，并且通过利用我们标准生产流程中的一套测量方法，我们已经能够确定是否存在任何潜在的制造限制。

外延生长过程中的一个担忧是晶圆形状在高温生长条件下的稳定性。晶圆形状在室温和超过1600°C时可能不同，更薄的晶圆可能会不可预测地改变形状。任何变化都会通过厚度或掺杂不均匀性对生长产生不利影响。在最坏的情况下，晶圆可能会在加工过程中破裂或从承载器上弹出。

我们的结果消除了将晶圆厚度从500 μm减

少到350 μm时的这种担忧。如果说有什么不同的話，更薄的晶圆反而改善了薄膜厚度和掺杂均匀性，尽管这可能取决于反应器设备的设计。请注意，我们需要进行更多轮的生长实验才能建立具有统计显著性的结论。然而，我们的初步研究表明，在外延生长过程中使用更薄的200 mm晶圆不存在相关问题。

由于薄型和厚型SiC器件在化学工艺和器件设计方面的相似性，我们的器件制造团队希望所有外延晶圆的表面状态相似。为了验证是否如此，我们使用原子力显微镜(AFM)和共聚焦成像技术仔细检查了我们的材料。用于AFM测量粗糙度，粗糙度性能相匹配，薄膜和厚膜的平均粗糙度(Ra)均小于0.2 nm。根据共聚焦成像，厚膜的长程粗糙度大于薄膜，平均粗糙度(Ra)约为0.6 nm。

这些发现与衬底厚度无关，尽管在共聚焦成像尺度上，稍微多一点的粗糙度在空间分布上略广一些。这表明，就像掺杂和厚度均匀性一样，表面粗糙度相对于晶圆厚度而言可能不是一个問題。然而，有必要减少厚膜的表面粗糙度，并进一步改进空间依赖性。

由于更厚的外延层会导致更大的缺陷和更高的薄膜应力，选择更薄的衬底会加剧应力问题。因此，当在更薄的衬底上生长更厚的外延层时发现形状问题，我们并不感到惊讶。使用直径200 mm的碳化硅(SiC)，在500 μm厚度的衬底上生长13 μm厚度的外延层会导致20-40 μm的弯曲度(Bow)；将厚度增加到115 μm，并将掺杂浓度降至 $10^{15} \text{ cm}^{-3}$ 的中段，弯曲度会增加至80 μm左右。

图2: 用于估算500 μm厚度200 mm直径衬底上生长115 μm厚度外延层的器件可用面积的拼接图像图(带有初步墨迹标记)。使用了任意的5 mm×5 mm网格进行可视化。请注意，并非所有缺陷都被正确识别，但可以看到宏观缺陷(如三角形缺陷)的面积效应，如插入图片所示。

如果然后将衬底减薄至 350  $\mu\text{m}$ , 弯曲度会增加至 100  $\mu\text{m}$  以上, 从而在器件制造过程中带来处理错误和晶圆破裂的风险。虽然 100  $\mu\text{m}$  的晶圆弯曲度与离子注入过程中可能发生的数百  $\mu\text{m}$  弯曲度相比似乎微不足道, 但并非所有的制造工具都能从那个起点开始处理。我们的观点是, 如果打算采用仅 350  $\mu\text{m}$  厚度的衬底来生长更厚的外延层, 可能需要做更多的工作来补偿晶圆形状问题。

碳化硅 (SiC) 最大的缺点是其晶体生长过程中固有的缺陷以及相对容易形成缺陷。在晶锭生长过程中产生并存在于衬底中的缺陷, 要么通过生长的延续, 要么通过转化为其他类型的缺陷, 传播到外延层中。缺陷的来源可能是微管、穿透位错 (threading dislocations)、堆垛层错 (stacking faults)、表面制备造成的亚表面损伤, 或者仅仅是清洁不充分导致的表面沾污; 更一般地说, 任何破坏晶格自然堆叠的因素都会导致缺陷。例如, 一种称为“三角形”的常见缺陷——它是一种晶体堆叠紊乱, 表现为生长表面可见的三角形——其尺寸随着外延生长而增大, 从外延生长 13  $\mu\text{m}$  时的 0.4 mm 长增加到 115  $\mu\text{m}$  厚薄膜时的 3.2 mm。您可能会想, 这有什么大不了的, 因为器件通常尺寸为 25  $\text{mm}^2$  或更大, 所以一个三角形缺陷应该只影响一两个芯片。

正如我们已经提到的, 薄膜应力随着厚度以及薄膜与衬底之间的掺杂差异而增加。因此, 加上碳化硅 (SiC) 基平面位错 (basal plan dislocations) 非常低的形成能 (formation energy), 诸如三角形之类的缺陷有可能产生基平面位错。这些位错从源缺陷处出现, 沿着晶圆垂直滑移。因此, 一个最初只影响一两个器件的缺陷现在可能会影响五到十倍的芯片, 从而大幅降低良率。

好消息是, 通过精细管理外延生长过程中晶圆上的温度分布, 可以减少过度的薄膜应力。即

使这种收益是以增加晶圆弯曲度为代价, 这也使得能够处理更薄的晶圆而不会增加薄膜缺陷。

不巧地是, 并非我们所有的测量都特别顺利。由于扫描不完整, 我们最初关于带有厚外延层的薄晶圆的最大弯曲度数值是不正确的。我们花了一点时间和精力, 通过微小调整, 克服了这个简单工具限制, 纠正了这个错误。

我们还遇到了与缺陷自动检测相关的问题, 原因是检测算法是针对不同尺寸的缺陷或更光滑的表面进行训练的。这意味着我们将应用于更薄外延层的准确的缺陷分类和数据采集方法, 用在更厚外延薄膜的初期阶段会遇到困难。

我们遇到的与晶圆弯曲度扫描和缺陷检测相关的问题并非不可克服。就缺陷而言, 它们甚至与衬底厚度无关。然而, 在这些技术能够服务于

图3: 用于估算 500  $\mu\text{m}$  厚度和 350  $\mu\text{m}$  厚度 200 mm 衬底上生长 74  $\mu\text{m}$  厚度外延层的器件可用面积的拼接图像图 (带有初步墨迹标记)。显示了 75-85% 的 5×5 可用区域。

图4: 准备进行封装的 10kV 裸芯片。

图5：高性能半桥 10 kV、

50 mΩ 全碳化硅 (SiC)

功率模块。

大批量制造工艺之前，需要进行干预和开发。总而言之，更薄的晶圆会导致形状问题，必须在外延生长之前或生长期间解决。但如果温度分布和应力得到有效管理，额外的应力诱导缺陷应该不会成为问题。这听起来还不错，除了预测的良率看起来并不那么高，而且成本仍然很高。

为了说明这一点，我们考虑用于 1200 V MOSFET 晶圆的 5 mm × 5 mm 器件。在这种情况下，可用面积超过 90%。但如果需要更厚的外延层，由于增大的面积效应，可用面积会下降到 70% 左右。如果器件尺寸增加，根据简单的泊松统计，可用面积会进一步下降。现在，那片对于 1200 V MOSFET 可用面积超过 90% 的碳化硅 (SiC) 晶圆，对于 10 kV MOSFET 而言可能低于 40%，而这甚至是在外延片进入器件制造厂之前。

### 可行的厚度？

让我们回到最初的问题：减薄碳化硅 (SiC)

衬底是否会限制使用更厚外延层制造高电压器件的能力？也许不会。很明显，关键是要控制晶圆形状并管理外延生长应力，以防止器件制造过程中的复杂情况，从而保持低成本。为了支持这些努力，需要进行调整以确保测量和计量方法与当前最佳实践和行业标准保持连续性。但同样非常重要的是，碳化硅 (SiC) 衬底制造商需要继续专注于减少缺陷。如果没有更低的缺陷浓度，器件尺寸和能力或器件良率将继续需要权衡取舍，并且无论外延生长过程如何优化，成本都将保持高位。

最后，推动碳化硅 (SiC) 衬底变得更薄的努力将继续下去，因为降低其成本仍然是一个巨大的动力。在此背景下，创新者将找到处理晶圆形状的方法，衬底制造商将继续降低缺陷密度，有助于提高器件良率并削减成本。

出于纯粹的技术需求，对于更高电压器件的使用将继续提升，采用 10 kV MOSFET 或更高电压的 IGBT 将为其铺平道路。碳化硅 (SiC) 变革正逢其时！CSc

## MICRO-MECHANICS ON STRATEGIC MATERIALS

- In stock for all vacuum and ultra vacuum applications :

**Molybdenum and Tantalum screw products**

(screws, nuts, rings) « Usable in Clean Rooms »

- In stock for laboratory machines :

**Standard substrate support (Molybloc)**

Dimensions :

- 1 ½ inches

- 2 inches

- 3 inches

Possibility of substrate support with cavity and washer, on request and according to drawings

- Stock of platens blanks for all types of MBE from various manufacturers.

- « Usable in clean rooms » **Platens and washers**

produced according to drawings.

**RABOUTET SA**

Avenue Louis Armand • B.P. 31 • 74301 Cluses Cedex FRANCE

T. +33 (0)4 50 98 15 18 • info@rabouet.fr

[www.rabouet.fr](http://www.rabouet.fr)

# 碳化硅结型势垒肖特基二极管的高温挑战

**摘要：**近来，国外已有一些基于碳化硅材料的高温器件研究，公开报道的长寿工作结温分别高达600°C、800°C和1000°C；为了探索用碳化硅材料实现高温半导体器件的可行性，研究团队设计了一个碳化硅结型势垒肖特基二极管，利用普通碳化硅电力电子器件的制程，制作了测试样品，测试分析了200°C~281°C温度区间该二极管主要参数的变化情况；测试结果证明，使用碳化硅材料和普通的碳化硅制程来制造高温半导体器件，是一条可行的技术路线；后续，研究团队将逐步展开碳化硅场效应管、运算放大器、数模转换器等器件的设计和验证，并逐步挑战更高的工作结温。

作者：杨良<sup>1</sup>，吉吟东<sup>2</sup>，刘超超<sup>3</sup>，宋亚东<sup>4</sup>，曹建武<sup>5</sup>，罗宁胜<sup>6</sup>

- 1. 深圳爱仕特科技有限公司，广东 深圳 518118；

- 3. 江苏晶利恒半导体科技有限公司，江苏 如东 226400；

- 5. 深圳市慧亚科技有限公司，广东 深圳 518100；

- 2. 清华大学信息科学技术学院，北京 100084；

- 4. 苏州安萨斯半导体有限公司，江苏 苏州 215131；

- 6. 合肥光电半导体研究院特种封测技术实验室，安徽 合肥 230088

## 引言

高温半导体器件 (High Temperature Semiconductor Devices) 是指工作结温在150°C以上且具备高可靠性能的半导体器件，通常应用于极限环境 (Extreme Environment) 例如航空航天、石油钻探等；这些应用往往需要模拟前端 (Analog Front End, AFE) 来将模拟的传感器信号数字化，并传输给后方的控制计算机进行解算；控制计算机解算后发出必要的控制指令给前端的执行机构 (Executive Machinery)，从而实时调整受控对象的姿态。

30多年以来，全球高温半导体器件的制造商，仅有寥寥数家；过去高温半导体器件的实现主要依赖于绝缘层上硅(Silicon on Insulator, SOI)工艺，一般的商用产品都做到了标称结温225°C；近年的器件设计和SOI工艺创新，使得SOI高温器件的长寿结温已达300°C<sup>[1-2]</sup>、450°C<sup>[3-5]</sup>，有些SOI高温传感器的工作结温已达600°C<sup>[6-7]</sup>。

用于电力电子的高压大电流碳化硅器件，其理论研究和批量制造已经非常成熟，但将这类器件应用于低压小电流的高温极限环境，尚未见诸报道；依据William Shockley的理论，“二极管”(Diode)是“三极管”(Transistor)，包括“双极型三极管”(Bipolar Junction Transistor, BJT)和

“场效应管”(Field Effect Transistor, FET)的基础，碳化硅二极管的基础特性，决定了碳化硅三极管和其他半导体器件的特性。

多数商用级别的碳化硅“电力电子器件”(Power Electronics Devices)，基于“四方体碳化硅”(4H Silicon Carbide, 4H-SiC)材料，普遍做到了标称结温175°C，少数做到了200°C；基于4H-SiC的高温半导体器件，国外领先的研究机构进行了有益的探索，多数采用了“结型场效应管”(Junction Field Effect Transistor, JFET)设计构型及其变体，分别实现了工作结温600°C<sup>[8-9]</sup>、800°C<sup>[10]</sup>和1000°C<sup>[11]</sup>的运算放大器和逻辑电路；在高温封装等方面，芯片级别做到了500°C<sup>[12]</sup>，功率总成级别则做到了400°C<sup>[13]</sup>。

迄今，国内极限应用所需的高温半导体器件，几乎完全依赖进口；近年国际贸易环境充满了变数，全球供应链的不确定性显而易见；中国政府从战略安全的高度出发，提出了“全国产化”、“全程自主可控”等产业指导政策，特别是在核心元器件方面，鼓励开展广泛的产学研合作，从多个路径发展基于自主知识产权的支撑性研发。

为此，研究团队基于自身“碳化硅肖特基势垒二极管”(SiC Schottky Barrier Diode, SiC SBD)和“碳化硅金属氧化物场效应管”(SiC Metal Ox-

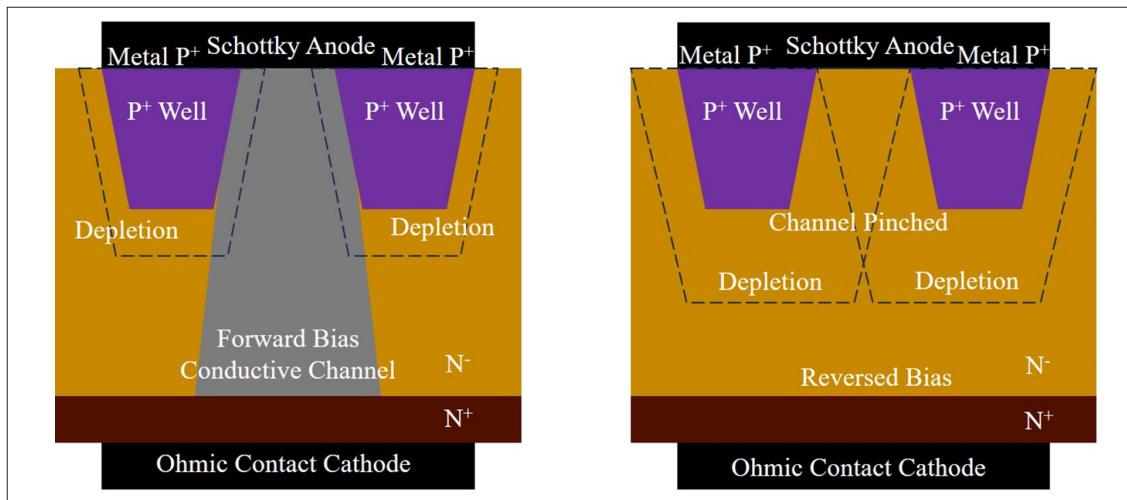

图1: JBS的导电通道及其夹断

ide Field Effect Transistor, SiC MOSFET) 等电力电子器件的设计经验，以“碳化硅结型势垒肖基二极管”(SiC Junction Barrier Schottky Diode, SiC JBS) 为起点，设计并使用普通的 SiC 器件编程，制作了测试样品 (Device Under Test, DUT)，并对 SiC JBS 的高温特性，进行了初始的探索；后续，研究团队将基于早期的测试结果，从 SiC MOSFET 开始，逐步设计、制造并验证 AFE 所需的、结温 300°C 的系列 SiC 高温半导体器件。

## 1 技术路径

### 1.1 SBD 和 JBS

将金属体与 N 型半导体进行“肖特基接触”(Schottky Contact)，在接触界面就形成了“金属 - 半导体”P-N 结；由于两种材料的“功函数”(Work Function) 存在差异，该 P-N 结的两端存在电位差，该电位差即肖特基势垒 (Schottky Barrier)；该 P-N 结构成的二极管即为 SBD。

在 SBD 正极金属层的下侧，植入均匀或不均匀的 P 阵 (P Well) 阵列，就构成了 JBS；这些 P 阵周边有一个耗尽层，并生成了附加的 P-N 结；这些 P 阵的尺寸和间距设计，使得耗尽层在正向偏置的条件下不会交叉 (图 2 左)，从而保有“导电通道”(Conductive Channel)；而当反向偏置电压达到一定的数值时，相邻的耗尽层将会被放大并交叉，形成一个“夹断区域”(Pinched Area)，如图 1 右所示；夹断区域阻挡了 P-N 结上反向偏置的进一步增加，避免了“势垒降低效应”(Barrier Lowering Effect)；JBS 不仅保有 SBD 的优点，更消除了 SBD 固有的软击穿特性 (Soft Breakdown Characteristic)，兼具高耐压、低漏电流的优

势；由于“N”层的存在，JBS 的实际上也是“夹层二极管”(P-intrinsic-N Diode, PiN Diode) 构造，具备 PiN 二极管的绝大部分特征。

研究团队拟将高压大电流碳化硅器件的设计和制造方法，转用于低压小电流的高温半导体器件；与电力电子器件主要用于开关应用不同，此时，研究团队的主要关注点，是在低压小电流的条件下，SiC JBS 主要参数的高温特性。

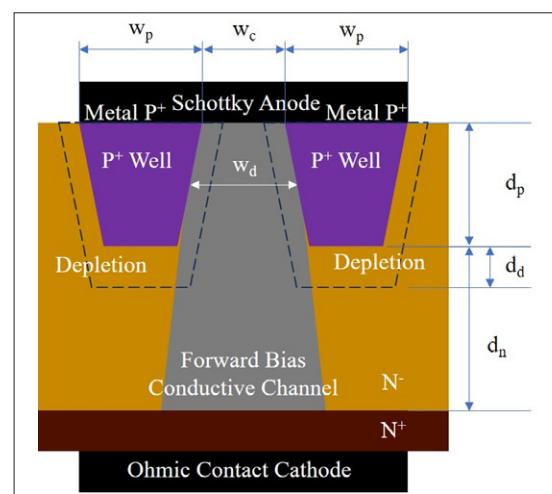

### 1.2 SiC JBS 的基础理论

SiC JBS 的基础理论和设计，前人已有诸多研究，给出了精确的理论计算公式，并得到了实践的检验<sup>[14-22]</sup>；这些计算公式除了依赖于器件的尺寸参数，也需要掺杂浓度等工艺参数；图 2 给出了 SiC JBS 剖面 (立面) 尺寸参数，其中  $w_p$  为 P 阵宽度， $w_c$  为相邻 P 阵间距； $w_d$  为掩模板宽度； $d_p$  为 P 阵深度， $d_d$  为零偏压时的耗尽层厚度，而  $d_n$  为 N 外延层的厚度。

图2: SiC JBS 的尺寸参数

SiC JBS 的主要表征参数有正向压降 ( $V_F$ )、正向导通电阻 ( $R_{ON}$ ；或比导通电阻,  $R_{ON,SP}$ )、正向电流 ( $I_F$ ；或正向电流密度,  $J_{FS}$ )，以及反向击穿电压 ( $V_{BK}$ ) 和反向漏电流 ( $I_R$ ；或反向漏电流密度,  $J_{RS}$ ) 等；鉴于研究团队的探索目标是器件的高温特性，所以主要关注器件的  $V_F$ 、 $I_F$  和  $I_R$  等参数在目标温区的变化情况；对于  $V_F$  有<sup>[17]</sup>，

$$V_F = \frac{n k T}{q} \ln \left( \frac{J_{FS}}{A T^2} \right) + n \varphi_B + J_{FS} R_{ON,SP} \quad (1)$$

这里，n 为理想因子（取决于制程，常值 1~2），k 为“波兹曼常量”(Boltzmann Constant,  $1.380649 \cdot 10^{-23} \text{J/K}$ )，T 为节温 (K)，q 为“电子电荷量”(Electron Charge,  $1.602177 \cdot 10^{-19} \text{C}$ )；A 为“理查德森常量”(Richardson Constant, 约为  $140 \text{A/cm}^2 \text{K}^2$ )， $\varphi_B$  为 SiC JBS 的势垒高度，理论和经验值均为  $1.11\sim1.15$  电子伏特 (eV，常值  $1.602177 \cdot 10^{-19} \text{J}$ )；而  $J_{FS}$  可由下式计算<sup>[18]</sup>，

$$J_{FS} = A T^2 e^{\frac{-q \varphi_B}{k T}} \left( e^{\frac{q V_a}{k T}} - 1 \right) \quad (2)$$

$J_{FS}$  的单位为  $\text{A/cm}^2$ ； $V_a$  为中间变量，可计算为，

$$V_a = \varphi_B + \frac{k T}{q} \ln \left( \frac{w_c + 2 w_p}{w_d} \cdot \frac{J_{FS}}{A T^2} \right) \quad (3)$$

而对于  $J_{RS}$ ，则有<sup>[18]</sup>，

$$J_{RS} = A T^2 e^{\frac{-q}{k T} (\varphi_B - \Delta \varphi_B)} \quad (4)$$

式 (4) 中考虑了势垒降低效应的势垒变化量；实际上对于 SiC JBS， $\Delta \varphi_B$  是可以忽略的；由以上各式可知，SiC JBS 的表征参数，主要与节温、势垒高度和二极管的详细尺寸相关，而势垒高度则与 SiC 外延片的 N- 浓度、阳极金属选择相关；在给定外延片、阳极金属，确定了设计尺寸之后，制程工艺过程参数（离子注入和温度曲线等）就成为决定器件参数散布和高温特性的决定性因素。

### 1.3 研究课题的技术路径

项目团队的初始考虑，是如何利用现有普通的 4H-SiC SBD 和 MOSFET 制程，即常见的高压大电流电力电子 SiC 制程，来多快好省地制作测试样品；经过充分调研，基于 4H-SiC 外延片的可获得性，研究团队设计了一颗 1200V60A 的 4H-SiC JBS；通常，AFE 的供电电压一般不超过 60V，航空应用的常见供电电压为 270V，石油钻探的供电电压则常用 500V 的供电电源；所以，1200V60A 的 SiC JBS，对于高温半导体的极限应用，是一个适当的探索起点。

## 2 4H-SiC JBS 芯片设计

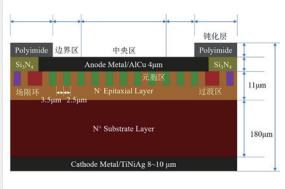

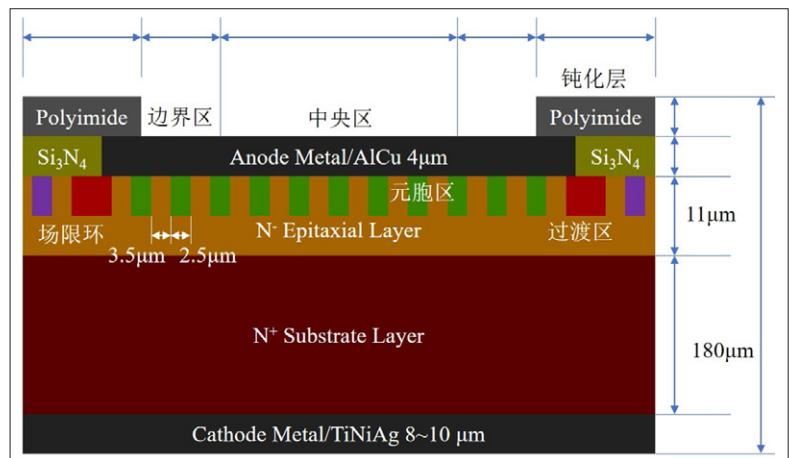

### 2.1 器件的平面设计

参考图 3，芯片的表面区域被划分为“终接区”(Edge Termination Area)、“边界区”(Boundary Area) 和“中央区”(Central Area) 三个区域；终接区布置了终结环(Termination Loop)，在边界区、中央区布置了 JBS 元胞，密度安排有所不同；有些设计在中央区域，还增加了“反向 SBD”(Reversed SBD, RSBD)；有些设计在边界区域也加入了 RSBD，本次的 DUT 设计未予采用。

图3: 4H-SiC JBS

芯片的平面设计

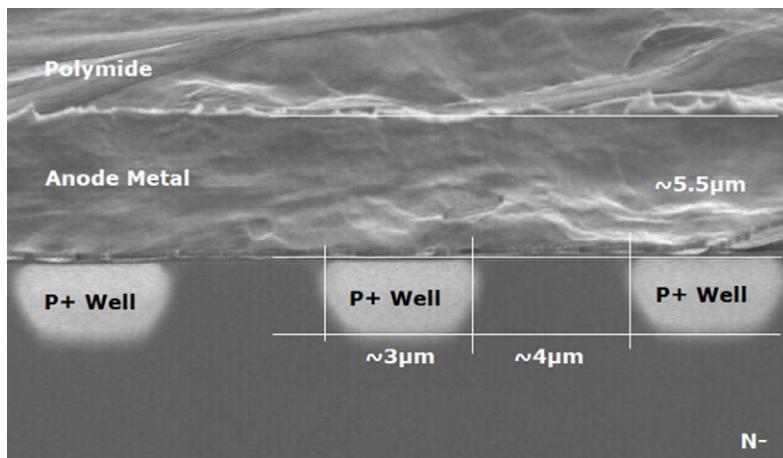

### 2.2 器件的立面设计

图 4 展示了器件的立面剖面构造，图中场限环，宽度一般为  $0.5\sim2.0 \mu\text{m}$ ，间距为  $0.5\sim2.0 \mu\text{m}$ ；边界区域总宽为  $50 \mu\text{m}$ ，中央区域的面积则依据过流能力要求，尺寸可调；立面厚度尺寸，芯片总厚度  $180 \mu\text{m}$ 、外延层  $11 \mu\text{m}$ ，这是常见的 4H-SiC 外延片厚度；图中亦可见 P 阵列，宽度为  $\sim3 \mu\text{m}$ ，P 阵间距为  $\sim4 \mu\text{m}$ ，数量取决于金属 P 极的尺寸，本次的 DUT 设计，P 极宽度为  $500 \mu\text{m}$ ，可以容纳大约 80 个 P 阵。

SiC JBS 的立面尺寸与平面尺寸一样，均可视需要缩放；本次的 DUT 设计，尺寸偏大，后续设计将予以缩减。

图4: 4H-SiC JBS芯片的立面设计

### 2.3 器件的工艺尝试

研究团队与制程工程师配合，对离子注入、掺杂浓度控制等，进行了一定的调整；针对各个工艺环节的温度曲线，进行了不同的配置尝试；研究团队也对惰性气体及其压力的配置等做了一定的探索，例如高温退火时配置不同的气体、压力组合等等。

如前所述，低掺杂度是制作 SiC JBS 的前提条件；DUT 的 N<sup>-</sup>掺杂浓度为  $1 \times 10^{16}/\text{cm}^3$ ，由外延片供应商控制，制程进行了必要的测试验证；P 阵的浓度，最终确定为  $6 \times 10^{18}/\text{cm}^3$ ；测试样品制作完成后的剖面电镜图，参见图 5。

图 5 中可见，由于 SiC 材料的特性，几乎没有横向扩散，P 阵的尺寸可以得到精确的控制，P 阵的形貌一致性非常理想。

### 2.4 器件的制造和高温封装

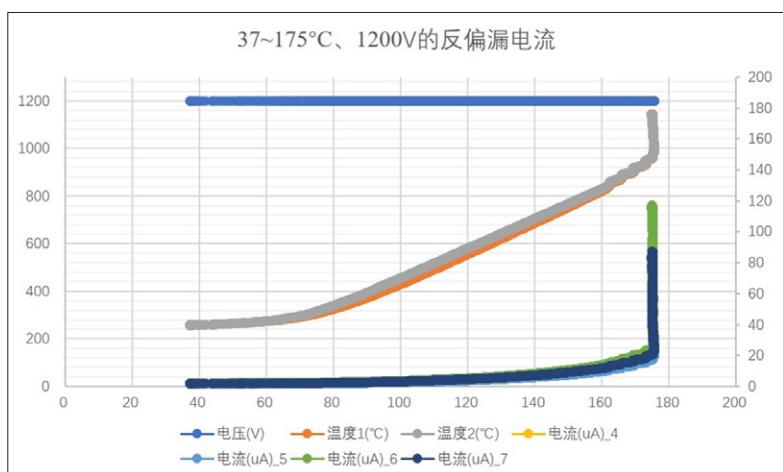

DUT 采用了普通的 SiC MOSFET 制程，生产编号为 C-ME033-5；制程的“晶圆级测试”(Chip Probing Test, CP Test) 之高压反偏漏电流数据，

图5：工艺完成后的P Well形貌和尺寸

图6：CP Test数据曲线

参考图 6，竖轴左为反偏电压 (1200V)，竖轴右为漏电电流 (200μA 量程)，横轴为环境温度；图的中间橙棕色曲线为 2 个结温探头的读数，图的下方为 4 个电流探头的读数；显然，结温从 65°C 左右开始以较大斜率线性升高，在环境温度 175°C 时几乎垂直上跳，同时，4 个电流探头的读数也垂直起跳，从早前的约 20 μA 迅速拉抬到接近 80~120 μA，约为 37°C 时电流读数 (<2 μA) 的 40~60 倍。

当然，此处的漏电流值是在 1200V 高压反偏条件下测得的，如前所述，高温半导体器件的 AFE 应用并不需要这么高的电压；限于测试条件，研究团队选择了 TO-247-2 高温封装的 DUT 用以进行高温测试挑战；该封装底面 (N 极) 采用银烧结工艺，正面 (P 极) 采用了常规的邦定工艺，具体为 350μm 铝线邦定；塑封材料，研究团队选择了常见的 EME-E500HA 高温环氧树脂成型材料，标称耐温可达 350°C。

## 3 高温测试

### 3.1 测试内容与测试方法

CP 测试的温度已达 175°C，因此研究团队选择了环境温度 200、225、250、275 和 300°C，5 个温度点位，测试了 30 个 DUT；研究团队的主要关注点为，DUT 的正向电压、正向电流和反向漏电流这三个关键指标，在 200~300°C 温变区域的变化情况，分析在较低电压下 SiC JBS 与高压条件下参数的差异。

### 3.2 测试环境

高温测试，选择了某型高温测试机台，参考图 7；该测试机台采用电调高速控温，理论温度可达 300°C，但实测只能达到 281°C。

图7：高温测试机台

### 3.3 测试结果及分析

#### 3.3.1 测试前后的样品外观

图8可见，DUT塑封材料的外观，除了激光标识字符发黑之外，塑封本体未受高温影响；金属电极（铝镀镍材质）在高温烘烤后，有氧化现象出现。

#### 3.3.2 测试数据

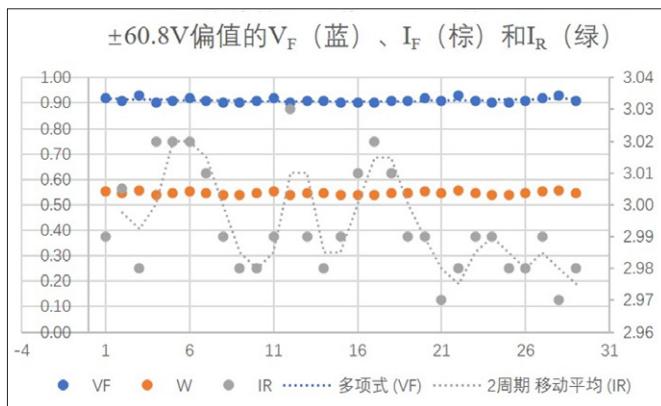

对于30个DUT，研究团队首先测量了常温状态下SiC JBS的伏安特性，偏置电压设置为±60.8V；实测正向偏置时，使用了一个输出电压自动可调的恒流源，没有串联限流电阻，

图8：测试前后的器件外观

设定限流为600mA恒流；常温正向测试的结果，各个DUT的表现完全一致， $V_F$ 为0.9V， $I_F$ 为600mA设定值；功耗为0.54W，导通电阻为1.5Ω，非常稳定；在常温、反偏60.8V条件下测试反偏漏电流，只有约3nA，非常稳定。常温状态的测试数据汇总，参见图9，

图9：常温±60.8V低压偏置的参数散布

图中，上端蓝色曲线为正向压降 $V_F$ ；橙色曲线为正向耗散功率（左轴）；下方的灰色曲线，为反向偏值得漏电流（右轴），实测数值最小为2.97nA，最大为3.03nA，散布范围恰好为±1%。

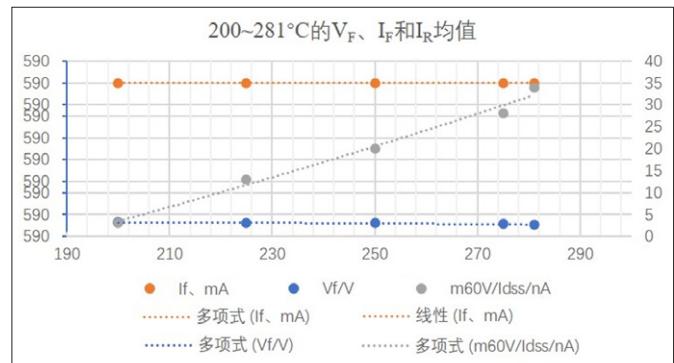

对于高温环境，研究团队分别在200°C、225°C、250°C、275°C和281°C共五个采样点，测试了30个DUT的 $V_F$ 、 $I_F$ 和 $I_R$ ；每个温度台阶间隔保持20分钟再予取数，保证器件结温与环境温度一致；在60.8V的正向偏置条件下，在200°C~281°C的温度区间， $V_F$ 从3.2V下降到2.5V， $I_F$ 则稳定保持在590mA，参见图10，

图10：高温60.8V正偏的伏安特性

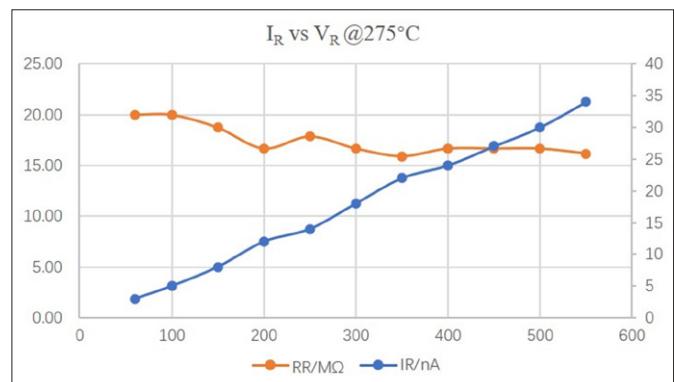

而在200°C~281°C的温度区间，在60.8V反向偏值的条件下，二极管的反向漏电流也始终保持在3nA，与常温时完全一致；对此，研究团队进行了现场分析，认为在较低反偏电压的条件下，二极管的反向漏电流极小，与结温几乎无关；为了证实这个推论，临时增加了在275°C高温环境中，60.8V~550V反向偏值电压下的漏电流测试，测试结果参见图11，

图11：结温275°C，60.8V~550V反偏的IR曲线

图中，蓝色曲线为反偏漏电流数值（nA），橙色曲线为反偏电阻值（MΩ）；在275°C的高温环境，DUT的反向漏电流，从60.8V时的3nA，上升到550V时的34nA，几乎是线性的；考虑到测试仪器的误差，后续研究团队将用经过高精度校准的仪器进行重复测试，并更换高温测试机台，保证300°C的温度测试目标。

#### 3.3.3 测试结果分析

测试数据证明，对于一个耐压1200V的大功率SiC JBS，在低偏置电压条件下，在测试的温变范围内， $V_F$ 和 $I_R$ 呈线性变化的趋势，而 $I_F$ 则几乎没有变化；这些结论，非常有利于设计运算放大器、基准电源和数模转换器等高温半导体器件的温度补偿电路。

而在275°C的环境温度条件下，当偏置电压从60.8V上升到550V时，DUT的反向漏电流依然表现出理想的线性；这说明，如果按照高压大电流标的来设计高温SiC MOSFET，在供电电压较低时，至少在60~550VDC供电电压区间，SiC MOSFET的高温特性，是可以准确预测的。

## 4 结论

本次测试的目的是验证用现有的、普通的 SiC 制程工艺制作的 SiC JBS，具有实现高温半导体器件的潜力；遵循高压大电流电力电子 SiC SBD 的设计和制程，制造可用于极限环境的高温半导体器件，是完全可行的技术路径；最为重要的是，这条技术路径并不需要特殊的制程装备，也不需要巨量的研发经费。

研究团队将致力于缩小现有 SiC JBS 样品的面积，减少 P 阵的数量，进而缩小  $V_F$ 、 $I_F$  的散布范围，降低  $I_R$  和 P-N 节电容的数值，并进行测试验证；研究团队将会积累测试数据，从目标结温 300°C 开始，逐步展开高温 SiC MOSFET、运算放大器和逻辑门等 AFE 所需的、系列高温半导体器件的设计，制造这些高温半导体器件，并验证其可靠性与寿命，

逐步将其国产化、系列化和商用化。

理论上，SiC 材料的耐温可达 1650°C；未来，研究团队不仅聚焦于 SiC 高温半导体器件的产品设计，而且也会持续挑战更高的工作结温边界。CS

### 作者简介：

杨良（1963-），男，北京人，清华大学系统工程硕士，清华大学工程博士在读，工程师，现任江苏晶利恒半导体科技有限公司 CTO，目前主要从事高压大电流 4H-SiC SBD/MOSFET 芯片的设计和制造，及 4H-SiC JBS 和 MOSFET 高温半导体器件的探索性研究。

## 扩展阅读

- [1] BRUCE W. O, BILL J. J, MARK R. L, SOI CMOS for Extreme Temperature Applications[R], Plymouth, Minnesota, USA, Honeywell Aerospace, 2007

- [2] CHRISTIAN S, ALESSANDRO C, MAKSYM P, et al., Design Criteria of High Temperature Integrated Circuits Using Standard SOI CMOS Process up to 300°C[J], New York, USA, IEEE Access, Open Access Journal, Vol 12, 2024

- [3] GRELLA K, VOGT H, PASCHEN U, High Temperature Reliability Investigations of EEPROM Memory Cells Realised in Silicon-on-Insulator (SOI) Technology[C], Oxford, UK, IMAPS High Temperature Electronics Network (HiTEN), 2011

- [4] KELBERER A, DREINER S, GRELLA K, et al., Experimental reliability studies and SPICE simulation for EEPROM at temperatures up to 450 °C[C], Cambridge, UK, International Conference and Exhibition on High Temperature Electronics Network (HiTEN), 2015

- [5] ANDREA G, LIONELLO D, DOMENICO A, et al., SOI-based, High Reliable Pressure Sensor with Floating Concept for High Temperature Applications[C], Brescia, Italy, EUROSENSORS 2014

- [6] REBERTO S, EDGARD C, JARED H, et al., A Very High Temperture (400+°C) Inverter for Energy Storage Applications Utilizing Silicon on Insulator (SOI) and Silicon Carbide (SiC) Electronics[R], Fayetteville, USA, Arkansas Power International, Inc. (APEI), 2010

- [7] KURTZL A. D, NEDL A. A, EPSTEIN A. H, Improved Ruggedized SOI Transducers Operational Above 600°C[R], Lexington, USA, Twenty-First Transducer Workshop, 2004

- [8] KURTAL A. D, NEDL A. A, EPSTEIN A. H, Ultra High Temperature, Miniature, SOI Sensors for Extreme Environments[C], Santa Fe, USA, IMAPS International HiTEC Conference, 2004

- [9] PHILIP G. N, DAVID J. S, MICHAEL J. K, et al., Recent Progress in Extreme Environment Durable 4H-SiC JFET-R Integrated Circuit Technology[R], Cleveland, USA, NASA Glenn Research Center, NASA, 2021

- [10] MICHAEL J. K, PHILIP G. N, Practical 4H-SiC JFET-R Analog Integrated Circuit Design for Extreme Environment Applications[R], Cleveland, USA, NASA Glenn Research Center, NASA, 2021

- [11] PHILIP G. N, DAVID J. S, CHEN L. Y, et al., Demonstration of 4H-SiC Digital Integrated Circuits Above 800 °C[J], Cleveland, USA, IEEE ELECTRON DEVICE LETTERS, VOL. 38, NO. 8, 2017

- [12] PHILIP G. N, DAVID J. S, MICHAEL J. K, et al., Demonstration of 4H-SiC JFET Digital ICs Across 1000 °C Temperature Range Without Change to Input Voltages[R], Cleveland, USA, NASA Glenn Research Center, Ohio Aerospace Institute, 2019

- [13] CHEN L Y, PHILIP G. N, DAVID J. S, et al., A 96% Alumina based Packaging System for 500°C Test of 4H-SiC Integrated Circuits[R], Cleveland, USA, Technology Crossover Extra Vaganza, 2021

- [14] PEREZ R., VELLVEH M., GODIGNON P., et al, Analysis of 1.2 kV JBS Rectifiers Fabricated in 4H-SiC[J], Bristol, UK, SEMICONDUCTOR SCIENCE AND TECHNOLOGY, 21 (2006) 670–676, 2006

- [15] ZHU L, PAUL T, KENNETH A. J., et al, Design, Fabrication, and Characterization of Low Forward Drop, Low Leakage, 1-kV 4H-SiC JBS Rectifiers[J], New York, USA, IEEE TRANSACTIONS ON ELECTRON DEVICES, VOL. 53, NO. 2, 2006

- [16] ZHU L, CHOW T P, Analytical Modeling of High-Voltage 4H-SiC Junction Barrier Schottky (JBS) Rectifiers[J], San Jose, USA, IEEE Transactions on Electron Devices, TED, Volume: 55, Issue: 8, 2008

- [17] KHEMKA V, PATEL R., CHOU T. P., et al, Design Considerations and Experimental Analysis for Silicon Carbide Power Rectifiers[J], New York, USA, Solid State Electronics, 43, 1999

- [18] TETSUO H., TAKASHI S., Reverse Characteristics of a 4H-SiC Schottky Barrier Diode[C], Tsukuba, Japan, Materials Science Forum Vols. 389-393 (2002) pp. 1169-1172, 2002

- [19] AMIT S. K., Development of Process Technology for Fabrication of 4H-SiC Silicon Carbide Schottky Barrier Diodes[R], Singapore, Nanyang Technological University, 2009

- [20] SEONG J. M., MYEONG C. S., NGOC T. N., et al, High-Performance Temperature Sensors Based on Dual 4H-SiC JBS and SBD Devices[J], Basel, Switzerland, MDPI, 2020

- [21] JAN V., PAVEL H., STANISLAV P., et al., Impact of Electron Irradiation on the ON-State Characteristics of a 4H-SiC JBS Diode[J], New York, USA, IEEE TRANSACTIONS ON ELECTRON DEVICES, VOL. 62, NO. 6, 2015

- [22] DENIS P., DHERBECOURT P. LATRY O., et al., Robustness of 4H-SiC 1200 V Schottky Diodes under High Electrostatic Discharge Like Human Body Model Stresses[C], St. Etienne du Rouvray, France, Diamond & Related Materials, 2014

# 为 GaN 加入超结结构

通过超结技术，增强型 GaN 晶体管的阻断电压突破 10kV

作者：魏进、沈波；北京大学

**如**今，GaN 功率器件已在消费电子领域广泛应用，并取得了显著的市场份额。它们通常用于阻断几百伏电压，其中 650V 增强型高电子迁移率晶体管（HEMT）尤为普及。

然而，在更高电压等级下，SiC 被视为取代传统硅功率技术的主要竞争者。对于 GaN 功率 HEMT 在千伏级电压下的应用，目前仅有少量研究报道，而这类电压等级正是高压电网、轨道交通和工业应用所必需的。尽管如此，GaN 仍具备巨大潜力，其理论性能优于现有技术。

开发适用于千伏级电压的 GaN 器件面临两大挑战：

1. 关键性能指标（FOM）远低于理论值。该指标等于阻断电压的平方除以单位面积导通电阻。缩小这一差距至关重要，因为它能使 GaN 器件在更小尺寸下实现相同击穿电压，从而通过大幅缩小芯片尺寸降低成本。

2. 高压应力下严重的动态导通电阻退化。这源于 GaN 中显著的电荷俘获效应，尤其在千伏级电压下更为明显。

提升超高压 GaN 晶体管性能指标的可行方法是：在不增加栅漏距离的前提下提高阻断电压。这可以通过引入复杂的场板、栅极终端扩展、表面处理或添加 GaN 帽层等方式实现。然而，这些方案都伴随着工艺复杂性、可靠性和性能之间的权衡，因此在实际应用中需谨慎评估。

一个前景广阔 的替代方案是超结（Superjunction）结构，该结构已成功应用于硅功率器件中，显著提升了性能指标。超结被视为管理电场、提升 GaN 器件阻断电压的有力候选方案。然而，在增强型横向 GaN 器件中实现超结结构非常困难。

## GaN 超结技术的突破

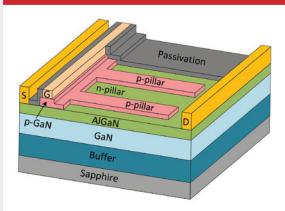

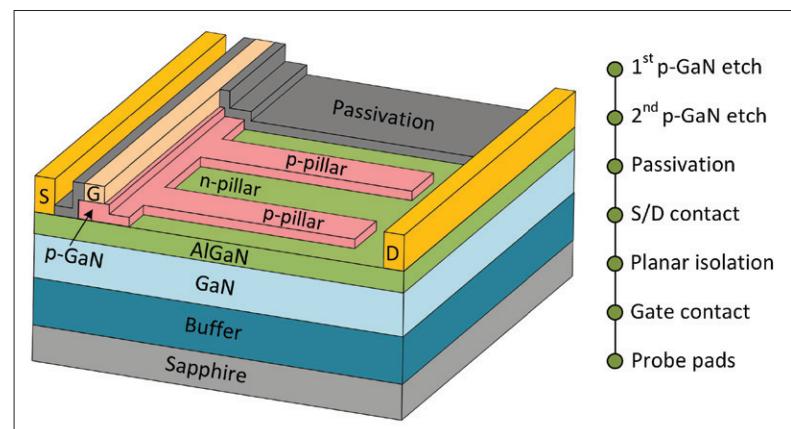

最近，北京大学团队提出了一种基于标准增强型 p-GaN 栅 HEMT 平台的新型超结概念（见图 1）。

该器件采用标准 p-GaN 栅 HEMT 外延片制造，具备增强型工作特性。超结结构通过在垂直于电流方向上交替排列 p 型/n 型“柱状”区域实现：

- p 柱为薄层 p-GaN 条

- n 柱为相邻 p 柱之间的二维电子气（2DEG）条

- p 柱宽度固定为 4 μm，通过光刻调节 2DEG 条宽度实现电荷平衡。这种方法为研究器件性能随电荷平衡变化提供了自由度。

器件制造基于 2 英寸蓝宝石衬底 GaN 外延片，结构包括：

90nm p-GaN 层 - 15nm Al<sub>0.2</sub>Ga<sub>0.8</sub>N 势垒层 - 200nm 非掺杂 GaN 层 - 缓冲层

制造流程包括：

1. 栅极区域外部分刻蚀 p-GaN；2. 第二次刻蚀定义 p 柱结构；3. 300°C 下沉积 SiO<sub>2</sub> 层；4. 源漏欧姆接触（Ti/Al/Ni/Au, 810°C 氮气退火 30 秒）；

图1：所提出的超结 p-GaN 栅 HEMT (SJ-HEMT) 的结构与工艺流程序列图。

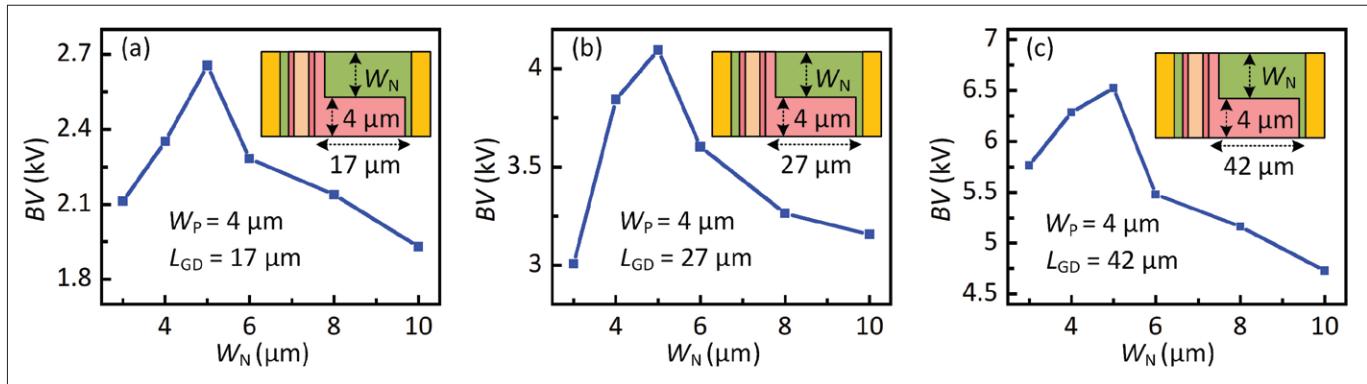

图2：当 p 柱宽度固定为 4  $\mu\text{m}$  时，不同栅-漏距离 ( $L_{GD}$ ) 的超结 HEMT 阻断电压 (BV) 与 n 柱宽度 ( $W_N$ ) 的实测关系。对所有  $L_{GD}$  而言， $W_N/W_p = 5 \mu\text{m}/4 \mu\text{m}$  (电荷平衡点) 均获得最高阻断电压。

5. 氟离子注入实现平面隔离；6. 栅极 Ni/Au 堆叠沉积并在氧气中退火形成 p-GaN 欧姆接触；7. 添加探针垫。

值得注意的是，该超结 HEMT 的制造工艺与标准 p-GaN 栅 HEMT 兼容，仅需增加一次 p-GaN 刻蚀步骤。因此，该结构可在现有代工厂中轻松实现。

### 电荷平衡设计

电荷平衡是所有超结器件的核心。在我们提出的超结 HEMT 中：

- 低压漏极应力下，p 柱与 n 柱相互耗尽，耗尽区随应力增加而扩展

- 高压下，p 柱与 n 柱完全耗尽，耗尽区迅速扩展

此行为使得电场分布更均匀，击穿电压更高。然而，由于 GaN 器件中存在极化电荷、不完全电离和内部俘获等复杂机制，实现电荷平衡比硅器件更具挑战。

为此，团队开发了类似 JFET 的测试器件，用于研究电荷平衡效应。通过测试 n 柱与 p 柱电流，分析其在反向偏压下的耗尽行为。当 n 柱与

p 柱在同一偏压下同时耗尽时，即实现电荷平衡。

测试结果表明：

- 当 n 柱宽度为 5  $\mu\text{m}$ 、p 柱为 4  $\mu\text{m}$  时，实现电荷平衡

- 这是首次在文献中实验验证 GaN 器件的电荷平衡

击穿电压测试进一步验证了电荷平衡效果（见图 2）。固定 p 柱宽度为 4  $\mu\text{m}$ ，研究不同栅漏距离 ( $L_{GD}$ ) 下，n 柱宽度与阻断电压的关系。结果表明：在 n 柱宽度为 5  $\mu\text{m}$  时，所有  $L_{GD}$  下均获得最高阻断电压，再次验证电荷平衡点为 n 柱 5  $\mu\text{m}$  / p 柱 4  $\mu\text{m}$ 。

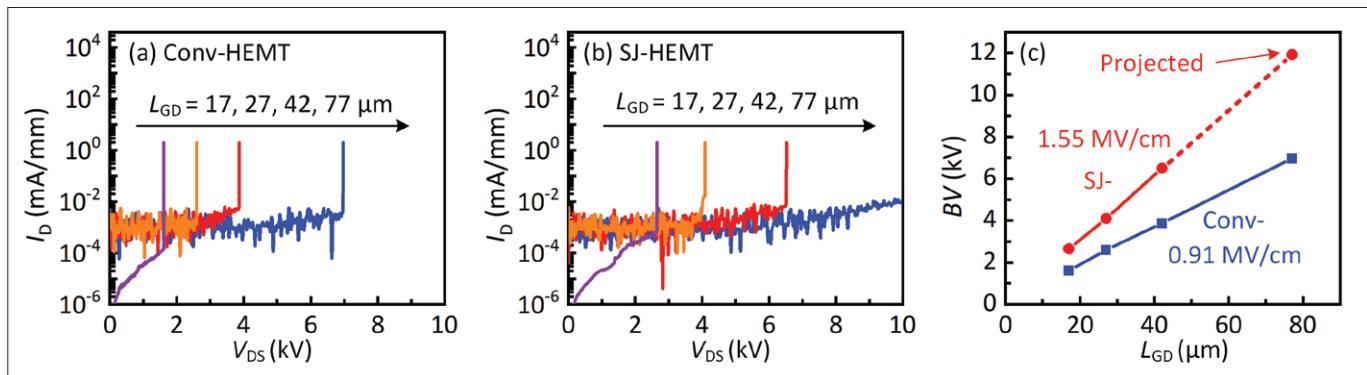

对比传统 p-GaN 栅 HEMT ( $L_{GD}$  从 17  $\mu\text{m}$  到 77  $\mu\text{m}$ ) 发现：传统器件平均击穿场强为 0.91 MV/cm，最大阻断电压 6,965V，结器件平均击穿场强达 1.55 MV/cm，42  $\mu\text{m}$   $L_{GD}$  下击穿电压为 6,525V。77  $\mu\text{m}$   $L_{GD}$  下，超结器件击穿电压超过 10kV，线性外推值为 11,935V。

这是首次实验展示击穿电压超过 10kV 的增强型 p-GaN 栅 HEMT，是横向 GaN 功率器件在高压应用领域的重要里程碑。

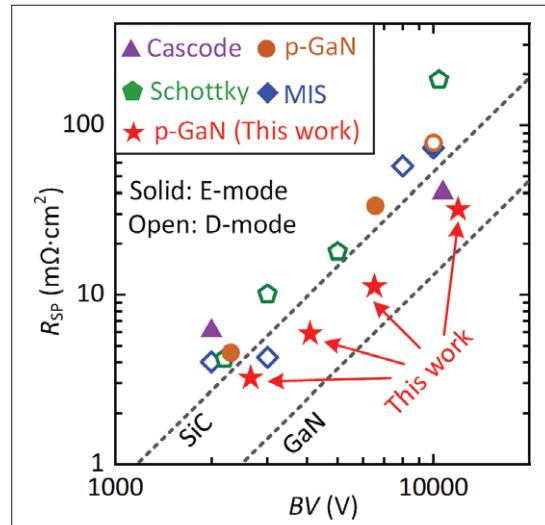

这一击穿电压的大幅提升，为千伏级器件显

图3：(a) 传统 p-GaN 栅 HEMT 与 (b) 超结 HEMT (n/p 柱宽度分别为 5  $\mu\text{m}$ /4  $\mu\text{m}$ ) 的动态电流-电压曲线；(c) 阻断电压 (BV) 随栅-漏距离 ( $L_{GD}$ ) 的变化关系。对于栅-漏距离 77  $\mu\text{m}$  的超结 HEMT，实测阻断电压超过 10 kV (设备量程上限)，线性外推值为 11,935 V。

图4: 超结 HEMT 在 6.5 kV 漏极应力后，动态导通电阻与静态导通电阻之比低至 1.50。

著缩短  $L_{GD}$  打开了大门，同时还能使比导通电阻更低、有源区面积较传统设计减少 20–40%。更关键的是，据数值仿真显示，电荷平衡的超结 HEMT 实现了电场分布优化，在同等阻断电压下峰值电场强度更低。借助这一改进，超结 HEMT 有望提升高压可靠性，对热电子效应、高温反向偏置应力以及电流崩塌等具有更强的抵御能力。

## 性能提升

该超结 HEMT 具备独特优势：导通状态下，p 柱与 n 柱下的 2DEG 均参与导电；而传统硅超结 MOSFET 仅 n 柱导电。

在导通状态下，当 p 柱与 p-GaN 栅直接相连时，p 柱下方的二维电子气 (2DEG) 可通过场效应产生。测试显示 n 柱与 p 柱下的薄层电阻分别为  $416\Omega/\square$  和  $411\Omega/\square$ ；导通电阻无明显退化；所制备的超结 HEMT 在  $L_{GD}$  为 77  $\mu\text{m}$  时，阈值电压为 0.9 V (定义在  $10 \mu\text{A mm}^{-2}$  的漏极电流密度下)，满足电力系统对增强型工作的要求。其对应的导通电阻为  $36.4 \Omega \cdot \text{mm}$  (定义在  $V_{DS}=1 \text{ V}$ 、 $V_{GS}=3.5 \text{ V}$  条件下)，折合比导通电阻  $32.03 \text{ m}\Omega \cdot \text{cm}^2$ 。

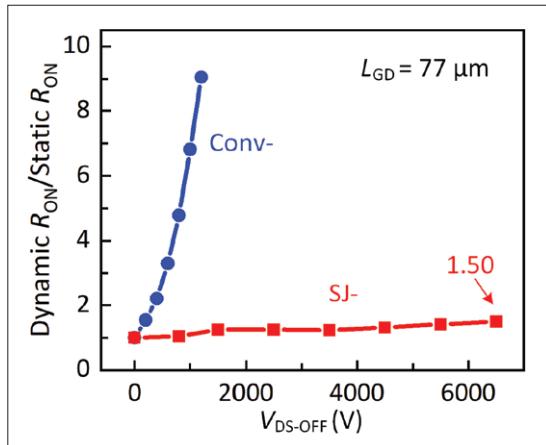

传统 GaN HEMT 的一个固有弱点是动态导通电阻退化，源于本征俘获效应导致的负电荷累积，这会造成额外的功率损耗。

此外，超结 HEMT 有效抑制了传统 GaN HEMT 中因电荷俘获导致的动态导通电阻退化问

图5: 超结 HEMT 与最新高压 (> 2 kV) GaN 功率器件的“比导通电阻-击穿电压”性能对比图。

题。其机制包括:p 柱中的空穴有效屏蔽表面陷阱；空穴注入 / 发光加速陷阱恢复。

凭借这些优势， $L_{GD}$  77  $\mu\text{m}$  的超结 HEMT 在承受高达 6500 V 的关态应力后，动态导通电阻与静态导通电阻之比仅为 1.50，达到超低水平。

基于上述结果可以得出结论：所提出的超结 HEMT 具有更高的稳定性与可靠性，在千伏级应用中展现出巨大潜力。据我们所知，本研究首次报道了 GaN 功率 HEMT 在 6.5 kV 漏极应力下的动态导通电阻特性。这一突破为 GaN 晶体管迈向超高压应用铺平了道路，结果证实超结 HEMT 技术克服了千伏级 GaN 器件实用化的关键可靠性障碍。

与现有最先进的高压 GaN 功率 HEMT 相比，超结 HEMT 在  $L_{GD}$  42  $\mu\text{m}$  下品质因数 (FOM) 高达  $3.81 \text{ GW cm}^{-2}$ ；在  $L_{GD}$  77  $\mu\text{m}$  下，阻断电压超过 10 kV，同时保持  $32.03 \text{ m}\Omega \cdot \text{cm}^2$  的比导通电阻，对应的预测 FOM 达到  $4.45 \text{ GW cm}^{-2}$ 。这一里程碑式成果重新定义了单沟道 GaN HEMT 的性能上限。

更值得关注的是，超结 HEMT 与常规器件工艺高度兼容，且天然具备单沟道平面结构，便于构建高压集成平台。这些进展成为弥合 GaN 材料理论潜力与超高压实际器件性能差距的关键一步。OSc

## 扩展阅读

- ▶ 1. J. Yang et al. “10-kV E-mode GaN Lateral Superjunction Transistor” in IEDM Tech. Dig., Sec. 25-3 (2024)

- ▶ 2. J. Yang et al. “Charge Balance Design of 1200-V E-Mode p-GaN Gate HEMT Toward Enhanced Breakdown Voltage and Dynamic Stability” Electron Dev. Lett. 46 636 (2025)

# 用无缝 III-V 族集成革新硅基光子的竞赛

直接在硅上生长 III-V 族纳米脊激光器，绕过了现有集成方法的种种复杂步骤，为可扩展、低成本的光子集成电路（PIC）量产铺平道路

作者：Bernardette Kunert 与 Joris Van Campenhout, imec

**在**当今数据驱动的世界里，对更快、更高效的数据计算与传输需求正以前所未有的速度增长。除了日常对高分辨率图片即时访问、无缝视频流、沉浸式增强现实体验之外，人工智能与机器学习的快速扩张带来了更大挑战。这些技术依赖海量机 – 机数据交换，进一步放大了对高速、低延迟的需求。

为跟上这些需求，光数据传输必须超越传统长途网络，向芯片级延伸。这对光纤到户（FTTx）部署以及芯片间光互连都有影响——在这些场景中，超高速、低功耗的数据传输正变得愈发关键。随着数据量持续激增，优化传输效率的创新方案至关重要，其中重点在于降低每传输比特的功耗，以确保计算基础设施可扩展且可持续。

这一转型的关键技术是硅基光子，它利用已成熟的 CMOS 制造工艺，实现光学器件的大规模生产。然而，硅基光子集成电路（PIC）全面部署的长期障碍在于，它们缺少一个关键元素：光源。

由于材料本身的限制，硅无法高效发光。产业界迄今通过使用 III-V 族化合物半导体填补这一空白——这类材料因其卓越的光电特性而备受青睐。但将这些晶体材料集成到硅基光子中，一直是一项艰巨的工程挑战。

因此，目前大多数数据通信产品仍依赖在原生 III-V 衬底上单独加工的 III-V 光源，随后通过微组装激光封装或高精度倒装焊接技术，将其固定到硅基光子芯片上。这些混合集成方案虽有效，

却成本高、难以规模化，使得 PIC 器件昂贵且产量低。

为应对这一问题，产业界正在探索替代集成方法。例如，微转移印刷——一种后道工序，通过并行转移预制 III-V 组件到硅基光子晶圆，显著提高产能。另一种异构集成方案则采用裸片 – 晶圆键合，将未加工的 III-V 器件芯片先贴到硅基光子晶圆，再进行 III-V 器件图形化及 CMOS 后端金属互连。

后一种方法已获得商业牵引，目前至少两条商业量产线支持该工艺。然而，它对复杂键合技术及昂贵 III-V 衬底的依赖仍是瓶颈；此外，制造过程中衬底被当作废料丢弃，引发健康、安全及环境方面的担忧。

最终目标是在硅晶圆上直接单片生长 III-V 材料，从而摆脱对外部 III-V 衬底及复杂组装步骤的需求。然而，硅与 III-V 材料晶格结构差异巨大，导致单片生长时 III-V 层产生应变；应变释放后，会在 III-V 薄膜沉积过程中形成位错、尤其穿透位错等缺陷。这些晶体缺陷不仅出现在硅界面，还会贯穿整个器件堆叠，降低性能，使其无法商用。

## 纳米脊工程

数十年来，研究人员一直致力于控制不可避免的应变释放，并阻止位错缺陷穿透至有源层。探索的技术包括：在硅与 III-V 之间生长极厚的过渡缓冲层、采用退火处理修复部分缺陷、引入应变超晶格层以控制并隔离缺陷，使其局限在局部区域。然而，这些方法的成效有限。

一项突破性进展是首次在硅上单片生长 InAs 量子点激光器获得成功。这些零维纳米结构将载流子（电子与空穴）限制得比传统量子阱更紧——在量子阱中载流子可在二维平面内移动，而量子点中的电子与空穴更不易遇到缺陷，因此量子点结构比基于多量子阱的传统激光器更耐缺陷。凭借这些特性，量子点激光器已实现可用于未来 PIC 的可靠性水平。

推动单片生长及整体集成光子学进步的制造方法之一是“选择性区域生长”（SAG）。该技术仅在预定义的氧化硅图形内沉积 III-V 材料，减少大面积材料去除，使工艺比传统二维生长更高效。SAG 还可利用“深宽比捕获”（ART）：制作深槽以捕获驰豫缺陷，抑制其向器件上方传播。由于仅对硅衬底选定区域进行外延，而非整片覆盖，该方法还能减少应变，缓解裂纹形成及硅片翘曲等常见难题。

然而，基于 ART 的 SAG 也有缺点：对缺陷削减至关重要的窄沉积图形同时限制了可集成 III-V 材料的体积，从而制约了可制造器件的范围。

于是，“纳米脊工程”（NRE）应运而生——这是 imec 开创的尖端集成方案。通过用 MOCVD（实现选择性的首选沉积技术）精修 SAG，并以极窄、拉长的沟槽增强 ART，NRE 在高效抑制缺陷的同时显著增加了可用 III-V 材料的体积。这是通过持续超出沟槽图形的生长以及精心控制的纳米脊形貌实现的。

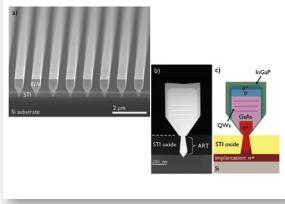

这一突破不仅拓展了基于 III-V 器件的设计空间，也重新定义了其功能。纳米脊本身即可作为波导，用于发光二极管、激光器、调制器、光

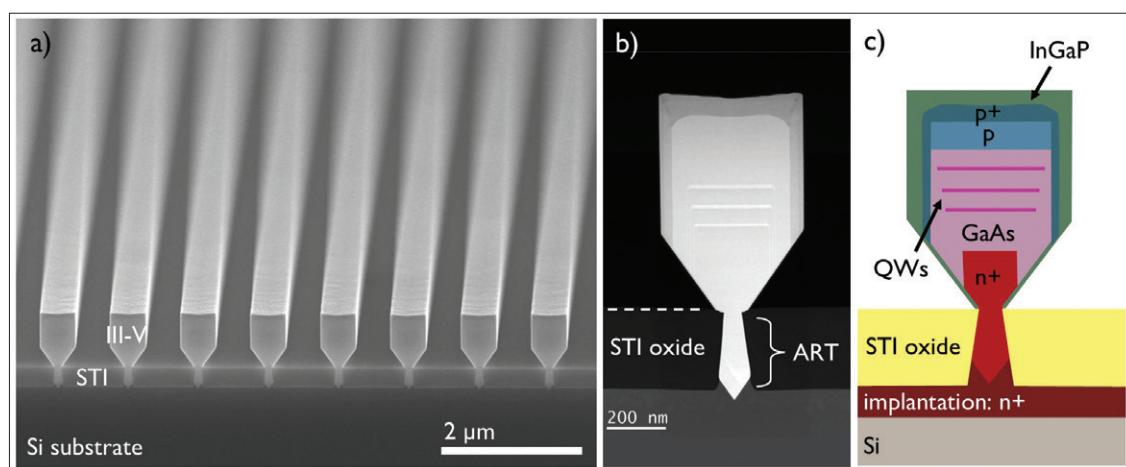

图1: (a) 在300 mm图形化氧化硅/硅晶圆上通过MOCVD生长的III-V族纳米脊阵列扫描电子显微镜图像。氧化硅图形采用浅沟槽隔离 (STI) 工艺制备。(b) III-V族纳米脊激光器横截面高角环形暗场扫描透射电子显微镜图像，突出显示不同的III-V材料体系。(c) 纳米脊器件堆叠示意图 (QW：量子阱；n<sup>+</sup>：重掺n区；p：p型掺杂区；p<sup>+</sup>：重掺p区)。

电探测器等光电子组件。此外，当多根纳米脊并联接触时，还可提供足够电流驱动异质结双极晶体管——一种常用作射频功率放大器的晶体管。

imec 近期的里程碑——在 300mm 硅片的 CMOS 中试线上完成纳米脊激光器全流程加工，标志着向可扩展、低成本、环境可持续地集成高质量 III-V 器件迈出了关键一步。

### 制造挑战

要将这一愿景变为现实，imec 研究人员必须克服三大难关。第一，确保在 300mm 硅衬底上无缺陷地生长纳米脊。ART 已被证明可在多种材料体系中减少失配缺陷，尤其对窄沟槽内的 GaAs 有效。然而，为使该方法生效，必须先在沟槽内完成完全应变弛豫，然后才能在其上均匀延伸纳米脊。为此，imec 团队优化 MOCVD 条件，促进 III-V/ 硅界面处的高效应变释放，并使穿透位错在沟槽内滑移。

一旦建立起均匀的 n 型 GaAs 基脊，我们便生长 InGaAs/GaAs 多量子阱堆叠作为激光的光学增益介质，接着沉积 p 型 GaAs 接触层，最后用 InGaP 层覆盖纳米脊波导，以增强载流子限制并减少 III-V 表面载流子损耗（见图 1）。

对未加工纳米脊的阴极发光测量显示，纳米脊波导中的失配缺陷密度极低，低于  $6 \times 10^4 \text{ cm}^{-2}$ ，对于如此薄的 III-V 层而言，这是非凡成就。

第二项挑战是设计低损耗的接触方案。通过 n<sup>+</sup> 离子注入硅层及沟槽内 n 型 GaAs 实现电子注入相对直接，但在纳米脊顶部建立稳固的 p 接触则更为棘手。若直接在纳米脊顶部使用连续金属条，会引入过大光学损耗。于是，我们沿纳米脊方向分布了孤立的 p 型插塞（p-plug）。为实现高效空穴注入，这些金属插塞被选择性地穿透 InGaP 层，直达 p 型 GaAs。这种周期性 p 接触设计引入独特的拍频模式，支持离散波导模式，与金属插塞阵列重叠最小。该现象也有助于单模激光工作。为制作法布里 – 珀罗激光腔，我们用干法刻蚀在纳米脊两端刻出反射面。

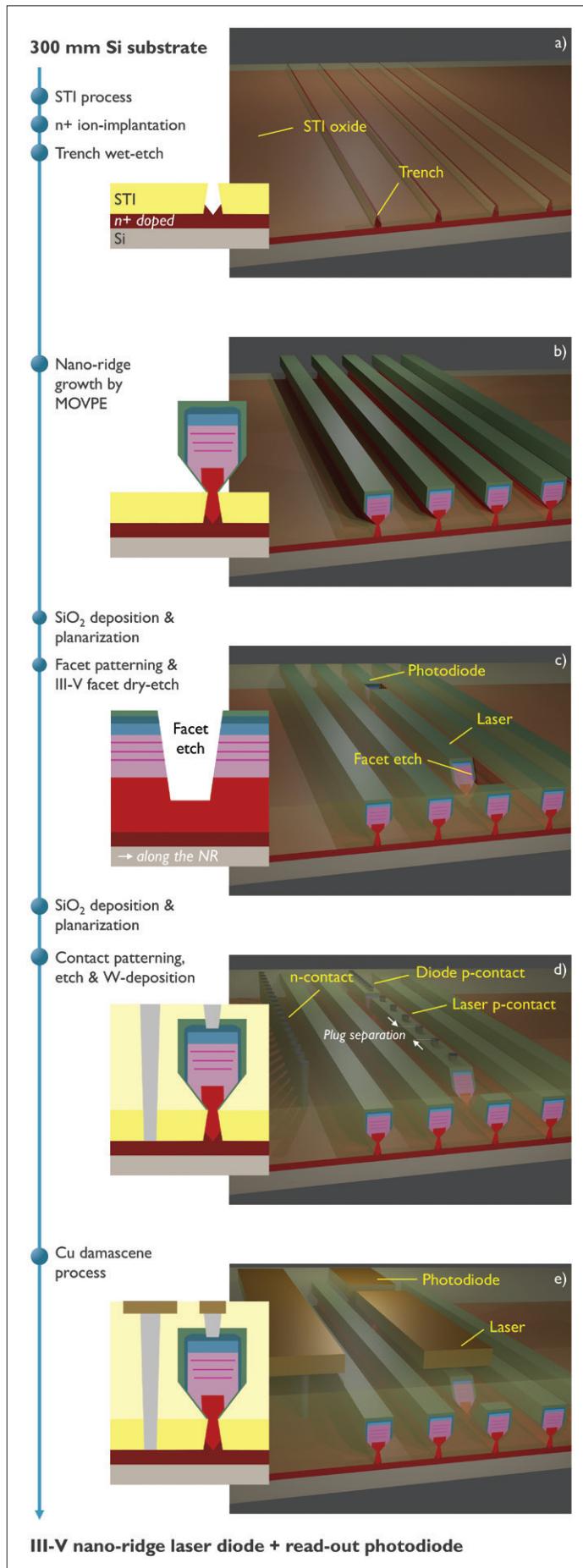

最后，在 CMOS 中试线内集成并加工 III-V 材料又带来一系列挑战。大多数半导体制造设备并非为 III-V 材料设计，甚至无法容忍 300mm 硅片上 III-V 残留带来的污染风险。此外，许多必要

◀ 图2：在imec CMOS中试线执行的300 mm简化工艺流程示意图（W: 钨；Cu: 铜）。更多细节见Y. D. Konick等，《自然》63763 (2025)。

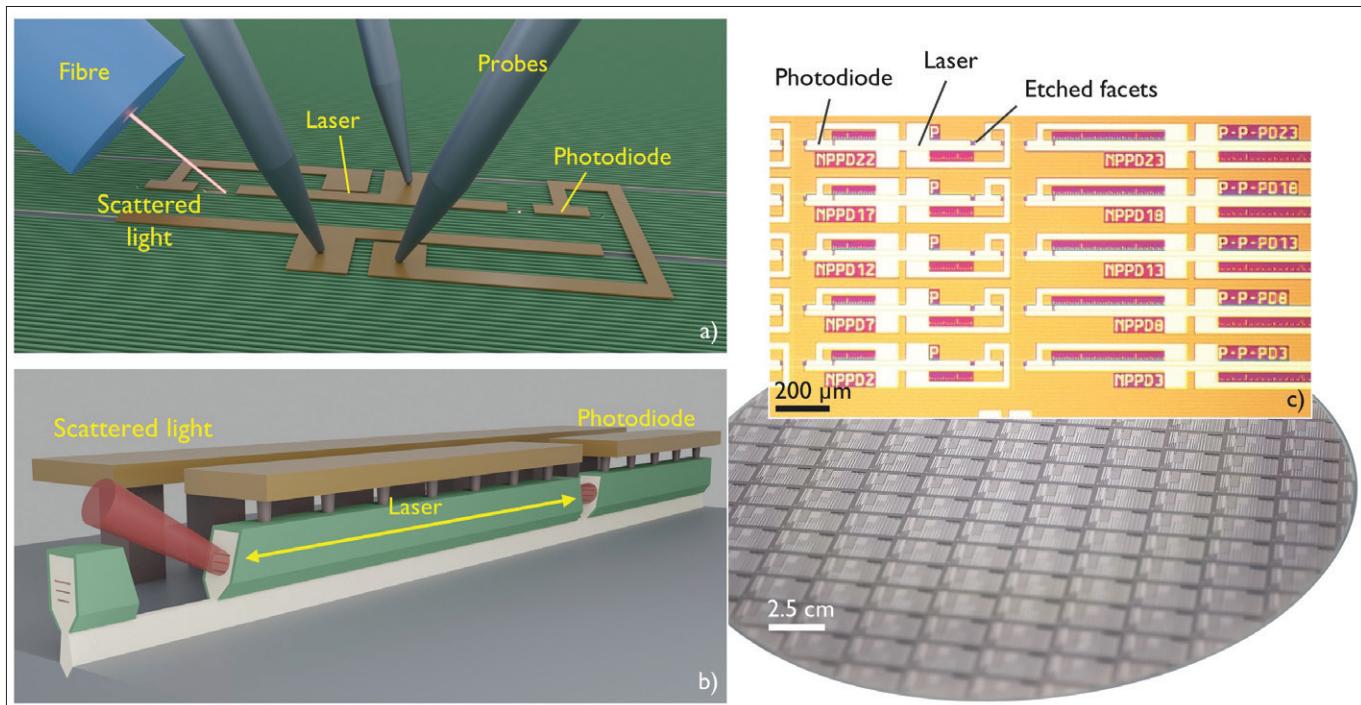

图3: (a) 晶圆级读出测试装置示意图：左侧端面向上散射的光可被多模光纤收集。三根电探针分别驱动纳米脊激光器与光电二极管。 (b) 纳米脊腔体示意图 (忽略氧化物)，由两个干法刻蚀端面构成，内置光电二极管收集右侧激光端面发出的光，左侧光被散射。 (c) 已加工器件的俯视光学图像。插图为完全加工后的300 mm晶圆照片。

工艺必须从零开发。我们依托 imec 富有的 III-V 材料加工经验，建立起受控的制造环境，以适应这些非标准 CMOS 流程。

鉴于全新顺序工艺步骤及器件可操作性固有的不确定性，我们设计了一套包含多种物理器件参数变化的掩膜版，系统评估激光腔长、沟槽宽度、p-plug 间距对器件功能的影响，从而提高成功概率。

为实现对这些纳米脊激光器的快速、晶圆级表征，我们创新性地在激光器同一线路上集成纳米脊光电探测器。这种耦合器件布局提供了一种优雅高效的方法，可在整片晶圆上获取性能统计，确保对器件运行进行全面评估。有关 300mm 工艺流程及测量配置的更多细节见图 2 与图 3。

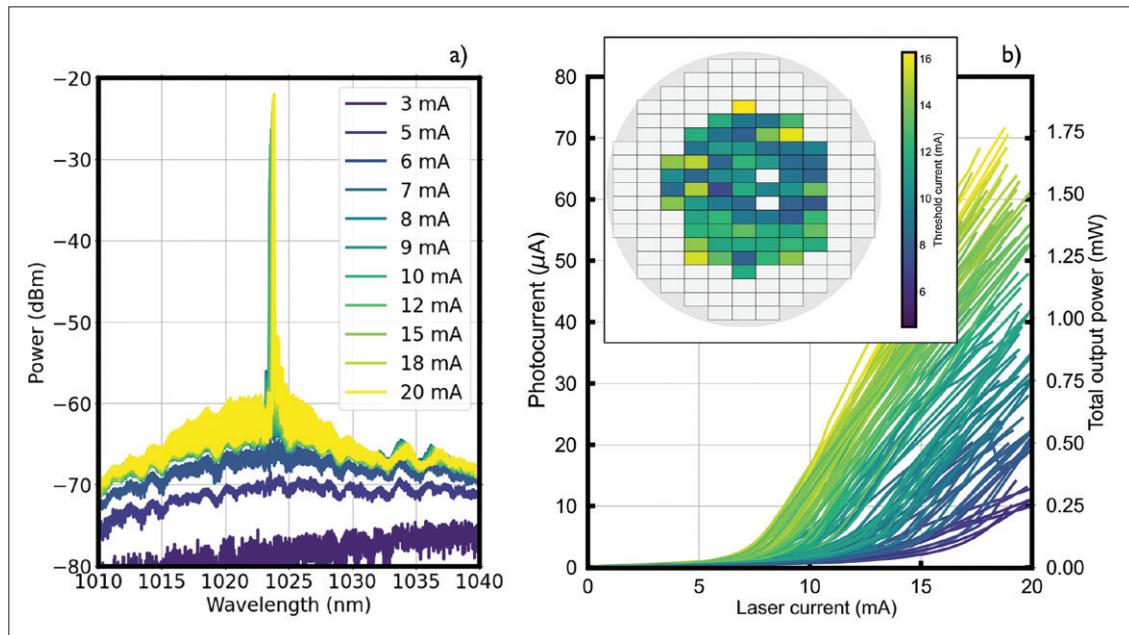

## 纳米脊激光器

利用晶圆级制造，我们对数千个 GaAs 纳米脊器件（包括激光器、光电探测器及测试结构）进行了读出测试，结果极具前景：超过 300 个功能纳米脊激光器在室温下发出约 1025 nm 激光，光电探测器电流呈现出清晰的阈值行为（见图 4）。

考虑到开创一条全新 300mm 工艺流程的风险——如短路、反射面质量不佳、接触电阻过高，这些发现标志着重大进步，证明纳米脊激光器可在大规模下可靠制造，使 III-V 族与硅的集成更

接近现实应用。

为验证上述结果，我们进行了额外测量：包括晶圆级顶部辐射激光检测，以及对切割后裸片端面发射光谱的裸片级分析。这些测试确认了激光工作，阈值电流低至 5 mA，斜率效率最高  $0.5 \text{ WA}^{-1}$ ，最大总输出功率 1.75 mW。对于亚微米截面的纳米脊而言，这些数值令人鼓舞。此外，由 p 接触插塞形成的周期光栅结构在法布里-珀罗谐振腔中起到稳定单模工作的作用，边模抑制比超过 30 dB。

为进一步提升集成效率，长期目标是实现 III-V 材料在硅上的直接外延生长，本工作已证明其可行性。

目前 NRE 技术的研发重点在于优化接触方案，以缓解局部高电流注入点，从而延长器件寿命。此外，我们正研究替代 GaAs 基光学增益介质，使激光发射波长红移，拓展应用范围。

另一有前景的方向是利用 III-V 纳米脊的波导特性，实现与硅基光子波导的高效耦合，从而开发外腔激光器，进一步提升该技术的多功能性。

一个特别值得注意的现象是：仅在 p-plug 间距超过  $3 \mu\text{m}$  的器件中观察到激光发射，这表明若插塞密度过高，顶部金属接触的吸收损耗将显著影响激光性能。然而，增大 p-plug 间距也带来性能权衡，每个接触点的电流密度随之升高。尽

图4: (a) 从1.4 mm长激光腔的解理端面收集的不同驱动电流下的光纤输出光谱。(b) 2 mm长器件的光电二极管电流(左)及对应总输出功率(右)随激光驱动电流的变化。插图为含功能性2 mm长激光器的裸片分布晶圆图, 颜色编码表示对应阈值电流。

管初步可靠性测试显示连续波激光发射超过500小时, 进一步研究揭示, p-plug处的高电流密度会诱发局部缺陷, 最终导致器件失效。

更令人鼓舞的是, 除p-plug周围区域外, 纳米脊波导其余部分保持高晶体质量, 未出现新增失配缺陷。这一发现表明, 通过进一步优化接触设计, 可显著提升这些纳米脊激光器的长期可靠性, 为硅基光子学铺平道路。

### 未来重点

据我们所知, 本演示首次在300mm硅片上成功实现全流程III-V纳米脊激光器。通过在硅上直接单片沉积III-V, 该方法摆脱了对III-V衬底及复杂键合技术的依赖, 并充分利用CMOS中试线的先进制造能力。这一突破对高量产规模、提高良率、降低生产成本至关重要, 是硅基光子

大规模普及的关键。然而, 尽管该成果意义重大, 纳米脊工程技术仍处于早期开发阶段。

此项工作是imec更广泛的III-V集成工艺路线探索任务的一部分。短期内, 研究重点仍是混合方案, 如倒装焊接及转移印刷; 中期来看, 基于裸片键合的异构方法预计将进一步成熟。

超越器件级创新, 还需大量工作优化制造工艺、提升产能。实现全面商业化需与半导体设备供应商紧密合作, 改进加工技术, 确保与现有CMOS制造基础设施兼容。值得鼓舞的是, 全球在异构集成方面的持续努力, 加之III-V工艺技术在CMOS环境中日益重要的地位, 将不断推动设备能力与制造工艺的进步。

通过应对这些挑战, imec旨在加速III-V-on-Si激光器的开发, 使其更接近在未来一代硅基光子技术中的大规模部署。CS

### 扩展阅读

- [1] Y. D. Konick et al. “GaAs nano-ridge laser diodes fully fabricated in a 300-mm CMOS pilot line” *Nature* 637 63 (2025)

- [2] C. I. Ozdemir et al. “Low Dark Current and High Responsivity 1020nm InGaAs/GaAs Nano-Ridge Waveguide Photodetector Monolithically Integrated on a 300-mm Si Wafer” *J. Light. Technol.* 39 5263 (2021)

- [3] Y. Shi et al. “Novel adiabatic coupler for III-V nano-ridge laser grown on a Si photonics platform” *Opt. Express* 27 37781 (2019)

- [4] P.-Y. Hsieh et al. “Degradation Mechanisms of Monolithic GaAs-on-Si NanoRidge Quantum Well Lasers” *J. Light Tech.* 43 5811 (2025)

# 无石英的 GaN-on-GaN 外延片的 HVPE 扩大生产

住友化学针对外延片市场，开发了一种无石英的 HVPE 反应器，用于大规模生产，可容纳 6 英寸衬底。

为了通过降低生产成本来增加 GaN 功率器件普及，日本住友化学公司开发了一种无石英的 HVPE 反应器，用于大规模生产，可容纳 6 英寸衬底。

该公司的这一最新成就是建立在其先前的成功基础之上的，该公司已证明无石英的 HVPE 可以生长出具有创纪录室温迁移率的 GaN 层。外延层还具有非常低的硅、氧和碳背景浓度。

该团队的发言人伊藤告诉《化合物半导体》杂志，无石英的 HVPE 技术现已非常接近完全优化。“室温下的迁移率接近理论值，杂质浓度低于二次离子质谱测量的检测限。”

为了强调其新工具的能力，住友化学的工程师使用他们的反应器生产了 4 英寸和 6 英寸的 GaN 外延片。这涉及到生长一个硅掺杂的 GaN 层，随后通过各种表征技术进行检测。

在本研究中使用的 4 英寸衬底是内部生产的，使用了空洞辅助分离方法。该衬底具有均匀的贯穿位错密度为  $1\text{-}3 \times 10^6 \text{ cm}^{-2}$ ，偏离角为  $0.4^\circ$ ，从精确的 +c 平面倾斜到 m 方向。“故意使用偏离角是为了防止出现小丘，”伊藤解释说。

对于 6 英寸晶片的生长，住友化学团队使用了 GaN-on-sapphire 模板。不过，6 英寸的自支撑 GaN 衬底正在开发中。

生长条件包括大气压、大约 1 微米 / 分钟的生长速率、使用氨和一氯化镓作为源气体，以及使用氢气和氮气的混合物作为载气。

根据傅里叶变换红外光谱，生长在 4 英寸本征衬底上的硅掺杂 GaN 外延层厚度为 14.1 微米，标准偏差为 3.4%。对此，该团队在他们的论文中评论说，传统的 HVPE 生长的 GaN 倾向于表现出较大的厚度变化，而优化后的无石英 HVPE 系统导致了均匀的分布，类似于 MOCVD 生长的外延膜。

对于在 6 英寸模板上生长的外延片，厚度均匀性略高，标准偏差为 4.4%。

为了评估掺杂，住友化学的工程师考虑了施主和受主密度之间的差异，由非接触式电容 - 电压仪器确定。对于生长在 100 毫米自支撑 GaN 上的 MOCVD 生长 GaN，标准偏差为 14.3%——而

对于通过无石英 HVPE 在 100 毫米自支撑 GaN 上生长的 GaN，仅为 3.0%。

该团队还对最新的 GaN 外延层进行了光致发光测量，并将其光谱与使用原型反应器生产的等效样品进行了比较。与使用更早的反应器生长的膜相比，使用最新反应器（为大规模生产设计）生长的膜具有更强的近带边发射，这归因于抑制了碳污染。同样令人鼓舞的是绿光发光的减少，这表明点缺陷密度降低——这归因于反应器设计的改进，该设计抑制了气体到生长区域的泄漏。

为了在无石英的 HVPE 反应器中展示载流子控制，住友化学的工程师通过改变硅源速率进行了实验，每生长 600 纳米 GaN 就进行一次阶跃变化。通过二次离子质谱分析掺杂轮廓，确定每个层中的掺杂水平是恒定的，并且在界面处硅浓度发生了陡峭变化。

这项研究还表明，使用最新的无石英 HVPE 反应器，可以在从  $1 \times 10^{14} \text{ cm}^{-3}$  到  $1 \times 10^{18} \text{ cm}^{-3}$  的宽范围内实现硅浓度的线性掺杂。

由于许多功率器件在千伏范围内运行，因此在低于  $1 \times 10^{16} \text{ cm}^{-3}$  的范围内控制载流子浓度至关重要。在这方面表现出色的是，住友化学的最新无石英 HVPE 反应器能够生产出具有 10kV 或更高击穿电压的器件。

住友化学并不打算生产和销售其无石英的 HVPE 反应器。“我们是一家 GaN 衬底供应商，我们计划销售通过无石英 HVPE 生产的 GaN-on-GaN 外延片，”伊藤说。

目前，住友化学正在销售直径达 4 英寸的 GaN 衬底，并向器件制造商和研究机构提供通过无石英 HVPE 生长的外延片。

“此外，我们正在开发 6 英寸的 GaN 衬底，并将很快能够提供 6 英寸的 GaN-on-GaN 晶片，”伊藤补充道：“通过这一举措，我们希望为垂直 GaN 器件市场的早日建立做出贡献。”

## 参考文献

S. Kaneki et al. Appl. Phys. Express 18 055502 (2025)

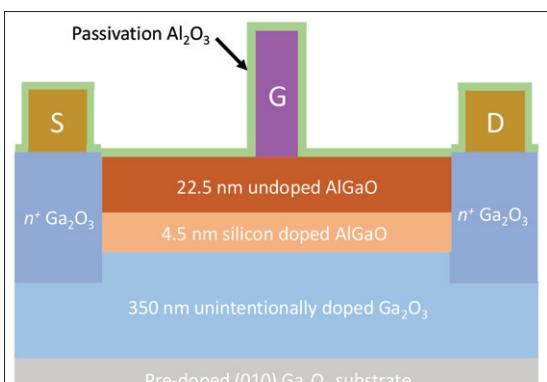

# 钝化 $\beta\text{-Ga}_2\text{O}_3$ 器件

通过温和的刻蚀、退火以及添加一层厚的  $\text{Al}_2\text{O}_3$  钝化层， $\beta\text{-Ga}_2\text{O}_3$  射频器件的性能正被推向一个新高度。

**布**法罗大学的工程师们声称，他们首次成功实现了  $\beta\text{-Ga}_2\text{O}_3$  射频器件的陷阱钝化。这是通过使用一层相对较厚的  $\text{Al}_2\text{O}_3$  实现的，该层可防止电流崩塌——这是射频器件性能的一大障碍。

该团队的 FET 通过“精心设计”的制造步骤，解决了早期器件中的缺陷问题。

这些最新进展将有助于提升  $\beta\text{-Ga}_2\text{O}_3$  射频器件的能力。该材料具有高临界电场和良好的饱和速度，因此其 Johnson 优值（评估射频材料潜力的重要指标）高于 SiC 和 GaN。

布法罗大学的异质结 FET 制造过程包括：在再生长重掺杂  $\text{Ga}_2\text{O}_3$  之前，先刻蚀掉  $\text{Al}_2\text{O}_3$  层和非故意掺杂  $\text{Ga}_2\text{O}_3$  层。此前的器件采用了高功率反应离子刻蚀，导致该层与二维电子气之间的界面电阻过高，限制了跨导和射频性能。

其他研究团队已证实，真空 MBE 退火可部分修复等离子体刻蚀造成的损伤，降低刻蚀功率可减少损伤并降低接触电阻。

布法罗大学团队在其最新晶体管中同时采用了这两种策略。器件制造始于一块来自 Novel Crystal Technology 的外延片，其结构为：在铁掺杂绝缘衬底上，通过 MBE 生长了 350nm 厚的非故意掺杂  $\beta\text{-Ga}_2\text{O}_3$  层。

在该平台上，团队添加了一层 4.5nm 厚的  $\beta\text{-}(\text{Al}_{0.21}\text{Ga}_{0.79})_2\text{O}_3$ ，硅掺杂浓度为  $1.5 \times 10^{19}\text{cm}^{-3}$ ，接着是一层 22.5nm 厚的未掺杂  $\beta\text{-}(\text{Al}_{0.21}\text{Ga}_{0.79})_2\text{O}_3$

一层相对较厚的  $\text{Al}_2\text{O}_3$  可钝化  $\beta\text{-Ga}_2\text{O}_3$  射频器件中的陷阱

势垒层。

随后的制造步骤包括：选择性低功率反应离子刻蚀，缓慢去除  $\text{AlGaO}$  层，并在非故意掺杂  $\text{Ga}_2\text{O}_3$  层处停止，避免造成损伤。工程师用去离子水清洗样品后，将其放入 MBE 腔体中，在  $10^{-10}\text{Torr}$  的真空下于  $600^\circ\text{C}$  退火 1 小时。最终，他们通过原子层沉积 (ALD) 生长了一层 100nm 厚的重掺杂 n 型  $\text{Ga}_2\text{O}_3$ ，去除生长掩模，添加电极，并用 100nm 厚的  $\text{Al}_2\text{O}_3$  进行钝化。

漏极电流与漏源电压的关系图未在低电压下发现非线性现象。

该团队将此改进归因于工艺优化，包括低功率刻蚀、再生长前的盐酸浸泡以及分子束外延 (MBE) 退火。另一个好处是峰值漏极电流的提升，在栅源电压为 3V 时达到了 500mA/mm。

测量结果还表明，在钝化后，阈值电压没有显著偏移，峰值漏极电流和跨导也未出现崩塌，这凸显了厚  $\text{Al}_2\text{O}_3$  层的优势。

请注意，该团队此前的器件曾存在阈值电压漂移的问题，这可能是由高温沉积或等离子体损伤引起的。

团队还进行了脉冲电流 - 电压测量，结果显示  $\text{Al}_2\text{O}_3$  可以钝化陷阱并消除色散现象。KBR、空军研究实验室、Teledyne Scientific 和康奈尔大学的合作团队也采用了类似方法，虽然获得了中等程度的色散改善，但他们使用的  $\text{Al}_2\text{O}_3$  层厚度仅为 20nm。

射频测量显示，在钝化前，FET 无法提供任何增益，且存在严重的 DC-RF 色散或电流崩塌。

具有钝化层且栅长为 191nm 的器件，其截止频率 ( $f_T$ ) 为 32GHz (栅源电压 -3V，漏源电压 7V)，最大振荡频率 ( $f_{MAX}$ ) 为 55GHz (栅源电压 -3V，漏源电压 15V)。

基于这些结果的对比分析，团队表示，其  $f_T$  和  $f_{MAX}$  的值在  $\beta\text{-Ga}_2\text{O}_3$  FET 中属于最高水平之一。

## 参考文献：

C. N. Saha et al. Appl. Phys. Express 18 071001 (2025)

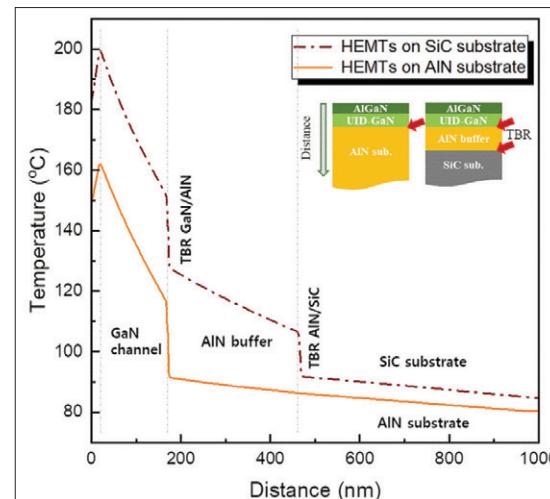

# 热壁 MOCVD 助力 GaN-on-AlN HEMTs

Aixtron 热壁反应器为 GaN-on-AlN HEMTs 带来了创纪录的迁移率

由 林雪平大学牵头的合作团队正在提升在 AlN 衬底上生长 GaN HEMTs 的性能标准。通过热壁 MOCVD 生长的薄沟道器件，据称结合了高载流子密度与创纪录的二维电子气迁移率。

林雪平大学与隆德大学的 Vanya Darakchieva 表示：“这要求在 AlN 上生长低杂质、低缺陷且具有优异结构质量的薄 GaN 层，这非常困难。”

团队成功的关键在于其 MOCVD 反应器。“我们的 Aixtron 反应器全球独一无二，采用热壁 MOCVD 工艺，最小化垂直与横向温度梯度，同时实现对气相化学的精确控制。”

在 AlN 衬底上开发 GaN HEMTs 可能令人惊讶，因为 AlN 衬底成本高、尺寸小且供应有限。但 Darakchieva 指出，得益于深紫外 LED 和新兴功率与射频应用推动的替代衬底制造方法和生态系统发展，成本有望显著降低。她提到了瑞典深科技初创公司 Xtal.works，该公司正在开发创新的 PVT 和 CVD 生长方法。

团队面临的一个挑战是 AlN 与 GaN 之间存在 2.4% 的晶格失配。当 GaN 生长厚度超过临界值时，会通过弹性机制（如从二维到三维生长模式的转变，或通过位错的塑性形变）发生应变弛豫。

AlN 衬底较高的表面能也导致镓原子结合能增加、扩散长度缩短，GaN 倾向于以岛状形核。

尽管存在这些问题，通过热壁 MOCVD 仍可在 AlN 衬底上实现高质量 GaN 外延生长。瑞典团队使用 Aixtron VP508GR 反应器，在小型 AlN 和 4H-SiC 衬底上制备了 GaN-on-AlN 异质结构。

在标准化学清洗后，将衬底加载入热壁反应器，在 1340°C 下氢气退火与刻蚀。异质结构的形成始于在 1250°C 下生长 300nm 厚的 AlN 层，随后在 1080°C 下生长 GaN 层，使用了不同的压力、V-III 比和镓前驱体流量。

扫描电子显微镜观察发现，标准条件下适用于 1μm 厚 GaN 层的平滑表面形貌，在尝试形成薄沟道时会导致覆盖不完全和稀疏岛状结构。

提高镓前驱体流量有助于岛状结构合并并提

与 SiC 衬底相比，AlN 衬底可显著降低器件 (热阻/温度)

高层覆盖率。进一步降低生长压力至 50mbar，有助于在优化条件下形成完全合并的 GaN 沟道层。

尽管 GaN 在 AlN 表面形核，但该衬底比 SiC 衬底实现了更高的 GaN 覆盖率。Darakchieva 等人将此优势归因于 AlN 更高的面外热导率，带来更高的表面温度，从而提高了原子迁移率和更快的聚集与合并速率。

使用更优生长条件和 AlGaN 势垒层以及 GaN 沟道与势垒之间的 AlN 中间层，团队制备了 HEMT 器件。

在 150nm 厚 GaN 沟道中，未使用 AlGaN 缓冲层的情况下，创纪录的迁移率分别为：SiC 衬底上  $1910 \text{ cm}^2/\text{V}\cdot\text{s}$ ，AlN 衬底上  $1805 \text{ cm}^2/\text{V}\cdot\text{s}$ ，采用两步生长法。

通过对整个器件结构及其各层的热导率测量，团队确定了热边界电阻，并通过 TCAD 模拟估算了热点温度。“比较在 AlN 和 SiC 衬底上同时生长的相同器件结构，AlN 上的器件结温低约 20%。”

最近，团队已在 SiC 和 AlN 衬底上制备了器件，正在评估其性能及结温测量。

## 参考文献

M. Kim et al. Appl. Phys. Lett. 127 032104 (2025)

| Advertiser    | 广告商名称          | 网址                      | 页码  |

|---------------|----------------|-------------------------|-----|

| AIXTRON SE    |                | www.aixtron.com         | BC  |

| CGB           | 北京华林嘉业科技有限公司   | www.cgbtek.com          | 3   |

| Evatec AG     |                | vatecnet.com/cn         | 7   |

| FERMI         | 费勉仪器科技(上海)有限公司 | www.fermi.com           | 2   |

| RABOUTET S.A. |                | www.raboutet.fr         | 22  |

| Riber         |                | www.ribert.com          | IFC |

| Park Systems  |                | parksystems.cn/nx-wafer | 1   |

## 欢迎投稿

《化合物半导体》(CSC) 是针对中国化合物半导体及光电市场出版的专业杂志，用简体中文出版。

本刊主要报道化合物半导体相关的材料、工艺、设备、器件、模块/组件、封测技术，及其发展趋势和相关厂房设施。与读者一起紧跟行业发展，共同面对在研发、制造过程中遇到的问题及挑战。

本刊的读者是活跃在化合物半导体及光电行业的技术管理人员、项目经理、科研人员、工程师以及从事开发、制造、工艺的专业人士。

本刊文章精选自英国物理协会著名杂志《Compound Semiconductor》，翻译并编辑成形；我们也报道全球平面显示制造商和研究机构的最新技术与资讯，以及撰写其他与本地市场息息相关的新闻和文章；并选编专业投稿。

本刊欢迎读者和供应商投稿，文章一经采纳，将在印刷版本和网上刊登。CSC 将为设计者和管理人员，提供一个展现国内外厂商的最新成果的平台。

### 文章投稿指南

1. 文章主题突出、结构严谨、短小精悍，中文字数不超过 3,000 字；

2. 文章最好配有两幅至四幅与内容相关的插图或表格；插图与表格分别用图 1、图 2 或表 1、表 2 的次序编号，编号与文中的图表编号一致；

3. 请注明作者姓名、职务及所在公司或机构的名称。作者人数以四人为限；

4. 请勿一稿多投；

5. 请随稿件注明联系方式（邮编、地址、电话、电子邮件）。

### 新产品投稿指南

1. 新产品必须是中国市场新上市、可以在中国市场上买到；

2. 有关新产品来稿的内容应包含产品的名称、型号、功能、主要性能和特点、用途；

3. 短小精悍，中文字数不超过 300 字；

4. 来稿请附产品照片。最好是在单色背景下简单的产品实物照片，照片的分辨率不低于 300dpi；

5. 注明能提供进一步信息的人员姓名、电话、电子邮件。

优先刊登中文来稿（翻译稿请附英文原稿）。来稿请用电子邮件寄到：minL@actintl.com.hk, lynnw@actintl.com.hk。

如果您有什么意见或建议，或者有什么想法同本刊编辑探讨，请不吝赐教。

## 行政及销售办公室 Administration & Sales Offices

### 行政人员 Administration

HK Office (香港办公室)

ACT International (雅时国际商讯)

Unit B, 13/F, Por Yen Buiding,

No. 478 Castle Peak Road,

Cheung Sha Wan, Kowloon, Hong Kong

Tel: 852-28386298

Publisher (社长) - China

Adonis Mak (麦协林), adonis@actintl.com.hk

Editor in China (中国版编辑)

Min Lu (陆敏), minL@actintl.com.hk

Lynn Wang (王清玲), lynnw@actintl.com.hk

UK Office (英国办公室)

Angel Business Communications Ltd.

6 Bow Court, Fletchworth Gate, Burnsall

Road, Coventry, CV5 6SP, UK

Tel: +44 (0)2476 718 970

Chief Operating Officer

Stephen Whitehurst

stephen.whitehurst@angelbc.com

Tel: +44 (0)2476 718970

### 销售人员 Sales Offices

**Asia (亚洲)**

Floyd Chun (秦泽峰), floyd@actintl.com.hk

Tel: 852 2838 6298

**China (中国)**

Mini Xu (徐若男), minix@actintl.com.hk

Tel: 86 187 7196 7314

Ron Wang (汪毓翀), ronw@actintl.com.hk

Tel: 86 186 9404 8156

Mandy Wu (吴漫), mandyw@actintl.com.hk

Tel: 86 156 2304 9536

Grace Zhu (朱婉婷), gracez@actintl.com.hk

Tel: 86 159 1532 6267

Cecily Bian (边团芳), cecilyb@actintl.com.hk

Tel: 86-135 5262 1310

**Taiwan, Singapore, Malaysia**

(台湾, 新加坡, 马来西亚)

Floyd Chun (秦泽峰), floyd@actintl.com.hk

Tel: 852 2838 6298

**Korea (韩国)**

Lucky Kim, semieri@semieri.co.kr

Tel: 82-2-574-2466

**US (美国)**

Janice Jenkins, jjenkins@brunmedia.com

Tel: 724-929-3550

Tom Brun, tbrun@brunmedia.com

Tel: 724-539-2404

**Europe (欧洲)**

Shehzad Munshi, sm@angelbcl.co.uk

Tel: +44 (0)1923 690215

Jackie Cannon

Jackie.cannon@angelbc.com

Tel: +44 (0) 1923 690205

# 2026 研讨会计划

Conference Schedule

CHIP China 晶芯研讨会

CS CON 2026 化合物半导体

先进技术及应用大会

## CSC Webinar

1/4/12月

线上

- 大数据与AI驱动的先进半导体智能量检测

- “内卷”与突围：如何破除SiC产能过剩？

- Micro-LED：显示技术的下一个“风口”

- PIC的新应用

- GaN下一个增长极

- 超宽禁带器件：最终解决方案？

- 面向未来通信：5G-A与6G的射频前端革新

## CSC化合物深研会

9月

无锡

### 主题：破局·增效·可持续——化合物半导体的 下一代技术与市场格局

- 破局与突围：SiC产能与可持续发展

- 后台积电时代，GaN市场谁主沉浮？

- 800V HVDC下的价值链博弈：器件供应商如何破局？

- 超宽禁带半导体的“破晓”时刻：氧化镓与金刚石的产业化路径

- 异质集成：超越“摩尔定律”的化合物半导体新范式

- 化合物半导体的“绿色”与可持续性：机遇与挑战并存

## CHIP China晶芯研讨会

5月

苏州

- TGV技术推动封装应用创新发展

- 面板级封装技术加速崛起进程

- AI驱动光电合封呈现新态势

- 3D封装助力AI算力提升

- 先进封装优化终端设备体验

- 2.5D封装设计实现成本管控

- 混合键合技术持续发展升级

- 推进先进互连技术国产化

- 攻关先进封装新装备技术

## 芯界深研会

3月

武汉

### 主题：共筑先进半导体制造芯生态

- 晶栈架构革新3D NAND存储技术

- 存储与AI融合提升数据处理能力

- AI+SMT协同：半导体制造智能化的必然路径

- 大尺寸晶圆均匀性瓶颈：关键技术如何破局？

- 先进封装热失控：器件热管理的突围路径

- 异构集成浪潮：半导体封测的未来范式

- 纳米级失效定位：半导体分析技术的未来方向

- 晶圆缺陷困局：机器学习如何实现“精准预判”？

## 芯界深研会

8月

合肥

### 主题：共筑先进半导体制造芯生态

- 车规级SiC模块封装技术研发

- SiC功率半导体产品研发及制造

- 车规半导体SMT贴片与激光焊接协同优化

- 车规芯片供应短缺：

产业链如何构建弹性保障体系？

- 宽禁带功率半导体：

新能源领域的下一代核心器件

- 未来芯片与先进制造：

制程突破与产能保障的联动

- 3D堆叠创新：解锁高密度集成新可能

- 功率半导体新材料应用：

重构高能效器件技术格局

\*以上主题暂定，请以会议举办议题为准

化合物半导体 半导体芯科技

CS SEMICONDUCTOR CHINA SS SILICON SEMICONDUCTOR CHINA

SiSC半导体芯科技

ACT化合物半导体

AIXTRON

# THE G10 SERIES

SiC power epi production

platform with 150/200 mm

wafer size flexibility

Your **Productivity Solution**

for All Advanced Epitaxy Materials