# Connecting the Compound Semiconductor Community

Volume 23 Issue 4 JUNE 2017

🔰 @compoundsemi

www.compoundsemiconductor.net

Shining in space by vertical integration

The third dimension: The logical step for III-Vs

CS shares enjoy a tremendous 12 months

Processing SiC in a dedicated 150 mm line

### 25 wafer, 200 mm productivity

Scale up, don't get boxed in

**INSIGE** News Review, News Analysis, Features, Research Review, and much more... Free Weekly E News round up go to: www.compoundsemiconductor.net

## YOU THINK, GLOBAL MEGA TRENDS REQUIRE BEST PERFORMANCE III-V MATERIALS WE THINK THAT TOO.

#### THE AIX2800G4-TM

3D-SENSING AUGMENTED REALITY AUTONOMOUS DRIVING CLOUD COMPUTING INTERNET OF THINGS/5G NEXT GENERATION DISPLAYS

DISCOVER THE AIX2800G4-TM.

Tool of Record for all AsP-based materials for next generation applications.

Market leading technology delivering best yield combined with highest productivity in the industry.

AIXTRON SE info@aixtron.com · www.aixtron.com

Viewpoint

By Dr Richard Stevenson, Editor

### Going vertical

WHEN I THINK OF vertical integration I tend to think of Infinera, the maker of InP photonic integrated circuits that are incorporated into its systems that are deployed in optical networks. It would appear that this in-house strategy has served the company well: it has formed a highly successful multi-million dollar business with devices that are notoriously difficult to make with high yields.

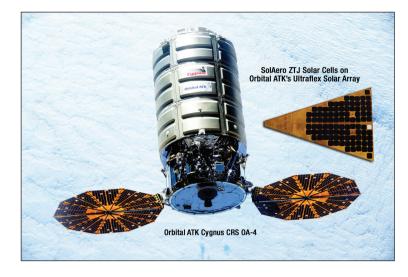

Obviously, Infinera isn't the only vertically integrated III-V chipmaker. Another example is Cree, a pioneer of LEDs that is now a leading force in solid-state lighting; and SolAero, a company that has been carved out of Emcore and makes solar cells and satellite panels.

The latter entity has been pursuing a vertically integrated strategy for many years. Emcore's cells for satellites first hit the market in 1997, and four years later it acquired TecStar, a maker of solar panels.

For more than a decade, Emcore continued in this vein. However, the break up of the business units in late 2014, with ownership of the solar arm taken over by Veritas Capital, has spawned a flurry of activity.

The strengthening of solar capabilities has come through a combination of acquisitions and investment. In 2015 SolAero bought Alliance Spacesystems, equipping the company with lightweight frame technology for satellites; and in 2016, it acquired Vanguard Space Technologies, a move that

richardstevenson@angelbc.com +44 (0)1291 629640

+44 (0)1291 629640

+44 (0)2476 718209

+001 724 539-2404

+001 724-929-3550

+44 (0)1923 690205

+44(0)1923690200

+44 (0)1923 690214

editorial@rebeccapool.com

richardstevenson@angelbc.com

jessica.harrison@angelbc.com

chrise-p@dircon.co.uk

tbrun@brunmedia.com

jjenkins@brunmedia.com

jackie.cannon@angelbc.com

sharon.cowley@angelbc.com

mitch.gaynor@angelbc.com

Editor Richard Stevenson

Editor Richard Stevenson

Publisher Jackie Cannon

Contributing Editor Rebecca Pool

Sales Executive Jessica Harrison

Director of Logistics Sharon Cowley

USA Representatives Tom Brun Brun Media

Design & Production Manager Mitch Gaynor

Janice Jenkins

News Editor Christine Evans-Pughe

strengthened expertise in engineering in space (see the interview of p.32 of this issue for details).

In May 2016 SolAero won a contract to supply solar panels to One Web, a company with ambitious plans that aims to bring the opportunity for connectivity to everyone across the globe via a vast array of satellites. To fulfil this mission, it plans to launch three satellites per day.

To keep pace, SolAero is investing \$10 million to replicate its know-how from its other two sites to its headquarters. By taking this step, it will streamline operations by avoiding having to ship parts around the country while completing its orders.

This move gives the company a unique capability, which should enable it to improve margins in an industry that is experiencing very tough conditions.

Rivals that just produce cells these days will be envious of SolAero's position. With the collapse of the fledgling CPV market, it's now precarious to just be making devices – and far better to be enjoying the benefits of vertical integration.

| Circulation Director Jan Smoothy                                                   | jan.smoothy@angelbc.com        | +44 (0)1923 690200 |  |  |  |  |  |

|------------------------------------------------------------------------------------|--------------------------------|--------------------|--|--|--|--|--|

| Chief Executive Officer Stephen Whitehurst                                         | stephen.whitehurst@angelbc.com | +44 (0)2476 718970 |  |  |  |  |  |

| Directors Bill Dunlop Uprichard - EC, Stephen Whitehurst - CEO, Jan Smoothy - CFO, |                                |                    |  |  |  |  |  |

| Jackie Cannon, Scott Adams, Sharon Cowley, Su                                      | khi Bhadal, Jason Holloway     |                    |  |  |  |  |  |

Published by Angel Business Communications Ltd, Hannay House, 39 Clarendon Road, Watford, Herts WD17 1JA, UK. T: +44 (0)1923 690200 E: ask@angelbc.com

Accounts & Multi Media Angel Business Communications Ltd, Unit 6, Bow Court, Fletchworth Gate, Burnsall Road, Coventry CV5 6SP, UK. T: +44 (0)2476 718 970 E: info@angelbc.com

Compound Semiconductor is published eight times a year on a controlled circulation basis. Non-qualifying individuals can subscribe at: £105.00/e158 pa (UK & Europe), £138.00 pa (air mail), \$198 pa (USA). Cover price £4.50. All information herein is believed to be correct at time of going to press. The publisher does not accept responsibility for any errors and omissions. The views expressed in this publication are not necessarily those of the publisher. Every effort has been made to obtain copyright permission for the material contained in this publication. Angel Business Communications Ltd will be happy to acknowledge any copyright oversights in a subsequent issue of the publisher. The paper used within this magazine is produced by chain of custody certified manufacturers, guaranteeing sustainable sourcing. US mailing information: Compound Semiconductor, ISSN 1096-598X, is published 8 times a year, Jan/Feb, March, April/May, June, July, August/September, October, November/ December by Angel Business Compunications Ltd, Unit 6, Bow Court, Fletchworth Gate, Burnsall Rd, Coventry CV5 GSP UK. The 2017 US annual subscription price is \$198. Airfreight and mailing in the USA by agent named Air Business Ltd, c/o Worldnet Shipping Inc., 156-15, 146th Avenue, 2nd Floor, Jamaica, NY 11434, USA. Periodicals postage paid at Jamaica NY 11431. US Postmaster: Send address changes to Compound Semiconductor, ISSN 1096-598X (Print) ISSN 2042-7328 (Online) © Copyright 2017.

# CONTENIS

#### **COVER STORY**

#### Perfecting 200 mm processing tools

As the demand for MEMS, sensors and mobility expands, heterogeneous devices on 200mm substrates will become more common to address that increased demand.

#### 22 GaAs sales to plateau

Price erosion and a slowing of smartphone growth will lead to a very modest increase in the GaAs market

# 28 CS shares enjoy a tremendous twelve months

Topping this year's shareprice leaderboard are the suppliers of epiwafers, substrates and MOCVD tools

# 32 SolAero: Mastering vertical integration

Acquisitions and investment enhance SolAero's capabilities in solar power technologies for satellites.

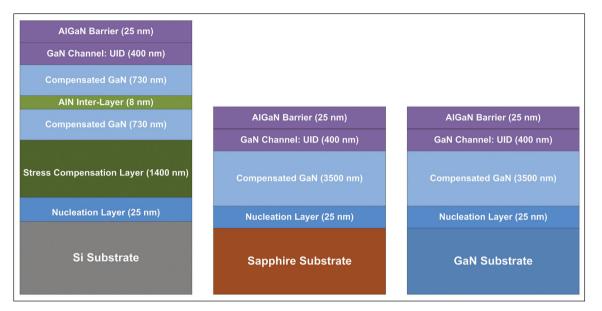

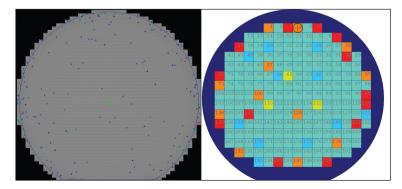

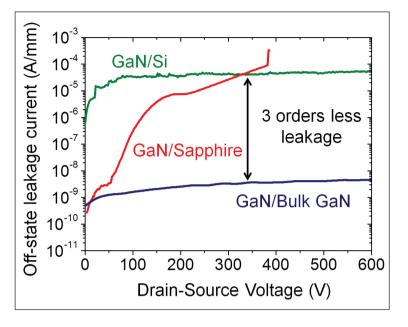

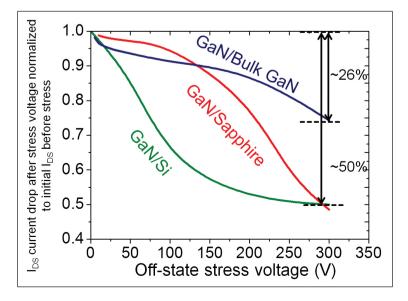

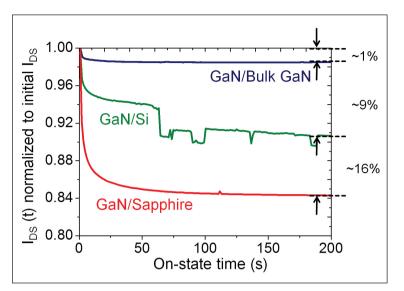

# 36 GaN HEMTs: The substrate conundrum

With GaN HEMTs, is the additional cost of a native substrate a price worth paying?

#### 40 Wet BATCHSPRAY power device manufacturing

Siconnex vendor view

#### 42 The third dimension: Logical steps for III-Vs

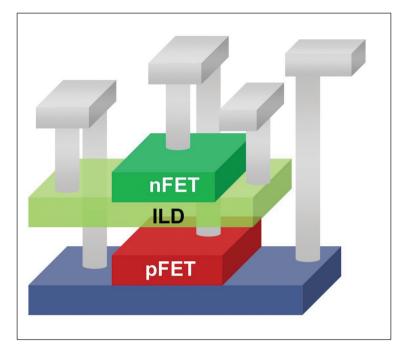

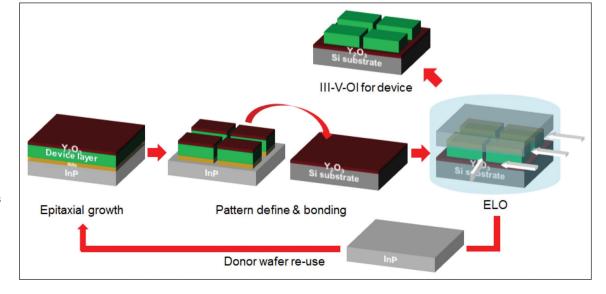

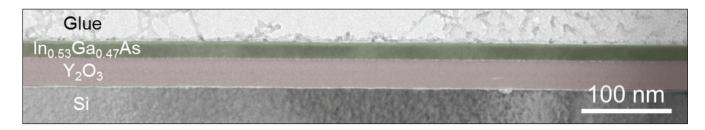

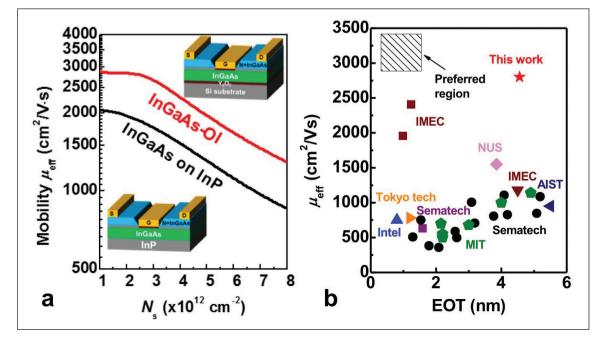

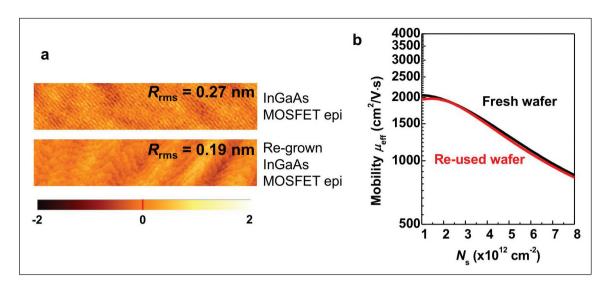

Wafer bonding and substrate re-use offer a route to making a InGaAs-on-insulator MOSFET architecture that could slash power consumption, while increasing transistor density via vertical stacking

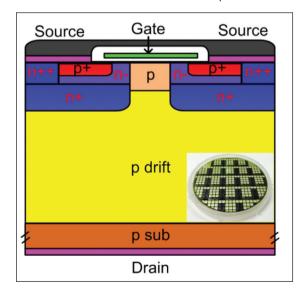

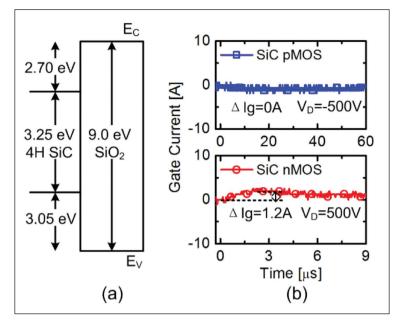

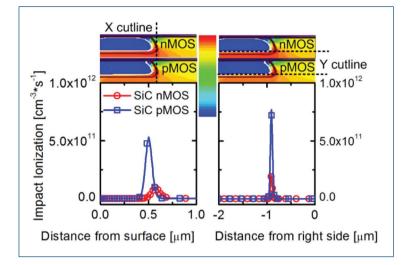

#### 47 Making a debut: The p-type SiC MOSFET

Breaking new ground with SiC MOSFETs that are p-type, rather than n-type, swells the promise for the future of complementary inverters

#### news

- X-Fab and Exagan make first 200mm GaN-on-silicon devices

- Mitsubishi, Nokia Bell Labs and UC San Diego develop ultra-fast GaN envelope-tracking amplifier

- 38 IEEE awards George Craford for contributions to LED lighting

- Cambridge Nanotherm addresses UV-LED thermal management challenges

- Infineon starts volume production of first full-SiC-module

- 12 StratEdge packages to include high-power GaN transistors and MMICs

- 4 Cree President and CEO Chuck Swoboda steps down

#### news analysis

- 16 Akash: flying high ahead

- **18** Setting the SiC standard

#### research review

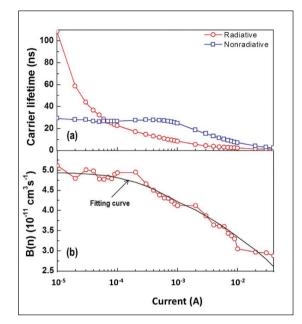

- 51 Differential carrier lifetimes offer insight into LED droop

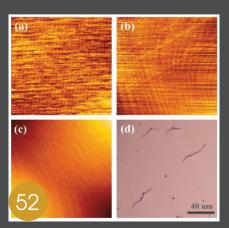

- 52 Perfecting the GaN Schottky barrier diode

- 53 A hike in UV LED power

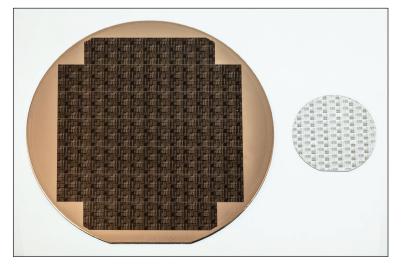

# X-Fab and Exagan make first 200 mm GaN-on-silicon devices

X-FAB SILICON FOUNDRIES and Exagan, a GaN start-up, have demonstrated mass-production capability to make highly efficient high-voltage power devices on 200 mm GaN-onsilicon wafers using X-Fab's standard CMOS production facility in Dresden, Germany.

This accomplishment is the result of a joint development agreement launched in 2015, enabling cost/performance advantages that could not be achieved with smaller wafers.

Exagan and X-Fab have successfully resolved many of the challenges related to material stress, defectivity and process integration while using standard fabrication equipment and process recipes.

Combined with the use of 200 mm wafers, this will significantly lower the cost of mass producing GaN-onsilicon devices. By enabling greater power integration than silicon ICs, GaN devices can improve the efficiency and reduce the cost of electrical converters, which will accelerate their adoption in applications including electrical vehicle charging stations, servers, automobiles and industrial systems.

The new GaN-on-silicon devices have been built using substrates fabricated at Exagan's 200 mm epi-manufacturing facility in Grenoble, France. These epi-wafers meet the physical and electrical specifications to produce Exagan's 650 V G-FET devices as well as the tight requirements for compatibility with CMOS manufacturing lines.

The industry's previous work with GaN had been limited to 100 mm and 15-mm wafers due to the challenges of layering GaN films on silicon substrates. Exagan's G-Stack technology enables GaN-onsilicon devices to be manufactured more cost effectively on 200 mm substrates by depositing a unique stack of GaN and strain-management layers that relieves the stress between GaN and silicon layers. The resulting devices have been shown to exhibit high breakdown voltage, low vertical leakage and high-temperature operation.

"This is a major milestone in our company's development as we accelerate product development and qualification," said Frédéric Dupont, president and CEO of Exagan. "It demonstrates the combined strengths of our epi material, X-Fab's wafer fab process and our device design capabilities. It also confirms the success of our vertically integrated fab-lite model, with expertise from materials to devices and applications. It's perfect timing to establish GaN technology and products on the most competitive 200 mm platform just as GaN power products are getting broad traction in IT server. consumer electronics and automotive markets."

#### WIN Semiconductors completes second phase of fab expansion

WIN SEMICONDUCTORS has completed the second phase of expansion of its newest wafer fab, Fab C. It says this will boost its GaAs wafer manufacturing capacity by over 20 percent. According to the company, this operation is now fitted with state-of-the-art clean rooms, efficient process lines and advanced equipment for GaAs MMIC production, epitaxial growth of compound semiconductors, as well as fabrication and test of optical devices. Serving customers in mobile PA, WiFi, wireless infrastructure and optical markets, WINSemiconductors provides a broad portfolio of HBT, pHEMT, integrated BiHEMT technology solutions and optical devices. WIN Semiconductors' manufacturing services can support applications from 50 MHz to 150 GHz and through light-wave.

"In response to increasing demand across all market segments, we continue to add manufacturing capacity at our third wafer fab located in Guishan, Toayuan City, Taiwan. Known as Fab C, the facility now supports mass production of a wide range of compound semiconductor technologies. When fully built out, the 706,000ft<sup>2</sup> facility will more than double our capacity", said Kyle Chen, senior VP and COO of WIN Semiconductors.

#### Advantech releases second generation GaN Ka-band BUCs

Advantech Wireless has released its second generation of 100 W to 125 W K\_a-Band Block Upconverter (BUC), based on GaN technology.

The new GaN-based BUCs are designed for  $K_a$ -Band LEO and GEO satellite up-link applications. The GaN-based SSPB-3010Ka series are integrated units, complete with power supply, phase-locked oscillator, mixer, filter and proprietary cooling mechanism.

Intended for outdoor operation, the second generation GaNbased systems are the most advanced GaN based Ka-Band units in the market providing higher power and linearity, higher reliability and very low spectrum regrowth.

"GaN technology allows us to reach power levels that were not possible before, and to serve customers that are looking for solutions in fast growing market segments," said Cristi Damian, VP business development at Advantech Wireless.

"Advantech Wireless is a pioneer in Ka-Band solid state technology, with products in the field since 2005. The new 100/125W K<sub>a</sub>-band SSPAs take advantage of advanced GaN technology to deliver unmatched performance and reliability."

# Mitsubishi, Nokia Bell Labs and UC San Diego develop ultra-fast GaN envelope-tracking amplifier

MITSUBISHI ELECTRIC, Nokia Bell Labs and the Center for Wireless Communications at UC San Diego have developed an ultra-fast GaN envelopetracking power amplifier (PA) for next next-generation wireless base stations.

Believed to be a world first, the PA supports a modulation bandwidth up to 80MHz, which is four times wider than the signals reportedly used in other envelope-tracking power amplifiers. Technical details will be presented during the IEEE MTT International Microwave Symposium (IMS) 2017, which will be held in Honolulu, Hawaii, USA from June 4 to 9.

To help meet the demand for increasing wireless capacity, mobile technologies are shifting to next-generation systems that use complex modulated signals with large peak-to-average power ratio (PAPR) and extra-wide modulation bandwidth. This will require power amplifiers to operate most of the time at backed-off power levels that are well below their saturation levels.

Generally, power amplifiers achieve high efficiency near their saturation power levels, but significantly degraded efficiency at backed off levels, as in the case of 4G LTE\* signals (>6dB PAPR). Envelope-tracking power amplifiers have been studied extensively as a means to enhance power-amplifier efficiency, but so far the supply-modulator circuit has been the bottleneck limiting modulation bandwidth for advanced wireless communications, such as LTE-Advanced.

The newly developed ultra-fast GaN envelope-tracking power amplifier achieves state-of-art performance thanks in part to Mitsubishi Electric's highfrequency GaN transistor technology and design innovation for the GaN supplymodulator circuit.

Using Nokia Bell Labs' real-time digital pre-distortion (DPD) system, the power amplifier has demonstrated efficient operation even with 80MHz modulated LTE signals, the world's widest modulation bandwidth for this purpose as of May 19, 2017. The new GaN envelope-tracking power amplifier uses Mitsubishi Electric high frequency GaN in supply-modulation circuits, which enable high-speed operation. The result is highly efficient amplification of complex signals with modulation bandwidth up to 80MHz.

The technology achieves a worldclass drain efficiency of 41.6 percent in such wide-bandwidth operation, thereby reducing base-station energy

consumption while increasing wireless communication speed and capacity. Further, the real-time DPD system enables pre-distortion for wideband signals to correct the output signal from the power amplifier, resulting in an adjacent channel leakage ratio (ACLR) of -45dBc for LTE 80MHz signals, which satisfies the wireless communication standards.

In view of its leading system-level performance, the new envelope-tracking power amplifier is believed to be a highly promising candidate for next-generation wireless base stations.

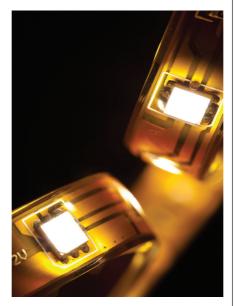

# IEEE awards George Craford for contributions to LED lighting

LUMILEDS has announced that George Craford, Lumileds Solid State Lighting Fellow, was selected for the IEEE Edison Medal for 'a lifetime of pioneering contributions to the development and commercialisation of visible LED materials and devices'.

Craford will be presented with the medal at the IEEE Honours Ceremony in San Francisco on May 25, 2017, during the IEEE Vision, Innovations, and Challenges (IEEE VIC) Summit.

Craford's career spans from the early days when LEDs were first developed to delivery of high brightness LEDs suitable for commercial use in a variety of applications, including LED bulbs. He is best known for his invention of the yellow LED in 1972. Craford then led the development of increasingly brighter red, orange and amber LEDs.

In 1979, Craford began work at Hewlett-Packard, where his team pioneered the development of AllnGaP LEDs using metalorganic chemical vapor deposition (MOCVD). MOCVD was then a relatively expensive lower volume process and had not been used for the high volume commercial production of LEDs. AllnGaP LEDs increased the performance of red and yellow LEDs by more than ten times. Craford's team continued to achieve technology breakthroughs in AllnGaP LEDs, eventually reaching 100 lm/W. "Not only was George responsible for substantial breakthroughs in technology, but with his team, ensured that the technology could be reliably and cost effectively manufactured," said Mark Karol. 2017 IEEE Awards Board Chair.

One can see the impact of Craford's early work in the colour LEDs now ubiquitous in traffic signals, emergency and automotive lighting. Craford's later work focused on making white LED light cost effective for retail, office, architectural, outdoor and industrial lighting markets. In the early 2000s, his team's work enabled commercialisation of the first high power LEDs in the 10-20 lumen range. Such LEDs contributed to the creation of the

first LED bulbs to meet the high efficiency and long lifecycle requirements to win the US Department of Energy's 'L Prize' for a 60W-equivalent LED bulb.

"George has terrific instinct for what will work, but at the same time he's got that practical engineering side that drives a solution until it produces the best results," said Jy Bhardwaj,CTO of Lumileds.

Today, Craford is Lumileds Solid State Lighting Fellow at Lumileds. He is an IEEE Life Fellow and a member of the National Academy of Engineering. He has received numerous awards including the 2002 National Medal of Technology and the 2015 US National Academy of Engineering Charles Stark Draper Prize. He has also been awarded the International SSL Alliance Global Solid State Lighting Development Award, the Strategies in Light LED Pioneer Award, the University of Illinois Alumni Distinguished Service Award, the IEEE Morris N. Liebmann Award, the IEEE Third Millennium Medal, the Optical Society of America Nick Holonyak Jr. Award, the International Symposium on Compound Semiconductors Welker Award, the Materials Research Society MRS medal, the Electrochemical Society Electronic Division Award and the Economist Innovation Award.

#### Osram shows third generation plant growing LED

AT this year's Lightfair in Philadelphia (USA), Osram Opto Semiconductors showed a new high power LED prototype designed to promote plant growth.

The Oslon Square Hyper Red is a third-generation 2 W LED designed to cut the cost of plant lighting systems by featuring improved emission characteristics, higher optical output, and better corrosion resistance.

Plants need water and light to grow. By using LEDs with different wavelengths, commercial growers are now able to control each individual stage of plant growth. With a wavelength of 660 nm the prototype of the Oslon Square Hyper Red, for example, can control the growth of blossom. Together with the deep blue (450 nm) and far red (730 nm) versions, the Oslon family covers the entire spectrum of plant growth.

The prototype of the LED has an integrated 2 mm x 2 mm chip which provides improved performance. By using the latest technologies, developers have been able to achieve a typical radiant power of 905 mW with radiant efficacy of 60 percent, at a current of 700 mA and an operating temperature of 25°C. This represents an improvement of 13 percent in terms of radiant power and 25 percent better radiant efficacy compared with the current Oslon SSL. The beam angle of the Oslon Square Hyper Red is 120°.

"Thanks to its high corrosion resistance and long life, the new Oslon Square Hyper Red is extremely reliable. Our new flagship product therefore also meets the usual high quality standards of the entire Oslon family", said Kok Peng Lim, product manager SSL at Osram Opto Semiconductors.

### SEMICONDUCTOR

Watlow's Thermal System Solutions Enable Next Generation Technology

#### Watlow<sup>®</sup> offers:

- Precision designed heater circuits embedded in ESCs and chamber components

- Innovative solutions for gas line heating

- Thermal system integration with heaters, sensors and controllers

- Analytical, FEA and CFD capabilities

- Over 12,000 square feet of cleanroom manufacturing

🎶 WATLOW.

#### Powered by Possibility

Visit us at **SEMICON®WEST** booth #5344, and ask us about our new ATS technology.

For more information visit our website at www.watlow.com

# Cambridge Nanotherm addresses UV-LED thermal management challenges

THERMAL management company Cambridge Nanotherm has launched Nanotherm DMS, a direct-metallised single-sided thermal management solution for UV-LED modules.

UVA LEDs are rapidly displacing traditional UV lamps in the industrial printing industry, speeding up print times and reducing cost. UVC LEDs are also opening up applications like portable sterilisation units that can provide millions with clean drinking water, or let you sterilise your toothbrush when you're camping.

However, UV LEDs present a significant thermal challenge. UVC LEDs often only convert 5 percent of power into photons. The remainder must be conducted away as heat via the base of the LED to a thermally conductive PCB to avoid the LED die overheating.

As shorter wavelengths of UV light degrade organic material the choice of PCB is often limited to inorganic materials, discounting cost-effective metal-clad PCBs (MCPCBs) that rely on an organic epoxy based dielectric layer. Ceramics such as  $AI_2O_3$  or AIN are used, but they present a conundrum to LED designers - low-performance but cost-effective  $AI_2O_3$  (25W/mK), or high-performance but expensive AIN (140-170W/mK). Ceramic is also brittle and prone to cracking, far from ideal for new of portable applications and equally an issue for industrial applications overtighten a screw and the module PCB will fracture.

Cambridge Nanotherm has developed Nanotherm DMS to address these issues. It combines the robustness and manufacturability of aluminium with the high thermal performance of AIN and as it undergoes thin-film processing, it's entirely inorganic. Nanotherm's direct metallised single-sided PCB (Nanotherm DMS) uses an extensively patented electro-chemical oxidation (ECO) process to convert the surface of aluminium into an alumina dielectric layer. This nanoceramic alumina has a thermal conductivity of 7.2W/mK which, coupled with being just tens of microns thick and using a direct metallisation process, gives a composite thermal performance of 152W/mK.

While this is slightly inferior to the very best and most expensive AIN substrates, the mechanical robustness of the Nanotherm metal board permits better approaches to mounting so measured system performance exceeds that of AIN. Cambridge Nanotherm sales and marketing director Mike Edwards said: "UV LEDs are opening up incredible new opportunities for applications ranging from the life changing to lifestyle changing. The challenge for module manufacturers remains how to balance thermal requirements with cost and practicality. With Nanotherm DMS there is now an option that brings together the performance of ceramics with the robustness and manufacturability of MCPCBs and being fully inorganic it won't degrade with use."

#### CST Global to increase laser test throughput

CST Global, the UK-based III-V optoelectronics foundry, has introduced an automatic visual inspection machine, increasing laser throughput and test accuracy. According to Colin Jackson, production project engineer at CST Global, the new inspection machine takes throughput from 10,000 lasers per shift to 30,000. CST Global worked with the visual inspection machine manufacturer, Keyence, and software developer, Wolf, to commission, develop and optimise the new machine.

"The Visual Inspection machine brings other key benefits to CST Global. We now only need one inspector per shift, allowing us to re-deploy valuable resources elsewhere. We can track wafer batch quality, working with our key suppliers to help increase yield. Finally, we are streamlining the visual inspection process to handle yet more gel packs per shift. We expect throughputs to near 40,000 lasers per shift, shortly," adds Jackson.

Osram Opto Semiconductors is leading a project called UNIQUE to develop high-power AlGaN-based UV LEDs (with wavelengths in the 260 to 280nm range) for disinfection applications. By developing a small, cost-effective, energy-efficient, mercury-free, long-life UV diode the project partners are looking to gain a strong position on the growing market for UV LEDs and use the results of the project to strengthen Bavaria as a location for business. UNIQUE is funded by the Bavarian Ministry for Economic Affairs, Media, Energy and Technology, and involves five Bavarian companies and research institutions.

Aprotec GmbH is responsible for the design of a special installation for producing AIN volume crystals by evaporating AIN powder at over 2000°C.

The Fraunhofer Institute for Integrated Systems and Device Technology (IISB) is in charge of developing a process chain for producing AIN substrates. Osram Opto Semiconductors is developing the UVC LED chip with the associated component epitaxy and processing on the basis of the AIN substrate. UV LED chips need the protection of a gas-tight package that offers a constant vacuum and therefore a stable atmosphere for the chip. Developing a permanently vacuum-tight package from inorganic UV-stable materials and evaluating the structure and connections are the tasks of SCHOTT AG in Landshut.

# Infineon starts volume production of first full-SiC-module

INFINEON is starting volume production for the EASY 1B, the first full-SiC module that was announced at last year's PCIM 2016. At PCIM in Nuremberg, the company is showing additional module platforms and topologies for the 1200 V CoolSiC MOSFET family. Infineon says it is now able to bring the potential of SiC technology to a new level.

"SiC has reached a tipping point: Taking cost-benefit analysis into account, it is ready for use in a variety of applications," said Peter Wawer, division president Industrial Power Control from Infineon. "In order to make the new semiconductor technology a revolution to rely on, however, it needs a partner like Infineon. Products tailored to the application, our own production capacities, comprehensive technology portfolio and system understanding: these four building blocks have made us the market leader for power semiconductors. We want and will also achieve this with our SiC product portfolio." The new 1200 V SiC MOSFETs have been optimised to combine high reliability with performance. They show dynamic losses which are an order of magnitude lower than 1200 V silicon IGBTs. First products will initially support upcoming system challenges in applications such as photovoltaic inverters, uninterruptible power supplies (UPS) and charging/storage systems. The new configurations will also enable new solutions in industrial drives, medical technology or auxiliary power supplies in the railway sector in the near future, according to Infineon.

One major advantage of the trench technology with the 1200 V SiC MOSEFT lies in an extended robustness. This is due to the lower failure in time (FIT) rate and the short-circuit capability, which can be adapted to the respective application. Thanks to a threshold voltage (V th) of 4 V and the recommended switch-on threshold ( $V_{GS}$ ) of +15 V, the transistors can be controlled like an IGBT and safely switched off in the event of a fault. The SiC MOSFETs enable very fast switching transients. In addition, Infineon's technology offers an easy adjustability of the transients via gate series resistors. The EMC behavior can thus be easily optimised. Last year, Infineon announced the lead products EASY 1B (Half-Bridge / Booster) as well as the discrete TO-247-3pin and -4pin solutions. The EASY 1B platform is well established and an ideal module platform for fast switching devices. At this year's PCIM fair, Infineon will be exhibiting additional module platforms and topologies based on the 1200 V SiC MOSFET technology. This extends the performance spectrum of the CoolSiC MOSFETs step by step.

Among others, Infineon is showcasing the following SiC modules: EASY 1B with B6 (Six-Pack) topology module has an on-resistance of only 45 mΩ. An integrated body diode ensures a low-loss freewheeling function. The EASY 1B is suitable for applications in the fields of drives, solar or welding technology. EASY 2B with Half-Bridge topology offers an enhanced performance with an on-resistance of 8 m $\Omega$  per switch. The low-inductance module concept is suitable for applications with more than 50 kW and fast switching operations. These include solar inverters, guickcharging systems or solutions for uninterruptible power supplies.

62 mm with Half-Bridge topology features even higher power with on-resistance of 6 m $\Omega$  per switching function. This module platform offers the possibility of low-inductance connection of systems in the medium power range. A great variety of applications make use of this, including medical technology or auxiliary power supplies in the railway sector, to name a few. Because of the large number of possible applications, Infineon anticipates a rapid spread of this module. The lead products introduced at PCIM 2016, EASY 1B and the two discrete devices TO-247-3pin and -4pin, are gradually entering volume production during this year. The Half-Bridge configuration for the EASY 1B is now available. Its market launch is supported by various driver modules and demo boards, which are also available from now on. The new product configurations are available as samples, and the serial start is planned for 2018.

picoquant.com/materialsscience

# StratEdge packages to include high-power GaN transistors and MMICs

STRATEDGE CORPORATION, a company that makes high performance semiconductor packages for microwave, millimeter-wave, and high speed digital devices, has expanded its LL family of high-power laminate copper-molycopper (CMC) base packages to include both GaN transistor and MMIC device packages and package assembly services.

The packages can now accommodate large MMICs, with die attach areas as

high as 5.92 x 12.14 mm. They operate at frequencies from DC to as high as 63GHz for applications in communications, radar, automotive, aerospace, defense, and those requiring high power millimeter-wave signals.

In addition to the packages, which are manufactured in StratEdge's San Diego, California facility, StratEdge offers complete automated assembly and test services for these packages, including gold-tin solder die attach. These assembly processes are said to routinely generate >96 percent void-free attachment with bond line thicknesses of <6 microns when used with the new LL series of packages. This is particularly important for GaN power amplifiers where efficient thermal transfer is critical for improved operation and reliability of the device.

The LL family of CMC-base packages dissipate heat from high-power compound semiconductor devices,

such as GaN, GaAs, and SiC. These laminate power packages are built with a base material ratio of 1:3:1 CMC, which provides a good thermal match for alumina-based materials and a GaN chip.

"StratEdge was one of the first to market with laminate power packages for GaN devices," said Tim Going, StratEdge president. "StratEdge has continued to develop packages to handle the requirements of new materials and devices. Our LL family additions can handle frequencies up to 63 GHz and large MMIC devices, and our precision automated assembly and test services enable the chips to operate with the efficiency and electrical integrity they were designed to achieve."

StratEdge will be exhibiting at the 2017 International Microwave Symposium (IMS2017), to be held 6-8 June 2017, at the Hawaii Convention Centre in Honolulu, Hawaii.

#### Raytheon GaN radar surpasses 1000 operational hours

RAYTHEON has announced that its GaNpowered Active Electronically Scanned Array (AESA) proposed upgrade to the Patriot Air and Missile Defense has surpassed more than 1,000 hours of operation in just over a year - half the time of a typical testing program.

"We achieved this milestone so quickly because of our successful experience developing and maturing GaN for programs like the US Navy's Air and

Missile Defense Radar," said Doug Burgess, director of AESA programs at Raytheon's Integrated Defense Systems business. "We're ready to take the next step and get this radar into the hands of our customers."

During the course of the 1,000 hours, Raytheon's GaN-based AESA prototype radar routinely demonstrated 360° capability by working together with a second GaN-based AESA antenna that was pointed in a different direction. As targets flew out of one array's field of view and into another, the two arrays seamlessly passed information back and forth, tracking the target continuously. The main array also detected and tracked tactically maneuvering fighter jets and thousands of other aircraft, according to the company.

"Raytheon's GaN technology is backed by 19 years of research and \$300 million in investment, while our competitors are either new to the market or primarily build GaN for commercial applications," said Ralph Acaba vice president of Integrated Air and Missile Defense at Raytheon's Integrated Defense Systems business.

Raytheon's GaN-based AESA radar will work with the Integrated Air and Missile Defense Battle Command System and other open architectures. It maintains compatibility with the current Patriot Engagement Control Station and full interoperability with NATO systems. A number of current and expected future Patriot Air and Missile Defense System partner nations in Europe and Asia have expressed interest in acquiring GaNbased AESA.

Poland submitted a Letter of Request for GaN-based AESA Patriot, March 31. Raytheon's GaN-based AESA technology also meets Germany's requirements for the German Taktisches Luftverteidigungssystem, or TLVS, tactical air and missile defence system.

#### OUR THIN FILM PRODUCTION SYSTEMS LEAD THE WAY

From the precision AIScN films required for BAW filters in the **next generation 5G mobile networks**, to cost effective AIN deposition on Si for **GaN Power Devices** and plasma damage free deposition of TCOs on GaN in **LED applications**, our thin film production solutions reduce your process development times, enhance yields or increase tool throughput.

Evatec's Advanced Process Control (APC) technologies set new standards in thin film deposition through 'in situ" capability for control of mechanical, optical or electrical properties during the deposition cycle.

MORE INFO

ADVANCED PACKAGING • PHOTONICS • MEMS • OPTOELECTRONICS • POWER DEVICES • WIRELESS • THE THIN FILM POWERHOUSE www.evatecnet.com

#### SiC via Etch for RF Device Manufacture

- High SiC etch rate enabling maximum throughput

- Smooth sidewalls for problem free post etch metallisation

- High selectivity to underlying GaN layer giving a smooth, low damage stop on the GaN device layers

www.oxford-instruments.com/SiCvia

The Business of Science®

### Cree President and CEO Chuck Swoboda steps down

CREE'S CHAIRMAN, president and CEO Chuck Swoboda will step down from his executive positions and as a member of the board of directors following a transition period. Swoboda stated: "I have had the privilege of leading Cree for 16 years, which has been extremely rewarding both professionally and personally. My decision to change my work-life balance follows a recent medical issue, which was resolved, and which caused me to revaluate my priorities."

He added: "I believe that this is a good transition time for Cree as we have three core businesses poised to enter another phase of accelerated growth. I know that under its next CEO, Cree will continue to disrupt markets with new technologies and superior-performing products that deliver great value to our customers while consuming less energy. I look forward to working with the Cree board to find the right leader and to ensure a smooth handoff to my successor."

Swoboda intends to stay on until a successor is appointed, and thereafter

will remain available as a consultant to the company to ensure a seamless transition of leadership responsibilities. Since joining Cree in 1993, Swoboda has held numerous executive positions with the company, leading Cree from a near start-up to today's technology market leader, with approximately 6,400 employees worldwide. Swoboda has served as a member of the Cree board rs since 2000, as chief executive officer since 2001, and chairman since 2005.

In 2010, Mr. Swoboda was named Ernst & Young's Entrepreneur of the Year for

the Carolinas, and in 2013 he was named The Edison Report's Lighting Industry Person of the Year. Cree was recognised as one of MIT Technology Review's 50 Smartest Companies for 2014, and as one of Fast Company's World's 50 Most Innovative Companies in 2015. Robert A. Ingram, lead independent director of the Cree board said"

"The board extends its deep appreciation to Chuck for his outstanding leadership over the past 16 years as CEO, and for his 24 years of service to Cree. During that time, his passion for the business and focus on innovation has helped transform industries and has enabled the company to achieve an eight-fold increase in revenue."

Ingram concluded: "Given Chuck's decision, he and the rest of the board agree that now is the right time to accelerate the process to identify a new CEO to lead Cree and further grow our three businesses. We look forward to Chuck's continued leadership as we conduct our CEO search and transition."

#### Soraa expands into directional Iuminaires

GaN on GaN LED specialist Soraa has announced its expansion into the directional luminaire market. The new Arc range is built around a very low profile die-cast heat sink, and optimised for superior thermal management.

"Soraa's core GaN on GaN technology is what makes us different than every other LED company in the world," says Susan Larson, VP at Soraa responsible for the Fixture business and the design lead for Soraa Arc. "It's the science behind our technology that gave my team the ability to design shallow fixtures, small apertures and narrow clean beams, unmatched by anyone else." Soraa Arc will initially be offered in track, pendant, downlight, and surface mounted designs as well as with fixture SNAP accessories, including trims, Snoot and wall washes in a variety of colour light engines with full spectrum 95CRI, R9>95 and Rw 100 typical. Black and white finishes are standard; custom colours are available on request. Arc luminaires with 9°, 10° and 15° beam spreads are also compatible with the existing Soraa SNAP System to further customise beam and light colour.

"Having recently previewed the Arc directional fixtures, our customers are thrilled to now have an end-to-end solution from Soraa they can rely on for a wide range of applications," says George Stringer, senior VP of sales at Soraa.

#### The most cost effective method to excellent quality.

"Now offering Germanium Reclaim"

#### III/V-Reclaim

Wald 10 84568 Pleiskirchen / Germany Telefon: +(49) 8728-911093 Telefax: +(49) 8728-911156 E-Mail: sales@35reclaim.com Internet: www.35reclaim.com

- We recycle your GaAs and InP wafer (all formats and sizes)

- One and double side polished wafer

- Best surface quality for direct use in Epitaxy

- Backside thinning of fully structured wafer

- O Thin wafer (60 μm)

- Single wafer processing possible

- We buy used wafer and sell recycled wafer

#### **EXHAUST GAS ABATEMENT**

#### ZERO DOWNTIME SOLUTION FOR MOCVD MANUFACTURING CLEANSORB® PRIMELINE PD

#### .....

- Safe, dry chemical conversion of hazardous gases to stable solids

- Proprietary CLEANSORB<sup>®</sup> media

- No handling of toxic waste

- Practically maintenance-free

- Local Refill service worldwide

#### news analysis

## Akash: flying high ahead

With its GaN-on-diamond power amplifiers entering satellite markets, Akash Systems is reaching for the sky, reports Rebecca Pool. AS GLOBAL DEMAND for data soars and today's communications infrastructure struggles to suffice, GaN industry veterans have joined forces to tackle the problem head on.

Akash Systems was founded in January 2016 by GaN pioneer and former Group4Labs chief executive, Felix Ejeckam, with Cree executive, Ty Mitchell, to drive GaN-on-diamond technology firmly into the satellite communications space.

As Mitchell tells *Compound Semiconductor*: "We wanted to solve the biggest problem in satellite communications today – data access and cost – and are focused on providing fast, cost-effective and high-bandwidth communications across Earth and in deep space."

To this end, the company is developing and supplying next-generation small, powerful and cost-effective CubeSats, with, of course, the RF power amplifiers that power these systems. But as always, speed and power come at a price, and it's heat.

While today's GaN-based HEMTs can ideally reach an incredible 40 W/mm RF power at 10 GHz frequencies or more, thermal heating limits power densities to around 10 W/mm. Mitchell is certain GaN-on-diamond will make the difference.

#### news analysis

"Look at any communications application and the power amplifier is the most power hungry and hottest element in the system, but GaN-on-diamond could change this," he says. "High thermal conductivity diamond can remove the heat in an amplifier by up to four times faster than any other substrate in use today."

"Using GaN-on-diamond RF amplifiers we intend to create small, powerful and cost-effective satellites that provide much higher data rates for services that depend on information density and quality, like high definition video streaming," he adds.

And with ex-Qorvo heavyweights, Kris Kong and Paul Saunier, also in tow, the company is moving forward fast. GaN-on-diamond hybrid power amplifiers and MMIC power amplifiers are already entering the market. Meanwhile plans to work with satellite system makers and design CubeSat systems and subsystems are well underway.

By 2019, Akash aims to deliver various sized CubeSats, and 300 W K<sub>a</sub>-band transmitters, with blisteringly fast downlink data-rates of 100 Gbps to 1 Terabit, as well as extremely high-resolution earth imaging and terapixel video capabilities. Then by 2021, the company intends to have satellites in low Earth orbit offering communications bandwidth for cheap, high-speed global broadband access, live streaming imaging and more.

"We'll have our product line of amplifiers filled out during 2018 and at the same time will complete our initial CubeSat design," highlights Mitchell. "In 2019 we will continue to iterate on the CubeSat designs and then get a window for launch."

"Timing is aggressive – it has to be – but it is absolutely do-able, and we have a firm plan to get there," he asserts.

#### Potent IP

Akash Systems' satellite ambitions have been years in the making, starting in 2003 when Ejeckam launched Group4 Labs to develop methods for fabricating the first ever GaN-on-diamond wafers. By lifting GaN epitaxy from its original growth substrate – silicon – and transferring it to a synthetic CVD diamond substrate, Ejeckam and colleagues could enable customers to manufacture high performance RF and power semiconductors.

Crucially, Group4's GaN-on-diamond technology was the first of its kind to become commercially available. By 2013, the company had concluded its DARPA Near Junction Thermal Transport (NJTT) program, and partners at Raytheon and Triquint Semiconductor had separately announced that their GaN-on-diamond devices had outperformed GaN-on-SiC. In HEMTs, for example, Raytheon achieved a three times improvement in GaN-on-diamond's RF areal power density, compared to GaN-on-SiC devices.

Still, come mid- 2013, the company's intellectual property and assets were acquired by technology partner Element Six. And by the start of 2016, Ejeckam left Element Six, and he and Mitchell began negotiations to buy back the IP from Element Six.

"We had been talking about how powerful this technology could be at a systems level as it would solve the heat problem in electronics systems," says Mitchell. "Also at Cree, I had seen first-hand how a fundamental technology could have a huge impact at the systems level, and expand, even create, new industries."

"So we figured that if we could use this GaN-ondiamond IP we would have something very exciting," he adds.

Given this, the pair worked with global RF and microwave component manufacturer, RFHIC, to jointly buy back the all-important IP from Element Six. And by mid-2016 Akash Systems had agreed to acquire Element Six's patents and IP rights relating to the technology for use in satellite communications with RFHIC acquiring technology rights for several applications including wireless communications.

So as RFHIC gets ready to deliver RF power transistors and systems for wireless infrastructure markets, Akash has its sights firmly set on satellites. Right now fabrication takes place on 100 mm GaNon-diamond wafers, although scaling up to 150 mm in the future is a clear option. Price-wise, Mitchell is adamant that the overall cost-per-Watt for amplifiers based on the GaN-on-diamond is competitive with GaN-on-SiC devices and is confident satellite pundits can see the benefits of his company's technology.

Still, as he highlights, Akash is not setting out to compete with GaN-on-SiC devices. "The purpose of GaN-on-diamond is not to supplant GaN-on-SiC and I believe the technologies are actually complementary."

"However, GaN-on-diamond will enable satellite systems to reach new levels of performance," he adds. "We want to redefine what people believe are the limitations in satellite communications." Akash Systems is developing and supplying next generation CubeSats.

## Setting the SiC standard

With a state-of-the-art SiC line up and running, and packaging facilities soon to come online, the New York Power Electronics Manufacturing Consortium is poised to deliver next generation power devices, discovers Rebecca Pool.

> In a breakthrough for power MOSFET qualification, the New York Power Electronics Manufacturing Consortium (NY-PEMC), led by the State University of New York Polytechnic Institute (SUNY Poly), recently produced patterned wafers in its SiC process line at SUNY Poly's Albany, NY, campus.

> As Jeffrey Hedrick, Vice President of SUNY Poly, tells *Compound Semiconductor:* "This means we are up and running, our tools are up and running, and our engineers and scientists are now working hard to fabricate these advanced devices."

It all started in 2014 when the General Electric Company (GE) partnered with SUNY Poly to build a state-of-the-art 150 mm process line for silicon carbide MOSFETs and diodes.

Forming the New York Power Electronics Manufacturing Consortium – NY-PEMC – with SUNY Poly, GE provided more than \$100 million in intellectual property, while overall investment in the consortium, including support from New York State, reached \$500 million.

Then, come 2015 and another \$100 million in New York State funds, GE and SUNY Poly revealed plans to establish a power electronics packaging facility at the Computer Chip Commercialization Center (Quad-C) located on SUNY Poly's Utica campus.

And with Danish power module manufacturer, Danfoss Silicon Power, recently joining GE and SUNY Poly to set up SiC power module packaging operations here, NY-PEMC looks set to become the 'silicon carbide corridor' of North America.

Hedrick certainly thinks so. Heading up both the wafer fabrication and packaging arms of NY-PEMC, he highlights how the manufacturing consortium will help provide much needed jobs and revitalise the economy of Upstate New York.

GE will fabricate cutting-edge SiC chips that will

then be assembled and packaged by Danfoss for integration into systems. Fabrication capabilities will top 15,000 wafers a year, and with Danfoss earmarked to operate the only domestic high-volume packaging centre in a burgeoning US market, the future for NY-PEMC looks bright.

"GE and Danfoss are our core members, and we expect to add other key partnerships in the near future," says Hedrick.

"We're equipped to easily run 15,000 wafers a year, which is more than sufficient for the next three years, and we have the expansion capabilities to increase this figure to 50,000 when the market ramps up to higher volumes."

#### Latest developments

In recent months, activities at NY-PEMC's wafer fabrication arm have focused on scaling up its baseline process flow to manufacturing readiness. The process flow includes technology developed at the GE Global Research Center in Niskayuna, New York. And as Hedrick points out: "GE has been continually working with us to transfer technology from its research centre to our line in Albany."

Right now, the wafer fabrication facility is in its final stages of ISO 9001 certification in a SiC-dedicated Class-1 capable cleanroom. All tools, including photolithography, reactive ion etching, metallization, metrology, measurement, in-line electrical test and more, are nearing full installation. And the consortium's team of engineers intends to have the process flow verified and qualified – to automotive AEC-Q101 reliability specifications – by the end of this year.

"We're focusing on process setup and verification right now," explains Hedrick. "But very soon we will be able to fabricate qualified MOSFET devices with unmatched reliability."

Indeed, come 2018, 1.2 kV MOSFET fabrication will be well underway, and this is just the beginning. Hedrick

#### news analysis

and colleagues intend to offer 1.7 kV MOSFETs shortly thereafter, and then higher voltage devices and integrated circuits by 2020.

What's more, the tools installed in the SiC process line are 200 mm-capable equipment from top-tier manufacturers, and as Hedrick points out, have been 'chucked down' to support 150 mm wafers.

"The industry is currently transitioning to 150 mm substrates and will eventually transition to 200 mm substrates," highlights Hedrick. "In a few years from now when the 200 mm substrates are technically and economically viable, we will be able to chuck our tools up at a low cost. "As the market ramps up, we're going to be ready," he adds.

Meanwhile, activities are also well underway at the packaging centre at Quad-C in Utica. The site will house manufacturing lines for industrial, transportation, and automotive applications, while additional lines will be devoted to research and development, and prototyping of new modules and power blocks. "We have a very aggressive schedule to get the packaging facility set up for Danfoss and we are ordering many of the custom tools right now," says Hedrick. "These have a lead time of up to eight months and we'll get many of them by the end of this year. We'll start installing these tools as soon as we can, and have the first three lines qualified in 2018," he adds.

So with all systems go for the next few years, what does the longer-term hold for NY-PEMC?

Hedrick, for one, hopes to continue extending what he describes as the power electronics ecosystem within NY-PEMC.

"I'm currently seeking additional funding to create a design centre for power electronics devices and systems," he says. "We're also very open to working with businesses that may want to bring SiC substrate and epi wafer production capability to New York. We'll continue to develop this high-tech corridor across New York, and I expect that many consumable and equipment suppliers will soon be joining us."

### Perfecting 200 mm processing tools

As the demand for MEMS, sensors and mobility expands, heterogeneous devices on 200 mm substrates will become more common to address that increased demand.

Devices such as GaN-on-Si for RF (Radio Frequency)and power, and BAW/FBAR and MEMS on various substrates, will require a new generation of 200 mm process tools to satisfy the needs for high-throughput and high yield lift-off compatibility. Batch sizes will also be enlarged to match that of other process steps. High collection efficiency of precious metals will continue to a driver for reduced device cost and excellent wafer and batch film uniformity will continue to be required for new device performance across all materials of interest.

Ferrotec announces a new lift-off metal deposition system to meet these needs for 200 mm substrates, the Temescal UEFC-6100 ultra-efficient electron beam evaporator.

A key factor to achieve high yield lift-off is the near normal incidence of the deposition across the entire wafer surface. This is best achieved with the line of sight material travel of e-beam deposition at long source-to-substrate distances. The UEFC-6100 is designed for source-to-substrate (SR) distances of 43" (1092 mm) or 46" (1168 mm) to achieve  $\leq$  5 degree incident angles at all locations on a wafer's surface.

Dual-axis and patented no-contact, magnetically driven HULA (high uniformity lift-off assembly) wafer motion ensures excellent uniformity across multiple process conditions. HULA motion also delivers the highest material collection efficiency for precious metals by minimizing the need for large area uniformity masks while maintaining a high wafer packing fraction. Throughputs are further aided by the intelligent conic chamber designs; which minimize and optimize both volume and total non-substrate coated surface areas within these systems.

These factors improve pump down times by minimizing outgassing surfaces and their coating based degradation in pump times due to condensate build-up over multiple operating cycles.

A large 25x (200 mm) wafer batch also improves throughput while limiting the need for tracking split lots that may be required in smaller tools. As the size and value of the wafers increases, automated wafer handling becomes more preferred. This new system design is matched with the Ferrotec Wafer Valet automatic wafer handling system to eliminate the need for operators to handle individual wafers, which speeds tool load and unload times and reduces the risk of handling errors.

The combined effect of all these design factors is pointed out in the table below. The table compares performance for deposition of a 1 micron thick gold layer of the UEFC-6100, with two other tool designs; an existing tool originally designed for 150 mm wafers at 43" throw distance that could hold up to 18 x 200 mm wafers, and a theoretical "best design" for a traditional box style system with a single axis of rotation carrier that could handle 25 x 200 mm wafers.

With the assumption that masking to achieve uniform films is required, it is clear the UEFC-6100 outperforms the traditional designs in all areas listed.

|                                         | FC-4400,<br>43"SR | UEFC-6100,<br>43"SR | UEFC-6100,<br>46"SR | Single Axis<br>"Best Design",<br>46"SR |

|-----------------------------------------|-------------------|---------------------|---------------------|----------------------------------------|

| Max Angle of incidence, degrees         | 5.1               | 5.1                 | 4.8                 | 4.8                                    |

| Number of wafers per run                | 18                | 25                  | 25                  | 25                                     |

| Net Cycle time, minutes                 | 70.1              | 68.0                | 68.0                | 78.0                                   |

| Wafers produced per hour                | 15.4              | 22.0                | 22.0                | 19.2                                   |

| Collection Efficiency                   | 17.9%             | 23.3%               | 21.7%               | 19.2%                                  |

| Cost of Au per wafer (at \$50/gram), \$ | \$162.14          | \$124.94            | \$133.85            | \$151.26                               |

| 1                                       |                   | Ĩ                   | All samples mo      | deled for 5/a sec Dep rat              |

Table 1. Performance comparison for deposition of 1 micron gold layer.

# REVOLUTION in 200mm!

## Meet the Next Generation in Compound Semi

Introducing Ferrotec's Temescal UEFC-6100 evaporator, the first electron beam system optimized for metallization on 200mm substrates. Wafer sizes are evolving and this new system is ideally suited to meet expanding demands for RF filter and other emerging compound semi heterogeneous integrated substrates.

The UEFC-6100 is engineered for production, with a 25 wafer batch size, the unique Temescal conic chamber, the HULA–High Uniformity Lift-off Assembly, and the Auratus<sup>™</sup> deposition process enhancement methodology.

Don't let evolution pass you by, find out more. Contact Ferrotec at 1-925-371-4170.

Price erosion and a slowing of smartphone growth will lead to a very modest increase in the GaAs market, argues Eric Higham from Strategy Analytics in an interview with Richard Stevenson

# GaAs sales set to **plateau**

Will the introduction of 5G deliver a hike in GaAs sales? And how long might it be before sales of phones with 5G technology take off?

A I think the answer to that question is being defined as we speak. We have done a number of 5G projects this year. We have talked to a lot of equipment guys, and a lot of operators, to get a sense of what they're looking for.

I'm kind of envisioning it as a multi-variable equation that is getting solved. The solution is going to determine the technology.

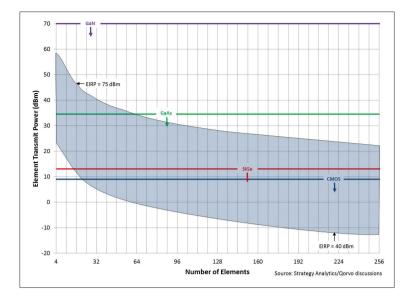

One of the things that is going to be fundamental is the definition of massive MIMO. How many of these beams do you have? The equipment guys tend to talk about transmit power in terms if EIRP – effective isotropically radiated power. Those numbers are going to be fixed, and they'll be a number for a macro-cell, or a micro-cell. But the more antenna beams that you are going to have in your massive MIMO network, the lower each transmitter needs to be for a fixed EIRP.

So, if you say my definition of massive MIMO is going to be 16 antenna beams, that implies a different level of power than if it's going to be 128. Depending on what the number of antenna beams you are going to have, you can run from GaN all the way to RF CMOS to meet the power requirements.

There are lots of other factors in this multi-functional, multi-variable equation that I'm talking about. What is going to percolate to the surface sooner or later is power consumption. I heard a company talking about having done a CMOS PA at millimetre-wave frequencies – it might have been E-band – but it has 8 or 10 percent power-added efficiency out of that PA.

Eric Higham

If you think that you are going to be doing a massive number of additional base-stations, and each one has a very low power-added-efficiency, how do you find all that power?

The other interesting thing is that as we start to talk about these massive MIMO antennas at 28 GHz or the true millimetre-wave frequency range, antenna physical spacing starts to become an issue.

As you go higher in frequency, the wavelength spacing between radiators gets to be a very small physical distance. How do you handle that? Is that running lines along different dimensions? That adds loss and denigrates performance.

With GaN, because for a given power output you can make the chip smaller than other technologies, that might give that technology a leg up, particularly on

the packaging standpoint. As these antennas that are half-wavelength spaced tend to be cross-polarised, you tend to have two antennae at that location – and you can put two GaN amplifiers in a package, and maintain that spacing at 28 GHz right up to the antenna radiating element. That might not be the case with other amplifiers, because the amplifiers physically have to be bigger.

The GaAs community is very excited about what is going to happen. For the middle of the range, the number of antennae result in a power level that would be pretty easy for GaAs to handle.

So that's positive, but until we get more consensus on what that architecture is going to look like, I definitely wouldn't rule out GaN, even for the lower power. Nor would I would rule out silicon for some versions, but that's probably RF CMOS.

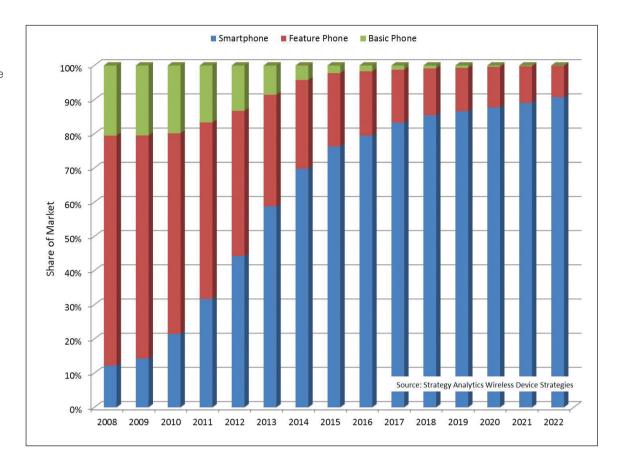

Smartphones penetration continues to rise, but the rate of growth is in decline.

### Will there much growth in the global GaAs microelectronics market over the next five years?

A It looks like a little bit of a kick up if you look at the five-year forecast. We will have a little dip in the next couple of years, followed by an upward trending line to get to that little kick-up. But these downs and ups are a percent, or less than a percent, from year to year, so relatively flat.

The cellular market is the largest single driver by far. If you expand that a little bit and call it the wireless market, which will pull in base stations, WiFi and VSAT, then that's 80 percent of the GaAs market. So the trend for cellular, and broader scale wireless, is driving the overall market. Right now, the cellular trend is price erosion, with other technologies capturing share. Smartphones

are driving the cellular market, and the big negative is that we are starting to reach a time in history where smart phone penetration is starting to definitely slow down.

On the flipside, handset quantity goes up every year, and you've still got more complexity. The US just finished its 600 MHz auction, and now handset manufacturers are going to have to figure out how to squeeze that frequency band in amongst all the others.

#### So is the GaAs content in mobile devices still on the up?

A The complexity is increasing, definitely. I'm sure you'll have seen the announcements about speed trials and speed results as we trend towards 5G. Operators are doing that with bigger chunks of spectrum, but also with carrier aggregation.

What does that mean for the handset? More linearity in the power amplifier, and definitely more complexity and more sophistication in that front-end.

What makes answering your question a little bit more challenging is that device manufacturers have done a great job at being able to do multi-mode, multiband – and the number involved in the multi portion of that is increasing. If you are covering five bands or eight bands, that not five or eight PAs. It hasn't been that way for a long time, but I think that the number of distinct PAs is decreasing.

When you started to aggregate, and two bands became one band, it was never twice the price or twice the die area. It was always a little bit less than that. The phone manufacturers are not going to say we like you guys, so we're going to give you more money. So it's conflicting forces. If you look at the bill-of-materials. I think that's going up, but perhaps slowly. That's a positive – one of the only positives in the cellular market.

Several years ago, the leading players in GaAs HBT technologies were championing their BiFET and BiHEMT technologies. Are these now in production?

A I think they are. There were being championed as a difference maker, but the reasons for the BiFET have gotten less compelling. However, the more hybrid approach has gotten to be less expensive. If you are going to have to make a couple more wire bonds, or a couple more part placements, I don't think that's significant any more.

#### Is there much investment in GaAs technology. For example, are features sizes shrinking?

A In the silicon industry, everybody is so interested in Moore's Law. That node size is decreasing pretty quickly. The claim is that the GaAs industry isn't doing anything similar. I certainly would say that the GaAs industry is not changing feature sizes as quickly as the silicon industry. But we are seeing a trend towards smaller gate sizes. I know that Qorvo announced a 90 nanometre process in the last year or so, geared towards at the time optical applications. But I'm sure they ported that over to millimetre wave, so point-topoint radio and emerging 5G. I think it's not unusual to see foundries that are in the hundreds – 120, 130 – or down below 100.

#### S Is most of the world's production now on 6-inch lines?

A Yes, but I don't think it makes sense to obsolete 4-inch lines. The premise that the mobile handset market drives the GaAs market, and price erosion there is strict, means that it makes sense to go to 6-inch to get to that cost reduction. One of the foundries told me, probably a couple of years ago, that they were seeing somewhere in the 10-15 percent per quarter die shrink, so that's cost saving. If it gets smaller, it gets cheaper. I think companies that have 4-inch are selectively using that 4-inch for some of the other 50 percent of the market that is not handset. This may not have that same negative slope on the price erosion.

The number of makers of GaAs parts seems to be declining. Anadigics is no more, and TriQuint and RFMD have merged to form Qorvo. Does this entity and Skyworks have a stranglehold on the market?

A Qorvo and Skyworks account for almost 60 percent of the market. And if you throw in Broadcom and WIN Semiconductor, you are almost up to 75 percent. The GaAs market is bifurcating into the top two heavyweights that are mobile device driven, and everybody else. Everybody else has a pretty wide range of customers – there are 50, or 60 or 70 companies that do something in the GaAs market. Not everyone has their own foundries – a lot of those guys are buying chips and building higher level assemblies. But it's a big universe of companies that will produce devices that have GaAs devices in them.

C The capabilities of Qorvo and Skyworks seems to have increased, with products that contain several different technologies. The days of thinking of them as simply GaAs HBT makers are long gone, aren't they?

A Very true. Just look at the top-line revenues that both of them report, a smaller and smaller portion of that is GaAs these days.

If you look back in history, Skyworks got left out when Nokia was the biggest handset manufacturer, and Nokia was tied in tightly with RFMD. So Skyworks looked for other manufacturers, other markets and other technologies to remain in that position they had. History has moved forward, and throwing your rod in with Nokia for smartphones turned out not to be the best decision in the world. Some of the other guys that Skyworks looked at, such as Samsung, got to be much more important.

Skyworks has also done a great job of diversifying technology and end markets. They have got involved with the internet-of-things, smart metering - what you might not think of as mainstream markets if you think of Skyworks as strictly a GaAs company. That's in their DNA to find other markets for their technology. Pretty early on they acquired SiGe Microsystems, and had SiGe technology for a while. With Qorvo, with Green Peak, their IoT acquisition, those guys can now do everything on silicon. Now Qorvo can go to shows where you might not think a GaAs company would be. With both of those guvs, they have really done a good job in having a technology portfolio. Part of the challenge has been getting comfortable with that outsource model, where they don't have the RF CMOS and the SiGe foundry under their roof.

Has the merger of RFMD and TriQuint led to the cost savings that were hoped for?

In the silicon industry, everybody is so interested in Moore's Law. That node size is decreasing pretty quickly. The claim is that the GaAs industry isn't doing anything similar. I certainly would say that the GaAs industry is not changing feature sizes as quickly as the silicon industry

For 5G, the number of antenna employed for the MIMO architecture will determine the power requirements, and thus the suitable technologies. A Yes, but I don't think it has materialised quite the way they thought it was going to. We all know that synergy is another word for layoffs, and I think that when that \$150 million synergy was first announced, most people looked it and thought that's got to be foundry. They would have thought that they've got duplication of foundry, too much capacity, and something is going to happen with that – but it hasn't.

The reason for that is that they have done a really good job in repositioning the foundry, and they have been helped by a big uptick in the filter market. I think that Qorvo, definitely more than Skyworks - but Skyworks to a little extent - have branched off into filters, and things that aren't active parts anymore. For five or six years, growth of Skyworks' GaAs revenue has outpaced the overall market. That allowed them to increase their lead over Triguint and RFMD and then Qorvo. This last year, Skyworks, for the first time in my memory, underperformed the GaAs market growth, which wasn't much. Qorvo seems to have got things squared away and closed the gap on Skyworks a little. They are coming out with new products that are addressing new product segments, and the financial results seem to be forming in a positive direction. So we can assume that they are ready to move forward, and are not spinning their wheels.

#### Solution In general, are profit margins tight for suppliers of components for handsets?

A Yes. However, even though price erosion has been pretty constant in that market, I think they've gotten better by using technology. They've been able to make the multi-mode, multi-band PAs incorporate more bands. So they retain a large portion of that overall revenue by creating a better mouse trap, if you will, to address the problem. They don't just have to compete on whether everything will be cheaper than the guys down the street. I think Qorvo has benefited from a strong filter capability, from the module standpoint. Perhaps they can capture more revenue by supplying a fully integrated module with a number of filters and PAs, rather than just selling them individually.

### C The GaAs HBT is under threat from silicon technologies, such as SOI. How strong is this challenge?

A I think that there have been some interesting developments. About three-to-four years ago Qualcomm announced the RF360 platform that had CMOS PAs and was going to target the latest release of LTE. Shares for WIN, TriQuint, RFMD and Skyworks from before the Qualcomm announcement to the Qualcomm announcement underwent a step function. But as we see now, Qualcomm has just entered into an agreement with one of the Japanese companies to do PAs in GaAs for their higher-frequency, higherperformance offerings.

At the time, we were saying if anyone can get their foot in the door with CMOS PAs, it will be Qualcomm. They have a tremendous amount of expertise to throw at the problem, they've got the name. Having said that, for the lower feature phones, entry-level 3G and the 2.5G that still exists, there is a lot of CMOS PA content. It's just that the drive until recently was to have the latest and greatest smartphone. I don't believe CMOS has gotten much traction in those next-generation, higher-frequency 4G, 4.5G phones, but it is definitely taking market share away from GaAs in the lower side of the market. The good news there is a lot of people are being transitioned, and people are turning off 2 G networks and going to higher data-rate capability.

#### In non-mobile GaAs technologies, is there a place for the little guy?

A If you exclude WiFi, markets are all fairly small. Here you can get some better gross margins than the high volume markets. They end up being the targets of the ecosystem of 50 or 60 companies who aren't Qorvo or WIN or MACOM or Skyworks. None of these guys are big, or have a portfolio that addresses every single market, but they have all found niches. I think what keeps the little guy going is finding those niches where they can do a value added, performance-driven solution, and not have to worry about squeezing that last fraction of a penny out of the cost of the price.

For point-to-point radio, test-and-measurement, and other markets, you can almost count volumes on your hand, and you can get good gross margins. Hittite is the classic example. Those guys minted that 70 percent gross margin quarter after quarter. They would not set foot in the high-volume market, because there is nowhere to get the margins there. I think that's what keeps the second tier, in terms of revenue, going. They find that niche, and they do a good job of that niche.

#### **Siconnex BATCHSPRAY® Acid:** Efficiency has a name.

#### ADVANTAGES

- Automated dry-in, dry-out process

- Five processes possible in one sequence

- Repeatability thanks to process control

- Equipment footprint of 1.2 m x 2 m

- Up to 80% less DI water

- Up to 80% reduction in process media

- Closed system

- User safety

- Chemical mixing management system

industry finance

# CS shares enjoy a tremendous twelve months

Topping this year's shareprice leaderboard are the suppliers of epiwafers, substrates and MOCVD tools

BY RICHARD STEVENSON

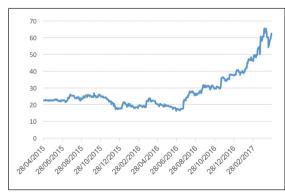

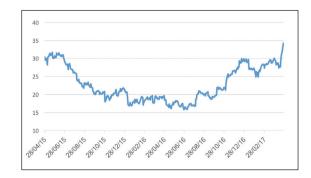

IF YOU OWN a portfolio of shares in compound semiconductor companies, you'll be pleased by performance over the last 12 months. While it's not been as stellar as it was seven years ago, when shares in every firm listed on the *Compound Semiconductor Shareprice Leaderboard* delivered double-digit growth, the majority of companies have outperformed the technology-rich NASDAQ – and even that has shot up by nearly 27 percent in the last year.

Example of success include the two industry heavyweights Qorvo and Skyworks, which have delivered gains in share price of 51 percent and 49 percent, respectively, during the twelve months up to the end of this April. Last year, those performances would have been good enough to secure the second and third spots on the table, but this year it's placed them eighth and ninth.

Topping the table this year is epiwafer supplier IQE, which has seen its share price rocket by more than

200 percent; next on the list is substrate maker AXT, with an appreciation of just over 160 percent; and third is MOCVD manufacturer Veeco, which has seen its share price climb by nearly 80 percent.

Possible drivers behind the growth in IQE's valuation can be found in the company's results for the year ending 31 December 2016. These figures, which were reported on 21 March, reveal a 16.4 percent hike in year-over-year annual revenue from £114.0 million to \$132.7 million. The increase in sales is attributed to success in multiple markets, plus an 11 percent post-Brexit strengthening of the US dollar against sterling. Adjusted operating profit also climbed, increasing by nearly 17 percent to £22.1 million.

Commenting on the 2016 annual results, IQE CEO Drew Nelson picked out the photonics division as the "star of the show", thanks to its year-on-year growth in sales of more than 43 percent. "This is being driven by VCSEL and InP technologies, which enable a broad range of applications, from fibre optic communication

to advanced sensors and industrial processes." Margins from this sector are high, with an operating profit of £6.9 million on sales of just \$22.8 million.

Sales of IQE's photonic products are expected to increase, with the depth and breadth of photonics development programmes and customer qualifications providing a solid platform for strong growth. The company is now shipping 6-inch VCSEL epiwafers, which are claimed to slash the unit cost of chips, and thereby accelerate the adoption of this technology. Devices can be used in 3D sensing, data communications, data centres, gesture recognition, health and cosmetics.

The lion's share of IQE's sales comes from the wireless sector. Here it claims to have 55 percent of the global market. The company "performed well" in this sector, according to Nelson, with sales up 15 percent. However, margins are far tighter than they are in photonics, with annual sales of £91.2 million

#### industry finance