Volume 21 Issue VIII November / December 2015 📴 @compoundsemi www.compoundsemiconductor.net

#### LED droop: More evidence for Auger

Exposing flaws in modelling LEDs

### Positive vibes for silicon carbide

**COMPOUND** SEMICONDUCTOR Free Weekly E News round up , go to www.compoundsemiconductor.net

AN ANGEL BUSINESS COMMUNICATIONS PUBLICATION

CRA

0 de

YOU THINK,

### AIXTRON SYSTEMS SHOULD OFFER YOU THE BEST COST OF OWNERSHIP.

### WE THINK THAT TOO.

THE NEW AIX R6.

Revolutionizing an industry is not about changing everything. It's about making the good even better. Introducing: The new AIX R6. It has everything you expect from the industry's technology leader plus **better usability, better throughput and better cost of ownership.**

AIXTRON SE · info@aixtron.com · www.aixtron.com

# editorialview

by Dr Richard Stevenson, Editor

### Where is the boundary?

ONE POPULAR APPROACH for driving technology forward involves identify weaknesses in incumbent products, and devising ways to address them. If the weaknesses are significant, and the rewards for addressing them lucrative, then you can bet that many will be chasing the prize.

On some occasions, one technology is an obvious successor - think of the LED head torch, and its forerunner based on the filament bulb. In these cases, the battle will be fought over factors such as the speed to market, bang-per-buck, and the strength of the marketing campaign.

In others instances, firms pursue different technologies to break into an established market with a supposedly superior product. When this happens, it might be a case of winner-takes-all - and it may also be a matter of horses for courses, which is the case in the power transistor arena.

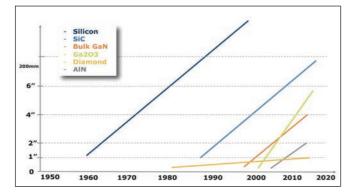

In this sector, silicon devices currently rule the roost, but they have several weaknesses, including a limited range of operating temperatures and an efficiency that is not that high. To exploit these drawbacks, many companies, from start-ups to multinationals, are developing chips based on two wide band-gap materials: GaN and SiC.

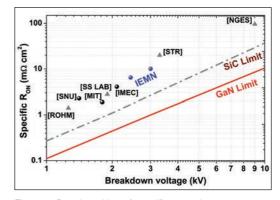

Analysts that are following this market, such as Yole Développement, are arguing that both materials can enjoy success. That's because they believe that a boundary exists at 600 V, with higher voltages reserved for SiC, and the lower realm awaiting occupation by GaN-on-silicon.

The thinking behind this is that GaNon-silicon is better suited to lower voltages, thanks to its lower chip costs. But at higher voltages, leakage currents hit unacceptable values - so it is the SiC devices, grown on native substrates, that are likely to emerge as the successors to silicon.

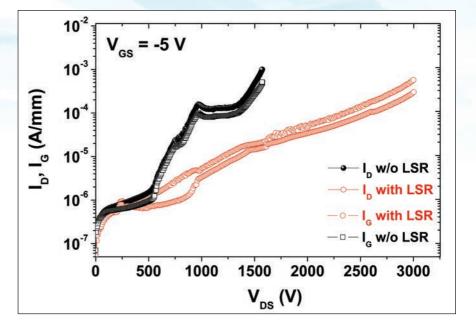

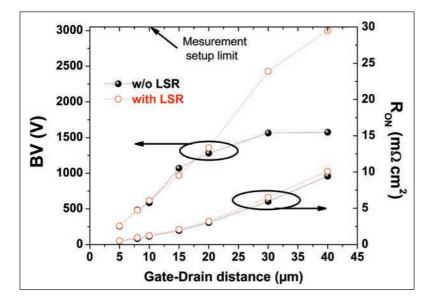

But this vision is not a forgone conclusion. There are some research teams that would question this outlook, because they are developing technologies to propel GaN-on-silicon transistors to higher voltages. This includes the group led by Farid Medjaboub, from IEMN in France, that has developed a technique to slash leakage currents through selective substrate removal. Taking this approach has already increased the blocking voltage of the GaN HEMT to 3 kV and beyond.

Over the next few years, it will be interesting to see whether this technique is used to extend the blocking voltage of commercial GaN HEMTs. If this happens, there should be a shifting of the boundary between both of the wide bandgap technologies. SiC would still be a winner, but GaN would grab the bigger prize.

Editor Richard Stevenson richardstevenson@angelbc.com +44 (0)1291 629640 Contributing Editor Rebecca Pool News Editor Christine Evans-Pughe Publisher Jackie Cannon Senior Sales Executive Robin Halder Sales Manager Shehzad Munshi USA Representatives Tom Brun Brun Media Janice Jenkins Amy Rogers Director of Logistics Sharon Cowley Design & Production Manager Mitch Gaynor

editorial@rebeccapool.com chrise-p@dircon.co.uk jackie.cannon@angelbc.com +44 (0)1923 690205 robin.halder@angelbc.com +44 (0)2476 718109 +44 (0)1923 690215 shehzad.munshi@angelbc.com tbrun@brunmedia.com +001 724 539-2404 +001 724-929-3550 jjenkins@brunmedia.com +001 678-714-6775 arogers@brunmedia.com sharon.cowley@angelbc.com +44 (0)1923 690200 mitch.gaynor@angelbc.com +44 (0)1923 690214 Circulation Director Jan Smoothy +44 (0)1923 690200 jan.smoothy@angelbc.com Chief Operating Officer Stephen Whitehurst stephen.whitehurst@angelbc.com +44 (0)2476 718970 Directors Bill Dunlop Uprichard - CEO, Stephen Whitehurst - COO, Jan Smoothy - CFO, Jackie Cannon, Scott Adams, Sharon Cowley, Sukhi Bhadal, Jason Holloway

Published by Angel Business Communications Ltd, Hannay House, 39 Clarendon Road, Watford, Herts WD17 1JA, UK. T: +44 (0)1923 690200 F: +44 (0)1923 690201 E: ask@angelbc.com

Angel Business Communications Ltd, Unit 6, Bow Court, Fletchworth Gate, Burnsall Road, Coventry CV5 6SP, UK. T: +44 (0)2476 718 970 F: +44 (0)2476 718 971 E: info@angelbc.com

Compound Semiconductor is published eight times a year on a controlled circulation basis. Non-qualifying individuals can subscribe at: £105.00/€158 pa (UK & Europe), £138.00 pa (air mail), \$198 pa (USA). Cover price £4.50. All information herein is believed to be correct at time of going to press. The publisher does not accept responsibility for any errors and omissions. The views expressed in this publication are not necessarily those of the publisher. Every effort has been made to obtain copyright permission for the material contained in this publication. Angel Business Communications Ltd will be happy to acknowledge any copyright oversights in a subsequent issue of the publisher. The paper used within this magazine is produced by chain of custody certified manufacturers, guaranteeing sustainable sourcing.US mailing information: Compound Semiconductor, ISSN 1096-598X, is published 8 times a year, Jan/Teb, March, April/May, June, July, August/September, October, November/ December by Angel Business Communications Ltd, Unit 6, Bow Court, Fietchworth Gate, Burnsall Rd, Coventry CV5 GSP. UK. The 2015 US annual subscription price is \$198. Airfreight and mailing in the USA by agent named Air Business Ltd, c/o Worldnet Shipping Inc., 156-15, 146th Avenue, 2nd Floor, Jamaica, NY 11434, USA. Printed by: Pensord Press. ISSN 1096-598X (Print) ISSN 2042-7328 (Online) © Copyright 2015.

### features

### 32 GaN transistors: Breaking barriers adoption

Grow GaN transistors on silicon and their bang-perbuck increases

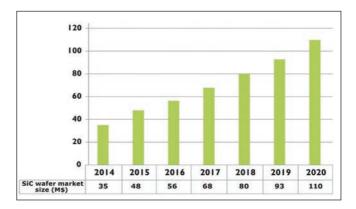

36 A positive outlook for the SiC substrate

Sales of SiC substrates will rise significantly as shipments shift to the 6-inch format and established suppliers face increased competition from Chinese start-ups

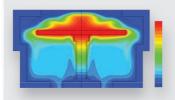

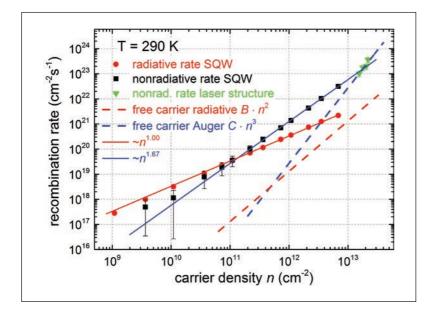

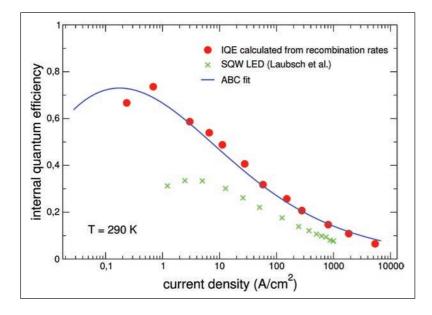

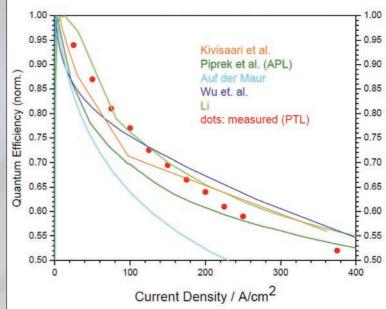

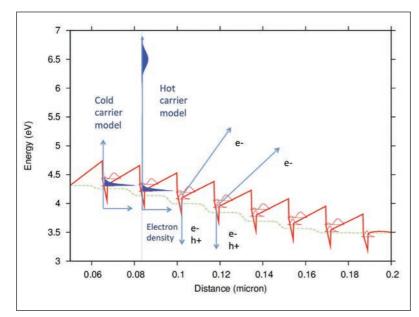

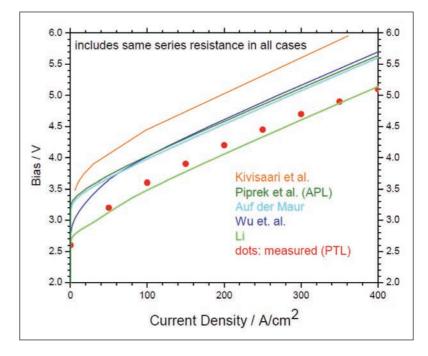

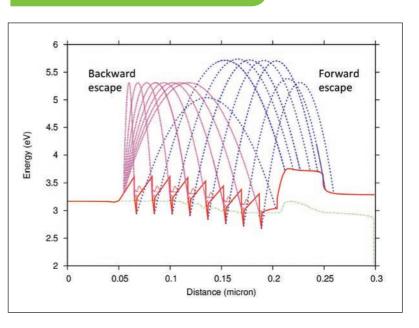

### 40 LED droop: Physics beyond the common model

Optical spectroscopy exposes fundamental flaws in the well-known model for LED droop

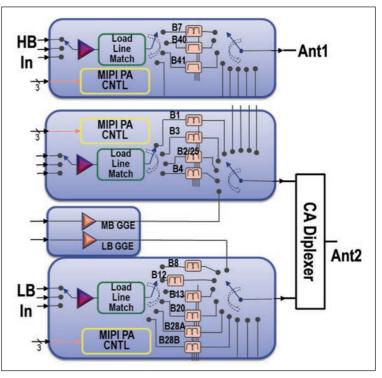

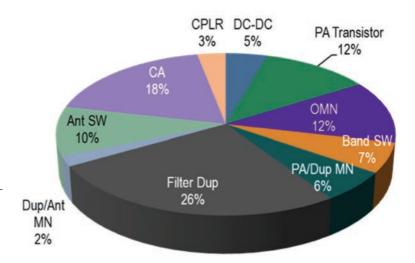

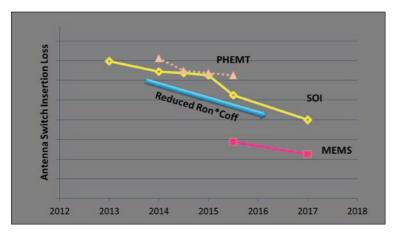

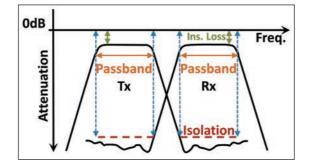

### 48 Multiple materials enhance front-ends

The front-ends of smartphones should not be served by a single material

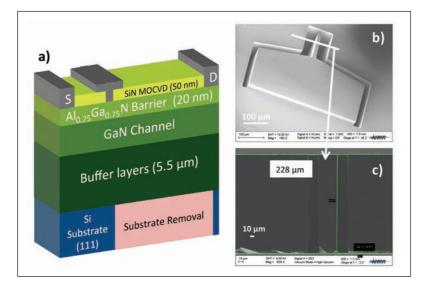

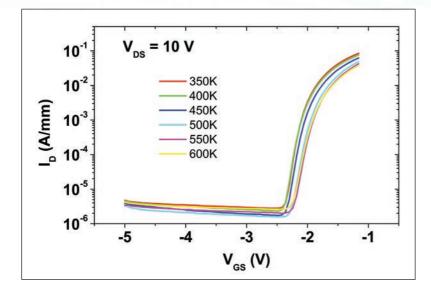

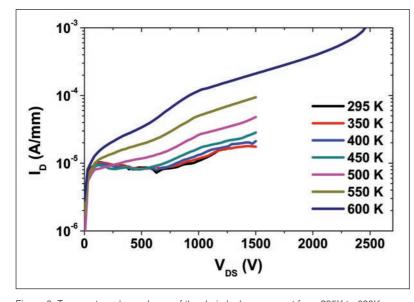

### 58 Extending the capabilities of GaN-on-silicon HEMTs

Removing the substrate allows GaN-on-silicon transistors to combine high operating temperatures with blocking voltages beyond 3 kV

### 64 Targeting spectroscopy with antimonide sources

By delivering great performance at low cost, GaSbbased devices are the ideal sources for gas sensing

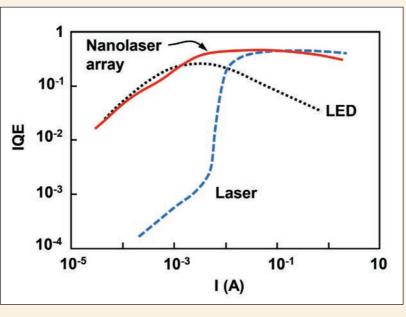

### 70 Can Auger recombination be good for LEDs?

The benefits of Auger: A reduction in turn on voltage and higher wall-plug efficiency

#### news

- 06 Osram announces €3 billion investment programme

- 07 Soraa moves ahead with manufacturing plans

- 08 Imec and Ghent University show InP laser arrays on silicon

- 10 Qorvo delivers solid Q2

- 11 AXT acquires GaAs line from Hitachi Metals

### news analysis

- 12 POET Technologies: From Lab To Fab

- 14 GaN: beyond the basestation

- 16 Plessey: bright and bold

- 22 MACOM set to mass market GaN

- 24 Delivering the future

- 26 Oclaro hits 2016 on a high

- 28 InP: great expectations

- 30 Beyond radar

### research review

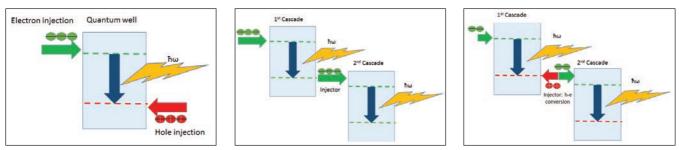

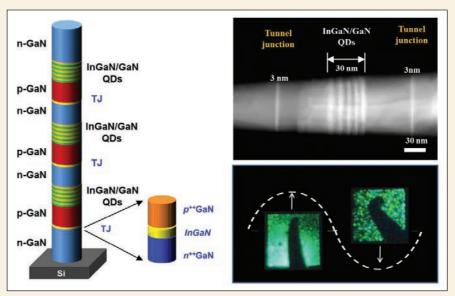

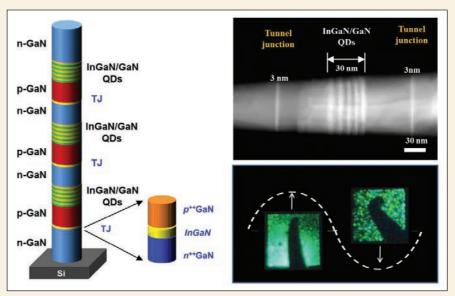

- 74 Optimising LEDs with tunnel junctions

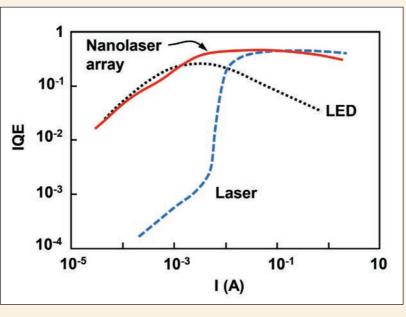

- 75 A better laser for lighting

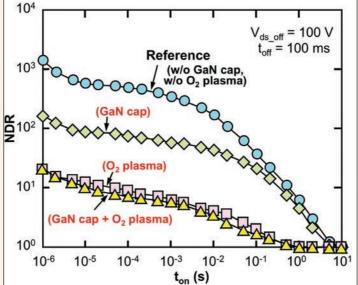

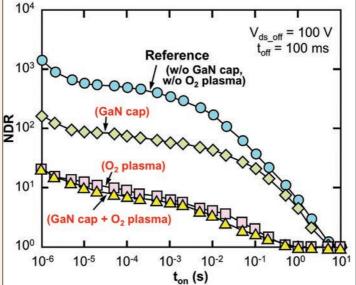

- 76 HEMTs: Oxygen plasma treatment eliminates

### NEWS REVIEW

## Osram announces €3 billion investment program

OSRAM has announced that it will invest around  $\in$ 3 billion in new technologies and applications by 2020. Of this, around  $\in$ 2 billion will be spent on R&D to expand into new markets. Another  $\in$ 1 billion will be for the construction of a new LED chip plant in Malaysia.

"With a focus on profitability, flexibility, and entrepreneurship, following a phase of strategic realignment, we are now launching the 'Diamond' innovation and growth initiative. This means we are switching the focus to sustainable growth, benefitting even stronger from the potential offered by semiconductorbased technologies," said Olaf Berlien, CEO of Osram Licht AG.

'Diamond' comprises several strategic measures. In a first step, Osram will invest around €370 million in its Opto Semiconductors (OS) segment for a new LED chip plant in Kulim, Malaysia. Since further expansion measures are already being planned, the company expects to invest a total of around €1 billion there by 2020. The new plant will represent the largest and latest 6-inch LED chip production site worldwide, according to the company.

Osram says that the additional production capacity and its technological leadership will enable it to significantly increase its market share in the fast growing general lighting markets. This market segment is the largest in the area of opto semiconductors, with a current volume of around  $\in$ 5.7 billion. Given average annual growth rates of 7.5 percent, it offers the company the greatest potential until 2020.

Through economies of scale, Osram says it can also reduce its cost position in other market activities such as automotive lighting as well as applications for mobile devices, in which Osram already has a strong presence.

Osram is also planning additional investments in the Specialty Lighting (SP) segment to enable a broad-based rollout of new technologies in the market and to realise further growth potential in areas such as automotive lighting. For example, Osram is currently the only company in the world offering laser modules for headlamps ready for series production. Another new technology in the field of automotive lighting is organic light-emitting diodes (OLEDs), which is also about to be rolled out for use in rear lights of vehicles. Osram expects the market for laser and OLED applications in the automotive sector to amount to around €1.1 billion in 2025.

In the recently created Lighting Solutions & Systems (LSS) segment, Osram will be focusing on intelligent, more technologically demanding lighting solutions. Given the increasing importance of complex lighting solutions, Osram is also shifting the focus on expanding the electronics and software expertise. Over the next two years, new capacities for electronic ballasts and light management systems will be created for this purpose.

In line with the announced innovation and growth initiative, Osram will increase its R&D budget significantly. By doing so, the company intends to promote in particular the development of smart city applications, wireless lighting control as well as laser and OLED technology.

Osram has kept its research quota at just over six percent of revenue over the past years. After the initiated carve-out of the general lighting lamps business, the increased research expenditure will account for approximately 9 percent of revenue by FY 2016.

"Investments in research and development have paid off for the company in the past by taking it to a clear number one position in the automotive sector and leading to groundbreaking applications with opto semiconductors. Through the intended increase in research intensity, Osram wants to further strengthen its technical expertise for semiconductor-based technology and extend its market position," said CEO Olaf Berlien. According to the company, the 'Diamond' innovation and growth initiative will focus the company on balanced growth and add value for employees, customers, and shareholders. In addition to highrevenue areas that hold large growth potential for the company, lucrative niche areas, where Osram is already in a good position, will continue to make a valuable contribution to overall returns. The company has set itself several targets to complete in the final year 2020.

One of these goals is to achieve revenue of between  $\in$ 5 billion and  $\in$ 5.5 billion. After the carve-out of the lamps business, this would correspond to an average annual growth rate of 8 percent.

Another asim is earnings before interest, tax, depreciation, and amortisation (EBITDA) of between  $\in 0.9$  billion and  $\in 1$  billion. This would correspond to an average annual growth rate of around 9 percent.

In addition, the company aims to generate earnings per share of around €5, which would be equivalent to an average annual increase rate of around 25 percent compared with fiscal 2015. The announced share buyback program is included in this target.

## Soraa moves ahead with New York manufacturing plans

SORAA, a developer of advanced lighting products and GaN-on-GaN LED technology, will open a new semiconductor fabrication plant in Syracuse, New York.

In partnership with the State of New York, the company will construct a new stateof-the-art GaN-on-GaN LED fabrication facility that will employ hundreds of workers.

Working in coordination with SUNY College of Nanoscale Science and Engineering (SUNY Poly CNSE), the new facility is on pace for shell completion by the end of this year with production beginning in the second half of 2016.

Soraa currently operates an LED fabrication plant in Fremont, California, one of only a few in the United States. "Central New York's economic growth is due in large part to high-tech companies like Soraa that recognise the region's wealth of assets and resources," Governor Cuomo said.

"Today's announcement not only means economic stability for the region, but it also strengthens Central New York as leader in the development of the clean technology that will help light and power the future."

"Syracuse is an optimal location for the new fabrication facility for a number of reasons including the innovative hightech vision and strategy of Governor Cuomo; the ability to attract some of the best and brightest scientists and engineers in the world; and the capacity to tightly control the product quality and intellectual property around our lighting products through our partnership with SUNY Poly CNSE," commented Jeff Parker, CEO of Soraa.

"Since we launched our first product in 2012, global market reception for our high quality of light LED products has been phenomenal and sales have soared. The new facility will significantly increase our manufacturing capacity to meet this growing demand."

### Infinera demos 100G on-demand at Supercomputing conference

INFINERA, a maker of InP photonic integrated circuits (PICs) and network equipment, and Corsa Technology, a software-defined networking (SDN) company, have announced a new demonstration of SDN-enabled ondemand 100 gigabits per second (100G) packet services.

The demo, which took place at the International Conference for High Performance Computing, Networking, Storage and Analysis (SC15) in Austin, Texas, show the feasibility of delivering the scalable, high-bandwidth services required by high-performance computing (HPC) and advanced research & education (R&E) applications.

Features include dynamic multilayer provisioning, precision switching and terabit traffic management, over a converged packet-optical transport network.

Infinera and Corsa collaborated to create the proof-of-concept demo using Corsa's 100G DP6400 switching platform, Infinera's Cloud Xpress metro

optical transport platform and Infineradeveloped SDN control capabilities. Also at the SC15 conference, Infinera has announced it would deliver 1.5 terabits per second (Tb/s) of transmission capacity with network firm CenturyLink to support SCinet at the SC15 conference. SCinet is a powerful network created each year to support the research applications and experiments taking place at the conference, connecting the Austin Convention Center to networks around the world.

The 1.5 Tb/s of line-side capacity connects the Austin Convention Center to CenturyLink's global fibre optic network, using the Infinera DTN-X platform. The terabit deployment demonstrated CenturyLink's rapid provisioning of 100 Gigabit Ethernet (GbE) services from the conference to CenturyLink's point of presence in Austin and to six major US cities across the country.

CenturyLink operates a 250,000-routemile US fibre network and a 300,000-route-mile international transport network. Through a dedicated network connection, the company delivers 100 GbE Optical Wavelength Service to enterprise customers; research, financial and educational institutions; and Internet content providers across the US and in select international cities.

The DTN-X Family is a key part of the Infinera Intelligent Transport Network, and includes the chassis-based XTC series and the new XT series. The DTN-X Family was recently extended with the addition of Infinera's DTN-X XTC-2 and XTC-2E for metro applications as well as with the DTN-X XT-500, a new compact platform to address long-haul high-capacity point-to-point interconnect applications.

### **NEWS** REVIEW

### Imec and Ghent University show InP laser arrays on silicon

IMEC AND GHENT UNIVERSITY have presented, for the first time, arrays of InP lasers monolithically integrated on 300 mm silicon substrates in a CMOS pilot line.

This breakthrough, published in *Nature Photonics*, provides a path toward high-volume manufacturing of costeffective photonic integrated circuits (PICs) with monolithically integrated laser sources. Such laser-powered PICs could change the way data is transferred between future logic and memory chips.

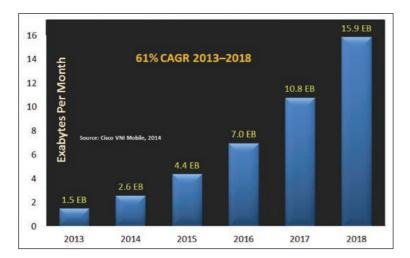

Over the past few years, demand for data communication between servers in cloud datacentres has been growing exponentially, following strong growth in social networking, cloud computing and big data applications.

Silicon photonics technology enables cost-effective manufacturing of fibre-

optic transceivers, which in turn provides continued scaling of server and datacentre capacity with improved power efficiencies. However, widespread adoption of this technology has been hampered in part by the lack of monolithically integrated laser sources.

The integration on silicon of efficient INP based light sources, currently driving long-range telecommunication networks, is known to be very challenging, owing to the large mismatch in crystal lattice constants between both materials.

Imec and Ghent University overcame these structural differences and largely suppressed the detrimental crystal defects that typically form at the interface between silicon and InP.

Using a production grade MOVPE growth reactor, InP semiconductor was selectively grown on silicon in a prepatterned oxide template, realising InP

waveguide arrays across the entire 300 mm substrate.

#### Subsequently, periodic grating structures were etched in the top layer of these waveguides, providing the optical feedback required for laser operation. Lasing operation was demonstrated for all tested devices consisting of an array of ten InP lasers. Typical lasing threshold powers of around 20 mW were observed at room temperature under optical pumping.

Lasing performance showed small variability along the array, illustrating the high material

quality of the heteroepitaxial grown InP. In addition, accurate control on the distribution of lasing wavelengths in the array was demonstrated by modifying the grating parameters.

The newly demonstrated approach for integrating lasers with silicon has been carried out in Imec's 300 mm CMOS pilot line facility, therefore providing a path to large volume manufacturing.

Ongoing research efforts focus on growing more complex layer stacks to enable electrical injection of the lasers and emission in the 1300 nm wavelength range, along with integration with silicon based waveguide devices.

This work has been carried out as part of imec's industry affiliation program on Optical I/O, which targets the development of a scalable, silicon-based optical interconnect technology for highbandwidth chip-level I/O.

The work was also partly supported by the European Commission through an ERC starting grant awarded to Dries Van Thourhout of Ghent University for research on Ultra Low Power Photonic ICs (ULPPIC).

This five year project aims to develop novel active photonic devices with lower power consumption, for integration on next generation electronic and photonic ICs.

Imec's research and development work on Optical I/O is performed in cooperation with key partners in its core CMOS programs including Huawei, GlobalFoundries, Intel, Micron, Panasonic, Qualcomm, Samsung, SK Hynix, Sony and TSMC.

### **MBE GROWTH SPECIALISTS**

Growth and device fabrication of arsenide/antimonide based III-V semiconductors notably:

- Narrow bandgap materials (InSb up to AIAs)

- Antimonide doping capability

- InGaAs/AlInAs structures lattice matched to InP substrates

- AlInGaAsSb lattice matched to InAs, GaSb or InP substrates

- Quantum dots/wells on GaAs substrates

- Antimonides on GaAs substrates using relaxed buffer layers

Supplier of low volume wafer requirements. Research work enquiries welcome.

Contact Tel - + 44 (0) 1236 781 900

Email – sales@quantumdevicesolutions.com

West of Scotland Science Park, Glasgow, G20 OSP

8 www.compoundsemiconductor.net November / December 2015 Copyright Compound Semiconductor

### Optimize the Thermal Performance of your Process Equipment.

Extensive computational tools enable product designs to be highly refined for ultimate performance.

Multi-zone circuit layouts in a polyimide construction are highly customized to deliver exacting performance up to 250°C.

EZ-ZONE® RM Multiloop controllers are fully scalable with up to 152 PID Loops and 256 monitor points per system. Washing at low provides innovative solutions to help process tool manufacturers meet the needs of the semiconductor technology roadmap. Our approach is to work collaboratively to help solve complex thermal challenges associated with state-of-theart manufacturing processes; helping to improve yield, throughput and cost of ownership. This includes innovative heaters, controllers and sensors for use in front-end and back-end applications such as CVD, PECVD, Etch, Diffusion, Bonding, IC test and more.

ASSURANT<sup>™</sup> gas and pump line heaters feature high temperature capabilities with low outgassing.

### Contact Watlow<sup>®</sup> today for the latest thermal solutions for semiconductor applications.

| European | Technical Sales Offices               | Italy |

|----------|---------------------------------------|-------|

| Germany  | +49 (0) 7253-9400-0<br>info@watlow.de | Spair |

italyinfo@watlow.com +34 91 675 1292 info@watlow.es

UK

France +33 1 41 32 79 70 info@watlow.fr

+44 (0) 115-964-0777 info@watlow.co.uk

+39 02 4588841

###

### NEWS REVIEW

### Qorvo delivers solid Q2

QORVO, a provider of RF and other technologies for mobile, infrastructure and aerospace/defence applications, has announced financial results for its fiscal 2016 second quarter, ended October 3, 2015. Qorvo also announced a new oneyear \$1 billion share repurchase program which expired on November 4, 2016. Share prices rose nearly 15 percent in response.

"The Qorvo team delivered a solid September quarter, with quarterly revenue increasing 12 percent year-overyear, led by strong 19 percent year-overyear growth in Mobile Products, " said Bob Bruggeworth, president and CEO of Qorvo.

"Design activity during the quarter was particularly robust, as we secured multiple opportunities to expand content in the marquee smartphones launching in calendar 2016 and 2017 and positioned IDP to accelerate growth across its target markets."

Steve Buhaly, chief financial officer of Qorvo, said: "In the nine months since Qorvo's formation, revenue has grown 25 percent from the same period in the prior year while non-GAAP operating income has nearly doubled. We're proud of this performance and are excited about our opportunities in the coming year."

On a GAAP basis, September quarterly revenue was \$708.3 million, gross margin

was down slightly at 40.2 percent (41.5 percent previous quarter), operating income was greatly increased at \$18.0 million (compared to a \$1.3 million loss in Q1) and net income was up to \$4.4 million (compared to \$2.0 in Q1), or \$0.03 per diluted share based on 150.8 million shares outstanding.

On a non-GAAP basis, September quarterly revenue increased sequentially to \$707.4 million and gross margin was 49.7 percent (down from 51.5 percent in Q1). Operating expenses declined sequentially, yielding operating income up at \$194.8 million (compared to \$187.8 million in Q1), or 27.5 percent of sales. Net income was \$183.3 million, or \$1.22 per diluted share based on 150.8 million shares outstanding.

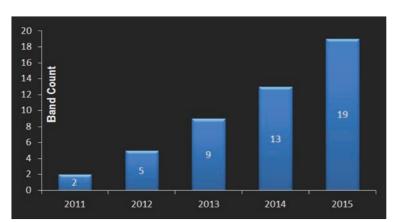

Strategic highlights include capturing multiple LTE reference design wins for multimode PAs, multimode transmit modules, switches, duplexers, and multiplexers; capturing BAW (bulk acoustic wave) filter and amplifier wins at Tier 1 automotive suppliers; solidifying long-term defence and aerospace market position by establishing multiple multiyear supply agreements; participating in pre-5G and 5G demos at major basestation OEMs; sampling high performance GaN-based macro cell PAs to the five leading base station OEMs; capturing an increasing percentage of DOCSIS 3.1 sockets with hybrid GaAs and GaN products.

### IQE appoints director for Compound Semiconductor Centre

IQE PLC, a supplier of advanced semiconductor wafer products and services, has appointed Wyn Meredith as director of the Compound Semiconductor Centre (CSC), the new joint venture, between IQE and Cardiff University was formally launched later this month.

IQE has a long standing relationship with Wyn who has been working on its behalf in a variety of roles, most recently developing links to education and funding bodies.

In his new role Wyn will be responsible for developing funding opportunities in

external programs and will report to the CSC board of directors.

Wyn, who holds a PhD in Optoelectronics from Heriot Watt University, joins IQE from his current role as Commercial Director at Compound Semiconductor Technologies Global Ltd (CST).

### Lumileds accelerates outdoor LED fixture design

Lumileds has introduced the Luxeon XR-M line of Matrix Platform solutions, designed as a turnkey solution for outdoor LED fixtures.

These building blocks integrate three, four or five Luxeon M LEDs on a metal core PCB, providing a platform that enables fixture manufacturers to accelerate their design of streetlights, high bay and low bay luminaires. For instance, the 2 x 2 LED square version, in combination with industry standard optics and driver, yields a complete IP66 solution, according to the company.

"Luxeon XR-M incorporates Luxeon M, one of our most efficient and top selling, high power LEDs. The boards can be connected in parallel or series for driver design flexibility, and the wide variety of lens options means designers have multiple turnkey options to release a full range of luminaires much faster to market," said Andrew Cohen, product manager of the Matrix Platform at Lumileds.

The Luxeon XR-M achieves 140 Im/W at 4000K, 70 CRI, T<sub>c</sub>=85degC and 700 mA drive current. Using constant pitch between the LEDs and PCBs, combining multiple Luxeon XR-M modules achieves the most uniform, distributed light patterns. Each Luxeon XR-M module provides 3,300 to 5,500 Im and is available in colour temperatures of 4000K, 5000K and 5700K with a minimum CRI of 70.

This new product is part of the Lumileds Matrix Platform of infinitely configurable LED boards, linear flex and modules featuring Luxeon LEDs. The Matrix Platform comes in both off-the-shelf and built-tospec options, offering a virtually limitless range of solutions for any application.

### NEWS REVIEW

### AXT acquires GaAs line from Hitachi Metals

AXT, a manufacturer of compound semiconductor substrates, has acquired highly automated processing and cleaning equipment for GaAs substrates from Hitachi Metals.

The production line includes automated equipment for wax mounting/ demounting, edge grinding, wafer sawing, polishing and cleaning. In addition, AXT has licensed from Hitachi Metals associated technical information and applicable patents intended to enable AXT to use the equipment in full production.

The equipment has been uninstalled in Japan and shipped to AXT's production facility in Beijing, China where it is currently being installed. SCIOCS, the related spin-off from Hitachi Metals, will assist in the installation and optimisation process. This production line is ideally suited for 4in and 6in GaAs and InP manufacturing processes and AXT intends to supply such GaAs substrates to SCIOCS and other customers.

"This acquisition comes at a time when AXT is making a concerted effort to invest in automated manufacturing equipment to increase sales of its InP substrates and 6in semi-insulating GaAs substrates," said Morris Young, AXT's chief executive officer. "We plan to leverage the automation and manufacturing technology acquired to further enhance our product quality and consistency. We are highly appreciative of the multifaceted partnership between the two companies."

The terms of the acquisition are not being disclosed. However, it is not expected to have a meaningful impact on the cost of operations going forward.

### MACOM announces datacentre chipset

MACOM TECHNOLOGY has announced a chipset for CWDM (coarse WDM) and PSM4 (parallel single mode) applications in the datacentre. The chipset includes the complete lineup of electronic and optical chips to achieve the lowest power consumption in a QSFP28 form factor.

As new mega-datacentres continue to expand to service the demand for highspeed data communications, the volume of 100G transceivers is expected to grow exponentially with the parallel need for lower power, smaller size and lower cost components. Macom has consolidated the high-speed semiconductor content in 100G transceivers and now offers a complete solution including lasers, drivers, clock data recovery (CDR), and transimpedance amplifiers (TIAs) – optimised to provide differentiated performance, power, size and cost benefits.

Macom's M37046 and M37049 are said to be the lowest power and smallest quad channel receive and transmit CDRs with market leading performance. The MAOM-002301 and MAOM-002304 are single and quad-channel direct modulated laser (DML) drivers that offer

the lowest power solution in the market. In addition, Macom's 127/129/131/ 133D-25C-LCG11 family of distributed feedback (DFB) lasers covers CWDM and PSM4 wavelengths, offering highperformance over broad operating temperature range. The M03002 and M03102 are single and quad-channel TIAs offering the industry's lowest noise and power consumption for 28G applications.

"This chipset demonstrates the value which Macom brings to our end customers and the industry as a whole," said Vivek Rajgarhia, VP of Strategy, Networks. "By providing the complete solution in a neat bundle, we can provide cost and power efficiency benefits which solve our customers' high speed networking challenges."

#### We bring quality to light.

### LED test & measurement

### Solutions from the world leader

Instrument Systems continues to set the benchmark in LED metrology. Whether testing individual LEDs (standard or high-power), LED modules, or OLEDs – the global LED industry relies on us to engineer superior measurement equipment for high-speed production testing applications.

### **POET Technologies:** From Lab To Fab

Can POET Technologies deliver commercial optoelectronic IC production? Rebecca Pool talks to CEO, Suresh Venkatesan, to find out.

TO SAY THE LAST FEW MONTHS have been action-packed for GaAsbased optoelectronic IC pioneer, POET Technologies, would be an understatement.

First, semiconductor industry trailblazers from Global Foundries and Applied Materials were hired. Second, the company hitched up with Anadigics to transfer its laboratory-proven VCSEL manufacturing to a commercial 6-inch process.

And now, investor relations advisor, Robert Ferri Partners, an organisation renowned for coaching up-and-coming tech-related businesses, has been brought in.

As Suresh Venkatesan, ex-Global Foundries senior vice president of technology development and now POET chief executive tells *Compound Semiconductor*: "To be taken seriously, the technology has to be transfered out of the lab and into something that can be manufactured on a wholesale basis."

"We're in the process of accelerating this transition today and will have detectors and VCSELs built using our proprietary process and Anadigics' commercial manufacturing process by the first quarter of 2016."

#### Talent grab

Venkatesan jumped aboard POET Technologies in June this year, joining former Global Foundries chief executive, Ajit Manocha, and ex-vice president of emerging technologies and products at Applied Materials, Subhash Deshmukh. Manocha is now co-executive vice chairman at the company while Deshmukh is chief operating officer.

The sudden swell of talent at POET has not gone unnoticed by industry pundits. One investor at US stock market analysis firm, Seeking Alpha, wrote at the time: "Professionals of this caliber simply do not leave leadership roles at multi-billion corporations for a tiny tech firm on a whim".

And as Venkatesan highlights, the move is exciting. "I've already taken many technologies from early concept to commercialisation but it's always been under the umbrella of large-scale companies such as Motorola and Global Foundries."

"With POET I get another chance to grow something from its concept phase that also has the potential to be substantially disruptive to the semiconductor industry," he adds.

The crux of POET's technology hinges on a patented materials system, pioneered by the company's chief scientist, Geoffrey Taylor. This supports monolithic fabrication of ICs comprising active and passive optical, and high-performance analog and digital electronics, components.

Right now, the company has its sights firmly set on manufacturing a 10 GHz VCSEL-based transceiver by early 2016, with the first step in its 'lab to fab' being to port its 3-inch fabrication process from the University of Connecticut's facilities to Anadigics' foundry in New Jersey.

The transfer is well underway and

Venkatesan is confident that Anadigics is the place to be.

"There are multiple foundries out there, but Anadigics has a state-of-the-art sixinch facility," he says. "We're targeting high-volume, low-cost markets and having the cost advantage of larger wafers is so important. And to be frank, I didn't want to go through multiple wafer transitions."

Also critically for POET, the New Jerseybased foundry has 6-inch VCSEL processing capabilities.

"There aren't too many companies out there today that have this. Most foundries are still at three or four inch, while many six inch foundries in the Far East don't yet process optical components," points out Venkatesan.

"In terms of long-term high-volume manufacturing we're still evaluating who this will be, but it is this mix of six-inch

facility and VCSEL capability that has engaged us initially with Anadigics," he adds.

With foundry in tow, POET is also about to pin down its epitaxy wafer supplier. According to the chief executive, the company is currently working with several external epi-vendors with a single source to be announced soon.

"We're still in the process of scaling up here, but over the course of this year, as epi-wafers are built and qualified, we will finalise our exact source," he says.

#### High volume, low cost

POET's first target market is short-range data communications. Power-hungry server farms, for example, are already looking for alternatives to the direct attach copper (DAC) cable assemblies for short-reach interconnects.

According to Venkatesan, POET's VCSEL-based transceiver will provide the

answer and be ready by 2017.

As Venkatesan highlights, thanks to its CMOS-based integrated process manufacturing, POET's components will be competitive with DAC.

"The main customer pain point in the DAC market is cost, and we are in parity with copper," he says. "But then the next important consideration is power and here, we can blow the socks off anything you get with DAC."

"We make what's on the wafer ten times more energy efficient, ten times cheaper and more than ten times smaller," he adds.

If successful at high volume manufacture, POET's monolithic opto-electronic process platform will extend the end of Moore's law, and even change the face of monolithic optical integrated circuit fabrication. But given the company's ambitious and aggressive commercialisation plans, how realistic is this goal?

Clearly cash could be a sticking point. Still at the end of September, the company unveiled a very healthy balance sheet of \$20.5 million in cash, expected to carry development for the next eight quarters, well beyond prototype demonstrations.

And Venkatesan is confident that with the process proven on a large-scale, licensees will follow.

"You don't attract good licensees until you demonstrate the value of your technology as a real product," he says. "Our strategy is to now focus on products and tie up licensees in the transceiver space and adjacent market segments. Yes, our roadmap is aggressive, but a lot of development has been going on for a fair amount of time," he adds. "We are creating disruption; it's exciting and risky, but no innovation comes without risk."

# **GaN:** beyond the basestation

As the GaN RF power amplifier penetrates wireless base stations, industry developments hint handsets could be next. Rebecca Pool talks to Qorvo to find out more.

IN A LITTLE over a decade, the mighty GaN transistor is transforming from novelty device into a must-have in a growing number of applications. Thanks to US government initiatives, GaN – with its staggeringly high power density – is the star technology in radar, electronic warfare and satellite, and is infiltrating more routine spaces, most notably wireless basestations.

Sumit Tomar, general manager of wireless infrastructure at Qorvo, is confident this passage to the more ordinary will continue. He believes GaN has already uprooted LDMOS, as the technology of choice for RF power amplifers in the high capacity base stations of 4G LTE network providers. And the endless need for greater network capacity and faster services, driven by rising mobile data demand, will only fuel this move.

"Next-generation base station platforms will go into production by the end of 2016, and we believe these will be based on high-power GaN RF amplification," he says. "LDMOS is limited beyond 2.4 GHz, so GaN comes into play here. At 4.5G and 5G we expect significant GaN adoption in base stations, particularly at frequencies greater than 1.8 GHz."

Tomar is also certain that network operators will opt for GaN-on-SiC power amplifiers, over GaN-on-silicon versions. GaN's impressive power density means devices can be housed in relatively small packages and still dissipate heat, but factor in silicon and this can change.

"Silicon has a poor thermal conductivity, compared to silicon carbide, and our customers are worried that GaN-onsilicon power amplifiers cannot dissipate heat as efficiently," he asserts. "This could reduce overall life cycle, raise the risk of field failure, which is a major issue for the basestation OEM customer."

"For power levels over 100 watts, all major players in the basestation market are not looking at anything on silicon for precisely this reason," he claims.

Right now, major GaN RF device providers, Cree, Sumitomo, Freescale, and of course Qorvo, are pursuing GaNon-SiC processes. In contrast, MACOM prides itself on being the world's only provider of GaN-on-silicon technology for RF applications, with its devices being used in military and communications applications.

However, earlier this month, MACOM started sampling a GaN-on-silicon wideband RF transistor for operation up to 200 W, and reckons the device delivers a performance to rival GaN-on-SiC.

As Michael Ziehl, vice president of marketing RF and microwave at MACOM said at the time: "We expect to see ramping commerical adoption of our GaN technology in other RF applications in the future, including 4G/LTE base stations."

Still, Tomar is confident leading systems providers, Freescale, NXP Semiconductor and Infineon are all looking to adopt GaN-on-SiC over GaNon-silicon.

"These players dominate the power market and are all pursuing GaN-on-SiC. GaN-on-silicon has a play at power levels less than 100 W, but at more than 300 W, the technology just isn't there," he says.

#### A different device

But basestations aside, industry players are beginning to explore the opportunities for high power density GaN power amplifiers in wireless handsets. Earlier this year, a group of researchers from Intel, led by co-director of Components Research in Technology and Manufacturing, Robert Chau, revealed an enhancement-mode GaN MOS-HEMT.

Designed for RF power amplifiers, as well as voltage regulators, in low power mobile silicon-on-chips, the researchers claim the transistor out-performs industry-standard GaAs RF power amplifier transistors in the power output and efficiency stakes.

Chau declined to comment on the latest development, but stated in his paper: "This work shows for the first time that the application space of GaN electronics can be expanded beyond the existing high-voltage power and RF electronics to include low power mobile SoCs."

Intel is the first company to publicly share such results, but doesn't appear to be alone in its development of GaN RF power amplifiers for next-generation handsets.

Tomar is quick to highlight Qorvo's GaAs process development, saying: "It gets tricky to put a higher supply voltage amplifier inside a handset but we have a unique pHEMT GaAs process that we can scale to serve the need of 5G handsets."

But at the same time, GaN HEMT development for power amplifiers in future handsets is clearly underway. "We are also working on GaN processes that I believe can go as low as 10V and in the future will go lower," says Tomar.

"I do not want to discuss this publicly," he adds. "But we will keep looking at different flavours of GaN, as well as other processes, and will see where the market goes."

### NEWS ANALYSIS

IN SEPTEMBER, UK-based Plessey revealed plans for a massive £60 million expansion at its Plymouth LED facility, after securing a £30 million loan from Deutsch Bank and having won £6.7 million in local government funds.

"To actually get a tier one bank on board at this stage [of our company development] is quite an achievement and very exciting for us," remarks Plessey's chief financial officer, lain Silvester.

"Using the Deutsch Bank Loan, Regional Growth Funds and our own cash generation, we will now add capacity as sales ramp," he adds.

Expansion plans are aggressive. Over the next two and a half to three years, the company intends to increase production capabilities by a factor of thirty – adding at least ten new reactors to the facility – while more than tripling the workforce to around 535 employees. As Mike Snaith, Plessey's operations director points out, the company has all the necessary tools to support current MOCVD throughput, with some redundancy.

However, to scale production, Plessey will now buy two additional reactors and expand bulk gas capability ready for at least another ten MOCVD reactor chambers, capable of 6-inch and 8-inch LED manufacture. The company has yet to confirm whether or not the new reactors will be sourced from Aixtron, Germany, or Veeco, US.

"Our Plymouth site has three clean room areas and our intention is to have all in-house capability for high-volume MOCVD GaN-on-silicon growth, high precision and large die alignment, deep trench etch, wafer bond and lift-off as well as a full back-end toolset," says Snaith. "One of the clean rooms will retain CMOS tooling to add additional passive components and allow for the power management and sensors, integrated into the silicon platform. At the same time, the company has recently patented technology relating to chip-scale optics, in which the LED lens is integrated on-chip.

According to Silvester, development will now continue apace, with the first integrated LED products reaching market as early as the second quarter of next year.

"Everyone understands the cost advantage that using silicon wafers will bring but this is actually secondary to some of the integration that we can provide within the device," says Silvester.

"Silicon substrates offer opportunities that just aren't available to sapphire, so using our existing CMOS skills and our engineering base, we will now develop these integrated LED devices."

But integration aside, a key goal for

### Plessey: bright and bold

With a hefty £30m bank loan and massive expansion underway, where next for GaN-on-silicon LED pioneer, Plessey, asks Rebecca Pool.

According to Silvester, come the end of next year around 150 new employees will already be on board, doubling today's headcount. The lion-share of new jobs will fall within the facility itself, with Plessey hiring more MOCVD operators, process engineers and skilled workers to manage the facility.

"We will see fairly modest growth on the commercial side of the business, but we operate all day and night, so really, this is going to be about scaling up production," says Silvester.

Since 2010, Plessey has been developing GaN-on-silicon LEDs using two Aixtron Crius II MOCVD reactors in a 7 by 6-inch wafer configuration. But this is set to change. manufacture of monolithic LEDs." And production will, at least for now, remain at Plymouth. "A typical competitor will have between fifty and one hundred reactors, and we are now looking to have about fifteen in our facility over the next three to four years," says Silvester.

"Whether or not we continue to manufacture in the UK, beyond this point, we will have to see, but growth over the next four years will certainly be driven by our Plymouth facility," he adds.

#### More integration

In addition to rapid expansion, siliconbased chip-scale packaging is well underway at Plessey, and the company intends to develop a range of integrated LED devices, that have, for example, Plessey has been to move from 6-inch to 8-inch wafer fabrication. The LED manufacturer has been working closely with Aixtron to address the MOCVD reactor re-tooling issues that accompany scaling, and Silvester asserts the latest Deutsche Bank backing will now accelerate this transition.

"We have an ongoing programme devoted to our eight inch process and most certainly we'll be moving towards eight inch production within four years," he says.

"Next year the new reactors will be six inch and beyond that we'll be re-tooling to eight inch," he adds. "Clearly a key goal is to set up eight inch production as fast as we can."

### 6<sup>th</sup> CS International Conference 2016 Brussels Belgium

CS International 2016 will provide timely, comprehensive coverage of every important sector within the compound semiconductor industry.

The 6<sup>th</sup> CS International conference will be held at the Sheraton Brussels Airport Hotel, in Belgium on Tuesday 1st & Wednesday 2 March 2016. The sixth CS International conference will build on the success of its predecessors, with industry-leading insiders delivering more than 30 presentations spanning sectors.

Visit www.cs-international.net for further information on this event

### **Book your place NOW!**

Visit www.cs-international.net/register.php to secure your place

### **TWO DAYS, FIVE THEMES** OVER 30 INSPIRING PRESENTATIONS

### Five key themes lie at the heart of CS International 2016:

- The quest for 5G,

- Driving deployment of wide bandgap power devices

- Exploiting opportunities for LEDs and lasers

- Making heterogenous integration a hit

- Capturing light, generating cash

Within each topic there is a key-note presentation from one of the most influential companies within this sector; one talk by a leading market analyst who will discuss trends within the industry and presentations by the leaders of firms developing cutting-edge technology in this field.

Connecting, informing and inspiring the compound semiconductor industry.

**Conference Chair:** Drew Nelson President, CEO, IQE

### This two day event covers five themes

#### The Quest for 5G

What challenges will GaAs and CMOS power amplifiers face in making the transition from 4G to 5G? And will faster data links play into the hands of GaN-based amplifiers for base stations?

**KEYNOTE James Klein: Qorvo |** Compound semiconductors: At the core of 5G

ANALYST Eric Higham: Strategy Analytics | Will chipmakers and foundries benefit from 5G? STRATEGYANALYTICS

**SPEAKERS**

Duncan Pilgrim: Peregrine Semiconductor | CMOS: Game on!

Peter Gammel: Skyworks Inc | Technology requirements and initiatives for 5G smartphones

Takahisa Kawai: SEDI | GaN for 5G base stations

#### Sumitomo electric device innovations

QOLVO

Peregrine

SKYWORKS

#### Driving deployment of wide bandgap power devices Is SiC set to displace silicon in electric cars? And how will this material help to revolutionise the efficiency and operation of electrical grids? KEYNOTE Daniel Fernandez: EU Project SPEED | Silicon carbide wide band-gap devices for energy applications ANALYST Pallavi Madakasira: Lux Research | Hype versus reality: driving adoption of wide band gap > luxresearch power electronics **SPEAKERS** ANVIL Peter Ward: Anvil Semiconductors | Driving down the cost of SiC devices for consumer applications EPIGAN Markus Behet: EpiGan | GaN on silicon - a truly revolutionary semiconductor technology matures FBH Fordinary Brown Institut Hans-Joachim Würfl: FBH Berlin | GaN normally-off devices for highly efficient power switching E LATEC Marta Borasio: Laytec | Reliability and yield limiting variances in power-electronic manufacturing early detection by advanced in-situ monitoring Mark Dineen: Oxford Instruments Plasma Technology | Latest developments in plasma etch processing for power and RF devices **PEAG** Yumin Gao: Evans Analytical Group | Advanced material characterization for Compound Semiconductor R&D and Manufacturing

All speakers and presentations are subject to change. ©2016 Angel Business Communications Ltd.

## CONFERENCE

### Connecting, informing and inspiring the compound semiconductor industry.

#### Exploiting opportunities for LEDs and lasers

Can LED bulbs meet the most demanding lighting applications, such as those found in the retail sector? And what are the opportunities for infrared and ultra-violet LEDs?

| KEYNOTE Abdelmalek Hanafi: BMW   Doubling driver visibility with laser-based headlights                      | BMW                               |

|--------------------------------------------------------------------------------------------------------------|-----------------------------------|

| ANALYST Pars Mukish: Yole Développement   Opportunities for IR LEDs                                          | V Développement                   |

| SPEAKERS                                                                                                     |                                   |

| David Cheskis: Anadigics I 6-inch VCSEL wafer fabrication manufacturing advances                             |                                   |

| Augustinas Vizbaras: Brolis Semiconductors   Mid-infrared light sources: manufacturability and applications  |                                   |

| Paul Crump: Ferdinand-Braun-Institut   High-power, high-efficiency lasers for fibre lasers and other markets | FBF Fredund<br>Fredund<br>Fredund |

| Reinhard Windemuth: Panasonic   Solutions for LED manufacturing                                              | Panasonic                         |

| Bedwyr Humphreys: Seren Photonics   Semi-polar Gallium Nitride enabling super high power automotive LE       | Ds seren                          |

#### Making Heterogenous Integration a Hit

III-V channels are poised to make an introduction in next-generation logic circuits. But how will they be introduced, and what impact will they have?

| KEYNOTE Yanning Sun: IBM   III-V/Si integration: Moore and more                                                     |                   |  |

|---------------------------------------------------------------------------------------------------------------------|-------------------|--|

| ANALYST Nadine Collaert: IMEC   Heterogeneous integration of high mobility materials on a 300mm Si platform         | Cimec             |  |

| SPEAKERS                                                                                                            |                   |  |

| Suresh Venkatesan: POET Technologies   A comprehensive technology platform for opto-electronic Integration          | POET Technologies |  |

| Lukas Czornomaz: IBM I Hybrid IIIV/SiGe technology for CMOS and beyond, opportunities for 3D monolithic integration | IBM.              |  |

| Thomas Uhrmann: EVG   Heterogeneous Integration enabled by Advanced Wafer Bonding                                   | EVG               |  |

#### **Capturing Light, Generating Cash**

What is needed to kick-start significant deployment of concentrating photovoltaic technology? And what are the opportunities for III-V detectors operating in the infrared?

KEYNOTE Carlos Algora: Technical University of Madrid | Perspectives of concentrator photovoltaic technology

ANALYST Frank Dimroth: Fraunhofer ISE | Terrestrial III-V solar cells - challenges and opportunities

**SPEAKERS**

Paul Sharps: Solaerotech | High efficiency multi-junction solar cells - what's next?

Andreas Umbach: Finisar | Propelling detectors to 100 Gb/s and beyond

Fraunhofer

All speakers and presentations are subject to change. ©2016 Angel Business Communications Ltd.

### **Book your place NOW!**

Visit www.cs-international.net/register.php to secure your place

### **PLATINUM SPONSORS**

INSTRUMENT

The Business of Science®

### **GOLD SPONSORS**

# MACOM set to mass market GaN

Will MACOM's latest GaN-on-silicon transistor nudge GaN from niche to norm, asks Rebeeca Pool.

WITH A SPOTLIGHT ON GaN, September was quite a month for MACOM. Celebrations of shipping more than one million GaN-on-silicon RF power devices were swiftly followed by the news that the company was sampling 100 W GaN-on-silicon HEMTs.

The latest continuous-wave wideband transistor, designed for DC to 2.7 GHz operation, boasts a 70 percent drain efficiency, which appears to have got many RF industry players excited.

As MACOM highlights, the latest 100 W transistor can now deliver a performance to rival more expensive GaN-on-SiC, with a cheaper volume production cost structure than LDMOS.

"We've made a breakthrough in drain efficiency which is now 10 percent better than the best of the LDMOS parts, targeted at similar applications in ISM frequency band applications," highlights Mike Ziehl, vice president of RF and Microwave. "So for the same given CW power, you have less heat dissipation and can reduce the costs of cooling and power supplies."

"These 100 W devices have caused some excitement, particularly in the RF Energy community," he adds.

MACOM manufactures both GaN-onsilicon and GaN-on-SiC HEMTs, and from word go has firmly outlined where it believes each technology belongs. Due to the high cost of growing SiC boules, this flavour of transistor will service low-volume, niche applications such as broadband electronic warfare jammers and radar systems, where the emphasis is also on performance.

In contrast, GaN-on-silicon has already been proven in military communications applications and MACOM is certain that cost-sensitive, high-volume applications will embrace the technology on 8-inch wafers. Indeed, the company is in the process of scaling manufacture to larger wafer sizes.

"We have long been a leader in L-band and S-band pulsed power radar and customers looking for the ultimate in performance still prefer GaN-on-SiC," says Ziehl.

"But for higher volume, commercial applications, we think GaN-on-silicon has to be the solution."

Right now, MACOM has its eyes on RF energy applications, such as the magnetron-powered microwave oven. In late December 2014, Freescale caused a furore when it delivered the first silicon LDMOS FETs to replace the mighty magnetron in the microwave oven. But the excitement could be short-lived.

"Solid state devices can be used to control cooking much more accurately than a magnetron, but the LDMOS transistor is only 60 percent efficient so you are giving away efficiency in today's systems," points out Ziehl. "Our Gen4 GaN-on-silicon transistor is much closer in efficiency to the magnetrons used in existing systems, which will make a big difference to manufacturers of the end product."

#### **Thermal concerns**

Other new markets for the 100 W GaNon-silicon HEMTs include automotive ignition and plasma lighting, but what about base stations? GaN-on-SiC power amplifiers are beginning to uproot LDMOS devices in high capacity base stations of 4G LTE networks.

However, concerns over silicon's poor thermal conductivity, relative to SiC, could slow demand for GaN-on-silicon versions. As Qorvo wireless infrastructure general manager, Sumit Tomar, told *Compound Semiconductor*, in late September: "Our customers are worried that GaN-on-silicon power amplifiers cannot dissipate heat as efficiently."

Ziehl disagrees. While the vice president did not want to detail customer discussions, he highlighted: "This is not a materials discussion on whether its silicon or silicon carbide, this is a product discussion."

Indeed, as Ziehl highlights, during GaNon-silicon HEMT manufacture, MACOM thins its wafers, optimises the die attach and die attachment methods, die layout and more.

### NEWS ANALYSIS

Will the latest 100W GaN-on-silicon transistor open new markets for the GaN technology?

"We pay attention to every step of transistor assembly, and even at 100 W, I can show you our GaN-onsilicon parts that have a better thermal rating than other manufacturer's 100 W GaN-on-SiC parts," he asserts.

"We have customers that come to us and say, 'well I need a SiC transistor as its thermally superior', and then we educate them as to what our GaNon-silicon product does compared to other products in the market at similar power level," he adds.

So where next for MACOM's GaN-onsilicon technology? According to Ziehl, the 100 W HEMTs are only the first in a family of 200 W and 300 W transistors; these are expected to sample late this calendar year.

What's more, the company also expects its first GaN-on-silicon devices to enter high-volume production in 2016, which will surely mark a watershed for commercial GaN. Still, the vice president remains balanced.

"This is all about offering the right choice of GaN to the application. If you look at RF energy, it's higher volume so GaN-on-silicon is the solution, but for electronic radar, its GaN-on-SiC," he says. "We offer what meets our customers' challenges, and sometimes they buy both."

# Delivering the future

With III-V and CMOS integration well underway, novel ICs from Singapore-MIT program, SMART-LEES, could reach market soon. Rebecca Pool reports.

FROM THE OUTSET, researchers from the Singapore-MIT Alliance for Research and Technology, working on low-energy electronics systems, decided not to reinvent the wheel.

Brought together by the Singapore government and MIT in January 2012, the SMART-LEES team intends to create fundamentally new integrated circuits based on III-V materials and silicon as Moore's Law collapses. And according to academic Eugene Fitzgerald from MIT, working with silicon has always been the priority.

"Silicon foundries already have CMOS manufacturing in place and these organisations can't be expected to change processes just to carry out crazy stuff for universities," he says. "Yet, whenever someone comes up with a new device it is difficult to insert that into the manufacturing infrastructure."

"We know from a capital point of view it doesn't make sense to build new infrastructure end-to-end for this," he adds. "So from the very beginning we have said that III-V materials have to fit into a silicon design kit."

With this in mind, researchers from the SMART-LEES programme, based at

MIT, National University of Singapore and Nanyang Technological University, have been working with myriad industrial partners on this very issue.

Silicon CMOS powerhouses, Global Foundries, Singapore, and Japan-based Tower Semiconductor-Panasonic joint venture, TPSCo, are key manufacturing partners. Meanwhile Aixtron, Germany, IQE, UK, Austria-based EVG, and Samco of Japan, all join forces with the project later on along the IC supply chain.

And with weighty board members from IQE, Netherlands-based Lumileds and Analog Devices, US, also backing the project, SMART-LEES clearly has clout.

"We set up the board to have stakeholders that would be interested in seeing this succeed," highlights Fitzgerald.

"But we also put together a research team from materials, device and circuit design that can simultaneously influence each other," he adds. "And because we can't re-work the entire CMOS process, we developed 'modular processing'."

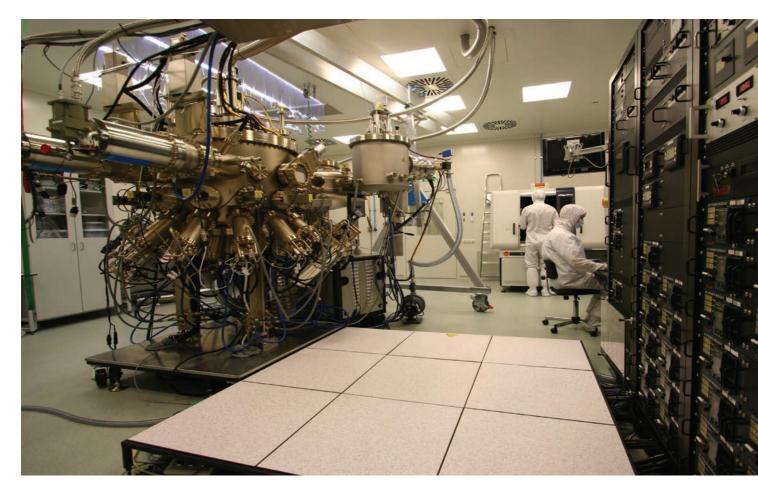

Here, the researchers take 200 mm silicon wafers from the front-end of their partner's CMOS manufacturing

processes and then use existing CMOS design tools to develop novel ICs at the SMART-LEES 200 mm facility in Singapore.

This fab houses two Alixtron CRIUS reactors and *in-situ* optical monitoring tools, so here, III-V layers are added and devices are fabricated. The wafer is then returned to the foundry for the back-end processes that connect the III-V and silicon CMOS devices within the die.

"We've set up LEES so we can add any kind of III-V material, but it has to be done so that the wafer looks like it never left the foundry," says Fitzgerald. "The wafer will return with dielectric and contact areas so that you start the back-end of the foundry process, it looks like it never left."

And as he adds: "What this actually does is to induce innovation that is exactly aligned to future manufacturing requirements. We innovate around, say, particular temperatures and processes so [our results] are ready for commercialisation."

Indeed, in 2012, the LEES team started work on GaN, GaAs and InP deposition on silicon substrates, but as Fitzgerald points out, 'things have moved on'. The researchers are now focusing on InGaAs and GaN, integrating an InGaAs HEMT, GaN HEMT and GaN LED into silicon design platforms.

"We now have an entire process and design toolkit which can include latticemismatch engineering such as aspect ratio trapping and metamorphic buffers," explains the MIT Professor. "We do a lot of epi- and wafer-bonding, and have basically created an engineered substrate that can support whatever device we want."

"We transfer the CMOS processes to the top of this, process the III-V devices... and send them back to the foundry," he adds. "So we can design, for the first time, circuits as part of a very real foundry process, and that's not easy to do. There's no special research process and this is unique."

Clearly, the main thrust of the LEES manufacturing model is to get novel integrated circuits into the marketplace faster and more easily, but when will industry see real devices? It could be sooner rather than later. According to Fitzgerald, test chips will be delivered next year and he expects to see

prototypes in very real applications some

two to three years later.

LEES has a cleanroom equipped with epitaxy and microfabrication tools capable of handling 200 mm wafers, and a characterization facility providing inspection and characterization of wafers and devices. Credit: SMART LEES

"We pretty much know how to put III-Vs onto silicon wafers, but when we started, the complete unknown was how to then transfer the CMOS onto this engineered substrate," he says. "But we're now moving wafers back and forth between the foundry and thanks to sizable enough funding, our companies and researchers can collaborate in ways that wouldn't normally be possible."

"Soon, we're going to have the one thing that everyone wants," he concludes. "And that's to have a design kit for both III-V devices and CMOS."

### NEWS ANALYSIS

Suppliers of optical components are benefiting from the growth in cloud computing and internet traffic. One company in this position is Oclaro, which is sampling its QSFP28 transceiver to data centres upgrading to 100G infrastructures.

### Oclaro hits 2016 on a high

Following a hefty restructure, Oclaro posts impressive financials. Can industry expect more of the same, asks Rebecca Pool.

EARLIER THIS AUTUMN, optical component and module supplier, US-based Oclaro, revealed a key milestone in its first quarter 2016 financial results that set investors buzzing.

By generating its first positive adjusted EBITDA of \$4.2 million, it had spectacularly increased what is essentially net income by \$25 million in just two years.

At the same time, \$87.5 million revenues came in at the high end of guidance, up by more than \$5 million from the fourth quarter. And gross margin reached 2 percent, marking an increase of 6 percent from last quarter.

Clearly the results spell good news for a company that has recently taken severe measures to reach profitability.

In 2014, chief executive, Greg Dougherty, announced a major re-structuring

programme, culling staff numbers by some 50 percent to 1500.

Meanwhile, operating sites were reduced and the company's GaAs laser diode business sold to II-VI for \$115 million, bringing in some \$88 million in cash.

Following the results, shares stood at \$3.38. They have edged upwards throughout the past year as rival Finisar shares drift down. And as Dougherty said in his recent earnings call: "We have firmly put the turnaround challenges behind us."

Alex Henderson, senior analyst at USbased investment banking and asset management firm, Needham, was somewhat surprised by Oclaro's latest results.

As he tells *Compound Semiconductor*: "Revenues were ahead, but within the range of expectations for improving growth. [But] we were surprised at the sharply better than expected gross margins."

The Needham analyst attributes the company's results to three key factors: first, production is streamlined; second, money-losing legacy products have been ditched; and third, manufacturing takes place in regions that have benefited from a strong US dollar; namely Japan and Europe. And now, Oclaro looks set to achieve profitability.

"The company is on the cusp of profitability," says Henderson. "It's already cash-flow positive, and while annual price reductions in the March quarter are likely to slow improvement, it will likely hit the mark in the June quarter."

Potent products According to Oclaro's Dougherty, latest quarterly revenues were primarily

This isn't an enormous surprise. While 100 Gigabit Ethernet has been a long time coming, industry pundits predict 2016 is set to be a breakthrough year.

IHS Infonetics, for one, has predicted next year will be 'huge' for 100G as products reach market and internet content providers, for example, shift from 40G to 100G optics, driving sales.

Anticipating rising demand for 100G transceivers, Oclaro increased capacity for its 100G client-side transceivers in early 2015 and has been sampling its QSFP28 transceiver to data centres upgrading to 100G infrastructures. It has also started shipping its DWDM lineside analog-coherent transceiver – deemed to be the company's 'biggest deal' by Henderson – for deployment in this quarter.

And pleasingly for Oclaro, demand from China, for client and lineside 100G products, is rising.

According to Dougherty: "It appears our customers are preparing for awards for 100G systems from China Mobile and China Telecom... and we expect to see continued 100G sales growth in China."

Henderson concurs, and points out that other industry players including MACOM, Inphi, Oclaro and Lumentum are also reporting ramping China orders.

"This demand is likely to cause abnormal demand in the first half of 2016," he says. "If stronger China demand picks up enough, it could cause [Oclaro's] March quarter to buck seasonal patterns, resulting in even earlier [profitability]."

So the future looks bright for Oclaro. With shrewd product development beginning to pay off, it has nearly clawed its way back to profitability.

But competition is fierce, and size-wise, the company is small compared to the likes of Finisar and even NeoPhotonics. Could scale be an issue?

Henderson thinks not. "Competition is stiff in VCSEL short-range optics but less so in [Oclaro's] high-end integrated segment," he says,

"Also, we do not see China-based players moving up in scale with the fab and integrated optics capabilities. Oclaro has a very good technology and strong management with a clear roadmap," he adds. "This and its strong offerings could vault them over the next few years."

### InP: Great expectations

As AXT buys Crystacomm, Morris Young, AXT CEO, tells Rebecca Pool about plans for 6-inch InP substrate growth, mobile markets and more.

EARLIER THIS YEAR, compound semiconductor substrate maker, AXT, acquired California-based InP substrate developer, Crystacomm in an all-cash deal.

While AXT is perhaps best known for supplying wireless device markets worldwide with GaAs substrates, the California-based business also grows InP substrates, which begs the question; why buy Crystacomm? The answer lies in markets and quick, cost-effective crystal growth.

Ten years ago, AXT's GaAs substrate sales were rising rapidly, largely thanks to increasing GaAs content in mobile products and a resurgent LED industry.

Smartphones, netbooks and more, were supporting new features that demanded an increasing number of power amplifiers and switches, reliant on GaAs substrates.

Meanwhile, automotive and display lighting was driving LED sales with 2-, 3and 4-inch GaAs substrates scooping the lion's share of the market.

Fast-forward a decade and the semiconductor market is a different place. "The cellphone switch business,

which we supplied with GaAs pHEMTs, has been beaten back by SOI taking market share," points out AXT chief executive Morris Young. ""The GaAs landscape has taken this on the chin; for example, Hitachi Cable went out of business."

"Also, business opportunities do exist for LEDs, but pricing pressures have been very severe, so we don't have a lot to report here," he adds.

But amid the struggle, InP has become, in Young's words, 'AXT's bright spot'. As the chief executive highlights: "In 2010, InP substrates were a small portion of our revenue contribution, but this business segment has since grown very nicely and InP now claims the largest proportion of our revenue."

#### New applications

Right now AXT's InP substrates are largely supplied to manufacturers of lasers and photodetectors for fibreoptics network applications, including fibre-to-the-home as well as data centre communications.

However, device manufacturers are increasingly keen to harness the material's high electron mobility in the fabrication of HBTs and HEMTs. Indeed, looking to the future, 5G mobile networks could hold tremendous promise for this flavour of substrate.

According to Young, next-generation wireless communications networks will demand frequencies as high as 25 GHz, which devices fabricated on silicon substrates, and even GaAs wafers, will struggle to support. "InP is the natural choice as it has the properties to enable the increasing requirements of 5G, and is also lower in cost and power consumption than GaN," he says. "We know a very large wireless device maker has been looking at InP very seriously."

And this is where AXT's latest acquisition is important. Crystacomm was the first to deliver 2-, 3- and 4-inch commercial InP substrates and is also leading the development of 6-inch InP technology, which could prove vital to the development of cost-effective, InP-based transistors for 5G wireless devices.

What's more, while AXT has pioneered Vertical Gradient Freeze (VGF) growth for InP, and other substrates, Crystacomm has focused on Liquid Encapsulated Czochralski (LEC) growth.

Compared to LEC growth, VGF growth can produce substrates with relatively low defect densities and higher mechanical strengths, leading to better epi-layer quality and higher circuit yields during device production, as well as superior device performances. But when it comes to 6-inch InP wafers, VGF growth is simply too expensive.

As Young asserts: "If you want a substrate with a very low etch pit density and low stress then VGF is the way forward, in fact VGF has won the race in producing materials for GaAs-based devices."

"But in HEMT and HBT applications, LEC has hung on to the market for quite a while, and has this unique opportunity to bring the larger diameter of 6-inch InP

into play at potentially higher yields," he adds. Young won't yet confirm that, for example, the etch pit densities, in 6-inch, LEC-grown, InP substrates will be sufficiently low enough for nextgeneration wireless devices.

6-inch InP substrate growth is in its infancy, and as he highlights: "6-inch GaAs took a US Defense Production Act Title III program and millions of dollars in funding to achieve. This is a fairly major task and we still need partners."

But the prospect is clearly there and in the meantime, he is keen to offer AXT customers a choice of VGF- or LECgrown substrates.

"Internally we will allow the technologies to compete," he says. "If, for example, you can tolerate a slightly higher etch pit density, then we could provide you with an LEC material at, perhaps, a discounted price."

#### Work in progress

Right now, Crystacomm's crystalgrowth equipment and processes are being installed at AXT's Fremont facility. Crystacomm founder and chief executive, George Antypas, is leading activities and will stay on as a consultant to AXT.

Equipment includes a 6-inch crystal growth prototype system but as Young emphasises, the prime focus will be to repeat what Crystacomm can do with its 2-, 3- and 4-inch crystal growth equipment at the Fremont facility. The team intends to turn to the 6-inch system in a year, to a year and a half. Looking to the longer term, Young is excited about the potential market opportunities for InP substrate providers. As he highlights, right now, only a few InP providers exist including, AXT, Sumitomo Electric, WaferTech and InPACT.

"During the nascent stage of GaAs, there were around twenty substrate makers worldwide although many have now dropped out," he says. "In comparison, in InP, we only have a few. The material is very challenging but I believe we can develop it."

### NEWS ANALYSIS

As solid-state GaN power amplifiers permeate radar applications, UK developer, Diamond Microwave, is eyeing new markets. Rebecca Pool reports.

EARLIER THIS AUTUMN, UK-based Diamond Microwave launched its latest in a rapidly growing line of GaN-on-SiC pulsed solid-state power amplifiers that can also operate in continuous wave mode.

The latest 1 kW X-band device operates over a 1200 MHz bandwidth, at 9.5 GHz, is described as ultra-compact and primarily targets the radar applications that traditionally would have relied on travelling wave tube amplifiers.

As Ian Davis, business development manager at Diamond Microwave, puts it: "Like all our GaN solid state PAs, these amplifiers employ a chip-and-wire microwave design.... and [have] a powerto-volume ratio that we believe to be among the highest in the industry."

Since it span out from the diamond electronics team of synthetic diamond materials developer, Element Six, in 2006, Diamond Microwave has witnessed much change.

Setting out to develop a diamond MESFET for future microwave power modules, chief executive, Richard Lang said at the time: "The technical challenges are high... there is much work to be done to realise a practical device."

And he was right. Five years later, diamond transistor development

had dwindled, and as Davis now says: "We successfully demonstrated that the approach most researchers were using to produce a diamond transistor was flawed."

Still, the time wasn't wasted. According to the business development manager, Diamond Microwave had built a GaN power amplifier with the intention of

replacing its GaN transistors with a diamond-based version.

Clearly, this was never meant to be, but as Davis highlights: "GaN was now emerging as a practical semiconductor material and we had developed a very good GaN amplifier here."

"We won a major contract with a prime defence manufacturer for further development and are now producing GaN solid-state power amplifiers."

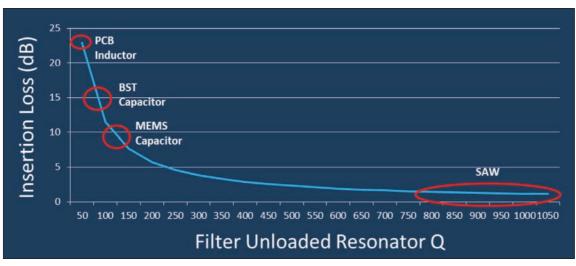

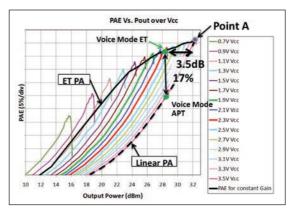

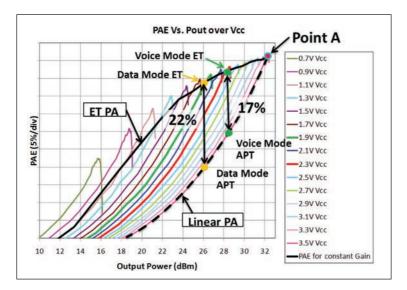

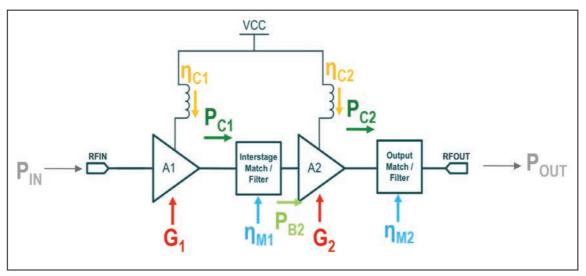

Today, radar – both civil and defence – applications are Diamond Microwave's number one market. GaN power devices are steadily displacing travelling wave tube amplifiers at higher and higher frequencies, and the company is chasing the resulting market share.