# COMPOUND SEMICONDUCTOR SENSON

CONNECTING THE COMPOUND SEMICONDUCTOR COMMUNITY

VOLUME 31 ISSUE V 2025

COMPOUNDSEMICONDUCTOR.NET

## AIXTRON

## THE NEW G10 SERIES

Your Productivity Solution for All Advanced Epitaxy Materials

## G10-SiC

- ▶ 9x150 mm (6") or 6x200 mm (8")

- New hardware & process surpassing Single Wafer Reactor uniformities

- ► +50% productivity per fab area with large batch technology & small footprint

#### **End Markets/Products:**

EV inverters & charging infrastructure

## G10-GaN

- ▶ 8x150mm (6") or 5x200mm (8")

- ▶ 1st fully automated compact GaN MOCVD cluster designed 100% for Si Power fabs

- Novel hardware solution for unmatched barrier uniformities and device yields

#### **End Markets/Products:**

Power Electronics & Wireless communication

## G10-AsP

- ▶ 8x150 mm (6") or 5x200 mm (8")

- ▶ 1<sup>st</sup> fully automated AsP MOCVD system enabling 10x lower defect density

- Unmatched wavelength uniformity on all wafer sizes

#### **End Markets/Products:**

Micro LED, Optical Data communication, 3D-sensing & LiDAR

# BY RICHARD STEVENSON EDITOR

## A blast from the past

IN YOUR SPARE TIME, do you immerse yourself in technology developed in a bygone era? If so, maybe like me, you while away your hours trying to optimise the fidelity of your record player? Or maybe you help to run a steam train, or are fascinated by film-based cameras.

In our industry, it feels like it's a golden rule to never look back. Instead, we focus on the future, allured by promise of new materials and architectures that enable betterperforming devices. This might involve bigger bandgaps that improve electrical conversion efficiencies, or device miniaturisation, such as smaller microLEDs and RF sources operating at higher frequencies.

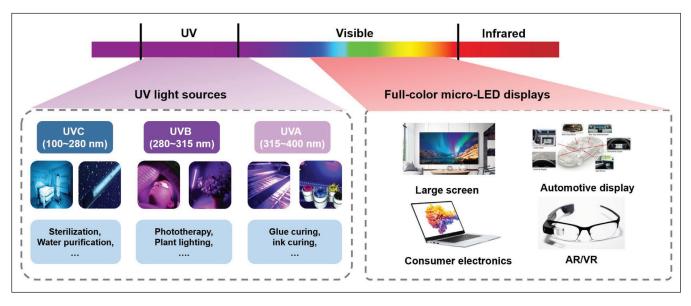

Bucking this trend, and to good effect, is US start-up NS Nanotech (see p. 16). It's employing a novel approach to producing relatively powerful sources in the deep-UV that draw on technology developed for the TVs of yesteryear, which were based on cathode ray tubes.

This move comes against a backdrop of several decades of development of deep-UV LEDs, involving researchers within our community devoting a great deal of effort to increasing the efficiency and output power of these devices, and plunging new depths, in terms of wavelength. Gains in UV LED performance have been very hard to come by, due to a number of challenges, including realising reasonable values for doping and light extraction – and while today's devices are much better than their predecessors, they are pitiful when compared with their blue-emitting cousins.

Offering more power is Nanotech's alternative approach to producing solid-state sources emitting in the deep UV. Rather than using electroluminescence, it employs cathodoluminescence, with hot electrons emitted from a filament bombarding a wide bandgap semiconductor to generate UV light.

And what is this semiconductor that's whacked by countless electrons? While the obvious contender is AIN, NS Nanotech sees the situation differently, employing a material we are only just starting to hear much about, BN. It has an even bigger bandgap, with its band-edge emission delivering UV light at 215 nm, an ideal wavelength, as it avoids any concerns associated with causing harm to humanity.

In fact, the 500-microwatt sources that are

being marketed by NS Nanotech are being touted as a great aid to all of us, by providing air disinfection in private cars, Ubers, ambulances and air ambulances.

By helping reduce the spread of diseases, this product can play a key role in increasing the health of nations — and it could also help to combat pandemics, an issue that matters, even if that's the last thing we want to think about day

It's interesting to note that for those wanting higher powers than NS Nanotech can provide in this part of the deep UV – think owners of movie theatres wanting to prevent germ spreading – the leading solution is a lamp based on krypton chloride

Tube-based technology is also key to providing high powers at very high frequencies, and in the minds of some audiophiles, is the best option for driving high-efficiency

speakers. So, in some fields of engineering, the technologies of yesteryear have never gone away – and maybe that should be food for thought for our community.

## 22 HRL's GaN: from innovation to qualification

Maintaining the tradition of being 'first' in technology innovation, HRL's latest T3L GaN technology delivers a world-leading high-frequency performance with a process that's manufacturable, stable, predictable and reliable

## 18 CMOS: Not just for silicon

While CMOS may be synonymous with the manufacture of silicon ICs, it's a versatile process can also be applied to the production of photonic and microwave circuits employing compound semiconductors

## 28 Empowering power devices

Novel material combinations and innovative architectures take GaN and  ${\rm Ga_2O_3}$  power devices closer to fulfilling their full potential

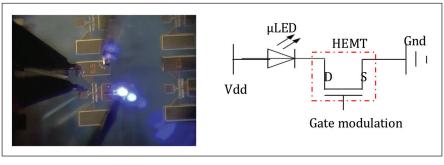

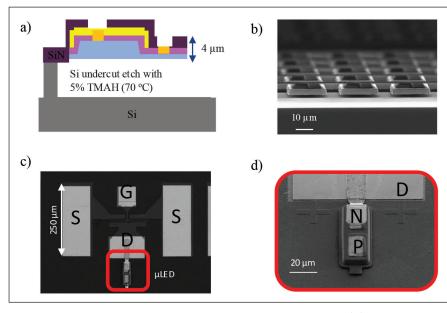

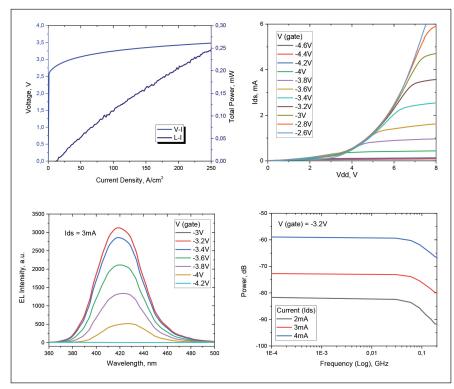

## 34 Shrinking the size of LiFi through heterogeneous integration

Combining microLEDs and GaN HEMTs via transfer printing creates chip-scale systems that are opening new possibilities for visible light communication

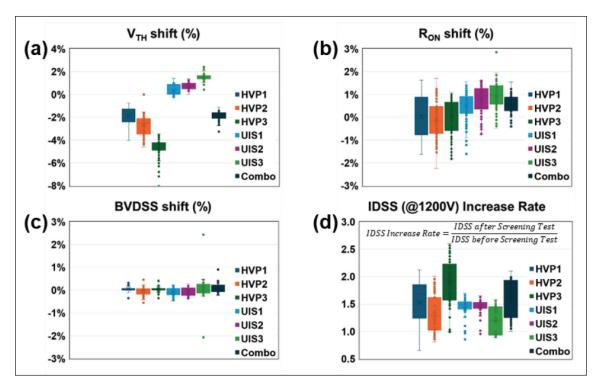

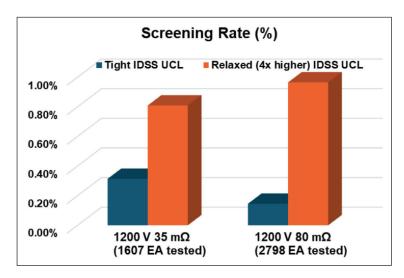

## 38 Scrutinising SiC MOSFETs

Efforts by chipmakers to improve the SiC MOSFET include investigations to understand how the design of the trench influences ruggedness, the role of the substrate on device quality, opportunities for superior screening, and the origin of shifts in threshold voltage

## 48 Strain modulation techniques for enhancing LED efficiency

By promoting the heteroepitaxy of high-efficiency LEDs in the UV and the red, strain modulation is accelerating the development of III-Nitride optoelectronics

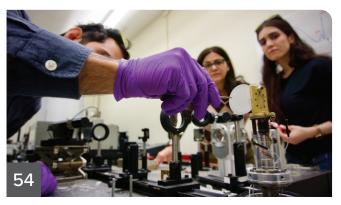

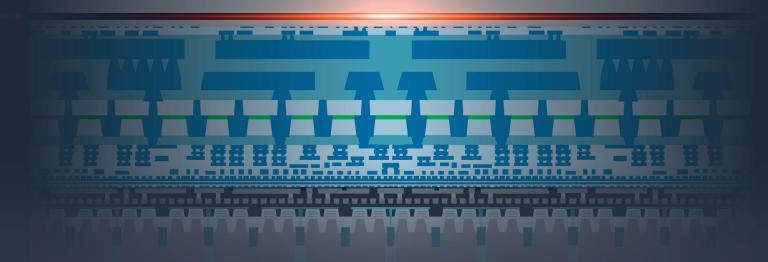

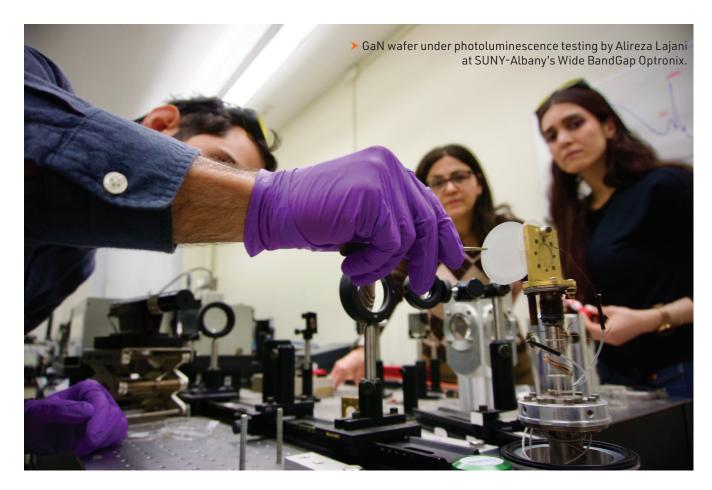

## 54 The quest for Be-tter p-doping

One promising option for enabling effective *p*-type doping in GaN and its related alloys is to introduce beryllium, possibly in the form of impurity complexes

## **NEWS ANALYSIS**

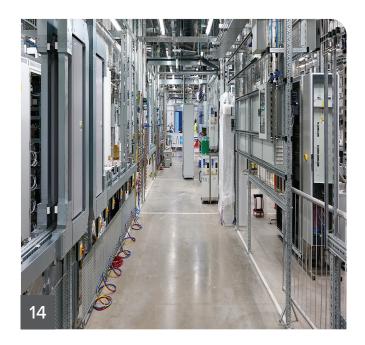

## 14 KLA: Expanding within the CS cluster

Equipped with a demonstration lab capable of accommodating more than 100 modules, KLA's new, purpose-built facility should spur further growth of its deposition and etch tool businesses

## 16 Retro-tech revolutionises the deep UV

Compact sources of deep-UV emission from NS Nanotech are providing air purification through cathodoluminescence of boron nitride

## RESEARCH REVIEW

- 58 A GaN-on-silicon foundation for Ga<sub>2</sub>O<sub>3</sub> transistors

- 59 Cooling RF GaN HEMTs with all-around diamond

- 60 Scaling quartz-free HVPE of GaN-on-GaN epiwafers

## **NEWS**

- **06** Wolfspeed announces restructuring agreement

- 07 Researchers discover LED 'Efficiency Cliff'

- 08 A\*STAR launches 200mm SiC open R&D line

- 09 Renesas to abandon SiC production

- 10 GaN companies strengthen patent portfolios

- 11 NICT-Sony collaboration makes laser breakthrough

- 12 GlobalFoundries boosts 're-shoring' investment

News Editor Christine Evans-Pughe **Design & Production Manager** Mitch Gaynor **Director of Logistics** Sharon Cowley

**Event & Media Sales Executive** Ranjodh Shergill

Circulation Scott Adams Publisher Jackie Cannon christine.evans-pughe@angelbc.com

mitch.gaynor@angelbc.com sharon.cowley@angelbc.com

ranjodh.shergill@angelbc.com scott.adams@angelbc.com jackie.cannon@angelbc.com

+44 (0)1291 629640

+44 (0)1923 690214 +44 (0)1923 690200

+44 (0)2476 718970

+44 (0)1923 690205

Chief Executive Officer Sukhi Bhadal sukhi.bhadal@angelbc.com Chief Technical Officer Scott Adams scott.adams@angelbc.com Directors Jackie Cannon, Sharon Cowley

Published by Angel Business Communications Ltd 6 Bow Court, Fletchworth Gate, Burnsall Road, Coventry CV5 6SP, UK. T: +44 (0)2476 718970 E: info@angelbc.com

+44 (0)2476 718970

Compound Semiconductor is published nine times a year on a controlled circulation basis. Non-qualifying individuals can subscribe at: £115.00 per annum (UK), €165 per annum (Europe), \$198 per annum (air mail) (USA). Cover price £4.50. All information herein is believed to be correct at time of going to press. The publisher does not accept responsibility for any errors and omissions. The views expressed in this publication are not necessarily those of the publisher. Every effort has been made to obtain copyright permission for the material contained in this publication. Angel Business Communications Ltd will be happy to acknowledge any copyright oversights in a subsequent issue of the publication. Angel Business Communications Ltd (Copyright 2025, All rights reserved. Contents may not be reproduced in whole or part without the written consent of the publishers. The paper used within this magazine is produced by chain of custody certified manufacturers, guaranteeing sustainable sourcing. US mailing information: Compound Semiconductor, ISSN 1096-598X, USPS Permit Number 25366, is published 9 times a year, Combined Jan/Feb, March, Combined April/May, June, July, Combined August/September, October, November, December by Angel Business Communications Ltd, Unit 6, Bow Court, Fletchworth Gate, Burnsall Rd, Coventry CV5 65P, UK, Airfreight and mailing in the USA by agent named World Container INC 150-15, 183rd St, Jamaica, NY 11413, USA. Periodicals Postage Paid at Brooklyn, NY 11256. POSTMASTER: Send address changes to Compound Semiconductor, Air Business Ltd, c/o World Container INC 150-15, 183rd St, Jamaica, NY 11413, USA. Periodicals Postage Paid at Brooklyn, NY 11256. POSTMASTER: Send address changes to Compound Semiconductor, Air Business Ltd, c/o World Container INC 150-15, 183rd St, Jamaica, NY 11413, USA. Periodicals Postage Paid at Brooklyn, NY 11256. POSTMASTER: Send address changes to Compound Semiconductor, Air Business Ltd, c/o World Container INC 150-15, 183rd St, Jamaica, NY 11413, USA. Periodicals Posta

## Wolfspeed announces restructuring agreement

Proposed pre-packaged plan of reorganisation includes filing for Chapter 11

TROUBLED US SiC specialist

Wolfspeed has entered into a

Restructuring Support Agreement (RSA)

with key lenders. These include holders

of more than 97 percent of its senior

secured notes; Renesas Electronics'

wholly owned US subsidiary; and

convertible debt holders holding more

than 67 percent of the outstanding

convertible notes.

The transactions envisioned by the RSA are expected to reduce the company's overall debt by around 70 percent, representing a reduction of approximately \$4.6 billion, and reduce the company's annual total cash interest payments by approximately 60 percent.

As part of the RSA, the company intends to solicit approval of the pre-packaged plan of reorganisation and then file voluntary petitions for reorganisation under Chapter 11 of the US Bankruptcy Code in the near future. Wolfspeed says it expects to move through this process quickly and emerge by the end of Q3 2025.

"After evaluating potential options to strengthen our balance sheet and right-size our capital structure, we have decided to take this strategic step because we believe it will put Wolfspeed in the best position possible for the future," said Robert Feurle, Wolfspeed's CEO.

"Wolfspeed has tremendous core strengths and great potential. We are a global leader in SiC technology with an exceptional, purpose-built, fully automated 200 mm manufacturing footprint, delivering cutting-edge products for our customers."

"A stronger financial foundation will enable us to focus acutely on innovation in rapidly scaling verticals undergoing electrification where quality, durability and efficiency matter most."

Feurle continued, "As we move forward, we are grateful for the confidence and support of key lenders, who share our vision for the future and believe in our growth prospects. I also want to thank our incredibly talented team for their resilience and hard work, and our customers and partners for their ongoing support."

According to the transactions contemplated by the RSA, the company will receive \$275 million of new financing in the form of second lien convertible notes, fully backstopped by certain of its existing convertible debt holders.

The RSA contemplates a paydown of its senior secured notes of \$250 million at a rate of 109.875 percent, with certain modifications to reduce go-forward cash interest and minimum liquidity requirements. Another aspect of the RSA is an exchange of \$5.2 billion of existing convertible notes and Renesas' existing loan for \$500 million of new notes and 95 percent of the new common equity, subject to dilution from other equity issuances, with Renesas loan claims entitled to additional incremental consideration to the extent

certain regulatory approvals are not obtained by an agreed upon deadline.

Pursuant to the transactions, existing equity will be cancelled, and the existing equity holders will receive their *pro rata* share of 3 percent or 5 percent of new common equity, subject to dilution from other equity issuances and potential reduction from certain events.

All other unsecured creditors are expected to be paid in the ordinary course of business.

Wolfspeed says it is continuing to operate and serve customers with SiC materials and devices throughout the process. The company plans to continue to pay vendors in the ordinary course of business for goods and services delivered throughout the restructuring process via an All-Trade

Vendors are expected to be unimpaired in the process. Wolfspeed also intends to file customary motions with the Bankruptcy Court to support ordinary-course operations including, but not limited to, continuing employee compensation and benefits programmes.

## Researchers discover LED 'efficiency cliff'

University of Illinois team uncovers challenges in sub-micron LED performance

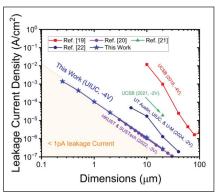

Researchers at the University of Illinois Urbana-Champaign (UIUC) have successfully fabricated InGaN blue LEDs down to 250 nm in size, a critical step for next-generation high-resolution displays and optical communications. However, their study, published in Applied Physics Letters, reveals a new challenge: a sharp 'efficiency cliff' when these LEDs are scaled to submicron dimensions.

The team, led by Can Bayram from the department of Electrical and Computer Engineering, who is director of the Innovative Compound semiconductoR LABoratory (ICORLAB), employed a top-down fabrication approach using electron-beam lithography on QST substrates.

The resulting submicron LEDs, some as small as 250 nm by 250 nm, initially demonstrated promising electrical characteristics, including ideal forward voltage and remarkably low leakage current density. This suggested that the chemical treatments and passivation techniques were effective in recovering sidewall damage from the etching process.

Despite these positive indicators, the study found a dramatic decrease approximately 70 percent – in peak external quantum efficiency (EQE)

as the LEDs were scaled from 2 μm down to 250 nm. This 'efficiency cliff' is a surprising outcome, particularly as the EQE remained relatively stable for devices scaled from 20 µm down to 2 μm, according to Bayram.

"Our findings show that the conventional sidewall passivation methods, which work well for microLEDs, are not sufficient when we push the dimensions into the submicron realm," he explained. "The issue appears to be that as the LED mesa size becomes comparable to the distance carriers can diffuse laterally, the impact of the sidewalls and any associated non-radiative recombination becomes overwhelmingly dominant, even with current state-of-the-art passivation."

The research indicates that at these ultrasmall scales, the proportion of the LED's active region affected by sidewall defects significantly increases. While the team achieved good recovery of sidewall damage, evidenced by low leakage currents, the standard passivation (an atomic layer deposited bilayer of Al<sub>2</sub>O<sub>2</sub> and SiO<sub>2</sub>) could not sufficiently suppress surface recombination in these submicron devices.

This study underscores a critical hurdle for the practical implementation of

➤ Leakage current density compared with the literature. The device leakage current is low, around 1 pA at -5 V. This low, sidewall-limited leakage current is attributed to good passivation quality and negligible bulk leakage current.

top-down fabricated sub-micron LEDs, says Bayram. While the successful fabrication of 250 nm LEDs with good electricals is a promising starting point, overcoming the 'efficiency cliff' is paramount. "These results call for a fundamental rethinking of how we manage sidewall effects in these tiny light emitters," Bayram added. "Novel passivation strategies, potentially involving new materials or techniques to prevent lateral carrier diffusion. will be essential to unlock the full potential of sub-micron LEDs for future technologies."

## A\*STAR launches 200 mm SiC open R&D line

New initiatives and partnerships unveiled at SEMICON Southeast Asia 2025

SINGAPORE'S Agency for Science, Technology and Research (A\*STAR) hosted the inaugural 'Innovate Together' event at SEMICON Southeast Asia 2025, while announcing the world's first industry-grade 200 mm SiC Open R&D Line.

"Singapore's semiconductor ecosystem is built on strong collaborations between public agencies, academia, and industry partners," said Yeo Yee Chia, deputy chief executive (Innovation & Enterprise) at A\*STAR.

"The Innovate Together event exemplifies our commitment to fostering these partnerships and accelerating innovation to address industry challenges and capture new opportunities in the global semiconductor landscape."

At the heart of Innovate Together was the launch of the SiC Open R&D Line. Designed to enable joint SiC innovation between researchers and companies, the aim is for the facility to strengthen Singapore's capabilities in wide bandgap semiconductor research and address future demands for highpower applications.

In addition, A\*STAR unveiled two other initiatives to strengthen Singapore's semiconductor research and innovation capabilities:

- Phase two of Lab-in-Fab, a 200 mm R&D and manufacturing line focused on piezoMEMS, involving partners STMicroelectronics, ULVAC, and the National University of Singapore. This will build on Singapore's strong R&D ecosystem to accelerate the development of new piezoelectric materials and devices.

- EDA Garage, an initiative that will provide local companies, especially start-ups and SMEs, with cost effective access to advanced electronic design automation tools. This will nurture local semiconductor

companies and enable them to innovate faster and better.

To kickstart international collaborations in semiconductor training and R&D, A\*STAR IME signed Memorandums of Understanding with key partners, including the Uzeltexsanoat Association, representing Uzbekistan's electronics sector, the Singapore Semiconductor Industry Association, the Indian Institute of Technology, Kharagpur, and the Fraunhofer Institute for Electronic Nano Systems ENAS.

These partnerships pave the way for internship programmes, joint research projects, and knowledge exchange through training and knowledge sharing activities.

At the sidelines of the SEMICON Southeast Asia 2025 event, A\*STAR also formalised its partnerships with GlobalFoundries and Nearfield Instruments, to expand capabilities in advanced packaging and drive innovation in semiconductor metrology technologies.

Under an Memorandum of Understanding, GlobalFoundries will gain access to A\*STAR's advanced R&D facilities, capabilities and technical support for technology development in advanced packaging and workforce skills enhancement.

The multi-year research collaboration between A\*STAR IME and Nearfield Instruments will accelerate the development of advanced metrology solutions that enable efficient chip production.

The Innovate Together event featured expertise from other institutions on key technological areas that are important for the future of Singapore's semiconductor industry.

Speakers from A\*STAR, National University of Singapore, Nanyang Technological University, Singapore, and the National Semiconductor Translation and Innovation Centre shared the latest insights on advanced packaging, photonics, MEMS, and millmetre-wave and beyond.

## Renesas to abandon SiC production

Japanese giant halts SiC chip plans amid Chinese price war and Wolfspeed uncertainty

RENESAS is abandoning plans to produce SiC chips for EVs. according to TrendForce, citing a report by Nikkei.

This move by the Japanese semiconductor firm has apparently been prompted by slow growth in the EV market, coupled with a SiC chip supply glut driven by Chinese manufacturers. The decision is asociated with Renesas' SiC partner Wolfspeed, planning to file for Chapter 11 bankruptcy.

In July 2023, Renesas announced its entry to the power SiC market through a ten year partnership with Wolfspeed. The deal included a \$2 billion deposit from Renasas to secure supply for both 150 mm and 200 mm SiC wafers.

Renesas had initially planned to begin manufacturing SiC power chips for EVs in early 2025 at its Takasaki plant in Gunma Prefecture. However, the company has since disbanded the SiC team at the facility, according to Nikkei. The latest research from TrendForce shows weakening demand in the automotive and industrial sectors and slow shipment growth for SiC substrates in 2024. Simultaneously, intensifying competition and sharp price declines have driven global revenue for *n*-type SiC substrates down 9 percent year-over-year to \$1.04 billion.

Chinese vendors TanKeBlue and SICC have risen to prominence, capturing 17.3 percent and 17.1 percent of the global market share, respectively. Price competition with Chinese rivals is expected to intensify over the mediumto-long term, making it more difficult for a late arrival like Renesas to generate

profits from SiC chip production. TrendForce adds that while Renesas has reportedly decided to halt inhouse production of SiC power chips, the company does not plan to exit the

market entirely. Instead, it may continue to develop its own SiC designs while outsourcing manufacturing to foundries, then selling the finished products under its own brand.

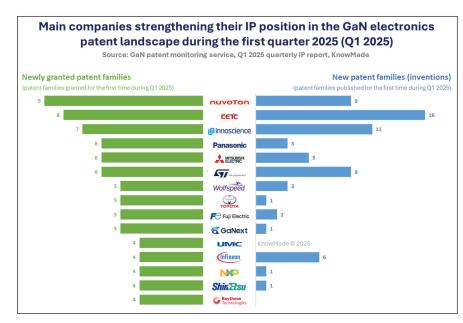

## GaN companies strengthen patent portfolios

KnowMade Q1 IP patent report shows companies are addressing critical aspects of GaN technology

KNOWMADE has published its Q1 2025 IP report on GaN electronics, highlighting robust patenting activity across both power and RF segments, amid on-going patent disputes between power GaN companies.

Recent patent filings emphasise critical aspects of power GaN technology such as gate design and packaging, resulting in sustained patent portfolio growth. Meanwhile, key RF market players keep expanding their IP activities in the RF GaN landscape, underlining the technology's role in next-generation wireless applications.

During the first guarter of 2025, a total of 540 new patent families were published, with Xidian University and major Chinese entities such as CETC and Innoscience leading the patent filings, followed by contributions from Nuvoton, STMicroelectronics, and Toshiba. Over 330 patent families were granted for the first time, notably reinforcing portfolios at Innoscience, STMicroelectronics, Infineon, Navitas, and EPC, alongside significant grants to Panasonic and TSMC. The quarter also saw more than 110 patents abandoned and over 70 patents expired, primarily from wellestablished patent holders including Wolfspeed, Infineon, and Fujitsu.

Approximately 10 IP collaborations (patent co-filings) were recorded, most partnerships formed between industry and academic organisations. For instance, Safran published a patent application with CNRS, CNAM and several universities in Paris, for an on-board aeronautical power circuit with active filtering. Also, Volkswagen cooperated with the University of Tennessee on GaN-based three-level active neutral point clamped power module designs, resulting in joint patent publications in Q1 2025.

Nearly 40 patent transactions took place this quarter, predominantly within China, such as the transfer of several RF GaN

patents from Xidian University to Huawei and power module company Macmic Science & Technology's acquisition of a GaN device patent from UESTC.

Toshiba, Texas Instruments (TI), and Rohm each published more than six new inventions. In particular, Rohm introduced multiple innovations aimed at enhancing the reliability of normallyoff GaN devices by leveraging p-GaN gate layer techniques and superlattice buffer structures. TI unveiled a novel gate structure incorporating a p-type poly-silicon layer to decouple parasitic capacitances and improve gate depletion behaviour, alongside trenchbased substrate-to-source connections for GaN power devices and a HEMT design featuring a doped barrier to boost threshold voltage stability and drain current stability. Moreover, TI disclosed a packaging solution wherein a GaN FET is co-packaged with its driver for optimised half-bridge modules.

Sony, Sumitomo Electric, and Macom disclosed six, five, and four RFfocused inventions, respectively. While Sumitomo and Sony were focused on RF GaN device designs, Macom's patenting activity related to RF amplifier circuitry and advanced packaging techniques. Interestingly, Sumitomo focused on RF GaN-on-SiC devices fabricated on nitrogen-polarity GaN epitaxial structures.

Academic research also made a significant contribution on this topic with UCSB publishing an invention that improves the linearity of deep-recess GaN MIS-HEMTs through corrugation of N-polar structures. MONDE Wireless, a UCSB spin-off, also mentioned N-polar GaN HEMTs grown on miscut substrates in another Q1-2025 patent publication.

New entrants to the GaN electronics IP landscape were predominantly Chinese, with LED manufacturer Anhui GaN Semiconductor filing several epiwafer patent applications for both power and RF uses, and battery manufacturer CATL submitting its first GaN-related invention targeting battery management systems. In the US, Tesla entered the arena with a packaged IC featuring enhanced power surge heat dissipation, and Soctera, a Cornell University spinoff, proposed a GaN device structure using an AIN back barrier layer and an in-situ two-step passivation process to mitigate current collapse.

## NICT-Sony collaboration makes laser breakthrough

Practical surface-emitting laser for 1500 nm communications uses quantum dots as gain medium

JAPAN'S National Institute of Information and Communications Technology (NICT), in collaboration with Sony Semiconductor, has developed what is claims is the world's first practical surface-emitting laser for 1550 nm communications that employs quantum dots (QD) as the optical gain medium.

The results of this research Electrically pumped laser oscillation of C-band InAs quantum dot vertical-cavity surfaceemitting lasers on InP(311)B substrate were published in Optics Express, in March year.

This innovation not only facilitates the miniaturisation and reduced power consumption of light sources in optical fibre communications systems but also offers potential cost reductions through mass production and enhanced output via integration, according to the researchers.

NICT's role was to develop the reflective semiconductor multi-layer fabrication and quantum-dot crystal growth technology using MBE. Sony undertook the device design for the entire VCSEL structure and device process technology.

Fabricating a VCSEL requires growing a highly reflective semiconductor multilayer film known as a distributed Bragg reflector to enhance light intensity;

however, fabricating DBRs that operate at 1550 nm has been challenging, because the combination of materials that can be grown is limited. In this study, the NICT team developed a technology that can precisely grow DBRs by strictly controlling the ratio of materials in the crystal growth and realised a semiconductor DBR

with a reflectivity exceeding 99 percent, even at 1550 nm.

In addition, strain-compensation techniques were applied to VCSEL production to accurately cancel the internal crystal strain (strain generated within the material) that occurs around the quantum dots, thereby significantly increasing the density of the quantum dots and improving the light-emitting performance.

Sony contributed a device design and fabrication process that enables highly efficient current injection employing a tunnel junction. VCSELs emit light perpendicular to the wafer surface; therefore, even if quantum dots emit light, conventional electrode placement obstructs light extraction.

Laser light Quantum **VCSEL**

> Sony addressed this by implementing a tunnel junction structure that permits efficient current flow while facilitating light extraction employing a precise device process.

Through the integration of these two technologies, the team succeeded in lasing VCSELs using quantum dots at 1550 nm as a light-emitting material with a small current of 13 mA (low threshold). Furthermore, polarisation fluctuations were eliminated, resulting in a stable output.

In the future, the researchers hope to develop the quantum-dotbased VCSEL technology further to enhance the capacity and reduce power consumption in optical fibre communication systems beyond 5G era.

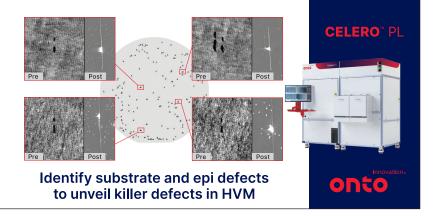

## **Seeing the Unseen:**

Root-Cause-Defect **Mapping for SiC and GaN in Compound Semiconductors**

ontoinnovation.com

## GlobalFoundries boosts 're-shoring' investment

Company commits to a further \$3 billion on next-generation GaN tech, packaging innovation, and silicon photonics

GLOBALFOUNDRIES says it is working with the Trump Administration, with support from tech companies Apple, SpaceX, AMD, Qualcomm, NXP and GM, to onshore critical components of the supply chain with a total \$16 billion investment in expanding chip manufacturing and packaging across its facilities in New York and Vermont.

This latest announcement builds on the company's existing US expansion plans of more than more than \$13 billion funding to both advance manufacturing of 200 mm GaN-onsilicon semiconductors at its facility in Essex Junction, Vermont; and for its recently launched New York Advanced Packaging and Photonics Center. GF is committing an additional \$3 billion, which includes advanced research and development initiatives focused on nextgeneration GaN technologies, packaging innovation, and silicon photonics.

The company says its investment is a strategic response to the explosive growth in Al, which is accelerating demand for next-generation semiconductors designed for power efficiency and high-bandwidth performance across data centres, communications infrastructure and Alenabled devices.

Tim Breen, CEO of GlobalFoundries said: "The Al revolution is driving strong, durable demand for GF's technologies that enable tomorrow's data centres – including GF's leading silicon photonics, as well as GaN for power applications. Meanwhile at the edge, GF's proprietary FDX technology is uniquely positioned to support Al functionality with low power consumption. With all these technologies and more manufactured right here in the US, GF is proud to play its part in accelerating America's semiconductor leadership."

"GlobalFoundries investment is a great example of the return of United

States manufacturing for critical semiconductors," said US Secretary of Commerce, Howard Lutnick. "President Trump has made it a fundamental objective to bring semiconductor manufacturing home to America. Our partnership with GlobalFoundries will secure US semiconductor foundry capacity and technology capabilities for future generations."

"GlobalFoundries has supplied semiconductors for Apple products since 2010 and we're excited to see them expand right here in the United States. These chips are an essential part of Apple products like iPhone, and they're a powerful example of American manufacturing leadership," said Tim Cook, Apple's CEO

Gwynne Shotwell, president and COO at SpaceX said: "Advanced semiconductors are critical to the advanced satellite capabilities, which SpaceX has been pioneering for over two decades. We are excited by the expansion of GlobalFoundries' manufacturing base right here in the US, which is core to Starlink's growth and our commitment to manufacturing in the US, as well as our mission to deliver high-speed internet access to

millions of people around the world."

"As a strategic supplier of Qualcomm, GlobalFoundries shares our vision for strengthening US chip production capacity. This commitment from GlobalFoundries will help secure a resilient semiconductor supply chain to support the next wave of US technology innovation, especially in areas vital to enabling power efficient computing, connectivity, and edge intelligence," said Cristiano Amon, president and CEO of Qualcomm Incorporated.

"This collaboration allows us to scale efficiently, expand production in the US and continue delivering for our customers. It's a strong step forward in building a resilient, high-performing semiconductor supply chain in the United States, "said Kurt Sievers, CEO of NXP Semiconductors.

"Semiconductors are critical to the future of vehicles, and their importance will only grow. GlobalFoundries' investment supports our work to secure a reliable, US-based chip supply – essential for delivering the safety, infotainment and features our customers expect," said Mark Reuss, president of General Motors.

MBE IS OUR DNA

Global market leader for research and production

MBE not only changes how we do it, it also changes what we can do.

Riber is the world leading supplier of MBE processing equipments and related services.

Capitalizing on 30 years of experience, the core philosophy of the company is to design systems in close association with customers. Riber invented and designed major features which are now found in all MBE systems.

Riber plays a key role in the development of MBE technology, providing customers with solutions from equipment to epitaxial growth.

RIBER

**INNOVATIVE SOLUTIONS FOR SEMICONDUCTOR INDUSTRY**

## KLA: Expanding within the CS cluster

Equipped with a demonstration lab capable of accommodating more than 100 modules, KLA's new, purpose-built facility should spur further growth of its deposition and etch tool businesses

#### BY RICHARD STEVENSON, EDITOR, CS MAGAZINE

RIGHT NOW, the South Wales compound semiconductor cluster is thriving. Behind those positive vibes is Vishay's investment of SiC manufacturing technology at its Newport fab, the completion of the Centre for Integrative Semiconductor Materials at Swansea University, and most recently, the opening of a tremendous new facility for the development and production of KLA Corporation's deposition and etch equipment.

Opening on 22 May to much fanfare, KLA's £138 million facility sits at the heart of the cluster, in an industrial area on the outskirts of Newport that's also home to IQE and the CS Catapult.

To mark this key day in KLA's history, the company took the opportunity to show 100 or so VIPs around its purposebuilt 237,000 ft<sup>2</sup> three-story facility.

Accommodating up to 750 employees, this brand-new building features: more than 25,000 ft<sup>2</sup> of cleanroom space for R&D; more than 35,000 ft<sup>2</sup> for bespoke manufacturing; plenty of office space, with lots of natural light; and a canteen and a gym for all its staff.

During the opening ceremony, KLA's VP Product Marketing, SPTS Products, Dave Thomas, spoke exclusively to *Compound Semiconductor*, detailing plenty of sound reasoning behind the relocation, the trends that the company is seeing within the compound semiconductor industry, and how the new facility and the management at KLA will help to continue a ramp in sales of the company's etch and deposition tools.

#### Local firm, global brand

The roots of the etch and deposition division of KLA can be traced back to the days of ElectroTech, which in

other side of the Severn estuary from the CS cluster. Over the years, this company re-located to South Wales, with a couple of local moves supporting expansion of the business.

In the last 15 years this venture has thrived, with sales of the SPTS etch and

1984 established a subsidiary, Special

Research Systems, in Bristol - just the

In the last 15 years this venture has thrived, with sales of the SPTS etch and deposition tools rocketing from around US\$50 million to US\$500 million. Supporting this phenomenal growth is the acquisition by KLA in 2019, which has driven a doubling of revenue from this division and a commensurate increase in headcount. This expansion has driven demand for a bigger facility, with space not only for the expanded workforce, but also for aiding the development and demonstration of tools and processes.

Thomas believes that the acquisition by KLA came at just the right time for SPTS. "When you're going from a few hundred million towards a billion, you have to start thinking differently. You need to act more corporately, have much better control over your internal processes, and certainly be better connected with your customer base at multiple levels."

As well as offering all this, incorporating SPTS into the KLA fold has provided the finance and bold vision for building a purpose-built facility. Without doubt, this would be located in the compound semiconductor cluster, highly valued for a number of reasons.

According to Thomas, one crucial benefit of remaining within the cluster is that it enhances joint development with local companies and universities.

"There are programmes that we have running with Swansea University, where

➤ In the basement of KLA's new facility is a 'sub-fab', providing the necessary infrastructure for supporting tool assembly and the running of tools to aid and attract customers. Credit: Matt Lincoln

## NEWS ANALYSIS I INVESTMENT

they're helping us to understand the link between the device and the wafer process," remarked Thomas. "Just recently, we're developing an endpoint system for silicon carbide trench etching, and we're trying to figure out how tolerant is the device to the trench characteristics."

Thomas argues that another benefit of operating within the cluster is that is helps with discussions with local and national government, because those officials have now grasped a basic understand of the importance of the compound semiconductor industry.

#### From MEMS to compounds

Sales of equipment to the MEMS industry provided initial success in the etch and deposition tool market. "We were the first licensees of the Bosch process," explained Thomas, adding that back in 1995, they worked with this German powerhouse to develop the deep-silicon-etching Bosch process.

Today, the MEMS sector is still valued by KLA, accounting for around 10-15 percent of sales of its etch and deposition tools. However, greater revenue is coming from the compound semiconductor industry. Here, involvement dates back several decades, with success underpinned by efforts to understand the specific characteristics of all the main materials.

Expansion into the compound semiconductor sector began with GaAs, which has some key differences to silicon from a processing perspective.

However, while it is more difficult to etch GaAs than silicon, it's still easier than InP, according to Thomas: "You've got a very heavy metal, indium, with a very light element, phosphorus. When you come to etch it, it's very easy to etch one in preference to the other. and create a rough surface. You need to move to high-temperature etching to liberate both materials."

KLA also has capabilities in wide bandgap materials, particularly SiC and GaN. "Silicon carbide is very difficult to etch because it's so tough. You have to really hit it hard," said Thomas, who explained that a markedly different approach is required for GaN, which is easily damaged. "These subtleties, they're part of our DNA now, and we understand them."

Armed with all this hard-won expertise, KLA's deposition and etch tools are winning sales in all the major compound semiconductor markets.

In the RF market, KLA's process equipment is employed for the production of various devices, including those based on GaAs, InP and GaN on both silicon and SiC.

"The RF market is in a state of recovery," said Thomas, who is expecting growth to continue over the next few years.

In the power semiconductor sector, there has been huge growth over the last few years, driven by SiC devices for electric vehicles and infrastructure. However, recently, there has been some 'softening', according to Thomas, who remarked that the company is also active in the GaN market. "We work with pretty much all customers you can think of in the GaN power space and the SiC space."

Another key sector is photonics. "This is the exciting one for me right now," revealed Thomas, who explained that makers of lasers for optical communication are enjoying tremendous growth, and there's also the promise of co-packaged optics.

For those in the silicon industry. advanced packaging is synonymous with flip-chip bumping. Technologies like TMSC's CoWoS, that unite memory and logic with interposers, have become well-established.

"The next step in that progression is to bring photonics onto that package," argued Thomas, who elaborated by explaining that progress hinges on the addition of InP or GaAs lasers onto the silicon-centric packages.

"It's such a clash of cultures, because you've got four and six-inch wafers versus twelve-inch wafers," remarked Thomas.

Along with his colleagues, Thomas is trying to bring the two camps together, drawing on KLA's strong relationships between both the makers of VCSELs and edge-emitting lasers, and the big five in silicon that employ hybrid bonding. "The marriage of the two is not going to be easy, but we're right in the middle of that and we can help."

#### The demo lab

One of the assets of KLA that should help in this endeavour is its new demonstration lab, able to house over 100 process modules.

"We don't really often sell anything without demonstration first," revealed Thomas, who explained that to win orders it's imperative to either prove that KLA's tools are superior to the incumbents, or are capable of being employed for a new manufacturing process. In both cases, customers tend to send wafers to KLA, which runs them through its tools and reports the data.

"We collaborate a lot during that process," said Thomas, revealing that this can involve plenty of calls, and trips to the customer's offices. "Better still, they come here, and they sit with us in those demo rooms - and they watch, they learn, they advise, and we work together." Typically, in this preferred modus operandi, engineers from the chipmaker will spend a week at KLA.

As well as demonstrating processes to customers, the demo room is used for R&D - this accounts for about 40 percent of activity. Efforts on this front include refining processes to make them more manufacturable, and the development of new hardware.

#### Managing the move

Today there are only a handful of tools in the demo lab, and office space in the new facility is populated very lightly. Over the next six-to-nine months, groups will move from one side of Newport to the other to set-up in the new facility. As this involves decommissioning and recommissioning, while meeting customer needs, it will be an exciting and challenging time. However, there's no doubt that these efforts will be rewarded.

"We will have a really engaged workforce and a really engaged set of customers who want to come here and work with us," commented Thomas, who expects that the new facility will also act as a magnet to recruiting highly capable employees.

"When I have a vacancy for a product manager, I'd like to see 10 CVs from Swansea and Cardiff universities, and local schools. I want to take local talent because, to me, if we can continue to build locally from here, I think that's a really good story for us."

## Retro-tech revolutionises the deep UV

Compact sources of deep-UV emission from NS Nanotech are providing air purification through cathodoluminescence of boron nitride

#### BY RICHARD STEVENSON, EDITOR, CS MAGAZINE

WHEN IT COMES to device design, our industry is quite insular. We focus on improving performance by optimising epitaxy or the architecture of our chips. But at times we might be missing a trick, and would benefit from approaches involving more out-of-the-box thinking.

Doing just that with considerable success is the Michigan-based start-up NS Nanotech. Drawing on cathode-ray tube technology that lies at the very heart of the televisions of yesteryear, it has just released an improved version of its cathodoluminescence-based 215 nm source that's a compelling candidate for air purification in relatively confined public spaces.

The NS Nanotech source goes deeper than AlGaN-based UV LEDs – they have been under development for decades, with developers striving to improve the efficiency and output, so that those emitters could be deployed in various

applications, including curing and the purification of air, water and surfaces.

Motivation for the development of deep-UV LEDs is the addressing of many weaknesses of the incumbent solution, a gas-discharge lamp that is fragile, bulky, and is some cases contains mercury, which is of great concern to humanity's health. However, while the power produced by deep-UV LEDs continues to increase, it's not that high, limiting success.

As well as offering more power, the technology from NS Nanotech produces emission at a preferable wavelength. While no light in the UV is perfectly safe to humans, the most damaging to the skin and eyes is in the range 240 nm to 280 nm.

"It's right where mercury bulbs are, where all the UVC LEDs are," says NS Nanotech CEO and co-founder Seth Coe-Sullivan. "The lowest

> commercial LED available is at 235, which isn't quite as bad as 240, but it's awful close."

Coe-Sullivan points

out that the only two

commercial sources

beneath that harmful

band are krypton

chloride bulbs, with an

emission peak at 222 nm,

and NS Nanotech's source.

Note that there is little to be gained by going below 200 nm, as light in this spectral domain is absorb ed by oxygen, hampering its transmission.

## Superior successor

Back in October 2024, NS Nanotech introduced its first far-UVC ShortWaveLight 215 nm emitter; and recently, it has unveiled a second-generation variant, with an output of 500  $\mu$ W, 60 percent higher than its predecessor.

"Compared to any far-UVC LEDs on the planet, this is massively powerful, certainly the most powerful semiconductor device at this colour," says Coe-Sullivan.

Both generations of far-UVC ShortWaveLight 215 nm emitter are vacuum tube devices that feature semiconductor emitters. These products employ a filament, providing hot electrons that are accelerated to semiconducting material, which emits UV light via cathodoluminescence. The increase in the output power of the successor comes from optimising the vacuum tube before pinch off.

#### AIN versus BN

The obvious candidate material for providing cathodoluminescence is AIN, a key semiconductor for producing deep-UV LEDs. But NS Nanotech uses BN, as this has better bandgap emission when quantum wells are not employed.

"If you just buy bulk boron nitride powder, you'll get essentially zero emission at 215 nanometres," warns Coe-Sullivan. "You'll get all defect emission, which is far lower energy than the bandgap."

To avoid this fate, the team at NS Nanotech employs a refined

➤ Emission at 215 nm results from the bombardment of electrons into a BN powder.

process for producing BN powders, involving licensing technology from Japan. The BN bulk powder is coated on a disc about a square centimetre in size, with cathodoluminescence providing 215 nm emission of the company's products, which are roughly the size of a golf ball.

The primary application for NS Nanotech's technology is reducing the spread of diseases in small, confined spaces. This approach to improving public health is known to succeed, thanks to the pioneering work of Niels Ryberg Finsen, who received the 1903 Nobel Prize for Medicine for studies into the use of deep-UV emission to disable micro-organisms.

Interest in using deep-UV sources to kill viruses rocketed during the pandemic, but has fallen away, with many wanting to simply move on from those difficult times. However, while this view is understandable, failing to learn lessons from the Covid-19 outbreak leaves humanity vulnerable to the next pandemic, which could take many forms.

Speculating on possibilities, Coe-Sullivan remarks: "Is it a measles outbreak in Texas? Is it the bird flu crossing over to humans? Is it something we can't name?"

He has no doubt that the likelihood of another pandemic is only going to increase year by year, pointing out that the planet's population is increasing, many are living closer to animals, and germ-sharing is on an upward curve.

One significant opportunity for passing on germs occurs in confined spaces, such as those found in cars. It is here that NS Nanotech is hoping to make a difference, promoting its products for deployment in private cars, Ubers, ambulances and air ambulances.

"Vibration testing has been really key," claims Coe-Sullivan, revealing that one of the company's 215 nm sources has been fitted in a pick-up truck that's been driven on dirt roads for last six months. Encouraginaly, this field test has not produced any degradation to the deep-UV product.

In movie theatres, there's also much interest in using sources in the 200 nm-230 nm band to kill bacteria. Here, more power is needed, so lamps based on krypton chloride that emit around 30 milliwatts are used.

➤ The primary application for far-UVC ShortWaveLight 215 nm products made by NS Nanotech is to sterilise the air in vehicles.

> "Krypton chlorine is a great product," says Coe-Sullivan. "But if you're in a car, Krypton chlorine is the wrong product, and our product is the right product."

> What's also clear is that while the whiteemitting filament bulb now belongs in the museum, other vacuum-based technologies are going strong, and will have a role to play in society for many more years.

## **CMOS: Not just for silicon**

While CMOS may be synonymous with the manufacture of silicon ICs, it's a versatile process can also be applied to the production of photonic and microwave circuits employing compound semiconductors

#### BY JAMES PAN FROM NORTHROP GRUMMAN

SILICON ICs – invented in 1950s – are used in almost everything. Better known for their deployment in smartphones and computers, they are also integral to the operation of automobiles, washing machines, air conditioners, vacuum cleaners and so on. In all these cases, the ICs operate in total darkness, because silicon has an indirect bandgap. Due to this characteristic, silicon can absorb light, but it cannot emit it.

In our daily life, electrons and light are intertwined. We use electrons to generate light and other forms of electromagnetic radiation, such as microwaves. And while we might think of photons when we think about lasers and LEDs, they are electron devices — as are radar and lidar.

Now we need to start applying the principle of working with electrons and photons, which are intertwined, in ICs. Development is already underway, as compound semiconductors, such as GaAs, InP, and other III-V and II-VI compounds, are now used with silicon. Consider, for example, microwave photonic CMOS, which includes III-V or II-VI materials for lasers or millimetre-wave diodes, in the CMOS drain region, through a process called 'selective epitaxy'.

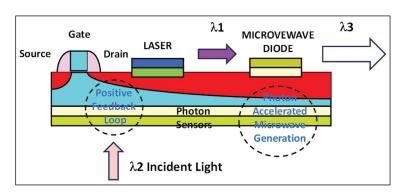

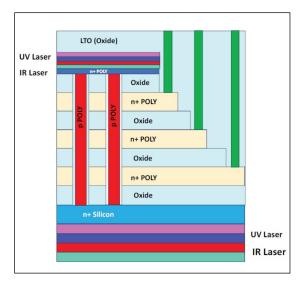

> Figure 1. Microwave photonic CMOS and image sensors. Positive feedback loops convert light to light currents. Photon-accelerated microwave generation produces modulated light wave and millimetre wave signals.

It's possible that these ideas might strike you as a little odd. I'm sure you have heard of the acronym CMOS – its full name 'complementary metaloxide semiconductor' – and you'll know that it's a process employed to make billions of silicon ICs. But it's quite possible that this is the extent of your knowledge. And, to be fair to you, why should you know any more than this, given that many will believe that CMOS is not of any relevance to the compound semiconductor industry.

Well, I understand your position – but you are in danger of falling behind the times. Change is now afoot, thanks in part to our work at Northrop Grumman, a leader of lasers, millimetre-wave devices, and ASICs (Application Specific Integrated Circuits). We are developing a CMOS process for light-emitting structures and microwave circuits. It's a revolutionary breakthrough that will enable the integration of both compound semiconductors and silicon for almost 'all products' in the \$500 billion CMOS industry, which is growing rapidly.

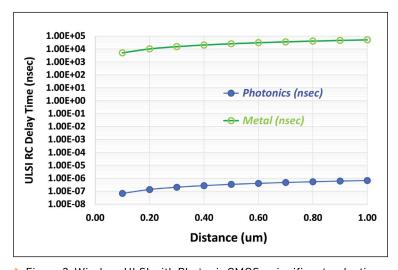

Our efforts are not the first to unite silicon and the compounds in ICs. Long gone are the days when silicon photonics is a new entity, having been pioneered by companies such as IBM and Intel, with products forming a small part of the IC industry. Today silicon photonics has already entered ULSI (Ultra Large-Scale Integration) markets, a point well-illustrated by the delivery of a webinar last August by Global Foundry's Anthony Yu, who gave a presentation entitled *Bringing Silicon Photonic Technology to the Forefront*). Within this development there's microwave photonic CMOS, involving modern processors that include hundreds of billions or trillions of CMOS transistors.

Based on such activities, a new trend is emerging – most, or even all of these many billions of CMOS transistors are no longer going to be fabricated only in silicon. Instead, they will incorporate GaAs, InP, or other compound semiconductors used in lasers and LEDs.

Behind this revolution is the move in modern societies to replace wireless tools with non-wireless tools, a migration observed in the uptake of smartphones, and changes to the connectivity of computers. In this particular case, the advantages of implementing compound semiconductors with silicon are wireless ULSI, and eliminating heating of the copper wires, and delays associated with their resistance and capacitance. There's the promise of replacing billions of copper wires in ULSI with wireless photonic CMOS technologies.

You may be wondering how III-Vs are introduced using a CMOS process. One illustrative example is the addition of GaAs in the CMOS silicon drain region, using either low-temperature selective CVD or selective epitaxy. For the former, the CVD tool includes an *in-situ* chamber in ultra-high vacuum, where native oxides on silicon are sputtered and etched, prior to sending the wafer to the CVD chamber for GaAs epitaxy. Note that all these processes proceed under high vacuum.

As GaAs is deposited right before the silicide process, in the BEOL (Back End of the Line), there are no contamination concerns, enabling the use of silicon lines (see Figure 1 for an illustration of the process integration of photonic CMOS).

Thanks to the introduction of III-Vs, the era of microwave photonic CMOS is within our grasp. For this technology, options for the optical source include GaAs LEDs, emitting in the 800 nm to 900 nm range, threshold-less tunnel lasers on silicon, and microwave-generating devices. Note that microwave photonic CMOS can outperform traditional laser diodes, due to improved thermal reliability, higher external quantum efficiencies, and superior lasing powers.

To produce microwave photonic CMOS, an ultralow-resistance threshold-less tunnel laser or LED is crafted in the drain region; and in either the well, channel or below the drain region, narrowbandgap photon sensors or avalanche photodiodes are added, made from SiGe or other compound narrow bandgap materials. In addition, microwave diodes, made from silicon, SiGe, or other compound semiconductors, are added in the drain region. Note that the MOSFET, lasers, microwave diodes, and photon sensors are fabricated as one integral transistor.

Alongside the optical sources, dielectric microoptical waveguides are transferred that are

suitable for sub-1 nm CMOS technology nodes.

The dimensions of the micro-optical waveguides

can be less than 100-300 nm, with guided optical

signals confined with total reflection, despite the

wavelength being longer than the width of the

waveguide. For the sub-1 nm nodes, channel length

is typically 5-20 nm, but the 'width' of the CMOS

can be in the range of hundreds of nanometres, or

even a few microns.

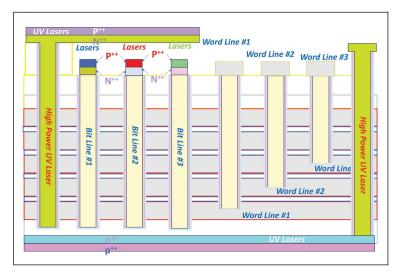

> Figure 2. Ultra-High-Speed Microwave Photonic Vertical NAND FLASH.

> Figure 3. Wireless ULSI with Photonic CMOS – significant reduction of RC delays and heat.

> Figure 4. An alternative method of fabricating Ultra-High Speed Microwave Photonic Vertical NAND FLASH (Vertical NAND FLASH, which has replaced NOR FLASH.

## OPINION I CMOS

There is no doubt that these new forms of CMOS have great potential. One of their greatest assets is that the laser microwave CMOS process is 100 percent compatible with existing CMOS fabrication, and there is no threat of cross contamination. Another exciting opportunity is the introduction of far more sophisticated nonlinear optical computing. However, there are challenges - compared with photonics computing, which is already available and implemented, microwave computing needs advanced knowledge, and the development of micro-antenna, microwave filters, multiplexers, and

I'm not saying that applying CMOS to the compounds is easy. But the rewards justify the endeavour.

### **FURTHER READING**

- ➤ H. Liu et. al. "Near-infrared germanium PIN-photodiodes with >1A/W responsivity," Light: Sci. Appl. 14 9 (2025)

- ➤ J. Boucher et. al. "Ultra high efficiency 1550nm multijunction pulsed laser diodes," Proc. of SPIE 7480 74800K (2009)

- Y. Zhao et. al. "Epitaxially-Stacked High Efficiency Laser Diodes Near 905 nm," IEEE Phtonics J. 14 155706 (2022)

- Y. Niu et. al. "External-feedback-coupled microring lasers on a III-V-on-Si photonic chip for reservoir computing," Proc. SPIE 13370, Smart Photonic and Optoelectronic Integrated Circuits 2025, 133700H (March 2025)

- Y. Xue et. al. "High-speed and low dark current siliconwaveguide-coupled III-V photodetectors selectively grown on SOI," Optica 9 1219 (2022)

- ➤ Rizzo et. al. "Fabrication-Robust Silicon Photonic Devices in Standard Sub-Micron Silicon-on-Insulator Processes," Opt. Lett. 48 215 (2022)

- R. Palmer et. al. "Low-Loss Silicon Strip-to-Slot Mode Converters," IEEE Photonics J. 5 2200409 (2013)

- C. Li et. al. "Subwavelength silicon photonics for on chip mode-manipulation," PhotoniX 2 11 (2021)

- ➤ J. Pan et. al. "Optoelectronic CMOS Transistors: Performance Advantages for Sub-7nm ULSI, RF ASIC, Memories, and Power MOSFETs," MRS Advances 4 2585 (2019)

- ➤ Global Foundry, "Bringing Silicon Photonic Technology to the Forefront," Laser Focus World webinar, August 13, 2024.

## kSA MOS for Stress Measurement

## Control your (thin-film) stress!

- Measure real-time curvature, stress, reflectivity and growth rate

- 2D curvature/stress measurement allows for surface anisotropy determination

- Plus the best support in the industry

- Learn more by visiting our website: k-space.com

# **Connecting Semiconductors and Electronics**

## SMART DATA-AI

WORKFORCE DEVELOPMENT

**Global** ADVOCACY

Sustainability

1000+ STANDARDS

THOUGHT LEADERSHIP

## **SEMICON**

**TECH**COMMUNITIES

**SEMI**UNIVERSITY

**Cyber** Security

#### About SEMI:

SEMI connects more than 2,500 member companies and 1.3 million professionals worldwide to advance the technology and business of electronics design and manufacturing. The breadth and depth of our events, programs and services help members accelerate innovation and collaboration on the toughest challenges to growth.

## COVER STORY I HRL

## HRL's GaN: from innovation to qualification

Maintaining the tradition of being 'first' in technology innovation, HRL's latest T3L GaN technology delivers a world-leading high-frequency performance with a process that's manufacturable, stable, predictable and reliable

BY SATYAKI GANGULY, F. ERDEM ARKUN, ANDREA ARIAS-PURDUE, DAVE FANNING, ANDY FU, DMITRY VEKSLER, DAN DENNINGHOFF AND ANDREA CORRION FROM HRL LABORATORIES

> BY OFFERING increases in power, efficiency and bandwidth over other semiconductor technologies. RF GaN devices are continuing to make a substantial impact in commercial and defence applications. But to ensure the future success of this class of device, its progress must not grind to a halt. Due to the proliferation and complexity of RF signals, the electromagnetic environment is increasingly crowded, driving urgent demand for GaN technologies operating at higher frequencies - and in particular, the millimetre-wave range that spans 30 GHz to 300 GHz.

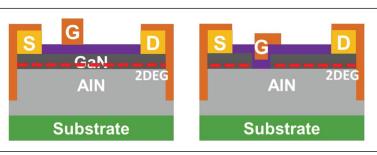

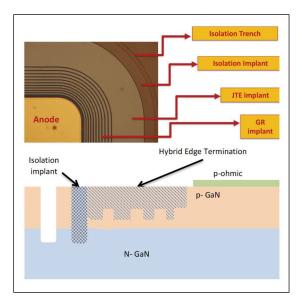

Meeting this need is not trivial. It requires a rethinking of GaN materials and fabrication approaches, including a move away from many of the standard features incorporated into lowerfrequency technologies, such as standard annealed ohmic contacts, large field-plates to manage electric fields, and the standard AlGaN/GaN HEMT epitaxial structure.

Unfortunately, those that take on the challenge of moving to higher frequencies also come up against a number of trade-offs. To give just one example, when decreasing the gate length to sub-100-nm dimensions and eliminating field plates to enable

high-frequency operation, peak electric fields in the device increase, impeding reliability. What's needed are out-of-the box, innovative solutions.

At HRL Laboratories, LLC, we have a long history of exceling on this front. By redefining the boundaries of what's possible today, we invent solutions to tomorrow's problems. Employing an ownership model that prioritises purpose over profit, we invest in ambitious ideas and take strategic risks on projects that significantly advance the state of the art, pursuing paths that others might overlook. This culture is reflected in our legacy of groundbreaking work on high-frequency GaN.

For many years, our portfolio of millimetre-wave GaN devices and circuits has featured cutting-edge innovations that break performance trade-offs and push the boundaries for high-frequency GaN. One of our latest technology nodes - T3L GaN builds upon our previous successes, while adding innovations that ensure high linearity and reliability, such as a graded epitaxial structure and a gate minifield-plate. In recent times, we have also invested tremendous effort into GaN technology maturation, qualification, model development, and external foundry services. The result is that today we are

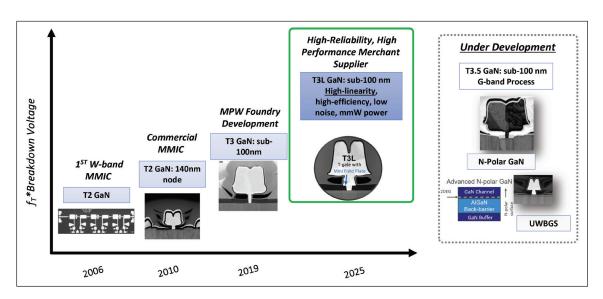

Figure 1: The evolution of HRL's millimeterwave GaN foundry offerings over time.

offering GaN with world-leading high-frequency performance – such as T3L – to external designers via reliable, mature, open foundry offerings.

## HRL GaN odyssey

We have been investing in GaN materials, transistors, and circuit development since the late 1990s, and we have a long history of 'firsts' for RF GaN MMICs, particularly in high-frequency technology demonstrations.

Our early investments associated with in-house epitaxial growth capability enabled innovations such as  $n^+$  GaN ohmic contact regrowth by MBE, and vertically scaled layer structures necessary for high-frequency performance.

As we continue to develop and advance our GaN technology, we draw on our extensive expertise in high-frequency MMIC design and fabrication. Our background includes a strong track record as a provider of high-frequency GaAs and InP-based circuits.

Key milestones in GaN RF technology include unveiling the first Ka-band GaN MMIC power amplifier at the 2004 IEEE International Microwave Symposium, the first W-band GaN MMIC power amplifier at the 2006 International Electron Devices Meeting, and the first G-band GaN MMIC at the 2014 IEEE Symposium on Compound Semiconductor Integrated Circuits.

Over the years, our high-frequency GaN technology nodes – which have utilised 'T'-gates, as opposed to gamma- or field-plate gates – have targeted progressively higher-frequency operation (see Figure 1). Our T3L node is built upon our 40 nm-gate T3 node, but features key modifications to improve linearity and dynamic range – this results in an enviable combination of outstanding linearity, noise, output power, and efficiency for millimetre-wave applications. Much of this pioneering work in high-frequency GaN was made possible through financial

support from the US government, with programmes such as DARPA WBGS, DARPA NEXT, and DARPA DREAM, among others.

## HRL T3L GaN technology

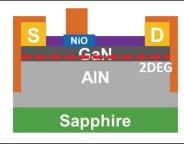

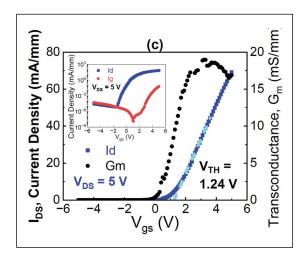

Our T3L GaN HEMT technology was initially developed under DARPA's Dynamic Range-enhanced Electronics and Materials (DREaM) programme, which had the goal of developing new designs and materials for RF transistors with an unprecedented dynamic range in millimetre-wave systems. To succeed in this endeavour, we combined a graded-channel AlGaN/GaN epitaxial structure, providing precise control of transistor transconductance, with a scaled 40-nm T-gate and mini-field-plate. One of the key merits of the graded-channel epi and mini-field-plate is a

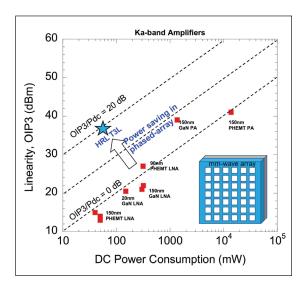

➤ Figure 2. For Ka-band amplifiers linearity versus DC power consumption with typical linearity FOM of around 0 dB has been shown. Star represents the fiducial point illustrating HRL's T3L GaN linearity that sets HRL apart. Adapted from J. -S. Moon *et al*. International Microwave Symposium - IMS 2022, pp. 302-304, 2022.

## COVER STORY I HRL

distribution of the electric field across the device's active area that improves linearity and reduces signal distortion – that's particularly beneficial for high-frequency applications, where RF signal integrity and linearity are crucial. Meanwhile, the short gate length supports a high cut-off frequency (f<sub>r</sub>) of 170 GHz, and a maximum oscillation frequency  $(f_{MAX})$  of 347 GHz.

Drawing on these strengths, our GaN MMICs that incorporate the T3L transistor technology and onchip pre-matching networks have demonstrated a world-record peak power-added efficiency of 45 percent at 94 GHz, and a corresponding power density of more than 2 W mm<sup>-1</sup>. These two characteristics are key performance metrics for efficient power amplifiers. The power-added efficiency of our GaN MMICs at 30 GHz is worldbeating, with values as high as 70 percent.

Modern-day phased arrays and high-dynamic-range RF front ends require amplifiers with high linearity. Traditionally, this linearity requirement has been fulfilled with low-noise amplifiers, operating with a higher DC power consumption, or power amplifiers that are run at a reduced power-added efficiency and power density.

Neither of these options is preferable. Industry is reluctant to meet linearity requirements by taking

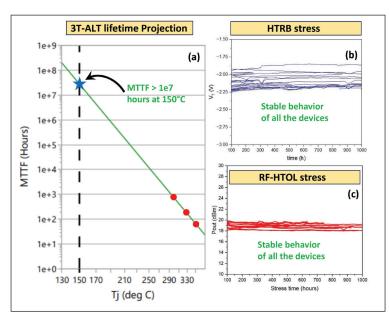

Figure 3. Three-temperature accelerated life (3T-ALT), hightemperature reverse-bias (HTRB), and RF high-temperature operating life (RF-HTOL) tests of HRL's T3L GaN. (a) Median-timeto-failure (MTTF) versus junction temperature for T3L GaN discrete devices under DC-ALT stress. Red data points represent the extracted MTTF values at the stress temperatures, while the green solid line is the fit and extrapolation as described in the text. The star represents the fiducial point to illustrate the predicted MTTF lifetime at the junction temperature, Tj, of 150 °C, of more than 1 x  $10^7$  hours. (b) Threshold voltage of discrete devices during HTRB stress and (c) RF output power (Pout) during HTOL stress, both showing excellent stability up to at least 1000 hours.

a hit in efficiency or consuming more power, especially as payload power needs to be allocated to increased bandwidth and newer software-defined features. Moreover, many airborne platforms are size, weight and power (SWaP) constrained.

What's urgently needed are devices with a high linearity-to-power-consumption figure-of-merit. In this regard, a common figure-of-merit for benchmarking is the ratio of the Output Third-Order Intercept Point (OIP3) (a measure of linearity) to DC power consumption. Judged against this metric, known for short as OIP3/PDC, our T3L GaN technology that employs key design and process breakthroughs delivers a record 17.5 dB at 30 GHz. That's a jaw-dropping improvement, more than 30 times better than the best previous Ka-band lownoise amplifiers featuring GaAs pHEMTs and AIGaN/GaN HEMTs (see Figure 2).

Key features of our T3L GaN technology include two-level metal interconnects with 5  $\mu m$  plated airbridges, 50  $\Omega/\text{sq.}$  thin-film resistors, 300 fF  $\text{mm}^{\text{-}2}$ metal insulator metal capacitors, and 50 µm SiC with through-substrate vias and backside metal.

Our T3L GaN is well-positioned for success in a range of cutting-edge applications within the millimetre-wave domain. Deploying our technology in 5G and beyond wireless communication enables faster data transmission and improved signal quality; in high-resolution radar systems, T3L GaN provides better target detection and imaging capabilities; in electronic warfare and defence systems, T3L GaN enables robust performance in challenging environments; and last but not least, in satellite communications T3L GaN ensures reliable, efficient signal transmission over long distances.

#### T3L GaN technology qualification

Recently, we have invested heavily in the qualification and maturation of our RF GaN technology, to meet the ever-growing demand and requirements of key strategic customers. Lifetime assessment is the first step towards meeting such expectations.

The first inception of our T3L GaN on the DARPA DREaM programme demonstrated the tremendous potential of our technology. Since then, by devoting much effort to technology maturation and qualification, we have been led to implement several minor proprietary changes to the epitaxial structure and fabrication processes, to further improve yield, manufacturability, and reliability.

To understand the lifetime of our first-in-class sub-100-nm GaN HEMTs, we have undertaken temperature-accelerated lifetime testing on our 4 x 37.5 µm T3L GaN discrete transistors with a dissipated power of around 4 W mm<sup>-1</sup> and junction temperatures ranging from 300°C to 380°C (results are shown in Figure 3). Note that, to drive devices to failure, we have intentionally employed stress temperatures that are far higher than the recommended operating condition, which typically ranges from 150°C to 225°C.

For this study, we defined the failure criteria as a 20 percent degradation in device on-resistance from its initial value. To determine values for the median-time-to-fail (MTTF) and lifetime, we analysed the failure time distribution with an Arrhenius temperature-accelerated lifetime model, lognormal statistics, and maximum likelihood estimation.

Based on this approach, we find that despite having one of the shortest gate lengths in the GaN industry, our T3L device lifetime is no shorter than 100 years at a junction temperature of 150°C. This is a MTTF benchmark that other GaN manufacturers typically strive for.

In addition to temperature-accelerated life testing, we have also performed off-state high temperature reverse-bias (HTRB) and on-state RF high temperature operating life (RF-HTOL) reliability testing on T3L devices (see Figure 3). For HTRB testing at an ambient temperature of 150°C, we stressed a group of discrete transistors from multiple wafers using a gate bias of -7 V and a drain bias of 35 V, which corresponds to 250 percent of the operating quiescent voltage (14 V). Under these conditions, we evaluated the stability of various device parameters, such as the threshold voltage.

Applying these conditions for HTRB testing, we determined that device performance is stable up to at least 1000 hours. This is a key reliability benchmark.

On-state qualification of our T3L MMICs through RF-HTOL stress also showed excellent stability, with minimal shift in critical RF-paraments after 1000 hours of stressing.

Successfully passing 1,000 hours of HTRB and RF-HTOL testing, in addition to hitting the state-of-theart MTTF benchmark, serves as a testament to our stable, predictable, and reliable GaN T3L process.

Note that our GaN manufacturing process aligns with a remark made by one of the fathers of statistical process control, the US engineer Harold Dodge, who is famous for the phrase 'you cannot inspect quality into a product'. The implication of his statement is that it's critical to build quality and reliability into the product during the manufacturing process. Abiding by this philosophy, we do not

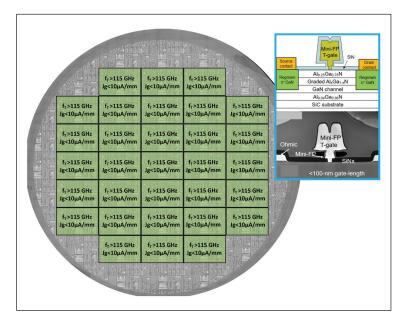

> Figure 4. Wafer map of a typical T3L GaN (gate length less than 100 nm, source-to drain of 900 nm) showing uniform peak  $f_T$  at a  $V_{DS}$  of 5 V and gate leakage current density measured at  $V_{DS}$  = 8 V and  $V_{GS}$  = -5 V. Schematic cross section and the corresponding scanning electron microscopy image of a representative T3L GaN transistor taken from such a wafer is shown in the inset.

implement any additional burn-in or screening when choosing devices for reliability testing. Instead, all our reliability results come from devices randomly picked across multiple wafers after fabrication.

According to a T3L GaN wafer map of peak  $\rm f_{\tau}$  and gate leakage current, tested on in-line process control monitors, there is excellent uniformity associated with our T3L GaN process fabricated on a 100 mm SiC wafer (see Figure 4, which has an inset that shows a schematic cross-section of a W-band capable T3L GaN transistor, as well as a corresponding scanning electron microscopy image).

## Technology maturation and foundry service

We are the first fab (ISO 9001 certified) to develop and offer a sub-100 nm GaN MMIC process technology through our foundry services. With US government support, in 2019 we launched an open commercial multi-project-wafer (MPW) foundry service for our 40 nm GaN-on-SiC T3 technology, and since 2021 we have offered quarterly MPW runs. To-date, we have sold 86 MPW tiles to 30 unique customers. Our foundry services include process design kits (PDKs) in both ADS and AWR, secure

Thanks to the maturation of our sub-100 nm GaN processes, we have seen increasing demand, especially for applications in the V/W-bands. Customers are encouraged to engage with our open foundry for GaN PDK and device model access and support for low-to-moderate volume production

## COVER STORY I HRL

management of customers' design verification, wafer microfabrication, RF probing, and the delivery of singulated MMICs.

To continue to advance our T3L technology node, this year we are launching a T3L GaN MPW service, and adding advanced interconnect features, such as copper pillars for flip-chip compatibility.

Historically, our GaN foundry interests have been balanced across research institutions, companies in the aerospace and defence sector, and commercial private-sector entities. Thanks to the maturation of our sub-100 nm GaN processes, we have seen increasing demand, especially for applications in the V/W-bands. Customers are encouraged to engage with our open foundry for GaN PDK and device model access and support for low-to-moderate volume production.

#### Beyond T3L GaN

In addition to our T3L RF-GaN technologies, we continue to innovate, motivated by the goal of pushing the boundaries of future technologies that will be transformative for the warfighter. One such innovation is N-Polar GaN, a technology we are exploring for its potential to deliver higher power. N-Polar GaN is showing promising capabilities compared with traditional GaN, but it is still advancing through the maturity stages, supported by early government investments in both academia and industry.

We are also making strides in the Ultra-Wide Bandgap Semiconductors (UWBGS) programme that's funded by DARPA. This initiative focuses on developing key processes for realising next-generation devices, including high-efficiency UVC LEDs, laser diodes, high-power RF transistors, and power-conversion electronics.

Through these efforts, we continue to position ourselves at the forefront of technological advancements that will shape the future of military and commercial applications.

By combining world-record efficiency, output power, linearity, and noise figures with excellent device reliability, stability, and uniformity, our current GaN technology is uniquely positioned to address rapidly evolving needs in the millimetrewave RF application space. On top of that, our heavy investment in maturation and capacity to support customer engagements is ensuring a bright future for our GaN, and helping to continue to shape the future of GaN for the broader community.

HRL Laboratories conducts contract research and development with support from various US government agencies, including DARPA, US Air Force, OUSD, and ONR. The organisation gratefully acknowledges this vital support in driving the advancement of cutting-edge technologies and scientific innovation.

### **FURTHER READING**

- ➤ M. Micovic et al. "Apparatus and method for reducing the interface resistance in GaN heterojunction FETs", US Patent 8686473 B1 (2014)

- D. J. Denninghoff et al. "Adaptable 40 nm GaN T-Gate MMIC Processes for Millimeter-Wave Applications", IEEE BiCMOS and Compound Semiconductor Integrated Circuits and Technology Symposium-BCICTS (2023)

- ➤ J. -S. Moon et al. "W-Band Graded-Channel GaN HEMTs With Record 45% Power-Added-Efficiency at 94 GHz, IEEE MWTL **33** 161 (2023)

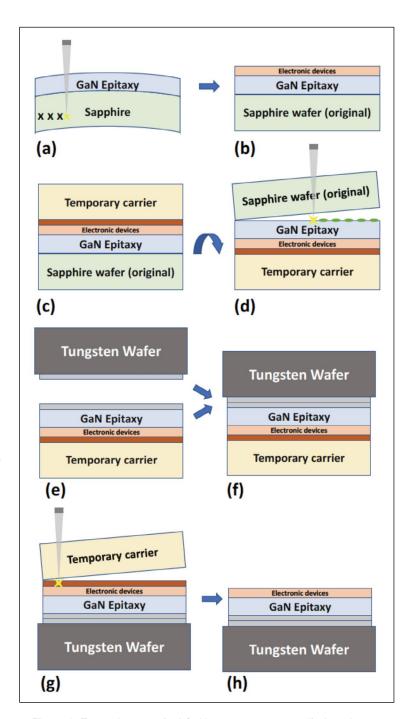

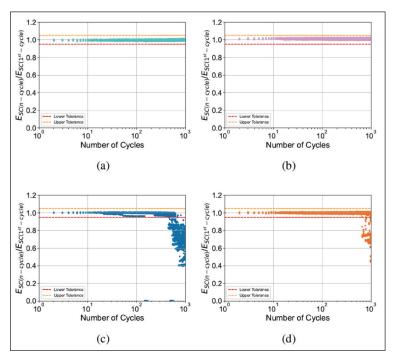

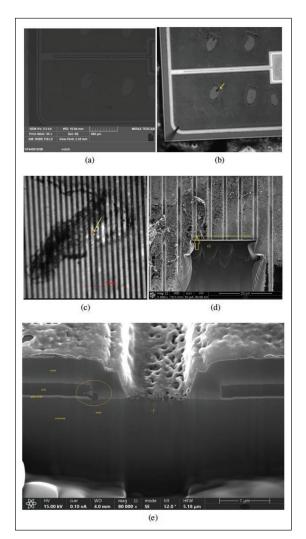

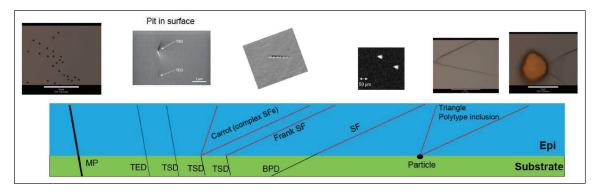

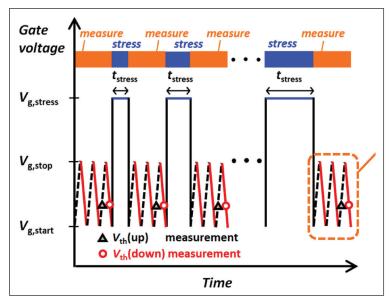

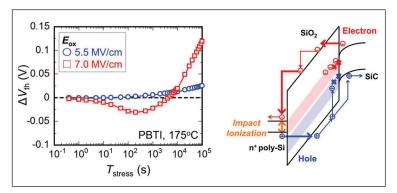

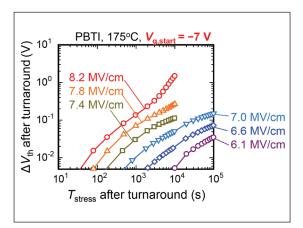

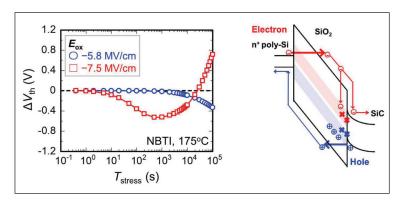

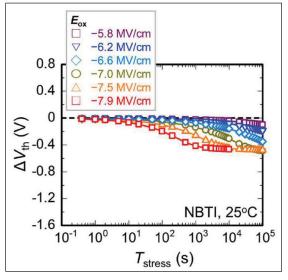

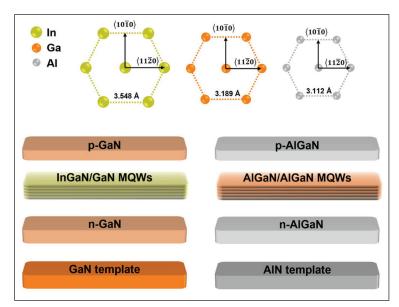

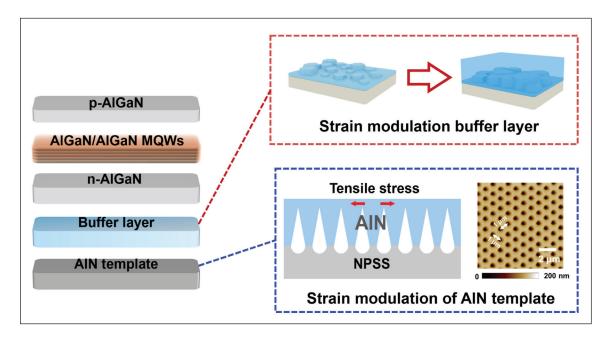

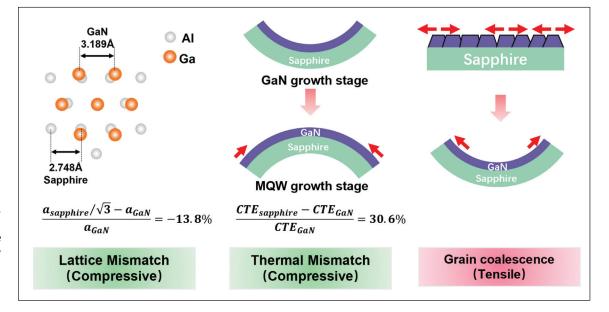

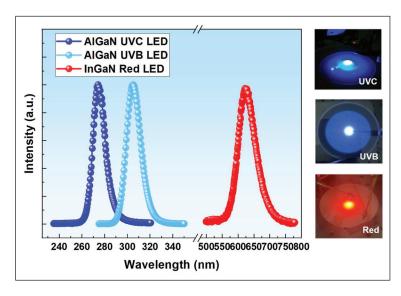

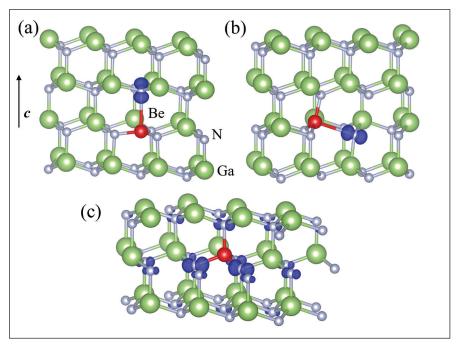

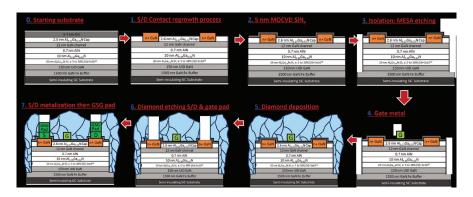

- ➤ J. -S. Moon et al. "High-speed graded-channel AlGaN/ GaN HEMTs with power added efficiency > 70% at 30 GHz", IET Electron. Lett. 53 678 (2020)