# CONNECTING THE COMPOUND SEMICONDUCTOR COMMUNITY

### Pureon drives SiC wafer manufacturing to a new level

#### VOLUME 28 ISSUE IV 2022

### INSIDE

News, Analysis, Features, Editorial View, Research Review and much more

#### VENTURING TO VENUS

AN ANGEL BUSINESS COMMUNICATIONS PUBLICATION

SiC unlocks the door to uncooled electronics capable of handling the cold temperatures found on Venus

### STOCKS AND SHARES

Makers of epitaxial tools take the top three spots on this year's compound semiconductor share price leaderboard

PUREON

#### COMPOUNDSEMICONDUCTOR.NET

### HELPING OUT IN THE DEEP UV

Gallium oxide and a family of stannates combine excellent conductivity with high transparency

## Global mega trends require best performance III-V materials AIX 2800G4-TM

1 an

TL

3D sensing

Augmented reality

Autonomous driving

Cloud computing

Internet of things

Next generation displays

Discover the MOCVD tool of record for AsP-based applications

Made in Germany

www.aixtron.com

.>>>>>

### VIEWPOINT By Dr Richard Stevenson, Editor

### Conquering the deep UV

IT IS COMMON KNOWLEDGE that the Achilles' heel of semiconductor light sources is their feeble emission in the deep UV. That's not that surprising, given that devices emitting in that spectral domain are plagued by point defects that sap efficiency and an incredibly high degree of internal reflection that hampers light extraction.

However, substantial progress is being made, with breakthroughs reported this year in LEDs and lasers – these accomplishments are detailed in this edition's research review. These gains in performance are significant stepping stones towards the commercialisation of GaN-based emitters for disinfection, curing and free-space communication. Note that for the latter, it is a major asset to have wavelengths within the UVC, which is the spectral range from 200 nm to 280 nm. That's because emission is then in the solar-blind region, where there is minimal interference, as well as the opportunity for non-line-of-sight communication, thanks to very strong atmospheric scattering.

For LEDs with a standard emitting area, record-breaking output powers have resulted from switching from a single-emitter to an array of 16 by 16 microLEDs with diameters of 25  $\mu$ m (see p. 61). In comparison, for similar structures with smaller arrays of larger emitters, the output did not even beat that of the standard LED – while with the 16 by 16 array, output rocketed to almost 85 mW, nearly an order of magnitude higher than the control. The team attributes this leap in output power to a suppression of light absorption and a homogeneous injection current.

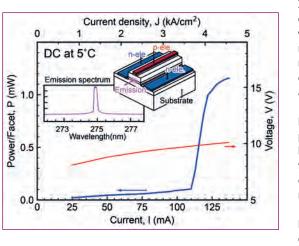

For lasers in the UVC, the milestone of continuous-wave emission is tantalisingly

close (see p. 58). Lasers with an output power of around a milliwatt are now capable of this form of emission at an ambient temperature of 5  $^{\circ}$ C.

Success has come from combining the knowledge gained from prior work with a new architecture. The team that has had this success has built on the merits provided by using a free-standing AIN substrate and polarization-induced doping. To realise continuous-wave emission, their ground-breaking design combines these virtues with: an active region with fewer point defects, and thus a higher quantum efficiency; a cladding layer with a high aluminium content that cuts the leakage of optical modes; and a pair of *n*-type electrodes on the top of the laser that reduces its resistance.

Even better results are on the horizon for both the UVC LED and the laser. The LED promises to produce an even better performance by using a larger array of smaller emitters, while the laser has the potential to deliver emission at higher temperatures by increasing the injection efficiency – it is currently just 10 percent. Realising such success will enable devices operating in the UVC to take a significant step towards shedding their tag of being poor light emitters.

Free weekly e-news roundup go to: compoundsemiconductor.net

### CONTENTS

18

#### VOL. 28 ISSUE IV 2022

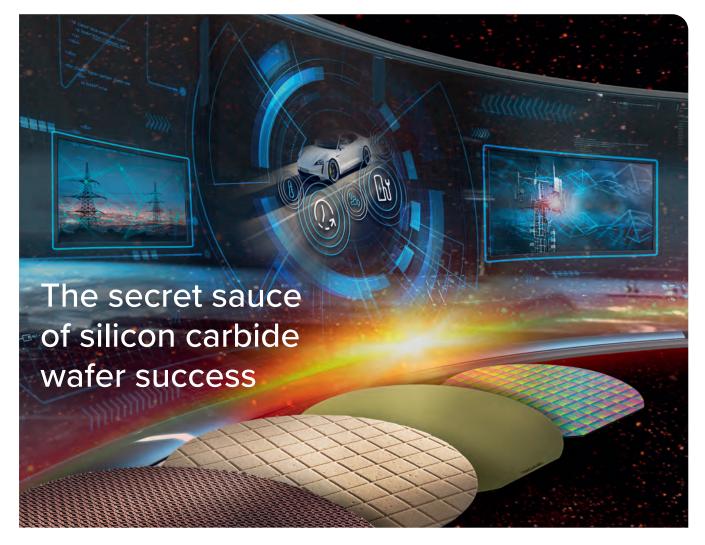

### THE SECRET SAUCE OF SILICON CARBIDE WAFER SUCCESS

Nearly all devices we use today depend on semiconductors. New technical advancements and requirements necessitate the use of SiC for many demanding semiconductor applications

### 24 Makers of epitaxial tools take the top spots

Those making MOCVD and MBE reactors have grabbed the top spots on this year's share price leaderboard

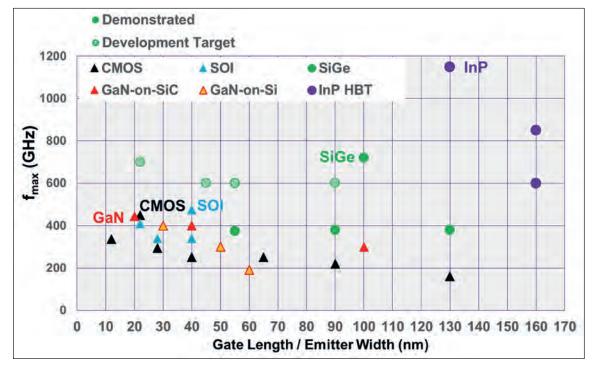

### **30** Strengthening the credentials of the III-V transistor

Fast transistors are poised for far greater deployment, thanks to efforts by fabs and those working on internal production lines

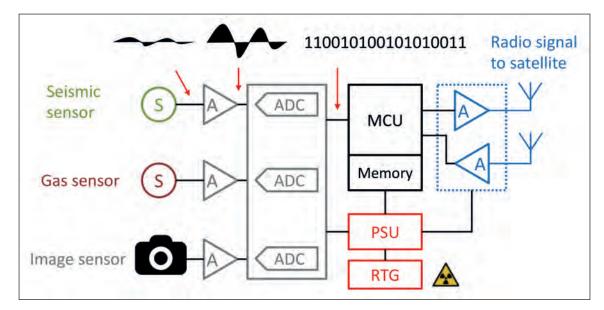

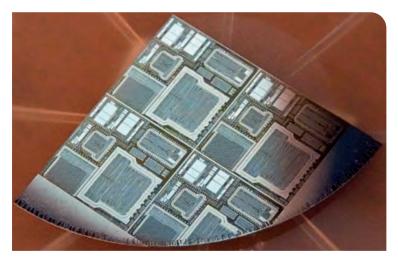

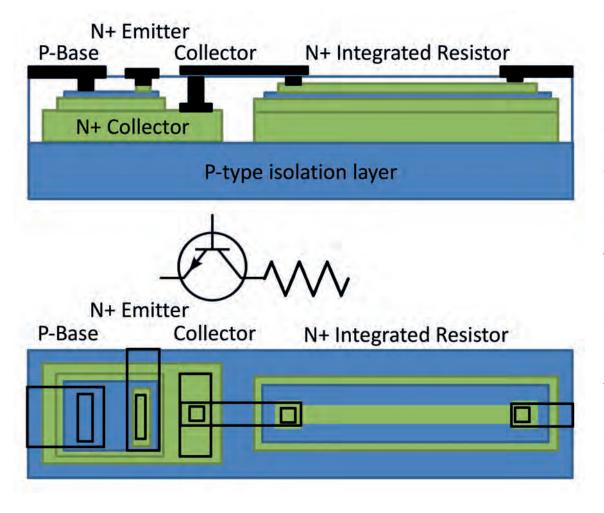

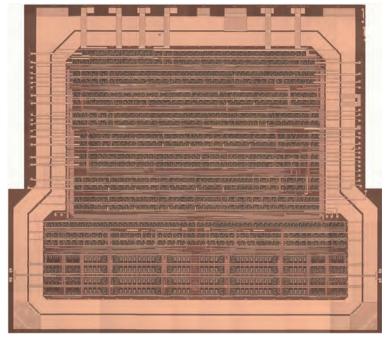

### 36 Venturing to Venus

SiC unlocks the door to uncooled electronics that's capable of handling the extreme temperatures on Venus

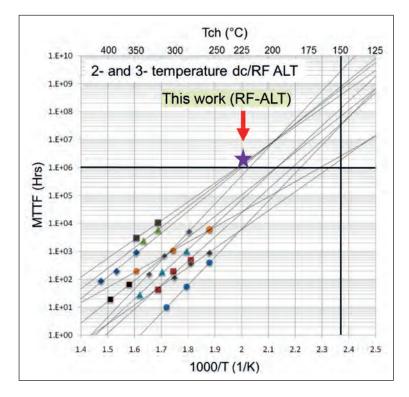

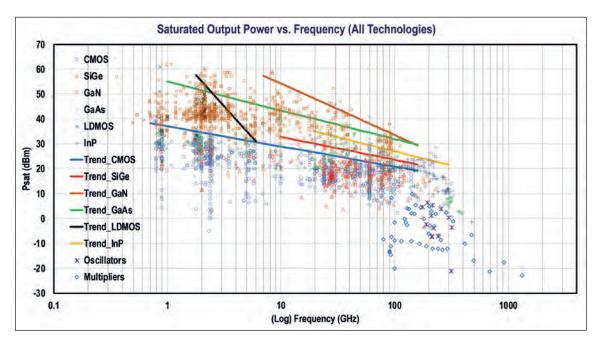

### 42 Ensuring reliability at elevated frequencies

Experimental investigations underscore the opportunities for GaN HEMTs in 5G and 6G networks

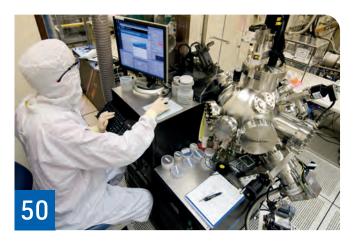

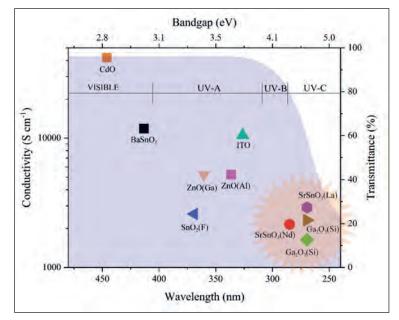

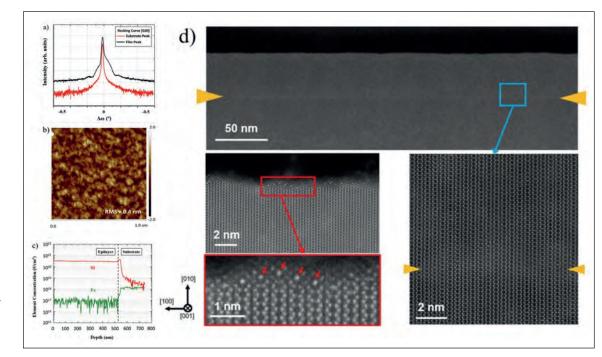

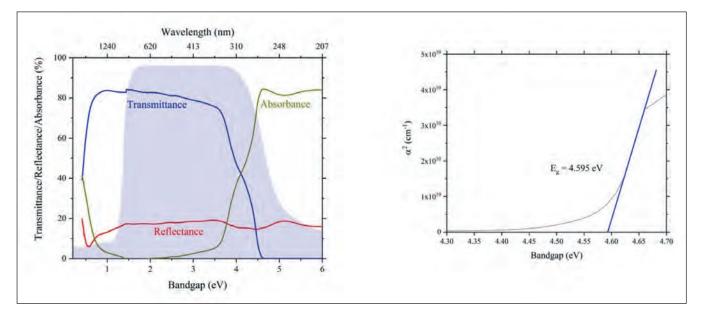

### 50 Taking transparent conducting oxides into the deep UV

How do you combine high conductivity with excellent transparency in the deep UV? By turning to gallium oxide and a family of stannates

### **NEWS ANALYSIS**

### 14 Building a photonics ecosystem for Europe

By 2030, PhotonDelta intends to have created a pan-European integrated photonics industry that will churn out 100,000 wafers a year

### 16 Billion dollar fab that could change industry

In an iconic moment for silicon carbide and EVs, Wolfspeed opens 'the first, largest and only 200 mm SiC fab in the world'

### **RESEARCH REVIEW** 58 UVC laser delivers continuous-wave emission 60 Novel field plate boosts the blocking voltage 61 MicroLEDs propel UVC output

### **NEWS**

- 06 Soft-Epi to ship GaN red epiwafers for microLEDs

- 07 Vertical integration shapes the SiC ecosystem

- 08 Penn State to lead \$7.5 million study of radiation effects on GaN

- 09 ST and Macom make RF GaN-on-silicon prototypes

- 10 Lumileds adds new high power horticulture and stadium LEDs

- 11 ST reveals details of Semikron SiC partnership

- 12 Laserline unveils 3kW CW output blue diode laser

Editor Richard Stevenson Contributing Editor Rebecca Pool News Editor Christine Evans-Pughe Sales Executive Jessica Harrison USA Representatives Brun Media Tom Brun

Janice Jenkins Publisher Jackie Cannon

Director of Logistics Sharon Cowley Design & Production Manager Mitch Gaynor

richardstevenson@angelbc.com +44 (0)1291 629640 editorial@rebeccapool.com chrise-p@dircon.co.uk +44 (0)2476 718970 iessica.harrison@angelbc.com

tbrun@brunmedia.com +001 724 539-2404 +001 724-929-3550 jjenkins@brunmedia.com jackie.cannon@angelbc.com sharon.cowley@angelbc.com

+44 (0)1923 690205 +44 (0)1923 690200 +44 (0)1923 690214 mitch.gaynor@angelbc.com

Circulation Director Scott Adams Chairman Stephen Whitehurst Chief Executive Officer Sukhi Bhadal Chief Technical Officer Scott Adams Directors Jackie Cannon, Sharon Cowley Published by Angel Business Communications Ltd

6 Bow Court, Fletchworth Gate

Burnsall Road, Coventry CV5 6SP, UK. T: +44 (0)2476 718 970 E: info@angelbc.com

scott.adams@angelbc.com stephen.whitehurst@angelbc.com sukhi.bhadal@angelbc.com scott.adams@angelbc.com

+44 (0)2476 718970 +44 (0)2476 718970 +44 (0)2476 718970 +44 (0)2476 718970

Compound Semiconductor is published nine times a year on a controlled circulation basis. Non-qualifying individuals can subscribe at: £105.00/e158 pa (UK & Europe), £138.00 pa (air mail), \$198 pa (USA). Cover price £4.50. All information herein is believed to be correct at time of going to press. The publisher does not accept responsibility for any errors and omissions. The views expressed in this publication are not necessarily those of the publisher. Every effort has been made to obtain copyright permission for the material contained in this publication. Angel Business Communications Ltd will be happy to acknowledge any copyright oversights in a subsequent issue of the publication. Angel Business Communications Ltd will be happy to acknowledge consent of the publishers. The paper used within this magazine is produced by chain of custody certified manufacturers, guaranteeing sustainable sourcing. US mailing information: Compound Semiconductor, ISSN 1096-598X, is published 8 times a year, Jan/Feb, March, April/May, June, July, August/September, October, November/ December by Angel Business Communications Ltd, Unit 6, Bow Court, Fletchworth Gate, Burnsall Rd, Coventry CV5 GSP, UK. The 2022 US annual subscription price is \$198. Airfreight and mailing in the USA by agent named World Container Inc, 150-15, 1837 Gtreet, Jamaica, NY 11413, USA. Periodicals postage paid at Brooklyn, NY 11256. US Postmaster: Send address changes to Compound Semiconductor, Air Business Ltd, c/o WN Shipping USA, 156-15, 146th Avenue, 2nd Floor, Jamaica, NY 11434, USA. Printed by: The Manson Group. ISSN 1096-598X (Print) ISSN 2042-7328 (Online) © Copyright 2022.

We strive for accuracy in all we publish; readers and contributors are encouraged to contact us if they recognise an error or omission. Once a magazine edition is published [online, in print or both], we do not update previously published articles to align old company names, branding, marketing efforts, taglines, mission statements or other promotional verbiage, im-ages, or logos to newly created or updated names, images, typographic renderings, logos (or similar) when such references/images were accurately stated, rendered or displayed at the time of the original publication. When companies change their names or the images/ket used to represent the company, we invite organizations to provide Angel Business Communications with a news release detailing their new business objectives and/or other changes that could impact how customers/prospects might recognise the company, contact the organisa-tion, or engage with them for future commercial enterprise.

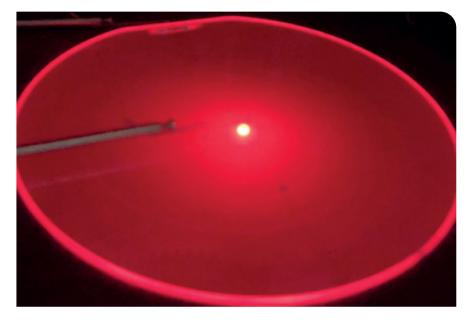

### Soft-Epi to ship GaN red epiwafers for microLEDs

SOFT-EPI, a South Korean company that specialises in GaN-based epitaxial growth using MOCVD, has announced that it is shipping GaN red epiwafers for microLEDs. The company says its breakthrough technology can massproduce red LEDs using existing MOCVD without additional equipment investment. MicroLEDs are considered a key technology for the metaverse platform for enabling next-generation displays for augmented reality, virtual reality, mobile phones, and smart watches.

To make these displays with microLEDs, existing AlGaInP red LED technology has been used. However, AlGaInP has a problem: its efficiency plummets as the chip size becomes smaller, due to its high surface recombination rate.

Also, because it is mechanically weak, the yield drops sharply when transferring, and the expensive wafer prices make the process cost high. Due to these issues, red GaN epi has been receiving much attention from the display industry as an alternative solution, not least because it uses the same material as blue and green microLEDs.

So far, due to technical difficulties, only three or four companies worldwide are known to have succeeded in making GaN LEDs. And these are known to have exclusive contracts with Meta and

Google, says James Kimoon Lee, VP of Sales and marketing at Soft-EPI Inc. "It means microLED developers are having difficulties in their R&D because they cannot get red GaN epi elsewhere," he adds.

Inseong Cho, CTO of Soft-Epi, said: "Efficiency still needs to be improved, but it is now good enough compared to top tier developing companies, or we might be top. Anyone interested can visit our homepage where we open our achievement. And we will continue to improve performances along with customers." Soft-Epi uses patterned sapphire, but the technique is applicable to sapphire, silicon, SiC and GaN. The standard wafer sizes is 4-inch, but 2-inch and 6-inch are available. Wavelength is 620 nm to 670 nm. Wall Plug Efficiency is said to be over 2 percent. Ultimately, this technology will make red, green, and blue sources on one wafer simultaneously. There are also plans to remove the transferring process.

Soft-Epi has already succeeded in making red and green emitters on one wafer, and has a plan to add blue to this pairing this year.

### IQE delivers first 8-inch VCSEL wafers

IQE, a supplier of compound semiconductor wafer products and advanced materials, has announced the world's first commercially available 200 mm (8-inch) VCSEL epiwafer.

IQE says its 200 mm epiwafers will enable a step-change in unit economics for compound semiconductors, leading to the expansion of the market it can target. The increase in wafer size will expand to new foundry partnerships, including silicon-based foundries. Furthermore, it enables the integration of compound semiconductors on silicon, allowing adoption across a wider range of devices and applications.

IQE's 200 mm VCSEL development is an example of the company's continued innovation with the aim of expanding the market for wireless and 3D sensing. 3D sensing was

made economical within premium smartphones in 2017 when IQE developed and scaled VCSEL epiwafers from 100 mm to 150 mm. The introduction of 200 mm is said to create opportunities beyond the smartphone, into a broad range of intelligent connected devices and also enabling applications in the Metaverse.

Americo Lemos, CEO of IQE, commented: "As we set out in our results in March, a key focus area is growing our business by extending our roadmap to 200 mm to establish new foundry partnerships. This advancement will expand the market for both wireless and photonics applications and service the growing demand for compound semiconductors as macro trends such as 5G and the Metaverse proliferate and capture more value for our technology."

### Vertical integration shapes the SiC ecosystem

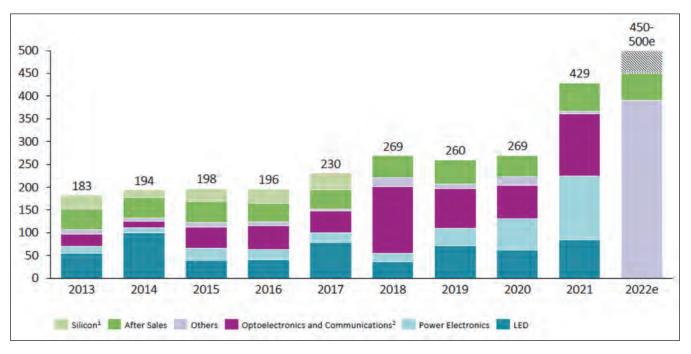

THE SiC device market will reach \$6.3 billion in 2027, according to Yole Développement.

Poshun Chiu, technology and market analyst, Compound Semiconductors & Emerging Materials at Yole, comments: "With more 800 V EVs coming, SiC is expected to grow quickly. Meanwhile, charging infrastructure and photovoltaics are two markets supporting the EV trend. More chargers are needed to support the increasing volume of EVs, and renewable energy shares the same objective of zero  $CO_2$  emission with EVs. These are the markets for SiC to gain more momentum."

SiC market players are working hard to generate more revenue in this multibillion-dollar business. Companies including STMicroelectronics, Wolfspeed, Onsemi, and Infineon Technologies have announced billion-dollar revenue objectives. Despite the different paths chosen by each player, the similarity of business model among them can be clearly identified.

The IDM – integrated device manufacturer – business model is the one chosen by leading players to supply devices, especially power modules. This business model represents a higher dollar value to grow the revenue. The SiC ecosystem has been reshaped by major players in the past years. According to Yole, two main trends impact its supply chain: vertical integration of wafer manufacturing, and module packaging, to gain more revenues in the coming years. In this context, end-system companies, for example, automotive OEMs, are adopting SiC quicker and more flexibly to manage the supply with multiple wafer suppliers in the market.

Innovative approaches to SiC wafer production have been proposed. Even now, the SiC wafer still accounts for a major part of the cost of a SiC device. According to Amine Allouche, technology and cost analyst at System Plus Consulting: "SiC raw wafer cost represents more than 60 percent of the epi-wafer cost for 1200 V SiC MOSFETs. Even though SiC wafer capacity has been expanding, there is still a strong motivation for innovation in quality, throughput, and cost."

8-inch SiC wafers are considered as the critical step to scaling up production. The objective is clearly to increase yield and gain advantages in the next round of competition. Major IDMs are developing their own manufacturing capability of 8-inch SiC wafers; already, some wafer suppliers are shipping samples.

Another approach to optimising the wafering process is to produce more wafers from a single boule. Solution suppliers, such as DISCO, have developed laser cutting systems to increase throughput; Infineon Technologies has qualified its 'cold split' technology; and Soitec has applied its SmartCut technology to produce a SiC wafer that combines a thin layer with a lower defect rate and a handle wafer with lower resistivity. Meanwhile, Japanese company, Sumitomo Metal Mining, has planned to ramp up its engineered SiC wafers in the coming years; and KISAB, a Swedish start-up, is offering wafer-based approaches to offer high-quality SiC wafers.

With a multi-billion-dollar prospect in the coming five years in a strong market mainly driven by EV applications. SiC is expected to enter more and more applications. To make it happen, ecosystem evolution and innovations are the most critical factors to watch. IDM is the main business model in SiC. In addition, major SiC players are moving all along the supply chain toward the module level. The strategy is to create value. In parallel, innovation never stops. Therefore, new entrants are bringing new approaches to improve scaling, throughput, quality, or cost.

### Advanced Compound Semiconductor Foundry Services

MOCVD • Fabrication • Testing

Advanced III-V semiconductor solutions for optoelectronics application in the biotechnology, telecommunications, energy, industrial, and security industries.

MasimoSemiconductor.com | 603-595-8900

### **INDUSTRY NEWS**

# Penn State to lead \$7.5 million study of radiation effects on GaN

TO BETTER PREDICT and mitigate radiation-induced damage of wide bandgap semiconductors, the US Department of Defense has awarded a team led by Penn State a five-year, \$7.5 million Defense Multidisciplinary University Research Initiative Award.

According to Rongming Chu, who will spearhead the project, wide bandgap semiconductors, such as GaN, are inherently more resistant to radiation, due to stronger atomic bonds. However, researchers have yet to reach the full potential of radiation hardness in wide bandgap semiconductor electronics.

"Preliminary studies have indicated that the radiation resistance appears to be limited by defects in the semiconductors, rather than by the material's intrinsic properties," Chu said. "In this project, we seek to understand the radiation effects of these defects, so that we may develop a strategy to redesign the wide bandgap semiconductor device for the ultimate radiation hardness."

Examples of defects include unwanted impurities, displacement of atoms from their original sites, and dangling atomic bonds at the interface between dissimilar materials.

"There is a risk of these defects becoming electrically active under a high electric field, with energetic electrons, causing detrimental effects to device performance," Chu said. "Today's wide bandgap semiconductor electronic devices are designed such that this risk is minimised under normal operating conditions. However, radiation can force the device out of its normal operating condition by exciting additional energetic electrons interacting with the pre-existing defects. It can also knock atoms out of their original positions, modifying pre-existing defects and generating new defects."

The project will have an interdisciplinary team. Collaborators include Patrick Lenahan, distinguished professor of engineering science and mechanics; Miaomiao Jin, assistant professor of nuclear engineering; and Blair Tuttle, associate professor of physics, all from Penn State; and Tania Roy, University of Central Florida; B. Reeja Jayan, Carnegie Mellon University; and Michael Flatté, University of Iowa.

Chu noted that, at Penn State, the team will use tools and experts affiliated with the Radiation Science and Engineering Center and the Nanofabrication and Materials Characterisation User Facilities at the Materials Research Institute.

"The strength of our project comes from a combination of expertise: my research group's capabilities on GaN devices, Lenahan's expertise in defect spectroscopy, Jin's radiation damage modeling, Tuttle's defect theory work, Roy's electrical characterisation of radiation effects, Jayan's defect

structure characterisation and Flatté's transport theory work," Chu said.

"The teamwork also extends beyond the investigators of this MURI project – especially Michael Lanagan, professor of engineering science and mechanics, who was very instrumental in coordinating this multidisciplinary team effort."

The grant will support 16 graduate students, including 11 at Penn State, to perform multidisciplinary research encompassing physics, computation, materials science and engineering and electrical engineering, as they pursue a variety of master's degrees and doctorates.

"Not only will the research prepare next-generation technologists to take on technical challenges, but, through our collaborative work with national laboratories and industry stakeholders, the students will also learn the professional skills needed bridge fundamental research to real-world applications," Chu said.

Contact us about sponsorship NOW as it will be another full house Contact us at: info@angel-tech.net Or call us on +44 (0)2476 718970 and speak to Sukhi Bhadal or Stephen Whitehurst

### ST and Macom make RF GaN-on-silicon prototypes

STMICROELECTRONICS and Macom Technology Solutions have announced the successful production of RF GaNon-silicon prototypes.

The companies say that prototype wafers and devices manufactured by ST have achieved cost and performance targets that would allow them to effectively compete with the incumbent LDMOS and GaN-on-SiC technologies on the market.

These prototypes are now moving to the next big milestones – qualification and industrialisation. ST is on target to hit these milestones in 2022. With this progress, ST and Macom have begun discussions to further expand their efforts to accelerate delivery of advanced RF GaN-on-silicon products to the market.

"We believe that the technology has now reached performance levels and process maturity where it can effectively challenge the established LDMOS and GaN-on-SiC and we can offer attractive cost and supply-chain advantages for high-volume applications, including Wireless Infrastructure," said Edoardo Merli, Power Transistor Sub-Group general manager and executive VP of STMicroelectronics. "Commercialising RF GaN-on-silicon products are the next big milestone in our collaboration with Macom and with continued progress, we look forward to fully realising the potential of this exciting technology."

"Together, we continue to make good progress in moving the GaN-on-silicon technology towards commercialisation and high-volume production," said Stephen Daly, Macom president and CEO. "Our collaboration with ST is an important part of our RF Power strategy and I am confident that we can win market share in targeted applications where the GaN-on-silicon technology meets the technical requirements." RF GaN-on-Silicon offers high potential for 5G and 6G infrastructure.

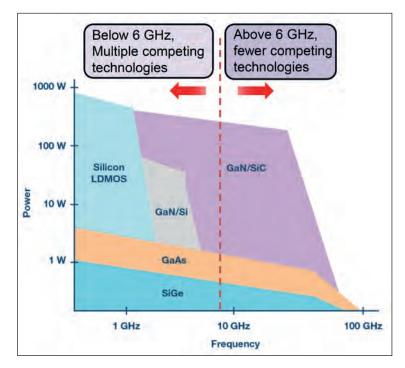

The long-term incumbent RF power technology, LDMOS, dominated earlygeneration RF power amplifiers. GaN can offer superior RF characteristics and significantly higher output power than LDMOS for these RF PAs. Further, it can be manufactured on either silicon or SiC wafers.

RF GaN-on-SiC can be more expensive because of the competition for SiC wafers from high-power applications and because of its non-mainstream semiconductor processing.

On the other hand, the GaN-on-silicon technology under development by ST and Macom is expected to offer competitive performance paired with large economies of scale, enabled by its integration into standard semiconductor process flows.

### Soitec releases first 200 mm SmartSiC substrate

Soitec, the French semiconductor materials specialist, has released its first 200 mm SiC SmartSiC wafer. With the release, Soitec says it is now able to enlarge its SiC product portfolio beyond 150 mm, take the development of its SmartSiC wafers to the next level and cater to the growing demand of the automotive market.

The 200 mm SmartSiC substrate emerged from Soitec's pilot line at its Substrate Innovation Centre within CEA-Leti in Grenoble. The release enabled Soitec to demonstrate the quality and performance of a 200 mm SmartSiC wafer and conduct a first round of key customer validations.

Soitec launched the construction of a new fab in France, Bernin 4, in March 2022. It is primarily dedicated to manufacturing of SmartSiC wafers in 150 mm and 200 mm and is expected to be operational by the second half of 2023. Soitec's SmartSiC technology is said to significantly enhance the performance of power electronics devices and boost electric vehicles' energy efficiency. The technology consists in bonding a very thin layer of high-quality SiC to a very low resistivity polySiC wafer.

"Soitec's SmartSiC substrates will be key for energy-efficient electromobility," says Christophe Maleville, CTO of Soitec. "Our unique

technology allows us to pioneer cuttingedge engineered substrates and open up new perspectives for power electronics in the automotive and industrials markets."

He added: "The addition of 200 mm to our SiC substrate family allows us to further differentiate our portfolio and address an even larger variety

of customer requirements, in terms of product quality, reliability, volume, and energy efficiency. The release of a 200 mm SmartSiC wafer is an important milestone in the development and deployment of our SmartSiC technology. It underpins our technological leadership, our capability to drive innovation and launch nextgeneration wafer technologies."

### **INDUSTRY NEWS**

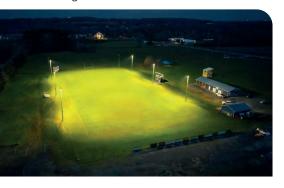

# Lumileds adds new high power horticulture and stadium LEDs

Lumileds has announced two new LEDs. The first is the Luxeon SunPlus HPE, a high power, deep-red (660 nm) LED designed specifically for the horticulture lighting industry. The second is the Luxeon HL2Z, an undomed, CSP, single-sided, high-power LED for stadium lighting that delivers more than 315 lumens and more than 160 lumens-per-Watt from a compact 2.3 mm<sup>2</sup> package that is just 0.36 mm high.

Luxeon SunPlus HPE is is said to achieve the highest PPF and PPE from its industry standard 3.5 mm<sup>2</sup> ceramic package. The new deep-red LED is part of the SunPlus horticulture portfolio that covers a broad range of wavelengths and colours, including white, purple, and lime, in a variety of mid-power, highpower, and CoB packages which offers flexibility to growers to create a specific Lighting mix required for various types of crops to give growers the edge. "Much of the horticulture market is adopting solutions that use a mix of white and deep-red LEDs," said LP Liew, senior product marketing Manager at Lumileds. "The new Luxeon SunPlus delivers top notch performance. And it's available with extremely short lead-times. At the end of the day, it's the highest performing LED and its shipping."

According to Lumileds, its Luxeon SunPlus HPE has the robustness to stand up to harsh horticulture environments and deliver the longevity expected of all Luxeon LEDs. It pairs exceptionally well with the high-efficacy Luxeon SunPlus 3030 and 5050 LEDs, the two most commonly deployed white LEDs. This white and deep-red horticulture combination can significantly drive down the system cost and reduce operating costs, due to the solution's superior efficacy. The Luxeon SunPlus HPE, with its industry standard package, has various off-the-shelf optical solutions available to enable designers to select the right viewing angles to achieve the appropriate intensity of light for the crops. Luxeon SunPlus is a single portfolio engineered to address the full breadth of horticulture lighting applications.

The Luxeon HL2Z has already been adopted by M3 Innovation, whose MAKO Sports Lighting Solution (pictured above) uses the Luxeon HL2Z to deliver 150,000 lumens from each of its modules designed to illuminate athletic fields, parks, stadium fields and other outdoor facilities. "With Luxeon HL2Z, we were able to completely rethink what can be achieved in a sports lighting solution, the power, optical control, and design possibilities are what made the MAKO disruptive in the market" said Joe Casper, executive officer at M3 Innovation.

"Customers that are engineering street lights, stadium lights and other high luminance directional applications benefit from an un-domed source as it makes it easier to increase optical efficiency and to realize narrow beam angles and complex light distributions," said Alvin Yeoh, product manager. "With Luxeon HL2Z, everything from array configuration design to DLC qualification is simplified and system costs can be lower by 20 percent or more."

In addition to the available LM80 data, rayset data and visual inspection prove the excellence of Luxeon HL2Z's colour consistency across the beam, enabling it to support high quality illumination indoors or outdoors. Luxeon HL2Z is specified for R9 $\geq$  40 for 70CRI, R9  $\geq$  0 for its 80CRI, and R9  $\geq$  50 for 90CRI parts meaning that solutions with Luxeon HL2Z can qualify for DLC Standard or Premium listing.

### SK raises stakes in local SiC power specialist

SK Inc, the holding company of the South Korean SK Group, is acquiring a majority stake in local SiC power semiconductor manufacturer Yes Power Technix.

SK is spending \$94.8 million to raise its stake from 33.6 percent to 95.81 percent in order to advance into the EV component business.

Yes Power Technix, founded in 2017, is South Korea's only power semiconductor company specialising in the design and manufacture of SiC power chips widely used in electric vehicles. SK said it aims to expand the power semiconductor portfolio to other high value-added products, such as GaN-on-SiC power chips used in satcoms and radar devices.

### ST reveals details of Semikron SiC partnership

STMICROELECTRONICS has revealed that it is supplying SiC technology for the eMPack electric-vehicle (EV) power modules from Semikron, one of the world's leading manufacturers of power modules and systems.

This is the result of a four-year technical collaboration between the two companies to design-in ST's advanced SiC power semiconductors. SiC is quickly becoming the automotive industry's preferred power technology for EV traction drives, contributing to greater driving range and reliability. Semikron recently announced it had secured a billion-euro contract to supply their innovative eMPack power modules to a major German car maker, beginning in 2025.

"ST's industry-leading SiC devicemanufacturing capabilities and in-depth expertise with the technology enabled us to integrate these cutting-edge semiconductors with our advanced manufacturing processes, which enhance reliability, power density, and scalability to meet the needs of the automotive industry," said Karl-Heinz Gaubatz, Semikron CEO and CTO.

"As we now move towards volumeproduction, our collaboration with ST brings the assurance of a robust supply chain that gives control over quality and delivery performance. Leveraging our SiC technology, Semikron's advanced scalable eMPack family of power modules is ready to make a major contribution towards zero-emission motoring," said Edoardo Merli, Power Transistor Sub-Group general manager and executive VP of STMicroelectronics.

"In addition to its transformative effect in e-mobility, our SiC technology, now in its third generation, is driving increased efficiency, performance, and reliability in sustainable energy and industrial power-control applications."

Engineers from ST and Semikron cooperated to integrate ST's SiC MOSFETs, which control power switching in the main EV traction inverter, with Semikron's fully sintered direct pressed die (DPD) assembly process. DPD enhances module performance and reliability and enables cost-effective power and voltage scaling. Using the parameters of ST's SiC MOSFETs, supplied as bare dice, Semikron has established 750 V and 1200 V eMPack platforms, addressing applications from 100 kW to 750 kW and battery systems from 400 V to 800 V.

Upgrade your legacy equipment with powerful control, automation, and monitoring capabilities

#### Real-time control, monitoring, and analysis

- Currently running in over 80x systems worldwide

- Intuitive user-friendly interface

- Future process data comparison capability

- Utilize databases to extend equipment life, past 20 years

- Continuous support and maintenance

- No subscriptions or annual service fees

- Highly customizable Imperium Software Modules

Imperium Process Control Software is an enhanced replacement for legacy Emcore, Veeco, Thomas Swan, Aixtron, TNSC, Structured Material Inc. (SMI), and any MOCVD / CVD / HVPE control software.

www.agnitron.com

sales@agnitron.com

+1 952.937.7505

### **INDUSTRY NEWS**

### Laserline unveils 3kW CW output blue diode laser

LASERLINE presented the world's first blue diode laser with a 3 kW CW output power at *Laser World of Photonics* 2022. The laser was especially designed for welding, cladding and additive manufacturing of copper components. It is a further milestone in the power development of blue highpower diode lasers.

Back in 2019, Laserline presented the world's first blue CW diode laser with up to a 1 kW CW output power, whose power was subsequently raised to 2 kW just a year later. The blue 3 kW diode

laser that is now being showcased in Munich displays the highest performance class of industrial lasers in the blue wavelength spectrum to date. In line with the 1 kW and 2 kW Laserline diode lasers, the new laser operates at a wavelength around 445 nm.

This spectral range is absorbed much better by non-ferrous metals, such as copper and gold, compared with infrared radiation. Among other benefits, this allows heat conduction welding of copper components close to the surface, along with more energyefficient and climate-friendly processes.

Increasing the CW output power to 3 kW now makes it possible to have additional application options. In joining and cladding processes, much faster welds and higher deposition rates can be achieved. In the case of keyhole welding of electrical conductors, such as copper hairpins, larger crosssections can be handled with moderate heat input using blue lasers only.

Where hybrid solutions combining blue and infrared lasers continue to be

required, less infrared energy is needed today. This clearly optimises the operation costs and the CO<sub>2</sub> balance of the applications.

Laserline has also introduced a new high-power-cladding-solution based on a 45 kW IR diode laser. This was developed in cooperation with the Fraunhofer Institute for Material and Beam Technology. This high-powercladding-solution is meant to optimise the industrial cladding of components that are subject to wear and corrosion.

Being the first process of its kind, it enables wear and corrosion protection coatings for large components – such as power plant elements, brake discs, hydraulic cylinders or plain bearings – to be readily implemented for seriesproduction and in a cost-effective manner.

Access to the use of a higher diode laser power class with up to 45 kW output power further increases the efficiency and productivity of the process. This enables higher order rates and larger quantities at reduced process costs.

### II-VI makes multimillion-dollar expansion in Taiwan

II-VI Incorporated will extend its ion implanter disk refurbishing services to Asia, with a multimillion-dollar expansion in Hsinchu City, Taiwan, which is expected to come online in July 2022.

The acute shortages of semiconductor devices in the global supply chain are driving strong demand for refurbishment of wafer fabrication equipment.

The expansion in Taiwan will effectively double II-VI's global disk refurbishing capacity. Batch implanter tool owners in Asia will benefit from a rapid turnaround service that will enable them to maintain their tools in operation and sustain their production output.

"The market demand for used ion

implant equipment already exceeds availability by about a factor of ten, including in Asia," said Sohail Khan, executive VP, New Ventures & Wide-Bandgap Electronics Technologies.

"Our 25 years of expertise and innovations in disk refurbishment enable our customers to achieve an average of 30 percent savings on costof-ownership over OEM service," added Khan.

"By coming to us, customers will reduce their maintenance costs and get the most out of their ion implanter equipment from higher reliability and longer service life."

II-VI implants tens of thousands of wafers per week and adds tools and capacity as required to support

customers' changing needs. The company maintains a large complement of high- and medium-current and highenergy production implanters handling 2-inch to 12-inch substrates.

II-VI provides ion implantation services for silicon and compound semiconductor wafers, including heated ion implantation for SiC wafers.

### PUREON

### Pureon – A total process solution provider for SiC Wafering

Are you looking for a **solution provider** to help **increase SiC wafer production**? Discover our complete set of solutions for SiC wafering process from ingot slicing to CMP Polish!

#### **Pureon solutions highlights**

- Trusted solution provider to the SiC substrate manufacturing market for nearly 20 years

- Innovative developer of environmentally friendly wire saw slurries

- Engineered slurry formulations providing process efficiency and stability

- Broad polishing pad offering for all process steps

- Customized process solutions: pad and slurry combinations for optimum cost of ownership

Pureon offers eco-friendly **wire sawing slurries** for slicing of the SiC ingots. Next generation non-oil based wire saw slurries are enabling faster cuts and improved wafer geometry.

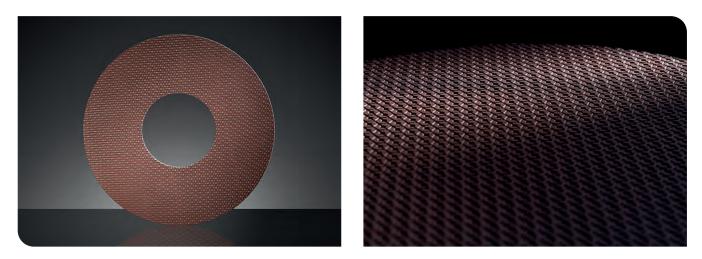

Pureon provides the market leading **polishing pads** for SiC wafer manufacturers! They are uniquely designed for diamond mechanical polishing and final CMP polishing of SiC wafers where flatness and ultra-precision surface finish are critical. Higher removal rates coupled with lower defects make these the go to solution for the SiC wafer manufacturers.

**Diamond polishing slurries** from Pureon are eco-friendly and ideal for polishing SiC wafers! The water soluble, ready-touse diamond suspensions are designed for rapid and stable processing of SiC wafers. Our slurry suspensions are optimized for highest performance in finishing processes from bulk to fine polishing on various pad combinations, ultimately producing sub nanometer SiC surface roughness.

**IRINO** – The next generation processing solution for the SiC wafering process! The new composite polishing pad is poised to provide step function improvements in bulk processing of SiC substrates by providing dramatically enhanced material removal rates compared to traditional polishing methods. You can use it for rapid bulk processing of super hard materials such as SiC wafers and accelerate your wafering process to achieve your goals!

#### **Get in touch with us and learn more about our solutions.** Pureon AG, Kreuzlingerstrasse 1, CH – 8574 Lengwil, pureon.com

### Building a photonics ecosystem for Europe

By 2030, PhotonDelta intends to have created a pan-European integrated photonics industry that will churn out 100,000 wafers a year. Here's how, reports **REBECCA POOL**

IN APRIL THIS YEAR, PhotonDelta, of The Netherlands, secured a mighty €1.1 billion in public and private funds to kick-start a pan-European integrated photonics industry. By 2030, the photonics umbrella organisation, which provides InP, SiN and silicon photonics production and prototyping facilities, aims to have created an 'ecosystem' of hundreds of companies delivering more than 100,000 wafers per year, and photonicsrelated products, to industries worldwide.

As PhotonDelta chief executive, Ewit Roos, highlights, funds will be invested in photonics startups and other businesses to scale activities, expand production and research facilities, attract engineers and also to develop, what he describes as, a 'worldclass' design library.

"Two to three years ago no-one spoke about strategic autonomy in Europe, but the current chip shortage and today's geopolitical situation have triggered European policymakers to make sure we are not dependent on Asia and the US for this key technology," highlights Roos. "As well as this, we've also seen a need to accelerate the development of photonics technologies in The Netherlands and the rest of Europe."

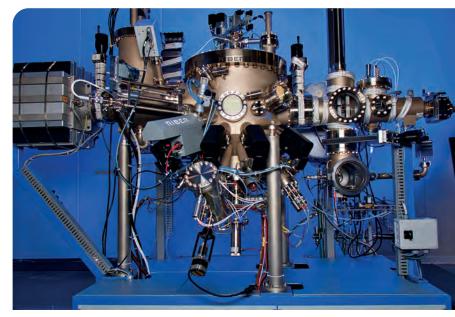

> A quantum photonic processor from QuiX, of The Netherlands. [Daniel Verkijk, QuiX Quantum]

Indeed, thanks to the likes of Philips and Mathworks, The Netherlands has a rich heritage in tech research and development, with myriad home-grown start-ups already forming the basis of a photonics

supply-chain. For example, in The Netherlands alone, LioniX International, Bright Photonics and Smart Photonics have been pushing back the boundaries of photonics design and fabrication, while Phix has been developing photonic integrated circuit (PIC) packaging processes. Staying in The Netherlands, start-ups and scale-ups such as Surfix, MantiSpectra, Quix, Effect Photonics, and so many more, have developed PICs for a broad range of applications, whilst across Europe, a vast array of start-ups including aiXscale Photonics, Germany, and Ommatidia LiDAR, Spain, have been following similar trajectories. What's more, Belgium-based imec is home to SiN and SiPh platforms for CMOScompatible PIC fabrication; and joint European platform for photonic integrated components and circuits, JePPIX, can be used to develop prototypes based on InP and SiN photonics.

"In The Netherlands, we are strong in research, photonics integration and parts of [photonic chip] manufacturing, but you need all kinds of other expertise to make photonic integrated circuits," says Roos. "At PhotonDelta, we want to bring all of this together and increase the pace of development for photonics manufacturing, in both the front-end and back-end... My dream is that we do for photonic integrated circuits what TSMC has done for today's electronic ICs."

#### Planning the future

Since 2019, PhotonDelta has been investing in in many start-ups, including Effect Photonics, to develop its DWDM optical SoC technology, Phix, with its high volume PIC back-end foundry packaging facility, and Smart Photonics and its InP foundry processes. Looking forward, investment will continue up and down the integrated photonics supply chain, but at faster pace. Roos points to InP production at Smart Photonics' foundry, SiN PIC development at LioniX, and quantum photonic processor development at QuiX, also of The Netherlands, as just a few investment targets.

Along the way, PhotoDelta has also been offering the legacy semiconductor industry practice of multiproject wafer runs with partners Smart Photonics, LioniX, imec and JePPIX, to reduce the cost of PIC protoyping. "All these players will be receiving a lot of support from us, and it's also important that

### NEWS ANALYSIS | PHOTON DELTA

we work with imec, as we will then have all the important platforms; CMOS, silicon photonics, InP and SiN," points out Roos. "We're not necessarily doing anything new with these firms, but we are accelerating activities."

Critically, Roos is keen to ensure that large-scale photonics production is reliable, stable and robust. Looking at wafer production, some 5,000 4-inch InP wafers are currently being manufactured at Smart Photonics, but Roos anticipates some 100,000, 6-inch InP wafers being produced every year come 2030. LioniX could also be churning out up to 50,000 8-inch SiN wafers, a year, by the same time. Meanwhile, Roos hopes to achieve fully-automated, higher-speed back-end production come 2030 with a comprehensive design library and automated wafer-scale, generic, integration technology across silicon, silica and InP substrates. "You can only survive if you have a world-class library of building blocks that can be used in manufacturing," he says.

"We have put a lot of emphasis, in the next six years, on application technology," he adds. "And to be more focused on what high-volume customers require for next-generation applications, be it for automotives, biosensing, agriculture, quantum photonics - you name it."

Clearly, a solid pan-European photonics integration supply chain will demand an equally solid workforce. Roos is confident this will follow, and highlights how Dutch photolithography systems manufacturer, ASML, attracts tens of thousands of job applications every

PIC wafer from one of PhotonDelta's multi-projectwafer runs here multiple chip designs from different businesses are combined onto a single wafer to cut prototyping and processing costs.

year thanks to its attractive working environment and conditions. Still, the PhotonDelta chief executive is keen to keep an eye on the rest of the world.

"European sovereignty doesn't mean you have to have all of your volume production capacities within European borders – that would be insane and against all economic rules," he says. "But we need to have strategic assets within our borders so the world also comes to us - and for us, this will be photonics integrated circuits and photonics engines."

### Driving tomorrow's technologies

Compound semiconductors provide the key enabling technologies behind many new and emerging applications. CSconnected represents the world's first compound semiconductor community based in and around South Wales in the UK

# The billion dollar fab that could change industries

In an iconic moment for silicon carbide and electric vehicles, Wolfspeed opens 'the first, largest and only 200 mm SiC fab in the world'. What comes next, asks **REBECCA POOL**

> On the day that Wolfspeed opened its 200 mm automotive-qualified SiC fab in Mohawk Valley, Upstate New York, the SiC tech supplier also announced a multi-year agreement with Lucid Motors, to supply SiC power semiconductors. Right now, these can be found in the luxury, all-electric Lucid Air.

> Wolfspeed is making wafers for Lucid Air electric cars – an Air vehicle cuts the ribbon at the new 200 mm SiC facility. The two industry developments go hand-in-hand because, as Lucid's senior vice president of product and chief engineer, Eric Bach, exclaimed at the company's ribbon-cutting event: "We need every single SiC chip that we can get." Indeed, a few weeks earlier, Rohm Semiconductor revealed that Lucid was using its SiC MOSFETs in the Air's on-board charger. However, the latest events also signal to the SiC industry that great things are coming.

Officially opened on April 25th and dubbed 'the first, largest and only 200 mm SiC fab in the world', the Mohawk Valley facility is churning out SiC

MOSFETs and packaging these up into its XM3 halfbridge power module. Six of these SiC packages will be used in each Lucid Air power-train inverter, providing the low switching losses and high power density necessary for the sedan's modest-sized, 74 kg, 500 kW electric motor.

The Air itself is Lucid's first production model, and has already won the *2022 MotorTrend Car of the Year*, beating the all-electric Porsche Taycan and Mercedes-EQ EQS. The vehicle boasts up to 1100 horsepower and an impressive range of 520 miles.

As Wolfspeed chief executive, Gregg Lowe – who perhaps not surprisingly drives a Lucid Air – highlighted at his facility opening: "This all-electric car has every whistle and bell you can imagine; it's breaking all kinds of electric vehicle records including driving range and recharge time."

Accolades aside, the new facility opens at a time when the buoyant SiC industry is bucking general, worldwide trends. Driven by electric vehicles, analysts predict billion dollar growth for the SiC market with France-based Yole Développement forecasting figures beyond \$6 billion by 2027, up from \$1 billion in 2021.

In preparation, SiC players far and wide, including Sanan IC, Rohm, II-VI and Infineon, have been building up production capacities. But what sets the new Wolfspeed facility apart is its 200 mm wafers.

Competitors are working on this larger wafer size – for example, STMicroelectronics announced its first 200 mm SiC wafers for prototype devices in July last year while Sanan IC has aired hopes of manufacturing many thousands of 200 mm wafers come 2024. Still, the Mohawk facility is the world's first 200 mm fab, which could accelerate the

### NEWS ANALYSIS | WOLFSPEED

industry transition to the larger wafer size, given many companies work with legacy 200 mm silicon wafer equipment. Current yield figures are not available, but the larger-sized wafer is set to raise chip yields by nearly 85 percent compared with 150 mm wafers, helping to ensure the future wafer supply many manufacturers are still striving to truly secure.

#### Further expansion

Following Wolfspeed's billion dollar investment, the Mohawk Valley SiC fabrication facility comes in at 674,000 ft<sup>2</sup> and is home to a 150,000 ft<sup>2</sup> clean room. Coupled with expanding operations in Durham, North Carolina, Wolfspeed intends to establish what it calls a national SiC corridor along the US East Coast, and also raise SiC wafer and device production capacity by 30-fold, by 2024, from 2020 levels.

Looking beyond 2024, this figure is only set to swell. In its latest earnings call, on 4 May, for the third fiscal quarter of 2022, Wolfspeed revealed a revenue of \$188.0 million, a 37 percent revenue increase compared to the same time in 2021, and up 9 percent from the previous quarter in 2022.

In the same call, Lowe also pointed to future

capacity expansion saying: "A top priority going forward is increasing capacity for both materials and devices... Wolfspeed will very likely need to add more materials production as well as consider the construction of another wafer fab."

"At this point in time, I can't tell you precisely when and where, but it will certainly be

sooner than we anticipated back at our Investor Day [November 2021]," he added.

This spells good news for manufacturers of SiC devices worldwide, the future SiC industry, but also the US East Coast, a region that many at Wolfspeed's ribbon-cutting event referred to as 'Silicon Carbide Valley'. While the Mohawk facility has already generated more than 200 jobs, come 2029 numbers are expected to rise to 600. And along the way, Wolfspeed has been investing millions of dollars in neighbouring SUNY Polytechnic Institute, creating an internship programme, scholarship scheme as well as two endowed faculty chairs, to secure its future workforce.

As SUNY Poly acting president, Tod Laursen, highlighted at the event: "We now have the

The Air itself is Lucid's first production model, and has already won the 2022 MotorTrend Car of the Year, beating the all-electric Porsche Taycan and Mercedes-EQ EQS. The vehicle boasts up to 1100 horsepower and an impressive range of 520 miles

opportunity to build a curriculum specific to the SiC industry, collaboratively with our industry partner [Wolfspeed]."

And his words were backed by New York governor, Kathy Hochul, who also said: "Tell us the skills that you need and we will make sure that our world class institutions in the Mohawk Valley are teaching those skills... [This] is where it's happening, I can feel the energy." > Chief executive of Wolfspeed, Gregg Lowe, shows New York governor, Kathy Hochul, the manufacturing processes at the new SiC fabrication facility in Marcy, New York, US.

Nearly all devices we use today depend on semiconductors. New technical advancements and requirements necessitate the use of silicon carbide (SiC) for many demanding semiconductor applications. Due to its physical and electronic properties, SiC based devices are well suited for high temperature and high-power/high-frequency electronic devices enabling the advancements in Electric Vehicles (EVs), 5G and IOT technologies. While they bring a lot of benefits for the end-user, the production of high-quality SiC substrates presents many challenges to wafer manufacturers. Pureon has been providing state-of-the-art solutions to SiC wafer manufacturers for over 15 years in the various process steps of slicing and surface finishing.

### BY DR. WILLIAM GEMMILL, TERRY M. KNIGHT, DIPL.-ING. HELGE WILLERS, DR. RAVI BOLLINA AND ARTHUR LENART FROM PUREON

LIVING HAS BECOME SMARTER! Our day starts with the alarm from our smartwatch. We clap our hands to turn on the light in our smart home. While we wait for the coffee machine to make our coffee, we check our smartphone for the latest news and updates. Then we unplug our electric vehicle from the charger and drive to work. At work we do our job by being connected to the whole world with the help of cloud-based computers and audiovisual communication systems. Semiconductors improve our daily lives

We have followed Gordon Moore's Law to once unimaginable levels, and semiconductors have revolutionized the way we work, communicate, travel, entertain, harness energy, and treat illness. They not only make useful devices of our daily life possible, but also make them more compact, less expensive, and more powerful. Take for example the evolution of mobile phones: The first devices

in the 80s were very heavy, cost nearly as much as a car, and held a charge for only about 30 minutes of talk time. Today, our smartphones are highly intelligent mobile devices, nearly as powerful as a regular computer and are available for everybody. Amazingly, the greatest potential still lies ahead. As the building blocks of technology, SiC based semiconductors will continue to enable great breakthroughs: from aerospace and consumer electronics to energy and medicine - entire industries will be transformed. A good example for this transformation is the automotive industry. Electric vehicles have evolved from an ecological niche product to a preferred everyday alternative. This development was supported by more powerful electric drivetrains, using higher currents and more effective circuits. This is where Silicon Carbide plays a dominant role.

#### Why Silicon Carbide?

The answer is quite simple: more power, higher efficiency and better reliability at higher voltages. There is a transformation not only in the industry but also of semiconductor materials itself. To handle the increased requirements of electric devices, SiC has become the preferred substrate material for advanced semiconductors, especially for power electronics. It allows a 10x higher dielectric breakdown field strength, 15x higher breakdown voltages and offer 3x higher thermal conductivity. In addition, SiC enables higher operating temperatures (up to 400°C vs 150°C for Silicon) and has a 2–3 times higher current density.

The ability of SiC semiconductors to perform at high temperatures, voltages and power has resulted in its increased demand in multiple industries. Data centers for example use SiC for power supplies enabling substantial reduction in power required for cooling systems.

In addition, uninterruptable power supply (UPS) systems ensure a stable, consistent source of power. Another example are 5G base stations: they process an increasing amount of data resulting in a rise of power requirements. SiC semiconductors are used for MHz switching and deliver increased power at a reduced size.

### Breakthrough for electric vehicles thanks to SiC

Especially the automotive industry benefits from the advantages of SiC. Thanks to the higher efficiency of SiC semiconductors, manufacturers like Porsche were able to make the transition from 400 V to 800 V batteries. This results in faster charging times, smaller batteries and longer ranges. Other applications that benefit from SiC:

- **On-board battery charger:** Converts the external AC into DC to charge the battery and can double the power in half the size

- On-Board DC/DC Converter: Converts the on-board battery voltage into a clean ~12VDC bus to power on-board equipment

"The future of e-mobility will be shaped to a large extent by further improvements in efficiency. To achieve this, losses must be reduced above all by means of appropriate new technologies. High voltage levels such as 800 volts are just as much a part of this as very efficient semiconductors based on silicon carbide and intelligent thermal management. The Taycan already demonstrates this in part, but technological progress still offers plenty of potential for further improvements in future Porsche models."

Dr. Michael Steiner, Dr. Ing. h.c. F. Porsche AG Member of the Executive Board - Research and Development

- **Powertrain:** The inverter, electric motor, and its mechanical attachment to the driveline. Switching losses to less than 80% with 30% smaller size. Results in a smaller battery (less weight, less heat) and longer range

- Off-Board DC fast charger: Faster DC charge stations for rapid recharging

#### Challenges for the industry

As the demand over the next five years is expected to increase massively, the main challenge for the industry is not only the sheer volume of wafers required but also the changing specifications of the wafers to reflect those of silicon wafers. Tighter tolerances and specifications will push current and future manufacturing methods. Innovation will be critical to overcome these challenges. Taking a proactive approach to anticipate shifts in manufacturing technologies requires developing a deep relationship with process engineers and R&D based upon trust and know-how to develop next generation products.

SiC substrate manufacturers have the drive to improve process efficiency and reduce wafer production costs because the market is striving for power device price parity with Si based devices. Furthermore, the enormous growth in demand (production ramps, new facilities, etc.) and the navigation of global supply chain constraints amidst a surge in demand for both SiC based applications and an overall surge in demand for all types of semiconductors requires innovation in the manufacturing processes.

#### Optimizing costs from the beginning

Cost per wafer will become a driving factor when developing or optimization of a process step. Most will look to decrease process times, or cheaper consumables, thinking that will drive down the cost. As SiC is increasingly adopted in device manufacturing and moving from a R&D material to commercialization, increase in yield is where a significant improvement in cost of ownership will be achieved. Maximizing yield while minimizing rework, will increase throughput on existing processes.

A major challenge for the industry is the lack of availability of reliable partners for providing surface finishing solutions in manufacturing processes. Unproven solutions and unreliability in new vendors cause the risk of slowing or even halting production or scale-up efforts. This often leads to long lead times for consumables, tools and customer qualification which is a massive hindrance to expand production capacity. That is why consumables have an impact on the whole process. The consistency of pads, slurries and templates run-to-run and lot-to-lot is critical in this effort in optimizing yields.

### PUREON- A total process solution provider for silicon carbide wafering

Pureon has many years of experience in the

semiconductor industry and has developed proven solutions for wafer production. Pureon supports manufacturers to establish reliable and efficient processes. Pureon's semiconductor history with two decades of developing products for the SiC market, contributes to overcoming the critical manufacturing challenges.

Early engagements with customers in their roadmaps to identify bottlenecks, define resources and expectations is critical. As a consumable manufacturer with in-house wafer processing capability, Pureon is able to conduct testing and generate data with its own polishing and surface laboratories. This capability provides both Pureon with significantly shorter development cycle times and customers with representative data to mitigate risk in the testing and qualification of new products. This benefits wafer manufacturers by shortening the testing and acceptance at their sites. Pureon teams up with OEM's to run full scale tests to confirm findings. This removes the challenge of a customer having to take a tool or cell out of production to do testing and collect data to compare to current process of record.

### Optimizing current and developing new processes

A major challenge for the industry is the limited

### **Discover brilliance with Pureon**

Pureon delivers industry-leading solutions for surface finishing of high-tech materials in the most demanding applications. From abrasives through formulated products to process optimization – Pureon is the competent problem-solver. For many years the company with Swiss and North American heritage has been supplying solutions for the manufacturing of semiconductor substrates, devices, and precision optics. Pureon solutions are total, providing customers with enabling technology for the entire process range: from material or crystal slicing, lapping, polishing, device polishing and cleaning. Based on Swiss precision and many years of experience in supplying the semiconductor industry, Pureon has established total quality processes ensuring the high quality of its products – inter alia precise diamond particle sizes and ship to control practices. The company has also expanded into China and other markets, providing a global presence. Due to its diverse material and application know-how, Pureon has been at the forefront of the change in materials technology. This established Pureon's position as a reliable partner supporting the growth of the SiC wafer market and protecting customers supply chains.

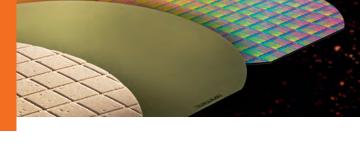

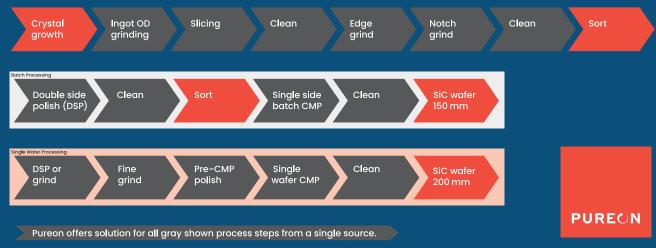

#### A General Process Flow for the Manufacture of SiC Wafers

availability of ingots and wafers, thus increasing the demand to ship anything that can be made. This has emphasized the importance of efficient and reliable production processes. However, any process change could lead to a full requalification, which could take months. Therefore, manufacturers have the drive to optimize their current production processes to benefit from lower process costs. Pureon supports this effort in supplying solutions that extend consumable lifetimes and shortening cycle times, while optimizing and improving yields.

At the same time the market requirements are changing. Hence, the industry is migrating closer to prime silicon wafer specs, requiring manufacturers to develop new processes. A good example is the move from 150 mm to 200 mm wafers, requiring completely different manufacturing flow and equipment. To realize high volume manufacturing processes for these new requirements, new manufacturing technologies are being introduced in all process steps. Pureon's focus on innovation and forward-looking development strategies are uniquely positioned to provide SiC wafer manufacturers with next-generation solutions, supporting the market's maturation through increasing productivity and reducing cost of ownership.

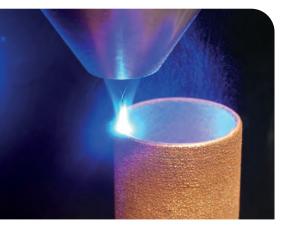

### Multi-wire saw processing of SiC ingots – secret sauce for optimum ingot slicing

To prepare SiC substrates for device fabrication one must first cut wafer blanks from the single crystal or ingot. The primary way to do this is through the use of a multi-wire saw that utilizes a thin wire moving at high speeds in combination with a diamond abrasive slurry to precisely cut wafer blanks from the SiC ingot. Major inputs to this process include speeds and feeds, type and size of wire, and the properties of the diamond abrasive slurry. The quality of the cut is judged in the responses of wafer shape, namely bow, warp and total thickness variation (TTV). Successfully cutting high quality blanks at the wire saw step is arguably the most important step of the wafer production process, as downstream improvements in wafer shape are very difficult to achieve.

Pureon provides solutions for the wire saw process in the form of the diamond abrasive slurry and close collaboration with wire saw OEMs as well as customers to optimize this process. Within the wire "As the world develops into a greener and more connected place, evolving technology is enabling this new reality. New semiconductor materials make energy conversion and transmission more efficient. Innovative optical systems transmit

exponentially growing amounts of data with ever increasing speeds. The processes used to manufacture the high-tech components and systems that are the building blocks of our future world need to evolve at the same pace. That is the reason why for us at Pureon, progress is never finished. Innovation comes with a deep understanding of polishing processes and materials. Therefore, customers across the world look at Pureon: As a leading manufacturer of diamond abrasives, slurry formulations and polishing pads, we put our in-depth expertise to work every day. Our application experts and abrasive specialists are striving to develop tailor-made polishing solutions for the SiC market, always with the needs of our customers in mind."

Martin and Daniel Spring CEOs of Pureon

saw slurry consumable space there are two types: oil-based and non-oil-based formulations. Pureon offers both oil-based (WSO) and non-oil-based (WSG) slurry solutions. Pureon proprietary chemistry and classified diamonds in the slurries provide lotto-lot consistency which translates to reproducible processes at the customers' site. Furthermore, this eliminates the need to in-house mix wire saw slurry and reduces overhead. Whether it is the first wafer or the 1000th wafer, the properties of the TTV, bow, warp and surface quality are precisely controlled. Hence improving the yield and quality of the wafers.

#### Exciting opportunities for multi-wiresaw processes

Pureon's latest advancements in wire saw slurry offerings are exhibiting exciting opportunities to improve bow, warp, and TTV compared to existing solutions, all while reducing the environmental and occupational hazards associated with traditional oil-based slurries. Recent advances in non-oil based slurry formulation designs are proving to provide excellent wafer quality. These solutions are enabling customers to produce higher quality wafers off the

| Wire Saw Slurry | Description                          | Performance* |           |  |

|-----------------|--------------------------------------|--------------|-----------|--|

|                 |                                      | TTV (μm)     | Warp (µm) |  |

| Oil-based       | Oil-based slurry                     | 4-6          | 8-15      |  |

| WSG-52          | 1st generation non-oil based slurry  | 5-7          | 8-15      |  |

| WSG-56          | Next generation non-oil based slurry | 2-4          | 5-8       |  |

> Table 1. Data collected on 25 wafers cut using 3-6 µm diamond with 160 µm straight wire.

> WSG is an advanced glycol based diamond suspension for multi wire saw slicing of SiC boules- with proprietary additives for enahnced stability of the suspension.

saw, setting their subsequent processing up for success as seen in Table 1.

### Diamond mechanical polishing of SiC wafers

The next major process in the manufacture of SiC substrates is the mechanical polishing of the wafers using a polishing slurry containing diamonds and a polishing pad. Typical processes are performed on either double side, single side or some combination of double and single side polishing tools. The output from this process step is to present a very flat and relatively low roughness wafer to the final polishing operation.

Critical inputs include the proper selection of diamond based polishing slurry and polishing pad, processing parameters such as polishing pressures, and table speeds, as well as machine selection. Of the critical inputs, the polishing slurry and pad contribute the most to a successful process optimization. Pureon has identified optimum process solutions when it comes to providing customers with maximum process performance in terms of material removal rates, wafer shape, and surface quality, by marrying the appropriate polishing pad and polishing slurry with respect to installed tooling. Pureon's extensive experience in the processing of SiC wafers via diamond mechanical polishing can be leveraged to maximize process efficiency no matter the tool set in customers facilities. Table 2 describes the DMP process flow for bulk and fine removal steps.

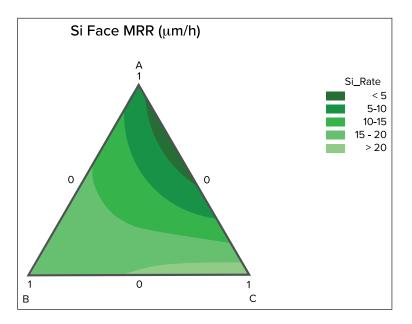

Diamond based slurry development has, over the years, been a major focal point for Pureon's innovation team. The company has identified highly optimized formulations that allow for modulation of material removal rates on the different faces of the SiC substrates. Pureon identified diamond types that work synergistically with the appropriate polishing pads and process parameters that continue to extract more performance from this process and drive efficiency gains, see for example Figure 1. Pureon sees great opportunity in driving down cost of ownership for this process step as the 150mm SiC substrate market matures in the coming years.

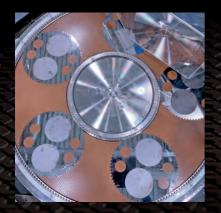

### Chemical mechanical polishing of SiC wafers

The final major process of SiC wafer production is typically referred to as the chemical mechanical polishing (CMP) step. This process step aims only to prepare the substrate surface for epitaxial growth, while imparting zero or as little as possible change to wafer shape. This is typically achieved using a highly reactive chemical based polishing slurry and a polyurethane based or a urethane impregnated felt type of polishing pad to remove only a few microns from the wafer surface. Wafers are delivered to the polishing pad and held in place via a template or wafer fixture in single-side batch tools or via vacuum chuck with a backing film in single-wafer tools. The materials used in these wafer carriers are exposed to the highly reactive chemistry of the polishing slurry, thus requiring robust tolerance to the reactive chemistry.

Pureon continues to develop advanced wafer carriers and films for use in this process to extend the service life, resulting in improved cost of ownership. Pureon has also worked closely with the industry to bring two new polishing pads for SiC CMP to the market as recently presented at the 2021 ECSCRM in Tours, France. These next generation CMP polishing pads are enabling higher productivity and increased quality from the CMP process. The formulation of final polishing slurries has been the subject of extensive research over the years, and innovation continues in this area. Therefore, it is critical for optimization to have a deep understanding of the interactions between the different consumables combinations in this process step. Pureon works closely with final CMP slurry providers to couple their technology with the optimum polishing pad, pad conditioning process

| Process Step | Process Goals                                                                         | Inputs                                                                                 | Outputs                                                                                           |

|--------------|---------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------|

| Bulk DMP     | <ul> <li>Maximize MRR</li> <li>Remove saw damage</li> <li>Improve geometry</li> </ul> | <ul> <li>As-cut wafers</li> <li>Pad &amp; Slurry</li> <li>Process</li> </ul>           | <ul> <li>Wafers near target thickness</li> <li>Appropriate geometry</li> </ul>                    |

| Fine DMP     | <ul> <li>Minimize roughness</li> <li>Reduce sub-surface damage</li> </ul>             | <ul> <li>Bulk DMP process wafers</li> <li>Pad &amp; Slurry</li> <li>Process</li> </ul> | <ul> <li>Sub 1 nm roughness</li> <li>Low surface defects</li> <li>Wafers ready for CMP</li> </ul> |

Table 2. Goals, inputs and outputs for successful DMP processes.

and wafer templates or carrier films. Advancements in final CMP polishing pad technology continue to drive increases in productivity. Pureon continues to drive innovative solutions for consumables and processes for the final polish of SiC wafers.

#### Driving into the future with Pureon

The growth of the SiC device market requires significant advancements in substrate manufacturing, both in the current state and in the development of next generation substrates. Pureon has been supporting the SiC wafering industry for almost 20 years with their knowledge, solutions, and experience in this market. Their experts continue to innovate, to improve substrate yields and lower the cost of SiC wafers, thus enabling a faster adoption of this technology. Pureon drives SiC manufacturing to new limits, enhancing all our lives. That's why innovation and pushing the limits never ends at Pureon. Learn more about their newest solution for lapping SiC wafers using the new pad IRINO-PRO-C. More details and technical presentations will be made during the ICSCRM in Davos, Switzerland, from 11 - 16 September 2022.

> Figure 1. Representative silicon face MRR ( $\mu$ m/h) response surface in a three component mixture design using 3  $\mu$ m monocrystalline diamond.

> Combined with application-tailored diamond suspensions from Pureon, IRINO-PRO-C allows for high surface qualities and impressive stock removal rates at the same time.

### Makers of epitaxial tools take the top spots

Those making MOCVD and MBE reactors have grabbed the top three places on this year's share price leaderboard

#### BY RICHARD STEVENSON, EDITOR, COMPOUND SEMICONDUCTOR

WE ARE LIVING in turbulent times. Just as we started hoping we were entering a more prosperous era, thanks to widespread roll-out of vaccines that would help us to approach normality, Putin's forces invaded Ukraine. Now bloodshed dominates our news, and we are all having to contend with far higher prices for fossil fuels.

Against this backdrop, many companies feel like boats in a storm, tossed about by forces beyond their control. Over the last few years they have had to endure the fall-out from Covid – including staff off work, working from home, and disruptions to supply lines – and the recent hike in energy bills. All are taking their toll on profitability.

These factors are also to blame for a sluggish stock market. Over the last 12 months the Dow Jones has remained broadly flat, while European and Asian shares have tended to fall in value. Caught up in this malaise are technology stocks – the NASDAQ is slightly down on where it stood a year ago – and it's of little surprise that the valuation of the majority of compound semiconductor companies has fallen over this timeframe.

However, whether it's simply a matter of being in a more sheltered place at a bad time, or being able to navigate a better path in treacherous conditions, some of the firms within our industry have not been hit as hard as others. Producers of epitaxial equipment have fared particularly well, with German MOCVD maker Aixtron seeing its share price rise by 18 percent in the last 12 months. There are times when this gain might have been good enough for a mid-table spot on our shareprice leader board, but this year it has put the German outfit in the lead by a considerable margin.

#### Aixtron accelerates

Look at the financial figures and Aixtron has good reason to claim the top spot. Sales for fiscal 2021, which is aligned with the calendar year, totalled

> Left: The AIX G5+ is said to be a state-of-the-art planetary reactor module for growing GaN-based epilayers on 150 mm and 200 mm silicon, sapphire and SiC substrates.

€420 million – that's up almost 60 percent yearover-year – while shipments hit a record €181 million in the fourth quarter. Margins are healthy and increasing, with gross margin rising from 40 percent to 42 percent year-over-year. This has helped to drive up the consolidated net profit from fiscal 2020 to 2021 by 175 percent to €94.8 million.

Soaring sales have come from shipments to chipmakers in various sectors. In fiscal 2021, revenue for MOCVD tools sold to makers of SiC and GaN power electronics doubled year-over-year, with sales to the optoelectronics and solar sectors not far behind. LED-related revenues increased by 39 percent compared with 2020.

Speaking to investors on 24 February, 2022, on the release of the fiscal 2021 results, company CEO Felix Grawert explained that for the GaN power electronics sector, Aixtron is at the start of a growth cycle that will last for several years. Behind this ramp is the increased adoption of GaN-based power switches in IT infrastructure, renewable energies, data centres and white goods. "Some customers are even telling us that their roadmaps have been pulled in by two-to-three years due to the acceleration of adoption," remarked Grawert. Within this dynamic market, Aixtron is supporting substantial expansions at existing customers and shipping tools to new players.

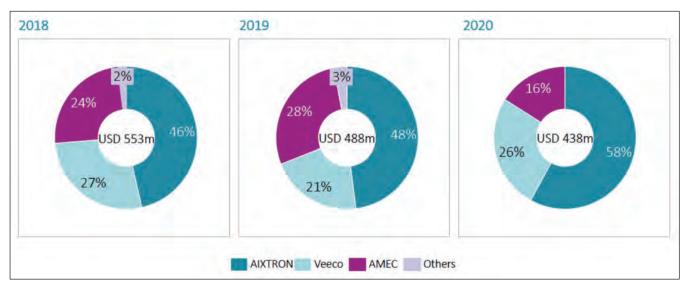

Grawert has been delighted to see a growth in orders from SiC chipmakers, which accounted for 15 percent of all equipment orders in the fourth quarter. Based on the order pipeline, further growth is expected, supported by a new tool that accommodates 6-inch and 8-inch wafers. "Even though it is still in development, we are already receiving sizeable orders for it," remarked Grawert. Aixtron continues to play a key role within the LED market. While the microLED sector grabs the headlines, sales are also strong for MOCVD reactors for red, orange and yellow LEDs that are deployed in fine-pitch displays and horticulture applications, such as indoor farming.