# CONCOMPOSITION CONTRACTOR CONTRAC

Volume 26 Issue 8 NOVEMBER / DECEMBER 2020

🔰 @compoundsemi

www.compoundsemiconductor.net

## Flying high with concentrating PV

## Evaluating new switching technologies

## Lasers speed visible light communication

#### Ditching LEDs to focus on power electronics

## Super-fast optical interconnects

**INSIGE** News Review, News Analysis, Features, Research Review, and much more... Free Weekly E News round up go to: www.compoundsemiconductor.net

# Best performance for next generation SiC power electronics to address global mega trends

# AIX G5 WW C

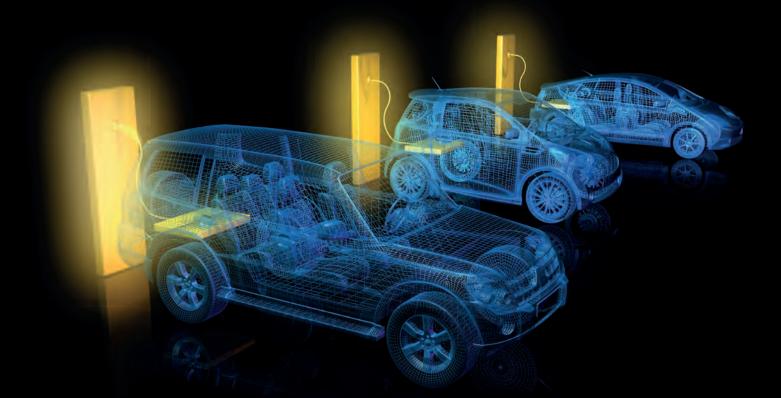

- Electric vehicles: on board chargers, power inverters

- Infrastructure: charging stations

- Renewables: solar and wind

- Industrial: motor drives, power supplies

- Power distribution: HVDC

Discover our SiC epi production batch tool with single wafer performance

info@aixtron.com www.aixtron.com

# Viewpoint

By Dr Richard Stevenson, Editor

## To space and back ... and out again

IS LIFE ON EARTH deriving much benefit from all the cash poured into numerous space programmes? It's fair to say that space blankets, freeze-dried food and space-aged swimsuits are hardly important breakthroughs in the history of mankind. But there has been a significant pay-off in the form of the silicon solar cell, which is now making a significant contribution to cutting carbon dioxide emissions on this planet.

The silicon solar cell is no longer used by satellite designers. Cells accommodating III-Vs are now the established incumbent, thanks to their combination of higher efficiencies and a greater robustness to radiation.

While the higher efficiencies of III-Vs are valued on earth, their price is far too high to make an impact. Even when lenses or mirrors concentrate sunlight several hundred times to trim power generation costs – a neat solution that also boosts efficiency – commercial success has not followed. Interest in this approach did take-off a decade or so ago, but a credit crunch and tumbling silicon prices pulled the rug from under this nascent industry.

In an interesting turn of events, this concentrating technology could now have a future in space.

Miniaturisation is making this move viable. That is realised by transfer-printing thousands of tiny multi-junction cells to a backplane and adding a vast array of radiation-hardened glass

lenses, used to protect these chips while focusing the sunlight.

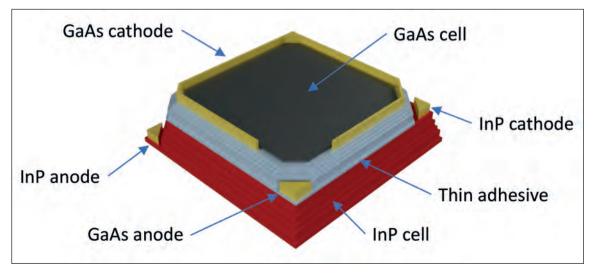

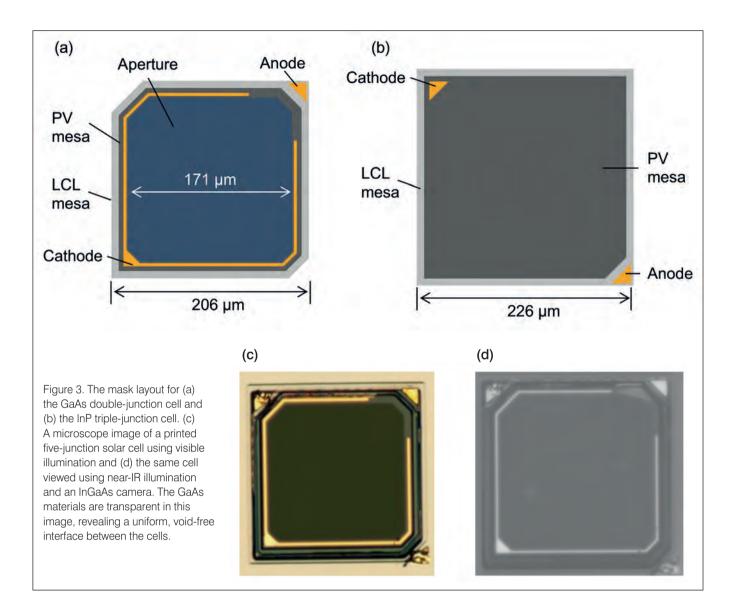

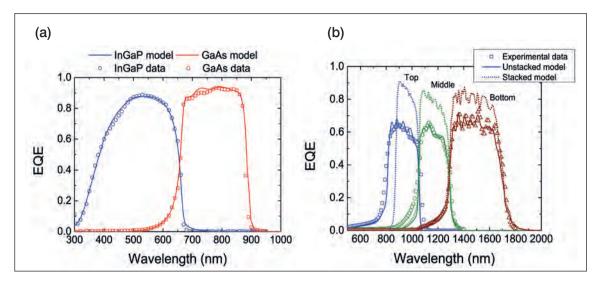

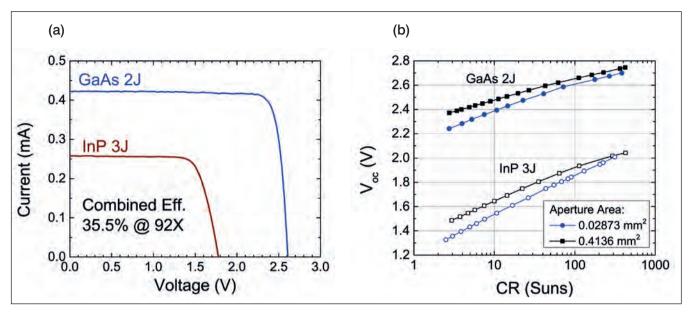

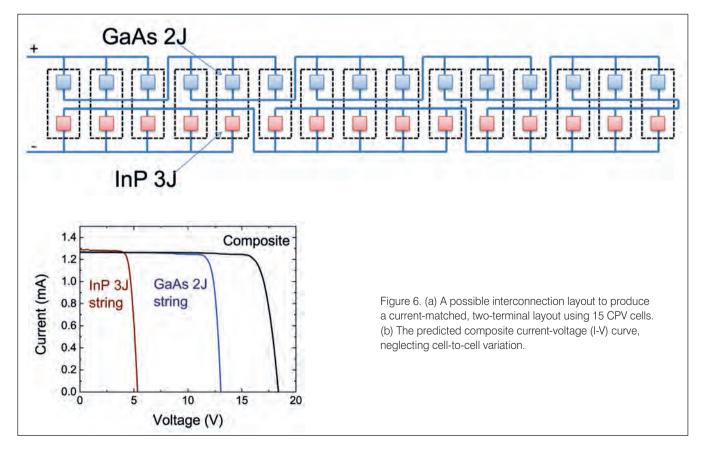

Trailblazing this design is US collaboration involving engineers from industry and academia. In this team's design, power is generated from a five-junction cell, created by stacking a triple-junction device based on InP and its associated alloys to a dual-junction device made from InGaP and GaAs (see *Flying High with CPV*, starting on p. 48 for details). To maximise the power, devices are strung together in different configurations to enable the current from both types of material to match. The latest results demonstrate an efficiency in excess of 35 percent, and there is a clear pathway to 38 percent, a figure that surely gives a technology developed for power generation on earth a chance of significant success in space.

| Editor Richard Stevenson                                              | richardstevenson@angelbc.com                       | +44 (0)1291 629640 | Circulation Director Scott Adams                                 | scott.adams@angelbc.com                 | +44 (0)2476 718970                                              |

|-----------------------------------------------------------------------|----------------------------------------------------|--------------------|------------------------------------------------------------------|-----------------------------------------|-----------------------------------------------------------------|

| Contributing Editor Rebecca Pool<br>News Editor Christine Evans-Pughe | editorial@rebeccapool.com<br>chrise-p@dircon.co.uk |                    | Chairman Stephen Whitehurst                                      | stephen.whitehurst@angelbc.cc           | m +44 (0)2476 718970                                            |

| Sales Executive Jessica Harrison                                      | jessica.harrison@angelbc.com                       | +44 (0)2476 718970 | Chief Executive Officer Sukhi Bhadal                             | sukhi.bhadal@angelbc.com                | +44 (0)2476 718970                                              |

| USA Representatives Brun Media                                        |                                                    |                    | Chief Technical Officer Scott Adams                              | scott.adams@angelbc.com                 | +44 (0)2476 718970                                              |

| Tom Brun                                                              | tbrun@brunmedia.com                                | +001 724 539-2404  | Directors Jackie Cannon, Sharon Cowley                           |                                         |                                                                 |

| Janice Jenkins                                                        | jjenkins@brunmedia.com                             | +001 724-929-3550  | Published by Angel Business Communication                        | ons Ltd, Unit 6, Bow Court, Fletchworth | n Gate, Burnsall Road,                                          |

| Publisher Jackie Cannon                                               | jackie.cannon@angelbc.com                          | +44 (0)1923 690205 | Coventry CV5 6SP, UK. T: +44 (0)2476 718 970 E: info@angelbc.com |                                         |                                                                 |

| Director of Logistics Sharon Cowley                                   | sharon.cowley@angelbc.com                          | +44 (0)1923 690200 |                                                                  |                                         |                                                                 |

| Design & Production Manager Mitch Gaynor                              | mitch.gaynor@angelbc.com                           | +44 (0)1923 690214 |                                                                  |                                         | When you have finished with<br>this magazine please recycle it. |

Compound Semiconductor is published eight times a year on a controlled circulation basis. Non-qualifying individuals can subscribe at: £105.00/e158 pa (UK & Europe), £138.00 pa (air mail), \$198 pa (USA). Cover price £4.50. All information herein is believed to be correct at time of going to press. The publisher does not accept responsibility for any errors and omissions. The views expressed in this publication are not necessarily those of the publisher. Every effort has been made to obtain copyright permission for the material contained in this publication. Angel Business Communications Ltd will be happy to acknowledge any copyright oversights in a subsequent issue of the publication. Angel Business Communications Ltd © Copyright 2020. All rights reserved. Contents may not be reproduced in whole or part without the written consent of the publishers. The paper used within this magazine is produced by chain of custody certified manufacturers, guaranteeing sustainable sourcing. US mailing information: Compound Semiconductor, ISSN 1096-598X, is published 8 times a year, Jan/Feb, March, April/May, June, July, August/September, October, November/ December by Angel Business Communications Ltd, Unit 6, Bow Court, Fletchworth Gate, Burnsall Rd, Coventry CV5 GSP. UK. The 2020 US annual subscription price is \$198. Airfreight and mailing in the USA by agent named World Container Inc, 150-15, 183rd Street, Jamaica, NY 11413, USA. Periodicals postage paid at Brooklyn, NY 11256. US Postmaster: Send address changes to Compound Semiconductor, Air Business Ltd, c/o WN Shipping USA, 156-15, 146th Avenue, 2nd Floor, Jamaica, NY 11434, USA. Printed by: The Manson Group. ISN 1096-598X (Print) ISSN 2042-7328 (Online) © Copyright 2020.

We strive for accuracy in all we publish; readers and contributors are encouraged to contact us if they recognise an error or omission. Once a magazine edition is published [online, in print or both], we do not update previously published articles to align old company names, branding, marketing efforts, taglines, mission statements or other promotional verbiage, im-ages, or logos to newly created or updated names, images, typographic renderings, logos (or similar) when such references/images were accurately stated, rendered or displayed at the time of the original publication. When companies change their names or the images/lext used to represent the company, we invite organizations to provide Angel Business Communic-actions with a news release detailing their new business objectives and/or other changes that could impact how customers/prospects might recognise the company, contact the organisa-tion, or engage with them for future commercial enterprise.

# CONTENTS

## 18 COVER STORY Scrutinising GaN HEMTs by quantitative cathodoluminescence

Quantitative cathodoluminescence aids development and production of GaN HEMTs by delivering nondestructive measurements for threading dislocations, composition, and doping

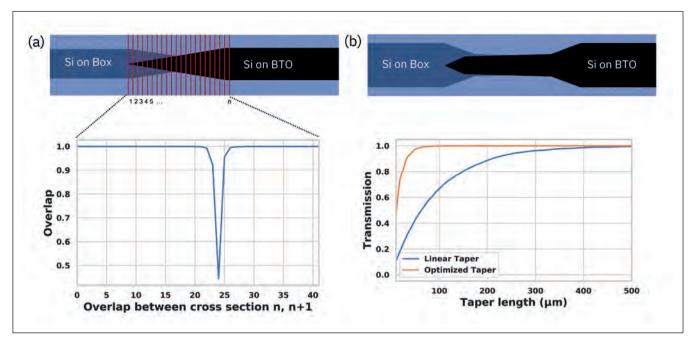

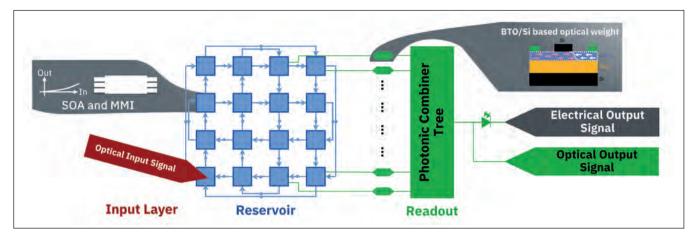

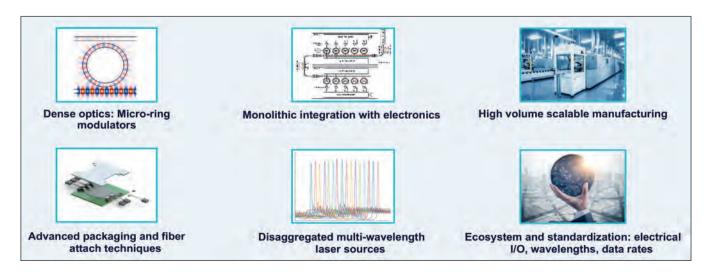

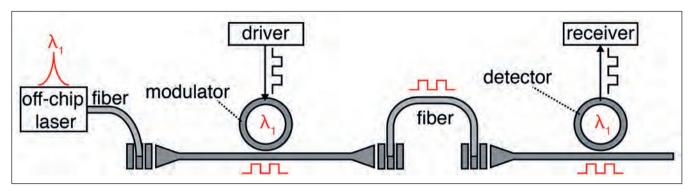

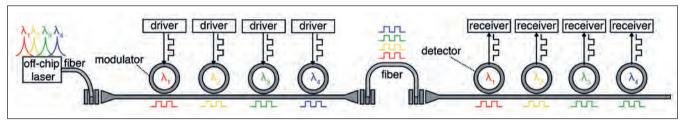

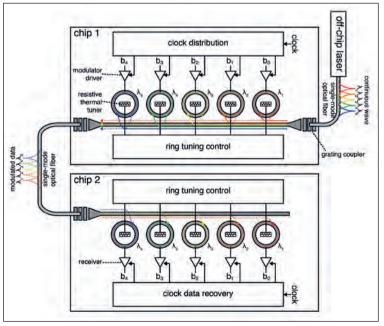

## 26 Enhancing silicon photonics with III-Vs and barium titanate

Heterogeneous co-integration of barium titanate and III-V semiconductors on a silicon photonics platform enables efficient optical transceivers and novel neuromorphic devices

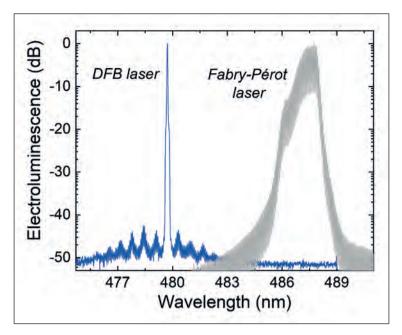

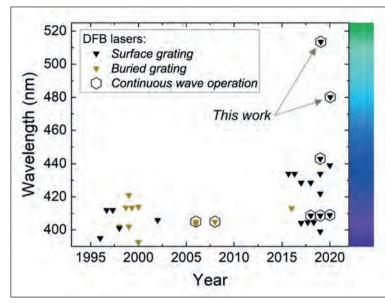

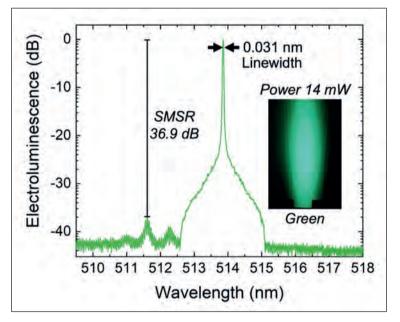

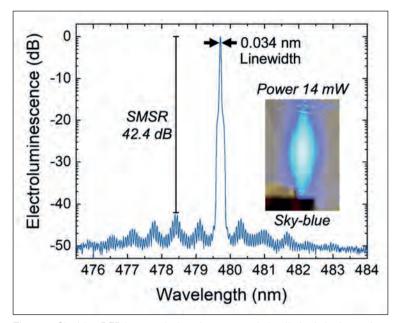

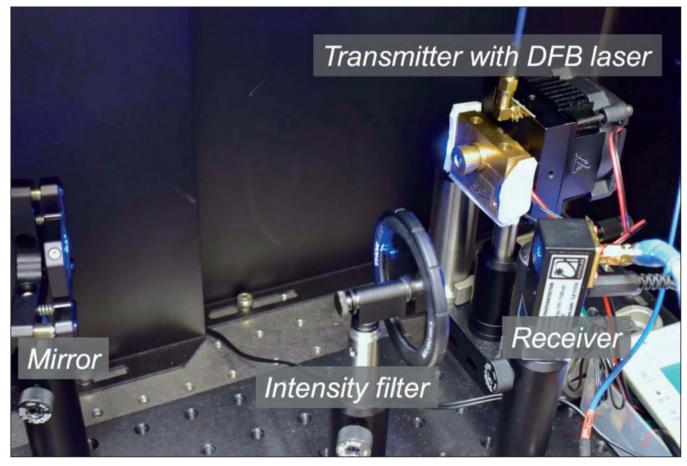

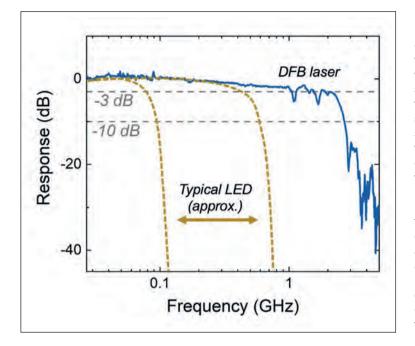

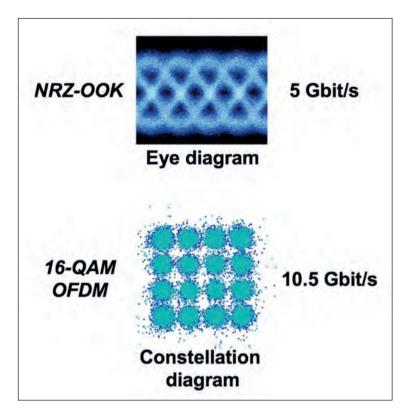

# 34 Lasers: Accelerating visible light communication

GaN-based single-mode lasers get ready to revolutionise communication

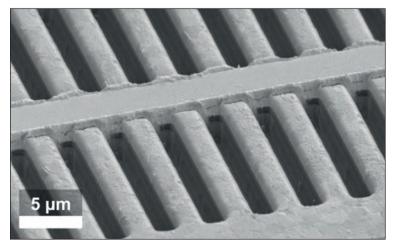

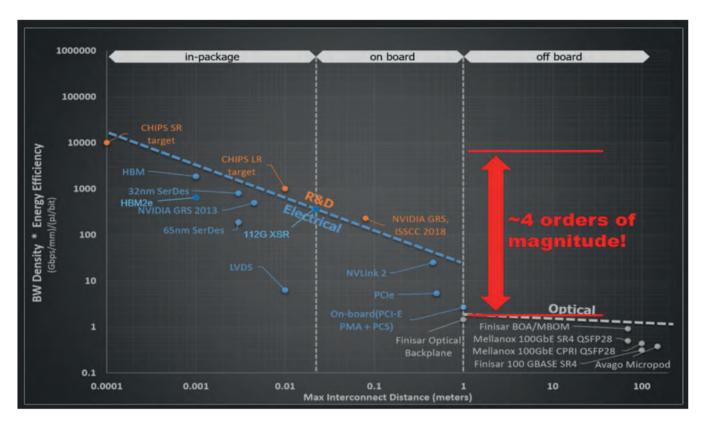

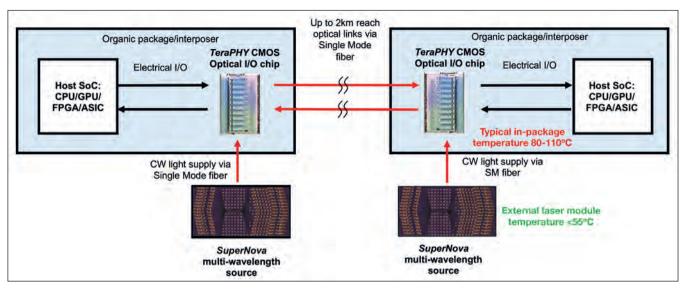

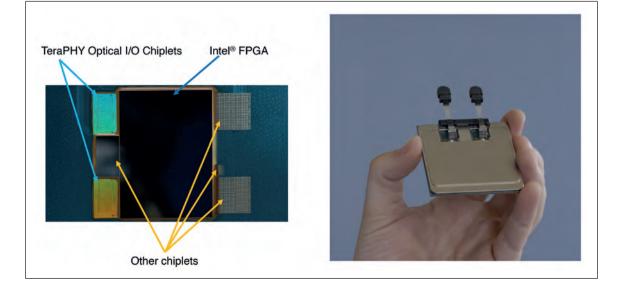

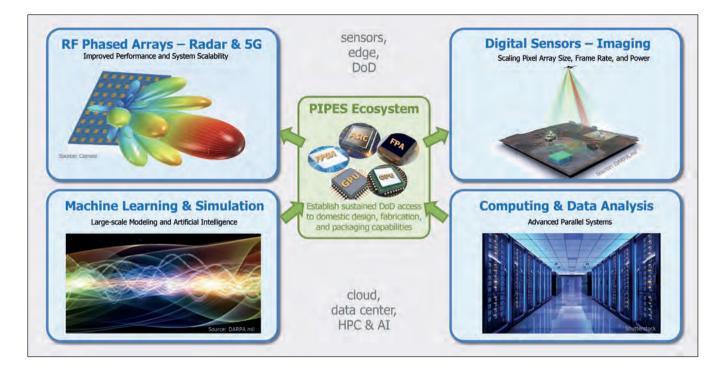

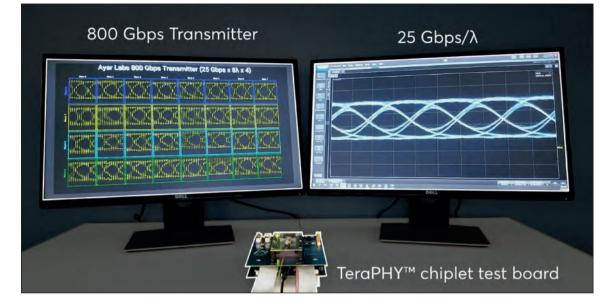

# 40 Super-fast optical interconnects

Universal chip-to-chip optical interconnects are delivering off-package communication at the bandwidth density and energy cost of in-package electrical incumbents

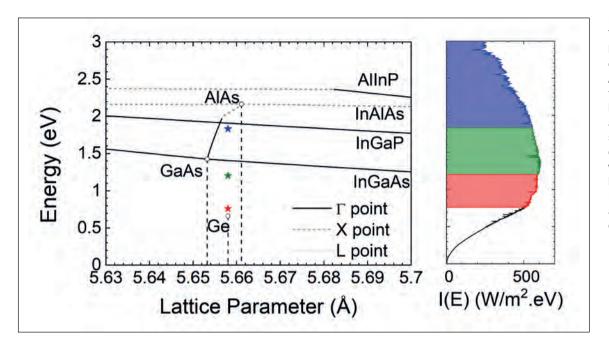

## 48 Flying high with CPV

Operating at almost 100 suns, vast arrays of five-junction micro-concentrator cells promise to set a new benchmark for extra-terrestrial power

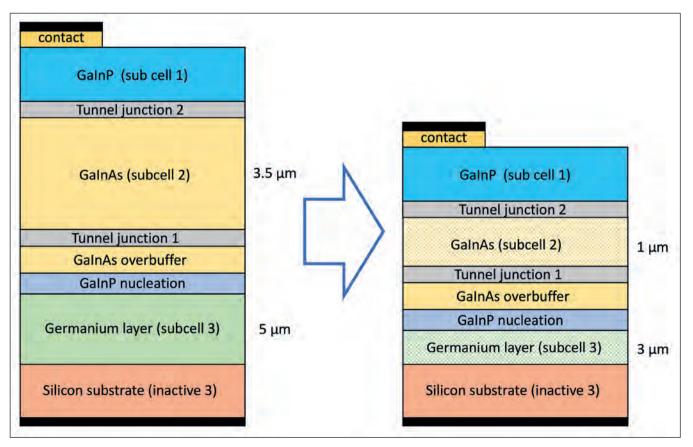

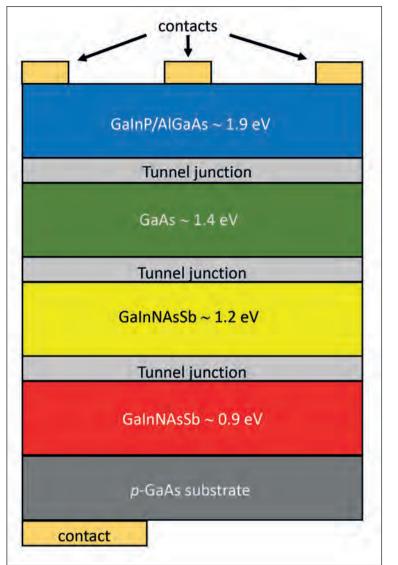

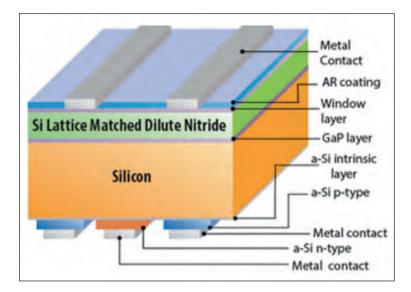

## 56 Building better solar cells

Better-performing solar cells result from the introduction of dilute nitrides, novel separation layers and germanium-on-silicon templates

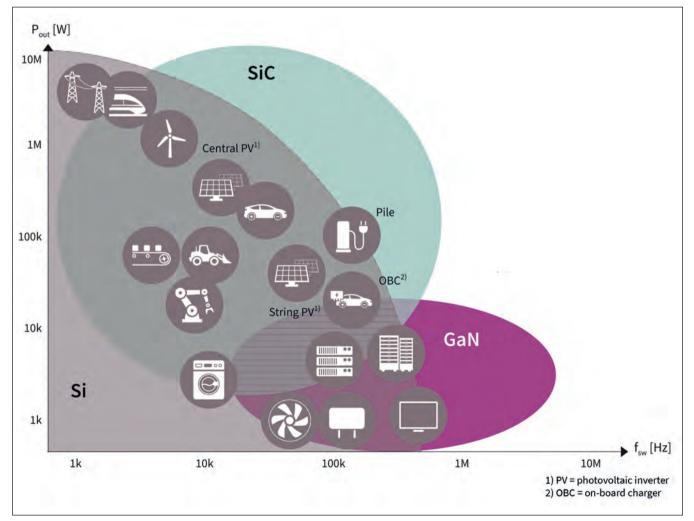

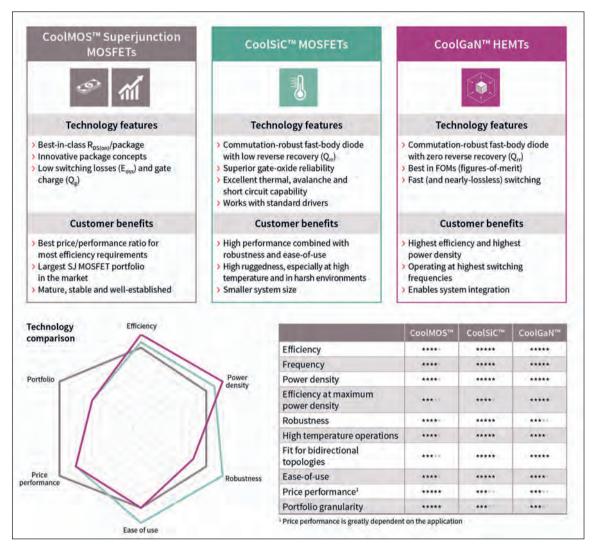

# 60 Evaluating new switching technologies

It takes more than a change in part number to move to a wide bandgap technology; what's required is a systemic approach, considering all aspects of design

#### NEWS

- 06 IQE develops path for VCSEL growth on silicon

- 07 Transphorm releases high-voltage GaN reliability data

- 08 Mitsubishi to launch 4-terminal 1200 V SiC MOSFETs

- 10 Qorvo to build RF semiconductor packaging centre

- 1 IQE announces technology for RF filters

- 12 MicroLED chip revenue to reach \$2.3 billion in 2024

- 13 AngelTech Virtual 2 proves a hit

- 14 'Topping off' ceremony at Cree/Wolfspeed's SiC fab

## NEWS ANALYSIS

#### 16 Cree: Stepping out of the light

As Cree exits the LED industry, its chief executive Gregg Lowe tells *Compound Semiconductor* what will come next

## RESEARCH REVIEW

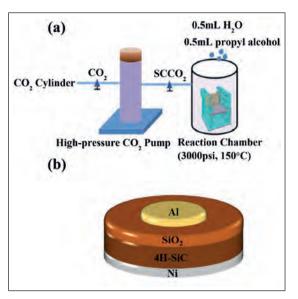

66 Supercritical carbon dioxide spawns superior MOSFETs

A low-temperature treatment with supercritical  $CO_2$  improves the interface between SiC and SiO<sub>2</sub>

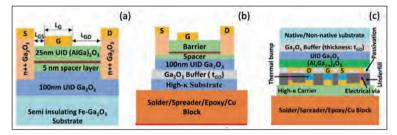

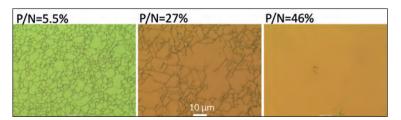

### 67 Building better Ga<sub>2</sub>O<sub>3</sub> transistors

Wrapping modulation-doped Ga<sub>2</sub>O<sub>3</sub> FETs in highly conductive materials addresses concerns related to thermal management and carrier transport

# 68 AIPN enlarges the nitride family

Growth of AIPN epilayers promises better HEMTs and VCSELs

## IQE develops path for VCSEL growth on silicon

WAFER PRODUCTS firm IQE has announced the successful development of its IQGeVCSEL 150 technology for 6-inch VCSELs on germanium, a critical step in the pathway to 200 mm and 300 mm VCSEL technology.

VCSELs are a key component in telecom and 3D sensing systems. Applications include high-speed data centre infrastructure; facial recognition, proximity sensing and LiDAR time-of-flight sensors on mobile handsets; in-cabin and environmental sensing for autonomous drive vehicles; and 3D image recognition.

As demand for VCSELs grows and technical requirements become more stringent, there is the need to scale to larger wafer diameters and demonstrate a path for integration with CMOS technology.

IQGeVCSEL 150 is a key development milestone in addressing this. Germanium substrates are readily available in diameters up to 200 mm and provide a clear route for VCSEL growth on silicon

substrates (through the use of IQE's world-leading germanium-on-silicon templates) up to 300 mm.

Using this unique, patent pending technology, IQE has demonstrated device performance parity between identical VCSEL structures grown on germanium and conventional GaAs. While the conventional growth of VCSELs on 200 mm GaAs substrates is currently virtually impossible, the use of germanium removes this limitation. This is because germanium substrates allow for optimal strain management, resulting in a VCSEL wafer that is ten times flatter compared to VCSEL on GaAs.

This not only simplifies the subsequent wafer fabrication process but results in a wafer that is up to three times more uniform. The improved wafer flatness provides additional design flexibility for thicker device architectures required to access longer-wavelength VCSELs. Finally, the germanium substrates are available with zero defect density, resulting in higher quality VCSEL epi-material compared with GaAs.

Rodney Pelzel, CTO of IQE, commented: "I am delighted to announce the successful development of IQGeVCSEL 150 technology. Demonstrating device parity with GaAs but with a more uniform VCSEL wafer and improved flatness is a highly significant milestone, and we have begun sampling with partners and customers. In addition, this provides clear line-of-sight to growth on larger diameter wafers as well as VCSEL growth on silicon at 200 mm and 300 mm wafer sizes."

## University of Glasgow spin-out to make revolutionary lasers

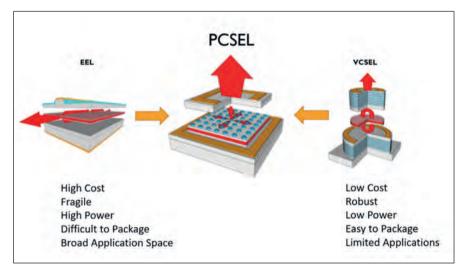

VECTOR PHOTONICS, a University of Glasgow spin-out, has announced it will commercialise its photonic crystal surface-emitting lasers (PCSELs), which it describes as the most significant innovation in laser design and manufacture for 30 years.

Vector Photonics CEO, Neil Martin, said: "PCSELs are low cost, robust, have a broad wavelength range and high power. This combination of key characteristics gives them a huge advantage over most of the laser technologies used today.

According to Martin, this includes VCSELs, which are robust, but compromise wavelength range and power, and EEL's (edge-emitting lasers), which have broad wavelength range, but are expensive to make and are fragile to handle.

"PCSELs emit light from their top surface, like VCSELs, making them easy to package and incorporate into PCBs

and electronic assemblies. They are also produced in a similar way to EELs, allowing us to draw on existing supply chain expertise and capacity as we grow."

The Vector Photonics' commercial team, comprising Neil Martin and Euan Livingston, has detailed knowledge of the entire photonics supply chain. The technical team includes the inventors of the all-semiconductor PCSEL technology, Richard Taylor, David Childs and Richard Hogg.

Vector Photonics' initial focus is hyperscale data centre applications, however, PCSEL technology brings critical, new functionality to LiDAR, mobile consumer, biometric and sensing markets.

## Transphorm releases high-voltage GaN reliability data

TRANSPHORM, a supplier of high-reliability, high-performance GaN power conversion products, has released updated information regarding its GaN technology's quality and reliability.

Currently, Transphorm's GaN platform offers a FIT rate of less than 1 failure per billion hours in real-world applications – indicating very high reliability. The FIT calculation is based on more than 10 billion field hours of operation accumulated from an install base of approximately 250 MW.

Transphorm's devices are in use today across a wide range of applications spanning 65 W to 3 kW. Examples include universal, fast-charging adapters for smartphones and laptops; rugged, broad industrial power modules; and 1.5 to 3.0 kW Titanium class data centre power supplies, which meet the high power efficiency ecodesign requirements mandated by The European Parliament and The Council (ErP: Directive 2009/125/EC).

SiC power devices are an alternative power conversion solution and in a later stage of maturation than power GaN solutions. Although SiC offers more than a trillion hours of field operation compared to Transphorm GaN's 10 billion hours due to being commercially available longer, recent reports indicate that SiC's field failure

FIT rate is 4.1. This illustrates the high field reliability achieved to date by Transphorm's GaN with a FIT of less than 1.

Extrinsic reliability, also referred to as early life failure (ELF) or infant mortality, is determined via in-house manufacturer analysis – identifying material, design, and process control defects that may cause parts to fail. Alternatively, field failure measures the number of devices that fail in customer systems in production in relation to the total number of parts sold.

When assessing FIT rate, the above two metrics – ELF and field failure – are studied. The convergence of these two rates means a semiconductor manufacturer's internal reliability assessments are accurate; a customer can have confidence in that reported level of device performance.

In January 2019, Transphorm announced a field failure FIT of 3.1. Later in 2019, the

field failure FIT decreased to 2.2. And now Transphorm's field failure FIT of less than 1 aligns closer to its current ELF FIT rate of 0.61.

For customers, knowing the ELF statistics of a technology is essential to controlling warranty claims. Transphorm follows the standard industry practice as defined in JEDEC's JESD74A

standard for measuring its early life failure rate. Ensuring conservative results, Transphorm tests its devices to their maximum spike rating at an appropriate use temperature of 85 °C. Despite JEDEC qualification requiring early life failure rate testing, only silicon device manufacturers commonly report it – most GaN and SiC power electronics manufacturers do not.

"To the best of our knowledge, Transphorm is currently the only high voltage GaN semiconductor company to report ELF," said Ron Barr, VP of Quality and Reliability, Transphorm. "We understand that customers require certain information when comparing wide bandgap technologies. So, we aim for transparency here. And accuracy, as we frequently see reliability data being calculated differently or manipulated in uncommon ways yet being reported as the same metric type. Given this trend, our education efforts are focused heavily on explaining the proper methods that must be used to prove business-critical metrics and why."

#### Advanced Compound Semiconductor Foundry Services

MOCVD · Fabrication · Testing

Advanced III-V semiconductor solutions for optoelectronics application in the biotechnology, telecommunications, energy, industrial, and defense industries.

MasimoSemiconductor.com | 603-595-8900

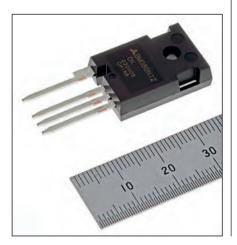

## Mitsubishi to launch 4-terminal 1200 V SiC MOSFETs

MITSUBISHI ELECTRIC has announced the coming launch of a new series of SiC MOSFETs, the N-series of 1200 V devices in a TO-247-4 package, which achieves 30 percent less switching loss compared with the existing TO-247-3 package products.

According to the company, the new series will help to reduce the power consumption and physical size of powersupply systems requiring high-voltage conversion, such as electric vehicle on-board chargers and photovoltaic power systems. Sample shipments will start this November.

The new series devices come in a four-pin package to help reduce power consumption and physical size of power-supply systems. They feature a figure of merit (FOM3) of 1,450 m $\Omega$ -nC and high self-turn-on tolerance. The TO-247-4 package is equipped with an independent driver source terminal as well as a conventional 3-pin package.

The four-pin package is said to help reduce parasitic inductance, a problem in high-speed switching. Eliminating gate-source voltage drops due to current variations helps to reduce switching loss by approximately 30 percent compared with TO-247-3 products.

Using a higher carrier frequency to drive the new power semiconductors helps reduce switching-power loss, enabling smaller, simpler cooling systems as well as smaller reactors and other peripheral components, thereby helping to reduce the

power consumption and physical size of overall power-supply systems.

There will be six models for a variety of applications including models compatible with Automotive Electronics Council's AEC-Q101 standards for use not only in industrial applications, such as photovoltaic systems, but also EV applications. Creepage distance (shortest distance over surface between two conductive parts) between drain terminal and source terminal has been made wider than in TO-247-3 package products for more flexible application, including in outdoor installations where dust and dirt easily accumulate.

The global leader in wafer outsourcing

World leading technology

Complete materials range

MOCVD, MBE & CVD platforms

Advanced substrates

Multiple, manufacturing sites (Europe, Asia, USA)

Advanced R&D facilities

## **Enabling advanced technologies**

Offering the Industry's Broadest Product Portfolio

# Qorvo to build RF semiconductor packaging centre

QORVO, a US provider of RF semiconductors, has been selected by the US government to create a stateof-the-art heterogeneous integrated packaging (SHIP) RF production and prototyping centre.

The SHIP programme will ensure that microelectronics packaging expertise and leadership is available for both US defence contractors and commercial clients that require design, validation, assembly, test and manufacturing of next-generation RF components.

The exclusive SHIP Other Transaction Agreement (OTA), worth up to \$75 million, was awarded to Qorvo by the Naval Surface Warfare centre (NSWC), Crane Division. This program is funded by the Office of the undersecretary of defence for Research and Engineering's Trusted and Assured Microelectronics Program (T&AM), and is administered by the Strategic & Spectrum Missions Advanced Resilient Trusted System (S<sup>2</sup>MARTS) Other Transaction Agreement (OTA), managed by National Security Technology Accelerator (NSTXL).

Under the SHIP programme, Qorvo will design and deliver the highest levels of heterogeneous packaging integration. This is essential to meet the size, weight, power and cost (SWAP-C) requirements for next-generation phased array radar systems, unmanned vehicles, electronic warfare platforms and satellite communications.

James Klein, president of Qorvo Infrastructure and Defence Products, said, "We are honoured to be selected to establish state-of-the-art RF packaging capability for the US Department of defence (DoD). This award reflects Qorvo's proven track record as a global leader in RF technology with over 35 years of experience. As part of this collaboration, Qorvo will expand its proven capabilities in Texas to create a SOTA facility that best serves the needs of the US government and commercial customers."

Qorvo's US-based capabilities include manufacturing, packaging and testing for both high- and low-power applications ranging from DC to 100 GHz.

Qorvo holds a defence Microelectronics Activity (DMEA) Category 1A trusted source certification for package assembly, test and wafer foundry services at its Richardson, TX location.

## Infineon expands SiC supply base with GTAT

INFINEON TECHNOLOGIES AG and GT Advanced Technologies (GTAT) have signed a supply agreement for SiC boules. The contract has an initial term of five years. With this supply contract, the German semiconductor manufacturer adds a further element to secure its growing base material demand in this area.

Under the brand name CoolSiC, Infineon now already markets a large product portfolio for industrial applications and is rapidly expanding its offerings towards consumer and automotive products.

"We are seeing a steadily increasing demand for SiC-based switches, especially for industrial applications," says Peter Wawer (pictured right), president of Infineon's Industrial Power Control Division. "However, it has become clear that the automotive sector is quickly following suit. With the supply agreement we have now concluded, we ensure that we will be able to meet the rapidly growing demand of our customers with a diversified supplier base."

GTAT's high-quality boules will provide an additional source for competitive SiC. This supports Infineon's ambitious SiC growth plans, making good use of its existing in-house technologies and core competencies in thin-wafer manufacturing.

"We are very excited to enter into a long-term supply agreement with Infineon," says Greg Knight, president and CEO of GT Advanced Technologies.

"GTAT will enable Infineon to achieve a secure high-quality internal SiC wafer supply by applying their proprietary thin-wafer technology to GTAT's crystal. The growth of SiC device adoption is tied largely to the aggressive cost down of the substrate, and this agreement is a significant step towards achieving that goal."

SiC has mainly been used up to now in photovoltaic

inverters, industrial power supplies, and the charging infrastructure for electric vehicles. This is where the advantages of SiC at the system level, compared to classical silicon solutions, have already come into play.

Other industrial applications such as uninterruptible power supplies and variable-speed drives are increasingly making use of the new semiconductor technology. In addition, electric vehicles show enormous potential for application options, including the main inverters for the drive train and on-board battery charging units.

## IQE announces technology for RF filters

IQE, a manufacturer of advanced semiconductor wafer products, has announced the successful development of its IQepiMo template technology for RF filters and for any application requiring low-resistance buried electrodes.

Built on its cREO technology platform, IQepiMo templates are available in diameters of up to 200 mm and trials are underway with potential customers and partners.

The cREO platform provides a buffer layer to integrate GaAs, InP, GaN and other compound semiconductors with silicon, allowing the potential of producing compound semiconductor epitaxial layers on lower-cost silicon wafers up to 300 mm diameter and opening up the possibility of integrating CS performance and functionality with existing CMOS processing capabilities for true next-generation system-on-chip devices.

Low-resistance contacts are essential for the efficient operation of almost all electronic circuits. As dimensions shrink, the limitations of existing technologies are exposed, resulting in compromised device performance.

This is especially true of RF filters, which are electronic components that allow or prevent the transmission of selected signals or frequencies. As 5G technology

rolls out worldwide, the requirements for RF devices are becoming significantly more demanding.

For RF bulk acoustic wave (BAW) filters, the higher frequencies of 5G translate into an electrical penalty for thinner electrodes that must be accommodated. IQepiMo eliminates this electrical penalty by providing bulk-like metal resistance for very thin layers (down to 50 nm).

In addition, IQepiMo templates enable higher quality piezoelectric layers to be fabricated from customers' current processes, offering a clear path for improved quality AIN piezoelectric materials. As such, IQepiMo extends the capability of existing customer processes for next generation applications.

Rodney Pelzel, CTO of IQE, commented: "I am pleased to announce the successful development of IQepiMo templates based on IQE's patented cREO technology. These templates will mean that customers, while using their existing processes, can fabricate higher quality, better performing BAW filters and eliminate the electrical penalty that had until now been inherent in the application of current technology to higher frequencies."

## MicroLED chip revenue to reach \$2.3 billion in 2024

SINCE THE INTRODUCTION of Sony's large-sized modular microLED display in 2017, other companies, including Samsung and LG, have successively made advances in microLED development, in turn generating much buzz for the technology's potential in the large-sized display market, according to TrendForce.

Emissive microLED TVs are expected to arrive on the market between 2021 and 2022. Even so, many technological and cost-related challenges are yet to be solved, meaning microLED TVs will remain ultra-high-end luxury products at least during the technology's initial stage of commercialisation.

TrendForce indicates that microLED technology will likely first enter the market in several applications, including small-sized head-mounted AR devices, wearables such as smartwatches, highmargin products such as automotive displays, and niche products such as high-end TVs and large-sized commercial displays.

After this initial wave of products, microLED technology will subsequently see gradual integration in mid-sized tablets, notebook computers, and desktop monitors. In particular, microLED will see the highest potential for growth in the large-sized display market, mainly since these products have a relatively low technological barrier.

MicroLED chip revenue, driven primarily by TV and large-sized display integration, is expected to reach \$2.3 billion in 2024.

Taiwanese and Korean manufacturers are working to overcome technological roadblocks. At the present stage, the vast majority of microLED TVs and large-sized displays features a traditional LED architecture of RGB LED chip packages paired with passive matrix (PM) drivers. Not only is PM costly to implement, but it is also limited in terms of how far the pixel pitch of the display can be decreased, making microLED technology viable for only commercial displays currently.

However, various panel manufacturers and display brands have in recent years

developed their own active matrix (AM) solutions, which make use of an active pixel addressing scheme and feature TFT glass backplanes.

Furthermore, the IC design for AM, compared to PM, is relatively simpler, meaning AM requires less physical space for routing. All of these advantages make AM the more suitable solution for highresolution microLED TVs.

Korean companies (Samsung/LG), Taiwanese companies (Innolux/AUO), and Chinese companies (Tianma/CSOT) have all currently demonstrated their respective AM display applications. With regards to the LED light source, Samsung has partnered with Taiwanbased PlayNitride to create a full-colour microLED display manufactured using semi-mass transfer of RGB LED chips.

This process differs from the traditional method of LED display manufacturing, which utilises RGB LED chip packaging technology instead. Conversely, Taiwanbased panel manufacturers AUO and Innolux have pioneered a colour rendering technology that combines blue-light LED chips with quantum dots or LED phosphors.

On the other hand, the cost of microLED displays depends on the display

resolution and chip size. As users demand higher resolution displays going forward, microLED chip consumption will also skyrocket. TVs and LED displays in particular will far dwarf other applications in microLED chip consumption. For instance, a 75-inch 4K display requires at least 24 million RGB microLED chips for its subpixel array.

Therefore, the manufacturing cost, which includes technologies such as semi-mass transfer, and material cost of microLED chips will remain sky-high for the time being.

In light of this, TrendForce believes that technological and cost-related issues will remain the greatest challenge to the market availability of microLED TVs and large-sized microLED displays.

As TVs trend toward large sizes and high resolutions in the future, manufacturers must confront increasing difficulties in microLED technologies, including mass transfer, backplanes, drivers, chips, and inspection and repair.

Once these technological bottlenecks have been overcome, whether the cost of microLED manufacturing will undergo a corresponding, rapid drop will then determine microLED's viability as a mainstream display technology.

# AngelTech Virtual 2 proves a hit

OVER 1700 DELEGATES took the opportunity to watch, listen and learn as a host of industry luminaries provided some great insight into the latest developments in the compound semiconductor and specialised photonic integrated circuit technology sectors. Angel Business Communications CEO and Event Organiser, Sukhi Bhadal, was delighted with the second AngelTech event, as it brought together the research, vendor and end-user communities for some valuable education and networking opportunities.

"Following on from the continued disruption the Covid-19 pandemic has caused to the events industry, we were disappointed when we had to twice postpone physical Brussels event in March and then again in November. We have been delighted with the continued support the compound semiconductor and photonic integrated circuits community has given us. The second AngelTech event was a fantastic success with over 1700 delegates registered, 25 sponsors signed up and some inspirational speakers. The event, held on our own virtual event platform 'Connect', allowed us to keep the community connected, learning and developing business."

There is a significant overlap between the PIC and the compound semiconductor industry. Some photonic circuits are formed from InP, while others, such as those made from silicon or polymers, depend on III-Vs for the light source. Due to this close working relationship, the CS and PIC summits kicked off with a shared session that included some of the ways that III-Vs play a role in photonic circuits.

One talk by Geza Kurczwell from Hewlett Packard Enterprise focused on this theme, outlining how quantum dots could aid internal communication in supercomputers, while presentations from analysts at Yole Développement and Strategy Analytics detailed the promising outlook for the PIC industry, which has opportunities in many sectors.

This year the compound semiconductor industry has grabbed the headlines in the mainstream press for the role UV LEDs can play in combatting the Covid-19 epidemic. Detailing this opportunity, along with

several others, Jennifer Pagan from Aquisense Technologies described how UV LEDs can assist healthcare. While the performance of this device lags behind its light-emitting cousin, Haiding Sun from the University of Science and Technology China, outlined several novel architectures that could help it to catch up.

Advances in visible LEDs continue. The green gap thwarts this sector, but it could be overcome by switching to the cubic form of GaN, argued David Wallis from Kubos Semiconductors. Despite difficulties in making green LEDs, the performance of all forms of visible LED continues to increase, and they are now capable of providing the light source in colour projectors for homes and offices, according to Benjamin Schulz from Osram Opto Semiconductors. Another lucrative opportunity for the LED lies in displays, where arrays of tiny chips provide direct emission. Transferring vast numbers of miniature LED Chips onto a backplane is time-consuming, even with massive parallel-transfer techniques, but microfluidics offers a promising alternative, revealed Paul Schuele from eLux Display.

As well as advancing devices made from established material systems, the AngelTech Online Summit considered the potential of new materials. One is AIScN, offering an opportunity for enhancing the channel in GaN-based HEMTs, claimed Stefano Leone from Fraunhofer IAF; and another is gallium oxide, capable or record-breaking field strengths, explained Andrew Green from the US Air Force Research Laboratory.

• The AngelTech Virtual 2 platform remains live on-demand for the next three months, where you can network with the community, reach out to the exhibitors and watch all presentations.

You can register for access to the portal or sign in by going to: https:// virtual.angel.events/932-858-004/auth

## WAFER ID MARKING & SORTING

InnoLas Semiconductor GmbH is a Germany based company which is focussed on high-quality wafer ID marking as well as high-reliability wafer sorting equipment for the semiconductor industry.

# 'Topping off' ceremony at Cree/Wolfspeed's SiC fab

GOVERNOR ANDREW CUOMO has announced the 'topping off' of Cree/ Wolfspeed's brand new, state-of-theart, automotive-qualified and 200 mmcapable power and radio frequency SiC wafer fabrication facility at the Marcy Nanocenter, which is located on the SUNY Polytechnic Institute campus near Utica.

Empire State Development's acting Commissioner, president and CEO Eric Gertler, alongside executive members from Cree/Wolfspeed, Oneida County and Empire State Development, joined distinguished guests in commemorating the placement of the final steel beam atop the new fab. This symbolises a major construction milestone for the project, which remains on schedule for production to begin in 2022.

"This milestone is proof of our commitment to the Mohawk Valley and is another step towards strengthening the research and scientific assets that New York needs to attract high-tech industries and build back better," Governor Cuomo said. "Cree/Wolfspeed has already proven to be a great partner, and we are proud to have them establish roots in the region as we continue to support and grow the advanced manufacturing infrastructure of New York State."

"The Mohawk Valley is leading the way in technology and innovation with new investments and opportunities," Lieutenant Governor Kathy Hochul said. "The progress at the SiC wafer fab at the Marcy Nanocenter will further advance wafer fabrication and production in the state. This significant investment will create hundreds of new jobs and provide internship and research opportunities for students in the area. The construction project is a testament to our efforts to build back better and strengthen the economy in the Mohawk Valley and across the state."

Cree CEO Gregg Lowe said, "All involved in this project should be proud of where we are today – from Cree/Wolfspeed employees, to our vendors, New York State, generous community partners and the residents who have welcomed us into this amazing community. SiC is

at the forefront of green technologies – including electric vehicles, renewable energy and energy storage – that will greatly reduce greenhouse gases. The technology that will be created at this fab – right here in your backyard – will power our customers to build a brighter future that is sustainable for all."

SUNY chancellor Jim Malatras said, "Today's ceremony is a symbolization of the foundation and partnership we are continuing to cultivate with Cree, who has been working closely with SUNY Polytechnic Institute to help our students excel in STEM leadership positions through hands-on learning internships. We are proud to collaborate with what will be the world's largest SiC fabrication facility in Marcy by way of the Wolfspeed project, and know that upon its completion the Mohawk Valley will reap the benefits of this workforce development initiative and added jobs."

Cree/Wolfspeed has taken many steps forward since announcing it would build its newest facility in New York State. Currently, the company has 40 fulltime employees in New York and had 24 interns this past summer from local universities throughout the state.

Cree also has multiple job openings listed for the fab, which include engineering and technician-related positions. Additionally, Cree announced in July that it will establish the "Cree/ Wolfspeed Scholarship" program and endowed chairs as part of its ongoing, long-term commitment to the Mohawk Valley to help expand the local economy and develop a pipeline of high-tech professionals.

The programme is designed to educate the next-generation, high-tech workforce by increasing student opportunities in STEM education and graduation rates, as well as by providing access to funds to assist students in advancing their education.

Cree/Wolfspeed has committed to investing at least \$1 billion through the construction of the fab, creating over 600 new jobs within eight years and will provide internships and research opportunities for State University of New York students.

SUNY has also committed to match up to \$5 million in semiconductor-related research funding from Cree/Wolfspeed for the SUNY system.

New York State is providing \$500 million in performance-based, capital grants from Empire State Development to reimburse a portion of Cree/Wolfspeed's costs of construction and fitting out the new facility and acquiring and installing machinery and equipment, as well as \$1 million in Excelsior Jobs tax credits.

# WE'VE SEEN TOMORROW. WE'RE READY TODAY.

HYDROGEN GENERATION from water is at the heart of the manufacturing industry's decarbonised future, and the world's. Right now, Cummins is advancing the next generation of alkaline and PEM technologies and delivering some of the world's safest, most compact and cost-efficient onsite systems for industries worldwide. If you're ready for #GENERATIONH, so are we.

Find out more at now.cummins.com/hydrogen

cummin

R

#### **NEWS ANALYSIS** CREE

# Cree: Stepping out of the light

As Cree exits the LED industry, its chief executive Gregg Lowe tells *Compound Semiconductor* what will come next

#### **BY REBECCA POOL**

WHEN CREE announced plans to sell its LED business to Smart Global Holdings in October for up to \$300 million, stock prices leapt by 7 percent. The move followed divestment of Cree's lighting arm in 2019, and comes as China-based manufacturers continue to capture market share from the likes of Lumileds, Osram and Nichia, largely thanks to cheaper production.

With an emphasis on his company now being a 'pureplay semiconductor company', Cree chief executive, Gregg Lowe, is committed to driving revenues in SiC and GaN markets, with electric vehicles currently being the sweet spot. Indeed, according to Lowe, recent meetings with Germany-based car manufacturers indicated that Covid-19 has accelerated electric vehicle adoption.

"With everything around the world shutting down, the skies cleared and these manufacturers have seen a big pull here from consumers," he says. "Europe has a multi-trillion dollar Covid-19 relief fund – 30 percent of this targets green energy initiatives that include electric vehicles and charging stations."

"Also, the EU parliament recently voted to increase its goal of cutting emissions by 40 percent to 60 percent by 2030," he adds. "As horrible as this crisis is, there is this silver lining that's very exciting for compound semiconductors and silicon carbide."

#### **Rising demand**

The latest development from Cree is not a surprise. Since the end of 2019, the company has been stacking up power semiconductor contracts with the likes of ABB Power Grids and joining forces with automotive players including Germany-based car parts manufacturer, ZF, and The Volkswagen Group.

Earlier this year Cree also revealed a partnership with Zhengzho Yutong, a Chinese manufacturer of commercial vehicles. Here, Cree's 1200 V SiC devices

#### NEWS ANALYSIS CREE

will be integrated to Yutong's power modules and used in the powertrain systems of electric buses. And working with long-time distributor, Arrow Electronics, Cree introduced 650 V SiC MOSFETs for electric-vehicle onboard chargers, switched-mode power supplies in industrial applications and more.

"The results that we've got on this platform have just been astounding," says Lowe. "Arrow identified \$750 million worth of opportunities across tonnes of different end-products including electric motorcycles, plasma generators and electrosurgical instruments. And when you think about this, we actually launched this platform in April – probably the worst part of the pandemic," he highlights.

Along the way, the company also secured \$700 million in design-ins for its power semiconductor arm, Wolfspeed, in quarter one this year, up from \$600 million from the fourth quarter of fiscal 2020. Factor in recent financial results which indicate that for the twelve months ending in June 2020, Cree's LED products raised \$433 million in sales while Wolfspeed brought in \$471 million, and the move makes clear sense.

As Lowe emphasises: "The LED market has certainly got tougher and this really allows us to focus on our [Wolfspeed] business – investors have been pretty happy with this, we received a fair price and we're ready to move forward."

So what next? LED activities will continue at Cree's key fabrication plant in Durham, North Carolina, as Smart Global Holdings rents production space for, as Lowe puts it, 'the time being'. In his words: "Smart's CEO came from Lumileds, he really understands the business so this is a good opportunity for them."

At the same time, Cree has been outsourcing its LED wafer production and processing at Durham, to make more room for SiC capacity. The company intends to continue raising SiC production in Durham, as construction of its New York, Mohawk Valley wafer fab continues.

"We're already working on our pilot line here and we're also hoping to make this facility weather-tight by early 2021," says Lowe. "We'll start installing the first set of tools in the summer of 2021 and then we can also transfer the pilot line to the factory."

Cree intends to increase capacity and SiC crystal growth from a 2017 baseline by 30 percent to 2024. Investments in 200 mm wafer production continue with Lowe anticipating an industry shift to the larger wafer size in 2024. And for the Cree chief executive, the worst of the SiC capacity constraints may be over.

"Capacity is tight but I think the adoption of electric vehicles is accelerating the way that people are thinking about this," he says. "We're going to need to expand beyond our 30 times increase, and we have the capital and ability to modulate our capacity based on what the demand is going to be."

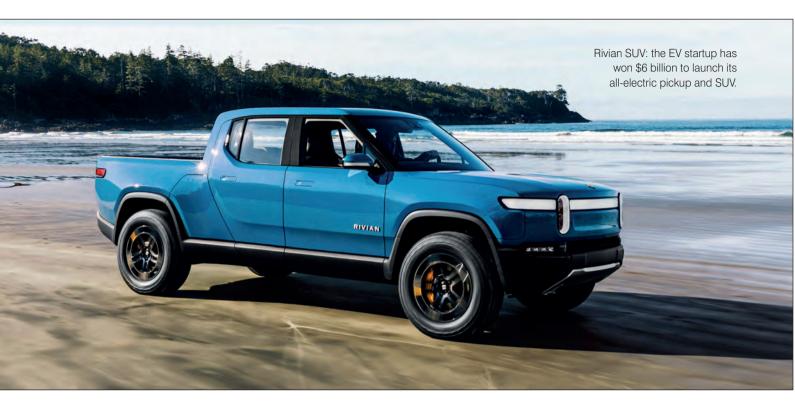

Indeed, it isn't just Europe that appears to have an appetite for more electric vehicles. Over in the US Tesla's cars are shifting faster than most would have imagined; the company surpassed the 1 million production mark this year. EV start-up Rivian has raised some \$6 billion, from the likes of Ford and Amazon, ahead of the much awaited launch of its all-electric pickup and SUV. Also, in September this year, Lucid Motors unveiled an all-electric saloon vehicle with a 517 mile range – Tesla's Model S reaches 402 miles.

"At the same time, I see China leap-frogging the internal combustion engine as it's going to be really tough for them to catch up with the West [in this industry] now," points out Lowe. And given that over the last three quarters, more than half of the company's new design-ins came from automotive partners, electric cars look set to be the market to watch for the time being. As Lowe says: "I tell, this is a great time to be a silicon carbide company."

But where does this leave GaN? Following US-China tensions, and the Huawei equipment ban from many nations, including the US, RF GaN activities relating to the roll-out of 5G have dwindled for Cree and competitors in this space.

Lowe says that the present situation makes it 'impossible' for Cree to sell to Huawei, which is one of the world's largest makers of 5G phones and networking equipment. Meanwhile, he reckons the current pandemic has also slowed 5G roll-out across Europe and the US. Still, he is adamant GaN remains important to Cree. "We see opportunities for GaN in aerospace, and 5G is still a pretty good opportunity for us," he says "There's a handful of non-Huawei RF manufacturers out there – we're engaged with all of them and we're winning." Gregg Lowe with Michael Baecker, Head of Volkswagen Purchasing Connectivity, when Cree was chosen as silicon carbide partner for Volkswagen's FAST programme.

# **Scrutinising Gan HEMTs** by quantitative cathodoluminescence

Quantitative cathodoluminescence aids development and production of GaN HEMTs by delivering non-destructive measurements for threading dislocations, composition, and doping

## BY MATTHEW DAVIES AND CHRISTIAN MONACHON FROM ATTOLIGHT

COMPOUND SEMICONDUCTORS share many of silicon's characteristics. However, there are some notable differences, causing some characterisation techniques for silicon to fail to provide accurate information for compound semiconductors. This state of affairs is most evident with GaN. To ensure

attolight

competitive pricing, GaN transistors and LEDs are grown on foreign substrates, giving rise to a very high defect density in the epilayers, a situation never found in silicon devices.

Helping to characterise various compound semiconductor devices, including those made from GaN, is a non-destructive technique known as quantitative cathodoluminescence spectroscopy. This is being trailblazed by our team at Attolight

of Lausanne, Switzerland, which has launched tools that support this form of metrology.

Previously, our team reported how quantitative cathodoluminescence spectroscopy can assist manufacturers of solar cells, lighting, and display technologies (see, for example, Cathodoluminescence for high-volume manufacturing, from the July 2018 edition of *Compound Semiconductor*). Here we consider how this technique can monitor the quality of the heterostructure of another device, the GaN-on-silicon HEMT (if you are not familiar with this device, take a look at the box "The basics of the GaN HEMT").

For this class of transistor, quantitative cathodoluminescence spectroscopy allows engineers to optimise end-of-line yield by focusing on three key metrics: the threading dislocation density; the aluminium content of the AlGaN layer above the channel; and the magnesium doping content of the *p*-type GaN gate, key to the realisation of a normally-off HEMT.

## COVER STORY CHARACTERISATION

To ensure optimal process chain management, engineers need to draw on rapid non-destructive feedback from metrology tools at every step of the process chain. This holds true for pilot lines, and for those found in dedicated research and development facilities and high-volume fabs. For those working in research and development, faster feedback accelerates development, while improving its efficiency and trimming costs. In the high-volume fab, faster non-destructive feedback reduces workin-progress and aids rapid process steering - in an ideal case, the effective work-in-progress is zero for a given process step. This is possible when feedback from a metrology tool is available within the downtime of a process tool between subsequent processes, a situation that occurs, for example, when cleaning an epi-reactor.

Our Säntis platform – for use after the growth of the epiwafers – offers rapid, reliable, non-destructive feedback of various metrics previously only accessible via destructive, time-consuming methods. Armed with this new, high-resolution eye on the epiwafers, fab managers and their engineers are well-positioned to make critical processing decisions. This includes deciding whether certain wafers should proceed to front-end processing, and whether there is a need to tweak the growth recipe, based on immediate feedback on key performance indicators.

In the remainder of this article we describe studies of GaN HEMTs using our Säntis 300 full-wafer quantitative cathodoluminescence platform. These investigations, which include proprietary measurement and analysis methods specifically developed for power HEMTs, represent the current state of development of our technologies for epi process control in GaN manufacturing.

#### Determining dislocations...

Dragging down the performance of GaN HEMTs are threading dislocations. If they intersect the channel formed by the two-dimensional electron gas, or connect the substrate to the gate contact, they can cause device leakage currents [2] and potentially impair long-term device robustness. Developers of GaN HEMTs have devised several solutions for cutting the leakage current through these channels. However, those working in this field are still to grasp a full understanding of this issue - they don't have a complete picture for what allows current leakage via these dislocations, or how to effectively control leakage, and they don't know the impact of dislocations on device performance and robustness. Consequently, there is a need to analyse threading dislocations in the epilayers, as this will shed more light on this issue and help to control the process, leading to better devices.

As cathodoluminescence has been around for decades, it is often assumed that counting threading dislocations by this technique is trivial. But it's not: it is far more complex than it would first appear to ensure reliable determination of the threading dislocation density to a standard that meets the expectations of process control metrology.

However, quantitative cathodoluminescence is incredibly insightful, combining simple counting of threading dislocations and determining their density with many new metrics. They include the local spatial distribution of threading dislocations; their geometric order and size; and the ability to discriminate between this imperfection and other structural defects, such as V-shaped pits. Thanks to this broad range of capabilities, quantitative cathodoluminescence spectroscopy is a very powerful tool for supporting the development and production of the GaN HEMT.

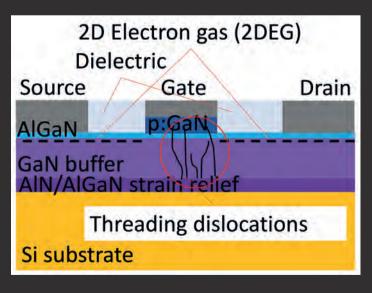

#### The basics of the GaN HEMT

At the heart of the junction-gated, normally off HEMT [1] is a twodimensional electron gas (2DEG), formed at the interface between the large band gap  $Al_xGa_{t,x}N$  (with *x* typically 10-20 percent) and regular GaN. To ensure normally-off operation, a *p*-type doped GaN layer is inserted between AlGaN and the gate contact.

For devices with this design, performance is impacted significantly by the:

- Dislocation density. Dislocations are ultimately linked to leakage current [2]

- Magnesium concentration in *p*-type GaN. This affects the Fermi level of GaN underneath the gate, and ultimately the blocking power of the device

- Aluminium concentration in AlGaN. This affects directly the 2DEG concentration [3]

This is the general design of the junction-gated, normally-off HEMT, typically used for power-conversion applications. Threading dislocations are present in the entire sample. This sketch just indicates their presence and direction, especially under the gate, where they have potentially the largest impact.

#### **COVER STORY** CHARACTERISATION

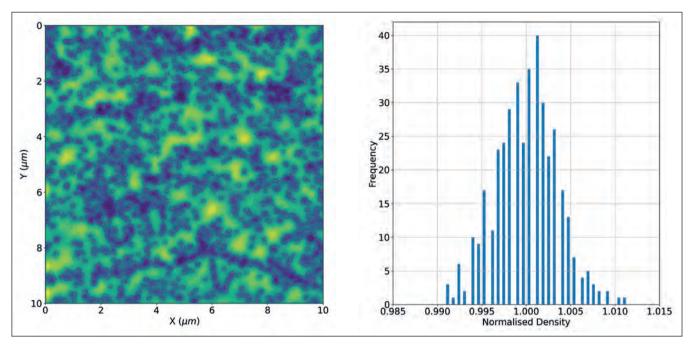

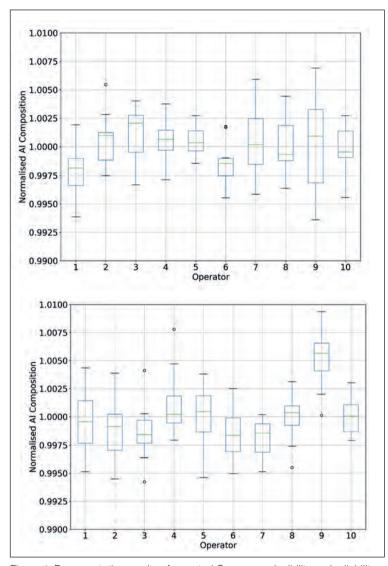

Figure 1. (a). A cathodoluminescence image with threading dislocations identified by the highlighted Attolight image reconstruction solution. (b) Histogram of normalised threading dislocation densities, recorded over several hundred iterations of the image reconstruction algorithm.

One technique with the potential to help quantitative cathodoluminescence is machine vision, which has improved in recent years, leading to widespread implementation in many industries. However, there are pitfalls when applying machine vision to small, densely packed features, such as the clusters of threading dislocations found in the epilayers of GaN-on-silicon HEMTs. In these heterostructures, where on average there are around ten threading dislocations per square micron, traditional feature-detection algorithms can suffer from a drop in accuracy.

We have addressed this weakness with an innovative image reconstruction method that draws on the results of Monte-Carlo and numerical simulations, and material-specific knowledge and assumptions. After investigating hundreds of iterations across different images, we determined a reconstruction reproducibility, evaluated in terms of 3 sigma, of  $\pm 1.05$  percent (see Figure 1). In addition, our technology resolves up to 40 percent more defects than a benchmark feature-detection solution.

If threading dislocation imaging by quantitative cathodoluminescence is to be employed into process control its capabilities must be more than just accurate counting of these defects in a single image. It may appear that to maximise precision of detection, engineers should record fewer higher-resolution images, each with fewer features. But this can fail to

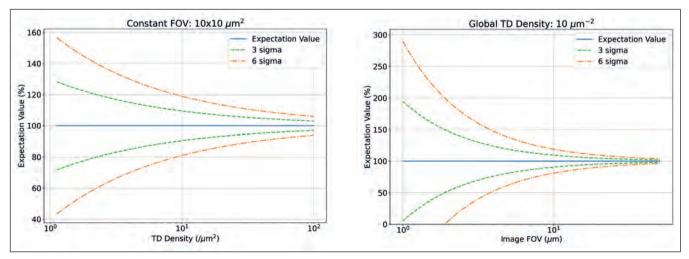

Figure 2. (a) Representative uncertainty (expressed as a percentage of the expectation value) for varying threading dislocation densities when considering a constant image area (FOV) in a single  $10 \times 10 \ \mu m^2$  image. (b) Representative uncertainty (expressed as percentage of the expectation value) for a constant threading dislocation density of  $1 \times 10^9 \ cm^2$ , evaluated for a single image with a varying FOV.

consider both the accuracy and the management of sampling error. This is critical to allowing quantitative cathodoluminescence to play an important role in process control.

As illustrated in Figure 2, when smaller images are used to determine the threading dislocation density, there are fewer features present – and the image is more susceptible to random statistical fluctuation. While an individual image can provide a more precise detection of threading dislocations, in certain circumstances the sampling error overrides this gain, resulting in an inferior accuracy for the result.

Consider, for example, a single image with a small field of view. This can result in an extremely large range of possible values due to random statistical fluctuation, an effect exacerbated by lower threading dislocation densities. In an extreme case, when imaging a sample with a defect density of  $1 \times 10^9$  cm<sup>-2</sup> – this equates to an average of ten defects for every square micron – there is a small but non-zero probability of finding no defects in a single  $2 \times 2 \mu m^2$  field of view (this is illustrated in Figure 1 (b)).

The solution is to combine a high sampling rate with an optimised field-of-view. Note, however, that it is not possible to process images with an infinitely large field-of-view with high precision, despite the apparent benefits that this would have on minimising sampling error. To realise sampling rates that ensure sufficient repeatability and reproducibility of process control metrology tools, there needs to be excellent, reliable automation, and repeatability of the detection algorithm. We offer this by combining: the automation of the Säntis 300 platform, with due consideration of sampling error and repeatability; with an innovative approach, employing a proprietary image reconstruction method to detect features.

#### ... and epilayer compositions

Situated at the heart of every HEMT, whether it is normally-on or normally-off, is a layer of AlGaN that is integral to the formation of the two-dimensional electron gas channel. By carefully controlling the AlGaN growth, engineers can set the electron gas concentration and ultimately determine key characteristics, such as the threshold voltage and the on-state series resistance.

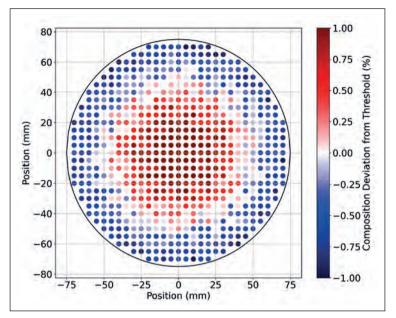

The growth of the heterostructure for the GaN HEMT is never perfect. Due to epitaxial reactor design, substrate bow, and the kinetics of the growth process, there are radial wafer-level dependences associated with epilayer composition and thickness (see Figure 3). The variations they produce on critical layers – in the case of HEMTs, the AlGaN layer; and in LEDs, the active region – drive down wafer-level homogeneity and device yield. While metrology and monitoring of critical epilayers can't eradicate this, they do play a crucial role in maximising homogeneity and manufacturing yield.

Figure 3. The Säntis 300 platform is capable of producing a wafer map of the aluminium composition of a buried AlGaN layer in a GaN HEMT structure (simulated data).

A very widely adopted, quick approach for determining the composition of epilayers involves measuring the peak of the photoluminescence. However, this is not applicable to all epitaxial structures, including buried AlGaN layers surrounded by GaN cladding. When AlGaN is buried, its energetic state relative to that of the neighbouring GaN layers results in an extremely low emission rate under optical excitation. Compounding matters, the excitation process for the AlGaN layer is inefficient, especially as the layers above it absorb most, if not all, of the incident laser light. Due to these two factors, it is impossible to measure the photoluminescence from a buried AlGaN layer.

Options for overcoming this problem are to either interrupt the growth after deposition of AlGaN, or to expose AlGaN by etching the material above it. Neither are ideal, being destructive processes. Regardless of whether the wafer is etched, or the growth interrupted, material used for photoluminescence measurements cannot be processed into devices. Another limitation is that this approach involves an indirect feedback loop, because measurements are performed on sister wafers.

Our approach offers a superior alternative, adjusting the electron-beam penetration depth to more efficiently and precisely excite the buried AlGaN layer. We have proven the accuracy and reproducibility of our technique by using a nested Gage study to compare equivalent wafers with and without a top p-type GaN layer (see Figure 4). This study shows a strong measurement reproducibility, with standard deviations below  $\pm$  0.25 percent [of normalised value], based on over 100 repeat measurements.

#### COVER STORY CHARACTERISATION

Figure 4. Representative results of a nested Gage reproducibility and reliability study on the determination of aluminium composition in the AlGaN layer of: (a) a full normally-off GaN HEMT structure (buried layer); and (b), the equivalent HEMT structure with the p-type GaN cap removed (surface layer).

When assuming a 14 percent specification limit (target  $\pm 7$  percent), we record a Gage variance below 10 percent for each sample.

#### **Doping control**

In normally-off GaN HEMTs magnesium doping influences various device characteristics, including robustness, off-state leakage and threshold voltage. The pioneers of GaN devoted much effort to developing a process for realising magnesium doping, with success in the 1990s allowing GaN to overtake ZnSe and become the best material for making blue and green LEDs and lasers. In the decades that have followed, those working on GaN have made a great deal of progress in understanding magnesium doping, with the self-compensation mechanism investigated and discussed in the research community [5]. Yet despite these advances, magnesium doping in the GaN HEMT still presents complications. Issues include enhanced leakage paths, stemming from an interplay between magnesium acceptors and threading dislocations [6].

The traditional technique for measuring magnesiumdoping in GaN is Secondary Ion Mass Spectrometry (SIMS). Used alongside Hall effect measurements, it allows engineers to uncover the ratio of incorporated magnesium to electrically active magnesium. Unfortunately, SIMS and Hall effect measurements are both destructive, with the former sometimes even requiring the shipment of a sample to a specialist lab.

However, long waiting times for both on- and offsite SIMS measurements no longer need to hamper progress, thanks to our proprietary technique for determining the magnesium concentration by quantitative cathodoluminescence. Our approach, based on detailed spectroscopic analyses, draws on a deep understanding of electron-matter interactions and the cathodoluminescence technique, as well as material-specific expertise.

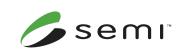

#### To prove the capability of quantitative

cathodoluminescence spectroscopy for determining magnesium doping, we have compared the results it produces to those provided by SIMS. Measurements on multiple samples yields a root-mean-square error of 3.8 percent for the derived relationship between magnesium concentrations determined by SIMS and by quantitative cathodoluminescence. To determine the repeatability of our technique, we have carried out a nested Gage reproducibility and reliability study (see Figure 5). This investigation uncovered good reproducibility, with a standard deviation below  $\pm$  1 percent over 100 repeat measurements, when assuming a 60 percent specification limit (target  $\pm$  30 percent) and a Gage variance below 10 percent.

#### Three virtues

One of the great virtues of our approach is that it is nondestructive. This prevents wafers from being periodically sacrificed to determine a property - a particularly welcome asset for determining the magnesium content in GaN HEMTs, as all alternative techniques are destructive. The two other prominent virtues are that this technique is comparatively fast, enabling acquisition from dozens of sites per wafer, and therefore giving a sense of the homogeneity of the properties; and the approach has versatility, providing measurements of threading dislocation density, AlGaN composition and magnesium-doping levels. Although it takes time to move between samples, due to the need to exchange wafers under vacuum, fabs that invest in this tool save space and reduce complexity of their feedback cycle (all these benefits are highlighted in Table 1, which also outlines the pros and cons of other techniques).

Thanks to the virtues of the Säntis 300 platform, it is ideal for process control, providing non-destructive feedback

Katy Crist Director, Marketing & Communications Tokyo Electron

# YOU SEE WHAT'S NEXT.

WE ATTRACT WHO'S NEXT.

## Attract, hire and retain your 21st century workforce with SEMI.

No one does MORE to fill the talent pipeline for the semiconductor industry. SEMI connects industry, talent and education for members worldwide. To access the next generation of leading minds, visit **semi.org/semiismore**.

## **SEMI IS** MORE

## COVER STORY CHARACTERISATION

in research and development labs and production fabs. By offering insights not available by other techniques, alongside faster feedback on existing metrics, it drives faster, more efficient development cycles in the lab, and trims work-in-progress in production cycles.

#### **Further reading**

- [1] M. Meneghini *et al.*, Power GaN Devices: Materials, Applications and Reliability. Springer Nature, 2017.

- [2] S. Usami *et al.* Appl. Phys. Lett. **112** 182106 (2018)

- [3] Y. Ohmaki *et al.* Jpn. J. Appl. Phys. **45** L1168– L1170 (2006)

- [4] I. Rossetto, *et al.* Microelectronics Reliability 76-77 298 (2017)

- [5] A. Klump *et al.* J. Appl. Phys. **127** 045702 (2020)

- [6] J. Chen *et al.* Appl. Phys. Express **12** 051010 (2019)

- [7] V. Yon *et al.* Phys. Status Solidi **257** 1900579 (2020)

Figure 5. Representative results of a nested Gage reproducibility and reliability study on the determination of the magnesium concentration in the p-type GaN layer of a full normally-off GaN HEMT structure.

| Use case                                          | Competing techniques | qCL competitive advantage                                                                                                     |

|---------------------------------------------------|----------------------|-------------------------------------------------------------------------------------------------------------------------------|

| Threading dislocation density                     | XRD                  | <ul> <li>Fast (&lt;1 min/site vs &gt;10<br/>min/site)</li> <li>Tailored depth<br/>sensitivity[7]</li> </ul>                   |

|                                                   | 2 photon absorption  | <ul> <li>Fast (&lt;1 min/site vs &gt;10<br/>min/site)</li> <li>Tailored depth<br/>sensitivity[4]</li> </ul>                   |

|                                                   | TEM/AFM              | <ul> <li>Fast (&lt;1 min/site vs &gt;60 min/site)</li> <li>Non-destructive</li> <li>Statistics (see Figure 3.)</li> </ul>     |

| Al content in Al <sub>x</sub> Ga <sub>1-x</sub> N | XRD                  | <ul> <li>Fast (&lt;1 min/site vs &gt;10<br/>min/site)</li> </ul>                                                              |

|                                                   | SIMS                 | <ul> <li>Fast (&lt;1 min/site vs &gt;10<br/>min/site)</li> <li>Non-destructive</li> </ul>                                     |

|                                                   | PL                   | <ul> <li>Better excitation<br/>efficiency, stronger<br/>signal, more reliable<br/>results</li> </ul>                          |

| Mg content in p:GaN                               | SIMS                 | <ul> <li>Fast (10 min/site vs &gt;60 min/site)</li> <li>Non-destructive</li> <li>Measures activated par of dopants</li> </ul> |

|                                                   | Hall effect          | <ul> <li>Non-destructive</li> <li>Fast (10 min/site vs &gt;60 min/site)</li> </ul>                                            |

Table 1. Alternative techniques for analysing GaN HEMT epiwafers highlight the advantage of the Attolight solution.

# LITHOSCALE® MLE<sup>™</sup> Maskless Exposure Lithography System

**GET IN TOUCH** to discuss your manufacturing needs **www.EVGroup.com**

EVG<sup>®</sup> LITHOSCALE<sup>®</sup>

# **Enhancing silicon photonics** with III-Vs and barium titanate

Heterogeneous co-integration of barium titanate and III-V semiconductors on a silicon photonics platform enables efficient optical transceivers and novel neuromorphic devices

### BY PASCAL STARK AND BERT JAN OFFREIN FROM IBM RESEARCH EUROPE AND STEFAN ABEL FROM LUMIPHASE AG

RECENTLY GLOBAL DATA TRAFFIC has been increasing at a compound annual growth rate of more than 25 percent. Due to this exponential rise, worldwide data traffic is tipped to reach 400 Exabytes per month in 2022. To cope with this hike in growth, which shows no sign of slowing, there needs to be a rapid scale-up in data transmission capacity and speed.

The lion's share of the traffic occurs within datacentres, where data is routed through optical fibres over distances from a few metres to a few kilometres. Inserted at the interfaces between optical

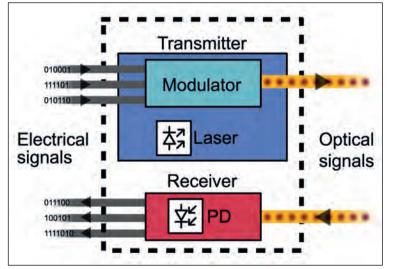

Figure 1. An optical transceiver provides an interface between electrical and optical communication channels. The transmitter converts electrical signals into optical signals. Vice-verse, the receiver is used to convert optical signals into electrical signals.

fibres and the electronic domain, involving computing and routing units, are high-speed optical transceivers (see Figure 1) – they are the most critical element in optical communication links.

There are two parts to the optical transceiver: the transmitter and the receiver. The transmitter contains a high-speed electro-optical modulator, which encodes input signals onto an optical carrier by a continuous-wave laser diode. After encoding, the optical signal is transmitted over an optical fibre. When the optical signals reach the transceiver, they are converted from the optical domain to the electrical domain with a photodetector.

Our team at IBM Research Europe has been pioneering a platform that paves the way to compact, high-bandwidth, power-efficient optical transceivers. At the heart of our technology is the co-integration of barium titanate (BTO), selected for its extremely strong electro-optic switching properties, with ultra-thin III-V technology, which provides a gain material for light emission, on a single silicon photonics platform. Lumiphase further develops such efficient switching products based on BTO photonic technology for commercial exploitation.

Here we detail how we integrate these different functional materials onto a silicon photonics platform. To fully unleash the functionality of all the layers, we have taken much care to ensure that we transfer light with low loss between different photonic layers. Efforts have also been directed at developing devices for potential applications such as optical transceivers and novel neuromorphic photonic architectures.

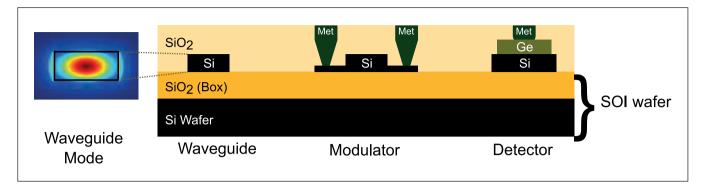

Figure 2. A silicon photonics platform with a waveguide, electro-optic modulator and germanium photodetector. Devices are fabricated on a silicon-on-insulator wafer (SOI). The waveguide mode shows the electric field intensity (red depicts high intensity, blue is for low intensity) in the waveguide (black box).

#### Silicon photonics: power and flexibility

The foundation for our work is silicon photonics. It offers efficient routing, manipulation, detection and modulation of light at telecommunication wavelengths, which span the range 1.3 µm to 1.55 µm. Today, silicon photonics is a mature photonic integrated circuit (PIC) technology, suitable for highvolume, low-cost production in CMOS foundries. Most commercial platforms are limited to the integration of PICs with optical components, such as waveguides, modulators and detectors, but also approaches to combine electronic and photonic integrated circuits (EPICs) are being developed. These approaches bring on-board electronic circuits, such as drivers, amplifiers, or control electronics, monolithically cointegrated with photonic components. Our technology is compatible with both PIC and EPIC platforms.

Silicon photonics is based on guiding light in silicon waveguides clad by SiO<sub>2</sub>. Manufacturing this technology in state-of-the-art processing facilities enables the production of waveguides with propagation losses below 1 dB/cm. Due to the high refractive index contrast between silicon and its native oxide, light is well confined in the waveguides, enabling the realisation of low-loss bends with radii below 10 µm. In addition to waveguides, there are many other passive building blocks in silicon photonic circuits, including: splitters and combiners; low-loss waveguide crossings; tapers; reflectors, which may be based on Bragg gratings; and Echelle gratings. Thanks to many years of research and development, various structures have been established, including passive filters that provide wavelength multiplexing and demultiplexing on photonic chips.

It is also possible to produce some active components with silicon photonics. One example is the electrooptic modulators based on the plasma dispersion effect in silicon. Injecting or depleting carriers creates an electrically induced change in the refractive index. Instead of solely changing the real part of the refractive index, there is also a shift in the imaginary part, due to the plasma dispersion effect. As designers of advanced modulators do not welcome this change in absorption, it must be avoided to boost the performance of future generations of silicon photonic modulators.

Two of the biggest drawbacks of silicon are that it cannot emit light; and that it is transparent at telecommunication wavelengths, making it unsuitable for efficient high-speed photodetectors. To equip circuits with these functionalities, direct-bandgap materials such as III-Vs are co-integrated with silicon. The most common approach for light detection is to add germanium, integrating this on silicon waveguides used for advanced photodetection. Far more challenging is the monolithic integration of the light source.

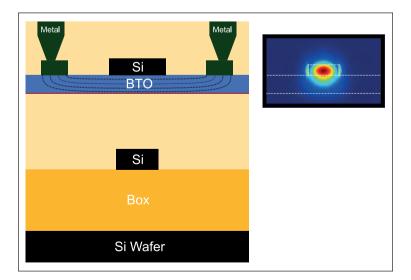

Figure 3. Cross section of a hybrid BTO/silicon device integrated on a silicon photonics platform. The refractive index of the BTO film (blue layer) can be tuned by applying an electric field (dotted lines). The inset shows the electrical field intensity of the optical mode in a hybrid silicon/BTO device. A large fraction of the optical power overlaps with the barium titanate film.

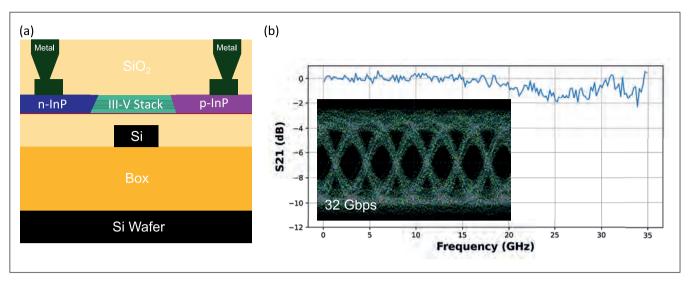

Figure 4. (a) Ultra-thin, CMOS compatible III-V integration on a silicon photonics platform. (b) Frequency response of a III-V photodetector. The inset shows an eye-diagram of the detector operated at 32 Gbit/s (NRZ signal) without using digital signal processing.

#### Roles for barium titanate and III-Vs

A novel material for improving the performance of silicon photonics is the ferroelectric oxide barium titanate (BTO). It is blessed with one of the largest known Pockels coefficients – this means that it produces one of the most significant changes in refractive index upon application of an electric field. Additional merits of the Pockels effect in BTO are that the refractive index changes are ultra-fast, its static power consumption is extremely low, and it tunes purely the real part of the refractive index, without any absorption.

Exploiting all these strengths enables the construction of ultra-small, energy-efficient, fast modulators, optical switches, and tuning elements, operating by modulating the phase of an optical wave but not its amplitude. Note that there is no Pockels effect in silicon and realizing these functions directly in silicon through the plasma dispersion effect leads to much less favourable properties.

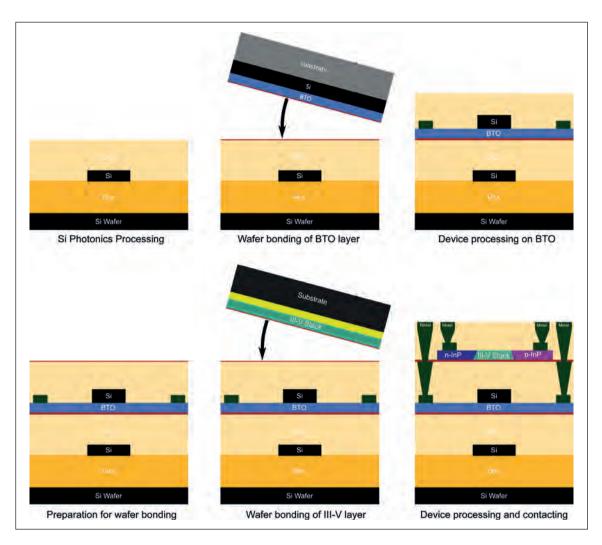

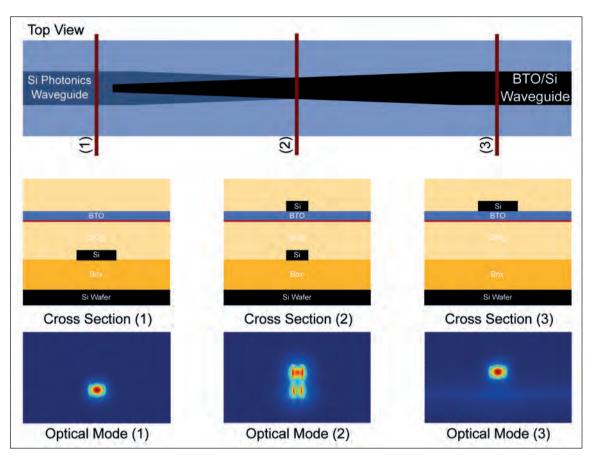

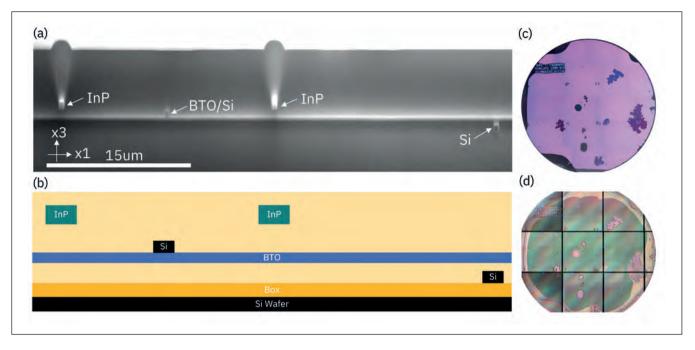

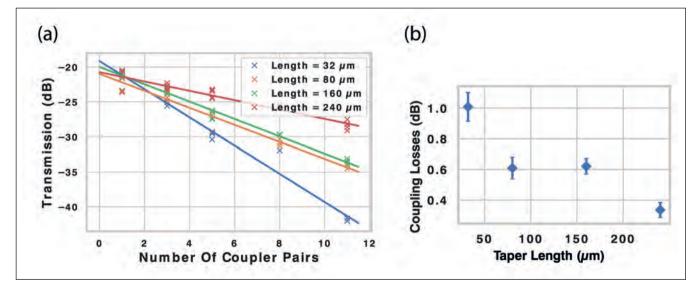

We integrate BTO by loading large silicon-on-insulator (SOI) substrates into an MBE chamber and epitaxially growing a thin film of this oxide. Subsequent lowtemperature molecular wafer-bonding allows us to transfer the BTO films to a silicon photonics wafer. By limiting the thermal budget, we ensure that the integration of BTO is compatible with CMOS foundry processes, enabling co-integration with CMOS circuits. That is a major asset for high-speed applications, because monolithic co-integration limits unwanted capacitive effects.