## COMPOUND SEMICONDUCTOR

CONNECTING THE COMPOUND SEMICONDUCTOR COMMUNITY

## SUPERIOR SHOWERHEADS

VOLUME 30 ISSUE I 2024

COMPOUNDSEMICONDUCTOR.NET

## **INSIDE**

News, Analysis, Features, Editorial View, Research Review and much more

## Handling extreme temperatures

AIN diodes and transistors deliver high breakdown voltages and operation at incredibly high temperatures

## Integrating III-Vs and silicon

To draw on the benefits coming from scaling, silicon and the III-Vs must be united via epitaxy and processing in silicon fabs

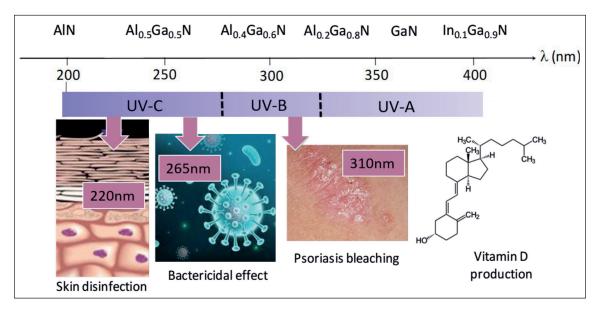

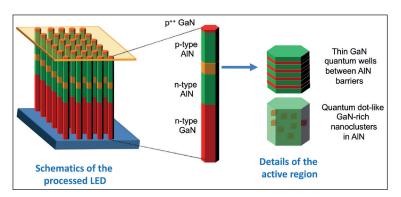

## Nanowires for UVC emission

AIN nanowires with short-period superlattices based on AIN and GaN are trailblazing a path to a new class of UVC emitter

## What's Your Next Big Thing?

- Micro LED Displays

- Autonomous Driving / 3D Sensing

- Communication Infrastructure

- Solar Cells

• ...

## G10-AsP

The Enabling MOCVD Solution

## Fully Automated MOCVD for High Volume Production of GaAs/InP Based Materials

www.aixtron.com

## **VIEWPOINT**

By Richard Stevenson, Editor

## The power puzzle

IF YOU ARE a device designer, the material that you'll use is often beyond question. If you are going to design a laser for long-haul optical links, it is incredibly unlikely that you'll look beyond InP; if you are working on the architecture for a powerful RF source, it is sure to revolve around GaN-on-SiC; and if you want a source of emission in the deep-UV, the standout design is an LED based on AlGaN – that's the primary rival to the mercury-based lamp.

But when it comes to power electronics, the situation is far more complex, and evolving. Today GaN-on-silicon dominates at relatively low voltages, thanks to its competitive pricing and its superior performance to the silicon devices it's displacing, and efforts are underway to increase market penetration at higher voltages, such as 650 V and a kilovolt or so. That's a domain where SiC MOSFETs and Schottky barrier diodes are currently having much success.

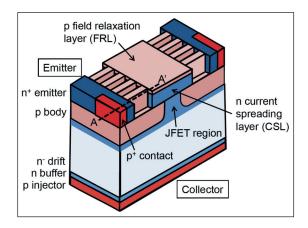

As well as the battle for this particular domain, efforts are underway to develop devices operating at even higher voltages. In contention are devices based on GaN and SiC, as well as those made from Ga<sub>2</sub>O<sub>3</sub> and AlN, with progress on all fronts reported at the most recent International Electron Devices Meeting (IEDM), held in San Francisco in mid-December.

One reason why it's hard to pick a winner at this stage is that all the candidates have significant strengths and weaknesses. For example, extending the SiC MOSFET to higher voltages leads to a much higher on-resistance and ultimately high switching losses.

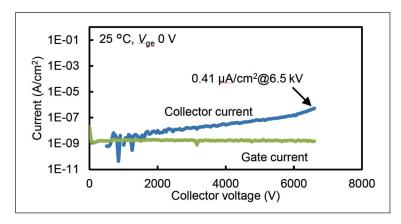

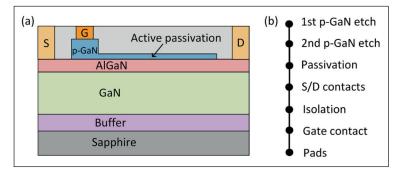

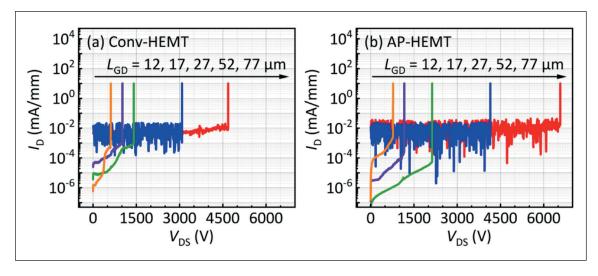

Much of the progress

reported at IEDM has

involved innovative device

architectures. For example,

a team from China and

Japan realised 5 kV

GaN HEMTs that are

free from multiple

field plates by

introducing an

active-passivation

design that's

based on a

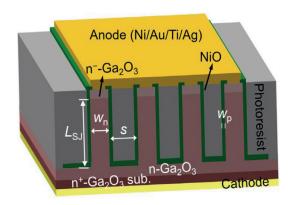

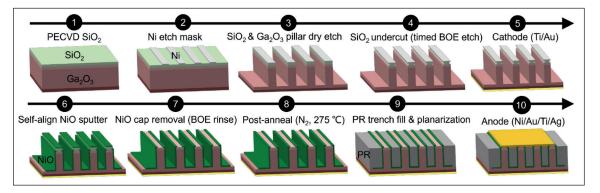

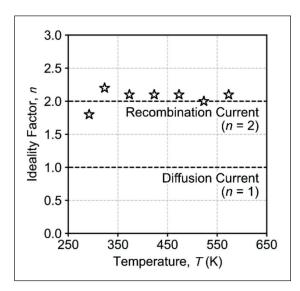

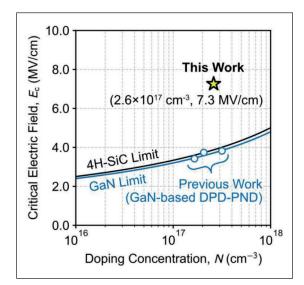

Of all the novel power devices presented at the most recent IEDM (see pages 28 to 33 for my report), the design that impressed me the most is the first superjunction device made from  $\text{Ga}_2\text{O}_3$ . Superjunction structures demand charge-balancing, a difficult feat with  $\text{Ga}_2\text{O}_3$ , due to its lack of p-type doping. To overcome this issue, a US team paired  $\text{Ga}_2\text{O}_3$  with NiO – the latter offers a far higher level of doping, thereby allowing the use of much thinner layers. Superjunction Schottky rectifiers sporting this design and featuring 1.8  $\mu\text{m}$ -wide  $\text{Ga}_2\text{O}_3$  pillars wrapped

in 120 nm-thick NiO can block 2 kV, and are said to set a new benchmark for the trade-off between blocking voltage and specific on-resistance.

It's impossible to say if this particular device, or the others that I've reported on, will go on to realise great commercial success. But it's going to be fascinating to watch the race unfurl over the coming years, and see which designs kick on to generate substantial sales for the power electronics industry.

thinned p-GaN

layer.

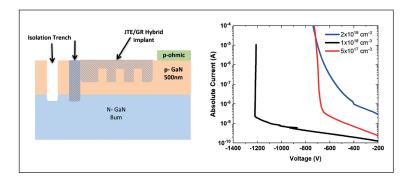

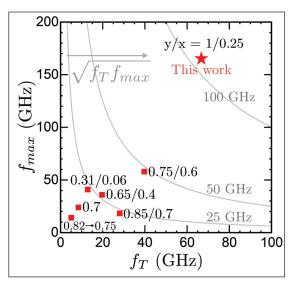

## 28 Pushing the power envelope

Novel designs enrich the performance of power devices employing a range of semiconducting materials

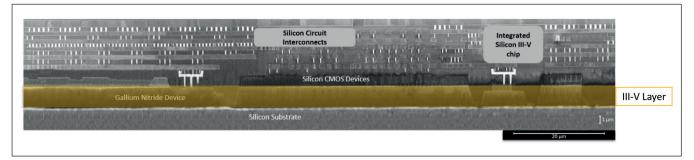

## 34 How to integrate silicon and III-Vs

To draw on all the traditional benefits that come from scaling, silicon and the III-Vs must be united via epitaxy and processing in silicon foundries

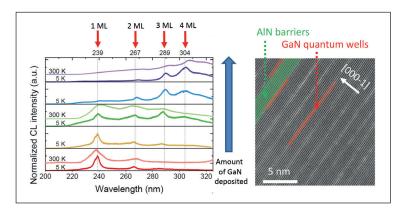

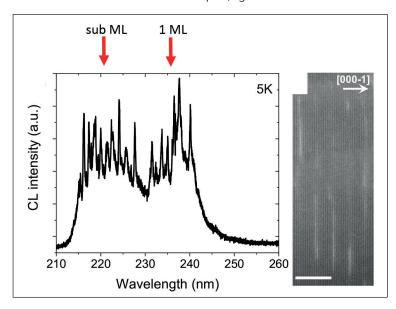

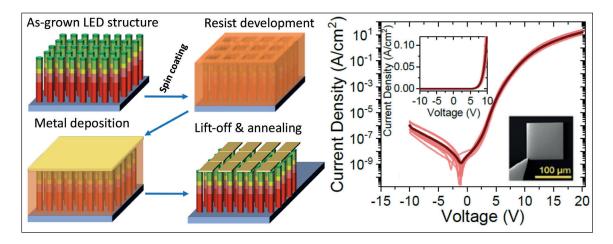

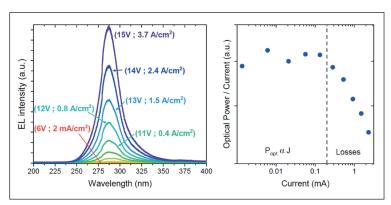

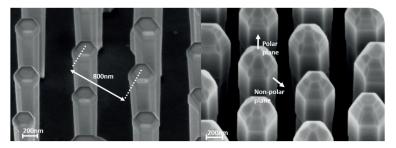

## 40 Nanowires for UVC emission

AIN nanowires with short-period superlattices based on AIN and GaN are trailblazing a path to a new class of UV-emitting devices

# 34

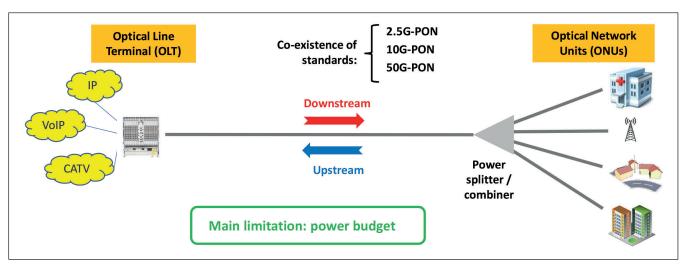

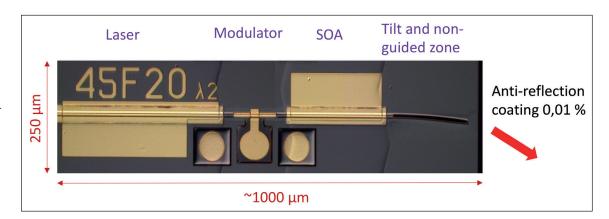

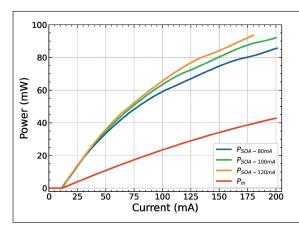

## 46 Extremely high-power transmitters for access networks

Sources that combine a laser, a modulator and an amplifier in a single device are laying the foundations for high capacity access networks

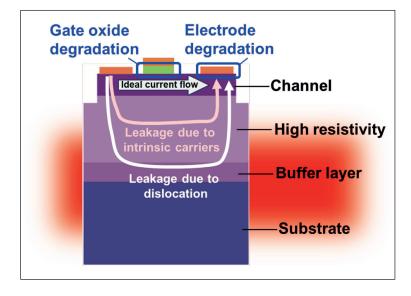

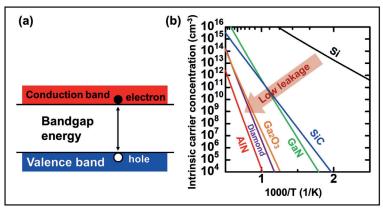

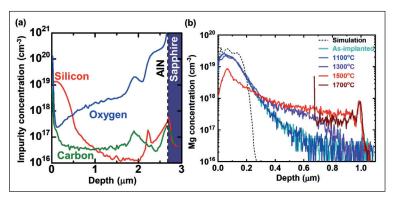

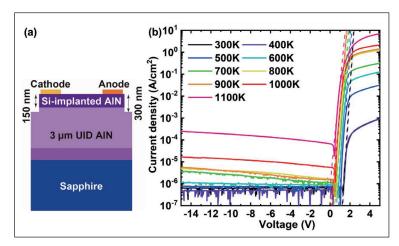

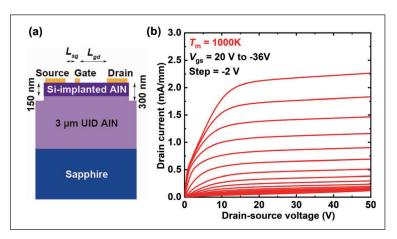

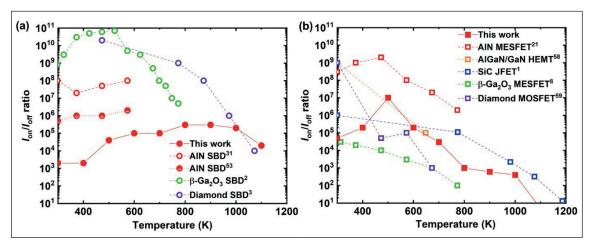

## 50 Extreme-temperature devices using AlN

Diodes and transistors with AIN channels deliver high breakdown voltages and operation at incredibly high temperatures

## **NEWS & MARKET ANALYSIS**

## 12 A Clas-SiC case of evolution

With a new CEO set on pursuing bold plans for expansion, is Clas-SiC changing course?

## 14 The world's biggest SiC fab

Infineon's construction of the world's largest SiC fab, in terms of both its footprint and its capacity, remains on track for opening in the third quarter of this year

## 16 Challenges for high-volume microLED manufacturing

Despite strong momentum, most microLED manufacturers are still experiencing delays in ramping volumes

## **RESEARCH REVIEW**

- 56 The case for better templates

- 57 Advancing vertical GaN diodes

- 58 Accelerating the AlGaN HEMT

## **NEWS**

- 06 Renesas to acquire Transphorm

- 07 Acquisitions in power

- **08** VCSEL research centre opens in Italy

- **09** Infineon and Wolfspeed extend SiC wafer agreement

- **10** BluGlass completes GaNWorks acquisition

- 11 Rohm and Toshiba to collaborate on power devices

Editor Richard Stevenson richardstevenson@angelbc.com +44 (0)1291 629640

**News Editor** Christine Evans-Pughe christine.evans-pughe@angelbc.com

Design & Production Manager

Mitch Gaynor mitch.gaynor@angelbc.com +44 (0)1923 690214 **Director of Logistics** Sharon Cowley sharon.cowley@angelbc.com

+44 (0)1923 690200

Senior Sales Executive

Jacob Caulfield

jacob.caulfield@angelbc.com

+44 (0)2476 718979

Marketing & Logistics Executive Eve O'Sullivan

+44 (0)2476 823 123 eve.osullivan@angelbc.com Circulation Scott Adams

scott.adams@angelbc.com

Publisher Jackie Cannon jackie.cannon@angelbc.com +44 (0)1923 690205

USA Representatives Brun Media

Janice Jenkins jjenkins@brunmedia.com +1.724-929-3550 Tom Brun tbrun@brunmedia.com +1 724 539-2404

**Chief Executive Officer** Sukhi Bhadal

sukhi.bhadal@angelbc.com +44 (0)2476 718970

Chief Technical Officer Scott Adams

scott.adams@angelbc.com +44 (0)2476 718970 Directors

Jackie Cannon, Sharon Cowley

Published by

Angel Business Communications Ltd 6 Bow Court, Fletchworth Gate, Burnsall Road, Coventry CV5 6SP, UK. T: +44 (0)2476 718 970 E: info@angelbc.com

Compound Semiconductor is published nine times a year on a controlled circulation basis. Non-qualifying individuals can subscribe at: £105.00 per annum (UK), €158 per annum (Europe), \$198 per annum (air mail) (USA). Cover price £4.50. All information herein is believed to be correct at time of going to press. The publisher does not accept responsibility for any errors and omissions. The views expressed in this publication are not necessarily those of the publisher. Every effort has been made to obtain copyright permission for the material contained in this publication. Angel Business Communications Ltd © Copyright 2024. All rights reserved. Contents may not be reproduced in whole or part without the written consent of the publishers. The paper used within this magazine is produced by chain of custody certified manufacturers, guaranteeing sustainable sourcing. US mailing information: Compound Semiconductor, ISSN 1096-598X, is published 9 times a year, Jan/Feb, March, April/May, June, July, August/September, October, November, December by Angel Business Communications Ltd, Unit 6, Bow Court, Fletchworth Gate, Burnsall Rd, Coventry CV5 659. UK.Airfreight and mailing in the USA by agent named World Container INC 150-15, 183rd St, Jamaica, NY 11413, USA. Periodicals Postage Paid at Brooklyin, NY 11256. POSTMASTER: Send address changes to Compound Semiconductor, Air Business Ltd, c/o World Container INC 150-15, 183rd St, Jamaica, NY 11413, USA. We strive for accuracy in all we publish; readers and contributors are encouraged to contact us if they recognise an error or omission. Once magazine edition is published Jonline, in print or both), we do not update previously published articles to align old company names, branding, marketing efforts, taglines, mission statements or other promotional verbiage, images, or logos to newly created or updated names, images, typographic renderings, logos (or similar) when such references/images were accurately stated, rendered or displayed at the time of the original publication. Wh

## Renesas to acquire Transphorm

## Acquisition will provide Renesas with in-house GaN technology

RENESAS will acquire GaN specialist Transphorm for approximately \$339 million. The acquisition will provide Renesas with in-house GaN technology, expanding its reach into fast-growing markets such as EVs, computing (data centres, AI, infrastructure), renewable energy, industrial power conversion and fast chargers/adapters.

Renesas has recently announced the establishment of an in-house SiC production line, supported by a 10 year SiC wafer supply agreement. The addition of Transphorm will expand its wide bandgap portfolio with GaN technology and expertise.

Demand for GaN is predicted to grow by more than 50 percent annually, according to an industry study. Renesas says it will implement Transphorm's auto-qualified GaN technology to develop new enhanced power solution offerings, such as X-in-1 powertrain solutions for EVs, along with computing, energy, industrial and consumer applications.

"Transphorm is a company uniquely led by a seasoned team rooted in GaN power and with origins from the University of California at Santa Barbara," said Hidetoshi Shibata, CEO of Renesas. "The addition of Transphorm's GaN technology builds on our momentum in IGBT and SiC. It will fuel and expand our power portfolio as a key pillar of growth, offering our customers the full ability to choose their optimal power solutions."

"Combined with Renesas' world-wide footprint, breadth of solution offerings and customer relationships, we are excited to pave the way for industry-wide adoption of WBG materials and set the stage for significant growth. This transaction will also allow us to offer further expanded services to our customers and deliver significant immediate cash value to our stockholders," said Primit Parikh, co-founder, president and CEO of Transphorm and Umesh Mishra, co-founder and CTO of Transphorm. "Additionally, it will provide a strong platform for our exceptional team to further Transphorm's leading GaN technology and products."

The transaction is expected to close in the second half of calendar year 2024, subject to Transphorm stockholder approval, required regulatory clearances and the satisfaction of other closing conditions.

Pictured above: Transphorm CEO Primit Parikh and Renesas CEO Hidetoshi Shibata.

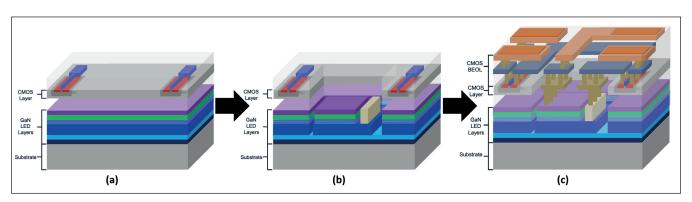

## Kopin and Micledi to collaborate on microLED displays

OPTICAL SYSTEMS firms Kopin Corporation and Imec spin-out Micledi Microdisplays have agreed to work together to design, develop, and manufacture microLED displays to provide a more immersive and information-rich AR experience for use in high-brightness light conditions.

The program will use Micledi's CMOS production flow and Kopin's backplane control and driving capabilities, along with its experience in manufacturing complete display systems, to create full colour microLED displays integrated with advanced CMOS technology for high-performance defence, enterprise, consumer, and medical systems.

"The demand for AR solutions, particularly for defence programmes,

has never been higher as users desire more immersive and information-rich experiences," said Bill Maffucci, senior vice president for business development and strategy at Kopin. "Micledi's microLED technology, combined with Kopin's advanced backplane design capabilities, aims to create microLED displays that address the demanding needs of emerging applications without the deficiencies of current technologies."

"We are pleased with Kopin's adoption and co-development of our disruptive AR display technology," said Sean Lord, CEO at Micledi. "To enable optimum microdisplays for AR, we believe Micledi has developed the world's first solution for microLED manufacturing in a 300 mm CMOS line, which allows integrating both a controller ASIC and

an emitter module on a 300 mm wafer in a highly efficient, high volume, and low-cost manufacturing flow."

Lord added: "Unique solutions can be tailored to the particular requirements of each end-use system, making Micledi 's microLEDs manufactured in collaboration with Kopin's backplane and system integration skills, applicable to a variety of specialised AR microdisplay systems."

## Acquisitions in power

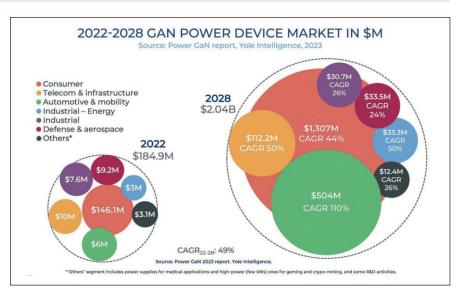

## Interest in GaN technology for cars is driving buyouts, says Yole

IN THE POWER GaN industry's second major acquisition in a year, following Infineon Technologies' purchase of GaN Systems, US-based Transphorm is to be acquired by a subsidiary of Renesas Electronics Corp of Tokyo, Japan. The acquisition adds to the billions of dollars invested in the power GaN industry since 2019 through partnerships, the construction of facilities, and M&As.

Yole Group's experts Milan Rosina and Taha Ayari say the automotive market is driving this activity. This sector, to be worth \$504 million by 2028, is attractive for players such as Renesas and Infineon, because it experiences higher margins and ROIs than the consumer sector.

The trend toward more integrated systems is notable in electric vehicles in particular, where OEMs are moving from today's 3-in-1 unit that integrates an EV drive motor, gearbox and inverter – to 5-in-1 or even 8-in-1 systems that also include power electronics controls such as DC-DC converters and onboard chargers. This is where the major opportunity lies for GaN to offer a high level of perceived value in reducing system costs, weight, volume and power losses.

Transphorm's automotive-qualified GaN technology was mentioned explicitly by Renesas as a reason for its purchase, to enable the development of enhanced power solutions for EVs. This followed Renesas' already strong ambition in targeting integrated power solutions for EVs with a recent partnership with Nidec, which will see the companies develop a 6-in-1 E-Axle.

Like Transphorm, GaN Systems has significant strength in the automotive sector, which was a major reason behind the Infineon acquisition in 2023. However, at \$830 million, Infineon paid more than double the \$339 million Renesas paid for Transphorm. With the two companies similar in size, with a

comparable market share, and strong GaN expertise and IP – what could be the reason behind the stark difference in value?

Could it be that GaN System's designwin pipeline is more attractive than Transphorm's? In the automotive sector alone, it has partnerships with Hella, Vitesco, Canoo, among others.

Unlike Renesas, Infineon already has inhouse GaN capacity, so the upcoming business it could gain through designwins is likely a big justification. And, thanks to design centres in Canada, the US, China and Taiwan, GaN Systems is in good stead to secure more of this type of business in the coming years. In this way, Infineon is playing the long game to secure a leadership position in the power GaN industry.

In contrast, it is likely that Renesas is satisfied with the in-house IP and GaN device production capacity it will gain (through Transphorm's epitaxy capabilities and its interest in GaNovation's AFSW wafer-fab). It is noteworthy that this AFSW fab is located in Japan, which may be considered as an advantage for Renesas to profit from a local GaN fab ready for high-volume production.

Renesas already has experience on GaN technology, working with EPC and GaN Systems (now an Infineon company) to develop systems like DC-DC converters and even spacegrade devices (following the acquisition of Intersil). Upon the completion of Transphorm, Renesas will have a complete power electronics portfolio, with power ICs, silicon power devices, SiC devices – after investing \$2 million in Wolfspeed to guarantee a 10-years SiC wafer supply - and Transphorm's GaN products. Renesas is now on track to compete with the leading power electronics players such as Infineon and STMicroelectronics.

Nevertheless, there is still a question as to whether the acquisition, expected to close by mid-2024, will be approved, particularly with Transphorm's work with the US government on several funded projects that can be related to defence.

In the next 5-10 years, IDMs are expected to become the dominant force in the power GaN ecosystem. While some fabless companies will co-exist by expanding into different markets – for example Navitas, which has entered the SiC sector by acquiring GeneSiC – Yole Group's analysts expect to see more M&As.

## VCSEL research centre opens in Italy

Centre of excellence will focus on applications in highspeed optical fibre data transmission links and optical sensing

VCSELence Torino, Italy, has been established as a centre of excellence for VCSELs in applications in highspeed optical fibre data transmission links and in optical sensing.

Relying on a well-established physical and technological background of VCSELs, VCSELence targets the experimental exploitation of these devices, pushing the application beyond the current limits. This will be achieved by performing highly sophisticated modelling of the in-laser phenomena supported by in-house experiments, with final tests of the device in the entire system.

VCSELence Torino unites the competences of several participating groups at DET (Department of Electronics and Telecommunication at Polytechnic University of Turin) at LINKS Foundations and at IEIIT-CNR (Institute of Electronics and Information and Telecommunications Engineering of the National Research Council).

All specialise in the fields of optical, electrical and spectral characterisation, modelling and advanced applications of semiconductor lasers covering all wavelengths for optical communication bands and for optical sensing.

The scientific goal is to advance the understanding of the dynamics of the coupled photon-carrier system in these opto-electronic emitters by joint theoretical and experimental investigations.

This will allow the realisation of improved devices designed ondemand, exploiting their ultimate limits and going far beyond the actual stateof-the-art.

VCSELence Torino will also be offering its services in modelling, design,

characterisation and system testing on a worldwide platform, to drive international research, and collaborative opportunities with innovative companies.

VCSELence Torino relies on an already existing large variety of European and world-wide funded projects with universities and companies and it intends extending them to the benefit of society.

VCSELence also builds on the existing photonics infrastructure of Links and Photonext (Interdepartmental Centre for Applied Photonics of Polytechnic University of Turin) where it shares a 300 m<sup>2</sup> lab and expresses the intent to become a significant player in the development of knowledge and expertise in the field of application of semiconductor technologies that will give benefit to Italy's economy.

It is expected that the new centre will also play an important role in advancing quantum physics-based technology.

Pierluigi Debernardi of CNR, with 25-years of experience on VCSELs, added: "Our Center of Excellence will be the research building for all scientists involved in modelling, design, technology and application of these low-cost semiconductor lasers, working together on the advancing of semiconductor optics research and optoelectronics".

## Purdue University wins SiC patent lawsuit against ST

PURDUE UNIVERSITY has won its patent infringement lawsuit against STMicroelectronics. US patent 7,498,633 covers technology involving SiC semiconductors invented by Purdue's James Cooper and his graduate student/ postdoctoral researcher Asmita

On Dec. 4, a jury returned a verdict in Purdue's favour, finding that ST infringed the patent by selling infringing SiC semiconductors. The jury awarded Purdue \$32.5 million in past compensatory damages, plus a running royalty on future sales.

"Winning this case is a great victory for Purdue," said Brian Edelman, Purdue Research Foundation (PRF) president. "As the university's tech transfer and commercialisation arm, we take managing and protecting Purdue intellectual property very seriously, and we hold ourselves and others accountable to the highest standards. Our preference is to reach a licensing agreement, but we have a moral obligation to protect Purdue IP, and that includes going to court to defend our rights. The jury recognised this semiconductor research from Purdue researchers, and the decision is great news for the inventors, Purdue University and Purdue Research Foundation."

Under the Bayh-Dole Act, contractors of inventions arising from federal governmentfunded research, such as US universities, own, patent and commercialise inventions through licensing. At Purdue, revenues from licensing are distributed among the inventors, their affiliated departments and the Purdue Research Foundation, which reinvests back into the commercialisation and innovation

## Infineon and Wolfspeed extend SiC wafer agreement

## Extended partnership includes a multi-year capacity reservation agreement

INFINEON and Wolfspeed have expanded and extended their existing long-term 150 mm SiC wafer supply agreement, originally signed in February 2018.

The extended partnership includes a multi-year capacity reservation agreement. It contributes to Infineon's general supply chain stability, also with regard to the growing demand for SiC semiconductor products for automotive, solar and EV applications and energy storage systems.

"As the demand for SiC devices continues to increase, we are following a multi-source strategy to secure access to a high-quality, global and long-term supply base of 150 mm and 200 mm SiC wafers. Our prolonged partnership with Wolfspeed further

strengthens Infineon's supply chain resilience for the coming years," said Jochen Hanebeck (pictured right), CEO of Infineon Technologies. "We have been working with Wolfspeed for more than 20 years to bring the promise of SiC to the automotive, industrial and energy markets, and to help customers leverage this energy-efficient technology to foster decarbonisation."

The adoption of SiC-based power solutions is rapidly growing across multiple markets. SiC solutions enable smaller, lighter and more cost-effective designs, converting energy more efficiently to unlock new clean energy applications.

To better support these growing markets, Infineon is continuously diversifying its supplier base to secure

access to high-quality SiC substrates.

Wolfspeed president and CEO Gregg Lowe said: "Industry estimates indicate demand for SiC devices, as well as the supporting material, will grow substantially through 2030, representing a \$20 billion annual opportunity. We are very pleased to continue our partnership with Infineon and to serve as a major supplier of SiC wafers in the years ahead."

## BluGlass completes GaNWorks acquisition

Completion follows successful installation and validation of GaN wafer processing equipment at the Silicon Valley fab

BLUGLASS has completed its acquisition of contract manufacturer GaNWorks Foundry, following the successful installation and validation of GaN wafer processing equipment at the company's laser production fab in Silicon Valley.

BluGlass says that testing has confirmed the *n*-side wafer metalisation, wafer thinning, and bar cleave equipment is meeting GaNWorks' operational benchmarks in-house. Product validation of new GaN lasers made at BluGlass' Silicon Valley fab is also underway, and wafer fab vertical integration is now complete.

BluGlass CEO Jim Haden said; "Our acquisition of GaNWorks' specialist wafer processing equipment, manufacturing process transfer, and experienced GaN engineers, will fasttrack development and production cycles, and deliver significant cost savings over the long-

Haden added: "We

have moved quickly to bring these complex processes in-house, having now completed process verification tests. and commenced validation of our first vertically integrated laser lots."

According to Haden, BliuGlass is already seeing the benefits of having all processes in-house under operational control. This enables quick identification of additional process optimisation

opportunities, which are expected to significantly enhance production yield, reliability, and throughput.

BluGlass is continuing to refine processes across its manufacturing supply chain to improve laser performance.

## Coherent introduces VCSEL-based illumination platform

COHERENT has introduced an illumination module platform for shortand mid-range lidar in automotive safety and robotic vision in industrial applications.

Using eight 940 nm VCSEL modules, the company has demonstrated a solution with several selectively addressable horizontal slices of the field of illumination.

In addition to offering a compact form factor and high power-conversionefficiency, the module is said to be a much lower-cost alternative than using large addressable VCSEL arrays.

Coherent has a demonstrator available for its customers to explore multiple VCSEL module positioning configurations and scanning algorithms for various depth-sensing modalities and types of scenery.

"A powerful aspect of the module platform is the ability to customise an optimized solution for use cases requiring up to 30 meters of depth sensing in bright daylight. Our illuminators exceed 30 percent total power conversion efficiency and have a compact footprint, only about a third of the size of a credit card," said David Ahmari, VP and general manager, Optoelectronic Devices & Modules Business.

"To achieve this breakthrough in efficiency and size, we are leveraging our state-of-the-art fivejunction VCSEL technology that enables each illuminator module to achieve up to 200 W of output power."

Customers of Coherent will be able to adjust the duration of the driving pulses to achieve both short- and mid-range lidar sensing. The FOI slices

are dynamically selectable depending on the number of VCSEL modules and the order in which they are scanned. A voltage supply of only 21 V is required, which is much lower, and therefore more efficient, than existing lidar technology.

## Rohm and Toshiba to collaborate on power devices

METI recognises joint silicon and SiC production plan as supporting stable, secure supply

AS A MEASURE towards a secure and stable semiconductor supply, Japan's Ministry of Economy, Trade and Industry (METI) has approved a plan by Rohm and Toshiba to collaborate on the manufacture and increased volume production of SiC and silicon power devices.

Current demand for power devices is expected to see continued growth as automotive and industrial applications shift towards greater electrification and efficiency.

For Rohm (one of the first mass producers of SiC MOSFETs), its SiC business is a priority project, with aggressive investment to increase production capacity.

Toshiba Electronic Devices & Storage has for decades supplied silicon power devices, mainly for automotive and industrial markets. The company started production on a 300mm wafer line last year, and is accelerating investment to enhance capacity. It is also advancing development of a wider lineup of SiC power devices, especially for automotive and power transmission and distribution applications.

Under intensifying international competition in the semiconductor industry, Rohm and Toshiba have been considering collaboration in the power device business for some time, and that resulted in the joint application.

Rohm and subsidiary Lapis Semiconductor will invest around \$2 billion.

Toshiba Electronic Devices & Storage and its subsidiary Kaga Toshiba will invest around \$677 million. The maximum government subsidy is \$885 milion, which is one-third of the total investment amount.

Production sites will be Kaga Toshiba for silicon power devices, and Lapis Semiconductor Miyazaki Plant No.2 for SiC power devices and SiC wafers.

## **Advanced Compound Semiconductor Foundry Services**

MOCVD · Fabrication · Testing

Advanced III-V semiconductor solutions for optoelectronics application in the biotechnology, telecommunications, energy, industrial, and security industries.

MasimoSemiconductor.com | 603-595-8900

## A Clas-SiC case of evolution

With a new CEO set on pursuing bold plans for expansion, is Clas-SiC changing course?

## BY RICHARD STEVENSON, EDITOR, CS MAGAZINE

INITIAL ENCOUNTERS can be misleading. At times first impressions are misguided, to be replaced with a far more informed view after digging a little deeper.

That could be the case for many following the fortunes of Clas-SiC, the Scottish SiC fab. It has just announced the appointment of a new CEO, who only joined the company as chief operations officer in summer 2023; and ambitious plans are now being touted for a major expansion, both in capacity and the technology portfolio.

However, go behind the headlines and what at first glance appears as a couple of major changes is actually a continuation along the same trajectory. The new CEO, Jen Walls, is an old hand, who devoted many years to helping lead Raytheon's SiC foundry services, from which Clas-SiC spawned. And when Walls joined Clas-SiC, her accession to CEO was already part of the company plan, and given that turnover has doubled in the last 12 months, efforts to increase capacity are a logical, natural progression.

Another contributor to continuation, rather than change, is retaining the three major strands of the company. "We have fast turnaround prototyping; low-to-medium volume manufacturing; and we also operate a licencing and royalty arm to the business, to give customers that have more capacity-hungry devices a route to high-volume manufacturing," says Walls.

One strength of this three-pronged approach is that it enables Clas-SiC to work with a wide range of customers from all over the globe. They include those that have gone no further than developing prototypes, and benefit from the reassurance that Clas-SiC can support their entire product lifecycle; and those that have already developed their SiC

➤ Karen Millar, Production Supervisor, and CEO Jen Walls, checking status of the high-temperature annealer. technology, and want to progress to low rate production.

## An engineering pedigree

Walls has devoted most of her career to engineering. As a teenager she won an engineering scholarship at Exxon Chemicals, enabling her to study integrated engineering at the local college on a block release basis while working at the ethylene plant.

"When I graduated, the oil industry was in downturn, but thankfully Scotland's silicon Glen was booming," recollects Walls. "So, my semiconductor journey started with NEC semiconductors, as a photo equipment engineer. I then moved into NEC's new 200 millimetre fab in Livingston, which at the time was the largest, most advanced fab in Europe."

When this fab closed in 2001, Walls moved to Raytheon, where she progressed through the ranks to take management positions while completing an MBA. She views the highlight of her time there as her role as SiC business manager, leading the process development team. However, she could not accomplish all she hoped for, because Raytheon did not give the SiC division the freedom it needed to thrive: "I always wanted the silicon carbide foundry within the defence company to be a standalone business," says Walls.

Seeking a new challenge, she started work as a business manager in the health sector, a role that allowed her to continue to draw on her engineering and manufacturing skills. "However, it never gave me the same fire in my belly. I always knew I would be back in the industry."

And six years later she was, when in July 2023 she joined Clas-SiC and resumed a working relationship with many colleagues from her time in the SiC division at Raytheon.

While preparing to take over from the outgoing CEO, Rae Hyndman, who is moving into retirement, Walls focused on trying to improve operational execution.

"It's worked extremely well," says Walls. "It's allowed me to make sure I fully understand the workings of the operation here at Clas-SiC, and it's allowed me to build a relationship with customers and employees, and importantly as well, the Clas-SiC board."

Viewing the change in CEO as evolutionary rather than revolutionary, Walls has much praise for Hyndman, whom she credits for taking the company from conception back in 2017 to qualification and then rapid growth, including an increase in headcount from 24 to the 80 employees today.

"Clas-SiC has grown extremely quickly," says Walls. "We're about a year ahead of where we thought we would be under the leadership of Rae."

## A legendary supporter

As well as benefitting from the support of the outgoing CEO, Walls is grateful for the guidance of the executive chairman, Carl Johnson, who cut his teeth founding II-VI more than 50 years ago, and led that company for more than 30 years.

"I have weekly goal and mentoring sessions with Carl," says Walls. "He has a wealth of experience and always brings a valued perspective to the table."

Walls is taking over the reins in an enviable position, with 70 percent of the fab capacity for 2024 already allocated. This healthy orderbook is partly behind the decision that now is the right time to expand.

"We're looking for about a £24 million investment," says Walls. "That will take our capacity to 2.5 times where we are today." The funding will be used to expand the clean room space and purchase additional tools for future process development and operational resilience.

Efforts in this direction are already underway. "Just now we are working on our 3.3 kV process design kit for MOSFETs," enthuses Walls.

With the chance to lead a growing company developing exciting new technologies, it's of no surprise that Walls is clearly revelling in her return to an engineering company.

The new CEO, Jen Walls, supporting Senior Equipment Engineer Graeme

One strength of this three-pronged approach is that it enables Clas-SiC to work with a wide range of customers from all over the globe

## The world's biggest SiC fab

Infineon's construction of the world's largest SiC fab, in terms of both its footprint and its capacity, remains on track for opening in the third quarter of this year

## BY RICHARD STEVENSON, EDITOR, CS MAGAZINE

WITHIN the SiC industry, much manufacturing takes place in-house. So, when these chipmakers want to increase production, they tend to boost internal capacity. That's in full flow right now, spurred on by the tremendous ramp in sales of electrical vehicles, which deploy SiC power devices in the on-board charger and DC-DC converter.

One of the companies grabbing the headlines for capacity expansion is the power-electronics giant Infineon, which lays claim to constructing the world's biggest 200 mm SiC fab, in both size and capacity. Initially backed by €2 billion of internal funding,

plans for the new fab in Kulim, Malaysia, were bolstered last summer with the injection of a further €5 billion for building and equipment.

Back then the company announced that the completion of the first phase of this fab remained on track for the third quarter of 2024, a deadline that's still on schedule, according to Ng Kok Tiong, Senior Vice President and Managing Director of Infineon Technologies Kulim. Over the next five years the completion of the second phase will proceed. Infineon's new SiC power fab, known as Kulim 3, is being built next to a pair of its 200 mm silicon

## NEWS ANALYSIS | PRODUCTION

fabs. However, even those fabs, constructed in 2006, were not the beginning of off-shoring of manufacturing by the European powerhouse in Malaysia. Through Siemens, which divested Infineon in 1999, there has been investment in Malaysia for almost 50 years, including the construction of a back-end assembly and test facility in another state, Malacca. The combination of fabs in Malaysia gives Infineon end-to end production within the country. In fact, the investment in semiconductor manufacturing is so strong that Infineon has more employees in Malaysia than any other country, including Germany.

According to Ng, one of the reasons why Infineon decided to expand its SiC production capability by building a third fab at Kulim is that this offers a very fast way to ramp capacity. That's partly because compared with other countries, approval can be granted for construction to take place during more hours of the day, thanks to local labour law.

One difficulty with building any new fab is winning approval for the water and electricity that's supplied to the site. Ng believes that this has been granted quickly for Kulim 3. Building a new fab next to existing ones helps, but in addition to that, Infineon benefits from having a large, welcomed presence in Malaysia.

"We are working very well with the government, with MIDA, which is the government agency for investment," remarks Ng, who adds that they get a lot of attention for any support that's needed.

Ng says that equipment will start being installed in Kulim 3 from April 2024, with production of SiC devices slated for the second half of the year.

Engineers at this fab will carry out all aspects on front-end processing, including production of SiC substrates from boules provided by five suppliers – two from China, two from the US, and one from Japan. Helping increase the margins associated with this process is the Cold Split technology that Infineon acquired from Siltectra in 2018. "With this new technology you can reduce some of the losses of the raw material," says Ng.

Construction of the 200 mm SiC fab is expected to create 900 jobs, with the vast majority taken by local people. To help with the training of Malaysian engineers, many are sent to Infineon's other SiC fab, located in Villach, Austria. In addition, experts from there visit the facility in Kulim.

To help attract the best local talent, the Kulim fab works very closely with local universities and polytechnics by offering placements for internship and final year projects. Ng and his colleagues have found that due to need for very specific expertise, even engineers graduating after a four-year programme can take 8 months of training before they can start making meaningful contributions. So, to avoid this delay, a programme has been

➤ Ng Kok Tiong is Senior Vice President and Managing Director of Infineon Technologies (Kulim) Sdn. Bhd., which is Infineon's first and only wafer fabrication plant in Asia. Ng is also currently the Chairman of the Semiconductor Fabrication Association of Malaysia.

introduced, with students spending time at the facility and having an engineer at the fab as a mentor. "By the time they graduate, they are already effective, because they know SPC, they know how to do the DoE, and things like that," says Ng.

Helping Infineon commit to investing in Kulim 3 are a number of design wins totalling €5 billion. They are roughly a 50-50 split between the electric vehicle and industrial sectors, with the latter a mix of solar and storage industries.

The plan is that by the end of this decade, production at both the Kulim and Villach sites will account for a 30 percent share of the SiC power market, which by then will be worth about €20 billion.

While emphasis is initially on SiC at Kulim 3, efforts are also underway to develop GaN products at this site. The first steps towards this, now underway, involves qualification of the growth process.

Based on all the plans for wide bandgap semiconductors at Kulim, there's no doubt that the long-term relationship between Infineon and Malaysia will only get stronger throughout this decade and beyond.

Helping Infineon commit to investing in Kulim 3 are a number of design wins totalling €5 billion. They are roughly a 50-50 split between the electric vehicle and industrial sectors, with the latter a mix of solar and storage industries

## Challenges for high-volume microLED manufacturing

Despite strong momentum, most microLED manufacturers are still experiencing delays in ramping volumes

### BY ERIC VIREY FROM YOLE INTELLIGENCE

THERE ARE MANY great attributes of displays based on microLEDs, which are miniature red, green and blue emitters with dimensions typically less than  $50 \mu m$ . Thanks to independent control of every sub-pixel, displays based on microLEDs combine high-contrast, high-speed, and wide viewing angles - merits also found in OLED displays - with superior colours, better contrast, higher brightness, lower power consumption, longer lifetime, environmental stability and ruggedness. In addition, with microLEDbased displays there is the possibility of integrating sensors and circuits, advances that would enable the production of thin displays with embedded sensing capabilities involving fingerprints, an in-display camera, a touch function and gesture control.

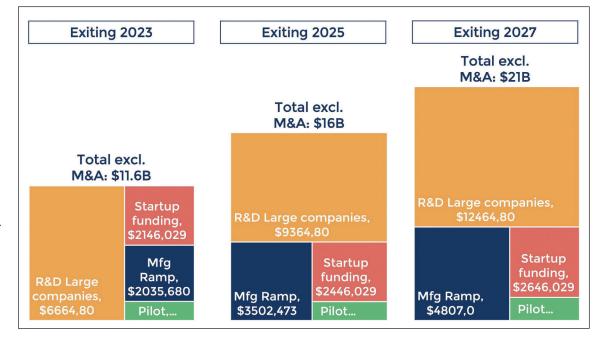

Spearheaded by efforts from Apple and others, microLEDs have generated tremendous excitement over the past decade. According to the *MicroLEDs 2023* report by our team at Yole Intelligence, \$12 billion has been spent on efforts associated with

microLED development and industrialisation, and another \$2.4 billion on mergers and acquisitions. While this is dwarfed by the building costs of OLED fabs since the mid-2000s, a expenditure totalling more than \$100 billion, it's indicative of strong momentum. All display makers now have sizeable microLED efforts and the first commercial products are on the market, including a number of AR headsets and a TV from Samsung. Expected to join this list in the spring is a luxury watch from Tag Heuer.

More products are sure to follow, as the supply chain shapes up and more companies invest in manufacturing capabilities. Making headlines on this front is Osram, which is spending a billion dollars to build an 8-inch microLED fab in Kulim, Malaysia, to serve Apple's needs for an upcoming smartwatch. As one might expect, this is by no means the only microLED activity in Asia: Taiwanese holding company Ennostar is building a 6-inch fab; most leading display makers in China have aligned

Figure 1.

Cumulative

investment

in microLED

development

and

manufacturing.

Taken from

microLEDs

report, Yole

Intelligence,

2023.

Credit: Yole

Intelligence

## MARKET ANALYSIS | MicroLEDs

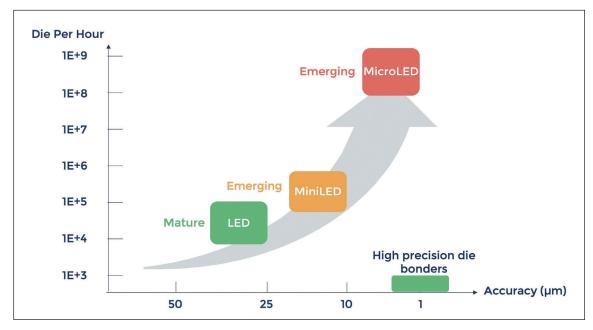

Figure 2. Required die assembly equipment capabilities for microLED vs. existing LED and miniLED solutions. Taken from microLEDs report, Yole Intelligence, 2023. Credit: Yole Intelligence

themselves with leading domestic producers of LEDs; and in Taiwan and South Korea, AUO and Samsung have started producing small volumes of smartwatch displays and microLED TVs, respectively. Some investments in microLED capability in China are substantial, with BOE spending \$300 million to acquire a controlling stake in HC SemiTek, which is using the entire proceeds to build a 6-inch microLED fab, and Sanan is spending nearly \$2 billion on a new fab, with \$200 million earmarked for microLEDs. In addition, JBD has completed its construction of a \$100 million, vertically integrated microdisplay fab near Shanghai, and Vistar has broken ground on a \$413 million microLED display project.

However, progress is not keeping pace with schedules. Osram's fab, initially slated to ramp in 2024, is now expected to start in late 2025; and while Ennostar's first phase is on track for mid-2024, the second phase has been pushed back by one-to-two years, to 2026 or 2027. Note that these are by no means the only projects to experience delays. But why is it taking so long to bring microLEDs to consumers?

## Mass transfer: a major hurdle

MicroLEDs are challenging. Making a display involves processing LED epiwafers into arrays of microLED chips, poised for transfer and integration into a heterogeneously integrated system incorporating LEDs, pixel-driving transistors, optics and so on.

To manufacture a microLED display with an 8K resolution, which is 7680 pixels by 4320 pixels, requires the transfer and assembly of almost 100 million microLEDs with a placement accuracy of ±1 µm – and that must occur in less than 10 minutes to ensure economical viability. Unfortunately, today's LED and die bonders are incapable of manipulating the very small die deployed in high-volume consumer applications, and at the required level of precision their throughput is typically limited to no more than around 1,000 die per hour. At this pace it would take 11 years to manufacture a single 8K TV. Recently developed miniLED transfer equipment trims this time, but it is still longer than a week.

What's needed is a paradigm change: the development of mass transfer technologies that manipulate and assemble far smaller die at a rate five orders of magnitude faster.

The good news is that progress has been spectacular, to the point that many industry players no longer see it as a fundamental roadblock. Only three years ago, a company developing microLED displays had to invent its own mass transfer process and build its equipment. Now, more than a dozen off-the-shelf tools are available from equipment makers. These first-generation tools are suitable for development, pilot lines, and, in some cases, for a first product.

However, to ensure costs meet expectations, the microLED has to be shrunk below 10  $\mu m$ . For

To manufacture a microLED display with an 8K resolution, which is 7680 pixels by 4320 pixels, requires the transfer and assembly of almost 100 million microLEDs with a placement accuracy of  $\pm 1~\mu m$  – and that must occur in less than 10 minutes to ensure economically viability

## MARKET ANALYSIS I MicroLEDs

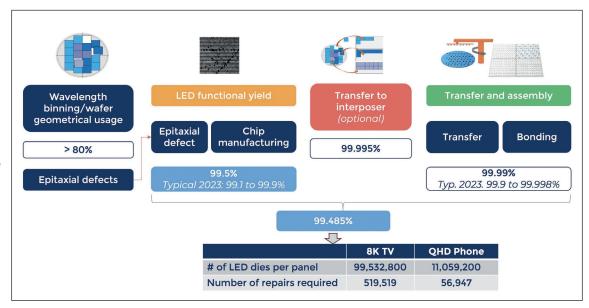

> Figure 3. Yield and repair in microLED display manufacturing. Taken from microLEDs report, Yole Intelligence, 2023. Credit: Yole Intelligence

example, the microLEDs that Apple will use in its smartwatch will be 6-8 µm. At those sizes, most tools struggle. Another challenge facing equipment makers is that their tools have to operate over large areas – at least 730 mm by 920 mm, and possibly up to 1500 mm by 1850 mm. These challenges associated with mass transfer are thought to be the culprit for Apple's smartwatch manufacturing ramp delay. This tech giant is working with a partner to develop a custom tool based on its proprietary MEMS-based technology.

## Yield and repair

Another factor to consider alongside transfer and assembly is yield, which has impact on cost. With microLEDs, bad (dead) pixels can originate from either a faulty die, a missed or misplaced die during transfer, or a defective electrical connection. Today, transfer yields range from 3N (99.9 percent) to 5N+. Meanwhile, microLED chip yields are between 99 percent and 99.5 percent.

While those numbers initially appear impressive, they equate to half a million defective pixels in an 8K TV. As the eye is incredibly sensitive to defects, manufacturers must develop effective yield management strategies that combine pixel redundancies and/or individual pixel repair with chip and pixel testing and binning.

To limit repair needs, it is critical for makers of microLED-based displays to use testing and inspection to remove bad die from the process flow as early as possible. Assisting in this endeavour are multichannel probe-card testing tools, but their workload is daunting, as it will not be long before there are 500 million die on a single 8-inch wafer. Even today's best commercial probers would take more than 40 hours to test one of those wafers. A better option for very small high-density chips is massively parallel, contactless testing. A tool providing this form of testing has been introduced to market in 2023 by the Korean company Top Engineering, but its capability is still to be demonstrated in volume production. Note that in 2020 Apple acquired start-up Tesoro, with the aim of developing an in-house solution.

As well as the need for tools and technologies for microLED mass transfer and massively parallel contactless testing, there are other challenges. They include the driving of the microLED displays, a task that requires innovation, as it is not possible to simply use the drivers of OLED displays. Another hurdle is to improve the external quantum efficiency of the microLED, which can plummet when scaled to very small dimensions.

One may view a microLED display as a new, complex puzzle. While many pieces already exist, some are yet to be perfected – and they need to be brought together, with the last few kinks ironed out, which will take more time. It is only after yields and costs get close to target that the first consumer products will appear. The next two-to-three years are going to be critical, with Apple's smartwatch and Samsung's TV projects acting as incubators for the entire industry. That watch is now expected in 2026, and if it fails, this would be a massive and potentially fatal blow.

Nevertheless, there is very strong momentum for the microLED. However, its innovators cannot let up, because the OLED keeps improving, so there's a sense of urgency to accelerate commercialisation and secure some success before OLEDs get too entrenched in all major target applications.

## FURTHER READING / REFERENCE

- ➤ MicroLEDs 2023, Yole Intelligence

- ➤ MiniLEDs 2023, Yole Intelligence

- ➤ MiniLED Displays 2023 Performance and optical construction, Yole Intelligence

- > Sony MicroLED display, Yole Intelligence

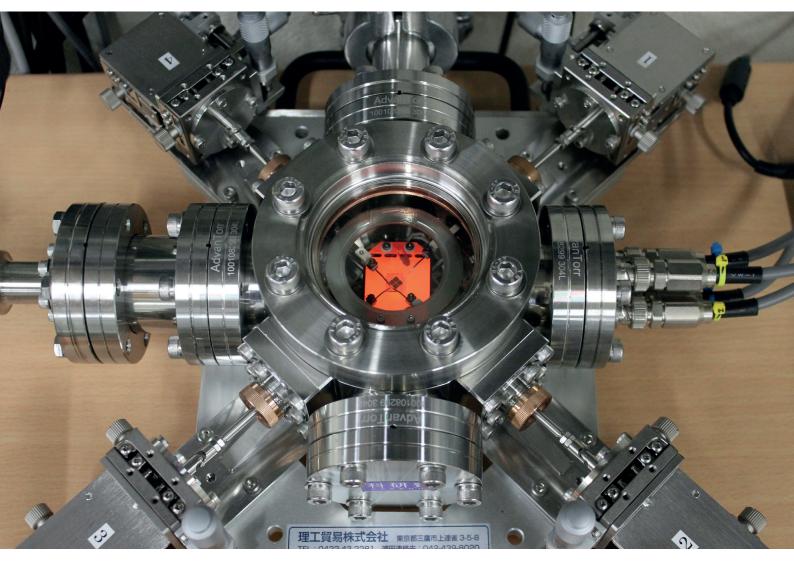

## OCTOPLUS 300

MBE System

## kSA MOS for Stress Measurement

## Control your (thin-film) stress!

- Measure real-time curvature, stress, reflectivity and growth rate

- 2D curvature/stress measurement allows for surface anisotropy determination

- Plus the best support in the industry

- Learn more by visiting our website: k-space.com

A novel showerhead featuring innovative gas injection accelerates MOCVD growth while expanding the palette of epitaxial materials to include AIScN.

BY AARON FINE, FIKADU ALEMA, WILL BRAND, VITALI SOUKHOVEEV, PAUL FABIANO AND ANDREI OSINSKY FROM AGNITRON POWER ELECTRONICS is undergoing a transformation. Silicon is being replaced with the likes of GaN and SiC, members of a family of wide bandgap materials that are enabling devices to be smaller, more efficient and high-performing. But that's just the beginning, with the focus shifting to the new frontier of ultra-wide bandgap materials, primarily AIN and Ga<sub>2</sub>O<sub>2</sub>.

Collectively, silicon's superiors are grabbing an increasing share of the power device market, with total sales projected to to exceed \$10 billion within just a few years. These high-performance alternatives are finding deployment in many sectors, including the military, electric vehicles, power supplies and photovoltaic inverters.

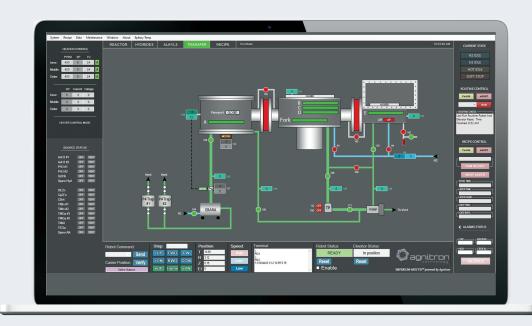

Playing a pivotal role within this dynamic landscape is our company, Agnitron Technology. We are developing and manufacturing an expanding portfolio of OEM semiconductor growth tools, including but not limited to MOCVD, CVD and HVPE technologies.

One of these three forms of deposition, MOCVD, is widely used for the manufacture of power electronics, as well as LEDs and lasers. This epitaxial growth technique, involving the deposition of substances onto a surface in a high-temperature chamber, ensures meticulous control of the film's thickness, its composition, and its quality. These assets make MOCVD ideal for crafting high-performance layered structures in various devices.

It's far from trivial to extend the use of MOCVD to the likes of AIN and  ${\rm Ga_2O_3}$ , due to persistent hardware challenges. At Agnitron, we have recognised and started to address these specific challenges.

### Gen III CIS

The biggest challenges in hardware design are associated with the showerheads, arguably the most crucial component for epitaxial semiconductor material growth. Traditional showerhead design focuses on facilitating multiple separate, consistent, uniform flows of temperature-regulated gases, by utilising various complex machining methods. Unfortunately, these designs result in expensive, fragile showerheads with a limited lifetime. Success has been held back by traditional manufacturing practices, which hamper efforts to realise faster growth rates, uniform film thickness and smooth surfaces – and the ability to grow films previously not possible with standard commercial MOCVD reactors.

Our team at Agnitron has broken through this impasse with an innovative, patent-pending showerhead technology that we incorporate into our vertical CIS Agilis reactors. Our triumph stems from advances in the initial design of the showerhead based on our previous Gen II CIS. When developing this particular reactor, which features a close injection showerhead (CIS), we focused on exploring a novel method for controlling the well-established hydride and alkyl delivery

The Agnitron Agilis 100 features a Gen III Close Space Injection Showerhead, aiding the growth of an AIN film.

system. The immediate outcomes, soon discussed, showcase that this design provides precise control over thickness uniformity and surface roughness, as well as enhancing film growth rates and reducing the particle count on the wafer.

The new showerhead can be applied across different Agilis reactors, for the growth of materials such as GaN, AIN and AIGaN alloys, as well as for oxide-based materials, like Ga<sub>2</sub>O<sub>3</sub> and AIGaO alloys. This innovative showerhead offers tremendous versatility, demonstrated by its ability to be heated to temperatures exceeding 150 °C that allow for the pre-heating of ammonia. This attribute also facilitates the growth of films utilising low vapor pressure precursors. An illustrative case is the growth of ternary and quaternary nitrides, including

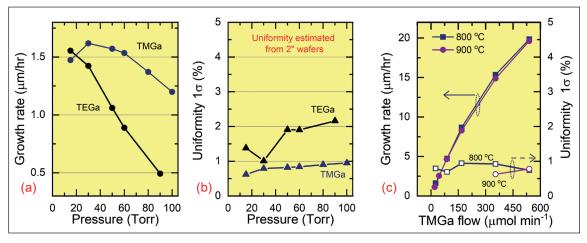

> Figure 1.  $Ga_2O_3$  film growth in an Agilis 100 reactor with the cutting-edge CIS showerhead. The growth rate (a) and uniformity (b) dependencies on chamber pressure for TEGa and TMGa. Growth rate and uniformity versus TMGa molar flow rate (c) for layers grown at substrate temperatures of 800 °C and 900 °C and constant growth pressure of 30 Torr, achieving around 20  $\mu$ m/hr at 540  $\mu$ mol/min with less than 1 percent, 1 $\sigma$  uniformity.

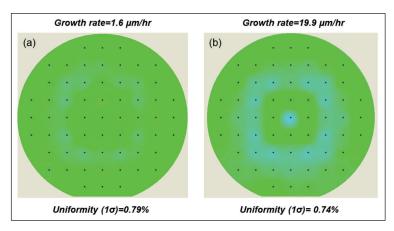

> Figure 2. Ga<sub>2</sub>O<sub>2</sub> twodimensional thickness map on a 50 mm sapphire substrate using the CIS. Films grown at 1.6 µm/hr (a) and 20 μm/hr (b). Uniformity remains below 1 percent for both growth rates. A 2 mm edge exclusion has been applied during the thickness map.

ScAIN, and YAIN, which have garnered a lot of interest recently for expanding the application possibilities of AIN.

## The Agnitron Agilis 100 MOCVD

One of our most prominent tools, the Agnitron's Agilis 100 MOCVD, is recognised for its compact footprint and outstanding adaptability, and is capable of the growth of an incredibly wide variety of materials. Designed for R&D with smaller substrates but capable of accommodating larger wafers up to 100 mm in diameter, this tool can be used to grow: Ga<sub>2</sub>O<sub>3</sub>, AIN, AIGaN, GaN, InGaN, III-V As/P alloys, MgZnO, ZnO, II-IV compounds; transition metal dichalcogenides, such as MoS<sub>2</sub>, MoSe<sub>2</sub>, WS<sub>2</sub>, WSe<sub>2</sub>; phosphorene, two-dimensional hexagonal BN, SiC, ScAIN, and YAIN.

Offering enhanced usability, our Agnitron Agilis 100 integrates optical reflectometry in the UV and blue with Imperium analytical control software to provide real-time measurements of growth rate and thickness. Additionally, the Agilis 100 offers UV light exposure during growth, a feature that ensures effective control of epitaxial film purity by reducing residual carbon incorporation and managing point defects. Moreover, our Agilis 100, along with all

our MOCVD/CVD systems, facilitates seamless plug-and-play switching between sources and gas distribution (showerhead) configurations - this is realised within just a few hours of maintenance. Another notable feature of the Agilis 100 is the option to add precursor distribution nozzles. This enables process refinement and wafer carrier cleaning, enhancing the appeal of these tools across a diverse range of applications.

There are two interchangeable configurations associated with the Agilis 100: the remote injection showerhead (RIS), and the CIS. The primary distinction is the placement of the showerhead relative to the wafer carrier. This ensures adaptable film growth options for meeting various research and development requirements.

Our RIS Agilis 100 reactor, capable of temperatures of over 1600 °C, features a distinctive remote injection showerhead that incorporates an optimised hydride or oxygen injector and uniformly distributes around it metalorganic precursors, such as trimethylgallium and trimethylaluminium. Commonly used for Ga<sub>2</sub>O<sub>2</sub> growth, this configuration encounters two primary challenges. Firstly, film growth is impeded, due to higher gas-phase reactions, resulting from the increased gap between the showerhead and the wafer carrier. Secondly, it is harder to realise uniform film thickness and doping, due to difficulties in maintaining flow laminarity across the wider showerhead-to-wafer carrier gap.

Despite these limitations, our RIS Agilis 100 MOCVD reactor offers exceptional thickness uniformity within a tight process window. This is accomplished by lowering the reactor pressure and introducing high total gas flows to suppress buoyancy, which threatens to lead to flow instabilities. However, while the RIS Agilis 100 enables uniformity below 2 percent across a 50 mm substrate, process efficiency falls, due to high gas and precursor

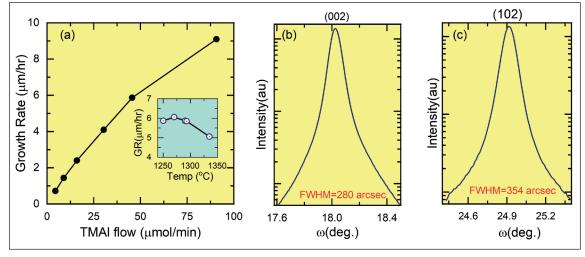

> Figure 3. (a) Growth rate as a function of TMAl molar flow rate. The inset in (a) shows the growth rate as a function of substrate temperature. X-ray rocking curves, obtained with 2.4 μm-thick AlN, show values for the full-width at half maximum of 280 arcsecs (002) (b) and 354 arcsecs (102) (c).

consumption, coupled with the narrow process window

As mentioned earlier, the challenges just discussed can be addressed by equipping the Agilis 100 with the new Gen III CIS showerhead. Note that this is available as an upgrade. We have conducted extensive testing of our Agnitron Agilis 100 reactor for  ${\rm Ga_2O_3}$  growth, with evaluation showcasing the enhanced performance that comes from introducing the new showerhead. This design overcomes the limitations associated with the RIS configuration.

## Agnitron and Ga<sub>2</sub>O<sub>3</sub>

One of the primary applications for our new Gen III CIS showerhead is the growth of epitaxial layers of  $\beta\text{-}\text{Ga}_2\text{O}_3$ , a pivotal material for advancing power device technology. Positioned to shape the future of the power semiconductor market,  $\text{Ga}_2\text{O}_3$  possesses fundamental properties that are conducive to the production of superior power devices while maintaining economic viability through the creation of high-quality melt-grown bulk substrates.

Over a decade of dedicated research in device and materials,  ${\rm Ga_2O_3}$  has demonstrated remarkable progress. Breakthroughs at the device level include a breakdown voltage now exceeding 8 kV and critical breakdown fields of more than 5 MV cm $^{-1}$ , surpassing the theoretical limits of SiC and GaN. Such success has established  $\beta\text{-}{\rm Ga_2O_3}$  as the most promising candidate for next-generation solid-state power-switching applications.

A critical process in the production of any material is the growth of the epitaxial layers. With  $\beta\text{-}\text{Ga}_2\text{O}_3$  films, epitaxy has been extensively explored with various methods. Of these growth technologies, MOCVD stands out for its ability to produce high-quality epitaxial films at a rapid growth rate, ensuring uniformity and controllable doping.

Our team at Agnitron Technology is leading many of the breakthroughs in  ${\rm Ga_2O_3}$  materials – they are spearheaded by the design and building of customised MOCVD reactors and processes for growing high-purity films of this oxide and its related alloys.

Our renowned Agnitron Agilis MOCVD reactors are widely adopted worldwide, utilised in prestigious institutions that include but are not limited to: the University of California, Santa Barbara (UCSB); Cornell University; US Naval Research Laboratory (NRL); the Ohio State University; Arizona State University; the University of Wisconsin; and Bristol University, UK. Our reactors are being used by research teams at these institutions, with these epitaxial tools behind the growth of high-purity  $Ga_2O_3$  films, including those with impressive electron mobilities of nearly  $200\ cm^2\ V^{-1}\ s^{-1}$  at room temperature and over  $23,000\ cm^2\ V^{-1}\ s^{-1}$  at low temperatures. Noteworthy results, underpinned by growth using our Agnitron reactors, have featured in

The results just presented highlight the Agnitron Gen III CIS's remarkable ability to surpass the thickness, doping, and composition uniformity requirements that are essential in production MOCVD, all while maintaining a high growth rate. As well as demonstrating state-of-the-art devices, this new capability offers a cost-effective solution for researchers using MOCVD to make radical breakthroughs in power electronics.

previous issues of CS Magazine – see issues 2 and 7 of 2022, and issue 3 and 6 of 2023.

The availability of native  ${\rm Ga_2O_3}$  substrates, reaching sizes of up to 100 mm in diameter, presents a significant opportunity for commercialising  ${\rm \beta\text{-}Ga_2O_3}$ -based power devices. However, as is often the case with epitaxy, the primary challenge lies in attaining precise thickness and doping uniformity, along with a consistently smooth surface, all while maintaining an industrially feasible growth rate. Our ground breaking Agnitron Gen III CIS showerhead tackles this challenge, offering a solution to elevate film quality. This advance is a critical step towards enhancing film manufacturability, and ultimately positioning  ${\rm \beta\text{-}Ga_2O_3\text{-}based}$  power devices for market success.

## Gen III CIS: Growing Ga<sub>2</sub>O<sub>2</sub>

We incorporated the Gen III CIS showerhead into our Agnitron Agilis 100 reactor for the growth of  ${\rm Ga_2O_3}$ . The results accentuate the showerhead's effectiveness in enhancing growth rates and producing exceptional thickness uniformity (see Figure 1 and 2). Using a substrate temperature of 800 °C, we studied the influence of chamber pressure on the growth rate of films produced

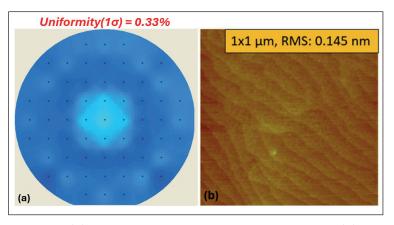

> Figure 4. (a) Thickness map for a 0.73  $\mu$ m-thick AlN film and (b) an atomic force microscopy image of a 2  $\mu$ m-thick AlN layer on a sapphire substrate. Notably, these films showcase exceptional smoothness, with a uniformity of less than 0.33 percent.

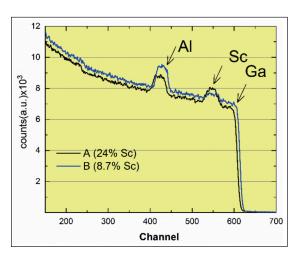

> Figure 5. Rutherford backscattering spectroscopy of ScAlN alloys grown on GaNon-sapphire templates using Agnitron's Agilis 100. The blue trace shows around 9 percent scandium, while the black trace shows 24 percent.

using two different gallium-based precursors: trimethylgallium (TMGa) and triethylgallium (TEGa). When investigating the influence of chamber pressure, we adopted consistent molar flow rates of 46 μmol min<sup>-1</sup> for TEGa and 25 μmol min<sup>-1</sup> for TMGa.

At elevated growth pressures, the growth rate falls for both TEGa and TMGa, due to unintended gas-phase reactions. These reactions deplete the precursor before it reaches the substrate, thereby reducing the necessary substrate surface reactions for film growth.

Despite TEGa having a higher molar flow rate, it is the films grown with TMGa that have a higher growth rate, highlighting the efficiency of the TMGa source. The accelerated growth kinetics of TMGa compared with TEGa stem from a pyrolysis process that involves two steps, rather than three. This enables TMGa to react more rapidly with oxidising gases and have a higher growth rate.

Compared with TEGa, the influence of growth pressure on films grown with TMGa is less pronounced, indicating reduced impact of gasphase reactions for films grown with this precursor. The uniformity of films grown with TMGa is notably superior, consistently measuring below 1 percent, while for TEGa it is below 2.5 percent.

"Unique features like wafer temperatures above 1400 degress C and chamber pressure lower than 50 torr offered by Agilis 100 can help explore optimised process conditions for ultrawide bandgap semiconductors, difficult to achieve with other commercially available reactors." Shubhra S. Pasayat, Assistant Professor, Department of Electrical and Computer Engineering, University of Wisconsin-Madison.

➤ Figure 6. A 0.15 µm-thick film of ScAlN grown on GaN-on-sapphire.

We have also studied the impact of flow rate on the Ga<sub>2</sub>O<sub>2</sub> growth rate. For TMGa it's a linear relationship, with the growth rate reaching approximately 20 µm/hr for a TMGa flow of 540 µmol/min (see Figure 1 (c)).

To evaluate film uniformity under different growth rates with TMGa, we produced thickness maps for two films (see Figure 2). These maps highlight the new showerhead's capacity to produce films with less than 1 percent non-uniformity, irrespective of growth rate.

Another encouraging result is that using silane as a dopant, Ga<sub>2</sub>O<sub>2</sub> films grown at 4.3 µm/hr with TMGa exhibit an electron mobility of 100 cm<sup>2</sup> V<sup>-1</sup> s<sup>-1</sup> and a free carrier concentration of 4.6 x 10<sup>17</sup> cm<sup>-3</sup>. This set of results confirms the new showerhead's ability to produce high-quality Ga<sub>2</sub>O<sub>2</sub> films.

## Gen III CIS: Growing AIN

The significance of AIN cannot be overstated. Blessed with remarkable properties, it is a superb candidate for next-generation high-power electronic and optoelectronic devices. Boasting a substantial bandgap of 6.1 eV, Schottky barriers exceeding 2 eV, an excellent thermal conductivity of more than 150 W m-1 K-1, and critical breakdown fields surpassing 15 MV/cm, AIN holds promise across various applications. To harness its full potential, high-temperature growth by MOCVD is employed, with temperatures exceeding 1300 °C to ensure a low defect density in the epilayers. Ideal for this task is the Agnitron Gen III CIS. Offering exceptional thermal control capabilities, it stands out by easily withstanding temperatures of over 1350 °C, and operating in close proximity to the susceptor, thanks to its new highly efficient thermal management.

Utilising our innovative CIS showerhead, we've conducted extensive tests, growing AIN on 50 mm c-plane sapphire substrates. Our results underscore our showerhead's versatility, allowing for adjustable aluminium molar flow rates and, consequently, demonstrating impressive film growth rates, ranging from 0.7  $\mu$ m/hr to around 9  $\mu$ m/hr (see Figure 3(a)).

We have explored the growth rate's dependence on substrate temperature, finding a less pronounced effect. However, as substrate temperature increases, the gradual decline in growth rate is evident, a parameter we plan to investigate in more detail. Notably, our Agnitron Gen III CIS allows fine tuning of the distance between the showerhead and the wafer – it can be below 10 mm, and more than 35 mm. This tremendous versatility facilitates diverse precursor allocations and growth scenarios, enhancing the showerhead's adaptability to varied experimental conditions.

Using our novel CIS showerhead reactor, we have grown a 2.4 µm-thick AIN layer on sapphire substrates at a growth rate of around 1.0  $\mu$ m/hr. X-ray diffraction indicates excellent crystal quality, with values for the full-width at half maximum of the diffraction peak of around 280 arcsecs and 350 arcsecs in the (002) and (102) directions. respectively (see Figure 3(b) and 3(c)). Note that these results are obtained without optimisation of the process conditions. These AIN thin films have a remarkable thickness uniformity and minimal surface roughness, with a uniformity of less than 0.5 percent for a AIN film that's around 0.7 µm thick, grown at about 0.7 µm/hr (see Figure 4(a)). Outstanding smoothness is evidenced by a rootmean-square roughness of just 0.145 nm for a AlN-on-sapphire film that's 2  $\mu m\text{-thick},$  and grown at 1.3 µm/hr (see Figure 4(b)). These findings underscore the efficacy of our new showerhead in producing high-quality AIN films at a high growth rate that exhibit impressive uniformity and surface characteristics.

## Why ScAIN?

High-performance microwave transistors and amplifiers are vital for wireless communication, with GaN-based HEMTs playing a key role. AlGaN serves as a common barrier material, forming a two-dimensional electron gas at the AlGaN/GaN interface. However, the critical thickness of AlN/GaN is insufficient for forming a Schottky gate contact, resulting in devices with high leakage. Emerging as a promising barrier layer is the alloy scandium aluminium nitride (ScAIN). Due to its high polarisation coefficients, its shows superiority over standard AlGaN barriers.

MOCVD is a promising growth technology for the growth of ScAIN on an industrial scale, as there is the potential to produce high-quality, uniform films on large wafers. However, to date, only the group at Fraunhofer IAF, in Freiburg, Germany, has demonstrated the growth of ScAIN by MOCVD. To address this shortcoming and help unleash the substantial market potential for the ScAIN material

system, we have been developing a commercialscale MOCVD process for ScAIN/GaN HEMTs.

Holding back the growth of ScAIN with existing commercial MOCVD reactors is the lack of scandium-based metal-organic precursors with a sufficiently high vapour pressure. The vapour pressure of these particular precursors is very low, and the introduction of a sufficient flux into the reactor chamber requires heating the sources to a relatively high temperature. That's far from trivial, as it demands that all the gas delivery components - including the mass flow controllers, pressure controllers and valves - sustain an even higher temperature to prevent precursor condensation in the delivery network. This necessitates the use of specialised components and assemblies that are capable of withstanding these far high temperatures. Current commercial MOCVD reactors are not designed to deliver such low-vapour-pressure precursors, as they are commonly built to handle the traditional metal organics, which have sufficiently high vapour pressure, even at room temperature.

We have addressed the challenge of gas delivery of scandium-based sources by developing and implementing a specialised high-temperature gas delivery system. We heat the source to 150 °C, and maintain the gas delivery network near 200 °C. By integrating this system with our Agnitron Agilis 100 reactor, we have developed the growth processes for producing high-quality ScAIN thin films on wafers up to 50 mm in diameter using commercially available scandium sources. Our ScAIN alloys have scandium compositions that can exceed 40 percent, despite an unoptimised process.

To evaluate the absorption band edge shift and the crystal quality of our ScAIN films, we have turned to optical transmission and X-ray diffraction. These techniques consistently demonstrate the successful incorporation of scandium into the AIN lattice while preserving the wurtzite structure. We meticulously control scandium integration by adjusting the source temperature, reactor pressure, substrate

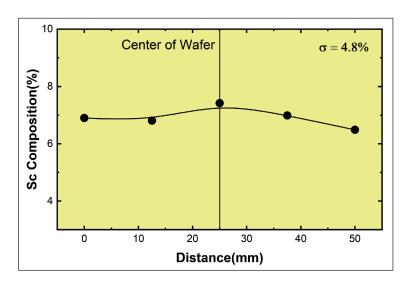

> Figure 7. Composition of a ScAlN film measured by Rutherford backscattering spectroscopy across the diameter of a 50 mm wafer. The average composition and coefficient of variation are 7 percent and 4.8 percent, respectively.

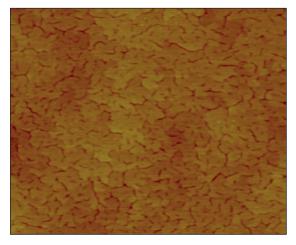

> Figure 8. A 2 µm by 2 µm scan of a ScAlN/ GaN HEMT structure grown on SiC. The root-meansquare (RMS) roughness is 0.20 nm.

temperature and ammonia flow rate. For accurate determination of the scandium composition in our ScAIN thin films, we utilise both energy-dispersive X-ray spectroscopy and Rutherford backscattering spectroscopy. The results from both techniques are in good agreement (see Figure 5 for Rutherford backscattering spectroscopy results, highlighting peaks for scandium, aluminium and gallium in four films).

Introducing our Gen III showerhead for ScAIN growth delivers a remarkable performance. Consistently, it is capable of producing highly uniform ScAIN films with a thickness uniformity of less than 1 percent. We investigated the scandium compositional uniformity of these films with Rutherford backscattering spectroscopy (see Figure 6). The measurements reveal a uniform scandium content across the entire wafer: the average scandium composition is 7 percent, and the variation is 4.8 percent of the mean value (see Figure 7). These preliminary results show a promising compositional uniformity, and we expect further improvement following the manipulation of showerhead temperature and process flowrates. The root-mean-square (RMS )surface roughness of

a ScAIN/AIN/GaN HEMT structure, grown on SiC substrate, is just 0.2 nm (see Figure 8). In the non optimized ScAIN/GaN HEMT structure sheet carrier concentration was measured 1.9 x 10<sup>13</sup> cm<sup>-2</sup> and electron mobility about 900 cm<sup>2</sup> V<sup>-1</sup> s<sup>-1</sup>.

Success with ScAIN opens the door to the growth of a number of technologically significant nitride materials that have to be grown with low-vapour pressure precursors. They include transition metal nitrides, such as NbN and YAIN.

The results just presented highlight our Agnitron Gen III CIS's remarkable ability to surpass the thickness, doping, and composition uniformity requirements that are essential in production MOCVD, all while maintaining a high growth rate. As well as demonstrating state-of-the-art devices, this new capability offers a cost-effective solution for researchers using MOCVD to make radical breakthroughs in power electronics.

### Innovation pedigree

Standing at the forefront of semiconductor innovation, our team at Agnitron Technology is revolutionising the growth of wide and ultrawide bandgap materials with our ever-advancing portfolio of cutting-edge MOCVD tools. Our focus on overcoming longstanding challenges in showerhead design has spurred the introduction of the Gen III CIS showerhead, showcased in the Agilis 100 reactor. The results obtained with this tool are transformative, enabling us to demonstrate enhanced growth rates, improvements to thickness and alloy composition uniformity, and a film quality exceeding production MOCVD standards. Success on all these fronts comes while maintaining a high growth rate. As well as delivering exceptional performance, the Agnitron Agilis 100 MOCVD system stands out from the crowd for its adaptability and seamless configuration changes. This tremendous versatility enables a spectrum of epitaxial growths, allowing users to explore any imagined possibilities.

As we continue to push the boundaries of materials growth, our tools and growth technologies are paving the way for advancements in power electronics, while solidifying our position as a leader in the semiconductor research equipment manufacturing industry. Our belief is that by focusing on such innovation, we will bolster the future viability of our customers to bring their products to market faster, more reliably, with higher quality and thus make a more meaningful contribution to society at large.

Agnitron would like to acknowledge Greg Haugstad of the University of Minnesota Characterization Facility (UMN CharFac) for conducting RBS measurements and Prof. Chirag Gupta of the University of Wisconsin Madison for XRD measurements.

## FURTHER READING / REFERENCE

- $\triangleright$  F. Alema et al. "Fast growth rate of epitaxial  $\beta$ -Ga<sub>2</sub>O<sub>3</sub> by close coupled showerhead MOCVD" J. Cryst. Growth 475 77 (2017)

- ➤ G. Seryogin et al. "MOCVD growth of high purity Ga<sub>2</sub>O<sub>2</sub> epitaxial films using trimethylgallium precursor" Appl. Phys. Lett. **117** 262101 (2020)

- Y. Zhang et al. "MOCVD grown epitaxial  $\beta$ -Ga<sub>2</sub>O<sub>3</sub> thin film with an electron mobility of 176 cm<sup>2</sup>/V s at room temperature", APL Mater. 7 022506 (2019)

- M. Baldini et al. "Semiconducting Sn-doped β–Ga<sub>2</sub>O<sub>3</sub> homoepitaxial layers grown by metal organic vapour-phase epitaxy" J. Mater. Sci. 51 3650 (2015)

- ➤ S. Manna et al. "Tuning the piezoelectric and mechanical properties of the AIN system via alloying with YN and BN" J. Appl. Phys. 122 105101 (2017)

- S. Leone et al. "Metal-Organic Chemical Vapor Deposition of Aluminum Scandium Nitride" Phys. Status Solidi RRL 14 1900535 (2020)

## Upgrade your legacy equipment

with state-of-the-art process control, automation, and monitoring capabilities

## Real-time control, monitoring, and analysis

- Currently running in over 100x systems worldwide

- Intuitive user-friendly interface

- Future process data comparison capability

- Utilize databases to extend equipment life, past 20 years

- Continuous support and maintenance

- No subscriptions or annual service fees

- Highly customizable Imperium Software Modules