# COMPOUND 35 SEMICONDUCTOR

CONNECTING THE COMPOUND SEMICONDUCTOR COMMUNITY

VOLUME 31 ISSUE I 2025

AN ANGEL BUSINESS COMMUNICATIONS PUBLICATION

COMPOUNDSEMICONDUCTOR.NET

# AIXTRON

# THE NEW G10 SERIES

Your Productivity Solution for All Advanced Epitaxy Materials

#### G10-SiC

- ▶ 9x150 mm (6") or 6x200 mm (8")

- New hardware & process surpassing Single Wafer Reactor uniformities

- ► +50% productivity per fab area with large batch technology & small footprint

#### **End Markets/Products:**

EV inverters & charging infrastructure

#### G10-GaN

- ▶ 8x150mm (6") or 5x200mm (8")

- ▶ 1st fully automated compact GaN MOCVD cluster designed 100% for Si Power fabs

- Novel hardware solution for unmatched barrier uniformities and device yields

#### **End Markets/Products:**

Power Electronics & Wireless communication

#### G10-AsP

- ▶ 8x150 mm (6") or 5x200 mm (8")

- ▶ 1<sup>st</sup> fully automated AsP MOCVD system enabling 10x lower defect density

- Unmatched wavelength uniformity on all wafer sizes

#### **End Markets/Products:**

Micro LED, Optical Data communication, 3D-sensing & LiDAR

# **VIEWPOINT**

BY RICHARD STEVENSON, EDITOR

## New beginnings

The ending of one year and the beginning of another always offers the opportunity to make a fresh start. For some of us, this will take the form of a handful of New Year resolutions, or a to-do list – but for others, it's simply a chance to leave behind what's gone wrong and embark on a new chapter of our lives.

At the start of a new year, it's not only you and I that can strike out in a different direction with renewed vigour. Companies can do it too. This may come from the top and permeate down. But it can also be inspired by employees, returning recharged and enthused from a break over the Christmas holidays to devise and implement new plans in January that promise greater growth and profitability.

Two of the stalwarts of our industry, Wolfspeed and IQE, will certainly be keen to put their recent past behind them and blaze a new path. Both parted ways with their CEOs in the final quarter of 2024, a year that saw their share prices plummet – in the case of the SiC pioneer, by 80 percent.

While Wolfspeed has not excelled in recent times under the leadership of its ex-CEO, Greg Lowe, history may view him kindly – he led the re-direction of the company from the production of LEDs to a more promising future.

Whoever succeeds Lowe will not find it easy to turn Wolfspeed's fortunes around. Growth in the EV market has been more sluggish than hoped, and this maker of SiC substrates and devices has had to shelve plans to build a new fab in Germany, and is closing a facility at its Durham headquarters. Wolfspeed is also in the process of shedding 20 percent of its workforce, a painful move that will lead to a loss of hard-won expertise.

It's also going to be a challenge to replace IQE's recent leader, Americo Lemos. He had a tough ask, having to take

over from the company's charismatic founder, Drew Nelson, who understand both the technology and the business inside out.

What should concern anyone willing to have a crack at leading this global leader of epiwafer manufacturing is that whether our industry is booming or going through tougher times, IQE is yet to deliver a financial performance that has led to lucrative dividends for its shareholders. While it is clear that the outsourcing model can generate business within our industry, one may wonder if it can ever provide a healthy financial return to investors over many years.

There's no doubt that when the new leaders of IQE and Wolfspeed are appointed, they will initially face some difficult decisions. But at least they are working in an industry that is sure to grow, as compound semiconductors continue to play an ever-increasing role in all of our lives, throughout 2025 and beyond.

## 24 Multiple materials vie for RF success

Researchers at the recent International Electron Devices Meeting reported breakthroughs in RF devices made from many different materials

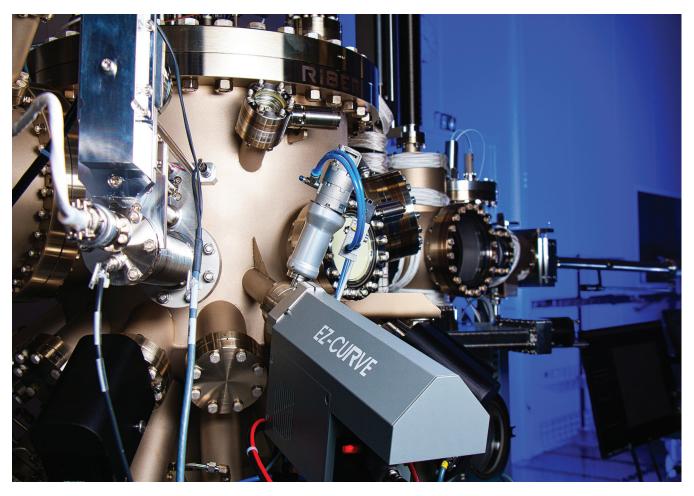

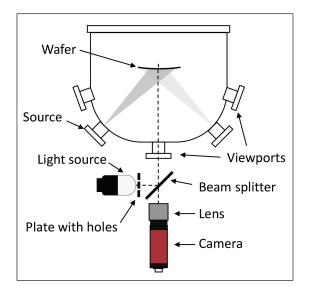

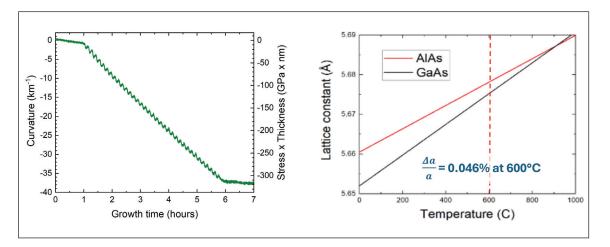

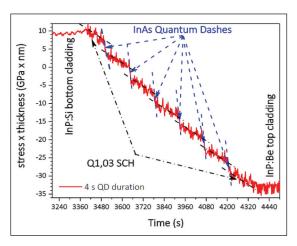

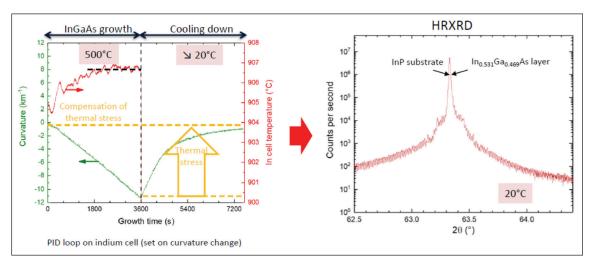

## 32 Gaining greater insight into the epitaxial process

A new generation of *in-situ* tools enables engineers to delve far deeper into the details of their epitaxial processes

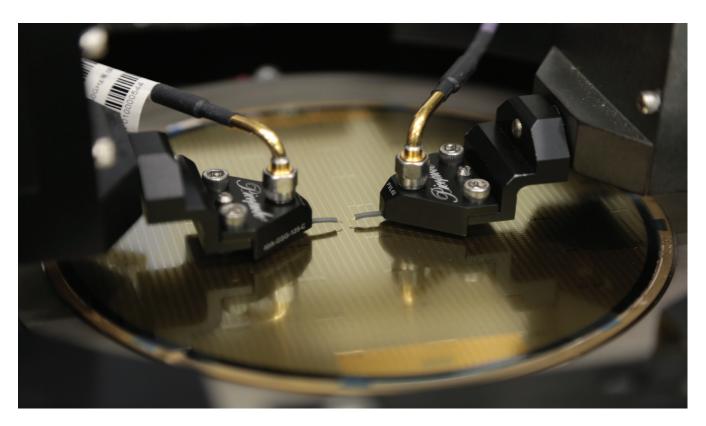

## 36 Manufacturing miniaturised GaAs power amplifiers

Introducing a foundry service for 70 nm GaAs pHEMTs supports the production of power amplifiers operating at frequencies up to hundreds of gigahertz

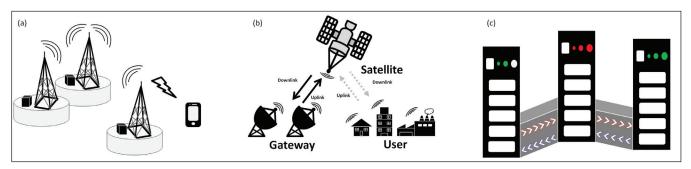

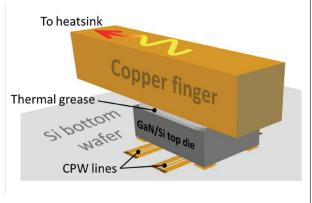

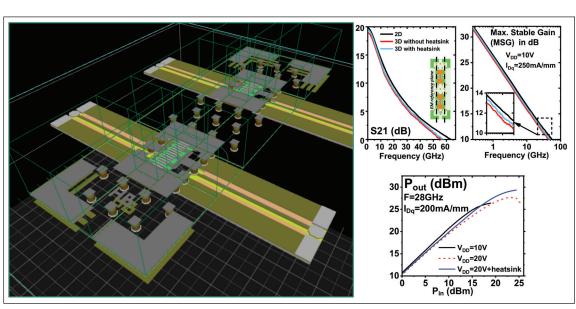

## 40 Boosting the bang-per-buck with RF integration

The hybrid integration of GaN and silicon paves the way for high-efficiency, cost-effective 5G and millimetre-wave RF systems that provide a cutting-edge power density and scalability

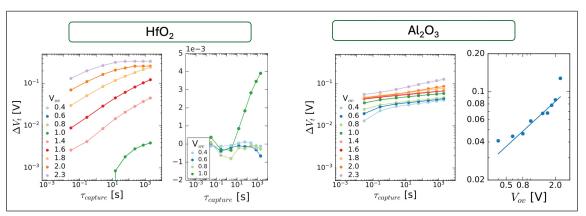

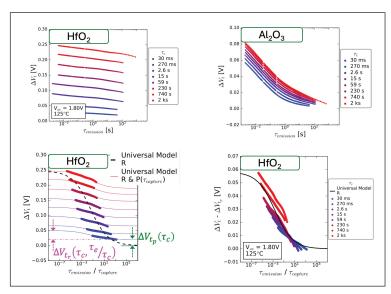

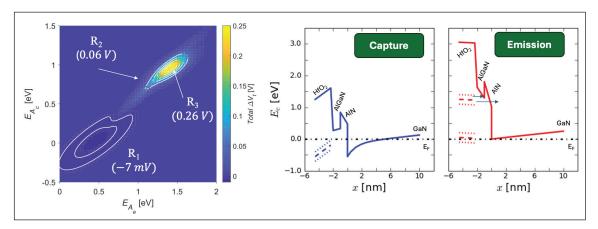

## 46 Scrutinising traps in GaN MOS-HEMTs

Experiments expose the physical and energetic locations of defects that are impairing the performance and reliability of GaN MOS-HEMTs operating in 5G millimetre-wave bands

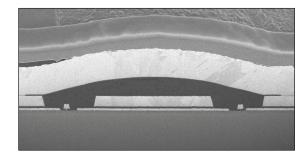

#### 52 Revolutionising semiconductor etching

Metal-assisted chemical etching is a damage-free process that produces trenches with an unprecedented aspect ratio

#### **NEWS ANALYSIS**

#### 14 300 mm SiC: A format for when?

Is the unveiling of a 300 mm SiC substrate by SICC going to drive a relatively rapid shift to high-volume production with this format?

#### 16 Going through the gears with gallium nitride

VisIC plans to ramp production of its GaN depletionmode HEMTs for electric vehicle inverters before the end of this decade

#### RESEARCH REVIEW

58 Realising red LEDs on ScAlMgO<sub>4</sub> substrates

- 59 SiC MOSFETs: Understanding the benefits of plasma nitridation

- 61 A debut for the native AIN transistor

#### **NEWS**

- 06 Bosch nets \$225 million for US

- 07 Imec makes breakthrough with GaAs lasers on silicon

- 08 Polar Light Tech makes microLED breakthrough

- **09** GF gets \$9.5 million for GaN chip production

- 10 EU project to develop high-voltage DC WBG tech

- 11 Aixtron opens innovation centre

- 12 XDC and Lumileds develop novel 140 pixel-per-inch microLED display

- 13 IQE and Quintessent partner on QD lasers for Al

Editor Richard Stevenson richardstevenson@angelbc.com +44 (0)1291 629640

News Editor Christine Evans-Pughe christine.evans-pughe@angelbc.com

**Design & Production Manager** Mitch Gaynor

mitch.gaynor@angelbc.com +44 (0)1923 690214

**Director of Logistics** Sharon Cowley sharon.cowlev@angelbc.com +44 (0)1923 690200

Senior Sales Executive Jacob Caulfield

iacob.caulfield@angelbc.com +44 (0)2476 718979

Senior Logistics Executive

Eve O'Sullivan +44 (0)2476 823 123 eve.osullivan@angelbc.com Circulation

Scott Adams scott.adams@angelbc.com

Publisher Jackie Cannon jackie.cannon@angelbc.com +44 (0)1923 690205

Chief Executive Officer

Sukhi Bhadal sukhi.bhadal@angelbc.com +44 (0)2476 718970

Chief Technical Officer

Scott Adams scott.adams@angelbc.com +44 (0)2476 718970

Directors

Jackie Cannon Sharon Cowley Published by

Angel Business Communications Ltd 6 Bow Court, Fletchworth Gate Burnsall Road, Coventry CV5 6SP, UK. T: +44 (0)2476 718 970 E: info@angelbc.com

Compound Semiconductor is published nine times a year on a controlled circulation basis. Non-qualifying individuals can subscribe at: £115.00 per annum (UK), €165 per annum (Europe), \$198 per annum (air mail) (USA). Cover price £4.50. All information herein is believed to be correct at time of going to press. The publisher does not accept responsibility for any errors and omissions. The views expressed in this publication are not necessarily those of the publisher. Every effort has been made to obtain copyright permission for the material contained in this publication. Angel Business Communications Ltd will be happy to acknowledge any copyright oversights in a subsequent issue of the publication. Angel Business Communications Ltd (Copyright 2025, All rights reserved. Contents may not be reproduced in whole or part without the written consent of the publishers. The paper used within this magazine is produced by chain of custody certified manufacturers, guaranteeing sustainable sourcing. US mailing information: Compound Semiconductor, ISSN 1096-598X, USPS Permit Number 25366, is published 9 times a year, Combined Jan/Feb, March, Combined April/May, June, July, Combined August/September, October, November, December by Angel Business Communications Ltd, Unit 6, Bow Court, Fletchworth Gate, Burnsall Rd, Coventry CV5 65P, UK, Airfreight and mailing in the USA by agent named World Container INC 150-15, 183rd St, Jamaica, NY 11413, USA. Periodicals Postage Paid at Brooklyn, NY 11256. POSTMASTER: Send address changes to Compound Semiconductor, Air Business Ltd, c/o World Container INC 150-15, 183rd St, Jamaica, NY 11413, USA. Periodicals Postage Paid at Brooklyn, NY 11256. POSTMASTER: Send address changes to Compound Semiconductor, Air Business Ltd, c/o World Container INC 150-15, 183rd St, Jamaica, NY 11413, USA. Periodicals Postage Paid at Brooklyn, NY 11256. POSTMASTER: Send address changes to Compound Semiconductor, Air Business Ltd, c/o World Container INC 150-15, 183rd St, Jamaica, NY 11413, USA. Periodicals Posta Jamaica, NY 1143, USA. We strive for accuracy in all we publish; readers and contributors are encouraged to contact us if they recognise an error or omission. Once a magazine edition is published [online, in print or both], we do not update previously published articles to align old company names, branding, marketing efforts, taglines, mission statements or other promotional verbiage, images, or logos to newly created or updated names, images, typographic renderings, logos (or similar) when such references, the cacurately stated, rendered or displayed at the time of the original publication. When companies change their names or the images/text used to represent the company, we invite organizations to provide Angel Business Communications with a news release detailing their new business objectives and/or other changes that could impact how customers/prospects might recognise the company, contact the organisation, or engage with them for future commercial enterprise.

Printed by: The Manson Group. ISSN 1096-598X (Print) ISSN 2042-7328 (Online) © Copyright 2025

## Bosch nets \$225 million for US SiC fab

Proposed project could comprise more than 40 percent of all US-based SiC device manufacturing capacity

THE Department of Commerce has signed a preliminary memorandum of terms with Bosch to provide proposed funding of \$225 million to expand the company's SiC, factory in Roseville, California.

Under the agreement, the United States would support Bosch's investment of \$1.9 billion to modernise its SiC manufacturing facility under the CHIPS and Science Act, enabling the company to produce chips on 200 mm wafers starting in 2026, the Commerce Department said.

This funding would support the expansion of Bosch's largest SiC device factory globally, which would significantly increase the company's production capacity and create up to 1,000 construction jobs and up to 700 manufacturing, engineering, and

research and development jobs in California.

When at full capacity, the project is expected to produce the majority of Bosch's total capacity of SiC semiconductors and could comprise more than 40 percent of all US-based SiC device manufacturing capacity.

Bosch, a tier 1 automotive supplier, is differentiated by having specialised semiconductor business within its portfolio. In addition, Bosch is a leading provider of trench gate SiC semiconductors for the car industry.

"The Roseville investment enables Bosch to locally produce SiC semiconductors, supporting US consumers on the path to electrification," said Paul Thomas, president of Bosch in North America

and Bosch Mobility Americas.

"Producing this key technology in the US underscores our leadership in the mobility market."

Bosch expects to produce its first chips on 200 mm wafers in its Roseville facility starting in 2026. The facility will perform both front-end device manufacturing and backend testing, sorting and dicing processes.

# Imec makes breakthrough with GaAs lasers on silicon

Fabrication of electrically-pumped nano-ridge lasers on 300 mm wafers highlights the potential of direct epitaxial growth of III-V materials on silicon

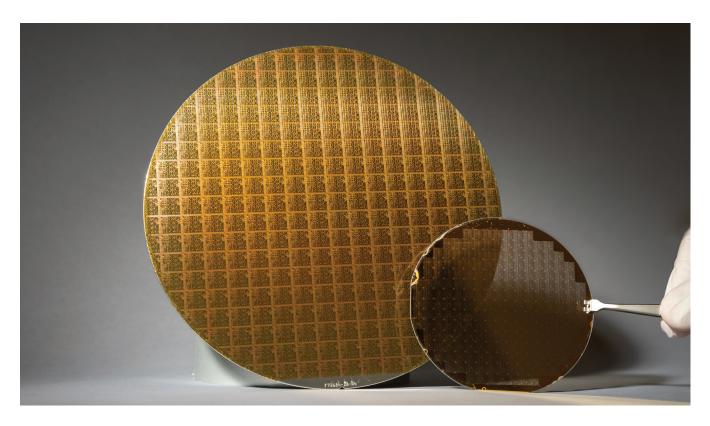

BELGIAN research organisation Imec has announced a significant milestone in silicon photonics with the successful demonstration of electrically-driven GaAs-based multi-quantum-well nanoridge laser diodes fully, monolithically fabricated on 300 mm silicon wafers in its CMOS pilot prototyping line.

Achieving room-temperature continuous-wave lasing with threshold currents as low as 5 mA and output powers exceeding 1 mW, the results, detailed in *Nature*, demonstrate the potential of direct epitaxial growth of high-quality III-V materials on silicon. This breakthrough provides a pathway to the development of cost-effective, high-performance optical devices for applications in data communications, machine learning and artificial intelligence, according to Imec.

The lack of highly scalable, native CMOS-integrated light sources has been a major roadblock for the widespread adoption of silicon photonics. Hybrid or heterogeneous integration solutions, such as flip-chip, micro-transfer printing or die-to-wafer bonding, involve complex bonding processes or the need for expensive III-V substrates, which are often discarded after processing. This not only increases costs but also raises concerns about sustainability and resource efficiency. For that reason, the direct epitaxial growth of high-quality III-V optical gain materials selectively on large-size silicon photonics wafers remains a highly sought-after objective.

The large mismatch in crystal lattice parameters and thermal expansion coefficients between III-V and silicon materials inevitably initiates the formation of crystal misfit defects, which are known to deteriorate laser performance and reliability. Selective-

area growth (SAG) combined with aspect-ratio trapping (ART) significantly reduces defects in III-V materials integrated on silicon by confining misfit dislocations within narrow trenches etched in a dielectric mask.

"Over the past years, Imec has pioneered nano-ridge engineering, a technique that builds on SAG and ART to grow low-defectivity III-V nano-ridges outside the trenches. This approach not only further reduces defects, but also enables precise control over material dimensions and composition. Our optimised nano-ridge structures typically feature threading dislocation densities well below 10<sup>5</sup> cm<sup>-2</sup>. Now, Imec exploited the III-V nano-ridge engineering concept to demonstrate the first full wafer-scale fabrication of electrically pumped GaAs-based lasers on standard 300 mm silicon wafers, entirely within a CMOS pilot manufacturing line," says Bernardette Kunert, scientific director at Imec.

Leveraging the low-defectivity GaAs nano-ridge structures, the lasers integrate InGaAs multiple quantum wells as the optical gain region, embedded in an *in-situ* doped *p-i-n* diode and passivated with an InGaP capping layer. Achieving room-

temperature, continuous-wave operation with electrical injection is a major advancement, overcoming challenges in current delivery and interface engineering. The devices show lasing at around 1020 nm with threshold currents as low as 5 mA, slope efficiencies up to 0.5 W A<sup>-1</sup>, and optical powers reaching 1.75 mW, showcasing a scalable pathway for high-performance silicon-integrated light sources.

"The cost-effective integration of highquality III-V gain materials on largediameter silicon wafers is a key enabler for next-generation silicon photonics applications. These exciting nano-ridge laser results represent a significant milestone in using direct epitaxial growth for monolithic III-V integration," said Joris Van Campenhout, fellow Silicon Photonics and director of the industry-affiliation R&D program on Optical I/O at Imec.

This project is part of a larger pathfinding mission at Imec to advance III-V integration processes towards higher technological readiness, from flip-chip and transfer-printing hybrid techniques in the near term, over heterogeneous wafer- and die-bonding technologies and eventually direct epitaxial growth in the longer term.

## Polar Light Tech makes microLED breakthrough

Red pyramidal microLED is based on the same material as green and blue

SWEDEN-BASED Polar Light Technologies has realised red light of 625 nm based on its non-etching bottom-up concept. This means the company has built red, green, and blue pyramidal microLEDs using the same material compound.

The pyramidal design has the ability to be manufacturable while maintaining excellent microLED performance, laying the foundation for monolithic RGB displays, according to Polar.

Blue and green microLEDs have been in the market for years, but reaching a red colour has been difficult, due to fundamental challenges in the material properties. There are several workarounds or alternatives for reaching a red colour, but they all come with some compromises, such as efficiency, manufacturability, or the need to integrate with other material systems.

"Pursuing Polar Lights' innovative pyramidal LED concept has been about overcoming those challenges without compromises. Thanks to a great tech team, we have succeeded in realizing the red-emitting microLEDs based on our innovative pyramidal structure", says Lisa Rullik, CTO of Polar Light Technologies.

Polar Light Technologies' microLED is composed of pyramid shapes that are built with a novel bottom-up approach,

a technology that has a number of benefits, according to the company.

One is that the inevitable strain in the lattice-mismatched InGaN/GaN structures is reduced, which is important to be able to manufacture blue, green, and red microLEDs with the same material system, that is, to build monolithic RGB.

The approach also makes it possible to integrate the frontplane with a backplane.

In addition, no etching is needed, which means performance is maintained for smaller dimensions, since no etching damages occur.

Other benefits are that it enables nanoLEDs, it is easier to manufacture and integrate with CMOS and TFT, and it there is a narrow emission cone, which is important for microprojectors.

#### Rohm develops 1 kW class infrared laser diode

ROHM has developed a high output infrared laser diode - RLD8BQAB3 for use in Advanced Driver Assistance Systems (ADAS) equipped with lidar for distance measurement and spatial recognition.

The 125 W, 8 channel (1 kW class) arraytype product is the latest in a range of devices based on patented technology to achieve the narrow emission width of lasers, enhancing long-distance, high accuracy lidar.

Rohm will initially start supplying samples for consumer and industrial applications, such as drones, robot vacuum cleaners, automated guided vehicles, and service robots.

Lidar is seeing growing adoption in recent years across a variety of applications that require automation. But to detect information at greater distances with more accuracy, there is a need for laser diodes that serve as light sources to achieve high kilowattlevel output while allowing multiple light sources to emit light at close intervals.

The RLD8BQAB3 is an ultra-compact surface mount device designed for lidar applications that use 3D time-offlight systems to carry out distance measurement and spatial recognition. The optimised design features eight emission areas (each 300 µm wide) per element, installed on a submount affixed to a high heat dissipation substrate.

The package's emitting surface incorporates a clear glass cap - an industry first for a surface mount laser diode – eliminating the risk of light scattering caused by scratches during dicing that tends to occur with resin-

encapsulated products, ensuring high beam quality.

Each emission area is wired with a common cathode, enabling the selection of the irradiation method based on application needs - ranging from individual emission that increases the number of light-emitting points to industry-leading simultaneous emission at ultra-high outputs of 1 kW class.

The new product retains the key features of Rohm's conventional laser diodes, including uniform emission intensity across the emission width.

On top of that, the array configuration narrows the regions of reduced emission intensity between channels, while the bandpass filter minimises the effects of ambient light noise from the sun and other sources.

## GF gets \$9.5 million for GaN chip production

Funding moves GF closer to large-scale production of next-gen GaN chips for RF and high-power applications

GLOBALFOUNDRIES (GF) has received an additional \$9.5 million in federal funding from the US government to advance the manufacturing of GF's essential GaN-on-silicon semiconductors at its facility in Essex Junction, Vermont.

The funding moves GF closer to largescale production of GaN chips.

With the award, GF will continue to add new tools, equipment and prototyping capabilities to its market-leading GaN IP portfolio and reliability testing as the company moves closer to full-scale manufacturing of its 200 mm GaN chips in Vermont.

"GF is proud of its leadership in GaN chip technology, which is positioned to make game-changing advances across multiple end-markets and enable new generations of devices with more energy-efficient RF performance and faster-charging, longer-lasting batteries," said Nicholas Sergeant, VP of IoT and aerospace and defence at GF.

"We appreciate the US government's partnership and ongoing support of our GaN programme. Realising full-scale GaN chip manufacturing will be a catalyst for innovation, for both

our commercial and government partners, and will add resilience and strengthen the semiconductor supply chain."

The new funding, awarded by the US Department of defence's Trusted Access Program Office (TAPO), represents the latest federal investment to support GF's GaN programme in Vermont.

"This strategic investment in critical technologies strengthens our domestic ecosystem and national security, and ensures these assets are readily available and secure for DoD utilisation.

In concert with key partners, this approach fortifies defence systems, empowering resilience and responsiveness," said Nicholas Martin, director at defence Microelectronics Activity. In total, including the new award, GF has received more than \$80 million since 2020 from the US government to support research, development and advancements to pave the way to full-scale GaN chip manufacturing.

## EU project to develop high-voltage DC WBG tech

'MoWiLife' project to produce SiC and ultra-wide-bandgap devices for DC wind and solar energy applications

A NEW three-year multi-partner Horizon Europe funded project, called MoWiLife (Condition Monitoring and Wide Bandgap Power Electronics – Leading Innovations for the European Energy Sector), will be working on technology for DC wind and solar energy applications.

This includes the development of a 2.3 kV SiC MOSFET with temperature sensing and self-protection features. Additionally, the project explores the potential of ultra-high voltage and ultra-wide bandgap semiconductors, including diamonds as semiconductor materials, for energy savings.

The project features two wind energy converter pilots and two university-developed pilots: a TRL 5 DC-DC converter and a TRL 5 DC circuit breaker.

The basis for the four pilots is the 2.3 kV SiC MOSFET, which will be developed by project partner Infineon. It includes a source-gate *p-i-n* diode, whose on-state voltage has a strong temperature dependence and can be read out by the gate drive, which will be developed by Rostock University. In addition, self-protection features will be integrated into the SiC chip for robustness and direct water cooling will be realised for higher output power.

The two wind energy converter pilots

are being realised by two industrial partners. A leader in wind energy, Vestas – supported by University of Aalborg – will develop a TRL 6 SiC converter with +20 percent power density and digitaltwin Condition and Health Monitoring. The start-up RKL, together with Rostock University, will develop a TRL 5 wind energy power stack with Condition and Health Monitoring based on online chip temperature and on-state voltage measurement.

Solar medium-voltage DC collection grids and meshed high-voltage transmission grids will play an important role in the future. As third and fourth pilots, a TRL 5 DC-DC converter and a TRL 5 DC circuit breaker, including condition monitoring, are being developed by the MoWiLife university partners KTH Stockholm and

the University of Aberdeen.

The Aberdeen HVDC research team will be responsible for developing and validating a functional SiC MOSFET hybrid high-voltage DC circuit breaker, which builds on previous research projects at Aberdeen.

Jovcic said: "DC electrical systems have not been much utilised since AC systems have been preferred with traditional overland power transmission and conventional electricity generation. However, AC power can only be transmitted over relatively short distances with subsea cables, and as we look increasingly to offshore wind or tidal technology to meet growing demand, solutions are needed to create high-voltage DC connections and to eventually develop an HVDC grid."

#### US ITC says Innoscience infringed EPC GaN patent

EFFICIENT POWER CONVERSION (EPC) has announced the conclusion of the Presidential review period for the US International Trade Commission's (ITC) final determination, affirming that Chinese GaN firm Innoscience infringed EPC's foundational patent for GaN technology.

The ITC's decision is now final, implementing an import and sales ban on Innoscience products in the United

States without a license from EPC. "This ruling marks a milestone for EPC and fair competition in GaN technology," said Alex Lidow, CEO and co-Founder of EPC. "We will safeguard our IP to drive innovation and support our customers in shaping the future of power electronics."

EPC's case against Innoscience began in May 2023, culminating in the ITC's final determination issued in July 2024. EPC's intellectual property has been consistently upheld across multiple jurisdictions, including the China National Intellectual Property Administration's decisions in April and May 2024.

EPC says this decision opens new pathways for it to expand access to its technology through licensing agreements, fostering collaboration and innovation with global partners.

## Aixtron opens innovation centre

Company prepares for transition to 300 mm wafers for GaN and other compound semiconductor applications

MONA NEUBAUR, Minister for Economic Affairs of the State of North Rhine-Westphalia, Germany, has opened Aixtron's new Innovation Centre at the company's headquarters in Herzogenrath.

The high-tech building is designed for the next big step in compound semiconductor technology: the transition to 300 mm wafers for GaN and other compound semiconductor applications.

The larger wafer size offers customers the productivity gain of 2.25 times more wafer area compared with the currently used 200 mm wafers.

Furthermore, customers can use their 300 mm fabs and processing equipment for the first time for compound semiconductors. This will make the production of GaN semiconductor devices not only more cost-effective, but offer opportunities to technology performance gains in the future.

"With the new 300 mm-capable cleanroom at the Innovation Centre, we will further expand our technological market leadership," said Aixtron CEO Felix Grawert. "We already have the first 300 mm GaN prototype systems, which have also been integrated into pilot lines at several customers. And this is precisely where Aixtron's innovative strength and DNA come into play."

"With 300 mm wafer technology, we are bringing compound semiconductors for the first time into the mainstream of the semiconductor fabrication. The Innovation Center is a major element of our strategy, providing space and capabilities for next-generation technologies. The step towards 300 mm in compound semiconductors is a landmark milestone, that is set to trigger numerous growth options for the industry in the years to come." explains Michael Heuken, VP of Advanced Technologies at Aixtron.

Neubaur said: "Aixtron's new innovation centre is an impressive example of the innovative strength and future viability of the semiconductor industry in North Rhine-Westphalia. The launch of 300 mm wafer technology is a

Pictured from left to right: Beniamin Fadavian. Felix Grawert. Mona Neubaur, Christian Danninger

milestone for the energy efficiency and competitiveness of our region. Our global competitiveness benefits enormously from robust domestic semiconductor production, because semiconductors are essential for the transformation towards climate neutrality: without them, no computer would run, no car would drive, and neither wind nor solar plants could produce energy."

#### **Advanced Compound Semiconductor Foundry Services**

MOCVD · Fabrication · Testing

Advanced III-V semiconductor solutions for optoelectronics application in the biotechnology, telecommunications, energy, industrial, and security industries.

MasimoSemiconductor.com | 603-595-8900

## XDC and Lumileds develop novel 140 pixel-perinch microLED display

High assembly yield of 13 x 20 μm<sup>2</sup> LEDs and microlCs demonstrate readiness for volume production

X DISPLAY COMPANY (XDC), a developer of semiconductor devices for displays, and LED company Lumileds, have developed a 140 pixels-per-inch (ppi) microIC-driven microLED prototype display.

MicroICs are an XDC innovation that integrate the display driver with the emitters, replacing the traditional TFT backplane to bring benefits in power consumption and visual performance.

The companies describe the novel display technology as a milestone for microLED displays in mobile consumer applications including smartwatches, smartphones, tablets, and PCs.

"We see a lot of potential for microLED displays in mobile consumer electronic devices" said Ross Young, CEO of DSCC. "This XDC and Lumileds breakthrough will improve the cost, power, and brightness display profile significantly and help accelerate adoption of these technologies."

The new microLED display has an architecture based on a cluster drive system combined with microLEDs that measure  $13x20 \mu m^2$ . The result is a peak brightness of 2360 cd m<sup>-2</sup>. Notably, the mass transfer process employed in the development of these prototypes achieves 99.9998 percent microLED sub-pixel yield and a 99.992 percent percent microIC transfer yield, according to the partners. The processes used to manufacture the prototype are massproduction ready.

"XDC's mass transfer, bonding, and display driving technologies have

created new opportunities to transform the world of displays," said Brendan Moran, senior director of Display Technology at Lumileds. "Lumileds has successfully implemented XDC's transfer-ready microLED technology into our volume production LED fabrication facilities. Together, we are setting new standards in the microLED industry and advancing mobile display technology."

"This milestone is made possible by Lumileds's device expertise and manufacturing process discipline applied from the very start. The result is repeatable, high-quality microLED displays," said Matt Meitl, EVP and cofounder of XDC. "Our long collaboration has resulted in microLED displays sought by customers in the mobile device space."

The microICs, microLEDs, and the transfer equipment used in this prototype can be deployed for interested customers.

## Plessey and Meta announce brightest red microLED display

PLESSEY SEMICONDUCTORS and Meta Platforms have announced the development of what they claim is the world's brightest red microLED display suitable for augmented reality (AR) glasses.

The display offers a brightness up to 6 milion nits at high resolution ( $<5 \mu m$ ) with low power consumption – overcoming critical technical challenges that will help pave the way for the next computing platform.

This achievement follows Meta's recent announcement of the Orion AR glasses prototype. Orion combines the look and feel of a regular pair of glasses with the immersive capabilities of AR due to its 70-degree field of view, SiC

high-performance waveguides, custom silicon, microLED projectors, integrated input system, and more.

As part of its long-term agreement, Plessey is continuing to work with Meta by dedicating its manufacturing operations to support the development of prototypes and new technologies for potential use in the XR category.

Jason Hartlove, VP of Display and Optics, Meta's Reality Labs, said: "Our work with Plessey has pushed the boundaries of what's previously been possible, and it's only the beginning the future is starting to look up."

Keith Strickland, CEO of Plessey added: "Plessey is proud to be working alongside Meta to drive the development of microLED display technology. The collaboration between Meta and Plessey has delivered a major breakthrough in the development of AR technology, and we are excited to see the impact that this innovation will have on the industry. With the world's brightest red microLED display, we are one major step closer to making AR glasses a mainstream reality."

## IQE and Quintessent partner on QD lasers for AI

Partners establish commercial quantum dot epitaxial wafer supply chain for AI optical interconnects

COMPOUND SEMICONDUCTOR wafer company IQE has strengthened its partnership with Quintessent, a pioneer in quantum dot laser technology and heterogeneous silicon photonics, to establish the world's first largescale quantum dot laser (QDL) and semiconductor optical amplifier (SOA) epitaxial wafer supply chain.

This milestone is backed by an initial purchase order of \$0.5m for delivery of production wafers to Quintessent through 2025.

The rapid expansion of Al-driven applications has placed significant requirement in data centres power consumption driving the migration from copper chip to chip connectivity to silicon photonics. This has created an increasing demand for high-bandwidth, low-latency, energy-efficient and highly reliable optical interconnects.

Traditional laser technologies struggle to meet these requirements, making

QDLs and SOAs a critical innovation for future Al infrastructure which offer superior performance, including extended lifetimes, improved efficiency, lower noise and greater resilience to environmental fluctuations.

IQE and Quintessent have collaborated for over a decade to transition QDL technology from research to large-scale production. Building on research breakthroughs from John Bower's laboratory at the University of California, Santa Barbara, the partnership has successfully developed highly optimised and high performing gain GaAs-based quantum dot epitaxial wafers on 6-inch substrates versus state of the art 4-inch art InP lasers.

This achievement enables the production of hundreds of millions of high-performance edge-emitting lasers annually, according to the companies. Jutta Meier, Interim CEO and CFO of IQE, commented: "IQE is proud to strengthen our long-standing

partnership with Quintessent, driving the commercialisation of QDL technology. This commitment highlights our expertise in high-volume epitaxial wafer manufacturing and our proven ability to scale innovative semiconductor solutions into production. Our collaboration, spanning commercial products and DoD programs has delivered QDL wafers with exceptional reproducibility and lasing performance"

Alan Liu, CEO and co-founder, Quintessent, said: "The performance, cost, and reliability advantages that quantum dot-based lasers and amplifiers enable over their quantum well counterparts are exactly what our customers are demanding to address the soaring need for optical connectivity in Al driven compute. Through our partnership with IQE, we have brought this transformative technology to scale, positioning us to be the leader in delivering solutions leveraging quantum dot laser and SOA technology."

## 'Game-changing' VCSEL system targets clinical imaging

TRUMPF PHOTONIC COMPONENTS, a maker of VCSELs for industrial and consumer sensing, and iThera Medical are introducing a solution for optoacoustic imaging for clinical applications, which they will demo at Photonics West in San Francisco, 28 – 30 January 2025.

The photonic subsystem presented is based on a compact set-up of high power VCSEL arrays and bare ToF CMOS driver chips. The heat dissipation can be buffered in a small copper block, so the subsystem can be directly mounted within a medical handheld device with no active cooling.

According to Trumpf, the subsystem can replace current photonic systems and is described as a "game changer for routine clinical use", starting with

soft tissue perfusion and oxygenation measurements, applicable to a wide range of diseases.

"The power-efficient and compact photonic solution of Trumpf and iThera is scalable and paves the way towards future patch and sensor optoacoustic applications. The VCSEL technology, with its benefits like precision, compact structure, energy efficiency and wide range of wavelengths is perfect for this application," said Alexander Weigl, head of product management at Trumpf Photonic Components. "At Trumpf Photonic Components, we view the medical technology and life sciences sector as a growth area for numerous VCSEL wavelengths and applications," he added.

"Using VCSELs will allow us to cut light-source-related costs, volume and

power consumption of our marketleading optoacoustic imaging devices by a factor of 100," explained Patrick Leisching, CTO at iThera Medical GmbH

"Additionally, compared with the currently used tunable solid-state lasers, the VCSEL subsystem results in a downgrade of the laser safety classification from its current Class 4 to Class 1, eliminating the need for special safety measures, and it will provide a substantially improved operating stability," he commented. "These gamechanging improvements will facilitate the translation of our technology from research into routine diagnostic use and also enable future sensing applications, making optoacoustic technology widely accessible across different care settings," he said.

#### NEWS ANALYSIS | SUBSTRATES

### 300 mm SiC: A format for when?

Is the unveiling of a 300 mm SiC substrate by SICC going to drive a relatively rapid shift to high-volume production with this format?

#### BY RICHARD STEVENSON, EDITOR, CS MAGAZINE

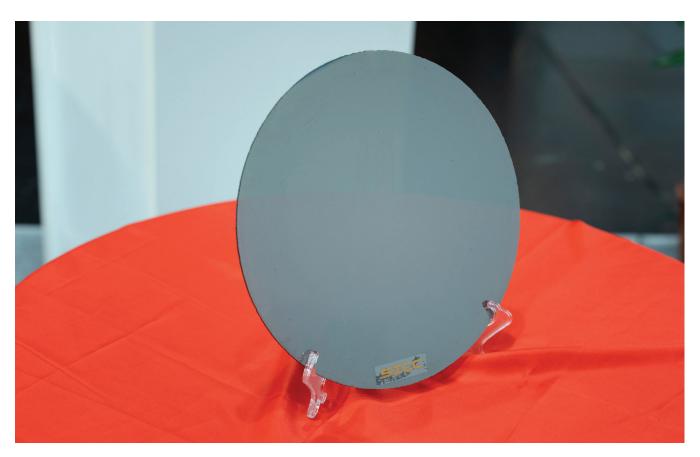

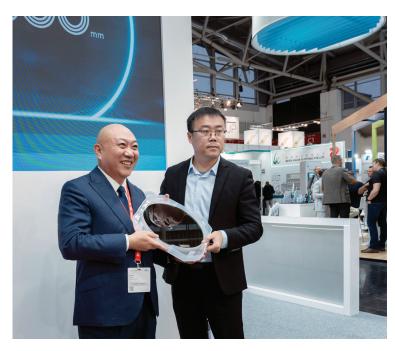

THOSE in our industry will probably remember the recent *Electronica* for the unveiling of the world's first 300 mm SiC substrate. This breakthrough, showcased to the world in mid-November from Munich, Germany, is undoubtedly a great demonstration of technical prowess. But is it going to have an impact in an industry that is only just starting to make the transition from 150 mm to 200 mm SiC lines?

Some may argue that this triumph, realised by one of the world's biggest manufacturers of SiC, SICC of Jinan, China, is of little relevance in the near term, but the trailblazer sees the situation differently.

Speaking of its behalf, Chairman Yanming Zong told *Compound Semiconductor* that one of the purposes behind this demonstration is the promotion of industrialisation of 300 mm SiC. While the rate of technical progress and the level of demand for this new format will influence the precise timing of SICC's commercialisation of 300 mm *n*-type SiC substrates, the anticipation is that small production volumes will begin in 2027.

At this stage, it's unclear which chipmakers will be keen to buy this new format. However, Zong believes that some of the leading makers of SiC devices may be willing to invest in upgrading their lines to trim costs, and he points out that some start-ups may see the benefit of beginning with larger wafers.

For all those making SiC devices, weighing on production costs is the slow growth rate of the boules, which are sliced to form substrates.

"We want to continuously reduce the cost of material per unit area by expanding the substrate size," remarks Zong, who hopes that one of the consequences of introducing larger wafers will be an increase in the bang-per-buck of SiC devices.

#### Swift scaling

Founded in 2010, SICC, which focuses on the R&D, production and sales of SiC substrate material, used equipment designed and installed by its R&D team to produce the record-breaking substrates. This multicultural, highly qualified team took just

18 months to enlarge its n-type boules from 200 mm to 300 mm.

The ground-breaking enlarged boule, produced using the same axial growth rate employed for manufacturing of 200 mm material, has a thickness of around 20 mm. From this ingot, it is possible to slice around 25 to 35 wafers with a thickness of 500  $\mu$ m. And as the team refines its process, it will be possible to produce thicker boules that yield more wafers.

Historically, SiC substrates have been plagued with a variety of imperfections that degrade and even kill devices. However, those issues have now been addressed by many companies, and as the process that's used to fabricate the 300 mm substrate is the same as that used to produce smaller wafers, there is no major barrier to realising state-of-the-art quality with the larger format.

Encouragingly, one of the critical defects, the micropipe, is not a significant issue in SICC's *n*-type 300 mm substrate. With further development, micropipe density is forecast to fall to below 0.2 cm<sup>-2</sup>, which is a degree of prevalence found in the company's 200 mm *n*-type SiC.

Of more concern are basal plane dislocations. However, while this class of defect needs to be reduced, the company is confident it can replicate the density found on its 200 mm *n*-type substrates.

Efforts will not have to be directed at improving surface roughness. SICC's 300 mm substrate has a roughness of just 0.2 nm, a figure comparable to that for the company's 200 mm wafers.

One of the next steps on the road to commercialisation is the verification of the quality of the epilayers produced on 300 mm substrates. Today, none of the suppliers of MOCVD reactors have tools designed to accommodate this size. However, Zong argues that they will have anticipated the unveiling of this format, and he does not expect tool availability to hold back progress.

The *n*-type 300 mm format that SICC is pioneering is suitable for producing power devices that operate at high voltages and high frequencies and are deployed in inverters and electric vehicles.

As well as being the world's second biggest producer of *n*-type SiC, SICC has other SiC-related products in its portfolio, including a heat dissipation SiC bare product that is said to combine exceptional thermal stability with ultra-high thermal conductivity.

For the last five years SICC has been the third largest producer of semi-insulating SiC, a popular platform for RF products. It also offers *p*-type SiC, the ideal platform for producing bipolar SiC IGBTs, which are attractive candidates for deployment in

SICC also offers *p*-type SiC, the ideal platform for producing bipolar SiC IGBTs, which are attractive candidates for deployment in high-power electronic systems, such as smart grids – they require devices than can handle 10 kV or more

high-power electronic systems, such as smart grids – they require devices than can handle 10 kV or more.

#### A novel growth process

To address concerns related to cost, high resistivity and defect control with p-type SiC, SICC has pursued and mastered an alternative growth technology to the standard approach, physical vapour transport. By turning to top-seeded solution growth, the company has been able to produced p-type substrates with low threading dislocations, zero stacking faults, and a uniform resistivity that's below 200 m $\Omega$  cm. These substrates have an off-cut of 4°.

To increase its capacity for producing 200 mm SiC wafers, SICC is now investing in its facility in Shanghai. This will help to satisfy the global demand for 200 mm SiC substrates. That's clearly going to be the leading format for the next few years, but beyond then there may be the introduction of 300 mm variants, thanks to the recent efforts of SICC.

➤ SICC unveiled its record-breaking 300 mm SiC *n*-type substrate at Electronica, held in Munich, Germany, in mid-November. On the left is the company's Chairman Yanming Zong, and on the right its CTO, Chao Gao.

## Going through the gears with gallium nitride

VisIC plans to ramp production of its GaN depletion-mode HEMTs for electric vehicle inverters before the end of this decade

#### BY RICHARD STEVENSON, EDITOR, CS MAGAZINE

DESIGNERS of electric vehicles are facing a dilemma when selecting the power electronics for their drive trains. To trim the bill of materials, they favour the use of the silicon IGBT. But this transistor fails to offer the efficiency of the pricier SiC MOSFET, which ensures a greater driving range for the automobile, an attribute that has spurred the commercial success of this class of transistor.

Due to these awkward trade-offs, designers of EVs will be enthralled by the tantalising prospect of a power transistor that delivers a performance on par with that of the SiC MOSFET, but for a price comparable with that of the silicon IGBT.

Preparing to offer just that in significant volume within the next few years is the Israeli-based producer of GaN power devices, VisIC Technologies, which is working in partnership with AVL, one of the leading developers, simulators and testers of many forms of green transportation.

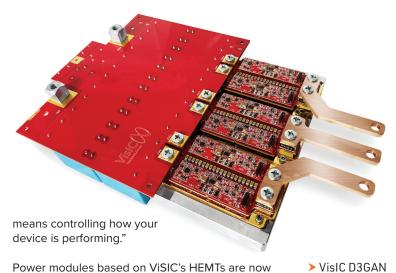

> AVL Dyno test setup with a VisIC D3GAN power inverter.

"We can really push the boundaries and technology with AVL," enthuses Dieter Liesabeths, Senior Vice President of Product at VisIC. He says that this partner excels in software knowledge and hardware experience, and will provide great support in the development of highly integrated inverters. "They also have the capability to go to a very high RPM with their motors, up to 30,000 RPM, which is really benefiting the GaN technology."

In December 2024, VisIC and AVL reported efficiencies for their inverter of 99.67 percent and 99.8 percent at 10 kHz and 5 kHz, respectively. These values for efficiency are said to be up to 0.5 percent higher than those for SiC inverters, an improvement that ensures a trimming of energy loss by more than 60 percent.

The partnership between VisIC and AVL determined these efficiencies by testing their inverter under 400 V, a voltage that's used in many city-type cars, as well as those made by Tesla.

Despite much interest is moving EVs to 800 V, these results are incredibly relevant, argues Liesabeths: "The majority of cars that will come out in the future will be 400 volts, because these are typical city-cycle cars, which are having smaller batteries."

For these EVs, most driving is in urban areas, where the typical average speed is around just 25 km hr<sup>-1</sup>. At these modest speeds, the load condition on the inverter is relatively low, and this drags down the efficiency of inverters with VislC's HEMTs to 99.2 percent. However, that's still better than that for inverters based on SiC operating at higher loads, thanks in part to the vanishingly small switching losses for GaN.

The GaN HEMT also has the upper hand in terms of price, costing about half that of the SiC MOSFET. The GaN HEMT is still about 20 percent more expensive than the silicon IGBT, but if the former were to be produced using 300 mm wafers, costparity with silicon might be within reach, thanks to the smaller size of the die.

#### NEWS ANALYSIS I POWER ELECTRONICS

Note that lower chip costs are a big deal for makers of EVs. "If you can replace silicon carbide, which is around 55 to 60 percent of the cost of the invertor, with gallium nitride, you're cutting your cost almost by half," says Liesabeths.

In addition, replacing SiC MOSFETs with GaN HEMTs ensures a substantial reduction in carbon footprint, as producing the former involves very high temperatures.

#### Depletion-mode devices

VisIC differentiates itself from its rivals with a patented D-mode HEMT technology, pairing its depletion-mode GaN transistor in series with a silicon MOSFET.

It's a novel configuration that enables direct driving of the GaN transistor, thereby avoiding losses that come from switching the silicon MOSFET; and it allows control over the slew rate, leading to greater robustness at the system level. What's more, the company's D-Mode technology offers a superior dollar-per-amp, as this form of HEMT can be smaller than its enhancement-mode cousin.

Many producers of GaN HEMTs partner with 200 mm foundries, which were in very high demand during the pandemic. However, this constraint has now eased, says Liesabeths, who can't see any difficulties or bottlenecks in the future for GaN. He points out that foundries offering GaN power electronic technologies are increasing their capacity, and those dedicated to silicon are branching out into GaN.

Initially, VisIC partnered with TSMC, which can handle all steps of production, by producing GaNon-silicon epiwafers and process them into HEMTs. But now VisIC is also starting to investigate an alternative supply chain, involving independent epiwafer specialists, as well as foundries that process this material into devices.

"Working with dedicated epi-partners means that we have better control, and more influence about the design itself," says Liesabeths. "The quality is the key differentiator here, because controlling epi

Power modules based on ViSIC's HEMTs are now undergoing full qualification, under the AEC-Q101 and AQG-324 criteria used in the automotive industry to verify reliability.

"We are confident that we are passing this qualification and even exceeding some of the requirements," says Liesabeths.

Looking ahead, plans for the partnership include developing very high-power inverters, operating in the 300 kW range, and demonstrating variants around 100-120 kW, suitable for city cars. Liesabeths says that accomplishing all of this will show that GaN is viable for "both ends of the spectrum".

For VisIC, another target is to produce GaN HEMTs for EVs in high-volume by 2028-29. "We are confident that by this time frame, we will see the first cars on the road," says Liesabeths, who is helping to lay the foundations for this success, via ongoing work with OEMs and tier ones.

If and when the EV industry moves to higher voltages, VisIC is well-prepared with its patented multi-channel devices that can handle up to 3.3 kV. "We were not utilising [this technology] so far, because we first want to demonstrate a viable solution for 400 volts," says Liesabeths. But his co-workers are developing 800 V devices for market, slated for release within the next two years.

The Next Generation in Process Control for **Compound Semiconductor Manufacturing**

#### **CELERO™ PL**

The Celero PL system delivers industry leading surface defect and subsurface photoluminescence sensitivity with up to 100% throughput gain over competing platforms across all wafer sizes.

Utilize Discover® software with the Onto product suite to achieve 360° wafer defect mapping, including subsurface defects!

\*150/200MM VERSION SHOWN

ontoinnovation.com

3-phase

system.

VM022 Gen 1

Power Core

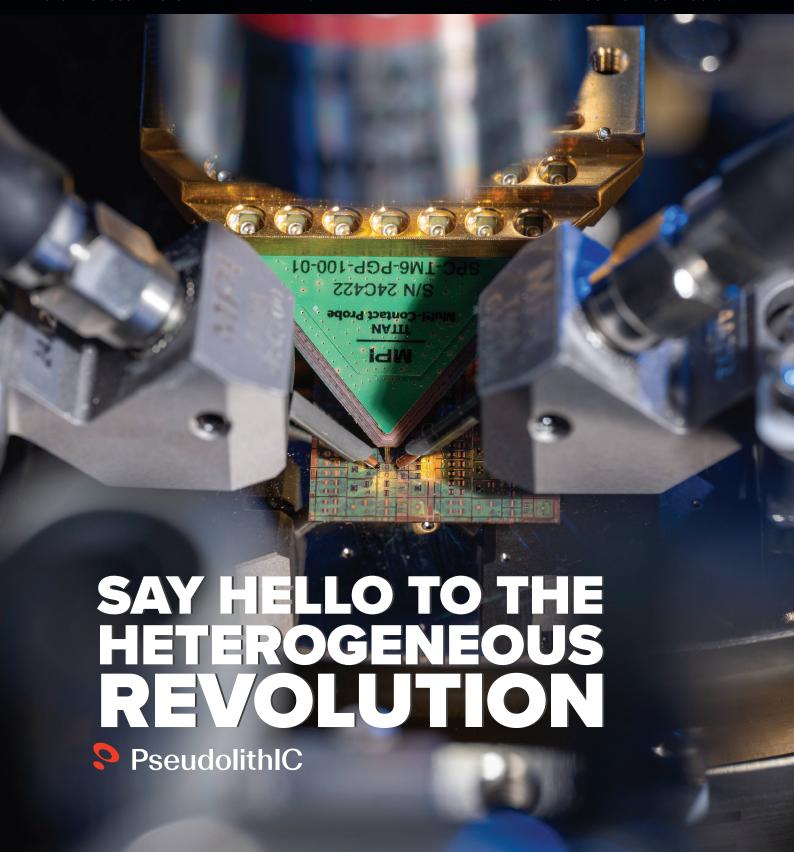

## Say hello to the heterogeneous revolution

Recent advances in circuits produced by heterogeneous integration highlight the potential for real world applications

BY CHRISTOPHER MAXEY, JUSTIN KIM, DAVE HODGE, MARK SOLER, BENNETT COY, DAN GREEN, JAMES BUCKWALTER AND FLORIAN HERRAULT FROM PSEUDOLITHIC INC.

> SINCE the advent of VLSI silicon CMOS, this technology's RF and millimetre-wave performance has taken a back seat during the inexorable drive towards smaller gate dimensions and higher device density. Stepping up to fill this gap have been a number of compound semiconductors, such as

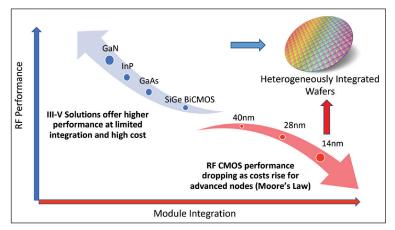

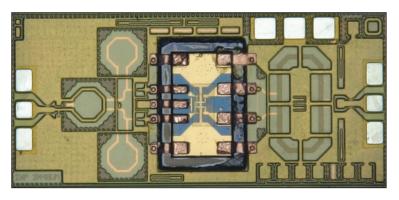

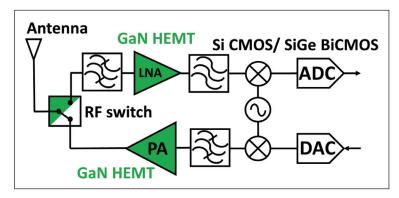

> Figure 1. Silicon CMOS and compound semiconductors provide unique benefits, while heterogeneous integration promises to deliver the best of both worlds.

GaAs, GaN, and InP, providing high gain and high output powers at ever higher frequencies. Thanks to these devices, it has been possible to construct solid-state phased-array radars, 5G/6G basestations and quantum computers. However, these applications pay a significant price in an ecosystem where many may see 'exotic' materials as an issue that slows and restricts adoption. Compared to silicon CMOS, it typically takes twice as long to fabricate compound semiconductor devices, which are 5 to 10 times as expensive per unit area, because they lack the fundamental economic benefits of high-volume manufacturing.

One attractive solution to addressing this issue is heterogeneous integration. Many are now investigating this approach that combines the disparate benefits of multiple technologies into a single integrated circuit (see Figure 1). Here, we review the rise in interest in heterogeneous integration, its progress in the context of the historical evolution of semiconductor technologies, and the potential inflection it offers to accelerate deployment of new devices into the marketplace. We also describe the contribution that our company,

#### TECHNOLOGY | INTEGRATION

PseudolithIC, is making – we are the pioneers of a number of 'first-ever' prototype designs, including the world's first millimetre-wave amplifier based on InP and GaN devices.

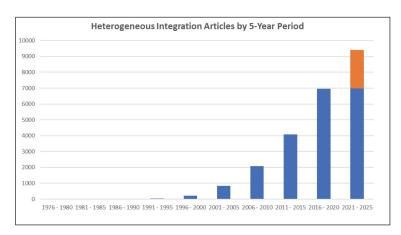

#### HI primed for impact

Evidence of accelerating interest in heterogeneous integration is found in increases in journal articles and patent filings over the last three decades (see Figure 2). At the turn of the millennium heterogeneous integration started to take shape as a bone fide topic, and since then there has been a steady rise in publications continuing to the present day. Alongside this trend, there has been a multiplication in both the number of potential approaches to realising integrated solutions, and the potential applications for heterogeneous integration. For example, integration of varying digitally focused chiplets has spawned multiple conferences and consortia, including the recent Universal Chiplet Interconnect Express consortium. Supporting and spurring on much of this activity are federally funded efforts, such as the DARPA CHIPS programme. There are also many efforts driven by government research programmes that focus on mixing optical technologies at the chip scale to trim the cost and improve the performance of photonic integrated circuits.

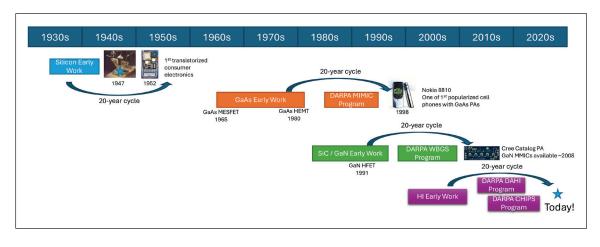

Looking more broadly at the history of semiconductor innovation, the timeline from a technology's first results to its commercial deployment has consistently been on the order of two decades. The time that it takes to develop a compound semiconductor device technology, such as that based on GaAs or GaN, is very similar to that for silicon (see Figure 3), with initial device results preceding deployment in commercial applications by about 20 years.

For both GaAs and GaN, development has been facilitated by significant industrial investment, underwritten in part by the US Government.

Development of GaAs devices has been supported by the DARPA MIMIC programme, while advances in GaN have been aided by the DARPA WBGS programme. Heterogeneous integration is now on the cusp of commercial employment, and has benefitted from similar developmental investment.

> Figure 2. Articles and patents referencing heterogeneous integration over five-year periods spanning the 1970s to today. The final period includes a linear extrapolation for the remainder of the current period (courtesy Google Scholar).

Based on historic rates of progress, we can conclude that heterogeneous integration is primed to realise its commercial impact.

#### Merits of the PseudolithIC approach

A number of research groups are focusing on RF applications, and exploring several approaches. We are involved in this area, but taking the technology much further, by commercialising a chip-scale 2.5D integration approach that leverages existing RF silicon and compound semiconductor ecosystems.

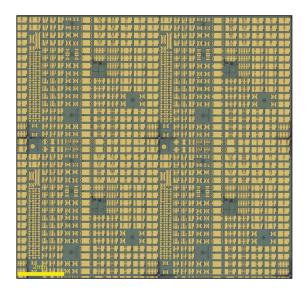

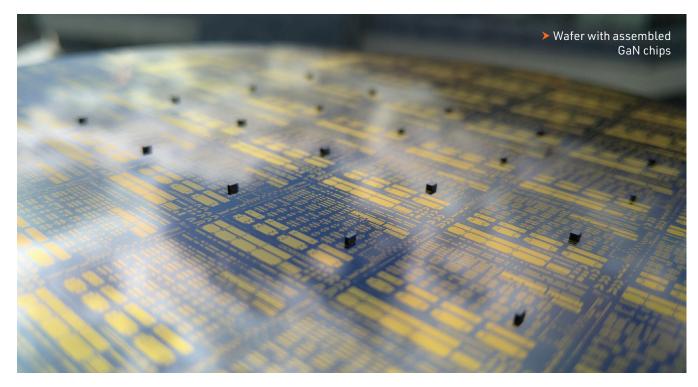

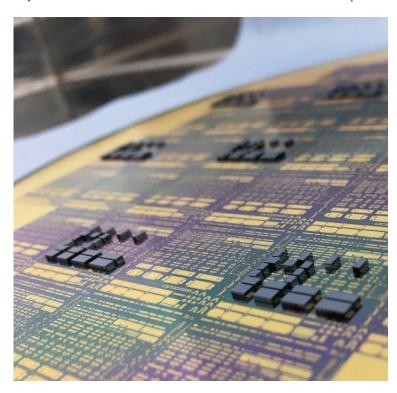

Our approach offers three critical value propositions over monolithic processes, which concentrate on a single material. First, we accelerate the design and fabrication process for a high-performance RF circuit. An example of this is designing new circuits and integrating exotic materials, such as N-polar GaN, faster than a traditional foundry, because we just require chiplets of the material, rather than an entire MMIC. Consequently, several thousand chiplets can be procured from a single tape-out (see Figure 4). Once we have sourced our chiplets and built up an inventory, our designers only need to design the interposer to produce a new pseudolithic IC, which we refer to as simply a PLIC. Second, our approach

Figure 3. A timeline illustrating the evolution of silicon, GaAs, GaN and heterogeneous integration as semiconductor technologies.

#### TECHNOLOGY | INTEGRATION

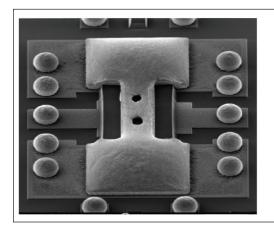

Figure 4. Micrograph of an example 'sea of transistors' wafer used for N-polar GaN chiplet fabrication.

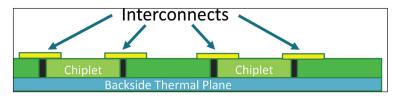

enables a true 'mix-and-match' of different devices, such as InP and GaN, in a single PLIC. This enables optimal architectures that are free from multi-chip modules. Finally, as the interposer is built on wafers with a diameter of at least 8 inches, they have at least four times the area of the 4-inch wafers used in typical III-V processes, leading to significant fab throughput and cost advantages.

> Figure 5. Cross section of a completed PseudolithIC PLIC with a chiplet embedded in a silicon interposer.

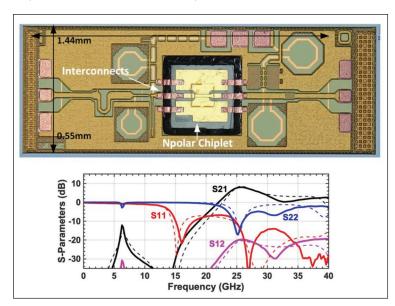

> Figure 6. (top) Chip microphotograph of the 26 GHz heterogeneously integrated amplifier illustrating the compact implementation of the input and output matching networks. For clarity, the HEMT chiplet and interconnect are highlighted. (bottom) Simulated (dashed) and measured (solid) S-parameters of the heterogeneously integrated amplifier. A peak gain of 8.0 dB occurs at 26 GHz.

To enjoy all these benefits, we employ an approach that begins by sourcing individual active III-V transistors – or even more complex integrated circuits – from either an established defence industrial base or a commercial foundry. After dicing these devices into singulated 'chiplets', they are embedded into a separately designed and fabricated silicon substrate interposer, which may feature passive networks, such as transformers, and active CMOS control circuity. By adopting a low-temperature process, we maintain the integrity of the chiplets and the *in-situ* CMOS devices. Our final step, completing integration at the wafer scale, is the fabrication of copper coplanar waveguide interconnects between the chiplet and interposer.

The finished product, a PLIC, is completely planar and compatible with commercial die attach, packaging, and chip-on-board processes, aiding downstream integration in higher-level systems. Critically, the PLIC is nearly indistinguishable from a single technology IC (see Figure 5, which shows a cross section of a PLIC after the chiplets are embedded in the interposer, and highlights the thermal advantages that result from direct access to the backside of the high-power chips).

#### First pass successes

Our unique process, which capitalises on the maturity and reliability of silicon to simplify the millimetre-wave and microwave MMIC design processes, results in an exceptionally high first-pass success rate. Exemplifying the advantages of our process are recent publications outlining how our technology can be used to produce an N-polar GaN power amplifier, an InP power amplifier, and a two-stage amplifier that features both InP and GaN technology.

Recent research shows that N-polar GaN HEMTs offer high-efficiency, high-power density, and excellent linearity for microwave and millimetre-wave applications. However, transitioning emerging GaN HEMT technologies into commercial applications is impeded by the lengthy foundry development cycle for a full MMIC process – this involves device maturation and qualification, and incurs a high cost, due to the specialised 4-inch epitaxial wafers. Our approach addresses some of these delays, with an acceleration of material to viability, thanks to the introduction of a heterogeneous design that embeds an N-polar transistor in a silicon interposer.

For the amplifier we have fabricated, we use a HEMT chiplet with: an 80 nm gate length; 500 nm gate-drain separation; and two fingers of 37.5  $\mu m$  width, for a total gate periphery of 75  $\mu m$ . Measurements of S-parameters for this amplifier suggest a peak output power of 150 mW (see Figure 6). Despite designing across two processes, there is excellent agreement between 20 GHz and 40 GHz, thanks to the maturity of our custom design environment that is adept at uniting silicon and

III-V technologies. The peak gain of our amplifier reaches 8.0 dB at 26 GHz. At this frequency, the input and output return loss exceed 16 dB and 12 dB, respectively. The reverse isolation, S12, is better than 20 dB across the frequency band. The measured amplifier is unconditionally stable from 0 to 40 GHz.

We have also demonstrated similar first-pass success with more mature process technologies, including a 250 nm lnP HBT process reported in early 2024. This process offers a 2.5 V supply with a maximum oscillation frequency ( $f_{max}$ ) approaching 650 GHz. The high value for  $f_{max}$ , and also for the cut-off frequency ( $f_{T}$ ), ensures that this technology is attractive for high-gain and high-efficiency blocks.

Additional attributes are a low supply voltage and a high collector current density of 2 mA  $\mu m^{\text{-}1}$ , strengths that support matching that is closer to a desired 50  $\Omega$ . Due to this, a lower impedance matching quality factor (Q) is required to match to the device, leading to wideband amplifier designs.

Our heterogeneously-integrated InP amplifier, shown in Figure 6, has differential-mode stabilisation included on the chiplet. To allow supply of the base voltage through the common mode node, a transformer with capacitive isolation is used on the input. The differential signals on the collector are combined through a sub-quarter-wavelength balun on the output. Using this configuration, our amplifier exhibits 10.6 dB of gain at 24 GHz, with a total power consumption of only 45.3 mW.

#### Combining GaN and InP

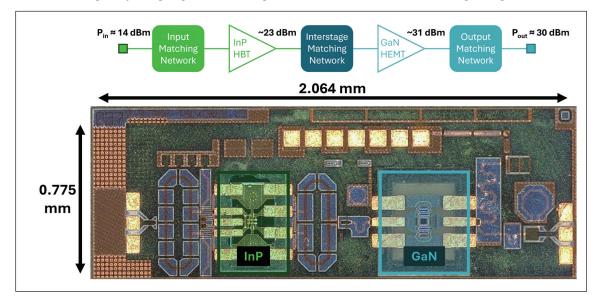

Building on our foundation that has established that single III-V technology heterogeneous integration is viable and commercially competitive, we have gone on to prove that our technology can mix and match different III-V device types in the same integration process. For this demonstration, we have drawn on the success of our previous two circuit designs, by designing and fabricating

➤ Figure 7. Chip micrograph of the Ka-Band heterogeneously integrated InP amplifier.

a two-stage amplifier that has an InP first stage and a GaN second stage. The motivation for making this single PLIC is that no single technology is best suited for all RF functions. In our Ka-band amplifier, we need an InP first stage to maximise gain and a GaN second stage to maximise output power (see Figure 8 for a die micrograph of the fabricated PLIC and a top-level schematic of the two stages).

As we had previously built and tested each stage independently prior to this design, we concentrated our efforts on a new interstage matching network and making slight adjustments to the previous input and output matching networks. This again demonstrates how we can accelerate the adoption of heretofore impossible circuit topologies through our unique process. Our combined amplifier measures over 20 dB of gain at 25.7 GHz, validating our approach of merging the two technologies.

#### Higher levels of integration

Transmit/receive modules are ubiquitous in commercial and defence electronics. Here there is an ever-present demand for higher performance, realised at a lower cost and at higher frequencies. Defence electronics is tending to migrate to the

Figure 8. High level schematic of the two-stage amplifier (top) and a die micrograph of the fabricated device (bottom).

#### TECHNOLOGY | INTEGRATION

Our triumphs include the world's first millimetre-wave amplifier that combines InP and GaN devices, a demonstration that underscores the extreme flexibility associated with combining different technologies. Another significant success is our dense transmit/receive module designs that combine InP, GaN and CMOS to deliver higher performance and lower cost

| Component              | Ideal Qualities                                                    | Candidate<br>Technologies |

|------------------------|--------------------------------------------------------------------|---------------------------|

| T/R switch             | Fast Switching Time<br>High Off/On Isolation<br>Low Insertion Loss | Si SOI CMOS<br>GaN HEMT   |

| Low-Noise<br>Amplifier | Low Noise Figure<br>Wide Bandwidth<br>Low Power Consumption        | InP HEMT<br>GaAs pHEMT    |

| Power<br>Amplifier     | High Output Power<br>High Efficiency<br>Ease of Matching           | GaN HEMT                  |

➤ Table 1. Design considerations for a Ka-Band T/R module.

V- and W-band to gain both bandwidth and a spectrum access advantage over potential adversaries. Similarly, commercial electronics are moving to higher frequencies, in this instance to satiate the growing demand for bandwidth in cellular and satellite communications networks. Heterogeneous integration is ideally suited to meet all these application requirements, providing an optimised performance in small form factors.

Conventionally, transmit/receive modules are constructed from multiple die, and packaged and interconnected with traditional PCB-style manufacturing techniques. This approach is adopted because no single monolithic process is ideal for each of the transmit/receive functions (see Table 1 for some of the design considerations for a typical transmit/receive module, including devices that best meet those requirements).

Building on our success with our multi-stage, multi-technology amplifier, we have designed and fabricated several generations of transmit/receive modules that mix different devices to achieve optimal performance in a very small form factor, typically around just 5 mm². According to our latest simulations, our technology can deliver an output power of 2 W from the transmit path of the module. The receive path can deliver 12 dB of gain at 28 GHz while maintaining a total noise figure below 2.5 dB for the module when accounting for switch loss. There is no doubt that heterogeneous integration holds the key to realising an optimal technology combination, and enabling great performance from a small form.

Following 20 years of public and private investment and research activity, it appears that heterogeneous integration is now poised for commercial adoption, thanks to continued maturation and evolution of the foundational manufacturing techniques. We have contributed to this development with a proprietary process that has yielded several 'first-ever' prototype designs, highlighting the key benefits of heterogeneous integration for RF and millimetrewave circuits.

Our triumphs include the world's first millimetre-wave amplifier that combines InP and GaN devices, a demonstration that underscores the extreme flexibility associated with combining different technologies. Another significant success is our dense transmit/receive module designs that combine InP, GaN and CMOS to deliver higher performance and lower cost. While this demonstration has targeted Ka-band applications, the approach extends readily to frequencies at W-band and beyond. These results highlight that the moment has now arrived to transition heterogeneous integration to various applications, from commercial 5G/6G telecommunications to defence electronics and beyond.

The authors acknowledge the support of DARPA Phase II SBIR support under the supervision of Drs. David Abe, Thomas Kazior and Timothy Hancock as well as NSF Phase I support under the supervision of Dr. Elizabeth Mirowski. A portion of this work was performed in the UCSB Nanofabrication Facility, an open access laboratory. The authors acknowledge the use of the Quantum Structures Facility within the California NanoSystems Institute, supported by the University of California, Santa Barbara and the University of California, Office of the President.

#### **FURTHER READING / REFERENCE**

- J. Kim et al. "Heterogeneously-Integrated Gallium Nitride and Indium Phosphide Devices for Ka-band Amplifiers" in The Proceedings of the 2024 RF Integrated Circuit Conference (RFIC), Washington, DC, June 2024.

- ➤ J. Kim et al. "A Heterogeneously-Integrated Ka-Band, N-Polar Gallium Nitride HEMT Amplifier" in The Proceedings of the 2024 International Microwave Symposium (IMS), Washington, DC, June 2024.

## MICRO-MECHANICS ON STRATEGIC MATERIALS

- In stock for all vacuum and ultra vacuum applications : (screws, nuts, rings) « Usable in Clean Rooms »

- In stock for laboratory machines : Standard substrate support (Molybloc) Dimensions :

- 1½ inches

- 2 inches

- 3 inches

Possibility of substrate support with cavity and washer, on request and according to drawings

- Stock of platens blanks for all types of MBE from various manufacturers.

- produced according to drawings.

#### **RABOUTET SA**

Avenue Louis Armand • B.P. 31 • 74301 Cluses Cedex FRANCE T. +33 (0)4 50 98 15 18 • info@raboutet.fr

## Multiple materials vie for RF success

Researchers at the recent International Electron Devices Meeting reported breakthroughs in RF devices made from many different materials

#### BY RICHARD STEVENSON, EDITOR, CS MAGAZINE

WITHIN the optoelectronic domain, the most suitable material for producing a particular device is pretty obvious. If you want to make a blue LED, use GaN; for a red variant, InGaP; and if you are to make a laser that's targeting the low-absorption windows of a fibre, use InP. Selecting the best material for light emitters is easy, because the leading contender is identified by its bandgap.

The waters get a little murkier in the power electronics arena. From a theoretical standpoint, the best semiconductor is the one with the widest bandgap, so AIN. But that's not the standout candidate when practical considerations are accounted for, such as the ease of doping, how hard it is to form an ohmic contact, and the availability and cost of suitable substrates.

When it comes to RF devices, it is even harder to determine what material to select. In part, that's because one must consider more figures of merit, and determine their prioritisation on a case-by-case basis. Practical considerations are also challenging, with decisions needing to reflect how difficult it is to miniaturise a particular device and improve its high-frequency performance. So, given all these complications, it is helpful to know the state-of-theart capabilities of RF transistors produced with a wide range of material systems.

An opportunity to get exactly that insight was given to delegates attending the most recent International Electron Devices Meeting (IEDM), held in San Francisco between 7th and 11th December.

At that conference, and in the on-demand talks that followed, attendees could hear presentations on record-breaking RF devices made from a wide variety of material systems, including InP, GaN, AlScN,  ${\rm Ga_2O_3}$  and diamond.

#### Marrying InP and silicon CMOS

Amongst the many materials that are suitable for producing RF transistors, InP offers a strong case as the leading option. By delivering an impressive performance, in terms of both gain and power efficiency, devices based on this III-V are compelling candidates for a number of millimetre-wave and sub-terahertz applications.

However, there is literally a high price to pay for the great performance of InP transistors. Their manufacture is costly, due to use of electron-beam lithography processes, and production on substrates that are at most 100 mm in diameter.

One application for InP transistors is phased arrays for radar systems. When these systems operate above 100 GHz, the antenna array pitch, which is governed by the operating wavelength, is of the order of 1 mm. This length scale necessitates the dense integration of InP power amplifiers and silicon CMOS beamformers.

An attractive approach to realising this integration, pioneered by the European microelectronics centre imec, is to position InP chiplets providing power amplification at precise positions on a fine-pitch carrier.

The capabilities of this approach, using an RF silicon interposer platform developed in house, were highlighted at IEDM by imee's Siddartha Sinha.

There is a significant financial benefit that comes from combining InP and silicon CMOS in this way. "If you are able to restrict the III-V content in your design to less than 20 percent of your area, there is a drastic reduction in cost," remarked Sinha, who added that these savings can be as large as a factor of five to ten. "We use InP only where it is needed, for RF power amplification, and everything else is built using standard CMOS technology."

Sinha pointed out that there are four significant packaging challenges to overcome when producing platforms operating above 100 GHz: realising sufficiently dense integration; dealing with the fall in transistor performance that comes from scaling, overcome by introducing more stages or new materials; addressing high interconnect losses; and managing the increase in thermal density.

"At imec we have developed a unique interposer-based solution that addresses these four issues," argued Sinha. He explained that he and his coworkers are able to realise dense integration with a 1 mm pitch for the arrays by using redistribution layers and a via pitch of 30  $\mu m$ , and they tackle the decline in device performance with miniaturisation with a CMOS beamformer and InP power amplifiers. To reduce interconnect loss, imec's engineers use smooth films of copper and low-loss polymers, and for thermal management they benefit from the use of silicon that has a much higher thermal conductivity than glass interposers.

To assess the capability of their technology, Sinha and co-workers have produced RF interposer stacks featuring: spin-coated layers on RF-friendly polymers, thick layers of copper that reduce low-frequency and DC losses, and interconnects that can operate up to 200 GHz (see Figure 1).

Transmission measurements on these interposers reveal line losses of 0.3 dB mm $^{\text{-}1}$  and 0.23 dB mm $^{\text{-}1}$  at 140 GHz for structures with polymer thicknesses of 15  $\mu$ m and 22  $\mu$ m, respectively. Broadband performance is realised, spanning 20 GHz to 170 GHz.

"These numbers are comparable to what you have in PCB or glass interposers, but with much higher integration densities – that is, much thinner substrate sizes," remarked Sinha.

Additional investigations have considered the combination of the interposer and InP transistors. To assess this, the team from imec flip-chip bonded a Teledyne 250 nm InP stack to its interposer with an in-plane alignment accuracy of 3  $\mu m$ .

Passive measurements of losses with this flip-chip architecture determined values of 0.9 dB mm<sup>-1</sup> and 0.3 dB mm<sup>-1</sup> at 140 GHz for the InP backend

> Figure 1. Engineers at imec have highlighted the potential of InP chiplets on a silicon interposer for millimetre-wave applications by demonstrating the low losses of this particular system.

microstrip and interposer microstrip, and an insertion loss of around 0.1 dB for one flip-chip transition over 20 GHz to 170 GHz.

"The interposer microstrip is about three times better than what you could get in an indium phosphide die back-end," said Sinha, who added, "keep in mind that CMOS back-ends are even more lossy than this, because they are not millimetrewave optimised."

The engineers from imec have also investigated the active performance of the InP power amplifier on the interposer, recording a peak small-signal gain of 16.3 dB and a 3 dB bandwidth spanning 116 GHz to 148 GHz. "These are state-of-the-art numbers, compared to even standalone PAs," claimed Sinha.

#### GaN on 300 mm silicon

Another material with a proven pedigree for providing RF amplification is GaN.

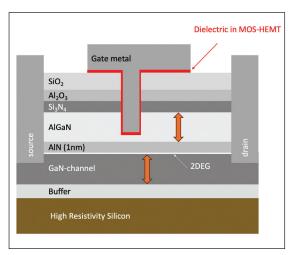

One of the leading developers of this technology is Intel. Back in 2019 this chipmaker unveiled the industry's first 300 mm GaN-on-silicon process for scaled enhancement-mode high- $\kappa$  gate dielectric GaN MOSHEMTs for power delivery and

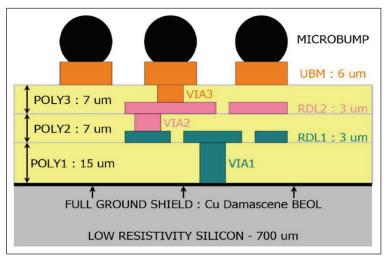

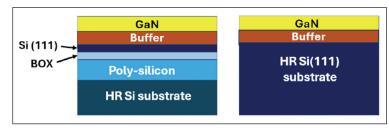

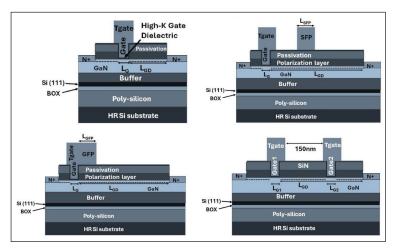

> Figure 2. (a) Intel has used 300 mm trap-rich SOI as a foundation for producing GaN MOSHEMTs on 300 mm silicon wafers. The thin silicon (111) layer serves as a crystalline template for GaN epigrowth. Beneath this is an underlying insulating buried oxide (BOX), and below that a trap-rich polysilicon layer that eliminates stray charges at the interface to the BOX, as well as a high-resistivity silicon substrate.

#### CONFERENCE REPORT I IEDM

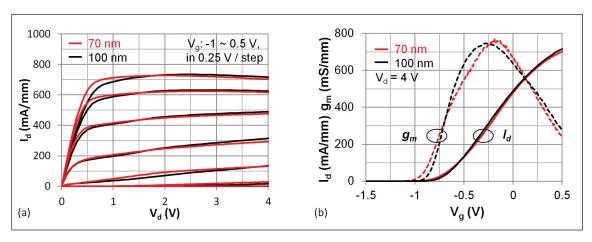

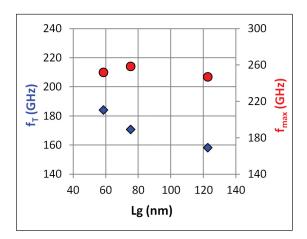

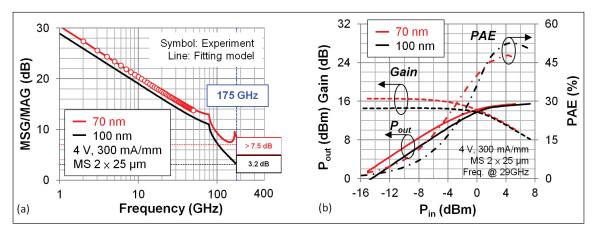

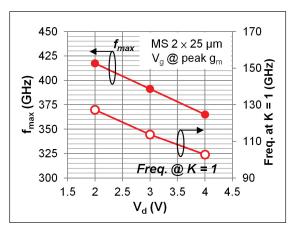

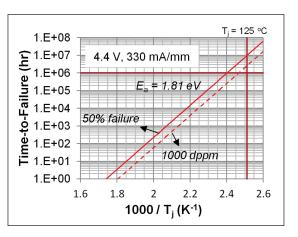

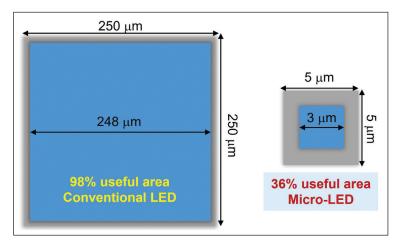

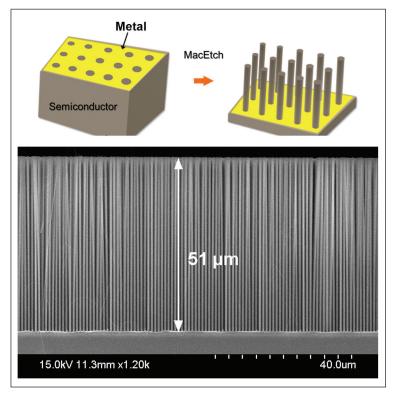

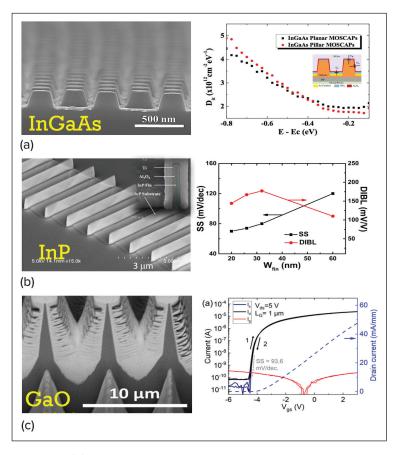

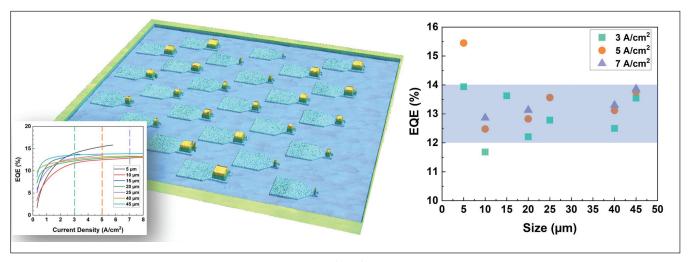

> Figure 3. On 300 mm trap-rich SOI substrates, Intel has fabricated four variants of the enhancement-mode high- $\kappa$  dielectric MOSHEMT. As well as the standard form of MOSHEMT, there are those with a source field plate, a gate field plate, and multi field plates.