# COMPOUND SEMICONDUCTOR

VOLUME 32 ISSUE 1 2026

AN ANGEL BUSINESS COMMUNICATIONS PUBLICATION

COMPOUNDSEMICONDUCTOR.NET

**NCODIN'S

NANOLASERS EYE AI

INFRASTRUCTURE**

AIXTRON

# THE G10 SERIES

1<sup>st</sup> fully automated AsP

MOCVD system enabling

10x lower defect density

Your **Productivity Solution**

for All Advanced Epitaxy Materials

## Optoelectronic opportunities in an AI-driven world

GIVEN that Nvidia has a market capitalisation of \$4 trillion, you might find it surprising to hear that the data centre market is only worth around half a billion dollars a year. But even so, that's still a substantial market to target by any company promoting a revolutionary technology to improve the performance of tomorrow's data centres, needed to support the growth of AI.

Within our industry, many companies see an opportunity here. They include makers of wide bandgap power devices that are championing the capability of their products to improve electrical efficiency while handling incredibly high power densities. And there are also the producers of optoelectronics, marketing lasers for data transfer.

Over short distances, copper is viewed as the ultimate solution for data transfer, thanks to its resiliency, robustness, and capability to facilitate high bandwidths. But once it's employed to transmit data over a few centimetres or more, losses rise and bandwidths fall – and optical-based links are more attractive.

There are plenty of optical-link technologies vying for success. They include a couple of options promoted by French researchers that are outlined in this issue.

One of these approaches, which is being pursued by CEA-Leti – and shares similarities with that of US company Avicena – is to use vast arrays of microLEDs. These tiny emitters are coupled to fibre bundles to transfer data between chips, which could be on the same board, on different boards, or even on different racks or servers.

Strengths of this approach include an opportunity for redundancy and the promise of an energy efficiency of only 0.5 picojoules-per-bit. While it's ten times this figure today, lower values will be realised during a three-year project that will draw on expertise from the lighting, semiconductor and fibre industries (for more details, see p. 16).

An even lower figure for this key metric of just 0.1 picojoules-per-bit has been realised by the French start-up Ncodin, which has just announced that it has secured funding totalling €16 million. Its core technology is InP-based nanolasers, which are attached to silicon-based waveguides, another approach that allows for redundancy (for more details, see p. 14).

Today Ncodin is working with a partner on the industrialisation of its technology. When success follows, a foundry will produce Ncodin's wafers, which will be marketed to some of the biggest names in the tech industry, such as Nvidia, Qualcomm, AMD and Intel. The expectation is that these giants will employ a third party to test, assemble and package systems that combine Ncodin's wafers with a variety of chips, such as those for memory and processing.

It could be a number of years before datacom infrastructure benefits from Ncodin's nanolasers or microLED technology promoted by CEA Leti. But AI is not going away – surely it's only going to get more pervasive – so there's a lot to be said for pursuing this promising opportunity.

Free weekly e-news roundup go to: [compoundsemiconductor.net](http://compoundsemiconductor.net)

## COVER STORY

### Ncodin's nanolasers eye AI infrastructure

Delivering a revolutionary energy-per-bit, the French start-up's nanolasers are a compelling source for on-chip communication in tomorrow's data centres

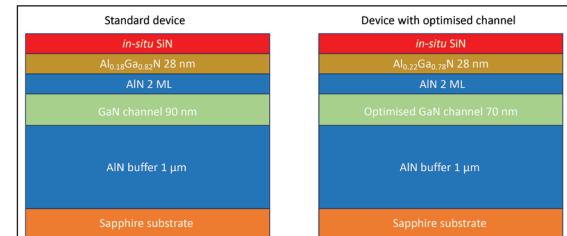

14

### 22 Clas-SiC: A thriving three-pronged attack

The Scottish SiC specialist is excelling on the three fronts. Alongside rising demand for prototyping, the manufacture of SiC devices at low-to-medium volumes

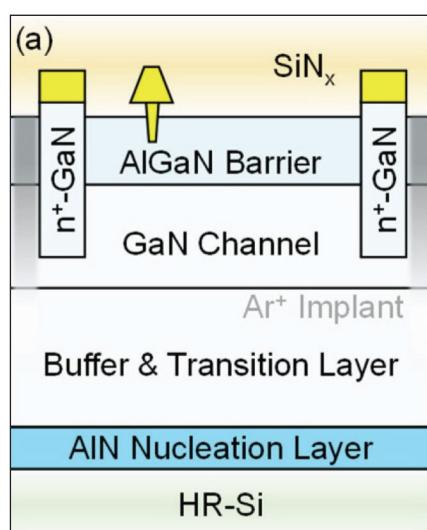

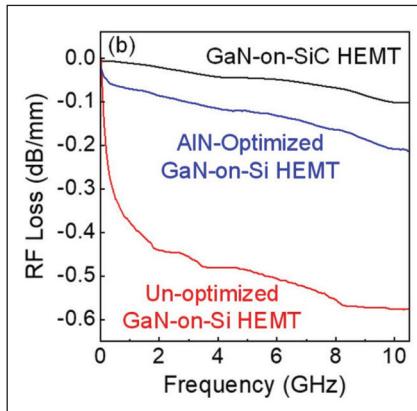

### 28 New directions for GaN electronics

Advances in epitaxy and processing are open up new opportunities for GaN in handsets, computation, and the delivery of RF signals in the X-band

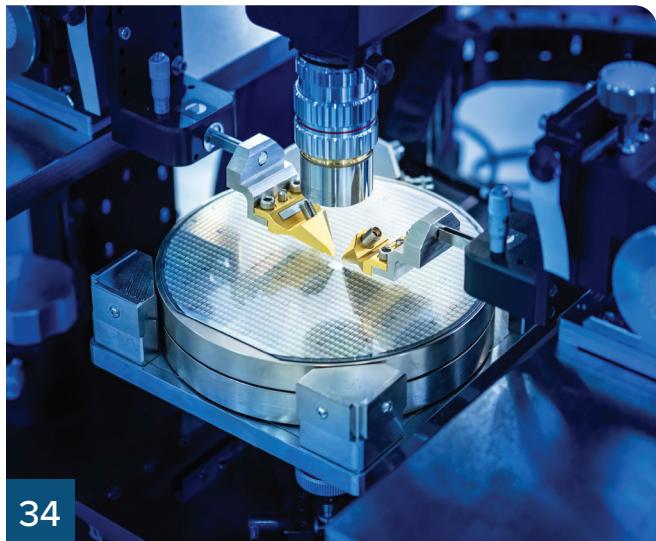

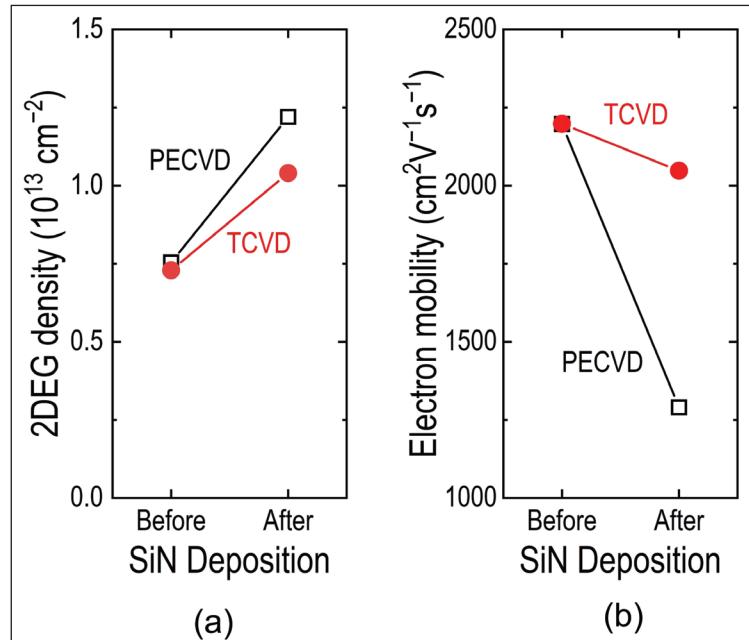

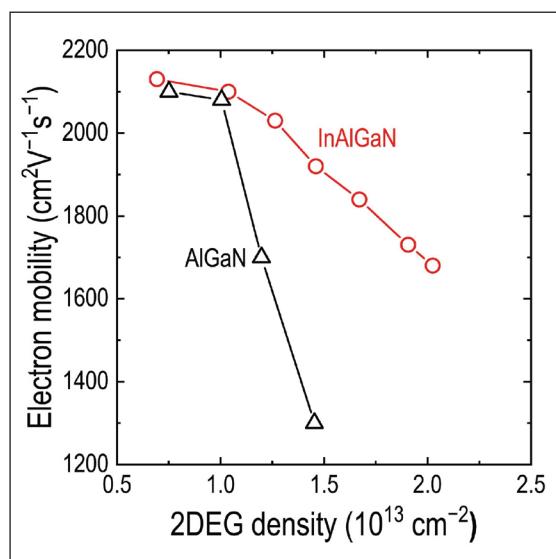

### 34 HEMTs: InAlGaN raises the ceiling

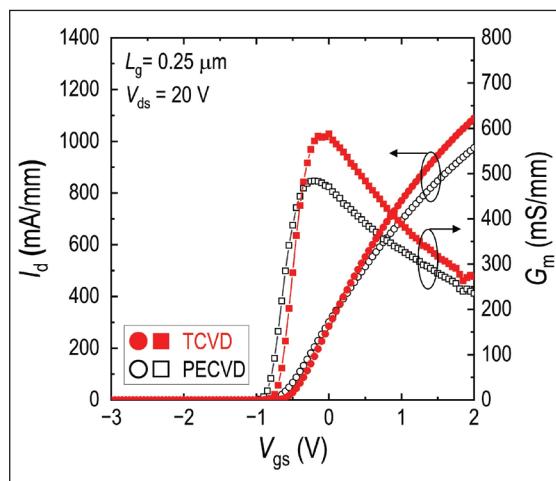

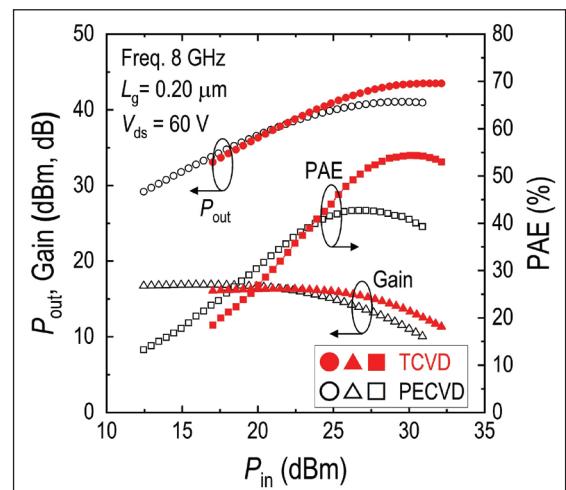

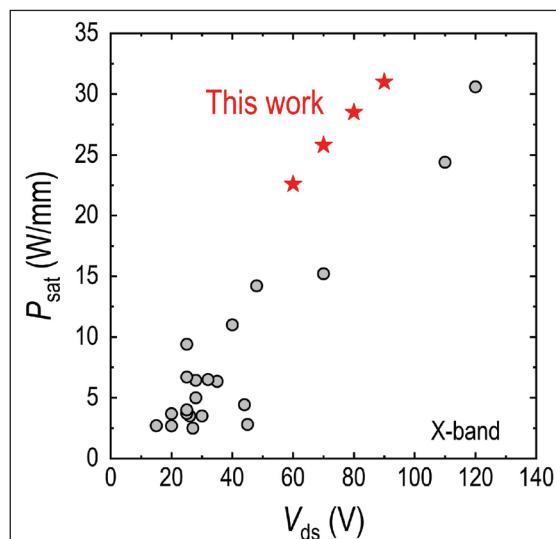

Thermal CVD equips next-generation InAlGaN/GaN HEMTs with high frequencies, exceptional powers and high reliability

16

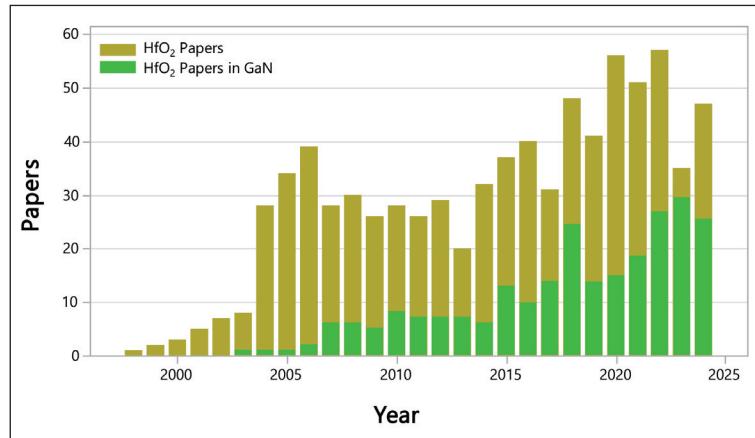

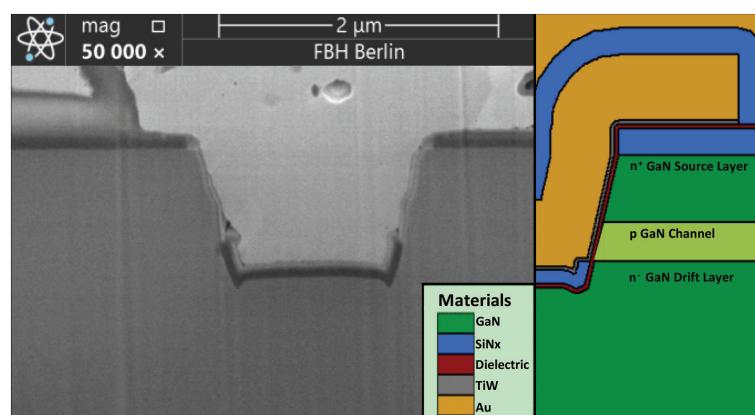

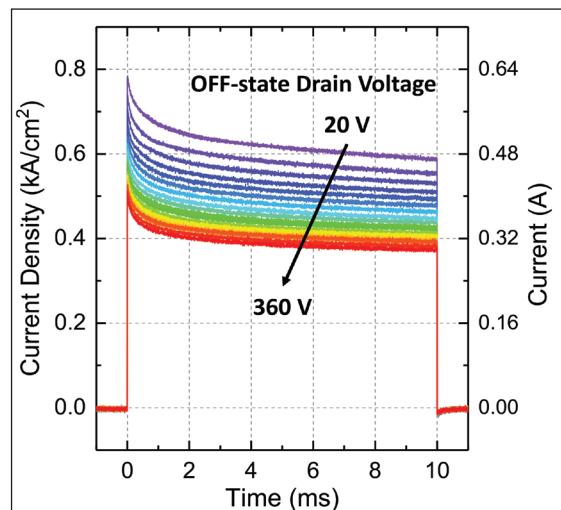

### 38 HfO<sub>2</sub> for better GaN transistors

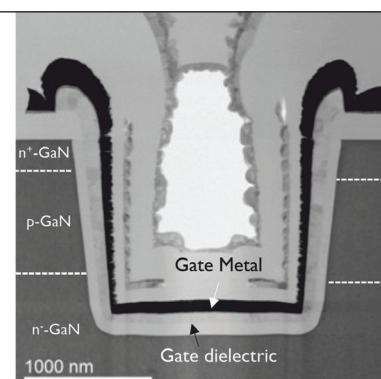

Introducing a HfO<sub>2</sub> gate dielectric improves the vertical GaN transistor, boosting its drain current density and its breakdown voltage

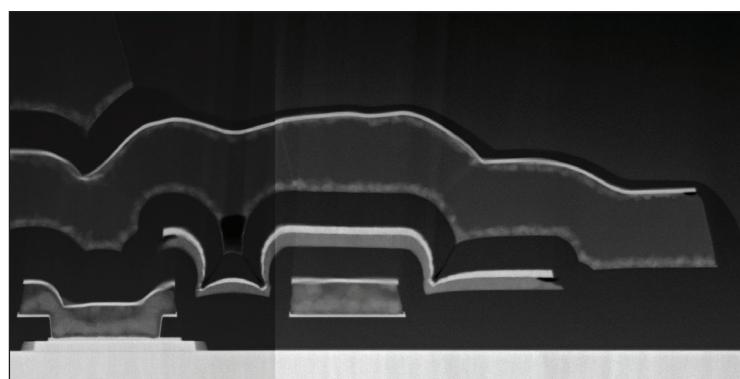

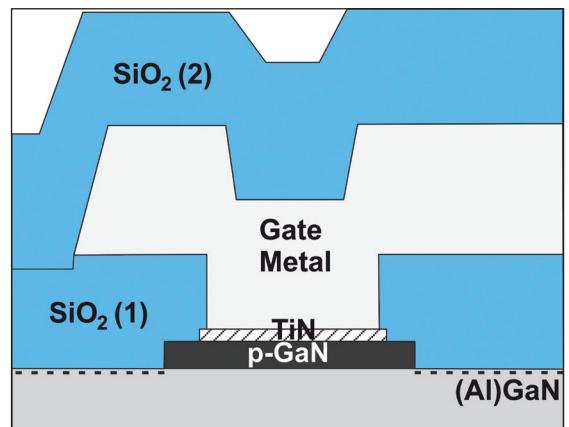

### 42 Engineered substrates enhance high-voltage GaN power electronics

Substrates with a ceramic AlN core and a silicon top surface provide a promising platform for the production of high-voltage, fast-switching GaN devices and ICs

34

## NEWS ANALYSIS

### 14 Ncodin's nanolasers eye AI infrastructure

Delivering a revolutionary energy-per-bit, the French start-up's nanolasers are a compelling source for on-chip communication in tomorrow's data centres

### 16 Aiding AI with the microLED

Promising to provide the most efficient links for tomorrow's energy-hungry data centres are links formed from vast arrays of microLEDs, employed alongside optical fibres and photodetectors

### 18 Polymatech: Propelling Indian optoelectronics

The launch of powerful UV LEDs for industrial curing helps to strengthen the emerging compound semiconductor industry in India

## RESEARCH REVIEW

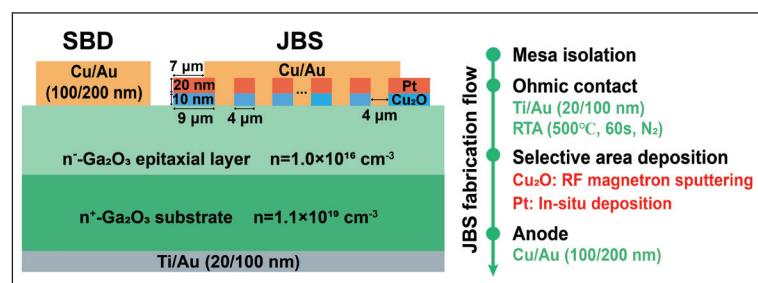

### 48 Building better UVB lasers

### 49 Advancing Ga<sub>2</sub>O<sub>3</sub> diodes with copper anodes

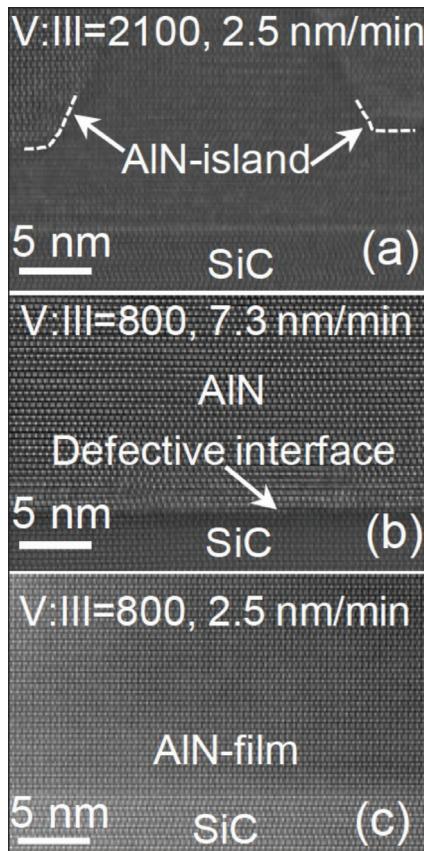

### 50 Improving MBE for GaN power devices

|                                            |                                   |                    |

|--------------------------------------------|-----------------------------------|--------------------|

| <b>Editor</b> Richard Stevenson            | richard.stevenson@angelbc.com     | +44 (0)1291 629640 |

| <b>News Editor</b> Christine Evans-Pughe   | christine.evans-pughe@angelbc.com |                    |

| <b>Design &amp; Production Manager</b>     |                                   |                    |

| Mitch Gaynor                               | mitch.gaynor@angelbc.com          | +44 (0)1923 690214 |

| <b>Director of Logistics</b> Sharon Cowley | sharon.cowley@angelbc.com         | +44 (0)1923 690200 |

| <b>Event &amp; Media Sales Executive</b>   |                                   |                    |

| Ranjodh Avern                              | ranjodh.avern@angelbc.com         | +44 (0)2476 718970 |

| <b>Circulation</b> Scott Adams             | scott.adams@angelbc.com           |                    |

| <b>Publisher</b> Jackie Cannon             | jackie.cannon@angelbc.com         | +44 (0)1923 690205 |

Compound Semiconductor is published nine times a year on a controlled circulation basis. Non-qualifying individuals can subscribe at: £115.00 per annum (UK), €165 per annum (Europe), \$198 per annum (air mail) (USA). Cover price £4.50. All information herein is believed to be correct at time of going to press. The publisher does not accept responsibility for any errors and omissions. The views expressed in this publication are not necessarily those of the publisher. Every effort has been made to obtain copyright permission for the material contained in this publication. Angel Business Communications Ltd © Copyright 2026. All rights reserved. Contents may not be reproduced in whole or part without the written consent of the publishers. The paper used within this magazine is produced by chain of custody certified manufacturers, guaranteeing sustainable sourcing. US mailing information: Compound Semiconductor, ISSN 1096-598X, USPS Permit Number 25366, is published 9 times a year, Combined Jan/Feb, March, Combined April/May, June, July, Combined August/September, October, November, December by Angel Business Communications Ltd, Unit 6, Bow Court, Fletchworth Gate, Burnsall Rd, Coventry CV5 6SP, UK. T: +44 (0)2476 718970

E: info@angelbc.com

W: angelbc.com

## NEWS

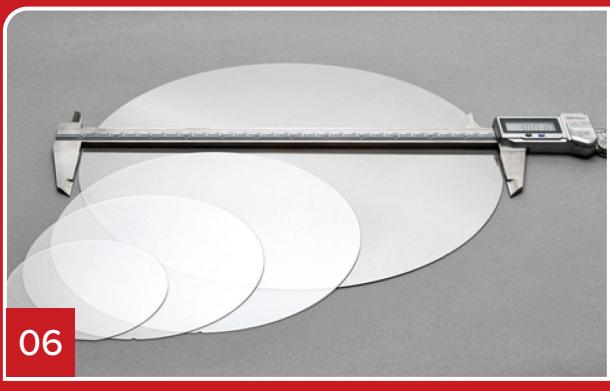

### 06 Wolfspeed makes 300 mm SiC breakthrough

### 07 Polar Light unveils the first nanoLEDs

### 08 Allos and Ennostar forge microLED partnership

### 09 Global EV SiC inverter installations hit record high

### 10 MicroLED reaches a make-or-break phase, says Yole

### 11 CGD appoints new CEO

### 12 Fuji and Robert Bosch collaborate on SiC modules

# Wolfspeed makes 300 mm SiC breakthrough

300 mm technology, enabling scalable platforms for AI, AR/VR, and advanced power devices

WOLFSPEED has announced a significant industry milestone with the successful demonstration of a single-crystal 300 mm SiC wafer.

This represents a major step forward for next-generation computing platforms, immersive AR/VR systems, and high-efficiency, advanced power devices, according to the company.

"Producing a 300 mm single crystal SiC wafer is a significant technical achievement and the result of years of focused innovation in crystal growth, boule growth, and wafer processing," said Wolfspeed CTO Elif Balkas.

"It positions Wolfspeed to support the industry's most transformative technologies, especially critical elements of the AI ecosystem, immersive virtual and virtual-reality systems, and other high-voltage device applications."

Wolfspeed says its 300 mm platform will unify high-volume SiC manufacturing for power electronics with advanced capabilities in semi-insulating substrates used in optical and RF systems. This convergence will support a new class of wafer-scale integration across optical, photonic, thermal, and power domains.

As AI workloads push data centers to their power limits, the demand for improved power density, thermal performance, and energy efficiency will continue to accelerate. Wolfspeed says its 300 mm SiC will enable integration of high-voltage power delivery systems, advanced thermal solutions, and photonic interconnects at wafer scale, extending system performance beyond traditional transistor scaling.

Next-generation AR/VR systems require compact, lightweight configurations that integrate high-brightness displays with expansive fields of view and effective

thermal management. SiC's material properties – including mechanical strength, thermal conductivity, and optical refractive control – suits it to multifunctional optical architectures.

Beyond AI infrastructure and AR/VR, moving SiC to a 300 mm platform could unlock a broader range of advanced power devices to support applications such as high-voltage energy transmission at the grid level and next-generation industrial systems that enable smaller, high-performance components that generate less heat.

## Onsemi to develop next-gen GaN power with GlobalFoundries

ONSEMI has signed a collaboration agreement with GlobalFoundries to develop and manufacture advanced GaN power products using GF's latest 200 mm eMode GaN-on-silicon process, starting with 650 V. This collaboration will speed up Onsemi's roadmap for high-performance GaN devices and integrated power stages, expanding its portfolio with high-voltage products to meet the growing power demands of AI data centres, electric vehicles, renewable energy, industrial systems, and aerospace, defence and security.

"This collaboration brings together Onsemi's system and product expertise with GlobalFoundries' advanced GaN process to deliver new 650 V power devices for high-growth markets. Paired with our silicon drivers and controllers,

these GaN products will enable customers to innovate and build smaller, more-efficient power systems for AI data centres, EVs, space applications, and beyond. We are on track to begin providing samples to customers in the first half of 2026, and scale rapidly to volume production," said Dinesh Ramanathan, SVP of corporate strategy, Onsemi.

"By combining our 200 mm GaN-on-silicon platform and US-based manufacturing with Onsemi's deep system and product expertise, we're accelerating high-efficiency solutions and building resilient supply chains for data centres, automotive, industrial, aerospace and defence, and other critical markets. With Onsemi as a key partner, we will continue to advance GaN semiconductors that meet the evolving

demands of AI, electrification, and sustainable energy," says Mike Hogan, chief business officer, GlobalFoundries.

Onsemi will pair its silicon drivers, controllers, and thermally enhanced packages with GF's 650 V GaN technology platform to deliver GaN devices with higher power density and efficiency. These include power supplies and DC-DC converters for AI data centres, onboard chargers and DC-DC converters for electric vehicles, solar microinverters and energy storage systems, motor drives and DC-DC converters, for industrial and aerospace, defence, and security applications. This effort means Onsemi's power semiconductor portfolio now includes the full spectrum of GaN technologies – from low-, medium- and high-voltage lateral GaN to ultra high-voltage vertical GaN.

# Polar Light unveils the first nanoLEDs

Swedish company says InGaN LEDs measuring 500 nm and smaller pave the way to monolithic RGB displays

POLAR LIGHT TECHNOLOGIES AB, a Swedish microLED company, has unveiled a breakthrough at SPIE Photonics West 2026, with the first series of nano-scale LEDs.

The company says its achievement illustrates the extraordinary flexibility of its patented pyramidal architecture, developed without requiring the traditional etching process.

Over the last several months, Polar Light has produced a series of electrically excited InGaN nanoLEDs, measuring 500 nm and smaller, which are built using the same monolithic architecture as Polar Light's existing microLED platform.

This new process makes it possible to scale the technology to significantly smaller dimensions without compromising performance or efficiency, according to the company.

“Reaching nanoLED scale without sacrificing LED performance or production capability is a major milestone for the industry,” said Oskar Fajerson, CEO, Polar Light Technologies. “NanoLEDs, in combination with our roadmap toward monolithic RGB, will enable the next generation of ultra-small, monolithic full-colour displays.”

MicroLED is widely regarded as the next display technology, due to its unparalleled brightness and low power consumption, making it possible to create whole new categories of display types for a wide variety of novel use cases.

In spring 2025, Polar Light demonstrated its first public prototype at Display Week. In January 2026, Polar Light announced a new €5 million+ funding round that will enable the company to bring its first products to market in late 2026.

## Mitsubishi samples new SiC-MOSFET bare dies

MITSUBISHI ELECTRIC has announced that it will shortly start shipping samples of four new trench SiC-MOSFET bare dies designed for use in power electronics equipment, such as electric vehicle (EV) traction inverters, onboard chargers, and power supply systems for renewable energy sources, including solar power.

These new power semiconductor bare dies will contribute to efforts to embed advanced bare dies in various power electronics equipment to lower power consumption while maintaining performance, according to the company.

Mitsubishi Electric exhibited the new trench SiC-MOSFET bare dies at the 40th Nepcon Japan R&D and Manufacturing show in Tokyo from January 21 to 23, as well as exhibitions in North America, Europe, China, India and elsewhere.

The four new trench SiC-MOSFET bare dies are similar to the company's existing trench SiC-MOSFET bare dies, but use a proprietary trench SiC-MOSFET structure to reduce power loss by approximately 50 percent compared to planar SiC-MOSFETs.

Furthermore, manufacturing processes including Mitsubishi Electric's proprietary gate oxide film manufacturing method suppress variations in power loss and on-resistance to ensure stable quality over a long period of use.

# Allos and Ennstar forge microLED partnership

**Collaboration to establish silicon fab-compatible supply chain for microLED products**

ALLOS SEMICONDUCTORS of Germany and Ennstar of Taiwan have announced a partnership to bring 200 mm GaN-on-silicon LED epiwafers for microLED applications into volume production. This collaboration represents a key milestone in establishing a silicon fab-compatible supply chain for microLED products.

Through this partnership, Allos will be able to deliver its GaN-on-silicon epiwafers at the volumes required by its customers, supporting their transition into microLED volume production. Ennstar takes on the role of Allos' manufacturing partner for 200 mm GaN-on-silicon LED epiwafers.

Ennstar has one of the world's largest LED manufacturing infrastructures and expertise in high-end LED technologies, including microLEDs. In addition to manufacturing, Ennstar will also contribute its advanced LED-related technologies to further enhance the product performance.

"With Ennstar we work with the best possible partner to provide our customers with a high quality and scalable supply of epiwafers. Together we can offer the industry's best combination of highest LED efficiency and superior on-wafer and wafer-to-wafer yields for microLED chip manufacturing," said Burkhard Slischka, co-founder and CEO of Allos.

"This partnership delivers competitive GaN-on-silicon microLED solutions and provides a scalable production pathway compatible with standard silicon foundry processes," said Terry Tang, president of Ennstar Corporation. "By partnering with Allos, we can now address the 200 mm GaN-on-silicon LED epiwafer segment alongside our existing market-leading microLED solutions, offering a uniquely

comprehensive value proposition to the rapidly evolving microLED industry."

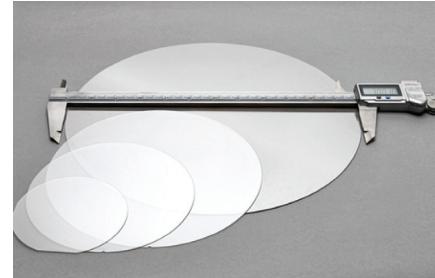

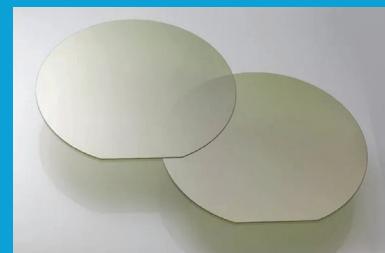

Designed for compatibility with standard silicon fabs, Allos' epiwafers are available in a thickness of 725 µm and conform to silicon industry cleanliness and contamination standards.

"We share our customers' vision that using standard silicon fabs for microLED manufacturing will unlock the yield and cost efficiencies needed to make mass production of microLEDs economically viable," explained Slischka. He added: "Through our partnership with Ennstar, we can now quickly scale up epiwafer production with increasing demand for microLED products."

The partnership also paves the way for 300 mm GaN-on-silicon LED epiwafers, enabling efficient integration with 300 mm logic wafers – essential, for example, to enable ultra-fast and energy-efficient optical interconnects between AI processors and memory chips using microLED light sources. Allos has already demonstrated 300 mm capability since 2020 and continues to refine the technology with lead customers.

## Coherent 300 mm SiC platform addresses AI needs

COHERENT has announced that its next-generation 300 mm SiC platform will address the increasing higher power density, faster switching, and thermal efficiency demands in AI data centre infrastructure.

"AI is transforming the thermal-management landscape in data centres, and SiC is emerging as one of the foundational materials enabling this scalability," said Gary Ruland, SVP and general manager at Coherent. "Our 300 mm platform, which we plan to ramp in high volumes, delivers new levels of thermal efficiency that translate directly into faster, more power-efficient AI data centres."

The platform's conductive SiC substrates provide low resistivity, low defect density, and high homogeneity, enabling low-dissipation, high-frequency, and good thermal stability.

In AI and data infrastructure, these properties boost energy efficiency and thermal performance in next-generation data centre systems.

In addition, the company says the technology brings benefits for AR/VR devices, enabling thinner and more efficient waveguides for AR smart glasses and VR headsets, improving reliability in compact immersive display modules.

# Global EV SiC inverter installations hit record high

Traction inverter installations for EVs reached 8.35 million units in 3Q25, says TrendForce

TRENDFORCE'S latest investigations indicate that total global traction inverter installations for EVs reached 8.35 million units in 3Q25, representing a 22 percent increase YoY, driven by ongoing growth in the new energy vehicles market. Battery EVs (BEVs) and plug-in hybrid EVs (PHEVs) were the main contributors to this expansion, with installation increases of 36 percent and 13.6 percent, respectively.

Automakers are progressively enhancing the integration of chassis electric drive systems to achieve goals for smarter and more efficient EVs. This aims to reduce wiring and hardware costs while bolstering communication efficiency and increasing driving range.

In 3Q25, over 70 percent of inverter installations were part of '3-in-1' or greater configurations, including components like reducers and motors. The adoption of '4-in-1' or higher integrated systems increased from 16 percent in the same period of 2024 to 23 percent.

TrendForce highlights that SiC power semiconductors, due to their compact size and higher voltage capacity, are

## 3Q24-3Q25 Changes in EV SiC Inverter Installations (Unit: Million Units)

Source: TrendForce, Jan. 2026

**TrendForce**

now crucial for advanced electric-drive systems. In 3Q25, worldwide SiC inverter installations reached a record high, surpassing 1.5 million units. The adoption rate in EVs rose from 14 percent in the same period of 2024 to 18 percent, and when focusing solely on new energy vehicles, it reached 22 percent.

A detailed analysis of vehicle models fitted with SiC inverters reveals that 84 percent of these installations are in BEVs, with the remainder in PHEVs and range-extended EVs. China remains the leading market, accounting for

approximately 75 percent of all SiC inverter installations, whereas demand in Europe and the US is declining. Against a backdrop of geopolitically driven global dynamics, this structural concentration poses a risk that is difficult for IDM suppliers to mitigate or relocate.

While inverter installation volumes keep rising with the overall vehicle market, the total market value in 3Q25 dropped by 10 percent YoY. This suggests that despite market growth, automakers are exerting greater pricing pressure on the supply chain.

### MASIMO SEMICONDUCTOR

#### GaAs/InP MOCVD Epitaxial Growth & Foundry Services

Engineered for Excellence.

**All manufacturing in Hudson, New Hampshire, United States**

ISO 9001 and ITAR registered

- 35+ years of experience providing III-V solutions for optoelectronics application in datacom, energy, biotechnology, industrial, and defense industries

- State-of-the-art MOCVD growth reactors for R&D and production of custom III-V materials on GaAs and InP substrates

- Fast turnaround for high-volume manufacturing

- Some products manufactured include photocathodes for night vision goggles, laser power converters, avalanche photodiodes, custom photodiodes and LEDs/LED array chips

- 1-inch to 6-inch substrate sizes available

- Chips delivered as die-on-tape or in gel-paks

603-595-8900

sales@masimosemi.com

MasimoSemiconductor.com

**SCAN to learn more**

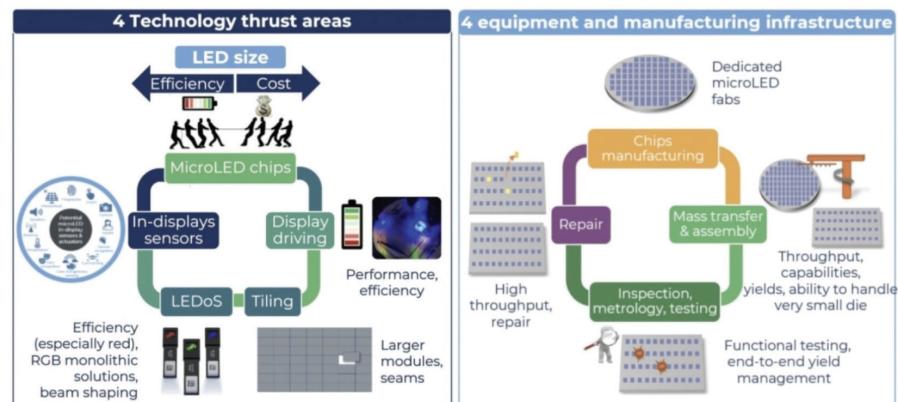

# MicroLED reaches a make-or-break phase, says Yole

MicroLED on TFT enters a decisive phase in 2025, with the first low-volume commercial products ramping at AUO

THE microLED industry is transitioning from hype to reality according to Yole's latest two reports: *MicroLED Markets, Applications, and Competitive Landscape 2025* and *MicroLED Technologies, Equipment, and Manufacturing 2025*.

After years of development, the first commercial displays, Garmin's smartwatch and Sony-Honda Afeela's automotive exterior display, entered low-volume production in 2025, manufactured on AUO's G4.5 line. Yole says this moment represents a critical test: the industry must prove that yields, manufacturability, and costs can converge toward a viable commercial path beyond niche B2B and LED-on-silicon applications.

Raphaël Mermet-Lyaudoz, technology and market analyst in photonics and display at Yole Group, commented: "MicroLED has progressed enough to exist without depending on a single flagship product. The momentum returned in 2025, supported by a clearer understanding of strengths, limitations, and realistic timelines."

Yet, the challenges remain significant. MicroLEDs must match OLED's cost while delivering differentiating performance, a demanding requirement that intensifies pressure on die efficiency at small pixel sizes, mass-transfer yields and throughput, repair strategies, and TFT-backplane limitations. Although investments in fabs and pilot lines continue, decision-makers remain cautious as processes and tools are still maturing.

The industry also faces a structural bottleneck: a lack of process standardisation. Today, most microLED display makers pursue unique architectures that require customised

equipment that is costly and complex. While some equipment suppliers, including Hardram, Coherent, Contrel, and PlayNitride, continue developing new generations of tools, others have stepped back due to uncertain prospects and daunting development challenges.

According to Eric Virey, principal analyst, display at Yole Group: "MicroLED supply chains are becoming clearer, with stronger alignment between chipmakers and panel makers. However, strategic questions remain,

particularly around foundry models, assembly distribution, and the maturity of large-stage, high-throughput tools."

Meanwhile, LED-on-silicon is emerging as the most promising volume driver, fueled by AI-accelerated demand for AR glasses and high-performance microdisplays. China leads the charge with JBD as the only player shipping in volume, while Sitan, Saphlux, Hongshi, Innovision and Raysolve scale new fabs. Outside China, alliances are forming around Porotech, PlayNitride, Micledi, Mojo Vision, Aledia, and others, each pursuing distinct architectures, materials, and manufacturing strategies.

MicroLED is also attracting growing interest for optical interconnects in data centers and high-performance computing, supported by major stakeholders such as TSMC, Intel, Nvidia, and Microsoft. Startups, including Avicena and Hyperlume, have raised significant funding to accelerate development in this emerging field.

After years of development, the first commercial displays, Garmin's smartwatch and Sony-Honda Afeela's automotive exterior display, will enter low-volume production in 2025, manufactured on AUO's G4.5 line

The microLED is entering a decisive phase, one defined by cautious investment, advancing supply-chain alignment, and a growing focus on manufacturability over the long term.

# CGD appoints new CEO

Appointment of Onsemi's Fabio Necco kickstarts next phase of growth for Cambridge company

CAMBRIDGE GaN DEVICES (CGD) has announced the appointment of Fabio Necco as CEO. The move is designed to drive forward CGD's entry into key markets.

Necco takes over as CEO from CGD co-founder, Giorgia Longobardi, who made the announcement, saying, "I am delighted to welcome Fabio to CGD and hand over the day-to-day leadership of the company while I channel my energy into my passion for bringing advanced, sustainable and energy-efficient power electronics solutions to market. Fabio is the right person with the right skill set to take CGD into its next growth phase, and I shall do all I can to support his initiatives as I transition into my new role as CMO at CGD."

Necco comes to CGD from Onsemi, the US-based semiconductor company specialised in delivering industry-leading intelligent power and intelligent sensing solutions, where he was vice president and division general manager with more than 25 years' experience in power electronics, application engineering, vehicle electrification, and data centres, all primary market focus points of CGD.

Necco said: "CGD is at an exciting juncture in its history. I have known CGD and Giorgia for years, and have long been impressed with its success under her leadership. I am very excited about CGD's unique technology, and to have been chosen to lead our entire team to the next stages of product development, as well as substantially increasing our presence in key markets."

Unlike many other GaN solutions,

CGD's ICeGaN technology uses a monolithic, single-chip approach that integrates all necessary components onto a single die, which substantially improves efficiency and performance.

As for CGD Co-founder, Giorgia Longobardi, in addition to her continuing role as CMO at CGD, she will continue to serve as a Director on CGD's Board and on the Advisory Board of the International Semiconductor Industry Group.

**TES**

Technology Engine of Science

**Creates Future!**

**200(150)mm Dual-Chamber**

**Tunable Triple Pair Nozzle**

Each nozzles play distinct roles to improve both thickness and doping uniformity

**200mm Performance**

Process reproducibility ensured Across the PM cycles (HCl free)

**THK  $\sigma = \pm 0.3\text{--}0.5\%$  / Avg. 0.69%**

**Doping  $\sigma = \pm 0.3\text{--}0.7\%$  / Avg. 1.07%**

**TRION**

**Tunable SiC Epi System**

**MOCVD for AIN Growth**

- Crystal Quality for AIN**

(XRD FWHM)

: (002) < 220arcsec

: (102) < 370arcsec

- Crack-Free AIN**

: Fast Gas Switchable Reactor

- Application**

- AIN, AlGaN Growth

- (Far)UVC, UV, UVA LED: 220-350nm

- Power Device (AIN, High Al-Content AlGaN, RF GaN)

- Photodetector (AlGaN-based)

**HESTIA**

# Fuji and Robert Bosch collaborate on SiC modules

Companies to work on EV SiC power modules with mechanical compatibility

FUJI ELECTRIC has announced an agreement with Robert Bosch GmbH to collaborate on SiC power semiconductor modules for electric vehicles that feature package compatibility.

Fuji Electric's SiC power semiconductor modules for EVs incorporate a unique packaging technology, designed to allow high power density in inverters. By modifying the size and number of mounted chips, the modules can accommodate a wide range of power requirements and circuit configurations from automotive manufacturer customers.

Moving forward, both companies intend to develop SiC power semiconductor modules with mechanical compatibility in terms of package outer dimensions and terminal positions. This will enable either module to be integrated into an inverter system without additional mechanical modifications, minimising the adjustment effort required for customers when using both module options in their systems.

This collaboration aims to shorten design periods and contribute to diversifying procurement sources.

As a result, customers will be able to use SiC power semiconductor modules from both companies without altering their inverter system specifications, leading to reduced design time and diversified procurement.

Both companies also plan to jointly develop user application technologies related to cooler design and various terminal connections when integrating SiC power semiconductor modules into inverter systems, and plan to provide technical support to customers.

## Atalco to establish large scale gallium plant

ATALCO, the only operating alumina refinery in the United States, has announced a partnership with the US Government to sustain and increase domestic alumina production and establish the country's first and only large scale primary gallium production circuit in Gramercy, Louisiana.

The company expects to produce over one million metric tonnes of alumina per year and up to 50 tonnes of gallium per year in Gramercy, Louisiana.

Both alumina and gallium are essential minerals for production of aerospace and defence systems, catalysts, semiconductors, and next-generation energy technology.

The partnership also involves Concord Resources Holdings in conjunction with Concord's majority shareholder, a fund managed by Pinnacle Asset Management, a leading commodities investment firm.

Atalco said: "Aligning this essential public sector support with private sector investment will secure onshore supply of alumina and gallium, which are contested commodity market segments currently dominated by China. This deal shows how quickly and decisively America can act to ensure long-term national security and economic resilience."

America's Department of War's Industrial Base Analysis and Sustainment programme has invested \$150 million of preferred equity in Atalco. Additional funding from the US Government is expected to close within 30 days of the equity closing. Pinnacle's fund, as the majority shareholder in Atalco via Concord, has invested more than \$300 million in private capital.

"For the past decade, our investment philosophy has centered on bolstering the US supply chain for critical minerals and other commodities," said Jason Kellman, chief investment officer,

Pinnacle Asset Management. "This strategic partnership plays an important role in strengthening our country's critical minerals supply."

"In addition to the core expansion of the Atalco facility, this investment unlocks significant growth potential, including increasing the site's mineral processing and power generation capabilities, all of which contributes to the long-term security of America's materials supply chain." said Scott Kellman, managing partner, Pinnacle Asset Management.

# RIBER's MBE 6000

**Leading

the way in mass-

production MBE**

**LOW RESIDUAL BACKGROUND**

**LOW ENERGY DEPOSITION**

**LOW TEMPERATURE**

**LOW DEFECTS DENSITY**

**RIBER**

info@ribер.com

www.ribер.com

INNOVATIVE SOLUTIONS FOR SEMICONDUCTOR INDUSTRY

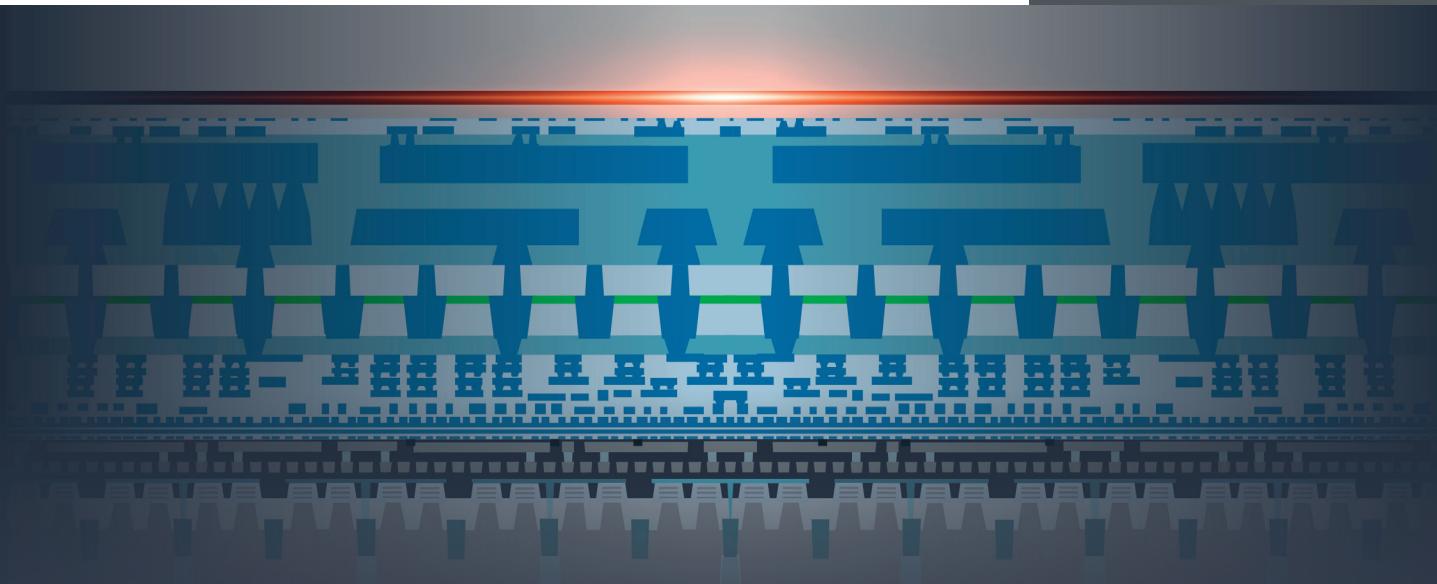

# Ncodin's nanolasers eye AI infrastructure

Delivering a revolutionary energy-per-bit, the French start-up's nanolasers are a compelling source for on-chip communication in tomorrow's data centres

BY RICHARD STEVENSON, EDITOR, CS MAGAZINE

SUPPORTING increasing adoption of AI is the building of more and more data centres. This roll-out of essential power-hungry infrastructure already accounts for hundreds of billions of dollars per annum, and total costs are forecast to exceed a trillion dollars a year by the middle of the next decade.

These eye-watering sums offer a fantastic opportunity for companies with technologies that can enhance critical hardware, especially if these products deliver breakthroughs in performance and efficiency.

One of the biggest issues in today's datacentres surrounds the transfer of data between chips. Although widely deployed for decades, copper is a bottleneck to higher speeds. And that's not its only downside, with other significant weaknesses including a limited reach and losses that lead to a significant contribution to overall energy consumption.

Offering attractive alternatives that address all these issues are various forms of optical links. There are a number of options for the light source – including edge-emitting lasers, VCSELs and microLEDs – and photons can be routed through optical fibres or waveguides in wafers.

Amongst these competing solutions, French start-up Ncodin, which has just raised €16 million, believes it has the winning formulation: miniature lasers that launch their emission into waveguides in silicon-based wafers.

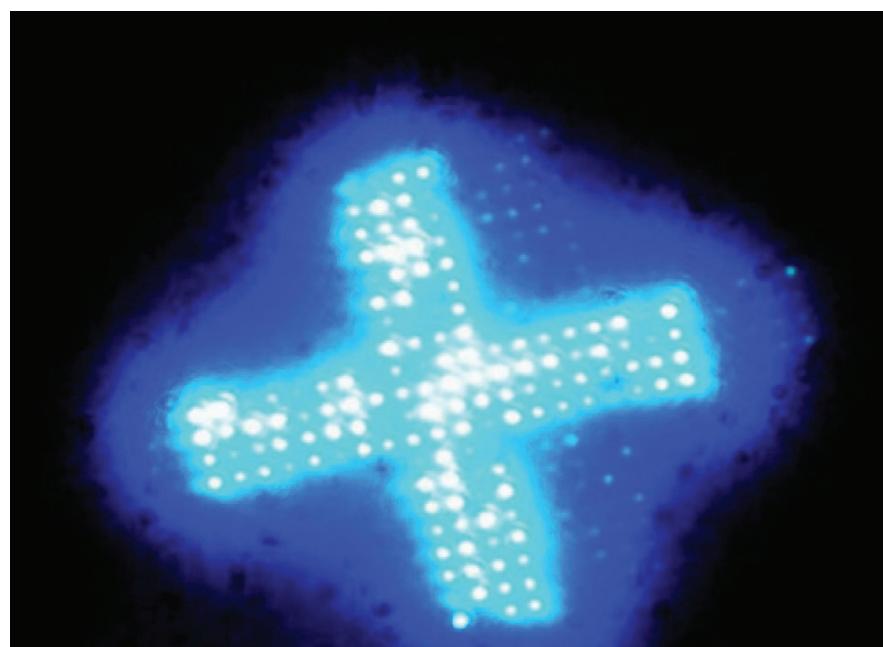

Optical interposers formed by this approach, featuring incredibly small lasers and photodetectors – both are created by bonding InP epiwafers to silicon substrates and subsequent photolithography – are claimed to deliver unrivalled efficiencies. Data transfer is incredibly fugal, at less than 0.1 pJ/bit, and integration can exceed 10,000 mm<sup>-2</sup>, enabling breakthroughs

in performance on two fronts – what is possible per Watt, and per dollar.

## A pioneering PhD

The origins of Ncodin can be traced back to the labs at the Centre for Nanosciences and Nanotechnologies, located in the southern suburbs of Paris, where co-founding CEO, Francesco Manegatti, developed these nanolasers during his PhD days.

Enthused by the emergence of a start-up ecosystem – in 2017, colleagues from this lab founded the quantum computing spin-off Quandela – Manegatti shifted his post-graduation plans from joining a big company to trying to commercialise the nanolaser technology he'd developed, a vision shared by his supervisor, now chief scientific officer and co-founder Fabrice Raineri.

Efforts in this direction began in late 2019 and continued during the pandemic, when these entrepreneurial partners started to try and secure initial funding and develop a first roadmap towards commercialisation.

The next steps involved: working with the support of CNRS on an R&D project; establishing a business plan; and bringing in third co-founder, Bruno Garbin, who switched roles from a postdoc in the laboratory to Ncodin's CTO.

Founding of the start-up followed in 2023, with Ncodin raising €3.5 million in a pre-seed funding round that closed in March 2024. Since then, headcount has mushroomed from four to 30 employees, and the company has established its own headquarters.

"We still exploit the facilities of CNRS, because this lab has the largest

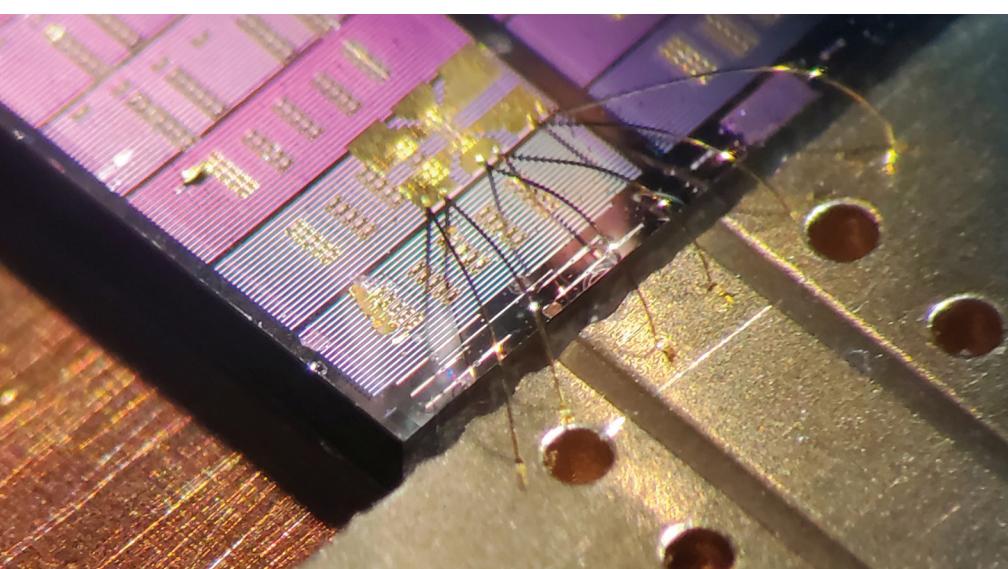

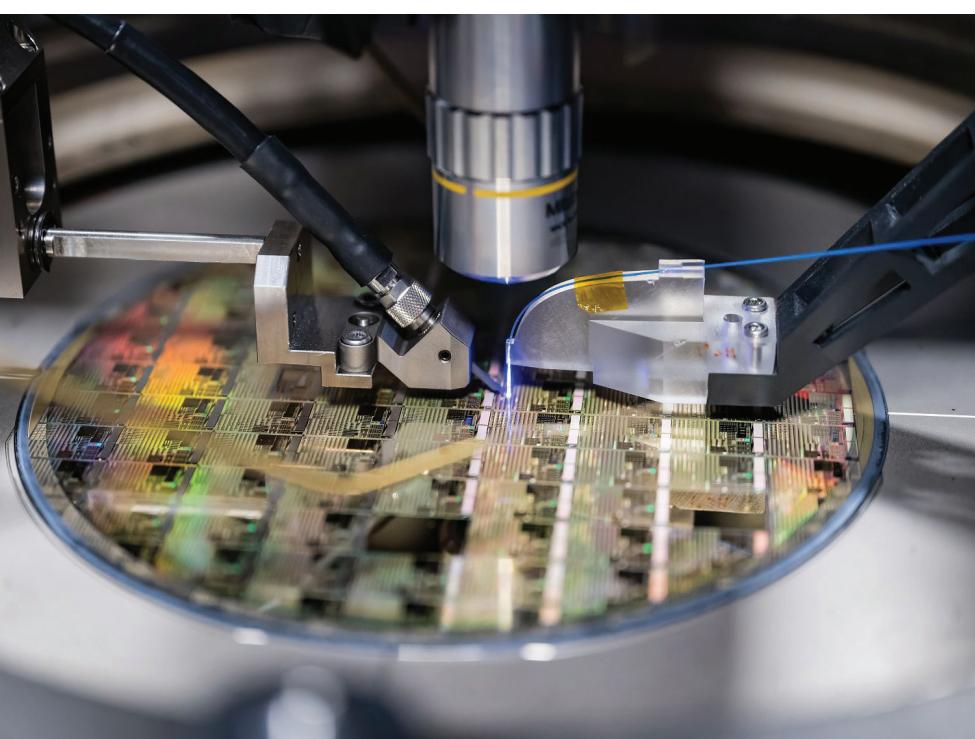

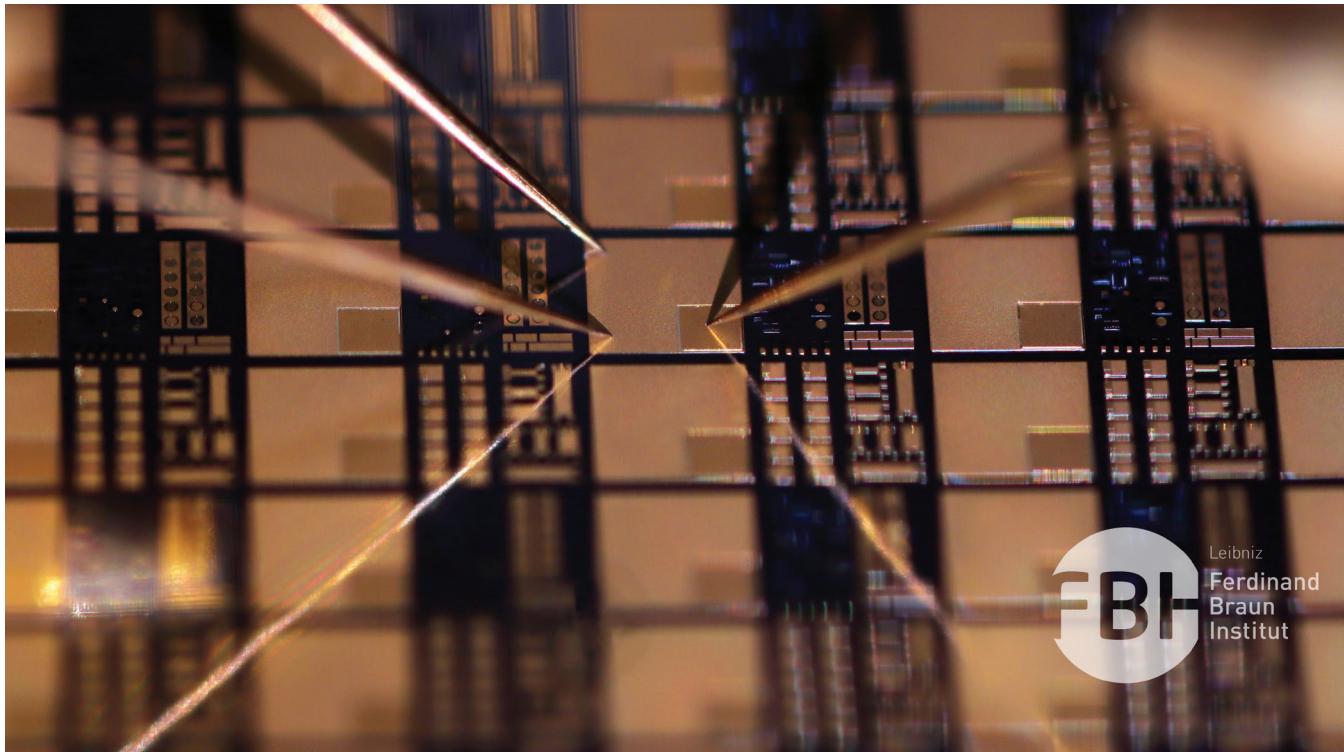

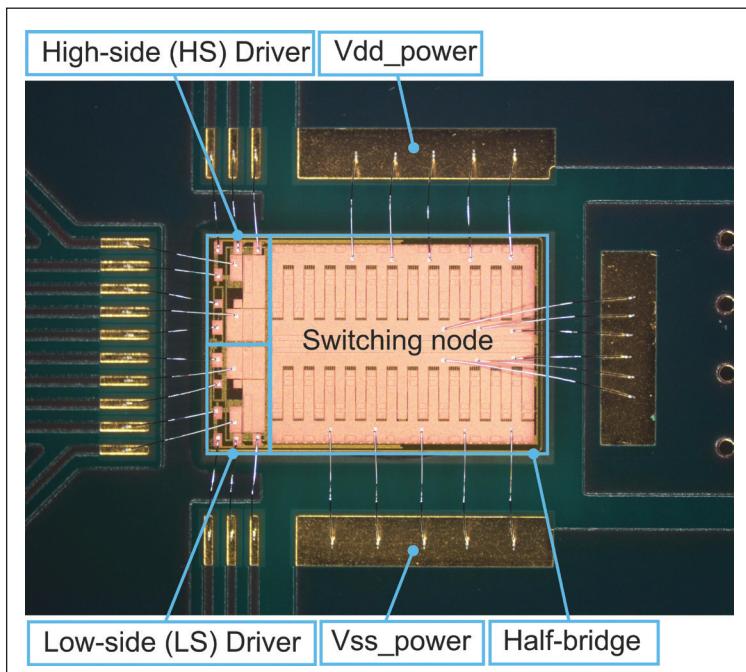

► Ncodin's silicon photonic chip integrating nanolasers, the core technology showing record energy efficiency below 0.1 pJ/bit. The wires provide a connection between the controller (an FPGA) and the nanolasers.

academic clean room of France. It's a 3,000-squared-metre clean room, where they have a lot of collaboration with private entities," explained Manegatti.

Ncodin uses this facility to develop its chip technology, and make proof-of-concept devices that are shared with partners.

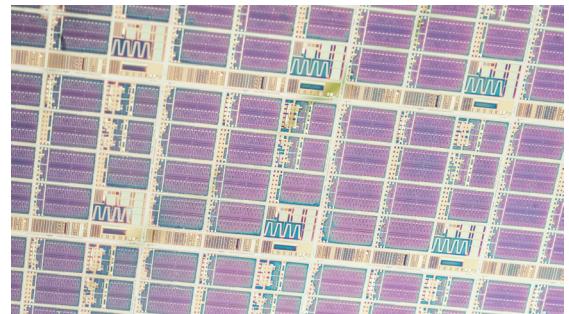

"In parallel, we are working on the industrialisation of our technology, to reproduce it in a CMOS pilot line on 300 millimetre [wafers]."

The start-up has always focused on optical interconnects. Neuromorphic architectures initially garnered consideration, but the primary goal is to complement copper and aid the scaling of infrastructure and process architecture.

"For extremely short reach, copper is best," argues Manegatti. "It's super resilient, it's super robust, you can deliver a high bandwidth."

But for connections beyond a few centimetres, links should switch to the optical domain, where Ncodin's solution addresses the challenge of transferring tens of terabits per second of bandwidth while consuming just a fraction of a picojoule per bit.

This is an attractive option for AI workloads, which are fulfilled through continuous communication between the compute element, which could be a GPU or an ASIC, and the high-bandwidth memory. For these tasks, nano-lasers promise to play a role in fulfilling demands for extremely fast retrieval of data, as well as the writing of data in the memory.

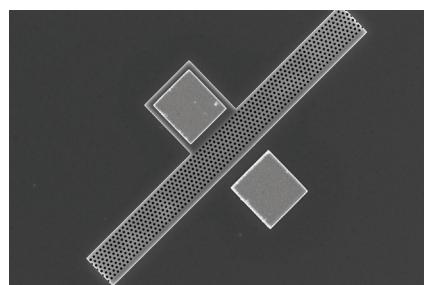

### Numerous nano-lasers

To produce its devices, the French start-up draws on external expertise for the growth of its epiwafers. Multiple coupons are crafted in these epiwafers, prior to hybrid bonding to silicon-based wafers. Subsequent lithography and patterning define the dimensions of lasers and photodetectors, both operating at telecom wavelengths. The emission from the lasers, which have a footprint that is 500 times smaller than their conventional cousins, evanescently couples into the waveguides in the underlying silicon wafers.

► Since its founding in 2023, headcount at Ncodin has increased to 30 employees.

Nanolasers produced by this process have an output of up to a few hundred microwatts – that's more than enough for the intended task – and an efficiency of around 15 percent. These low emitting powers prevent self-heating issues for these miniature sources, which are capable of delivering robust operation at temperatures approaching 100°C.

Thanks to the incredibly high density that can be realised with Ncodin's technology, the intention is to connect every input and output pin of every ASIC and every high-bandwidth memory to a nanolaser.

"Our goal is, of course, to add redundancy, to extend even further the lifetime and essentially the reliability of our chip," adds Manegatti.

The nanolasers are directly modulated, as it's not critical to have a high data rate per channel, thanks to the use of so many channels.

According to modelling by Ncodin, it's possible to realise data rates of up to 64 Gbit s<sup>-1</sup>. However, the nanolasers currently operate at 16 Gbit s<sup>-1</sup>.

► Ncodin's core technology is the production of telecom lasers with a footprint that is 500 times smaller than their conventional cousins.

"This is more than enough," argues Manegatti. "High-bandwidth memory, for example, is driven at 8 gigabits-per-second today."

Before Ncodin's optical interposers are deployed in data centres, they need to have proven reliability. Efforts in this direction are on-going, according to Manegatti, who remarks: "We are industrialising the solution, so the most important KPIs will be extracted during this project." Note, though, that his team have already demonstrated lifetimes that are well beyond a few thousand hours.

### The business plan

To produce its technology in volume, Ncodin will partner with a dedicated foundry to manufacture wafers packed with optical interposers.

"We'll sell the wafers to our customers, so chipmakers like Nvidia, Qualcomm, AMD, Intel, et cetera," says Manegatti. These household names will employ partners to test, assemble and package entire systems that combine Ncodin's wafers with a variety of chips, such as those for memory and processing.

Manegatti says that the main goal for now is to finish the industrialisation project, undertaken with a partner, and start qualification of its product.

"We're going to open an office in Silicon Valley, to be closer to our customers and partners, and to be able to engage in an even deeper relationship with them."

These plans, which make a lot of sense, promise to enable III-Vs to play yet another role in tomorrow's technology infrastructure.

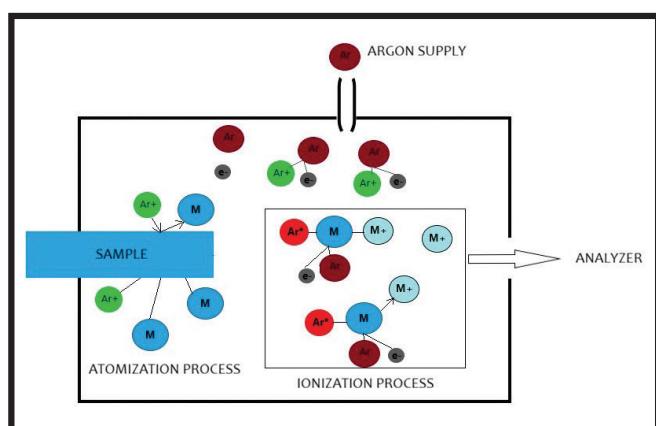

## Aiding AI with the microLED

Promising to provide the most efficient links for tomorrow's energy-hungry data centres are links formed from vast arrays of microLEDs, employed alongside optical fibres and photodetectors

BY RICHARD STEVENSON, EDITOR, CS MAGAZINE

AROUND the turn of the millennium many bought their first mobile phone, a purchase that helped to swell revenues for our industry on two different fronts. Sales created the first 'killer' application for the LED, coming from backlighting the displays and keypads of these handsets, and it led to rocketing revenue of GaAs HBTs and pHEMTs, with these devices deployed in RF amplifiers and switches.

Since then, there's not been another application that's delivered multi-billion-dollar sales for more than one class of device within the compound semiconductor industry. But that could change, thanks to AI, which is fuelling a hike in the roll-out of data centres.

Many makers of wide bandgap power devices are saying that they are aiming to exploit growth in data centres – efforts are directed at securing contracts for discrete components and modules for electrical infrastructure that combine exceptional efficiencies with the handling of high power densities. But there's also an opportunity within the optoelectronics sector, for sources and detectors that can form short-reach optical links that overcome a data transfer bottleneck while minimising the energy-per-bit.

Focusing on the latter is a three-year project starting this January. Led by French technology research institute CEA-Leti, this effort aims

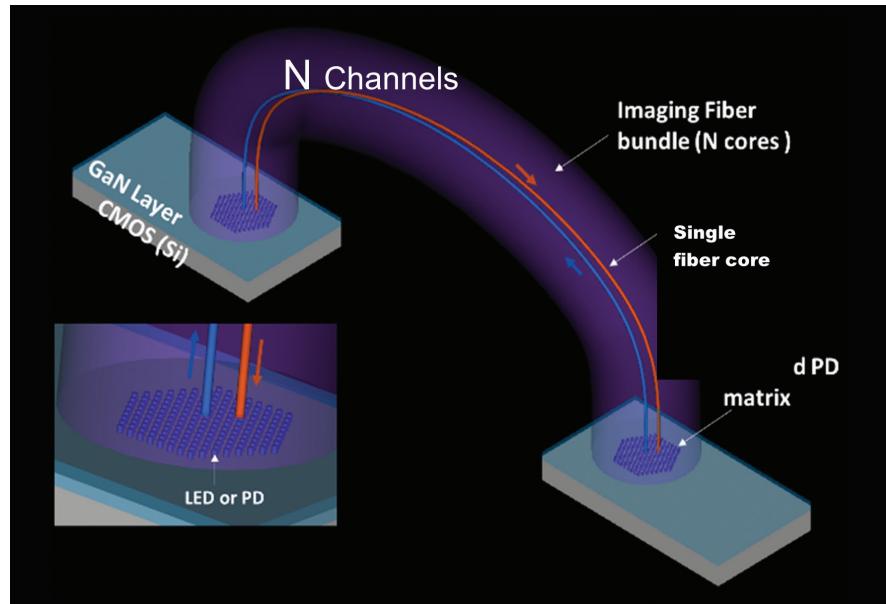

to drive the development of optical links formed by combining arrays of GaN-on-silicon microLEDs with fibres that have a relatively wide core and photodetectors. It is intended that this project will involve all the key players in the supply chain, including manufacturers of microLEDs, optical fibres, photodiodes and interconnects, as well as chipmakers, system integrators, and hyperscalers.

According to Jankus Vygintas, CEA-Leti Partnership Manager and spokesman for this three-year project – it's referred to as the *Multilateral MicroLED Data Link Program* – the proposed optical links could be deployed to transfer data from one chip to another within a board, or from one chip on one board to one chip on another board. Chip-to-chip transfer could even go from server to server or rack to rack, as the technology offers much appeal for links spanning 10 cm to 10 m.

Note that Vygintas is not suggesting the complete elimination of copper in data centres, arguing that this is the best choice for distances of just a few centimetres. But this should be the upper limit, as the longer these wires get, the more energy they consume.

Giving the success VCSELs have had in datacomms, they are another candidate for chip-to-chip links.

"For pluggables and so on, for longer distance links, it's probably the best developed technology" claims Vygintas, who explains that this surface-emitting laser can be viewed as a 'Ferrari' for short links, from both a cost and an efficiency perspective.

Providing a starting point for the project is the significant body of microLED work conducted by CEA-Leti that's led to the generation of around 100 patents. The well-renowned French research institute has been developing microLEDs since at least 2015, and around six years ago its efforts started to involve the modulation of these devices, initially to gauge their potential as sources for LiFi.

More recently, the focus has shifted to coupling the emission from microLEDs into fibres, and evaluating a key metric, the picojoules-per-bit.

"Nowadays, we are at around 5 picojoules-per-bit," reveals Vygintas, who adds that a primary objective of the project is to slash this critical figure to just 0.5 picojoules-per-bit.

"The other target is, of course, data density. In the long term, we aim to reach 10 terabit-per-second per millimetre."

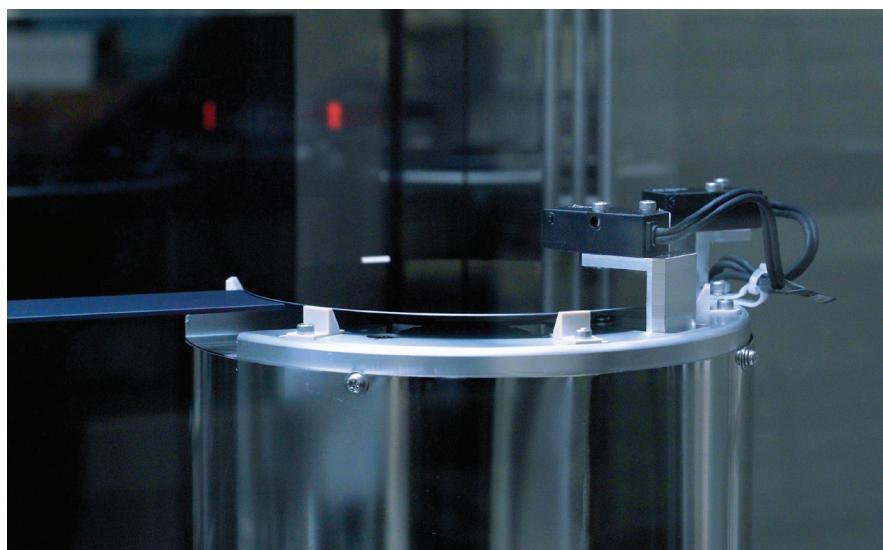

In CEA-Leti's 11,000 m<sup>2</sup> cleanroom researchers have developed a process for producing GaN-on-silicon LEDs on 200 mm substrates. Note, though, that the process can be scaled to 300 mm.

The team can shrink the size of its microLEDs to just a few microns – dimensions that are ideal for augmented reality, but a level of miniaturisation that introduce issues, including quenching at the edges of these emitters. For short-reach data links, Vygintas recommends using microLEDs with a size of around 10 µm, with emission coupled into fibres with a core of around 50 µm.

"We work on emission in the blue, but in principle, emission in green or red would be possible," says Vygintas.

While at first glance shifting emission to longer wavelengths is deleterious, driving a decline in efficiency that stems from an increase in indium content in the quantum wells, this view fails to grasp the bigger picture. That's because many more factors are at play, such as modulation bandwidth, fibre coupling and losses, and the efficiency of the detector – all contribute to the key metrics.

For data links, the emission from arrays of microLEDs is coupled into fibre bundles, a technology already employed for imaging in medical applications.

► Working principle of a microLED-based data link.

"We are testing all type of fibres, including plastic fibres," reveals Vygintas. "Some manufacturers provide glass multi-core fibres."

A key advantage coming from combining arrays of microLEDs with fibre bundles is a built-in redundancy at the system level.

"The VCSEL has to be well aligned, but in our case, we can afford some loss," claims Vygintas. The team at CEA-Leti tackles this task with partners that fabricate alignment and attach tools for the silicon photonics industry. These collaborators can use their technology to attach fibres to microLEDs.

Vygintas believes that an even better approach involves refining the design of the microLED so that it includes a resonant cavity that creates an emission profile tailored to coupling into a fibre. Such a device demands the introduction of Bragg mirrors made from dielectrics.

One of the options for the detector that's positioned at the other end of the fibre is a silicon-based diode, which is a well-established device; and the other contender is a GaN photodetector. While the latter is inferior today, it has a reasonable responsivity, and would simplify device integration. To try and improve performance, the team at CEA-Leti are aiming to optimise the epitaxial process for producing these devices.

Thanks to the fabrication of devices on silicon, drivers for these microLEDs can

be added by bonding to the backplane. Over the last four years Vygintas and co-workers have adopted this approach when they've been comparing various modulation schemes. While the more complicated ones may have greater promise, the team has concluded that the best solution is a basic on-off modulation scheme that simplifies amplification and photodetection.

"It should also be more efficient, because higher modulations can consume more energy," adds Vygintas.

He believes that CEA-Leti's status as a research institute ensures that it's in a great position to nurture the formation of an ecosystem for producing microLED-based short-reach optical links. Over the next three years, they will be bringing together those working in the lighting, semiconductor and fibre industries from all around the world. Some of these companies are already on-board – but their names cannot be revealed, due to non-disclosure agreements – and many more are expected to join.

"We occupy very special place in the whole ecosystem to provide prototypes. We are open to discussions with everybody," says Vygintas.

By adopting such a collaborative stance, CEA-Leti is giving the microLED a great opportunity to find its first killer application, and increase compound semiconductor content in the data centres of tomorrow.

Credit: Patrick Le Maitre, CEA

# Polymatech: Propelling Indian optoelectronics

The launch of powerful UV LEDs for industrial curing helps to strengthen the emerging compound semiconductor industry in India

DECADE after decade, our industry goes from strength to strength. This is evident in growing revenues that are now totalling many tens of billions of dollars per annum, and the expanding reach of our devices – they are now powering EVs, charging mobiles and illuminating our world in numerous ways, to name but a few applications.

As well as increases in sales and applications, our growth is highlighted by the range of locations producing these chips. Back in the twentieth century, makers of compound semiconductor devices were found predominantly in North America, Europe, Japan and South Korea. But in more recent times you can add Taiwan and China to that list, and now India.

Entry of the latter is gathering pace, spurred on by a desire by the Indian

government to make in India for India – that's an ambition that goes back well before the introduction of tariffs by Washington. Success is already underway, evident through: SiCSem, building India's first fab for manufacturing SiC chips; Navitas, providing a catalyst for the country to establish a GaN supply chain; and the efforts of Indian-based optoelectronics firm Polymatech Electronics, which has just expanded its portfolio of LED products. Its latest addition is a 'world-class' UV LED for curing applications, promoted at the recent Consumer Electronics Show (CES) in Las Vegas.

This UVA LED, emitting at around 400 nm, is said to deliver an industry-leading photon flux density that ensures sub-one-second curing.

Discussing this product with *Compound*

*Semiconductor*, CEO and Managing Director of Polymatech, Eswara Rao Nandam, says that his company's UV-LED platform can compete globally on three primary metrics: "One is electrical efficiency, second is operating lifetime, and third is optical power density."

For the latter, viewed by Nandam as actually the most important, the CW optical power density for the UVA LED is around  $150 \text{ W cm}^{-2}$ . As the chip size is typically a few millimetres squared, output is several watts.

Polymatech's UVA LEDs feature a chip-on-board architecture, selected for its superior thermal dissipation that stems from the aluminium substrates. Additional benefits of this particular design are uniform optical emission, an absence of interconnect losses, and a very high packaging density.

External quantum efficiency is 11.5 percent, notably higher than that for its siblings emitting in the UVC – they have values of 2-2.5 percent.

For the LEDs emitting at around 400 nm, lifetime is beyond 50,000 hours, based on defined operating conditions. This figure, defined by the time it takes for output to fall to 70 percent of its initial value, has been determined with the commonly adopted approach within industry that involves accelerated performance tests conducted at an elevated temperature and current.

According to Nandam, commercial opportunities for LEDs emitting in the UVA go well beyond what many

► Polymatech's key facility at Oragadam is used for advanced semiconductor packaging, R&D, ingot growth, wafer slicing, 3D printing and rapid prototyping.

imagine. As well as being employed for the curing of printing and packaging, these LEDs can provide a source for UV-cured coatings and finishes of automotive parts. There are also opportunities for very fast curing, found in electronics assembly, semiconductor assembly and 3D printing. Taken together, these applications create a global market for UV curing that's already worth many billions of dollars, and is growing fast. "I will not say [the market is] expanding, I will say it is exploding," enthuses Nandam.

### A family business

After graduating with an electrical and electronics degree from the Birla Institute of Technology and Science in Pilani, and gaining a doctorate in Electrical Engineering & Computer Sciences (EECS) from the University of California, Berkley, Nandam held positions in the compound semiconductor sector for several decades. During that time he has worked for various companies, including Nokia.

A key juncture came in 2011, when the tsunami in Fukushima sparked substantial losses for Japanese company Polymatech Electronics, a supplier of keypads for mobiles to the likes of Nokia, Ericsson, Sony and Motorola. Following that colossal and devastating tidal wave, Polymatech struggled for profitability for several years, ending up in arbitration. In 2018, the Nandam family purchased the company, revitalised it, and today its two key leaders are Eswara Rao Nandam and his son.

Under the leadership of this duo, Polymatech is expanding, in terms of its capacity, manufacturing sites, and where it plays within supply chains.

Initially starting with the packaging of chips for the automotive industry, Polymatech has expanded in many directions, drawing on sites it owns all over the world. There's a factory in Grenoble, France, that produces sapphire ingots and wafers; a site in the US that makes semiconductor testing and failure-analysis equipment; and there are advanced packaging facilities in India and Singapore. And recently Polymatech has purchased a company in Estonia that produces printed circuit boards.

This expansion is helping reposition Polymatech from a packaging company to one that makes products. Within the optoelectronics domain, as well as UVA LEDs that have just been announced, there are products emitting in the near infrared that help to diagnose issues beneath the skin, and those in the UVC for water purification

### In India, for India

In addition to overseas expansion, Polymatech is investing in its capabilities at home.

The key facility is at Oregadam, near Chennai. Here there's advanced semiconductor packaging, R&D, ingot growth, wafer slicing, 3D printing and rapid prototyping.

"We make everything here, and we give it to other places in Singapore, or in the USA, or in Estonia, *et cetera*," says Nandam, who adds that they are seeking permission from government for more land for this key site.

The two additional sites in India are located in Nava Raipur, which is home to a Polymatech industrial park that has facilities for ingot growth, wafer manufacturing, epitaxy, packaging, and product assembly; and Bannihalli, Krishnagiri, a site currently under construction that will be dedicated to manufacturing products for the Domestic Tariff Area (DTA).

All these efforts are helping to equip India with what Nandam views as "real manufacturing", rather than assembly services for other companies.

"We, Polymatech, are proudly building compound semiconductor expertise and developing skilled-engineer talent, anchoring India's high-value global chains."

This lofty goal is pursued while maintaining efforts overseas, an approach that makes strategic sense.

► Polymatech's UVA LED has an output of  $150 \text{ W cm}^{-2}$ , an external quantum efficiency of 11.5 percent, and a lifetime is beyond 50,000 hours.

"Singapore serves as a global customer interface," says Nandam, describing this facility as a bridge between Indian manufacturing and international markets.

Nandam believes that Polymatech started 2026 strongly, with attendance at CES generating enquiries related to system adoption that could be worth billions of dollars.

Goals for the rest of the year include stabilising the plant in Singapore, expanding the facility in Estonia, scaling the output power of its LEDs and driving their adoption.

And in addition, Nandam has another aim, which promises to leave a legacy: "I wish to establish India as a credible source of advanced semiconductor technology."

CEO and Managing Director of Polymatech, Eswara Rao Nandam, previously worked for Nichia and holds a PhD from the University of California, Berkley.

# INTERNATIONAL CONFERENCE

ANGELTECH

20-22 APRIL 2026

BRUSSELS

BELGIUM

CONNECTING, EDUCATING & INSPIRING THE COMPOUND INDUSTRY

CS INTERNATIONAL is part of the AngelTech series of events, which has produced for over 16 years, a portfolio of insightful, informative, and highly valued chip-level conferences.

Attracting more than 800 delegates and 80+ exhibitors consisting of co-located Advanced Packaging, PIC International, and PE International, plus a single exhibition area, delegates can dip in and out of every session

to put together their own tailor-made programme by selecting from over 130+ invited talks, delivered by leaders of the most innovative global companies of today.

With a significant overlap between the three conferences, attendees and exhibitors are exposed to the full relevant supply chains and customer and supplier bases.

## Key Themes for 2026

### Growing revenues in GaN Power Electronics

Sales of GaN transistors are tipped for tremendous growth throughout this decade and beyond. But what are the optimum strategies for exploiting this opportunity?

### microLEDs: How to gain market traction

The potential of the microLED is beyond question. But what's needed to ensure that this miniature marvel starts to generate significant sales?

### Revitalising the SiC industry

With profit margins shrinking, makers of SiC devices cannot rest on their laurels. But what are the key innovations to ensure success, in terms of production processes, fab operations and new device architectures?

### Advancing surface-emitting optoelectronics

What's needed to increase the spectral range and speed of the VCSEL, so it can target new applications? And how can the performance of PCSELs and UV LEDs improve, to drive their commercial success?

### Unlocking the potential of ultra-wide bandgap materials

Offering some tremendous characteristics, ultra-wide bandgap materials are poised for success. But which one is going to have the biggest impact? Will it be AlN? Or diamond? Or one of the oxides?

# ANGELTECH

## Sponsorship / Exhibition / Speaker OPPORTUNITIES AVAILABLE!

Sponsorship, exhibition, and speaker opportunities at CS International, enable and empower you to educate and penetrate compound semiconductor industry using a plethora of marketing tools.

Demand is high, with sponsorship, exhibition and speaking slots already being secured for 2026, so to avoid disappointment, please get in touch today.

## SPECIAL Event Discount:

Register before 31 MARCH 2026 and get 10% OFF!

Registration to AngelTech allows you to access both days of CS International, PIC International, Advanced Packaging and PE International.

10% OFF

### SPONSORS

#### PLATINUM

#### GOLD

#### MEDIA PARTNERS

#### SUPPORTING PARTNER

#### ORGANISERS

To find out more about our sponsor and speaker opportunities, contact us today on:

+44 (0) 2476 718970

[info@csinternational.net](mailto:info@csinternational.net)

[csinternational.net](http://csinternational.net)

ORGANISED BY

## Clas-SiC: A thriving three-pronged attack

The Scottish SiC specialist is excelling on the three fronts – alongside rising demand for prototyping, the manufacture of SiC devices at low-to-medium volumes is on the up, and the licensing side of the business is booming

**RICHARD STEVENSON, EDITOR OF CS MAGAZINE, INTERVIEWS

JEN WALLS, CEO OF CLAS-SiC WAFER FAB**

**RS:** What's your view on the current state of play in the SiC industry?

**JW:** It's changed a lot in the last 12 to 18 months. The number of players coming into the market has driven costs down, because capacity has been there. This has opened up new markets.

The cost of the substrate has reduced, bolstered by Chinese government subsidies. There has also been dramatic increases in quality for substrates, epitaxy, device performance and reliability.

Devices are more readily available than they were even a couple of years ago. Voltages are being pushed up in more applications, because device performance has increased. This wouldn't have happened before,

because silicon carbide was so expensive.

Price reductions have opened up markets for silicon carbide where it would not have played before, especially at lower voltages. Silicon carbide can now compete in consumer products, where GaN may have been the device of choice. Some of our customers are supplying makers of consumer products, like LG. That's been a huge change.

**RS:** A great deal of excitement in SiC has come from the EV market, which is suffering from some softness. Do you think that's a big issue?

**JW:** The compound annual growth rate of the EV market hasn't been at the levels suggested by Yole Group and

all the other market predictors. However, it's growing. You can see that yourself – you can see more EVs on the road.

Here at Clas-SiC, our customers aren't solely based on the EV market. I think the EV market is an absolute enabler to drive quality and device performance, but it's not all about the EV market.

Silicon carbide is now seen as a major enabler for data centres. The power systems for large data centres needed for the future of AI are going to need silicon carbide.

**RS:** When Clas-SiC founded in 2017, I'd argue that the world was a different place. While co-operation still exists, there's a move away from global supply chains towards sovereign capability. And there's also the rise in vertical integration. How do these trends impact the progress of Clas-SiC?

**JW:** Sovereign capability and silicon carbide supply chains are great opportunities for Clas-SiC.

We are licencing our technology to SiCSem, to build a fab in India for India. India's sovereign capability is driving that. It's an extremely high-profile project for the Indian government. This will be the first time that they have backed a compound semiconductor fab to this level.

Clas-SiC benefits, not just through the licence fee and the royalty payments, but through the capacity we will get in that fab. Part of the agreement is that we get 15 percent capacity in that high-

► Routine facilities pressure checks are vital to ensuring no unplanned downtime to the wafer fab.

volume fab. We access high-volume, lower-cost production, but without the associated CapEx.

It's very similar to the model we've already carried out in China. The Chinese fab is now up and running. It's qualified for diodes and it's going through MOSFET qualification.

For Clas-SiC, that's come at the right time. Here in the UK, manufacturing is expensive, electricity is expensive, and labour rates are high. To allow Clas-SiC to compete, that's very key for us.

For supply chains needing a route outside Asia, right now there are not many options available. That's good for us.

We've also signed an early engagement with a fab to be built in Bulgaria. It'll be good to have a high-volume route in Europe.

Our customers and others are nervous about US tariffs and where that's going to go. Again, that has put Clas-SiC in a good position.

**RS:** *Go back a few years and SiC substrate supply struggled to meet demand. Today, what's your view on SiC substrate and epiwafer supply, in terms of quality, quantity and pricing?*

**JW:** Chinese quality is still the best out there. That's what we are seeing, anyway. On our baseline MOSFET process, yields increased by 7 percent over the last year or so. That's huge.

Now there's overcapacity, so pricing's low. I don't think it's going to drop much more.

In the future, AR goggles will use silicon carbide for lenses. Our suppliers are already telling us that they're predicting 80 percent of their capacity will go for that type of material, rather than for device material. So, capacity could be an issue again in a few years if some companies can't survive without subsidies, and if a lot of capacity is taken up by AR goggles. I think the prediction is that in the next 3-5 years, everyone over the age of 18 will own at least one pair. That's going to take up a huge amount of capacity, so there's no way that the price is going to continue to drop as it has over the last 12 months.

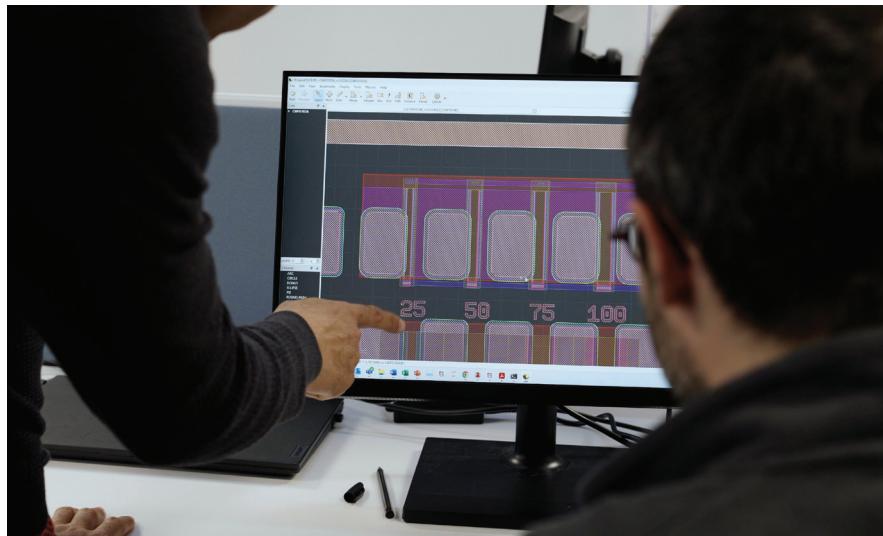

► Device scientists reviewing layout prior to mask making - an important step in device manufacture.

**RS:** *Are you happy to process epiwafers from all vendors? And do you offer recommendations to those seeking an epiwafer supplier?*

**JW:** We run a mixed model. Some of our customers supply wafers to us; others, we procure wafers on their behalf.

Normally, in production, we procure wafers on behalf of the customer, but at R&D, prototype-level, customers normally supply wafers to us. We now have PDKs for engineered substrates, plus p-type wafers. Having p-type wafers in the fab is a great leap forward, because if we can get a silicon carbide IGBT that would be amazing.

**RS:** *Around this time last year you secured £10 million of funding from Archean of India. Why did it invest, what's its return, and what's that funding been used for?*

**JW:** Actually, we received £10 million, and there was also a shareholder-to-shareholder arrangement, because Carl Johnson gave up equity in the company.

As well as being a sound business decision, it was a strategic decision for them, because they are the financial backers behind SiCSem Private Limited, who are building the fab in India. As part of that investment they get a seat on our board.

► A rapid-thermal-anneal tool loading station. Devices visit these tools at least twice during fabrication.

► Clas-SiC CEO Jen Walls at the SiCSEM fab groundbreaking ceremony in November 2025, attended by the Indian Government and dignitaries.

Ranjit Pendurthi, who's the Managing Director of Archean Chemical, sits on the Clas-SiC board now. Archean has brought a different perspective to our board, a really welcome perspective from my behalf.

**RS:** *Earlier this year, you signed a deal to set up a power fab in mainland Europe. What's Clas-SiC's role in this project, how much progress has been realised, and what is still to do?*

**JW:** Our role in the Bulgarian project will be the same as the Chinese and Indian licence agreements. We've signed an early engagement commitment to help them build a business plan to attract further investment.

We've been working in partnership with Wafer Fab Solutions, to help them to work on a toolset, and to help them build an OpEx and CapEx plan to feed into their business plan. The idea is that we will then help them set up the fab in Bulgaria and transfer our technology, whatever the generation of technology is at that point in time.

**RS:** *The founder of II-VI, Carl Johnson, is Clas-SiC's executive chairman. How much of a role is he playing in the direction of your company?*

**JW:** I personally value his mentorship over the years. He's a lot of experience. It's not just the technical side – he's run a huge company that's had varied revenue streams, the same as Clas-SiC does. We have our R&D revenue stream, our tech revenue stream, our production revenue stream, and our licencing revenue stream.

I have a weekly one-to-one with Carl that lasts an hour. That's the only input he has into the day-to-day running of Clas-SiC. The conversations are led by me. They can cover blue-sky thinking, a current issue we're having, or sometimes just how life's going for us.

I've been in the CEO role here at Clas-SiC for over two years. Clas-SiC has changed a lot over that time because the market has changed. Thankfully, Carl and the rest of the board have been extremely supportive to allow us to do that.

**RS:** *You have process design kits for 1200 V, 1700 V and 3300 V, and another for 2,300 V in development. How much interest is there in the higher voltages within this range?*

**JW:** There's a lot of interest. Electric cars require longer ranges and faster charging. Also, as governments are looking to improve grid infrastructure, devices that work at higher powers are required. We have customers prototyping as high as 6.5 kV with us. We even have others talking to us about 10 kV.

Our design kit is pretty flexible. We're really willing to get our customers to design and own the reliability of the device termination. We can adapt processes as much as we can. What the customer is doing is leveraging Clas-SiC's experience and processing of silicon carbide to push voltages higher. We're small and flexible enough that we're willing to do that.

These products at extremely high voltages, they'll never be high volume. They're probably quite niche. However, that's where Clas-SiC fits. So, it's a good part of our business.

**RS:** *In addition, you have a process design kit for diodes. Does this account for a significant proportion of your business?*

**JW:** Two years ago, I think diodes accounted for about 10 percent of the business. Last year it increased. This year it has decreased again.

One of the main drivers is that the licenced fab in China was mainly a diode customer. Now they've got their own fab. They're producing in their own fab. We get the benefit of royalties, but the diodes are not produced here at Clas-SiC.

Recently, we have attracted a few customers at an R&D level that are looking at a more bespoke-type diode technology. But I would say it's probably back down to 10 percent of our business.

**RS:** *There are two types of MOSFET: planar and trench. You offer the former, but are developing the latter. What's the motivation behind extending into trench MOSFETs?*

**JW:** Our customers have driven us towards developing a trench process. We have processed trench MOSFETs before, but it's been a customer-owned process. Now we are developing our own trench PDK, so customers will be able to design on our own process. The aim is to have a trench PDK by mid-year.

We also have super-junction on the horizon. The new kit we're bringing in is to help serve that technology roadmap. That's where the £ 10 million investment came in for technology advancement.

**RS:** *You offer both prototyping and low-to-medium volumes of production. Which of these accounts for most of Clas-SiC's day-to-day activity?*

**JW:** It's mixed. Having just come from the morning meeting, about 60 percent of the work-in-progress in the fab today is technology and 40 percent is production.

Most of the technology work is extremely engineering-intensive. We work with some major players in the industry that use us at an R&D level, because they're trying to leverage our expertise. I would hope in future that we will be able to licence parts of the process and black-box solutions.

Just now, for these people, we may use our gate-oxide process or our backside annealing process, but that's owned by Clas-SiC. They send us wafers just for that process. I hope in future we could licence these parts.

We also have long-standing, fab-less design companies.

**RS:** You also offer licensing of technology. How does that work in practice, and is it a significant part of your business?

**JW:** It's quite unique, as there are not many silicon carbide companies that will licence their technology and know-how right now.

While licensing is a key revenue stream for us, it's not only the revenue that's key – it's having capacity in these high-volume fabs. That's very much

part of our business model and strategy. In practise, we assist these fabs to get up and running by transferring our processes.

I think if I was to ask the owner of the Chinese fab, she would say that we've saved about three-to-four years in time-to-market because they qualified, prototyped and ran product here on our process while their fab was being built. They were able to sample customers. It became a process transfer, rather than a full qualification for their customers.

It's an ongoing relationship with our licenced customers. As we develop our technology, they will come back to licence the next generation. That's actually already happened with the Chinese fab.

At the ICSCRM Conference in 2025, Professor Anant Agawal stood up on stage and said that to make silicon carbide a success, it's going to take a village. And that is so, so true. I think collaboration is absolutely key.

**RS:** When transferring licenced technology and supporting these companies, do you send engineers to these fabs?

► In November 2025 Clas-SiC CEO Jen Walls addressed an audience of around 600 at the SiCSEM fab groundbreaking ceremony at Odisha.

**JW:** If I think back to China, our engineers were out there for about three months. Not the same engineers, because we would concentrate on one part of the process and set that up, and then another set of engineers would go.

That was an absolutely amazing experience for a lot of the guys and girls here at Clas-SiC. We sent graduate apprentices, we sent modern apprentices, as well as senior engineers, principal engineers.

## III/V-Reclaim

*More than just reclaiming...*

### Materials

GaAs

InP

Ge

GaSb

InSb

GaP

InAs

AlN

**Epi polishing**

low removal process for epitaxial layers to enable direct bonding

*Sustainable

Innovative

Unique*

**Backside thinning**

down to 50 micron

[sales@35reclaim.com](mailto:sales@35reclaim.com)

[www.35reclaim.com](http://www.35reclaim.com)

We still support these fabs through a consulting-type basis, and we'll continue to do that. It's an ongoing relationship.

We've been running this process for so many years, and developing it and improving it. Any problem they see, we have probably seen before. Where it's maybe taken them three weeks to get the root of a problem, we can fix it overnight.

**RS:** *The SiC industry is shifting to 200 mm wafers. As I understand it, you are still working with the 150 mm platform. Do you have plans to move over?*

**JW:** It would be too much investment right now. There's no immediate plan. However, when we're procuring equipment, we make sure that it's 200-millimetre-compatible.

Our licenced fabs are very much a route to 200 millimetre, because they are setting up as 200 millimetre.

We can compete at a low production level because of our varied revenue streams. In low-rate production, we can offer similar pricing to what these fabs can offer in China. However, that won't remain forever, so we do need to get our licenced fabs at 200 millimetre up and running.

**RS:** *With SiC, doping may be realised through both ion implantation and epitaxial growth with dopants. What do you see as the pros and cons of both approaches?*

**JW:** For me the jury's out. It's very early days. I think only time will tell.

We work with customers looking at and evaluating both methods. Implant is obviously an expensive process, and planters are costly CapEx investment. They're an expensive tool to manage in production. However, control is extremely good.

**RS:** *One area for improvement of the SiC MOSFET is its channel mobility. Many employ nitridation to address this issue, and there are reports of alternative, promising processes. Does Clas-SiC have a nitridation process, and if so, is it advancing?*

**JW:** We are always advancing, and what we have available right now is

**“** Electric cars require longer ranges and faster charging. Also, as governments are looking to improve grid infrastructure, devices that work at higher powers are required. We have customers prototyping as high as 6.5 kV with us. We even have others talking to us about 10 kV **”**

the best our customers have seen. Right now, there's ongoing work with Purdue University.

**RS:** *Within the UK community, is there much effort on SiC? And which research groups and companies are you collaborating with?*

**JW:** Specific silicon carbide activity within the UK is pretty limited. We have one commercial customer in the UK on silicon carbide that we're working with at a device level.

We work extremely closely with academia, with Warwick, the University of Glasgow, Strathclyde, and other universities around the UK.

We also work with some of the Catapults, NMS (the National Microelectronics Manufacturing Centre), and with partners that are looking to develop advanced module packaging or advanced packaging methods.