# COMPOUND SEMICONDUCTOR

CONNECTING THE COMPOUND SEMICONDUCTOR COMMUNITY

VOLUME 27 ISSUE IV 2021

**y** @compoundsemi

www.compoundsemiconductor.net

#### INSIDE

News, Analysis, Features, Editorial View, Research Review and much more

# SUPERIOR SWITCHING

New wavelength-blockers for datacom and telecom unite the strengths of InP and silicon photonics

#### SOARING SHARE PRICES

During the last twelve months many companies within the CS industry have outpaced the NASDAQ

## BUILDING BETTER DEEP-UV LEDS

Tunnel junctions tackle the transparency conductivity conudrum that has held back progress in deep-UV LEDs

# Global mega trends require best performance III-V materials

# **AIX 2800G4-TM**

- 3D sensing

- Augmented reality

- Autonomous driving

- Cloud computing

- Internet of things

- Next generation displays

Discover the MOCVD tool of record for AsP-based applications

Made in

Germany

info@aixtron.com www.aixtron.com

# VIEWPOINT

BY DR RICHARD STEVENSON, EDITOR

## Delivering data with microLEDs

WITHIN INDUSTRY, developing a new device doesn't just take a great deal of toil. It also needs a lucrative application that promises a great return on all the cash that's been poured into the project.

What's rarely predicted, but actually quite common, is substantial deployment of a device beyond its intended application. Take the GaN-based laser: developed to provide the optical source for the successor to the DVD player and recorder, this device is now having a second lease of life as a key component in laser welding systems for 'yellow' metals, such as copper. And who would have thought that the VCSEL, an obvious candidate for data transmission, would have gone on to enjoy a ramp in sales as the source for facial recognition in mobile phones.

Right now, almost all developers of the microLED are viewing this tiny chip as a direct-emitting pixel for an upcoming generation of displays that will set new benchmarks for efficiency and contrast. But Avicena, a start-up in Mountain View, California, is marching to a different beat – it sees the microLED as a great solution to the data bottleneck in computer systems. According to this west-coast venture, microLED-based optical links are set to speed data transfer within chips, between chips and across data centres.

This application is sure to raise a few eyebrows within the optolectronics industry. After all, much effort has already been devoted to developing various classes of laser for the task of moving data. But Avicena is advocating that for transporting data at distances from a millimetre up to ten metres, all these devices fall short in many regards: they are too large, they demand a high drive power, their performance drops off at elevated temperatures, they are pricey and their yield is poor.

By optimising the microLED, including its doping and quantum-well structure, the team at Avicena have increased the speed of this device so that it is capable of delivering data at 4 Gbit/s using on-off modulation. This is plenty fast enough, given that data transfer would take place along thousands of parallel lanes, each with its own microLED.

You might question this approach, viewing the routing of blue light through an optical fibre as not ideal, due to high levels of absorption and dispersion. But these are not show stoppers, thanks to the short link lengths; and blue emission is the sweet spot for a silicon detector, allowing CMOS-compatible fabrication of efficient receivers with integrated photodiodes.

According to Avicena, 10 Tbit/s links based on microLEDs, fibre and photodetectors could be produced for one-to-two orders of magnitude less than the cost of today's optical link technologies employed in data centres.

While I'm hopeful that the microLED will revolutionise displays once the technology for mass transfer has been refined, it's great to see that there are also other opportunities for this miniature light source.

Free weekly e-news roundup go to: www.compoundsemiconductor.net

# 20 CS shares race ahead

Stocks in the CS industry soar to well above pre-pandemic levels

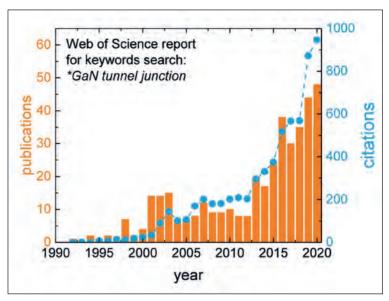

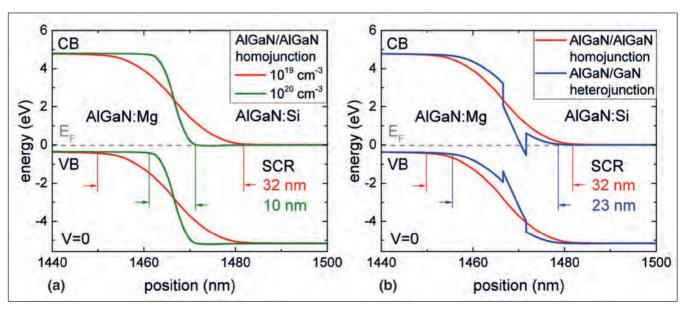

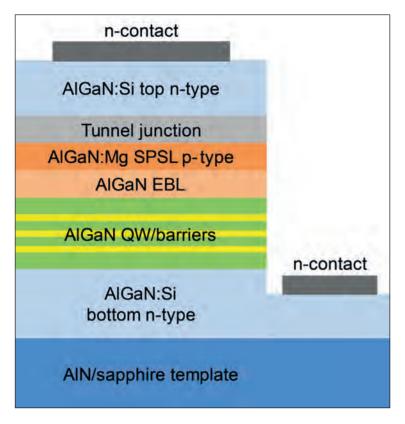

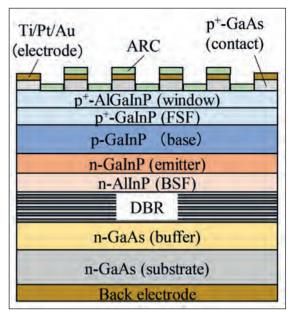

# 26 Tackling the transparency conductivity conundrum

Deep UV LEDs enjoy a hike in efficiency, thanks to the transparency of the MOCVD-grown tunnel junction

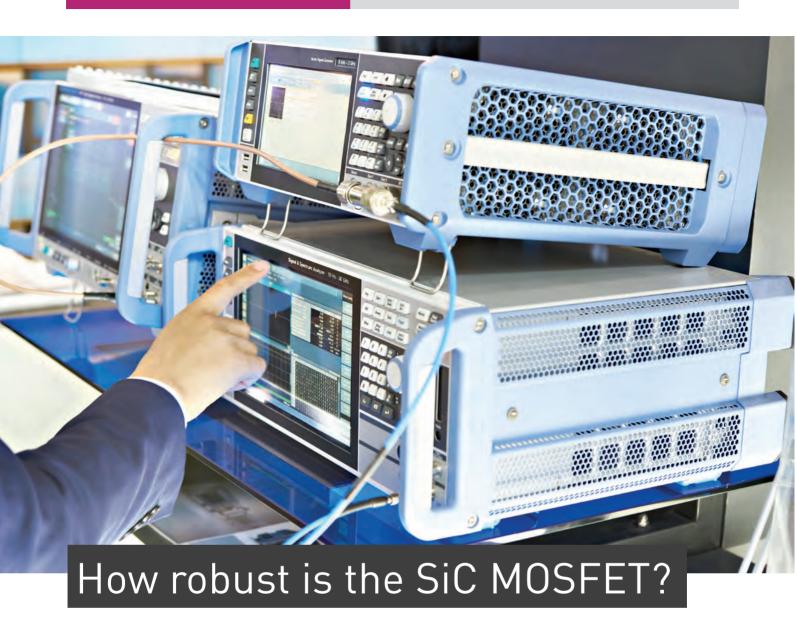

# 32 How robust is the SiC MOSFET?

Researchers at the International Reliability Physics Symposium report the results of investigations into the impact of defects and gate oxide quality on the performance of the SiC MOSFET

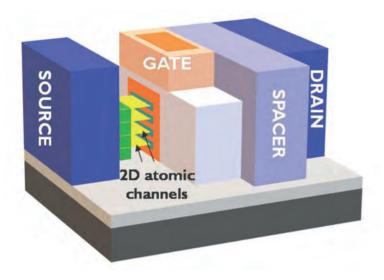

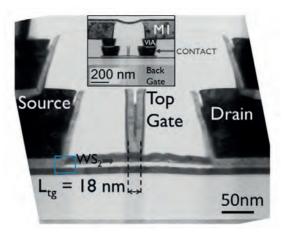

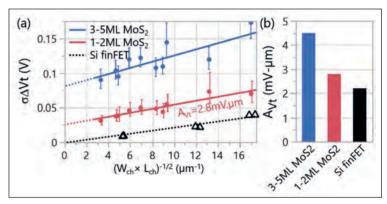

#### 40 2D transistors look to extend the logic roadmap

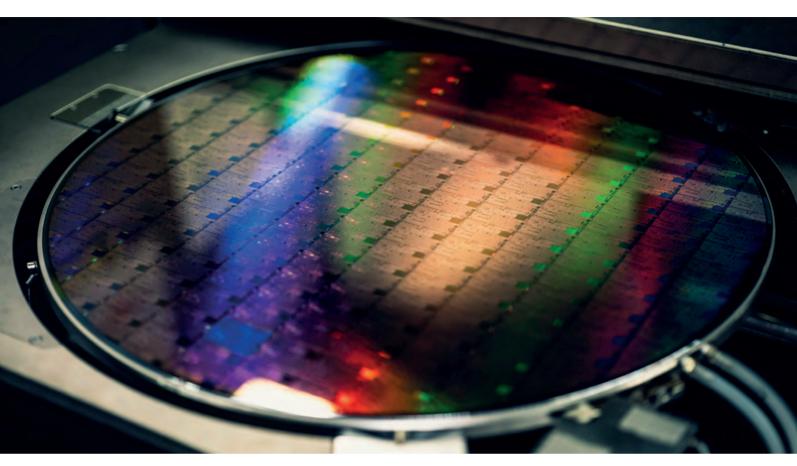

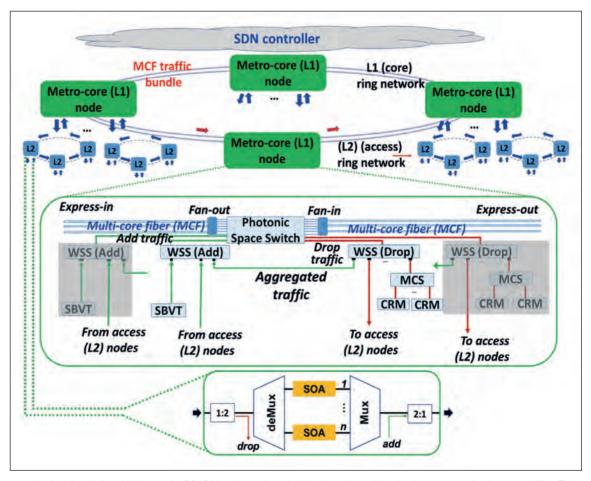

Development of WS<sub>2</sub> 2D transistors in a 300 mm CMOS fab provides a promising pathway for scaling the transistor

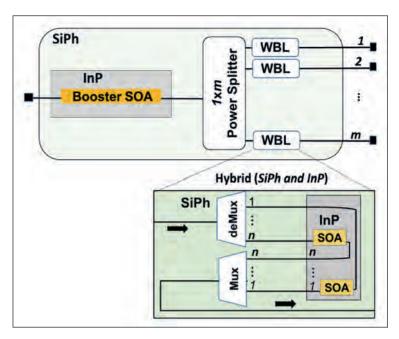

#### 44 Superior switching

Data centres and optical networks could benefit from a new generation of wavelength blockers, formed by uniting the strengths of InP and silicon photonics

#### **NEWS ANALYSIS**

#### 12 SiC: a glimpse of what's to come

From the industry transition to 200 mm wafers to future market leaders, Omdia analyst, Richard Eden, tells Rebecca Pool, what he expects will happen next

#### **RESEARCH REVIEW**

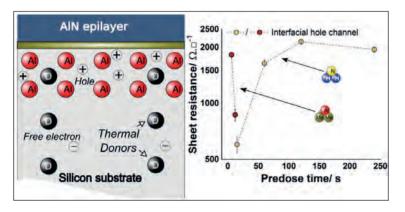

- 51 Exposing the origins of substrate conduction in GaN-on-silicon HEMTs

- 52 Powering underwater vehicles

- 53 AlN substrates shows promise for GaN HEMTs

#### **NEWS**

- 06 Sundiode develops stacked 3-colour microLEDs on a single wafer

- 07 Shifting from blue to red for better microLEDs

- 08 Showa Denko and Infineon sign SiC wafer agreement

- 09 Navitas to go public

- 10 EPC Launches DC-DC demo board for 48V mild hybrid cars

- 11 GaN power market to surpass \$1 billion in 2026

stephen.whitehurst@angelbc.com +44 (0)2476 718970

Editor Richard Stevenson Contributing Editor Rebecca Pool News Editor Christine Evans-Pughe Sales Executive Jessica Harrison USA Representatives Brun Media

Tom Brun Janice Jenkins

Publisher Jackie Cannon **Director of Logistics** Sharon Cowley Design & Production Manager Mitch Gaynor Circulation Director Scott Adams

richardstevenson@angelbc.com +44 (0)1291 629640 editorial@rebeccapool.com chrise-p@dircon.co.uk

scott.adams@angelbc.com

jessica.harrison@angelbc.com +44 (0)2476 718970

tbrun@brunmedia.com +001 724 539-2404 jjenkins@brunmedia.com +001 724-929-3550 jackie.cannon@angelbc.com +44 (0) 1923 690205 sharon.cowley@angelbc.com +44 (0)1923 690200 +44 (0)1923 690214 mitch.gavnor@angelbc.com

Chairman Stephen Whitehurst

Chief Technical Officer Scott Adams Directors Jackie Cannon, Sharon Cowley

Chief Executive Officer Sukhi Bhadal +44 (0)2476 718970 sukhi bhadal@angelbc.com

Coventry CV5 6SP, UK. T: +44 (0)2476 718 970 E: info@angelbc.com

+44 (0)2476 718970 scott.adams@angelbc.com Published by Angel Business Communications Ltd, Unit 6, Bow Court, Fletchworth Gate, Burnsall Road,

Compound Semiconductor is published eight times a year on a controlled circulation basis. Non-qualifying individuals can subscribe at: £105.00/e158 pa (UK & Europe), £138.00 pa (air mail), \$198 pa (USA). Cover price £4.50. All information herein is believed to be correct at time of going to press. The publisher does not accept responsibility for any errors and omissions. The views expressed in this publication are not necessarily those of the publisher. Every effort has been made to obtain copyright permission for the material contained in this publication. Angel Business Communications Ltd will be happy to acknowledge any copyright oversights in a subsequent issue of the publishers. The paper used within this magazine is produced by chain of custody certified manufacturers, guaranteeing sustainable sourcing. US mailing information: Compound Semiconductor, ISSN 1096-598X, is published 8 times a year, Jan/Feb, March, April/May, June, July, August/September, October, November/ December by Angel Business Communications Ltd, Unit 6, Bow Court, Fletchworth Gate, Burnsall Rd, Coventry CV5 6SP. UK. The 2021 US annual subscription price is \$198. Airfreight and mailing in the USA by agent named World Container Inc, 150-15, 183rd Street, Jamaica, NY 11413, USA. Periodicals postage paid at Brooklyn, NY 11256. US Postmaster: Send address changes to Compound Semiconductor, Air Business Ltd, c/o WN Shipping USA, 156-15, 146th Avenue, 2nd Floor, Jamaica, NY 11434, USA. Printed by: The Manson Group. ISSN 1096-598X (Print) ISSN 2042-7328 (Online) © Copyright 2021.

+44 (0)2476 718970

We strive for accuracy in all we publish; readers and contributors are encouraged to contact us if they recognise an error or omission. Once a magazine edition is published fonline, in print or bothl, we do not update previously published articles to align old company names, branding, marketing efforts, taglines, mission statements or other promotional verbiage, im-ages, or logos to newly created or updated names, images, typographic renderings, logos (or similar) when such references/images were accurately stated, rendered or displayed at the time of the original publication. When companies change their names or the images/flext used to represent the company, we invite organizations to provide Angel Business Communications with a news release detailing their new business objectives and/or other changes that could impact how customers/prospects might recognise the company, contact the organisa-tion, or engage with them for future commercial enterprise.

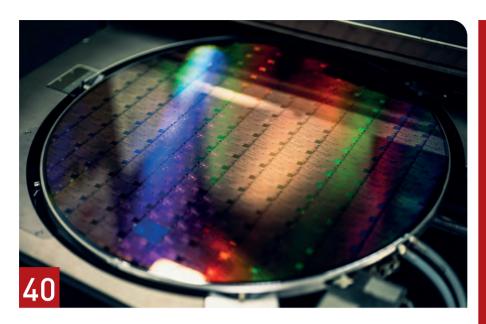

# Sundiode develops stacked 3-colour microLEDs on a single wafer

SUNDIODE, a Silicon Valley based company developing micro-LED technologies for display applications has announced the achievement of fully stacked 3-colour (RGB) microLED pixel devices on a single wafer. In the stacked-RGB pixel technology patented by Sundiode and developed in collaboration with KOPTI (Korea Photonics Technology Institute), a single pixel features three independently controlled microLED subpixels that are stacked vertically to allow full-colour emission from essentially the entire area of the pixel.

This pixel technology results in a very compact pixel structure and a substantial reduction in the pixel-transfer processing requirement for microLED display fabrication. In addition, the operation of a full-colour micro-display consisting of a pixel-array typically sized smaller than a penny is significantly enhanced due to increased utilisation of the extremely small pixel area.

The picture below shows a diced array of stacked-RGB pixels (left most). R, G, and B subpixels of three adjacent pixels of an array with each subpixel lit up separately (round-robin colours,

middle three), and the subpixels of the center pixel lit up simultaneously to 5400K white (right most).

The stacked-RGB pixel technology overcomes a particularly difficult obstacle to mass commercialisation of microLED displays: a need for laborious pixel-transfer processing. Whereas fabricating a microLED display using conventional planar-RGB technologies typically requires transferring discrete R, G, and B subpixels using a pick-and- place process, the stacked-RGB pixel technology substantially or even entirely removes such a requirement.

To achieve the stacked-RGB pixel device, epitaxial and fabrication technologies were developed on sapphire substrates that allow stacking multiple LED junctions where each LED is independently controlled.

This breakthrough multi-junction LED technology is pivotal in enabling full-colour generation. The well-defined spectral peaks of the three colours lend themselves to excellent colour-saturation characteristics and thus a very large colour space.

#### Nitride Semiconductors makes micro UV-LED breakthrough

NITRIDE SEMICONDUCTORS has succeeded in miniaturising the micro UV-LED chip for microLED displays. The company is now developing mass production technology.

Micro LED displays are being developed

by Apple and many other companies across the world. The red, blue, and green microLED chips that these companies are working on are under development. But it is proving difficult to miniaturise the red LED chip to  $50~\mu m$  or less.

Nitride Semiconductors' group is taking another approach by developing displays using micro UV LEDs to excite red, blue, and green phosphors. In this way, the cost of micro UV LED chips can be reduced, says Nitride.

Nitride previuously developed 385 nm micro UV LEDs that are 16  $\mu$ m x 48  $\mu$ m in size, and have a chip spacing as wide as 10  $\mu$ m in the horizontal direction and

30 μm in the vertical direction. About 3.4 million chips can be harvested from a 4-inch wafer.

The newly developed micro UV-LED chip has a chip size of only 12  $\mu$ m x 24  $\mu$ m, the chip spacing is 5  $\mu$ m in both the vertical and horizontal directions. About 14 million chips can be obtained from a 4-inch wafer, cutting costs by a factor of four.

When making a 25 mm square size display, 300,000 micro LED chips are required, but 11 micro LED displays can be made from one wafer. All chips are controlled by an IC driver to display a full-colour screen.

# Shifting from blue to red for better microLEDs

A NEW microLED developed at KAUST (King Abdullah University of Science and Technology) can efficiently emit pure red light and may help in the quest to develop full-colour displays based on just a single semiconductor.

Full-colour micro-displays can be created by combining red, green and blue (RGB) microLEDs. Now, a KAUST team of Zhe Zhuang, Daisuke lida and Kazuhiro Ohkawa have worked to develop a more efficient red LED.

The emission colour of an LED is determined by the material properties of the semiconductor. For example, nitride semiconductors can be used to make blue and green microLEDs, whereas phosphide semiconductors are generally used for red light. But combining different semiconductors in this way makes construction of RGB microLEDs more difficult and expensive. Besides, the efficiency of phosphide microLEDs reduces significantly with shrinking chip size.

Red-light emitting InGaN can be created by increasing the material's indium content. But this tends to lower the efficiency of the resulting LED because there is a mismatch between the separation of atoms in the GaN and InGaN, which causes atomic-level imperfections.

Moreover, damage to the sidewalls of an InGaN microLED induced during the fabrication process makes the new device less efficient. "But we have a chemical treatment to remove the damage and retain the high crystal quality of the InGaN and GaN sidewall interface," explains Zhuang.

Zhuang's team created and characterised a series of square devices with a side-length of 98  $\mu m$  or 47  $\mu m$ . Their 47  $\mu m$ -long devices emitting at a peak wavelength of 626 nm have an external quantum efficiency – the number of photons emitted from the LED per electron injected into the device – of up

to around 0.87 percent. According to the team, the colour purity of the red micro-LED is optimum because it is very close to the primary red colour defined by the industrial standard known as Rec. 2020.

"The next step is to increase the efficiency of the red microLED with even smaller chip sizes, maybe below 20 micrometers," says Zhuang.

"Then we hope to integrate RGB nitridebased LEDs for full-colour displays."

'Investigation of InGaN-based red/green micro-light-emitting diodes' by Z. Zhuang et al. Optics Letters **46** (2021)

# **Advanced Compound Semiconductor** Foundry Services

MOCVD · Fabrication · Testing

Advanced III-V semiconductor solutions for optoelectronics application in the biotechnology, telecommunications, energy, industrial, and defense industries.

MasimoSemiconductor.com | 603-595-8900

# Showa Denko and Infineon sign SiC wafer agreement

INFINEON TECHNOLOGIES has concluded a supply contract with the Japanese wafer manufacturer Showa Denko K.K. for an extensive range of SiC material including epitaxy.

The German semiconductor manufacturer has thus secured more base material for the growing demand for SiC-based products.

"Our broad and fast growing portfolio demonstrates Infineon's leading role in supporting and shaping the market for SiC-based semiconductors, which is expected to grow 30 to 40 percent annually over the next five years," says Peter Wawer, president of the Industrial Power Control Division at Infineon.

"The expansion of our supplier base with Showa Denko for wafers in this growth market marks an important step in our multisourcing strategy. It will support us to reliably meet the growing demand mid to long term. Furthermore, we plan to collaborate with Showa Denko on the strategic development of the material to improve the quality while cutting costs at the same time."

"We are proud to be able to provide Infineon with best-in-class SiC material and our cuttingedge epitaxy technology," says Jiro Ishikawa, Senior Managing Corporate Officer from Showa Denko K.K.

The contract between Infineon and Showa Denko K.K. has a two-year term with an extension option.

SDK expects the contract will enable Infineon to apply SDK SiC materials to various power semiconductor products and the two companies to accelerate improvement in quality of products by bringing together the two companies' knowledge.

Due to the homogeneity in properties and low density of surface defects, SDK SiC epiwafers materials, which were launched into the market in 2009, have been adopted by electronic device manufacturers as parts of various devices including power supply for servers of cloud computing systems, inverters for railcars and solar power generation systems, and converters installed in quick charging stands for EVs.

#### Infineon introduces CoolGaN IPS family

INFINEON has added the new CoolGaN IPS family of integrated power stage (IPS) products to its broad portfolio of wide bandgap power devices. The initial IPS portfolio consists of half-bridge and single-channel products, targeting low-to-medium power applications, including chargers and adapters and switched-mode power supplies.

The 600 V CoolGaN half-bridge IPS IGI60F1414A1L is ideally suited for compact and lightweight designs in the low-to-medium power range. Coming in a thermally enhanced 8x8 QFN-28 package, it enables systems with high

power density. The product combines two 140 m $\Omega$  / 600 V CoolGaN e-mode HEMT switches with dedicated galvanically isolated high- and

low-side gate drivers out of Infineon's EiceIVER family.

The IGI60F1414A1L is easy to control due to the isolated gate driver with two digital PWM inputs. The integrated isolation function, the clean separation of digital and power ground, and the reduced complexity of the PCB layout are crucial in achieving shorter development time, lower system bill-of-material and lower total cost. The gate driver's input-to-output isolation is based on Infineon's proven on-chip coreless transformer technology. This is said to guarantee high speed and excellent robustness even for extremely fast switching transients with voltage slopes exceeding 150 V/ns.

The switching behavior of IGI60F1414A1L can be easily adapted to the needs of different applications by means of a few passive gate path components. This allows slew rate optimisation to reduce electromagnetic interference efforts, steady-state gate current setting, and negative gate drive for robust operation in hard-switched applications.

Furthermore, due to the system-in-package integration and the highly accurate and stable propagation delay of the gate drivers, the IGI60F1414A1L enables the lowest possible system dead-times.

## Navitas to go public

GAN POWER chip company Navitas Semiconductor has entered into a definitive agreement to combine with Live Oak Acquisition Corp. II, a publicly-traded special-purpose acquisition company.

The transaction, which values the combined entity at a pro forma equity value of \$1.4 billion, will result in Navitas becoming a publicly-traded company on a national exchange.

Driven by increasing demand for connectivity, electrification away from fossil fuels, and efficient sustainable energy sources, Navitas predicts GaN ICs can address markets estimated to grow to over \$13 billion in 2026. Markets include mobile, consumer, enterprise (data centre, 5G), renewables (solar, energy storage) and EV / eMobility.

Navitas GaNFast power ICs integrate GaN power and drive plus protection and control to deliver simple, small, fast and efficient performance. Navitas is in mass production and ramping shipments to many major OEMs and aftermarket suppliers, including Dell, Lenovo, LG, Xiaomi, OPPO, Amazon, Belkin and dozens of others. Over 18 million GaNFast power ICs have shipped, with zero reported field failures.

Navitas has a proprietary process design kit and over 120 patents granted or pending. Navitas estimates that GaN can impact up to 2.6 Gtons of CO<sub>2</sub> reduction annually by 2050.

Gene Sheridan, co-founder and CEO of Navitas, commented: "Navitas was formed with the vision to revolutionise the world of power electronics while addressing significant sustainability challenges for our planet. Not only has Navitas' world-class team invented and patented revolutionary new technology, but we have also overcome all the key hurdles associated with successfully bringing it to market. We are proud to enter the public capital markets with strong operating momentum and investor partners who share our enthusiasm for our long-term mission."

"We are excited to partner with Navitas," said Rick Hendrix, CEO of Live Oak,

"This is the most compelling opportunity we have seen in the semiconductor industry, and we are delighted that Navitas' solutions contribute meaningfully to reduced carbon emissions through more efficient power delivery."

"The capital raised through this transaction will allow Navitas to accelerate that vision as they expand from mobile and consumer markets into even more power-intensive applications like data centers, solar energy and electric vehicles - all while delivering a significant CO<sub>2</sub> reduction as part of their net zero initiative."

Navitas was originally funded by the company's management team, along with venture capitalists.

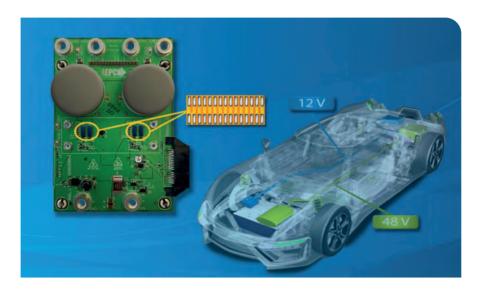

# EPC Launches DC-DC demo board for 48V mild hybrid cars

EPC has announced the availability of the EPC9137, a 1.5 kW, two-phase 48 V - 12 V bidirectional converter demonstration board based on its GaN FETs. The board operates with 97 percent efficiency in a very small footprint, according to the company.

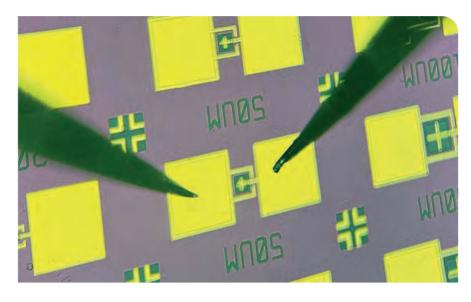

The design of board is scalable; that is, two converters can be paralleled to achieve 3 kW or three converters can be paralleled to achieve 4.5 kW. The board features four EPC2206 100 V eGaN FETs and is controlled by a module that includes the Microchip dsPIC33CK256MP503 16-bit digital controller.

By 2025, one in every ten vehicles sold worldwide is projected to be a 48 V mild hybrid. 48 V systems boost fuel efficiency, deliver four times the power without increasing engine size, and reduce carbon-dioxide emissions without increasing system costs. These systems will require a 48 V - 12 V bidirectional converter, with power ranging from 1.5 kW to 6 kW. The design priorities for these systems are size, cost, and high reliability.

EPC eGaN FETs can operate with 97 percent efficiency at 250 kHz switching frequency, enabling 800 W/phase compared to silicon-based solutions, which are limited to 600 W/phase due to the limitation on the inductor current at 100 kHz maximum

switching frequency. By using GaN FETs, it is possible to reduce the number of phases from five to four for a 3.5 KW converter while increasing efficiency. The efficiency of a four-phase GaN converter operating at 250 kHz is 1.5 percent higher than a five-phase silicon MOSFETbased converter operating at 100 kHz.

Overall, the DC-DC converter is three times faster, greater than 35 percent smaller and lighter, and offers greater than 1.5 percent higher efficiency compared with silicon MOSFET solutions. And the overall system cost is less. Additionally, the excellent efficiency and thermal performance of GaN FETs enables air cooling instead of water cooling and the small size of the GaN FETs strongly

reduce heat-dissipating aluminium housing for additional system cost saving.

"eGaN FETs provide the fast switching, small size, and high efficiency needed to further reduce the size and weight of 48 V – 12 V automotive power system converters. The demonstrated superior reliability of GaN FETs make them ideal for this very demanding application," said Alex Lidow, CEO of EPC. "The EPC9137 is an ideal example of the capabilities of GaN FETs to increase frequency and efficiency to allow smaller inductance for less phases and higher power density."

The EPC9137 demonstration board is priced at \$510.72/each and is available for immediate delivery from Digi-Key.

## GaN power market to surpass \$1 billion in 2026

THE GaN power market doubled in 2020 compared to 2019 and is poised to surpass the \$1 billion mark in 2026, according to Yole Développement. It forecasts that the markets for telecom and datacom, and automotive and mobility, will contribute in the mid- to long-term to overall growth, benefiting from GaN's ascension in fast chargers.

According to Yole, the GaN consumer power supply market will be the main driver, growing from almost \$29 million in 2020 to around \$672 million in 2026 with a CAGR of 69 percent.

Following the first small-volume adoption of GaN-based power supplies by Eltek, Delta, and BelPower in recent years, Yole expects a larger penetration of GaN. This market is expected to grow from \$9.1 million in 2020 to more than \$223 million in 2026. "The automotive and mobility market is also paying lots of attention to GaN, following big incentives for the electrification of cars and the interest in increasing driving range through system efficiency optimization." asserts Yole analyst Poshun Chiu.

Players such as EPC, Transphorm, GaN Systems, Texas Instruments and Nexperia are AEC qualified. The major IDM STMicroelectronics, through partnership

and acquisition, is also targeting GaN for EVs. Starting from 2022, GaN is expected to penetrate in small volumes in applications such as on-board chargers and DC/DC converters, mainly related to sampling by OEMs and Tier-1s. Yole expects the automotive and mobility market to reach more than \$155 million in 2026.

In 2020, the power GaN market doubled thanks to an impressive penetration of GaN devices in fast-charger applications. The adoption of GaN in the smartphone market is fueled by system compactness, high efficiency, and adapter multifunctionalities.

Fast charging is likely to be the killer application for the GaN power device market. So far. at least 10 smartphone OEMs have launched more than 18 phones with an inbox GaN charger. This growth will continue in the aftermarket as well, with companies like Apple, Xiaomi, and Samsung opting for an out-of-the-box charger solution.

In the long term, in cases where GaN has proven its reliability and high-current capabilities at a lower price, it can penetrate the more challenging EV/HEV inverter market and the conservative industrial market.

#### 2020-2026 power GaN market forecast split by application (Source: GaN Power 2021: Epitaxy, Devices, Applications and Technology Trends report, Yole Développement, 2021) 2026 Consumer Industrial \$1.1B Telecom & datacom Automotive & mobility Defense & aerospace Energy Others 2020 \$46M CAGR 2020-2026

ASK RICHARD EDEN, senior market analyst at Omdia, what single development has had the biggest impact on the SiC market in recent months, and his answer is the launch of Infineon Technologies' CoolSiC CIPOS Maxi: the world's first SiC IPM. This 1200 V integrated power module comprises a six-channel, silicon gate driver with six 1200 V CoolSiC MOSFETs. and signalled the end of the power semiconductor company's roll-out of CoolSiC products in 2020.

As Eden puts it: "Infineon is a juggernaut in power semiconductors, especially in discrete and modules... the IPM was anticipated a while ago and we always thought it was the logical thing to do."

"We will see more companies introducing SiC IPMs someone like On Semiconductor could be next - but Infineon was the first company to get this finished and released," he adds.

According to Eden, the IPM offers the benefits of SiC MOSFETs, over silicon MOSFETs and IGBTs, but with the ease of having a co-packaged gate drive IC. Critically, the move could see IPMs being used in both domestic and more demanding industrial applications.

But 2020 wasn't all about Infineon. Other key SiC developments centre on new generations of existing products, such as ST Microelectronics' fourth generation 750 V SiC FET platform, as well as increasing production capacities from Rohm Semiconductor, X-Fab, II-VI, and of course Wolfspeed, the Cree company. Indeed, Eden reckons that Wolfspeed's Mohawk Valley Fab in New York state - set to be the world's first 8-inch SiC fab with production scheduled for 2022 - will be a game-changer.

"Many other semiconductor companies buy Wolfspeed wafers, so this facility could trigger the transition from six- to eight-inch wafers in the industry," says Eden. "Also, many companies currently using six-inch wafers are working with old, eight-inch silicon wafer equipment, so the move to the larger wafer size might not be too difficult."

"Yields will be poor with these eight-inch wafers initially, and it will take a year or two to get them back up with this larger wafer size," he adds.

Following the concerted efforts to ramp SiC wafer production, twinned with the many industry supply agreements, Eden believes the SiC wafer supply shortages that plagued the industry from 2017 to 2019 are no longer an issue, for now. Analyst forecasts predict strong market growth, which he reckons could strain future supply levels. "I know companies such as Rohm, Cree and II-VI are trying to add capacity beyond when they think they will need, but we will have to wait and see," he says.

Eden also reckons that the current pandemic hasn't affected SiC market demand significantly. As he says, factories temporarily closed during the first major lockdown of 2020, but have since recovered with the market having also grown slightly. "The silicon semiconductor market was affected more severely than the wide bandgap segment," he says.

#### Market leaders

Earlier this year, and for the first time, Eden, with Omdia, ranked SiC semiconductor supplier market shares, with intriguing results. For the overall power discrete and module markets in 2018

and 2019, Wolfspeed lead the way, followed by STMicroelectronics, Infineon, On Semiconductor and Rohm. But individual markets tell a different story.

For the SiC rectifier device market alone, Wolfspeed had a huge lead in 2018 and 2019, capturing more than 40 percent of the market in each year. "Wolfspeed has this lead as it is the oldest incumbent supplier of SiC discretes and has been making these for around 20 years," highlights Eden.

Infineon, Rohm, STMicroelectronics and On Semiconductor are ranked from second to fifth, respectively, again largely thanks to longevity. "Rohm is the newest supplier here, but is now established as it was the first company to mass produce SiC MOSFETs in 2010, and developed SiC rectifiers around the same time," says Eden.

For the SiC power MOSFET markets, STMicroelectronics takes pole position, which according to Eden, is thanks to the company's significant contract to supply devices to battery electric vehicle maker Tesla. Yet despite its Tesla-dependence, he expects ST to maintain its lead.

"Currently at fourth place [following ST, Wolfspeed and Rohm] Infineon would surely be higher in the rankings if it hadn't focused on developing SiC JFETs ahead of SiC MOSFETs during the mid-2010s," he adds.

The full SiC and hybrid SiC module markets are quite different, with Mitsubishi Electric and On Semiconductor leading each market in 2019, respectively. Germany's Vincotech, Infineon and Wolfspeed also feature highly in these markets with China players, StarPower Semiconductor and CRRC Times Semiconductor also creeping into the module supplier top five. According to Eden, many module suppliers tend to buy in power transistors and assemble these in the modules, rather than manufacture the chips themselves. Also, going forward, he expects to see more China-based players enter module markets.

"StarPower is currently the largest Chinese power module manufacturer and is still quite small in the overall market," he says. "But there are other Chinese companies making power modules, such as Nanjing SilverMicro Electronics, and they will become more prevalent following the Chinese government drive to use silicon carbide for electric vehicles and industrial applications."

Eden doesn't believe that the US-China trade tensions have particularly affected SiC markets. But as he adds: "There is a trend for Chinese companies to want to buy Chinese products, as strongly influenced by the Chinese government."

So what does Eden reckon will come next for the SiC market? For the time being, he expects that SiC technology will happily co-exist with silicon and GaN, capturing market share from silicon throughout this decade. However, beyond this timeframe may bring change. "Right now, the GaN market is behind the SiC market but ultimately, by the 2030s and 2040s say, GaN might end up having the larger market share than SiC."

Indeed, thanks to wafer costs, Eden reckons GaN will always offer a cheaper alternative to SiC. He highlights how a silicon wafer currently costs around \$10, a GaN-on-silicon wafer costs around \$25, while SiC wafers currently come in at up to \$1000 each.

"The substrate is the determining factor for device cost, and I think that once yield, design and other challenges are resolved, GaN devices are going to be cheaper than SiC devices," says Eden. "Silicon carbide is potentially a stop-gap during the 2020s until gallium nitride is perfected – and then this technology will have a bigger market for discrete power semiconductors and power modules." However, at the end of the day, silicon, SiC, GaN and, potentially, Ga<sub>2</sub>O<sub>3</sub> semiconductors will co-exist, each occupying market niches, depending on the cost and performance benefits that each offer.

### World supplier market share estimates for SiC discretes and modules in all applications

#### (percentage dollar revenues)

|    |                                       | 2018            | 2019            | DIFF '19 vs. '18 |

|----|---------------------------------------|-----------------|-----------------|------------------|

| 1  | Wolfspeed                             | 26.0%           | 22.3%           | -3.8%            |

| 2  | STMicroelectronics                    | 14.2%           | 21.7%           | 7.4%             |

| 3  | Infineon Technologies                 | 10.7%           | 10.5%           | -0.2%            |

| 4  | ON Semiconductor                      | 4.6%            | 6.7%            | 2.1%             |

| 5  | ROHM Semiconductor                    | 8.4%            | 5.8%            | -2.5%            |

| 6  | Vincotech                             | 6.2%            | 5.3%            | -0.9%            |

| 7  | Mitsubishi (inc. Powerex)             | 4.0%            | 3.8%            | -0.3%            |

| 8  | CRRC Times Semiconductor (inc. Dynex) | 2.0%            | 1.4%            | -0.5%            |

| 9  | Microchip                             | 1.6%            | 1.3%            | -0.3%            |

| 10 | Fuji Electric                         | 0.8%            | 0.9%            | 0.1%             |

|    | Others                                | 21.4%           | 20.4%           | -1.0%            |

|    | Total Market Size =                   | \$703.1 million | \$888.1 million |                  |

|    | Growth Rate =                         | 3.30.000        | 26.3%           |                  |

|    |                                       |                 |                 |                  |

# Easing the chip-to-chip communication bottleneck by leveraging microLED display technology

High-speed optical emitters derived from GaN-based microLED displays can move data at much higher density and lower power than copper, bringing optical connections to the centimetre scale

BY BARDIA PEZESHKI, ROB KALMAN, ALEX TSELIKOV AND CAMERON DANESH FROM AVICENA MOST OF THE ENERGY consumed in computing systems is not in the computation, but in moving data, and the longer the distance, the greater the challenge in terms of energy and density. At longer length scales, fibre optic links have replaced copper, but at short distances the significant amount of energy required to convert data back and forth between photons and electrons makes optical interfaces prohibitive.

Although it may raise a few eyebrows, at these shorter length scales, optimized optical emitters derived from GaN microLEDs could be a promising candidate for optical communications by leveraging their success in the display industry. Such a move could transform the \$400 billion computer hardware industry and enable

entirely new architectures for parallel computing, machine learning, and processors.

Within the semiconductor industry, the days of enjoying rapid rates of progress on multiple fronts are long gone. There has been little increase in chip clock rates during the last two decades. There are also limits on the number of IC package input and output pins. Consequently, almost all high-performance chips utilize high-speed Serializers/De-serializers - known as SerDes - for input/output on the periphery of the die. Their role is to dramatically increase the bit rate compared with on-chip clock speeds so that all the information can be to squeezed through a limited number of pins. This takes energy, real estate, and chokes data flow and the situation is only going to get worse with future system advances being realised primarily through new architectures that interconnect more chips rather than improvements in raw transistor performance.

Basic physics accounts for the decline in performance of longer electrical interconnects, which are limited by resistance and capacitance of electrical lines. When lines are longer, more capacitance needs to be charged and discharged through their resistance. Increasing density is also problematic - making wires thinner and closer together increases both resistance and capacitance, decreasing maximum interconnect

CROME

Optical waveguide

Electrical

10

Input electrical

signal

Tx

circuit

lengths. And that's by no means the only issue to consider. There's crosstalk, non-linearities in the dielectric constant of the material causing distortions in the waveform, and the skin effect, which causes an increase in electrical resistance at higher frequencies.

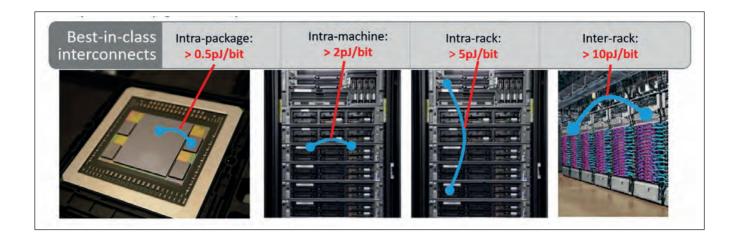

By packaging chips on silicon interposers with a far higher density of lines, electrical data-pipes can be connected to very wide busses and operate close to the clock speed of the chips. However, for reasons already outlined, a high density limits the reach, with chips typically having to be placed edge-to-edge. It is common to co-package high-bandwidth memory chips adjacent to the processor (see the leftmost illustration in Figure 1), and communicate over a bus that is typically about 1000 lanes wide, running at only 1 or 2 Gbit/s. Note that Intel's AIB bus. TSMC's LIPINCON bus and the Open Compute Project BoW busses are all wide and slow, with hundreds or thousands of lanes, each operating at 1 Gbit/s to 16 Gbit/s.

#### Different optics

It has been known for decades that even very short optical interconnects promise significant power and density advantages over electrical interconnects.

This advantage, based on 'quantum impedance transformation', hinges on the use of low-capacitance, LightBundle Electrical Interconnect 10 Individual LightBundle lane Optical signal Output electrical

PD

➤ Figure 2. Avicena's LightBundle interconnect a single lane.

➤ Figure 1.

Moving data

takes energy.

ao. the more

vou'll need to

move each bit.

pico-joules

The further you

with details of

signal

Rx

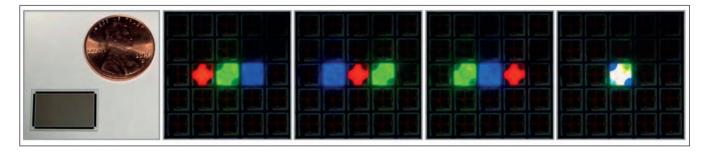

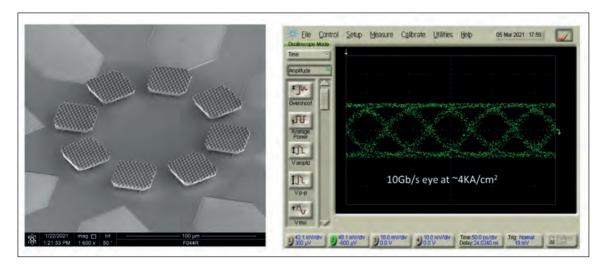

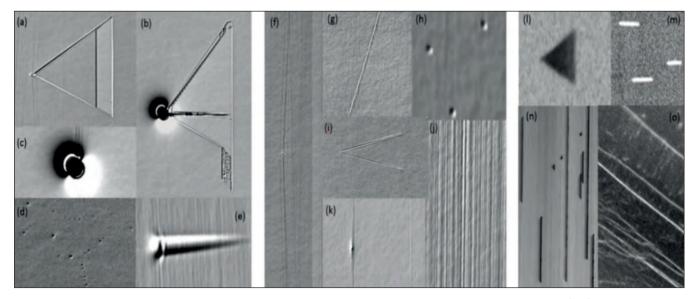

circuit

> Figure 3. Lifted-off high-speed light emitters on silicon, and open eyes at a 10 Gbit/s modulation rate. Large arrays can reach very high densities of data transfer.

high-quantum-efficiency optoelectronic devices. Unfortunately, despite decades of effort, such sources are still to emerge for short links. Edge-emitting lasers, VCSELs, quantum-well modulators and silicon photonics modulators all fall far short of what is needed for practical short optical interconnects (from 1 mm to 10 m). A litany of issues has prevented success, including a high drive power, large size, poor high-temperature performance, expensive and bulky packaging, and a poor yield.

These challenges are not insurmountable. What's needed is a very different approach; our team in Mountain View, California is pioneering a new type of optical emitter derived from high-speed microLEDs. These devices that we call CROMEs (cavity-reinforced optical micro-emitters) utilize very innovative epitaxial and device structures to achieve far shorter carrier lifetimes, and a much higher modulation bandwidth than their more common cousins deployed in ubiquitous lighting and display applications. We

have demonstrated CROMEs that are fast enough for current and future high-performance IC interconnects.

A significant advantage of using visible light is that it allows the fabrication of low-capacitance, large-area CMOS detectors, which can be integrated with simple amplifier circuits to form fast, extremely low power receivers. Thanks to the large area of the detectors, alignment is simple while the packaging cost is low.

There are several options for moving the light between chips. This can be carried out with monolithically fabricated waveguides on an interposer or with various kinds of multicore and imaging fibres. The use of highdensity multicore fibres is well established, having been employed for decades in imaging applications. and used in borescopes, medical endoscopy and other 'display' applications.

Operating in the visible spectrum with optimized CROMEs and CMOS-compatible photodetectors that

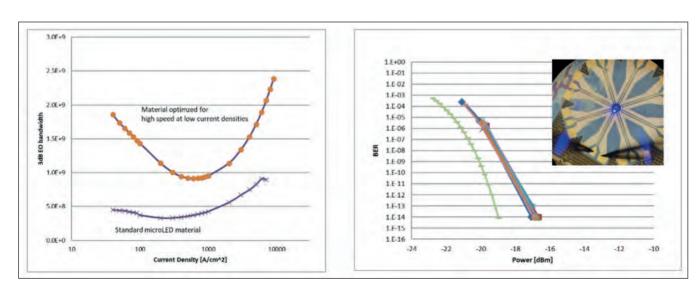

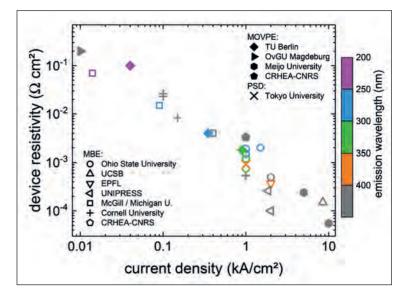

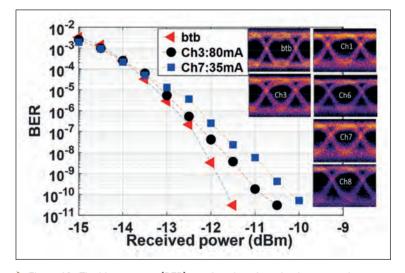

> Figure 4. CROMEs have a higher 3dB bandwidth than their conventional cousins, and can obtain high modulation speeds, even at low current densities. On the right, eight channels modulated at 1.25 Gbit/s show no error floors. The inset photo is a probe test of a single element of the eight-channel array.

are integrated with amplifiers, virtually all capacitance is eliminated. We estimate that such links can deliver an energy efficiency below 100 fJ/bit and deliver a multi-Tbit/s throughput at a density in excess of 10 Tbit s<sup>-1</sup> mm<sup>-2</sup>.

A block diagram of our 'LightBundle' approach, together with details of a single lane, is shown in Figure 2. Each lane consists of an optical transmitter, a fibre core (or waveguide), and a receiver. The CROME transmitters are powered by simple drive circuitry, driven between 20  $\mu\text{A}$  and 500  $\mu\text{A}$  and optically coupled to a waveguide. Each light emitter has a diameter between 1  $\mu\text{m}$  and 10  $\mu\text{m}$  and may be modulated up to around 10 Gbit/s. The receiver consists of a silicon photodetector, optically coupled to a waveguide and monolithically integrated with CMOS transimpedance and limiting amplifiers.

There has already been considerable interest in high-speed visible wavelength LEDs for free-space optical interconnects and 'LiFi', where LEDs are used to generate ambient lighting and transmit data. Such LEDs have a range of criteria to fulfil, needing to be both very efficient and fast. But in a chip-to-chip application considerations are markedly different, and one can trade off quantum efficiency for speed. In fact, the benefits of doing so are tremendous. By optimizing the device's doping, quantum well structure, device design, and other features, CROMEs can be fast enough for very high-density, highperformance IC interconnects. We have demonstrated CROME-based links with wide open eves at even 10 Gbit/s (see Figure 3), a speed previously accessible only with high-speed lasers or modulators.

Other factors that increase speed at very low current densities are coulombic enhancement, microcavity effects, and non-radiative recombination. All these help the CROMEs achieve high modulation speeds.

Figure 4 shows some CROME experimental results. At very low current densities the 3dB bandwidth reaches about 2 GHz (or around 4 Gbit/s for on-off modulation). Good link performance is realised at drive currents of a few tens of microamps. This allows the power consumption per bit to be far lower than

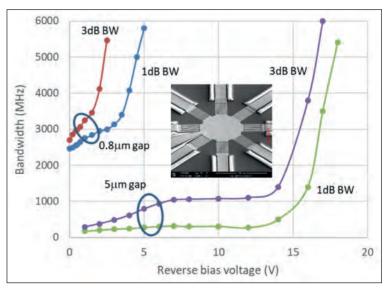

➤ Figure 5. The frequency response of eight-element CMOS-compatible detectors – data is limited by the 6 GHz bandwidth limit of the network analyzer used.

that for lasers. Note that even very small VCSELs, the most energy-efficient lasers, typically have a threshold current of a milliamp.

Using blue light for data transmission is incredibly advantageous at the receiver. Silicon is a nearly ideal material for detecting blue light, with an absorption length of just 0.2  $\mu m$ . This enables CMOS-compatible fabrication of receivers with integrated photodiodes. These photodiodes with very low parasitic capacitance (less than 10 fF) allow use of innovative, simplified transimpedance amplifier designs, enabling receiver power dissipation of below 50 fJ/bit. Such a low power is not possible with 'typical receivers', which are hampered by a much higher capacitance and greater complexity.

Such a detector structure can be fabricated by using the source and drain implant/diffusions for the CMOS transistors to make lateral *p-i-n* diodes. Our eight-element array, used for the multi-channel measurements of Figure 4, shows a bandwidth of over 6 GHz (see Figure 5). The shadowing by the

Using blue light for data transmission is incredibly advantageous at the receiver. Silicon is a nearly ideal material for detecting blue light, with an absorption length of just 0.2  $\mu m$ . This enables CMOS-compatible fabrication of receivers with integrated photodiodes

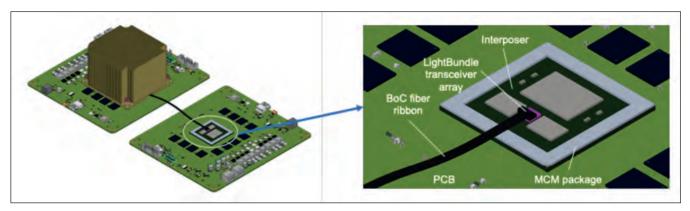

> Figure 6. A fibre-based architecture, showing two MCMs on different PCBs connected by a ribbon fibre interconnect. More advanced versions support interfaces directly to the surface of a complex IC.

fingers on the detector and a thin SOI substrate limited quantum efficiency to about 50 percent, but quantum efficiencies of more than 90 percent should be achievable in optimized devices.

#### Perfecting the package

We use highly multimode fibres and waveguides to realise efficient optical coupling to the sources and detectors. This relaxes alignment tolerances. One of the merits of this approach is that it allows us to select between a variety of useful packaging architectures, each with a different range of benefits.

Our fibre-based links are optimized for longer interconnects, spanning distances from 10 cm to 10 m. These links transfer data between chips and multi-chip modules at the board, shelf and rack levels. Transmitters are connected to receivers using high core-count or imaging fibre (see Figure 6).

A typical imaging fibre has hundreds or thousands of cores, each with a diameter ranging from 2  $\mu$ m to 20  $\mu$ m. Manufacture involves standard 'stack and draw' optical fibre fabrication techniques. Optical channels can be sent through this fiber on a square grid with 20  $\mu$ m centre-to-centre spacing, with each carrying 4 Gbit/s. This gives an areal interconnect bandwidth density of 10 Tbit s<sup>-1</sup> mm<sup>-2</sup>. Sending 256 of these channels through a fiber provides a total throughput of 1 Tbit/s. As such a fibre is less than 500  $\mu$ m in diameter,

multi-fibre ribbons and cables capable of carrying more than 10 Tbit/s are very compact and flexible. That's in dramatic contrast to bulky DAC twinax.

Since all our processes are fully CMOS compatible, interconnects can also be made directly from the surface of a large complex IC. This direct 'optical pin-out' enables ultra-dense, ultra-low-power optical interconnects directly from anywhere on an IC. Operating with an interconnect density of 10 Tbit s¹ mm² and an energy per bit of just 100 fJ/bit, these links could provide outputs and inputs for a 100 Tbit/s (bidirectional) switch IC from a 20 mm² footprint, and a power consumption of just 20 W.

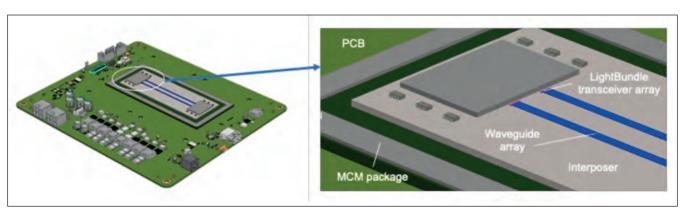

For distances of just 1 mm up to 10 cm, data can be routed through lithographically formed waveguides. An array of multimode waveguides, formed from  ${\rm SiO}_2$ ,  ${\rm SiN}$  or polymers, can be fabricated on a planar substrate. Deploying these 'optically-enhanced' interposers greatly increases practical interconnect distances while decreasing power consumption. The use of lithographic registration enables small sources, which have a typical diameter below 2  $\mu$ m, to be efficiently coupled into optical waveguides that are only slightly wider than the CROME diameter.

#### Compelling credentials

The strengths of our CROME interconnect technology go well beyond performance. They also fulfil all the

> Figure 7. Potential waveguide architecture on an 'optically-enhanced' interposer.

other requirements for practical high-volume products: they have a high reliability, they deliver excellent high-temperature operation, they are low in cost, easy to package, and they are compatible with existing high-volume manufacturing and test capabilities.

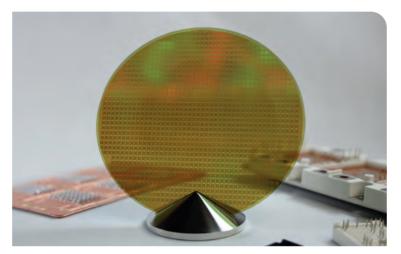

Our links' optical interfaces are formed from a variety of technologies that are used in very high volumes in different applications. From a manufacturing perspective, CROME arrays can be thought of as very small GaN microLED displays. As regular readers know, GaN is manufactured in huge volumes for solidstate lighting and power devices and is becoming increasingly important for displays. Production of this device is underpinned by a massive ecosystem that supports high volume, low-cost manufacturing. In general, GaN is a far more reliable and robust material system than other III-Vs, such as GaAs and InP, due to its excellent high-temperature performance and insensitivity to defects. Unlike devices made from other III-Vs, those built from GaN can operate at high temperatures, such as 150 °C, with extremely low failure-in-time rates.

We are able to draw on existing high-volume manufacturing processes used in the lighting and display industries for the mass transfer of thousands to millions of CROMEs from a sapphire source wafer to a target silicon CMOS driver wafer containing transceiver circuitry. Compared to display requirements, the data interconnect is very undemanding: there are fewer than tens of thousands of lanes, and the application is insensitive to colour and brightness variations, both critical concerns for display makers. Another positive for us is that some redundancy can be built in with spare channels, which is also done in wide slow electrical busses. Our transceiver circuitry and our photodiodes are manufactured using standard CMOS. We can use older process nodes, thanks to the modest link speeds. For coupling we can use polymer microoptics, similar to those in smartphone cameras.

By leveraging all these high-volume technologies, we estimate that the costs of these Tbit/s wide parallel GaN-based links are one to two orders of magnitude lower than the cost of other high speed serial optical link technologies, such as pluggable optical transceivers, board mounted optics, or even silicon photonics co-packaged optics aimed for datacenter and computing environments. Although our technology is multimode and limited to 10 m reaches, it clearly promises to have an important role to play in advancing the performance of computing systems.

# OPPORTUNITIES FOR CROME-BASED LINKS

CLOUD-SCALE data centres and high-performance computing are dominated by interconnects. To ease the data bottleneck, a great deal of attention and investment has been directed at the copackaging of silicon photonics with ASICs, GPUs and memory.

CROME-based interconnects offer a complementary technology to silicon photonics. While silicon photonics may provide an excellent solution for interconnects longer than 10 m, CROME-based links offer a far more dense, lower-cost solution at smaller length scales.

CROME-based interconnects could provide welcome solutions to various problems. As switch ASICs in routers and switches move to more than 100 Tbit/s total throughput, CROME-based interconnects could move the data from the switch ASIC to the chassis front plate, where standard ethernet transceivers could be deployed, and down the rack to the NIC cards in the servers. In the move towards disaggregated infrastructure, CROME-based links could provide low latency, low power connections to shared memory or connect processor clusters. These high-density links increase connectivity for both learning and inference in machine-learning and deep neural networks.

Looking further ahead, there are opportunities for optical interfaces to be implemented directly on large complex ICs, where they will provide the best power, latency, density, and cost. In decades gone by, the fundamental density and power limitations of electrical interconnects compelled the migration to SerDes-based input/output (I/O) for high-speed interfaces. Now these interfaces consume significant IC power and real-estate, and low power optical interfaces hold much promise. Introducing them could unlock the door to a new generation of ICs incorporating 'lightweight' high-performance IOs with greatly improved density, latency, and reach while consuming far less IC real estate and power.

In the latter part of the twentieth century, numerous groups in academia and research labs looked to photonics to revolutionize computing, pointing out that optical beams enable very high connectivity.

In this vein, a team at AT&T Bell Laboratories demonstrated simple optical computers using quantum well modulators with gratings and holograms. But despite massive funding and huge interest from DARPA and other resources, the technology never matured – perhaps because the components and the applications needed to make these breakthroughs did not exist. Today that's not the case. The technology and the need are now both there, and perhaps the dreams of the visionaries can be realized with these new CROME devices.

#### **FURTHER READING**

- D. A. B. Miller J. Light. Technol. 35 346 (2017)

- ▶ B. Pezeshki *et al.* "High speed microLEDs for visible wavelength data communication," Proceedings of SPIE, vol 11706 Light-emitting devices, materials, and applications XXV, 117060N, 2021.

- S. Rajbhandari et al. Semicond. Sci. Technol. 32 023001 (2017)

# CS shares race ahead

Stocks in the CS industry soar to well above pre-pandemic levels

#### BY RICHARD STEVENSON

WHILE THE PANDEMIC has taken its toll on all of us, it's been hardest on the poor. Those with bigger salaries are less likely to have lost their jobs, and if they've had a chance to invest any spare cash, they are probably enjoying a good return.

Canny investors will have considerably strengthened their financial position over the last year or so by buying shares in technology companies. As a glance at our annual Shareprice Leaderboard shows, over the 12 months up to the end of April 2020 the tech-heavy NASDAQ climbed by just over 60 percent, while some companies in our industry have fared even better (see Shareprice Leaderboard on p. 21). Topping our list is Cree, thanks to a valuation that has leapt more than three-fold. Substrate maker AXT is not far behind, and even third-placed II-VI has delivered a return over this timeframe of around 140 percent.

It's worth noting that all these impressive performances are not a simply a result of nosedives at the start of the pandemic followed by recoveries throughout last summer to regain the lost ground.

ALLOWS HALLOWS HALLOWS

> Construction of Cree's Mohawk Valley facility is well underway. This fab is the centrepiece to Cree's massive expansion plans.

Compare the share prices at the very beginning of last year to where they are at the end of April 2021, and you'll see that all but one of the companies we cover are enjoying an increase in valuation, with five doubling their worth over that timeframe (see the second Shareprice Leaderboard, on p. 23, that considers the period from the beginning of 2020 to late April of this year).

#### **Champion Cree**

Cree's soaring share price reflects the success it has had in transforming its business. It has now sold-off its LED chips and lighting businesses, which brought declining returns over the last decade or so, and has turned its attention to making SiC substrates, SiC power devices and GaN-on-SiC RF products. Marketed through the moniker Wolfspeed, sales of these products are ramping, and could continue to do so throughout this next decade and beyond as the company executes a massive capacity expansion programme to produce higher volumes more efficiently.

The company still has a long way to go along this road. Sales of its revamped portfolio are growing, with revenue for the third fiscal quarter of 2021, ending on 28 March, netting \$137.3 million. This is above guidance, an 8 percent increase sequentially, and up 21 percent compared with the equivalent fiscal quarter of the previous year. However, due to a combination of Covid-19 safety measures and a temporary increase in higher factory costs, gross margins are heading in the wrong direction, having fallen 0.4 percent sequentially, to 35 percent. This will have contributed to the loss for the latest fiscal quarter, which is \$24.7 million, according to non-GAAP accounting.

All figures should improve substantially over the coming years. Gross margin is tipped to climb towards 50 percent, thanks to the launch of the 200 mm Mohawk Valley Fab that will swell shipments. Construction of this fab accounts for much of the \$550 million that Cree is investing in capital expansion in fiscal 2021. Helping to pay for this is the sale of the LED business that recently netted around \$500 million.

During a third fiscal quarter earnings conference call, held on 28 April 2021, Cree's CEO Gregg Lowe

| Rank | Company                    | Ticker   | Share value, April 27, 2020 (\$) | Share value, April 27, 2021 (\$) | % appreciation | Change in Rank |

|------|----------------------------|----------|----------------------------------|----------------------------------|----------------|----------------|

| 1    | Cree                       | CREE     | 38.58                            | 119.76                           | 210.4          | +14            |

| 2    | AXT                        | AXTI     | 4.14                             | 11.61                            | 180.4          | +11            |

| 3    | II-VI                      | IIVI     | 31.10                            | 74.56                            | 139.7          | +9             |

| 4    | Veeco                      | VECO     | 10.24                            | 23.29                            | 127.4          | +6             |

| 5    | Qorvo                      | QRVO     | 90.93                            | 200.36                           | 120,3          | -2             |

| 6    | Aixtron (Frankfurt)        | AIX      | 11.04*                           | 22.89*                           | 107.3          | +3             |

| 7    | Skyworks                   | SWKS     | 97.80                            | 201.18                           | 105.7          | -2             |

| 8    | IPG Photonics              | IPGP     | 122.44                           | 234.06                           | 91.2           | +6             |

| 9    | IQE (London)               | IQE      | 51.6*                            | 88.05*                           | 70.6           | +7             |

| 10   | Infinera                   | INFN     | 6.01                             | 9.80                             | 63.1           | -9             |

| 11   | NASDAQ composite           | IXIC     | 8717.98                          | 14170.91                         | 62.5           | -5             |

| 12   | Emcore                     | EMKR     | 4.14                             | 6.69                             | 61.6           | -4             |

| 13   | WIN Semiconductor (Taipei) | 3015.TW0 | 9.00*                            | 13.30*                           | 47.8           | -9             |

| 14   | Riber (Paris)              | RIB      | 1.38*                            | 1.82*                            | 31,9           | -3             |

| 15   | Rubicon                    | RBCN     | 8.17                             | 10.54                            | 29.0           | -8             |

| 16   | Lumentum                   | LITE     | 79.24                            | 94.90                            | 19.8           | -14            |

> It's been a great 12 months for Compound Semiconductor stocks, with a rise in valuation across the board.

offered some insight into the latest trends in the markets where the company's products serve. "We are seeing more demand in our core automotive and RF markets, as well as additional interest in new areas across energy, industrials, and aerospace and defence," revealed Lowe. Diversity of deployment is impressive, including devices designed into forklifts, 3D laser printers, air conditioners, motor drives, robotic arms, flying vehicles and a beer truck.

Lowe added that the company's device pipeline now stands at more than \$10 billion, with new opportunities being identified at a rapid pace. In just the last quarter, the company's sales team secured more than \$580 million in design-ins; and over the last five quarters this figure totals \$2.5 billion.

Over the next few years, Cree is set to benefit from the \$2 trillion infrastructure plan recently unveiled by the US administration. Within the plan, \$100 billion is dedicated to increasing broadband access, with a special emphasis on 5G infrastructure. Remarking on this, Lowe commented: "This development, combined with strong sales of 5G smartphones during the pandemic, underscores how 5G is continuing to gain momentum and offers a global opportunity in the years ahead."

Also included in the infrastructure plan is significant funding for electric vehicles, including sales rebates, tax credits and charging stations. "We anticipate this will have a significant impact on the adoption of electric vehicles," reasoned Lowe. "We are now seeing US automakers make big commitments to ramp their EV efforts. For instance, General Motors and LG Chem recently announced plans to invest \$2.3 billion to build a battery cell plant to support the automaker's efforts to expand its electric vehicles."

Cree could also benefit from a ramp in electric vehicle production in Europe. On a recent trip to Germany, Lowe had very positive conversations with a number

of tier one carmakers, who are struggling with supply constraints associated with silicon chips. He offered them hope, telling them that Cree is going into production with the world's largest SiC fab, right in the middle of this supply issue. This great timing, which Lowe openly admits is more down to luck than judgement, bodes well for Cree's future. "[It] is certainly a very nice light at the end of the tunnel for some of these guys as they start placing bets on silicon carbide."

Until the Mohawk fab is up and running, sales are likely to show a moderate increase, rather than a massive ramp. During the next quarter revenue is tipped to rise to between \$142 million and \$148 million, with the majority of the increase coming from the power and RF device product lines. A small uptick is also anticipated from the materials division.

#### **AXT** accelerates

Throughout most of last year, AXT's share price hovered at around \$5, before leaping to almost twice that in November, and surging as high as just over \$15 in late February. The company's valuation has dropped back a little since then, but sales continue to climb. They leapt from \$22.1 million for the second fiscal quarter of 2020 that ended on 30 June 2020 to \$25.5 million and \$27.0 million in the third and fourth fiscal quarters that followed, and have broken the \$30 million barrier in the most recent quarter.

This growth is attributed to an increase in sales to chipmakers serving a broad range of markets, from 5G telecommunications and its related technologies to datacentre connectivity, LED-based sensing and display, healthcare monitoring and consumer devices.

Of the \$31.4 million netted in the most recent quarter, \$23.4 million came from substrate sales and \$8 million from the two joint-ventures: BoYu, a manufacturer high-temperature crucibles and tools for OLEDs; and JinMei, a diversified industrial supplier of high-purity materials.

#### **INDUSTRY I FINANCE**

> Earlier this vear II-VI has launched doublejunction VCSEL arrays, targeting next-generation world-facing 3D sensing applications.

As well as growing revenues, AXT is reducing reliance on its biggest customers. Company CFO Gary Fisher highlighted this welcome move in a call discussing earnings on 28 April, 2021, when he revealed that no customers accounted for 10 percent or more of overall revenue, and the top five contributed just 26 percent to total sales. "Usually, we do have at least one 10 percent customer," added Fisher. "And usually, the top five customers contribute approximately 35 percent to 40 percent of total revenue."

Gross margin is on the rise, reaching 36.8 percent in the latest fiscal quarter, up 2.9 percent sequentially and 10.2 percent year-on-year. Thanks to this, plus a favourable product mix and and increasing sales, net profit hit £3.4 million, up \$1.3 million sequentially.

During a recent earnings call, AXT CEO Morris Chang discussed sales for all three types of substrate produced: InP, GaAs and germanium.

Shipments of InP are seeing strong growth. "We saw continued strength from 5G and its related technologies," said Chang, who did not know whether these wafers were for optical connections for 5G equipment, or technologies such as passive optical networks that support 4G and 5G functionality. "But from our perspective, any modernization of telecom infrastructure that utilizes indium phosphide is positive for our business."

Demand for GaAs substrates has recently increased, due to sales to makers of LEDs and wireless products. For this class of substrate, revenue for the first fiscal quarter 2021 exceeded all quarters since the first fiscal quarter 2018. Sales in the coming quarter will be helped by strong demand by LED makers, but hindered by a softening of sales to those making wireless products.

AXT is continuing to invest in both its InP and GaAs technology. It is developing 6-inch InP substrates and has just unveiled 8-inch GaAs substrates for LED applications. Commenting on the latter, Chang remarked: "This is no longer a test tube laboratory program, because we are now shipping wafers according to our customer specifications. This is a tremendous step for AXT, and we are very proud of

our team." It is hoped that the large substrate size will help to provide scale and efficiency for very high volume manufacture of VCSELs for 3D sensors and LiDAR, and microLEDs for displays."

For germanium substrates, revenue for the recent fiscal quarter is down slightly. However, growth is expected this year, thanks to a strong satellite market. This should provide a modest increase in the next quarter.

For that quarter – the second fiscal quarter of 2021 – AXT predicts that contributions from germanium, plus growth in InP and GaAs revenues, will propel sales to between \$30.5 million and \$31.5 million. Profit is expected to be in the range \$2.6 million to \$3.4 million.

#### Third for II-VI

II-VI, third on our Leaderboard, has seen its share price follow the same trend as AXT: broadly flat to last November, climbing to peak in February, and now a little below that high point.

This multi-national powerhouse, with products that include GaAs electronic devices, SiC substrates, laser systems and components for optical networks, claimed several records in its last quarterly results, announced on 9 February, 2021. Quarterly sales broke new ground, hitting \$787 million, backlog reached a record \$1.08 billion, and cash from operations climbed to a new high of \$221 million.

The management at II-VI are very pleased with the integration of Finisar into the existing business. Discussing this in a second fiscal quarter earnings call, held on 9 February 2021, company CEO Chuck Mattera revealed that progress on this front is ahead of schedule: "We are now on track to achieve our \$150 million total synergy target in 24 months, or 12 months ahead of schedule. And we are now increasing our three-year total synergy target to \$200 million." This success is helping to strengthen margins and ensure a strong cash flow.

Details of particular product successes were highlighted in the call by Giovanni Barbarossa, who is Chief Strategy Officer and President of the Compound Semiconductor Segment.

Barbarossa revealed that products for 3D sensing increased more than 140 percent sequentially. "3D sensing growth came from shipments of production volumes of VCSEL arrays for multiple end customers, including for front-facing and worldfacing applications, as well as for other consumer electronics, and automotive in cabin sensing," said Barbarossa. According to him, sales of VCSEL arrays should continue to rise as II-VI expands its customer base with additional wins, including in the Android ecosystem and personal computing platforms. II-VI has devoted much time and effort to building up its 3D sensing products. Back in 2013 it bought Oclaro's GaAs laser business; three years on it purchased the Anadigics GaAs fab and the Epiworks facility; and in the autumn of 2019 it bought the Finisar fab.

"When we acquired Finisar some asked us which gallium arsenide fab we plan on closing," remarked Barbarossa. "Our answer was none because we needed the capacity to gain share and become the market share leader, by offering breakthrough solutions at scale."

As well as sensing, the VCSELs made by II-VI are targeting LIDAR. Barbarossa is confident of success in this sector, arguing that the company has the broadest portfolio of products in the industry. "Unlike our pure play laser competitors, we have an entire vertical integrated portfolio of both active and passive components, made from our engineering materials that are critical for these next generation LiDAR designs."

SiC products for power electronics could also help to grow II-VI revenue. Encouraging signs on this front include a purchaser of II-VI's SiC substrates winning selection by a tier-one automotive manufacturer in Japan.

Another promising portfolio of products are InPbased lasers. Shipments of high-data-rate coherent transceivers are on the rise, adding bandwidth to new and existing networks, and sales are up for 200G and 400G components. "We are also excited to announce that we have just sampled our first 800G transceivers to a large web-scale customer, who has already provided exciting feedback," added Barbarossa.

II-VI is widening its broad portfolio with the acquisition of Coherent, a manufacturer of a broad range of lasers, including CO, CO<sub>2</sub>, excimer, solid-state and fibre sources. II-VI emerged victorious in a bidding war with MKS Instruments and Lumentum during the first few months of this year. The stock-and-cash deal, worth around \$7 billion, is expected to close at the end of this year.

Results just in for the third fiscal quarter show that the company continues to thrive, generating a revenue of \$783 million and a cash flow from operations of \$447 million. For the fourth fiscal quarter, sales are expected to net \$752-802 million, with earnings of \$98-127 million.

#### Languishing Lumentum

Footing this year's table is laser diode manufacturer Lumentum. It's not that Lumentum has performed poorly – it's just that its peers have fared better. Over the timeframe considered in the annual Shareprice Leaderboard, Lumentum has seen a rise in its valuation by about 20 percent, while based on a pre-Covid reference point of the start of 2020, the increase in share price is around 17 percent.

Over the last year or so Lumentum's share price has not fluctuated wildly. It's nadir over that time has been just below \$70, and it has peaked at a little more than \$105.

Lumentum has been experiencing mixed fortunes. Sales of it VCSELs for 3D sensing applications have been strong, but shipments of telecom lasers have

| Rank | Company                    | Ticker   | Share value, January 2, 2020 (\$) | Share value, April 27, 2021 (\$) | % appreciation | Change in Rank |

|------|----------------------------|----------|-----------------------------------|----------------------------------|----------------|----------------|

| 1    | AXT                        | AXTI     | 4.36                              | 11.61                            | 166.3          | +12            |

| 2    | Cree                       | CREE     | 46.90                             | 119.76                           | 155.4          | +13            |

| 3    | Aixtron (Frankfurt)        | AIX      | 10.28*                            | 22.89*                           | 122,9          | +6             |

| 4    | Emcore                     | EMKR     | 3.05                              | 6.69                             | 119.3          | +4             |

| 5    | II-VI                      | TIVI     | 34.26                             | 74.56                            | 117.6          | +7             |

| 6    | Qorvo                      | QRVO     | 117.26                            | 200.36                           | 70.9           | -3             |

| 7    | Skyworks                   | SWKS     | 122.01                            | 201.18                           | 64.9           | -2             |

| 8    | IPG Photonics              | IPGP     | 146.99                            | 234.06                           | 59.2           | +6             |

| 9    | NASDAQ composite           | IXIC     | 9039.46                           | 14170.91                         | 56.8           | -3             |

| 10   | Veeco                      | VECO     | 14.93                             | 23.29                            | 56.0           | 0              |

| 11   | IQE (London)               | IQE      | 67.74*                            | 88.05*                           | 30.0           | +5             |

| 12   | Rubicon                    | RBCN     | 8.65                              | 10.54                            | 21.8           | -5             |

| 13   | WIN Semiconductor (Taipei) | 3015.TWO | 10.93*                            | 13.30*                           | 21.6           | -9             |

| 14   | Infinera                   | INFN     | 8.13                              | 9.80                             | 20.5           | -13            |

| 15   | Lumentum                   | LITE     | 81.25                             | 94.90                            | 16.8           | -13            |

| 16   | Riber (Paris)              | RIB      | 3.225*                            | 2.20*                            | -31.8          | -5             |

<sup>&</sup>gt; Comparing share prices of compound semiconductor companies to pre-Covid times shows that they have fared far better than just recovering from the nadir caused by the pandemic.

#### **INDUSTRY I FINANCE**

weakened, due to a push-out in 5G deployments. There has also been a sharp decline in sales of commercial lasers, due to weakness within the industrial sector.

While the company's management may also rue their failure to secure Coherent, market reaction to missing out on this deal has actually been favourable. When news broke in March that II-VI had finally won the bidding war, Lumentum's valuation climbed by around 5 percent, probably spurred on by a boost to the company's financial assets - it would now be in line for a termination fee, worth \$218 million.

Very recently Lumentum has released its results for its third fiscal guarter of 2021, ending 31 March. Sales missed guidance, coming in at \$420 million, down 12 percent sequentially and below the guidance given in February of \$425 million to \$440 million. This news didn't go down well with the market, with shares tumbling 15 percent.

Company CEO Alan Lowe accounted for unexpectedly low revenue in a quarterly earnings call given on 12 May. He blamed the sales shortfall on China's roll out of 5G, which is going slower than anticipated, due to geopolitical tensions with the US and shortages of electronic components. Continued delays in 5G fronthaul deployments in China have dragged down third quarter revenue for directly modulated lasers to significantly below year-ago levels. There will be no immediate improvement, with sales of this class of laser for the upcoming quarter expected to be down by more than \$20 million year-on-year. "At this time, we expect 5G fronthaul deployments could resume this summer," added Lowe. "This timing would drive increased demand for our products towards the middle of fiscal '22, once customers ramp up and burn through existing inventory."

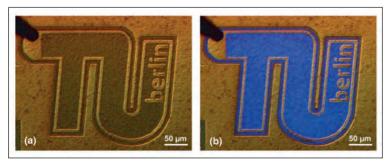

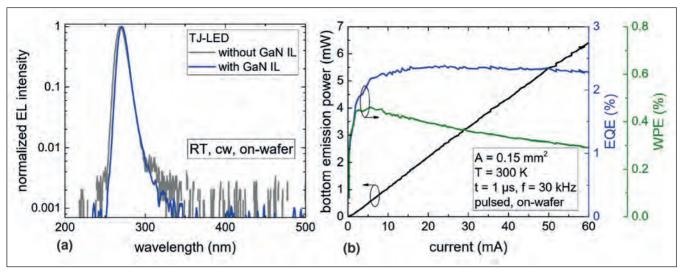

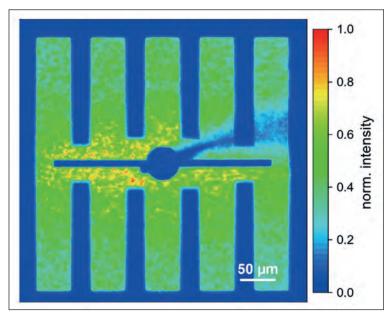

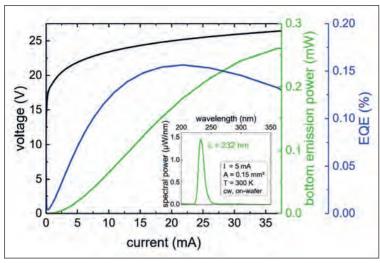

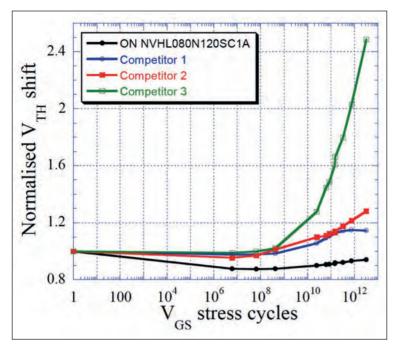

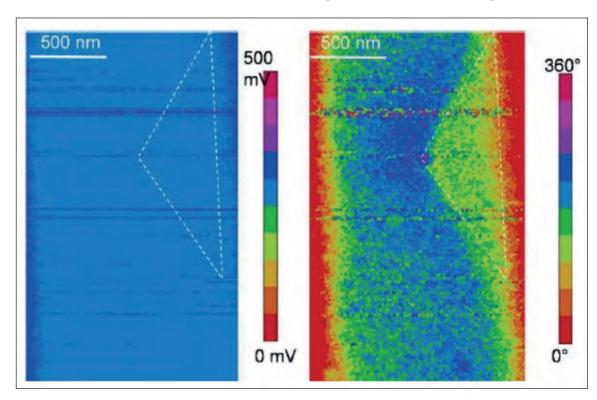

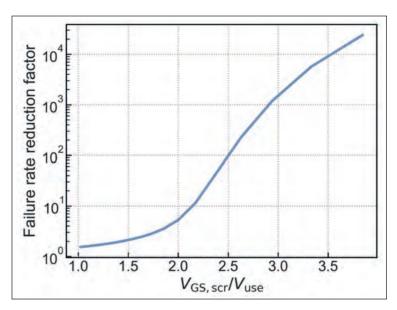

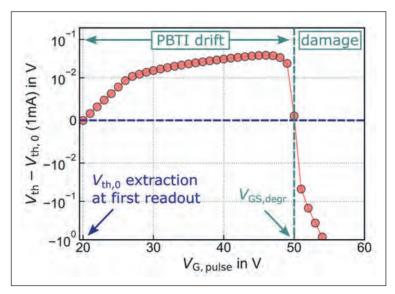

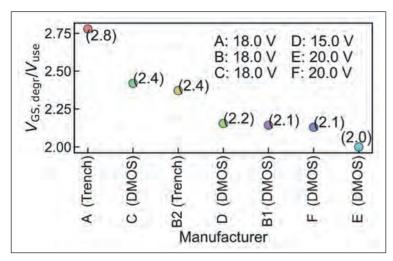

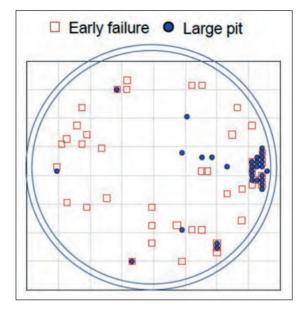

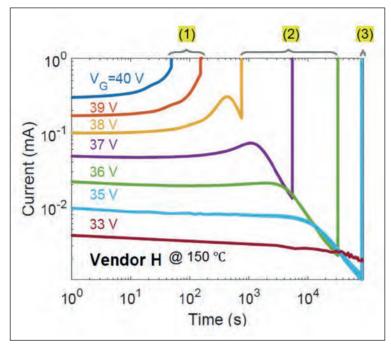

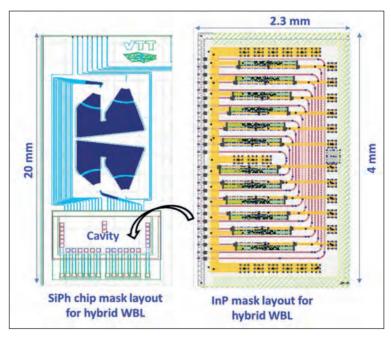

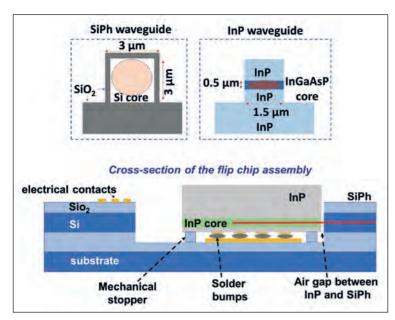

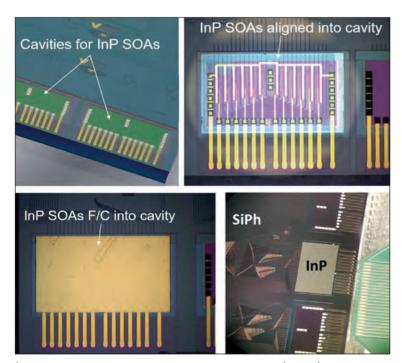

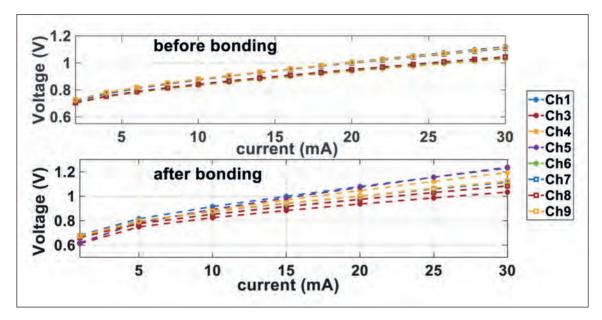

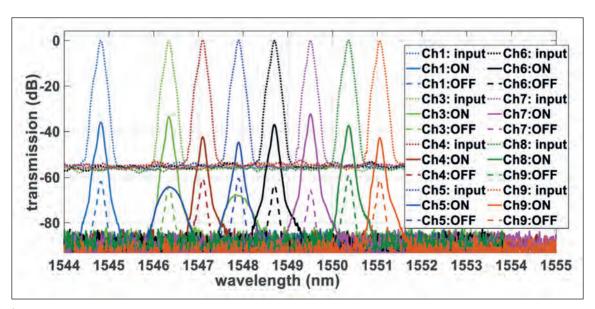

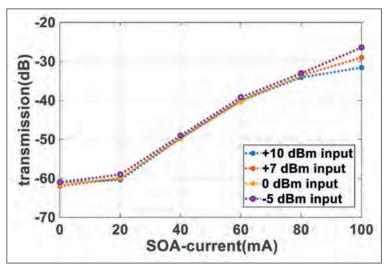

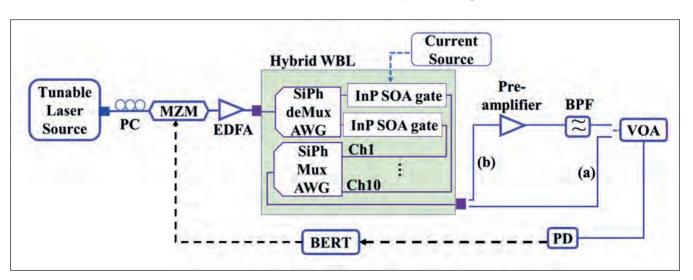

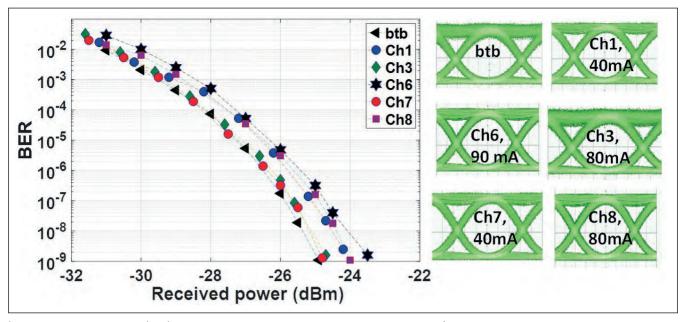

Another sector weakening in the short term is 3D sensing. Due to customer design decisions, the global market for 3D sensing lasers is expected to decline between 20 percent and 25 percent during Lumentum's fiscal 2022. However, during that fiscal year, and the one that follows, laser-based sensing is expected to expand into more applications and markets. Lowe says that this will set the stage for reacceleration of market growth in fiscal 2023.