# COMPOUND 35 SEMICONDUCTOR

CONNECTING THE COMPOUND SEMICONDUCTOR COMMUNITY

**VOLUME 31 ISSUE IV 2025**

COMPOUNDSEMICONDUCTOR.NET

SCALING THE GROWTH OF NOVEL MATERIALS

## RIXTRON

## THE NEW G10 SERIES

Your Productivity Solution for All Advanced Epitaxy Materials

#### G10-SiC

- ▶ 9x150 mm (6") or 6x200 mm (8")

- New hardware & process surpassing Single Wafer Reactor uniformities

- ► +50% productivity per fab area with large batch technology & small footprint

#### **End Markets/Products:**

EV inverters & charging infrastructure

#### G10-GaN

- ▶ 8x150mm (6") or 5x200mm (8")

- ▶ 1<sup>st</sup> fully automated compact GaN MOCVD cluster designed 100% for Si Power fabs

- Novel hardware solution for unmatched barrier uniformities and device yields

#### **End Markets/Products:**

Power Electronics & Wireless communication

#### G10-AsP

- ▶ 8x150 mm (6") or 5x200 mm (8")

- ▶ 1<sup>st</sup> fully automated AsP MOCVD system enabling 10x lower defect density

- Unmatched wavelength uniformity on all wafer sizes

#### **End Markets/Products:**

Micro LED, Optical Data communication, 3D-sensing & LiDAR

## BY RICHARD STEVENSON EDITOR

## Imperfect perspectives

It's very easy to get caught up in the mood of the moment, allowing this to exert too much influence on your thinking.

I found myself guilty of exactly this when preparing this issue. Let me explain...

For more than a decade, we've been using issue IV to look at how the valuation of many companies within our industry has changed over the last 12 months — and when I took on this task this year I feared the worst, fuelled by thoughts dominated by escalating tariffs, a tumbling stock market, and concerns over falls in GDP that threaten to lead to a global recession.

But when I compiled the data, it's not as bad as I feared (and although it's not pretty, it's worth noting that there has been a rally in stocks in the last few days). While it's true that for many companies, their share price has fallen over the last year, that's not the case for all. Bucking this trend and soaring high are Lumentum and Coherent, recording gains of around 20 percent and 40 percent, respectively, on our *Compound Semiconductor Share Price Leaderboard*.

What's behind this success? Primarily, it's the incredibly strong demand for InP lasers that are supporting data centres, particular those providing Al.

With this demand showing no sign of abating, and the sector suffering from an industry-wide shortage of InP capacity for optical components, Lumentum and Coherent are taking steps to boost production. As part of these efforts, Lumentum is constructing a large three-story facility and cleanroom in Thailand, and Coherent is planning to expand its 150 mm InP line in Sherman, Texas, supported by the US CHIPS Act.

Aside from Lumentum and Coherent, those on this year's Leaderboard have seen their share price head south. Some of these falls are modest, others are more significant, and Wolfspeed's is an alarming 87 percent, highlighting some significant concerns for the company. It's faced a perfect storm of a global decline in SiC substrate demand, high costs of capacity expansion, and doubts that it will actually get to receive \$750 million of funding under the US CHIPS Act.

Trying to navigate these incredibly choppy waters is the new CEO Robert Feurle, who will benefit from two recently appointed external advisers to the Board, Paul Walsh and Mark Jensen, who have both held CFO roles elsewhere.

Turning Wolfspeed into a profitable entity will not be easy, but there is still much promise, given that the long-term outlook for SiC is so strong. While it's easy to focus on the here and now – and clearly there are some severe problems to solve for Wolfspeed – outsiders should be wary off getting too caught up in this particular moment.

Free weekly e-news roundup go to: compoundsemiconductor.net

## Scaling the growth of novel materials

From 4-inch gallium oxide films to next-generation transition metal dichalcogenides, Agnitron's US-driven breakthroughs on large-area wafers are ushering in a new era of semiconductor devices

#### 18 The tipping point for AIN

Advances in AIN substates are positioning this nitride as a transformational material in next-generation electronic and optoelectronic applications

## 30 CS International champions the versatility of the nitrides

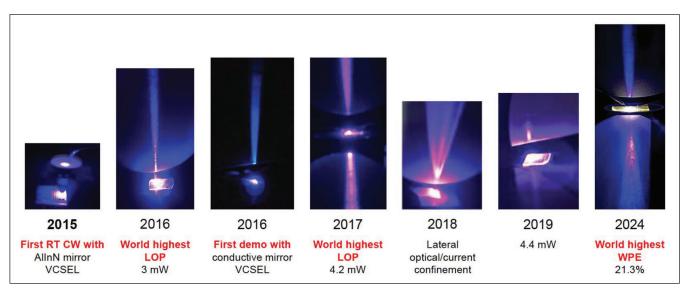

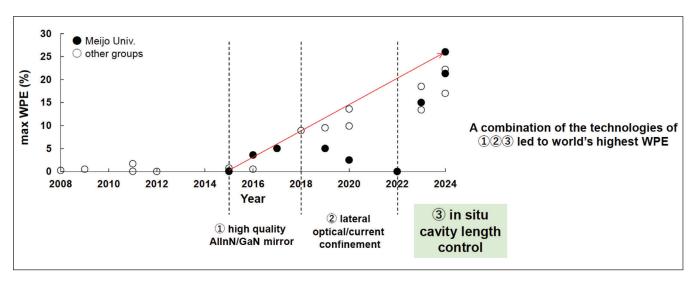

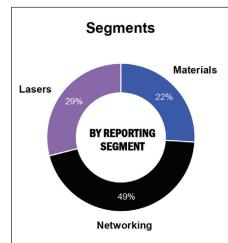

The portfolio of devices based on GaN continues to strengthen and expand, with recent key additions including polychromatic and nanowire microLEDs, VCSELs with improved efficiency, and GaN HEMTs for power electronics that are targeting new markets

#### 38 A tough 12 months for CS shares

Aside from a couple of makers of optical components, shares of companies in the CS industry have headed south over the last year.

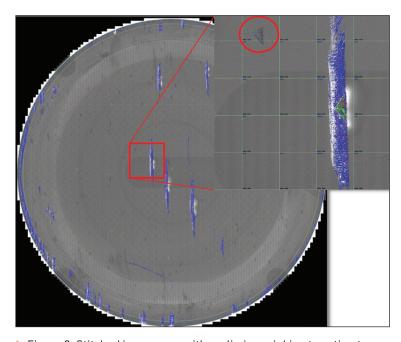

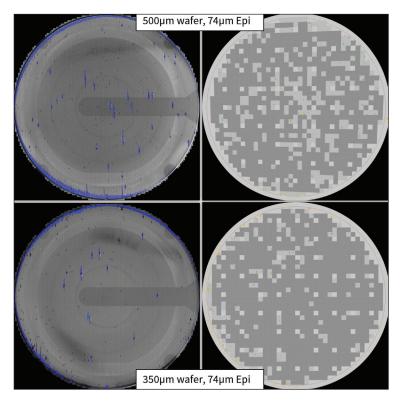

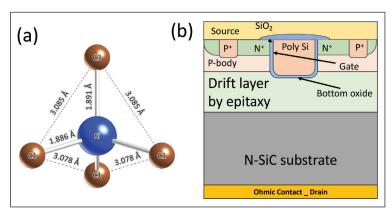

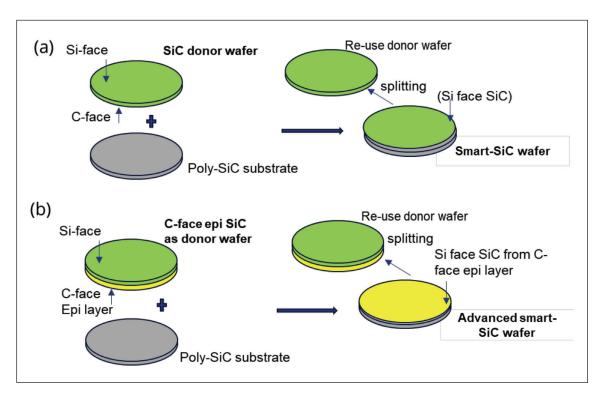

#### 42 Thick homoepitaxy on 200 mm SiC

The cost of SiC substrates needs to come down. But are we going to hamper these efforts by imposing limits on the thickness of this foundation?

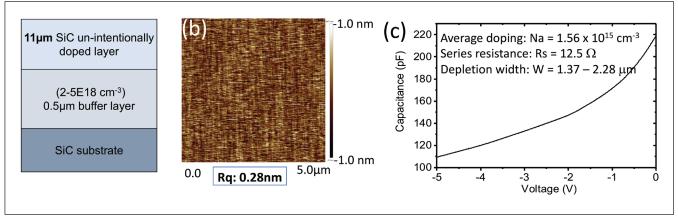

#### 46 Towards defect-free SiC epiwafers

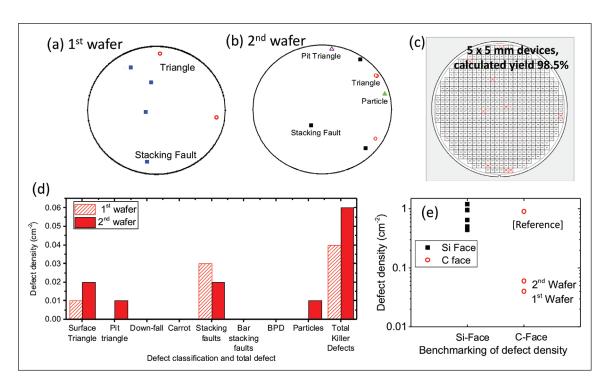

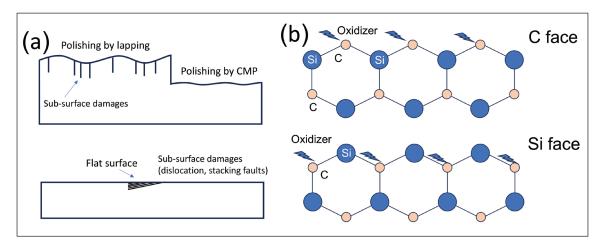

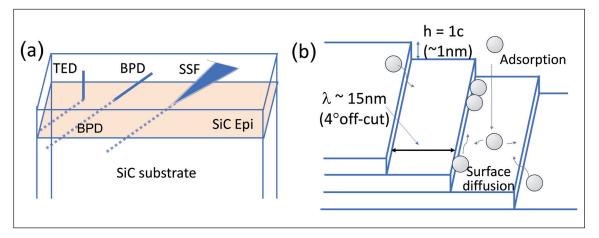

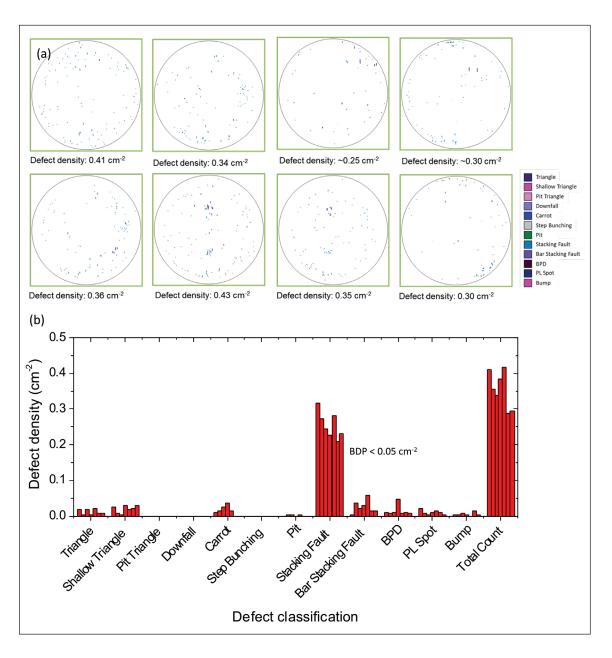

Helping to drive improvements in SiC power devices, advances in epitaxy are producing nearly defect-free layers of SiC on the carbon face, and those that that are free from basal plane dislocations on the silicon face

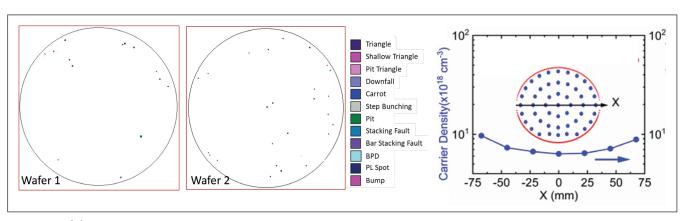

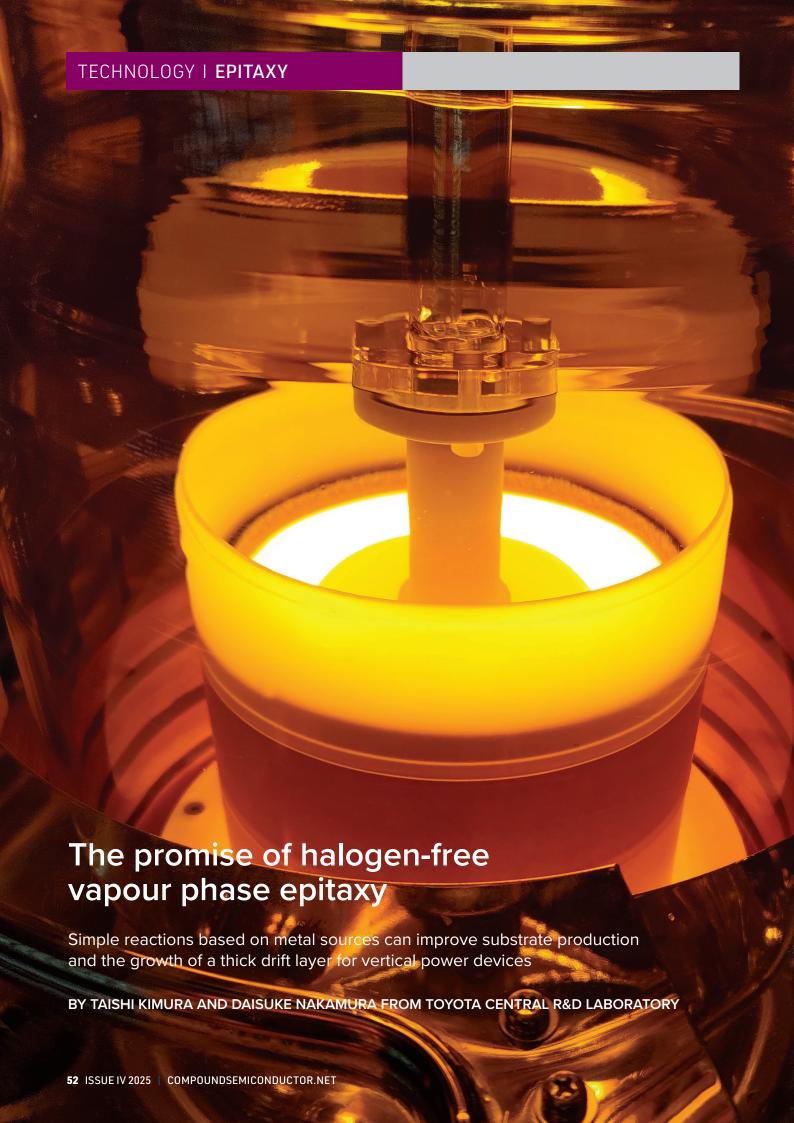

## 52 The promise of halogen-free vapour phase epitaxy

Simple reactions based on metal sources can improve substrate production and the growth of a thick drift layer for vertical power devices

#### **NEWS ANALYSIS**

#### 14 Smart GaN HEMT + IGBT = EV success?

Cambridge GaN Devices is targeting the powertrain of electric vehicles with the combination of IGBTs and its proprietary integrated circuit enhancement GaN technology

#### 16 Infineon's expanding 2 kV portfolio

Joining Infineon's 2kV MOSFETs are Schottky barrier diodes with identical voltage ratings

#### RESEARCH REVIEW

- 58 Increasing the efficiency of GaN **HEMTs**

- 59 Improving GaN-based mirrors

- **60** Debut for the vertical rutile GeO Schottky barrier diode

### **NEWS**

- 06 Worries about Wolfspeed as a 'going-concern'

- 07 Introducing trench-based superjunction SiC

- 08 IQE announces 2025 results and new CEO

- 09 Uviquity emerges from stealth with \$6.6m funding

- 10 Riber secures major order from Australia

- 11 Singapore-MIT group to make machines 'see' like humans

- 12 Indium Corp and Rio Tinto reveal gallium sourcing project

News Editor Christine Evans-Pughe **Design & Production Manager** Mitch Gaynor

**Director of Logistics** Sharon Cowley **Event & Media Sales Executive** Ranjodh Shergill

Circulation Scott Adams Publisher Jackie Cannon

richardstevenson@angelbc.com christine.evans-pughe@angelbc.com

mitch.gaynor@angelbc.com sharon.cowley@angelbc.com

ranjodh.shergill@angelbc.com scott.adams@angelbc.com jackie.cannon@angelbc.com

+44 (0)1291 629640

+44 (0)1923 690214 +44 (0)1923 690200

> +44 (0)2476 718970 +44 (0)1923 690205

Chief Executive Officer Sukhi Bhadal sukhi.bhadal@angelbc.com Chief Technical Officer Scott Adams scott.adams@angelbc.com Directors Jackie Cannon, Sharon Cowley

Published by Angel Business Communications Ltd 6 Bow Court, Fletchworth Gate, Burnsall Road, Coventry CV5 6SP, UK. T: +44 (0)2476 718970 E: info@angelbc.com

+44 (0)2476 718970

Compound Semiconductor is published nine times a year on a controlled circulation basis. Non-qualifying individuals can subscribe at: £115.00 per annum (UK), €165 per annum (Europe), \$198 per annum (air mail) (USA). Cover price £4.50. All information herein is believed to be correct at time of going to press. The publisher does not accept responsibility for any errors and omissions. The views expressed in this publication are not necessarily those of the publisher. Every effort has been made to obtain copyright permission for the material contained in this publication. Angel Business Communications Ltd will be happy to acknowledge any copyright oversights in a subsequent issue of the publication. Angel Business Communications Ltd (Copyright 2025, All rights reserved. Contents may not be reproduced in whole or part without the written consent of the publishers. The paper used within this magazine is produced by chain of custody certified manufacturers, guaranteeing sustainable sourcing. US mailing information: Compound Semiconductor, ISSN 1096-598X, USPS Permit Number 25366, is published 9 times a year, Combined Jan/Feb, March, Combined April/May, June, July, Combined August/September, October, November, December by Angel Business Communications Ltd, Unit 6, Bow Court, Fletchworth Gate, Burnsall Rd, Coventry CV5 65P, UK, Airfreight and mailing in the USA by agent named World Container INC 150-15, 183rd St, Jamaica, NY 11413, USA. Periodicals Postage Paid at Brooklyn, NY 11256. POSTMASTER: Send address changes to Compound Semiconductor, Air Business Ltd, c/o World Container INC 150-15, 183rd St, Jamaica, NY 11413, USA. Periodicals Postage Paid at Brooklyn, NY 11256. POSTMASTER: Send address changes to Compound Semiconductor, Air Business Ltd, c/o World Container INC 150-15, 183rd St, Jamaica, NY 11413, USA. Periodicals Postage Paid at Brooklyn, NY 11256. POSTMASTER: Send address changes to Compound Semiconductor, Air Business Ltd, c/o World Container INC 150-15, 183rd St, Jamaica, NY 11413, USA. Periodicals Posta Jamaica, NY 1143, USA. We strive for accuracy in all we publish; readers and contributors are encouraged to contact us if they recognise an error or omission. Once a magazine edition is published [online, in print or both], we do not update previously published articles to align old company names, branding, marketing efforts, taglines, mission statements or other promotional verbiage, images, or logos to newly created or updated names, images, typographic renderings, logos (or similar) when such references, the cacurately stated, rendered or displayed at the time of the original publication. When companies change their names or the images/text used to represent the company, we invite organizations to provide Angel Business Communications with a news release detailing their new business objectives and/or other changes that could impact how customers/prospects might recognise the company, contact the organisation, or engage with them for future commercial enterprise.

Printed by: The Manson Group. ISSN 1096-598X (Print) ISSN 2042-7328 (Online) © Copyright 2025

## Worries about Wolfspeed as a 'going-concern'

Company takes on external advisors to assist with strategic alternatives and capital restructuring

US SiC giant Wolfspeed has announced results for Q3 2025, with shares tumbling nearly 25 percent due to concerns for the company's long-term survival.

Q3 2025 revenue was \$185 million, compared with \$201 million for Q3 2024. The Mohawk Valley Fab contributed \$78 million in revenue compared with \$28 million in Q3 24. Gross margin was -12 percent.

While the top-line figures don't seem too bad, the company is struggling with \$6.5 billion of debt obligations.

And – as it said in the regulatory filing – "there is substantial doubt about the company's ability to continue as a going concern as of the issuance date, in accordance with the requirements of ASC 205-40."

Wolfspeed is waiting on \$750 million in federal funding under the US CHIPS Act. In March 2025, President Donald Trump said US lawmakers should get rid of the law and use the proceeds to pay debt.

Meanwhile, Wolfspeed's customers are dealing with tariff-induced uncertainty, with General Motors trimming its 2025 profit forecast, while Mercedes-Benz had pulled its earnings outlook for 2025, according to Reuters.

TrendForce's latest research shows that weakening demand in the automotive and industrial sectors slowed shipment growth for SiC substrates in 2024, with global revenue for *n*-type SiC substrates down 9 percent year-overyear. Despite the decline, TrendForce says long-term SiC demand remains strong as the 8-inch roadmap gains momentum. Wolfspeed leads the SiC substrate market with 33.7 percent market share in 2024 and is leading the transition to 8-inch wafers. Chinese vendors TanKeBlue and SICC have 17.3 percent and 17.1 percent market shares respectively, placing them in second and third place. Coherent, by

contrast, dropped to fourth place with a share of 13.9 percent.

Wolfspeed says its current operating forecast over the next 12 months will allow it to maintain operations and meet its obligations to customers, vendors and employees in the ordinary course of business. It has engaged external advisors Paul Walsh and Mark Jensen to the board to assist with strategic alternatives, including capital restructuring.

Walsh most recently served as CFO and SVP, Finance and Administration, at Allegro Microsystems. He previously served as CFO of Rocket Software and held multiple finance roles at Silicon Laboratories, ultimately serving as SVP and CFO. He currently serves on the boards of Kopin Corporation and Semtech Corporation.

Jensen brings an extensive background in finance and accounting, having most recently served as US managing partner, Technology Industry, at Deloitte from 2001 to 2012. Before joining Deloitte, he held senior roles as CFO of Redleaf Group and managing partner at Arthur Andersen. Jensen currently serves on the boards of 23andMe and Lattice Semiconductor.

Tom Werner, chairman of the board of Wolfspeed, said: "At the beginning of the year, the company outlined a plan focused on strengthening our capital structure, improving our path to profitability, and raising cost-effective."

capital to support our growth plan. I'm pleased to report that the board and management have made significant progress against all of the priorities we outlined – completing our \$200 million ATM offering, receiving \$192 million of our Section 48D cash tax refunds, simplifying the business to focus on our pure-play 200 mm capabilities and accelerating our path to cash flow breakeven, and hiring Robert Feurle (pictured left) as Wolfspeed's new CEO."

"Most importantly, we continue to work closely with our lenders on ways to address our capital structure, so that Wolfspeed has a strong financial foundation to support its continued success."

Feurle, added, "One of the key drivers in my decision to join the company was Wolfspeed's enormous potential, underpinned by strong foundational elements. The company's SiC technology is second-to-none and the company has already established a greenfield, best-in-class, fully automated 200 mm manufacturing footprint to provide next-gen solutions to our customers. I am aligning the organisation to drive innovation across the business and in key strategic verticals that demand quality, reliability, and efficiency precisely where our purpose-built 200 mm platform sets us apart."

Wolfspeed says its current operating forecast over the next 12 months will allow it to maintain operations and meet its obligations to customers, vendors and employees in the ordinary course of business.

## Introducing trench-based superjunction SiC

Infineon to use new SiC technology to expand the efficiency and compactness of its CoolSiC range

INFINEON is introducing trench-based SiC superjunction (TSJ) technology, adding to its existing CoolSiC product offering spanning 400 V to 3.3 kV.

"With the introduction of the TSJ concept, we are significantly expanding the technological capabilities of SiC," said Peter Wawer, president of Infineon's green industrial power division. "The combination of trench and superjunction technology enables higher efficiency and more compact designs – an important step for applications requiring the highest levels of performance and reliability."

Infineon says it intends to gradually expanding its CoolSiC product portfolio with SiC TSJ technology. This expansion will encompass a diverse range of package types, including discretes, molded and frame-based modules, as well as bare dies. The extended portfolio will cater to a broad spectrum of applications, targeting both the automotive and industrial sectors.

The first products based on the new technology will be 1200 V in Infineon ID-PAK for automotive traction inverters, and combine the advantages of trench technology and superjunction design, capitalising on Infineon's more than 25 years of experience in

SiC and silicon-based superjunction technology (CoolMOS).

This scalable package platform supports power levels of up to 800 kW, enabling a high degree of system flexibility.

Key benefits of the technology include increased power density, achieved through an up to 40 percent improvement in R<sub>DS(on)</sub>\*A, allowing for more compact designs within a given power class.

Additionally, the 1200 V SiC trench-superjunction concept in ID-PAK enables up to 25 percent higher current capability in main inverters without compromising short-circuit capability.

This advancement also results in enhanced overall system performance, according to the company, delivering improved energy efficiency, reduced cooling requirements, and higher reliability for demanding automotive and industrial applications.

Moreover, the

system benefits

from reduced

parallelisation

requirements,

which simplify

the design

process and lower

overall system

costs.

With these innovations, the Infineon ID-PAK package equipped with SiC TSJ technology contributes to the development of more efficient and cost-effective traction inverter designs for automotive applications.

As an early customer, Hyundai Motor Company development teams will engage with Infineon's trench-superjunction technology, using its benefits to enhance their EV offerings. This partnership is expected to drive the development of more efficient and compact EV drivetrains.

Initial ID-PAK 1200 V samples are available for selected automotive drivetrain customers. The SiC TSJ-based ID-PAK 1200 V package is expected to be ready for volume production in 2027.

#### IQE announces 2025 results and new CEO

Company announces 'solid' financials and appoints Jutta Meier as CEO

COMPOUND semiconductor wafer firm IQE plc has announces its results for the full year ended 31 December 2024.

Jutta Meier, CEO and CFO of IQE, commented: "IQE delivered a solid set of financials in line with our January 2025 trading update. Our focus has been on reducing costs and optimising our footprint, and I am pleased to see this has resulted in an improved adjusted EBITDA position year-on-year."

She added: "The strategic review remains ongoing and we have been encouraged by progress so far despite a challenging macro environment. IQE has a strong foundation from which to unlock value for all of our stakeholders and with a diverse customer pipeline, the continued end-market demand for our technology gives us confidence for the future. I am also delighted to be appointed as CEO as we continue to deliver on the positive progress we have made."

#### **Financial highlights**

Revenue for FY 2024 was £118.0 million, up £2.7 million sequentially.

Wireless revenue of £67.3 million increased 25 percent year-on-year, reflecting an increase in wireless GaAs sales linked to a higher penetration of Asian markets and an increase in GaN sales for 5G infrastructure.

Photonics revenue of £49.9 million decreased 16 percent year-on-year primarily because of softness in 3D Sensing and telecoms infrastructure markets, partially offset by a strong performance in Aerospace and Security markets for infrared-related products

CMOS++ revenue of £0.8 million was down 62 percent on a reported basis, reflecting a strategic rebalancing of the business' product portfolio and a shift in focus towards diversification into GaN Power and MicroLED sectors. In FY 2025 IQE will no longer reporting CMOS++ revenue as a standalone segment.

Cash and cash equivalents were £20.6 million as at 31 March 2025.

#### **Business update**

The company has been developing in various areas, including launching a Quantum Dot Laser foundry service for high-efficiency optical communications in data centres, with opportunity to take significant market share from incumbent laser technologies.

It has expanded the GaN RF Aerospace and Security business serving fast-growing end-market, including satellite internet constellation platforms (Low Earth Orbit Satellites – LEOS).

On the power front, IQE has a joint development agreement with X-FAB to create a Europe-based GaN Power device platform solution for automotive, data centres and consumer applications.

In other areas, it has developed InP and GaSb laser and detector technologies with a leading consumer OEM for healthcare sensing applications, and launched an 8-inch GaN-on-silicon microLED foundry service with in-house wafer cleaning, compatible with advanced Silicon CMOS manufacturing.

#### **Board update**

Jutta Meier has been appointed IQE's CEO following her successful period as Interim CEO. Jutta will continue in her dual role as CEO and CFO. Female representation on IQE's board now stands at an above average 57 percent.

Mark Cubitt will continue to act as executive chair, providing support to

Jutta and the executive leadership team through the ongoing strategic review. The composition of the Board will be re-evaluated following the conclusion of the Strategic Review.

Cubitt said: "I would like to recognise Jutta's success as CEO of IQE since she took on the interim role over six months ago. The Board felt she was an excellent candidate and in that time she has stabilised and refocused the business and rebuilt confidence with both customers and employees."

#### **Current trading and outlook**

Global markets are being impacted by macroeconomic uncertainty and as a result, some end customer demand is being fulfilled with existing inventory. This was visible in Q1 trading but is expected to correct in H2 2025. Costs and capacity continue to be optimised to improve margins and cashflow.

IQE says its customer pipeline remains strong and is predicted to grow in H2 2025, driven by new product and customer engagements. Additionally, existing segments, including Aerospace and Security and optical communications are also expected to deliver growth, offsetting anticipated softness in wireless segments resulting from challenged consumer markets, particularly in Asia.

There is currently no direct impact to IQE from the implementation of US tariffs, however developments are being closely monitored and options are being explored with both suppliers and customers to mitigate any potential risk.

Revenue and adjusted EBITDA for the full year are expected to be within the range of analyst forecasts for FY 2025, with weighting towards H2 consistent with the destocking seen in Q1 and typical industry seasonality. These forecasts assume the inclusion of IQE Taiwan revenues pending the outcome of the strategic review.

## Uviquity emerges from stealth with \$6.6m funding

US start up to develop PIC-based far-UVC technology for disinfection

UVIQUITY, a far-UVC start-up has emerged from stealth mode with \$6.6 million in seed funding. The round was led by Emerald Development Managers, an early-stage venture capital firm specialising in deep tech, with participation from AgFunder and Mann+Hummel, companies involves in food and agriculture venture capital and filtration solutions.

Uviquity is developing solid-state far-UVC (200 nm to 230 nm) semiconductor light sources designed to deliver safe, continuous, and chemical-free disinfection for air, food, and water applications.

The funding will support Uviquity's R&D efforts, accelerating the commercialisation of its proprietary PIC that couples blue laser light into frequency-doubling waveguides, enabling a scalable, single-chip far-UVC

solution that can integrate into a wide variety of applications using standard photonic packages.

"We believe far-UVC light is the future of pathogen control — and Uviquity's wide-bandgap semiconductor platform is the key to making it practical, scalable, and safe," said Scott Burroughs, CEO and co-founder of Uviquity. "This funding allows us to bring our vision to life and unlock a new standard for clean air, safe food, and pure water — at scale and without chemicals."

Far-UVC light has been proven safe for continuous exposure to human skin and eyes while rapidly inactivating all known pathogens, including viruses, bacteria, fungi, and mold spores.

Uviquity says its chip-based semiconductor approach offers a

compact, energy-efficient, and durable solution that can be integrated into light fixtures, air handling systems, food packaging and processing equipment, agricultural crop protection systems, water purification systems, and consumer appliances.

"With its proven team and novel technology, Uviquity fits perfectly with our goal to invest in exceptional companies that are solving real problems," said Cy Schroeder of Emerald Development Managers.

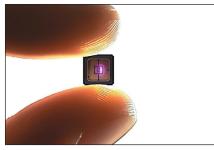

## Riber secures major order from Australia

MBE 412 cluster system to be used to advance research in IR technologies

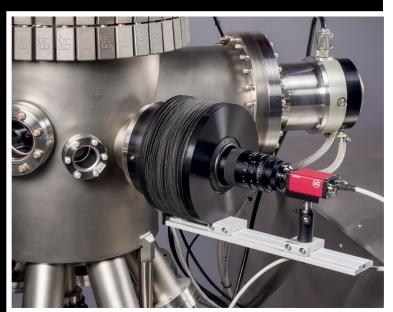

FRENCH MBE firm Riber has announced the sale of a research MBE 412 cluster platform with an automatic wafer transfer system to a leading Australian research laboratory.

The Western Australia Node of the Australian National Fabrication Facility (ANFF WA Node), based at the University of Western Australia, is the only research center in the country with expertise and device fabrication capabilities for infrared (IR) sensors, including high density imaging focal plane arrays.

To advance its research in IR technologies and to support the development of sovereign IR sensor capabilities in Australia, the ANFF WA Node has placed an order for a new Riber MBE 412 system. This dual chamber cluster platform will play a key role in long-term R&D efforts and is expected to significantly enhance the laboratory's capabilities.

Specially designed for research on nextgeneration infrared imaging devices, the MBE 412 system is fully automated, supports wafers up to

7 x 7 cm, and is equipped with Riber's Crystal XE software for state-of-the-art uniformity performance.

To meet customer needs, the system is mecury-compatible, enabling the growth of HgCdTe structures. All components - including equipment, pumps, and effusion cells - have been customised to comply with the lab's specific requirements, with comprehensive technical and process support provided.

The system will be installed in 2026 in a new laboratory at the University of Western Australia, adjacent to an existing MBE system.

Annie Geoffroy, chair and CEO of Riber commented: "We are proud to continue supporting our long-standing partners. This order placed 36 years after the acquisition of a first Riber 32P system still in operation today – illustrates the enduring trust in our technology. The MBE 412 platform, equipped with the latest innovations, reaffirms our commitment to delivering highperformance, reliable, and safe MBE solutions tailored to the evolving needs of research institutions."

### Finwave nets \$8.2 million

GaN INNOVATOR Finwave Semiconductor has announced a new \$8.2 milion bridge investment round, led by Fine Structure Ventures, Engine Ventures, and Safar Partners – with strategic participation from technology partner GlobalFoundries.

Finwave will use this investment to accelerate revenue generation, expand its product portfolio and continue developing GaN-onsilicon technology for high-power RF switches, power amplifiers for communications infrastructure, and power amplifiers for mobile devices.

"We are emboldened by the support of our investors, who share our belief in the commercial potential of our technology," said Pierre-Yves Lesaicherre, CEO of Finwave. "This funding round validates the years of engineering and innovation behind our proprietary GaN-on-silicon technology and provides resources we need to move from the development phase to delivering differentiated. high-performance products. More than just funding, this is a clear endorsement of our direction – and a strong signal that the industry believes in the path we're on."

"Since our initial investment. Finwave has made remarkable progress towards becoming a leader in GaN-on-silicon highperformance RF components," said Jennifer Uhrig, senior managing director, Fine Structure Ventures.

"Their strategic foundry partnership with GlobalFoundries and distribution partnership with RFMW have been particularly notable, legitimising their design capabilities and giving customers confidence in Finwave's ability to bring highperformance, reliable products to market"

### Singapore-MIT group to make machines 'see' like humans

WISDOM programme to use wafer-scale integration to combine LEDs and VCSELs, metasurfaces, and CMOS electronics

THE Singapore-MIT Alliance for Research and Technology (SMART) has launched a new interdisciplinary research group focused on developing next-generation 3D-sensing technologies for practical use across industries such as automotive, consumer electronics, aerospace and healthcare.

The multi-million-dollar WISDOM (Waferscale Integrated Sensing Devices based on Optoelectronic Metasurfaces) research group will use wafer-scale integration to combine three separate elements: optical metasurfaces; optoelectronic devices, with a focus on LEDs and VCSELs: and silicon CMOS electronics.

Jointly led by faculty from MIT and Nanyang Technological University, Singapore (NTU Singapore), the group will focus on developing ultra-thin, scalable sensing devices to allow machines such as autonomous vehicles and robots to perceive depth, shape and spatial detail safely and with more versatility, much like human vision.

Using this approach, the team aims to redefine the capabilities of lidar systems to enhance detection accuracy, extend range and field-of-view, and

reduce motion artifacts. The group thinks the technology also opens the door to new applications like glassesfree 3D displays and high-speed optical communication.

SMART WISDOM will be led by co-lead principal investigators Jueiun Hu, professor of materials science and engineering at MIT, and Tan Chuan-Seng, professor of electronic engineering at the school of electrical and electronic engineering at NTU Singapore.

"What makes me really excited about

WISDOM is that we're putting together pieces that haven't been combined before - to benefit a ton of industries and use cases. For example, think how a super light and powerful lidar system could make trips to planets beyond Mars a reality. It's like having a whole new set of eyes for exploration, and about making the seemingly impossible, possible," said Juejun Hu.

The project is supported by the National Research Foundation Singapore under its Campus for Research Excellence and Technological Enterprise programme.

## The Next Generation in Process **Control for GaN Devices**

#### Achieve high quality GaN on Si in HVM

CRYSTALLINE DEFECT INSPECTION

SURFACE EDGE OR **BEVEL DEFECT** INSPECTION

...for a range of wafer sizes! ontoinnovation.com

## Indium Corp and Rio Tinto's gallium sourcing project

Companies successfully extract gallium from feed sourced at Rio Tinto alumina refinery in Quebec

INDIUM CORPORATION and Rio Tinto have announced the successful extraction of gallium from feed sourced at Rio Tinto's Vaudreuil alumina refinery in Saguenay, Quebec, Canada.

They say that this achievement highlights the power of collaboration in building a more robust global supply chain for gallium.

Gallium is currently produced in limited quantities worldwide. This partnership is working to create a reliable and sustainable supply of this essential material to meet growing global demand for advanced technologies. Indium Corporation designed and developed this gallium extraction

process in the United States at its Rome, NY, research and development

"This milestone is a major step forward in our joint efforts to create a new and robust supply of gallium," said Ross Berntson, president and CEO of Indium Corporation. "Through this collaboration, we have demonstrated the viability of gallium extraction and laid the groundwork for commercial production to benefit industries worldwide."

Jérôme Pécresse, CEO, Rio Tinto Aluminium, added, "We are very proud to announce this significant milestone in our important research and development project to extract and valorise gallium from our aluminum operations in Quebec. Together, through this innovative partnership, Rio Tinto and Indium Corporation strive to strengthen the North American supply chain for gallium, a critical and strategic mineral."

Indium Corporation will continue to develop the extraction process at its research and development facility to meet the planned commercial scalability needs for a 3.5-tonne demonstration plant that would be located in Saguenay, Quebec, and then eventually commercial-scale capacity of 40 tonnes annually, addressing an estimated five to 10 percent of global gallium supply.

Large stock of Molybdenum and Tantalum

All parts made according to

#### **MICRO-MECHANICS** ON STRATEGIC MATERIALS

- In stock for all vacuum and ultra vacuum applications : (screws, nuts, rings) « Usable in Clean Rooms »

- In stock for laboratory machines : Standard substrate support (Molybloc) Dimensions:

- 1½ inches

- 2 inches

- 3 inches

Possibility of substrate support with cavity and washer, on request and according to drawings

- Stock of platens blanks for all types of MBE from various manufacturers.

- « Usable in clean rooms » Platens and washers produced according to drawings.

#### RABOUTET SA

Avenue Louis Armand • B.P. 31 • 74301 Cluses Cedex FRANCE T. +33 (0)4 50 98 15 18 • info@raboutet.fr

## **SENSING** Meet a semiconductor megatrend

# -InP-GaAs-GaSb

## RIBER'S MBE production systems

Multi 3" Multi 4" Multi 6"

For High performance P/Sb/As IR lasers and detector for:

**Defence**

Security

Sensing healthcare

Environment control

RIBER

INNOVATIVE SOLUTIONS FOR SEMICONDUCTOR INDUSTRY

#### NEWS ANALYSIS | POWER ELECTRONICS

### Smart GaN HEMT + IGBT = EV success?

Cambridge GaN Devices is targeting the powertrain of electric vehicles with the combination of IGBTs and its proprietary integrated circuit enhancement GaN technology.

#### BT RICHARD STEVENSON, EDITOR, CS MAGAZINE

TODAY'S DESIGNERS of power trains for electric vehicles face a difficult choice. Should they view cost as paramount and select silicon IGBTs; or should efficiency be the priority, and they deploy SiC MOSFETs? Whichever they choose, a significant compromise will be made.

But now there's the promise of a third way, pioneered by a handful of producers of GaN — they are claiming that they could offer products with a price close to that of silicon solutions, while delivering an efficiency similar to that of SiC, by pairing a GaN HEMT with a silicon transistor.

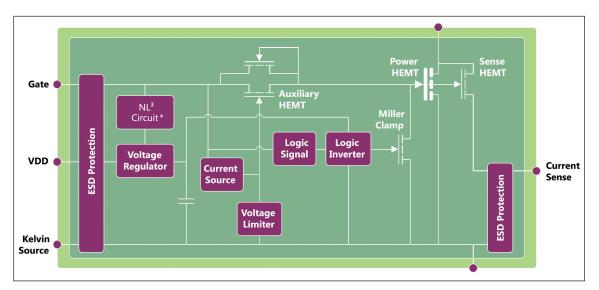

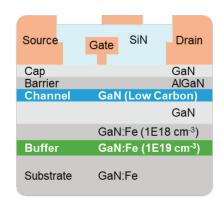

Amongst these trailblazers, Cambridge GaN Devices (CGD) claims that it is standing out from the crowd with its proprietary integrated circuit enhancement GaN technology, which it refers to as ICeGaN. The company is championing the combination of its 'intelligent' GaN HEMTs, which feature an enhancement-mode *p*-GaN HEMT rated at 650 V, and an IGBT. It's a patent-pending pairing with the moniker Combo ICeGaN.

According to Daniel Murphy, Director of Technical Marketing at CGD, the company's ICeGaN is its core technology, as well as its unique selling point. "This is what we're building the company around. The DNA of CGD, if you like."

One of the primary strengths of ICeGaN is that it provides ease of use. "You can essentially treat a GaN transistor like a MOSFET," says Murphy. Due to this, it's possible to use a very simple, low-cost driver to accompany the GaN HEMT.

Another great attribute of ICeGaN is that it facilitates zero-voltage switching, thanks to the inclusion of a Miller clamp. "There's no need for a negative voltage to be applied to switch the device," says Murphy, explaining that this refinement allows the driver to be simpler and cheaper. What's more, the Miller clamp ensures a very efficient turn-off of the GaN HEMT.

In addition to these valuable assets, absent in conventional GaN HEMTs, CGD's ICeGaN

#### NEWS ANALYSIS | POWER ELECTRONICS

> IceGaN is a form of smart power HEMT that features advanced sensing and protection capabilities.

technology has a slightly higher threshold voltage for the transistor.

"We've shifted it up to about three volts," says Murphy, explaining that this adjustment brings ICeGaN technology in line with standard silicon devices. "Hence, you can use standard silicon drivers."

The slight increase in threshold voltage also eliminates the danger of spurious turn-on.

With Combo IceGaN, higher efficiencies are realised by drawing on the complementary benefits of both classes of transistor.

"GaN comes into play at light loads, where you have very low switching losses. It brings increased efficiency," enthuses Murphy, who adds: "At high loads, and in some fault conditions, the robustness of the IGBT comes into play."

While the levels of efficiency provided by Combo IceGaN are not quite as high as they are with a full SiC solution, it provides a cost saving of around 40 percent to 50 percent, according to Murphy. And compared with only IGBTs, efficiency is 3 percent higher, based on measurements that consider the Worldwide Harmonised Light Vehicles Test Procedure cycle. "That obviously translates into either a less expensive battery or extended range," remarks Murphy.

As well as targeting the power train, CGD is pursuing opportunities in on-board chargers and DC-to-DC converters in electric vehicles, as well as industrial data centres, through the development of more innovative approaches. In this sector, power densities and power levels tend to increase year-on-year. "So, we're needing to improve the form factor all the time, and investigate different ways to address the packaging to meet the thermal requirements," says Murphy.

As all these applications involve very high power

levels, the increase in chip area associated with additional features of ICeGaN, such as advanced sensing and the protection function, is relatively modest. Thanks to this, CGD is able to produce highly functional, competitively priced products.

Like many players in GaN power electronics, CGD is fabless, with chips produced at TSMC. This world-renowned Taiwanese foundry is responsible for the growth of epiwafers and their processing into devices. Packaging is undertaken at another partner, ASE.

As the Combo GaN technology can incorporate a range of IGBTs, CGD is planning to operate at the chip level within the supply chain. "We're looking for module partners, we're looking for car makers, tier ones that are interested to adopt this approach, and then we would support them with the sale of bare die," says Murphy.

One of the reasons why CGD is focusing on the traction inverter within the electric vehicle market is the volume of GaN that's required. "It is so much higher, because the power level is so much higher," claims Muphy, who adds that the other big draw is the substantial technical challenge. "We're a company with lots of smart people, and we're very ambitious. So that's why we're targeting traction."

Given the conservative nature of the automotive industry, it will take time for CGD to penetrate this market. The plan is to begin by launching discrete products for on-board chargers and DC-to-DC converters in 2026.

"The idea is for traction to try and enter a carmaker platform around 2028 timescale, and sooner than that with on-board chargers and DC-to-DCs," says Murphy.

So, while the makers of SiC MOSFETs are going to face stiff challenge from other wide bandgap devices, the competition is not going to begin immediately.

## Infineon's expanding 2 kV portfolio

Joining Infineon's 2kV MOSFETs are Schottky barrier diodes with identical voltage ratings

#### BY RICHARD STEVENSON, EDITOR, CS MAGAZINE

HIGH ON THE AGENDA of many design engineers in increasing the electrical efficiency of their systems. Gains on this front trim carbon dioxide emissions and utility bills, while reducing heating, which simplifies thermal management and enhances reliability.

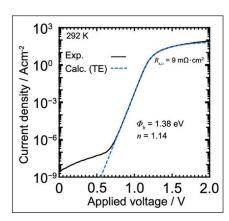

Today, two well-trodden routes may be taken to increase the efficiency of electrical systems. One of these proven pathways is to replace silicon power electronics with those that have a wider bandgap, as this reduces resistance. And the other common approach is to increase the voltage of the electrical system, and this enables a reduction in current and ohmic heating.

While both approaches pay dividends, rather than picking one over the other, it's better to adopt both practices. And helping to do just that is the trailblazer of the SiC Schottky barrier diode (SBD), Infineon Technologies: it added a 2kV SiC SBD last October, and has just introduced a sibling, rated at the same voltage and housed in a different

package. This pair of diodes complement Infineon's 2 kV MOSFET, launched in March 2024.

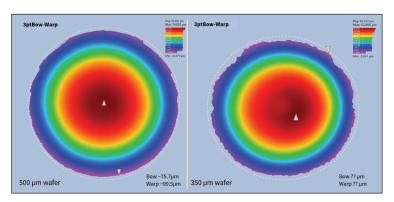

Infineon has been refining the SiC SBD for decades, having brought the first commercial device to market back in 2001. Major revisions to this diode since its debut include a new backside die metallisation and die attach technology, and more recently, the introduction of thin wafer technology, making an appearance in the fifth-generation portfolio. With these SBDs, the thickness of the die is

In 2018, the European powerhouse introduced a sixth-generation of SiC SBDs, featuring an electrochemical barrier between the metal and

slashed from 350  $\mu m$  to just 110  $\mu m$ .

semiconductor that reduces the knee voltage by around 0.1 volts.

"For 650 volts, this is a big advantage, but not so much for other blocking voltages," remarks Peter Friedrichs, Infineon's Vice President of SiC. "For that reason, Gen 6 remained at 650."

By offering fifth-generation 2 kV SiC SBDs in two different packages – initially TO-247PLUS-4-HCC, and now the TO-247-2 package – Infineon is giving design engineers the opportunity to select between a diode that majors on clearance and on creepage. The former metric is related to the physical distance between the pins, with a higher value reducing the chances of arcing, while creepage considers the conductance pathway along the package surface.

"[With the TO-247PLUS-4-HCC] there's an extra gap in the plastics that forms a longer creepage," says Friedrichs.

It's not clear which of the two variants will prove more popular. "We can scale both of them according to customer needs," says Friedrichs.

Infineon is mainly targeting two markets with its expanding portfolio of 2 kV power devices: the solar sector and the charging of electric vehicles.

To provide high-power, fast charging of electric vehicles, bus voltages as high as 1,500 V are employed. So, to ensure reliability in this application, power devices are ideally rated at 2 kV.

Within the solar market, one of the trends has been an increase in the output voltage of the panels. "Today, 1,500-volt panels are state-of-the-art, but there are already first solutions with 2 kV and even higher," says Friedrichs.

While it is theoretically possible to serve both these applications with silicon devices related at 2 kV, the electrical losses are unacceptable. So wide bandgap

➤ Infineon's

barrier diode

in a TO-247-

2 package

majors on

clearnace.

2kV SiC

Schottky

#### NEWS ANALYSIS | POWER ELECTRONICS

By offering fifth-generation 2 kV SiC SBDs in two different packages – initially TO-247PLUS-4-HCC, and now the TO-247-2 package – Infineon is giving design engineers the opportunity to select between a diode that majors on clearance and on creepage

devices with a low voltage rating have been adopted, using what is referred to as a multi-level topology.

"You stack components with a lower blocking voltage in series to manage the higher voltage," explains Friedrichs, illustrating this point by suggesting that rather than using a 2 kV device, two 1.2 kV devices may be used in series. However, as well as doubling the number of devices, multilevel topology designs increase the complexity for controlling the circuit and magnify cost at the system level.

As one would expect, Infineon's 2 kV devices are more expensive than their 1.2 kV siblings.

"2 kV comes at a higher price, since we need a thicker epitaxial layer, a thick drift zone and a larger area. This, of course, contributes to cost, but it's still more affordable than putting two 1.2 kV in series," explains Friedrichs.

For SiC devices, the substrate accounts for a significant proportion of device cost, especially for SBDs, even though they are smaller than MOSFETs. However, substrates costs are falling, with a significant reduction in the last 12 to 15 months, according to Friedrichs.

For both of the applications that Infineon is targeting humidity is an issue, as electric vehicles and solar panels operate outdoors. Friedrichs says that humidity is a particularly significant concern for solar applications, due to the low night-time temperatures that leads to condensation in the system. It's not possible to address these concerns with a perfect hermetic seal, and if moisture enters the power devices, this can impact long-term reliability.

Infineon has been aware of this issue for many years, having been supplying devices to makers of solar systems since 2010. "From that point onwards, we have integrated special measures to protect the silicon carbide chips against any moisture-related degradation," says Friedrichs.

to an extra gap in the plastics, the TO-247PLUS-4-HCC suits engineers requiring a high degree of creepage

> Thanks

Two sites for production of its SiC portfolio have been established by Infineon: Villach, Austria; and Kulim, Malaysia.

"In Kulim, we are just starting to ramp silicon carbide front-end production," says Friedrichs. "We start with the MOSFET. So, at the moment, all the diodes are produced in Villach."

But with demand for SiC power devices set to rise, it will potentially not be long before the Kulim fab is serving customers all around the world with a broad and expanding portfolio that includes high-voltage SBDs.

## The tipping point for AIN

Advances in AIN substates are positioning this nitride as a transformational material in next-generation electronic and optoelectronic applications

#### BY KASEY HOGAN FROM CRYSTAL IS

DEPLOYMENT of devices in space is increasing at a phenomenal rate, creating a lucrative opportunity for our industry. However, winning sales in such a harsh environment is not easy, as it involves extreme temperatures and persistent bombardment by radiation, conditions that make it very challenging for RF and power devices to deliver high levels of performance throughout the lifetime of the mission. In addition, reducing the payload mass is critical to easing launch costs and meeting the strict size, weight, and power constraints of aerospace systems.

But that's what's required – in fact there's demand for robust devices that combine a high-power density with a high-voltage capability and a highfrequency capability in many extreme environments; spanning both spaceborne and ground-based systems where reliability, efficiency, and compactness are critical.

The challenge of meeting these exacting requirements is driving interest in new semiconductor materials. Over the last decade, devices made from silicon have been displaced by those made from two wide bandgap materials, SiC and GaN, that are enabling a higher power density, improved thermal management, and broadband operation. But the defence and aerospace industries are not satisfied. Instead, it craves even higher levels of performance – and promising to fulfil them are ultrawide bandgap semiconductor materials, such as AIN, diamond, and Ga<sub>2</sub>O<sub>2</sub>.

Within that family of ultrawide bandgap devices, AIN has generated significant attention for many years. Judged by various figures-of-merit, there's no doubt that this nitride has tremendous potential. However, it has a reputation as a difficult material to dope, and it's been challenging to produce substrates with a significant size at volume. Due to these issues, some may have dismissed AIN as a material that's never going to make an impact.

But recent developments suggest otherwise, and there's good reason to believe that after showing its promise for several decades, AIN is now on the cusp of becoming a mainstream material for chip production.

For many years, significant technical challenges in the doping, contacting and the fabrication of devices, along with the availability and cost of native substrates, has hindered progress and the adoption of native AIN devices. Due to bandgap of 6.2 eV, AIN is challenging to dope, due to deeper dopant levels. In addition, it's far from easy to form an ohmic contact with standard metallisation. However, recent work shows that these challenges are not insurmountable.

Another attraction of AIN, which marks it out from the other members of the ultrawide bandgap community, is that it's part of the III-Nitride material system, which includes GaN and AlGaN. Thanks to this, it's possible to produce devices that leverage a very wide compositional range. Such devices could be produced on bulk single-crystal AIN substrates that provide a close lattice-matched foundation that minimises dislocation density and enhances thermal management, and ultimately unlocks the full potential of III-Nitride-based architectures. With recent advancements in AIN substrate technology, this is now a reality.

#### Commercially viable substrates

As well as its potential for serving in space, AIN has been viewed for many years as an enabling technology for optoelectronic devices, thanks to its high thermal conductivity, ultrawide bandgap, low dislocation density and its close lattice matching with other III-Nitrides.

Due to these strengths, AIN substrates are used to produce commercial UVC LEDs, with a manufacturing ecosystem producing thousands of 2-inch diameter substrates per year. Now that the

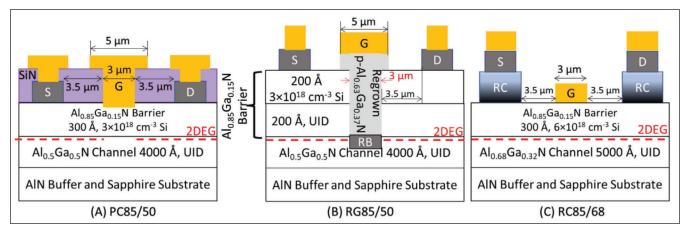

➤ Transistor epitaxial architectures and layout indicating locations of the source (S), gate (G), drain (D), regrown barrier (RB), regrown contact (RC), and 2D electron gas (2DEG).

viability of commercial optical-grade substrates is beyond doubt, this material is being considered for electronic device development.

To succeed in this new domain, it is critical that large-diameter, high-quality, native substrates are widely available – they are a crucial component in the semiconductor supply chain. Recently, much progress has been made on this front. Last year, my company, Crystal IS, reported the availability of 100 mm bulk AIN substrates for research purposes - along with announcements on consistent progress in quality and manufacturability. These milestones in the development of AIN substrates have spurred the development of AIN-based devices in areas ranging from academia to government programmes. There have been significant investments all over the world to develop an industrial supply chain. While technological barriers still exist to realising the full promise of AIN, it's important to note that there have been two recent works related to novel transistor structures on AIN that show progress. Read on to learn more about them.

#### Overcoming barriers for AIN-based devices

One of the strengths of the AIN substrate is that it provides a foundation for utilising aluminium-rich AlGaN layers or thick AlN layers - which may offer a transformational performance compared with what is possible with wide bandgap materials. Ultra-wide bandgap materials, such as AIN, have a high bond strength and a high thermal conductivity that allows for high breakdown fields and operation in extreme environments. Devices made from them are capable of reliable performance and longevity in space, sea, and desert.

Traditionally, research into AIN-based materials has been undertaken on thin AIN templates, grown on sapphire substrates. However, with the availability and cost-reduction of bulk AIN substrates with diameters of 2-inch. 3-inch and 100 mm, this research can now be conducted on material with far superior quality and thermal conductivity.

Having widespread availability of native substrates is helping to address the challenges associated with doping and contacting native AIN material, as well as aluminium-rich AlGaN, which has a high bandgap. A team at Sandia National Laboratory has recently reported a low ohmic contact resistivity in aluminium-rich layers, realised by utilising a re-grown reverse compositionally graded contact. They also describe a re-grown p-type AlGaN gate structure, which leads to a large positive threshold voltage and negligible gate leakage. Together, these developments provide a promising route towards high-current aluminium-rich AlGaN transistors that will enable a new operating regime for discrete highpower devices, by setting a new bar for breakdown voltage and on-resistance.

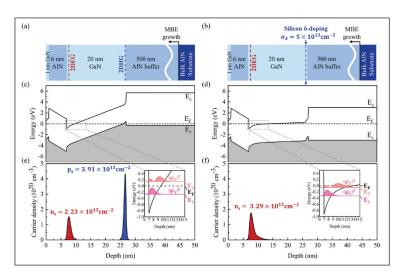

Another key breakthrough, coming from a team at Cornell University, is an AIN/GaN/AIN quantumwell HEMT on the bulk AIN substrate platform. This device offers substantial performance benefits for next-generation RF and power electronics.

➤ (a) Schematic of the epitaxial undoped AlN/GaN/AlN QW HEMT heterostructure. (b)  $\delta$ -doped AlN/GaN/AlN XHEMT heterostructure includes a sheet of n-type donors.

According to recent published work, this group has developed a so-called delta-doping method to enhance the electron mobility in the thin GaN well. Other efforts have focused on making the GaN layer thicker, to distribute the high electric field caused by the GaN/AIN polarisation discontinuity across a larger distance. However, this approach may induce significant defects into the material, limiting thermal performance.

Cornell's approach allows the channel to remain thin and strained, while enjoying the extremely high crystalline quality afforded by the AIN substrate. The delta-doping method offsets the high electric

#### **FURTHER READING / REFERENCE**

- ➤ R. Bondokov et al. "Development of 100 mm AIN Single-Crystal Growth and Subsequent Substrate Preparation" Phys. Status Solidi B 2500032 (2025)

- Y. H. Chen et al. "High conductivity coherently strained quantum well XHEMT heterostructures on AIN substrates with delta doping," Appl. Phys. Lett. 125 142110 (2024)

- ▶ B. Klein et al. "Al-Rich AlGaN Transistors with Regrown p-AlGaN Gate Layers and Ohmic Contacts," Adv. Mater. Interfaces 12 2301080 (2024)

field and the presence of an undesired polarisationinduced positive charge, without sacrificing crystalline quality or creating an unwanted second channel. This team's HEMT combines a high electron density and a high mobility with a low sheet resistivity. Controlling and enhancing the doping in this material through polarisation charge, rather than the traditional method of implantation or incorporation of dopant atoms, is a promising development.

Drawing on the recent increases in native AIN substrate availability by the main global players, now is time for RF and power device manufacturers to ramp up their development efforts on this material. While historical concerns around the technical challenges of doping and forming ohmic contacts remain, they can be overcome with significant effort and investment.

The key point is that the bulk AIN substrate diameter has reached the electronic-industry relevant diameter of 100 mm, and there's a proven route for this material to achieve commercially relevant volumes. Due to this triumph, AIN is now well positioned to lead the ultra-wide bandgap materials into the future, but to do so requires continued innovation within our community.

## Find your way in thin film technology with Evatec

From front and backside metallization for Si, SiC and GaN, to RF filters for 5G, and hybrid DBRs driving down production costs and enabling smaller device architectures in MicroLED, Evatec know-how in power devices, wireless and optoelectronics brings you innovative thin film production tools and processes that keep you on the right road.

Read more on all these topics in the latest edition of LAYERS.

Request your FREE copy now

Semiconductor & Advanced Packaging | Compound & Photonics | The Thin Film Powerhouse | evatecnet.com

## IR LayerRelease™ Technology

- Replacement for mechanical debonding thanks to through-silicon IR laser

- Enabling ultra-thin film or layer transfer from silicon carriers

- Nanometer-precision release of bonded, deposited or grown layers

- Front-end compatibility through silicon carriers and inorganic release materials

- Supporting future roadmaps in advanced packaging and transistor scaling

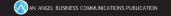

## Scaling the growth of novel materials

From 4-inch gallium oxide films to next-generation transition metal dichalcogenides, Agnitron's US-driven breakthroughs on large-area wafers are ushering in a new era of semiconductor devices

## BY WILLIAM BRAND, AARON FINE, FIKADU ALEMA, PAUL FABIANO AND ANDREI OSINSKY FROM AGNITRON

IN THE fledgling days of our industry, production of compound semiconductor devices just involved those based on GaAs and InP. But over a number of decades, our palate has expanded to include a number of new materials with more impressive characteristics. Devices made from GaN are now serving in the optoelectronic, RF and power domains, where they are generating substantial revenues, and SiC is supporting a revolution in mobility. But that's by no means the end of our journey. Now piquing much interest is gallium oxide (Ga<sub>2</sub>O<sub>3</sub>), an ultra-wide bandgap material that promises to deliver unprecedented efficiencies in electrical systems, and transition metal dichalcogenides (TMDs), which could spur advances in electronics, energy storage and sensors.

Helping to usher in a new era for compound semiconductor devices that is driven by the introduction and uptake of  $Ga_2O_3$  and TMDs is our company, Agnitron Technology. For nearly a decade, we have been leading the development of advanced MOCVD reactors and processes for high-quality  $Ga_2O_3$  and its alloys, and more recently we have been expanding our reach into TMDs. Due to this, our MOCVD systems are now deployed at leading universities and research institutions worldwide, supporting cutting-edge  $Ga_2O_3$  and TMD research.

More recently, we focused on scaling our MOCVD technology to support multi-wafer and largearea  $Ga_2O_3$  growth. In 2018, we introduced two new multi-wafer MOCVD platforms, both designed explicitly for  $Ga_2O_3$ . These reactors feature susceptor rotation speeds up of to 2000 revolutions-per minute (RPM), key to enabling excellent film uniformity and crystal quality. Our Agilis 700 supports wafer loading of up to one 6-inch wafer.

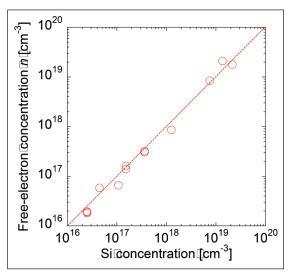

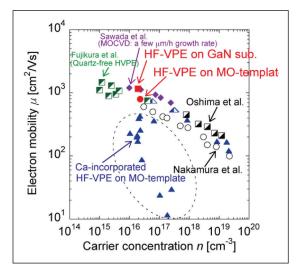

Working with our partners, we have used these platforms to demonstrate record-breaking material performance. Highlights with the Agilis 500 include the growth of Ga<sub>2</sub>O<sub>3</sub> thin films with exceptional purity and a record low-temperature electron mobility, exceeding 23,000 cm<sup>2</sup>/ V<sup>-1</sup>s<sup>-1</sup> [1]. Additional triumphs with our Agilis platform are: controllable doping down to low 1015 cm-3, a pre-requisite for drift layers in vertical power devices; and through the optimisation of silicon doping, conductivity values surpassing 2500 S cm<sup>-1</sup>, corresponding to free-carrier concentrations of  $3.4\times10^{20}~\text{cm}^{\text{-3}}$  [2]. Similar high-doping results have been independently reported by researchers from the Naval Research Laboratory (NRL) on an Agilis 500 tool operating at high rotation speeds [3].

#### Innovation in Gas injection: The Agilis 700 platform

We are continuing to pioneer advancements in semiconductor manufacturing equipment, exemplified by our newly redesigned Agilis 700 MOCVD platform. Central to this innovation is a novel gas injection methodology, replacing traditional central-injection and checkerboard patterns with an all new advanced Close-Injection Showerhead approach. By ensuring precisely controlled precursor flows in separated zones directly above the substrate surface, this refinement minimises gas-phase reactions and precursor depletion. The improved control delivers significant gains in uniformity and material quality - critical for large-area wafer deposition, and evidenced by recent preliminary electrical results from pioneering 4-inch Ga<sub>2</sub>O<sub>3</sub> devices.

The Agilis 700 underscores our commitment to scalability and flexibility, providing a robust platform for both research and production. It supports various substrate configurations, and can accommodate seven 2-inch wafers, a single 4-inch wafer or even a 6-inch wafer, all without compromising growth uniformity or material quality. Sharing core design features with its predecessors – the Agilis 100 (up to 3-inch wafers) and Agilis 500 (up to five 2-inch wafers) – the Agilis 700 bridges the gap between R&D and production, enabling seamless process translation across scales.

As well as providing a range of tools for research, we serve the needs of high-volume manufacturers through our GOX300 platform, an automated, production-focused MOCVD system. This mass-production tool builds on the reactor technology

and scalability principles of our Agilis line while incorporating automation and advanced process control that's tailored to industrial semiconductor production. The GOX300 allows manufacturers to access high-throughput, high-uniformity processing, which is essential for commercialising next-generation electronic and optoelectronic devices. We are very active in equipment innovation, with efforts extending further into reactor design, the optimisation of deposition efficiency, and supporting high-performance materials growth across a wide range of semiconductor applications.

#### Revolutionising deposition: The RDR reactor

Our proprietary Rotating Disc Reactor (RDR) is the core of our oxide MOCVD systems, including the Agilis 700. With over 16 years of innovation, our engineering legacy can be traced back to early RDR simulations at Sandia and MIT Lincoln Lab. While others with an interest in epitaxy focused on theory, we grasped the RDR's commercial potential – especially for wide and ultra-wide bandgap semiconductors.

This led to a dedicated effort to optimise our RDR for materials like  $Ga_2O_3$  and AIN. Significant successes have followed, including the deposition of the highest-purity  $Ga_2O_3$  film reported to date, solidifying our leadership in oxide MOCVD. Since 2018, our team and equipment users have contributed to over 250 peer-reviewed publications and conference papers focused on the epitaxial growth and device applications of  $Ga_2O_3$ .

Key to our success is our patented showerhead design that enables precise flow and thermal stability while preventing unwanted wall deposition – a common shortcoming in traditional systems.

The RDR's dimensionless process equations also allow it to scale easily, from a single 2-inch wafer to  $21 \times 2$ -inch configurations and even 12-inch substrates.

As we continue to advance our platform, our domestic innovation and our collaborative partnerships remain central to our mission.

#### Scaling Ga<sub>2</sub>O<sub>3</sub> to 4-inch wafers

Equipping our Agilis 700 reactor with an all-new gas-distribution flange that's optimised for growth of  $\beta\text{-}\text{Ga}_2\text{O}_3$  on large-area substrates ensures the growth of highly uniform epitaxial films. Vital to this optimisation is the support that's come from the Air Force Research Laboratory (AFRL) through the SBIR direct to Phase II program.

For this work, we selected trimethylgallium (TMGa) as the gallium precursor, due to its ability to facilitate faster deposition rates than the more conventional triethylgallium (TEGa), commonly used for  ${\rm Ga_2O_3}$  growth. Our films were grown under the following conditions: 800 °C growth temperature, 25 Torr

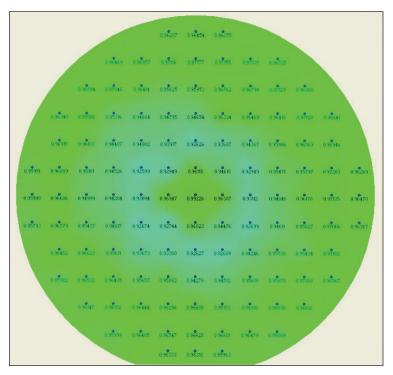

➤ Figure 1. Two-dimensional thickness map of  $Ga_2O_3$  film grown on a 4-inch sapphire substrate using the Bowtie showerhead. The growth rate was 2  $\mu$ m/hr, and a 2 mm edge exclusion has been applied during thickness mapping.

chamber pressure, 800 RPM susceptor rotation, and a molar flow for TMGa of approximately 240  $\mu mol\ min^{\text{-}1}.$

A key concern when using TMGa is the potential for carbon incorporation, introduced during decomposition of the methyl groups. Note that with TEGa, the threat of carbon contamination is avoided, due to different breakdown mechanisms. When we use TMGa, we mitigate the risk of carbon incorporation by maintaining a VI/III ratio above 500 – this condition has been previously identified as the threshold for avoiding carbon incorporation and ensuring film purity. Under these optimised conditions, we reached growth rates of around  $2 \ \mu m \ hr^{-1}$ , resulting in films with a thickness of around 1 µm. According to 121-point reflectivity mapping on a 4 inch substrate, thickness nonuniformity is just 1.39 percent. Realising this level of uniformity is essential for the scalability and reliability of Ga<sub>2</sub>O<sub>3</sub>-based devices.

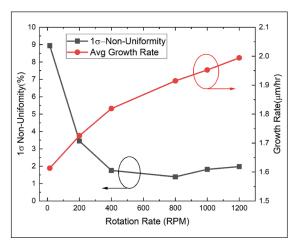

As part of our study into  ${\rm Ga_2O_3}$  thin-film growth on 4-inch substrates, we examined the effect of susceptor rotation speed on growth rate, varying RPMs up to 1200. We identified a clear linear trend between 400 RPM and 1200 RPM, where the growth rate increased from 1.8  $\mu$ m hr $^1$  to 2.0  $\mu$ m hr $^1$ . This increase is accompanied by little change in thickness non-uniformity, which remained stable across the RPM range. All our samples within this range exhibited a  $1\sigma$  value of less than 2 percent

(the best value, just mentioned, is 1.39 percent, at 800 RPM). However, we found that reducing the RPM below 400 led to a more rapid decrease in growth rate, and a significant increase in non-uniformity. For instance, at 200 RPM, non-uniformity jumps to approximately 3.5 percent, and at 0 RPM, it increases to 9 percent.

These results highlight that with our new gas-injection scheme, it is critical to maintain a high-speed rotation to ensure optimal growth rates and uniformity. The increased non-uniformity at lower RPMs also suggests that slower rotation speeds hinder diffusion of precursors, hampering controlled growth.

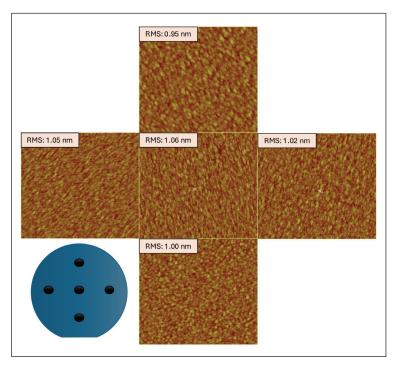

Due to the limited availability of native 4-inch  $Ga_2O_3$  substrates, we have also investigated the surface morphology and the electrical properties of  $Ga_2O_3$  films grown on native 2-inch (010) substrates. For this study, we formed an epitaxial structure consisting of a low-temperature nucleation layer, followed by 200 nm of unintentionally doped material, and a 65 nm silicon-doped layer. This stack is designed for the fabrication of a lateral FET, a common  $Ga_2O_3$  device.

Through optimisation of parameters – 800 °C growth temperature, 25 Torr chamber pressure, and 48  $\mu$ mol min-1 TEGa molar flow – we achieved a film thickness non-uniformity of just 0.83 percent. According to Atomic Force Microscopy (AFM), there is a uniformly smooth surface across the 2-inch wafer. Across five mapped locations, 5  $\mu$ m x 5  $\mu$ m AFM images show an average rootmean-square roughness of 1.02 nm. We attribute this high level of uniformity to the enhanced gasinjection system, which uses separate injection zones for metalorganic precursors and oxygen. This configuration improves adatom diffusion prior to oxidation, reducing surface roughness and improving film quality.

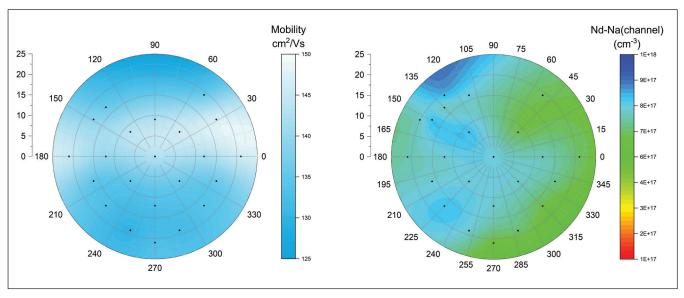

To assess the electrical properties of our films, one of our partners, Soctera Inc, fabricated Hall-effect pads and capacitors across the wafer. Measuring a

> Figure 2. Effect of susceptor rotation speed on film uniformity and growth rate.

total of 22 devices on our 2-inch sample determined an average electron mobility of 138.4 cm<sup>2</sup> V<sup>-1</sup>s<sup>-1</sup> and a mobility non-uniformity of 3.8 percent. The highest value recorded for electron mobility was 147 cm<sup>2</sup> V<sup>-1</sup>s<sup>-1</sup>. Average bulk electron concentration for the devices was  $4 \times 10^{17}$  cm<sup>-3</sup>. Capacitance-voltage measurements of the channel region indicate a higher electron concentration of  $7.3 \times 10^{17}$  cm<sup>-3</sup>, with an electron concentration non-uniformity of 8 percent. Using this reactor, a roughly 2  $\mu$ m-thick unintentionally doped (UID) Ga<sub>2</sub>O<sub>3</sub> film exhibited high electron mobility (around 179 cm<sup>2</sup> V<sup>-1</sup>s<sup>-1</sup> and low carrier concentration (9.9×10<sup>15</sup>cm<sup>-3</sup>). Further reduction of residual carrier concentration is possible through adjusting the oxygen-to-gallium ratio in the gas phase. These results demonstrate the reactor's capability to grow device-quality epitaxial films with excellent thickness and doping uniformity across a 2-inch wafer.

Through recent experiments, we have developed a process achieving  $2.5 \times 10^{20} \ cm^{-3}$  electron concentration and  $42 \ cm^2 \ V^1 \ s^{-1}$  electron mobility with RMS roughness values of less than  $0.5 \ nm$ . In the future, we plan to use this process as an ohmic regrowth for the source and drain terminals in the FETs to greatly improve our contact resistance.

Based on all these measurements of electrical characteristics, we conclude that our films are of excellent quality, with mobility values and electron concentrations that are promising for the future scalability of this growth technology. When larger native substrates become more readily available, this will unleash the promise of this growth method for large-scale device fabrication.

As highlighted in the preceding sections, the Agilis 700 equipped with the new gas-distribution flange has shown outstanding results in film material quality and uniformity. To access another aspect of film

➤ Figure 3. Two-dimensional atomic force microscopy (AFM) images taken from five locations on a roughly 300 nm-thick  $Ga_2O_3$  film grown on 2-inch Synoptic substrates using Bowtie Showerhead on the Agilis 700 reactor. The scan area is  $5 \times 5 \, \mu m^2$ .

growth, we began experimenting with the growth of gallium oxide alloys, specifically aluminum gallium oxide.

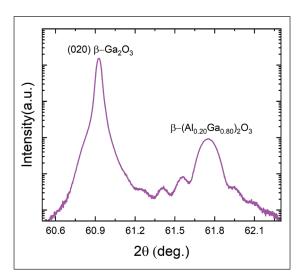

Using our standard growth conditions, as preciously described, we grew around 70-80 nm of (Al $_x$ Ga $_1$ .  $_x$ ) $_2$ O $_3$  with 100 nm of UID Ga $_2$ O $_3$  on 2-inch c-plane Sapphire and (010)  $\beta$ -Ga $_2$ O $_3$  substrate from Synoptics. For our metal-organic aluminum source, triethylaluminum (TEAI) was utilised for these experiments.

Figure 4. Hall mobility (left) and free electron concentration (right) maps for a 65 nm-thick FET channel grown on a roughly 200 nm-thick unintentionally doped  $Ga_2O_3$  layer on 2-inch Synoptic (010) β- $Ga_2O_3$  substrates.

Figure 5. X-ray diffraction ω-2θ scan profile for  $\beta$ -(Al<sub>n 20</sub>Ga<sub>n 80</sub>)<sub>2</sub>O<sub>3</sub>/Ga<sub>2</sub>O<sub>3</sub> grown on (010)  $\beta$ -Ga<sub>2</sub>O<sub>3</sub> Synoptics substrate using Agilis 700 with the improved gas-distribution flange. The thickness of the  $\beta$ -Al<sub>0.20</sub>Ga<sub>0.80</sub> layer is 70-80 nm.

The films exhibited an excellent thickness nonuniformity of 1.2 percent over a 2-inch wafer. Surface roughness remained low with an RMS roughness value of 0.8 nm over a 5 μmx 5 μm scan area assessed by AFM. The composition of the (Al Ga, ), O, was determined to be around 20 percent aluminium using X-ray diffraction and can be seen in Figure 5. The observation of Pendellösung fringes indicate a highly abrupt transition from  $\beta$ -Ga<sub>2</sub>O<sub>2</sub> to  $\beta$ -(Al<sub>y</sub>Ga<sub>1y</sub>)<sub>2</sub>O<sub>3</sub> and low surface roughness of both  $\beta$ -Ga<sub>2</sub>O<sub>3</sub> and  $\beta$ -(Al<sub>2</sub>Ga<sub>1,2</sub>)<sub>2</sub>O<sub>3</sub> layers. The success of uniform (Al<sub>x</sub>Ga<sub>1x</sub>)<sub>2</sub>O<sub>3</sub> growth expands the capabilities of (Al, Ga,,),O3/Ga,O3 heterostructures, enabling the development of epitaxial gate dielectrics and device structures such as HEMTs and MODFETs.

#### Advances in TMD growth

Building on our success in scaling ultra-wide bandgap materials, we have made significant progress in expanding scalable growth of two-dimensional (2D) materials, specifically TMDs, through MOCVD. These 2D materials, and particularly TMDs, are poised to revolutionise the electronics, optoelectronics, and quantum technologies.

The general formula for TMDs is MX<sub>2</sub>: M is a transition metal, such as molybdenum or tungsten; and X is a chalcogen, like sulfur, selenium, or tellurium. Unlike graphene, which lacks a bandgap, many TMDs possess sizeable and tuneable bandgaps, often transitioning from an indirect bandgap in the bulk to a direct one in monolayer form, making them ideal for semiconductor applications. Another strength of these materials is their layered structure, which enables mechanical exfoliation or chemical synthesis into monolayers, characteristics wellsuited to nanoscale devices and heterostructures.

Thanks to advances in large-area synthesis techniques for MOCVD, it's now possible to deposit wafer-scale TMD films with sizes of 4 inches and beyond, while ensuring precise control over composition and thickness - this is critical for scalable electronic and optoelectronic device integration. However, there's still work to do with MOCVD. Here, the key challenge is the temperaturedependent interplay between transition metal adatoms' low surface mobility and the chalcogen species' high desorption rate during film growth.

While high growth temperatures are needed to enhance the surface mobility of the metal and improve crystallinity over large areas, they also promote chalcogen desorption (loss), leading to vacancies and defects that compromise material quality.

Chalcogen vacancies also play a key role in determining the phase stability of TMD polymorphs. For instance, in MoTe<sub>2</sub>, the concentration of tellurium vacancies dictates whether the semiconducting 2H phase forms, or the metallic 1T' phase. These two phases are markedly different. The 2H phase features a hexagonal structure and exhibits a bandgap transition from indirect (around 0.8 eV in bulk) to direct (around 1.1 eV at the monolayer level), making it suitable for optoelectronic applications. Meanwhile, the 1T' phase has an orthorhombic structure and metallic conductivity, offering potential for quantum and topological devices. Due to these substantial differences, precise process control during MOCVD is essential for tailoring MoTe<sub>2</sub> and other TMD materials to specific applications.

Investing in the growth of TMDs by MOCVD makes much sense, because this technology is well suited to the growth of uniform films on large-area wafers. MOCVD offers tight control over critical parameters such as growth temperature and the chalcogen-to-transition metal flux ratio, which directly affect chalcogen vacancy concentrations and phase formation.

Over the past few years, we have been collaborating closely with Zakaria Y. Al Balushi's team at the University of California, Berkeley, to advance MOCVD growth of TMDs. As part of this effort, we have refurbished and upgraded a high-speed rotating disc MOCVD reactor and supported process development to enable wafer-scale growth.

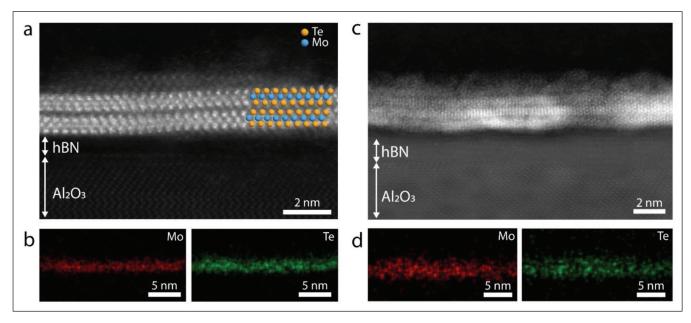

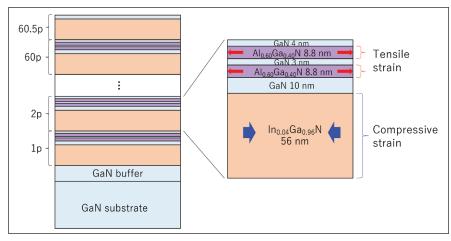

This partnership has provided new insight into how MOCVD growth conditions influence the uniformity and polymorph phase control of MoTe<sub>2</sub> on large-area wafers [4]. MoTe<sub>2</sub> films have been deposited using di-isopropyl telluride and molybdenum hexacarbonyl precursors, with hydrogen as the carrier gas. Growth has been conducted on 4-inch c-plane sapphire substrates, both bare and coated with ultra-flat hexagonal boron nitride (h-BN) layers, which were developed under the support of the AFRL through the SBIR direct to Phase II program. Nucleation

on bare sapphire has proved challenging, while h-BN/sapphire templates – grown by our team and provided to our partners at Berkeley – have enabled more uniform growth.

Note that we have extensive expertise in MOCVD growth of high-quality 2D h-BN on substrates up to 6 inches in diameter. These h-BN layers have a number of applications, which include serving as ideal templates for GaN or AlGaN/GaN HEMTs, and acting as sacrificial layers for transferring devices onto high-thermal-conductivity substrates, such as diamond [5].

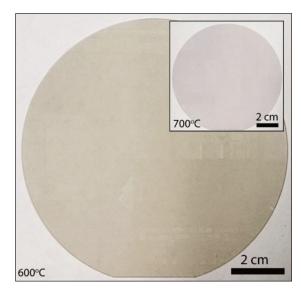

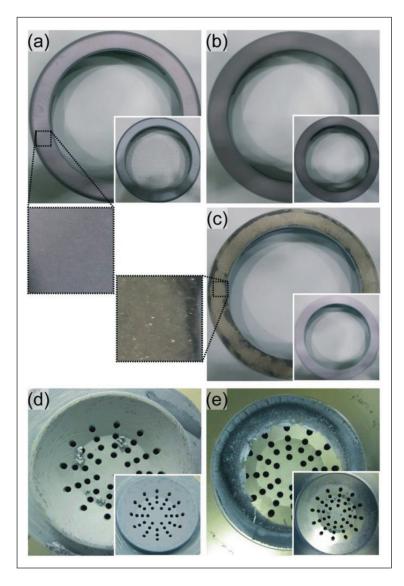

Our collaboration with the team at Berkeley has systematically investigated the effect of growth temperature on the optical properties of  $MoTe_2$  thin films, using controlled MOCVD experiments that involve the growth of  $MoTe_2$  on 4-inch h-BN/sapphire templates for 30 minutes. We have observed a distinct colour change with growth temperature, shifting from a darker brown at 600 °C (see Figure 6) to a pink hue at 700 °C (see Figure 6, inset), indicating changes in optical properties.

Greater insight into these films has been provided by cross-sectional scanning tunnelling electron microscopy. This technique reveals that  $MoTe_2$  films grown at  $600\,^{\circ}C$  exhibit well-crystallised bi- to tri-layers with a uniform molybdenum and tellurium distribution (see Figure 7 (a) and (b)). In contrast, growth at  $700\,^{\circ}C$  produces non-uniform 1T'-phase layers with poor contrast in transmission electron microscopy images and signs of oxidation (see Figure 7 (c) and 7 (d)), despite consistent elemental distribution. The most probable cause of this

➤ Figure 6. Images of the MOCVD-grown MoTe<sub>2</sub> on 4-inch h-BN/sapphire wafers at 600 °C and at 700 °C (inset).

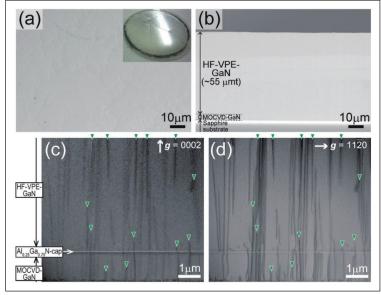

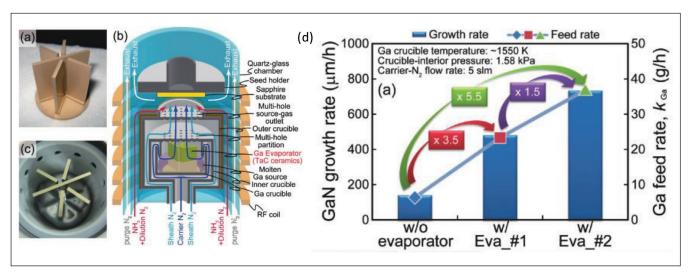

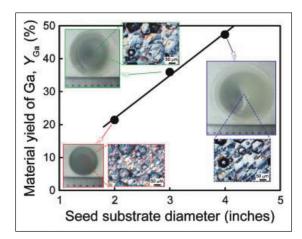

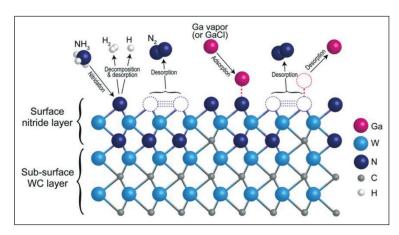

degradation is the greater chemical reactivity and instability of the 1T' phase.