# COMPOUND SEMICONDUCTOR

CONNECTING THE COMPOUND SEMICONDUCTOR COMMUNITY

VOLUME 29 ISSUE V 2023

COMPOUNDSEMICONDUCTOR.NET

### **INSIDE**

News, Analysis, Features, Editorial View, Research Review and much more

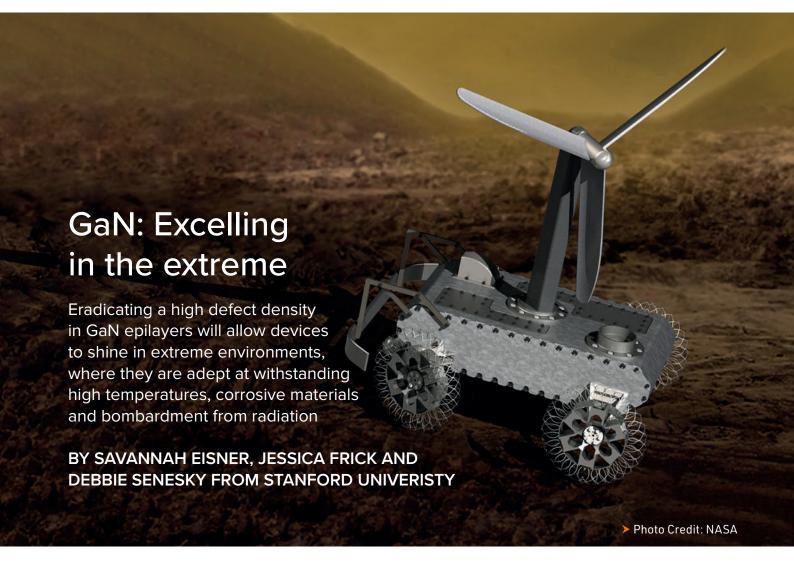

# GaN: Excelling in the extreme

Eradicating a high defect density in GaN epilayers will allow devices to shine in extreme environments

# Revolutionising GaN-on-silicon RF

GaN-on-silicon HEMTs have a great opportunity to serve in mobile applications requiring high-power millimetre waves

# New opportunities for deep-UV LEDs

Higher powers and efficiencies, alongside longer lifetimes, are driving interest in the deep-UV LED within the healthcare sector

### What's Your Next Big Thing?

- Micro LED Displays

- Autonomous Driving / 3D Sensing

- Communication Infrastructure

- Solar Cells

**...**

# G10-AsP

The Enabling MOCVD Solution

# Fully Automated MOCVD for High Volume Production of GaAs/InP Based Materials

# **VIEWPOINT**

By Richard Stevenson, Editor

## Covid's legacies?

WHAT WILL BE the lasting legacies of Covid? Surely one of them is a shift to working from home, at least some of the time. And without the grind of the daily commute, alongside diminished social interaction during the working day, you might think that this new regime could also lead to greater participation in community activities. But my anecdotal evidence suggests otherwise. Maybe more of us are simply more used to being at home more often.

During the height of the pandemic deep-UV LEDs drew much attention, offering an elegant solution to incapacitating the virus. Market analysts predicted a surge in sales for the device, suggesting that this would be a pivotal moment in the history of this deep-UV emitter.

But while heightened interest in the deep-UV LED has been great for raising its profile, the success of the vaccination programme has dealt a blow to any long-term hike in sales in the air disinfection market. Today, when companies are trying to eke out a profit against the backdrop of rising costs and strong wage demands, there's little appetite for equipping offices with units that use deep-UV LEDs to ensure healthy air.

Yet despite the collapse of this market, there's still much good news to celebrate in the deep-UV LED sector. Take AquiSense, a provider of water treatment systems based on this solid-state source. This company's revenue is continuing to rise at great pace; it has identified many, many opportunities to vastly increase sales; and it is seeing substantial improvement at the chip level that will help to ensure further success (to discover more about the prospects for AquiSense, and its views on the progress of makers of deep-UV LEDs, take a look at "Busting market myths" on p. 16).

Another impact of the pandemic was a shift in many conferences from in-person to on-line. However, while an online conference is better than nothing, there's no substitute for getting a community together, hearing developments from around the world, and discussing the most significant breakthroughs with others over lunches, dinners and coffee breaks.

Like many sectors within the compound semiconductor community, those working on deep-UV LEDs are now getting back to in-person meetings. This April, more than 220 of them gathered in Berlin for the third meeting of ICULTA – that's the International Conference on UV Light-emitting Technologies and Applications.

Included in this issue is a report on ICULTA from a member of its technical committee, Michael Kneissl from TU Berlin (see p. 32). One of his lasting impressions from that meeting, which reflects the observation from AquiSense, is that the performance of the deep-UV LED is rising fast. For example, at ICULTA ams Osram revealed that its third-generation of deep-UV LEDs are producing up to 200 mW at a wall-plug efficiency of 10 percent.

One can speculate that a contributing factor behind these impressive performance figures is a hike in investment in this device during the pandemic. But we don't know for sure. While some legacies from Covid are clear, others will be harder to identify.

Free weekly e-news roundup go to: compoundsemiconductor.net

# 24 Evaluating the pros and cons of power GaN

Switching to a vertical architecture addresses concerns associated with on-resistance and capacitance, but the choice of substrate involves compromise.

# 32 Expanding horizons for deep-UV

Tremendous progress is underway with the deep-UV LED, in terms of its use in healthcare and it gains in output power, efficiency and lifetime, in both the UVC and far UVC.

# 38 MBE: A game changer for GaN-on-silicon RF

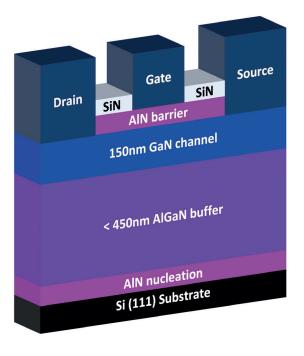

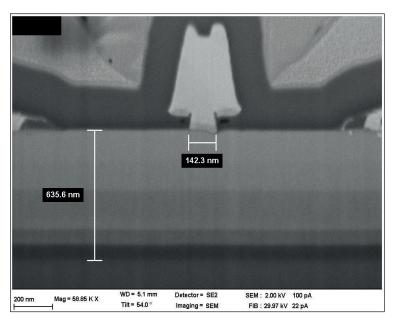

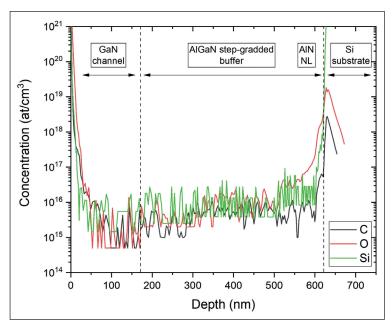

On the back of remarkable results at 40 GHz, GaN-onsilicon HEMTs have a tremendous opportunity to serve in mobile applications requiring high-power millimetre waves.

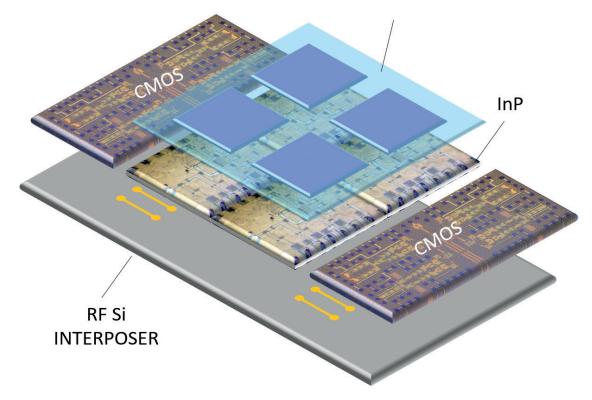

# 46 Scaling III-V technologies for 5G and 6G

Upscaling GaN HEMTs and InP HBTs to a silicon platform and in co-integrating them with CMOS components fulfils the requirements for next-generation high-capacity wireless communication.

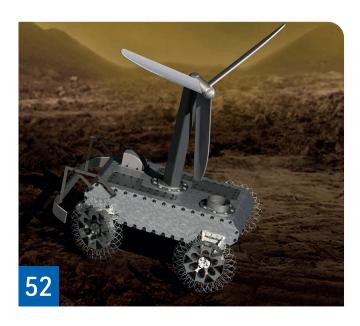

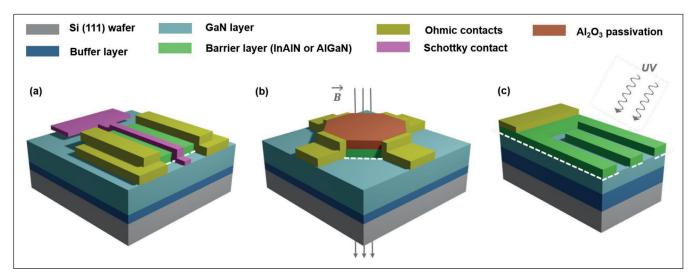

### 52 GaN: Excelling in the extreme

Eradicating a high defect density in GaN epilayers will allow devices to shine in extreme environments, where they are adept at withstanding high temperatures, corrosive materials and bombardment from radiation.

### **NEWS ANALYSIS**

### 16 Deep UV LEDs: Busting market myths

While the pandemic has propelled interest in the deep UV LED, it is water treatment that remains the long-term revenue driver for this device

### 18 A new home for the Institute for Compound **Semiconductors**

Nobel-prize-winning climate scientist Donald Wuebbles opens Cardiff University's Translational Research Hub, a new home for the Institute for Compound Semiconductors

### RESEARCH REVIEW

- 58 Refining GaN substrate thinning

- 60 Advancing the InGaAs MOSFET

- Improving the RF performance of β-Ga<sub>2</sub>O<sub>3</sub> MOSFETs

### **NEWS**

- 06 EPC embarks on a patent war with Innoscience

- 07 Setting new standards for **MBF**

- 08 ST and Sanan advance SiC ecosystem in China

- 10 Ams Osram adds eye safety feature to IR VCSEL

- 11 Vitesco and Onsemi sign long-term SiC agreement

- 12 Nexperia adds e-mode GaN FETs

- 13 Mitsubishi and Coherent sign SiC agreement

- 14 UK Space Agency funds SiC chip project

- 15 Chinese team defines fast charging law

**Editor** Richard Stevenson richardstevenson@angelbc.com +44 (0)1291 629640

News Editor Christine Evans-Pughe christine.evans-pughe@angelbc.com

Design & Production Manager Mitch Gaynor mitch.gaynor@angelbc.com

+44 (0)1923 690214

**Director of Logistics** Sharon Cowley sharon.cowley@angelbc.com

+44 (0)1923 690200

Senior Sales Executive Jacob Caulfield

iacob.caulfield@angelbc.com +44 (0)2476 718979

Circulation

scott.adams@angelbc.com

Publisher Jackie Cannon jackie.cannon@angelbc.com +44 (0)1923 690205

**USA Representatives** Brun Media

Janice Jenkins iienkins@brunmedia.com +1 724-929-3550

Tom Brun

tbrun@brunmedia.com +1724539-2404

Chief Executive Officer Sukhi Bhadal

sukhi.bhadal@angelbc.com +44 (0)2476 718970

Chief Technical Officer

Scott Adams scott.adams@angelbc.com +44 (0)2476 718970

Directors

Jackie Cannon, Sharon Cowley

Published by

Angel Business Communications Ltd 6 Bow Court, Fletchworth Gate Burnsall Road, Coventry CV5 6SP, UK. T: +44 (0)2476 718 970 E: info@angelbc.com

Compound Semiconductor is published nine times a year on a controlled circulation basis. Non-qualifying individuals can subscribe at: £105.00 per annum (UK), €158 per annum (Europe), \$198 per annum (air mail) (USA). Cover price £4.50. All information herein is believed to be correct at time of going to press. The publisher does not accept responsibility for any errors and omissions. The views expressed in this publication are not necessarily those of the publisher. Every effort has been made to obtain copyright permission for the material contained in this publication. Angel Business Communications Ltd © Copyright 2023. All rights reserved. Contents may not be reproduced in whole or part without the written consent of the publishers. The paper used within this magazine is produced by chain of custody certified manufacturers, guaranteeing sustainable sourcing. US mailing information: Compound Semiconductor, ISSN 1096-598X, is published 9 times a year, Jan/Feb, March, April/May, June, July, August/September, October, November, December by Angel Business Communications Ltd, Unit 6, Bow Court, Fletchworth Gate, Burnsall Rd, Coventry CV5 659. UK.Airfreight and mailing in the USA by agent named World Container INC 150-15, 183rd St, Jamaica, NY 11413, USA. Periodicals Postage Paid at Brooklyn, NY 11256. POSTMASTER: Send address changes to Compound Semiconductor, Air Business Ltd, c/o World Container INC 150-15, 183rd St, Jamaica, NY 11413, USA. We strive for accuracy in all we publish; readers and contributors are encouraged to contact us if they recognise an error or omission. Once magazine edition is published [online, in print or both], wed not update previously published articles to align old company names, branding, marketing efforts, taglines, mission statements or other promotional verbiage, images, or logos to newly created or updated names, images, typographic renderings, logos (or similar) when such references/images were accurately stated, rendered or displayed at the time of the original publication. When

### EPC embarks on a patent war with Innoscience

EPC takes Innoscience to court over four patents covering the design and manufacture of enhancement-mode GaN power semiconductor devices

A BATTLE of intellectual property has broken out, with US-based GaN specialist Efficient Power Conversion taking Chinese GaN firm Innoscience to court over four patents related to enhancement-mode GaN power semiconductor devices.

Innoscience has responded to the charges, arguing that after it undertook a thorough analysis, it found no infringement of EPC's intellectual property rights.

EPC has filed complaints in federal court and in the US International Trade Commission (ITC), asserting four patents of its foundational patent portfolio against Innoscience (Zhuhai) Technology Company, Ltd. and its affiliates (collectively, Innoscience).

These patents are said to cover core aspects of the design and manufacturing process of EPC's proprietary enhancement-mode GaN power semiconductor devices. According to EPC, these patents encompass innovations that enabled the company's GaN-based power devices to mature from a research project to a mass-producible high-volume alternative to silicon-based transistors and ICs with GaN devices having higher efficiency, smaller size, and lower cost.

EPC began making the first mass-produced commercial GaN transistors and integrated circuits in 2010. It claims that Innoscience recruited two EPC employees to serve as its CTO and head of sales and marketing. Shortly thereafter, Innoscience is said to have introduced a suite of products visibly identical to EPC's, boasting virtually equal performance across key performance metrics. More recently, Innoscience has claimed that many of its products have 'pin-to-pin compatibility with existing products' including EPC's products, in a bold and

aggressive campaign to market its suite of products to EPC's customers.

"I have always been a believer in fair cooperation as the foundation of global technology markets," said Alex Lidow, EPC's co-founder and CEO. "Only through cooperation can we unlock the potential of GaN technology and meet the world's energy security and sustainability goals. Strong protections and respect for intellectual property are essential to that trust and cooperation."

"I am confident that, through these decisive actions, we will reach a fair and reasonable resolution that levels the playing field and ensures a GaN ecosystem that works for all participants in this critical emerging technology," Lidow added

EPC has sued Innoscience in federal court and the ITC for patent infringement, seeking damages and barring Innoscience from importing its infringing suite of GaN products into the US.

In a robust defence of its position, Innoscience has responded to EPC's filing of a patent lawsuit, with intentions to "take all legal measures to counterattack".

Innoscience says that since its establishment, it has filed 753 relevant patents globally, with 129 patents granted. It claims that the allegations of technology plagiarism, based on the job changes of a few employees, are purely speculative and lack factual basis.

The Chinese chipmakers also argues that EPC has a significant disparity in terms of business scale, scope of operations, and technological strength. It points out that it is an Integrated Device Manufacturer with its core competence lying in the full vertical integration of the semiconductor industry, including chip manufacturing.

The company adds that it is globally recognised for its pioneering 8-inch GaN mass manufacturing process. Innoscience dismisses EPC as a fabless design company, with product designs primarily relying on a 6-inch foundry process platform. The Chinese firm belittles EPC for not possessing its own wafer fabrication facilities or corresponding manufacturing processes.

# Setting new standards for MBE

Riber and IntelliEPI qualify the largest MBE system for mass production of III-V compound semiconductors

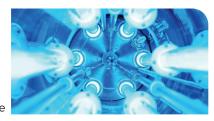

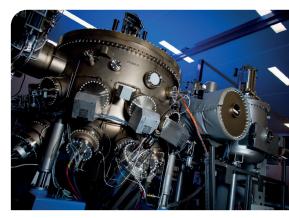

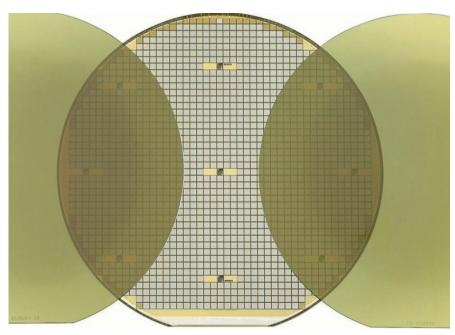

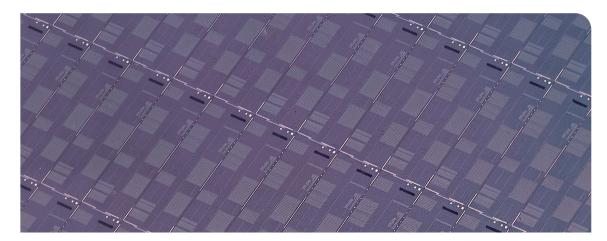

EPITAXY EQUIPMENT manufacturer Riber has announced a major milestones in a joint development program with IntelliEPI for the qualification of the new MBE 8000 production platform.

Riber's new flagship product, the MBE 8000, is believed to be the highest capacity MBE production tool available on the market, able to handle batches of eight 150 mm (6 inch) or four 200 mm (8 inch) wafers. The design of this machine benefits from over 20 years' experience in production MBE systems.

Following the delivery of the first MBE 8000 platform and after qualification work carried out in close cooperation with IntelliEPI, Riber says that the results obtained have exceeded expectations, particularly in terms of uniformities, defect densities, increasing yield, and interface abruptness, which is key for superlattice structures to achieve high performance lasers.

These performance figures combined with a high level of run-to-run repeatability control in large-scale production will enable a new generation

of lasers, according to the company, in particular for VCSEL technology with significant market opportunities in the field of smartphone under-display facial recognition.

In addition to the VCSEL market, the precise control of the doping uniformity and the process stability offered by the MBE 8000 platform will enhance microelectronic device performances, such as conductivity.

Over the past few months, as results were disclosed to several industrial customers, interest for this machine has grown quickly, leading to discussions for potential purchase, says Riber.

According to Yung-Chung Kao, IntelliEPI president and CEO: "From the initial evaluation so far, this Riber MBE 8000 has shown very impressive performance in terms of being able to produce high quality epi materials over such a large substrate platen area with excellent composition and thickness uniformity across the 8x6 inch platen. With this improvement, the MBE 8000 platform offers a solution to make large-scale production MBE technology

more competitive especially for high performance and high throughput market opportunities."

Christian Dupont, Riber's CEO: "Thanks to the efforts of Riber and IntelliEPI teams, we have reached a major step for MBE 8000 qualification. The results provided by the machine exceed our initial objectives. With an optimum cost-of-ownership and large capacity, the MBE 8000 equipment has strong commercial prospects. In addition, our milestone in this joint development program with IntelliEPI demonstrates the capability to bring MBE technology in high volume semiconductor industry."

# **Advanced Compound Semiconductor** Foundry Services

MOCVD · Fabrication · Testing

Advanced III-V semiconductor solutions for optoelectronics application in the biotechnology, telecommunications, energy, industrial, and security industries.

MasimoSemiconductor.com | 603-595-8900

# ST and Sanan advance SiC ecosystem in China

Companies to create a joint venture for high-volume 200 mm SiC device manufacturing

**EUROPEAN SEMICONDUCTOR** giant STMicroelectronics and Sanan Optoelectronics, a Chinese compound semiconductor company, have signed an agreement to create a new 200 mm SiC device manufacturing joint venture in Chongqing, China.

The new SiC fab is targeting to start production in Q4 2025 and full buildout is anticipated in 2028, supporting the rising demand in China for car electrification as well as for industrial power and energy applications. In parallel, Sanan Optoelectronics will build and operate separately a new 200 mm SiC substrate manufacturing facility to fulfil the joint venture's needs, using its own SiC substrate process.

The joint venture will make SiC devices exclusively for STMicroelectronics, using ST proprietary SiC manufacturing process technology, and serve as a dedicated foundry to ST to support the demand of its Chinese customers.

The total amount for the full buildout of the joint venture is expected to be about \$3.2 billion, including capital expenditures of about \$2.4 billion over the next 5 years, which will be financed by contributions from STMicroelectronics and Sanan Optoelectronics, local government support, and loans to the joint venture.

"China is moving fast towards electrification in automotive and industrial and this is a market where ST is already well-established with many engaged customer programmes. Creating a dedicated foundry with a key local partner is the most efficient way to serve the rising demand of our Chinese customers. The combination of Sanan Optoelectronics' future 200 mm substrate manufacturing facility with the front-end joint venture and ST's existing back-end facility in

Shenzhen, China, will enable ST to offer our Chinese customers a fully vertically integrated SiC value chain," said Jean-Marc Chery, president and CEO of STMicroelectronics.

"It is an important step to further scale up our global SiC manufacturing operations, coming in addition to our continuing significant investments in Italy and Singapore. This joint venture is expected to be one of the enablers of the opportunity we see to reach more than \$5 billion of SiC revenues by 2030. This initiative is consistent with ST 2025-27 \$20 billion plus revenue ambition and the associated financial model, previously communicated to the financial markets."

"The establishment of this joint venture will be a major driving force for the wide adoption of SiC devices on the Chinese market," said Simon Lin, CEO of Sanan Optoelectronics. "Being an international, well-known, high-quality SiC foundry service company, Sanan will also supply its SiC substrate to this new joint venture, by building a dedicated new SiC substrate factory. This is an important step for Sanan Optoelectronics' ambitions as a SiC foundry. With this new Joint Venture and the new SiC substrate capacity expansion, we are confident that we will continue to take the lead in

The completion of the project is subject to regulatory approvals.

the SiC foundry market."

# **Enabling Process Control Solutions** for **Compound Semiconductor** Manufacturing

### **ECHO**™ SYSTEM

Onto Innovation achieves in-line thickness measurements of single or multi-layered metal films up to 35 microns with its patented PULSE™ technology. The time resolved, non-destructive measurements provided by the Echo system enable critical metallization process control at production-worthy throughputs.

ontoinnovation.com

# FUSION AND HYBRID BONDING FOR HETEROGENEOUS INTEGRATION

1

- Enabling advanced 3D device stacking and chiplet integration for CMOS image sensors, memory and 3D system-on-chip (SoC)

- High-volume production equipment and process technology for Wafer-to-Wafer (W2W) and Die-to-Wafer (D2W) hybrid bonding

- GEMINI® FB Automated Production Wafer Bonding System delivers industry leading alignment accuracy and bonding performance

- Heterogeneous Integration Competence Center™ serving as leadingedge innovation incubator for EVG customers and partners

**GET IN TOUCH** to discuss your manufacturing needs **www.EVGroup.com**

# Ams Osram adds eye safety feature to IR VCSEL

Emitter for in-cabin sensing includes interlock loop method for safeguarding ultra-fast detection of faults

AMS OSRAM has enhanced its portfolio of infrared laser modules for automotive in-cabin sensing with the TARA2000-AUT-SAFE VCSEL family, which offers a more reliable and robust eye safety feature than existing automotive VCSEL modules.

A top-ten global car manufacturer has already selected this new product for a new design, and Ams Osram will supply it in mass production volumes starting in 2024.

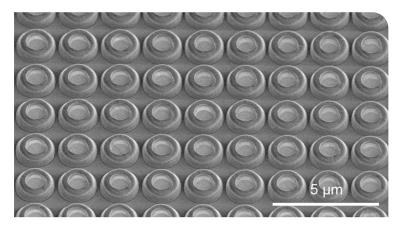

The new TARA2000-AUT-SAFE, which produces a tightly controlled beam of IR light at a peak wavelength of 940 nm, is suitable for the same use cases as the existing TARA2000-AUT family: driver monitoring, gesture sensing, and interior (cabin) monitoring. It consists of an Ams Osram VCSEL chip and micro-lens array (MLA) packaged in a compact module.

The new VCSEL, which has a wide field of illumination of 116 ° x 87 °, is optimised for cabin monitoring with 2D near infrared imaging and 3D indirect time-of-flight cameras.

A forthcoming version with a narrow field of illumination of 46° x 41°, the TARA2000-940-UN-AUT-SAFE, is suitable for driver monitoring. It is currently sampling with customers.

The TARA2000-AUT-SAFE family is said to offer increased reliability and simpler implementation for automotive manufacturers, due to the new, built-in interlock loop method for protecting eye safety.

The new device's resistive interlock circuitry is integrated on the MLA. Providing a near-instant response of less than 1  $\mu$ s to fault conditions, the TARA2000-AUT-SAFE can directly detect faults that could compromise eye safety, such as diffuser cracking or shear-off. The TARA2000-AUT-SAFE solves various design and

implementation challenges, and at a lower cost than competing products on the market today. The fast and reliable response is in contrast to the built-in photodiode method for eye safety protection in competing automotive VCSELs. In competing products, the photodiode signal is prone to faults caused by non-eye-safety related factors such as reflective objects in front of the VCSEL module, impairing the system's ability to protect eye safety.

In addition, the interlock loop is said to be easier to integrate, as its readout circuit only requires one AND gate or MOSFET. In comparison, the complex read-out circuit of photodiode includes an increased number of more expensive components. This means that the photodiode method results in a higher bill-of-materials cost, as well as a slower response to events that carry a risk to eye safety.

Firat Sarialtun, senior global marketing manager at Ams Osram, said: "We have been able to take our experience in other application areas and directly apply it to enhancing the TARA2000 family. Ams Osram has deep knowledge of interlock-based eye-safety designs, as we have had products that use the

interlock method in mass production in other end markets, such as consumer and industrial, for many years."

Sarialtun added: "We were the first in the industry to start mass production of an AEC-Q102 and ISO26262 compliant IR VCSEL module for in-cabin sensing in Q2-2021, and now we are taking VCSEL technology a step further with the interlook loop feature. Thanks to our deep engineering expertise across the whole optical assembly, the interlock circuit has been integrated directly on the lens and package, drawing on our deep understanding of each sub-component and technology in a complete VCSEL module."

The design of the TARA2000-AUT-SAFE builds on the high performance of the TARA2000-AUT. Housed in a robust ceramic package, the new device offers a maximum operating temperature of 125°C, supporting AEC-Q102 Grade 1 qualification as well as ISO 26262 for functional safety. Peak optical power output of a 100 µs pulse at 25°C/2 percent duty-cycle/5 A is 4 W.

The TARA2000-940-UN-AUT-SAFE and TARA2000-940-W-AUT-SAFE VCSEL emitters are sampling now.

# Vitesco and Onsemi sign long-term SiC agreement

Vitesco Technologies is securing SiC supply capacity worth \$1.9 billion

VITESCO TECHNOLOGIES and Onsemi have announced a 10-year long-term supply agreement worth \$1.9 billion for SiC products to enable Vitesco's ramp in electrification technologies.

Vitesco, an international manufacturer of drive technologies and electrification solutions, is providing an investment of \$250 million to Onsemi for new equipment for SiC boule growth, wafer production and epitaxy to secure access to SiC capacity.

The equipment will be used to produce SiC wafers to support Vitesco's growing SiC demand.

In parallel, Onsemi, a leader in intelligent power and sensing technologies, will continue to invest substantially into the end-to-end SiC supply chain.

In addition, Vitesco and Onsemi will collaborate on optimised customer solutions for Vitesco. Onsemi's highly

efficient EliteSiC MOSFETs will be used by Vitesco to execute the recent orders as well as future projects for traction inverters and electric vehicle drives.

"Energy-efficient silicon carbide power semiconductors are at the beginning of a big surge in demand. That is why it is imperative for us to get access to the complete SiC value chain together with Onsemi. With this investment we have a secure supply of a key technology over the next ten years and beyond," said Andreas Wolf, CEO of Vitesco.

Hassane El-Khoury, president and CEO of Onsemi, commented: "This collaboration will enable Vitesco to address their customers' demand for longer range and higher performance in electric vehicles. Onsemi provides superior performance and quality, supply assurance, and manufacturing at scale of SiC technologies based on decades of experience in manufacturing power semiconductor products in highvolume automotive applications."

### Nuburu and **GE** Additive collaborate on 3D printing

INDUSTRIAL BLUE laser firm Nuburu has signed a joint technology agreement with GE Additive, to explore the speed, accuracy, and commercial benefits of blue laser-based metal 3D

"As we continue to advance our proprietary blue laser technology, we have further increased both power and brightness to open up new applications," said Mark Zediker, CEO and co-founder of

"We've achieved key performance milestones that open new possibilities for significant advances in metal 3D printing. Working with GE Additive, and their expertise in metal additive manufacturing, will allow us to rapidly optimise our innovative area printing approach. That will accelerate the further expansion of our pioneering blue laser into innovative metal 3D printing solutions, which have the potential to change the landscape of military logistics; aerospace manufacturing; medical device fabrication, and beyond."

"As an industry leader in metal 3D printing and having been on the leading edge of qualifying parts in regulated industries, we're excited to evaluate Nuburu blue industrial laser technology and its benefits," said Chris Schuppe, general manager of engineering and technology of GE Additive.

This joint development agreement is in addition to an agreement with GE Additive to support Nuburu's previously announced AFWERX Small Business Innovation Research (SBIR) Phase II contract awarded to Nuburu in 2022.

### Nexperia adds e-mode GaN FETs

Company to offer both cascode and e-mode GaN FETs for low and high voltage use

NEXPERIA has released its first power GaN FETs in e-mode (enhancement mode) configuration for low (100/150 V) and high (650 V) voltage applications.

By augmenting its cascode offering with seven new e-mode devices, Nexperia says it provides designers with the optimum choice of GaN FETs from a single supplier alongside its portfolio of silicon-based power electronics components.

Nexperia's new portfolio includes five 650 V rated e-mode GaN FETs (with  $R_{DS(on)}$  values between 80 m $\Omega$ and 190 m $\Omega$ ) in a choice of DFN 5 mm x 6 mm and DFN 8 mm x 8 mm packages.

They improve power conversion efficiency in high-voltage, low-power datacom/telecom, consumer charging, solar and industrial applications.

They can also be used to design brushless DC motors and micro server drives for precision with higher torque and more power.

Nexperia now also offers a 100 V  $(3.2 \text{ m}\Omega)$  GaN FET in a WLCSP8 package and a 150 V (7 m $\Omega$ ) device in a FCLGA package.

These devices are suitable for various low-voltage, high-power applications to deliver, for example, more efficient DC-DC converters in data centers, faster charging (e-mobility and USB-C), smaller lidar transceivers, lower noise class D

audio amplifiers and more power dense consumer devices like mobile phones, laptops, and games consoles. GaN devices are increasingly entering mainstream power electronics markets, including server computing, industrial automation, consumer, and telecom infrastructure, thanks to their fast transition / switching capability (high dV/dt and dI/dt) and efficiency in lowand high-power conversion applications.

### Q-Pixel beats world record for pixels per inch

Q-PIXEL INC, a Los-Angeles based startup, has announced the world's first full-colour, ultra-high resolution microLED display.

Using its GaN-based Polychromatic microLED technology, Q-Pixel says it has achieved a full-colour LED display with a pixel density of 5,000 pixels per inch (PPI), surpassing the current world record of 2,000 PPI held by ITRI of Taiwan.

Q-Pixel believes the technology is a game-changer for the display industry by allowing full-colour tunability across a single 4-µm pixel. It says this approach can replace single-colour LEDs and addresses several challenges

to the microdisplay industry, including the need for pick-and-place, while at

the same time enabling ultra-high pixel density.

# Mitsubishi and Coherent sign SiC agreement

Companies to scale manufacturing of SiC power electronics on a 200 mm technology platform

MATERIALS and laser company Coherent Corp and Mitsubishi Electric have signed a memorandum of understanding (MoU) to collaborate on a programme to scale manufacturing of SiC power electronics on a 200 mm technology platform.

To meet the rapidly growing demand for SiC chips, in particular for electric vehicles, Mitsubishi Electric announced an investment of approximately \$1.8 billion in the five-year period ending March 2026. A major portion of the investment, approximately \$71 million, will be used to construct a new plant for SiC power devices, based on a 200 mm technology platform, and enhance related production facilities. Under the MoU, Coherent will develop a supply of 200 mm *n*-type 4H SiC substrates for Mitsubishi Electric's future SiC power devices manufactured at the new facility.

"We are excited to build on our relationship with Mitsubishi Electric, a pioneer in SiC power devices and a global market leader in SiC power modules for high-speed trains, including the famous Shinkansen in Japan," said Sohail Khan, executive VP of New Ventures & Wide-Bandgap Electronics Technologies at Coherent. "We have a long track record of supplying SiC substrates to Mitsubishi Electric and are looking forward to expanding our relationship with them to scale their new 200 mm SiC platform."

"Coherent has been for many years a reliable supplier of high-quality 150 mm SiC wafer substrates to Mitsubishi Electric," said Masayoshi Takemi, executive officer, group president, Semiconductor & Device at Mitsubishi Electric. "We are delighted to enter into this close partnership with Coherent to scale our respective SiC manufacturing platforms to 200 mm."

Coherent demonstrated the world's first 200 mm conductive substrates in 2015.

In 2019, Coherent began to supply 200 mm SiC substrates under REACTION, a Horizon 2020 four-year programme funded by the European Commission. Mitsubishi Electric made history by launching the world's first SiC power modules for air conditioners in 2010, and became the first supplier of a full SiC power module for Shinkansen high-speed trains in 2015.

### UK Space Agency funds SiC chip project

IceMOS to develop radiation-tolerant high-voltage superjunction SiC MOSFETs

THE UK SPACE AGENCY has awarded IceMOS Technology part of £300,000 funding in a project to develop SiC power transistors for space applications. This is in partnership with the UK space and defence trade association ADS, through the Space Technology Exploitation Programme (STEP).

The IceMOS Technology manufacturing centre of excellence located in Belfast, Northern Ireland, will focus on delivering an advanced engineered substrate, enabling a radiation-tolerant, high-voltage SiC engineered drain MOSFET for more efficient high power distribution electrical systems on spacecraft for low earth orbit, middle earth orbit and deep space exploration.

The company says the merger of a wide bandgap power MOSFET drain structure that can be tailored to be robust in harsh space radiation environments will create a new class of vertical power transistor.

Commercial applications aim to address society's increasing demand for energy conservation in systems such as Al-enabled cloud services and data centres, fast-charging stations for electric vehicles, photovoltaic energy generation and more.

"With this award IceMOS Technology is uniquely positioned to accelerate advances in the UK-space programme by making dramatic improvements in high-voltage power radiation-tolerant transistors," said Samuel Anderson, IceMOS Technology founder and

Anderson added: "It is an honour to be one of only three companies selected to participate in this prestigious programme to enhance UK space capability by developing this leadingedge technology that can lower costs

and significantly improve overall systems performance."

"Creative talent and technical space expertise can be found across the length and breadth of the UK," said Paul Bate, chief executive at the UK Space Agency.

Bate believes that these projects. delivered in partnership with ADS, are brilliant examples of that from Northern Ireland's growing space sector. "They will help catalyse investment, create jobs, and develop new capabilities within the space supply chain."

### Chinese team defines fast charging law

'Lichi Law' shows commercial GaN fast charging increases by 60 percent every 9 to 12 months

RESEARCHERS from South China Normal University, Red and Blue Microelectronics, Shenzhen Baseus Technology, Zhejiang University, and Shenzhen University have conducted research on GaN fast charging in the market in the past five years and found a regular trend made up of three elements.

First, the output power of commercial GaN fast charging increases by 60 percent every 9 to 12 months.

Second, the output power density of commercial GaN fast charging increases by 30 percent every 6 to 9 months.

And third, the output power density of commercial GaN fast charging increases by 50 percent every 20 to 24 months.

They are calling it 'Lichi Law' because the researchers gathered under a lychee tree on the Shenzhen University campus to discuss these developments.

In 2019, the technology of GaN fast-charging products was immature, resulting in a general fast charging power of only 20-30 W in the market, with a relatively large volume. This led to a power density of GaN fast charging generally being below 1 W/cm<sup>3</sup>.

However, by 2021, market technology had matured, and the characteristics of GaN devices were successfully used to reduce the volume of fast charging, resulting in a power density of GaN fast-charging products on the market generally exceeding 1 W/cm<sup>3</sup>.

This sparked fierce competition among major brands in the research and development of GaN fast charging. In 2023, Realme released a 240 W GaN fast charging product that was only 102 cm³ in size. This achievement successfully pushed the power density of GaN fast charging to reach 2.36 W/cm³, making it the highest power density in the market for GaN fast charging.

In terms of quality, Anker unveiled the market's first 30 W GaN fast charger in 2018, with a mass of 54 g and a power density of only 0.53 W/g.

As GaN fast-charging technology developed in 2022, OPPO released the first GaN fast charging product to break through 200 W. Weighing only 147 g, the OPPO 200 W charger achieved a power density of 1.36 W/g, making it the first brand in the market to exceed 1 W/g. Currently, the Realme 240 W released in 2023 boasts the fastest charging output power in the market, weighing only 166 g and achieving a power density of 1.44 W/g.

In October 2018, ANKER released the PowerPort Atom PD1, the world's first USB PD GaN charger, in New York, marking the official entry of GaN technology into the consumer market. In August 2020, Xiaomi released the Mi 10 with its accompanying 120 W GaN fast charger, making it the first mobile phone GaN charger to achieve an output power exceeding 100 W, and marking domestic manufacturers' success in the field of GaN fast charging.

In July 2022, iQOO released the iQOO 10 series of mobile phones, announcing that the fast charging technology of their mobile phones exceeded 200 W and releasing a 200 W GaN fast-charging charger, making them the first mobile phone manufacturer to achieve fast-charging power exceeding 200 W. In January 2023, Realme launched the GT Neo5 mobile phone at the MWC conference with 240 W GaN fast charging, achieving a power density of 2.36 W/cm³ and 1.45 W/g, leading the industry in terms of technical advancements.

According to product 3C report statistics, there has been significant growth in product power density over the past five years. In 2018, Anker

released the first GaN fast charger with a power density advantage of 0.56 W/cm<sup>3</sup>. In 2022, iQOO launched a 200 W charger, achieving a power density exceeding 2 W/cm<sup>3</sup>, reaching 2.01 W/cm<sup>3</sup>.

In October 2018, Anker released the first GaN fast charger with a low weight achieving a power density of 0.54 W/g. Four years later, in July 2022, iQOO launched a 200 W charger achieving a power density exceeding 1 W/g, reaching 1.36 W/g.

#### GaN fast charging data

The researchers say that the following three points show the key data. The interval between the launch of Anker's 30 W GaN fast charger in October 2018 and Xiaomi's 120 W GaN fast charger in August 2020 was 22 months. Subsequently, iQOO launched a 200 W GaN fast charger in July 2022, with an interval of 21 months.

Starting in October 2018, Anker released the first GaN fast charger with a power density of 0.56 W/cm³, due to its size advantage. In October 2019, OPPO released their 65 W GaN fast charger, achieving a power density exceeding 1 W/cm³, reaching 1.01 W/cm³, with a 12-month interval between the two. Then, in July 2022, iQOO launched their 200 W GaN fast charger, achieving a power density exceeding 2 W/cm³, reaching 2.01 W/cm³, also with a 12-month interval. Overall, there was a 33-month gap between the first and last releases.

Anker released the first 30 W GaN fast charger with a power density of 0.54 W/g in October 2018, and in July 2022, iQOO released a 200 W GaN fast charger, achieving a power density exceeding 1 W/g. Over the span of 45 months, the power density increased to 1.36 W/g. In January 2023, Realme released a 240 W GaN fast charger with a power density of 1.44 W/g.

HOW DO YOU apply the brakes to a pandemic? One option to prevent its spread is to introduce measures such as PPE and social distancing; and another is to disarm this virus, through the likes of vaccination, chemical treatment and bombardment by radiation.

It's the latter line-of-attack that drove intense interest in the UVC LED when Covid dominated the global agenda. But has this left a lasting legacy, as many would have hoped?

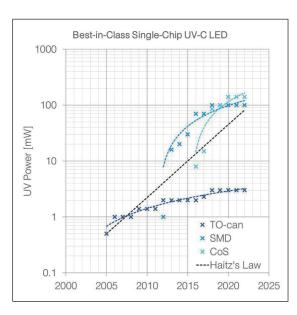

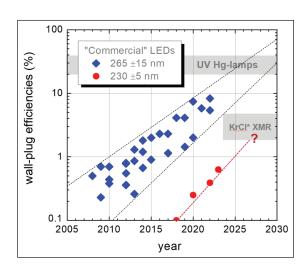

> AquiSense's in-house measurements indicate that UV LEDs are improving at a rate that exceeds the pace of Haitz's Law. Three types of device are included: those housed in TO cans; surface-mount devices (SMDs); and chip on substrate (CoS).

Well, probably not, according to executives at AquiSense, a US-based provider of water treatment systems employing LEDs emitting in the deep UV.

The President and CEO of this company, Oliver Lawal, reasons that while many considered using deep-UV LEDs to prevent airborne transmission of Covid, device development could not move fast enough.

Looking back at that time, Lawal says that he struggled to distinguish between marketing noise and real work. "I feel like some of it was just like banging on a drum."

Due to this, he wonders whether the producers of disinfection systems based on deep-UV LEDs that switched their focus to air disinfection are regretting that decision, given the transient nature of that market.

AquiSense's CTO, Jennifer Pagán, tends to agree: "If you pivoted into making office air disinfection systems that sit on your desk, you might have seen a really big upswing during Covid, but probably no one's buying them now."

Throughout the Covid outbreak, AquiSense continued to prioritise water treatment, a strategy that has always delivered revenue growth. "We doubled in the pandemic; but we doubled in the years before the pandemic and we doubled again after it," says Lawal.

To continue to drive sales, AguiSense is expanding its portfolio, including the launch last month of the PearlAqua Deca 30C. Helping to fill a gap in its range of water purifiers, this particular product, which has attracted plenty of pre-orders, will start being shipped in a matter of days. Lawal expects that the Deca 30C will enjoy most success in the beverage and healthcare industries.

### Tapping into massive markets

Opportunities to increase the company's sales are vast, given that millions of homes in North America and Europe are not connected to a municipal water supply.

It's also worth noting that for some homeowners that are connected, UV treatment still appeals, providing what Lawal describes as a "second barrier". While a wish for some, it's a necessity for the immuno-compromised, enabling sales to hospitals and care homes.

Thanks to the tremendous success of AquiSense, it's a top-three customer for many of the leading suppliers of UVC LEDs. Due to this, the company is in a great position to provide an informed view on the progress of these device makers, and the performance of their products.

Pagán says that following consolidation in the market around 2015, including the acquisition of SETi by Seoul Semiconductor, there has been an uptick in the number of players on the market over the last few years. New entrants include the likes of CrayoNano, ams Osram and Silanna, all joining the ranks of producers of high-power devices. These suppliers sit above a second tier, which includes a number of Chinese chipmakers, shipping lowerpower variants.

The power of the very best devices continues to increase at good pace, with internal measurements at AquiSense indicating a rate of improvement beyond that described by Haitz's Law (see Figure). Such gains in power are highly valued, enabling water treatment at either a faster flow rate or a higher dose.

Best-in-class devices are now edging 6 percent wall-plug efficiencies, according to Pagán, along with output powers that can be as high as 150 mW. "I think the target for a lot of manufacturers is to be at the 8 percent range within another twelve months or so."

With greater powers comes the temptation to try and increase the price – but this is a threat to far greater success for all involved, warns Lawal, who argues that many makers of UVC LEDs are underestimating the competitiveness of the incumbent technology, the mercury lamp. Should sacrifices in UVC LED pricing be made, India could move completely away from the mercury lamp within just 5 years, says Lawal.

"The Indian market currently has around 3 million mercury systems a year, and we believe we're on the verge of cracking a chunk of that market. But to do that, I can't go in at a price point that I'm going in in North America."

Another key characteristic of the UVC LEDs is its lifetime, with different producers quoting different values for the time taken for the intensity to fall by different values – this might be 90 percent, 70 percent or 50 percent.

A lack of standardisation is not a major concern for those at AquiSense, partly because they manage the situation by monitoring the device as it's used. There are three levels of sensing: pass/fail; temperature monitoring; and the recording of the intensity of the UV output. "I think we're unique," argues Lawal. "We're definitely the only company that is providing that level of operational sensing." Such scrutiny shows that AquiSense is well placed to comment on where developers of UVC LEDs should direct their efforts.

"I want them to focus on epitaxial growth, efficiency and contact efficiency," says Pagán, who believes that there has been too much emphasis on packaging.

It's a clear message - and should success follow, it will accelerate humanity's access to healthy drinking water in a post-Covid era.

### NEWS ANALYSIS I TOPIC

# A new home for the Institute for Compound Semiconductors

Nobel-prize-winning climate scientist Donald Wuebbles opens Cardiff University's Translational Research Hub, a new home for the Institute for Compound Semiconductors

### BY RICHARD STEVENSON, EDITOR, CS MAGAZINE

ONE THE CORNERSTONES of the world's first compound semiconductor cluster, situated in South Wales, is the Institute for Compound Semiconductors (ICS). Launched in 2015, the long-term plans for this driver of device development have always included a move to a new, purposebuilt facility with the capability to process wafers up to 200 mm in diameter. Now finally – and to the immense relief of some of those involved – this has been accomplished, with the new facility up and running and open for business.

To mark this key milestone in the life of the ICS, which is part of Cardiff University, this institute held an official opening on Thursday 18 May. At that celebration for what is now the largest building on the Cardiff Innovation Campus, and the new home to both the ICS and Cardiff Catalysis Institute – together they form what is known as the Translational Research Hub – Nobel-prize-winning

climate scientist Professor Donald Wuebbles unveiled a plaque to mark the occasion. He also delivered one of a number of talks that formed the centrepiece of this joyous occasion, showcasing the new capabilities of the ICS.

Those that spoke included Cardiff University's Pro Vice Chancellor Professor Rudolf Alleman, who discussed the many challenges associated with the construction of the Translational Research Hub, which is located on a site previously occupied by railway sidings. Initially the ICS was slated to be up and running in its new home in 2020, but who could have foreseen the problems caused by the Covid pandemic, or material supply issues associated with Brexit.

A reminder of the motivation for forming the ICS came from its Managing Director, Professor Peter Smowton. He explained that the vision for the facility, which is a resource that academia and UK

industry are able to use, came together in 2013 to address what he describes as 'the valley of death'. This phrase relates to the pitfalls that arise when trying to take a promising device technology from the fab and use it to establish a successful, highvolume product.

Smowton is well versed in the challenges of taking a bespoke device with champion results and building on this to create a high-performance, high reliability commercial product. His solution, adopted by the ICS, is that fundamental device development is undertaken with fab tools that are suitable for highvolume manufacture.

Aiding commercialisation of device development is not the only benefit of this approach, however, argues Smowton. He points out that at the heart of the research of many academics is the testing of a hypothesis, which hinges on being able to employ repeatable processes. So pure research also benefits from the highly capable, high-volume tools in the ICS, because they speed the drawing of conclusions from experimental work, as well as the level of rigour.

### A diverse research portfolio

During the official opening of the ICS, this institute showcased its diversified research programme, with brief talks given by a number of academics.

Dr Naresh Gunasekar, a member of the ICS who holds a lectureship position within the Condensed Matter and Photonics Group in the School of Physics and Astronomy, explained that one of his interests relates to the manufacture of wide bandgap semiconductors. His group is concerned with the efficiency of these devices, as well as testing their reliability.

Another researcher sharing their focus, Professor Khaled Elgaid from the ICS and Cardiff University's School of Engineering, spoke about the consequences of energy consumption arising from the shift from 4G to 5G. This evolution will lead to 100 billion connected devices. Armed with tremendous expertise in high-frequency transistors based on a variety of III-Vs, he is involved in the development of GaN HEMTs that are hoped to deliver a step-change in performance.

The ICS also develops sensors for healthcare. Arathy Varghese briefly discussed efforts at developing devices based on the GaN HEMT that could detect cancers and provide personalised healthcare in homes.

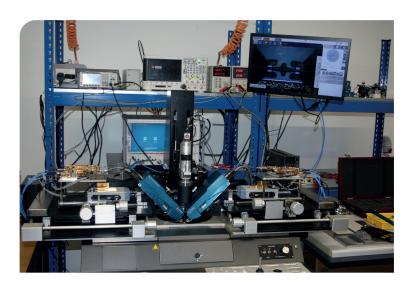

Attendees at the official opening of the Translational Research Hub were also given a tour of the premises. This included a visit to the lab that provides high-frequency measurements of III-V devices, where the current focus is on investigating the characteristics of GaN RF devices. This lab has expertise in measuring very high frequencies, and identifying driving conditions that match harmonics to enable exceptional efficiencies.

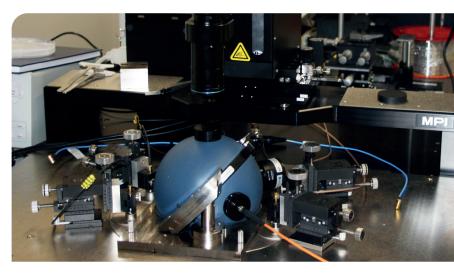

Visitors were also taken to a lab that provides on-wafer optical characterisation of light-emitting devices. As well as characterising VCSELs, this group has developed techniques to investigate the performance of edge-emitters, by etching into the epiwafer.

In addition to the capability to measure devices, the ICS is able to make them. There's an MBE reactor within the university, and ICS partners with IQE for epiwafers produced by MOCVD, which can be grown at the company's St Mellon's facility that is now focusing on development runs.

Processing of devices into epiwafers takes place in the cleanrooms at the ICS. The institute has an extensive range of tools, with the capability to define structures, deposit contacts and add passivation materials, including via atomic layer deposition. Dimensions, defined by photolithography, could soon be extended to the nanometre scale, thanks to the delivery of an electron-beam tool.

It's clear that the move into this well-designed and equipped building is enthusing those working there. The have waited a long time – but it's been worth it.

➤ On-wafer measurements of VCSELs and edge-emitting lasers are undertaken at the ICS.

> There is tremendous expertise in high-frequency measurements at the ICS.

# Streamlining SiC substrate production

A breakthrough tool delivers pinpoint accuracy when producing waferready SiC pucks

#### BY JEFF GUM FROM HARDINGE

INEFFICIENT and costly. It is those two words that best describe the traditional approach to shaping SiC boules.

However, there's now a new era for producing the wafer-ready SiC crystals. It began in late 2022, when our team at Hardinge introduced the BoulePro-200AX. With its single step dual-plane compensation capability, it is streamlining the SiC industry's process for transforming an as grown boule to a wafer-ready puck. Our launch of the BoulePro could not have come at a better time, given the incredibly high level of demand for SiC, which is the vital semiconductor material for the advancement of electric vehicles and other high growth markets.

There are a number of reasons behind the SiC industry's need for a new method for boule shaping. Concerns come from the inefficiencies of using multiple tool sets to perform different functions,

as well as the need to employ several operators to work these tool sets; the time lost to gluing and de-gluing boules to carriers for different steps; the increased process variation that comes from manual material handling and setups; and a lack of best practices driving optimisation and improvement.

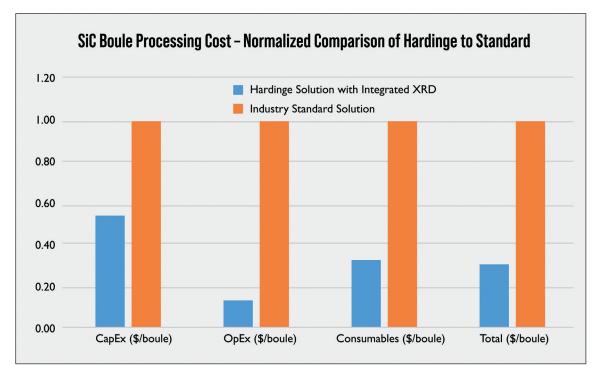

With 130 years of grinding and materials knowledge, our development team, supported by key SiC industry experts, has addressed all the inefficiencies of SiC boule processing by creating a comprehensive and cost-effective package. Our process optimisation enables significant cost reduction across the board, including consumables, OpEx, and CapEx.

For the last couple of years, we have been collaborating with a handful of SiC raw material suppliers to optimise the production process for fabricating a wafer-ready SiC puck. Drawing on deep experience in grinding, turning, milling, and

workholding, we have slashed costs through the optimisation of the right processing speeds, angles, workholding and machining tool types, as well as the incorporation of X-ray metrology into the machine.

### **Efficiency improvements**

Our BoulePro 200AX, with its manufacturing capabilities, checks all the boxes for improved process flow. This fully automated, self-contained machine tool can process as-grown SiC boules to wafer-ready pucks with no gluing/fixturing, external material setup or manual intervention.

Another strength of our BoulePro is its single step, dual plane compensation capability, enabled by inclusion of integrated X-ray diffraction. Thanks to this feature, the BoulePro carries out all the steps of the boule-to-puck conversion process in a dramatically shortened period.

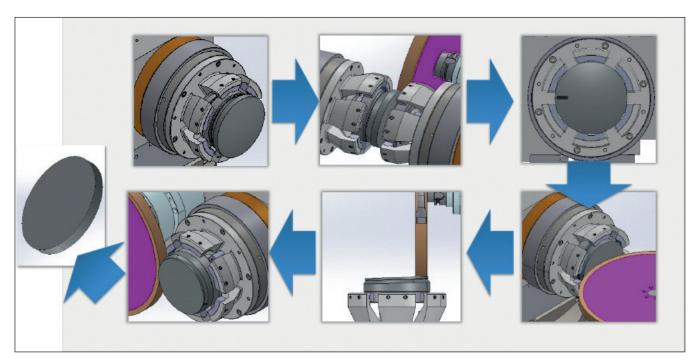

The traditional process flow for transforming a boule into a SiC puck can be adjusted from customer to customer, and from boule to boule. However, in general it begins with a manual or automated boule load, followed by machining the initial outside diameter, applying a rough dome grind and assessing the crystal orientation with X-ray diffraction. After this, a finish dome grind corrects the orientation, prior to handoff to a secondary workhead, seed side removal, a confirmation measurement by X-ray diffraction, the application of a final outside diameter and flat/notch, and finally manual or automated removal of the wafer ready puck (see Figure 1 for an illustration of this process).

The BoulePro slashes the time it takes to process a boule into a puck. While traditional approaches take over 24 hours, with the BoulePro it's just 2-3 hours, using an automated single setup solution. This saving in time contributes to a total cost reduction of nearly 70 percent, when taking labour, manufacturing footprint, scrap, capacity efficiency, and consumables into account (for details, see Figure 2). This gain will play a key role in helping SiC producers to reduce their production costs and grow the industry utilisation of this wide bandgap

#### The secret sauce

Without an industry standard Process of Record to produce wafer-ready SiC pucks, manufacturers have turned to individual approaches. In all cases, they employ a five-step process that begins by using X-ray diffraction to determine the crystal structure for the correct surface orientation, before applying a flat or notch. Outside diameter grinding follows, and then the removal of the seed side and the dome side.

Our experts have evaluated the steps in this process and their inherent inefficiencies. Drawing on our background as an international provider of customised grinding solutions, we have embarked on a clean sheet approach to an all-in-one solution, leveraging core expertise from more than a century of grinding experience.

The result of this effort, the BoulePro, is built on our industry leading USACH grinding machine platform. It features an integrated X-ray diffraction tool and

> Figure 1. The general process flow for producing a SiC puck is: boule load (manual or automated); application of the initial outside diameter (OD); rough dome grind; XRD taken; finishing the dome grind to the correct orientation; handoff to secondary workhead; seed side removal; XRD to confirm; a final OD and flat/notch; and removal of the wafer-ready puck (manual or automated).

### COVER STORY | HARDINGE

> Figure 2. The use of the BoulePro-200AX slashes CapExc, OpEx and costs associated with consumables.

a 5-axis capability, which enables it to orient, X-ray, grind, and/or cutoff the part to the customer's desired specifications. This is accomplished with full automation. Note that the BoulePro is capable of handling all current relevant sizes of SiC boule, including 100 mm, 150 mm and 200 mm material. Key to the exceptional efficiency of our tool is its advanced workholding of the SiC boule. There is no longer a need to glue and de-glue the boule to fixtures throughout each of the process steps - that is a major, incredibly time-consuming issue that current SiC producers face. In addition, the BoulePro eliminates the removal of the boule from one machine, along with its preparation for the next step and its installation in another tool.

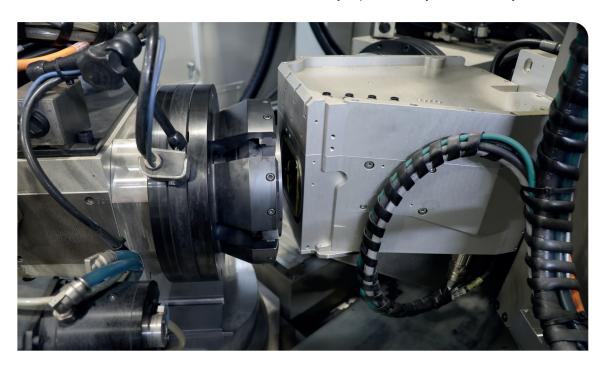

An imperative component of the BoulePro is the integrated X-ray diffraction system. It's essential to identify the crystal orientation, which is needed to ensure the proper placement of the primary flat or notch, and to machine the puck with the correct compensation in all planes. By taking this approach the full puck, from end to end, yields wafers with the correct orientation and geometry. With the BoulePro, the output from the X-ray diffraction system informs the tool of the location of the flat or notch, and how much of an adjustment must be made to crystal surfaces when final machining.

Another advantage that results from having the ability to perform X-ray diffraction analysis in situ,

> The Boule in the workholding on the left and the XRD (X-ray) machine on the right. The XRD is measuring the crystal orientation so that it is known and can be corrected in subsequent grinding steps.

The prototype machine in Elgin, IL that is being used for further development and customer demonstrations.

at any step the process allows, is the opportunity to switch the order of the process steps. One consequence is that the flat or notch can be applied later in the process, ensuring its orientation is highly

### Additional capabilities

There's more to the BoulePro than what meets the eye. Along with its featured proficiencies, additional capabilities can be included upon request.

One of these is the identification of foreign polytypes by UV light inspection. When SiC boules are placed under UV light, certain foreign polytypes, such as 6H, show up as a different colour. Identifying the location of the 6H inclusions allows their removal by the BoulePro, ensuring that the final SiC puck contains only the desired 4H polytype.

It's also possible to add the capability to apply a laser scribe to the surface of the finished SiC puck. This allows customers to track the lot number, the boule number, and so on. It is a feature that is valued for material tracking purposes.

Another capability that can be included within the BoulePro is a vision system. This can take high end photos of the boule or puck at any stage of the process, a feature desired by some customers.

### **Embracing the BoulePro**

This year customers from all over the world have been visiting our facility in Elgin, Illinois, to see the BoulePro in action. This facility is home to our USACH brand of specialised application grinding machines. Our team of engineers and application specialists at this facility drew on their expertise to quickly get a prototype BoulePro up and running to demonstrate this machine's capability. Visitors to the facility are now seeing how the production of SiC pucks can be undertaken with the final design of

this machine, which we expect to ship later this year. Even in its prototype form, customers are eager to see the BoulePro in action, given the market's rapid expansion. These visitors want to see first-hand how the BoulePro can accommodate their unique boule geometry through a full production process. After seeing what it can do for them, they leave with a spring in their step, excited by both the flexibility of the BoulePro, and how well our engineering and application experts adjust to their demands.

One area that has amazed our customers is the precise accuracy of the BoulePro, with its built-in X-ray diffraction machine. Due to the flexibility in the order of operations for the BoulePro's process, and as all parameters are controlled extremely tightly, our machine produces the angular correction on crystal orientation up to 100 times more accurately than the manual process currently used today. What this means for SiC producers is that they can meet and even exceed customer expectations and requirements as specifications evolve.

#### The BoulePro's bright future

Exciting times lie ahead. We have expansion plans underway to cater for increased volumes, given the market's overwhelming excitement for the BoulePro. Demonstrations are ongoing throughout 2023, with the first batch of customer machines scheduled to ship before year-end. We will utilise our global footprint to meet customer demand and aftermarket need, to ensure that our BoulePro supply and support services match customer requirements.

SiC presents unlimited opportunities in many other growth markets as well, and our BoulePro's general configuration and capabilities enable it to be a solution for these applications. We are excited to be at the forefront of this revolution, and viewed as a reliable trusted manufacturing partner that global SiC producers can count on for their fabrication needs.

# Evaluating the pros and cons of power GaN

Switching to a vertical architecture addresses concerns associated with on-resistance and capacitance, but the choice of substrate involves compromise

### BY RICHARD STEVENSON, EDITOR, CS MAGAZINE

THE OUTLOOK for the GaN power device is incredibly positive. Spurred on by ramping revenues for power supplies in the consumer, telecom and datacom sectors, sales are sure to rocket over the next few years. According to the French market analyst Yole Intelligence, total revenue is going to eclipse \$2 billion by 2027 – that's massive growth, considering sales in 2021 were worth just £126 million.

Yet despite all this success, GaN power devices are far from perfect. The harsh reality is that there are many opportunities for improvement. And while some progress might be baked into the upbeat forecast by Yole, it is clear that the more that's done to eradicate weaknesses, the better the long-term prospects for this class of power electronics.

At this year's CS Mantech, held in Orlando, Florida, in mid-May, the most noteworthy weaknesses of the GaN power device were discussed in detail by Mariko Takayanagi, a Senior Manager from Toshiba Electronic Device and Storage Corporation. Several speakers that followed Takayanagi discussed

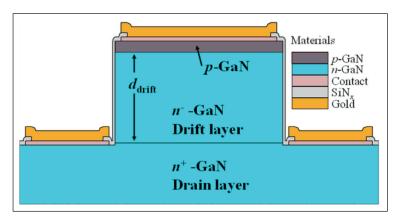

of the traditional power device. Those pursuing a vertical architecture include: Travis Anderson, from the US Naval Research Lab, who detailed the scalable manufacture of planar and vertical *p-i-n* diodes; Dinesh Ramanathan from NexGen Power Systems, who outlined what is claimed to be the world's first commercially available GaNon-GaN technology; and Eldad Bahat Treidel from FBH, Berlin, who described efforts to develop and characterise high-quality drift regions in vertical devices.

switching to a vertical architecture, which is one

option for addressing some of the weaknesses

### **Lateral limitations**

Takayanagi, who works for one of the largest and most established makers of power devices in the world, pointed out that according to market forecasts, for the next few years sales of SiC devices will be worth far more than those for GaN, despite the latter having superior potential, based on Baliga's figure of merit. The reason for this, argues Takayanagi, is that circuit designers cannot simply swap a silicon power device for one made from GaN.

Two of the great strengths of GaN are its very high values for mobility and saturation velocity. Together, they ensure that devices made from this material switch at frequencies that are more than an order of magnitude higher than those of silicon incumbents. Switching at far higher frequencies is a very valuable asset, because it tends to enable the introduction of far smaller passive components, particularly inductors and transformers. In turn, this enables a trimming of the size of electrical units. What's more, reverse recovery losses are close to zero, thanks to the non-existence of an anti-parallel body diode. This ensures that a low switching loss is even sustained at high frequencies.

The upshot of all these merits is the possibility to produce power-conversion equipment that is relatively small, while operating at very high power densities and efficiencies. All these strengths are valued by the designers of AC adaptors, micro-invertors, server power supplies and 5G/6G base stations.

### CONFERENCE REPORT | CS MANTECH

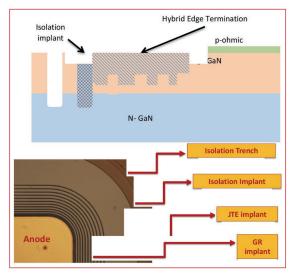

➤ Figure 1. The architecture (top) and an optical image (bottom) of the vertical *p-i-n* diodes developed at the Naval Research Laboratory, in collaboration with researchers at Vanderbilt University and Sandia National Labs.

Unfortunately, increasing the switching frequency with the introduction of GaN devices can bring its own problems. When moving to megahertz switching, electromagnetic noise may arise in regulated frequency domains. Rules are in place for good reason, as noise suppression is needed to avoid the erroneous turn-on of GaN power devices — if this were to happen, it could lead to a ground fault in power electronic equipment.

According to Takayanagi, the solution to combining a high efficiency at a high switching frequency with low noise generation is to minimise parasitic inductances and capacitances. This can be realised by placing the gate drive and the GaN power semiconductors as close to one another as possible, while minimising the parasitic inductances between the device terminals of a discrete power device.

It is a requirement that is included in what Takayanagi considers to be the three key criteria for the GaN power device, judged from an application viewpoint. These three pillars are: the need for a low on-resistance and parasitic capacitance, to ensure good switching characteristics, low energy loss and low noise; a threshold voltage that's above around 2.5 V, so that the device is immune to noise and will provide fail-safe operation; and a low overall cost.

The three classes of GaN power devices on the market today are different forms of HEMT. There is the normally-on transistor, which may also be described as a depletion-mode device; the normally-off transistor, also known as an enhancement-mode device; and the cascode variant. Takayanagi has evaluated the pros and cons of these three designs of HEMT.

Merits of the normally-on transistor, which is on when the gate is biased to zero, include a very high mobility and a zero reverse recovery capacitance, traits that are preferable for high-frequency switching. However, this class of HEMT has a threshold voltage around -10 V, with less than -15 V required to ensure turn off. According to Takayanagi, having the device on at zero gate bias is fatal for power conversion applications, as it requires engineers to put great effort into designing circuitry and gate control, to ultimately ensure safety. The additional circuitry increases parasitics and costs. Due to this, normally on HEMTs are unable to provide high efficiency, high power density and low noise.

Introduced to address issues surrounding the normally-on HEMT is the variant with a cascode configuration. In this case, the normally-on HEMT is connected in series to a silicon low-voltage MOSFET – the source terminal of the MOSFET is connected to the gate terminal of the normally-on HEMT. As a commercial gate driver may be used, there are no concerns relating to cost. But there are concerns associated with the reverse recovery capacitance and the additional on-resistance of the low-voltage MOSFET. It's possible to address these weaknesses by changing the configuration of the MOSFET and HEMT, but that introduces special drivers, additional

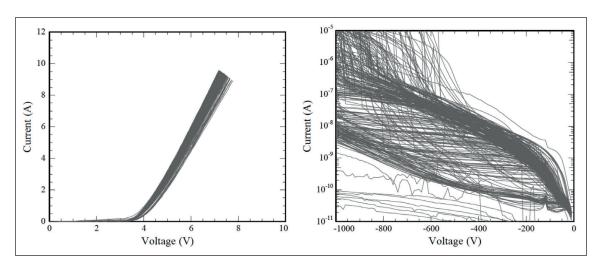

Figure 2. Vertical p-i-n diodes under forward and reverse bias have uniform turn-on characteristics, but a very broad distribution in breakdown behaviour.

### CONFERENCE REPORT I CS MANTECH

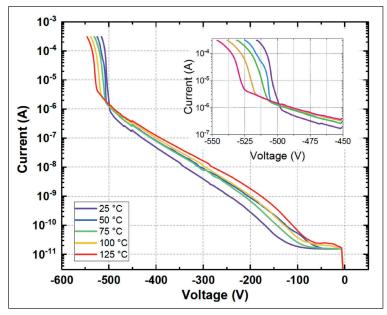

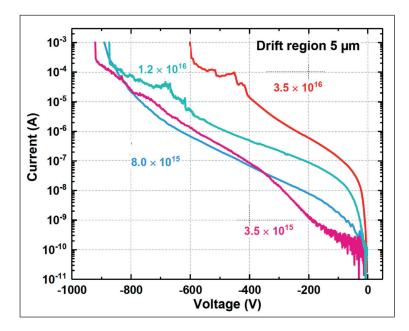

$\triangleright$  Figure 3. The reverse bias of a FBH Berlin p-n diode with a drift region doped to  $4 \times 10^{16}$  cm<sup>-3</sup> shows avalanche behaviour.

components, a power supply and the need for sophisticated control. The third class of commercial HEMT, which is described as normally-off, promises to be the ultimate solution to all three of Takayanagi's criteria. This mode of operation may be realised with a p-GaN gate, which is unfortunately sensitive to over-voltage. Addressing this particular weakness is the commercially available hybrid-drain embedded gate injection transistor, which maintains zero recovery capacitance and is blessed with an on-resistance that is considerably lower than that of cascode devices. However, the threshold voltage is less than +2 V, which is just shy of what a power electronic engineer desires, according to

➤ The winner of this year's CS Mantech 2023 Best Student Paper Award went to Yulin He for her paper Hybrid Etching **Process** on Type-II GaAsSb/ InP DHRT for 5G and Millimetre-Wave Power Amplification.

Takayanagi. This means that there is the threat of erroneous turn-on. Additional concerns are the need for a dedicated driver to provide a current source, and some reliability issues, such as instability due to trapped charges.

To enable GaN transistors to fulfil their potential, demonstrated by their excellent value for the Baliga figure of merit, Takayanagi suggests a need to switch to a different device architecture that combines a high threshold voltage with a low on-resistance and a low capacitance.

Offering promise on all these fronts are vertical GaN transistors. Ideally they are grown on a native foundation, as they require thick drift layers, so demand lattice matching of the substrate and epistructure.

#### Pilot production

In the US, a collaboration that's led by the US Naval Research Laboratory and includes researchers at Vanderbilt University and Sandia National Labs, has established a pilot production line for producing vertical GaN diodes. A major motivation for this work is to address significant challenges that are holding back the mass production and widespread adoption of vertical GaN devices. According to the team, the relationship between substrate specifications and device performance is not well understood, ion implantation technology for selective-area p-type doping is not reliable, and there is a poor understanding of device failure mechanisms, due to a lack of large data sets from electrical stressing.

Efforts by the partnership have focused on a comprehensive study of incoming metrology and wafer mapping. The team has developed a fully planar device process for making diodes, which can be scaled to provide practical voltage and current levels - the target is 10 A and 1.2 kV.

Key accomplishments by the team include establishing pass/fail criteria for incoming epitaxial layers, and identifying the impact of substrate and epiwafer defects on device performance. To succeed in this endeavour, they are producing a large quantity of devices, with more than 500 coming from every wafer. By employing a constant process, the engineers can directly probe the effect of scaling to large-area devices and to layers designed for higher voltage operation, such as 3.3 kV.

The pilot line uses 50 mm free-standing GaN wafers. Spokesman for the team, Travis Anderson from NRL, accepts that this size is not ideal for cost-effective high-volume manufacturing. He told Compound Semiconductor that high volume fab infrastructure available for supporting 50 mm wafers is not really available, and yield suffers when attempting to make devices of practical size – that is, greater than 1 mm<sup>2</sup> - due to the limited available area.

"At 100 mm it becomes much more feasible for a

### CONFERENCE REPORT | CS MANTECH

true production environment," added Anderson.

"However, 50 mm is more than sufficient for a

manufacturing demonstration to evaluate process

stability in an R&D environment, which was the goal

of our efforts."

There are concerns related to the cost, size and level of availability of GaN substrates. "I do not think the cost is prohibitive, particularly as 100 mm wafers are emerging," argues Anderson, who says that over the course of his collaboration's four-year programme, they have seen a significant shift in the economics of GaN wafers. "Even though the price has only modestly decreased, the quality and uniformity of the wafer has improved substantially, which improves our process yield." During the project, the team had no difficulty securing wafers from multiple sources. However, it should be noted that the total number of wafers they have used is not that high.

Anderson and his co-workers used their line to produce 1.2 kV diodes with an 8  $\mu m$ -thick drift layer doped to 1 x 10 $^{16}$  cm $^{-3}$ , and 3.3 kV variants with a 25  $\mu m$ -thick drift layer doped to 4 x 10 $^{15}$  cm $^{-3}$ . These devices featured an anode with dimensions varying from 300 nm to 500 nm, and a doping level from 3 x 10 $^{17}$  cm $^{-3}$  to 2 x 10 $^{19}$  cm $^{-3}$ .

"The *p-i-n* diode is an ideal test vehicle to understand the fundamentals of a GaN *p-n* junction," says Anderson. "Since the *p-n* junction is the building block of more complicated diodes and FETs, we chose to study the *p-i-n* diode first as a test vehicle to prove that we can reliability make high quality *p-n* junctions, evaluate edge termination processes, and study scaling to high current before moving to more complex three-terminal structures."

The metrology applied to the incoming wafers includes: C-V mapping with a mercury probe, to calculate doping and uniformity; optical profilometry; and X-ray diffraction mapping. The optical profilometry data is analysed with a machine learning algorithm that identifies bumps, pits, and regions of high roughness.

Anderson says that machine learning has been extremely helpful: "As we worked through the fabrication process, we used machine learning to correlate incoming metrology data to device performance data. By working with these data sets, we were able to develop algorithms to develop the appropriate incoming wafer and epi requirements, screen out wafers that would not yield well, and identify non-intuitive mechanisms that would impact device performance."

Following metrology, wafers are cleaned, before edge termination is realised using a multi-step nitrogen implant box file. This step isolates devices through the p-GaN layer and forms an edge termination region that utilises the hybrid structure, which consists of a junction termination extension

region, with guard regions superimposed via a spacer layer (see Figure 1). After cleaning, a front side *p*-ohmic metal contact and a backside *n*-ohmic metal contact are deposited.

Electrical measurements under forward bias have produced varied results. On an exceptional wafer, diodes have a highly uniform turn on, a low leakage and high current capability (see Figure 2 (a)). This is said to be indicative of a high-quality *p-n* junction and relatively few pinholes in the film. However, on inferior wafers many devices suffer from premature turn-on, due to shorting of the anode metal to the substrate. This is caused by pinholes in the epitaxial layer, due to particles introduced in the growth process.

Anderson and co-workers find a very broad distribution in the breakdown behaviour of their diodes (see Figure 2 (b)). For the best discrete devices, breakdown is 1.4 kV, with a leakage below 1 nA at up to 1 kV. But there are also many devices with a high leakage at a voltage just half that of breakdown.

The team are yet to determine the mechanism behind the wide variation in breakdown behaviour. However, they speculate that it could come from localised variations in drift layer properties, arising from variations in miscut or epitaxial defects.

Efforts have been directed at optimising the edge termination design, critical to realising an abrupt avalanche breakdown. The team varied the anode thickness, which ensured a systematic variation in the thickness of the remaining *p*-GaN layer. This led them to discover that they could slash the leakage current under reverse bias by more than two orders of magnitude by thinning the underlying *p*-GaN layer to less than 10 nm.

➤ Figure 4. The reverse bias of a FBH Berlin p-n diode with a drift region doped to 4 x  $10^{16}$  cm<sup>-3</sup> shows avalanche behaviour.

### CONFERENCE REPORT | CS MANTECH

> Figure 5. For p-n diodes with a drift region doped to 3.5 x  $10^{16}$  cm<sup>-3</sup>, plots of reverse bias reveal a hard breakdown.

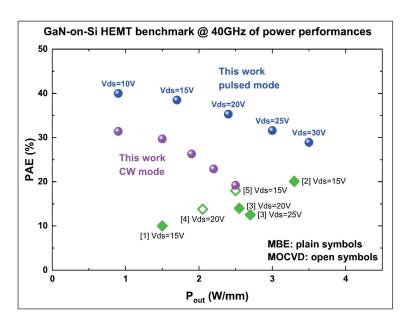

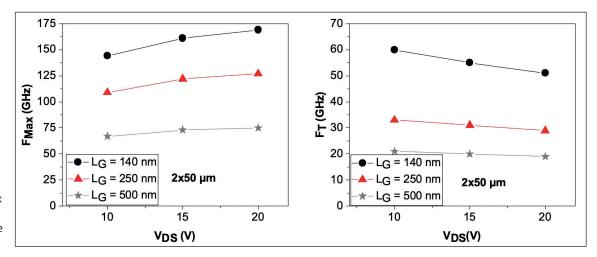

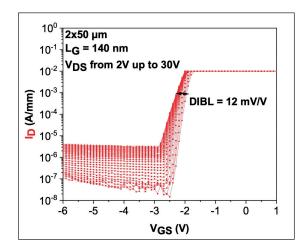

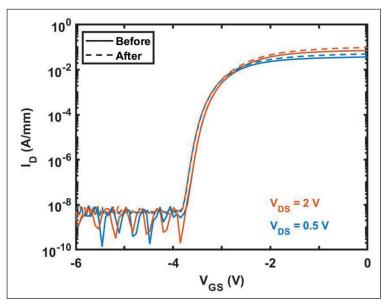

Encouragingly, the team can report two observations that are consistent with avalanche breakdown. One is an increase in the breakdown voltage at elevated temperature; and the other is the moving of an electroluminescence spot from the edge of the isolation implant to the edge of the anode.