# CONNECTING THE COMPOUND SEMICONDUCTOR COMMUNITY

# **CUBIC NITRIDES** Targeting amber emission

#### VOLUME 30 ISSUE VI 2024

#### AN ANGEL BUSINESS COMMUNICATIONS PUBLICATION

#### INSIDE

News, Analysis, Features, Editorial View, Research Review and much more

# All GaN power integration

Bipolar transport overcomes the inherent barriers of GaN p-FETs to pave the way to higher current densities

#### One tipping point at a time

The growth of GaN is inevitable as it displaces the silicon MOSFET in one application after another

#### COMPOUNDSEMICONDUCTOR.NET

#### GaN switches and CMOS drivers

Monolithic integration of GaN and silicon CMOS on 300 mm wafers will support power delivery in tomorrow's networks

# RIXTRON

# **THE NEW G10 SERIES**

#### Your Productivity Solution for All Advanced Epitaxy Materials

#### G10-GaN

- 8x150mm (6") or 5x200mm (8")

- 1<sup>st</sup> fully automated compact GaN MOCVD cluster designed 100% for Si Power fabs

- Novel hardware solution for unmatched barrier uniformities and device yields

#### End Markets/Products:

Power Electronics & Wireless communication

BIXTRON

#### G10-SiC

- > 9x150mm (6") or 6x200mm (8")

- New hardware & process surpassing Single Wafer Reactor uniformities

- +50% productivity per fab area with large batch technology & small footprint

End Markets/Products: EV inverters & charging infrastructure

#### G10-AsP

- ▶ 8x150mm (6") or 5x200mm (8")

- 1<sup>st</sup> fully automated AsP MOCVD system enabling 10x lower defect density

- Unmatched wavelength uniformity on all wafer sizes

#### End Markets/Products:

Micro LED, Optical Data communication, 3D-sensing & LiDAR

# **VIEWPOINT** By Richard Stevenson, Editor

# The optimal sweet spot

One of the questions that continues to pop up within our industry is this: What is the most appropriate level of vertical integration?

Throughout the late 1990s and the early 2000s, when production of GaAs-based transistors for mobile phones attracted a great deal of attention, a well-publicised debate centred on whether to outsource the epitaxial process. Beyond question, however, was the production of boules and substrates, which would be carried out by a company focusing on crystal growth.

That's not the case with the material of the moment, SiC. Within the big five – that's Wolfspeed, STMicroelectronics, Onsemi, Infineon and Rohm – the extent of vertical integration is expanding, beginning in some cases with the production of boules from powders and concluding with the shipping of packaged devices.

However, while this *modus operandi* makes much sense for companies that can invest hundreds of millions of dollars in their infrastructure, smaller firms need to identify a different sweet spot for their optimal operation within the SiC industry.

That includes SMC Diode Solutions, an American-owned company that has just opened a second fab in Nanjing, China. This chipmaker cut its teeth by producing silicon devices for makers of power supplies, and expanded its portfolio with SiC diodes in 2019, followed more recently by a range of MOSFETs.

Discussing the opening of this new 300,000 ft<sup>2</sup> fab that's created 300 jobs, company CEO and chairwomen Yunji Corcoran told *Compound Semiconductor* that when it comes to SiC, SMC would continue to focus on what it does best – making power devices from semiconductor epiwafers (see p. 14).

While this approach has much going for it, the downside is that there is a need to work within a supply chain, and possibly deal with the consequences of delays outside of SMC's control.

For the production of SiC Schottky barrier diodes, SMC is partnering with local producers. Corcoran says that the quality of the material that they are receiving is 'pretty good'.

To produce MOSFETs, a more complex structure, SMC sources its epiwafers from further afield. However, drawing on its internal analysis of defects in SiC, Corocan believes that local suppliers are improving, which is good news for both SMC and the global SiC industry.

The efforts of SMC show that there is space for plenty of smaller players in the SiC industry. Their efforts help to strengthen supply chains and increase the availability and deployment of this compelling class of power electronics.

Free weekly e-news roundup go to: compoundsemiconductor.net

# CONTENTS

#### VOL. 29 ISSUE VI 2024

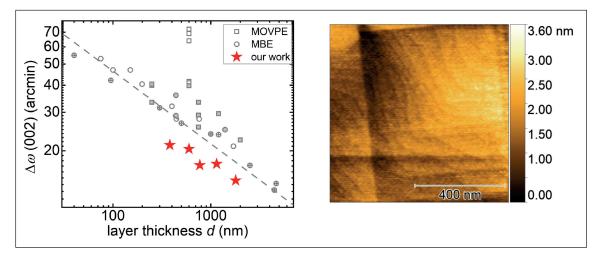

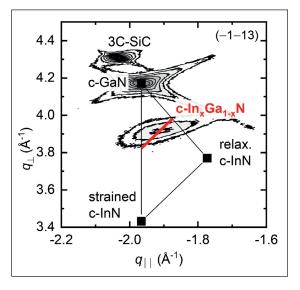

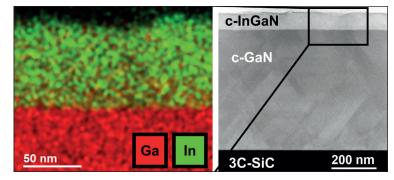

### 28 Tackling the amber emission challenge with cubic nitrides

The growth of cubic nitride by MBE promises to enable the production of microLEDs that span the entire visible range

# 16 Crushing MOSFETs one tipping point at a time

The growth of GaN is inevitable as it displaces the MOSFET in one application after another

# 18 What does the future hold for the compound semiconductor industry?

Growth is forecast for all leading forms of compound semiconductor device, driven in part by demand for more data, an uptake in AI, increasing opportunities for satellite communication and growing sales of electric vehicles

# 22 Bipolar *p*-FETs enable all-GaN power integration

Bipolar transport overcomes the inherent barriers of GaN *p*-FETs to pave the way to higher current densities

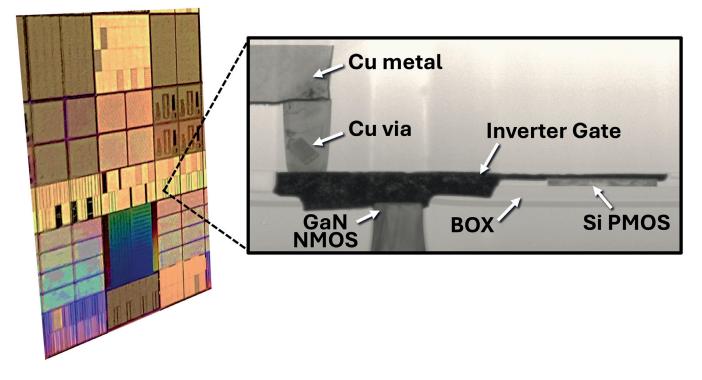

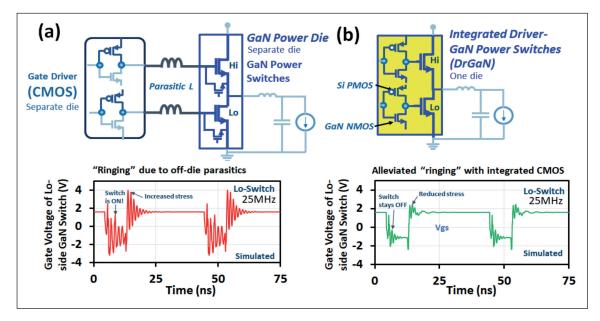

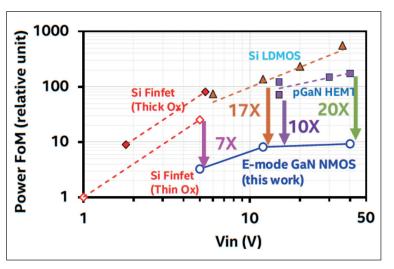

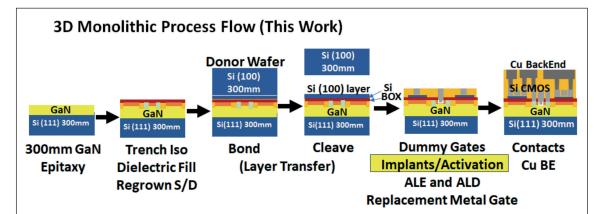

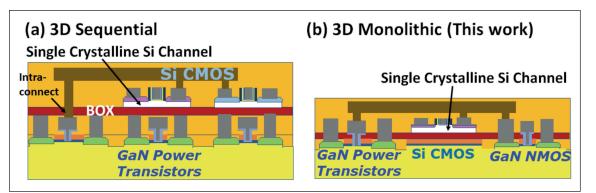

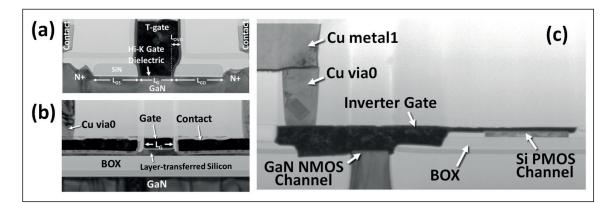

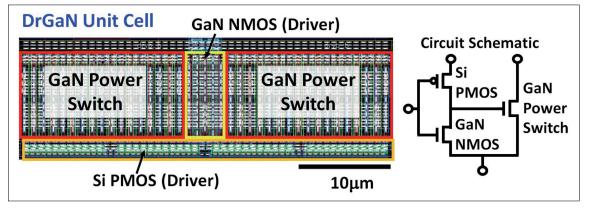

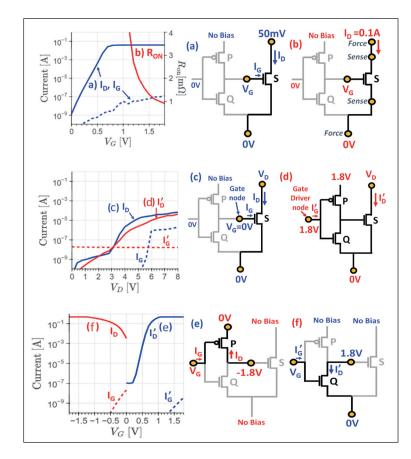

# 34 Combining a CMOS driver and a GaN power switch on 300 mm silicon

Intel's DrGaN technology, involving the monolithic integration of GaN and silicon CMOS on 300 mm wafers, will support power delivery in tomorrow's data infrastructure and communication networks

# 40 Raising the bar for power amplification

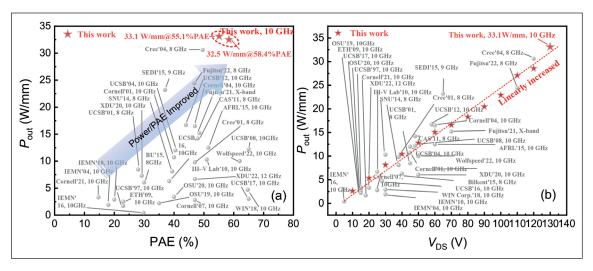

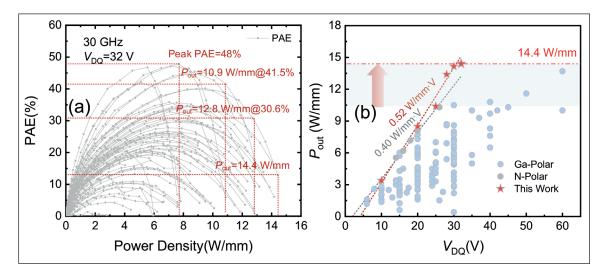

The performance of GaN-based amplifiers operating in the X- and Ka-bands record new highs through the introduction of an AIN buffer

# 44 Broadening the nitride palette with AlYN

AIYN provides a promising material for pioneering sustainable high-performance applications and green technologies

#### **NEWS ANALYSIS**

# 12 CSconnected: Maintaining momentum

Under leadership of its new managing director CSconnected will continue to focus on realising a high level of visibility and maintaining close relationships, while developing skills and strengthening supply chains

# 14 Swelling SiC shipments with a second fab

Opening an additional fab in Nanjing will help to grow sales of SMC Diode Solution's SiC products to around half the company's revenue

#### NEWS

- **06** Nokia to acquire Infinera for \$2.3 billion

- **07** Nexperia to invest \$200 million in Hamburg site

- 08 Onsemi takes next step in SiC innovation

- 09 Russian venture targets SiC power

- **10** Over £1 million for IQE to commercialise ultraRAM

- 11 VueReal and RiTdisplay forge microLED partnership

#### **RESEARCH REVIEW**

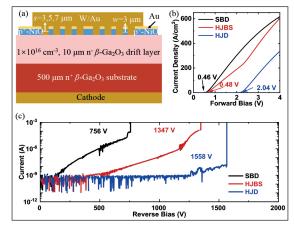

**50** Raising the bar for the  $\beta$ -Ga<sub>2</sub>O<sub>3</sub>

- 51 Irradiation-hardened GaN HEMTs

- 52 Enhancing mobility with mist CVD

News Editor Christine Evans-Pughe christine.evans-pughe@angelbc.com

Design & Production Manager Mitch Gaynor mitch.gaynor@angelbc.com +44 (0)1923 690214 Director of Logistics Sharon Cowley sharon.cowley@angelbc.com +44 (0)1923 690200

Senior Sales Executive Jacob Caulfield jacob.caulfield@angelbc.com +44 (0)2476 718979

Senior Logistics Executive Eve O'Sullivan +44 (0)2476 823 123 eve.osullivan@angelbc.com Circulation Scott Adams scott.adams@angelbc.com

Publisher Jackie Cannon jackie.cannon@angelbc.com +44 (0)1923 690205 Chief Executive Officer Sukhi Bhadal sukhi.bhadal@angelbc.com +44 (0)2476 718970

Chief Technical Officer Scott Adams scott.adams@angelbc.com +44 (0)2476 718970

Directors Jackie Cannon, Sharon Cowley

Angel Business Communications Ltd 6 Bow Court, Fletchworth Gate, Burnsall Road, Coventry CV5 6SP, UK. T: +44 (0)2476 718 970 E: info@angelbc.com

Compound Semiconductor is published nine times a year on a controlled circulation basis. Non-qualifying individuals can subscribe at: £105.00 per annum (UK), €158 per annum (Europe), \$198 per annum (air mail) (USA). Cover price £4.50. All information herein is believed to be correct at time of going to press. The publisher does not accept responsibility for any errors and omissions. The views expressed in this publication are not necessarily those of the publisher. Every effort has been made to obtain copyright permission for the material contained in this publication. Angel Business Communications Ltd will be happy to acknowledge any copyright oversights in a subscribe at the publishers. The paper used within this magazine is produced by chain of custody certified manufacturers, guaranteeing sustainable sourcing. US mailing information: Compound Semiconductor, ISSN 1096-598X, is published 9 times a year, Jan/Feb, March, April/May, June, July, August/September, October, November, December by Angel Business Communications Ltd, Unit 6, Bow Court, Fletchworth Gate, Burnsall Rd, Coventry CV5 65P. UK.Airfreight and malling in the USA by agent named World Container INC 150-15, 183rd St, Jamaica, NY 11413, USA. Periodicals Postage Paid at Brooklyn, NY 11256. POSTMASTER: Send address changes to Compound Semiconductor, Air Business Ltd, *clo* World Container INC 150-15, 183rd St, Jamaica, NY 11413, USA. We strive for accuracy in all we publish; readers and contributors are encouraged to contact us if they recognise an error or omission. Once a magazine edition is published foline in print or both), we do not update previously published atricles to align old company names, branding, marketing efforts, taglines, mission statements or other promotional verbiage, images, or logos to newly created or updated memory.prospects might necognise the company, we invite organizations to provide Angel Business Communications with a news release detailing their new business objectives and/or other changes that could impact how custom

### Nokia to acquire Infinera for \$2.3 billion

#### Creates global optical business with increased in-house capabilities and vertical integration

NOKIA will acquire the optical networking and chip company Infinera for \$2.3 billion.

Nokia and Infinera see a significant opportunity in merging to improve scale and profitability. The transaction also aligns strongly with Nokia's strategy to strengthen the company's technology leadership in optical and increase exposure to webscale customers, the fastest growing segment of the market.

The combined business will have significant in-house capabilities, including an expanded digital signal processor development team, expertise across silicon photonics and InP-based semiconductor material sciences, and deeper competency in photonic integrated circuit (PIC) technology.

Pekka Lundmark, president and CEO of Nokia, said: "In 2021 we increased our organic investment in optical networks with a view to improving our competitiveness. That decision has paid off and has delivered improved customer recognition, strong sales growth and increased profitability. We believe now is the right time to take a compelling inorganic step to further expand Nokia's scale in optical networks. The combined businesses have a strong strategic fit given their highly complementary customer, geographic and technology profiles. With the opportunity to deliver over 10 percent comparable earningsper-share accretion, we believe this will create significant value for shareholders."

David Heard, CEO of Infinera, said: "We are really excited about the value this combination will bring to our global customers. We believe Nokia is an excellent partner and together we will have greater scale and deeper resources to set the pace of innovation and address rapidly changing customer needs at a time when optics are more important than ever – across telecom networks, inter-data centre applications, and now inside the data centre."

Heard added: "This combination will further leverage our vertically integrated optical semiconductor technologies. Furthermore, our stakeholders will have the opportunity to participate in the upside of a global leader in optical networking solutions."

#### VisIC, Heraeus and Pink collaborate on GaN EV module

GaN COMPANY VisIC Technologies has partnered with materials company Heraeus Electronics, and sintering equipment firm Pink, to develop an advanced power module using D3GaN technology.

This combination of VisIC's D3GaN technology with Heraeus' sintering paste and Pink's silver and copper sintering process and sintering equipment is claimed to set a new benchmark for power module performance in the EV market. The partners expect it to drive the adoption of GaN technology in this field.

The module – based on a  $Si_3N_4$  ceramic substrate, an innovative silver sintering process and advanced top side interconnects – is claimed to deliver high reliability and performance for battery electric vehicles (BEVs).

The use of a  $Si_3N_4$  metal ceramic substrate is a key innovation.  $Si_3N_4$  is known for its high thermal conductivity, mechanical strength, and reliability under high-temperature conditions.

The adoption of the silver sintering process by Pink enhances the thermal and electrical conductivity of the module. Silver sintering is a lowtemperature bonding process that creates robust and reliable connections between components, improving the module's overall durability and efficiency. This process is said to be critical for the high reliability required in EV powertrains, where consistent performance is non-negotiable.

The resulting power module is designed to meet the stringent reliability and performance standards of the EV industry. It can deliver the high-power density of over  $500 \text{ A}_{ms}/650 \text{ V}$  and the efficiency needed for modern

BEVs, while also offering long-term reliability and durability at a cost point near silicon devices.

Tamara Baksht, CEO of VisIC, stated: "We are thrilled to work with the leading manufacturer of sintering processes of Heraeus Electronics and Pink and adapt their experience into GaN-based power modules to develop the next generation of power module for high-volume automotive inverter applications."

Andrea Pink, CEO of Pink, remarked: "We are excited to work with such a future driven company as VisIC, together with our long-term partner Heraeus Electronics, supporting the newest product innovation for GaN applications."

Heraeus Electronics Michael Jörger, EVP Head of Business Line Power Electronic Materials, added: "With our materials, application know-how and engineering services we are glad to work with our partners on speeding up the innovative approach of highly efficient GaN modules for automotive applications."

### Nexperia to invest \$200 million in Hamburg site

Expansion will focus on the next generation of wide bandgap semiconductors SiC and GaN

SEMICONDUCTOR manufacturer Nexperia will invest \$200 million to develop the next generation of wide bandgap (WBG) semiconductors, SiC and GaN, and to establish production infrastructure at its Hamburg site in Germany.

At the same time, wafer fab capacity for silicon diodes and transistors will be increased. The investments are jointly announced with Hamburg's Minister for Economic Affairs, Melanie Leonhard, on the occasion of the 100-year anniversary of the production site.

"This investment strengthens our position as a leading supplier of energyefficient semiconductors and enables us to utilise available electrical energy more responsibly," comments Achim Kempe, COO and managing director at Nexperia Germany.

"In the future, our Hamburg fab will cover the complete range of WBG semiconductors, while still being the largest factory for small signal diodes and transistors. We remain committed to our strategy of producing highquality, cost-efficient semiconductors for standard applications and power-intensive applications, while addressing one of the greatest challenges of our generation: meeting the growing demand for energy, while reducing the environmental footprint."

First production lines for high-voltage GaN D-Mode transistors and SiC diodes started in June 2024. The next milestone will be modern and costefficient 200 mm production lines for SiC MOSFETs and low-voltage GaN HEMTs. These will be established at the Hamburg factory over the next two years. At the same time, the investment will help to further automate the existing infrastructure at the Hamburg site and expand silicon production capacity by systematically converting to 200 mm wafers. Following the expansion of the clean room areas, new R&D laboratories are being built to continue to ensure a seamless transition from research to production in the future.

"The planned investment enables us to bring WBG chip design and production to Hamburg. However, SiC and GaN are by no means new territory for Nexperia. GaN FETs have been part of our portfolio since 2019, and in 2023 we expanded our range of products to include SiC diodes and SiC MOSFETs, the latter in collaboration with Mitsubishi Electric," said Stefan Tilger, CFO and managing director at Nexperia Germany

Tilger dded: "Nexperia is one of the few suppliers to offer a comprehensive range of semiconductor technologies, including silicon, SiC, and GaN in both E-mode and D-mode. This means, we offer our customers a one-stop shop for all their semiconductor needs."

#### Infineon steps up battle with Innoscience

GERMAN chip maker Infineon has expanded its GaN patent battle with China's Innoscience Technology, adding three patents to infringement allegations.

The amended complaint (filed in the US District Court for the Northern District of California) alleges that as many as 88 of Innoscience's GaN-based chips infringe Infineon patents. These include US Patent numbers 8,686,562; 9,070,755; and 8,264,003.

Earlier this year, Infineon Technologies Austria sued Innoscience alleging that 30 of its products infringed US Patent No. 9,899,481. A subsequent injunction stopped Innoscience from showing its GaN devices at last month's PCIM trade exhibition, held in Nuremberg, Germany, June 11th-13th.

Innoscience has since challenged both the validity of the original patent and the injunction, saying it only applies to the tradeshow.

Meanwhile, EPC is involved in a US court case with Innoscience about the validity of another GaN patent, '294, which EPC describes as its foundational patent.

### **Onsemi takes next step in SiC innovation**

#### Introduces latest generation EliteSiC M3e MOSFETs

ONSEMI has introduced its latest generation SiC technology platform, EliteSiC M3e MOSFETs. The company also disclosed plans to release multiple additional generations through 2030.

According to Onsemi, the EliteSiC M3e MOSFETs achieve a significant reduction in both conduction and switching losses. Compared with previous generations, the platform can reduce conduction losses by 30 percent and turn-off losses by up to 50 percent.

The EliteSiC M3e MOSFETs are also claimed to offer the industry's lowest specific on-resistance with short circuit capability, which is critical for the traction inverter market that dominates SiC volume.

Packaged in Onsemi's discrete and power modules, the 1200V M3e die delivers substantially more phase current than previous EliteSiC technology, resulting in approximately 20 percent more output power in the same traction inverter housing.

Conversely, a fixed power level can now be designed with 20 percent less SiC content, saving costs while enabling the design of smaller, lighter and more reliable systems.

Onsemi says that with each new generation of SiC, cell structures will be optimised to efficiently push more current through a smaller area, increasing power density.

Moreover the company says it can develop multiple generations in parallel

and accelerate its roadmap to bring several new EliteSiC products to market at an accelerated pace through 2030.

"We are applying our decades of experience in power semiconductors to push the boundaries of speed and innovation in our engineering and manufacturing capabilities to meet the rising global energy demands," said Mrinal Das, senior director of technical marketing, Power Solutions Group, Onsemi.

"There is a huge technical interdependency between the materials, device and package in SiC," added Das. "Having full ownership over these key aspects allows us to have control over the design and manufacturing process and bring new generations to market much faster."

Onsemi provides gate drivers, DC-DC converters, e-Fuses and more to pair with the EliteSiC M3e platform. The EliteSiC M3e MOSFET in the industry-standard TO-247-4L package is now sampling.

#### GlobalFoundries acquires Tagore GaN IP

GLOBALFOUNDRIES has acquired Tagore Technology's proprietary GaN IP portfolio, a high-power density solution designed to push the boundaries of efficiency and performance in a wide range of power applications in automotive, internet of things (IoT) and AI data centres.

As a part of the acquisition, a team of experienced engineers from Tagore, dedicated to the development of GaN technology, will be joining GF.

"We are committed to being the foundation of our customers' power applications today and for decades to come," said Niels Anderskouv, chief business officer at GF. "With this acquisition, GF takes another step toward accelerating the availability of GaN and empowering our customers to build the next generation of power management solutions that will reshape the future of mobility, connectivity and intelligence."

Amitava Das, co-founder and chief operating officer of Tagore Technology, added: "The accelerating demand for more power efficient semiconductors is dramatically increasing, and Tagore has been at the forefront of developing disruptive solutions using GaN technology for a wide range of power devices. The team and I are excited to join GlobalFoundries to increase our focus on market-leading IP that will help address power design challenges and support the continued evolution of automotive, industrial and AI datacenter power delivery systems."

In February 2024, GF was awarded \$1.5 billion in direct funding under the US CHIPS and Science Act, part of that investment is targeted towards enabling the high-volume manufacturing of critical technologies including GaN to securely produce more essential chips.

Combining this manufacturing capacity with the technical know-how of the Tagore team, GF hopes to transform Al system efficiency, especially in edge or IoT devices, where reduced power consumption is critical.

### **Russian venture targets SiC power**

Element and St. Petersburg Electrotechnical University form joint power chip company

RUSSIAN microelectronics company PJSC Element and St. Petersburg Electrotechnical University LETI (ETU LETI) have formed a joint venture called Letiel LLC, according to a story on Interfax, a news agency covering Russia.

"We plan to actively develop the area of high-tech power semiconductor devices and in future take leading positions among global manufacturers of SiC devices," Element president Ilya Ivantsov told Interfax.

"The objective of the joint venture with LETI will be to develop and research technologies to produce SiC devices, on the basis of which we will be able to build a modern and competitive power electronics product and technology line for various sectors of industry," Ivantsov said.

The new company will do research and development on SiC-based power devices, which are used in the production of modern electric vehicles, aircraft navigation systems and other sectors.

The venture, which is 51 percent owned by Element and 49 percent by LETI,

also plans to study and design photonic integrated circuits. These components are used in equipment for cellular networks, satellite systems and radio location.

"Mass production of solutions in the area of the electronic component base for power electronics and photonic integrated circuits will be rolled out at the facilities of Element Group's new plant in Zelenograd," the company said.

The partners have not specified how much they are investing in the venture,

which is headed by Element technology development director Konstantin Okunev.

Element was formed in 2019 with 19 microelectronics design, development and manufacturing assets belonging to investment group Sistema PJSFC and state corporation Rostec. Element's key portfolio companies are chip factory Mikron and microchip, molecular electronics research institute NIIME and electronics research institute NIIET. The group now includes about 30 enterprises.

#### Advanced Compound Semiconductor Foundry Services

#### MOCVD • Fabrication • Testing

Advanced III-V semiconductor solutions for optoelectronics application in the biotechnology, telecommunications, energy, industrial, and security industries.

MasimoSemiconductor.com | 603-595-8900

## Over £1million for IQE to commercialise ultraRAM

IQE to develop capability for growth of gallium antimonide and aluminium antimonide in Innovate UK project

AN INNOVATE UK project worth £1.1 milion has been awarded to the Lancaster University spinout firm Quinas, IQE and the universities of Lancaster and Cardiff.

Quinas will coordinate the project, which is the first step towards volume production of the universal computer memory ultraRAM invented by Lancaster University academic Manus Hayne.

UltraRAM, which exploits quantum resonant tunnelling, combines the nonvolatility of a data storage memory, like flash, with the speed, energy-efficiency, and endurance of a working memory, like DRAM.

Most of the funding for the one-year project will be spent at IQE, which will scale up the manufacture of compound semiconductor layers from Lancaster University to an industrial process at the Cardiff-based firm. This will involve IQE developing advanced capability for growth of GaSb and AISb for the first time.

The project follows significant investment to boost the UK semiconductor industry and the establishment of the world's first compound semiconductor cluster in South Wales.

Manus Hayne, who is the Lancaster team lead, co-founder and chief scientific officer at Quinas, said: "We are delighted that Innovate UK is supporting this ambitious project, and that IQE has committed to developing the first part of ultraRAM mass production."

It is estimated that the global memory chip market will be worth about \$320 billion by 2030, but the UK currently has no stake in it.

Hayne said: "UltraRAM represents a tremendous economic opportunity for the UK, and the efficiencies it could

bring to computing at all scales has the potential for huge energy savings and carbon emission reduction."

Jessica Wenmouth, Lancaster University's head of research commercialisation said: "I am delighted to support our spinout Quinas on its journey to scale this Lancaster-led innovation to an industrial process suitable for a semiconductor foundry 'fab,' thereby generating impact from research through commercialisation.

Wenmouth added: "This project not only aligns with Lancaster University's strategy to foster impactful research and innovation but also demonstrates

The goal of the one-year project to industrialise the process involves scaling up ultraRAM wafer diameters from 75 mm at Lancaster to 150 mm at IQE. This will be achieved by MOCVD rather than MBE, which is typically used at universities. the effective utilisation of strategic grant funding alongside private equity investment. Such collaborations are crucial for bringing new products to market and driving significant investment into the UK for emerging technologies, enhancing our national and global standing in cutting-edge fields."

The goal of the one-year project to industrialise the process involves scaling up ultraRAM wafer diameters from 75 mm at Lancaster to 150 mm at IQE. This will be achieved by MOCVD rather than MBE, which is typically used at universities.

Hayne said: "Lancaster will do some initial MBE as a control/template for the industrial growth. Our key role will be to characterise the antimonide material grown at IQE, and once sufficient quality is confirmed, we will fabricate and test ultraRAM on small areas of the wafers from IQE."

"In parallel with this, Lancaster will continue to work on ultraRAM scaling, by reducing the size of individual devices ('Moore's law') and making larger and larger arrays. Once devices are small enough and arrays are large enough, the following stage will be to demonstrate fabrication on a complete 8-inch wafer, and then to translate the process to an industrial one, suitable for a semiconductor foundry 'fab'."

# VueReal and RiTdisplay forge microLED partnership

Collaboration aims to accelerate the adoption of microLED displays into consumer markets and augmented reality

VUEREAL, the Canadian company behind MicroSolid Printing technology, has announced a partnership with Taiwanese emissive display firm RiTdisplay Corporation.

The companies have already worked together on automotive display and interior/exterior lighting systems.

Now they are expanding into consumer markets and augmented reality, using RiTdisplay's backplane process and VueReal's MicroSolid Printing platform, which enables the transfer of microLEDs.

"VueReal's technology is revolutionising the microLED space," said Reza Chaji, CEO of VueReal. "Our collaboration with RiTdisplay will not only accelerate the adoption of microLED displays, but also deliver unmatched performance and value to our customers, setting new industry standards."

"RiTdisplay is thrilled to partner with VueReal," said Robert Chen, general manager of RiTdisplay. "This collaboration allows us to combine our extensive expertise in emissive display production with VueReal's groundbreaking MicroSolid Printing technology."

Chen added: "Together, we are uniquely positioned to deliver cutting-edge displays that not only meet but exceed the evolving needs of our customers, offering innovative and commercially viable solutions that will redefine the display market."

This announcement follows VueReal recent plans to double its manufacturing space and introduce a new production line capable of producing displays.

### Driving tomorrow's technologies

Compound semiconductors provide the key enabling technologies behind many new and emerging applications. CSconnected represents the world's first compound semiconductor community based in and around South Wales in the UK

# **CSconnected:** Maintaining momentum

Under leadership of its new managing director CSconnected will continue to focus on realising a high level of visibility and maintaining close relationships, while developing skills and strengthening supply chains

#### BY RICHARD STEVENSON, EDITOR, CS MAGAZINE

ANYONE TAKING OVER the leadership of any organisation will be tempted to exert their new authority by announcing big and bold plans. But if the current direction of travel is working well, there's a strong argument for simply keeping going, while looking to make small and meaningful changes.

The latter approach is the one being adopted by Howard Rupprecht, the new managing director of CSconnected, a not-for-profit focusing on strengthening the reach and capabilities of the world's first compound semiconductor cluster, located in south Wales, UK.

"We're really building on a strong foundation," enthuses Rupprecht, who applauds all those that work at CSconnected for raising this cluster's international profile and visibility.

According to Rupprecht, his organisation is already incredibly well connected to many people and organisations, both in the compound semiconductor industry and in south Wales. "Our primary goal is to maintain that level of visibility and these relationships."

While focusing on those tasks, Rupprecht and his colleagues are looking to assist in developing skills and strengthening supply chains.

Skills development has been a part of CSconnected's mission for many years. Since 2017, it has been leading an educational group to co-ordinate activities and content. Now the not-for-profit is stepping up its efforts on this front, thanks to winning funding specifically earmarked for skills development from the Cardiff Capital Region.

When it comes to strengthening supply chains, the focus is on specialty components and services.

"We have multiple businesses using many, many local suppliers," remarks Rupprecht, adding: "We have secured funding to help local suppliers increase their business with the cluster companies through grants that help to increase their capacity or capabilities."

#### A broad background

Trained as mechanical engineer in the 1980s, Rupprecht has accumulated a broad range of expertise over his career. He views this diversity as a key asset for running a small organisation, such as CSconnected, that works with a variety of stakeholders operating in different sectors.

For more than the last 20 years, Rupprecht has held senior management roles in tech companies. Over those decades he has experienced diversity in technology, ranging from photonics to MEMS, compound semiconductors and PCB assembly, as well as the nature of the role – at times Rupprecht has led sales, product marketing, business development, operations and business management. However, while he sees this range of skills as important, he puts even more value on having experience in working in both the public and private sector.

To ensure a smooth transition in the leadership of CSconnected, Rupprecht, who joined this not-forprofit in January, and has spent the last few months working closely with its founder, Chris Meadows.

Motivation for parting company with his former employer, Rockley Photonics, has come from a desire to grow the entire industry and support the local community. "It feels like I'm waving the flag both for the region and the industry," reasons Rupprecht.

#### Valuing Vishay

In any industry, uncertainty impedes progress. This issue has hampered the cluster over the last few years, with

Howard Rupprecht, recently appointed as the managing director at CSconnected, has held many senior management positions within the technology sector. Prior to joining CSconnected, Rupprecht held the role

of senior director of operations strategy at Rockley Photonics.

#### NEWS ANALYSIS | CSCONNECTED

differing decisions surrounding the ownership of a jewel in the crown, the 200 mm fab in Newport. This facility, built by Inmos in 1980 and previously owned by several multi-national chipmakers, including Infineon, went into the hands of Nexperia in summer 2021. This takeover by a firm with a Chinese parent company initially had the backing of the British government, before it launched an enquiry and eventually reversed its decision, creating almost three years of disruption and uncertainty.

Commenting on this matter, Rupprecht remarks: "Clarity of policy and greater transparency is needed to avoid future debacles."

Rupprecht sees this fab, one of the biggest employers in the cluster, as an important facility for developing SiC and GaN power electronic capability in south Wales. However, this foundry is capable of making additional contributions, for example, its expertise in deep trench etching would also be valuable for the production of MEMS and photonic devices.

Since its launch in 2017, CSconnected has benefited from financial support from various sources. It is now coming to the end of a 55-month *Strength in Places* programme, which began in November 2020 and raised £25 million from the UK Research Initiative, alongside an additional £18 million from project partners. Another significant supporter of CSconnected is the Cardiff Capital Region, which has just secured £160 million to support local economic growth through the semiconductor investment zone.

For roughly the next three years CSconnected has core funding secured for a range of activities. As Rupprecht looks to strengthen support over that timeframe and beyond, he is keen to avoid dependency on a single project or a single activity, and is keen to pursue various sources of funding.

#### Seeking sovereignty

When the compound semiconductor cluster launched, its backers often argued for efforts that established strong supply chains within south Wales. Related to this cause, Rupprecht is keen to distinguish between sovereign independence and sovereign capability.

"I do think it's important that we have companies operating at different points in the value chain," says Rupprecht, arguing that much of this is now in place. For example, at one end of the spectrum is KLA, producing production equipment, and at the other is Microchip, shipping completed modules.

Over the coming years, it is possible that a supply chain forms in south Wales that begins with a SiC wafer and finishes by supplying a UK automotive company with a power module.

"That concept has already been demonstrated in a programme called Escape," reveals Rupprecht, adding: "But rather than having an integrated vertical UK supply chain, having all the companies

> While attending this year's CS Mantech, Howard Rupprecht (centre) explored an anechoic chamber at the University of Arizona with colleagues from the south Wales cluster. To the far left is Richard Shaddick from the Welsh Government, to the left is Chris Meadows, founder of CSconnected, to the right is Mike Jennings, an academic at Swansea University, and to the far right is Camille Colombier, marketing manager at CSconnected.

exporting their products to multiple competing customers around the world is more important."

#### Moving over

One sign that the cluster is thriving is that start-ups within the UK are relocating to this region to draw on its support and expertise.

Kubos, a pioneer of microLEDs based on cubic GaN, moved to within the cluster earlier this year, so that it can use the fab at the Translational Research Hub at Cardiff University to scale its technology in a costeffective way.

Within the region, there is also a fab at Swansea University, more suited to the development of power devices.

During the launch of the cluster, much was made of the economic benefits it would deliver, in terms of jobs and income generation. It would be easy to put these promises to one side after securing investment, but the cluster is taking these projections very seriously, with evaluations led by Max Munday's group within the Welsh Economic Research Unit at Cardiff University.

Quoting some findings from Munday and coworkers, Rupprecht says that since 2020 there has been a 28 percent increase in direct cluster company employment, and a 27 percent rise in sales over that time frame. "But the real big, big growth was gross added value, which has seen 122 percent growth over the same period."

These encouraging figures underscore the great momentum of the south Wales cluster, which Rupprecht will help to continue, while refining the support that's provided by CSconnected.

# Swelling SiC shipments with a second fab

Opening an additional fab in Nanjing will help to grow sales of SMC Diode Solution's SiC products to around half the company's revenue

#### BY RICHARD STEVENSON, EDITOR, CS MAGAZINE

WITHIN OUR INDUSTRY, one of the biggest trends is the growth in sales of SiC devices by companies with a strong pedigree in producing silicon power electronics. Of the current big five in SiC, Wolfspeed is the only player producing just wideband materials and devices, while STMicroelectronics, Onsemi, Infineon and Rohm have branched out into SiC after establishing a strong portfolio of silicon-based power electronics.

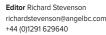

This direction of travel is also being pursued by some of the smaller players, such as SMC Diode Solutions, an American-led company that produces silicon and SiC power devices and has just opened its second fab in Nanjing, China. Opening this 300,000 square foot facility, which cost \$3 billion RMB (US \$410 million) and is creating 300 new jobs, will enable the company to boost production by 1.2 million silicon wafers and 60,000 SiC wafers per year – that equates to more than a quadrupling of the company's annual output.

> SMC's chairwomen and CEO Yunji Corcoran grew up in Nanjing before moving to the US to study for a PhD in Materials Science and Engineering at Stony Brook University. She has held the role of CEO at SMC since its founding in 1997. Founded in 1997, SMC started considering the expansion of its power portfolio to include SiC products in 2014. Back then, when far fewer producers of these power devices competed for sales, SMC's chairwomen and CEO Yunji Corcoran reasoned that expanding into this area would enable her small-to-medium-sized company to expand its range of products and potentially target new applications.

At that time, Corcoran considered diversifying into either SiC or GaN. However, she felt that the pioneers of SiC, particularly Cree, offered a better-defined product. If SMC manufactured these devices, Corcoran believed that it would have a great opportunity to sell them to its existing customers, predominantly large power-supply companies. According to her, compared with GaN power devices, those based on SiC are much closer to SMC's silicon power rectifier family.

SMC started its commercial expansion into SiC with the production of Schottky rectifiers, shipping from 2019 onwards. Beginning its SiC offering with this product made much sense. "We are a silicon diode company," argues Corcoran, pointing out that by starting with a SiC Schottky rectifier, it's been easier to find customers for its first range of products.

Once SMC starting working with SiC, Corcoran and her colleagues could see the tremendous potential for the SiC MOSFET.

Today the company produces both classes of power device. Its SiC Schottky barrier diode portfolio has products with blocking voltages from 600 V to 3.3 kV, and a wide range of current ratings, which can include those that target a customer's particular needs.

The family of SiC MOSFETs is not as broad. There are 1.2 kV MOSFETs with on-resistances ranging from 16 m $\Omega$  to 160 m $\Omega$ , as well as a recently introduced a 1.7 kV variant. However, there are plans to expand the range. "We are working on the 650 and the 3300 at this moment," enthuses Corcoran.

#### NEWS ANALYSIS | POWER ELECTRONICS

Silicon products are dominating SMC's sales today, with those based on SiC only accounting for 10 percent of revenue. Corcoran attributes this modest but growing proportion to working with large and rigorous customers that are thorough when designing and evaluating prototypes.

Just a small fraction of the products that SMC makes in China are sold on the domestic market. 90 percent of business comes from sales oversees. Accounting for this, Corcoran explains that while her home town is Nanjing, she moved to the US to study and work, and it is there that she acquired her business acumen.

Given current tensions between the US and China, one might expect it's not easy for a company to have a fab in Nanjing that ships most of its products overseas. But somewhat surprisingly, SMC's activities have not been impacted by trade wars.

"When the US applied the duties, we were very concerned," admits Corcoran. "But in the end, it did not decrease our sales much, because it's not that easy to source our product outside China." However, the situation may differ surrounding the SiC MOSFET.

#### Outsourcing growth

For the leading manufacturers of SiC diodes and MOSFETs, there is a tendency to shift to greater degrees of vertical integration. Now some companies are beginning with the production of SiC boules from powders and concluding with the shipping of packaged devices.

For SMC, there's little sense in trying to emulate these bigger players. Instead, the company is focusing on what it is good at.

"We are not doing the epi, we're not doing the substrates, and we don't even do the packaging," says Corcoran, who explains that SMC's two fabs are used to process epiwafers into power devices. For the company's silicon products, there is a plant that can package the chips into modules. In the future, the plan is to use this facility to produce modules from SiC MOSFETs made in-house.

SMC uses suppliers based in China for its SiC Schottky-barrier-diode epiwafers, with Corcoran describing the quality as "pretty good".

For MOSFETs, a more complicated structure, the local supply is not as strong. "But we're testing the Chinese substrates," says Corcoran. "I think they are coming along."

She explains that SMC is devoting much effort to understanding which kinds of defect impact the MOSFET. Equipped with that insight, the company will be better prepared to assess the quality of Chinese SiC MOSFET epiwafers, and ensure that when they switch to them, there is no reduction in device performance. Given current tensions between the US and China, one might expect it's not easy for a company to have a fab in Nanjing that ships most of its products overseas. But somewhat surprisingly, SMC's activities have not been impacted by trade wars

According to Corcoran, there are many good reasons for selecting Nanjing for its a second fab. As well as the advantage of being close to the first fab, this location benefits from: strong universities nearby; a good education system; a cost-of-living lower than that found in the cities on the east coast, such as Shanghai; and plenty of engineers with relevant expertise, partly due to a very large, local TMSC fab.

Today, SMC's fabs produce devices from 150 mm SiC epiwafers. However, the tools could be converted to handle 200 mm material – that's a move that is planned when the cost-per-unit-area of the larger format falls.

Another change may be an increase in the proportion of SiC devices produced in the fabs.

"We invested a lot of money in silicon carbide, and I hope we will have more than 50 percent of silicon carbide as our total revenue," says Corcoran. While sales of silicon devices are steadily increasing, she anticipates far faster growth for SiC products.

As well as shifting the balance of the product portfolio, SMC plans to penetrate new markets. The aim is to expand from simply serving the power supply sector to winning sales in renewable energy markets, including electric vehicles.

With more chipmakers with a silicon heritage now pursuing SiC, the chances that supply will satisfy demand are improving, helping humanity's efforts to try and curb its carbon footprint.

> Built in just 21 months, SMC Diode Solution's second fab will increase this chipmaker's production capacity by 1.2 million silicon wafers and 60,000 SiC wafers per year.

### Crushing MOSFETs one tipping point at a time

The growth of GaN is inevitable as it displaces the MOSFET in one application after another

#### BY ALEX LIDOW FROM EFFICIENT POWER CONVERSION

GaN POWER TRANSISTORS are at a tipping point. It's a juncture where any small change or action leads to significant and often irreversible effects, and the future of these devices has reached a point of no return, where the dynamics of the situation shift dramatically.

This tipping point is following more than a decade of volume production of the GaN transistor. Since our company, Efficient Power Conversion (EPC), starting producing them in March 2010, they have repeatedly been touted as the replacement for the aging power MOSFET. Fourteen years on, the promise that GaN will crush silicon is now being realised.

To understand the changing rate of adoption of GaN, one can draw lessons from the 45-year-old power MOSFET. It's a device I know intimately, having been one of its first developers, as well as an instrumental player in the launch of the first product in November 1978. Back then the bipolar transistor was the incumbent power transistor. Despite being ten times slower, it was much cheaper than the MOSFET.

MOSFETs eventually crushed bipolar transistors. This did not occur overnight, but one application at a time. The first tipping point came from desktop computers, with Apple and IBM turning to the MOSFET for their AC-DC power supplies.

By adopting the superior transistor of the day, these tech giants could shrink their power supplies enough to fit inside desktop housings, a breakthrough that played a crucial role in widespread adoption of these computers.

Following this breakthrough, our MOSFETs continued to increase their deployment in highperformance applications while we focused on reducing costs and accelerating the learning curve as quickly as possible. Initially adoption took time, but jumps occurred whenever a new application ramped successfully. With each new tipping point for an application, the benefits to the business would extend beyond this individual triumph to trim the time and increase the likelihood of subsequent successes. Motor drives for high-speed plotters ramped in 1982. Anti-lock brakes ramped in 1985.

By 1988, thanks to higher volumes and significant capital investments, the manufacturing cost for the MOSFET had plummeted to below that of the bipolar transistor. Since then, the world never looked back. At that point in time the MOSFET had officially reached its tipping point. And that's exactly where GaN stands today.

GaN has already been adopted in several disruptive technologies, to the point where MOSFETs are no longer even considered for new designs. Each novel application for GaN can be thought of as having crossed an individual tipping point. This roadmap for ever-expanding adoption includes lidar, fast chargers, satellite electronics, AI, DC-DC power supplies, and humanoid robots.

With nearly fifty years of experience to guide us, we can identify four key factors that have played a crucial role in ensuring that GaN reaches its tipping point and finally surpass the MOSFET. These four factors, which exist in addition to all the cost, performance, and reliability requirements, are as follows: the design community now clearly

#### OPINION I GALLIUM NITRIDE

understands the large value derived from GaN; the targeted application is facing a changing landscape that leads to many open design windows; the adoption of GaN is being pursued by user community leaders, who are enjoying subsequent business success; and the existence of well-trained technical talent has emerged, which is capable of working with GaN and efficiently extracting its benefits.

For GaN technology, lidar provided the first application for crossing the tipping point. The simple reason behind this success is that GaN is capable of operating at far faster speeds than the MOSFET. Dave Hall, the visionary founder of Velodyne and the father of modern lidar, fully appreciated this benefit, realising that GaN technology enables a car sensor to see farther and with higher resolution than radar. Hall developed a spinning lidar system using EPC's first-generation GaN transistors, sparking the birth of the autonomous car.

Considering lidar from the perspective of tipping point elements, one can conclude that: Hall had a clear understanding of the substantial value derived from GaN; lidar opened many new design windows as it became an essential sensor for autonomous vehicles; Velodyne had huge success, attracting lots of customers and competitors; and Hall, with some assistance from EPC's engineers, knew how to extract the maximum performance from of these transistors.

The second application to reach a tipping point is the satellite power supply. As well as outperforming the MOSFETs, GaN is virtually immune from degradation caused by radiation in space. The key champion in helping to reach this particular tipping point is Dan Sable, CEO and founder of VPT. Today, just four years after initial deployment in this application, GaN transistors account for 30 percent of the satellite market for MOSFETs, and are on track to take the final 70 percent as legacy designs become obsolete or uneconomical.

Providing the third tipping point for GaN is the fast charger. Here the standout is Gene Sheridan, CEO and co-founder of Navitas Semiconductor. Today, virtually all fast chargers use GaN, thanks to its

knowledge in overlapping sectors

capability to deliver high powers and recharge power-hungry cell phones, tablets and laptops in a fraction of the time that silicon-based chargers would take.

Following all this success, we are now standing on the precipice of one of the most significant tipping points in recent history: Al. Servers for Al, such as those made by Nvidia, have crossed a crucial threshold, with virtually all of them utilising GaN in the on-board 48 V – 12 V (or in some cases 5 V) DC-DC converters.

While the full impact of the AI revolution is only beginning to be fathomed, one inevitable outcome is related to the tipping point of humanoid robots. These robots, equipped with 40 or more high-performance motors, rely heavily on GaN technology for higher torque density, higher power efficiency, less noise, and a more compact design. It is a set of requirements that is making silicon obsolete and GaN indispensable.

Taking a step back from specific successes, one can see that the tipping points for GaN are occurring with greater speed and a higher frequency. As has been the case for the MOSFET, every new development is educating the user community on GaN's unique value and accelerating its inevitable adoption in additional applications. And with each new positive experience and business success resulting from GaN, global implementation is rising, creating more and more design-window opportunities. Additional gains are the emergence of new GaN advocates within the user community, and new sources of capital. Over the last few years, thousands of trained design and manufacturing engineers have gone up the learning curve, and now know how to extract the additional efficiencies of GaN. Adding to these factors, GaN is proven to be more reliable than silicon, across a wide range of power levels, with a price that is comparable to the MOSFET. Due to all these compelling factors, it is inevitable that GaN's adoption will only accelerate, consuming the \$12 billion MOSFET market while creating new markets of its own. In sum, GaN's tipping point is here.

Expertise: Moderators, Markets, 30 Years + Pedigree

Reach: Specialist vertical databases

**Branding:** Message delivery to high level influencers via various in house established magazines, websites, events and social media

### COMPOUND SSILICON PUP POWER PHOTONIC SENSOR SEMICONDUCTOR FOR POWER CONDUCTOR STATE CONCUMPTIONS

Specialists with 30 year+ pedigree and in-depth

Jackie Cannon T: 01923 690205 E: jackie@angelwebinar.co.uk W: www.angelwebinar.co.uk T: +44 (0)2476 718 970 E: info@angelbc.com W: www.angelbc.com

# What does the future hold for the compound semiconductor industry?

Growth is forecast for all leading forms of compound semiconductor device, driven in part by demand for more data, an uptake in AI, increasing opportunities for satellite communication and growing sales of electric vehicles

#### BY ALI JAFFAL, TAHA AYARI AND AYMEN GHORBEL FROM YOLE GROUP

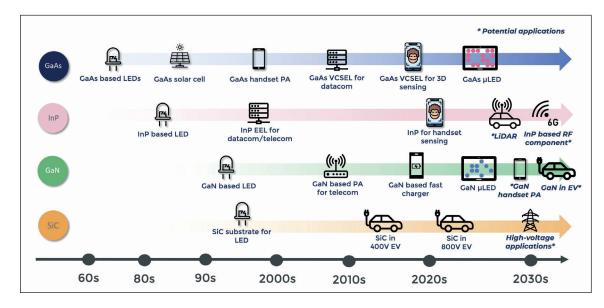

THE COMPOUND SEMICONDUCTOR industry is now booming, having established itself as a significant player alongside silicon-based semiconductors, bringing not only superior performance but also new functionalities that silicon cannot achieve, such as light emission. These semiconductors are becoming increasingly popular in power electronics, RF, photonics, and microLED displays. For power applications, sales are dominated by SiC and GaN devices; for RF applications, GaAs and GaN devices lead the way; for photonics, InP and GaAs are the leading material systems; and for LED/display applications, GaAs and sapphire are the key substrate materials.

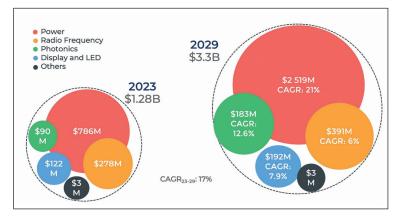

The compound semiconductor industry is wellestablished, having formed an entire ecosystem, with its own equipment for crystal growth, wafer manufacturing, front-end manufacturing, testing and packaging. According to recent market research by our company, Yole Group, the value of compound semiconductor substrates is rising at a compound annual growth rate of 17 percent over the 2023 to 2029 timeframe, to reach US\$3.3 billion<sup>1</sup>. Underpinning this growth is an expansion in key facilities that are supporting a transition to larger substrates. There is a migration to 200 mm wafers

for SiC and GaN-on-silicon, driven by power electronics growth in the automotive and consumer markets; in the photonics sector, the use of 150 mm InP is on the rise, spurred on by the datacom market; and in the microLED displays market, there is increasing use of 200 mm GaAs and sapphire. However, the latter application has been hit badly by Apple, who closed its microLED project earlier this year, after being the main player pushing for 200 mm substrates with it partner ams-Osram<sup>2</sup>.

Looking in more detail at the substrate market, a number of SiC substrate makers, including Coherent, Wolfspeed, SK Siltron, SICC and TankeBlue, are actively working on the 200 mm format, with initial volume shipments starting late last year. The Chinese SiC substrate supply is growing rapidly, and is fiercely competing with the US<sup>8</sup>.

For GaN-on-silicon for power applications, for the last 2-3 years volume production has involved 200 mm wafers, the format employed by the massive Chinese company Innoscience. All recent investments and capacity expansions are focused on this platform, including Infineon's GaN fabs in Villach and Kulim.

When it comes to InP, the mainstream substrate size is still 75 mm. However, market leaders such as Sumitomo Electric and AXT have the capability to produce good-quality 150 mm InP substrates, and this year they are shipping significant volumes for R&D. Sales of higher volumes are expected over the next few years.

Regarding GaAs, 150 mm substrates continue to dominate photonics and RF applications. Here the market is dominated by Sumitomo Electric and Freiberger.

As well as high-quality substrates, optimal devices demand high-quality epitaxy. This leaves chipmakers with one of two choices – to adopt the captive approach, and undertake epitaxy in-house; or to use an 'open' approach, drawing on the epitaxial services

#### MARKET ANALYSIS | THE CS INDUSTRY

of a number of players, including IQE, Landmark, VPEC, IntelliEPI and Sumitomo Chemical. We estimate that between 2023 and 2029 the open epiwafer market will expand at a compound annual growth rate of 19 percent to hit US\$2.5 billion. Sales from the SiC open epiwafer market are already soaring, and will climb to account for 64 percent of that total by 2029.

#### EVs and fast chargers are gaining

Since 2017-2018, sales of SiC and GaN devices have experienced rapid growth. Helping this has been Tesla's adoption of SiC in its inverters, a move that marked significant disruption in the EV market. Here SiC plays a crucial role in 800 V fast charging, significantly reducing the time it takes to accomplish this task. Today, high-volume EVs, such as BYD's Han and Hyundai's lonig 5, are being shipped with SiC technology. Sales to automakers have ramped the revenue of leading device manufacturers like STMicroelectronics, onsemi, Infineon, Wolfspeed, and Rohm. These pioneers of high-volume SiC power device production all realised record revenue in 2023, and are on track to net sales from these products of US\$1 billion by 2024-2025. We forecast that by 2029 the total market for SiC devices will exceed US\$9.6 billion<sup>3</sup>, with ramping revenue not only driven by the EV market – sales growth will also come from industrial, energy, and rail applications. Supporting this substantial hike in revenue is capacity expansion, business integration, and innovative business models.

Meanwhile, in the power GaN market the primary drivers of growth are still consumer applications. Recent trends include chargers with higher power capacities of up to 300 W, along with power supplies and motor drives for home appliances that offer a higher efficiency and compactness. We are foreseeing two additional catalysts for power GaN growth: automotive and data-centre applications. Due to these contributions, the power GaN market will be propelled to more than US\$2.25 billion by 2029<sup>3</sup>.

#### **Evolutions in RF**

In the RF domain, GaAs technology is a wellestablished building block for RF front-end modules in smartphones, and is showing growth opportunities in automotive applications. The other key material in RF is GaN-on-SiC. Over the last two decades this has been used to develop power amplifiers for defence and aerospace applications, with efforts given much support by the US government. With the advent of 5G, new macro base stations are adopting GaN technology over existing silicon LDMOS, a move that enables more complex architectures at higher frequencies with greater efficiency. RF GaN technology is also expanding into markets such as satellite communication and RF energy. According to our recent analysis, the total RF GaN device market will grow from US\$1.1 billion in 2023 to US\$2.07 billion by 2029<sup>4,7</sup>.

An alternative material system for RF devices that has garnered interest in recent years is GaNon-silicon. Last year Infineon introduced a GaNon-silicon power amplifier module processed on 200 mm wafers to the telecom infrastructure market, directly competing with GaN-on-SiC technology. With the potential to scale to 300 mm, RF GaN-onsilicon could offer performance and cost benefits to compete with GaAs technology for 6G PAs. Other companies exploring RF GaN-on-silicon technology include UMC, STMicroelectronics, GlobalFoundries, Sony and Finwave. As these newcomers invest in power GaN-on-silicon, they are able to use 200 mm facilities to enter RF applications without having to make risky investments.

A pioneer of 150 mm RF GaN-on-silicon technology is Macom. This US chipmaker has secured design wins for military tactical radios for over a decade. Last year Macom expanded into satellite communication by acquiring Ommic SAS, and enhanced its GaN-on-SiC portfolio by buying Wolfspeed's RF business. These acquisitions have elevated Macom to one of today's top four RF GaN device players.

#### Al drives photonics growth

The other major applications within the compound semiconductor industry are based on photonics. A significant market here is the GaAs VCSEL for 3D sensing in smartphones. This application began in 2017 with Apple, followed by Android makers like Huawei and Xiaomi. While US-China sanctions have slowed uptake, there has been a re-adoption of GaAs VCSELs for 3D sensing, with Chinese OEMs such as Huawei, in this case using this technology in its Mate 60 Pro model. This leads one to wonder whether we will now see more Chinese OEMs adopting GaAs VCSELs in the consumer market - and whether these chipmakers will be able to meet the cost target for low-end smartphones. What is beyond question is that GaAs VCSEL supply is growing in China, with several players demonstrating excellent capabilities, including Vertilite, Everbright photonics, RaySea, and QM lasers. This expertise will aid the adoption of VCSELs for automotive lidar in China. Note that China represents the biggest market for automotive lidar.

> 2023-2029 compound semiconductor substrate market by application (\$M). Source: Status of the Compound Semiconductor Industrv report, Yole Intelligence, 2024. Credit: Yole Intelligence.

#### MARKET ANALYSIS I THE CS INDUSTRY

Evolution of compound semiconductor applications - inflection points. Source: Status of the Compound Semiconductor Industry report, Yole Intelligence, 2024. Credit: Yole Intelligence.

In the optical communications sector, AI is driving GaAs VCSEL adoption in data centres. These emitters are being deployed in optical transceivers that transmit and receive data at 800G and beyond. Key to such high speeds are 100G/lane VCSELs. Coherent and Broadcom are already massproducing these devices, and Lumentum is set to follow later this year. Development of 200G/lane VCSELs for 1.6Tb pluggables is underway, with mass production forecast for 2026-2027. This begs the question: What technology will be used in 1.6Tb optical transceivers for short-reach applications between 2024 and 2026?

Also driven by AI are sales of InP edge-emitting lasers, with shipments to this application dominated by 100G and 200G/lane InP electro-absorptionmodulated lasers and high-power continuous-wave distributed-feedback lasers that are enabling 800G and 1.6T optical transceivers in long-reach applications.

Back in 2023, AI had yet to make a significant impact, and that year was a challenging one for the InP business. Headwinds came from a slowdown and increased inventories from hyperscalers and cloud service providers, as well as reduced consumer market adoption when Apple reverted to

#### FURTHER READING / REFERENCE

- [1] Status of the Compound Semiconductor Industry 2024 report, Yole Group

- > [2] "Did Apple just kill the microLED industry?" article, Yole Group

- [3] Power SiC and GaN Compound Semiconductor Market Monitor

- > [4] RF GaN Compound Semiconductor Market Monitor

- [5] Photonic GaAs and InP Compound Semiconductor Market Monitor

- [6] Emerging Semiconductor Substrates 2023

- > [7] RF GaN 2024

- > [8] Power SiC Manufacturing 2024

the GaAs VCSEL for proximity sensors, instead of using InP edge-emitting lasers.

Since the beginning of this year, the situation in the InP market has improved significantly. This is especially true for the datacom sector, which is driving growth in substrates, epiwafers, and devices. Several encouraging signs have emerged, such as Lumentum's acquisition of Cloudlight to ensure full vertical integration in its datacom business. However, the most significant development is the announcement of a 150 mm InP fab at Coherent. Will we now see other players adopting the 150 mm InP platform to reduce costs and meet market demand, especially if InP re-enters the consumer market in the short term and 6G in the long term?

After weighing up all the likely scenarios, we forecast that the GaAs and InP photonic bare die markets will reach US\$1.94 billion and US\$.3.5 billion, respectively, in 2029<sup>5</sup>.

#### What's next?

To push performance and cost limits, the compound semiconductor industry continues to explore new materials, platforms and designs. Now one critical question is this: Which emerging semiconductor substrate will be the next game changer? The answer is not obvious, as material scientists and industrial players are developing a number of new foundations for epitaxial growth, including  $Ga_2O_3$ , diamond, bulk GaN, GaSb, InSb, bulk AIN, smart-SiC, and an engineered substrate based on polycrystalline AIN. We are projecting that the emerging substrate market will grow to US\$264.5 million by 2028<sup>6</sup>, driven by power applications, particularly using engineered substrates.

Considering all these advances, the compound semiconductor market is set for sustained growth, especially in sectors where silicon falls short. The future of technology will undoubtedly be shaped by the ongoing evolution and impact of compound semiconductors.

Dimensions :

- 1½ inches

- 2 inches

- 3 inches

Possibilitiy of substrate support with cavity and washer, on request and according to drawings

- Stock of platens blanks for all types of MBE from various manufacturers.

- « Usable in clean rooms » Platens and washers produced according to drawings.

Cleaning and Dégassing

**RABOUTET SA** Avenue Louis Armand

B.P. 31

74301 Cluses Cedex FRANCE T. +33 (0)4 50 98 15 18 • info@raboutet.fr

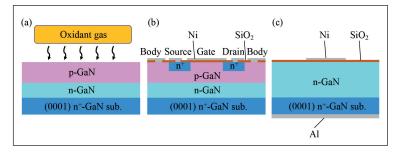

#### TECHNOLOGY | POWER ELECTRONICS

# Bipolar *p*-FETs enable all-GaN power integration

Bipolar transport overcomes the inherent barriers of GaN *p*-FETs to pave the way to higher current densities

# BY MENGYUAN HUA FROM SOUTHERN UNIVERSITY OF SCIENCE AND TECHNOLOGY

GaN POWER DEVICES have many attributes. They are renowned for their exceptional switching efficiency and high power density, strengths that are driving the development of miniaturised, energysaving power systems. Thanks to a wide bandgap and stable material properties, GaN-based power devices are also capable of maintaining a good performance in challenging environments, such as extreme temperatures and irradiation conditions. And in addition to these capabilities, GaN power devices are revolutionising power systems towards higher levels of integration and intelligence. Given all this, it's of no surprise that GaN-based HEMTs have rapidly surpassed traditional silicon devices to play an indispensable role in a number of fields, ranging from consumer electronics to industrial power supplies.

However, while much progress has been made to date, there is still much more to do. In this regard, one important area for improvement is the GaN power IC - today there is a significant challenge in realising the seamless integration of power devices with low-voltage peripheral circuits. In the latest approaches to hybrid integration, the siliconbased circuits that are used for driving, sensing and protecting functions, are integrated with GaN power devices through packaging. This results in non-negligible parasitic inductance, which can lead to gate ringing, particularly during high-power fast-switching transients. Two downsides of this are a limited switching speed and a compromised system reliability. What's more, the silicon devices in these hybrid designs fail to handle extreme environments as well as GaN devices, narrowing the

#### TECHNOLOGY | POWER ELECTRONICS

application scope. Consequently, moving to an all-GaN integration strategy has much appeal, including liberation from parasitic issues and the constraints of silicon-based devices, as well as the opportunity to unleash the full potential of GaN power ICs.

There are several straightforward approaches for all-GaN integration, such as leveraging established *n*-channel device technology, resistor-transistor logic and direct-coupled FET logic. However, all these methods are impaired by excessive power consumption, due to a significant static current that diminishes the efficiency of the power IC and necessitates enhanced heat dissipation strategies.

A promising solution to effectively blocking the static current is the GaN-based complementary logic IC, incorporating both the *p*-FET and the *n*-FET. In this design, the existing *p*-GaN layer on the E-mode GaN HEMT platform is used to fabricate the *p*-FET.

The simplicity of this approach has attracted much attention, leading to efforts directed at boosting *p*-FET performance via strategies that include reducing interface trap states, downscaling the device, and engineering the gate dielectric. But even with these refinements, the current density of the *p*-FET falls far short of that of the GaN HEMT. This gap in current density between the GaN *p*-FET and its *n*-FET sibling poses a significant hurdle for progressing GaN CMOS technology.

Limiting the current density of the GaN *p*-FET is the low conductivity of the *p*-GaN layer. Due to a considerable effective mass and strong scattering, the mobility of holes is nearly two orders of magnitude lower than it is for electrons. Compounding this issue, magnesium is the only effective dopant available for *p*-type GaN. Unfortunately, it's far from an ideal dopant, being held back by a low activation ratio and a deep energy level that restricts the hole concentration in the *p*-GaN layer to  $10^{18}$  cm<sup>-3</sup>. While innovative epi-structure designs involving N-polar GaN, AlN and GaN heterostructures, superlattices, and InGaN insert layers are able to enhance hole mobility or density, these approaches are incompatible with the existing commercial *p*-GaN gate HEMT platform.

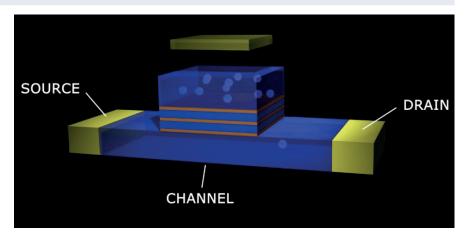

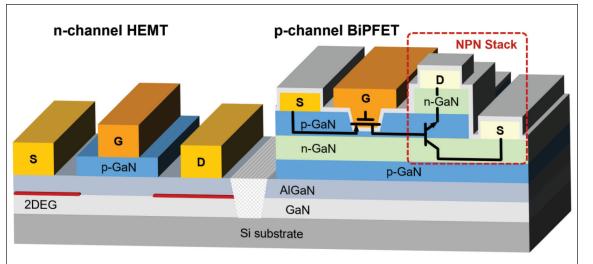

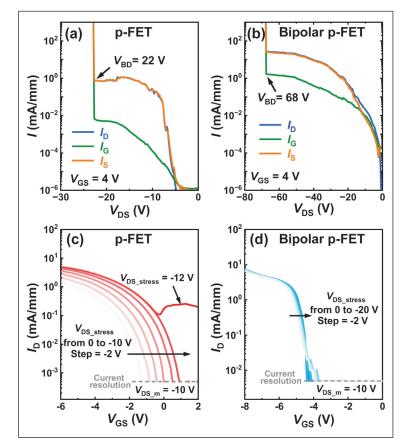

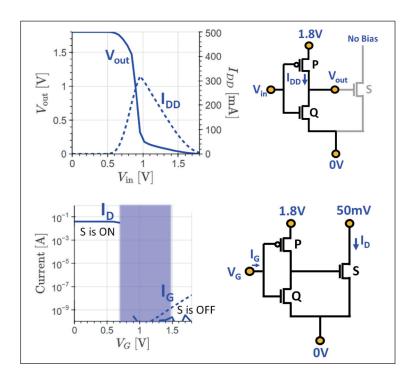

To overcome this challenge, our team at the Southern University of Science and Technology is pursuing an innovative GaN *p*-FET architecture endowed with a bipolar transportation capability (see Figure 1). This bipolar *p*-FET (BiPFET) features a conventional *p*-FET gate for maintaining *p*-type control logic, as well as an additional *n-p-n* GaN stack, which functions as a bipolar junction transistor that amplifies the current density. Operating in the on state, the p-channel turns on with a gate voltage below the threshold voltage. In this state, a minor hole current flows through the *p*-channel, and is injected into the base region of the *n-p-n* stack, initiating a substantial electron current. With electrons serving as majority carriers, the current density of the BiPFET is no longer confined by holes.

In addition to its remarkable conduction capability, the BiPFET inherently ensures a more stable threshold voltage and a higher drain-to-source breakdown voltage. When in the off-state, the bottom *n*-GaN region acts as a back-side field plate, extending the depletion region from the *p*-FET gate to the drain side. Thanks to this there is a more uniform electric field distribution, alleviating stress on the *p*-FET gate and improving the off-state breakdown voltage.

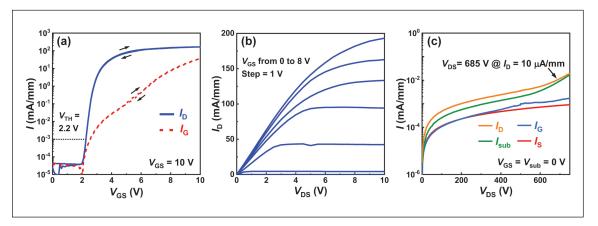

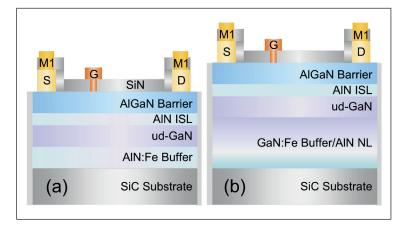

Another advantage of the BiPFET technology is that it is ready for integration with GaN HEMTs, thereby demonstrating outstanding compatibility and feasibility. The *n-p-n* stack can be realised through MOCVD growth, and the process flow of the BiPFET aligns well with that of the standard *p*-GaN gate HEMT. These strengths underscore the promising potential of the BiFET for the development of all-GaN ICs.

#### Demonstrating the concept

We have investigated the capability of our BiPFETs by producing these devices from a commercial

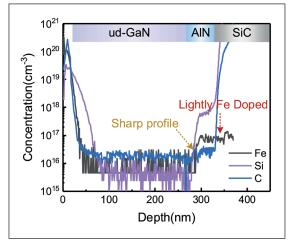

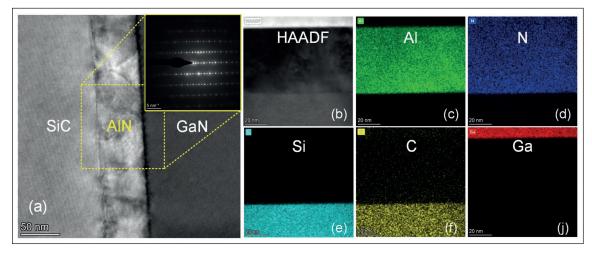

Figure 1. A promising option for GaN integration is the combination of the p-GaN gate HEMT and the bipolar p-FET. *p*-GaN HEMT platform featuring a 4.2 µm-thick GaN buffer layer, a 420 nm-thick undoped GaN channel layer, a 15 nm-thick  $AI_{0.25}Ga_{0.75}N$  barrier layer, and a 75 nm-thick *p*-GaN layer with magnesium doping at a concentration of  $2.5 \times 10^{19}$  cm<sup>-3</sup>. Using this platform, our partners at Suzhou Institute of Nano-tech and Nano-bionics, Chinese Academy of Sciences, led by Qian Sun, selectively grew the *n-p-n* stack by MOCVD. This stack comprises

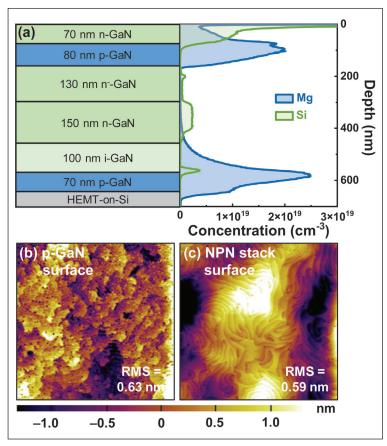

➤ Figure 2. (a) An n-p-n epi-structure on the conventional p-GaN HEMT platform and a secondary ion mass spectrometry depth profile of magnesium and silicon dopants. Atomic force microscopy images of the (b) initial p-GaN surface and (c) GaN surface after n-p-n stack growth on the E-mode GaN HEMT platform.

a 150 nm-thick bottom *n*-GaN collector layer with a silicon doping concentration of  $3 \times 10^{18}$  cm<sup>-3</sup>, a 130 nm-thick *n*-GaN layer with a silicon doping concentration of  $5 \times 10^{17}$  cm<sup>-3</sup> to enhance voltage blocking capability, an 80 nm-thick *p*-GaN base layer with a magnesium doping concentration of  $2 \times 10^{19}$  cm<sup>-3</sup>, and a 70 nm top *n*-GaN emitter layer with a silicon doping concentration of  $10^{19}$  cm<sup>-3</sup> (see Figure 2(a)).

Note that we insert a 100-nm undoped GaN layer between the bottom n-GaN and p-GaN layers to mitigate the impact of the magnesium memory effect. Encouragingly, this n-p-n epi-stack preserves the favourable surface morphology of the original p-GaN, with clear atomic steps (see Figure 2(b) and (c)).

The fabrication of our BiPFETs starts with two-step etching, using a chlorine-based inductively coupled plasma recipe. The first step involves etching the collector region to remove the *n*-GaN layer, part of the *p*-GaN base layer, and then the hard mask SiO<sub>2</sub> in the *p*-FET region. During the second step, we simultaneously etch the top *n*-GaN in the *p*-FET region and the remaining *p*-GaN in the collector region until we reach the target depth. After removing the hard mask, we activate dopants in the *p*-GaN layer by annealing our samples under nitrogen gas at 750°C for 30 minutes.

Following dopant activation, we add p- and n-ohmic contacts. To ensure an excellent p-ohmic contact on the etched p-GaN surface, we sputter a 50 nm-thick layer of magnesium on the contact region, prior to annealing at 600°C, to diffuse this metal into the GaN layer. After removing the annealed magnesium layer, we form p-ohmic contacts with conventional evaporation and annealing processes.

According to electrical measurements, the contact and sheet resistance for our *p*-ohmic contacts are  $57 \Omega$  mm and  $65 k\Omega/sq$ , respectively. These values are comparable to those for a fresh bare *p*-GaN layer without any etching.

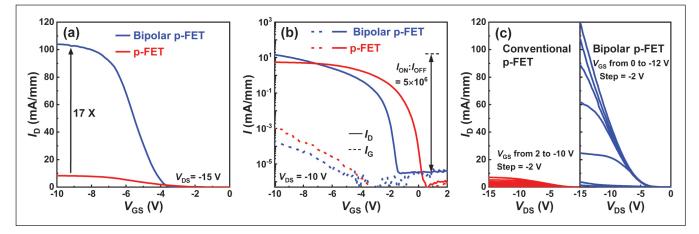

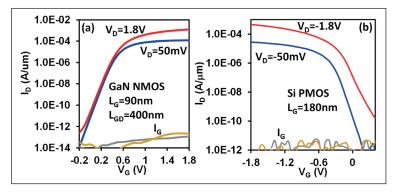

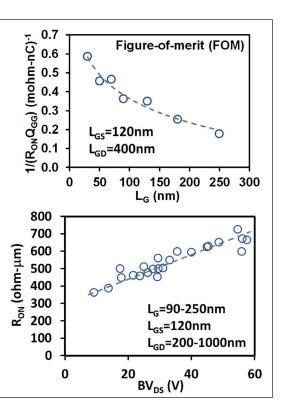

Figure 3. (a) Linear-scale transfer, (b) log-scale transfer and gate leakage current, and (c) output characteristics of BiPFETs compared with conventional p-FETs.

#### TECHNOLOGY | POWER ELECTRONICS

Our next step is to form *n*-ohmic contacts on upper and lower *n*-GaN layers through photolithography, evaporation, lift-off, and annealing.

Following contact formation, we undertake slow inductively coupled plasma etching to gradually recess the gate trench. By going slow, we minimise plasma-induced damage. Then, using atomic layer deposition, we add a layer of  $Al_2O_3$  that is approximately 22 nm-thick and serves as the *p*-FET gate dielectric. Evaporation of the gate electrodes follows, before we finalise the fabrication by defining contact vias and probing pads.

#### Improved current density ...

By integrating the *n-p-n* stack into the *p*-FET, we realise a substantial increase in the current density of the GaN *p*-FET. With identical MIS-gate dimensions as the *p*-FET, our BiPFET delivers a 17-fold hike in current density to more than 100 mA mm<sup>-1</sup> (see Figure 3). This enhancement in current density is particularly pronounced when comparing output characteristics.

It's worth noting that this substantial increase in current density is realised without compromising the performance of the MIS-gate. Our BiPFET maintains a high current on-off ratio and exhibits a low gateleakage current, signifying the well-preserved performance of the MIS gate (see Figure 3(b)). With moderate device scaling, we anticipate an increase in current density.

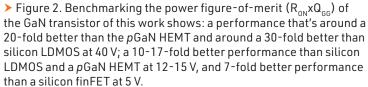

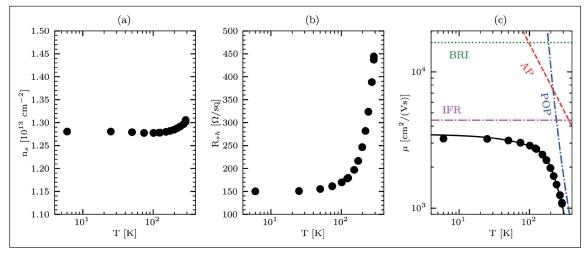

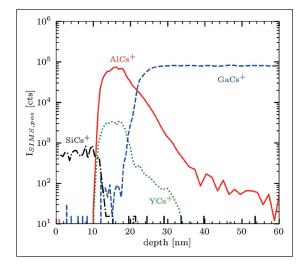

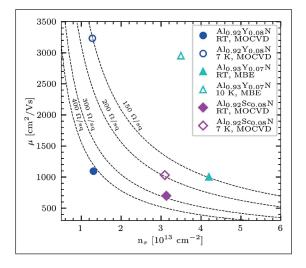

#### ... and enhanced stability