VOLUME 27 ISSUE VII 2021

@compoundsemi

www.compoundsemiconductor.net

## **INSIDE**

News, Analysis, Features, Editorial View, Research Review and much more

## **II-VI'S GOLDEN ANNIVERSARY**

A candid interview with II-VI co-founder Carl Johnson offers a wonderful insight into the early years

## **PROBLEMATIC POINT DEFECTS**

The intrinsic light-quenching point defect is dragging down the efficiency of GaN-based LEDs

## MORE MARKETS FOR MICROLEDS

Many opportunities beckon for light engines made with microLEDs that vary in pitch, size and wavelength

# Global mega trends require best performance III-V materials

## AIX G5+ C

- Next generation electric vehicles

- Efficient power supplies

- Wireless charging

- Next generation displays

- 4G/5G networks

Discover the MOCVD tool of record for all advanced GaN applications

\_\_ Made

\_\_in

Germany

info@aixtron.com www.aixtron.com

# VIEWPOINT

BY DR RICHARD STEVENSON, EDITOR

## Crystal clear objectives

In general, our industry is propelled by advances in device design, as this opens up new markets and swells sales. However, there are times when progress comes from other breakthroughs. Examples include the development of a new metrology techniques offering valuable insight, computational software that holds the key to designing a better chip, and the growth of larger crystals that unlock the door to producing more devices at lower cost.

During the latter years of the twentieth century, engineers devoted much effort to increasing the size of the GaAs substrate, as this supported a ramp in volumes of devices for switching and amplifying RF signals in mobile phones. By the turn of the millennia, leading fabs had installed 150 mm lines, which are still at the forefront of production today.

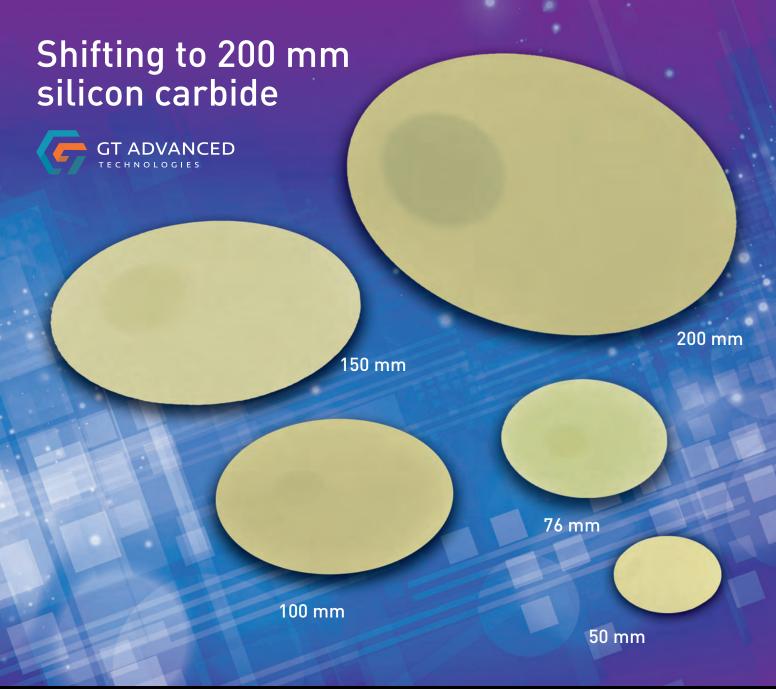

Now it is SiC that is seeing a shift to larger substrates to support an increase in the production of power devices, including those deployed in electric vehicles. Twenty years ago, producers of this foundation could only offer a limited supply of 50 mm substrates, but today 150 mm is the norm, and there are well-publicised moves to manufacture diodes and MOSFETs on a 200 mm variant. Cree's Wolfspeed arm is already building a massive fab for that dimension, and this summer STMicroelectronics joined the ranks of companies that can fabricate SiC substrates of this size.

One company helping the growers of SiC material to upgrade their output to the larger size is GT Advanced Technologies. Its contribution is welcome, because scaling of SiC is not easy, due to the lack of growth from the melt. Several alternative technologies are available, offering differing levels of maturity, with physical vapour transport leading the way (to find out why, head to p. 20).

A major supplier of SiC is II-VI, which lay claim to producing the world's first 200 mm SiC substrate back in 2015. This multi-national, celebrating its fiftieth anniversary this year, has crystal growth in its DNA. Just turn to p. 28 to hear directly from the company's first leader, Carl Johnson, on how his PhD work on cadmium telluride in the late 1960s led him to meet his co-founder, a crystal grower named James Hawkey, and go on to start a company.

To ensure the success of this start-up, the founders had to master the growth of cadmium telluride, a material needed for carbon dioxide lasers. The duo went through some tricky times, blowing up furnaces far too frequently, but by drawing on their complementary skills and staying positive, they got through this setback and began to grow the company.

As well as his great business acumen, Johnson must be admired for what he's giving back to our industry. Through the II-VI Foundation that he's initiated and funded, he is helping to bring on a new generation of scientists and engineers. Who knows, some might even go on to be the crystal growers of tomorrow, underpinning further advances within our industry.

Free weekly e-news roundup go to: www.compoundsemiconductor.net

Introducing larger wafers will accelerate the production of power electronic devices in fully depreciated 200 mm fabs

**CARBIDE**

## 28 II-VI: Milestones of its first leader

The first of a pair of features to mark the fiftieth anniversary of the compound semiconductor powerhouse II-VI

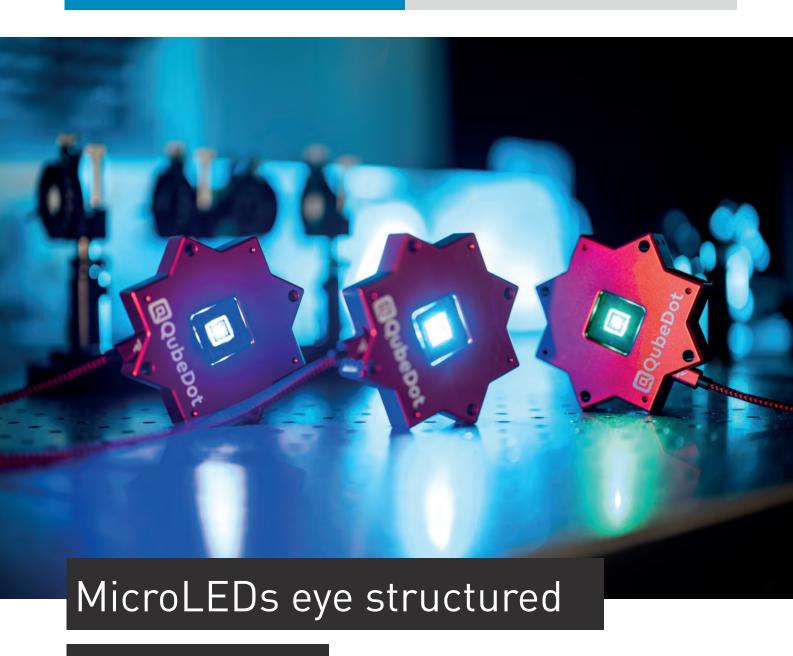

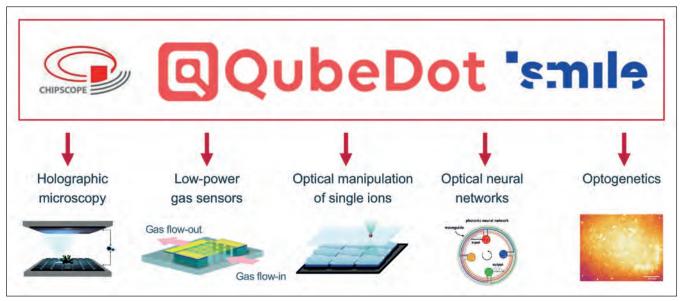

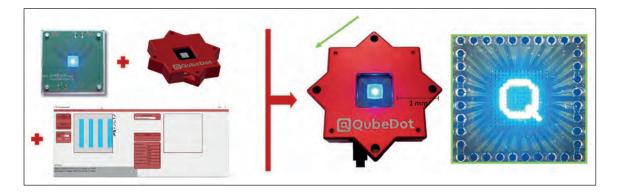

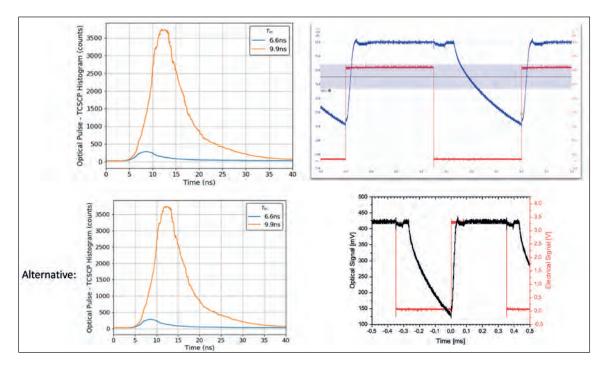

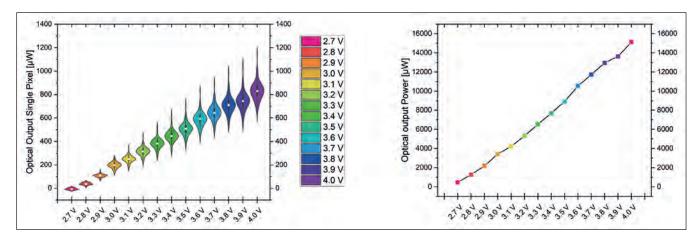

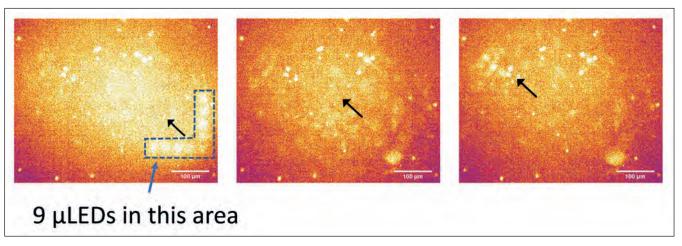

# 34 MicroLEDs eye structured illumination

Light engines formed from arrays of GaN microLEDs with a varying pitch, size and wavelength target numerous applications

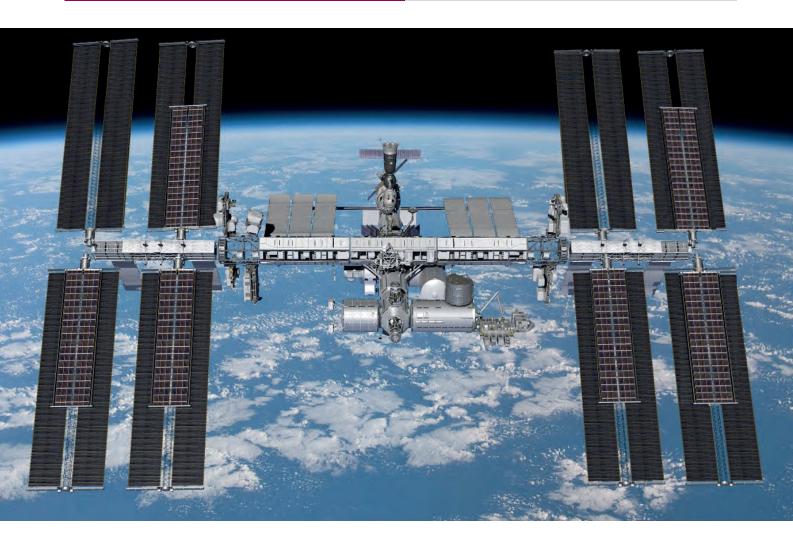

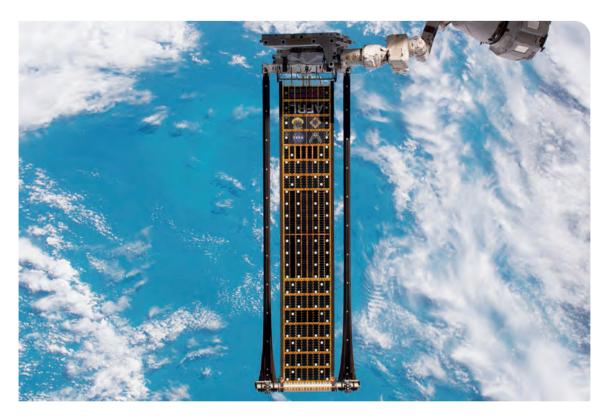

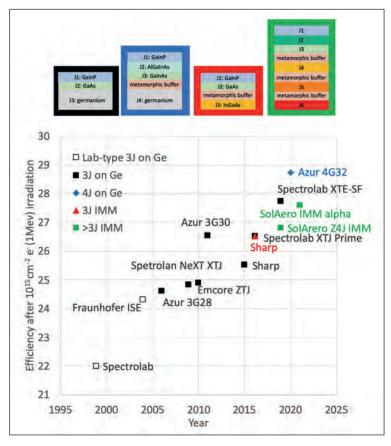

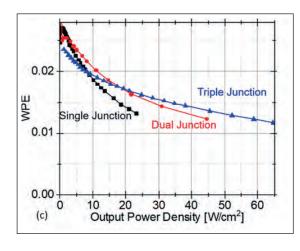

## 40 Refining the multijunction solar cell

Multi-junction cells continue to improve by offering greater flexibility, a path towards streamlined manufacture and falling production costs

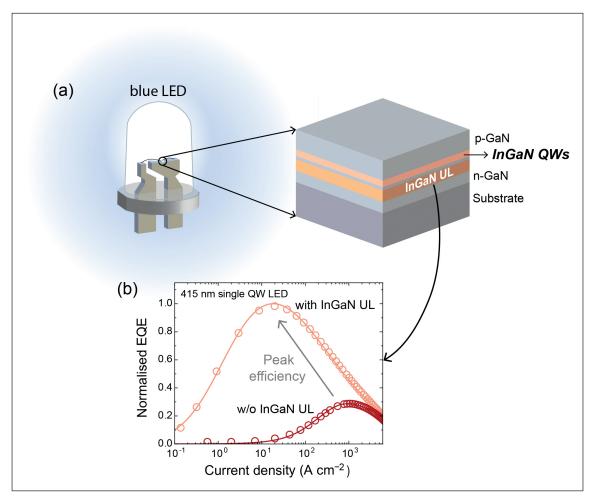

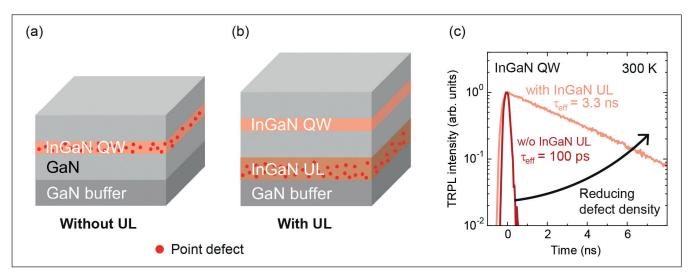

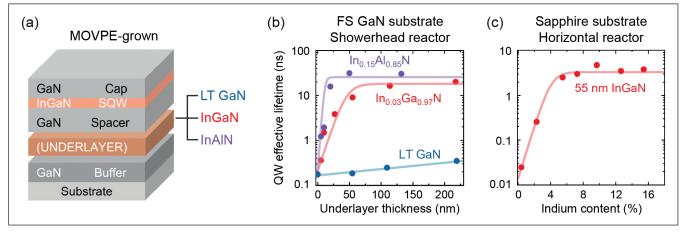

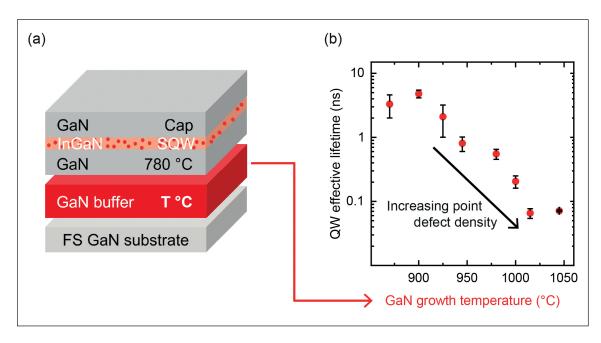

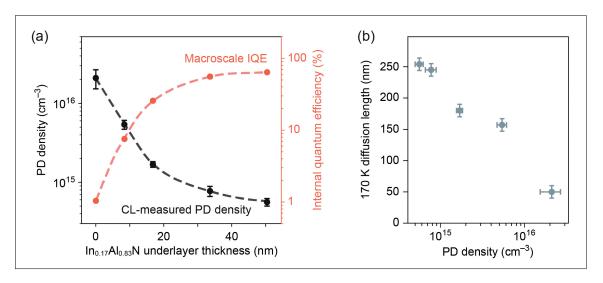

## 46 Point defects: the ultimate blue LED efficiency killers

A previously unknown class of intrinsic, light-quenching point defect is unveiled in InGaN quantum wells

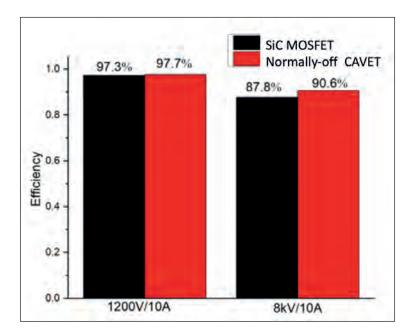

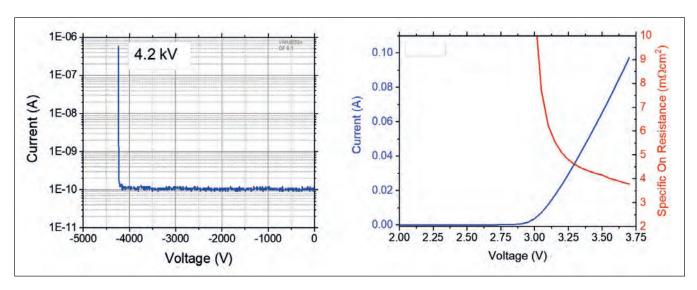

## 54 Targeting mediumvoltage power electronics with vertical GaN devices

Vertical GaN *p-n* diodes combine excellent efficiencies with incredibly fast protection from unwanted electromagnetic pulses

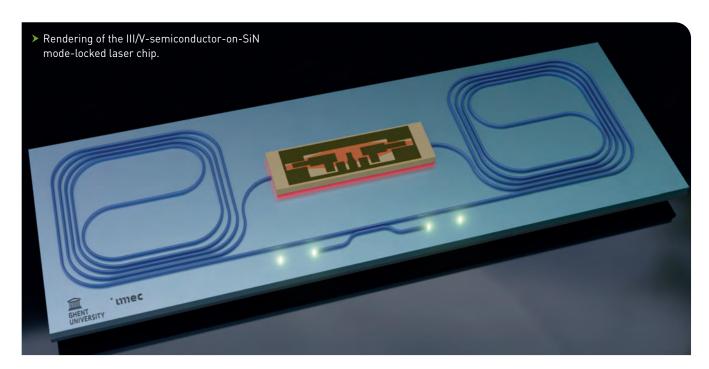

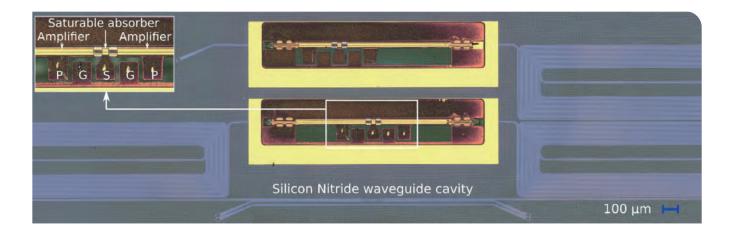

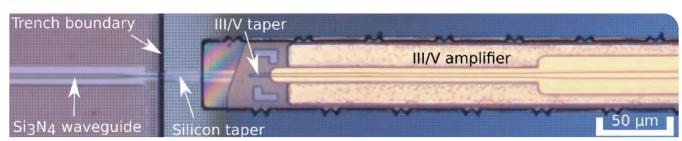

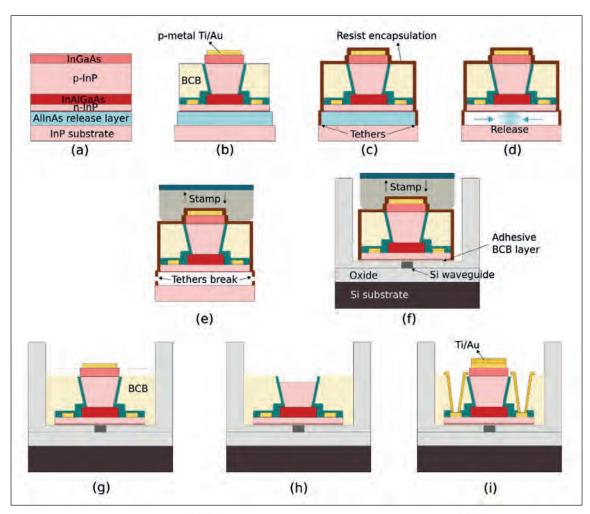

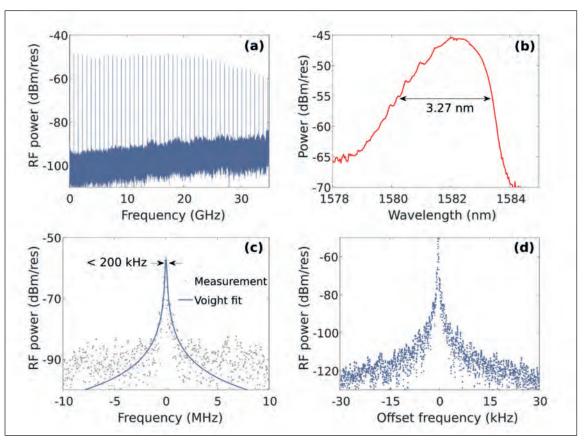

# 60 Mode-locked comb lasers for chip-scale spectroscopy

By integrating a semiconductor optical amplifier on a low-loss SiN photonic chip, an ultra-dense, low-noise laser comb is realized, delivering unprecedented precision for chip-scale spectroscopy

## **NEWS ANALYSIS**

## 16 AFTech: Creating the killer coating

A new coating for the incredibly expensive graphite parts in MOCVD reactors is set to slash the costs of SiC epitaxy

## 18 III-V Epi: a need for speed

UK foundry services provider, III-V Epi, intends to accelerate epitaxial structure manufacture for lasers, HEMTs and more

## **RESEARCH REVIEW**

- 66 Lateral gallium oxide MESFETs power ahead

- Diminishing droop with multi-junction LEDs

- 68 Pseudo-substrates produce better red microLEDs

## **NEWS**

- 06 Cree and ST expand SiC wafer agreement

- 07 AlScN project wins German innovation prize

- 08 Onsemi acquires GT Advanced Technologies for \$415 million

- 09 Trumpf unveils new VCSEL laser platform

- 10 X-FAB to offer heterogeneous integration using micro-transfer printing

- 11 GaN Systems signs capacity agreement with BMW for power transistors

- 12 NSF funds new US centre for optoelectronic and quantum tech

- 13 Applied Materials helps SiC chipmakers to move to 200 millimetre production

- 14 InP bare die market offering opportunities and profits

Editor Richard Stevenson Contributing Editor Rebecca Pool News Editor Christine Evans-Pughe Sales Executive Jessica Harrison USA Representatives Brun Media

Tom Brun Janice Jenkins

Publisher Jackie Cannon Director of Logistics Sharon Cowley Design & Production Manager Mitch Gaynor richardstevenson@angelbc.com editorial@rebeccapool.com chrise-p@dircon.co.uk

+44 (0)2476 718970 jessica.harrison@angelbc.com

+44 (0)1291 629640

tbrun@brunmedia.com +001 724 539-2404 iienkins@brunmedia.com +001 724-929-3550 jackie.cannon@angelbc.com +44 (0)1923 690205 sharon.cowley@angelbc.com +44 (0)1923 690200 mitch.gaynor@angelbc.com +44 (0)1923 690214

Circulation Director Scott Adams Chairman Stephen Whitehurst

Chief Executive Officer Sukhi Bhadal Chief Technical Officer Scott Adams Directors Jackie Cannon, Sharon Cowley

Published by Angel Business Communications Ltd, Unit 6, Bow Court. Fletchworth Gate. Burnsall Road. Coventry CV5 6SP, UK. T: +44 (0)2476 718 970 E: info@angelbc.com

+44 (0)2476 718970 scott.adams@angelbc.com stephen.whitehurst@angelbc.com +44 (0)2476 718970

+44 (0)2476 718970 sukhi.bhadal@angelbc.com scott.adams@angelbc.com +44 (0)2476 718970

Compound Semiconductor is published eight times a year on a controlled circulation basis. Non-qualifying individuals can subscribe at: £105.00/e158 pa (UK & Europe), £138.00 pa (air mail), \$198 pa (USA). Cover price £4.50. All information herein is believed to be correct at time of going to press. The publisher does not accept responsibility for any errors and omissions. The views expressed in this publication are not necessarily those of the publisher. Every effort has been made to obtain copyright permission for the material contained in this publication. Angel Business Communications Ltd © Copyright 2021. All rights reserved. Contents may not be reproduced in whole or part without the written consent of the publishers. The paper used within this magazine is produced by chain of custody certified manufacturers, guaranteeing sustainable sourcing. US mailing information: Compound Semiconductor, ISSN 1096-598X, is published 8 times a year, Jan/Feb, March, April/May, June, July, August/September, October, November/ December by Angel Business Communications Ltd, Unit 6, Bow Court, Fletchworth Gate, Burnsall Rd, Coventry CV5 6SP, UK. The 2021 US annual subscription price is \$198. Airfreight and mailing in the USA by agent named World Container Inc, 150-15, 183rd Street, Jamaica, NY 11413, USA. Periodicals postage paid at Brooklyn, NY 11256. US Postmaster: Send address changes to Compound Semiconductor, Air Business Ltd, c/o WN Shipping USA, 156-15, 146th Avenue, 2nd Floor, Jamaica, NY 11434, USA. Printed by: The Manson Group. ISSN 1096-598X (Print) ISSN 2042-7328 (Online) © Copyright 2021.

We strive for accuracy in all we publish; readers and contributors are encouraged to contact us if they recognise an error or omission. Once a magazine edition is published [online, in print or both], we do not update previously published articles to align old company names, branding, marketing efforts, taglines, mission statements or other promotional verbiage, im-ages, or logos to newly created or updated names, images, typographic renderings, logos (or similar) when such references/images were accurately stated, rendered or displayed at the time of the original publication. When companies change their names or the images/text used to represent the company, we invite organizations to provide Angel Business Communications with a news release detailing their new business objectives and/or other changes that could impact how customers/prospects might recognise the company, contact the organisa-tion, or engage with them for future commercial enterprise.

## Cree and ST expand SiC wafer agreement

CREE (through its Wolfspeed business) and STMicroelectronics have announced the expansion of an existing multi-year, long-term SiC wafer supply agreement. The amended agreement, which calls for Cree to supply ST with 150 mm SiC bare and epitaxial wafers over the next several years, is now worth more than \$800 million.

"This latest expansion to our long-term wafer supply agreement with Cree will continue to contribute to the flexibility of our global SiC substrate supply. It will continue to contribute importantly to our global SiC supply, complementing the other external capacity we have secured and the internal capacity we are ramping. The agreement will help meet the high volumes required by our product manufacturing operations in the next years, with a large number of automotive and industrial customer programmes in high volumes or ramping up," said Jean-Marc Chery, president and CEO of STMicroelectronics.

The adoption of SiC-based power solutions is rapidly growing across the automotive market as the industry moves from internal combustion engines to electric vehicles, enabling greater system

efficiencies that result in electric cars with longer range and faster charging, while reducing cost, lowering weight and conserving space. In the industrial market, SiC solutions enable smaller, lighter and more cost-effective designs, converting energy more efficiently to unlock new clean energy applications.

To better support these growing markets, device manufacturers are interested in securing access to high-quality SiC substrates to support their customers. "We are very pleased that STMicroelectronics will continue to

leverage Wolfspeed SiC materials as part of their supply strategy for the next several years," said Cree CEO Gregg Lowe. "Our long-term wafer supply agreements with device manufacturers now total more than \$1.3 billion and help support our efforts to drive the industry transition from silicon to SiC."

Lowe added: "Our partnerships and significant investments in increased production capacity ensure we are well positioned to capitalize on what we believe to be is a multi-decade growth opportunity for SiC-based applications."

## Infineon and Panasonic accelerate GaN development

INFINEON TECHNOLOGIES and Panasonic have signed an agreement for the joint development and production of the second generation (Gen2) of their proven GaN technology, offering higher efficiency and power density levels.

The high performance and reliability combined with the capability of 200 mm GaN-on-silicon wafer production mark Infineon's strategic outreach to the growing demand for GaN power semiconductors.

In accordance with market requirements, Gen2 will be developed as 650 V GaN HEMT. The devices will allow for ease of use and provide an improved priceperformance ratio, targeting, amongst others, high- and low-power SMPS applications, renewables, motor drive applications.

"In addition to the same high-reliability standards as for Gen 1, next-generation customers will benefit from even easier control of the transistor as well as a significantly improved cost position, thanks to moving to an 8-inch wafer manufacturing," says Andreas Urschitz, president of Infineon's Power and Sensor Systems Division.

Like the jointly developed Gen 1 devices, known as Infineon's CoolGaN and Panasonic's X-GaN, the second generation will be based on the normally-off GaN-on-silicon transistor structure.

This, in combination with the unmatched

robustness of the hybrid-drain-embedded gate injection transistor structure, is claimed to make these components the product of choice and one of the most long-term reliable solutions in the market

"We are delighted to extend our partnership and collaboration with Infineon on GaN components. Within the joint approach, we will be able to apply Gen1 and Gen2 devices on high quality and based on latest innovation developments", says Tetsuzo Ueda, associate director of Engineering Division, Industrial Solutions.

The market launch of the new 650 V GaN Gen2 devices is planned for the first half of 2023.

## AlScN project wins German innovation prize

THE Fraunhofer Institutes IAF and IIS together with the University of Freiburg/ INATECH netted second place with their joint project EdgeLimit – Evaluation of Power Electronics in Modern Edge Cloud Systems in the innovation competition Electronics for Energy-Saving Information and Communications Technology launched by the German Federal Ministry of Education and Research (BMBF).

The project EdgeLimit presents a concept for the use of novel power semiconductors for high-frequency amplifiers in 5G base stations for the new millimetre-wave frequency range at 26-34 GHz based on aluminum scandium nitride (AIScN). The project not only offers enormous potential savings in energy consumption and CO<sub>2</sub> emissions, but also an extraordinary level of innovation in the field of highfrequency electronics with a major leverage effect for microelectronics in Germany. This finds expression in the significant participation of industry in the second phase of the project, with a planned cooperation with Nokia Bell Labs, United Monolithic Semiconductors, Deutsche Telekom and Nokia Solutions and Networks.

Modern networked ICT systems increasingly have capacities for collecting and processing information at the edge of the network in addition to the central data-processing infrastructures (cloud), as well as systems for transferring data

between cloud and edge.

"This is where the EdgeLimit project comes in," says project coordinator Rüdiger Quay. "Our goal is to realize a complete antenna system, a so-called Remote Radio Head (RRH), which will enable more energy-efficient transmission in the millimeter-wave range of 5G while halving losses at the same time."

"We are working, for example, on intelligent edge solutions that take energy consumption into account during the design phase and reduce it to a minimum," says Albert Heuberger, Director of the Fraunhofer Institute for Integrated Circuits. By looking at the energy consumption of the radio units (massive MIMO antennas) in the 5G Testbed Industry 4.0 at Fraunhofer IIS, energy-efficient, distributed, secure edge cloud systems can be built and tested.

"The semiconductor technology we are pursuing, with which we have already gained a lot of experience at IAF, has the potential to fundamentally increase power efficiency in integrated circuits (MMICs) through better matching, higher gain and higher power density," elucidates Quay. Due to its high current-carrying capacity, AIScN allows significant advantages over established semiconductors such as silicon, GaAs and AIGaN/GaN. Based on this material, EdgeLimit aims to at least double power efficiency at the amplifier-level in new cellular frequencies as well as

halve losses in power converters. More energy-efficient electronics alone cannot counter the exponentially increasing energy consumption of ICT. The horizon of physical energy efficiency is closer than that of the realizable data throughput, which is growing faster and thus promoting a rebound effect. One solution is the intelligent and adaptive management of mobile communications systems, which ensures that energy is used as needed – an approach with enormous energy-saving potential.

To enable smart ICT, innovative power electronics architectures are required that allow electronics to be switched on and off as needed without compromising the latency of data transmissions.

"At the network level, large amounts of energy should be saved by intelligently networking transmission modules and antennas with on-demand control, for example in factory networks such as the new Bosch semiconductor fab in Dresden or for fast video transmission to cars," says Quay. "For this purpose, we are developing the necessary highfrequency electronics in EdgeLimit that are capable of being connected to intelligent network management. Because one thing is certain: In the further development of ICT, we must give resource efficiency at least the same priority as performance enhancement. This is the only way to reduce CO<sub>2</sub> emissions as digitization advances."

## **Advanced Compound Semiconductor** Foundry Services

MOCVD · Fabrication · Testing

Advanced III-V semiconductor solutions for optoelectronics application in the biotechnology, telecommunications, energy, industrial, and security industries.

MasimoSemiconductor.com | 603-595-8900

## Onsemi acquires GT Advanced Technologies for \$415 million

ONSEMI, a US supplier of intelligent power and sensing technologies, and GT Advanced Technologies, a US producer of SiC, have announced that they have entered into a definitive agreement under which Onsemi will acquire GTAT for \$415 million in cash.

The transaction is expected to better position Onsemi to secure and grow supply of SiC and meet rapidly growing customer demand for SiC-based solutions in the sustainable ecosystem, including EVs, EV charging and energy infrastructure.

Founded in 1994 in Hudson, New Hampshire, GTAT manufactures SiC and sapphire materials for high-growth markets.

Combining Onsemi's manufacturing capabilities with GTAT's technical expertise will accelerate SiC development and position Onsemi to better serve customers as the sustainable ecosystem rapidly ramps up over the next decade. This enhanced SiC capability will allow Onsemi to assure customers of supply of critical components and to further commercialize intelligent power technologies.

"This transaction reflects our confidence and stated commitment to meaningfully invest in SiC solutions to support the creation of intelligent power and sensing technologies to help build a sustainable future," said Hassane El-Khoury, president and chief executive officer of Onsemi.

"We are focused on deepening our leadership and innovation in gamechanging technologies that support the automotive and industrial sectors, and GTAT brings outstanding technical capabilities and expertise in developing wafering-ready SiC, which we intend to accelerate and expand to better empower customers in our high-growth end markets. We look forward to welcoming GTAT's talented employees to the Onsemi team and driving innovation together."

"Today's announcement marks the start of a new chapter for GTAT and is a testament to the value created by the hard work and strength of our team," said Greg Knight, president and chief executive officer of GTAT. "Onsemi is strategically positioned to scale our capabilities, providing the resources and platform to maximize the potential of our cutting-edge production techniques and ensure we remain on the forefront of advanced crystalline growth."

The acquisition also reinforces Onsemi's commitment to make substantial investments in disruptive, high-growth technologies, consistent with the company's recently announced 2025 target financial model described during its Analyst Day presentation. As Onsemi previously stated, capital expenditures are expected to be approximately 12 percent of revenue in 2022 and 2023, as Onsemi invests to drive differentiation and leadership, including in SiC. The transaction is not expected to impact the company's 2025 target financial model.

Onsemi plans to invest in expanding GTAT's research and development efforts to advance 150 mm and 200 mm SiC crystal growth technology, while also investing in the broader SiC supply chain, including fab capacity and packaging.

The transaction, which has been unanimously approved by the Boards of Directors of Onsemi and GTAT, is expected to close in the first half of 2022. Completion of the transaction is subject to regulatory approvals and other customary closing conditions. Approval of Onsemi's stockholders is not required in connection with the proposed transaction.

Onsemi intends to fund the transaction through cash on hand and available capacity under its existing revolving credit facility. The company expects the transaction to be marginally dilutive to its non-GAAP earnings per share in the immediate term and to be accretive within one year after close.

## **Vector Photonics** receives £600,000 for TITAN project

**VECTOR PHOTONICS** has received £600k for the newly awarded project called TITAN: PhoTonic CrysTal LAsers for EtherNet applications. The funding will drive the development of PCSELs for low-power consumption optical interconnections between servers in hyperscale data centres. Of the total project value, £300,000 has come from Innovate UK's Investor Partnership Programme. This has been match-funded by private investment from UKI2S, a specialist, deep-tech seed fund for UK-based, research spinouts; the Scottish Growth Scheme; and Equity Gap.

Neil Martin, CEO of Vector Photonics, said: "The rising power usage of hyperscale data centres is being driven by escalating demand from network-connected devices, such as smartphones, PCs and the IoT. Hyperscale data centres currently rely on high-performance lasers for the optical interconnects between servers."

These lasers require so much electrical power to operate that it is the heat they create, and the energy used by the systems cooling them, that have become the limiting factors to any increases in optical performance.

"The TITAN project will fund the early-stage development of PCSELs, which aim to solve this major heat problem. PCSELs require only half the electrical power of the incumbent lasers, for the equivalent system performance. Less heat is produced and less energy is used for cooling. Since we anticipate the system optical performance requirements of next-generation, hyperscale data centres increasing in future, it is only low-power consumption systems using PCSELs that can realistically facilitate this increase."

## Trumpf unveils new VCSEL laser platform

TRUMPF PHOTONIC COMPONENTS has revealed a new product platform called ViBO: VCSEL with integrated Backside Optics.

This VCSEL array technology supports a new generation of illumination devices that are inherently eye-safe over the whole product lifetime as the diffusor optics are monolithically incorporated into the laser array. This allows easy interfacing with the new platform and enhances reliability. Also, the form factor is significantly reduced compared to present hybrid VCSEL package solutions. ViBO can be directly SMD mounted onto a board or driver IC without additional wire bonding. This supports, for instance, easier integration under smartphone displays.

"ViBO has superior properties as well as cost advantages compared with standard top-emitting devices that are combined with external optics. Using ViBO as light source for 3D sensing applications offers more flexibility and freedom in design for its integration, as the footprint and the height are significantly smaller than hybrid solutions. This is especially interesting for consumer electronics such as smartphones or AR glasses", says Ralph Gudde, VP of marketing and sales.

"The smart combination of our highperformance VCSELs with unique, patented lens forms directly etched into the GaAs-substrate, gives our customers unprecedented benefits in creating tailored illumination profiles needed in advanced 3D sensing applications," adds Ralph Gudde. As well as flood and spot illumination, addressable zones can create linear and individual illumination profiles, as the emitting zones can be flexibly turned on and off.

In the first generation products, Trumpf focuses on the realization of illumination devices incorporating various diffusor designs for a wide range of emission angles to support various flood illumination applications for consumer and automotive. Having shipped millions of hybrid packaged products containing separate VCSEL arrays and diffusors, these widely used flood illuminators are viewed as the logical candidates

for the company's ViBO technology. With coplanar contact designs, the devices can be flip-chip mounted, yielding the most compact integration with the shortest electrical path and thus minimum electrical inductance. This design setup allows short pulses, high modulation speed and the flexibility of addressing multiple channels or even selected segments on the chip.

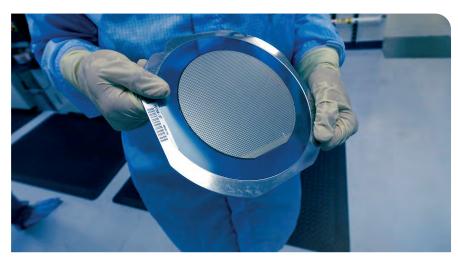

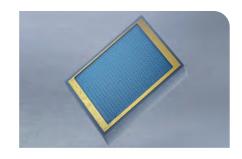

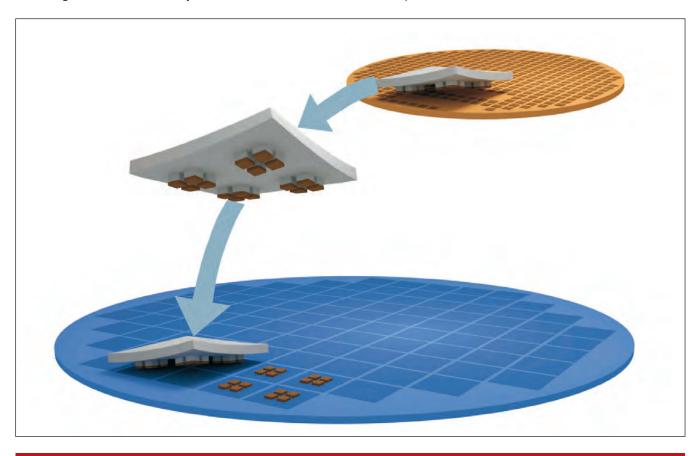

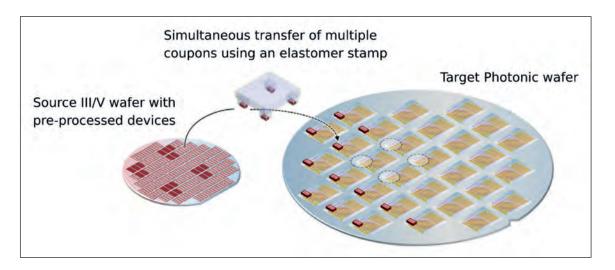

## X-FAB to offer heterogeneous integration using micro-transfer printing

X-FAB Silicon Foundries, a foundry for analogue/mixed-signal and specialty semiconductor solutions, is now able to support volume heterogeneous integration via micro-transfer printing (MTP), thanks to a licensing agreement that has just been secured with X-Celeprint.

This will mean that a diverse range of semiconductor technologies may be combined together, each being optimised for particular functional requirements. These technologies will include SOI, GaN, GaAs and InP, as well as MEMS.

In order to become the first foundry to provide customers with MTP-based heterogeneous integration, X-FAB has made substantial investments over the last two years. It has also established new optimised workflows and cleanroom protocols. This will allow customers to work with the foundry on heterogeneous design projects benefitting from a low-risk and fully

scalable business model that offers a clear migration to volume production.

X-Celeprint's proprietary massivelyparallel pick-and-place MTP technology stacks and fans-out ultra-thin dies based on different process nodes, technologies, and wafer sizes. It results in the formation of virtually monolithic 3D stacked ICs, which have enhanced performance, greater power efficiency, and take up less space. Furthermore, all this can be achieved at an accelerated rate, thereby significantly shortening time-to-market.

"By licensing X-Celeprint's disruptive MTP technology, we are uniquely positioned in our ability to facilitate the incorporation of numerous different semiconductor technologies. X-FAB customers will be able to utilize a technology that no other foundry is offering, and existing X-Celeprint customers may now tap into capacity levels that will easily meet their future demands," Volker Herbig, VP of X-FAB's MEMS business unit, explains.

"As a result, we can assist customers looking to implement complete multifunctional subsystems at the wafer level, even when there are high degrees of complexity involved. Signal conditioning, power, RF, MEMS, and CMOS sensors, optoelectronic devices, optical filters, and countless other possibilities will all be covered."

"Our agreement with X-FAB represents a major milestone in the commercialization of MTP technology, broadening the number of customers and applications," states Kyle Benkendorfer, X-Celeprint's CEO.

"High-volume heterogeneous integration of elements derived from various different source wafers will provide the semiconductor industry with significant new capabilities, including access to higher density devices with more functionality, fabricated at high yields and lower cost, within shorter timeframes."

# GaN Systems signs capacity agreement with BMW for power transistors

GaN SYSTEMS has signed a capacity agreement with BMW Group for GaN Systems' high-performance, automotive-grade GaN power transistors, which increase the efficiency and power density of critical applications in electric vehicles.

GaN power semiconductors are a key ingredient to achieve the small size, lightweight, and high efficiency required in the next generation of high-performance electric vehicles. Under the terms of the agreement, GaN Systems will provide capacity for multiple applications in series production. The guaranteed volumes by GaN Systems are a key building block for reliability in the supply chain for automotive players like BMW.

"Electric vehicles represent the future of transportation, and we are delighted to continue to support BMW with our design and production capacity," stated Jim Witham, CEO of GaN Systems. "This multi-hundred-million dollar agreement demonstrates BMW's commitment to innovation and sustainability."

BMW's relationship with GaN Systems began more than four years ago when BMW's engineers found that small size, lightweight, lowcost onboard chargers, DC/DC converters, and traction inverters were enabled by GaN. This led to investment

from BMW's venture capital firm, BMW I Ventures, to support and accelerate the automotive qualification of the GaN technology.

"The close collaboration among GaN Systems and BMW's engineers has helped to solidify the technology for automotive series production, resulting in the most advanced GaN power

transistors in the marketplace today," said Kasper Sage, managing partner BMW i Ventures.

"As electric vehicles become more prominent, the demand for critical semiconductor components is only going to increase, thereby making strategic partnerships with suppliers like GaN Systems even more important."

## NSF to fund new US centre for optoelectronic and quantum tech

THE US National Science Foundation has announced it will fund a new endeavour to bring atomic-level precision to the devices and technologies that underpin much of modern life, and will transform fields like information technology in the decades to come. The five-year, \$25 million Science and Technology centre grant will found the centre for Integration of Modern Optoelectronic Materials on Demand - or IMOD – a collaboration of scientists and engineers at 11 universities led by the University of Washington.

IMOD research will centre on new semiconductor materials and scalable manufacturing processes for new optoelectronic devices for applications ranging from displays and sensors to a technological revolution, under development today, that's based on harnessing the principles of quantum mechanics.

"In the early days of electronics, a computer would fill an entire room. Now we all carry around smartphones that are millions of times more powerful in our pockets," said IMOD director David Ginger (pictured above), the Alvin L. and Verla R. Kwiram Endowed Professor of Chemistry at the UW, chief scientist at the UW Clean Energy Institute and codirector of NW IMPACT.

"Today, we see an opportunity for advances in materials and scalable manufacturing to do the same thing for optoelectronics: Can we take a quantum optics experiment that fills an entire room, and fit thousands - or even millions

- of them on a chip, enabling a new revolution? Along the way we anticipate IMOD's science will help with a few more familiar challenges, like improving the display of the cell phone you already have in your pocket so the battery lasts longer."

Building on advances in the synthesis of semiconductor quantum dots and halide perovskites, the centre will integrate the work of scientists and engineers from diverse backgrounds, including: chemists with expertise in atomically precise colloidal synthesis, characterization and theory, which consist of engineered systems of nanoparticles suspended in a medium; materials scientists and mechanical engineers developing methods for the integration, processing and additive manufacturing of semiconductor devices; and electrical engineers and physicists who are developing new nanoscale photonic structures and investigating the performance limits of these materials for optical quantum communication and computing.

"NSF Science and Technology centres are integrative not only in the sense that they span traditional academic disciplines, but also in the sense that they seek to benefit society by connecting academic research with industrial and governmental needs, while also educating a diverse STEM workforce," said Ginger. "To this end, we're extremely lucky to have had the support of an amazing list of external partners across the fields of industry, government and education."

A partial list of IMOD's external partners includes companies such as Amazon, Applied Materials, Corning Incorporated, Microsoft, Nanosys and FOM Technologies, Inc.; government organszations like the National Renewable Energy Laboratory, the Pacific Northwest National Laboratory and the Washington State Department of Commerce; and educational partners including GEAR UP at UW, Catalyst @ Penn GSE and the centre for Education Integrating Science, Mathematics and Computing at Georgia Tech.

The centre will launch a series of mentorship, team science training and internship programmes for participants, including students from under-represented groups in STEM and first-generation students. centre scientists will also work with high-school teachers on curriculum development programmes aligned with the next-generation science standards and act as 'ambassadors' to K-12 students, introducing them to STEM

"In partnership with UW QuantumX and the Northwest Quantum Nexus, IMOD is launching a Quantum Training Testbed facility to provide cutting edge training and workforce development opportunities for students from across IMOD's participating sites and partners," said Kai-Mei Fu, associate professor of physics and of electrical and computer engineering at the UW, who is IMOD's associate director of quantum workforce development.

"We're excited to have such strong support from our partners in the region, allowing us to build on the investments that Washington state has already made in the Washington Clean Energy Testbeds to support workforce training and economic development. For example, Microsoft plans to donate a cryostat that will allow our students to cool samples down to within a few degrees of absolute zero to study phenomena such as quantum spin physics and decoherence, and we have plans to do so much more for our trainees. Right now, we're asking the question: 'What is the equipment we wish we had been able to experiment with as students?"

The 11 academic institutions that make up IMOD are the University of Washington; the University of Maryland, College Park; the University of Pennsylvania; Lehigh University; Columbia University; Georgia Institute of Technology; Northwestern University; the City College of New York; the University of Chicago; University of Colorado at Boulder; and the University of Maryland, Baltimore County.

# Applied Materials helps SiC chipmakers to move to 200 millimetre production

APPLIED MATERIALS has announced new products that help enable SiC chipmakers transition from 150 mm wafer production to 200 mm production, which approximately doubles die output per wafer, to help satisfy the world's growing demand for premium electric vehicle powertrains.

"To fuel the computer revolution, chipmakers moved to ever-larger wafer sizes, dramatically increasing chip output to satisfy burgeoning global demand," said Sundar Ramamurthy, group VP and general manager of the ICAPS group at Applied Materials.

"Today we are in the early stages of another revolution that will benefit from Applied's expertise in materials engineering at an industrial scale."

According to Gregg Lowe, president and CEO of Cree, electrification of the transportation industry is a rising trend. "We are accelerating this inflection point by leading the global transition from silicon to SiC with our Wolfspeed technology. Delivering the highest-performing SiC power devices on larger 200 mm wafers enables us to increase end-customer value and meet growing demand."

"Applied's support in helping speed

qualification of 200 millimetre processes in Albany and multi-equipment installations at our Mohawk Valley Fab is expediting this transition," Lowe added. "Moreover, new technologies being developed by Applied's ICAPS team, such as hot implant, have broadened and deepened our technical collaboration and helped accelerate our power technology roadmap."

SiC wafer surface quality is critically important to SiC device fabrication as any defects on the surface of the wafer will migrate through the subsequent layers. To produce uniform wafers with the highest quality surfaces, Applied has developed the Mirra Durum CMP\* system, which integrates polishing, measurement of material removal, cleaning and drying in a single system.

The new system has demonstrated a 50X reduction in finished wafer surface roughness as compared with mechanically grinded SiC wafers and a 3X reduction in roughness compared to batch CMP processing systems.

During SiC chip fabrication, ion implantation places dopants within the material to help enable and direct the flow of current within the high power producing circuits. The density and hardness of SiC material makes

it extremely challenging to inject, accurately place and activate the dopants while minimizing damage to the crystal lattice, which reduces performance and power efficiency.

Applied has solved this challenge with its new VIISta 900 3D hot ion implant system for 150 mm and 200 mm SiC wafers. The hot implant technology injects ions with minimal damage to the lattice structure, resulting in a more than 40X reduction in resistivity compared with implant at room temperature.

Applied's ICAPS (IoT, Communications, Automotive, Power and Sensors) business is developing additional products for the SiC power chip market including in PVD, CVD, etch and process control.

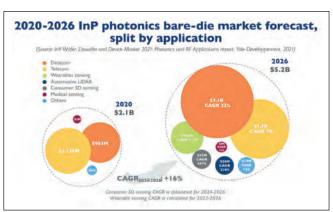

## InP bare die market offering opportunities and profits

"AT YOLE, we expect an initial slight market penetration of InP in 2022 in wearables, followed by a significant increase to \$255 million in 2026 with a CAGR 2022-2026 of 112 percent." asserts Ahmed Ben Slimane, technology & market analyst, Compound Semiconductors and Emerging Substrates at Yole Développement. He adds: "For LiDAR applications, InP could be promising, enabling eye safety at higher wavelengths. Leading companies such as Volvo, ZF, Continental, Daimler, etc. are interested in adopting InP-based LiDAR."

For smartphones, OLED displays are transparent at wavelengths in the range of 13xx to 15xx nm, explains Yole's analyst. OEMs interested in removing the camera notch on mobile phone screens and integrating the 3D-sensing modules under OLED displays are considering moving to InP edge-emitting lasers, replacing the current GaAs VCSELs. Even though this trend is currently in an early R&D phase, Yole sees a strong interest from several players, such as ams, Infineon Technologies, STMicroelectronics and several laser manufacturers and sensor players.

The InP Wafer, Epiwafer and Device Market 2021: Photonics and RF Application report delivers a comprehensive and detailed understanding of the InP industry, covering markets from wafers and epiwafers to bare dies. Including market trends and forecasts, supply chain, technology trends, technical insights and challenges analysis, take away and outlook, this study proposes an in-depth description of the ecosystem and main players' strategies.

As analysed by Yole's team in the new InP Wafer, Epiwafer and Device Market 2021: Photonics and RF Application report, as an indispensable building block for high-speed and long-range optical transceivers, InP laser diodes remain the best choice for telecom and datacom photonic applications. However, following the Covid-19 outbreak and the US-China trade tensions, telecom

infrastructure deployment was disrupted, resulting in a minor InP market slowdown in 2020. The requirement for more data transfer at higher speed in datacom is increasing, with technology migrating to single InP lasers targeting

state-of-the-art 100 Gbit/s output, making them preferable in 400 Gbit/s and 800 Gbit/s transceivers. Driven by high-volume adoption of high-data-rate lasers, the datacom bare die market reached around \$963 million in 2020. It is expected to be worth \$3.1 billion in 2026, due to a 22 percent CAGR during this period.

Meanwhile, the cyclic InP telecom market will continue its growth thanks to 5G deployment. Yole sees a comfortable increase from \$1.1 billion in 2020 to \$1.7 billion in 2026 at a CAGR2020-2026 of 7 percent. The InP industry is a dynamic market with lots of opportunities for legacy players and new entrants. In its InP technology and market analysis, Yole reports a fragmented market, with numerous companies, especially at the device level.

According to Ahmed Ben Slimane from Yole: "Two American players are leading the InP market: II-VI and Lumentum. Both have increased their market share and strengthened their position thanks to strategic mergers and acquisitions. Indeed, II-VI acquired Finisar in 2019, and Lumentum acquired Oclaro in 2018." II-VI and Lumentum have both vertically integrated business models: they generate revenues at bare die, device, and module-level. II-VI also offers epiwafer products. Their combined bare die market share is around 30 percent.

Facing II-VI and Lumentum, Yole identifies major Chinese players like Hisense and Accelink. Both companies are in the global top five and are increasing

step-by-step their share of the market. The two Chinese companies take advantage of the US-China trade tensions and the massive 5G transceiver deployment in Asia, explain Yole's analysts in the InP report. Sensing applications targeting the mass consumer and automotive markets are attracting new players.

Yole has identified several players interested in entering this market:

- Vertically integrated InP players with the know-how and an already established structure, as they can easily switch to sensing applications as soon as the market becomes bigger. II-VI and Lumentum are part of this segment.

- GaAs players with foundry capabilities could leverage the existing GaAs tools to switch to similar InP processes. Yole sees for example, ams and Trumpf.

- Emerging foundries or companies already working on InP-based solutions.

According to Poshun Chiu, technology & market analyst, Compound Semiconductors & Emerging Materials at Yole: "In the last category, we witnessed an increase in private investments and SPACs in the last year. These include, in Q4-2020, Luminar raised \$590 million and went public, then acquired OptoGration; in Q2-2021, Aeva went public with an initial valuation of \$1.7 billion; and in Q2-2021, Rockley Photonics announced its intention to go public at an initial valuation of \$1.2 billion with an Apple supported project for smartwatches."

# 200mm Process Has Arrived

## Introducing the Temescal Systems UEFC-6100

Welcome to your production future. Our UEFC-6100 is the first compound semiconductor production tool designed for 200mm lift-off processing. The world's leading manufacturers are welcoming our Auratus™ enhanced line of Temescal electron beam deposition systems, and you won't want to be left behind. We vaporize metals more efficiently. We deliver uniformity. We return unmatched savings. The results are overwhelming.

With a line of tools optimized for a range of production environments, whether 150mm or 200mm, small-batch or high-volume, this invasion could be coming your way.

Find out more before you take us to your leader. Contact Ferrotec at 1-925-371-4170 or visit temescal.ferrotec.com/200mm.

**UEFC-5700** 42 Wafers (150mm) 18 Wafers (200mm)

**UEFC-4900** 25 Wafers (150mm)

## AFTech:

## Creating the killer coating

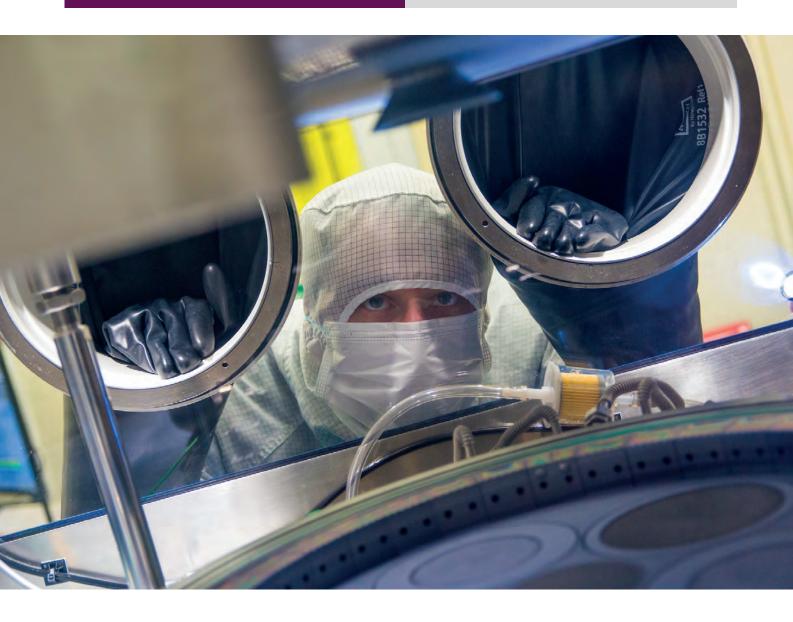

A new coating for the incredibly expensive graphite parts in MOCVD reactors is set to slash the costs of SiC epitaxy. REBECCA POOL talks to the ZOE TOLKIEN, THE RESEARCH DIRECTOR AT AFTECH that is making this happen

EARLIER THIS YEAR, UK-based MOCVD services provider, Advanced Furnace Technology, won more than £1 million in funds from UK Research and Innovation (UKRI) to develop a novel coating method for the lesser-known but eye-wateringly expensive graphite parts that are instrumental to epi-wafer growth.

From wafer carriers and exhaust collectors to ceilings and susceptors, the graphite 'furniture' found in MOCVD reactors is coated with highly stable SiC to prevent wafer contamination. But while the SiC coat works well for most III-V semiconductor wafer production, issues emerge when working with SiC materials.

According to Zoe Tolkien, director of research at AFTech, SiC-coated graphite internal furniture is integral to all MOCVD processes as it withstands the fast radiative heat cycles without cracking. What's more, cleaning these pricey parts to extend lifespan is critical to keeping manufacturing costs down.

"After a few runs, manufacturers of, say GaN wafers, pack up these parts and send them to us so we can clean them - this has become a booming business for us," she says. "But cleaning the silicon carbide deposits off a silicon-carbide coat part while leaving that coating intact is difficult."

"To our knowledge, no-one has managed to do this for a high-throughput, high-yield SiC commercial process - you just end up cleaning the coating off as well, which means the parts then need re-coating," she explains. "So a silicon carbide coat is just not practical for silicon carbide epi-growth."

Left: Tantalum carbide experimental CVD furnace chamber.

## **NEWS ANALYSIS I COATINGS**

The AFTech researchers developing the tantalum carbide coating for graphite furniture. Zoe Tolkien is third from the left.

But tantalum carbide (TaC) could provide the answer. The metal carbide has already attracted worldwide interest as a graphite coating; it provides a highly uniform coat, is stable at SiC's extreme epitaxial growth temperatures, can suppress impurity migration from the graphite part and can extend the graphite component life. Indeed, in June this year, US-based industry analyst Persistence Market Research estimated that the TaC coating for graphite market will expand at 5 percent compound annual growth rate over the next decade with key players coming from Japan, South Korea and Taiwan. Still, issues exist.

Thermal stresses between the TaC coat and graphite surface often lead to delamination of the coating from the substrate, reducing the useful lifetime of these graphite parts, an issue that Aixtron, for one, is currently trying to tackle. As detailed in UKRI's report about the AFTech project, parts from Aixtron's South Korea- and US-based suppliers have suffered from delamination, leading the reactor manufacturer to approach AFTech for a solution.

As Tolkien puts it: "We're not the first innovator here and our customer already has suppliers, but they want an additional supplier with expertise in CVD... so we're going to optimise the deposition process."

In the next four years, Tolkien and colleagues will work out how best to coat graphite parts with TaC to reduce thermal stresses, prevent delamination and extend lifetimes by up to 50 percent.

Right now, they are experimenting with the mass flow ratio of the reactive gases within their laboratory CVD set-up at AFTech. The general idea is to increase

this ratio of reactive gases as layers are deposited onto the graphite to produce a TaC gradient across the coating. Initial carbon-rich layers will more closely match the thermal expansion coefficient of the graphite substrate, reducing the chance of delamination. Meanwhile, the outer metal carbide-rich layers will provide the all-important stability crucial for SiC epitaxy.

Tolkien also intends to scale up the TaC deposition process ready for commercialization. "Scaling is never linear and there will be plenty of experimental work to reach a high-yield point [at scale] – the innovation is going to be in our method and careful process control," she says. "If we can overcome the mismatch of thermal coefficients, we'll have cracked delamination and will be able to extend the lifetime of these parts."

Assuming project success, then the future for AFTech is set to be dazzlingly bright. A delamination-free TaC-coating graphite process will first see the Cambridge-based company manufacturing the necessary internal furniture for MOCVD reactors that will be sold by a world-leading supplier. And then the company will also hold a critical place in the rapidly expanding SiC semiconductor supply chain.

"Ultimately we hope that we can improve the efficiencies of epi-wafer growth for the SiC semiconductor market," says Tolkien. "We're a small company but want to contribute to this ramp up of SiC devices that is so important to energy efficiency and carbon net zero. As far as I see, efficiencies are being achieved through innovations along the supply chain and we're hopefully going to be a part of that."

## III-V Epi: a need for speed

Recently launched UK foundry services provider, III-V Epi, intends to accelerate epitaxial structure manufacture for lasers, HEMTs and more. REBECCA POOL TALKS TO CTO, RICHARD HOGG, to find out how

> IN JULY THIS YEAR, III-V Epi launched, aiming to bring new III-V devices to market as quickly as possible. Led by UK industry veterans that hail from Gas Sensing Solutions, quantum tech hub, Quantic and the University of Glasgow, the new company is already providing myriad wafer foundry services that rely on MBE and MOCVD to commercial firms and research organisations around the world.

III-V Epi's MBE and MOCVD epitaxial structures are being used in lasers, LEDs, photodetectors, HEMTs and more. And key customers to date include an Asia-based tech giant, the UK start-up Vector Photonics, laser equipment suppliers, defence organisations and several universities, with more of the same coming soon.

"Myself and colleagues have worked together in the past and it was a natural progression to launch the company - we believe there's a massive unmet need here for low-to-medium volume [wafer production]," asserts Richard Hogg, III-V Epi chief technical officer, head of The Electronic and Nanoscale Engineering Division at Glasgow University, and chair of the scientific advisory board at Vector Photonics.

"In the past, all of III-V Epi's partners have had problems getting epi-wafers fabricated as [foundries] have been busy making, say, hundreds of thousands of VCSELs for handsets, mice or datacoms applications," he says. "But as soon as you come away from an application that isn't in an iPhone or Samsung phone, your volumes are down and you may only need a dozen wafers – so we're focusing on low-to-medium volume and prototype III-V epitaxial structures for device applications."

Right now, III-V Epi is using two MBE systems and two MOCVD reactors, with each instrument handling 2-inch to 4-inch wafer sizes. Recently developed structures include 980 nm VCSELs, antimonide photodetectors on GaAs substrates, novel multi-colour LEDs and Vector Photonics' photonic crystal surface emitting lasers. The company routinely performs regrowth in InP and GaAs-based systems while its InP distributed feedback MOCVD re-growth processes have been qualified for 1310 nm DRB lasers.

On a different tack, Hall Effect measurements were recently carried out for a partner that had fabricated devices on a newly-commissioned reactor. And the company is also working with other UK-based universities on developing routes to generating and commercializing intellectual property.

For now, the company is firmly sticking to antimonide, arsenide and phosphide materials, but alternative materials systems may follow in the future. "We're busy enough with three atoms right now," quips Hogg. "But there's always a possibility we could expand to nitrides or more exotic materials."

## From concept to structures

In a typical scenario, III-V Epi will spend some time working with customers to define an exact device design. This could, for example, involve converting a software simulation to a realistic design with specified layers and tolerances.

"We might ask, do you really want that tolerance on layer 17? And the customer might say no, but it is critical to layer 22," explains Hogg. According to the CTO, this process can take time, but once the final design is decided, the company will typically fabricate the necessary structure in eight-to-ten weeks.

III-V Epi currently has two engineers running its MBE systems and four engineers running its MOCVD reactors across its three partner organisations, a setup that Hogg reckons could be unique to the UK.

"We've got this mixed usage situation where we have both MBE and MOCVD capabilities, with neither within a university building," he says. "Many of the engineers working with III-V Epi's partners are from Glasgow University, and it has just made sense to collaborate – we've got so much knowledge about manufacturing and we can bring this together with our research and development."

In recent weeks, III-V Epi joined the European Photonics Industry Consortium (EPIC) and company growth is now expected. It's early days, but Hogg and colleagues anticipate strong demand for the materials systems they can manufacture, and at some point expect to recruit highly skilled tools operators and tool setters to ramp volumes.

"Our fast turnaround times are critical at the moment," says Hogg. "So much compound semiconductor capacity [is tied up] with a few big companies and getting spare capacity anywhere can be difficult."

"We're going to want to have the ability to ramp up volumes by using operators to run our tools overnight so we can manufacture 24/7," he adds.

Introducing larger wafers will accelerate the production of power electronic devices in fully depreciated 200 mm fabs

BY SANTHANARAGHAVAN **PARTHASARATHY FROM** GT ADVANCED TECHNOLOGIES

The goal of achieving carbon neutrality has gained momentum worldwide. Many steps are being taken to transform our global energy system, including a dramatic reduction in reliance on fossil fuels. The adoption of wide-bandgap semiconductors made from materials like SiC will provide energy-efficient devices that have almost no losses, creating a sustainable path to achieving net zero carbon emission.

Today's power converters, including AC-DC rectifiers, AC-AC transformers, DC-DC converters and DC-AC inverters, tend to employ silicon-based power electronic devices - the IGBT, short for insulated gate bipolar transistor, is among the most commonly used. However, demands for faster switching frequencies, high power ratings, high conversion efficiencies and high-temperature operation are driving the adoption of devices made from SiC. This wide-bandgap semiconductor combines a bandgap that is three

times that of silicon with a thermal conductivity that's also three times higher and a breakdown field that is ten times greater, making devices made from SiC a perfect choice for these operations.

Shipments of SiC power devices, which are made on native single-crystal substrates, have climbed in recent years. This has enabled SiC to move out of the lab and establish itself as a mainstay for power electronic devices, especially when breakdown voltages greater than 900 V are required.

The foundation for commercialization of SiC power devices came in 1999, when 50 mm diameter wafers hit the market, selling for \$495 a piece. While that seems an eye-watering price today, at the time this was considered a breakthrough. Now the majority of SiC power electronic devices, such as Schottky barrier diodes, MOSFETs, junction field-effect transistors and

cascodes, are built on 150 mm wafers, with fabrication taking place in fully depreciated 150 mm and 200 mm fabs that have become available as wafer sizes in the silicon industry have transitioned to 300 mm.

To provide year-on-year productivity growth in the semiconductor industry, engineers tend to pull on five well-known levers: shrinking device dimensions, introducing a new device design, improving equipment productivity, increasing line yield, and migrating to a larger wafer size. Of these five, the latter offers considerable gains, which is why there is so much interest in the development of 200 mm SiC wafers.

The obvious benefit of increasing the surface area of the wafer is that it drives up the number of devices, or die, that it can yield. This increase diminishes fabrication cost per device, since the number of process steps remains the same (see Table 1).

## Readily available fab capacity

Today silicon-based power devices, such as the IGBT, are mass-produced on 300 mm silicon wafers. That's because Tier 1 integrated device manufacturers (IDMs) have invested billions of dollars over the last few years on 300 mm fabs for making silicon power electronics.

Thanks to the migration of silicon power device manufacturing to 300 mm fabs, fully depreciated 150 mm and 200 mm fabs are now available for SiC production. Supporting this venture, IDMs have added toolsets for SiC device fabrication. These include: MOCVD reactors capable of growth up to 1600 °C; high-energy, high-temperature implanters; dopant-activation furnaces; metrology equipment; wafer-level testing; and die singulation tools. These fabs have enough excess capacity to handle several thousand wafer starts per week.

While Tier 1 IDMs have the benefit of fully depreciated and well-optimized day-to-day run yields aiding competitive manufacturing costs and device prices, it will not be so easy for newcomers with 200 mm fabs. These firms will encounter price pressure and lower yield numbers in the near term.

The introduction of 200 mm substrates is expected to bring down the overall device cost by 20-35 percent relative to production on a 150 mm platform. This can occur even if there is an increase in material costs at the wafer level. For the ease of achieving good wafer

|                                   | Wafer Diameter mm |      |       |       |

|-----------------------------------|-------------------|------|-------|-------|

|                                   | 76                | 100  | 150   | 200   |

| Surface area(A=π. r²) mm²         | 4534              | 7850 | 17663 | 31400 |

| Ratio increase over previous size |                   | 1.7  | 2.3   | 1.8   |

| Die Size (mm)                     | 4 x 4             | 4×4  | 4×4   | 4×4   |

| No. of dies/wafer                 | 172               | 338  | 858   | 1611  |

| Increase in the number of dies%   |                   | 97%  | 154%  | 88%   |

| Ratio of increase in devices      |                   | 2.0  | 2.5   | 1.9   |

Table 1. The number of die increase with wafer size.

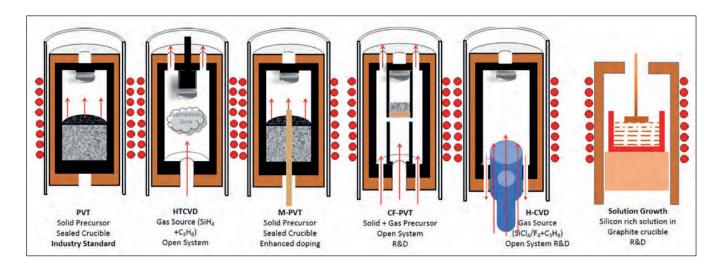

➤ Figure 1. There are several different techniques for producing bulk SiC.

geometry, there is an increase in wafer thickness as the wafer diameter grows. 150 mm-diameter SiC wafers have a thickness of 350  $\mu m$ , and the initial 200 mm SiC substrates introduced to the market will be 500  $\mu m$ -thick. As increased thickness reduces the number of wafers made from each puck, there is a slight rise in wafer cost. However, the increased thickness helps to ensure a good wafer geometry, while minimizing bow and warp.

Even with today's fabrication tooling capabilities, it is possible to produce 350  $\mu m$ -thick 200 mm wafers that would provide an additional reduction to substrate costs. However, that's not an essential step, as irrespective of wafer thickness, SiC wafers with a 200 mm diameter offer reduced device costs compared with their 150 mm siblings.

While moves to larger substrate sizes over the past two decades have helped to cut production costs for SiC devices, they are still about three times higher than those of silicon variants. That's not a showstopper, though, because when a circuit designer switches from silicon devices to those made from SiC, they get a 5-10 percent cost reduction at the

system level. The introduction of 200 mm SiC wafers will amplify this benefit and lead to further falls in overall system-level cost over the next few years.

## Scaling challenges

For elemental semiconductor materials such as silicon and germanium, as well as compound semiconductor materials such as GaAs and InP, crystalline material is grown from the melt. Crystal growers begin by taking a seed crystal, with a cross-section typically 10 mm by 10 mm, and use the thin neck created between the seed and the melt interface to increase the diameter of the crystal to the required level. Once this is established, the crystal is pulled out of the melt at a rate that depends on the material. This rate ranges from 1 mm/hour to 150 mm/hour.

One of the biggest downsides of SiC is that the material doesn't exist in a liquid phase, so crystals can't be grown from a melt. If SiC is held at a high temperature and low pressure, it dissociates into gaseous species without passing through the liquid phase. Due to this behaviour, SiC crystals are grown using a vapour phase technique called sublimation, or physical vapour transport (PVT). For growing material using

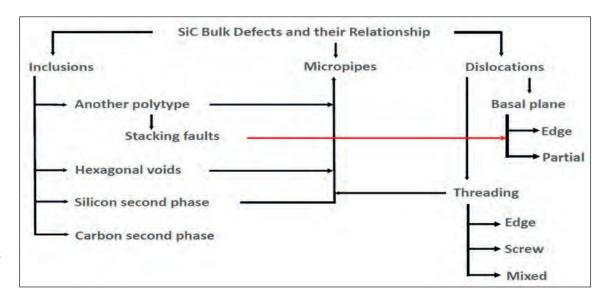

➤ Figure 2. Various defects observed in bulk SiC and their relationship.

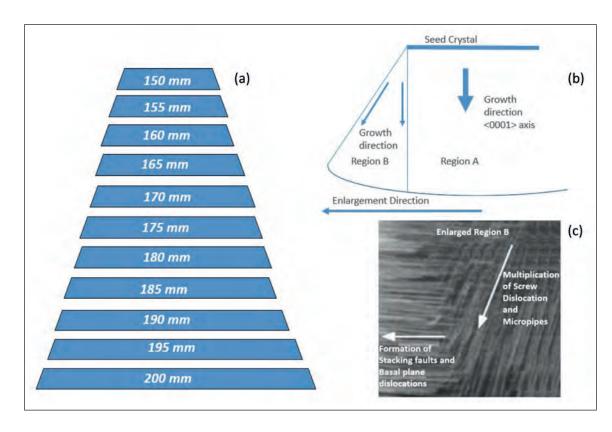

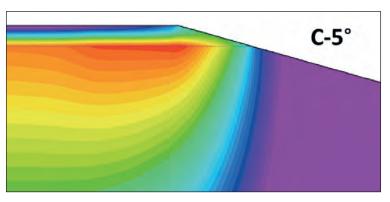

> Figure 3. Seed enlargement lies at the heart of the introduction of larger wafer sizes. Shown here are illustrations of: (a) a seed expansion process from 150-200 mm, and (b), the defects that can develop during the seed expansion process. The newly expanded region is susceptible to the formation of more defects (c).

this method, an essential ingredient is a seed crystal with a diameter similar to that of the boule (read on to discover how the seeds are expanded). With PVT, growth rates are in the range of 0.1-0.5 mm/hour.

To take the quality of SiC to a new high, and to enable a more precise control of the growth of this material, researchers have realized additional advances to the PVT process, and explored other viable options (see Figure 1). One refinement, adopted by industry, is the use of gaseous cracking to supply the carbon and silicon, rather than a solid SiC powder. This technique is called high-temperature chemical vapour deposition (HT-CVD).

Another alternative is modified PVT (M-PVT), an approach that incorporates an additional feed tube into the growth zone for the dopant gas, which could be nitrogen or other materials. This modification enables the production of low-resistivity SiC with uniform resistivity profiles. Using conventional PVT, one downside is that the dopant gas is introduced outside the growth zone. This prevents the production of low-resistivity material with good uniformity, due to limited diffusion.

At the research level, other techniques are being explored for the growth of crystalline SiC. These methods, which are a long way off producing commercial-scale SiC wafers, include halide CVD, as well as a combination of HT-CVD and PVT that is known as continuous-feed PVT.

Recently, there has been interest in the growth of bulk SiC from solution, as this has the potential for producing large-sized, high-quality SiC wafers. But this technique, still being researched, is not yet capable of achieving commercialization. One of its drawbacks is that due to the lack of a stoichiometric SiC liquid phase at atmospheric pressure, it is impossible to employ congruent melt growth. Another downside is that the solubility of carbon in molten silicon is very limited at very high temperatures. It is possible to enhance the solubility of carbon by turning to solvents, such as Ti-Si, Al-Si, Cr-Si, Fe-Si, Si-Sc, Si-Co, Sn-Si and Si-Ge. However, these solvents threaten to be incorporated in the grown crystal matrix. Another issue is that the growth of larger crystals is not sustainable with these methods.

Due to the considerations surrounding the growth of SiC by a variety of methods, today almost all commercially grown SiC crystals are produced by PVT. With this approach, PVT furnaces are either inductively or resistively heated.

## Crystal characteristics

SiC can be crystallized in three crystal structures: cubic (C), hexagonal (H) and rhombohedral (R). Variations of this material are far greater than these three, however, with SiC exhibiting more than 220 polytypes. These differ in how they occupy sites along the *c*-axis, with classification of the polytype depending on the number of Si-C layers in the unit cell. For power electronic applications, the best polytype is 4H SiC.

Difficulties inherent to vapour phase growth give rise to a variety of defects, including micropipes, screw dislocations, edge dislocations, stacking

## COVER STORY I SIC

faults, inclusions, and partial and mixed dislocations. Device performance is impaired by micropipes, screw dislocations and basal planar defects. However, the density of these imperfections can be reduced during crystal growth and subsequent epilayer deposition, which takes place prior to front-end processing. The relationship between the different defects in SiC is illustrated in Figure 2.

During the past twenty years, manufacturers of SiC have taken a step-by-step approach to expanding seed sizes. Progress is not easy, as this expansion is a time-consuming, iterative process, involving several cycles of learning and process optimization. The starting point for seed development dates back

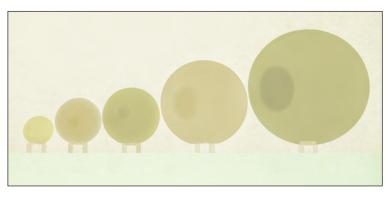

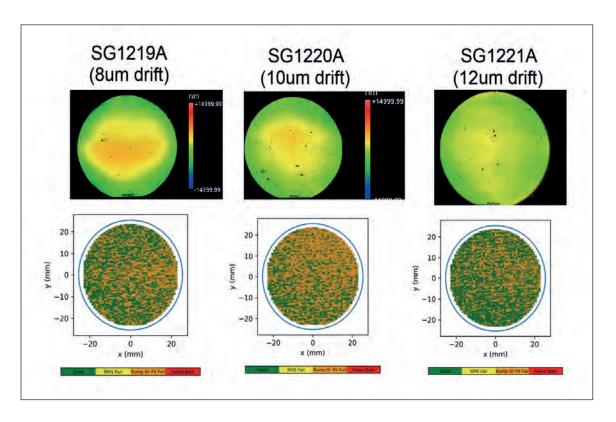

> Figure 4. GTAT's progress in crystal growth from 50 mm to 200 mm.

to the 1990s, with the formation of self-nucleated Lely platelets with a 4 mm by 4 mm cross-section. These days, efforts are directed towards expanding seeds from 150 mm to 200 mm, a challenging task given that the newly expanded region is susceptible to the formation of more defects (see Figure 3). Success in expanding seed dimensions demands a concurrent undertaking of several iterations of thermal and crystal growth computation, fluid dynamics and numerical modelling in a virtual platform, and hot zone design optimization for larger seed sizes. To preserve the quality of the crystal in the starting seed, there is a need to control the advancement of the solidgas interface and maintain the shape of the growth interface via careful selection of axial and radial temperature gradients.

## Evaluating economics

With the growth rate for 200 mm SiC crystals almost the same as that for their 150 mm siblings, there is no appreciable increase in the production cycle time, allowing equipment throughput to be maintained. Costs do rise slightly, however, due to an increase in the expense of hot-zone components,

## **ACKNOWLEDGEMENTS**

> The author profoundly thanks his colleagues and the worldclass manufacturing team at GTAT. Special thanks and sincere appreciation to GTAT colleagues Chris Van Veen, Henry Chou and Jeff Gum, and Simon Price of Exawatt for useful discussions and critical review.

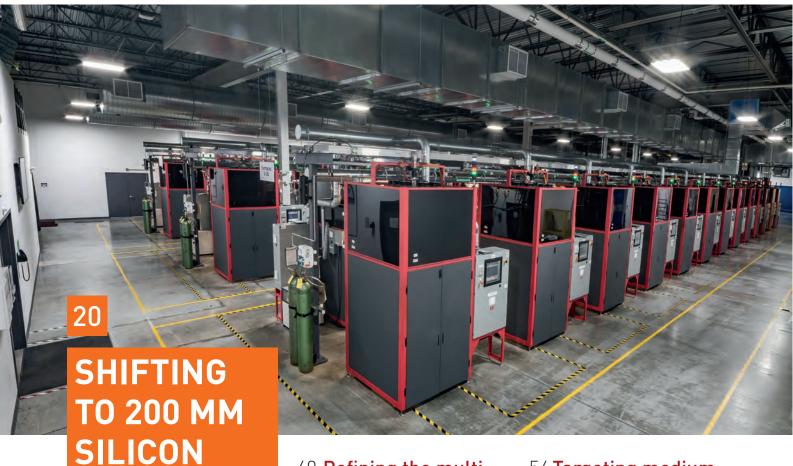

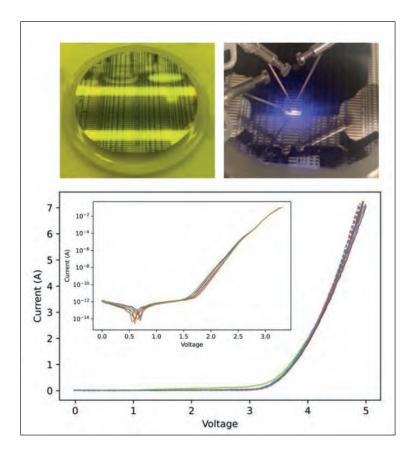

stemming from an increase in the size of this part in the growth chamber. Fortunately, there have been recent advances in graphite manufacturing, as well as a far better understanding of how to tune the growth process. Due to these gains, it is now viable to make cost-effective hot-zone components for 200 mm crystal growth, and if higher volumes are used, expenditure diminishes. Working in this manner, our team at GT Advanced Technologies (GTAT) has developed the SiClone 200 platform, which is capable of producing 150 mm and 200 mm diameter crystals without additional capex.

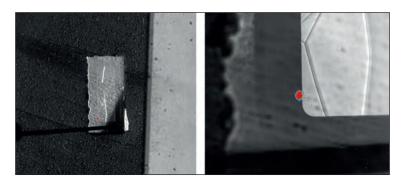

As well as crystal growth, seed/wafer fabrication involves outer diameter grinding, flat grinding, wafering, lapping and polishing - and each process needs to be optimized as the wafer diameter increases. There are already productivity increases at the wafering step, accomplished by reducing kerf loss during the slicing process. Traditionally, slicing SiC wafers involves multi-wire saws and diamond slurry, and leads to a kerf loss below 200 µm and a grinding loss of less than 100 µm, required for removal of subsurface damage. Introducing laser-based slicing trims total material losses for wafer processing by one-third, to around 100  $\mu$ m.

At the fab level, cost increases associated with migrating to 200 mm are minimal. Offsetting the relatively low add-on costs for 200 mm SiC crystal growth and wafer manufacturing is an increase in the number of dies per wafer. This makes the switch, which will deliver significant dividends in the power electronic industry, profitable and sustainable. Today's epi-ready 150 mm SiC wafers retail for \$750-\$900, and 200 mm wafers are expected to be priced at \$1300-\$1800. At GTAT, we have a roadmap to reduce costs even further.

Our company has a rich heritage as a manufacturer of crystal growth furnaces, with a global installed base of thousands of systems, and a strong track record in increasing wafer diameters (see Figure 4). Our know-how in equipment design, process scaling, facility planning, and the supply chain helps us to ramp SiC capacity faster, while competing successfully on price and quality. We are now in a position to push forward with 200 mm SiC, thanks to our continuous improvement, grounded in increased cycles of learning and optimization, along with R&D efforts. Our 200 mm product launch is slated for late 2021/early 2022.

If SiC continues to follow in the footsteps of the silicon industry, the next wafer size could be 300 mm. According to our initial thermal modelling, implementing unique hot-zone design components could minimize the applied shear stress, which is responsible for generating dislocations and micropipes, along with the von Mises stress that is to blame for boule cracking. If, further down the line, the industry seeks a 300 mm SiC wafer to reduce costs, we are confident in our ability to develop that nextgeneration crystal.

# THE GLOBAL LEADER IN EPIWAFER SUPPLY

**Enabling the Best RF, Photonics & Power Semiconductors**

'One-stop-shop' for III-V & Silicon epiwafer products

2" to 6" epitaxy ready substrates & polycrystalline materials

Multiple manufacturing sites; Europe, Asia & America

Leveraging 30+ years of compound semiconductor IP

Custom engineered structures; R&D to production volumes

EUROPE: +44 2920 839 400

AMERICAS: +1 508 824 6696

APAC: +886 3 579 8181

ALL INQUIRIES: sales@igep.com

RF

## **GaN HEMT**

5G Infrastructure Radar, EW/ECM, & SATCOM

## GaAs HBT / pHEMT / BiHEMT

5G Smartphones & Infrastructure WiFi6 Hotspots, GPS & IoT

## SiGe HBT

5G Smartphones WiFi6, Bluetooth, GPS & IoT

## **PHOTONICS**

InP Laser & Detector

Optical Comms & Data Centres

SW IR Imaging

**GaSb Laser & Detector**

MW-LW IR imaging

Biometrics

## GaAs VCSEL

3D Sensing & LiDAR

Datacoms

## **POWER**

## GaN on Si HEMT GaN on GaN

Electric Vehicle Systems

Power Conversion & Storage

## **GaAs Multi-Junction Solar**

High Efficiency Terrestrial CPV & Space PV

## **GaN LED & Laser**

MicroLED Display & AR/VR

UV Sterilisation

## A G E N D A 2 0 2 1

## DAY 1 AGENDA

Day 1 - Tuesday 9th November 2021

08:00 Registration and welcome refreshments

08:50 Housekeeping by Chris Meadows, Conference Chair

## SATISFYING DEMAND FOR MORE DATA

#### 09:00

Enabling wider mobile bandwidth no matter what frequency you choose.

Presented by Ben Thomas - Qorvo

#### 09:25

Presentation Title to be Confirmed

#### 09:45

Millimetre-wave MMICs and integrated solutions enabling highthroughput 5G deployments

Presented by Eric Leclerc - United Monolithic Semiconductors

## 10:05

The future of Germanium: Breakthrough Opportunities Presented by Pieter Arickx - **Umicore**

## 10:25

Improving yield for 5G market through defect inspection and metrology

Presented by Varun Gupta - KLA Corporation

## 10:45

5G drives Compound Semi business expansion" Presented by Claire Troadec - Yole Développement

## 11:05 MORNING BREAK

**Sponsored by Hewlett Packard Enterprise**

## SEEKING NEW OPPORTUNITIES FOR LEDs AND LASERS

## 11:35

Improving the architecture of the GaN VCSEL Presented by Tatsushi Hamaguchi - Sony Corporation

## 12:00

Can MicroLEDs and VCSELs revolutionize the Solid State Lighting Industry?

Presented by Pars Mukish - Yole Développement

## 12:20

Refining microLED technology

Presented by Wei Sin Tan - Plessey Semiconductors

## 12:40 LUNCH BREAK

Sponsored by Hewlett Packard Enterprise

#### 13:55

Advanced technology of plasma dicing for GaAs VCSEL Presented by Shogo Okita - **Panasonic**

#### 14:15

Optimizing 200mm Metal Lift-off for Smaller Dimensions Presented by Philip Greene - Ferrotec

#### 14:35

Recent trends in LED and LASER diode device material characterization

Presented by Yves Lacroix - YSystems Ltd

#### 14:55 AFTERNOON BREAK

Sponsored by Hewlett Packard Enterprise

## 15:25

Highly uniform thin films and tool stability - key drivers for future LED display production

Presented by Stefan Seifried - Evatec

## 15:45

Customer-specific VCSELs and VCSEL arrays technology development

Presented by Marcin Gåbski - VIGO System

## 16:05

Seeking new opportunities for LEDs and lasers Presented by Samuel Sonderegger - Attolight

## 16:25

Leading-Edge MOCVD Technology Enabling Next-Generation Photonics Applications

Presented by Mark McKee - Veeco

## 16:45

Compound Semiconductor Integration – Wafer Bonding towards new Di(e)mensions

Presented by Thomas Uhrmann - EV Group

## 17:05

Presentation title to be confirmed

## 17:05 Closing Remarks

17:10 Networking Drinks Reception and Dinner

2021 Agenda Correct as of 24 Aug 2021 8:40am

For the latest version of the agenda, visit **csinternational.net**

## **DAY 2 AGENDA**

## Day 2 - Wednesday 10th November 2021

08:00 Registration and welcome refreshments

08:50 Housekeeping by Chris Meadows, Conference Chair

## RAMPING VOLUMES IN THE POWER ELECTRONICS SECTOR

#### 09:00

Presentation title to be confirmed Speaker to be confirmed

#### 09:25

The SiC & GaN Power Semiconductor Market: Forecasts and Drivers

Presented by Richard Eden - Omdia

#### 09:45

Driving the adoption of CoolGaN technology Presented by Gerald Deboy - Infineon

#### 10:05

Solutions for high volume manufacturing of wide bandgap materials

Presented by Jens Voigt - AIXTRON

#### 10:25

Expanding opportunities for 650 V GaN FETs Presented by Frédéric Dupont - **Exagan**

## 10:45

Latest technologies for laser dicing, blade dicing of SiC and new ultra-thin grinding

Presented by Gerald Klug - DISCO HI-TEC Europe GmbH

## 11:05

Reinforcement Factories

Presented by Julie Orlando - Nanotronics

## 11:25 MORNING BREAK

Sponsored by Hewlett Packard Enterprise

## 11:55

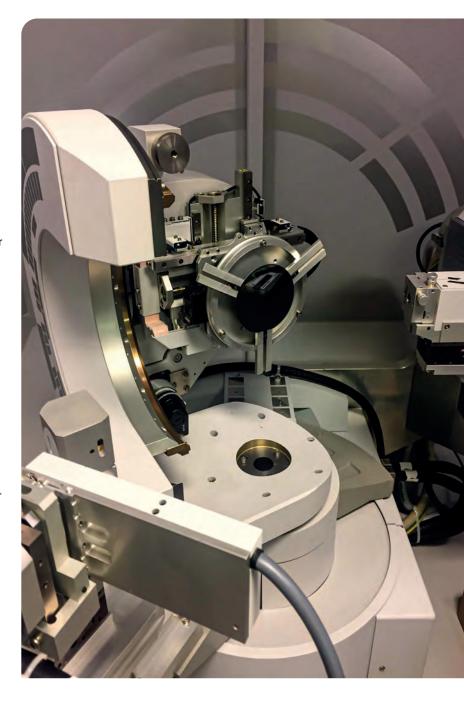

Using high speed XRDI to improve and monitor SiC substrate quality

Presented by Paul Ryan - Bruker

## 12:15

Advanced in-situ metrology for high-yield epitaxy of SiC/SiC, GaN/SiC and GaN/Si device structures

Presented by Iris Claussen - Laytec

## 12:35

Presentation Title to be Confirmed - Revasum

Presented by Rob Rhoades - Revasum

## 12:55

Unlocking The Full Potential of GaN Power: 650V, 1200V and Beyond Discreet Switches and Monolithic ICs on 200mm QST® Manufacturing Platform

Presented by Vlad Odnoblyudov - **Qromis**

#### 13:15

Advanced Plasma Processing solutions enabling the cost down per wafer and critical device performance required to accelerate the HVM of GaN and SiC Power devices.

Presented by Dr Mark Dineen - Oxford Instruments

#### 13:35

Hybrid monocrystalline silicon substrates for III-V heterostructures *Presented by Alexey Redkov - Alterphasic*

## 13:55 LUNCH BREAK

**Sponsored by Hewlett Packard Enterprise**

## TAKING WIDE BANDGAP DEVICES TO THEIR ULTIMATE LIMITS

#### 15:10

Ramping production of gallium oxide diodes and transistors *Presented by Kengo Takeuchi - FLOSFIA*

#### 15:35

A New Technology of Commercialization for GaN on Diamond HFMTs

Presented by Won Sang Lee - RFHIC US Corporation

#### 15:55

Presentation title to be confirmed - Soitec Presented by Marianne Germain - Soitec

## **ENHANCING THE AUTOMOBILE**

## 16:15

High-power blue VCSELs and VCSEL arrays

Presented by Masaru Kuramoto - Stanley Electric

## 16:40

Compound semiconductor adoption by automotive market Presented by Ezgi Dogmus - Yole Développement

## 17:00

Electrochemical Deposition of Gold as Optimal Choice for Device Cost and Performance

Presented by John Ghekiere - ClassOne

## 17:20

New CS Markets Challenge Traditional Reliability Testing Paradigms