# COMPOUND SEMICONDUCTOR

CONNECTING THE COMPOUND SEMICONDUCTOR COMMUNITY

# SUPERIOR SEALING GREENE TWEED SUPPORTS THE RAMPING CS INDUSTRY

VOLUME 30 ISSUE VII 2024

COMPOUNDSEMICONDUCTOR.NET

## INSIDE

News, Analysis, Features, Editorial View, Research Review and much more

## Ready or not, Al is here to stay

Al and machine learning hold the key to improving the running of every compound semiconductor fab

# Revolutionising RF oscillators

GaN IMPATT diodes enable compact and efficient solidstate oscillators that deliver high radio-frequency power

# Monolithically integrated lasers

Low-strain quantum cascade lasers are closing the gap to realising reliable infra-red sources on silicon

# AIXTRON

# THE NEW G10 SERIES

Your Productivity Solution for All Advanced Epitaxy Materials

### G10-SiC

- ▶ 9x150 mm (6") or 6x200 mm (8")

- ► New hardware & process surpassing Single Wafer Reactor uniformities

- ► +50% productivity per fab area with large batch technology & small footprint

#### **End Markets/Products:**

EV inverters & charging infrastructure

## G10-GaN

- ▶ 8x150mm (6") or 5x200mm (8")

- ▶ 1st fully automated compact GaN MOCVD cluster designed 100% for Si Power fabs

- Novel hardware solution for unmatched barrier uniformities and device yields

#### **End Markets/Products:**

Power Electronics & Wireless communication

## G10-AsP

- ▶ 8x150 mm (6") or 5x200 mm (8")

- ▶ 1<sup>st</sup> fully automated AsP MOCVD system enabling 10x lower defect density

- Unmatched wavelength uniformity on all wafer sizes

#### **End Markets/Products:**

Micro LED, Optical Data communication, 3D-sensing & LiDAR

# **VIEWPOINT**

By Richard Stevenson, Editor

## The long-term prospects for CPV

OVER THE COMING YEARS, the deployment of solar PV is forecast to rise substantially, before plateauing from 2037 at 3.4 TW per annum.

That figure for power generation is so big that's hard to put into perspective. It might help to know that all the PV installed to date stands at 1 TW. Or maybe it's easier to think that if 3.4 TW of power generation were provided by today's silicon panels, they would cover an area half the size of Belgium – or to put in another way, almost all of Hawaii or Shikoku.

As well as taking up a lot of land, 3.4 TW of silicon PV would consume a lot of the world's resources. Based on the make up of current panels, all the glass that's produced today would have to be given over to this application, which may well gobble up three times more silver than is on the market today.

These are scary numbers – and they encourage everyone in the PV industry to look at alternative forms of solar that are far less resource-intensive.

In this regard, concentrating photovoltaics (CPV) is a compelling candidate. Systems operating at several hundred suns or more use far, far less semiconductor material than those based on silicon, while the higher efficiency increases the power-generation density by around 30 percent, reducing the amount of land that's needed for power production.

One downside of CPV is that it's lacking a cohort of commercial pioneers. The technology appeared to be breaking through towards the end of the noughties, before the combination of a global credit crunch and plummeting prices of silicon PV thwarted success, causing its trailblazers to shut up shop.

But CPV may now be starting to see the very first steps of a revival. In Australia, RayGen is building novel plants

that combine many megawatts of electrical generation with substantial energy storage – and in Europe, efforts led by Fraunhofer ISE and tracker specialist Soltec have culminated in a refined form of CPV that employs five-junction cells from Azur Space Solar with an efficiency of around 40 percent (see p. 14 for details).

When you compare this latest design from the European team with those from the late noughties, you can see substantial improvements. They include the elimination of concrete structures to hold the trackers, a move to a higher level of concentration that trims costs –operation is now at 1000 suns - and the introduction of far smaller

cells that allow for thinner modules and passive cooling.

CPV will not grab the solar market by storm overnight. But as concerns mount over the consumption of material, and how much power can be produced from plots in sunny climes, this technology is sure to make a compelling case for its deployment.

Free weekly e-news roundup go to: compoundsemiconductor.net

## 20 Ready or not, Al is here to stay

The combination of AI and machine learning, in conjunction with automation, optimisation, and exception management, holds the key to improving the running of every compound semiconductor fab

# 28 Monolithically integrated QCLs on silicon

Low-strain quantum cascade lasers with optimised metamorphic buffer layers are closing the gap to realising reliable, high-power, infrared sources on silicon

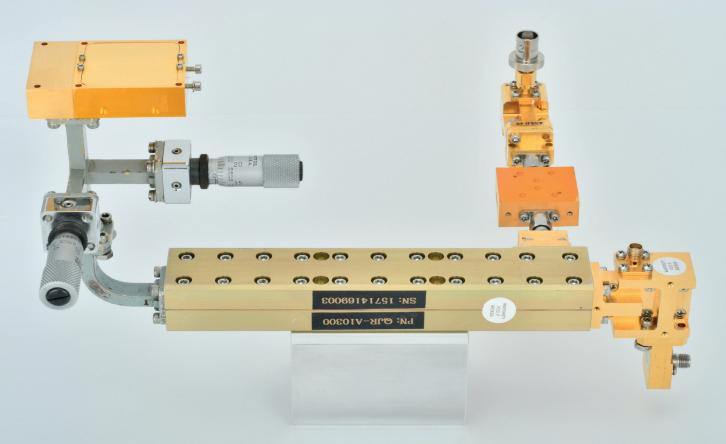

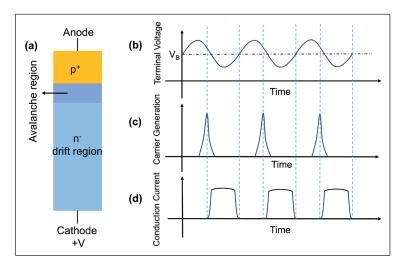

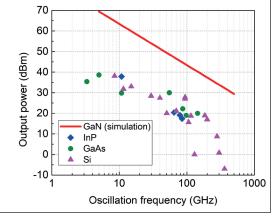

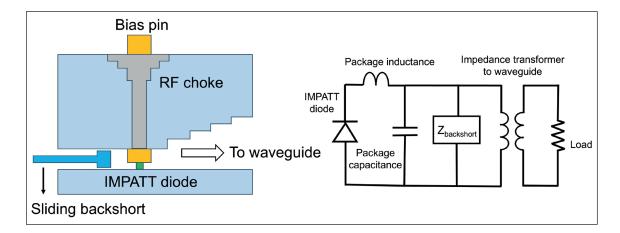

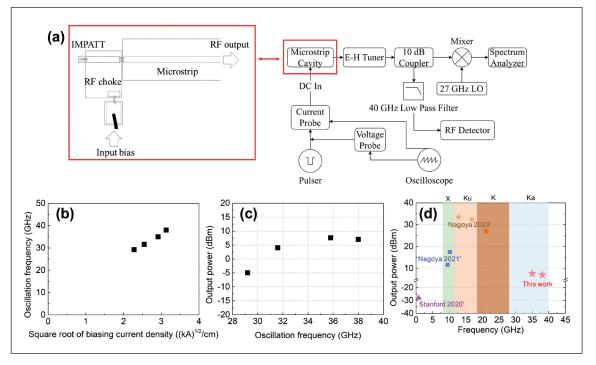

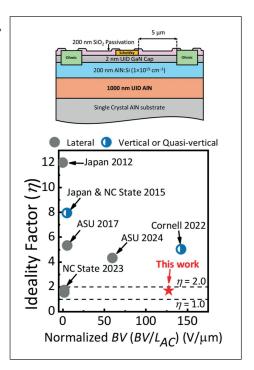

# 36 Revolutionising RF oscillators with GaN

GaN IMPATT diodes can enable compact and efficient solid-state oscillators that deliver higher powers in the millimetre-wave and beyond

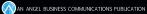

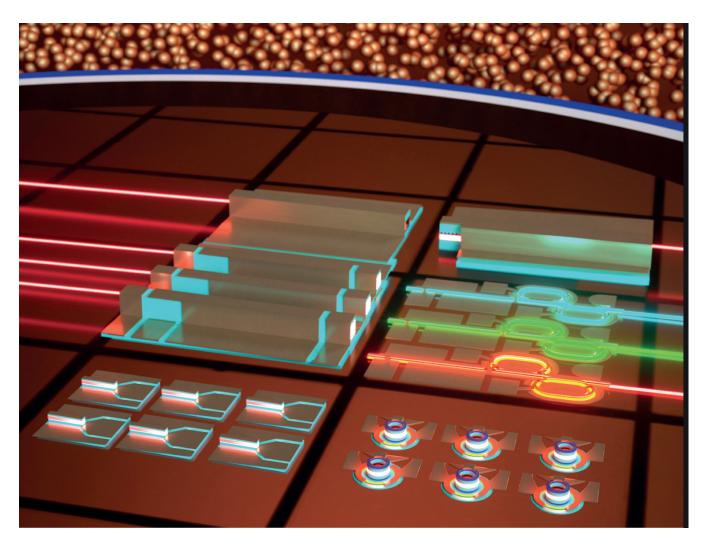

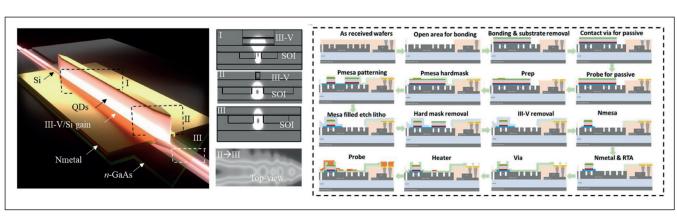

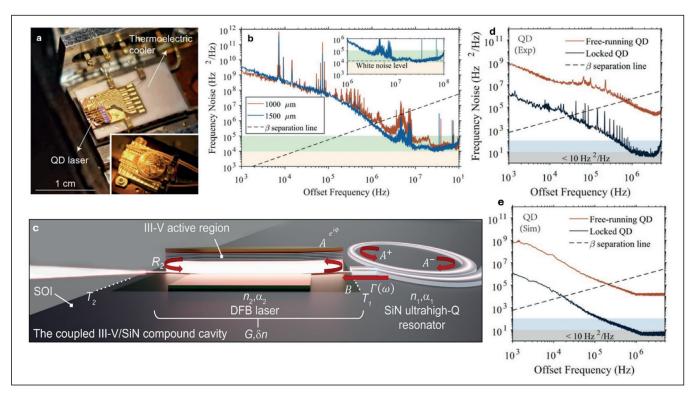

#### 42 Quantum dot lasers on silicon

Integrating quantum-dot lasers on silicon photonic chips promises to create high-speed devices for datacom and other applications

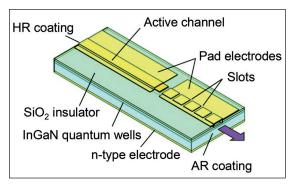

# 46 Propelling PCSEL emission to the mid-infrared

Turning to antimonides extends the emission of the PCSEL to the mid-infrared, enabling this source to provide a new class of cost-efficient active optical sensors

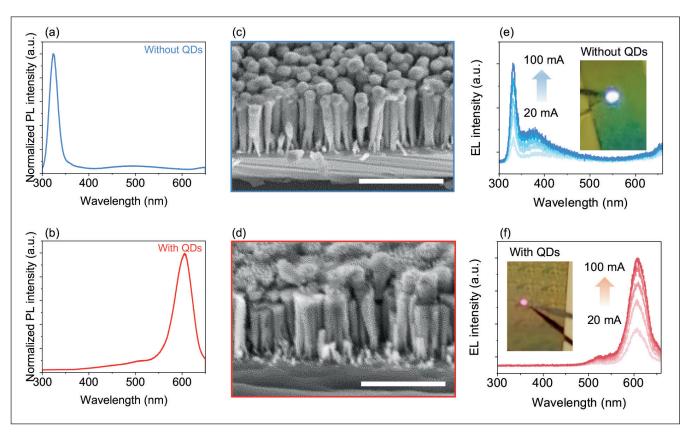

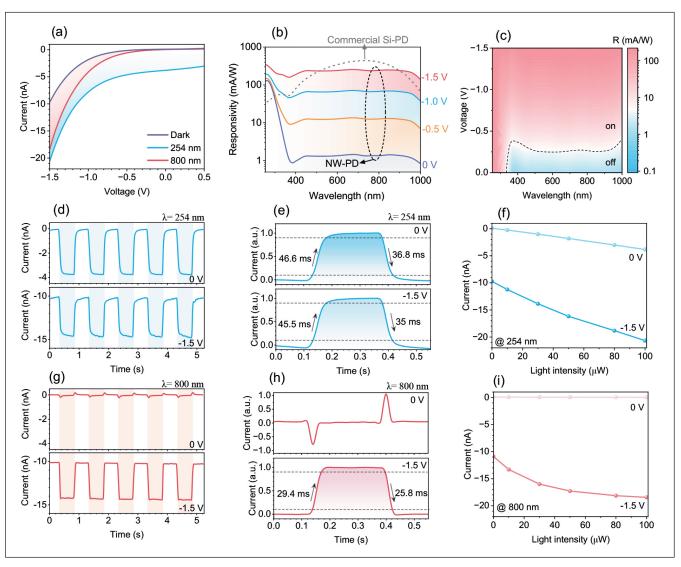

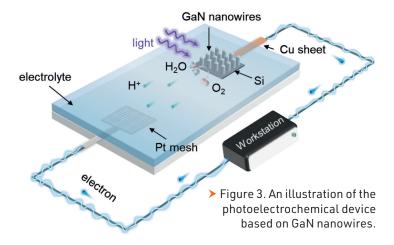

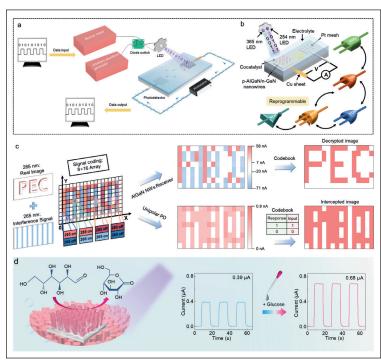

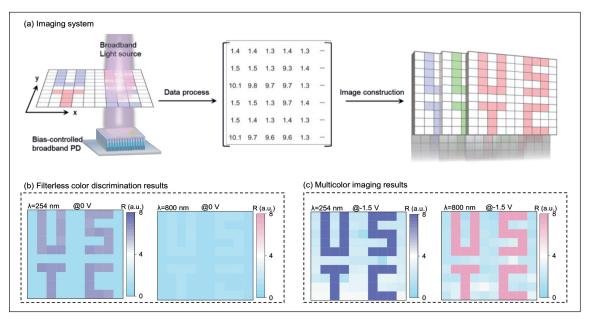

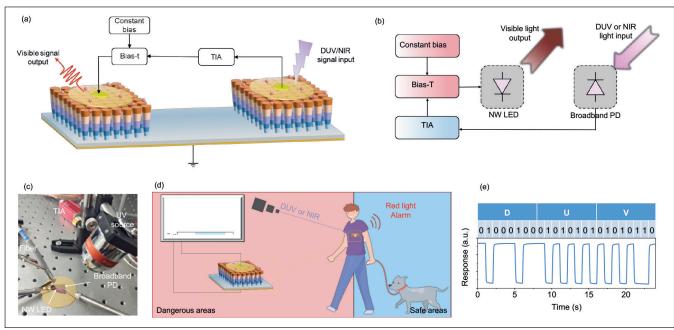

# 50 GaN nanowires on a silicon platform eye novel optoelectronics

Nitride nanowires with a large surface-to-volume-ratio offer intriguing optoelectronic properties that could advance integrated photonics

### **NEWS ANALYSIS**

## 14 CPV: Is a resurgence inevitable?

With record-breaking efficiencies and frugal materials usage, can concentrating photovoltaics (CPVs) succeed in tomorrow's solar sector?

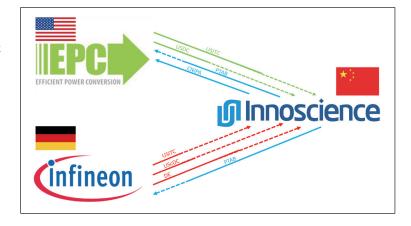

## 16 An escalating patents war

The battle over the intellectual property surrounding the GaN power transistor is intensifying, with EPC and Infineon attacking Innoscience over patent infringements that it vigorously denies

### RESEARCH REVIEW

- 58 Printing high-speed modulators on SOI

- 59 Boosting the performance of AlN-on-AlN Schottky barrier diodes

- 60 Realising tuneable InGaN laser diodes

#### **NEWS**

- 06 Power electronics: facing rapid capacity expansion

- 07 Infineon develops first 300 mm power GaN wafer

- 08 Lumileds addresses microLED efficiency through EQE and directionality

- 09 Sivers plans photonics spin-off

- 10 Finwave and GF partner on RF GaN-on-silicon

- 11 Element Six to lead DARPA **UWBG** programme

- 12 InP and TFLN: the way ahead for PICs?

Editor Richard Stevenson richardstevenson@angelbc.com +44 (0)1291 629640

News Editor Christine Evans-Pughe christine.evans-pughe@angelbc.com

Design & Production Manager Mitch Gaynor

mitch.gaynor@angelbc.com +44 (0)1923 690214

**Director of Logistics** Sharon Cowley sharon.cowley@angelbc.com

+44 (0)1923 690200

Senior Sales Executive Jacob Caulfield

jacob.caulfield@angelbc.com +44 (0)2476 718979

**USA Representative**

Darren Crawley darren.crawley@angelbc.com +44 (0)24 7671 8975

Senior Logistics Executive

Eve O'Sullivan

+44 (0)2476 823 123 eve.osullivan@angelbc.com

Circulation

Scott Adams scott.adams@angelbc.com

Publisher Jackie Cannon jackie.cannon@angelbc.com +44 (0)1923 690205

Chief Executive Office Sukhi Bhadal

sukhi.bhadal@angelbc.com +44 (0)2476 718970

**Chief Technical Officer**

Scott Adams

scott.adams@angelbc.com +44 (0)2476 718970

Directors

Jackie Cannon, Sharon Cowley

Angel Business Communications Ltd 6 Bow Court, Fletchworth Gate Burnsall Road, Coventry CV5 6SP, UK,

T: +44 (0)2476 718 970

E: info@angelbc.com

Compound Semiconductor is published nine times a year on a controlled circulation basis. Non-qualifying individuals can subscribe at: £105.00 per annum (UK), €158 per annum (Europe), \$198 per annum (air mail) (USA). Cover price £4.50. All information herein is believed to be correct at time of going to press. The publisher does not accept responsibility for any errors and omissions. The views expressed in this publication are not necessarily those of the publisher. Every effort has been made to a pola Business Communications Ltd © Copyright 2024. All rights reserved. Contents may not be reproduced in whole or part without the written consent of the publishers. The paper used within this magazine is produced by chain of custody certified manufacturers, guaranteeing sustainable sourcing. US mailing information: Compound Semiconductor, ISSN 1096-598X, is published 9 times a year, Jan/Feb, March, April/May, June, July, August/September, October, November, December by Angel Business Communications Ltd, Unit 6, Bow Court, Fletchworth Gate, Burnsall Rd, Coventry CV5 659. UK.Airfreight and mailing in the USA by agent named World Container INC 150-15, 183rd St, Jamaica, NY 11413, USA. Periodicals Postage Paid at Brooklyn, NY 11256. POSTMASTER: Send address changes to Compound Semiconductor, Air Business Ltd, c/o World Container INC 150-15, 183rd St, Jamaica, NY 11413, USA. We strive for accuracy in all we publish; readers and contributors are encouraged to contact us if they recognise an error or omission. Once magazine edition is published [online, in print or both), wed not update previously published articles to align old company names, branding, marketing efforts, taglines, mission statements or other promotional verbiage, images, or logos to newly created or updated names, images, typographic renderings, logos (or similar) when such references/images were accurately stated, rendered or displayed at the time of the original publication. When companies change their names or the images/fixed used to represent the comp

# Power electronics: facing rapid capacity expansion

A consolidation phase will follow the surge in manufacturing capacity, says Yole

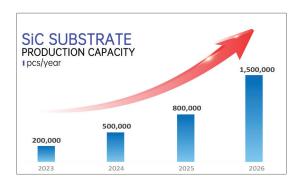

ACCORDING TO Yole's *Status of the Power Electronic Industry, 2024* report, the power electronics market will reach \$35.7 billion by 2029, growing at a CAGR of 7 percent from 2023, when it was \$23.8 billion.

The power electronics supply chain has recently rapidly expanded its manufacturing capacity, particularly for SiC and silicon devices, as well as SiC wafers. However, this will consolidate, driving technology innovations, price reductions, and new strategies, says

The discrete market, valued at \$15.5 billion in 2023, is projected to grow at a 3.9 percent CAGR to \$19.5 billion by 2029, driven mainly by xEV, OBC, DC-DC converters, and charging infrastructure. Automotive and consumer are the biggest market segments. Power modules, pushed by battery energy storage, EV DC chargers, and xEVs, are set to reach \$16.2 billion by 2029, with a 12.0 percent CAGR.

Milan Rosina, principal analyst for power electronics & battery at Yole Group, said: "The power device market is led by silicon, with SiC gaining ground in xEV and industrial applications, while GaN serves consumer power supplies and e-mobility. Gallium oxide could become a future contender."

Yole is projecting the SiC device market to reach nearly \$10 billion by 2029, with a compound annual growth rate (CAGR) of 24 percent from 2023 to 2029.

Here the key players are focusing on the transition to 8-inch wafers and addressing the associated challenges.

As of 2024, 400 V BEVs, such as those from Tesla, are the largest consumers of SiC. The introduction of more 800 V BEVs by OEMs is further accelerating this demand.

Wafer demand is rising accross the board, including 12-inch silicon wafers, with GaN-on-silicon using 6- and 8-inch wafers. SiC wafer capacity is expanding, risking oversupply due to lower xEV demand.

#### Power electronics supply chain

The power electronics supply chain is evolving due to five main factors, according to Yole. These are: expansion in wafer and device manufacturing capacity, with a shift toward larger wafer diameters: an increase in new silicon and SiC wafer manufacturers from China; mergers and acquisitions across wafer, device, packaging, and system manufacturers; device manufacturers diversifying technology portfolios (silicon, SiC, GaN); and finally, system makers horizontally integrating into various applications including photovoltaics, wind, EV DC charging, and battery energy storage systems.

"Recent years have seen rapid growth in manufacturing capacity, particularly

for SiC and silicon devices and wafers," says Rosina. "However, despite the demand drivers, the slowdown in xEV demand and the rush to increase capacity has led to overcapacity, especially in the SiC segment. This will likely lead to consolidation in the supply chain, fostering innovation, reducing prices, and creating new strategies. More partnerships, mergers, and acquisitions are expected in the coming years."

Chinese companies have a strong presence in end-systems like PV installations, wind energy, electric vehicles, and EV DC charging infrastructure and in power converter manufacturing. They also have extensive involvement in silicon and SiC wafer production and power device packaging.

The Chinese government and businesses are focused on addressing their reliance on foreign suppliers for bare dies, aiming to boost the market share of Chinese power device manufacturers in the near future.

# Infineon develops first 300 mm power GaN wafer

Company builds on existing large scale 300 mm silicon to more than double the number of GaN chips per wafer

INFINEON TECHNOLOGIES has succeeded in developing the world's first 300 mm power GaN wafer technology, claiming to be the first company in the world to master this groundbreaking technology in an existing and scalable high-volume manufacturing environment.

It believes the breakthrough will help drive the market for GaN-based power semiconductors. Production on 300 mm wafers, compared with 200 mm technology, offers 2.3 times more chips per wafer.

"This remarkable success is the result of our innovative strength and the dedicated work of our global team to demonstrate our position as the innovation leader in GaN and power systems," said Jochen Hanebeck (pictured above), CEO of Infineon Technologies AG.

"The technological breakthrough will be an industry game-changer and enable us to unlock the full potential of GaN. Nearly one year after the acquisition of GaN Systems, we are demonstrating

again that we are determined to be a leader in the fast-growing GaN market. As a leader in power systems, Infineon is mastering all three relevant materials: silicon, silicon carbide and GaN."

A significant advantage of 300 mm GaN technology is that it can utilise existing 300 mm silicon manufacturing equipment, since GaN and silicon are

very similar in manufacturing processes.

Infineon has succeeded in manufacturing 300 mm GaN wafers on an integrated pilot line in existing 300 mm silicon production in its power fab in Villach, Austria. The company is building on well-established existing production of 300 mm silicon and 200 mm GaN.

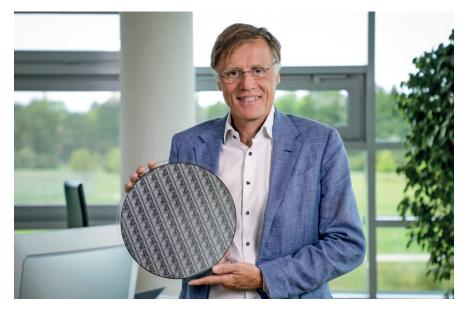

## **Advanced Compound Semiconductor Foundry Services**

MOCVD · Fabrication · Testing

Advanced III-V semiconductor solutions for optoelectronics application in the biotechnology, telecommunications, energy, industrial, and security industries.

MasimoSemiconductor.com | 603-595-8900

# Lumileds addresses microLED efficiency through EQE and directionality

Lumileds' R&D team realises Lambertian distribution from microLEDs

LUMILEDS has realised significant external quantum efficiency (EQE) performance for MicroLEDs in the past years. EQE, is the ratio between the energy contained in the light emitted from the LED and the energy in electrons injected into the semiconductor material.

- - - Lambertian 0.008 0.006 0.005 0.003 Incidence Angle (degrees)

However, for microLEDs, and display applications in particular, EQE on its

own is not a sufficient measure of performance. To properly assess the efficiency of a microLED, one must also be able to measure the directionality of the light. The directionality of light is critical for microLED displays, and for this reason, displays are often characterised by radiant or luminous Intensity, as seen from an angle.

"Most LEDs emit the majority of light from their top surface. This is especially true for thin film LEDs. When we shrink the size of thin film LEDs to become microLEDs, the 'side-emitting' surfaces become a significantly greater portion of the overall light-emitting surfaces," explained Brendan Moran, Lumileds' Senior Director of MicroLED Development.

"The thickness of what we described as a thin film for a larger size LED now becomes substantial relative to the length and width of the microLED. This is a key reason why microLEDs emit a large portion of light from their sides, resulting in a wide viewing angle distribution and a reduction of intensity emitted from the top surface. For display applications, even high EQE microLEDs can have relatively low onaxis intensity," said Moran.

The Lumileds R&D team has now developed microLEDs with a highly desirable light distribution that approximates Lambertian distribution. The team's innovation results in brighter displays that consume less energy.

Most LEDs emit the majority of light from their top surface. This is especially true for thin film LEDs. When we shrink the size of thin film LEDs to become microLEDs. the 'side-emitting' surfaces become a significantly greater portion of the overall light-emitting surfaces

## Coherent raises efficiency of InP CW lasers

LASER AND NETWORKING firm Coherent has launched a range of high-efficiency continuous wave (CW) distributed feedback (DFB)

Designed to operate in the O-band (1310 nm region), the InP lasers are claimed to redefine the capabilities of silicon photonics modulators used in 800G and 1.6T optical transceivers. Featuring a proprietary low series-resistance design, the lasers achieve approximately 15 percent greater power efficiency compared with the current industry standard. This breakthrough addresses the critical demand for reduced power consumption in silicon photonics transceivers. providing customers with a clear edge in operational efficiency.

"Our new family of CW lasers for silicon photonics is creating a wave of excitement among industry leaders," said Kou-Wei Wang, VP of InP Directly Modulated Lasers & Photodiodes. "By lowering power consumption, we're addressing one of the most pressing challenges faced by our customers today. And with our upcoming expansion to a state-of-the-art 6-inch InP fab in Sherman, Texas, by 2026, we expect production capacity to be five times our current production rate, a significant ramp given the complexity of this material. We are committed to leading the market with technology and supply chain capacity as our customers increase demand in the InP laser sector."

The first offering in this laser family is a 70 mW 1310 nm laser, designed for uncooled, nonhermetic operation up to an 85°C junction temperature. Commercial shipments of this laser begin in September 2024. Coherent will release a higher-power laser for cooled operations, along with lasers tailored for the CWDM grid, in 2025.

# Sivers plans photonics spin-off

Merger expected to unlock value and create an independent US NASDAQ traded photonics company

SIVERS SEMICONDUCTORS AB has entered into a non-binding letter of intent to merge its Sivers Photonics Ltd subsidiary with byNordic Acquisition Corporation, a publicly-traded special purpose acquisition company.

The merger is expected to unlock significant value and create an independent US NASDAQ traded photonics company. (Sivers Photonics currently has approximately 80 percent of its net revenue in the US).

Once the merger is finalised, the company plans to establish headquarters in Silicon Valley, CA, with the manufacturing operations remaining in the UK.

Sivers today consists of two subsidiaries addressing two different markets: wireless and photonics. The Sivers' Photonics subsidiary has particular focus on InP technology, with which it develops customisable lasers aimed at high-growth Al infrastructure and sensing applications for data centres, consumer healthcare and automotive lidar. The company has three issued patents and 16 patents pending across the US, UK, Canada and the World Intellectual Property Organisation.

Additionally, Sivers Photonics has development contracts to develop unique lasers for several leading silicon photonics providers, such as Ayar Labs, and is in discussion with several leading AI companies, including hyperscalers.

Subsequent to the proposed spinoff and Sivers Photonics merger combination, Sivers' remaining wireless business will consist of a portfolio of products in millimetrewave beamformer front-end integrated circuits, RF transceivers, repeaters, and software algorithms for millimetrewave RF performance for satellite and 5G infrastructure. Wireless business

net revenue growth was 155 percent in 2023, reaching approximately \$15 million. These markets are developing rapidly, and Sivers has secured a number of contracts and design wins that are projected to drive significant product revenue growth over the next 3-5 years.

"We believe the potential for Al Photonics is immense yet overshadowed by the equally exciting Sivers' Wireless business unit. With the attractive opportunity for silicon photonics in Al infrastructure and the emerging demand for photonic biometric sensors, we feel now is the right time to shine a light on this business unit as a standalone entity

to gain access to the US capital markets and create an opportunity for our shareholders to participate in its potential future success," said Bami Bastani, Sivers Semiconductor chairman.

"At the same time, we also look to capitalise on the success of the Sivers' Wireless business unit and the demand for our leading-edge millimetre-wave beamformer solutions for satellite and 5G, which has gained substantial traction with customers in these developing markets over the last several years, enabling us to create a fully fabless and less capital-intensive company that will remain listed under Sivers Semiconductors AB."

Subsequent to the proposed spin-off and Sivers Photonics merger combination, Sivers' remaining wireless business will consist of a portfolio of products in millimetre-wave beamformer front-end integrated circuits, RF transceivers, repeaters, and software algorithms for millimetre-wave RF performance for satellite and 5G Infrastructure

# Finwave and GF partner on RF GaN-on-silicon

New agreement to accelerate development of Finwave's E-Mode MISHEMT technology

GaN COMPANY Finwave

Semiconductor has announced a

strategic technology development

and licensing agreement with

GlobalFoundries (GF). This partnership

merges Finwave's RF GaN-on-silicon

technology with GF's US-based highvolume manufacturing capabilities and

legacy of RF innovation including RF

SOI and silicon-germanium solutions.

The two companies believe they can offer a solution for high-efficiency power amplifiers in applications where traditional GaAs and silicon technologies fall short. This includes new higher frequency 5G FR2/FR3 bands, 6G and millimetre-wave amplifiers, and high-power Wi-Fi 7 systems, where superior range and efficiency are critical.

Finwave's GaN-on-silicon enhacement-mode MISHEMT technology is designed to deliver high gain and efficiency at sub-5 V voltages. The collaboration will focus on optimising and scaling the MISHEMT platform to volume production at GF's 200 mm semiconductor manufacturing facility in Burlington, Vermont, using GF's 90RFGaN process.

"This agreement marks a significant milestone for Finwave," said Finwave Semiconductor CEO Pierre-Yves Lesaicherre. "By leveraging GlobalFoundries' extensive manufacturing capabilities and bringing Finwave's E-mode MISHEMT technology breakthrough to volume production, we are unlocking large growth opportunities as we address the increasingly demanding wireless communication landscape.

This partnership opens the door to further innovation and integration of RF front-ends onto a single GaN-on-silicon device. This has never been done before, and has the potential to reduce cost and size, both of which are at a premium in cellphones."

"As next-generation wireless networks require devices that operate at higher frequencies, Finwave's low-voltage GaN-on-silicon technology combined with GF's 90RFGaN platform will become a vital part of power amplifiers in future mobile phones, ensuring both robust performance and high-power efficiency," said Shankaran Janardhanan, VP and general manager of GF's RF Business.

Finwave and GlobalFoundries aim to qualify this technology for mass production in the first half of 2026.

## Geely EVs using Rohm SiC MOSFETs

ROHM has announced the adoption of power modules equipped with fourth generation SiC MOSFET bare chips for the traction inverters in three models of ZEEKR EV brand from Zhejiang Geely Holding Group, a Chinese car maker.

Since 2023, these power modules have been mass produced and shipped from HAIMOSIC Ltd. – a joint venture between Rohm and Zhenghai Group to Viridi E-Mobility Technology, a Tier 1 manufacturer under Geely.

Geely and Rohm have been collaborating since 2018, beginning with technical exchanges, then later forming

a strategic partnership focused on SiC power devices in 2021. This led to the integration of Rohm's SiC MOSFETs into the traction inverters of three models: the ZEEKR X, 009, and 001. In each of these EVs, Rohm's power solutions centered on SiC MOSFETs play a key role in extending the cruising range and enhancing overall performance.

The ZEEKR X features a maximum output exceeding 300 kW and cruising range of more than 400 km. The 009 minivan features an intelligent cockpit and large 140 kWh battery, achieving a maximum cruising range of 822 km. The flagship model, 001, offers a maximum

output of over 400 kW from dual motors with a range of over 580 km along with a four-wheel independent control system.

# Element Six to lead DARPA UWBG programme

Diamond substrate expert to partner with Orbray, Raytheon, Hiqute Diamond, and the universities of Stanford and Princeton on next-generation semiconductors

ELEMENT SIX, part of the De Beers Group, will lead a US Defense Advanced Research Projects Agency (DARPA) programme to develop advanced UWBG (ultra-wide bandgap) semiconductors.

The goal is to develop UWBG substrates, device layers, and junctions, for next-generation electronics, including high-power RF switches, amplifiers for radar and communications, high-voltage power switches, high-temperature electronics for extreme environments, and deep-UV LEDs and lasers.

E6's contribution will harness the company's expertise in large area CVD polycrystalline diamond and high-quality single-crystal diamond synthesis, to realise 4-inch device-grade single-crystal diamond substrates.

E6 will be partnering with Orbray in Japan (with diamond heteroepitaxy expertise), Raytheon (leaders in GaN RF devices), Hiqute Diamond in France (with dislocation engineering expertise), and Stanford and Princeton Universities in the US (with materials bulk and surface processing characterisation expertise).

Daniel Twitchen, chief technologist at Element Six, said: "Industrial diamond has disrupted multiple markets since its first scale synthesis in the 1950s, and I am confident that technology breakthroughs in ultra-wide bandgap semiconductors will help unlock another 70 years of positive disruption in the semiconductor industry."

E6 polycrystalline diamond wafers over 4 inches in diameter are already enabling telecommunication infrastructures and defence applications, being used as either optical windows in EUV lithography for silicon chips, or in thermal management applications for high-power density silicon and GaN devices

E6 SC diamond was a crucial enabler in the CERN Large Hadron Collider's monitoring systems, helping lead to the discovery of the Higgs boson. In partnership with high-power semiconductor leader ABB, E6 realised the first high-voltage bulk diamond-based Schottky diodes. Furthermore, E6 recently completed build and commission of an advanced CVD facility using its core technology in Portland, OR, powered by renewable energy sources.

# InP and TFLN: the way ahead for PICs?

IDTechEx report says addressing material challenges is crucial for advancing PIC technology

IDTechEx has published a new report, Silicon Photonics and Photonic Integrated Circuits 2024-2034: Market, Technologies, and Forecasts that explores emerging PIC materials including thin-film lithium niobate and barium titanite, along with new applications such as Al.

The report says that photonic transceivers for AI are poised to become the largest demand source for PICs, driven by increasing need for high-speed, efficient data processing in Al applications. Additionally emerging technologies such as programmable photonics, photonic quantum computers, and co-packaged optics will redefine the capabilities and applications of PICs, unlocking new potentials in computing, communication, and sensing technologies.

Despite these advantages, the PIC market faces several challenges. Material limitations complicate the development and performance of PICs.

While silicon and silica are common in current PICs, they are not the most efficient materials for light sources or photodetectors. This necessitates the combination of silicon with III-V materials; however, this brings another challenge to the table - integration complexity. Combining different materials and components into a single PIC requires intricate engineering and manufacturing processes, ensuring compatibility and consistent performance across the various materials.

While silicon remains dominant, several emerging materials are gaining traction. Thin-film lithium niobate (TFLN) offers moderate Pockels effect and low material loss, making it ideal for highperformance modulation applications, including quantum systems and future high-performance transceivers.

Monolithic InP continues to be significant due to its ability to detect and emit light, though it faces challenges related to high losses and costs. Barium titanite, known for its superior modulation performance, is anticipated to find applications in quantum photonic systems where

modulation efficiency is paramount. SiN provides lower losses compared to other materials but comes with higher costs and larger device sizes due to its low refractive index, limiting its current widespread adoption.

# RIBER'S MBE 6000

LOW RESIDUAL BACKGROUND

**LOW ENERGY DEPOSITION**

**LOW TEMPERATURE**

**LOW DEFECTS DENSITY**

CRYSTALLINE PERFECTION

HIGH UNIFORMITY

CONTROL AT MONOLAYER SCALE

HIGH REPRODUCIBILITY

RIBER

**INNOVATIVE SOLUTIONS FOR SEMICONDUCTOR INDUSTRY**

# CPV: Is a resurgence inevitable?

With record-breaking efficiencies and frugal materials usage, can concentrating photovoltaics (CPVs) succeed in tomorrow's solar sector?

SILICON IS THE entrenched technology for photovoltaics. Sales of panels made from this material are continuing to soar, supported by decades of high-volume production that cause prices to fall and ensure that this technology is ever more competitive. It's a direction of travel that leads many to assume that silicon will always hold a vice-like grip on the solar market.

But it's not a narrative everyone espouses. Calling it into question is Fraunhofer ISE academic Frank Dimroth, who is helping to commercialise a refined and superior design of CPV.

He argues that alternatives to silicon with superior efficiencies have good long-term prospects, based on the premise that investors in solar technology will always seek higher performances and a good return on the land they are using for power generation. Consequently, these investors want to select the solar technology that delivers the highest level of energy generation per unit area, a metric where silicon struggles.

The thought of shifting away from silicon will surprise many, given the vast amount of land that is unsuitable for the likes of farming and building dwellings.

"But even in the deserts, [land is] not really always available, because there are constraints in terms of not having a huge impact on the environment," counters Dimroth, who points out that governments only permit a certain amount of land to be transformed into industrial renewable-energy fields. Conversations Dimroth has had reveal that in countries such as the United Arab Emirates, where the land that's available is quite limited, there is a strong desire to produce a lot of renewable energy, making high-efficiency PV very attractive.

Against this backdrop, today's silicon solar panels are already encroaching their efficiency potential. Due to this, there is motivation to switch to an alternative materials technology that will deliver a significant boost in the power generation density. While this transformation will not happen overnight, and the rise of any alternative will be far from easy, Dimroth believes that there is good reason to believe that silicon's dominance will diminish eventually.

The two leading candidates for delivering higher power densities are III-V multi-junction solar cells under high concentration (CPV) and tandem solar cells made of perovskite absorbers.

The latter already achieves high efficiencies in the laboratory, but there are concerns over its capability to maintain a high performance over many years.

According to Dimroth, the stability of perovskites used in high efficiency solar cells is a major challenge. "There is interaction with moisture, which is a fundamental problem," argues Dimroth, who points out that ion migration also takes place in this class of materials and has been found to accelerate degradation.

Due to this instability, it is not clear whether these cells will ever reach the 30-year lifetime that silicon has today.

"In terms of cost structure, you want to have a very reliable technology that keeps going over 30 years, because then you can depreciate your power plants over 25 or 30 years," explains Dimroth.

> Dual-axis CPV systems developed by Fraunhofer ISE and Soltec, and incorporating five-junction cells from Azur Space Solar with an efficiency of around 44 percent, are designed to minimise both the bill of materials and production costs.

## NEWS ANALYSIS | PHOTOVOLTAICS

Modules that degrade before then fail to be commercially attractive, even if they offer gains in efficiency over silicon.

With CPV, cell efficiencies are ground-breaking – the current world record, held by Fraunhofer ISE, is 47.6 percent – and there are no concerns relating to the robustness and the reliability of this technology, which is quite similar to the solar cells used in space satellites for decades.

What's more, with CPV, volumes of materials required for power generation are relatively low. That's a big deal, argues Dimroth, given that solar deployments are forecast to climb substantially over the coming years, before plateauing at around 3.4 TW per annum in 2037. To put that figure in perspective, all the PV deployed until now stands at around just 1 TW.

If 3.4 TW were to be deployed using today's silicon PV, that would equate to 8.5 billion modules, covering an area of 15,600 km² – that's roughly half the size of Belgium. The resources consumed for this level of production are considerable, says Dimroth: "15,600 square kilometre would use all of the glass that is produced by the industry today, and, just as an example, three times more silver than is available on the market today."

While it is possible to increase production, using less material is more attractive, with CPV excelling in this regard.

#### A superior solution

Working with partners of the German-governmentfunded project micro-CPV and the Spanish firm Soltec, which has tremendous expertise in tracker technology, Dimroth and his colleagues at Fraunhofer have developed a new generation of CPV that boasts a module efficiency of 36.5 percent.

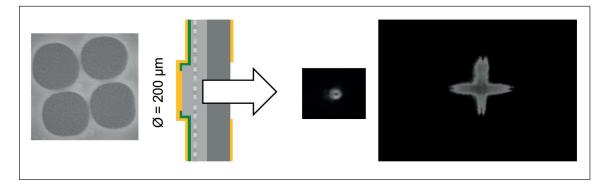

At its heart is a five-junction cell in pilot production at Azur Space Solar. Sunlight at a concentration of 500 to 1000 suns is focused onto the cells, just 750  $\mu m$  by 750  $\mu m$  in size, using a combination of a Fresnel lens and a glass ball that's approximately 1 mm in diameter and sits on top of the photovoltaic cell.

One of the merits of this design is that by using such a small cell – leading to the phrase micro-CPV – active cooling is not required. Helping to aid the thermal management is a printed metal circuit with traces transferring the heat away from the cell.

Much effort has been directed at minimising the assembly cost of these micro-CPV modules, which are similar in size to silicon panels, and have all the components sandwiched between a pair of glass sheets.

Contributing to a trimming of the costs is the use of glass balls for secondary optics that are enabling

concentration levels of 1,000 suns. These balls are already produced in high volumes, for example for reflectors in road networks.

As well as a minimised bill of materials, this micro-CPV design promise low assembly costs, realised by exploiting synergies with the emerging microLED display industry. To produce micro-CPV panels and microLED displays, myriad devices have to be transferred onto backplane, with a low cost for the panels key to commercial success. While Dimroth has not come up with all the solutions just yet, he's working on it, and looking to draw on what's been developed for the display industry.

Another lever for increasing the back-per-buck is a move to an even higher concentration. "I'm quite confident we can go to even 2,000 suns in the future," says Dimroth.

To help to refine, assess and validate their cuttingedge form of CPV, Dimroth and his co-workers are evaluating the tracker technology at the manufacturing site of Soltec, in Murcia, Spain.

"We want to demonstrate that this new tracking unit can fulfil the promises in terms of precision and economics," says Dimroth. There is hope that these efforts, involving dummy modules, will also attract investors keen to support the development of this micro-CPV technology and its tracking unit.

Looking further ahead, Dimroth hopes that in the next 18 months or so, the team will have a fully equipped prototype that fulfils expectation, in terms of power generation. This could provide the foundation for increasing manufacturing capacity for larger scale projects.

It's a sound plan that will hope to improve the prospects of CPV, which is the ultimate form of solar power generation, in terms of energy yield from a given area.

> Operating at a concentration of 1000 suns, the CPV systems developed by Fraunhofer ISE and Soltec offer an increase in the energy yield from a given area of 30 percent compared with silicon.

# GaN: An escalating patents war

The battle over the intellectual property surrounding the GaN power transistor is intensifying, with EPC and Infineon attacking Innoscience over patent infringements that it vigorously denies

#### BY RICHARD STEVENSON, EDITOR, CS MAGAZINE

WITHIN OUR INDUSTRY, last summer will be remembered as the start of a global war surrounding the intellectual property (IP) of the GaN power transistor. Back then, Efficient Power Corporation fired the first shots, accusing Innoscience of infringing four of its patents. In only a matter of days Innoscience shot back, denying any wrongdoing. More recently, another company has entered the fray, with Infineon claiming that Innoscience is also failing to respect its IP. And again, Innoscience is pleading innocence.

As claims and counterclaims are launched in courtrooms around the world, there is much value in hearing from those that combine expertise in this area with a neutral standpoint. Offering all this and more is David Radulescu, head of the patent litigation boutique firm Radulescu, who has been litigating semiconductor patents in courts throughout the US for three decades. More significantly, Radulescu also holds a PhD in compound semiconductor HEMTs and has previously devoted much effort to representing global companies fighting over IP associated with GaN-based LEDs.

In late July, Radulescu spoke for a second year in a row about the escalating IP war in a highly insightful webinar covering various patents that hold the key to deciding the outcome of the many court cases.

Before delving into details, Radulescu summarised the shots that had been fired to date: a pair of actions taken by both EPC and Innoscience in their battle, plus three fired by Infineon and another by Innoscience in their more recent skirmish.

This all kicked off last summer, when EPC announced it took legal action against Innoscience for infringing four of its patents. In the intervening months, EPC dropped two patents in its International Trade Commission (ITC) case, while initial rulings have been released on the other two this July. According to the administrative law judge (ALJ) in the ITC, both of EPC's patents are not invalid, but significantly, one of them is infringed.

What's also worth noting is that in the last couple of months action taken by Innoscience in China has also led to rulings that counterpart Chinese EPC patents were not invalid.

"We have Innoscience on its own turf losing in the Chinese Patent Office," remarked Radulescu, who added that the US Patent and Trademark Office (USPTO) is still considering the validity of the patent found to be infringed by the ALJ, although the claims and prior art at issue are identical.

Radulescu offered a closer look at the key patents after highlighting the recent stockpiling of US patents issued to Innoscience. In the past year-and-a-half, the Chinese chipmaker was issued 45 US patents, while EPC was issued only one, leading Innoscience to outpace EPC in the total number of US patents by 58 to 57.

#### Gate designs

Focusing on the shape of the gate structure is EPC's '508 patent, which the ALJ found to be not invalid but also not infringed. To put this patent in context, over the last few decades, a number of different gate structures have been used to produce GaN transistors, including: those that are self-aligned, with the gate and the insulator underneath having the same dimension (length); and those that have a T-shape or an inverted T-shape. The '508 patent describes a multi-step process involving the use of three different photoresist patterns to produce a self-aligned gate.

For the claims brought by EPC concerning this patent, the key issue, according to Radulescu, is whether "etching away the doped GaN layer, except a portion of the doped GaN layer beneath the gate contact," describes the Innoscience process.

"When you visually look at the [Innoscience] device, you see a gate ledge that is not co-extensive with the gate contact layer," said Radulescu, who is not surprised that the ALJ viewed this transistor as being different from that of EPC, and thus concluding that there was no infringement.

The other important matter relating to the '508 patent is that Innoscience has asserted that it is invalid, an argument that was rejected by the ALJ.

#### Doping and compensation

Radulescu believes that those involved in ruling on the EPC-Innoscience battle will have a more difficult decision to make when it comes considering claims surrounding the '294 patent entitled 'Compensated Gate MISFET'. In his view, what's crucial is to understand what is meant by 'compensated', against the backdrop of the difficulties that have had to be overcome to realise *p*-type doping in GaN, key to producing LEDs with this material system.

The key claim by EPC is whether the phrase 'compensated GaN layer' describes the GaN layer in Innoscience's devices that is presumed to be *p*-type based on its own publications.

It's important to note, argued Radulescu, that EPC's patent does not say anything about the GaN

layer's carrier type or its resistivity, characteristics that can be measured. Instead, it just uses the word 'compensated', a characteristic far harder to judge. This is because a picture or image of the device material is not determinative, but requires an understanding of semiconductor material science.

The other key point that Radulescu emphasised is that the '294 patent covers simply a transistor, and makes no reference to enhancement-mode or depletion-mode devices.

Many are assuming that the GaN employed by Innoscience is *p*-type. "They introduced magnesium, and I will be willing to bet that the hydrogen is intentionally removed after growth," remarked Radulescu, whom added that secondary ion mass spectrometry (SIMS) plots have been disclosed during the case. "Whether or not you can call it 'compensated' depends upon how you define what compensation is," added Radulescu.

Innoscience has argued that they do not employ a compensated GaN layer because they use a Schottky gate, as well as claiming that SIMS data reveals dopant activation, and testing confirms *p*-type conductivity. According to Radulescu, all these arguments were rejected by the ITC staff due to procedural errors of its counsel. For example, Innoscience offered evidence of the nature of the GaN through the testimony of an employee, an account viewed as problematic due to self-interest.

"Unfortunately for Innoscience, I don't think their best arguments were put forward," commented Radulescu, who explained that the full Commission will now review the ALJ's initial determination of infringement and issue a final decision on the investigation called a Final Determination, which is expected to issue in early November 2024.

Both Innoscience and EPC have tried to claim victory from the initial determination. Innoscience argues that it has won, because one of the patents was determined to not be infringed, while EPC is focusing on a finding of infringement.

The view of Radulescu is that while, in theory, EPC lost on three patents out of four, what really matters

#### NEWS ANALYSIS I IP

is that it has a ruling of a violation of the ITC statute against unfair competition by importing products that infringe US patents. And he believes that given how Innoscience's lawyers argued their defences, it will be far from easy to get the ALJ's determination reversed or modified, although not impossible.

Looking ahead, in March 2025, the US Patent Office will rule on the validity of the four patents asserted by EPC against Innoscience (which are also still at issue in EPC's District Court case against Innoscience in California). If the '294 patent is determined to be invalid, this decision could be appealed, dragging the case on for a couple more years. Significantly, under this scenario, the ITC's final determination will likely not matter as any potential importation ban would be expected to be stayed pending appeal. On the other hand, if the '294 patent is determined to not be invalid, and at the same time the full Commission agrees with the ALJ on infringement of the '294 patent, Innoscience's products found to infringe would presumably be subject to some form of importation ban as that is a typical remedy available to patent owners in these type of ITC investigations.

#### Infineon versus Innoscience

Infineon's actions against EPC began in March this year, when they brought a suit in San Francisco for a patent associated with high-voltage packages featuring so-called 'source sensing'. Innoscience response to this has been to file a petition this June with the US Patent Office, arguing for invalidation of every single claim.

Meanwhile in Germany, Infineon has also filed several cases, as well as obtaining a preliminary injunction that prevented a small fraction of Innoscience's high-voltage GaN transistors from being promoted at PCIM.

Commenting on this, Radulescu remarked: "Infineon outmanoeuvred Innoscience's lawyers, because they got that injunction without Innoscience actually being heard on any of the issues. It was a surprise, but not unusual for parties to go to Germany to try to get these preliminary injunctions and mess up trade shows."

Within the last few weeks, Infineon has stepped up its action, adding three more patents to the San Francisco case, and filing its own complaint with the ITC. On the merits, the first of four Infineon patents that have been asserted involves an additional connection to the source of the power transistor, so that the parasitic elements associated with the packaging and connections have a reduced impact on overall system performance.

Infineon's accusations centre on Innoscience's use of a Kelvin source that it claims practices the patented source sensing functionality, as well as an identical pin layout. Like Infineon's products, those in question from Innoscience have 8 pins, including one that's a Kelvin source sensor.

Regarding the three other patents, one is concerned with the thickness of a titanium nitride capping layer in an electrode stack. The other two concern so-called 'merged cascode transistors', with one patent concerned with adding curvature to interdigitated fingers to trim the electric field strength at the edge of the electrodes, and the other associated with combining a depletion-mode transistor with an enhancement-mode transistor to make a circuit. If the case is not settled beforehand, the ALJ's initial rulings on these patents are not expected until autumn 2025.

While it is impossible to predict the rulings of all the asserted claims to date in the GaN patent war, there is no doubt that substantial time and money will be spent over the next few years trying to defend IP and the products based on them. There are many different outcomes that could emerge, including licensing deals and import bans – but what is for sure is that interesting times lie ahead.

## YOUR PARTNER FOR **EXHAUST GAS TREATMENT**

#### PROCESS APPLICATION

- Ion Implantation

- Plasma Etch

- Chamber Clean

- Photovoltaics

- HDP-CVD

- LPCVD

- PECVD

- MOCVD

- ALD

#### **PLASMA** CONVERSION **SYSTEMS**

Removal of perflourinated compounds by high efficiency atmospheric plasma

#### **CLEAN-PROTECT**

emergency leakage in gas cabinets

#### **CLEANSORB®**

Point-of-exhaust absorption for process waste gas

#### **CLEANVENT**

Removal of hazardous gases during purging of vent lines

#### **CLEANSORB® Dry Bed Abatement**

- Safe, dry chemical conversion of hazardous gases to stable solids

- Proprietary CLEANSORB® media

- No handling of toxic waste

- ▶ Practically maintenance-free

- Local Refill service worldwide

www.csclean.com

VISIT US AT SEMICON EUROPA, 12TH - 15TH NOVEMBER 2024, MUNICH, GERMANY, BOOTH C1 219

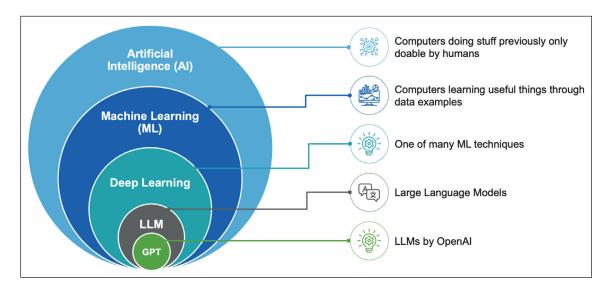

# **Ready or not,** Al is here to stay

The combination of AI and machine learning, in conjunction with automation, optimisation, and exception management, holds the key to improving the running of every compound semiconductor fab

#### BY JON HERLOCKER FROM TIGNIS

IN TODAY'S WORLD, everywhere we look we see claims of how Artificial Intelligence (AI) will disrupt our world. If you take these assertions at face value, you might start thinking that Al is some kind of magic that will solve almost all of humanity's issues. However, that's not the case. To ensure the successful application of AI, appropriate inputs and a level of creativity are mandatory. The reality is that the successful implementation of AI in a manufacturing environment is a combination of mathematics, science, and innovation.

While previous waves of AI enthusiasm have failed to deliver broad market benefits, today's and tomorrow's AI is certain to play a critical role in compound semiconductor manufacturing. Companies that successfully adopt either AI, machine learning (ML), or both of them before their peers will benefit from significant competitive advantages. According to management consultant McKinsey, AL/ML currently contributes between \$5 billion and \$8 billion to annual earnings at semiconductor companies – and that figure is forecast to increase ten-fold over the next two-to-three years.

Leading-edge device makers manufacturing at 10 nm and below are already years into their journey of deploying Al. For these chipmakers, their revenue and market valuation are justifying investing billions of dollars into custom-built Al solutions for their state-of-the-art fabs.

Despite manufacturing at mature process nodes, compound semiconductor fabs have much to gain from Al and ML (see Figure 1). That's because successful AI/ML projects focus on business value metrics that matter.

One famous formulation of business value in a manufacturing facility is based on Goldratt's Rules of Flow, which postulates that the two most important metrics for any factory are throughput and cost. AI/ML can directly improve both. Impacts include enhancing throughput by increasing yield and uptime, and trimming operating costs by reducing scrap and increasing engineering productivity.

It is possible to significantly improve throughput and cost metrics via AI/ML without having to invest millions of dollars of capital on new hardware. And if you have a leadership role in a compound semiconductor fab, part of your job in the next decade will be deciding where and when to invest in ML.

In addition to the core business properties outlined already, there are two additional business considerations of note: agility and resiliency.

Agility is the ability of a business to adapt to changes more quickly. How fast can you respond to changes in raw materials due to obsolescence? Or a change in product mix due to a market shift? And what about a dramatic change in workforce availability? There could also be market changes - like we are seeing with the opportunity in electric vehicles for makers of SiC and GaN power electronics.

When it comes to resiliency, this reflects the ability of a business to survive or even thrive in the face of losses – those of key personnel, equipment, customers, and facilities.

To understand where you should be considering applying AI/ML to improve productivity, agility and resiliency, you need to think about automation, optimisation, and exception management.

The first of these three considerations, automation, is the reduction of human intervention in a process. Human intervention tends to take place when there is the need to make a decision, or there is a need for human dexterity. AI/ML is a great enabler of increased automation. Turn to automation when you have humans spending non-trivial time on repetitive tasks, from tweaking recipes all the way to updating spreadsheets.

Optimisation is about making the best possible decision from the available data. It becomes a true superpower when paired with automation, enabling the equipment in your fab to continuously adjust key

## OPINION I TECHNOLOGY

Figure 1.

Decoding

AI/ML

terminology.

A Venn

diagram of the

most popular

ML tools.

parameters, so that it remains in an optimal range of operation. You should think about the times where you need to make human decisions regularly, and revisit the results of past decisions – for example, the parameters of your process recipes, your scheduling logic, or your preventative maintenance schedules.

The third consideration, exception management, is a core foundation of more advanced fabs (operationally, not by process node). While automation and optimisation are about creating increasingly predictable processes, even in the best fab environments, disturbances and exceptions happen. Equipment fails, software suffers from bugs, operators do unexpected things, material sometimes fails to meet specifications. As you automate more of your fab, how do you even know when something is wrong, or is about to go wrong? You should look to Al/ML to reduce exceptions, to better detect exceptions before they cause damage, and to diagnose and resolve exceptions more efficiently.

When we consider these three factors when applying Al/ML, one can sum it up as saying that more automation means less human intervention – lower cost, faster cycles, and more agility/resiliency. Meanwhile, optimising throughput and costs have direct and measurable business value, and exception management ensures that manufacturing processes remain stable and available, minimising exception cost. Automation, optimisation, and exception management all deliver direct revenue or cost benefits.

While AI is not magic, don't dismiss it as a distraction. It will move the business needle. It will increase your wafer flow, it will reduce your operational costs, and it will also increase your fab's agility and resiliency. There's no doubt that AI and machine-learning will become a critical part of the compound semiconductor manufacturing world, with those successfully adopting AI early enjoying significant competitive advantages. For those that fail to appreciate AI, their oversight will be seen in inferior balance sheets.

# Superior sealing

Greene Tweed's portfolio of precision seals offers tremendous support to empower the growth of the compound semiconductor industry

#### BY PRAGATI VERMA AND THYAG SADASIWAN FROM GREENE TWEED

FROM ULTRA-FAST communication and electric vehicles to energy applications and artificial intelligence, today's most innovative technologies rely on compound semiconductors. Excelling where silicon falls short, the unique properties of these chips support the innovation that's required for tomorrow's breakthroughs.

Given the growing demand for compound semiconductor technologies, it's of little surprise that this industry is generating substantial and growing sales. While well-established devices – such as LEDs that serve in general lighting and GaAs-based power amplifiers that are a key ingredient in mobile phones – no longer enjoy rapidly rising revenues, sales are growing fast in other sectors. The most notable of these is that of SiC power electronics, now deployed in automotive, industrial, energy, and rail applications. According to semiconductor market research analyst Yole Group, the SiC device market will increase in value to \$10 billion over the next five years, with SiC substrate and epiwafer shipments growing to over 3 million units.

#### When it can't fail

Driven by opportunities to grow their revenues, many makers of compound semiconductor devices are pursuing capacity expansion plans. Their investments will take many forms, from tools for epitaxial growth and metrology to securing a steady supply of a number of inconspicuous yet indispensable components.

The latter includes products that play a critical role in the manufacture of compound semiconductors, such as the patented Chemraz sealing technology developed by our company, Greene Tweed.

Well known for having have a strong pedigree in this area, we are a global leader in perfluoroelastomer (FFKM) Chemraz sealing solutions. It's an enviable position that we are not taking for granted, as we continue to lead the way with multi-million-dollar investments in facilities, alongside the launch of several new products and manufacturing automation technologies.

Several prominent chipmakers depend on our Chemraz seals. Using them for the production of their most powerful chips, they view second-best seals as not good enough for challenging manufacturing environments.

Demand for our products is growing as chipmakers turn to our Chemraz O-rings and sealing solutions for more demanding processes, where they are able to prevent contamination while withstanding aggressive chemicals and extremely high temperatures. When operating in the world's harshest semiconductor manufacturing applications, our products combine a tremendous level of performance with exceptional reliability.

Another factor that makes our Chemraz seals indispensable relates to the increasing need for ultraclean processing in manufacturing applications. As the first sealing solutions company to use cleanroom manufacturing in the US, we fully understand the significance of ultraclean operations in the semiconductor industry. We have devoted much effort to ensure that our seals control particle excursions that threaten contamination, while they increase uptime and boost wafer yield.

#### Balancing performance and costs

Greene Tweed understands that not every semiconductor application needs a Chemraz sealing solution. That's where our Fusion FKM (fluoroelastomer) products come in. They are field-tested in extreme temperatures, high pressures, corrosive chemicals, and volatile fluids.

The Fusion 707 has been specifically developed for flat panel display CVD and dry plasma etch equipment, where seal reliability and minimal contamination are essential. The 707 family of seals provides excellent chemical resistance and withstands various aggressive chemicals. Related to them is the Fusion 706 – it is ideal for a range of plasma equipment applications, from etch and plasma-enhanced CVD to plasma ashing applications, as well as those that must accommodate low sealing force materials, such as bonded slit valve gates.

Introduced earlier this year is the Fusion F07. This sealing solution is crafted to withstand common etch and CVD oxygen/fluorine-based gases in semiconductor processing sub-fab lines. The F07 handles continuous operating temperatures up to 180°C and has a minimum expected lifetime of six months. These figures are both better than those for standard FKM seals serving in the same applications. What's more, the F07 offers a lower cost of operations than premium FFKM materials.

That's not all. Greene Tweed's products help trim the costs of upgrading to larger wafers, such as a move from 150 mm to 200 mm. Note that the manufacture of compound semiconductor, such as SiC, is more expensive, due to the high cost

of material, as well as more complex manufacturing processes and lower production yields.

Many companies are trying to reduce the costs of switching to larger wafers by acquiring older tools and modifying and retrofitting them with software upgrades, so that they can work with the

some of these tools come with older and obsolete components, we are offering upgrade seal kits to improve the capabilities of older refurbished tools, a more prudent alternative to making massive investments in entirely new equipment. By upgrading tools so that they can incorporate the latest high-performance sealing solutions required to prevent contamination and maintain a cleanroom environment, compound semiconductor manufacturers can increase throughput and yield, critical to meeting the surge in demand while optimising profitability.

likes of SiC, or other

compound materials. As

Scaling up to provide chipmakers with the products that they will need during the anticipated boom is far from trivial. But the recent industry-wide supply crunch gripping the FFKM materials, which has coincided with a global surge in demand for chips, has given us valuable insights into how to meet the burgeoning demand while minimising the impact of possible disruptions.

Building on these insights, we are rolling out six major initiatives to ensure that we can promptly deliver high-performing sealing solutions, as customer needs evolve to meet the growing demand for semiconductors. These six initiatives, which we go on to discuss in detail, are: a new manufacturing facility in Korea; new innovations, designed for harsh conditions and expansion; the introduction of next-generation manufacturing to accelerate growth; the use of secured resources; fortification of supply chain resiliency; and ensuring that we are ready for the new tools that chipmakers will invest in.

#### A new facility in Korea

We are making significant investments to expand our global manufacturing capacity and capabilities within the semiconductor market. This initiative is exemplified by our construction of a new 6,500 m² facility in Ochang, Cheongju-si, Chungcheongbukdo, South Korea. Our new factory is equipped with end-to-end manufacturing process capabilities – from initial extrusion of raw materials to warehousing finished products. We have already

## COVER STORY I GREENE TWEED

started producing samples, and later this year we will transition to commercial production.

Featuring cleanroom space to maintain a pristine environment vital for components supporting chip fabrication, our new facility in South Korea will initially focus on our flagship Chemraz product line.

As well as increasing global capacity, this new facility for producing Chemraz products is underscoring our commitment to supporting customers based in South Korea and the surrounding region, including notable semiconductor leaders. This facility, which is creating a healthier global supply chain, will help us shorten lead times, build stronger co-development strategies with key customers, and enhance business continuity plans.

Aside from advanced manufacturing technology, our state-of-the-art plant in South Korea is equipped with solar panels and greywater recycling facilities to mitigate the environmental impact.

What's more, our new facility is designed with scalability in mind. It offers ample room for growth, enabling us to expand our production capabilities as demand increases. Over the next few years, we will be implementing a phased rollout of new production lines. This effort will begin by increasing capacity and adding automated equipment to enhance our production processes and reduce our lead times. Beyond that, we will be focusing on expansion, including an additional cleanroom, and integrating cutting-edge manufacturing technologies and processes.

Our long-term strategy is to ensure that we remain agile and responsive to our customers' evolving needs, while the demand for semiconductors grows over the remainder of this decade and beyond.

#### Outperforming in harsh conditions

As a global leader in FFKM seals, Greene Tweed knows that our Chemraz seals are critical for the most advanced semiconductor fabrication processes. To support our customers' growing needs, we have introduced two new highperforming, price-competitive products – the Chemraz G38 and G57.

This pair of products are designed to meet the evolving needs of various plasma applications, while being incredibly price competitive and delivered with world-class lead times. By expanding our line-up in this way, we are demonstrating our commitment to continuously innovating and responding to the demands of the market and ensuring that our customers have the best solutions at their disposal.

Custom-engineered to meet the demands of aggressive dry plasma systems, our Chemraz G57 technology provides improved plasma resistance and minimises contamination, resulting in less downtime and higher wafer processing yields in both static and dynamic oxide etch wafer-processing applications. This product has excellent chemical resistance and withstands temperatures up to 300°C, making it ideal for several applications, including endpoint windows, window seals, slit valve seals, bell jar seals, isolator valve seals, chamber seals, valve seals, lid seals, KF fitting seals, and gas inlet seals.

Meanwhile, the Chemraz G38 is targeting highdensity plasma systems, where seal reliability and minimal contamination are essential. The G38 has excellent chemical compatibility and is capable of

Expanding our manufacturing capacity is just one of the prongs of our multi-faceted strategy that is laying the foundations for supporting a strong upturn in the market. To ensure world-class lead times, we have secured a reliable supply of raw materials from multiple suppliers. With these partners, we are well-positioned to cater for an anticipated ramp in chip production over the next two years

withstanding a variety of aggressive chemicals. Recommended for bonded gate seals and chamber seals, this product delivers exceptional value in a number of applications, including deposition, remote plasma cleans, oxidation, diffusion, ion implant, implant anneal, and rapid thermal processing.

Our development of new technologies continues at pace, and we have another Chemraz sealing solution ready to roll out in the next 6-12 months. Helping to encourage us in this endeavour is the adoption of our existing sealing solutions, including Chemraz and Fusion F07 FKM, in semiconductor fabs being built all around the world.

#### Next-gen manufacturing

We are committing significant resources to automating manufacturing processes, as this enables us to scale capacity and quickly meet the growing needs of our evolving semiconductor customers. By supplementing core manufacturing processes with robotics and digital solutions, we are supporting production floor employees to eliminate process bottlenecks and trim lead times.

Our largest investments are associated with high-impact process steps, such as compression moulding, inspection, and packaging. The reasoning behind this is that it maximises efficiency and productivity gains. For compression moulding, operators are currently responsible for moving and servicing moulds between every cycle. However, we are moving towards an automated approach, using a 6-axis robot to move moulds. This will allow the operator to focus only on value-added activities and service more moulding presses. Similarly, for current

packaging operations, our operators are responsible for bagging and labelling parts individually – this is slow and tedious. Due to this, we are introducing an automated solution, involving multiple robots and an automatic bagging machine, as this will increase throughput and standardise bagging quality.

We are also building and utilising digital twins. It's a move that will allow us to proactively evaluate new innovative technologies and discover how to best introduce them into existing manufacturing facilities.

By turning to these technologies and dedicated technical resources, we are transforming our production lines. They are becoming more adaptable, and they are allowing us to scale up quickly to meet our customers' needs without compromising on excellence.

#### Secured resources

Expanding our manufacturing capacity is just one of the prongs of our multi-faceted strategy that is laying the foundations for supporting a strong upturn in the market. To ensure world-class lead times, we have secured a reliable supply of raw materials from multiple suppliers. With these partners, we are well-positioned to cater for an anticipated ramp in chip production over the next two years.

While running four factories with balanced workloads, we have significantly increased our workforce to stabilise the production process, in conjunction with bolstering our manufacturing capabilities by introducing new equipment in our plants in Korea, Taiwan and Selma. As well as keep pace with growth, these strategic moves

## COVER STORY I GREENE TWEED

will enhance our production capabilities, minimise delays, and accelerate delivery times.

#### Fortified supply chain resiliency

As we work to secure a steady supply of raw materials, we are proactively reducing our reliance on a single vendor or market. Here's why: The industry-wide FFKM supply crunch, which occurred during the pandemic-led surge in demand for semiconductors, has taught us the importance of diversifying and strengthening our supply chain. That's why we have carefully selected multiple sources of raw materials, located in separate regions.

Proactively identifying and mitigating many potential risks, ranging from those that are geo-political to those associated with regulatory matters and climate change events, has enabled us to build comprehensive supply chain resiliency, as well as a business continuity plan that we share with customers

to ensure transparency. By securing raw materials and building supply chain resiliency, our customers benefit from reduced downtime, helping them to meet the incredibly tight production schedules they face during fast-increasing demand when markets are booming. This is critical in many sectors within the semiconductor industry, where missing a timeto-market window threatens to slash sales.

#### Preparing for new tools

Our innovation in sealing solutions supports the unique needs of the compound semiconductor market, as well as the latest technology inflections in the silicon industry. We work with OEMs across these markets as they upgrade their tools to serve their customer base. Whether it's the latest innovations in etch or in deposition, we are taking proactive steps to keep up with market demand and growth.

For example, our bonded slit valves, lip seals, seals for electroplating solutions, vacuum line solutions, cryogenic seals, and many other sealing solutions are continuing to be widely adopted by equipment makers, creating value and yield enhancement for both silicon and compound semiconductor fabs. Most recently, Xyfluor materials have been qualified for use in electrostatic chucks that can operate at temperatures as low as -40 °C.

#### Ready for growth

Building cutting-edge compound semiconductor chips is a challenging, cost-intensive process that hinges on small yet essential components, such as our sealing solutions. Working closely with our customers and partners, we are ready to address the burgeoning need for sealing solutions from chipmakers, thereby ensuring the scalability and sustainability of their operations for the rest of this decade and beyond.

## SUMMIT CRYSTAL

8-inch 4H-SiC Substrate

8-inch 4H-SiC Ingot

SiC

R&D, production and sales of Silicon Carbide (SiC) single crystal material. The company has capability in mass production of

Guangzhou Summit Crystal Semiconductor Co., Ltd, a National High-Tech Enterprise, is engaged in the

8-inch 4H-SiC n-type Substrate with 0 MPD, 0 TSD, 0 SF and low BPD (≤200cm<sup>-2</sup>).

Address: No.8 Zhengxiang Road, Nansha District, Guangzhou City, Guangdong Province, China Tel: +86-20-39006699 Web: www.summitcrystal.com Email: sales@summitcrystal.com

# kSA MOS for Stress Measurement

# Control your (thin-film) stress!

- Measure real-time curvature, stress, reflectivity and growth rate

- 2D curvature/stress measurement allows for surface anisotropy determination

- Plus the best support in the industry

- Learn more by visiting our website: k-space.com

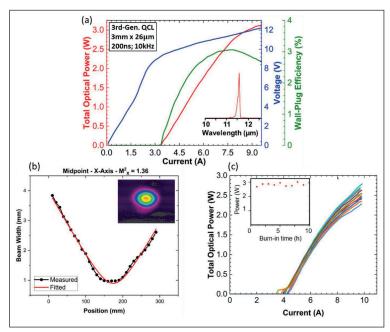

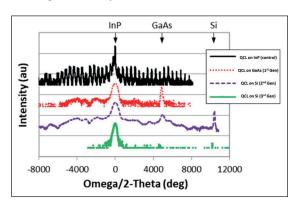

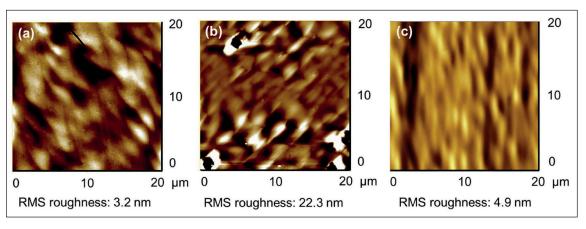

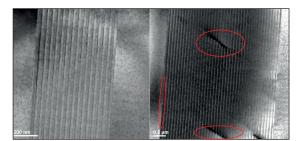

## Monolithically integrated QCLs on silicon

Low-strain quantum cascade lasers with optimised metamorphic buffer layers are closing the gap to realising reliable, high-power, infrared sources on silicon

BY ENRIQUE SANCHEZ CRISTOBAL, AHMAD AZIM AND LUKE MILLBOCKER FROM IRGLARE, MATTHEW FETTERS, AMY LIU AND JOEL FASTENAU FROM IQE, AND ALEJANDRO VILLALOBOS MEZA AND ARKADIY LYAKH FROM THE UNIVERSITY OF CENTRAL FLORIDA

> FOR DESIGNERS of semiconductor lasers, quantum wells are a fundamental building block for these nanoscale devices, as well as an incredible asset. Not only do these devices serve as effective generators of laser light through radiative recombination processes, but the use of quantum well engineering also allows for control of emission wavelengths through changes in material composition.

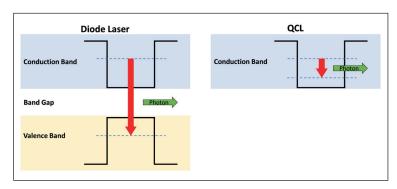

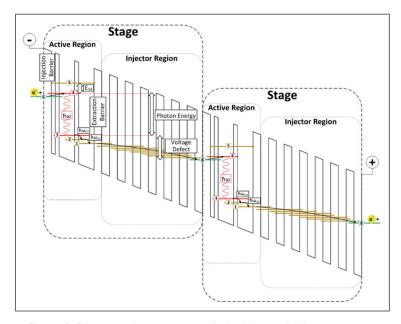

Common semiconductor lasers, such as laser diode and the VCSEL, emit at wavelengths determined by the difference between the lowest energy levels of the electrons in the conduction band and the highest energy of the holes in the valence band of the quantum well material. This is a limitation that can be overcome by another unique semiconductor structure, the quantum cascade laser (QCL), which achieves lasing through inter-sub-band transitions associated with different excited states of the conduction bands of two materials. (see Figure 1). At the heart of this semiconductor device is a superlattice composed of two alternating materials whose conduction bands work together to create a periodic quantum well structure, which emits infrared photons under an applied electrical bias. The material composition of the superlattice

constituents can be varied to achieve emission in a broad infrared range, and the periodic nature of this structure enables a single electron to generate multiple photons as it cascades through the superlattice (see Figure 2).

While QCLs are not as well-known as diode lasers and VCSELs, they are produced commercially, and are used in a range of critical sectors, including defence, spectroscopy, and free-space communication. In these applications they serve as compact, high-powered infrared sources that span the mid- to long-wave infrared range, thanks to a highly tuneable quantum well superlattice structure. More recent designs can deliver a continuous-wave output power of several watts at room temperature. enabling them to play pivotal roles in applications such as defence, where their low atmospheric losses at critical spectral windows allow them to be used in direct infrared countermeasure systems. Another important application is in the field of imaging, where QCL-based infrared microscopy has been successfully deployed for the rapid, precise classification of different cancer tissues.

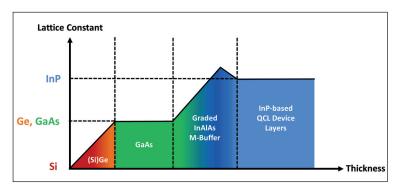

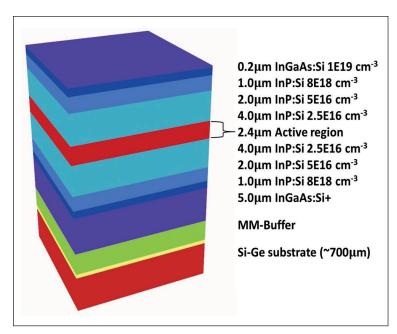

Up until now, QCLs have usually been produced with lattice-matched material systems, such as InP. However, while this is conducive to maximising material quality and device performance,

> it also significantly limits the opportunities for this device, due to the high cost and low scale of native

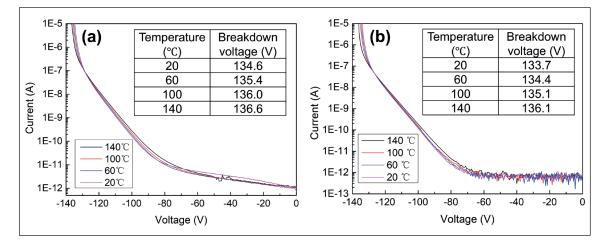

The solution to overcoming this limitation is to modify the fabrication of QCLs to be able to account for the lattice mismatch between non-native substrates and the active layers. In this regard, our team at IRGlare, working in partnership with engineers at The University of Central Florida and IQE, has broken much new ground. Our triumphs