# COMPOUND SEMICONDUCTOR

CONNECTING THE COMPOUND SEMICONDUCTOR COMMUNITY

VOLUME 31 ISSUE VII 2025

AN ANGEL BUSINESS COMMUNICATIONS PUBLICATION

COMPOUNDSEMICONDUCTOR.NET

## DRIVING ULTRA-WIDE BANDGAP BREAKTHROUGHS

AIXTRON

# THE G10 SERIES

SiC power epi production

platform with 150/200 mm

wafer size flexibility

Your **Productivity Solution**

for All Advanced Epitaxy Materials

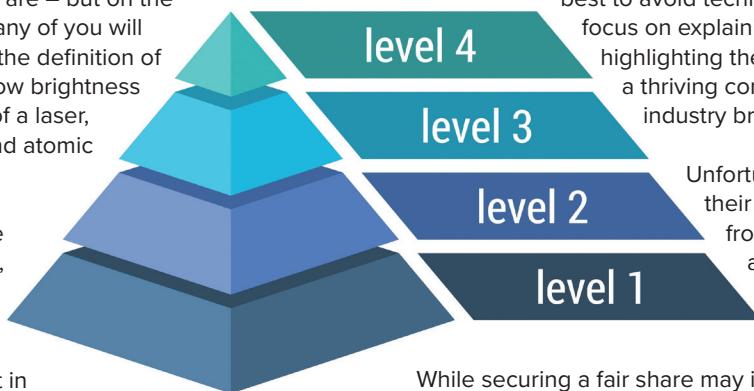

## The right level

ONE of my tasks as the editor of this publication is to ensure it's at the right level for its readership. I don't want to explain things to you that you already know, or go too far in the opposite direction, assuming content that is only well-known to those that are specialists in lasers, RF devices or power electronics. So, I assume you all will know what a substrate is, will have some familiarity with what MBE and MOCVD are, and don't need explanations for what LEDs and solar cells are – but on the other hand, I think that many of you will appreciate a reminder of the definition of Baliga's figure-of-merit, how brightness is defined in the context of a laser, and the mechanism behind atomic layer deposition.

While I grapple with these decisions on a daily basis, I'm sure this situation is not that unfamiliar to many of you, who will have devoted much effort in working out how to pitch your message at the level that's right level for your audience. If you are delivering a short presentation at an industrial conference, you'll want to avoid covering what's already familiar and focus on what's new, an objective that might be helped by having a speaking slot that goes after others that have already laid the foundations.

The dangers of working in an incredibly high-tech industry is that when you speak to those outside it, as well as possibly assuming too much knowledge on their part, you might also fall into the trap of trying to fill the gaps in their understanding. The reality is that there are those out there that are not fascinated by compound semiconductors, and you don't have to address this by explaining the need for

lattice matching, why MOCVD has a higher throughput than MBE, and why bandgaps matter when it comes to power electronics.

Expounding on this topic in this issue is Howard Rupprecht, Managing Director of CSconnected (see p. 18). He explains that when discussing matters with non-industrial stakeholders, which could include a wide range of government officials, it's best to avoid technicalities. Instead, one should focus on explaining industry dynamics, and highlighting the economic benefits that a thriving compound semiconductor industry brings.

Unfortunately, dignitaries spend their days conversing with leaders from many different industries, and to avoid accusations of favouritism, they tend to favour spreading pots over many initiatives.

While securing a fair share may initially appear a noble aim, funding that's spread thinly over many projects can fail to make an impact. And there's a strong case to be made that our industry should get a bigger slice of the pie.

In the south Wales cluster, they have a great case for receiving an above-average award. As well as a gross value-added contribution is three times the national average, since 2020 employment within the cluster has grown by 32 percent and total annual revenue has netted £500 million, with more than 90 percent involving purchases from overseas.

These are hard-hitting figures that are ideal to use when communicating in a clear and compelling manner with government officials and other stakeholders.

Free weekly e-news roundup go to: [compoundsemiconductor.net](http://compoundsemiconductor.net)

## COVER STORY

### Agnitron: Driving ultra-wide-bandgap breakthroughs

Advancing the capabilities of AlN, AlScN and aluminium-rich AlGaN is the Agnitron Agilis 100 MOCVD reactor

20

### 18 Effective communication with government and other stakeholders

Discussions with government officials and leaders of other bodies should avoid detailing core technologies and focus on tangible benefits of a flourishing compound semiconductor industry

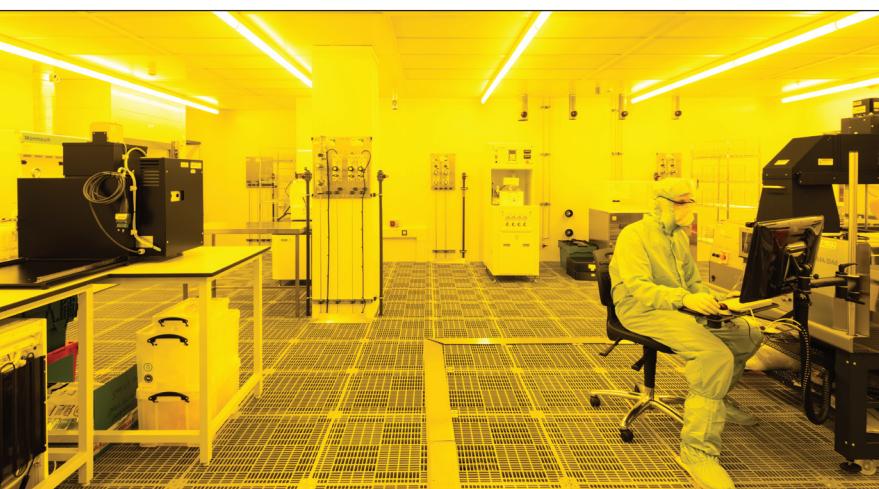

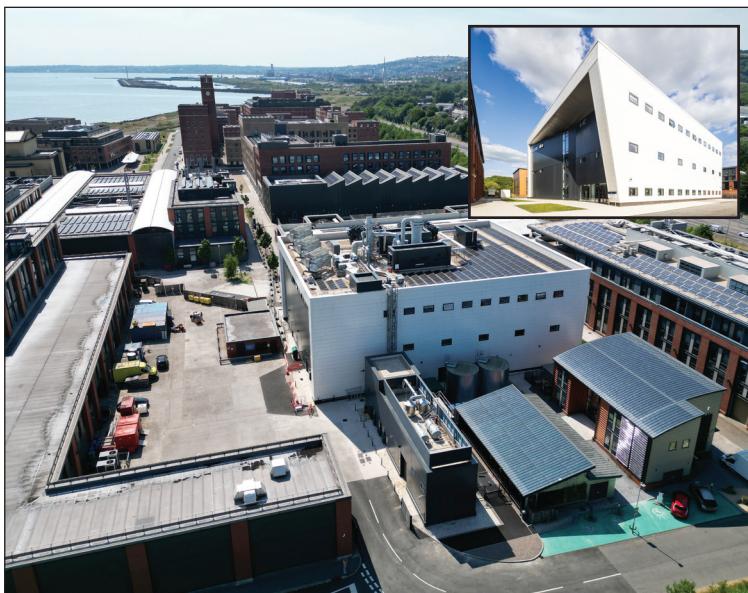

### 30 Swansea's superpower: The centre for integrative semiconductor materials

Buoyed by the emergence of Vishay Intertechnology within the South Wales compound semiconductor cluster, Swansea's recently constructed Centre for Integrative Semiconductor Materials (CISM) is focusing on power electronics while encompassing a broader portfolio of activities that includes CdTe solar cells and molecular electronics

### 36 The race to revolutionise silicon photonics with seamless III-V integration

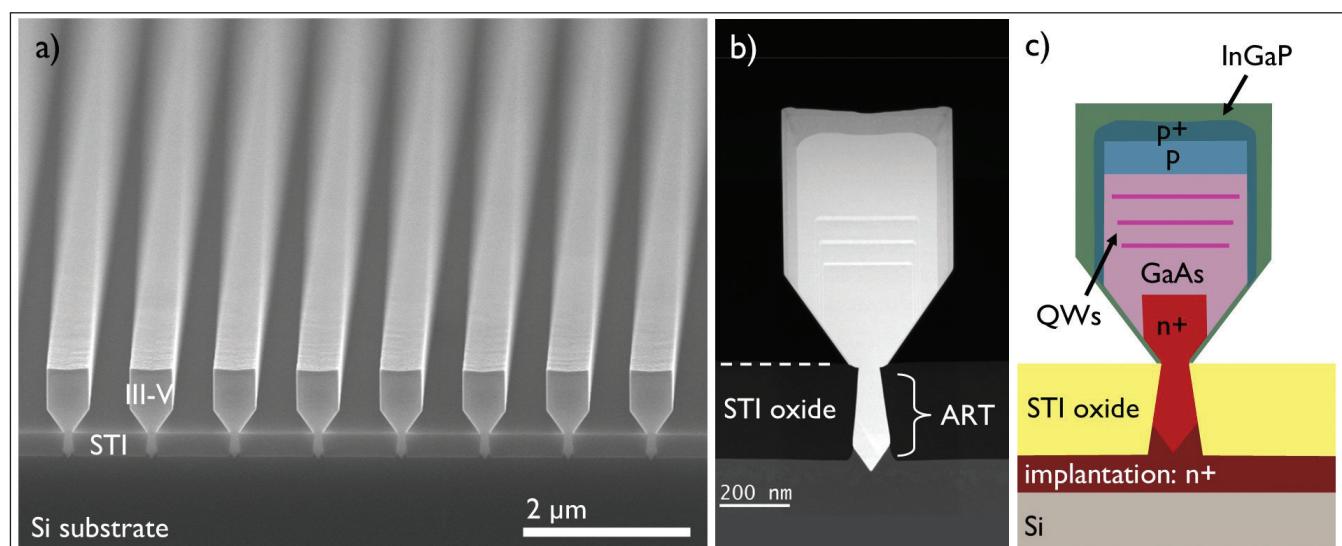

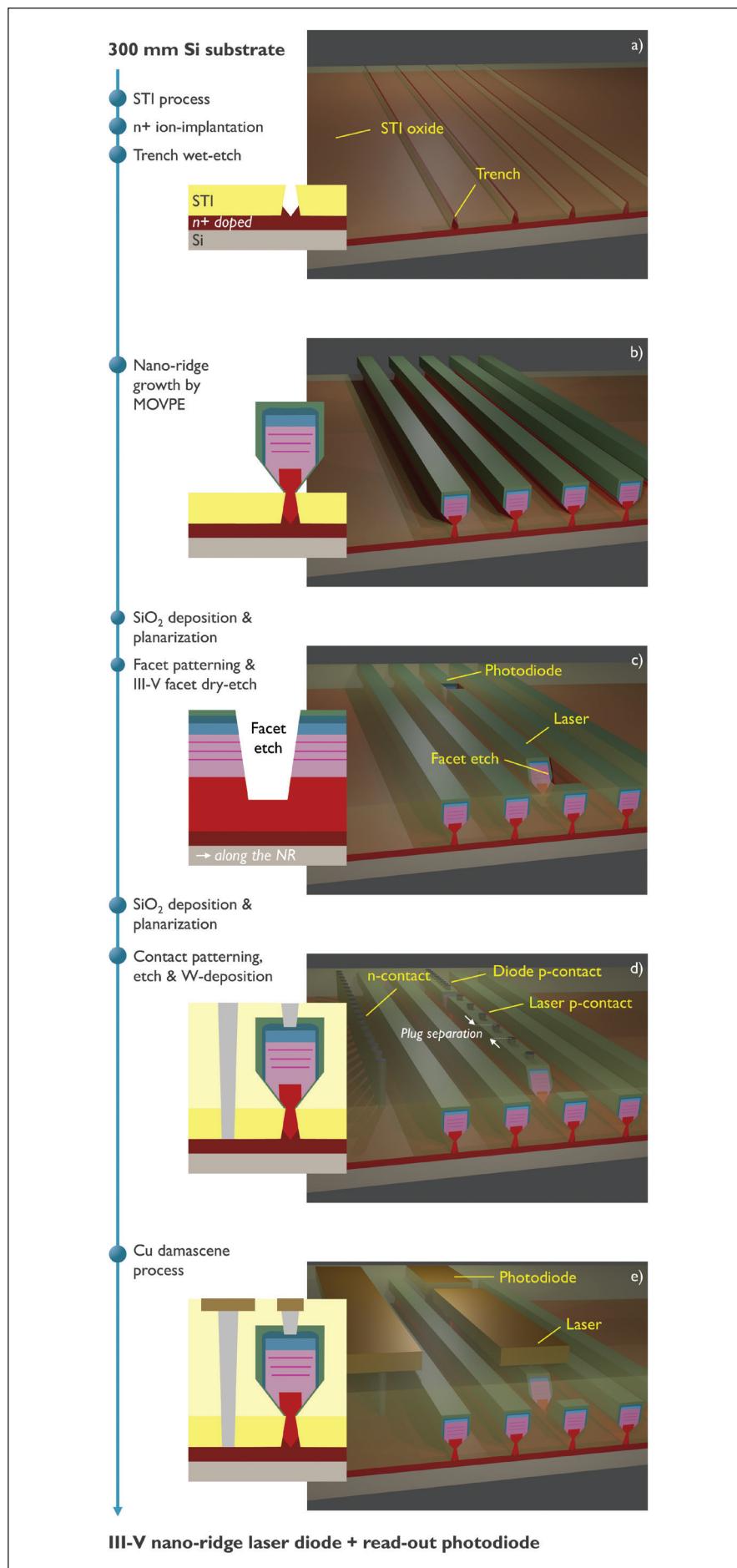

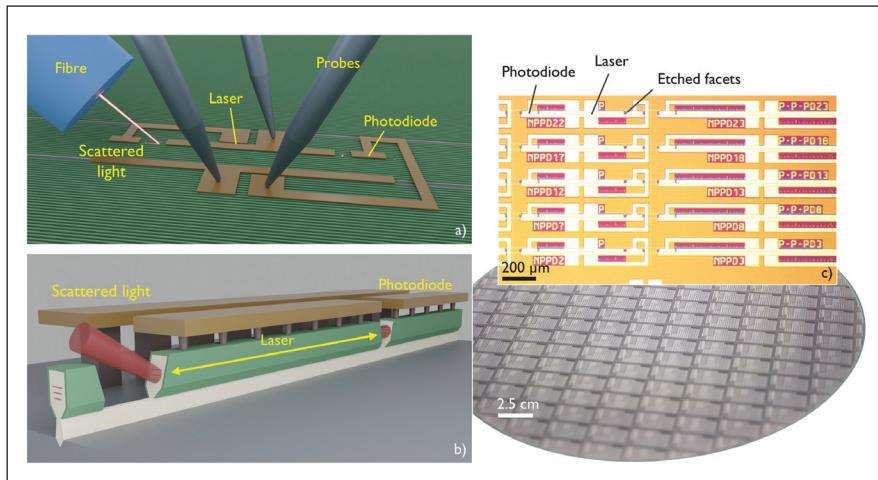

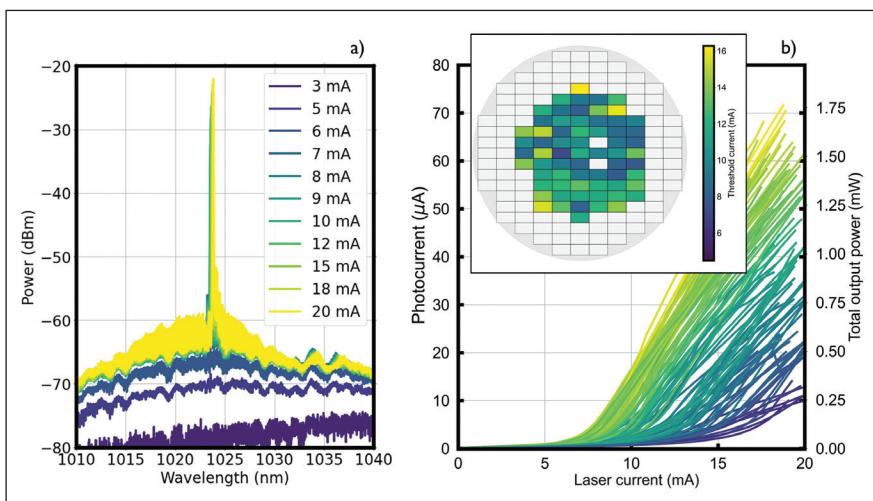

Growing III-V nano-ridge lasers directly on silicon sidesteps the complexities of existing integration methods and paves the way for scalable, cost-efficient PIC production

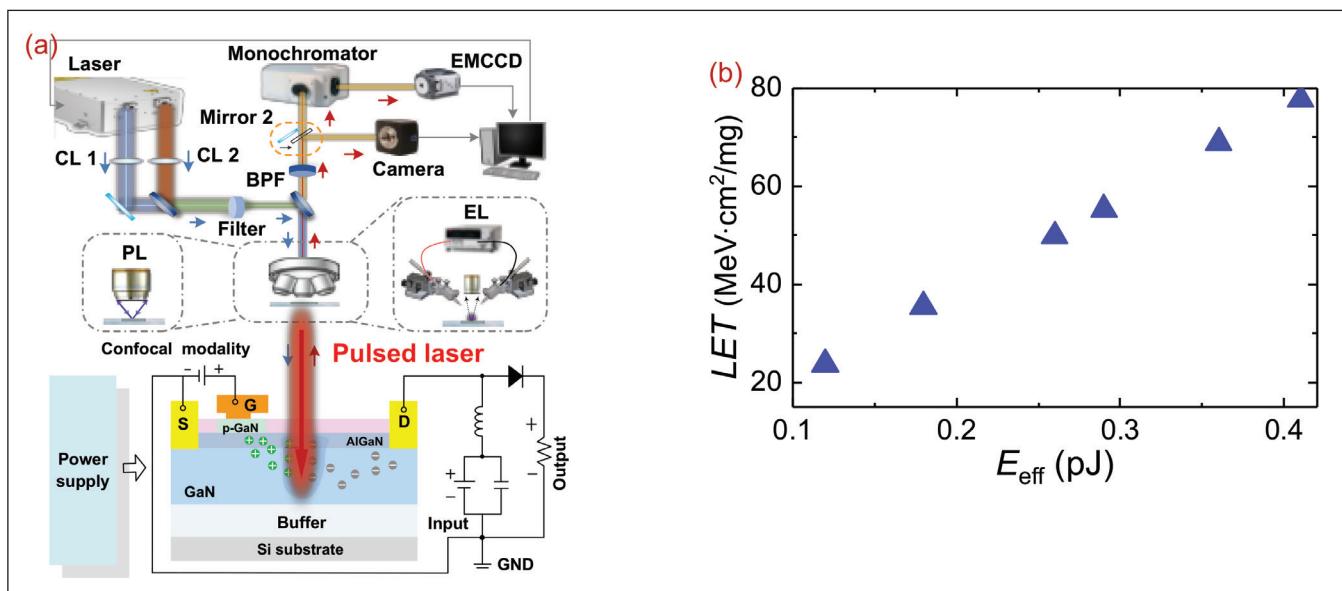

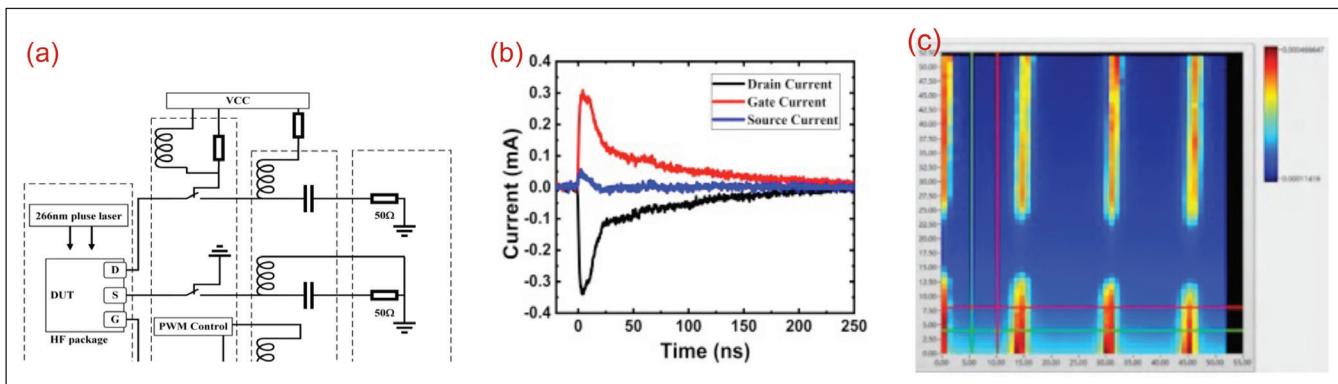

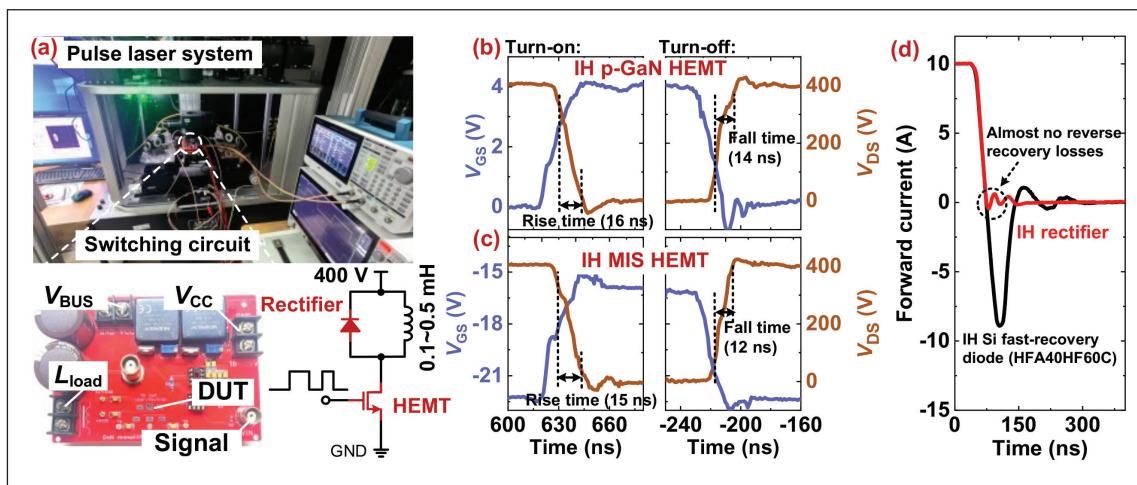

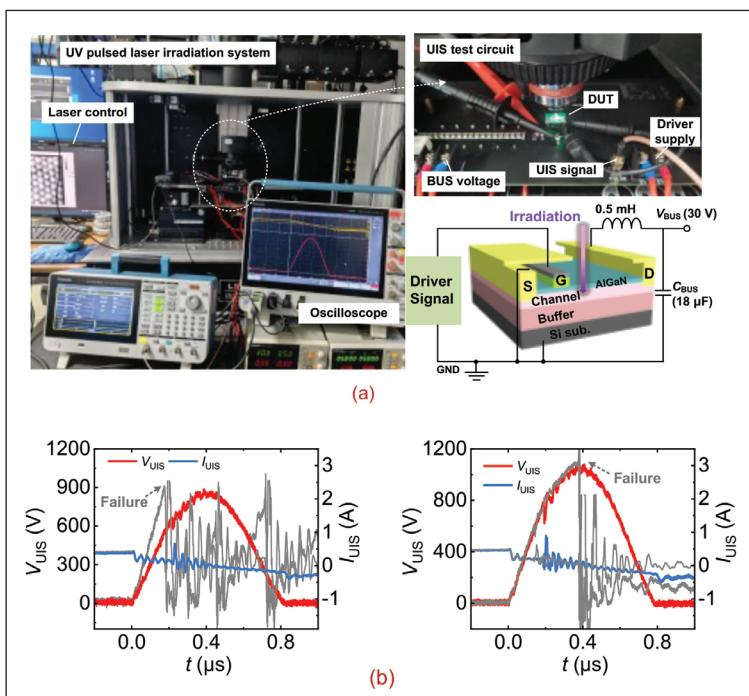

### 44 Evaluating radiation hardness with UV laser pulses

By delivering radiation-induced damage with a high spatial resolution, UV pulsed laser irradiation technology is providing a powerful approach for assessing GaN power electronics in space applications

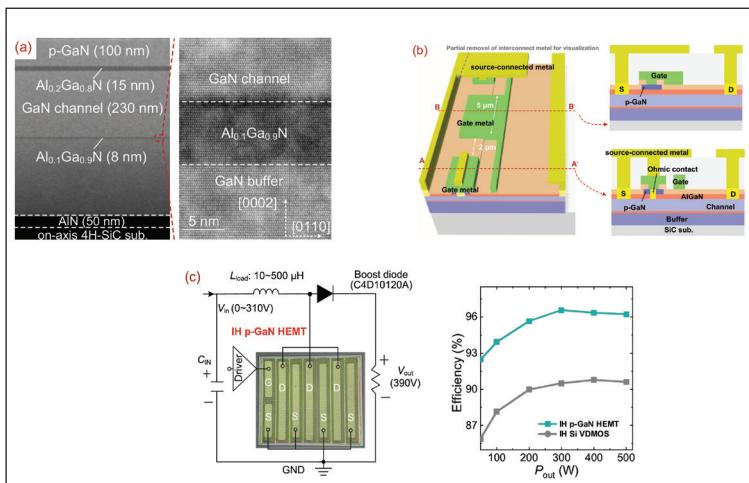

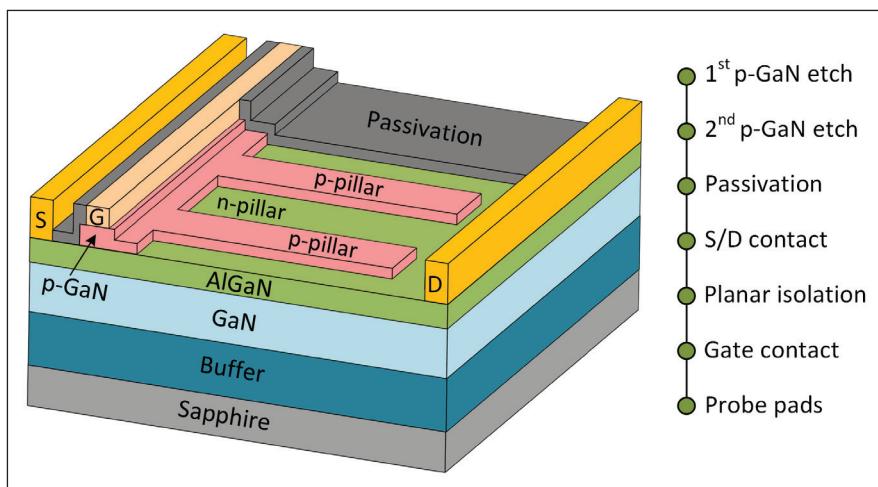

### 50 Giving GaN a superjunction

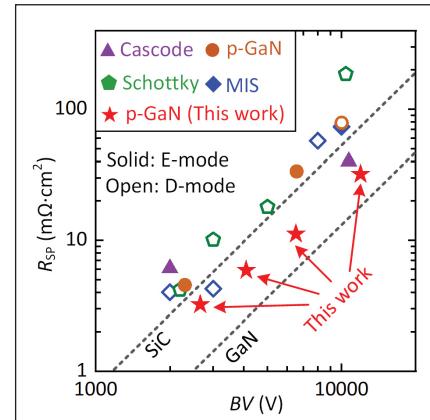

Equipping enhancement-mode GaN transistors with a superjunction boosts the blocking voltage beyond 10 kV

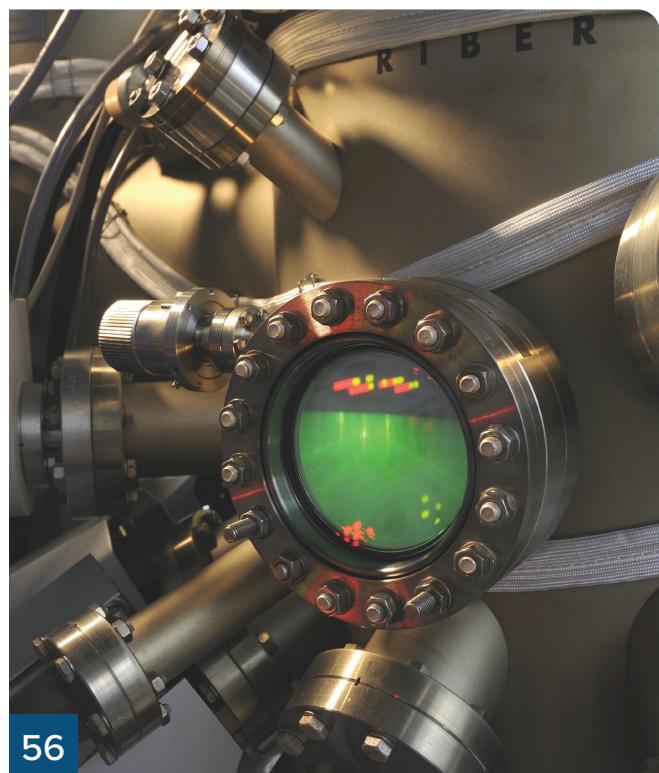

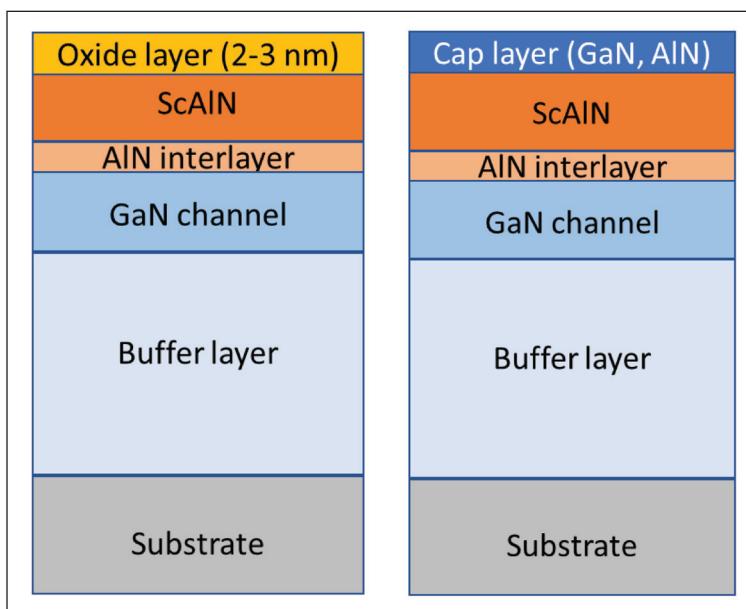

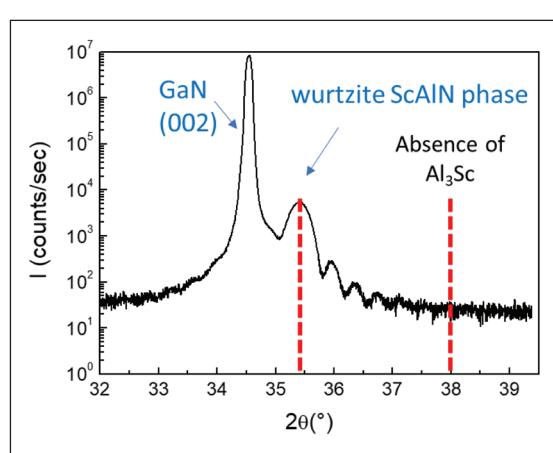

### 56 Ammonia MBE targets HEMTs that feature ScAlN

Enhancing GaN-based HEMTs with ScAlN, via growth by ammonia MBE, promises to improve the performance of high-frequency power devices

56

## NEWS ANALYSIS

### 14 Transforming transfer technology for microLEDs

Q-Pixel addresses the biggest bottleneck to manufacturing microLED displays with an out-of-the-box transfer technology that combines a critical hike in yield with superior throughput

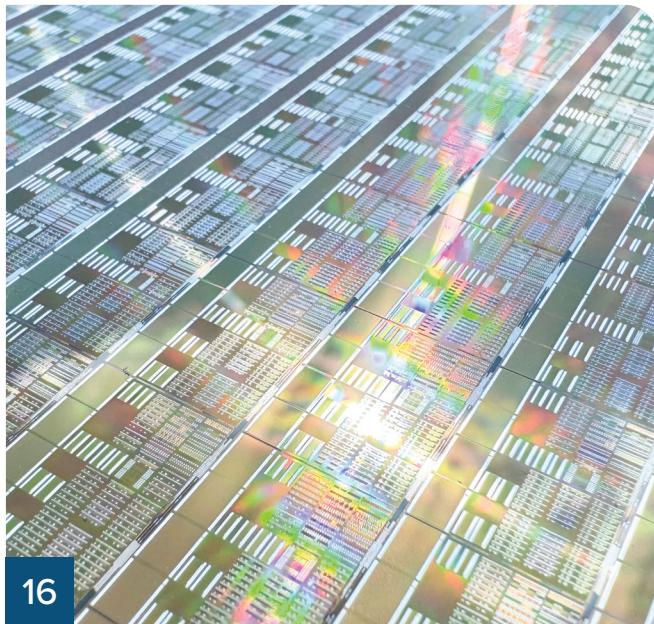

### 16 X-Fab: Normally-on, then normally-off

At X-Fab's Dresden foundry that's been churning out silicon devices for decades, production of normally-on GaN HEMTs is now underway, with normally-off variants soon to follow

## RESEARCH REVIEW

### 64 Passivating $\beta$ -Ga<sub>2</sub>O<sub>3</sub> devices

### 65 Hot-wall MOCVD helps GaN-on-AlN HEMTs

### 66 Mastering the manufacture of HEMTs with an AlN buffer

## NEWS

**06 Is Nvidia defining the future of power electronics?**

**07 NREL team constructs record-beating SiC module**

**08 Navitas names Chris Alexandre as president and CEO**

**09 IQE considers sale**

**10 SweGaN, Ericsson, Saab and Chalmers collaborate on 6G GaN PAs**

**11 Toshiba and SICC sign SiC MoU**

**12 UW-Madison opens ultra wide bandgap lab**

**Editor** Richard Stevenson

richard.stevenson@angelbc.com

+44 (0)1291 629640

**News Editor** Christine Evans-Pughe

christine.evans-pughe@angelbc.com

**Design & Production Manager**

Mitch Gaynor

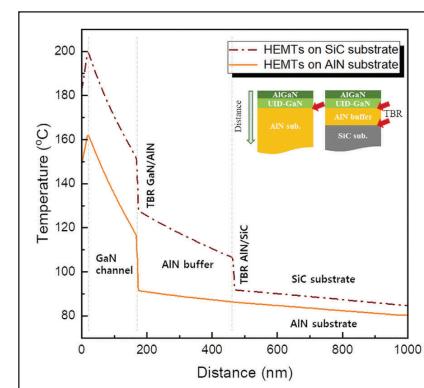

mitch.gaynor@angelbc.com

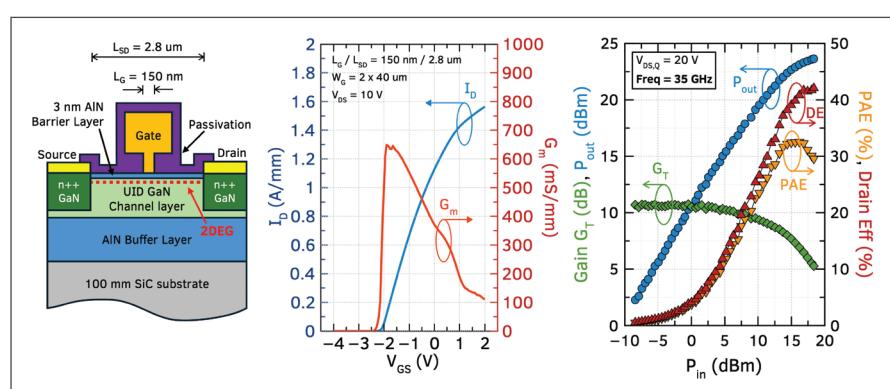

+44 (0)1923 690214

**Director of Logistics** Sharon Cowley

sharon.cowley@angelbc.com

+44 (0)1923 690200

**Event & Media Sales Executive**

Ranjodh Shergill

ranjodh.shergill@angelbc.com

+44 (0)2476 718970

**Circulation** Scott Adams

scott.adams@angelbc.com

+44 (0)1923 690205

**Publisher** Jackie Cannon

jackie.cannon@angelbc.com

+44 (0)1923 690205

**Sales and Product Manager** James Cheriton [james.cheriton@angelbc.com](mailto:james.cheriton@angelbc.com) +44 (0)2476 718970

**Chief Executive Officer** Sukhi Bhadal [sukhi.bhadal@angelbc.com](mailto:sukhi.bhadal@angelbc.com)

+44 (0)2476 718970

**Chief Technical Officer** Scott Adams [scott.adams@angelbc.com](mailto:scott.adams@angelbc.com)

+44 (0)2476 718970

**Directors** Jackie Cannon, Sharon Cowley

Compound Semiconductor is published nine times a year on a controlled circulation basis. Non-qualifying individuals can subscribe at: £115.00 per annum (UK), €165 per annum (Europe), \$198 per annum (air mail) (USA). Cover price £4.50. All information herein is believed to be correct at time of going to press. The publisher does not accept responsibility for any errors and omissions. The views expressed in this publication are not necessarily those of the publisher. Every effort has been made to obtain copyright permission for the material contained in this publication. Angel Business Communications Ltd © Copyright 2025. All rights reserved. Contents may not be reproduced in whole or part without the written consent of the publishers. The paper used within this magazine is produced by chain of custody certified manufacturers, guaranteeing sustainable sourcing. US mailing information: Compound Semiconductor, ISSN 1096-598X, USPS Permit Number 25366, is published 9 times a year, Combined Jan/Feb, March, Combined April/May, June, July, Combined August/September, October, November, December by Angel Business Communications Ltd, Unit 6, Bow Court, Fletchworth Gate, Burnsall Rd, Coventry CV5 6SP, UK. T: +44 (0)2476 718970

E: [info@angelbc.com](mailto:info@angelbc.com)

W: [angelbc.com](http://angelbc.com)

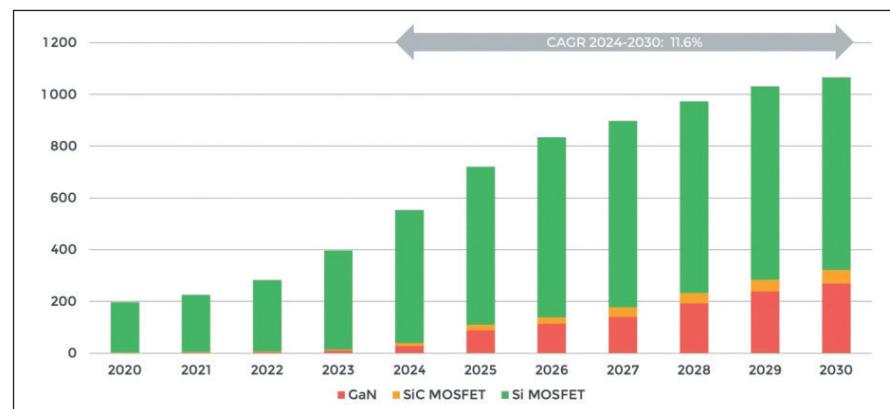

# Is Nvidia defining the future of power electronics?

Riding the AI boom, Nvidia is creating huge momentum for GaN in its 800 V data centre power infrastructure, says Yole Group

A RECENT article by Junko Yoshida for the Yole Group describes how Nvidia, a company that doesn't design or make power devices, is defining the features and functions of tomorrow's power electronics in moving to a 800 V high-voltage direct current (HVDC) data centre power infrastructure.

Yoshida's article describes the company as creating momentum behind GaN as like a 'Tesla moment for SiC'. And just as STMicroelectronics reaped the fruits of Tesla's early push for SiC, 'Infineon and Navitas are jockeying to profit from the emerging GaN moment driven by Nvidia'.

Many suppliers of wide bandgap semiconductors and silicon vendors are playing along, willing to invest in new technologies to deliver what Nvidia needs, writes Yoshida.

In the piece, Gerald Deboy, head of the System Innovation Group at Infineon Technologies, compared Nvidia to a maestro, orchestrating 'the entire world to architect a new way of building and operating data centres.'

Those enlisted by Nvidia include Infineon, MPS, Navitas, Rohm, STMicroelectronics, and Texas Instruments. Also in the mix are suppliers of power system components such as Delta, Flex Power, Lead Wealth, LiteOn, Megmee, and companies who build data centre systems, including Eaton, Schneider Electric and Vertiv.

A range of new power devices and semiconductors will be needed for the new HVDC data centre architecture.

According to Infineon's Deboy, for data centre power infrastructure that needs high-power, high-voltage solutions, SiC leads. But for conversion from 800 V to 50 V, space restraints dictate high-switching frequency. This makes it more of a GaN domain.

800 V AI data centres also demand

new semiconductor-based relays, explained Deboy. In data centres today, AC is distributed in three phases, with a normal relay and a normal switch turning power on and off like a light switch. In contrast, in a new high-voltage DC AI data centre, Deboy said that safety requires 'new semiconductor components that control over currents and inrush currents in a very well-maintained behaviour.'

Taken all together, Poshun Chiu, principal technology and market analyst at Yole Group tabbed Infineon as 'by far the leader in power electronics.' When AI data centres ask for a hybrid power electronics solution, noted Chiu, Infineon's strength shines in all three fields, ranging from SiC to GaN and silicon semiconductors. Infineon, added Chiu, covers every phase of the power chain in AI data centres, striving to offer the best technology fit for each stage.

Infineon, however, isn't alone in racing to capture Nvidia-driven AI data centre opportunities. Gene Sheridan, CEO of Navitas Semiconductor notes in the article, 'As you get closer to the processor, Nvidia gets more hands on.' Starting at 48 V, Nvidia is driving design, component selection and supplier selection, he said.

Navitas is taking advantage of its strength in GaN to address power electronics

solutions required by AI data centres. The acquisition of GeneSiC Semiconductor in 2022 has also helped Navitas bolster its wideband gap portfolio.

Beyond GaN or SiC, useful for traditional AC to DC converters, or 800 V DC-to-DC converters, Navitas also dabbles in '48 V down to power the processor,' which is closest to the processor.

Sheridan finds a new opportunity triggered by the industry's highest voltage SiC technology, which his company obtained via its GeneSiC acquisition. Ultra-high-voltage SiC technology will be essential in developing solid state transformers connected to the grid. Beyond data centres, Sheridan believes grids are getting upgraded to solid-state transformers everywhere, powering cities and homes, even connecting to renewable energy.

In the AI data centre market, Yole Group predicts that GaN will outgrow SiC. While SiC is focused on AC to DC, GaN used in DC to DC can also enter AC to DC. This is because GaN devices pose the potential for higher voltage.

"Although we see some upside market for SiC, about \$100 million in three to five years, the opportunity seems much bigger for GaN," explained Chiu.

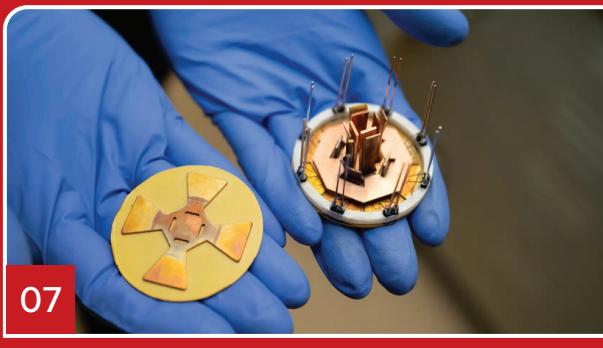

# NREL team constructs record-beating SiC module

Ultra-Low Inductance Smart (ULIS) module can achieve five times greater energy density than predecessor designs

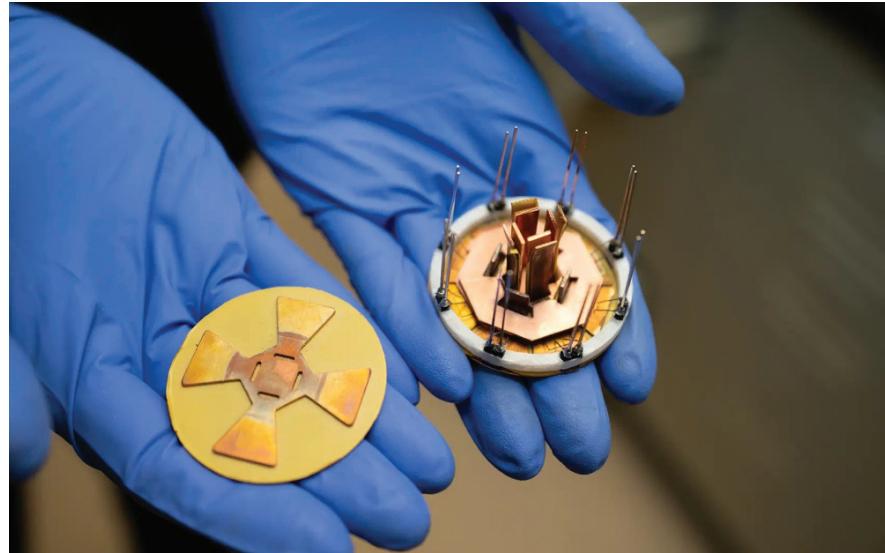

NREL has developed an Ultra-Low Inductance Smart (ULIS) SiC power module with a parasitic inductance seven-to-nine times lower than any current state-of-the-art SiC power module.

The 1200 V, 400 A module is capable of achieving five times greater energy density than predecessor designs in a smaller package, making it possible to build and power more efficient, compact, and lighter technologies for applications such as data centres, power grids, microreactors, and even heavy-duty vehicles, such as next-generation aircraft and military vehicles.

"We consider ULIS to be a true breakthrough," said Faisal Khan, NREL's chief power electronics researcher and the principal investigator for the project. "It's a future-proofed, ultrafast power module that will make the next generation of power converters more affordable, efficient, and compact."

Furthermore, Khan explained, ULIS is uniquely suited for high-intensity applications, like aviation and military operations, because the powerful, lightweight module also monitors its own state of health and can predict component failure before it occurs.

Unlike a typical brick-like power module, ULIS winds its circuits around a flat, octagonal design. The disk-like shape allows more devices to be housed in a smaller area, making the overall package smaller and lighter. At the same time, novel current routing allows for maximum magnetic flux cancellation, contributing to the power module's clean, low-loss electrical output – in other words, its ultrahigh efficiency.

"Our biggest concern was that the device switches off and on very quickly, and we needed a layout that wouldn't

create a chokepoint within the design," said Shuofeng Zhao, an NREL power electronics researcher who designed ULIS' flux cancellation architecture.

One of the original layouts, Zhao said, looked like a flower with a semiconductor at the tip of each petal. Another idea was to create a hollow cylinder with components wired to the inside. Sarwar Islam, another NREL power electronics researcher on the ULIS team, came up with the 2D structure, which made it possible to build the module balancing complexity with cost and performance.

"We squished it flat, like a pancake," Zhao said, "and suddenly we had a low-cost, high-performing design that was much easier to fabricate."

Where conventional power modules rely on bulky and inflexible materials, also ULIS takes a new approach. Instead of dissipating excess heat by bonding copper sheets directly to a ceramic base, ULIS bonds copper to a flexible polymer, called Tempriion, to create a thinner, lighter, more configurable design. Because the material bonds easily to copper using

just pressure and heat, and because its parts can be machined using widely available equipment, ULIS can be fabricated quickly and inexpensively, according to the NREL team. Manufacturing costs total hundreds, rather than thousands, of dollars.

A further breakthrough allows ULIS to function wirelessly, as an isolated unit that can be controlled and monitored without external cables. A patent for this low-latency wireless communication protocol is pending.

ULIS can scale to accommodate advancements in semiconductor devices using SiC, GaN, and even gallium oxide.

**"We squished it flat, like a pancake, and suddenly we had a low-cost, high-performing design that was much easier to fabricate"**

# Navitas name Chris Allexandre as president and CEO

Semiconductor veteran succeeds founder Gene Sheridan

GaN and SiC specialist Navitas Semiconductor has appointed Chris Allexandre as president and CEO, from September 1, 2025. Allexandre, who also joins the company's board of directors, succeeds Gene Sheridan, a Navitas founder.

"We are excited to welcome Chris Allexandre as our new president and CEO," said Richard J. Hendrix, chairman of Navitas' board of directors. "Chris is joining Navitas at a pivotal moment in its evolution. We believe his track record of driving transformation and delivering sustainable and profitable growth, operational excellence and business leadership in power semiconductor markets makes him the right leader for the next chapter of Navitas."

He added: "On behalf of the board of directors, I'd like to thank Gene Sheridan for his vision in creating and leading Navitas over the last decade. Gene has established an exceptional company that stands ready to pursue the next phase of electrification in higher-power applications ideally suited for Navitas' portfolio of GaN and SiC solutions. We deeply appreciate Gene's leadership and impact, and his invaluable contributions to the board's succession planning and recruiting efforts, which have brought Navitas to this important transition point."

"I am incredibly proud of what we have accomplished at Navitas," said Sheridan, reflecting on his 11-year tenure at the company. "Building the industry's only next-gen, pure-play power semi company has been the privilege of a lifetime. As we look to the future, I'm confident that Chris Allexandre is the right choice to lead Navitas in its mission to electrify our world."

Allexandre brings more than 25 years of experience in the semiconductor industry. Most recently, he served in senior executive roles at Renesas Electronics, including SVP and general manager of its power division from October 2023. Allexandre oversaw Renesas' \$2.5 billion power management business and led the pivot and execution of its power strategies toward the cloud infrastructure, automotive and industrial markets, including Renesas' acquisition and integration of Transphorm, a supplier of GaN solutions, in June 2024. Allexandre was previously Renesas' chief sales and marketing officer from 2019 to 2023.

"I am honoured and thrilled to join Navitas and look forward to working with this world-class team to accelerate our leadership in GaN and SiC technologies," said Allexandre. "With power demand growing in AI data centre and critically needed

energy infrastructure, I see promising opportunities to drive expansion in these important markets. I also want to thank Gene for his great support planning for this transition, and for everything he has done for Navitas."

Prior to his tenure at Renesas, Allexandre held executive roles at Integrated Device Technology (IDT) (acquired by Renesas in 2019) as SVP of sales and marketing; at NXP as SVP, worldwide sales for mass market; and at Fairchild Semiconductor as SVP of worldwide sales, marketing and business operations.

Allexandre began his career at Texas Instruments, beginning in its New College Graduate rotation programme, and over 16 years progressing through a series of business and sales roles based in Europe and China, becoming TI's VP of sales for EMEA and a member of TI's strategic leadership team in 2012.

## WEBINARS

Specialists with 30 year+ pedigree and in-depth knowledge in overlapping sectors

For more information contact:

Jackie Cannon **T:** 01923 690205 **E:** jackie@angelwebinar.co.uk **W:** [www.angelwebinar.co.uk](http://www.angelwebinar.co.uk)

**T:** +44 (0)2476 718 970 **E:** info@angelbc.com **W:** [www.angelbc.com](http://www.angelbc.com)

**Expertise:** Moderators, Markets, 30 Years + Pedigree

**Reach:** Specialist vertical databases

**Branding:** Message delivery to high level influencers via various in house established magazines, websites, events and social media

**Angel**

BUSINESS COMMUNICATIONS

# IQE considers sale

Company expands scope of ongoing Strategic Review to incorporate the potential sale of the company

COMPOUND SEMICONDUCTOR wafer firm IQE plc has announced a trading update for the full year ending 31 December 2025, and that it's extending the scope of its ongoing Strategic Review to incorporate the potential sale of the company

IQE has previously said that trading in H1 2025 was impacted by macroeconomic uncertainty and as a result, some end customer demand was fulfilled with existing inventory.

The group says it has continued to experience weakness in wireless markets, largely as a result of softness in mobile handset sales, and this is expected to persist through 2025. In addition, delays to federal funding cycles in US military and defence sectors are resulting in the deferral of orders into 2026.

Revenue for FY 2025 is expected to be between £90.0 million to £100.0 million, resulting in an adjusted EBITDA position of between £(5.0) million to £2.0 million. H1 2025 revenue is expected to be at least £44.0 million. The group will report its interim results on 23 September 2025.

The board says there's significant market opportunity for IQE because of the group's leading position in providing

advanced compound semiconductors across several market verticals and to a base of global marque customers.

The board is now expanding the scope of the previously announced Strategic Review to also incorporate the potential sale of the company and is seeking buyers. While the Strategic Review process remains ongoing, IQE is progressing negotiations with multiple parties for the sale of the group's Taiwan operations.

Should the sale of Taiwan be concluded, it is expected that the proceeds from such sale will be used to fully repay the group's Revolving Credit Facility with HSBC Bank and Convertible Loan Notes issued in March 2025, as well as providing IQE with cash to invest in its core operations. The board continues to be advised by

Lazard on the full scope of the Strategic Review.

Julia Meier, CEO of IQE, commented: "We have updated our expectations for the full year to adjust for the deferral of certain contracts in our wireless and photonics segments.

This is a result of continued global and macro uncertainty which has impacted the unwinding of customer inventory levels pre-built in 2023 and 2024, the sale of new mobile handsets and the release of budgetary spending across the US military and defence sector.

"Looking ahead, while the Strategic Review remains ongoing I am encouraged by the progress we are making and remain confident in our ability to unlock value for all of our stakeholders."

**Next Generation Defect Inspection & Metrology for Co-packaged Optics**

## Advanced 2D Inspection with Onboard 3D Metrology

[ontoinnovation.com](http://ontoinnovation.com)

**Dragonfly®**

Inspection and

Metrology

**onto** innovation.

# SweGaN, Ericsson, Saab and Chalmers collaborate on 6G GaN PAs

Partnership will combine advanced modelling and fabrication to optimise PA performance across telecoms and defence

SWEGaN, a European semiconductor manufacturer specialising in GaN-on-SiC epitaxial wafers, announces the launch of a two year project funded by Vinnova (Sweden's innovation agency) with Ericsson, Saab, and Chalmers University of Technology, aiming to revolutionise GaN-based power amplifier technology for next-generation 6G networks.

The project targets the 7 - 15 GHz frequency range (X/Ku bands), a critical spectrum for future 6G applications. By leveraging SweGaN's proprietary QuanFINE epitaxial GaN-on-SiC solutions, the collaboration will deepen understanding of the material properties and the HEMT device characteristics and develop high-efficiency PA circuits that support energy-efficient, high-capacity wireless systems.

"This Vinnova-backed collaboration is a major milestone for SweGaN and our partners," said Jr-Tai Chen, CEO of SweGaN. "With this project, we're combining world-class expertise from telecom, defense, and academia to unlock the full potential of our QuanFINE materials for 6G." The project ensures vertical integration

across materials, device processing, and system-level design, and it follows a dual-track approach.

The academic track focuses on the influence and process variations on HEMT device-level performance by advanced modeling. The goal is to extract empirical models and define design boundaries for optimal PA efficiency.

The industrial track centres on PA design, fabrication, and benchmarking using state-of-the-art foundry processes. Industry partners will supply high-performance devices for modeling and validation, ensuring alignment with real-world system needs. The collaboration will deliver insights into

how epitaxial design, processing, and circuit architecture impact device and system-level performance.

"This collaboration strengthens the bridge between civilian and defense technologies. By working closely with leading partners across the value chain, we accelerate the development of RF technologies that will have real-world impact in both defense and civilian domains," said Johan Carlert, head of microwave and antenna design at Saab.

"At Chalmers, we're thrilled to contribute our modeling and device expertise to a project with such high industrial relevance," said Christian Fager, professor at Chalmers University of Technology.

**HORIBA**

**New Value in Wafer Inspection for Inspection Efficiency and Yield Improvement**

**Xtrology**

Fully Automated Thin Film Inspection System

- Film Thickness

- Defects Inspection

- Crystallinity

- Optical Properties

- Composition / Stoichiometry

- Stress

# Toshiba and SICC sign SiC MoU

Companies announce intention to collaborate on improving SiC wafer quality

Toshiba and SICC have signed a memorandum of understanding (MoU) under which these two companies hope to work together to improve characteristics and quality of SiC power semiconductor wafers made by SICC, and enable expanded supply of stable, high-quality wafers from SICC to Toshiba.

According to Toshiba, it has an established track record in developing, manufacturing and selling SiC power semiconductors for railways, and is currently accelerating the development of SiC devices for applications including server power supplies and cars.

This work includes reducing power losses in SiC devices and improving their reliability and efficiency.

The proposed collaboration with SICC, a Chinese developer of SiC wafers, is expected to help drive forward improved solutions for various applications and to accelerate business expansion.

Since its founding in 2010, SICC has concentrated on producing single-crystal SiC wafers. Following its initial public offering in 2022, the first in China to focus on SiC, the company has expanded its market share.

In 2024, SICC introduced the market's first 12-inch SiC wafer, and in 2025 it announced 12-inch wafers for all products, including *n*-type, semi-insulating, and *p*-type.

In the proposed collaboration with Toshiba, SICC says it aims to link SiC power semiconductor manufacturers' requirements and expectations for SiC wafer element technology to improved wafer quality and reliability, and to contribute to the expansion of the SiC power semiconductor market.

Toshiba and SICC say they are still discussing specific collaboration details.

## Keep it clean

In semiconductor and thin film manufacturing, there is zero tolerance for quality inconsistencies in hydrogen deliveries.

Take control with **Nel** on-site hydrogen generation.

Call one of our sales engineers or visit us online:

+1.203.949.8697 / [www.nelhydrogen.com](http://www.nelhydrogen.com)

**nel** •

The future belongs to the frontrunners

# UW-Madison opens ultra wide bandgap lab

New US facility will focus on an emerging class of III-nitride semiconductors, such as AlGaN and AlN

The University of Wisconsin-Madison has opened an Ultra-Wide Bandgap Semiconductor MOCVD Laboratory, a facility that will focus on the emerging class of ultra wide bandgap III-nitride semiconductors such as AlGaN and AlN.

At the moment, fabricating and characterising ultra-wide bandgap semiconductors is challenging because they require expensive equipment and deep expertise in MOCVD or other advanced commercialisation-friendly deposition techniques.

Shubhra Pasayat (pictured above centre), who oversees the new facility as the lab's principal investigator, set up a commercial Aixtron MOCVD reactor for research when she first joined UW-Madison in 2021.

The new facility takes this to the next level with an Agnitron Agilis 100 system that can handle higher temperatures and lower pressures. This will allow Pasayat and her students to design

and precisely synthesise high-quality 2-inch diameter wafers of high-aluminium content ultra-wide bandgap materials.

The lab is described as being at the centre of UW-Madison's rising III-nitride ecosystem. The onsite faculty's broad expertise in chip design and architecture, materials characterisation, fabrication, advanced packaging, and systems integration means these ultra-wide bandgap semiconductors can go from the drawing board to the motherboard all on one campus – streamlining and improving the research process.

## Wolfspeed launches 200 mm SiC materials portfolio

WOLFSPEED has announced the commercial launch of its 200 mm SiC materials products, marking a milestone in the company's mission to accelerate the industry's transition from silicon to SiC. It is also offering 200 mm SiC epitaxy for immediate qualification, which, when paired with the company's 200 mm bare wafers, will deliver breakthrough scalability and improved quality, enabling the next generation of high-performance power devices, according to the company.

"Wolfspeed's 200 mm SiC wafers are more than an expansion of wafer diameter – it represents a materials

innovation that empowers our customers to accelerate their device roadmaps with confidence," said Cengiz Balkas, chief business officer.

The company says that the improved parametric specifications of the 200 mm SiC bare wafers at 350  $\mu\text{m}$  thickness and enhanced doping and thickness uniformity of the 200 mm epitaxy enables device makers to improve MOSFET yields, accelerate time-to-market, and deliver more competitive solutions across automotive, renewable energy, industrial, and other high-growth applications. "This advancement reflects Wolfspeed's long-standing

## CSA Catapult appoints Caroline O'Brien as CEO

THE UK's Compound Semiconductor Applications (CSA) Catapult has appointed Caroline O'Brien as its new CEO, who will join in late September.

A semiconductor industry specialist, O'Brien is currently CEO of Kubos Semiconductors and brings over 30 years of experience in the technology sector, where she has developed a broad knowledge of working with VC-backed businesses and blue-chip multinationals.

She has held senior commercial and executive positions in several companies, focusing on developing and commercialising new technologies and products.

O'Brien holds a B.Eng in Electronics and Electrical Engineering and an MBA from the University of Bath.

Martin McHugh stepped down as CEO of the Catapult in March 2025 and Raj Gawera, who joined the board in 2021, was appointed CEO on an interim basis from April 1 2025 and will return to his previous role as non-executive director.

commitment to pushing the boundaries of SiC materials technology," said Balkas. "This launch demonstrates our ability to anticipate customer needs, scale with demand, and deliver the materials foundation that makes the future of more efficient power conversion possible."

# WHEN IT CAN'T FAIL

FROM ADVANCED MATERIALS TO

PRECISION DESIGNS, OUR PRODUCTS

ARE ENGINEERED FOR PERFORMANCE

AND RELIABILITY

Discover our solutions for

the semiconductor industry

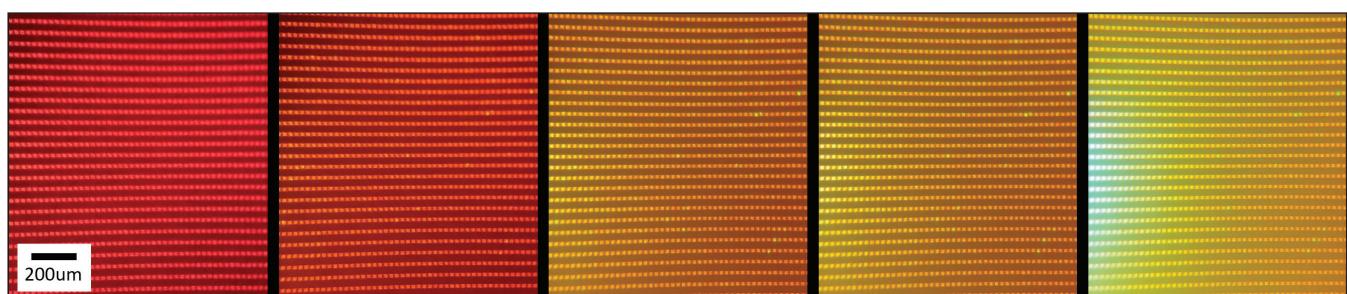

## Transforming transfer technology for microLEDs

Q-Pixel addresses the biggest bottleneck to manufacturing microLED displays with an out-of-the-box transfer technology that combines a critical hike in yield with superior throughput

BY RICHARD STEVENSON, EDITOR, CS MAGZINE

FOR around a decade or so, it feels like our industry has been on the cusp of a revolution in displays. But this breakthrough is yet to materialise. The only well-known display that's based on the microLED is the Samsung MS1A, a 110-inch TV that retails for an eye-watering \$150,000 – it's so expensive that it's not going to win many sales, even to those with piles of cash and a strong interest in home entertainment.

Many would argue that the biggest barrier to the widespread manufacture of displays based on the microLED is the transfer technology employed to move vast numbers of these miniature marvels from processed epiwafers to a backplane.

While transferring microLEDs is not a pre-requisite for very small displays – they can be produced by bonding arrays of microLEDs formed on GaN-on-silicon epiwafers to a CMOS backplane that drives these emitters – a

transfer process is non-negotiable for manufacturing displays for watches, smartphones, TVs and outdoor screens.

The big issue with conventional approaches to transferring microLEDs – such as the massively parallel techniques that involve picking-up vast numbers of these tiny emitters with an elastomeric stamp and placing them down on a backplane – is insufficient yield.

This view might raise a few eyebrows, as at first glance the yield figures realised with these traditional techniques look very impressive. But the reality is that they are not up to the task, argues J.C. Chen, CEO of Q-Pixel, a start-up with a yield-busting technology that's looking to license its microLED-related technologies to chipmakers and those wishing to produce displays.

According to Chen, a commonly quoted yield figure for transfer technologies

is 99.99 percent. "But in the microLED industry that's a no-no," claims Chen, pointing out that 24 million chips must be transferred to make an ultra-high-definition TV.

Expanding on this point, Chen explains that with a yield of 'four-nines', there are typically around 100 'dead' pixels for every million transferred.

"One hundred is very difficult to repair. But if you have 'five-nines' or 'six-nines', you have only one dead pixel."

Part of the reason why 'dead' pixels are unacceptable is that our benchmark is today's OLED and LCD screens, and they have an incredibly low level of defects.

"If you have 100 defects, you cannot really compete, no matter how good you are," says Chen, who explains that it's not possible to trade imperfections from dead pixels for the superior brightness and lower power

► Prototype panel demonstration of Q-Pixel's proprietary transfer process, using 10 µm tuneable polychromatic microLEDs to produce a display with a pixel density of over 500 pixels per inch. There are no missing pixels, and yield is more than 99.9995 percent.

consumption of displays based on microLEDs.

Breaking through this yield-related barrier is Q-Pixel's novel transfer technology, known as Q-Transfer, that is claimed to have a yield of more than 99.9995 percent.

Chen and his co-workers have demonstrated the production capability of Q-Transfer by using this technology to make prototype colour displays with 10 µm pixels, that are spaced close enough together to provide a density of more than 500 pixels-per-inch.

Q-Pixel stresses that as well as the phenomenal yield, this approach resulted in zero missing pixels.

For understandable reasons, Chen is tight-lipped when it comes to discussing the details of the Q-Transfer technology, which is credited to 'out-of-the-box' thinking. But he says that Q-Transfer is compatible with most transfer technologies, without much modification.

The origins of Q-Transfer can be traced back to Covid times, which hampered much company activity, but allowed the team to mull over challenging issues and come up with novel ideas.

Since then, they have been developing a new approach to microLED transfer. Efforts began with small displays, which gave encouraging results. However, bigger displays are needed to convince the display industry that Q-Transfer can

be a game-changer. "We need at least a watch-size display. If you have just a 1 centimetre by 1 centimetre, it's probably too small," argues Chen.

Now Q-Pixel is demonstrating that its transfer technology is capable of producing displays for small watches.

"That means the technology has become available to industry," says Chen, who explains that this involves licensing Q-Transfer, and working with Q-Pixel on technology transfer.

Those interested in pursuing this will be keen to discuss throughput, as this plays a key role in determining the cost of manufacture. Those enquiring on this front will not be disappointed, according to Chen, as when Q-Transfer is applied to existing transfer approaches, the speed is similar, if not better.

### Completing the puzzle

Chen views Q-Transfer as the last piece in the puzzle, when it comes to overcoming challenges to ensure an economically viable approach to producing microLED displays.

The company's other key technology is its colour-tunable GaN-based microLEDs. With this elegant device, emission wavelength is determined by driving conditions.

For all forms of GaN-based LED, there are concerns related to the efficiency in the red. Reaching this spectral domain demands an increase in the indium content in the quantum wells, a

move that increases strain, leading to declines in crystal quality and emission efficiency.

Chen believes that for some applications, such as those that are indoors, the efficiency of Q-Pixel's colour-tunable microLEDs is sufficient.

But for outdoor applications, it's not so clear, due to a lack of data. "Honestly, we are not up to that point yet."

What is beyond question is that microLEDs are incredibly compelling candidates for deployment in outdoor displays. Unlike those based of OLEDs and LCDs, they are not impaired by exposure to UV light, and they do not burn out.

Having demonstrated the key technologies to kick-start mass production of microLED displays, the next goal for Q-Pixel is to start working with companies that have invested in equipment to manufacture this class of display.

Such a partnership would be based on licensing technology from Q-Pixel. "We are basically an IP company. We're just doing the R&D and some demonstration," says Chen.

He believes that such ventures could allow the microLED industry to take off.

"The whole industry is not moving fast enough," laments Chen. "But I think that we can make it happen faster. That's our goal."

- Based around a hot topic for your company, this 60-minute recorded, moderated zoom roundtable would be a platform for debate and discussion

- Moderated by an editor, this can include 3 speakers

- Questions prepared and shared in advance

**Cost: £7500**

**Contact: Jackie Cannon**

**jackie.cannon@angelbc.com**

ANGEL

EVENTS

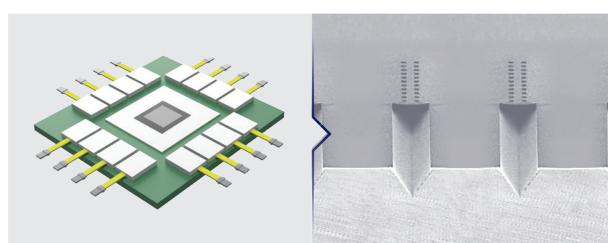

## X-Fab: Normally-on, then normally-off

At X-Fab's Dresden foundry that's been churning out silicon devices for decades, production of normally-on GaN HEMTs is now underway, with normally-off variants soon to follow

BY RICHARD STEVENSON, EDITOR, CS MAGAZINE

EVEN if you don't know much about economics, you'll be familiar with the idea that supply rises and falls to meet demand. So, given that sales of GaN power devices are rising fast and will continue to climb, one should expect global GaN foundry capacity to increase over the coming years.

Against this backdrop, TSMC's recent decision to move away from offering a GaN foundry service will have raised a few eyebrows. It's a move that bucks the trend, as companies looking to outsource production of GaN HEMTs

and Schottky barrier diodes are benefitting from an increasing choice of foundries, with this service now starting to be offered in Europe for the first time, thanks to efforts at X-Fab's Dresden facility.

At this fab, opened in 1961 and taken over by X-Fab about 15 years ago, chip production is dominated by silicon power devices for automotive applications, manufactured on a 200 mm line capable of producing 350 nm CMOS technologies. But X-Fab is now expanding the use of this facility,

by offering customers the opportunity to design and make normally-on (D-mode) GaN HEMTs with blocking voltages from 100 V to 650 V. This is the first step in the formation of a commercial GaN portfolio, soon to be strengthened with the introduction of normally-off (E-mode) HEMTs and Schottky barrier diodes. All these devices are complementing those based on SiC, produced at the Lubbock Fab in Texas, and give X-Fab's customers a tremendous choice when it comes to the two leading wide bandgap technologies for power electronics.

X-Fab has been developing and refining GaN technology since 2015, with efforts originating from interest from a lead customer. This led to an initial process flow for D-mode devices.

"We didn't stop there," reveals the X-Fab's GaN Technical Marketing Manager, David Auffret, who says they also developed a Schottky barrier diode, viewed within X-Fab as a variation of the HEMT, thanks to the foundry's modular approach to device production.

A decade on from its first foray into GaN power technology, Auffret argues that now is the right time to offer this capability to customers.

According to Auffret, GaN has now reached a high level of acceptance within the power electronics industry. "If you go to conferences, you will see more and more talks about GaN." What's more, customer interest in GaN is high and increasing.

► X-Fab has been developing GaN HEMT technology at its Dresden foundry since 2015.

Within the GaN power electronics industry, much production occurs at IDMs, which produce some very impressive products. However, these off-the-shelf components, regardless of the performance they offer, may not meet everyone's needs.

Helping to address this limitation, X-Fab has been sampling D-mode technology. At its heart is a core platform that's open to all, rather than one that's customised for just one or two customers.

Interested parties are able to draw on X-Fab's process-design kits (PDKs), which are undergoing continuous improvement.

"The goal is to have something similar to our CMOS business," says Auffret. "The PDK will enable the customer to make first-time-right design, and have a faster time to market."

Another advantage of working with X-Fab is that customers wanting a unique product can customise process flow.

In the final quarter of this year, X-Fab will start running multi-project wafers through its lines. "It's cutting the development cost, not only for the customer but also for us. It's really a win-win," says Auffret.

With multi-project wafers, customers can trim their time to market, while reducing proto-typing costs, by avoiding paying for mask sets. And rather than footing the bill for the manufacture of two or three wafers populated with thousands of die, they receive just 50 or so die, enough for evaluation purposes.

While X-Fab's D-mode technology is new to customers, it has a level of maturity that comes from production on a well-established 200 mm line featuring substantial monitoring. The engineers at Dresden have produced test chips, with measurements revealing an on-resistance of less than 2 mΩ cm<sup>2</sup>, at 650 V.

The decision to begin by offering normally-on HEMTs sets X-Fab apart from a number of rivals – many of them are focusing on the normally-off variant that provides much-valued fail-safe operation.

► The 200 mm line at the Dresden Foundry has focused in producing devices using 350 nm CMOS technology, but will soon also provide the production of GaN-based D- and E-mode HEMTs and Schottky barrier diodes.

However, despite this weakness, normally-on HEMTs are in demand: they have a higher efficiency; they are better-suited to continuous sensing, making them attractive for medical applications; and with the addition of external circuitry, fail-safe operation can be realised.

Interest in X-Fab's D-mode HEMTs is strongest for 650 V devices, and there is some demand up to 1200 V. In comparison, for the E-mode variants under development, which can be produced by processing modified epiwafers with just a couple of extra masks thanks to the foundry's modular approach, interest is at 650 V and below.

X-Fab does not have facilities for epi-growth, so sources material from partners. "Three of them are qualified or about to be qualified," says Auffret, who adds that customers can also provide their own epiwafers to the foundry.

For both approaches, epiwafers need to be produced on thick silicon substrates that are less prone to bow and warp that results from lattice and thermal mismatches between the GaN epilayers and its foundation.

At the Dresden foundry, processing stops at the wafer level. "We don't provide any packaging," says Auffret, who explains that X-Fab does work with some partners for dicing. What may

come as a surprise is that as well as offering back-side grounding, there's micro-transfer capability at X-Fab, which has the potential to unite GaN power devices with silicon CMOS circuitry, by placing one technology on top of the other.

With interest in GaN on the rise, opportunities for production on 300 mm substrates are attracting debate. The view of Auffret is that now is too early, as this larger size would drive up chip costs, rather than delivering economies of scale. While X-Fab is involved in 'close' discussions with epiwafer and equipment suppliers regarding the larger format, the 200 mm platform is viewed as the sweet spot, not just for now, but also for the near future.

Looking ahead, another evolution that X-Fab will want to optimise, in order to maximise sales and profits, is the transition from CMOS to GaN at the Dresden fab. Today, CMOS is fully loading the fab, and funding its existence until GaN is ready to ramp.

Producing both classes of technology in the same foundry places X-Fab in an enviable position. While some within our industry are having to fight against silicon to ensure success, the Dresden fab can churn out chips, while reacting to any twists and turns within the power electronics industry.

# Effective communication with government and other stakeholders

Discussions with government officials and leaders of other bodies should avoid detailing core technologies and focus on tangible benefits of a flourishing compound semiconductor industry

BY HOWARD RUPPRECHT FROM CCONNECTED

SEMICONDUCTORS are ubiquitous and largely invisible. As the little black boxes attached to circuit boards, we are all utterly reliant on their functionality for virtually everything we do – yet we take their easy availability and low cost for granted.

During the pandemic, when semiconductor shortages thwarted car sales, the importance of these chips – and our dependence on them – finally started to resonate among policymakers. Geopolitics (particularly between China, the US and Taiwan) further escalated supply chain risks, prompting calls for 're-shoring', supported by huge subsidies.

But it's far from easy to construct sovereign supply chains. Semiconductor design and manufacturing is an exclusive club, only a few countries are members, and none of them enjoys full independence or capabilities to make the latest semiconductors.

Like many countries involved in our industry, to ensure that the UK maintains its membership, some level of governmental support is needed to continue to develop unique sovereign capabilities, which are traded with allies. But for those with leadership roles in semiconductor companies and associated bodies in the UK – and those holding similar positions in other countries – what's the key

to successfully communicating our industry needs to national and regional policymakers, and justifying these investments to the nation at large, including the taxpayers?

It's fair to say that politicians and civil servants are unlikely to read *Compound Semiconductor* magazine, so it's essential to use different channels. In our case, at CSconnected, we are working with a wide range of non-industrial stakeholders, from local politicians that have semiconductor facilities within their constituencies, to national government departments whose role is to deploy

funding for growth. From holding local events, to managing an All-Party-Parliamentary-Group, we strive to avoid explaining technicalities, focusing instead on increasing awareness and understanding industry dynamics, and the subsequent economic benefits that a thriving CS industry can deliver.

I don't need to tell you that semiconductors are not a commodity, and must be viewed markedly differently from the likes of oil and steel. Our sector produces highly differentiated individual components, with the market for them skewed by massive national and regional intervention, to support local industry. It is crucial to drive home the point that these are not 'subsidies for a failing industry', but are a price that's well worth paying to maintain a strategically important leadership position in a global industry. One should view support for the semiconductor industry as more akin to regularly watering an orchard. If it stops, trees will ultimately yield less fruit and eventually die. Sometimes nature supplies the necessary rain, and sometimes we need to irrigate to ensure long-term sustainability.

Publicly funded support tends to takes the form of R&D funding, generally leveraged by both public and private equity. In an industry spending around 16 percent of its revenue on R&D, it is essential to continually innovate, as this type of

work creates and sustains many highly paid knowledge-intensive positions. Equally, it's important to support the building of research and scale-up facilities with leading-edge equipment, to create an open access environment where deep-tech companies can develop the future. In south Wales, we are succeeding on this front with the Centre for Integrative Semiconductor Materials, at Swansea University. It's essential to explain to local stakeholders how these investments support long-term job creation, enable leverage for further investment, facilitate entrepreneurship and drive industrial scale-up.

In our locality, the compound semiconductor cluster works with the Welsh Economic Research Unit at Cardiff University to independently track the economic impact of local investment. Since 2020, employment has grown by 32 percent within the cluster, gross valued-added contribution is more than three times that of the national average, and we are proud to export over 90 percent of the collective £500 million in annual revenue from cluster companies. Ultimately, it's these numbers that resonate with our stakeholders and benefactors when justifying investment.

For us, the biggest challenge is associated with the public sector answering to a different group of stakeholders. Probably including some democratically elected decision makers, this group is made up of individuals that have their own vested interests,

whether at a local constituency or ministerial portfolio level. As there are many competing sectoral and geographical investments on the table, this group will inherently struggle to focus, as doing so will threaten accusations of excluding worthwhile ventures. The result is that public money tends to be spread thinly across numerous causes, rather than being effectively focused.

Decision making can also be painfully slow, requiring independent evidence and adherence to onerous public procurement rules. This drawn-out process results in long cycles of investment and subsequent impact that often transcends political terms, bringing a risk of jeopardy from a changing strategy if the political incumbent changes. Against this backdrop, it's not uncommon for former policy makers to fail to see the results of their decisions until after their term in office.

Some of what I'm describing is common across western democracies. This is why we are unlikely to see the kind of focus evident in Taiwan, South Korea or China, where there are closer industrial links to long-term policy and government support. This is unfortunately a disadvantage in such a fast-moving global market. Private companies are essentially autocratic and have the freedom to make fast, bold decisions on investment and strategy (within the bounds of applicable law) without having to seek approval beyond major shareholders.

Given the different perspectives that exist, what's needed to effectively work with government?

Our experience shows that working as a group has stronger impact and is more efficient for all parties. So, if a delegation is visiting our cluster, we collectively mobilize. A single voice representing a large group with common needs is more effective.

In addition, we devote much effort to building long-term relationships with the government and its officials. Like any relationship, we have good and bad times, but we all need to collaborate. We must accept that there will be a turnover of people, so a level of mutual re-education will be periodically required, and relationships must exist at many levels.

Finally, it's important to find common ground. Some things are easier for government to do than others. For instance, an investment in skills development has a wide impact on the community, while still supporting the development of essential resources needed for cluster growth. Equally, there may be a preference for interventions that leverage large amounts of private equity.

What's clear is that the future success of the UK's semiconductor industry will depend in part on successful collaboration between industry and public stakeholders – and we will endeavour to keep these relationships active and constructive.

**CS ROUNDTABLE**

Connecting Leaders & Experts in the Compound Semiconductor Field

- Based around a hot topic for your company, this 60-minute recorded, moderated zoom roundtable would be a platform for debate and discussion

- Moderated by an editor, this can include 3 speakers

- Questions prepared and shared in advance

**Cost: £7500**

**Contact: Jackie Cannon**

[jackie.cannon@angelbc.com](mailto:jackie.cannon@angelbc.com)

**ANGEL**

**EVENTS**

# Agnitron: Driving ultra-wide-bandgap breakthroughs

Advancing the capabilities of AlN, AlScN and aluminium-rich AlGaN is the Agnitron Agilis 100 MOCVD reactor

BY FIKADU ALEMA, WILLIAM BRAND, BENJAMIN BRAND, AARON FINE, VITALI SOKHOVEEV AND ANDREI OSINSKY FROM AGNITRON TECHNOLOGIES

WITHIN the family of known semiconductors, AlN possesses a number of tremendous attributes. They include a remarkably wide bandgap of 6.2 eV, a Schottky barrier height of more than 2 eV, an outstanding thermal conductivity, and a critical breakdown field exceeding 15 MV cm<sup>-1</sup>. Thanks to these great characteristics, the Baliga Figure of Merit for AlN is far higher than that for GaN, SiC, and even other ultra-wide bandgap materials, like Ga<sub>2</sub>O<sub>3</sub>, making AlN a leading contender for future high-power and high-temperature electronic applications.

Also offering much promise is a relatively novel ternary alloy that's closely related to AlN: AlScN. For scandium concentrations of more than 20 percent or so, AlScN combines ferroelectric switching behaviour with excellent thermal stability and CMOS compatibility, making it highly suitable for non-volatile memory and pyroelectric sensors operating above 600°C. Due to its robustness in ferroelectric applications, devices made from AlScN promise to provide reliable performance in extreme environments, while pyroelectric capabilities enhance sensitivity and durability in thermal detection and surveillance applications. Additional assets include: exceptional piezoelectric properties, supporting applications such as filters, resonators, energy-harvesting transducers, and MEMS sensors in harsh and high-temperature conditions; and an ultra-wide-bandgap, enabling use in high-temperature RF electronics exceeding 500°C. What's more, AlScN holds significant promise for optoelectronic applications, including spatial light modulators, further extending its applicability across a broad temperature range.

Critical to leveraging the vast potential of both AlN and AlScN is the growth of high-quality epitaxial material with characteristics suitable for making high-performance devices. Assisting in this endeavour is our team from Agnition Technology, offering MOCVD reactors that are tailored to producing AlN-based epiwafers with ground-breaking levels of free electron concentration, and AlScN-based epiwafers with exceptional material quality.

### AlN challenges

Despite their immense potential, AlN-based power devices are still in their early stages of development, with several key challenges to overcome. Obstacles include: a lack of cost-effective, large-area native substrates; difficulties in achieving high-efficiency doping; and the need for reliable, low-resistance ohmic and Schottky contacts. Fortunately, these difficulties are steadily being addressed through continued progress in AlN epitaxy, doping, and contact engineering, with advances unlocking pathways to a new generation of power devices that surpass the limitations of today's wide bandgap technologies.

One of the main challenges hindering deployment of AlN power electronics is achieving sufficiently high and stable *n*-type carrier concentrations and mobilities in device layers needed in diodes and

transistors. Dopants typically come from group IV elements, and include silicon and germanium, with the former the most extensively studied. However, when silicon dopants are used in AlN, they fail to form the shallow hydrogenic donors they do in GaN. Instead, when adding a small amount of silicon to AlN, the result is a deep-level defect known as a DX centre. This deep-level defect, an electron trap near the conduction band edge with an activation energy ranging from 78 meV to 345 meV [1], leads to poor carrier activation at room temperature.

Increasing silicon doping initially improves the free-electron concentration, but only up to a point. Beyond a critical doping level, there's a fall in free-carrier concentration – a phenomenon known as the compensation knee. This detrimental decline in free-carrier concentration comes from compensation mechanisms, including the formation of DX centres, cation vacancies, silicon-vacancy complexes, and other point or extended defects. All these mechanisms fundamentally limit the effectiveness of heavy doping in AlN, and are a critical barrier to achieving technologically relevant *n*-type conductivity.

### Point defect control in AlN

To enhance the electrical properties of AlN, and ultimately realise stable and efficient *n*-type doping, it's essential to control the formation of point defects. In this regard, one must consider the formation energy of a point defect. This energy, strongly influenced by the crystal's chemical potential and the position of its Fermi level, determines the equilibrium concentration. By tuning the crystal's chemical potential and the position of its Fermi level, it's possible to cut the density of compensating defects, and thereby enhance the activation efficiency of intentional dopants.

The chemical potential depends on growth conditions and can be controlled by process optimisation. For AlN, epitaxial films can be formed with a number of techniques, including MOCVD, MBE, HVPE, and sputtering. Amongst them, MOCVD stands out as the most mature and widely adopted method for forming high-quality, device-grade films. This growth technology provides excellent crystalline quality, low dislocation densities, wafer-scale uniformity, and precise doping control, making it suitable for scalable production.

With MOCVD, the chemical potential can be controlled by adjusting growth parameters, such as temperature, reactor pressure, and the V/III precursor ratio. In parallel, it's possible to dynamically manipulate the position of the Fermi level with UV-assisted epitaxy. The mechanism behind this is the injection of minority carriers into the crystal, which occurs when light with a wavelength above the bandgap is absorbed. It's a process that's referred to as defect quasi-Fermi level control. Adjusting the growth parameters to control the chemical potential and using UV light to manipulate the Fermi level dynamically increases

the formation energy of compensating defects, such as carbon substituting nitrogen ( $C_N$ ), nitrogen vacancies, and impurity complexes, making their formation less favorable [2].

### Agilis 100 reactors for AlN growth

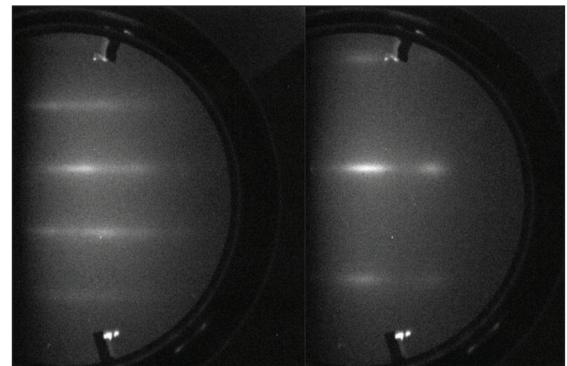

Through a DARPA-funded project, we have been actively developing an MOCVD process for growing thin films of high-quality AlN. This effort employs our Agilis 100 MOCVD platforms, equipped with two different showerhead geometries: a remote-injection showerhead (RIS) and a close-injection showerhead (CIS). These studies have involved growth on c-plane AlN substrates obtained from domestic suppliers.

For both configurations, reactor design and process conditions have delivered a significant impact on the resulting film quality, particularly with respect to improvements in surface roughness, background carbon and oxygen incorporation, and structural and electrical properties of the AlN films. The CIS configuration, featuring a short distance between the showerhead and substrate, allows the use of a wide range of ammonia flow rates (V/III ratios) without negatively impacting the growth rate. This flexibility is particularly valuable, as the V/III ratio plays a critical role in controlling impurity levels in the grown films, such as the carbon and oxygen concentrations.

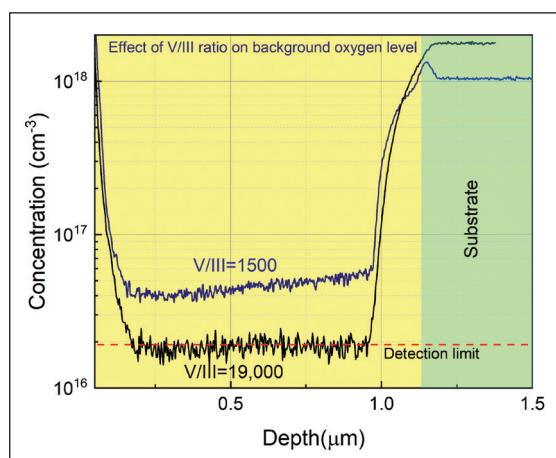

According to secondary ion mass spectrometry (SIMS) measurements, our AlN films grown in the CIS reactor at a high V/III ratio of 19,000 have oxygen concentrations near the detection limit, which is around  $2 \times 10^{16} \text{ cm}^{-3}$ . In contrast, films grown at a lower V/III ratio of 1,500 have an oxygen concentration approximately 2.3 times the detection limit (see Figure 1). We have observed similar trends for films grown in our RIS reactor, underscoring the importance of high ammonia flow in suppressing oxygen incorporation across different reactor designs.

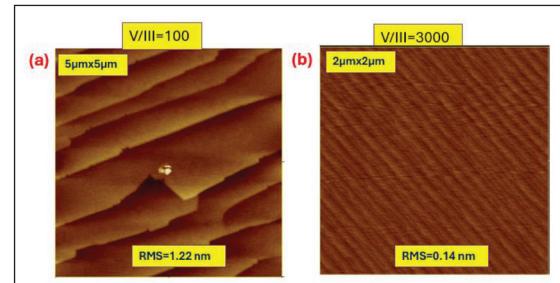

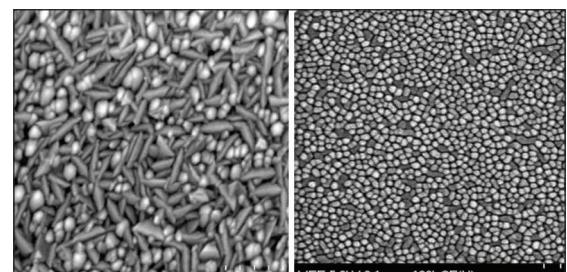

As well as offering the opportunity to control impurities, the V/III ratio impacts surface morphology. Assessments with atomic force microscopy highlight the benefits of a higher V/III ratio when growing AlN films that are around 1  $\mu\text{m}$ -thick in the RIS reactor, using trimethylaluminum (TMAI) as the source of

► Figure 1. Secondary ion mass spectrometry depth profiles of oxygen (O) concentration in AlN layers grown in the CIS reactor at two different V/III ratios: around 19,000 (black trace) and around 1,500 (blue trace).

► Figure 2. Atomic force microscopy images of undoped AlN films that are around 1  $\mu\text{m}$ -thick and grown on AlN substrates using RIS MOCVD. TMAI provides the aluminium source, and V/III ratios are (a) 100 and (b) 3000.

aluminium. When increasing the V/III ratio from 100 to 3,000, under otherwise identical conditions, atomically smooth, step-flow surfaces without any visible pits are maintained. However, the higher V/III ratio produces a significantly smoother surface, with values for root-mean-square (RMS) roughness comparable to those of the starting substrate. We can conclude that the benefits of increasing the V/III ratio are reduced impurity incorporation and improved surface smoothness – both are critical attributes for device-quality AlN layers.

We have also investigated the influence of substrate temperature and silane flow on film morphology. This work determined that unintentionally doped AlN films grown between 1200°C and 1300°C consistently produce smooth surfaces with RMS roughness values around 0.18 nm. We did not observe any surface pits in these epilayers, indicating high-quality growth that's independent of temperature within this range.

However, the intentional introduction of silane, to provide silicon doping, causes surface morphology to become more sensitive to process conditions. In this case, one must carefully optimise growth parameters to suppress pit formation and maintain a high film quality.

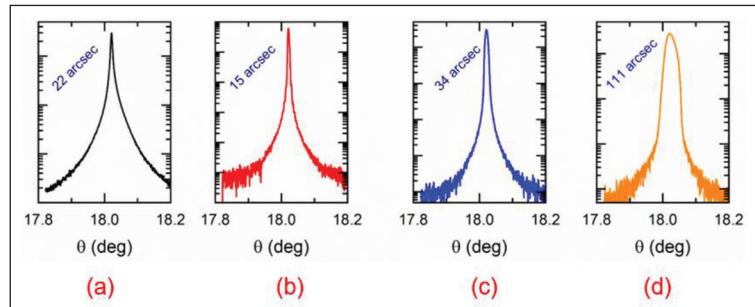

To evaluate the crystalline quality of our AlN films grown using RIS and CIS reactors, we have turned to high-resolution X-ray diffraction. This investigation considered films formed with TMAI as the aluminium source, using different V/III ratios, and with and without intentional doping. For AlN layers grown in the RIS reactor, (0002) rocking curves have a full width at half-maximum (FWHM) ranging from just 15 to 110 arcseconds (see Figure 3). To put those figures in perspective, the typical FWHM specification for a bulk AlN substrate is below 100 arcseconds. Therefore, we can conclude that our MOCVD-grown AlN films – regardless of doping – exhibit excellent crystalline quality that's comparable to or exceeds that of the substrates.

Another encouraging finding is that a range of AlN layers grown in our CIS reactor have FWHM values

below 20 arcseconds. This confirms that both configurations of the Agilis 100 can produce high-quality AlN epitaxial layers.

### Encouraging electrical results

Amongst the various process parameters that influence the quality of AlN films, it is well established that the growth pressure plays a significant role in the activation energy of silicon dopants in AlN. To investigate this effect, we have grown a series of silicon-doped AlN layers in the RIS MOCVD reactor by systematically varying the growth pressures.

Our study revealed a clear trend: at standard pressures, often around 20 Torr as typically used by other researchers, AlN films exhibit relatively low free carrier concentrations in the  $10^{15} \text{ cm}^{-3}$  range, while Hall mobilities can exceed  $30 \text{ cm}^2 \text{ V}^{-1} \text{ s}^{-1}$ . In sharp contrast, films grown under lower pressures show significantly enhanced carrier concentrations, ranging from  $1.3 \times 10^{16} \text{ cm}^{-3}$  to  $4.4 \times 10^{16} \text{ cm}^{-3}$  – more than an order of magnitude higher than values usually reported for silicon-doped AlN [3].

According to SIMS measurements, the silicon doping concentrations in these low-pressure films remain in the low  $10^{18} \text{ cm}^{-3}$  range. Comparison of these doping levels with the corresponding free-carrier concentrations reveals activation efficiencies exceeding 1.5 percent under the lowest growth pressure conditions, representing a substantial improvement over films grown at standard pressures.

The exact mechanism behind enhanced activation is unclear. One plausible explanation is that low-pressure growth drives the system away from thermodynamic equilibrium, thereby suppressing the

► Figure 3. High-resolution X-ray diffraction rocking curves for the (0002) reflection of AlN films grown on native substrates using the RIS reactor. The layers were grown under varying growth conditions: (a) unintentionally doped AlN layer grown using a V/III ratio of 100, (b) a doped AlN layer grown using a V/III ratio of 100, (c) a doped AlN layer grown using a V/III ratio of 3000, and (d) a doped AlN layer grown using a V/III ratio of 1500.

formation of silicon-related DX centres and enhancing dopant activation. Under these non-equilibrium conditions, the chemical potential of the film can be altered, influencing the formation energies and concentrations of compensating point defects.

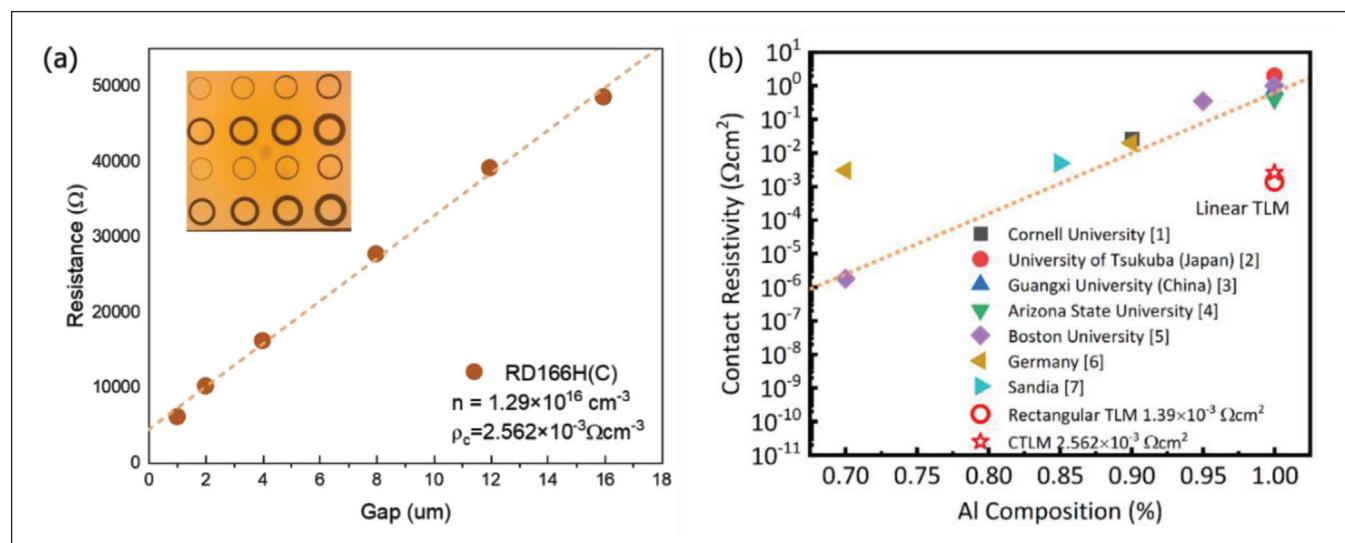

To evaluate the electrical contact quality of our AlN layer grown at low pressures, we have collaborated with Houqiang Fu's team at Arizona State University. Fu and his colleagues have fabricated circular transfer-length measurement structures and determined a contact resistivity of  $2.56 \times 10^{-3} \Omega \text{ cm}^2$  (see Figure 4). This is an impressive figure, as typical AlN contact resistivities range from 0.1 to  $100 \Omega \text{ cm}^2$  [4-6].

Further evidence of the merit of low-pressure growth for good electrical contacts comes from rectangular transfer-length measurement structures, processed

► Figure 4. (a) Extracted resistance versus gap spacing from circular transfer-length measurements with data corrected for pad geometry. (b) Benchmark comparison of contact resistivity, with the red star and circle representing results from AlN samples grown at Agnition Technology. References: [1] Appl. Phys. Express **15** 061007 (2022); [2] Appl. Phys. Express **16** 064005 (2023); [3] Cryst. Growth Des. **24** 3960 (2024); [4] Appl. Phys. Express **17** 074001 (2024); [5] Appl. Phys. Lett. **90** 062115 (2007); [6] Photon. Res. **8** 1381 (2020); [7] Phys. Status Solidi A **214** 1600842 (2017).

| AlGaN: Si layers                        | n (cm <sup>-3</sup> ) | $\mu$ (cm <sup>2</sup> /Vs) | $\rho$ (mΩ.cm) | Reactor type used       |

|-----------------------------------------|-----------------------|-----------------------------|----------------|-------------------------|

| Al <sub>0.75</sub> Ga <sub>0.25</sub> N | 1.1×10 <sup>19</sup>  | 33.0                        | 17.6           | RIS                     |

| Al <sub>0.77</sub> Ga <sub>0.23</sub> N | 4.5×10 <sup>18</sup>  | 72.3                        | 19.1           | RIS                     |

| Al <sub>0.77</sub> Ga <sub>0.23</sub> N | 1.2×10 <sup>18</sup>  | 96.8                        | 18.6           | CIS                     |

| Al <sub>0.75</sub> Ga <sub>0.25</sub> N | 9.8×10 <sup>18</sup>  | 24.0                        | 27.0           | C. E. Quiñones et al[3] |

| Al <sub>0.83</sub> Ga <sub>0.16</sub> N | 2.8×10 <sup>18</sup>  | 23.3                        | 94.8           | RIS                     |

► Table 1. Electrical properties of silicon-doped AlGaN layers with a high aluminium content (around 75–84 percent), grown using RIS and CIS MOCVD reactors. The table summarises the free-carrier concentration (n), electron mobility ( $\mu$ ), and resistivity ( $\rho$ ) of each sample. For comparison, representative best values reported in the literature are included.

without mesa isolation. In this case, contact resistivity is even lower:  $1.39 \times 10^{-3} \Omega \text{ cm}^2$ . Taken together, these results highlight the promise of low-pressure MOCVD growth for realising high-activation-efficiency, low-resistivity silicon-doped AlN layers [7].

As is the case for AlN, with its related alloy AlGaN, it is hard to realise a high conductivity when the aluminium content is high, due to dopant compensation. But success is possible, and through careful optimisation of the growth process in our Agilis 100 MOCVD reactor with CIS and RIS showerheads, we have demonstrated highly conductive silicon-doped AlGaN films with aluminium compositions exceeding 75 percent. For films with an aluminium mole fraction of 75–80 percent, we consistently realise resistivities below  $25 \text{ m}\Omega \text{ cm}$  (see Table 1) – that's significantly lower than literature values [3]. The corresponding carrier concentrations are up to  $1.1 \times 10^{19} \text{ cm}^{-3}$ , and mobilities can be as high as  $97 \text{ cm}^2 \text{ V}^{-1} \text{ s}^{-1}$ .

Drawing on our optimised growth conditions for high-aluminium-content AlGaN, in combination with our low-pressure AlN growth that yields a free-carrier concentration of  $1.3 \times 10^{16} \text{ cm}^{-3}$ , we have partnered with the team at Arizona State University to produce a Schottky barrier diode structure. To ensure smooth band alignment between AlN and AlGaN layers, this heterostructure incorporates a graded AlGaN transition layer, effectively minimising the conduction band discontinuity at the interface.

► Figure 5.

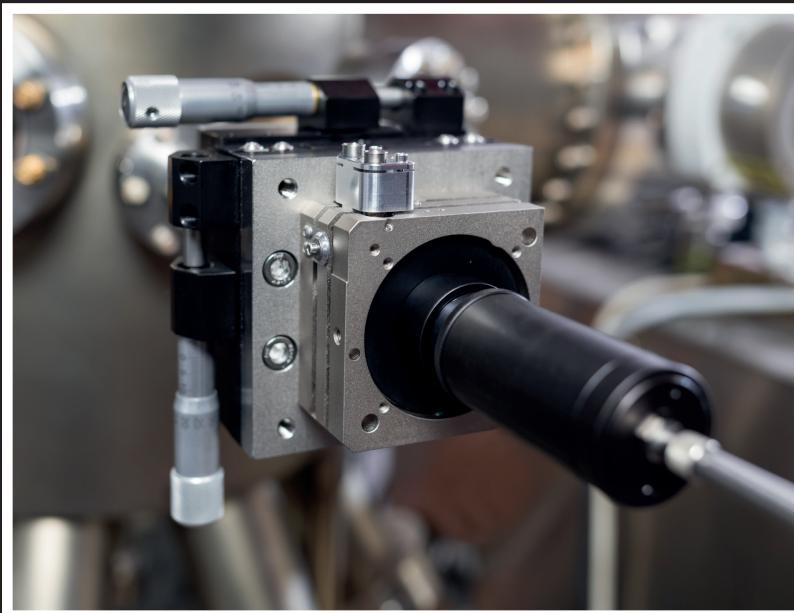

An RIS

reactor with

UV exposure

capability.

Our diodes deliver excellent electrical performance. Plots of current-voltage reveal a current density exceeding  $4 \text{ kA cm}^{-2}$  at 20 V. Using this data, we have calculated that the specific on-resistance is below  $20 \text{ m}\Omega \text{ cm}^2$  at  $+15 \text{ V}$  [7]. These results are particularly remarkable, given the wide bandgap nature of AlN. They underscore the viability of our epitaxial processes for high-performance vertical diode applications.

### UV-assisted growth of AlN

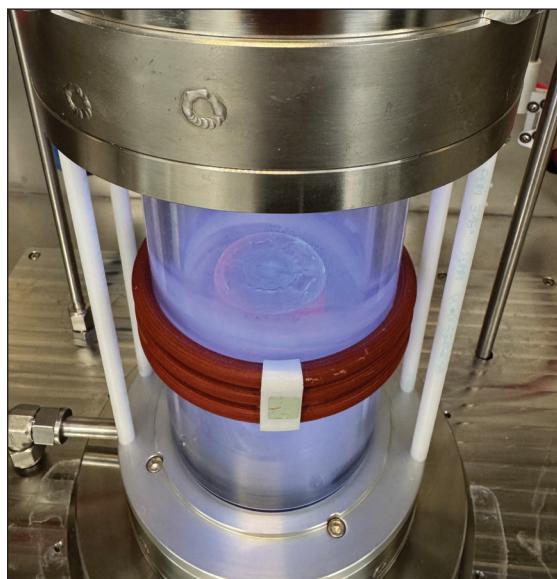

We have also investigated the benefits of applying UV light during growth, an addition that suppresses compensating point defects in AlN. For this effort, we developed a new-generation RIS for the Agilis 100 reactor (see Figure 5). Designed from the ground up, this new showerhead incorporates UV light from either deuterium or Hg-Xe lamps. Switching between these sources is easy, with selection based on employing the most suitable spectral range for optimal defect control.

Constructed using US Patents 12,011,764 B1 and 12,337,388 B2, along with other proprietary technologies, our showerhead features a port for a fibre optic cord. With this approach, UV light is delivered through a single ultra-precise UV viewport, ensuring minimal distortion and losses, without the need for a light pipe. UV light entering the growth chamber is uniformly distributed across a 2.3-inch OD wafer carrier via a carefully engineered funnel, developed to ensure perfect coverage while minimising space within the showerhead and preserving gas dynamics and precursor delivery. Fully interchangeable with legacy Agilis 100 and Agilis Mini systems, our innovative design allows existing users to upgrade seamlessly, maintaining our commitment to scalable, high-performance MOCVD hardware for advancing ultra-wide bandgap materials, such as AlN.

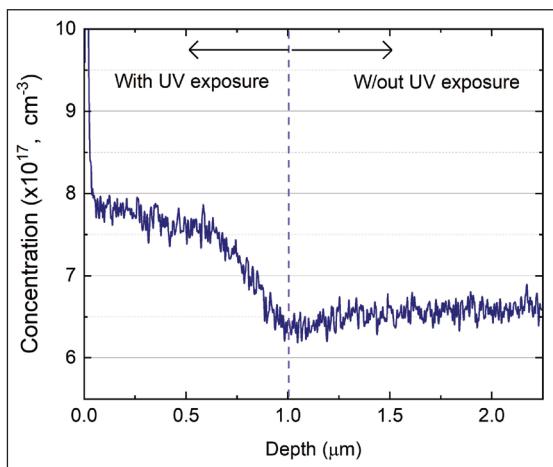

To evaluate the effect of UV illumination on silicon incorporation in AlN, we have grown a  $2 \mu\text{m}$ -thick silicon-doped film of this nitride on an AlN substrate. For this investigation we grew the layer in two segments in the same MOCVD run: the first  $1 \mu\text{m}$  without UV exposure, and the second  $1 \mu\text{m}$  with UV exposure.

According to SIMS, UV exposures increase the silicon concentration. In this AlN sample, UV exposure causes the silicon concentration to rise by almost 20 percent from  $6.5 \times 10^{17} \text{ cm}^{-3}$  to  $7.7 \times 10^{17} \text{ cm}^{-3}$ .

► Figure 6. SIMS depth profiles showing silicon concentration in AlN layers grown using the RIS reactor with and without UV exposure. UV illumination during growth resulted in approximately a 19 percent increase in silicon incorporation compared to the non-UV-exposed region.

To assess the electrical impact of our UV-assisted growth, we have grown additional single-layer silicon-doped AlN films, both with and without UV exposure, and characterised them with Hall-effect measurements. We found that UV exposure increases the carrier concentration from around  $8.0 \times 10^{14} \text{ cm}^{-3}$  to  $1.3 \times 10^{15} \text{ cm}^{-3}$ , produces a slight reduction in electron mobility from around  $107 \text{ cm}^2 \text{ V}^{-1} \text{ s}^{-1}$  to  $90 \text{ cm}^2 \text{ V}^{-1} \text{ s}^{-1}$ , and ultimately trims resistivity from around  $65 \Omega \text{ cm}$  to  $55 \Omega \text{ cm}$ . The upshot is enhanced conductivity, driven by a higher free-electron concentration. Separately, a silicon-doped AlN layer grown without UV achieved a mobility of more than  $120 \text{ cm}^2 \text{ V}^{-1} \text{ s}^{-1}$  mobility with an electron concentration of around  $4.3 \times 10^{14} \text{ cm}^{-3}$ .

These results show that UV-assisted MOCVD growth effectively enhances silicon incorporation in AlN films, and improves electrical conductivity. This significant benefit comes with a slight reduction in mobility, probably due to either modified defect dynamics or increased scattering, associated with the altered growth environment.

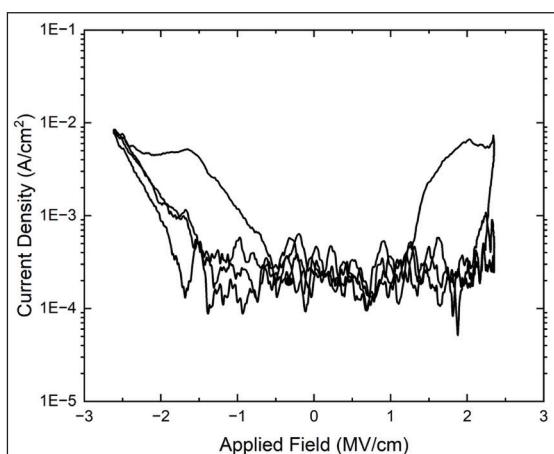

### Ferroelectric AlScN films

Over the last few years, we have extensively utilised our R&D MOCVD reactor for the growth of high-quality thin films of AlScN. At first our primary goal was to explore the growth of AlScN using  $\text{Cp}_3\text{Sc}$ , which was the most widely used precursor at the time. But this state-of-affairs has recently changed, and now we are evaluating the growth of AlScN using ASGARD, an alternative scandium precursor offering many advantages compared with  $\text{Cp}_3\text{Sc}$ . Unlike  $\text{Cp}_3\text{Sc}$ , which stays solid up to  $240^\circ\text{C}$ , ASGARD is liquid at room temperature and thus provides the higher vapour pressure needed for efficient scandium delivery to the reactor. This allows for faster growth rates and improved consistency.

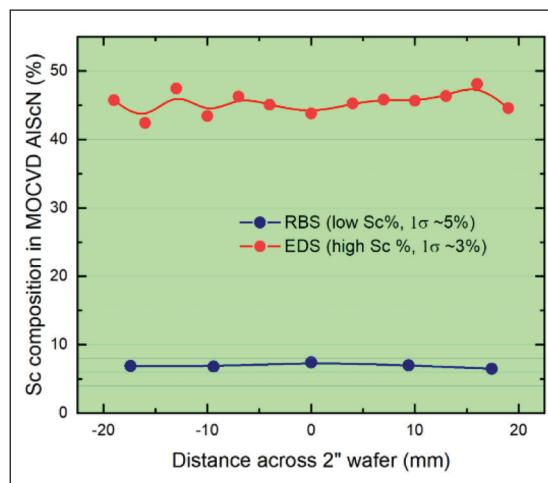

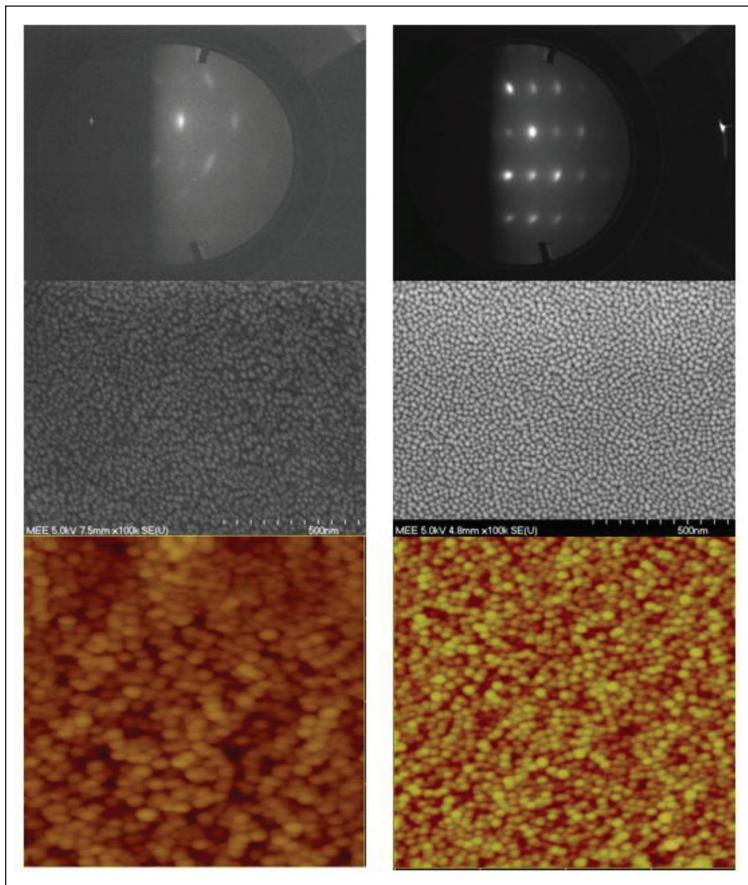

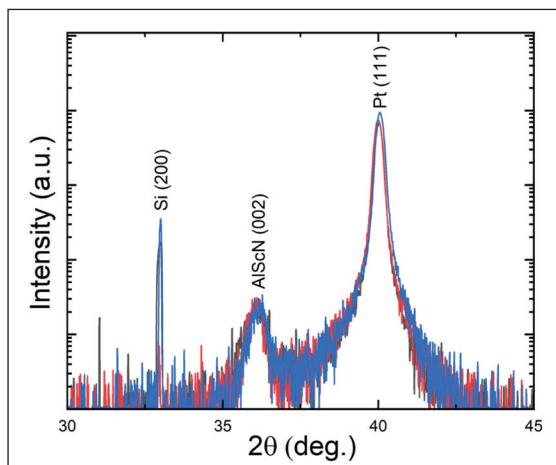

To address the notoriously low vapour pressure of scandium precursors, we have developed a fully integrated high-temperature delivery module for our Agilis platforms. This module couples a dedicated, heat-traced gas panel – it's capable of maintaining precursor lines, mass-flow controllers, and valves at up to  $150^\circ\text{C}$  – with our third-generation CIS, which features coolant channels and a flange rated for sustained operation above  $130^\circ\text{C}$ . Strengths of this combination include the elimination of cold spots, preventing precursor condensation, and the delivery of a stable, perfectly metered scandium flux directly into the growth zone.