# COMPOUND SEMICONDUCTOR

CONNECTING THE COMPOUND SEMICONDUCTOR COMMUNITY

VOLUME 29 ISSUE VIII 2023

COMPOUNDSEMICONDUCTOR.NET

### **INSIDE**

News, Analysis, Features, Editorial View, Research Review and much more

### Field-emission transistors

III-Nitride field-emission vacuum transistors unlock the door to compact circuits delivering high powers at high frequencies

### Chiral light from topological LEDs

Strong magnetic fields during crystal growth enable LEDs to transfer chirality from electrons to photons

### Improving SiC process control

Makers of SiC power devices produce better transistors when they adopt infrared spectroscopy and picosecond ultrasonics

### What's Your Next Big Thing?

- Micro LED Displays

- Autonomous Driving / 3D Sensing

- Communication Infrastructure

- Solar Cells

• ...

## G10-AsP

The Enabling MOCVD Solution

## Fully Automated MOCVD for High Volume Production of GaAs/InP Based Materials

## **VIEWPOINT**

By Richard Stevenson, Editor

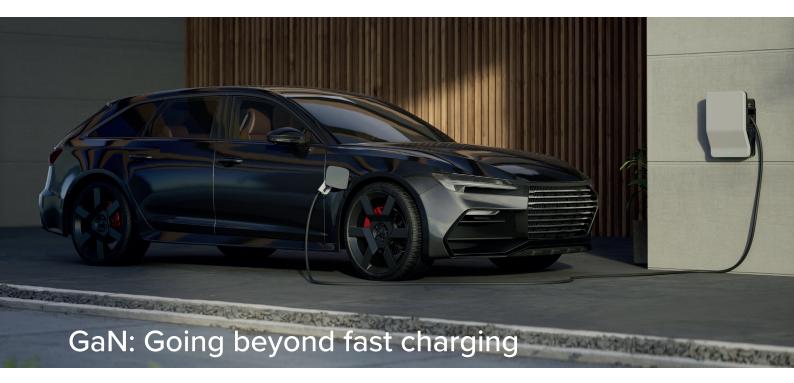

### GaN's next killer application

MANY compound semiconductors can barely boast of one killer application. GaN, though, already counts four, and more will surely follow.

For this particular material, the first three killer apps were associated with the LED. Backlighting the keypads and screens of mobiles spawned the first of the multi-billion-dollar markets, with similar levels of success following from the backlighting of a variety of screens, and then the dominance of the light bulb. In all these markets, manufacturers that pushed the performance boundaries got their first, and were rewarded with high margins. But as time went on and more chipmakers fulfilled the specifications, competition squeezed prices, ultimately leading to commoditisation.

It's a similar story for GaN transistors in fast chargers, the first killer app for this material in power electronics. As well as generating revenue, success in this market has provided a great opportunity for promoting the strengths of this GaN power transistor far beyond its pioneers. However, competition is now fierce, with little profit to be made. Illustrating just how entrenched this form of transistor is in fast charging, it's now even deployed in hybrid toys and chargers, such as those launched this summer by GravaStar to coincide with a world-wide release of the movie *Transformers: Rise of the Beasts*.

So where will the next killer applications for GaN come from? It's hard to predict, but there are a few leading contenders. On the optoelectronics side are displays based on the microLED, which are sure to feature GaN emitters; and in the power arena, GaN is tipped to win substantial business in the growing market for electric vehicles, and possibly in inverters supporting the distribution of energy from renewables.

Interest in microLEDs has been strong for quite a few years, but commercialisation, at least on a large scale, is still some way off. What's needed is the development of simpler manufacturing processes that don't compromise

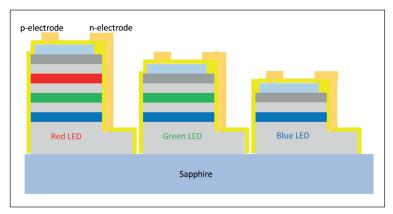

yield. Offering promise on that front is the three-in-one microLED that's being pioneered by engineers at Toyoda Gosei. Development of this device has involved the growth of a GaN-based epitaxial stack on sapphire that features quantum wells emitting in the red, green and blue (see p. 52). Through a combination of etching and localisation of carriers, that team has realised red, green and blue emission, and ultimately a wide colour gamut. However, the efficiency of the red and blue emission is a concern – increasing this in the blue should be possible by improving the etching process, but the pathway for a higher efficiency in the red is far from clear.

For the makers of GaN power devices, the upcoming opportunities involve more strenuous

operating conditions than those required for fast chargers, such as higher powers and more varied operating temperatures. To fulfil these requirements, Navitas has launched a new range of GaN ICs, known as GaNSafe, discussed in an interview starting on page 14. Will it spawn another killer app for GaN? Who knows, so stay tuned to find out about its future, along with that of the microLED.

Free weekly e-news roundup go to: compoundsemiconductor.net

### 22 Efficient enlargement of bulk AlN

Introducing expansion angles in excess of 45 degrees can slash the time it takes to realise bulk AIN grown by physical vapour transport with industrially relevant crystal diameters

### 28 The road to SiC process control

Manufacturers of SiC power devices produce better transistors when they turn to metrology techniques involving Fourier transform infrared spectroscopy, optical critical dimension and picosecond ultrasonics

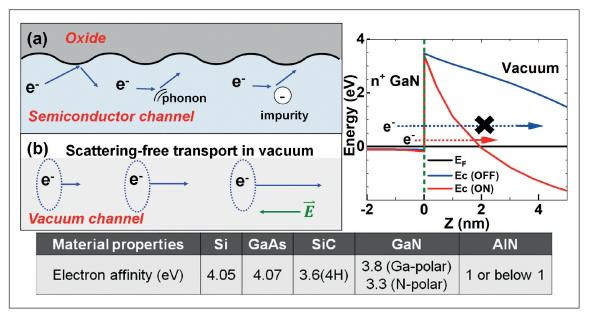

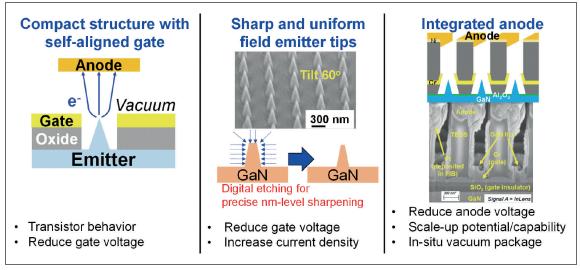

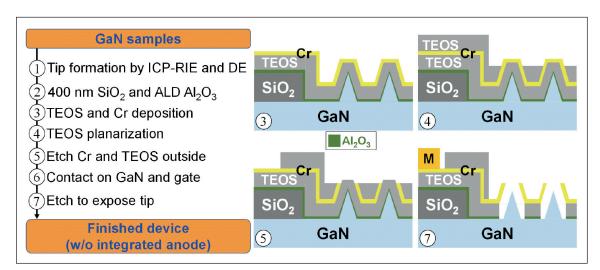

### 38 III-Nitride field-emission vacuum transistors

Field-emission transistors featuring III-Nitrides unlock the door to robust, compact vacuum-electronics-based circuits that deliver high powers at high frequencies

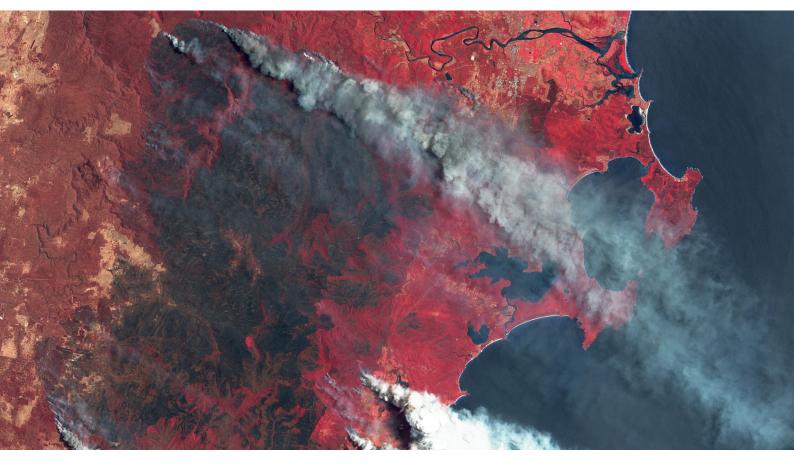

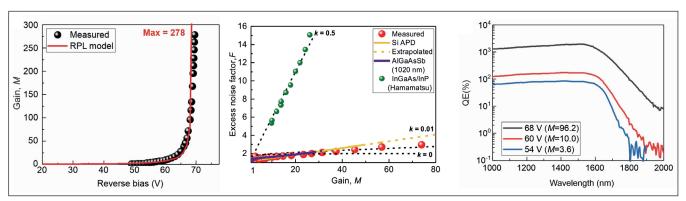

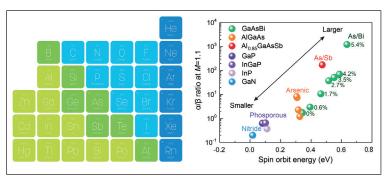

### 44 Antimonides enhance avalanche photodiodes

Turning to antimonides for the fabrication of avalanche photodiodes delivers high gain in the infrared, while quashing excess noise

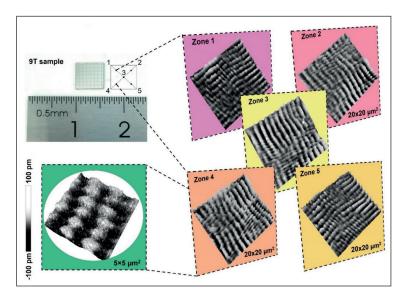

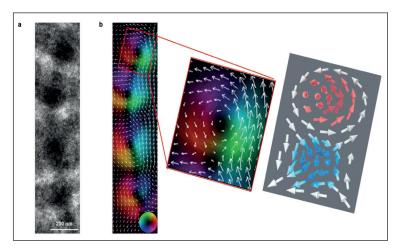

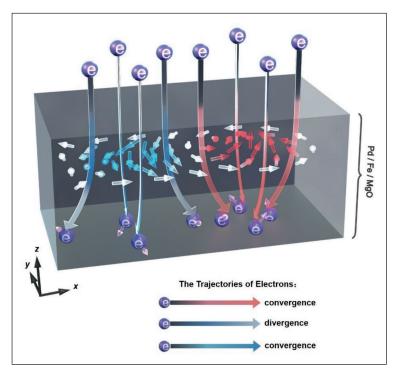

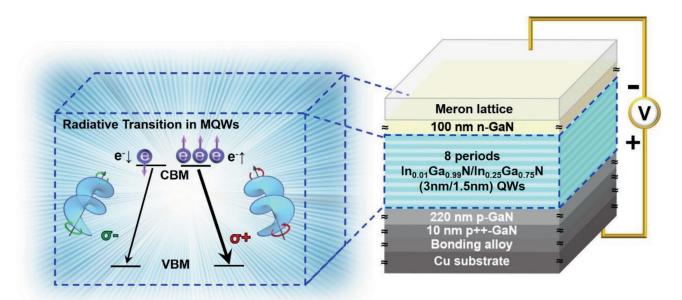

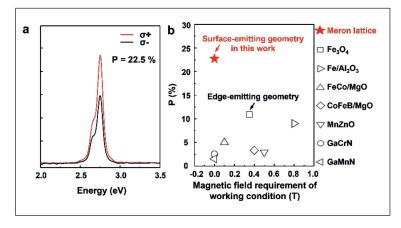

### 48 Realising chiral emission with topological LEDs

Applying strong magnetic fields during crystal growth enables the fabrication of LEDs that transfer chirality from electrons and photons

#### **NEWS ANALYSIS**

### 14 Going beyond fast charging

Navitas has introduced a range of GaNSafe ICs to expand its sales into electric vehicle, solar and data-centre markets

### 16 PowerAmerica powers on

Five years of additional funding will swell domestic production of SiC and GaN power devices

#### RESEARCH REVIEW

- 52 The three-in-one microLED

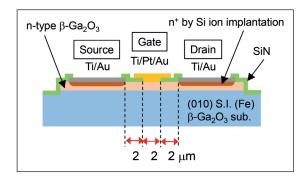

- **53** Mist epitaxy of β- $Ga_2O_3$  devices

#### **NEWS**

06 Indian team makes home-grown GaN power switch

> Nexperia partners with Kyocera AVX on 650 V SiC rectifier module

- **07** £300k award for Quinas ULTRARAM

- 08 Denso and Mitsubishi invest \$1billion in Coherent's SiC business

- **09** Yuanjie Semiconductor to supply lasers to POET

- 10 Germany commits to Ams Osram funding

Steady growth for power electronics

- 11 GF awarded \$35 million to accelerate GaN plans

- 12 J2 to build Hong Kong's first 8-inch SiC fab

GaN Systems co-founder joins QPT

Editor Richard Stevenson richardstevenson@angelbc.com +44 (0)1291 629640

News Editor Christine Evans-Pughe christine.evans-pughe@angelbc.com

**Design & Production Manager**Mitch Gaynor

mitch.gaynor@angelbc.com +44 (0)1923 690214 **Director of Logistics** Sharon Cowley sharon.cowley@angelbc.com

+44 (0)1923 690200

Senior Sales Executive

Jacob Caulfield

jacob.caulfield@angelbc.com +44 (0)2476 718979

Marketing & Logistics Executive Eve O'Sullivan

+44 (0)2476 823 123 eve.osullivan@angelbc.com Circulation Scott Adams

scott.adams@angelbc.com

**Publisher** Jackie Cannon jackie.cannon@angelbc.com +44 (0)1923 690205

USA Representatives

Brun Media

Janice Jenkins jjenkins@brunmedia.com +1 724-929-3550 Tom Brun tbrun@brunmedia.com +1 724 539-2404

Chief Executive Officer

Sukhi Bhadal

sukhi.bhadal@angelbc.com +44 (0)2476 718970

Chief Technical Officer Scott Adams

scott.adams@angelbc.com +44 (0)2476 718970 Directors

Jackie Cannon, Sharon Cowley

Published by

Angel Business Communications Ltd 6 Bow Court, Fletchworth Gate, Burnsall Road, Coventry CV5 6SP, UK. T: +44 (0)2476 718 970 E: info@angelbc.com

Compound Semiconductor is published nine times a year on a controlled circulation basis. Non-qualifying individuals can subscribe at: £105.00 per annum (UK), €158 per annum (Europe), \$198 per annum (air mail) (USA). Cover price £4.50. All information herein is believed to be correct at time of going to press. The publisher does not accept responsibility for any errors and omissions. The views expressed in this publication are not necessarily those of the publisher. Every effort has been made to obtain copyright permission for the material contained in this publication. Angel Business Communications Ltd © Copyright 2023. All rights reserved. Contents may not be reproduced in whole or part without the written consent of the publishers. The paper used within this magazine is produced by chain of custody certified manufacturers, guaranteeing sustainable sourcing. US mailing information: Compound Semiconductor, ISSN 1096-598X, is published 9 times a year, Jan/Feb, March, April/May, June, July, August/September, October, November, December by Angel Business Communications Ltd, Unit 6, Bow Court, Fletchworth Gate, Burnsall Rd, Coventry CV5 659. UK.Airfreight and mailing in the USA by agent named World Container INC 150-15, 183rd St, Jamaica, NY 11413, USA. Periodicals Postage Paid at Brooklyin, NY 11256. POSTMASTER: Send address changes to Compound Semiconductor, Air Business Ltd, c/o World Container INC 150-15, 183rd St, Jamaica, NY 11413, USA. We strive for accuracy in all we publish; readers and contributors are encouraged to contact us if they recognise an error or omission. Once magazine edition is published Jonline, in print or both), wed not update previously published articles to align old company names, branding, marketing efforts, taglines, mission statements or other promotional verbiage, images, or logos to newly created or updated names, images, typographic renderings, logos (or similar) when such references/images were accurately stated, rendered or displayed at the time of the original publication. When

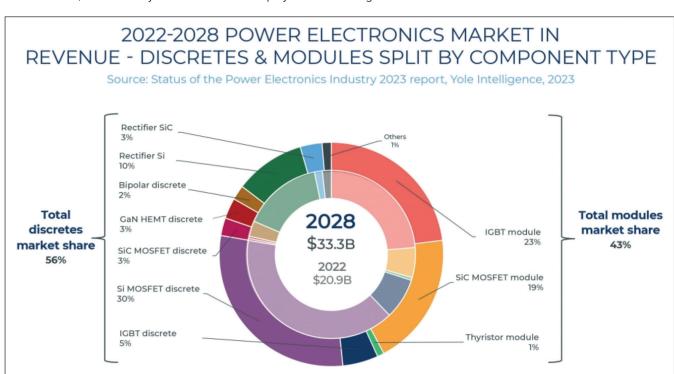

### Steady growth for power electronics

Total power electronics market expected to grow to \$33.3 billion by 2028, according to Yole

RENEWABLES, increased efficiency, and government regulations for different segments will driving steady growth of around 8 percent for power electronics over the next five years, according to Yole Intelligence's annual power electronics report, Status of the Power Electronics Industry 2023.

In 2022, the total power electronics market was worth \$20.9 billion, including discretes and modules. Yole expects it to grow to \$33.3 billion by 2028.

Worth \$14.3 billion in 2022, the discrete market is expected to reach \$18.5 billion by 2028. The main applications driving this growth are xEV, DC charging infrastructure, and automotive.

Consumer remains the largest market for discrete devices even if it is in decline.

In parallel, the module market is pushed by xEV and renewables applications. It includes both photovoltaic and wind. According to Yole Intelligence, this market should reach \$14.8 billion by 2028. The top three companies remain the same as the previous year: Infineon Technologies, Onsemi, and STMicroelectronics, who show significant SiC revenue boosts.

Ana Villamor, team lead analyst, power electronics at Yole Intelligence said: "The power device market is split into three different materials: silicon, SiC, and GaN. Without doubt, silicon is the major part of this market, though SiC is gaining momentum. At Yole Intelligence, we see the growing demand for modules for xEV. In parallel, GaN's main application will continue to be consumer power supplies."

In the long term, total wafer production is increasing alongside the growing power electronic device demand from renewables, automotive and industrial applications. To meet this demand, silicon wafers for power applications will grow to about 47 million 8-inch equivalent wafers per year. Meanwhile, wafer players are focusing on 12-inch.

SiC's transition to 8-inch is taking place, and in the coming years, this will take a greater share of the market.

Today, China is the largest buyer of power components, followed by Asia/ Pacific and Europe. New growth areas, previously less active in semiconductor manufacturing, are found where major companies are investing to supply Asia, other than China, such as Malaysia, Vietnam, and Singapore.

At the device level, the top manufacturers are pushing the three different device technologies: silicon, GaN, and SiC. "We have noticed that a few players pushing GaN have stepped back on R&D to wait for a market increase before investing further, such as Onsemi and Alpha and Omega," adds Villamor.

From the manufacturing side, China remains the leader in investments for manufacturing expansion in 300 mm, as well as in 200 mm and 150 mm.

### £300k award for Quinas ULTRARAM

Lancaster University spinout gets funding to commercialise compound semiconductor memory

LANCASTER UNIVERSITY spinout company Quinas Technology has been awarded £300,000 from Innovate UK to commercialise the universal compound semiconductor-based computer memory ULTRARAM.

ULTRARAM is described as combining the best properties of DRAM and flash into a single device. It is fast, non-volatile, has high endurance and is orders of magnitude more energy efficient than other memory technologies. It achieves these properties by harnessing a quantum mechanical process called resonant tunnelling.

In a paper ULTRARAM: A lowenergy, high-endurance, compound semiconductor memory on silicon, published in Advanced Electronic Materials (2022), the team described implementing ULTRARAM on a silicon substrate; a vital step toward costeffective mass production.

The ULTRARAM outlined in this paper uses InAs quantum wells and AISb barriers to create a triple-barrier resonant-tunnelling structure. The 2.1 eV conduction band offset of AISb with respect to the InAs that forms the floating gate and channel provides a barrier to the passage of electrons that is comparable to the SiO<sub>2</sub> dielectric used in flash memory. However, inclusion of two InAs quantum wells (of different thicknesses) ensures transparency to electrons when a low voltage (around 2.5 V) is applied, due to resonant tunnelling.

By using the triple-barrier resonanttunnelling heterostructure as the barrier between floating gate and channel, rather than the usual monolithic material, the paper authors say that a charge-based memory with extraordinary properties can be achieved. The memories showed clear 0/1 logic-state contrast after around no more than 10 ms duration program/ erase pulses of about 2.5 V.

Furthermore, the Quinas team found that the combination of low voltage and small device capacitance per unit area resulted in a switching energy orders of magnitude lower than DRAM and flash, for a given cell size.

Extended testing of the devices revealed retention in excess of 1000 years and degradation-free endurance of over 10<sup>7</sup> program/erase cycles, surpassing recent results for similar devices on GaAs substrates.

The inventor of ULTRARAM is Manus Hayne, professor of the Physics Department at Lancaster University and chief scientific officer at Quinas.

He said: "This is a significant first step for a newly formed company and has fired the starting gun in the race to commercialise ULTRARAM, but it will be a marathon, not a sprint. We look forward to tackling the challenges that lie ahead."

The award from the UK's national innovation agency follows the completion of the intensive and highly competitive ICURe programme, which is designed to validate the commercial viability of leading-edge science and aid spinout formation.

Quinas' CTO, Peter Hodgson, who led the ICURe submission, said: "The funding will allow us to demonstrate the performance of the memory devices at near-state-of-the-art feature sizes and help secure the significant investment required to bring a new technology to market."

### **Advanced Compound Semiconductor** Foundry Services

MOCVD · Fabrication · Testing

Advanced III-V semiconductor solutions for optoelectronics application in the biotechnology, telecommunications, energy, industrial, and security industries.

MasimoSemiconductor.com | 603-595-8900

## Denso and Mitsubishi invest \$1 billion in Coherent's SiC business

#### Coherent to operate the business as an independent subsidiary

COHERENT has announced that Denso and Mitsubishi Electric have agreed to invest an aggregate \$1 billion (\$500 million each) in its SiC business.

The investment will be in exchange for a 12.5 percent non-controlling ownership interest, with Coherent owning the remaining 75 percent. Prior to the completion of the transaction, Coherent will separate and contribute the business to a subsidiary, which will continue to be led by Sohail Khan, Coherent's executive VP, Wide-Bandgap Electronics Technologies.

This SiC subsidiary will enter into longterm supply arrangements with Denso and Mitsubishi Electric that support their demand for 150 mm and 200 mm SiC substrates and epitaxial wafers.

"We are excited to expand our strategic relationships with Denso and Mitsubishi Electric to capitalise on the significant demand for SiC," said Vincent Mattera, Jr., Chair and CEO, Coherent. Mattera added, "After a thorough review of strategic alternatives for our SiC business, we determined that the creation of a separate subsidiary and the strategic investments from Denso and Mitsubishi Electric, two leaders in SiC power devices and modules, is the best path forward to maximise shareholder value and position the business for long-term growth."

According to Mattera, the investments from the strategic partners will be used to accelerate Coherent's capacity expansion plans and help sustain its leadership position, while ensuring the development of a robust and scalable supply for the rapidly growing market for SiC-based power electronics, largely driven by the explosive growth of the global electric vehicle market.

"We are very pleased to establish a strategic relationship with Coherent, which has a world-class track record in SiC wafer manufacturing. Through this investment, we will secure a stable procurement of SiC wafers, which are critical for BEVs, and contribute to the realisation of a carbon-neutral society by promoting the widespread adoption of BEVs," said Shinnosuke Hayashi, president and COO of Denso.

Masayoshi Takemi, executive officer, group president, Semiconductor & Device of Mitsubishi Electric, said: "Demand for SiC power semiconductors is expected to grow exponentially as the global market for electric vehicles increases in line with the transition to a decarbonised world. To capitalise on this trend, we have decided to expand our SiC power semiconductor production capacity, including by constructing a 200 mm wafer plant in the Shisui area of Kumamoto Prefecture."

"We are delighted to strengthen our partnership with Coherent by investing in this new SiC company, which will provide us with a stable supply of high-quality SiC substrates essential for our increased supply capacity," added Takemi.

### Indian team makes home-grown GaN power switch

RESEARCHERS at the Indian Institute of Science (IISc) have developed a home-grown GaN power switch that can have potential applications in systems like power converters for electric vehicles and laptops, as well as in wireless communications. The entire process of building the switch – from material growth to device fabrication to packaging – was developed in-house at the Centre for Nano Science and Engineering (CeNSE), IISc.

"It is a very promising and disruptive technology," says Digbijoy Nath, associate professor at CeNSE and corresponding author of the study published in *Microelectronic Engineering*. "But the material and devices are heavily import-restricted. We don't have GaN wafer production capability at commercial

scale in India yet." The know-how of manufacturing these devices is also a heavily-guarded secret with few studies published on the details of the processes involved, he adds.

To design the GaN power switch, the IISc team used a MOCVD technique developed and optimised over a decade by researchers in the lab of Srinivasan Raghavan, professor and chair, CeNSE.

GaN transistors typically operate in depletion mode – they are on all the time unless a negative voltage is applied to turn them off. But power switches used in chargers and adapters need to work the other way around.

To achieve this operation, the team

combined the GaN transistor with a commercially available silicon transistor to keep the device normally off.

"The packaging of the device was also indigenously developed," explains Rijo Baby, PhD student at CeNSE and first author of the study. After packaging and testing, the team found the device performance to be comparable to state-of-the-art switches available commercially, with a switching time of about 50 nanoseconds between on and off operations.

Going forward, the researchers plan on scaling up the device dimensions so that it can operate at high currents. They also plan to design a power converter that can step up or step down voltages.

### Yuanjie Semiconductor to supply lasers to POET

Collaboration will enable POET's joint venture, Super Photonics Xiamen, to ramp optical engines to high-volume

Canadian PIC company POET Technologies has announced that it is collaborating with Yuanjie Semiconductor Technology (YST), a Chinese supplier of lasers.

The partnership will enable POET's joint venture, Super Photonics Xiamen (SPX), to ramp optical engines to high-volume production using YST's lasers.

POET, SPX and YST will initially collaborate on 100G CWDM4, POET ONE, 100G LR4 and 200G FR4 transmitter products. All the design verifications and reliability testing of the optical engines is complete and all will be released to production this month.

Current module customers for these products include ADVA, Beijing FeiYunYi and Fibertop, along with others whose names have not yet been disclosed.

"As we start ramping production of our optical engines, securing an additional reliable laser source that is well established in the industry with known good quality is of utmost importance to our business," said Suresh Venkatesan, chairman and CEO of POET.

He added: "Our partnership with YST has enabled POET and SPX to deliver reliable, high-performance optical engines to customers. SPX will start production of 100G CWDM4, POET ONE (a 100G single chip TxRx engine), 100G LR4 and 200G FR4 optical engines using YST's directly modulated lasers this month and we expect to extend the collaboration to other products in the future."

Peter Zhang, CEO and chairman of the board at YST said. "Our superior quality lasers and reputation for reliability will complement POET's Optical Interposer technology, which offers a unique and highly adaptable platform to module makers." Zhang added: "We will continue to collaborate with POET on high-speed optical engines while supporting SPX to ramp current products to high volume production."

### Germany commits to Ams Osram funding

Intention to provide IPCEI funding to drive next-generation optoelectronic semiconductor technologies

AMS OSRAM will get substantial public funding from the German federal government and the Free State of Bavaria to boost the further development of semiconductor technology. The envisaged IPCEI funding (Important Project of Common European Interest) will support Ams Osram in making its own investments in the research and development of optoelectronic components at its Regensburg location.

The subsidy is thought to be more than €300 million, which will be mainly invested in activities for the research and development of optoelectronic semiconductors and their manufacturing processes, creating 400 new high-tech jobs. In addition, Ams Osram will invest in new clean room and laboratory facilities for research, development and pilot production for working on applications such as UV-C LEDs for disinfection and

near-infrared emitters for lidar for autonomous driving. Another special focus will be microLEDs.

Automation and Al generally play a major role in Regensburg, enabling Ams Osram to break new ground at its production facilities. The construction of the first pilot assembly line for 8 inch wafer production is currently underway in order to launch the cost-efficient large-scale production of highly innovative microLEDs in the very near future.

"By expanding our development activities in the field of optoelectronic semiconductors, we can create room for innovation and accelerate the time to market for our products", emphasises Aldo Kamper, CEO of Ams Osram.

Hubert Aiwanger, Bavarian Minister of Economic Affairs, stresses: "Ams Osram stands for high tech made

in Regensburg. As the Bavarian state government, we deliberately participate in the financing of this IPCEI project. This is fully in line with our intention to further expand Bavaria as a top international location for the semiconductor industry. Every euro is well invested and will create new jobs in a highly innovative environment."

Ams Osram has been developing semiconductors in Regensburg for 50 years. 2,700 employees currently work at the location.

### Nexperia partners with Kyocera AVX on 650 V SiC rectifier module

NEXPERIA, has announced it has entered into partnership with Kyocera AVX Components (Salzburg) GmbH, an international supplier of advanced electronic components, to jointly produce a new 650 V, 20 A SiC rectifier module for high-frequency power applications ranging from 3 kW to 11 kW power stack designs, aimed at application like industrial power supplies, EV charging stations, and onboard chargers.

This release will represent a further deepening of the existing, long-lasting partnership between the two companies.

Space-saving and weight reduction are the key requirements for manufacturers of the next generation power applications. The compact footprint of this new SiC rectifier module will help to maximise power density, thereby reducing the amount of required board space and lowering the overall system cost.

Thermal performance is optimised using a combination of top-side cooling and an integrated negative temperature coefficient sensor, which monitors the device temperature and provides real time feedback for device or system level prognosis and diagnosis.

This rectifier module has a low inductance package to enable high-frequency operation and it has been qualified to operate with a junction temperature of up to 175 °C.

"This collaboration between Nexperia and Kyocera AVX combines cuttingedge silicon carbide semiconductors with state-of-the-art module packaging

and will allow Nexperia to better serve the market demand for power electronic products which offer exceptionally high levels of power density," according to Katrin Feurle, Senior Director of the Product Group SiC at Nexperia.

She adds: "The release of this rectifier module will represent the first step in what is envisaged as a long-term SiC partnership between Nexperia and Kyocera AVX".

### GF awarded \$35 million to accelerate GaN plans

US funding brings Vermont fab closer to large-scale production of next-generation GaN chips

GLOBALFOUNDRIES has been awarded \$35 million in federal funding from the US government to accelerate the manufacturing of GaN-on-silicon chips at its facility in Essex Junction, Vermont.

With the new funding, awarded by the Department of Defense's Trusted Access Program Office (TAPO), GF plans to purchase additional tools to expand development and prototyping capabilities, moving closer to at-scale 200 mm GaN-on-silicon production.

GF says it also plans to implement new capabilities for reducing the exposure of GF and its customers to supply chain constraints of gallium, while improving the speed of development, assurance of supply and competitiveness of US-made GaN chips. The funding builds on previous collaboration with the US

government – including \$40 million in support from 2020-2022.

GF's facility in Essex Junction, Vermont,

near Burlington, was among the first major semiconductor manufacturing sites in the United States. Today around 1,800 GF employees work at the site.

### J2 to build Hong Kong's first 8-inch SiC fab

Company plans to start volume production in the next couple of years

THE Hong Kong Science and Technology Parks Corporation (HKSTP) has signed an agreement with mainland China-based J2 Semiconductor to set up an R&D Centre at the Hong Kong Science Park, and Hong Kong's first SiC 8-inch wafer fab.

J2 Semiconductor will invest an estimated \$900 million (HK\$6.9 billion) into the project, with plans to start volume production in the next couple of years. It expects to reach annual production capacity of 240,000 SiC wafers in 2028, and create more than 700 job positions in Hong Kong.

Sunny Chai, chairman of HKSTP said, "The plan of establishing J2 Semiconductor's R&D Centre in the Science Park will promote

Hong Kong's R&D and advanced manufacturing capabilities of thirdgeneration semiconductor devices. J2 Semiconductor brings the core technology and expertise to Hong Kong in advanced chip design, fabrication process and semiconductor product development."

J2 Semiconductor mainly provides SiC devices with a focus on automotive, power conversion and communications.

## Midas **OD** Grinder **DRIVING INNOVATION** IN SIC GRINDING The **WEAL** machine for SiC grinding. **Built to** specific needs. VER AND OVER AGAIN. WELDONSOLUTIONS.COM 717-846-4000

### GaN Systems co-founder joins QPT

GEOFF HAYNES, co-founder of GaN Systems and one of the pioneers of GaN technology. is joining UK start-up QPT as an advisor.

QPT's qGaN module solution enables GaN transistors to be run at up to 20 MHz with nanosecond switching to deliver better operational precision. The technology in a variable frequency drive, for example, enables motors to be driven at up to 99.7 percent efficiency at peak load with hardly any decrease in efficiency at lower loads. This overcomes a challenge for conventional designs today, where efficiency can drop off rapidly at lower loads.

Haynes said: "I have been following the progress of QPT's technology with considerable interest. It solves the thermal and RF problems that GaN is now facing that currently form an insurmountable major barrier for the widespread use of GaN in high

power, high voltage, hard switching applications."

He added: "I visited the company's laboratory and was so impressed with its solutions that I am joining the company as an advisor to help them rapidly deploy this technology to the market. With it, GaN can now operate at the high frequencies needed to deliver significant power savings and open up applications worth billions as it provides a far superior performance and efficiency than SiC."

Rob Gwynne, founder and CEO of QPT, added, "We are delighted that Geoff Haynes is coming onboard. He is a world authority on GaN and knows the challenges that it currently faces that limit its use. He immediately understood how our solutions and patents unlock the next phase in the evolution of GaN to become the enabling technology of choice for power electronics."

At Greene Tweed, certainty is our specialty.

For 150 years, we've equipped critical sectors including the semiconductor industry with materials and engineered components that perform — no excuses, no exceptions.

Join our legacy of trusted partnership and innovation. **Visit gtweed.com today**.

Navitas has introduced a range of GaNSafe ICs to expand its sales into electric vehicle, solar and data-centre markets

### BY RICHARD STEVENSON, EDITOR, CS MAGAZINE

IN THE FAST CHARGING of mobile devices GaN found its first killer application. But as is often the case with mass market adoption, phenomenal success has led to lower margins and ultimately commoditisation. So, for the makers of this class of device, efforts must now be directed at developing new products for new applications.

That's the latest strategy of the US-based wide bandgap specialist Navitas Semiconductors, which unveiled its GaNSafe portfolio this September.

Strictly speaking, this fabless firm has also had success in a handful of other consumer applications, with its established range of GaN devices deployed to drive motors in washing machines, hairdryers and vacuum cleaners. "But there has been a glass ceiling into data centre, into solar and into electric vehicles," says Stephen Oliver, Navitas' VP of Corporate Marketing & Investor Relations. He told *Compound Semiconductor* that while the company's previous products excel in efficiency, reliability and quality, they don't meet all the needs for lengthy operation at high powers. "The GaNsafe range breaks through, smashes that glass ceiling, and can now be taken seriously by customers in the high-power areas."

There is a rich heritage behind the GaNSafe portfolio, which today has four parts, each designed

to operate at 650 V and handle up to 800 V. Together spanning the delivery of electrical power between 1 kW and 22 kW, these packaged ICs that are based on Navitas' fourth generation of GaN benefit from three rounds of about one-fifth die shrink compared with the debut range that came out in 2018. Over the intervening years the company has equipped the GaN IC with more features, such as lossless current sensing and 2 kV electrostatic discharge protection. The launch of GaNSafe includes the addition of short-circuit protection and a higher operating temperature.

To enable higher power operation, GaNsafe features refinements to both the IC and its packaging. The three key advances at the chip level are: the introduction of a Miller clamp; a more intelligent approach to handling short-circuits, as well as ensuring overcurrent protection; and an absence of overshoot and undershoot during switching. Note that even a well-designed device, operating in an efficient manner, can run into problems by generating electromagnetic interference (EMI). But with GaNSafe it is possible to reduce any spikes in EMI via external programming.

"That means that the design team doesn't have to do another spin and cross their fingers and hope they found the thing that's making the spike," enthuses Oliver. "You can tune it in in real time."

#### Perfecting the package

Innovation is also seen in the 10 mm by 10 mm package, referred to as TOLL – Transistor Outline Lead-Less. Despite the tremendous functionality of the GaNSafe IC, just four external connections are used, allowing leads to be fused together. This creates what is essentially a solid lump of copper, aiding thermal performance, a particular valuable asset in solar systems that undergo wide variations

in temperature every day.

Navitas has also 'keyed' some of the pins in its GaNSafe design, creating a ridge metal surrounded by plastic. It's a design that ensures a tough joint, aiding the mechanical integrity of the product. Another strength of GaNSafe is that it is better at handling humidity and preventing liquid ingress. "It's a longer path for any humidity to get into the package and destroy it," explains Oliver.

Since the start of this year, about 40 of Navitas' customers have been working with products from the GaNSafe portfolio. These firms include: Enphase, a producer of power inverters for the Solar Industry; and Geely, a maker of power systems for the electric vehicle (EV) market that supplies its products to Volvo's EV off-shoot Polestar, as well as Proton and Lotus.

To help succeed in new markets, Navitas has set up design centres for a data centre power team and an electric vehicle team. Both are staffed with a mix of talent, including experts in devices and those with real-world system knowledge, gained in previous roles outside Navitas. These design teams offer tremendous support to customers, including details for the full bill of materials, circuit diagrams, a PCB layout, and results of tests of EMI, thermal characteristics and efficiency.

One reason why these design teams are needed is that some of the companies that they work with are only just starting to move away from silicon power devices.

"With GaN, we are asking people to go from 50 kilohertz switching for the system to 500 kilohertz-to-a-megahertz, which means that they can't use the same control chip from their favourite provider that they've used for the last 20 years," says Oliver. Navitas can help in this instance, by advising customers about suitable replacement components.

#### Minimising manufacturing costs

To produce its GaN devices, Navitas partners with an undisclosed packaging partner and the world's biggest foundry, TSMC. Some may question

this approach, claiming that it's hard to develop breakthrough technologies with external fabs, while warning that it is risky to depend on partners when there's a need to ramp volume. But Oliver questions both these views, seeing the situation very differently.

"Circuit development has nothing to do with the fab," counters Oliver "It's all about good engineers sitting around the table, having good ideas and making it happen."

And while he agrees that it's vital to have capacity, he argues that the crucial question is whether it is economical to have that capacity. He sees no sense in spending billions on new fabs — as Wolfspeed and Infineon are doing — and points out that there is no need to buy new equipment to make state-of-the-art GaN devices. At TSMC, Navitas' latest ICs are produced on 500 nm equipment around 30 years old.

Fabs with this level of capability are very common, with plenty in the US running silicon products on 6-inch and 8-inch lines at low margins. Retrofitted with a handful of tools, they can produce GaN ICs within a year, a move that is welcome, thanks to the higher margins.

With access to capacity clearly not an issue, and GaN ICs gaining traction in new markets, Navitas looks assured of a successful future.

> Through sourcing and 'keying', GaNSafe ICs deliver a superior thermal performance to their predecessors.

### NEWS ANALYSIS | STRATEGIC INVESTMENT

### PowerAmerica powers on

Five years of additional funding will swell domestic production of SiC and GaN power devices

LATE THIS SUMMER, the US renewed its commitment to accelerating the development and deployment of more efficient power electronics by funding five more years of PowerAmerica, the Department of Energy's first Clean Energy Manufacturing Innovation Institute.

In the first year of this second phase of funding, which will see a shift in a focus from SiC to roughly equal backing of both this class of device and that based on GaN, PowerAmerica is contributing another \$8 million. A call for proposals will soon follow, with projects maintaining the existing formula for funding — that's private funding supporting federal funding, with both contributing 50 percent of costs.

The latest \$8 million builds on \$70 million of initial federal funding in the first phase, alongside combined contributions of \$81 million from member partners, which total 90 and include those from industry, academia and national labs.

Drawing on that total investment of \$151 million, the 196 projects supported by PowerAmerica have been a great success. The 73 projects led by industry, along with 112 led by academia and another 11 fronted by National Energy Labs, have spawned more than ten wide bandgap technologies.

Chris Saldaña, director of the US Department of Energy Advanced Materials and Manufacturing Technologies Office, which is responsible for renewing funding for PowerAmerica, argues that another impressive aspect of PowerAmerica is the relatively high proportion of projects that

have reached commercial status. Note that these projects aren't necessarily directly linked to product commercialisation:

"They are pre-competitive in nature, so commercialisation isn't the immediate goal. You have a group of companies, universities, government organisations that come together to work on problems of importance for us, the clean energy sector."

Highlights of successes so far from PowerAmerica include the creation of a SiC chip pilot line in the US, owned by X-FAB.

"The purchase and process development for that line was done through Power America, and has had a major impact in terms of meeting growing demand for those devices," says Saldaña.

PowerAmerica also supported Wolfspeed's development of 3.3 kV, 6.5 kV and 10 kV MOSFETs. "The 3.3 kilovolt MOSFETs are in production," enthuses Saldaña.

While the first phase focused on SiC, GaN was not neglected. Funding supported the growth of Navitas, which has mushroomed from a start-up to a billion-dollar company listed on the NASDAQ exchange. Growth has come from rocketing sales of GaN ICs for laptop and cell phone power supplies.

Funding from PowerAmerica is also driving the uptake of SiC in heavy vehicles. John Deere has developed a 200 kW, 1050 V DC bus inverter based

#### NEWS ANALYSIS I STRATEGIC INVESTMENT

on SiC that enables 25 percent fuel savings. Cynics might argue that all of these initiatives could have happened without the support of PowerAmerica. But that misses the point.

"The goal of the Manufacturing USA institutes is to supercharge innovation in these technology spaces that we invest in," says Saldaña. And he points out that while individual advances at companies are to be celebrated, it is important to not overlook the collective impact, which is more than the sum of its parts. "We're trying to move the whole sector forward, not necessarily individual companies, individual commercial products."

Growth in domestic production of wide bandgap power electronics is also helping to trim US greenhouse gas emissions. As well as supporting the proliferation of electric vehicles, increased production of SiC power electronics is underpinning the rejuvenation of an electric grid, making it more reliable, more responsive and better at working with renewable energy technologies.

#### Upskilling the workforce

Another major contribution by PowerAmerica is the creation of a highly skilled workforce for producing and deploying wide bandgap power electronics. Efforts have already included STEM programmes for 9,000 students in their last year of school, and the training of more than 400 masters and PhD students.

Having tracked the destinations of these graduates, it is clear that training is providing a great return on investment, with the majority entering and remaining within the wide bandgap power electronics industry.

"When you create this critical mass of activity in an area, they're going to be part of the same community moving forward, and will help to push the mission that they were trained under through the Institute," says Saldaña. Motivated by this success, PowerAmerica is developing training materials, training programmes and certification to support those wanting to further their careers within this sector.

Efforts are also being directed at attracting everyone to this industry. "There's a strong emphasis on diversity, equity, inclusion and accessibility through the Institute," says Saldaña.

Another appeal of working in the US semiconductor industry is its long-term support. That extends beyond PowerAmerica, which will certainly run for the next five years and quite possibly more, to an initiative called Energy Efficiency Scaling for Two Decades. It's a national programme that aims to double the energy efficiency of microelectronics every two years. Success will drive disruptive innovation, giving yet more impetus to America's burgeoning semiconductor industry.

### kSA ICE for MOCVD and MBE

### Real-time Deposition Monitoring

- Real-time temperature, curvature, growth rate, reflectivity, and more

- Custom configured for your chamber geometry

- Plus the best support in the industry

- Learn more by visiting our website: k-space.com

### Empowering electric vehicles with superior SiC

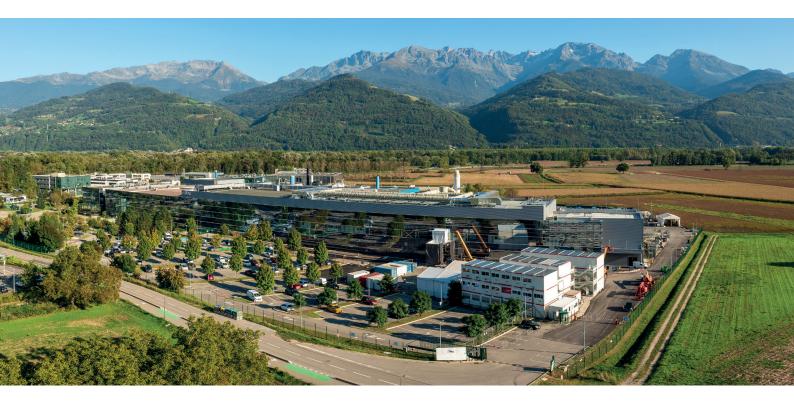

SmartSiC substrates hold the key to ramping volumes of better SiC devices for automotive and industrial applications

### BY EMMANUEL SABONNADIÈRE, CHRISTOPHE MALEVILLE AND CYRIL MENON FROM SOITEC

IN SEPTEMBER 2021, SmartSiC made its debut in *Compound Semiconductor* magazine. Pioneered by our company, Soitec, this novel material technology is a game-changer within the SiC industry: it is enabling a new generation of engineered substrates that consist of a thin layer of single-crystal SiC, bonded on a polycrystalline SiC wafer. Now two years on from this unveiling, SmartSiC is starting to fulfil its potential, delivering impressive results.

The impact of SmartSiC will be colossal. It has fundamentally changed perspectives for SiC, especially for 200 mm acceleration, and it is starting to reshape the SiC industry with a much greener technology. The great strengths of SmartSiC, compared with incumbent single-crystal SiC wafer, include an unparalleled ten-times hike in re-use capability and an eight-fold enhancement in electrical conductivity. Due to these massive improvements in key metrics, SmartSiC is opening new frontiers for high-performance SiC devices and their applications.

As well as these exceptional capabilities at the wafer level, SmartSiC is demonstrating its capability to produce a foundation that ensures better diodes

and transistors. Measurements reveal a reduction in the drain-source on-resistance of 1200 V MOSFETs of between 10 percent and 15 percent, and around a 15 percent decrease in forward-voltage at a rated current in 650 V SiC diodes. These noteworthy improvements in device-level performance translate into a significant advantage in the fabs, with the opportunity for around a 25 percent increase in the number of high-quality die that can be produced from every 200 mm wafer for 25 mm² dies.

Leading the way, STMicroelectronics is the initial adopter of SmartSiC technology. Its collaboration with us has been dedicated to the rigorous automotive qualification of SmartSiC. The ultimate goal for our partnership is to qualify SmartSiC on ST SiC MOSFET technology in mid-2024, with products based on SmartSiC available from Q3 2024 onwards. Meeting this target will position both of us at the forefront of innovation in the EV sector.

Our SmartSiC technology continues to evolve and improve. Recently, we increased the crystal quality of our SmartSiC wafers with a specific epitaxy preparation, realised before the layer transfer of single-crystal SiC. Thanks to this advance, we have

drastically reduced the basal plane dislocation density in our material. In turn, this will lead to better device performance.

This year, SmartSiC became a 'must-have' technology for key leaders in the SiC industry. With over a thousand prototypes under assessment and more than thirty prospects and clients, SmartSiC is now being adopted. High-volume production will take place at our new plant, Bernin4, which opened this September, following the installation of initial industrialisation lines over the summer months. When fully up and running, this fab will have a capacity of 500,000 wafers per year. Note that the production process used in this fab is flexible, starting with 150 mm wafers and adding 200 mm wafers in the first half of 2024. Once the ten-fold re-use goal is attained, another significant advantage will emerge: a secured production process, thanks to reserves of refreshed wafers that we will hold.

To put it succinctly, given all the strengths of SmartSiC, this technology is an obvious choice for any SiC device maker wanting to process 200 mm wafers – and that's before considering current global scarcity of this material.

#### High-volume manufacturing

The unparalleled performance of SmartSiC is not just attracting the attention of makers of SiC power devices. Our technology is also garnering significant attention further along the supply chain, from Tier 1 and OEM companies within the automotive industry. What pleases them is that it will not be long before we attain IATF and ISO9001 certification at Bernin4, aligning with the standards of our other manufacturing plants in Bernin and Pasir-Ris. Note that our company, and our SmartSiC portfolio, are deeply committed to an impressive environmental, social and governance agenda.

High on our agenda when developing our production process is energy efficiency, with much effort directed at reducing energy consumption. Perfectly aligning with this objective, SmartSiC is starting to play a pivotal role in realising substantial reductions in carbon footprint when compared with traditional bulk SiC materials. Such a synergy is vital in supporting the ongoing EV revolution, which is making a crucial contribution to combating climate change. Our company, and SmartSiC, are actively aiding this cause at various levels, from wafer production to power device development and system integration.

Building Bernin4 has not been easy. As well as a supply crisis in construction materials, there's been a flurry of industrial construction projects in the Grenoble region. Yet despite these issues, we have completed the 2000 m² clean room for SmartSiC on time, with just 18 months elapsing from breaking ground to the construction of the first prototypes.

Our state-of-the-art clean room is seamlessly integrated into our pre-existing infrastructure. Due to this, we have established crucial links with Bernin 2 (300 mm silicon-on-insulator wafers), raw materials storage and the finished products warehouse. This strategic connectivity enhances operational efficiency by ensuring optimised flow and maximising flexibility for the facility.

To provide a high-skilled workforce for Bernin 4, we are gradually transferring over operators, technicians and engineers trained on the SmartSiC pilot line at CEA/LETI in Grenoble. These staff are being integrated into the Bernin 4 organisation to manufacture the first industrial prototypes. Bernin 4 benefits from the same digital resources supporting the other plants on the site: a semiconductor manufacturing execution system, a process control system, and manufacturing equipment that's monitored using statistical process control, fault detection and classification, and computerised maintenance management systems. The production line is scheduled to receive ISO 9001 certification by October 2023, and plans are in place to obtain IATF certification in 2024.

### COVER STORY I SOITEC

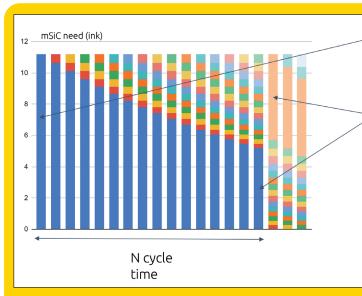

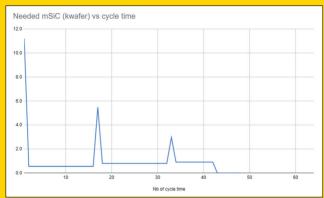

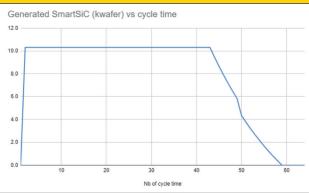

1st cycle time: need to insert a large number of mSiC to create the initial flow

Following cycle time: replace loss

16th cycle time (because 15 refresh): replace the remaining mSiC of the 1st insertion

Following cycle time: replace loss

Targeting a 10,000 SmartSiC production per cycle time with a steep ramp up (permanent regime since the 2nd cycle time), around 11,000 single-crystal SiC substrates are injected for the first cycle time to initially load the line. To compensate for losses linked to yield, for of each following cycles, roughly 600 single-crystal SiC substrates are added per cycle time. Considering a maximum number of refresh of 15x, the first injection of SmartSiC has to be replaced at the 16th cycle time, equating to around 5,000 single-crystal SiC substrates in this example. Losses linked to yield are compensated for in each of the following cycles (roughly 800 single-crystal SiC substrates per cycle time). The graphs show the number of monoSiC substrates injected in the line every cycle time (left) and the number of SmartSiC wafers produced versus cycle time (right). Based on a realistic industrial scenario, we can see that the manufacturing kinetics are such that the number of SmartSiC wafers generated exceeds rapidly the number of single-crystal SiC substrates inserted to reach a factor of 10x across N cycle time.

#### A quick, efficient ramp up

One of the great strengths of our SmartSiC industrial line is that we are able to manufacture more than 10 SmartSiC substrates from a single-crystal SiC substrate.

By adjusting the single-crystal SiC supply volumes, we can deliver a very steep ramp up in the production of SmartSiC substrates. This is accomplished by injecting a larger quantity of singlecrystal SiC from the start of production, to load the line, a point illustrated in Figure 1. Starting with just over 11,000 SiC wafers, we can yield around 10,000 during the first cycle (Figure 1 shows the number of single-crystal SiC wafers present in the line as a function of the cycle time, with the colour indicating the origin of the wafers – in blue, 1st injection; in red, 2<sup>nd</sup> injection; in orange, 3<sup>rd</sup> injection; and so on).

During our industrialisation of SmartSiC, we control ramp up, and then we retain a steady state by adjusting the level of injection of single-crystal SiC substrates in the line. By using single-crystal SiC substrates over N cycle times – an approach that provides a degree of inertia – we ensure a level of resilience, in terms of the number of SmartSiC wafers that we produce, by catering for the possibility of irregularity in the number of single-crystal SiC wafers injected in each cycle

As well as pioneering SmartSiC, we are playing a key role in driving the development of the polycrystalline SiC supply ecosystem. This effort includes a joint-development agreement with Mersen, a renowned French-based company with broad materials expertise. Together we are crafting the most efficient polycrystalline SiC wafers. Our joint strategy is to qualify suppliers across different regions. We have already established long-term contracts with two suppliers and we are actively engaging with a third. Notably, Bernin 4 can accommodate a high degree of flexibility from our suppliers, as this facility allows for a seamless transition between 150 mm and 200 mm wafers.

#### Automotive and industrial markets

Our SmartSiC is targeting markets that are tipped for phenomenal growth. For the Light Vehicles market, worldwide production is forecast to increase at a low-to-mid single digit compound annual growth rate (CAGR) through to 2030. Within this, battery EVs are the dominant driving force, predicted to climb at a CAGR of above 20 percent. Thanks to this rapid growth, the CAGR for SiC modules is 32 percent. In addition, there is a profound shift towards electrification in industrial applications, providing additional opportunities for SmartSiC.

We will quickly penetrate these markets by ramping our production by a factor of ten in just 18 months at our Bernin facility. Our expectation is that by 2030, the SmartSiC share of the SiC market will be higher than 30 percent. The SmartSiC wafer manufacturing process also reduces  $\mathrm{CO}_2$  emissions by 70 percent compared with current monocrystalline SiC substrates.

Our progress aligns with one of our key values, which is contributing to a reduction in climate change. We are deeply committed to environmental, social and governance performance, with considerable effort directed at reducing water and energy consumption, as well as minimising waste. Moreover, our strategic SiC programme that led to the development of SmartSiC involved a strong commitment to greener values, while delivering superior results compared with bulk SiC.

### Efficient enlargement of bulk AIN

Introducing expansion angles in excess of 45 degrees can slash the time it takes to realise bulk AIN grown by physical vapour transport with industrially relevant crystal diameters

### BY CARSTEN HARTMANN AND THOMAS STRAUBINGER FROM THE LEIBNIZ INSTITUTE FOR CRYSTAL GROWTH

THE ULTRA-WIDE band gap semiconductor AIN, as well as its ternary cousin AlGaN, has a number of attributes that make this material system a promising one for electronic and optoelectronic devices. This class of nitrides can withstand harsh conditions and high temperatures, and thanks to the very wide bandgap, can be used to make LEDs that emit in the deep and far UVC. The largest markets for such devices, which span 220 nm to 280 nm, are the disinfection of drinking water and waste water treatment. However, emission in this spectral range can also be deployed for surface sterilisation and bio-chemical sensing. As well as these opportunities in deep-UV photonics, AIN-based devices are compelling candidates for next-generation highfrequency power-conversion. Already, AIN-based high-power transistors are outperforming those made from the two most common wide bandgap semiconductors, SiC and GaN.

Due to a lack of native substrates, researchers exploring the capability of AIN and its alloys began by using sapphire substrates for the development of epitaxial layers. However, even when they turned to complex processing steps, the threading dislocation densities in the AIGaN layers remained high – typically in excess of 1 x 108 cm<sup>-2</sup>. The high density of these threading dislocations is one of the primary reasons why the potential of the AIN material system is yet to be fully exploited.

#### The power of PVT

Offering a promising way forward is the growth of AIN crystals by Physical Vapour Transport (PVT). In recent years, this approach to the growth of AIN with a high degree of crystallinity has advanced significantly, laying the foundation for substantial improvements in device performance. Successes include the fabrication of electrically injected

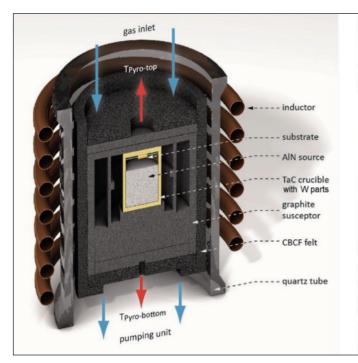

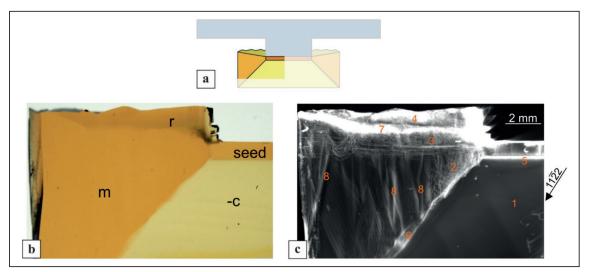

Figure 1. (a) A sketch of the setup, with four identical PVT reactors built at IKZ. (b) one shown here with opened housing for a better view of the heated setup. For more details see C. Hartmann et al. Cryst. Eng. Comm. 18 3488 (2016).

deep-UV laser diodes and LEDs with high output power over long lifetimes.

Pioneers of AIN substrates produced by PVT include Hexatech Inc., which has introduced AIN substrates with diameters of up to 2 inches and threading dislocation densities below 1 x 10<sup>4</sup> cm<sup>-2</sup>. Hexatech is offering this material to selected scientific partners.

Another provider is Crystal IS, which demonstrated 4-inch AlN substrates with an 80 percent useable area earlier this year, and makes 3-inch AlN substrates for internal use.

For both these trailblazers, progress has been slow and hard won. To increase the diameter of the AIN crystals to the size they are today, engineers at these companies have devoted more than a decade to producing generation after generation of crystals, each with a larger diameter. Increases in size have come from dynamic growth of unfaceted regions. This enlargement, occurring at the beginning of crystal growth (cone-shaped), is restricted to small expansion angles.

Our team at IKZ – that's the common shorthand for the Leibniz Institute for Crystal Growth in Berlin, Germany – has developed an approach that overcomes this restriction. PVT is also used to grow our bulk AIN crystals, produced with an inductively heated graphite setup (see Figure 1).

A foundation for our latest success is our expertise acquired through the growth of SiC boules by PVT. When moving from SiC to AIN growth we retained the reactor, the thermal insulation felt (carbonbonded carbon fibre), and large parts of the graphite components. The growth temperature for both materials is around 2200 °C.

One key difference between the growth of AlN and SiC is the ambient atmosphere. For SiC, an argon atmosphere below 50 mbar is employed, while for AlN its  $\rm N_2$  at a pressure of more than 400 mbar. Crucibles also differ, with graphite used for the growth of SiC, and tungsten or TaC used for AlN. Note that these two options are the only refractory materials capable of withstanding the reactive aluminium vapour under growth conditions.

To produce a high-purity AIN source — it contains less than 150 ppm wt oxygen — we start with a commercially available AIN powder and apply multiple sublimation—recrystallisation steps. During crystal growth, this source, located in the lower part of the crucible, decomposes gradually into aluminium

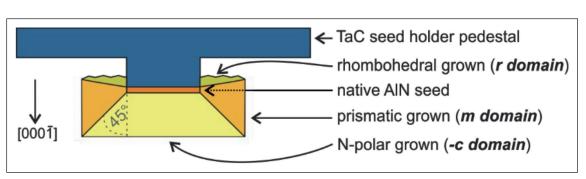

> Figure 2. Simplified sketch of the seed holder design: TaC pedestal and fully faceted grown crystal with an expansion angle of 45°. For more details see C. Hartmann et al. Appl. Phys. Express **16** 075502 (2023).

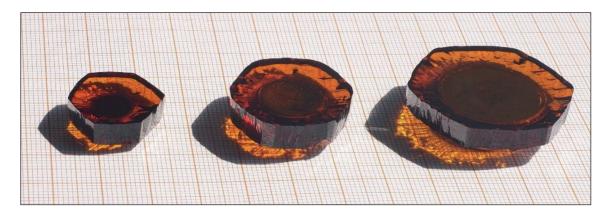

Figure 3. Three AlN crystals of subsequent crystal generations (17 mm, 27 mm, and 37 mm in diameter).

and  $\rm N_2$  vapor species. The aluminium vapour pressure in the crucible depends on the temperature, and typically ranges from 50 mbar to 150 mbar – one may imagine an aluminium 'fog' inside the  $\rm N_2$  ambient. During growth, gaseous aluminium species diffuses along the concentration and temperature gradient through the nitrogen ambient in the growth space, before re-condensing on the AIN seed.

#### Seeding the growth

Recently, we have developed a seed holder design that positions the seed on a TaC pedestal. With this arrangement, crystals grow freely without contact to parasitic grains (see Figure 2). This design allows high radial thermal gradients – the driving force for diameter expansion.

With this new configuration we have realised far higher lateral growth rates. At a seed temperature of 2230 °C growth rates are as fast as around 200  $\mu$ m/h in both the N-polar and the prismatic m directions, resulting in huge expansion angles of around 45° along the entire crystal length. The crystal habit consists of the (000 $\overline{1}$ ) N-polar top facet, the (10 $\overline{1}$ 0) prismatic m facets, and (101x1x2) rhombohedral r facets. The full diameter spans the entire crystal length, ensuring that all cut r2-plane wafers have the same (final crystal) diameter.

AIN seeds with a diameter of 8 mm and a threading dislocation density below 1 x 10<sup>3</sup> cm<sup>-2</sup> provided the starting point for this work. These first-generation seeds were prepared from spontaneous nucleated

AIN crystals. Using our seeded process, growth on them produced crystals with a length of 5-7 mm and a diameter between 18-24 mm. With just two to three steps, we magnified dimensions, producing AIN crystals with diameters of more than 30 mm, which are very suitable for preparing 1-inch substrates (see Figure 3). Based on our current findings, we can't foresee any obstacles to a fast scale-up to industrially relevant diameters of up to 4 inches or more.

If AIN substrates are to make a significant impact, a substantial increase in production speed and availability must go hand-in-hand with maintaining high material quality — note that the latter is possible, according to our characterisation.

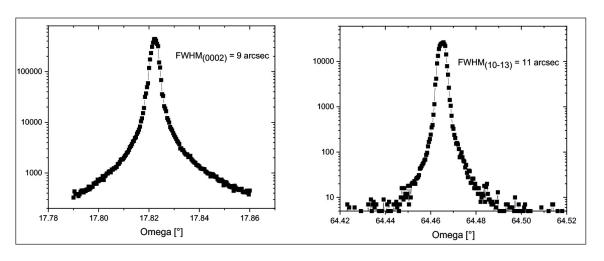

Measurements of symmetric 0002 and asymmetric 1013 rocking curves on the -c facet of the crystals with an open detector aperture reveal typically a single sharp peak with a full-width at half-maximum of 11 arcsec (see Figure 4). Such a sharp peak is indicative of a high structural quality, including a low dislocation density and an absence of small-angle grain boundaries.

Often rocking curves are used to determine the dislocation density in wide bandgap materials and epilayers. However, this approach only provides meaningful results for dislocation densities down to  $5 \times 10^4$  cm $^2$ , as at lower dislocation densities there is no peak broadening compared with perfect, dislocation-free AIN. Another issue is that bulk crystals often show inhomogeneously distributed dislocation densities, having wide areas with very

Figure 4.

Double crystal rocking curves (semi logarithmic scale) measured with open detector aperture in the 0002 (a) and 1013 reflection (b).

Figure 5. (a) A sketch with a highlighted area of an m-plane sample prepared from a seeded crystal with diameter of 20 mm; (b) Transmission photograph of a 1 mm-thick cross-section m plane sample. The several growth domains (-c, m, and r) are distinguishable by the different colours. (c) White-Beam X-Ray Topography (WB-XRT) stitched images (11\overline{2}\)2 reflection) of the cross-section sample. No dislocations are visible in the -c grown domain (1). Dislocations exist only in the m domain near the -c/m boundary (2). Further dislocations exist in the upper part of the m domain (3) and in the r domain (4). The lower half of the sample is dislocation free. Strain contrasts are visible at the domain boundaries (5,6,7) and within the m-domain (8). For more details see C. Hartmann et al. Appl. Phys. Express 16 075502 (2023). The WB-XRT image was recorded by Merve Pinar Kabukcuoglu, Elias Hamann, and Daniel Hänschke from the Institute for Photon Science and Synchrotron Radiation, Karlsruhe Institute of Technology. We thank the Institute for Beam Physics and Technology for the operation of the storage ring, the Karlsruhe Research Accelerator.

few dislocations and local dislocation clusters. It's not possible to uncover the details of these variations with rocking curves, which only offer an average over the recorded area. To identify the lateral dislocation distribution, one can turn to X-ray topography or defect-selective etching.

We have scrutinised an m-plane sample cut from a seeded crystal with a 20 mm diameter using white-beam X-ray topography. This involved the selection of the  $11\overline{2}$ 2 reflection, which is sensitive to all possible types of dislocations (a, c, and a+c type).

From this form of X-ray topography, we have established that the entire -c grown domain of this sample is dislocation free. The only dislocations that exist are in the m domain near the -c/m boundary and in the r domain. We find that dislocations start at the seed rim and stay in the *m* area without crossing the -c/m domain boundary. So far, we are yet to determine the origin of these dislocations. Possible explanations include: insufficient polishing quality at the seed rim; unfavourable initial growth conditions, such as gradients that are too large, at the seed rim; and contact between the r domain and the seed holder. We have also observed additional contrast features at several domain boundaries and within the *m* domain, caused by strain that stems from different impurity concentrations.

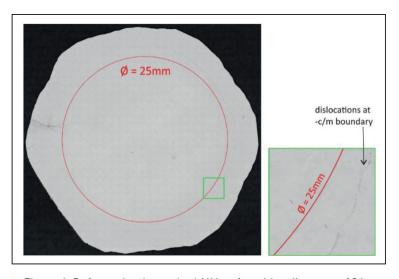

To obtain defect information over the entire diameter, we prepared a wafer from a crystal 34 mm in diameter. We characterised the wafer with defect-

selective etching (see Figure 6). With this technique we determined that the medium etch-pit density, using a standardised 21-point measurement, is  $5 \times 10^3$  cm<sup>-2</sup> inside the 25 mm target diameter. We also uncovered a linear arrangement of dislocations, occurring at the domain boundary between the -*c* and *m* grown domains. The origin of the associated etch pits can be traced back to dislocations formed at the seed rim, which continued along the -*c*/*m*

> Figure 6. Defect selective etched AlN wafer with a diameter of 34 mm an average etch pitch density of  $5 \times 10^3 \, \mathrm{cm}^{-2}$  inside the 25 mm target diameter. The -c/m domain boundary with an increased etch-pit density is outside of the 25 mm target diameter (green square). For more details see C. Hartmann *et al.* Appl. Phys. Express **16** 075502 (2023).

Figure 7. (a) 25 mm epi ready Al-polar AlN substrate; (b) atomic force microscopy (AFM) image of Al-polar epi-ready surface after chemo-mechanical polishing (off-cut of 0.4°); (c) AFM image of a 5 µm-thick Al-polar AlN epi layer (offcut of 0.4°) grown by MOCVD. We thank Marcel Schilling, Tim Wernicke, and Michael Kneissl from the TU Berlin (section 'Experimental Nanophysics and Photonics') for the homoepitaxial growth of the AlN epi layers and the recording of the AFM images.

boundary in the m domain (compare with Figure 5 (c)). Recently, we have been pursuing further diameter enlargement of our AIN crystals. Our efforts have involved selecting the c-plane wafer close to the top of the crystal, where the -c/m boundary is close to the crystal edge, and using a seed diameter that gets as close as possible, but below, the -c/m boundary. This approach promises to provide a shortcut to the development of commercial substrates with a diameter of 100 mm or more.

One of the highlights of our work on AIN is the fabrication of an epi-ready 25 mm substrate with an *m* flat (see Figure 7 (a)). The entire substrate area is grown on the -c facet, clearly identified by homogeneous yellowish colouring. To produce this substrate, our team in our preparation lab developed a complete AIN preparation line, beginning with the sawing of c-plane wafers and including lapping, mechanical polishing and chemomechanical polishing. The latter form of polishing using silica under basic conditions ensures a rootmean-square surface roughness below 0.3 nm (see

Figure 7 (b)). Encouragingly, when MOCVD is used to grow pseudomorphically homoepitaxial layers on this substrate, the epilayer matches the quality of its foundation (see Figure 7 (c)). We can adjust the substrate off-cut – this mainly determines the step widths/macro step formation – precisely between 0.05 and 0.5 degrees.

Our institution is now selling epi-ready single crystalline wafers with a diameter of 10 mm. These substrates are divided into a range of grades, with some better suited to research purposes and others more aligned to technology development.

By the end of next year, we hope to offer 1-inch prototype substrates and 2-inch demonstrators. We are also keen to investigate the performance of devices that are built on our substrates, and are open to project ideas for AIN-based opto-electronic or high-power devices. In such a collaboration we will be able to provide AIN substrates with diameters presently up to 1-inch that feature tailored optical, electrical and structural properties.

#### **FURTHER READING**

- > C. Hartmann et al. "Efficient diameter enlargement of bulk AIN single crystals with high structural quality" Appl. Phys. Express 16 075502 (2023)

- > C. Hartmann et al. "Favourable growth conditions for the preparation of bulk AIN single crystals by PVT" Cryst. Eng. Comm. 22 1762 (2020)

- > R. Dalmau et al. X-Ray "Topography Characterization of Large Diameter AIN Single Crystal Substrates" Mater. Sci. Forum 1004 63 (2020)

- R. T. Bondokov et al. (Invited) "Development of 3-inch AIN Single Crystal Substrates" ECS Trans. 109 13 (2022)

- ▶ H. Amano et al. "The 2020 UV emitter roadmap" J. Phys. D: Appl. Phys. 53 503001 (2020)

- ▶ J. Kotani et al. "24.4 W/mm X-Band GaN HEMTs on AIN Substrates With the LPCVD-Grown High-Breakdown-Field SiNx Layer" IEEE J. Electron Devices Soc. 11 101 (2023)

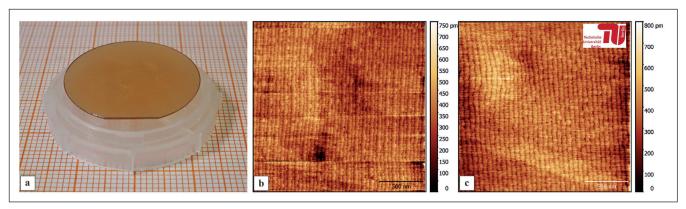

MBE IS OUR DNA

Global market leader for research and production

MBE not only changes how we do it, it also changes what we can do.

Riber is the world leading supplier of MBE processing equipments and related services.

Capitalizing on 30 years of experience, the core philosophy of the company is to design systems in close association with customers. Riber invented and designed major features which are now found in all MBE systems.

Riber plays a key role in the development of MBE technology, providing customers with solutions from equipment to epitaxial growth.

RIBER

INNOVATIVE SOLUTIONS FOR SEMICONDUCTOR INDUSTRY

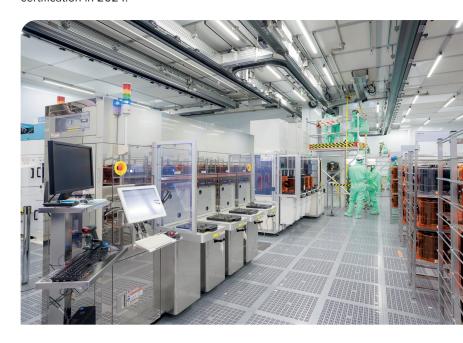

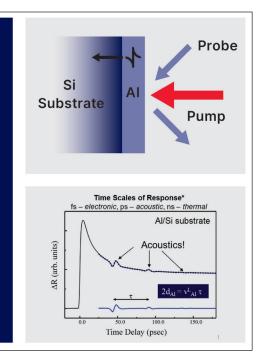

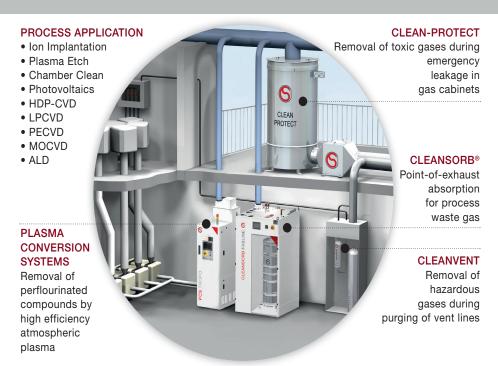

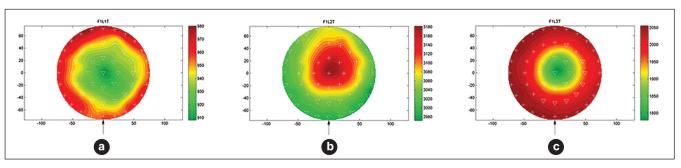

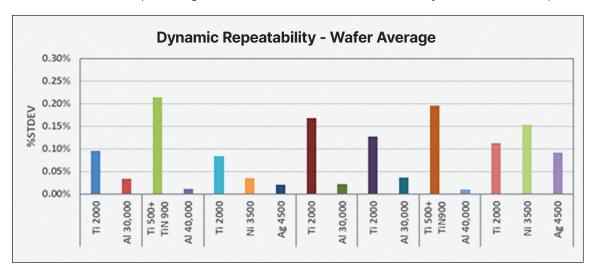

### The road to SiC process control

Manufacturers of SiC power devices produce better transistors when they turn to metrology techniques involving Fourier transform infrared spectroscopy, optical critical dimension and picosecond ultrasonics

#### BY NICK KELLER FROM ONTO INNOVATION

EFFORTS at curbing carbon dioxide emissions are stepping up, with more electric vehicles on our roads and the installation of renewable energy sources on the rise. Alongside these advances, the makers of these green technologies are increasing the electrical efficiency of their offerings, with silicon-based power devices being ditched in favour of superior alternatives based on the likes of SiC.

Supporting this move are the superior physical properties of these compounds. Compared with

silicon, semiconductors such as SiC have wider-bandgaps, a higher electron saturation velocity, a higher critical electric field and a larger thermal conductivity. Drawing on all these strengths, power transistors offer higher operating

frequencies, higher power ratings, elevated operating temperatures, better cooling capability and lower energy loss – just the traits that the market wants.

Today's manufacturers of SiC power devices are tending to focus on trench-based devices, a design that reduces on-resistance and increases carrier mobility. But there is a trade-off, with these strengths coming at the expense of increased fabrication complexity.

To address this issue, high-volume manufacturers of SiC power devices must adopt inline process control at several key steps, including optical

metrology methods like Fourier transform infrared (FTIR) spectroscopy, optical critical dimension (OCD) and picosecond ultrasonics. When armed with these techniques, chipmakers are far better informed when undertaking critical

> processing steps, including epilayer growth, trench etch, gate poly-

silicon etch back, and frontside/backside contact metallisation.

All of these three process control techniques that have just been mentioned can play a major role in streamlining SiC production. When FTIR is adopted alongside advanced algorithms, SiC manufacturers can extract epilayer thickness and carrier concentrations for two- and three-layer stacks. What's more, FTIR can non-destructively characterise the depth and the dopants in the implant layer directly on SiC substrates before and after the anneal process step. That's a significant benefit, as it removes the need for monitoring silicon wafers and secondary ion mass spectrometry when undertaking implant characterisation.

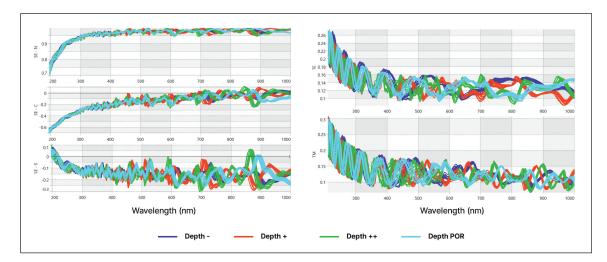

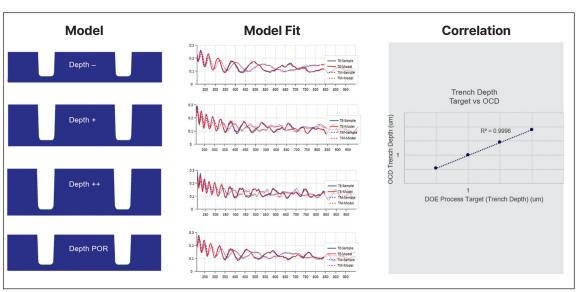

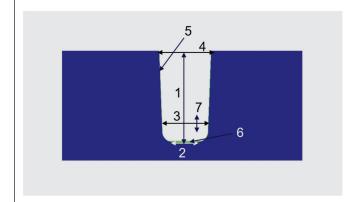

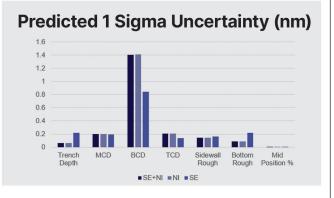

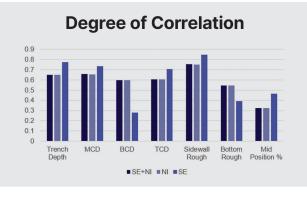

Meanwhile, the introduction of a multi-channel OCD

tool in a SiC fab can accurately and non-destructively determine trench depth, bottom and top widths, and bottom rounding at the trench etch step, when this technique draws on electromagnetic solvers that utilise advanced rigorous coupled wave analysis. Note that bottom rounding of the trench is critical to preventing a high electric field density, and ultimately premature device failure. Lastly, picosecond ultrasonics can improve efficiency in a SiC fab by measuring frontside and backside metal contact thickness. Together, these non-destructive, in-line process control methods empower chipmakers to solve many of the challenges posed by the increased fabrication complexity of SiC power devices.

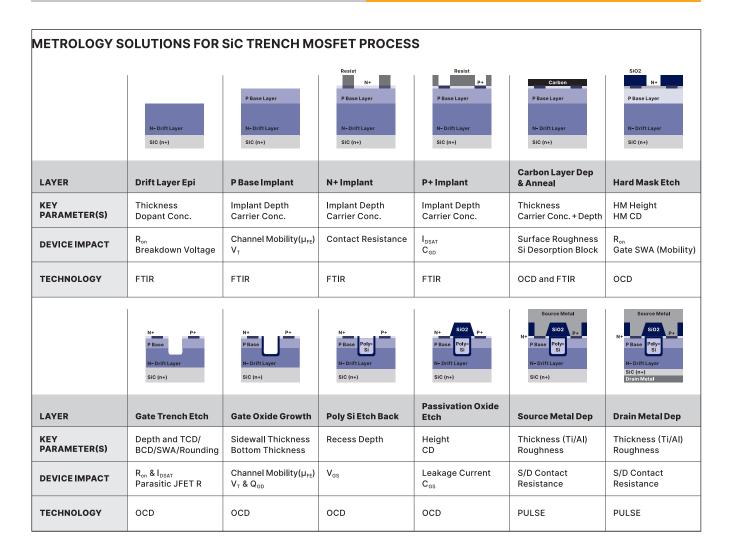

Soon we will take a closer look at all three techniques. But before we do, let's take a minute to review the process steps for making a simplified SiC trench MOSFET and a SiC trench insulated-gate bipolar transistor (IGBT). This is outlined in Figure 1, which illustrates the process flow for the SiC trench MOSFET, and shows the key process steps, key parameters, device performance impact and the proposed process control solution. This figure also illustrates the process flow for a SiC trench IGBT device. While the steps are very similar, there are differences. The most significant is that a SiC trench IGBT has a p substrate and a  $n^+$  buffer layer before the drift layer.

#### Scrutinising layers with FTIR

Incorporating a Michaelson interferometer, a broadband light source and a fast Fourier transform (FFT) algorithm, FTIR spectrometers are well suited to studying the layers of SiC devices. This technique, requiring acquisition of infrared spectra extending from the near-IR to the far-IR, is quick, non-destructive and highly sensitive to molecular and free-carrier absorption. By measuring both transmission and reflectance spectra, a single tool can measure the elemental composition of epilayers and their thickness. A well-designed system is capable of obtaining the characteristics of five epitaxial layers from a single scan.

Spectroscopy in the IR offers much insight, including values for the carrier concentration of doped semiconductors. This is possible due to free carrier absorption, a process described by the Drude model, which accounts for the frequency-dependent conductivity of metals. The Drude model can be used to calculate the plasma frequency, which depends on the concentration of free carriers and their effective mass. For wavelengths above the plasma frequency, the electric field of the incident light oscillates so fast that the material acts like a dielectric. That's not the case for wavelengths below the plasma frequency, which absorb light. Note that

> Figure 1. SiC trench **MOSFET** process flow.

### TECHNOLOGY I METROLOGY

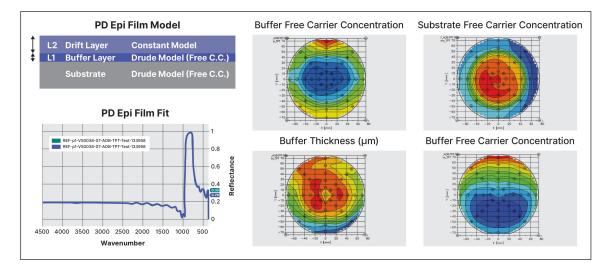

Figure 2. PD Epi model fitted to the experimental spectra from the FTIR system and the wafer maps for all parameters of interest.

the absorption coefficient is directly proportional to the free carrier concentration.

The information garnered by FTIR spectroscopy is incredibly valuable to makers of SiC trench MOSFETs and IGBTs. For the SiC MOSFETs, the thickness and the carrier concentration of the drift layer directly determines the breakdown voltage of the transistor. Meanwhile, for the IGBT, the buffer layer thickness and the free carrier concentration determine a number of key characteristics, including switching speed and conduction losses.

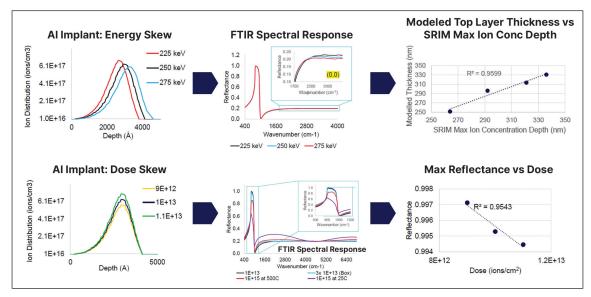

FTIR spectroscopy also offers great insight into the ion implantation process. Measuring the depth and free-carrier concentration of the p,  $p^+$  and  $n^+$  regions is critical, because all these features influence the channel mobility, contact resistance, threshold voltage and saturation current.

At Onto Innovation we are supporting this task, having developed a new analysis engine called PD Epi, which enables the modelling of complex epitaxial film stacks in compound semiconductors. Our analysis engine provides direct modelling

of carrier concentrations and film thicknesses of multiple layers, including the substrate. Utilising Drude oscillator models and gradient layers, our engines determine the carrier concentration profile through the structure during the diffusion and implantation process.

To illustrate the power of our PD Epi model, we have used it to characterise an IGBT epiwafer. Using our model we have determined the buffer and drift layer thickness, and the carrier concentration for the buffer layer and the substrate. This study involved a Design Of Experiment (DOE) methodology, with the drift layer thickness varied from 5  $\mu m$  to 30  $\mu m$ . while all other parameters of interest were kept constant.

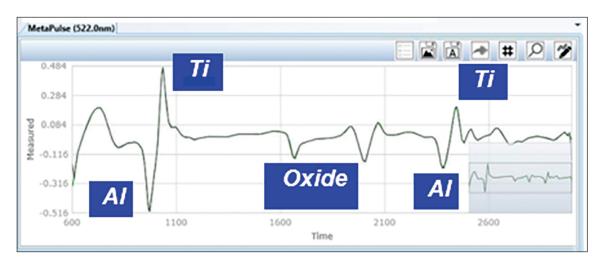

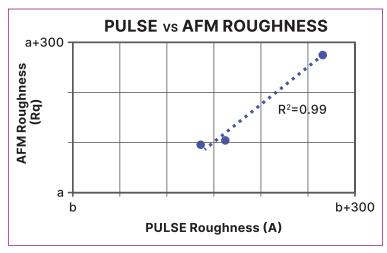

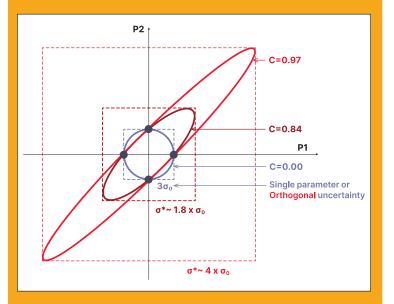

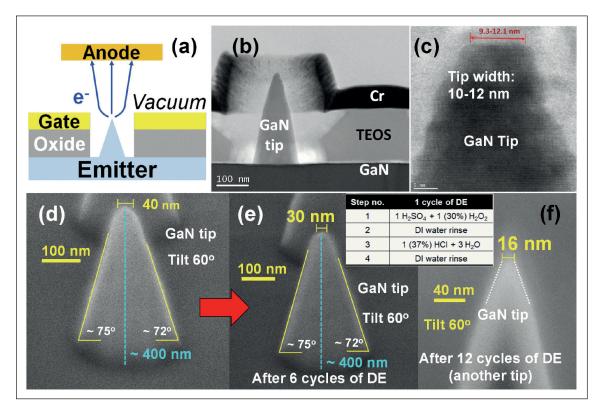

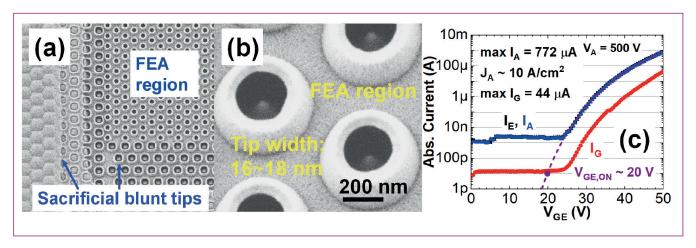

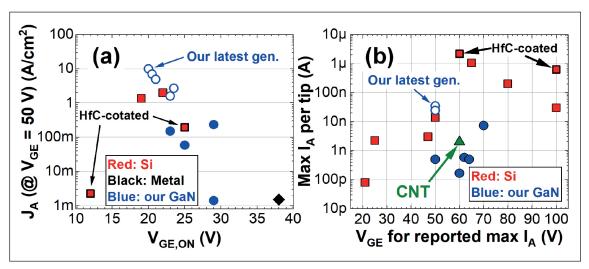

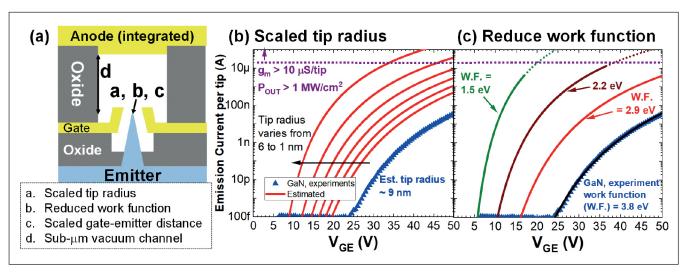

An example of results on these IGBT epiwafers, obtained with our PD Epi model and fitted to the experimental spectra from the FTIR, is shown in Figure 2, which has wafer maps for all parameters of interest. We have correlated the measured drift layer thickness to the expected thickness. This gave a coefficient of determination (R2) exceeding 0.99, demonstrating that the predictive capabilities