# COMPOUND SEMICONDUCTOR

CONNECTING THE COMPOUND SEMICONDUCTOR COMMUNITY

VOLUME 31 ISSUE VIII 2025

AN ANGEL BUSINESS COMMUNICATIONS PUBLICATION

COMPOUNDSEMICONDUCTOR.NET

## TAKING THE GUESSWORK OUT OF **SiC PRODUCTION**

PVA TePla Scientific Visual

AIXTRON

# THE G10 SERIES

**G10-GaN**

1<sup>st</sup> fully automated compact

GaN MOCVD cluster designed

100% for Si Power fabs

Your **Productivity Solution**

for All Advanced Epitaxy Materials

## Deep UV LEDs are shedding their feeble credentials

WHEN one thinks of deep-UV LEDs, it's easy to focus on the negatives – and there are plenty of them.

After all, these short-wavelength emitters are often impaired by a lattice mismatch that spawns light-quenching defects, and a low doping efficiency for holes that hampers carrier injection. And then there's the low extraction efficiency, particular troublesome at the very shortest wavelengths, due to a switch in the dominant direction for polarisation to transverse magnetic; and the need for novel forms of epitaxy to get the best out of these devices, even though this still produces a performance that falls well short of those for blue LEDs.

But while there is still a significant gap between the performance of UVC LEDs and their visible cousins, it's not quite the chasm it once was. Take the best 265 nm devices from ams Osram, slated to enter commercial production around this time next year (see p. 14). Their output power is 200 mW, realised at a wall-plug efficiency of just over 10 percent, and the lifetime is 20,000 hours, well beyond what's required in some applications.

During the pandemic, UVC LEDs attracted a great deal of attention as sources for killing Covid-19. Since then, interest has waned in using these emitters for disinfecting air and surfaces, and water treatment is once again seen as the biggest application by many – and certainly by those at ams Osram.

For all potential markets for the deep-UV LED, competition comes in the form of the mercury lamp. It's bulky, fragile, has a lifetime less than that of the best UV LEDs, and it takes several minutes to reach full power – but, and it's a big but, this incumbent is capable of producing a substantial output.

Due to the limitations of the mercury lamp, LEDs emitting at 265 nm – that's the sweet spot for germicidal effectiveness – are ideal for point-of-use applications. These sources can be fitted to taps, water dispensers, and the point-of-entry to one's home.

Where deep-UV LEDs face far stiffer competition is large-scale water treatment, associated with industrial and municipal applications, where the source is on all the time. Here the power of the solid-state source emitter is an issue, and gains are required to win market share.

Based on the progress of all classes of LEDs, those emitting in the UVC are going to continue to increase in power, while offering a reduction in the cost-per-lumen. And while this market will only be worth a fraction of that of the general lighting market, it's yet another example of compound semiconductor devices aiding humanity's advances.

Free weekly e-news roundup go to: [compoundsemiconductor.net](http://compoundsemiconductor.net)

## COVER STORY

### Taking the guesswork out of SiC production

Thanks to advances in metrology, it's now possible to scrutinise a SiC puck before it's wafered and identify material defects that govern yield and profitability

22

### 18 GaN: Tracking fast-charging with 'Lichi Law'

All forms of GaN fast charger are delivering an increase in output power of around 50 percent every 12 months

### 30 Breakthroughs in blue and green laser diodes

More powerful and efficient GaN-based lasers are aiding displays and simplifying copper processing

### 34 High-bandwidth energy-efficient networks

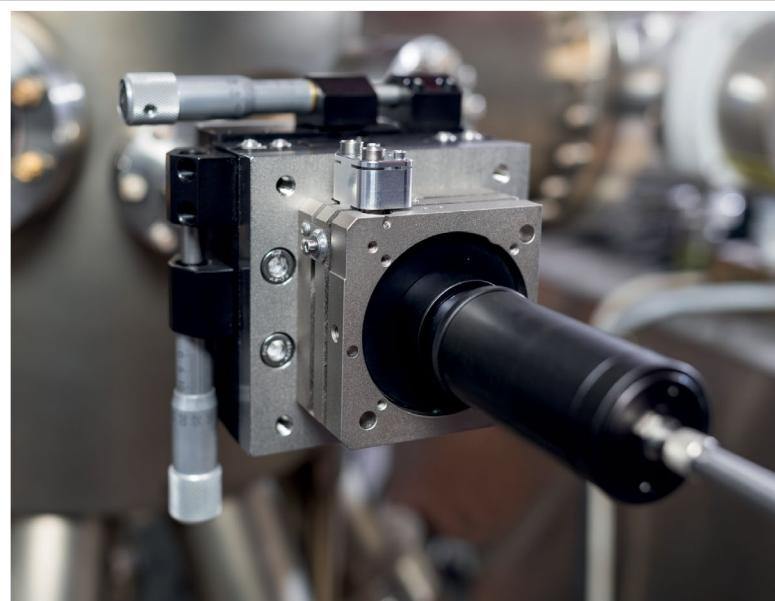

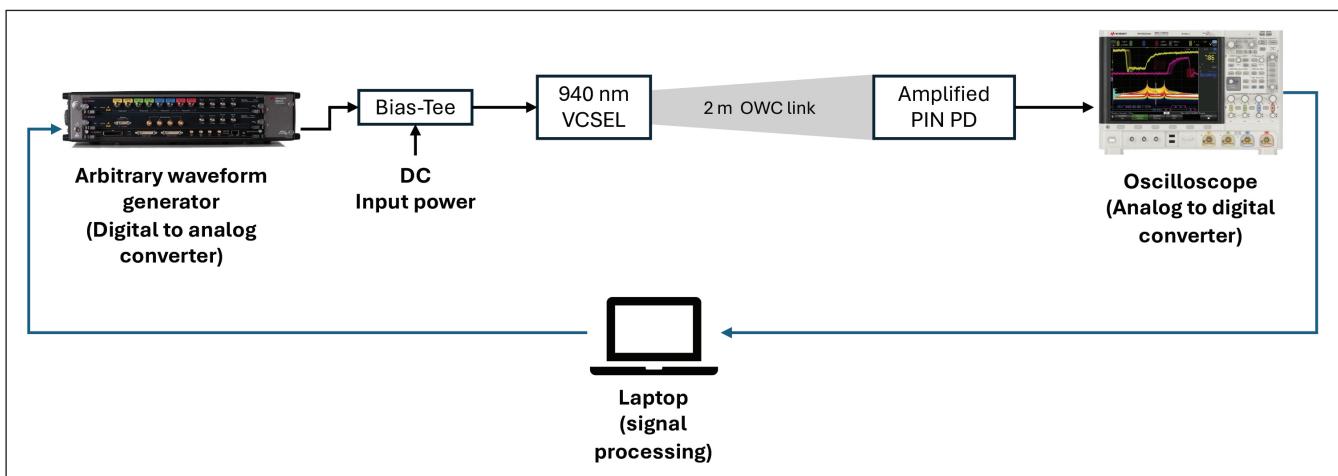

Arrays of VCSELs promise to provide incredibly efficient LiFi communication at terabit data rates

### 40 When every microsecond counts

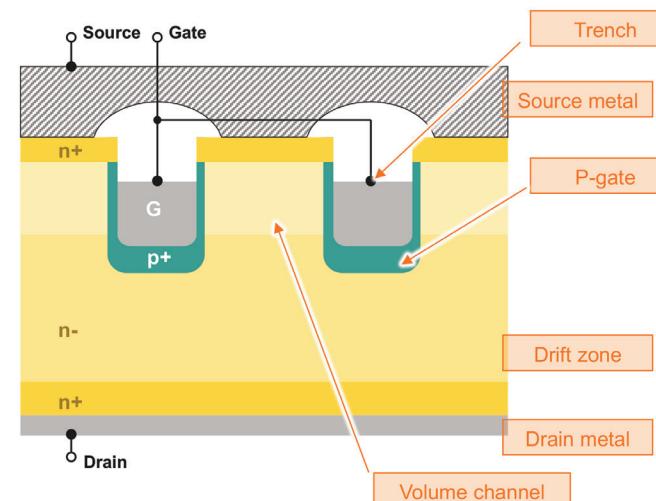

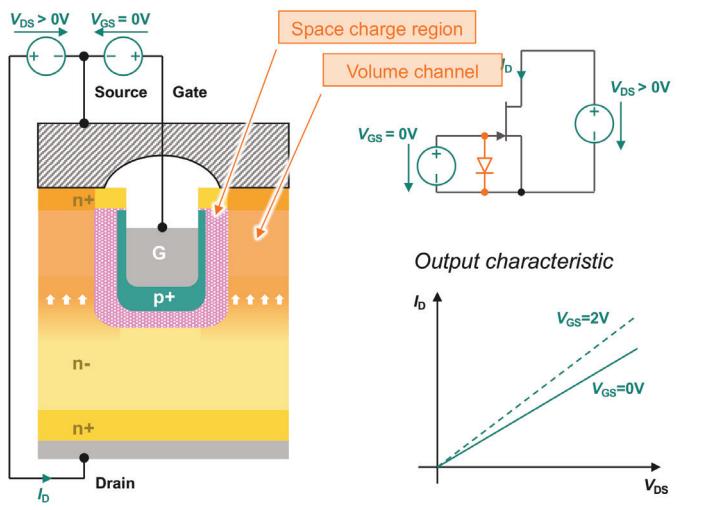

Infineon's CoolSiC JFET is a new class of switching device that enables power distribution systems to be immune from delays

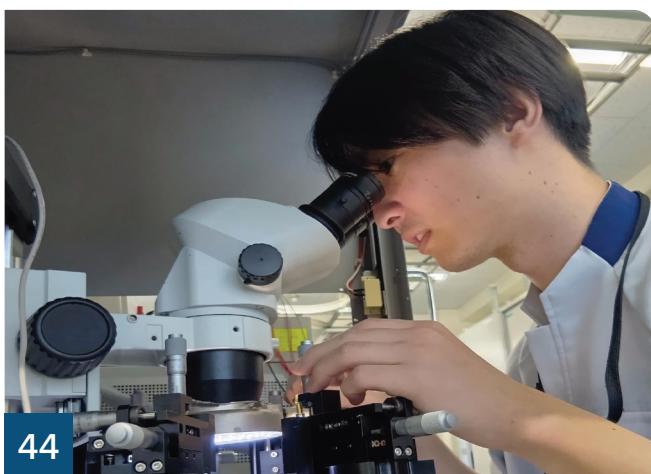

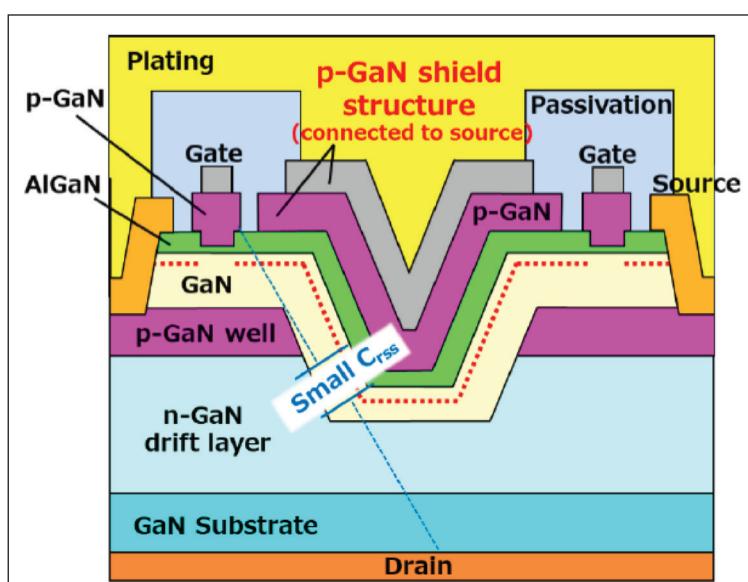

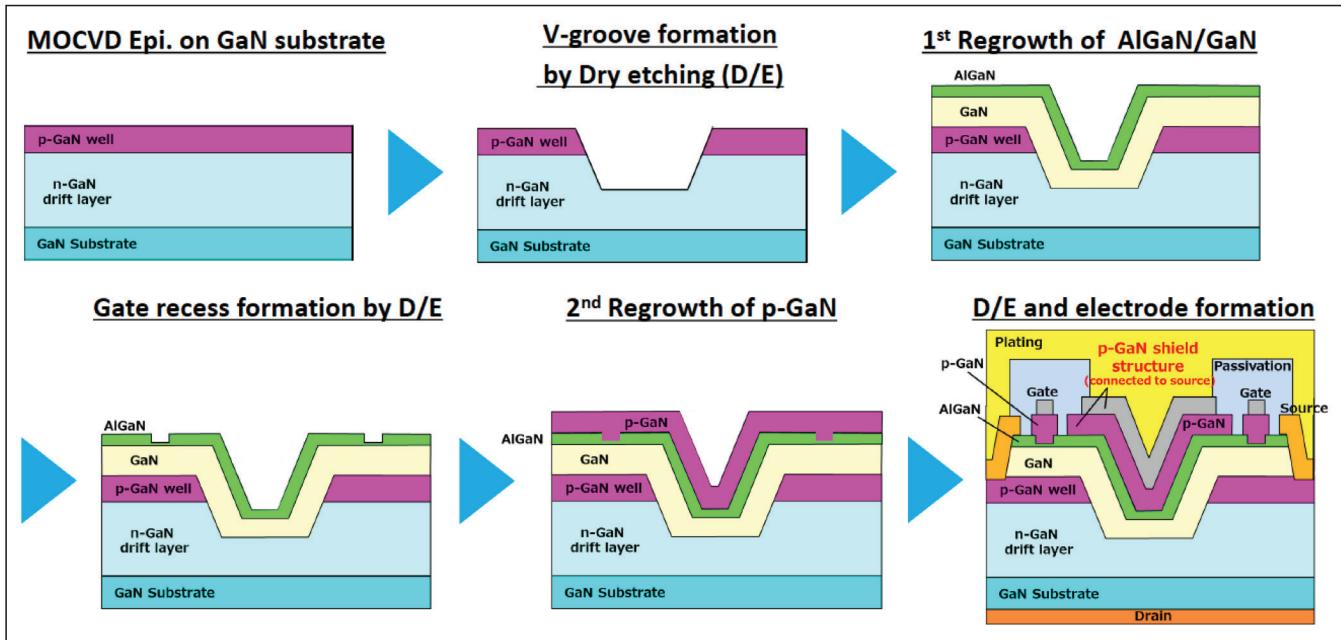

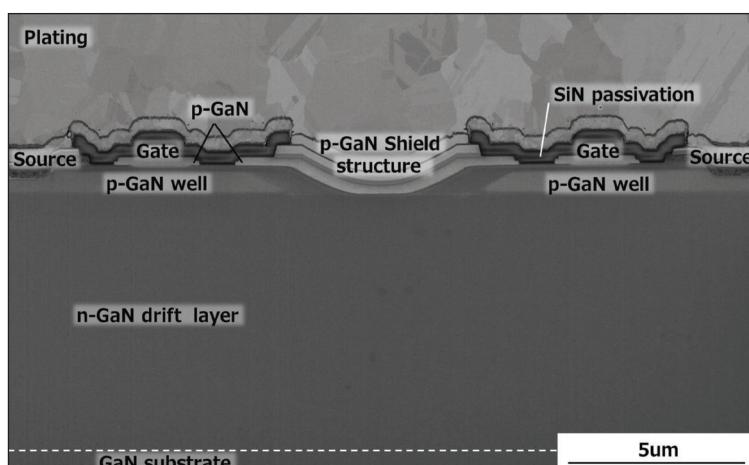

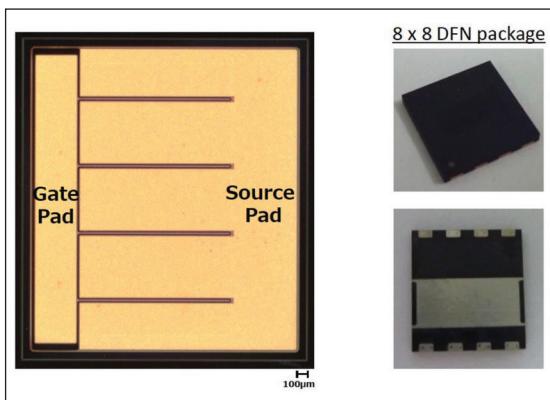

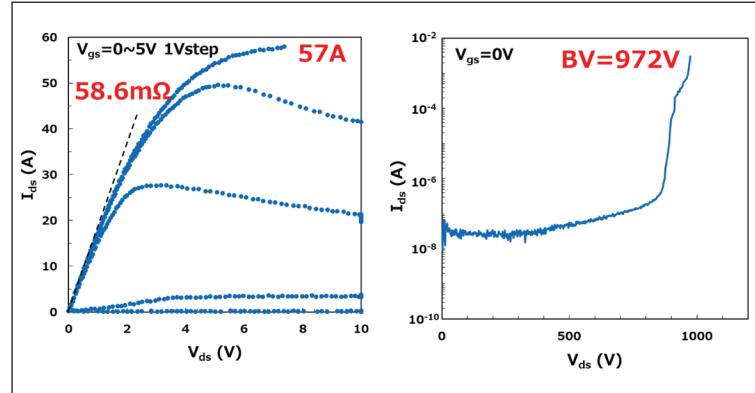

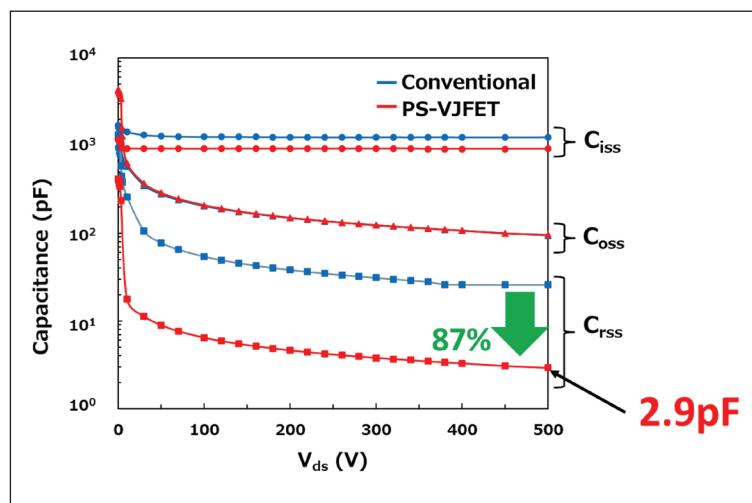

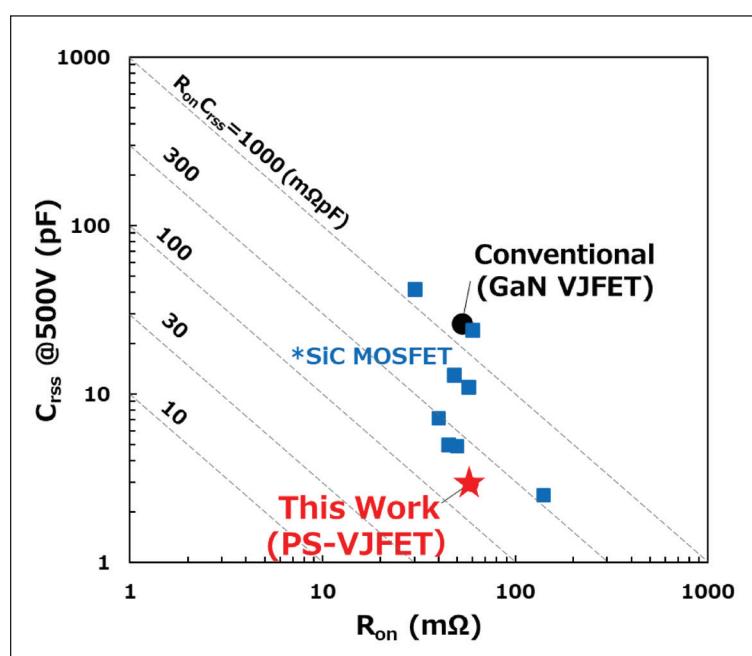

### 44 Cranking up the switching speed with a *p*-GaN shield

Adding a *p*-GaN shield to a vertical GaN-on-GaN transistor trims capacitance and enhances high-power, high-speed switching

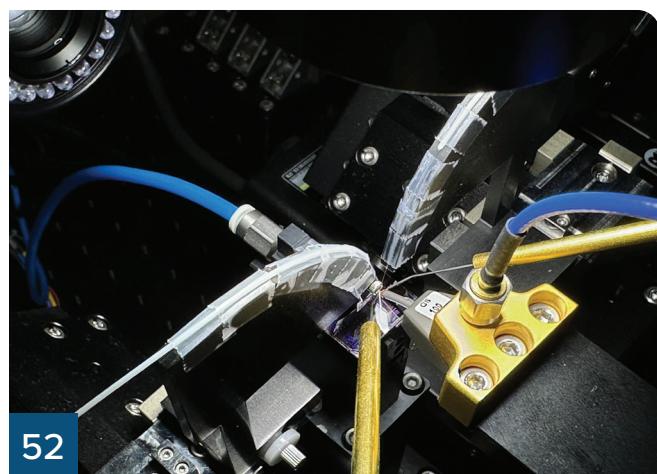

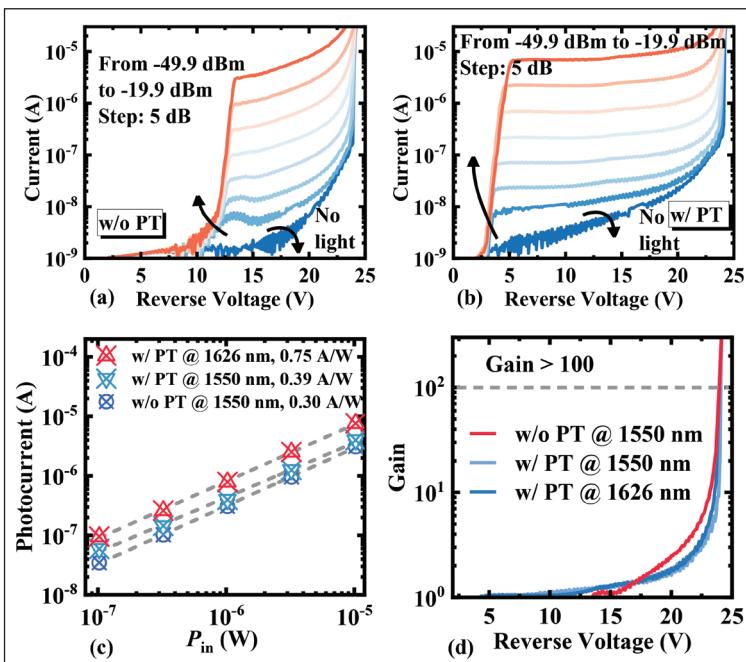

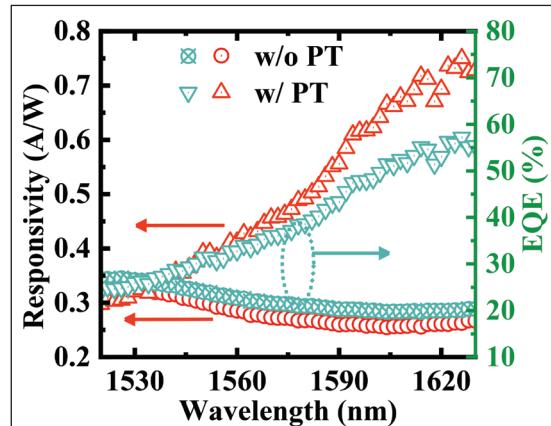

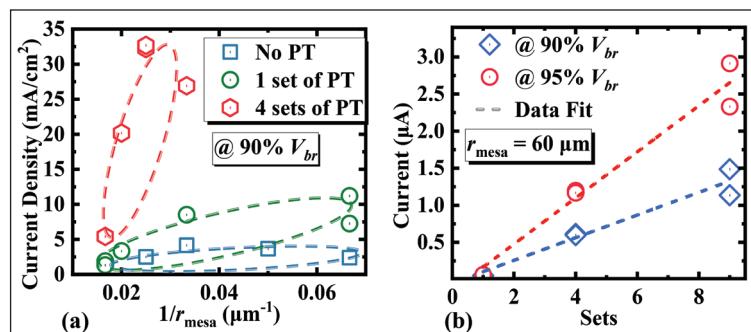

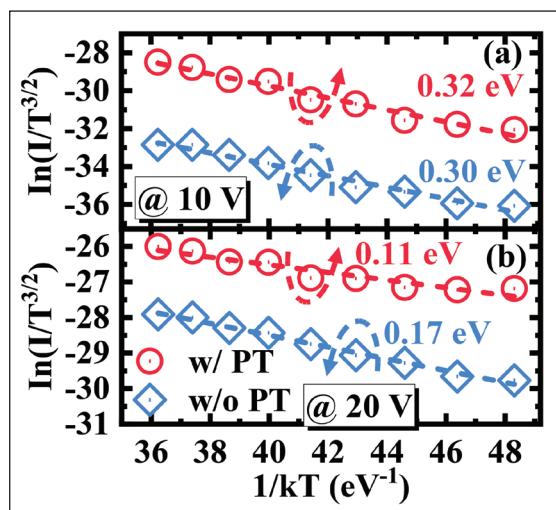

### 52 Trapped light boosts detection efficiency

InGaAs avalanche photodiodes equipped with photon-trapping structures realise record-breaking efficiency, aiding sensing in tomorrow's applications

44

52

## NEWS ANALYSIS

### 14 UVC LEDs up their game

More powerful, efficient and longer lasting UVC LEDs are making a compelling case for water purification

### 16 Wolfspeed: Making material gains

The pioneer of SiC starts to offer 200 mm substrates and epiwafers to all

## RESEARCH REVIEW

### 58 Aluminium treatment boosts the efficiency of green LEDs

### 59 Two-step anneal aids SiC interfaces

### 60 GaN: Reducing the on-resistance of GaN p-n diodes

|                                            |                                   |                    |

|--------------------------------------------|-----------------------------------|--------------------|

| <b>Editor</b> Richard Stevenson            | richard.stevenson@angelbc.com     | +44 (0)1291 629640 |

| <b>News Editor</b> Christine Evans-Pughe   | christine.evans-pughe@angelbc.com |                    |

| <b>Design &amp; Production Manager</b>     |                                   |                    |

| Mitch Gaynor                               | mitch.gaynor@angelbc.com          | +44 (0)1923 690214 |

| <b>Director of Logistics</b> Sharon Cowley | sharon.cowley@angelbc.com         | +44 (0)1923 690200 |

| <b>Event &amp; Media Sales Executive</b>   |                                   |                    |

| Ranjodh Shergill                           | ranjodh.shergill@angelbc.com      | +44 (0)2476 718970 |

| <b>Circulation</b> Scott Adams             | scott.adams@angelbc.com           |                    |

| <b>Publisher</b> Jackie Cannon             | jackie.cannon@angelbc.com         | +44 (0)1923 690205 |

## NEWS

### 06 Imec launches 300 mm GaN programme

### 07 Vertical Semiconductor raises \$11 million

### 08 Rohm and Infineon to collaborate on SiC packages

### 09 Ams Osram and Nichia sign broad IP agreement

### 10 Northrop Grumman opens access to US chip facilities

### 11 Europe's tech giants unite to secure photonics future

### 12 Novosense, UAES and Innoscience join forces on GaN

Compound Semiconductor is published nine times a year on a controlled circulation basis. Non-qualifying individuals can subscribe at: £115.00 per annum (UK), €165 per annum (Europe), \$198 per annum (air mail) (USA). Cover price £4.50. All information herein is believed to be correct at time of going to press. The publisher does not accept responsibility for any errors and omissions. The views expressed in this publication are not necessarily those of the publisher. Every effort has been made to obtain copyright permission for the material contained in this publication. Angel Business Communications Ltd © Copyright 2025. All rights reserved. Contents may not be reproduced in whole or part without the written consent of the publishers. The paper used within this magazine is produced by chain of custody certified manufacturers, guaranteeing sustainable sourcing. US mailing information: Compound Semiconductor, ISSN 1096-598X, USPS Permit Number 25366, is published 9 times a year, Combined Jan/Feb, March, Combined April/May, June, July, Combined August/September, October, November, December by Angel Business Communications Ltd, Unit 6, Bow Court, Fletchworth Gate, Burnsall Rd, Coventry CV5 6SP, UK. T: +44 (0)2476 718970. E: info@angelbc.com W: angelbc.com

**Sales and Product Manager** James Cheriton james.cheriton@angelbc.com +44 (0)2476 718970

**Chief Executive Officer** Sukhi Bhadal sukhi.bhadal@angelbc.com +44 (0)2476 718970

**Chief Technical Officer** Scott Adams scott.adams@angelbc.com +44 (0)2476 718970

**Directors** Jackie Cannon, Sharon Cowley

Angel BUSINESS COMMUNICATIONS

# Imec launches 300 mm GaN programme

Aixtron, GlobalFoundries, KLA Corporation, Synopsys, and Veeco join imec's GaN power electronics program track on 300mm as first partners

IMEC, the Belgian research and innovation hub, has announced Aixtron, GlobalFoundries, KLA Corporation, Synopsys, and Veeco as first partners in its 300 mm GaN open innovation programme track for low- and high-voltage power electronics applications.

This programme track, part of imec's industrial affiliation programme on GaN power electronics, has been set up to develop 300 mm GaN epi growth, and low- and high-voltage GaN HEMT process flows.

As well as reducing GaN device manufacturing costs, the use of 300 mm substrates will also allow the development of more advanced power electronics devices, such as efficient low-voltage point-of-load converters for CPUs and GPUs.

Stefaan Decoutere, fellow and programme director of the GaN power electronics program at Imec: "The benefits of transitioning to 300 mm wafers go beyond upscaling production and reducing manufacturing costs. Our CMOS-compatible GaN technology now has access to 300 mm state-of-the-art equipment that will allow us to develop more advanced GaN-based power devices. Examples are aggressively scaled low-voltage *p*-GaN gate HEMTs for use in point-of-load converters, supporting energy-efficient power distribution for CPUs and GPUs."

As part of the 300 mm GaN programme, a baseline lateral *p*-GaN HEMT technology platform will first be established for low-voltage applications (100 V and beyond), using 300 mm silicon (111) as a substrate. For this, process module work centred around *p*-GaN etch and Ohmic contact formation is ongoing.

Later, high-voltage applications are targeted. For 65 V and above, developments will utilise 300 mm semi-spec and CMOS-compatible QST engineered substrates (a material with poly-crystalline AlN core). During

the developments, control over the bow of the 300 mm wafers, and their mechanical strength are prime concerns.

The launch of the 300 mm GaN programme follows successful 300 mm wafer handling tests and mask set development. Imec expects to have full 300 mm capabilities installed in its 300 mm cleanroom by the end of 2025.

"The success of the 300 mm GaN development also hinges on the ability to establish a robust ecosystem and jointly drive innovation from 300 mm GaN growth and process integration to packaging solutions," adds Stefaan Decoutere. "We are therefore pleased to announce Aixtron, GlobalFoundries, KLA Corporation, Synopsys, and Veeco as first partners in our open R&D programme track on 300 mm GaN and hope to welcome more partners soon. Developing advanced GaN power electronics requires close coupling between design, epitaxy, process integration, and applications – a coupling that has proved to be critical for our pioneering work on 200 mm GaN."

**“The success of the 300 mm GaN development also hinges on the ability to establish a robust ecosystem and jointly drive innovation from 300 mm GaN growth and process integration to packaging solutions. ”**

# Vertical Semiconductor raises \$11 million

MIT GaN spin-out bets on the next wave of power growth for AI chips and data centres

VERTICAL SEMICONDUCTOR, a spin-out from the Massachusetts Institute of Technology (MIT), has announced \$11 million in seed funding to help accelerate development of vertical GaN transistors to deliver the next wave of power to AI chips in data centres.

The company's GaN transistors are designed to ease data centre power bottlenecks by pushing energy conversion closer to the chip. This is said to improve efficiency by up to 30 percent and enable a 50 percent smaller power footprint in AI data centre racks.

"The pace of AI is not only limited by algorithms. The most significant bottleneck in AI hardware is how fast we can deliver power to the silicon," said Cynthia Liao, CEO and co-founder of Vertical. "We're not just improving efficiency, we're enabling the next wave of innovation by rewriting how electricity is delivered in data centres at scale."

Vertical's technology is built on a decade of research at MIT's Palacios Group – a GaN research lab. The company has demonstrated the technology on 8-inch wafers using standard silicon CMOS semiconductor

► Pictured above: founders of Vertical Semiconductor: Josh Perozek, Cynthia Liao, and Tomás Palacios

manufacturing methods, enabling integration with existing process technology and making it ready for real-world deployment for devices from 100 V to 1.2 kV.

"The Vertical team has cracked a challenge that's stymied the industry for years: how to deliver high voltage and high efficiency power electronics with

a scalable, manufacturable solution," said Matt Hershenson, Venture Partner at Playground Global, which led the funding round. "They're not just advancing the science – they're changing the economics of compute."

Additional investors include JIMCO Technology Ventures, Milemark Capital, and Shin-Etsu Chemical.

**TES**

Technology Engine of Science

**200(150)mm Dual-Chamber**

**Tunable Triple Pair Nozzle**

Each nozzles play distinct roles to improve both thickness and doping uniformity

**200mm Performance**

Process reproducibility ensured Across the PM cycles (HCl free)

**THK  $\sigma = \pm 0.3\text{--}0.5\%$  / Avg. 0.69%**

**Doping  $\sigma = \pm 0.3\text{--}0.7\%$  / Avg. 1.07%**

**TRION**

**Tunable SiC Epi System**

**MOCVD for AlN Growth**

**Loading Capa**

|    |         |    |          |

|----|---------|----|----------|

| 3G | 1x6inch | 4G | 1x8inch  |

|    | 1x4inch |    | 3x4inch  |

|    | 6x2inch |    | 14x2inch |

**Crystal Quality for AlN**

(XRD FWHM)

:(002) < 220arcsec

:(102) < 370arcsec

**Crack-Free AlN**

: Fast Gas Switchable Reactor

**Application**

- AlN, AlGaN Growth

- (Far)UVC, UVB, UVA LED: 220-350nm

- Power Device (AlN, High Al-Content AlGaN, ScAlN)

- Photodetector (AlGaN-based)

**HESTIA**

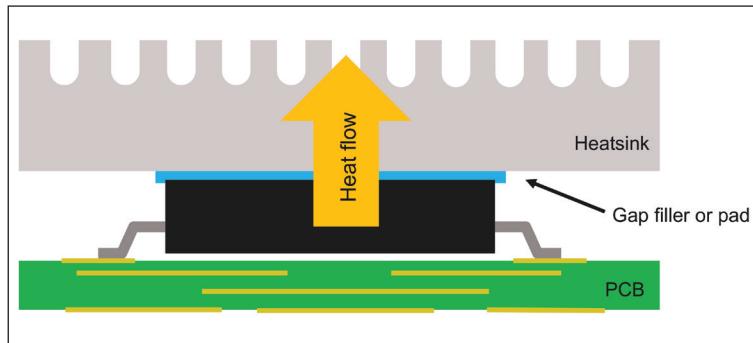

# Rohm and Infineon to collaborate on SiC packages

Companies to second source selected packages for SiC power chips with plans to expand to GaN in the future

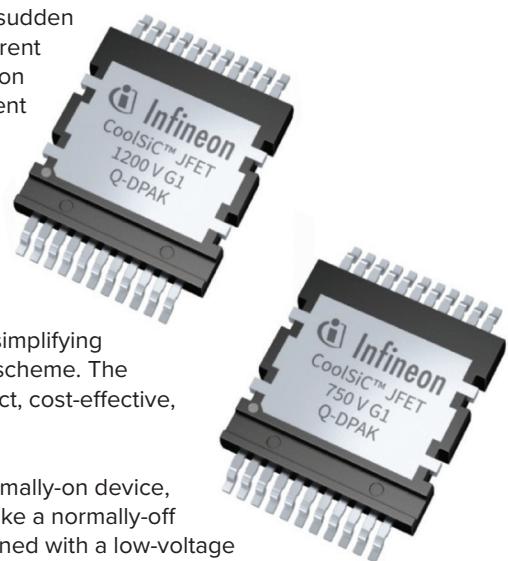

Rohm and Infineon have signed an agreement to collaborate on packages for SiC power semiconductors used in applications such as on-board chargers, photovoltaics, energy storage systems, and AI data centres.

The partners aim to enable each other as second sources of selected packages for SiC power devices, a move which will increase design and procurement flexibility for their customers. In the future, customers will be able to source devices with compatible housings from both Rohm and Infineon.

As part of the agreement, Rohm will adopt Infineon's innovative top-side cooling platform for SiC, including TOLT, D-DPAK, Q-DPAK, Q-DPAK dual, and H-DPAK packages. Infineon's top-side cooling platform offers several benefits, including a standardised height of 2.3 mm for all packages.

At the same time, Infineon will take on Rohm's DOT-247 package with SiC half-bridge configuration to develop a compatible package. That will expand Infineon's recently announced Double TO-247 IGBT portfolio to include SiC half-bridge solutions.

Rohm's DOT-247 delivers higher power density and reduces assembly effort compared with standard discrete

As part of the agreement, Rohm will adopt Infineon's innovative top-side cooling platform for SiC, including TOLT, D-DPAK, Q-DPAK, Q-DPAK dual, and H-DPAK packages

packages. Featuring a unique structure that integrates two TO-247 packages, it enables a reduction in thermal resistance by approximately 15 percent and inductance by 50 percent compared with the TO-247. The advantages bring 2.3 times higher power density than the TO-247.

Rohm and Infineon plan to expand their collaboration in the future to include other packages with both silicon and wide-bandgap power technologies, such as SiC and GaN.

"We are excited about working with Rohm to further accelerate the establishment of SiC power devices," said Peter Wawer (above left), division president green industrial power at Infineon. "Our collaboration will provide customers with a wider range of options and greater flexibility in their design and procurement processes, enabling them to develop more energy-efficient applications that will further drive decarbonisation."

"Rohm is committed to providing customers with the best possible solutions. Our collaboration with Infineon constitutes a significant step towards the realisation of this goal, since it broadens the portfolio of solutions," said Kazuhide Ino (above right), member of the board, managing executive officer, in charge of power devices business at Rohm.

## CGD partners with GlobalFoundries

CAMBRIDGE GaN Devices (CGD) has announced that it is working with GlobalFoundries (GF) to strengthens CGD's fabless strategy, expanding the supply chain for the company's single-chip ICeGaN power devices.

Simon Stacey (pictured above), COO of CGD, said: "Applying the CGD design flow to the excellent GF process design kit (PDK) is essential to enabling CGD to develop and manufacture our next generation GaN power devices at a much faster time to market. We are delighted to be partnering with GF, as their renowned foundry services and commitment to GaN are a perfect fit for our ICeGaN power devices."

ICeGaN combines a GaN switch, interface and protection circuitry on the same GaN chip, in contrast to most other solutions that use multi-chip or co-packaged solutions.

CGD's pioneering single-chip technology runs with standard silicon MOSFET drivers and is built using a standard silicon CMOS wafer fab process. This means that there is no need for a specialist process in the wafer fab. Using GF's 8-inch process also ensures the manufacturing costs of CGD products remain inherently competitive, according to the company.

# Ams Osram and Nichia sign broad IP agreement

Comprehensive cross-license agreement covers thousands of patent-protected innovations in LED and laser technologies

AMS OSRAM and Nichia have expanded their long-standing IP collaboration with a comprehensive cross-license agreement covering thousands of patent-protected innovations in LED and laser technologies.

The agreement, signed by Aldo Kamper, CEO of Ams Osram, and Hiroyoshi Ogawa, president of Nichia, grants both companies mutual access to each other's patents for nitride LED and laser components. And, for the first time, also covers sophisticated LED packages and LED modules, such as matrix headlamps. The move aims to strengthen the IP protection both companies offer to their customers.

Ams Osram and Nichia have invested heavily in R&D over decades. They say that with the new patent cross-license agreement, customers will gain enhanced IP safety when using products based on their patented technologies. Both companies have a long history of cross-license agreements, which started in 2002 and continued through today, with an update in 2010. The new agreement

covers R&D results from the last 15 years.

"In an industry driven by innovation, intellectual property is the foundation of trust and long-term value. Unfortunately, we continue to see LED and laser products entering the market that do not meet essential IP standards. Together with Nichia, we encourage customers to scrutinise claims of IP compliance and to choose partners holding a unique IP position like Ams Osram and Nichia", said Kamper.

"As the two global leaders in the LED and laser industry, Nichia and Ams Osram have renewed the most comprehensive and robust cross-licensing agreement in the sector. Customers who select products from Nichia or Ams Osram benefit from extensive patent protection, ensuring confidence in their business activities. Standing together, we will continue to safeguard the market's integrity by encouraging respect for intellectual property throughout our industry", said Ogawa.

**GaAs/InP MOCVD Epitaxial Growth & Foundry Services**

Engineered for Excellence.

All manufacturing in Hudson, New Hampshire, United States

ISO 9001 and ITAR registered

- 35+ years of experience providing III-V solutions for optoelectronics application in datacom, energy, biotechnology, industrial, and defense industries

- State-of-the-art MOCVD growth reactors for R&D and production of custom III-V materials on GaAs and InP substrates

- Fast turnaround for high-volume manufacturing

- Some products manufactured include photocathodes for night vision goggles, laser power converters, avalanche photodiodes, custom photodiodes and LEDs/LED array chips

- 1-inch to 6-inch substrate sizes available

- Chips delivered as die-on-tape or in gel-paks

SCAN to learn more

603-595-8900

sales@masimosemi.com

MasimoSemiconductor.com

# Northrop Grumman opens access to US chip facilities

New business model aims to expand secure production of defence microelectronics on US soil

NORTHROP GRUMMAN has announced that its Microelectronics Centre is now open for external aerospace and defence companies to access the company's three US government-accredited semiconductor manufacturing facilities.

According to the company, this decision expands the secure production of defence microelectronics on US soil. The open-access business model allows commercial businesses, aerospace and defence companies, the US Government, academia, federally funded research and development centres and others, to design, manufacture, package and test microelectronics domestically for commercial and defence applications.

It will also give access to end-to-end US-based advanced packaging facilities with reliable semiconductor design, post-processing, assembly and test for current and future generation technologies.

Northrop Grumman-produced semiconductor products and components will also be available for purchase via an online storefront. Vern Boyle, vice president of the Northrop Grumman Microelectronics centre: "By opening our defence-grade manufacturing facilities to partners, Northrop Grumman is expanding and strengthening the resilience of

America's semiconductor industry and supply chain. We are providing partners with unprecedented access to design and develop domestic chips as well as the ability to directly purchase from us, enhancing collaboration across the broader defence industrial base."

Northrop Grumman's Microelectronics centre is comprised of three manufacturing facilities – two US government-accredited semiconductor foundries in California and Maryland and an advanced packaging facility in Florida.

Foundry services include silicon mixed-

signal, analogue, or digital ASIC's; GaAs or GaN compound semiconductor MMIC's; or power transistors in silicon or SiC.

The packaging facility is capable of 100 mm to 300 mm wafer bumping, probing, and dicing, which allows multiple smaller, specialised chips to be combined into a single, more powerful electronics package. Unlike traditional methods that place multiple chips side-by-side into a system, advanced packaging integrates multiple specialised chips together with high-density connections into a 3D chip stack.

**HORIBA**

**New Value in Wafer Inspection for Inspection Efficiency and Yield Improvement**

**Xtrology**

Fully Automated Thin Film Inspection System

- Film Thickness

- Defects Inspection

- Crystallinity

- Optical Properties

- Composition / Stoichiometry

- Stress

## Europe's tech giants unite to secure photonics future

Bosch, Volkswagen, Nokia, Zeiss, Trumpf and other industry leaders urge the EU to create €2 billion photonics programme

IN a joint statement, some of Europe's biggest industrial names, including Bosch, Volkswagen, Mercedes-Benz, Nokia Bell Labs, Zeiss, Trumpf, Ams Osram and EssilorLuxottica have urged the EU to create a €2 billion photonics programme in the next EU Framework Programme (FP10).

The call from companies across Europe's defence, automotive, healthcare, manufacturing, and telecoms sectors, aims to unlock €6-8 billion in private co-investment and secure Europe's tech sovereignty. They argue that without a bold and dedicated strategy, Europe risks falling further behind China and the US in the global race for photonics – the light-based technologies that underpin 20 percent of the EU economy.

The joint statement calls on the EU to establish a €2 billion stand-alone photonics programme under FP10; to launch Photonics Grand Challenge proposals in fields such as AI, space, quantum, and defence; and to strengthen resilient European supply chains for critical photonics components and materials.

"Photonics is the invisible force behind everything from AI and quantum computing to secure communications, energy, healthcare, defence, and mobility," said Lutz Aschke, president of Photonics21. "But Europe is at risk of losing its critical, competitive edge unless FP10 delivers a stand-alone €2 billion photonics programme, capable of unlocking €6-8 billion in industrial co-investment."

The signatories stress that photonics is one of the few digital technologies where Europe has long been a leader, but warn that China's share of the global photonics market has surged from 10 percent in 2005 to 32 percent in 2022, while Europe's has slipped to 15 percent.

"Photonics is a strategic technology for Europe's prosperity, autonomy, and security. This joint statement shows that Europe's industrial leaders stand united," said Aschke.

# Midas OD Grinder DRIVING INNOVATION IN SiC GRINDING

THE **IDEAL** MACHINE FOR

SiC GRINDING. BUILT TO

**YOUR** SPECIFIC NEEDS.

**QUALITY.**

OVER AND OVER AGAIN.

weldon

SOLUTIONS

**WELDON SOLUTIONS.COM**

**717-846-4000**

# Novosense, UAES and Innoscience join forces on GaN

Chinese trio sign agreement to reshape GaN power electronics for new energy vehicles

CHINESE FIRMS Novosense Microelectronics, UAES, and Innoscience have signed a strategic co-operation agreement to jointly advance GaN power electronics for new energy vehicles (NEVs).

The three parties will collaborate on next-generation intelligent integrated GaN products with Novosense bringing experience in analogue and mixed-signal IC design; UAES (a joint venture of Zhong-Lian Automotive Electronics and Robert Bosch) contributing knowledge in system integration and automotive applications; and Innoscience bringing expertise in GaN device technology.

Building on the combined expertise, the partners aim to tackle critical challenges such as efficiency, reliability and cost. They say the resulting new devices will deliver more reliable GaN driving and protection features, enabling higher power density and paving the way for commercial adoption across the automotive industry.

Xiaolu Guo, deputy general manager of UAES, said: "UAES has been at the forefront of automotive electronics for decades, consistently responding to industry needs through innovation. GaN technology is a vital enabler for vehicle electrification. Partnering with Novosense and Innoscience allows us to integrate capabilities from device to system level, driving

GaN industrialisation and delivering efficient, reliable and cost-effective solutions for our customers."

Shengyang Wang, founder, chairman and CEO of Novosense, commented: "Upgrading the NEV industry requires deep collaboration across the value chain. By combining UAES's system integration expertise with Innoscience's GaN leadership and Novosense's IC design capabilities, we are creating a powerful synergy. This strategic partnership sets a benchmark for industry collaboration, ensuring both technological breakthroughs and market value creation."

Jingang Wu, CEO of Innoscience, added: "The potential of GaN in automotive power electronics is only beginning to be realised. True impact will come from aligning device innovation with system requirements. We look forward to working closely with Novosense and UAES to extend the boundaries of GaN applications in automotive electrification and to translate technological advantages into tangible industry benefits."

**"The potential of GaN in automotive power electronics is only beginning to be realised. True impact will come from aligning device innovation with system requirements. We look forward to working closely with Novosense and UAES to extend the boundaries of GaN applications in automotive electrification and to translate technological advantages into tangible industry benefits"**

## Axcelis and Veeco to merge

AXCELIS TECHNOLOGIES and Veeco Instruments have agreed to combine in an all-stock merger. The resulting company is expected to have an enterprise value of around \$4.4 billion.

The combination will create the fourth largest US wafer fabrication equipment supplier by revenue, and will offer a product portfolio spanning ion implantation, laser annealing, ion-beam deposition, advanced packaging solutions and MOCVD.

"This combination marks a transformational milestone for both Axcelis and Veeco, establishing a new leader in semiconductor capital equipment with complementary technologies, a diversified portfolio and an expanded addressable market opportunity," said Russell Low, president and CEO of Axcelis.

He added: "We have long admired Veeco's history of innovation and its track record of delivering breakthrough products. I had the privilege of previously working at Veeco and I hold deep appreciation for its incredible talent, culture and innovation. Together, we will be well-positioned to serve large and growing end markets poised to benefit from significant secular tailwinds, creating exciting opportunities for employees and accelerating next-generation innovation for our customers."

"This merger capitalises on the core competencies of both Veeco and Axcelis to address our customers' critical needs," said Bill Miller, CEO of Veeco. "With increased R&D scale, the combination of these two exceptional businesses will accelerate our ability to solve material challenges, enable advanced chip manufacturing and build an even stronger company that can deliver superior value for all stakeholders."

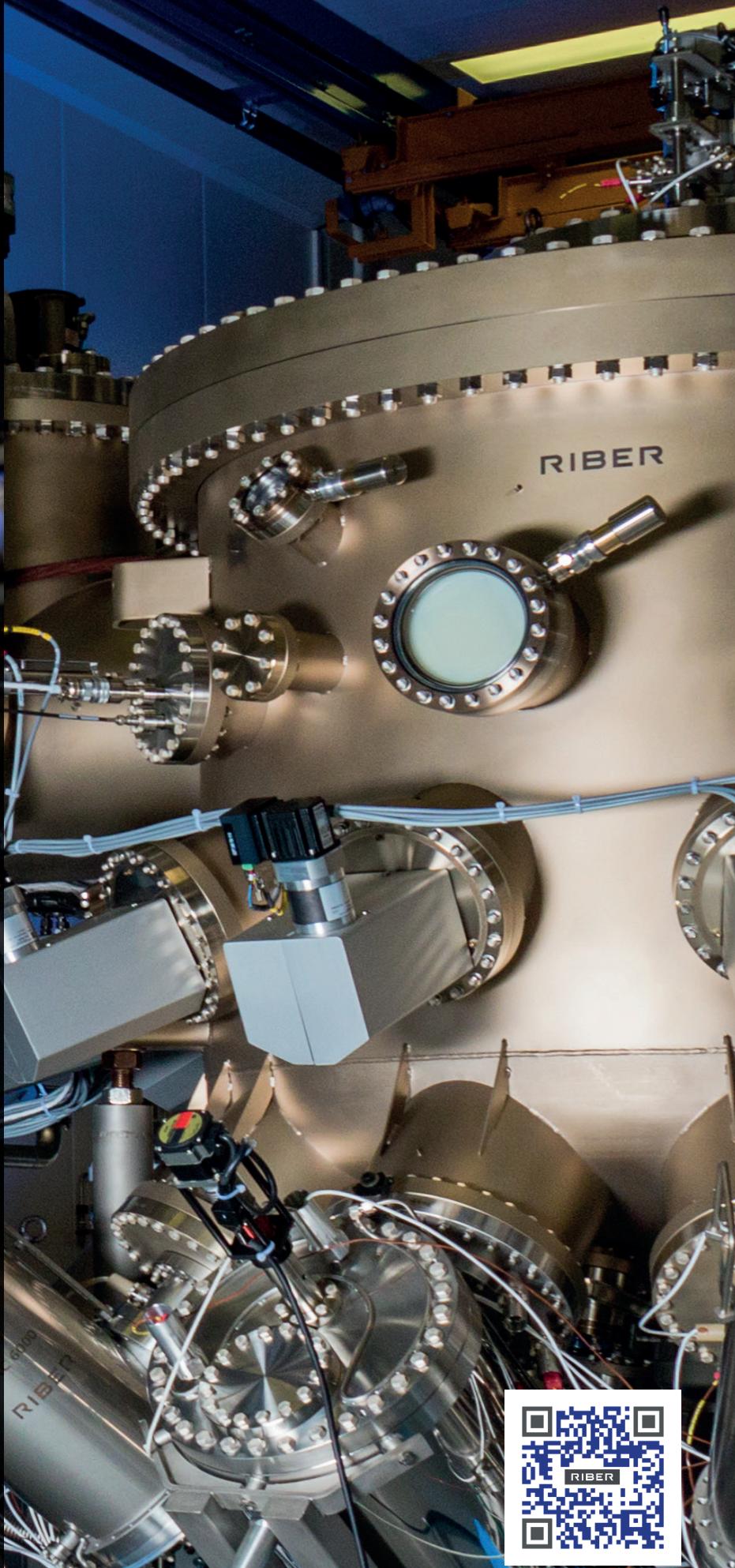

# RIBER's MBE 6000

**Leading

the way in mass-

production MBE**

**LOW RESIDUAL BACKGROUND**

**LOW ENERGY DEPOSITION**

**LOW TEMPERATURE**

**LOW DEFECTS DENSITY**

**CRYSTALLINE

PERFECTION**

**HIGH

UNIFORMITY**

**CONTROL AT

MONOLAYER

SCALE**

**HIGH

REPRODUCIBILITY**

**RIBER**

[info@riber.com](mailto:info@riber.com)

[www.riber.com](http://www.riber.com)

**INNOVATIVE SOLUTIONS FOR SEMICONDUCTOR INDUSTRY**

## UVC LEDs up their game

More powerful, efficient and longer lasting UVC LEDs are making a compelling case for water purification

BY RICHARD STEVENSON, EDITOR, CS MAGAZINE

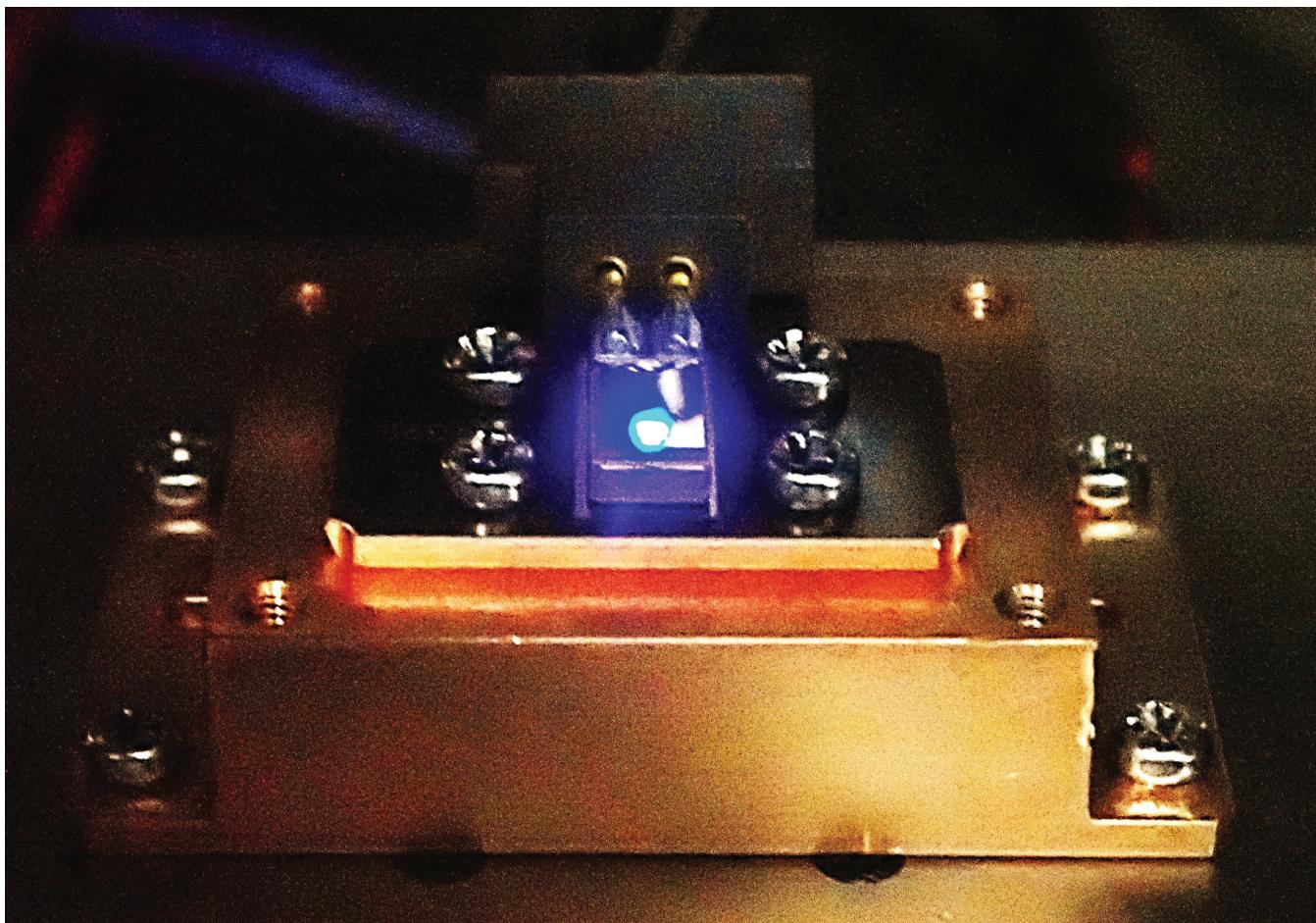

IN YEARS GONE BY, the performance figures for nitride-based LEDs operating in the deep-UV fell far short of those emitting in the blue. But differences in the key characteristics of these two emitters are narrowing all the time, and the metrics for UVC LEDs now feature a number of impressive specifications.

Take the recent announcement from ams Osram, for its latest generation of UVC LEDs, slated to enter volume production in just over a year. Its best 265 nm-emitters now deliver an optical output of 200 mW at a wall-plug efficiency of just over 10 percent, while offering a lifetime of more than 20,000 hours.

When commenting on these figures, ams Osram's Senior Key Expert for Applications, Alexander Wilm, refrains from singling out any one number. Instead, he claims that it's the combination of the three that's particularly impressive.

Wilm points out that there are UVC LEDs on the market that are more powerful, and also those with a higher wall-plug efficiency. "But having this efficiency at this output power and at more than 20,000 hours lifetime, that is something that is not that easy to do. That's why we think we are really unique."

The latest device from ams Osram has almost double the efficiency of its most powerful commercially available 265 nm LED, which delivers 115 mW at a wall-plug efficiency of 5.3 percent. And if the European opto-electronics powerhouse wanted to grab the headlines with an even higher wall-

► UVC LEDs have attracted much interest over many years for the disinfection of air and surfaces.

plug efficiency number than the 10.2 percent it is quoting for its latest devices, it could boast a value of almost 15 percent, realised by dialling down the drive current of its flagship LED to 20 mA.

"But then you only have 15 milliwatts, which is very little, so it will not help you in applications," warns Wilm, who is focusing on meaningful figures, and ultimately the practical deployment of ams Osram's products.

Recent improvements to the performance of the company's UVC LEDs have come through refinements to epitaxy, alongside

improvements in chip and package design.

Brighter, more efficient devices can be attributed to an increase in the conversion of electrons to photons, and to better light extraction from the chip.

"The biggest improvement we made is the new package," says Wilm. He explains that improving the interaction of the package and the chip has led to an increase in outcoupling of UV emission.

While there is much interest within the UV LED industry in AlN substrates that offer excellent thermal conductivity and lattice-matching with epilayers,

engineers at ams Osram are using sapphire substrates for their devices.

"Sapphire is a standard material for LED production. It's available, widely used, and the base for our other LEDs," remarks Wilm. "Right now, we believe that sapphire is the future for us."

### Covid's legacy?

During the height of the Covid-19 pandemic, UVC LEDs were widely viewed as an attractive option for killing this coronavirus. But since then, interest has dwindled in using this class of LED for that application.

However, Wilm does not see this as a major impediment for the future of the UVC LED, as by far its biggest application is water treatment, a multi-billion-dollar sector that's growing fast.

For water treatment, UVC LEDs compete with mercury lamps, the incumbent solution. Lamps emit significant powers, but have a number of weaknesses: they are bulky; fragile; they take several minutes to warm up; have a lifetime that's shorter than a UV LED (typically lasting 8,000 to 14,000 hours); and their disposal is far from trivial, due to the damaging effects of mercury on human health.

Another weakness of the mercury lamp is that its emission peak, fixed at 253.7 nm, is not ideal for water treatment.

"The peak of the germicidal effectiveness is at 265 nanometres," says Wilm, who adds: "We steered our LEDs exactly to this sweet spot."

There are a number of opportunities for UVC LEDs within the water treatment sector.

One is point-of-use, with solid-state emitters fitted to a water tap. And there is also what's referred to as point-of-entry, with water bombarded by UVC as it enters a home.

In both these cases, the UV source only needs to be on when water is flowing. As well as ruling out the mercury lamp for this application, due to its very slow warm-up time, this operating condition allows the driving conditions for the device to be adjusted, to get more out of the LED – and use fewer of them. As

► Point-of-use water treatment is an application where UVC LEDs are an ideal light source.

this solid-state emitter is off far more than it's on, it doesn't need a lifetime as long as 20,000 hours, so this can be traded for a higher output power, produced by cranking up the current.

Where the mercury lamp dominates is large-scale water treatment, associated with industrial and municipal

applications. In these cases, the UVC source is on all the time, and high powers are the key yardstick.

"200 [milliwatts] is a good starting point," says Wilm, who points out that even more powerful devices will follow. "If you compare it to five years back, the power that you got was around below 50."

Among the customers already buying UVC LEDs from ams Osram is Hergy International, a Taiwanese producer of water sterilisation equipment. 265 nm LEDs manufactured by ams Osram are deployed in Hergy's Perazim series of drinking water sterilisers, which include a model that processes 2 litres of water per minute while consuming just 3 W, and a variant that handles flows of up to 6 litres per minute.

When 200 mW UVC LEDs enter volume production towards the end of 2026 they may lead to an even more impressive range of products from Hergy – and they may be joined by more competitive rivals, given that ams Osram's more powerful 265 nm emitters will be available to all.

By then, ams Osram – as well as its peers – may have even reported more impressive results. After all, UVC LEDs are getting ever more powerful, efficient, and long lasting, and these trends show no sign of abating.

**For water treatment, UVC LEDs compete with mercury lamps, the incumbent solution. Lamps emit significant powers, but have a number of weaknesses: they are bulky; fragile; they take several minutes to warm up; have a lifetime that's shorter than a UV LED and their disposal is far from trivial, due to the damaging effects of mercury on human health**

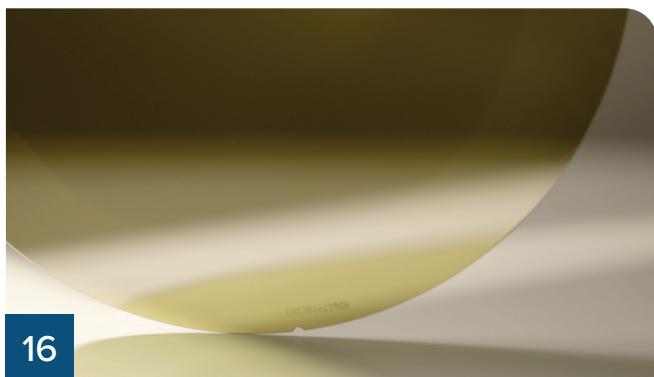

# Wolfspeed: Making material gains

The pioneer of SiC starts to offer 200 mm substrates and epiwafers to all

BY RICHARD STEVENSON, EDITOR, CS MAGAZINE

FOR THE last year or so, Wolfspeed has been in the news for the wrong reasons. Recent coverage of this SiC specialist has focused on its crippling debt, a filing for Chapter 11 Bankruptcy protection, and a global market softness that holds back its exploitation of a vastly expanded production capacity.

These ferocious headwinds have caused the company to lay off many staff, and are behind a share price that's fallen through the floor.

However, over the last few weeks Wolfspeed has started to change the narrative. Helping to drive this are a filing of positive press releases: one details a financial restructuring process that has enabled the company to emerge from Chapter 11 protection and substantially reduce its debt – a good move, but one that's been very, very hard on existing shareholders; and another outlines the opening up of its 200 mm substrate and epiwafer expertise to all.

In the halcyon days of the SiC industry, when global substrate supply struggled to keep pace with demand, Wolfspeed signed a handful of substantial wafer supply agreements totalling around \$2 billion. These deals enabled the likes of Infineon, STMicroelectronics, onsemi and Rohm to secure 150 mm SiC substrates from the world's leading supplier.

Last year Wolfspeed started to expand this side of its business by offering its 200 mm substrates to selected high-volume customers, while fine-tuning material specifications. And now it's gone one step further, opening up this product to all.

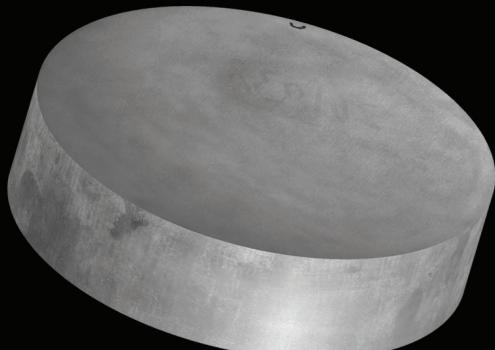

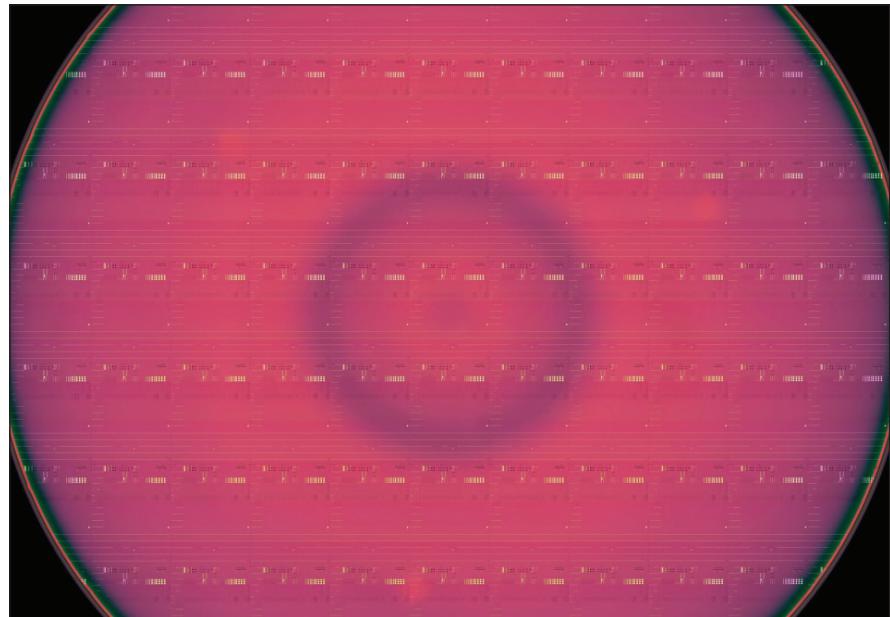

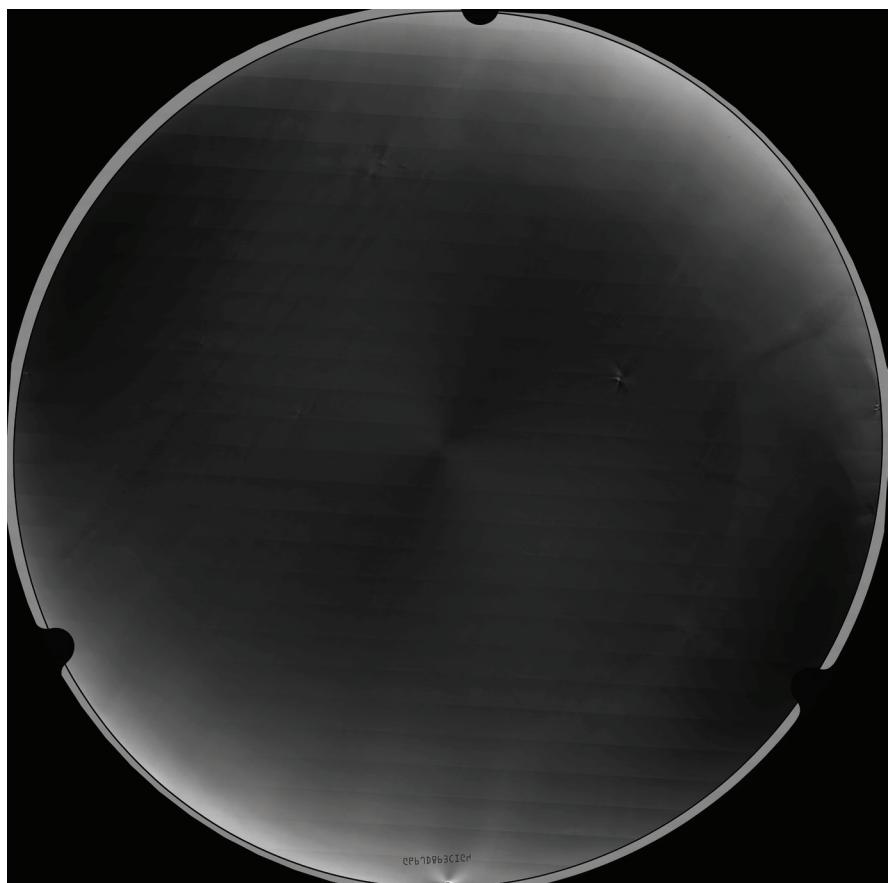

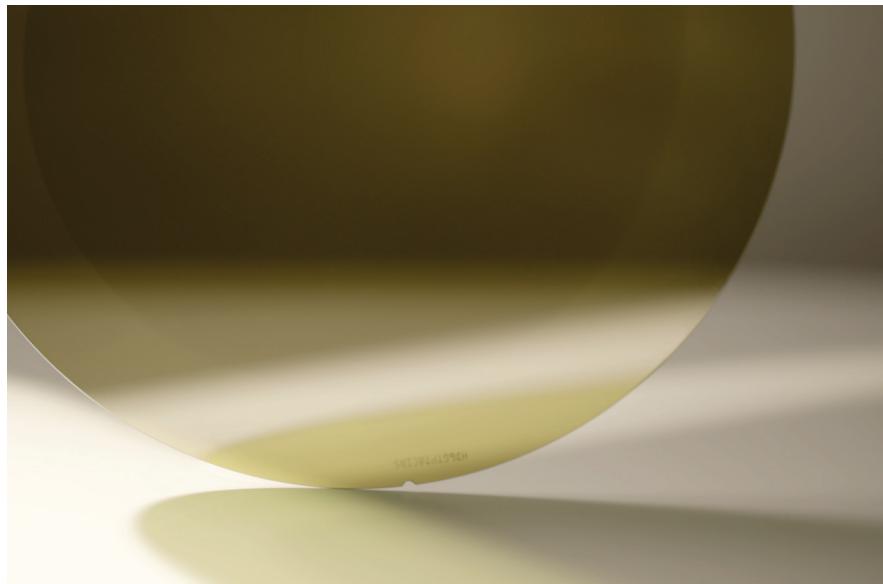

► The uniformity in the cross-polarised image underscores the quality of Wolfspeed's 200 mm substrates.

According to Cengiz Balkas, Wolfspeed's Chief Business Officer, this latest step reflects the company's readiness to supply the industry with the quality and volumes of 200 mm SiC that will be needed.

"We've gone through these wafer transitions many times in our history," says Balkas, who explains that migrations from one diameter of substrate to a larger variant always

begin with internal use of the larger size. "Once we go through that initial heavy lifting of getting everything settled in, we come to market and start ramping our commercial customers."

For the company's 200 mm format, substrates are manufactured at its historic facility in Durham, North Carolina, with production of SiC MOSFETs and Schottky barrier

diodes undertaken at the device factory in Mohawk Valley, New York.

As Wolfspeed is the largest consumer of 200 mm substrates, used to make its 600 V, 1200 V and 1700 V SiC MOSFETs and Schottky barrier diodes, it's of no surprise that the majority of this material is deployed for internal chip production. "But we definitely have enough volume to start ramping our customers," says Balkas.

### Quantity and quality

Any chipmaker that uses Wolfspeed's 200 mm substrates will not trade a larger size for inferior quality. "They're definitely better than our 150 mm wafers millimetres," says Balkas, explaining that they have lower densities of micropipes, screw dislocations and basal plane dislocations, as well as a lower residual stress and better surface parameters.

Improvements in material quality will continue at Wolfspeed, and while efforts are focused on the 200 mm format, insights into how to produce better boules will be applied to the manufacture of 150 mm products.

For all forms of SiC substrate, Wolfspeed will be following the well-known pathway for the semiconductor industry, making substrates better and cheaper over time. According to Balkas, the cost-per-unit area of the company's substrates is on a "pretty significant reduction curve".

Prices that customers pay for this format are confidential, and will depend on volume. It's possible that those switching from 150 mm to the larger format will initially pay more per-unit-area when ordering small quantities to get going, but as volumes increase for both the customer and Wolfspeed, the larger format will be the more economical one.

Spurred on by the growth of the SiC market, more companies are producing substrates, with Wolfspeed facing particularly fierce competition from China. According to the market research firm Yole, Wolfspeed is still the clear leader in this sector, but its market share is in decline.

In any market, rivals always look for factors that allow them to stand out from the crowd. Viewed in these terms,

Balkas believes that Wolfspeed's vertically integrated approach gives it a crucial edge.

"We make automotive-qualified power devices in our New York factory," says Balkas, who points out that this allows Wolfspeed to have a credible case when customers consider placing orders for 200 mm substrates.

A number of producers of SiC substrates are looking to raise their profile by showcasing 300 mm substrates. While this is an impressive feat, it is far from clear how long it will be until high-volume production of SiC power devices even begins on 300 mm lines.

"For us, next steps are to get through the 200-millimetre transition and ramp the industry on 200-millimetre. It looks pretty early to me to discuss 300-millimetre," argues Balkas.

### Outsourcing epitaxy

Within the wide bandgap power electronics industry, many of the producers of GaN HEMTs are fabless, while the SiC sector is dominated by those with their own production lines.

Given this, one may not expect much demand for SiC epitaxy. But there is, and always has been, according to Balkas.

"What we see, especially in the early stages of a diameter change, is that our customers really have a need for epi services. If I look at the 150 mm-millimetre long-term agreement, we

had a significant amount of 150 volume – that was a combination of availability of epi, quality of the epi, and the pricing that we can offer."

For epitaxy on 200 mm SiC, Wolfspeed offers thickness and doping uniformities of  $\pm 8$  percent and  $\pm 12$  percent, respectively, as baseline specifications – figures derived by considering all points within an area that's defined by edge exclusions of 3 mm for usable area, and 4 mm for doping uniformity. Useable area is more than 85 percent, for a 5 mm by 5 mm grid.

Those impressed with these figures and interested in securing these epitaxial services should have no concerns whatsoever related to Wolfspeed keeping their IP completely confidential.

"We're extremely proud of our history and reputation in the market," says Balkas, who reveals that the company has multiple protection rules to prevent any customer information relating to their epiwafer design from reaching those within the company that work on Wolfspeed's own devices. "Our track record is spotless."

By combining epitaxial services on 200 mm SiC with substrate access to all, Wolfspeed is in a great position to lead this industry's production of power devices on the larger format. It's a significant milestone that will be welcomed by producers of SiC MOSFETs and Schottky barrier diodes. But only time will tell how much this will do to help to revive the fortunes of Wolfspeed, and fill its vastly expanded capacity.

# GaN: Tracking fast-charging with 'Lichi Law'

All forms of GaN fast charger are delivering an increase in output power of around 50 percent every 12 months

BY XINKE LIU FROM SHENZHEN UNIVERSITY

THE SILICON INDUSTRY is well-known for its laws. The most famous of these, attributed to Intel co-founder Gordon Moore, states that the number of components on an IC doubles every year. And also known to many is the law formulated by Robert Denard: as transistors are reduced in size, there's no change in power density, as voltage and current scale with the length of the channel. Note, however, that since the mid-noughties, it appears that Dennard scaling has broken down.

There are also laws within the compound semiconductor industry. Maybe you have heard of Haitz's law, which states that every decade the LED's cost-per-lumen falls by a factor of ten, and that for a given wavelength, the light generated by a packaged device increases by a factor of 20. And more recently, thanks to the efforts of a Chinese collaboration that I am involved with, there's 'Lichi law', describing the performance changes associated with GaN charging, named after the lychee

trees that are near my laboratory at Shenzhen University.

Over the last few years sales of GaN power devices have rocketed, following their adoption into consumer fast-charging products. Our collaboration has been delving into performance-related aspects of this, by conducting in-depth market research, and back in 2023 we identified the development laws at that time, leading us to propose Lichi law – it states that, on average, for every 12-month interval, the output power of commercial GaN fast chargers increases by about 50 percent. Two years on, we have found that consumer GaN fast charging is still following Lichi Law, and the industrial market is now enjoying similar dynamics.

To illustrate this rapid rise in output power, consider that back in 2018 the Anker GaN fast charger launched to market delivered just 30 W. While impressive at the time, a number of brands are now launching products

with an output power of more than 300 W, and a power density exceeding  $3.3 \text{ W cm}^{-3}$ .

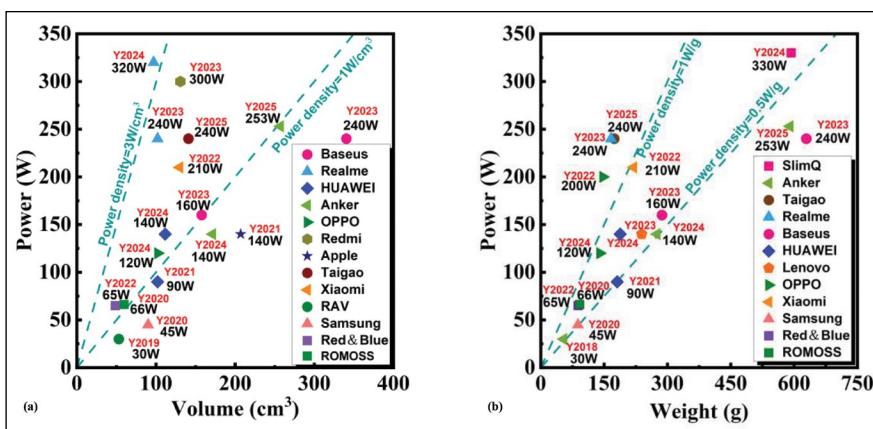

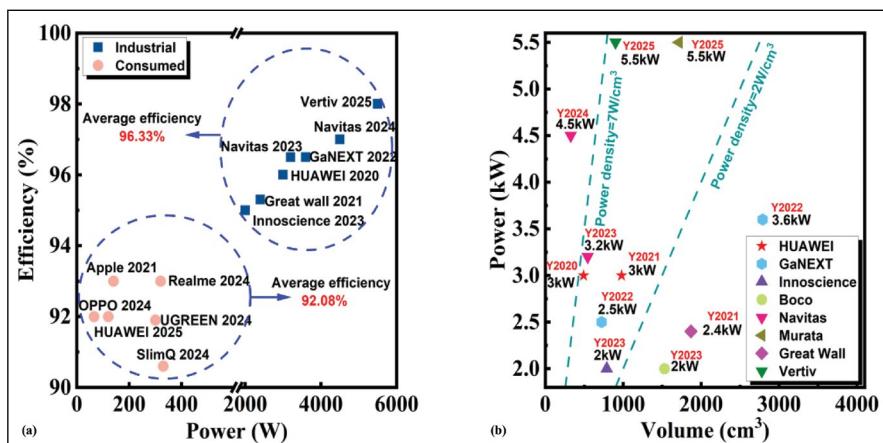

Our work includes a survey for 3C certification data of GaN fast-charging products, which has enabled us to produce a visual comparison of the power parameter distribution of products listed in different years (see Figure 1).

Based on this data, one can see that fast-charging products before 2021 are predominantly concentrated below  $1 \text{ W cm}^{-3}$ , with power density generally in the range  $0.7\text{--}0.9 \text{ W cm}^{-3}$ , reflecting the state of maturity of early GaN technology. By 2023, most fast-charging products surpassed  $1 \text{ W cm}^{-3}$ , with some even exceeding  $2 \text{ W cm}^{-3}$ , which may be the industry's first experimental high-density products. Fast-charging products are clustered in the  $1\text{--}3 \text{ W cm}^{-3}$  band from 2024 to 2025. So far, the maximum power density is  $3.3 \text{ W cm}^{-3}$ , but a few products are appearing at around just  $1.8 \text{ W cm}^{-3}$ , reflecting the technology stratification of the market – some vendors are pursuing the ultimate density, while others are focused on cost and stability.

Looking at the distribution of the mass of these chargers (see Figure 1 (b)), it is clear progress has been made. In 2018, when Anker introduced the first 30 W GaN fast charger, it had a mass of 54 g and a power density of only  $0.53 \text{ W g}^{-1}$ . In 2022 OPPO broke new ground, with its 200 W GaN fast charger with a mass of 147 g and a power density of  $1.36 \text{ W g}^{-1}$  – this was the first fast charger to break through 200 W and have a power density of over  $1 \text{ W g}^{-1}$ .

► Figure 1. (a) GaN fast-charging output power-product volume diagram. (b) GaN fast-charging output power-product quality diagram.

Since then, Realme and Taigao have raised the bar, launching 240 W GaN fast chargers with power densities of 1.44 W g<sup>-1</sup> and 1.37 W g<sup>-1</sup> in 2024 and 2025, respectively.

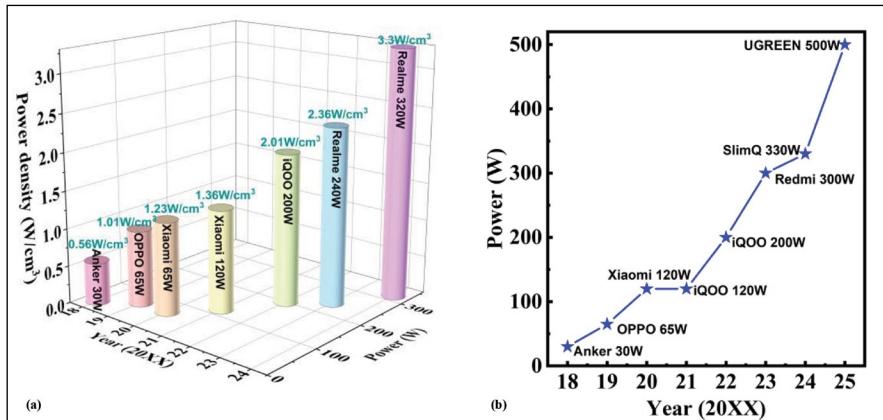

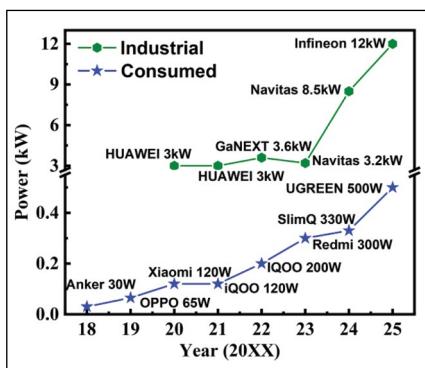

We have also collected data on the maximum power and power density of GaN fast-charging products over time, and plotted power density growth (see Figure 2 (a)) and power growth (see Figure 2 (b)). These graphs show that power and power density rise over time with a rate of increase that's highly consistent with the previously proposed 'Lichi Law' – that is, for every 12 months, the output power of commercial GaN fast-charging power units increases by about 50 percent.

Another observation is that GaN technology is accelerating its penetration from consumer-grade fast charging to industrial-grade power supplies, a trend that began in 2020. This finding has come out of conducting a comprehensive study, spanning 2018 to 2025, of consumer-grade fast charging and industrial-grade GaN power products (see Figure 3).

Compared to consumer-grade GaN fast-charging products, industrial-grade GaN power supplies are on average 4 percent higher, in terms of efficiency, and more than threefold higher, in terms of power output.

We have also determined that GaN has been more widely and deeply applied in the industrial sector, and its high-power, high-efficiency characteristics can be given full play in industrial scenarios, where it can fulfil demand for high-performance power supplies for industrial equipment.

Our extensive investigation of market dynamics has also identified a clear trend in increasing output powers. Between 2020 and 2021, we found that GaN technology was mainly verified in the initial stage of low and medium power scenarios. An example of this is Huawei's launch of 3000 W products with the potential for power density improvement. Come 2022, GaNEXT launched 3600 W GaN server power supplies with a 20 percent increase in power over their predecessors, but still with lower volumes and efficiencies, due to packaging technology. At that time, the average power density of these industrial power supplies

► Figure 2. Consumer GaN fast charging in recent years, evaluated in terms of (a) power density and (b) power.

► Figure 3. (a) Efficiency-power diagrams for industrial and consumer GaN power supplies. (b) Power-volume diagram for industrial GaN power supplies.

did not exceed 5 W cm<sup>-3</sup>, with sales predominantly oriented to lightweight scenarios, such as edge computing.

The last few years have seen significant progress. Since 2023, Navitas has made breakthroughs in GaN server power supplies, with power densities

ranging from 5.88 W cm<sup>-3</sup> for 3200 W products in 2023 to 13.79 W cm<sup>-3</sup> for 4500 W modules in 2024, representing a 134 percent increase in volumetric efficiency in two years. At this point GaN technology began to be scaled for data centre applications, with an 8500 W prototype unveiled in 2024 with a 136 percent power increase from 2022, marking a breakthrough for GaN in medium-to-high power boundaries.

When deployed in industrial GaN power supplies, the power output density of GaN is generally within the range 3-6 W cm<sup>-3</sup>. Underscoring the outstanding advantages of GaN in industrial applications, that power output density is two-to-three times higher than that in consumer GaN fast charging.

Our comprehensive study of the evolution of GaN in power charging includes a review of peak power data of industrial GaN server power supplies, and parameters of consumer-

► Figure 4. GaN consumer-grade fast charging and industrial-grade power supply development.

grade products. This has enabled the construction of a power-year coordinate system, and a comparative chart of power evolution technology development between industrial and consumer fields (see Figure 4).

By undertaking a thorough analysis of this chart, we have observed the trajectory of GaN technology. Our data shows that the performance

improvement for GaN power devices is highly consistent with 'Lichi law'. Specifically, the output power of industrial-grade GaN power supplies increases by about 50 percent every 12 months.

We can conclude that through our study of consumer-grade GaN fast charging and industrial-grade GaN server power supplies, the output power of GaN fast charging tends to increase by about 50 percent every 12 months.

● *Contributors to Lichi's Law include: Zhixiang Zhong, Yutong Wu, Bing Jiang and Hezhou Liu from Shenzhen University; Jingbo Li from Zhejiang University; Jinping Ao from Jiangnan University; Lixuan Chen from Unilumin Group Co., Ltd; Yuxi Wan and Daohua Zhang from Shenzhen Pinghu Laboratory; Zhanwu Yang from Red & Blue Microelectronics (Shanghai) Co; and Shengsen Chen from Cotell Intelligent Technology (Shenzhen) Co. Ltd.*

► Every March, the fragrance of lychee flowers flows through the Li-Garden at Shenzhen University. For the next few months, as the lychee heads towards a full blossom, it's attractive to sit beside these trees and ponder. During such times, the initial ideas were formed on the possibility of a law related to progress in GaN power chargers.

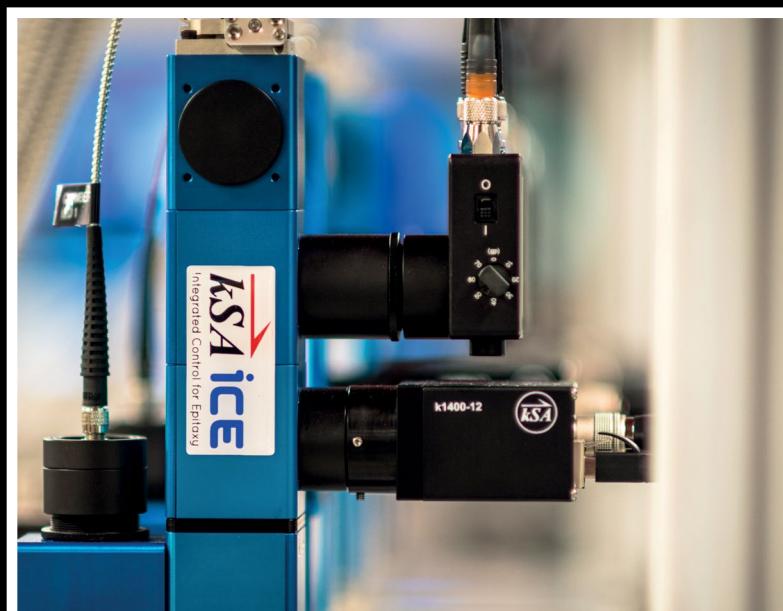

## kSA ICE for MOCVD and MBE

### Real-time Deposition Monitoring

- Real-time temperature, curvature, growth rate, reflectivity, and more

- Custom configured for your chamber geometry

- Plus the best support in the industry

- Learn more by visiting our website: [k-space.com](http://k-space.com)

*Putting Light to Work*

Since 1992

# ANGELTECH

**SAVE THE

DATE

20-22

APRIL

2026**

**Sheraton Brussels

Airport Hotel**

To find out more about our sponsor and speaker

opportunities, contact us today on:

+44 (0) 2476 718970

or email:

[info@csinternational.net](mailto:info@csinternational.net)

[info@picinternational.net](mailto:info@picinternational.net)

[info@peinternational.net](mailto:info@peinternational.net)

[info@angel-tech.net](mailto:info@angel-tech.net)

## Taking the guesswork out of **SiC production**

Thanks to advances in metrology, it's now possible to scrutinise a SiC puck before it's wafered and identify material defects that govern yield and profitability

BY IVAN ORLOV, CAROLINE CHÈZE AND FRÉDÉRIC FALISE FROM SCIENTIFIC VISUAL, AND MARKUS STÖHR AND MICHAEL SCHÖLER FROM PVA TEPLA

WITHIN the semiconductor industry, SiC is a transformative material. This wide bandgap compound drives innovation in power electronics, electric vehicles, renewable energy and advanced communications, thanks to its remarkable properties that include a high electron saturation velocity and breakdown field, exceptional thermal conductivity and mechanical robustness. These strengths enable diodes and transistors to operate at higher voltages, higher frequencies and more extreme temperatures than ever before.

We have been closely following the evolution of SiC and have witnessed staggering progress that's been made over the last three decades to position this material as the backbone of efficient power electronics. We're not alone in knowing there's far more to come, with many forecasting SiC will remain central to the industry for the foreseeable future.

While today SiC is seen almost exclusively as a material for high-performance power devices, its potential extends to several other promising applications, including AR glasses, interposer layers in advanced packaging, data centers, and AI chips.

All these applications are leading to an increase in demand for high-quality substrates at accessible prices. There is plenty of headroom when it comes to improving the quality and, especially, the yield of SiC material. These improvements, however, are hindered by crystalline defects that impact device performance and reliability.

To name just a few examples, there are micropipes that threaten to trigger leakage currents and breakdown, basal plane dislocations and stacking faults that cause bipolar degradation, and polytype regions that may lead to premature failure.

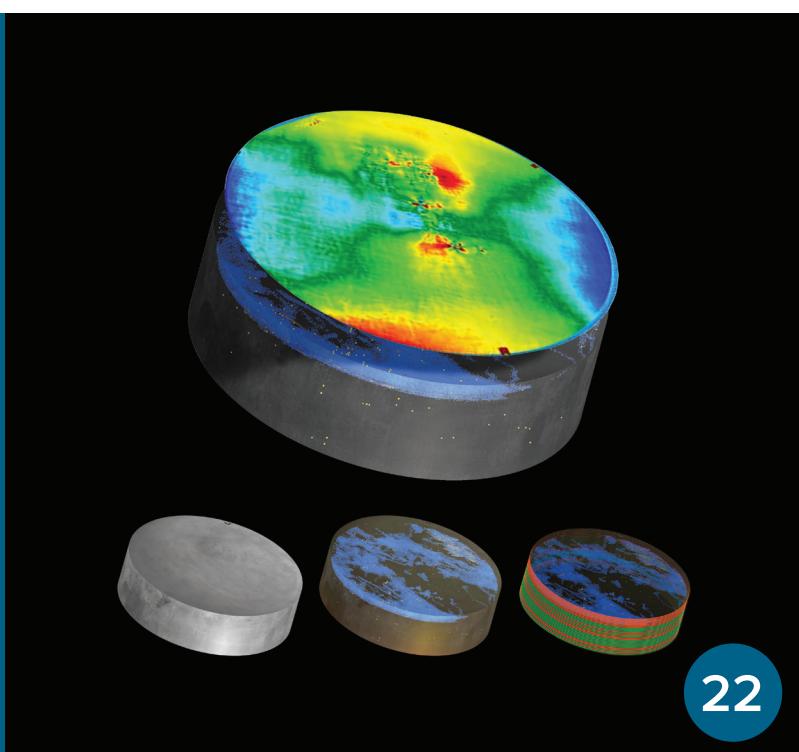

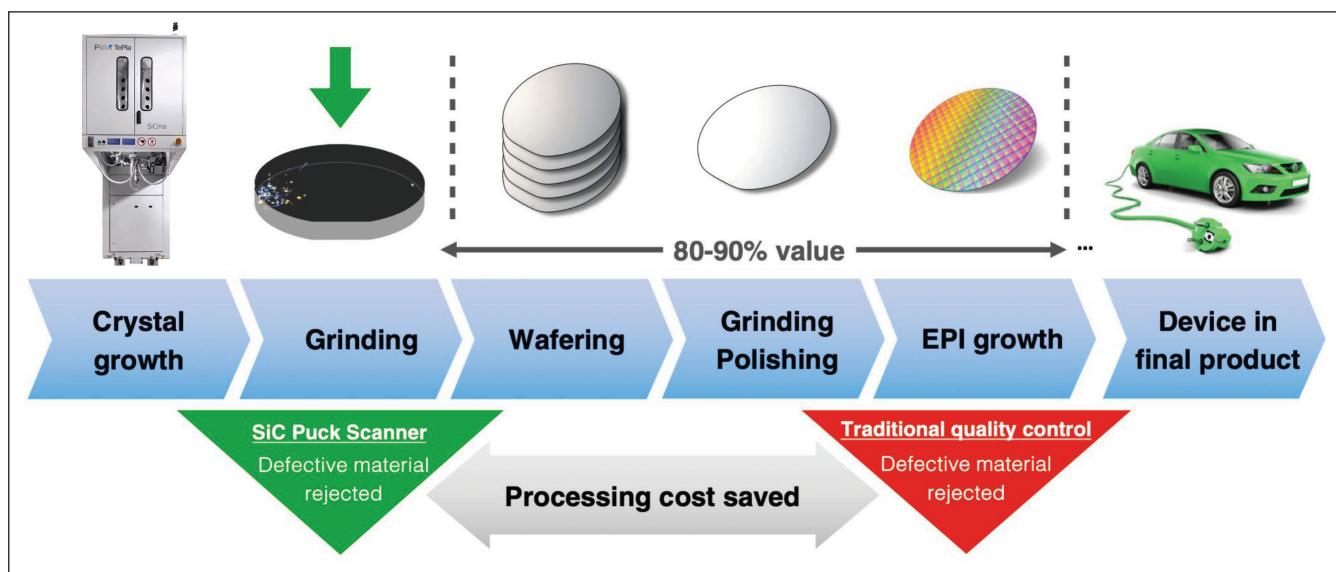

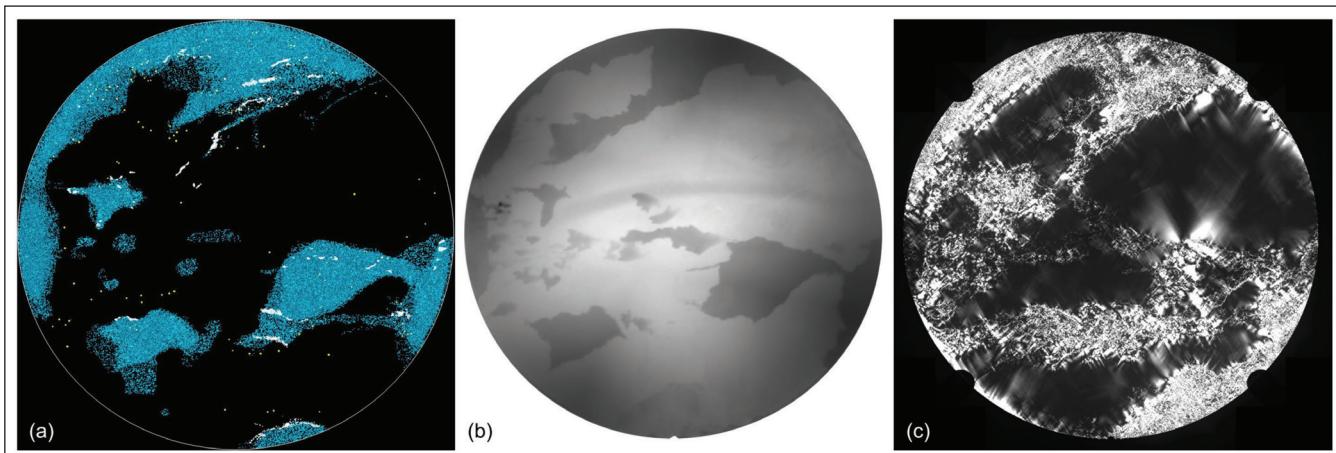

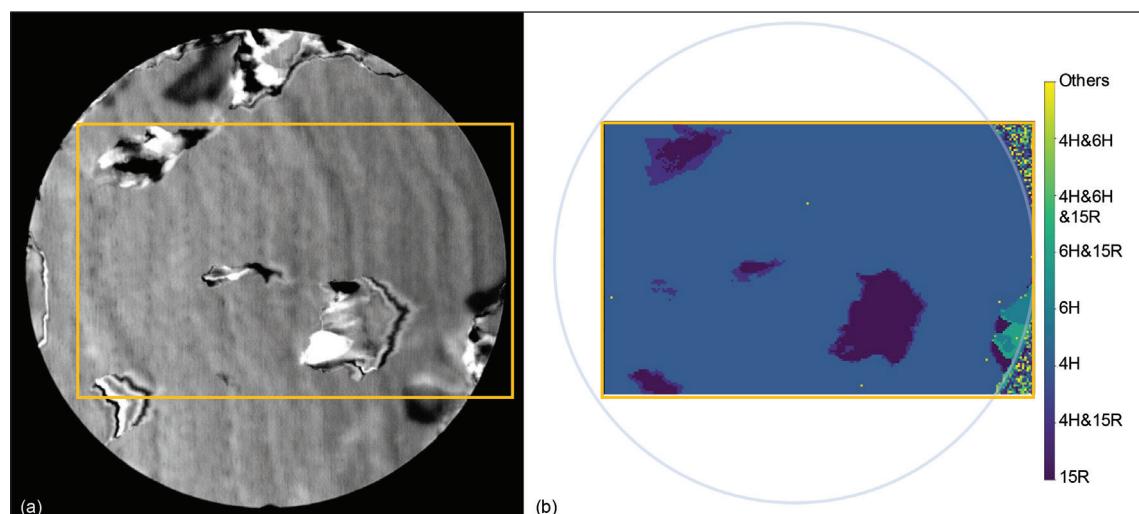

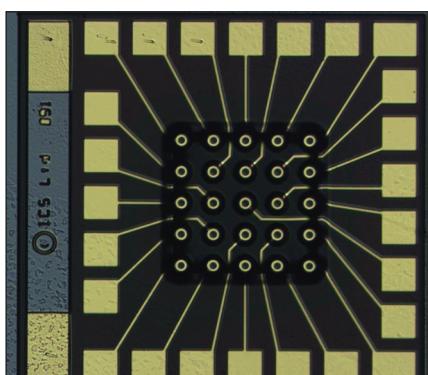

To mitigate these risks, it is imperative to identify and reject 'killer' defects. However, today's practice is to undertake comprehensive defect inspection at the wafer stage (see Figure 1) – and we would argue that's too late, given that by then significant time and cost have already been invested in slicing and polishing.

It's easy for downstream device makers and final users to overlook the significance of this problem,

because defective material is filtered out earlier in the chain. Yet, the associated cost is built into every SiC device.

To fully understand the importance of this issue, note that substrates can represent up to 40 percent of the final device cost, and SiC material yields can be as low as 50 percent. Thus, continuing to only detect 'killer' defects at the wafer stage is a substantial cost barrier to mass adoption of SiC.

As SiC utilisation accelerates, our industry faces a pressing question: How can manufacturers ensure a high substrate quality while increasing wafer diameter? In response, PVA TePla and Scientific Visual now offer pioneering metrology solutions that redefine quality control for SiC.

### The SiC Puck Scanner

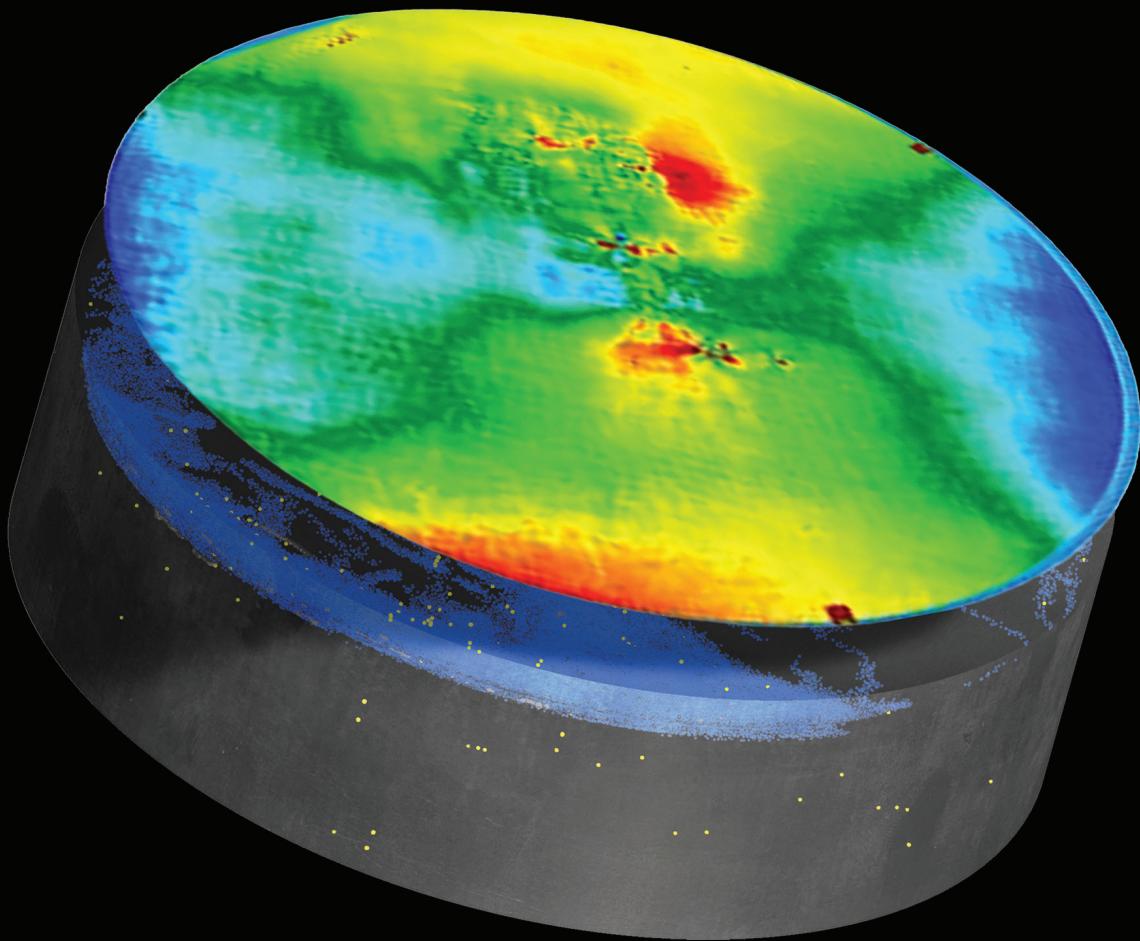

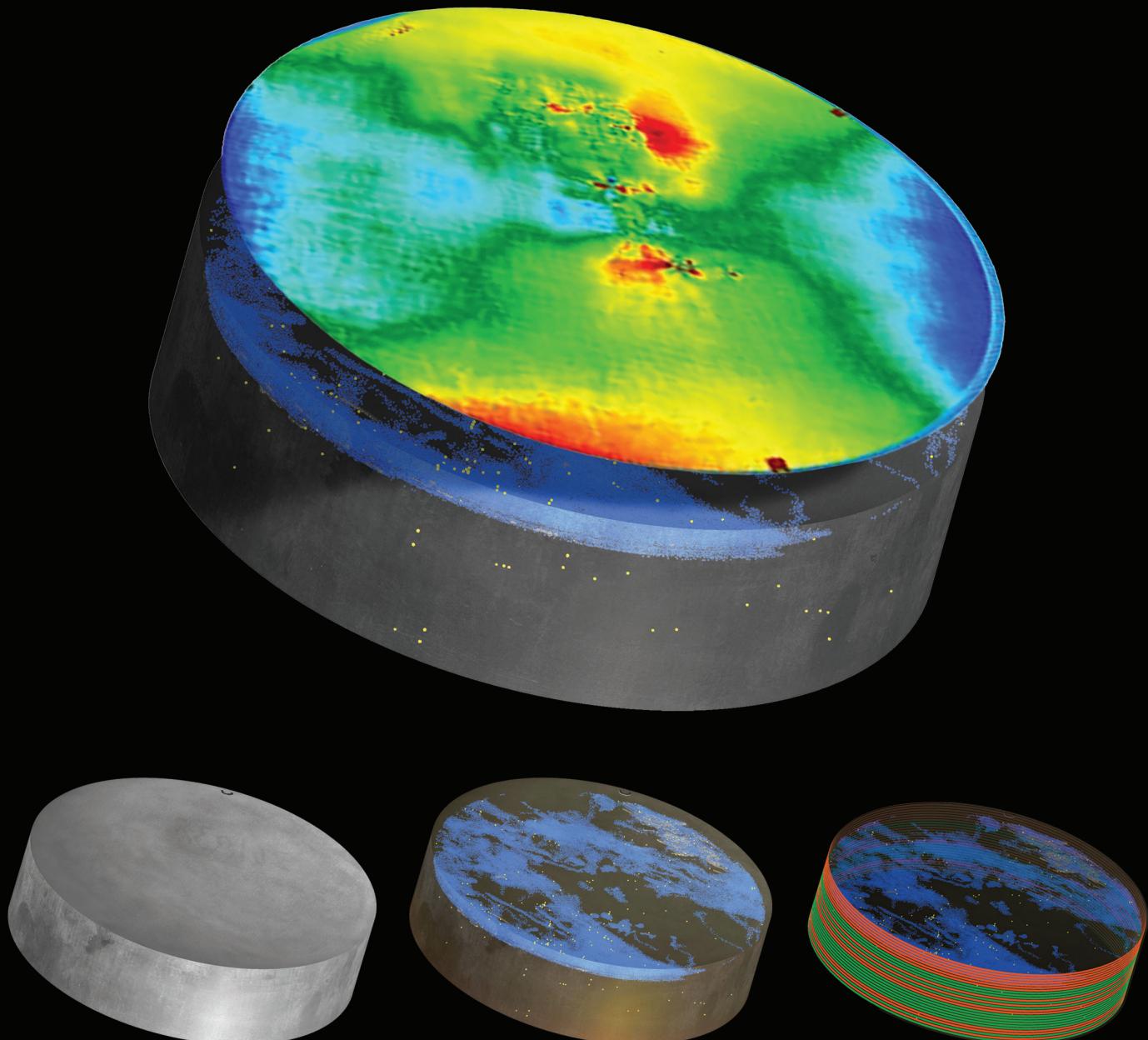

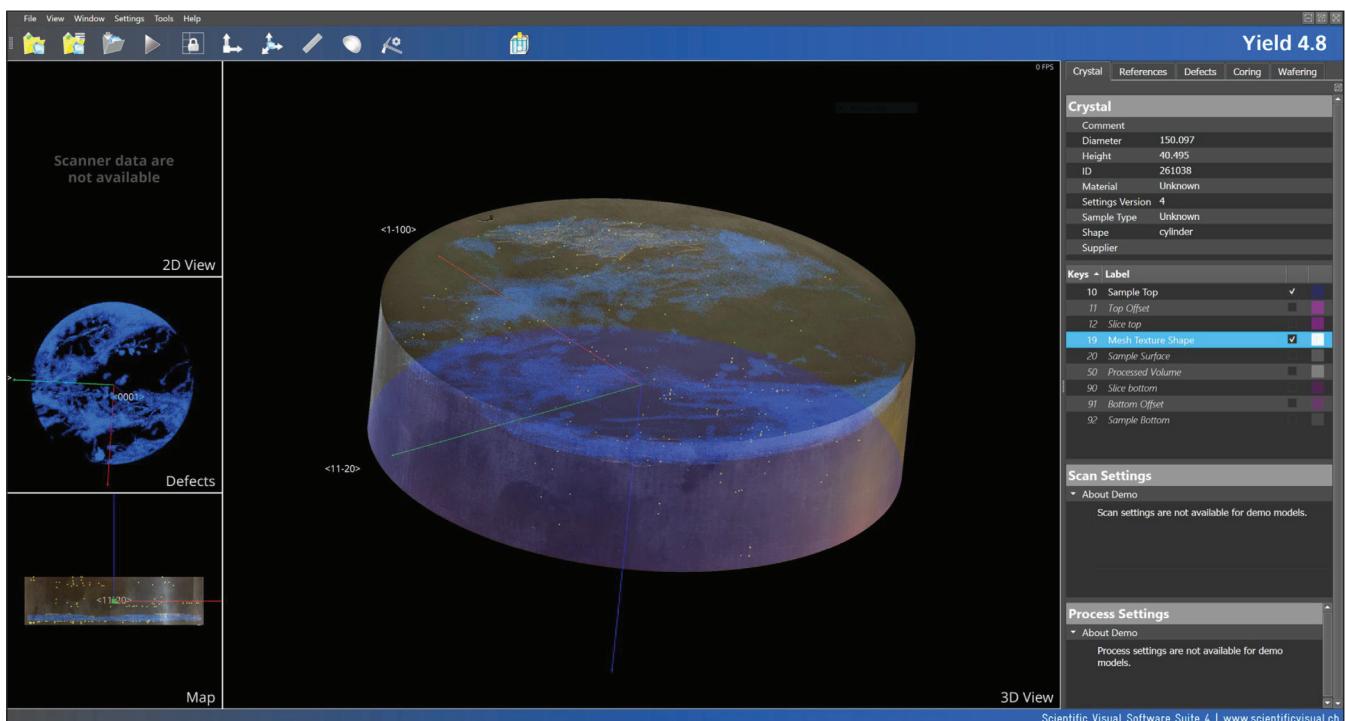

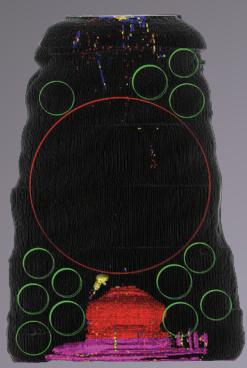

This September we unveiled the new SiC Puck Scanner at the International Conference on SiC and Related Materials, in Busan, South Korea. It is the first system to deliver non-destructive three-dimensional defect mapping directly within the puck volume (see Figure 2). It's a game changer, leveraging advanced tomography to visualise critical defects before any wafering or costly processing begins.

With this tool, sub-standard pucks can be set aside prior to the costly wafering stage, allowing manufacturers to dedicate their slicing capacity solely to high-grade material. For the first time, producers can apply reproducible, quantitative defect metrics rather than relying on subjective visual checks.

A further advantage is that the scanner enables SiC substrate makers to move beyond 'one-size-fits-all' decisions and instead adopt more tailored wafering strategies.

► Figure 1. Traditionally, the first comprehensive control of SiC defects in the production chain takes place at wafer level (red triangle), when substantial resources have already been devoted to processing. The new SiC Puck scanner shifts the quality control to an earlier stage (green triangle).

► Figure 2. 3D defect map – output of the SiC Puck Scanner. Shown here is the puck that's been used for the end-to-end study. Scans reveal lattice defects with micron-scale resolution, including polytypes, micropipes, voids, inclusions, dislocation clusters, and others. Colours correspond to defect morphology.

For instance, by drawing on precise defect coordinates, manufacturers can optimise wafering strategies by specifying the optimal cut levels. In case of wire-saw slicing, the goal is to position more defects within the kerf, thus excluding them from future wafers. This is achieved through Smart Wafering, a computer-aided patent-protected routine embedded in the YieldPro software that computes the most efficient puck position (offset) in a wafering system. As an example, we measured a 7 percent or greater increase in quality wafers compared to the ‘blind’ wafering in low- and mid-defective pucks.

In laser wafering, this technique allows one to identify suitable slicing regions and skip overly defective areas that could distort the cleaving track. Maximising yield is achieved by reducing processing, and delivering more high-quality material – all without expanding growing capacity. Additionally, each puck can be assigned to applications most aligned with its defect profile.

Volumetric defect mapping allows manufacturers to make data-driven decisions at the earliest possible point in the production chain. In practice, we have found that up to 50-60 percent of the wafering cost

can be preserved by rejecting defective material early, rather than scrapping wafers after processing. Furthermore, digital maps provides transparent quality data that can be shared with colleagues and customers.

The benefits of puck scanning extend well beyond immediate cost savings. Scanning also serves as a tool for rapid improvement of bulk SiC growth. Each crystal defect is a message about a growth issue. Interpreting these messages promptly is key.

A traditional quality feedback loop involves puck wafering, wafer-level inspection, and a subsequent feeding of quality measurements back to the crystal growth team – a process that often takes months, with the message arriving too late to take corrective measures. The original wafer sequence in the puck is frequently lost, hindering efforts to trace the stack of defect formation in the puck. The puck scanning keeps the information and shortens the feedback loop to just a few hours. Now growth teams can inspect the furnace output almost instantly (grinding is still needed), and adjust parameters prior to starting the next growth cycle. For the first time, producers can quantitatively measure

The benefits of puck scanning extend well beyond immediate cost savings. It also serves as a tool for rapid improvement of bulk SiC growth. Each crystal defect is a message about a growth issue. Interpreting these messages promptly is key.

Large stock of Molybdenum and Tantalum

All parts made according to drawings in these materials

## MICRO-MECHANICS ON STRATEGIC MATERIALS

- In stock for all vacuum and ultra vacuum applications :

**Molybdenum and Tantalum screw products**

(screws, nuts, rings) « Usable in Clean Rooms »

- In stock for laboratory machines :

**Standard substrate support (Molybloc)**

Dimensions :

- 1 1/2 inches

- 2 inches

- 3 inches

Possibility of substrate support with cavity and washer, on request and according to drawings

- Stock of platens blanks for all types of MBE from various manufacturers.

- « Usable in clean rooms » **Platens and washers** produced according to drawings.

Cleaning and Dégassing

**RABOUTET SA**

Avenue Louis Armand • B.P. 31 • 74301 Cluses Cedex FRANCE

T. +33 (0)4 50 98 15 18 • [info@raboutet.fr](mailto:info@raboutet.fr)

[www.raboutet.fr](http://www.raboutet.fr)

## III/V-Reclaim

More than just reclaiming...

*Sustainable

Innovative

Unique*

### Materials

GaAs

InP

Ge

GaSb

InSb

GaP

InAs

AlN

**Epi polishing**

low removal process for epitaxial layers to enable direct bonding

**Backside thinning**

down to 50 micron

[sales@35reclaim.com](mailto:sales@35reclaim.com)

[www.35reclaim.com](http://www.35reclaim.com)

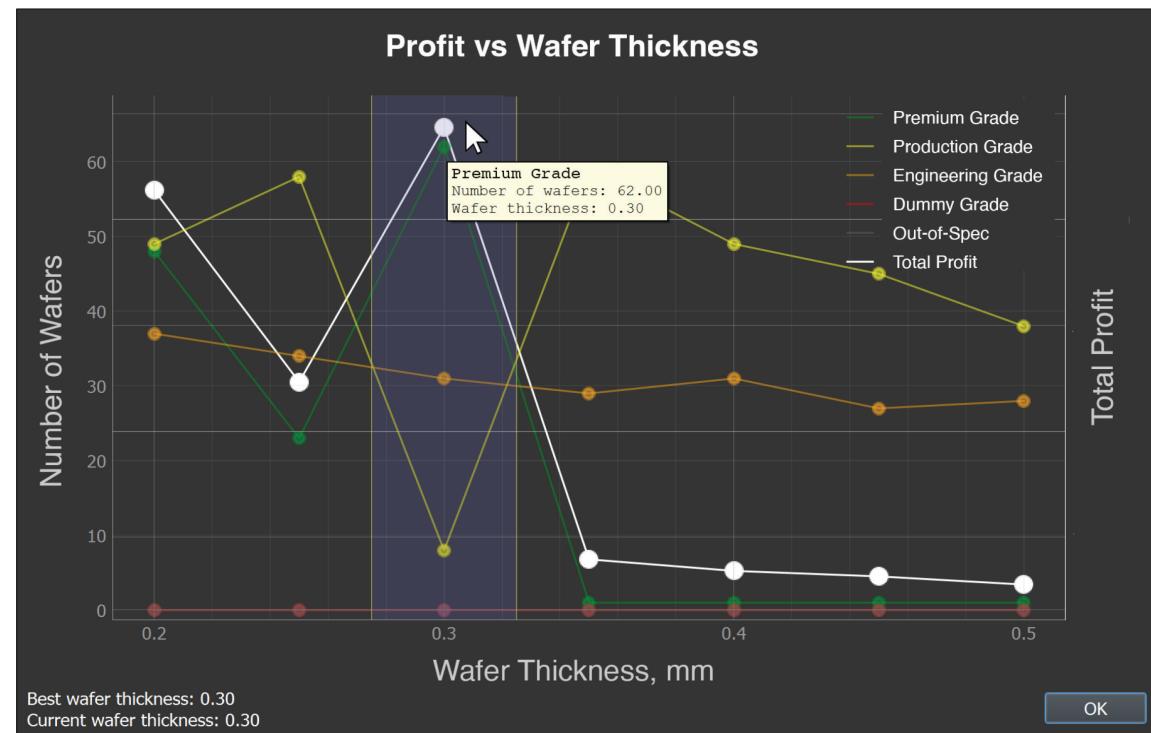

► Figure 3. Profitability plot of a puck processing. It shows profit as a function of wafer thickness, taking into account defect distribution, as well as wafering and polishing costs. Coloured curves represent the number of wafers obtained in each grade, while the white curve indicates the total monetary profit. In this example, the maximum number of premium-grade wafers is achieved at a thickness of 0.3 mm.

the effectiveness of recipe changes or furnace modifications on defect reduction.

After all, what gets measured gets managed.

As well as driving yield improvements in traditional production, we are working to open new possibilities. Let's now talk about the financial implications.

Down the production chain, the value of epi-ready wafers is graded by well-established metrics, that include defectiveness. Knowing the defect constellation while still at the puck stage makes it possible to predict these metrics in advance. This feature, currently in beta testing, is embedded within the YieldPro software coming with the new scanner. It lets users define custom wafer grades – such as Prime, Production, or Engineering – based on specific defect limits or existing industry standards. Using 3D puck scans, future wafers are auto-classified accordingly after the puck scanning. These grading protocols can be shared with downstream partners or customers.

This capability in turn allows manufacturers to evaluate puck processing profitability, factoring in defect levels, as well as wafering and polishing costs.

For example, the YieldPro software can build a profitability curve as a function of wafer thickness to assess how different wafer thicknesses influence financial gain (see Figure 3).

As trade of pucks between growers and wafer manufacturers increases, objectively determining their yields is becoming increasingly important. Thanks to an assessment of quality at the puck level – before wafering begins – manufacturers of SiC substrates can align their production with specific orders, customer requirements, and market conditions.

Given the significant benefits of the SiC Puck Scanner, it's not surprising that we are seeing swift interest in it. The upstream chain is now adopting automated quality control, following the trend established downstream.

### Case Study: From puck to wafer – digital traceability in action

The SiC Puck Scanner can detect a wide range of defects: polytypes, micropipes, voids, inclusions, dislocation clusters, microcracks, and more. While the device is not a substitute for post-wafering inspection, as it's possible that some minor defects

**“** The success of SiC in power electronics and e-mobility depends on detecting defects at the earliest stages. From a cost perspective, preventing defective material from propagating into processing is essential. It is reassuring that PVA and Scientific Visual are addressing this challenge with a dedicated metrology tool. **”**

*Jochen Friedrich, Head of Materials Department, Fraunhofer IISB*

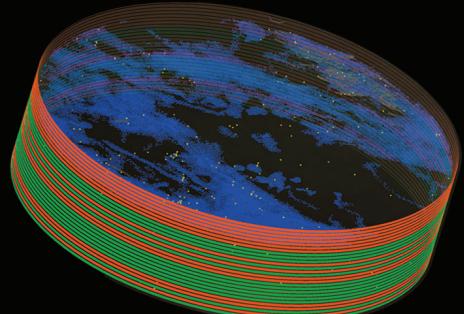

► Figure 4. Example of correlation between SiC puck inspection and wafer inspection (a) 1mm-thick layer taken from the SiC Puck 3D twin at 1.62 mm depth, (b) the corresponding wafer under UV light, (c) the same wafer analysed by dislocation and stress mapping.

may go undetected, it provides an essential first line of defence. During the scanner's development, we continuously evaluated the accuracy of its performance by studying the correlation between puck inspection results and wafer-level defects through end-to-end case studies. While most of the tested material remains under NDAs, we received permission to disclose one case involving one of the thickest pucks we inspected.

A 150 mm-diameter, 40.7 mm-thick SiC puck was scanned in SiC Puck Scanner to generate a full volumetric defect map. It was then sliced into 1 mm-thick wafers and analysed with traditional wafer inspection methods: Raman spectroscopy, UV illumination and near-infrared photoluminescence imaging. By tracing initial wafer orientations and positions within the puck, we were able to reconstruct detected defects layer by layer for the above techniques, and correlate them with the initial puck scan.

Results demonstrated a strong correlation between the defects detected in the puck and those

observed in extracted wafers (see Figures 4 and 5). As expected, the characterisation revealed polytype regions, dislocation walls, and inclusions present in the sample – but not individual dislocations.

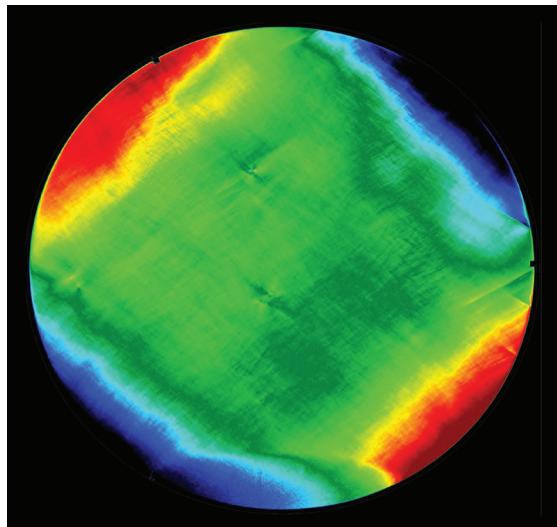

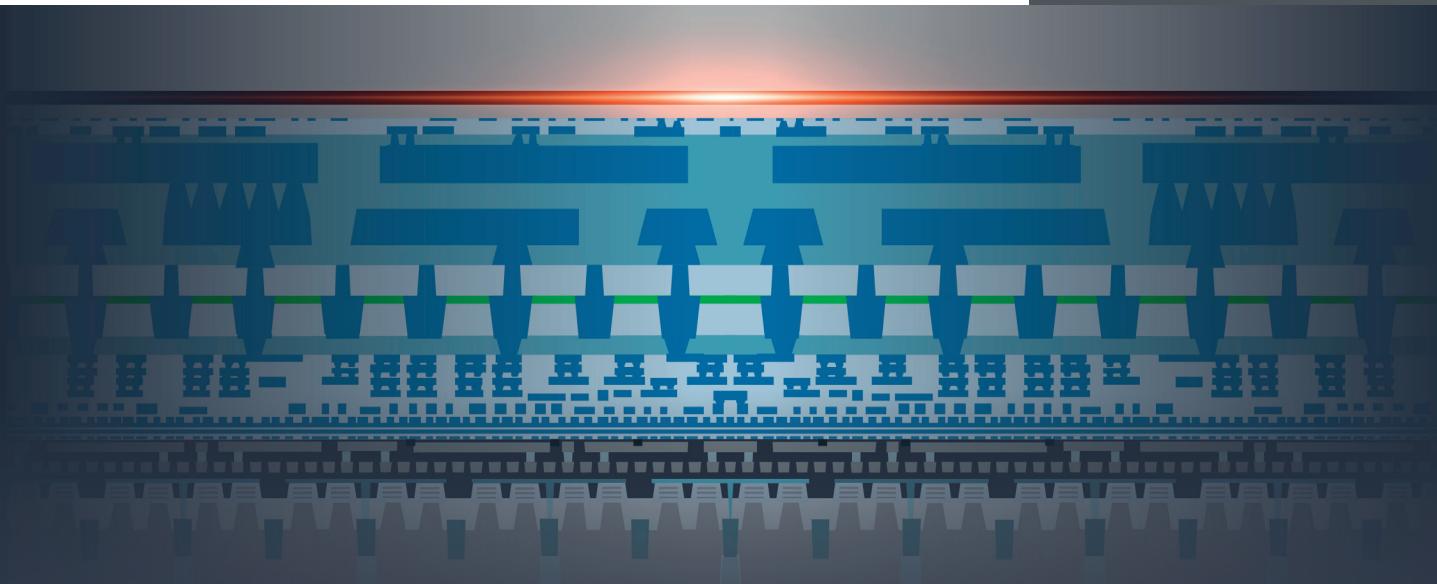

Finally, the produced wafers were inspected for stress using SIRD SiC 200 – Scanning InfraRed Depolarization stress-measurement technique (see below). This allows one to bring the volumetric defect results and post-wafering stress measurement into one 3D model (on the cover page), and study the correlation between internal defects and stress level in the material, which paves the way for multi-method metrology.

### SiC-Wafer-Stress Metrology: The SIRD SiC 200 system

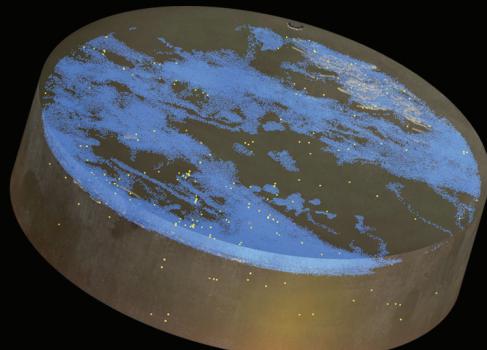

Stress measurements at the wafer level can be performed using new PVA TePla's SIRD SiC 200 Scanning Infrared Depolarisation tool. This tool provides fully automated, quantitative stress mapping across a broad range of dopings and materials (see Figure 6). Because the entire measurement and evaluation process is recipe-based and features

► Figure 5. Example of correlation between SiC puck inspection and wafer inspection: (a) Raw image of 65  $\mu$ m-thick layer at 1.62 mm depth revealed by the SiC Puck scanner, (b) Raman heatmap of part of the resulting wafer with thickness 1 mm.

► Figure 6. Shear stress map measured by the SIRD SiC 200 system. The map shows the shear stress distribution inside the 150 mm SiC wafer, with large, extended stress fields at the outer edge and smaller defect-induced stress fields.

automated wafer handling, no operator intervention is required. This ensures reliability and repeatability at scale and supports 24/7 fab production. Achieving this level of automation is challenging; however, our team at PVA TePla draws on more than 25 years of experience in 300 mm silicon metrology.

Quantifying stress within a wafer is critical because stress correlates with defect growth and results in geometric deformations, such as bow and warpage. These deformations significantly reduce yield and impair device performance and reliability. By providing rapid, non-destructive, operator-independent stress analysis, the SIRD SiC 200 system enables customers to identify hidden risks before they escalate into costly problems. The SIRD SiC 200, having the ability to detect stresses at as low as 100 Pa, is therefore essential.

High sensitivity in stress measurements is crucial because process control requires detecting minuscule changes in the stress field for effective and reliable monitoring of each step. Additionally, this sensitivity enables the detection of defects inside the wafer, from micropipes to threading dislocations. This is possible because each defect causes a characteristic surrounding stress field. Measuring stress also offers valuable insight into process monitoring, from crystal growth to epitaxial-

layer deposition. Each of these processes leaves a distinct stress fingerprint embedded within the wafer. This information becomes increasingly important as wafer sizes increase and process control windows narrow.

The SIRD SiC 200 system can be deployed in fabs to monitor the SiC substrate production process in its entirety – from measuring substrate-level stresses during crystal growth to detecting defects during epitaxy monitoring. After configuring a dedicated recipe for each process step, the system automatically measures and analyses wafers to calculate key indicators such as stress distribution and defect count. No operator access is necessary, because everything operates via SECS/GEM and overhead transport systems, in compliance with SEMI GEM300 standards.

Advanced metrology is set to revolutionise the SiC crystal industry as profoundly as it transformed the automotive and electronics manufacturing sectors earlier. Paradoxically, while the later stages of semiconductor production have embraced automated metrology, digital twins, and data-driven quality feedback loops, the early stages – crystal growth, inspection, and wafering – still largely depend on intuition and manual judgment.

We are glad to witness a gradual shift in this landscape. At Scientific Visual and PVA TePla, we are helping shape that future, delivering innovations that provide measurable, real-world value. Early-stage defect detection, yield optimisation, and objective quality grading are no longer optional – they are essential for any company striving to compete in the SiC space.

With our solutions, manufacturers are empowered to reduce waste, boost throughput, and secure a clear competitive advantage. But adopting advanced metrology is about more than improving quality – it means forging a supply chain that is resilient, transparent, and ready for the future. Getting rid of unnecessary processing translates into a lesser environmental footprint of SiC substrate production. As the industry evolves, those who invest in early-stage inspection and digital traceability will stand best poised to lead not only in innovation but also in sustainability.

SiC's future depends on intelligence and precision from the very start of the production chain. We are proud to be at the forefront of this development.

## FURTHER READING

► FAQ on SiC Puck Scanner

► SIRD Wafer Stress Measurement

► PVA TePla Metrology Portfolio

- We gratefully acknowledge the professional collaboration and timely support from Lapmaster Wolters (Switzerland, Germany) for puck wafering, Ntek Latent Technologies Inc. (Taiwan) for wafer surface preparation, VisionTec (Singapore) for wafer optical and photoluminescence characterisation, and the PVA TePla Tech-Hub team (Germany) for Raman measurements.

- Ready to elevate your SiC production? Contact us for a demonstration or visit us at SEMICON Europa, Booth C1531.

# GETTING CRYSTAL CLEAR

Automated quality control of industrial crystals

At Scientific Visual, we transform crystal data into actionable insights. From watch covers to 300-kg raw boules, our Swiss-engineered scanners reveal microscopic defects within the crystal volume before machining begins. This enables fabs to recover more usable material, avoid costly downstream losses, and improve crystal growth faster through early-stage defect identification.

Explore data-driven crystal processing.

Visit [scientificvisual.ch](http://scientificvisual.ch) today.

Unprocessed crystal

3D scan with defect map

Coring plan and graded end items

## Breakthroughs in blue and green laser diodes

More powerful and efficient GaN-based lasers are aiding displays and simplifying copper processing

BY RYOTARO KONISHI, YOJI NAGAO, TSUYOSHI HIRAO, KATSUHIRO KISHIMOTO, TERUYUKI MORITO, TOMONORI MORIZUMI, YOSHITAKA NAKATSU, TOMOYA YANAMOTO AND SHIN-ICHI NAGAHAMA FROM NICHIA CORPORATION

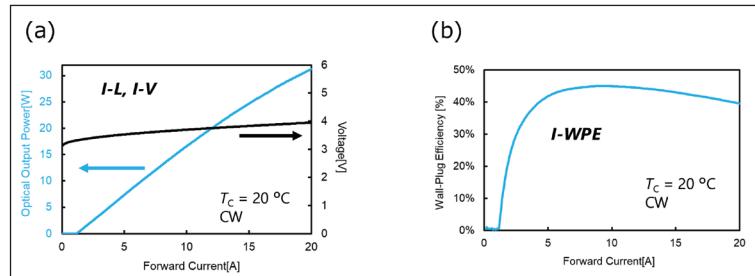

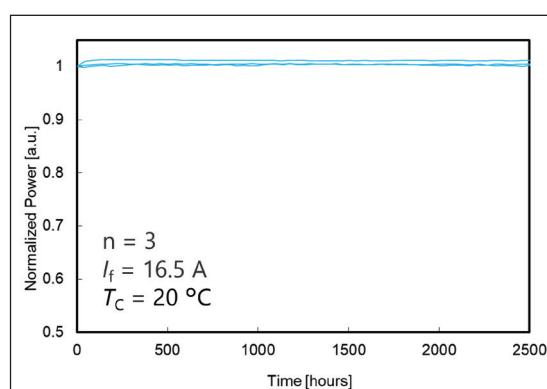

RECENT IMPROVEMENTS to GaN-based laser diodes (LDs) are positioning these sources as pivotal technologies in various applications. Opportunities have emerged in displays and laser processing, thanks to increases in the efficiency of this class of laser, along with a narrowing of its spectral width and the advent of exceptional reliability.

Within the display industry, the high efficiency and output power of GaN-based blue and green LDs are contributing to improved colour reproduction and brightness in digital cinema projectors, laser TVs, and large laser projectors. In addition, these emitters are supporting the development of high-performance RGB laser-light sources, enabling a wider colour gamut and enhanced visual experiences.

Meanwhile, in the industrial domain, high-output-power blue LDs are significantly enhancing laser processing capabilities, particularly for challenging materials like copper. These powerful sources are enabling high-precision and efficient metal welding, cutting, and processing, opening new fields in manufacturing and processing technology. They include opportunities in sectors such as the automotive industry.

### Technological advances in blue lasers

As is often the case with compound semiconductor technologies, improvements to the performance of GaN LDs have taken place over many years. Nichia, as the pioneer and leading producer of GaN LDs, has driven these advancements.

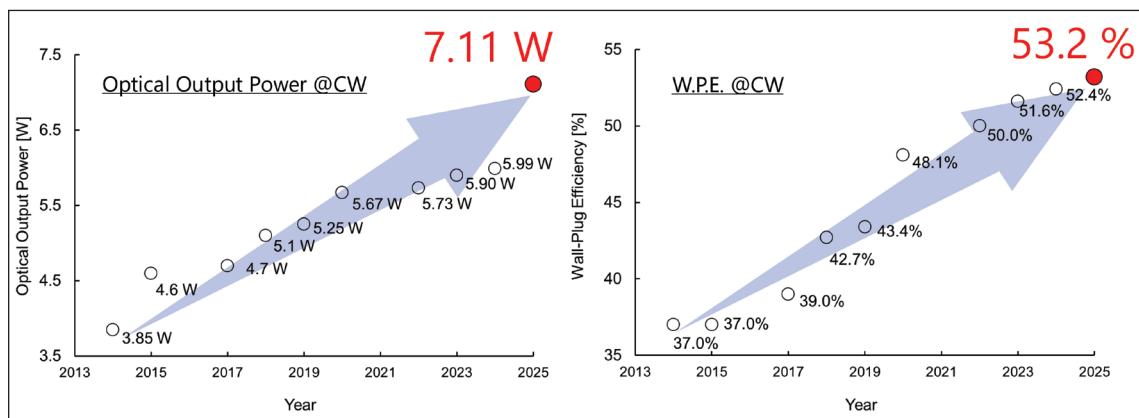

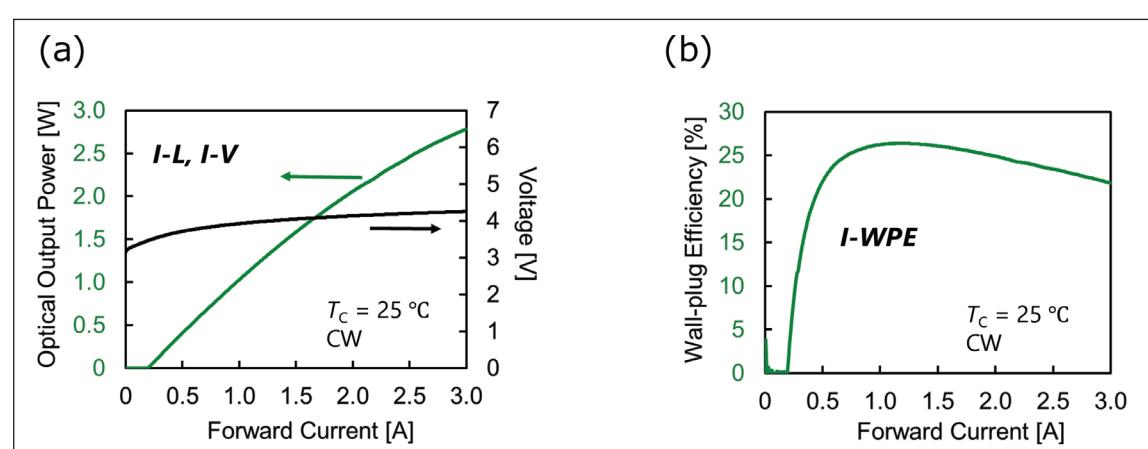

► Figure 1.

Nichia's

history of the

455 nm blue

LDs.

The development of blue LDs, pioneered by our company, began in earnest in the early 2000s, with the first successful demonstration in 2001. Back then, lasers delivered a modest optical output of just 5 mW. Thanks to rapid advancements, the first watt-class LDs were introduced in 2007. By 2022, we realised another impressive milestone in the history of the GaN LD, the first device surpassing a wall-plug efficiency of 50 percent.

Increases in the wall-plug efficiency and optical output of these blue LD chips have not come in the form of a handful of big jumps, but steady improvements over many years. This progress is attributed to both technological innovation and optimisation of the manufacturing processes (see Figure 1).

Our 455 nm blue LDs have a mere 2 nm spectral width, concentrating almost all their optical energy within this narrow range, which is approximately one-tenth of the spectral width of conventional LEDs. This capability to convert half of the electrical input power into laser light within a range of just 2 nm highlights the efficiency of our technology. However, this efficiency still lags behind the best GaAs-based LDs, indicating room for further improvement.

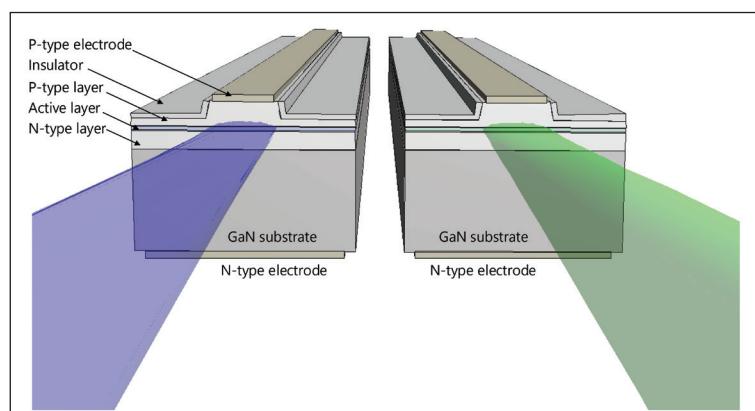

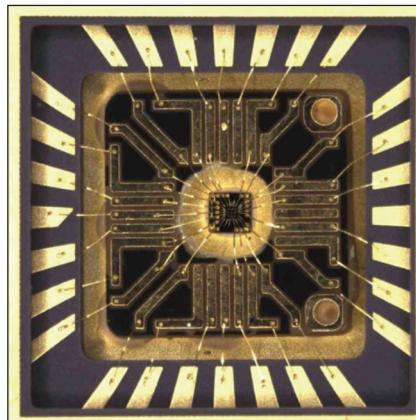

The manufacture of our LDs begins by loading a 2-inch c-plane freestanding GaN substrate into an MOCVD reactor and depositing an epitaxial stack consisting of *n*-type layers, and the active region, and finally *p*-type layers. Subsequent etching of the *p*-side of this epiwafer creates a ridge structure, to which we add *n*-type and *p*-type electrodes (see Figure 2). Production of the laser is completed with the addition of mirrors, created by cleaving the wafer and coating the bare facets with dielectric mirrors.

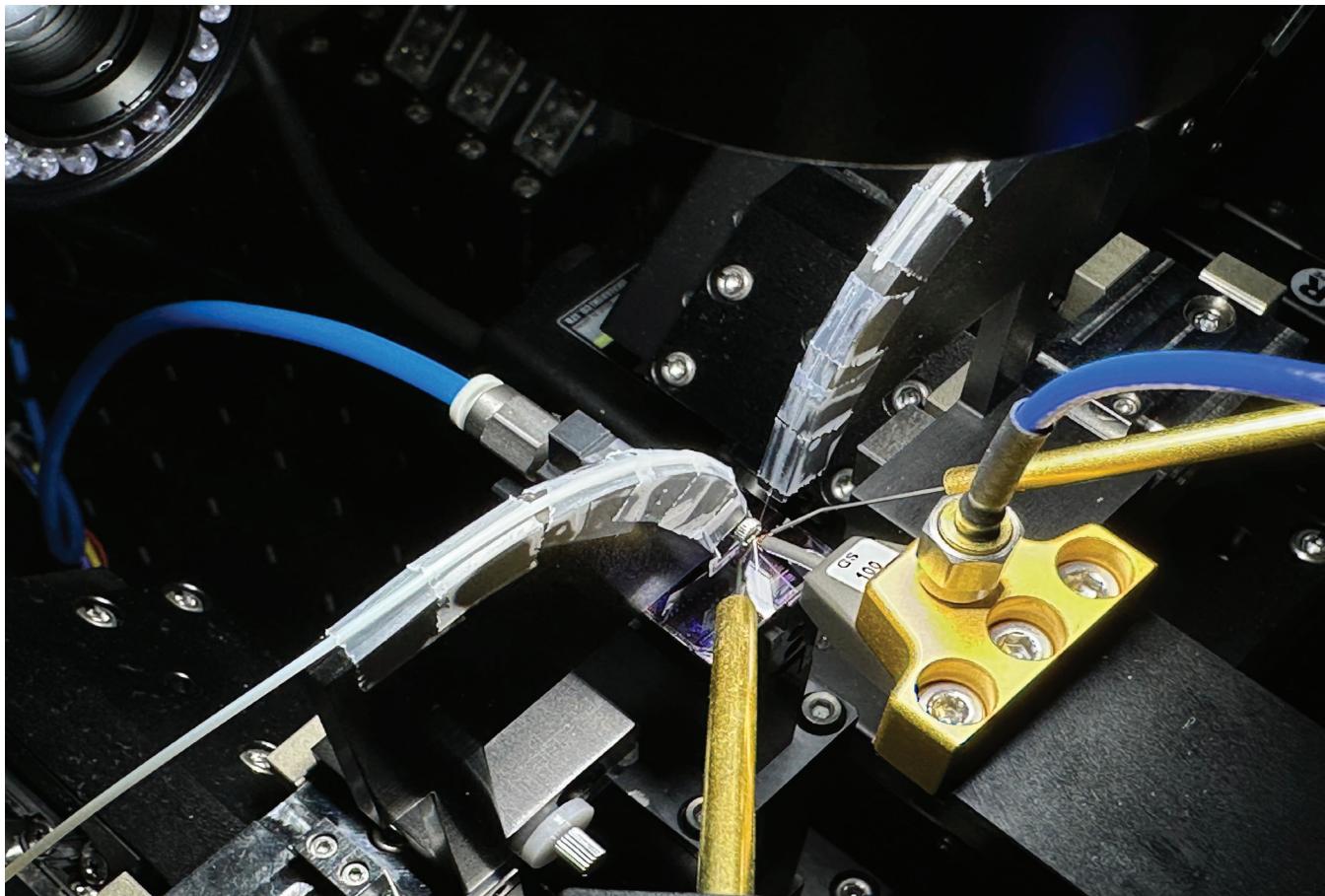

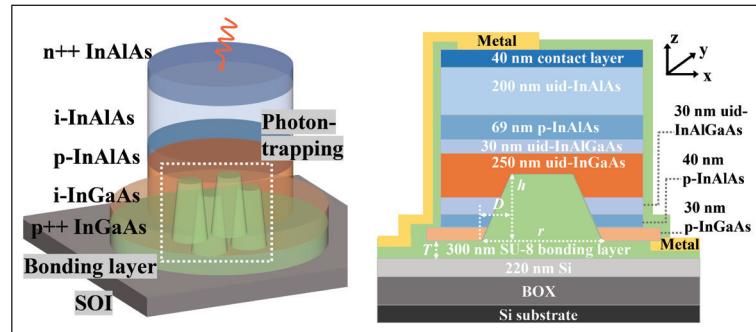

To minimise optical absorption losses, we meticulously design the optical confinement structure of our epitaxial stack. This careful consideration is crucial for ensuring that our LDs have a high efficiency and performance. In the final step of the laser manufacturing process, we employ a junction-down method to mount our chips into TO-Can packages. This approach trims thermal resistance and enables optimal heat dissipation.