# COMPOUND SEMICONDUCTOR SENSON

CONNECTING THE COMPOUND SEMICONDUCTOR COMMUNITY VOLUME 31 ISSUE IX 2025 COMPOUNDSEMICONDUCTOR.NET FOR TA

# THE G10 SERIES

platform with 150/200 mm

wafer size flexibility

Your **Productivity Solution** for All Advanced Epitaxy Materials

# GaN: Going in which direction?

IN OUR INDUSTRY, we use a number of figures-ofmerit to judge devices. We can benchmark LEDs by their lumens-per-Watt and their lumens-per-dollar, and assess the performance of power devices by Baliga's figureof-merit: it's calculated by squaring the breakdown voltage and dividing that figure by the specific on-resistance.

As well as these rather precise figures, there's another one that's far more vague - it's the bang-per-buck.

Revolutionary devices often excel in the 'bang'. Think, for example, of the vertical GaN transistor. Compared to its conventional cousin that's netting substantial sales via the fast charging of mobile devices, it offers a higher breakdown voltage for a given chip area, along with superior reliability and simplified thermal

But what about the 'per buck'. Well, that's been a major sticking point. Traditionally, vertical GaN transistors have been produced on GaN substrates, a foundation that has many weaknesses. Drawbacks include a high

price, limited

management.

availability, and relatively small diameters that hamper scaling, an issue that's probably to blame for the death of start-ups that have tried to commercialise this device.

Overcoming this limitation is the MIT spin-out Vertical Semiconductor. This fabless firm is

pioneering the use of engineered substrates with a diameter of 200 mm for the production of vertical GaN transistors (see 'p. 14' for more details). By switching to this foundation, Vertical is able to manufacture its power devices in 200 mm foundries that are primarily used to produce silicon devices with CMOS technology.

While the approach is novel, the markets Vertical is targeting are anything but. Yes, you've guessed it – it's EVs and data centres, with the later spurred on by the growth of Al.

Given the tremendous excitement in both those booming markets by many producers of GaN power devices, it would be easy to assume that sales to these sectors are already substantial, and will rocket over the next few years.

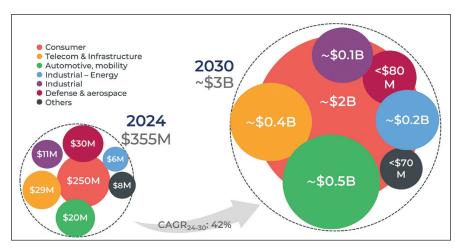

> But the reality is somewhat different, at least according to well-respected market analyst, Yole Group. Figures from their latest report on GaN power devices show that the consumer market generated sales worth \$250 million in 2024, and is forecast to be worth \$2 billion in 2030. In comparison, while the rate of growth in the EV and telecom

> > & infrastructure sectors will grow even faster, by 2030 revenues will still be far behind, with estimated values of \$0.5 billion and \$0.4 billion, respectively.

Sales, though, are only part of the equation. Margins matter, and they are often squeezed in long-standing applications. So, the focus of EVs and data centres

is understandable, given the potential to combine multi-billiondollar revenues with significant profits in the 2030s.

Free weekly e-news roundup go to:

compoundsemiconductor.net

### 18 AIScN: A nitride for computation?

The novel ternary AIScN enables a silicon-compatible, wake-up-free ferroelectric memory for next-generation AI hardware

# 20 Progressing the PCSEL towards high-volume production

By developing and refining the PCSEL, manufacturers of optoelectronic device are laying the foundations for the commercial success of this very promising class of laser

### 26 GaN HEMTs enter SiC territory

Rigorous testing demonstrates the reliability and robustness of commercial 1250 V GaN HEMTs paired with a low-voltage silicon MOSFET to ensure normally-off operation

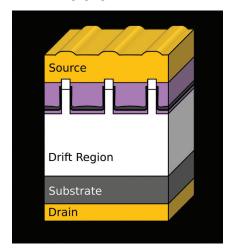

# 34 Driving the electric revolution with SiC IGBTs

FOR<sup>2</sup>ENSICS, an EU-funded initiative, is targeting simplification of medium-voltage DC converters with ultra-high-voltage SiC IGBTs

### 40 Low-pressure CVD of Ga<sub>2</sub>O<sub>3</sub>: Growth and beyond

Advances in low-pressure CVD-based growth of  $Ga_2O_3$  and its *in-situ* etching address two critical bottlenecks: high-quality, high-growth-rate films; and damage-free patternability

### 46 Sculpting at the micro-scale

Emerging fabrication techniques are re-writing the rulebook for on-chip components

### **NEWS ANALYSIS**

### 14 The vertical GaN transistor: Time for take-off

Using 200 mm foundries, MIT start-up Vertical Semiconductor will produce finFETs on engineered

### 16 GaN's stalwart sector: Consumer electronics

While makers of GaN power electronics enthuse about the opportunities associated with AI and EVs, fast chargers will be the dominant application throughout this decade and beyond

### RESEARCH REVIEW

- 50 Breaking through the 10 kV barrier

- 51 Slashing the sheet resistance of **ScAIN**

- 52 Platinum provides a promising contact for p-type SiC

# **NEWS**

- 06 Imec achieves record GaN breakdown voltage

- 07 Qorvo and Skyworks to merge

- 08 Infineon's Chief Marketing Officer joins Wolfspeed

- 09 Macom to manufacture HRL's GaN-on-SiC process

- 10 NcodiN secures €16 million to tackle Al bottlenecks with miniature laser

- 11 GlobalFoundries licenses GaN tech from TSMC

- 12 CEA-Leti looks to microLED for AI data links

News Editor Christine Evans-Pughe **Design & Production Manager** Mitch Gaynor

**Director of Logistics** Sharon Cowley Event & Media Sales Executive Ranjodh Shergill

Circulation Scott Adams Publisher Jackie Cannon christine.evans-pughe@angelbc.com

sharon.cowley@angelbc.com

mitch.gaynor@angelbc.com

ranjodh.shergill@angelbc.com scott.adams@angelbc.com jackie.cannon@angelbc.com

+44 (0)1291 629640

+44 (0)1923 690214 +44 (0)1923 690200

+44 (0)2476 718970

+44 (0)1923 690205

Sales and Product Manager James Cheriton james.cheriton@angelbc.com +44 (0)2476 718970

Chief Executive Officer Sukhi Bhadal sukhi.bhadal@angelbc.com Chief Technical Officer Scott Adams scott.adams@angelbc.com

+44 (0)2476 718970 +44 (0)2476 718970

Directors Jackie Cannon, Sharon Cowley

Published by Angel Business Communications Ltd, 6 Bow Court, Fletchworth Gate, Burnsall Road, Coventry CV5 6SP, UK. T: +44 (0)2476 718970

E: info@angelbc.com

W: angelbc.com

Compound Semiconductor is published nine times a year on a controlled circulation basis. Non-qualifying individuals can subscribe at: £115.00 per annum (UK), £165 per annum (Europe), \$198 per annum (air mail) (USA). Cover price £4.50. All information herein is believed to be correct at time of going to press. The publisher does not accept responsibility for any errors and omissions. The views expressed in this publication are not necessarily those of the publisher. Every effort has been made to obtain copyright permission for the material contained in this publication. Angel Business Communications Ltd will be happy to acknowledge any copyright oversights in a subsequent issue of the publication. Angel Business Communications Ltd © Copyright 2025. All rights reserved. Contents may not be reproduced in whole or part without the written consent of the publishers. The paper used within this magazine is produced by chain of custody certified manufacturers, guaranteeing sustainable sourcing. US mailing information: Compound Semiconductor, ISSN 1096-598X, USPS Permit Number 25366, is published 9 times a year, Combined Jan/Feb, March, Combined April/May, June, July, Combined August/September, October, November, December by Angel Business Communications Ltd, Unit 6, Bow Court, Fletchworth Gate, Burnsall Rd, Coventry CV5 659, UK. Airfreight and mailing in the USA by agent named World Container INC 150-15, 183rd St, Jamaica, NY 11413, USA. Periodicals Postage Paid at Brooklyn, NY 11256. POSTMASTER: Send address changes to Compound Semiconductor, Air Business Ltd, c/o World Container INC 150-15, 183rd St, Jamaica, NY 11413, USA. Periodicals Postage Paid at Brooklyn, NY 11256. POSTMASTER: Send address changes to Compound Semiconductor, Air Business Ltd, c/o World Container INC 150-15, 183rd St, Jamaica, NY 11413, USA. Periodicals Postage Paid at Brooklyn, NY 11256. POSTMASTER: Send address changes to Compound Semiconductor, Air Business Ltd, c/o World Container INC 150-15, 183rd St, Jamaica, NY 11413, USA. Periodicals Post lastra st, Jamaica, NY 11413, USA. Periodicals Postage Paia da throokyn, NY 11250. PUS IMAS Let. Send address changes to Compound Semiconductor, Air Business Ltd, Cro World Container Inc. 109-16, IBSrd St, Jamaica, NY 11413, USA. We strive for accuracy in all we publish; readers and contributors are encouraged to contact us if they recognise an error or or omission. Once a magazine edition is published for line, in print or both], we do not update previously published articles to align old company names, branding, marketing efforts, taglines, mission statements or other promotional verbiage, images, or logos to newly created or updated names, images, typographic renderings, logos (or similar) when such references/images were accurately stated, rendered or displayed at the time of the original publication. When companies change their names or the images/text used to represent the company, we invite organizations to provide Angel Business Communications with a news release detailing their new business objectives and/or other changes that could impact how customers/prospects might recognise the company, contact the organisation, or engage with them for future commercial enterprise.

Printed by: The Manson Group. ISSN 1096-598X (Print) ISSN 2042-7328 (Online) © Copyright 2025

# Imec achieves record GaN breakdown voltage

Achieves voltage resistance exceeding 650 V on Shin-Etsu Chemical's 300 mm QST substrate

BELGIAN research hub Imec has achieved a record GaN breakdown voltage exceeding 650 V using Shin-Etsu Chemical's 300 mm-diameter QST substrate, which has been adopted for Imec's 300 mm GaN power device development programme, launched in October 2025.

The initial results showed that Imec has successfully fabricated a 5 µm-thick high-voltage GaN HEMT, using Aixtron's Hyperion MOCVD equipment, with a breakdown voltage of over 800 V.

The results show that the QST substrate, which has a thermal expansion coefficient matched to GaN, can stably deliver excellent GaN crystal growth performance, even at large diameters.

Shin-Etsu Chemical, licensed by US company Qromis, manufactures 150 mm and 200 mm QST substrates, as well as GaN-on-QST epitaxial substrates

of various diameters. In September 2024, it started providing 300 mm QST samples in a joint initiative with Qromis. Shin-Etsu Chemical and Qromis have also established a close partnership to provide 300 mm QST substrates for Imec 's 300 mm CMOS fab in Leuven, Belgium.

Because Imec's existing silicon wafer production line can be used for GaN, increasing the substrate diameter is expected to reduce production costs. However, GaN growth on silicon wafers suffers from increasingly poor production yields at larger diameters, due to issues such as wafer warpage, preventing practical mass production.

The 300 mm QST substrate solves this issue by enabling the epitaxial growth of thick-film 300 mm GaN for highvoltage applications without warping or cracks - previously unattainable on silicon substrates – thus significantly reducing device costs.

To date, Shin-Etsu Chemical has been enhancing facilities for 150 mm and 200 mm QST substrates and is currently working toward the mass production of 300 mm QST substrates.

The QST substrates are currently being evaluated by many Japanese and international customers for applications such as power devices, high-frequency devices, and LEDs. They are currently in the development phase for practical applications to address the recently increasing interest in AI data centre power supplies.

# SiCSem breaks ground on India's first SiC fab

CHENNAI-BASED SiCSem has broken ground on India's first end-toend SiC semiconductor production facility. The plant at Info Valley-II in Bhubaneswar represents the largest single investment (around \$220 million) in the state of Odisha's emerging semiconductor ecosystem.

SicSem is partnering with British firm Clas-SiC Wafer Fab to set up the facility, which will eventually produce 60,000 SiC wafers annually and package 96 million units.

The aim is for the fab to help India become self-sufficient in power semiconductor devices for electric vehicles, fast chargers, green energy, photovoltaic inverters, motor controls, and beyond 5G communication.

The plant will create 5,000 direct and indirect employment opportunities and is expected to become operational by 2027-28.

The project received approval from the India Semiconductor Mission in August 2025.

# Qorvo and Skyworks to merge

Joint company will form a \$22 billion US-based RF, analogue and mixed-signal company

QORVO, known for its RF expertise and GaAs/GaN processes, and Skyworks, a maker of analogue and mixed-signal semiconductors, have agreed to combine the two companies in a cash-and-stock transaction that values the joint US-based enterprise at approximately \$22 billion.

"This combination marks an important milestone for our industry and for Skyworks," said Phil Brace, CEO and president of Skyworks. "Combining Skyworks' and Qorvo's complementary portfolios and world-class engineering teams will strengthen our ability to meet growing customer demand across mobile and diversified broad markets. With enhanced scale, a more diversified customer base and operational synergies, we can bring even greater innovation to our customers and sustainable value to our shareholders."

"Qorvo and Skyworks share a culture of innovation and a commitment to solving our customers' most complex challenges," said Bob Bruggeworth, CEO and president of Qorvo. "Together with Skyworks, we can accelerate innovation and deliver broader and more comprehensive solutions across numerous growth areas. We are excited to leverage the combined strengths of our teams and product and technology

portfolios to build on our capabilities in mobile and significantly expand our presence in defence and aerospace, edge IoT, AI data centre, automotive and other industries powered by secular growth trends."

With combined *pro forma* revenue of approximately \$7.7 billion and Adjusted EBITDA of \$2.1 billion, the view is that the combined company will be better positioned to compete against larger players – supported by a stronger, more balanced revenue base that enables more predictable performance, a more efficient cost structure and resilient cash generation through cycles.

The combined company also has over 12,000 issued and pending patents, which should enable faster

development of system-level solutions and new design-win opportunities, according to the press announcement.

Under the terms of the agreement, Qorvo shareholders will receive \$32.50 in cash and 0.960 of a Skyworks common share for each Qorvo share held at the close of the transaction, which implies a combined enterprise value of approximately \$22 billion.

The boards of directors of both companies have unanimously approved the transaction, which is expected to close in early calendar year 2027, subject to the receipt of required regulatory approvals, approval of Skyworks shareholders and Qorvo shareholders and other closing conditions

# Infineon's chief marketing officer joins Wolfspeed

Matthias Buchner to broaden customer base for next-generation 200 mm SiC platform

SiC specialist Wolfspeed has appointed Matthias Buchner as SVP of global sales and chief marketing officer, effective December 1, 2025. Buchner will report directly to CEO Robert Feurle.

Buchner joins Wolfspeed from Infineon Technologies AG, where he most recently served as SVP of marketing for the Power & Sensor Systems division, responsible for strategic communication, partnership management, distribution marketing, digital marketing and marketing operations for a business worth at least \$3 billion.

Over his more than 20-year career, he has held senior leadership positions at Infineon, Micron Technology, and other technology companies, with deep experience in both silicon and SiC power solutions, business development, and global customer engagement.

Buchner will lead Wolfspeed's sales and marketing organisations with a focus on leveraging the company's next-generation SiC devices, produced on its 200 mm manufacturing platform. The appointment supports Wolfspeed's strategy to broaden its customer base across diverse, high-growth markets including automotive, renewable energy, industrial power systems, and Al-driven data infrastructure.

"Attracting a world-class sales and marketing executive like Matthias at this critical juncture underscores Wolfspeed's commitment to capturing the immense opportunities ahead," said Robert Feurle, Wolfspeed's president and CEO.

He added: "His global leadership experience across silicon and SiC technologies - spanning automotive, industrial, and other competitive markets - will be instrumental as we strengthen our customer relationships

and expand into rapidly growing segments such as AI data centers, renewable energy, grid infrastructure, and aerospace and defence. With Matthias joining our team, Wolfspeed is exceptionally well positioned to translate our vertically integrated SiC platform into sustainable, profitable growth."

Buchner said: "I am very excited to join Wolfspeed at this important moment for the company and the industry, Wolfspeed's deep domain expertise in producing SiC devices sets the industry standard for performance and quality in today's competitive landscape. Building strong, trusting relationships with our customers will be a key focus for me immediately out of the gate, as we work together to accelerate the global transition from silicon-based to siliconcarbide-based technologies."

Wolfspeed recently came out of Chapter 11 with a strategic refinancing initiative to strengthen its balance sheet and position it for sustained, profitable growth. In conjunction with this effort, Wolfspeed has rationalised its production footprint. This includes the planned closure of its 150 mm device fab on the Durham campus by the end of calendar 2025, as well as the decision to discontinue development of a proposed fab in Saarland, Germany.

## Onsemi reveals vertical GaNon-GaN semiconductors

ONSEMI has introduced vertical GaN-on-GaN power semiconductors, which it says set a new benchmark for power density, efficiency and ruggedness for Al data centres, electric vehicles, and other energy intensive applications.

Dinesh Ramanathan, SVP of corporate strategy, Onsemi said: "Vertical GaN is a game-changer for the industry and cements Onsemi's leadership in energy efficiency and innovation."

By conducting current vertically, the new vertical GaN power semiconductors can handle high voltages of 1,200V and above in a monolithic die, switching high currents at high frequency with superior efficiency to deliver smaller and lighter systems.

The technology, developed by Onsemi's Syracuse, New York, R&D team, can cut losses in high end power systems by almost 50 percent, according to the company. By operating at higher frequencies, it can also reduce the size, including passives like capacitors and inductors by a similar amount. Compared to commercially available lateral GaN, vertical GaN devices are approximately three times smaller.

The company is sampling both 700 V and 1,200 V devices to early access customers.

# Macom to manufacture HRL's GaN-on-SiC process

Macom to transfer advanced T3L high frequency semiconductor process into volume production

MACOM TECHNOLOGY has entered into an agreement with HRL Laboratories to license and manufacture HRL's proprietary 40 nm T3L GaN-on-SiC process technology. HRL and Macom will work collaboratively on a rapid process transfer of this proprietary semiconductor process from HRL's facility to one of Macom's US Trusted Foundries.

HRL, jointly owned by Boeing and General Motors, is regarded as a pioneer in the R&D of innovative RF and microwave GaN-on-SiC process technologies. T3L uses a proprietary epitaxial structure and an advanced gate design, which contribute to its high performance and enhanced reliability at millimetre-wave frequencies.

T3L was matured by HRL under the Office of the Undersecretary of Defense's (OUSD) State-of-the-Art Radio Frequency Gallium Nitride (STARRY NITE) and DARPA's Dynamic Range Electronics and Materials (DREaM) programmes, along with additional HRL funding that includes owner contributions.

"We're pleased to partner with HRL and look forward to establishing

We were not part of the STARRY NITE or DREaM programmes; however, Macom and our customers will soon be the beneficiaries of the results, as we industrialise this technology

a close working relationship. T3L is one of the most advanced highfrequency semiconductor processes in the industry, which we anticipate will enhance our existing portfolio and accelerate execution of our roadmap," said Stephen Daly, President and Chief Executive Officer, Macom. "We were not part of the STARRY NITE or DREaM programmes; however, Macom and our customers will soon be the beneficiaries of the results, as we industrialise this technology."

"This new relationship with Macom demonstrates HRL's expertise at developing and proving technology concepts and then transitioning them into production," said Rob Vasquez, president and CEO, HRL.

"Our GaN-on-SiC process technologies were established over many years of diligent work, and we're excited to now partner with Macom to advance the work into high volume production."

# NcodiN secures €16 million to tackle AI bottlenecks with miniature laser

Transforming the future of AI hardware with optical interposers featuring integrated nanolasers

NCODIN, the deep-tech startup pioneering optical interposer technology with integrated nanolasers, has secured €16 million in oversubscribed Seed financing round.

The funding will propel NcodiN from R&D to industrial scale, enabling product development, key engineering hires to support the industrialisation of its technology in a CMOS pilot line on 300 mm wafers, and the buildout of its supply chain and customer partnerships.

The equity round was led by MIG Capital, with participation from Maverick Silicon, PhotonVentures, and Verve Ventures, alongside continued support from existing backers Elaia, Earlybird, and OVNI.

Transforming the Future of Al Hardware, NcodiN is developing NConnect, a new generation of photonic interposers designed to overcome the 'copper wall' – the performance and energy limits of electrical interconnects that constrain Al systems. At its core is the world's smallest laser, enabling dense integration on silicon and unprecedented scalability without disrupting existing processor architectures.

This breakthrough allows chipmakers to pack supercomputer-level power into a single processor, paving the way for faster, more efficient AI hardware. This fundraising will accelerate industrialisation of the platform, including an industrial pilot to demonstrate compatibility with advanced packaging techniques.

With this round, NcodiN will also establish a Silicon Valley presence, expand its R&D capacity, and scale its team in preparation for large-scale manufacturing partnerships – bringing new technology to break the copper wall and redefine AI hardware performance.

"This funding marks a pivotal milestone for NcodiN. We are delivering the missing piece for the industry's most pressing challenge: enabling extremely highmemory bandwidth to power the Al factories of tomorrow. Our technology unlocks wafer-scale superchips by providing the most energy-efficient interconnects for networking across tens of chiplets – an essential component in the architectures everyone is chasing. As new generations of GPUs and AI accelerators emerge to keep pace with rapidly evolving GenAl algorithms, NcodiN is laying the photonic foundation that makes them possible," said Francesco Manegatti, CEO and Cofounder. NcodiN.

"Memory bandwidth has become a defining bottleneck in AI, with copper interconnects struggling to deliver the reach and efficiency required for next-generation systems. NcodiN's photonic interposers unlock memory bandwidth and capacity beyond copper's limits. We are excited to support NcodiN as they enable architectures that will define the future of AI hardware," explained Josh Miner. Mayerick Silicon.

Over the past 18 months, NcodiN has earned broad industry recognition for its vision and breakthrough work addressing Al's interconnect bottlenecks. The company has demonstrated proof-of-concept nanolasers with record energy efficiency below 0.1 pJ/bit, integrated nanodetectors, and full optical links, all on silicon. In parallel, NcodiN has

established an independent cleanroom that now serves as a hub for rapid prototyping and joint development with industry partners.

To strengthen its foundation, NcodiN has expanded its network of strategic advisors, welcoming, among others, Eli Yablonovitch, Gus Yeung and Peter de Dobbelaere. Yablonovitch is a pioneer of photonic crystals and cofounded of Luxtera, Ethertronics, Luminescent, and Alta Devices.

Yablonovitch remarked: "NcodiN is addressing the next big opportunity in silicon photonics, the silicon photonic interposer, which permits high-bandwidth communication in a multi-chip system, particularly for AI and Machine Learning. To do this, they embed high-performance nanolasers in silicon, thereby combining physics elegance with manufacturability. This has the likelihood of revolutionising all future large scale cyber systems."

Oliver Kahl, Principal, MIG Capital, added: "NcodiN is working at the centre of the Al infrastructure market, a sector experiencing rapid, significant growth driven by the surging demand for generative Al, the proliferation of big data, advancements in specialised hardware like GPUs, and the widespread adoption of cloud computing. The company's ambitious team is shaping and empowering the future of computing to drive innovation across multiple industries."

"At Elaia, we've been proud backers of NcodiN since it's early days when it was a CNRS spin-off. While copper interconnects struggle to keep up, NcodiN is rewriting the rules with the world's smallest laser and a revolutionary optical network. This isn't just innovation; it's the key to unlocking the next leap in Al and hyperscale performance," added Clément Vanden Driessche, Elaia.

# GlobalFoundries licenses GaN tech from TSMC

Deal aims to accelerate US-manufactured power range for data centre, industrial and automotive customers

GLOBALFOUNDRIES (GF) has entered into a technology licensing agreement with TSMC for 650 V and 80 V GaN technology.

This move aims to accelerate GF's next generation of GaN products for data centre, industrial and automotive power applications and provide US-based GaN capacity for a global customer base.

GF will qualify the licensed GaN technology at its manufacturing facility in Burlington, Vermont, using the site's expertise in high-voltage GaN-on-silicon technology to accelerate volume production for customers seeking next-generation power devices.

Development is set for early 2026, with production to begin later in the year.

"This agreement reinforces GF's commitment to innovation and its strategic focus on differentiated technologies that address essential power devices that we use to live, work and connect," said Téa Williams, senior vice president, power business at GlobalFoundries.

She added: "With the addition of this proven GaN technology, we will accelerate the development of our next-generation GaN chips and deliver differentiated solutions that address critical power gaps for mission critical applications from the data centre, to the car, and to the factory floor."

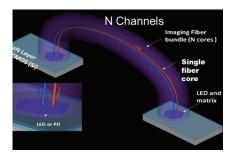

# CEA-Leti looks to microLED for AI data links

Multilateral project aims to increase high-performance computing speed and efficiency with 'orders-of-magnitude' data-transfer gains

CEA-LETI is launching a multilateral programme on microLED technology for ultra-fast data transfer, with a focus on accelerating AI growth. The lab-to-fab initiative draws on the institute's deep expertise in microLED process technology. The three-year initiative was announced at SEMICON Europa in Munich.

Set to begin in January 2026, it aims to engage manufacturers of microLEDs, optical fibres, photodiodes, and interconnects, as well as chipmakers, system integrators, and hyperscalers.

"Over the past decade, the computing power required to train leading-edge Al models has exploded by factors of millions, doubling roughly every threeto-four months as systems become more complex and data-hungry," said CEA-Leti CEO Sébastien Dauvé.

"Supercomputers demand ever-faster communication links with very high energy efficiency and ultra-low latency – but interconnect performance is lagging behind compute power. That gap calls for a paradigm shift capable of boosting high-performance computing speed by orders of magnitude."

Currently the tech industry is using slower copper-based data systems and

costly laser-based solutions. MicroLEDs, supported by a mature technology base, offer a compelling alternative – consuming less energy than either copper- or laser-based systems.

In a recent report on MOSAIC, Microsoft's novel optical-link technology, a Microsoft team noted that 'microLEDs are significantly smaller than traditional LEDs (and) can be modulated at several Gbps using a simple on-off scheme'.

The report, MOSAIC: Breaking the Optics versus Copper Trade-off with a Wide-and-Slow Architecture and MicroLEDs, also noted that the technology 'achieves ten times the reach of copper, reduces power consumption by up to 68 percent, and offers one hundred times higher reliability than today's optical links'.

"MicroLED represents a true paradigm shift for short-range optical, point-to-point data interconnects," Dauvé added. "It delivers extremely high data-density transfer rates with far better energy efficiency than current technologies. Unlike silicon photonics or VCSELs, the microLED is scalable for massive parallel communication. By combining the complementary expertise of our programme members, we aim to break through the interconnect power and density bottlenecks that limit next-generation computing."

CEA-Leti has been developing microLED technology for more than 15 years. The institute holds roughly 100 patents. Its use of silicon wafers and standard processes to produce microLEDs both scales and transfers easily to standard microelectronics foundries.

The institute will lead the Multilateral MicroLED Data Link Program with financial backing from its industrial partners. Together, members will map out a technical roadmap that sets clear objectives, milestones, and deliverables, and will track progress closely – adjusting course as needed to keep the collaboration on pace and on target.

### 20-22 April 2026

Sheraton Brussels Airport Hotel, Brussels, Belgium

### CONNECTING THE ADVANCED PACKAGING INDUSTRY

The 1st Advanced Packaging International builds on the momentum driving the next era of semiconductor innovation. Over two days, industry leaders and academic experts will deliver around 40 presentations across four key themes:

- Heterogeneous Integration

- Getting the Best Out of Incumbent Solutions

- Advancing Thermal Management

- Optimising Packaging Architectures

Conference attendees will gain insights into the materials, methods, and technologies reshaping chip-level packaging and system integration.

From cutting-edge thermal solutions to the reimagination of wirebond and leadframe formats, the event provides a comprehensive look at how packaging is enabling system-level innovation.

The two-day conference also includes expert panels and a dedicated poster session, creating multiple avenues for peer-to-peer engagement and technical exchange across the packaging ecosystem - from researchers and R&D teams to product engineers and system architects.

Advanced Packaging International is part of AngelTech, which delivers a portfolio of insightful, informative, and highly valued chip-level conferences.

Bringing together an Innovation Summit and four co-located conferences with more than 120 presentations, 700+ delegates, and over 80 exhibitors, AngelTech is the premier global event covering compound semiconductor, photonic integrated circuit, power electronic, and advanced packaging technologies. With significant overlap between the conferences, attendees benefit from exposure to full supply chains, customer bases, and partner ecosystems.

### **SPECIAL Event Discount:**

Register before 31 January 2026 and get 10% OFF!

Registration to AngelTech allows you to access both days of **PIC International**, **Advanced Packaging International**, **CS International** and **PE International**.

To find out more about our sponsor and speaker opportunities contact us today on: +44 (0)2476 718970 or email: info@angel-tech.net https://ap-international.net

CO-LOCATED WITH:

### NEWS ANALYSIS | POWER ELECTRONICS

# The vertical GaN transistor: Time for take-off

Using 200 mm foundries, MIT start-up Vertical Semiconductor will produce finFETs on engineered substrates

### BY RICHARD STEVENSON, EDITOR, CS MAGAZINE

THERE'S a lot to be said for the vertical GaN transistor. Compared to its horizontal sibling, it delivers a higher breakdown voltage and current for a given footprint, while offering superior reliability, and simplifying thermal management.

However, efforts by start-ups to commercialise the vertical GaN transistor have flopped, and today it is the lateral variant that enjoys commercial success, thanks in part to establishing a 'killer' application, the fast-charging of mobile devices.

Holding back the success of the superior geometry is its native foundation. As well as a high price tag, the GaN substrate is limited in size, with a typical diameter of just 50 mm. This prevents device fabrication on established 200 mm lines that benefit from economies of scale, as well as the use of more modern processing equipment.

Trailblazing a solution to these limitations is Vertical Semiconductor, a spin-out of Tomás Palacios' group at MIT. Vertical is pioneering the use of 200 mm engineered substrates for the manufacture of GaN finFETs, an approach that allows the outsourcing of chip production to numerous foundries with silicon CMOS capabilities.

Founded last year, Vertical initially maintained a low profile, before announcing this October that it's secured \$11 million in funding. This investment will be used to develop commercial devices on foundry lines that will enable the start-up to target the data-centre market. Here there is a much-publicised ramp in energy demand, due to the growth of AI, and GaN finFETs promise to make an impact by trimming energy losses and simplifying infrastructure. According to Vertical, its devices can increase efficiency by up to 30 percent, and enable a 50 percent reduction in the footprint of the power supplies.

### NEWS ANALYSIS | POWER ELECTRONICS

It should be noted that the finFET is not the only class of vertical GaN transistor. For well over a decade, the global GaN research community has been exploring different designs, including the currentaperture vertical electron transistor and the trench MOSEFT.

A significant weakness of both those designs is the demand for either epitaxial regrowth or the inclusion of p-type GaN layers – requirements that lead to a hike in fabrication complexity and cost, or an inferior channel carrier mobility.

Vertical is pursuing a different design, the finFET. This class of transistor only requires *n*-type GaN layers, so it can be produced without epitaxial regrowth.

Another strength of the finFET is the much-coveted normally-off operation, resulting from narrow fin channels that ensure all electrons are depleted at zero bias.

Back in 2019, benchmarking of the 1.2 kV GaN-on-GaN finFETs produced in Palacios' group, using a figure-ofmerit for power switching that included all possible conduction and switching losses, highlighted the superiority of this design over all the state-of-the-art silicon and SiC power transistors and large-area GaN R&D devices.

This success has provided the core technology for Vertical, co-founded by Palacios and the company's CEO and CTO, Cynthia Liao and Joshua Perozek.

### The backstory

While Perozek's path to CTO is a familiar one, involving the progression from a researcher in Palacios' group to technical lead in the start-up, Liao has arrived from a markedly different background.

After completing a degree in business administration at Western University, Ontario, she spent the first ten years of her career working in energy infrastructure, as well as energy and climate policy.

"I came to MIT as a mid-career MBA student in the Sloan-Fellow programme. And my goal was to actually pivot my experiences into a more entrepreneurial journey, and specifically using technology that I felt was quite exciting at MIT to make an impact around climate and energy."

Through a class at MIT, Liao met Perozek and Palacios. Enthused by the technology and its potential, she started supporting this lab, talking to potential customers. And after the class ended, the collaboration continued with much success, including the winning of competitions, the securing of initial support, and entry into an accelerator programme.

When Liao and Perozek graduated in summer 2024 they decided to incorporate the company.

Over the last year or so, Vertical has secured capital that will support its efforts to develop its first prototype packages, slated for sampling by the end of this year, before progressing to launch what's described as a fully integrated solution.

To execute these plans, Vertical will be working with suppliers of engineered substrates, and providers of epiwafer and foundry services.

Helping to bridge the transition between R&D and volume production is the work Perozek undertook during his time in Palacois' group, involving transfer of the technology from the research lab to the MIT Lincoln Laboratory. These efforts led to the fabrication of the first GaN finFETs on 200 mm wafers.

### Targeting data centres

Another goal that Liao and her colleagues have been focusing on is generating demand with customers.

"We are engaging across the data

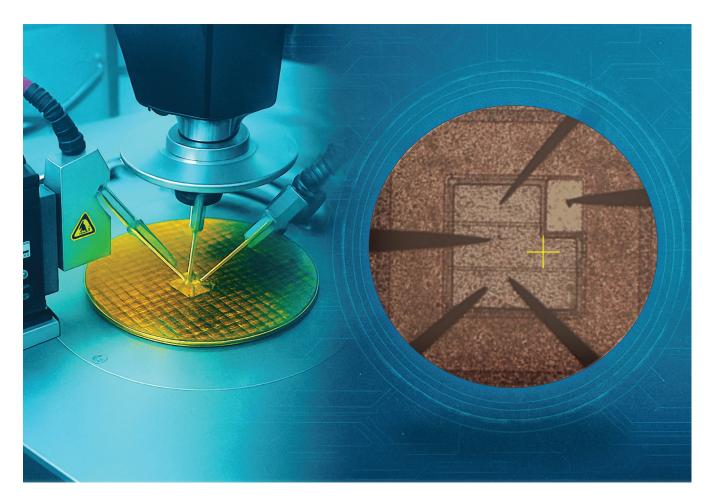

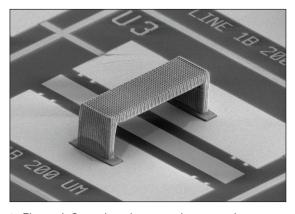

Vertical's GaN finFETs feature a bottom contact on the backside of a 200 mm engineered substrate.

centre power value chain, and working with customers to understand how that architecture is continuing to evolve, in order to serve the demands of these XPUs going into the future," says Liao.

Data centres have various requirements for power, ranging from lower-voltage point-of-load to solid-state transformers and solid-state circuit breakers.

"We're excited about plugging ourselves into these different application areas, which go into industrial power supplies, grid interfaces, and renewable energy technologies," remarks Liao.

She also sees opportunities for the team's finFETs in electric vehicles, where they promise to extend the driving range while offering a smaller form factor than the incumbents.

But there is a downside of this market from Vertical's perspective: this is the relatively long qualification times, which hamper the start-up from establishing itself in the power market.

"Our goal is to get these devices into customers' hands, and then work on the reliability and qualification needed for automotive production," explains Liao, before adding that despite this priority, Vertical has started to engage with customers in the mobility and vehicle space.

The team at Vertical, now totalling six employees and expected to increase in number over the coming months, is developing a portfolio of devices with blocking voltages from 100 V to 1,200 V.

These GaN finFETs will be shipped as packaged die. "If people want bare die, we're happy to provide that. But we find that package is preferred," says Liao.

Over time. Vertical will expand its range, introducing devices with higher blocking voltages. That's relatively easy to do, as thanks to growth on engineered substrates, the thicker GaN layers needed to withstand higher voltages do not introduce significant bow and warp.

But for the next 12 months, Vertical's focus will be on producing working devices at scale with a foundry partner, and creating a clear path towards qualification. "That's our number one target," says Liao.

# GaN's stalwart sector: Consumer electronics

While makers of GaN power electronics enthuse about the opportunities associated with AI and EVs, fast chargers will be the dominant application throughout this decade and beyond

### BY RICHARD STEVENSON, EDITOR, CS MAGAZINE

PICK UP a handful of press releases from the leading makers of GaN power devices and it's easy to spot a common theme – the tremendous opportunities associated with AI, and to a lesser extent, EVs. Both these applications demand efficient delivery of high voltages at high power densities, a task GaN is great at fulfilling.

Given the frenzied excitement and great importance ascribed to AI and EV by leading manufacturers of GaN power devices, it would be easy to fall into the trap of assuming that these applications are already significant – and if they are not dominating now, they soon will be.

So, given this state of affairs, the latest GaN report from Yole Group delivers a valuable, much-needed reality check. Yes, the EV and AI markets are growing very fast – but they are dwarfed by that of consumer electronics, and that's not going to change throughout this decade.

According to Yole Group's latest forecast, detailed in its *Power GaN 2025* report, in 2024 sales associated with the consumer electronics market totalled \$250 million, and they will climb with a compound annual growth rate (CAGR) of 35 percent to \$1.53 billion by 2030. In comparison, the CAGRs for the 'telecom & infrastructure' and 'automotive, mobility' sectors will be much higher over the same timeframe. They are forecast to have CAGRs of 53 percent and 73 percent, respectively, with corresponding annual

revenues rising to \$384 million and \$540 million by 2030.

Offering insight into these trends, Yole Group's Roy Dagher, who holds the role of Technology and Market Analyst, Compound Semiconductors, explained that in 2024 about 70 percent of GaN power device revenue came from the consumer segment, a figure that will fall to 53 percent in 2030.

Dominating sales within the consumer sector are fast chargers, accounting for a share of around 90 percent in 2024. However, this sector is diversifying, with GaN power devices seeing increasing deployment in 'white goods', which includes home appliances, such as fridges, freezers and TVs. "We believe that it's going to grow massively in the next few years," remarks Dagher.

The consumer electronics sector also includes GaN devices for overvoltage protection. It's an application Innoscience is championing, in the form of a bi-directional switch technology that allows two devices to be replaced with just one.

To put the current status of the AI market in perspective, sales of GaN power devices to the telecom & infrastructure sector totalled just \$29 million in 2024. In today's data centres, these devices provide DC-to-DC and AC-to-DC conversion.

The sector that Yole Group refers to as 'automotive, mobility' is even

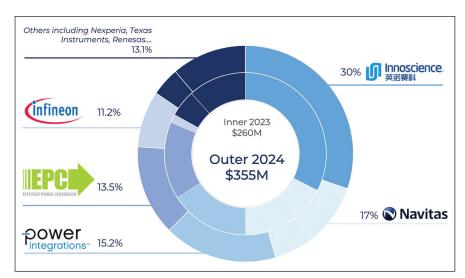

➤ GaN device players' market share in 2023-2024. Source: *Power GaN 2025* report, Yole Group

smaller, with last year's revenue worth just \$20 million. In this market, GaN devices are used for DC conversion in automobiles, and in power supplies for lidar systems. For the latter, Yole Group forecasts sales of GaN power devices to generate revenues of around \$200 million by 2030.

### Margins matter

For any chipmaker, sales are only part of the equation. Profit margins are also critical, and this accounts for the high levels of interest in the Al and EV markets.

According to Dagher, consumer electronics is the go-to market for newcomers. One of is appeals is its fast time-to-market.

"There's a lot of competition," says Dagher. "Margins are low, because there's a lot of players there. Prices get cut down."

Promises of higher profits are not limited to sales in EV and data-centre markets, and extend to industrial applications. They include motor drives, a sector that EPC and Infineon are targeting, as well as photovoltaics, with Enphase deploying GaN power devices in its micro-inverters.

### The big players

Topping the list of producers of GaN power devices is the Chinese chipmaker Innoscience, which enjoyed a 30 percent market share in 2024, a figure expected to nudge a little higher this year.

Dagher attributes this success to a number of factors, including a high production capacity and Innoscience's migration to 200 mm substrates ahead of all its rivals.

"They have this strategy to capture market share by cutting down prices and increasing volume," argues Dagher, who points out that Innoscience also benefits from a strong domestic supply

Leaders of the chasing pack include: Navitas; Power Integrations; EPC; Infineon, which acquired GaN Systems in March 2023; and Renesas, which bought Transphorm in summer 2024.

When considering all those on this list, plus smaller players, Dagher notes that

➤ GaN power device market, by end markets. Source: Power GaN 2025 report, preliminary results, Yole Group

one trend is the move towards vertical integration. "Companies are trying to control the supply chain, from epitaxy to packaging."

Backing up this claim, Dagher notes that the fabless company Navitas recently hired a senior epitaxy director. He also points out that EPC, which has a fablite business model and partners with Vanguard and Episil, has its own epitaxial lines; and that Power Integrations is undertaking its own epitaxy.

"There exist some foundry services that could help these companies go a long way. But in future, the IDM model will control most of the market."

While those looking for a foundry partner can no longer work with TSMC, there are many other companies offering these services for the production of GaN power devices, including a number of new entrants,

Topping the list of producers of GaN power devices is the Chinese chipmaker Innoscience, which enjoyed a 30 percent market share in 2024, a figure expected to nudge a little higher this year

such as Global Foundries, PSMC, Polar Semi and Samsung.

Another trend that Dagher is forecasting for the coming years is an increase in the blocking voltage provided by GaN products, so that they can start to compete directly with SiC MOSFETs and diodes.

Efforts in this direction, which will propel GaN to 1200 volts and beyond, include the introduction of multi-level topologies. There's also EPC's stacking of devices, an approach it refers to as series output parallel topology that's employed to increase the blocking voltage of products for data centres. Further innovation on this front includes Onsemi's release of GaN-on-GaN vertical transistors, and Power Integration's devices that are grown on sapphire.

"[Power Integration] has today already commercialised 1,250 volts. They plan to use it in the data centre," says Dagher, who points out that this company has also produced a variant operating at 1700 volts – but it can only handle low powers.

Gains in performance and/or pricing may also results from the introduction of engineered substrates, such as the QST platform from Qromis, and Infineon's efforts to produce devices on a 300 mm line.

So, while the dominant application for GaN is unlikely to change in the next five years, this part of the power electronics industry will certainly not be standing still.

# AlScN: A nitride for computation?

The novel ternary AIScN enables a silicon-compatible, wake-up-free ferroelectric memory for next-generation AI hardware

BY MINGRUI LIU, XIAOJUAN SUN AND DABING LI FROM STATE KEY LABORATORY OF LUMINESCENCE SCIENCE AND TECHNOLOGY, CHANGCHUN INSTITUTE OF OPTICS FINE MECHANICS AND PHYSICS. CHINESE ACADEMY OF SCIENCES

DUE to rapid advances in AI, the traditional computing architectures, which separate storage and computation, are facing critical speed and power bottlenecks. The latter is not helped by frequent data migration between processors and memory, accounting for more than 60 percent of total power consumption, while energy efficiency for actual computation remains below 10 percent.

Note that we literally do far better. By utilising synaptic networks for information transmission and processing, our brains provide highly parallel storage and computation. This leads to advanced intelligence, far surpassing that of computers, with a power consumption of just 20 W. Imagine if computer memory could emulate neural synapses – such a breakthrough would revolutionise the global electronics industry.

Offering much promise on this front are ferroelectric materials. Featuring electric-field-tuneable polarisation, ferroelectrics enable information writing via electrical pulses, and non-volatile storage/computation through remanent polarisation. And they have another key asset, multi-domain state regulation, that enables high-precision linear conductance modulation, and ultimately multi-level storage, closely mimicking synaptic weight updates in biological learning. These strengths

ensure that ferroelectrics are an ideal platform for energy-efficient neuromorphic devices.

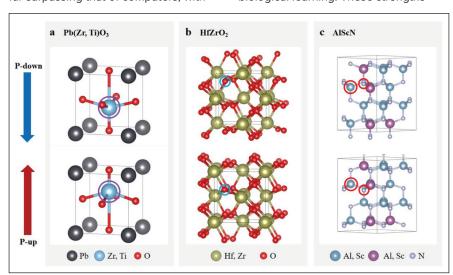

### Why wurtzite ferroelectrics? Unfortunately, most ferroelectrics are

oxides. This makes them challenging to integrate into mainstream semiconductor platforms. But there's hope, with recent advances in wurtzite-structured ferroelectric nitrides providing new opportunities to overcome this dilemma. This class of materials breaks new ground by combining a compatibility with silicon platforms with: enhanced remanent polarisation, a key metric that is 2-6 times higher than that for HfO<sub>2</sub> or perovskite ferroelectrics; sustainable thickness scaling; a high Curie temperature of more than 1100°C; and a stable ferroelectric phase.

Although the discovery of wurtzite nitride ferroelectrics has promise, there are concerns, related to high coercive fields that result in an increased switching voltage and degraded endurance and 'wake-up effects' - they cause devices to require repeated electrical cycling to reach peak performance.

The root cause of these issues lies in microscopic domain evolution, as the polarisation direction of these ferroelectrics is governed by the stacking order of the metal and nitrogen atoms. Unlike oxide ferroelectrics, where polarisation reversal involves a more straightforward single-atom movement, simultaneous motion of metal and nitrogen atoms is required.

Figure 1. (a) In ABO<sub>3</sub>-type perovskite ferroelectrics represented by Pb(Zr,Ti)O<sub>3</sub>, polarisation reversal involves the movement of B-site atoms. (b) In hafnium-based ferroelectrics, polarisation reversal involves the movement of oxygen atoms. (c) In wurtzite nitride ferroelectrics represented by AlScN, polarisation reversal involves the simultaneous movement of nitrogen and metal atoms.

This leads to larger energetic switching barriers, manifesting as wasted power and operational instability. Due to this, it is critical to clarify real-time domain dynamics under external electric fields and manipulate, at low fields, the motion of the domain walls - they are the boundaries between oppositely polarised regions.

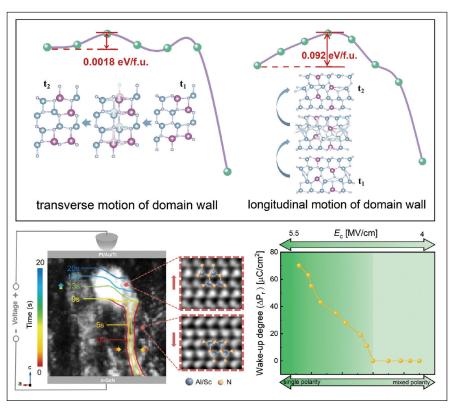

Our team at the Chinese Academy of Sciences has addressed these challenges in wurtzite ferroelectrics by focusing on real-time domain wall motion in representative  $AI_{0.75}Sc_{0.25}N$ films. Our primary tools are dark-field transmission electron microscopy and first-principles simulations.

We have found that under the same bias, the transverse motion of the domain wall (perpendicular to the c-axis [0001] direction) invariably precedes the longitudinal motion (along the c-axis), due to a 98 percent reduction in energy barriers. This is a game-changing finding, fundamentally breaking the traditional ferroelectric switching model and providing a new framework for polarisation reversal in complex lattice systems.

Based on our observations, it is possible for high-domain-wall-density AIScN, ideally with a mixed polarity penetrating the entire film, to realise polarisation reversal through transverse motion of the domain wall. However. single-polarity films need additional reversed-domain nucleation and longitudinal motion with higher energy barriers, thereby exhibiting high coercive fields and wake-up behaviour.

This is an exciting discovery. It implies that a promising pathway for reducing the overall polarisation reversal energy of wurtzite ferroelectrics is to maximise lateral domain wall movement while suppressing longitudinal migration.

### Engineering the breakthrough

Guided by the underlying mechanism, we have cut the overall energy cost by promoting the transverse motion of domain walls, realised by regulating the mixed polarity penetrating the entire film. This strategy delivers a 25 percent reduction in the coercive field strength while maintaining a high remanent polarisation and completely eliminating wake-up effects across 150 mm-diameter films. To the best of our knowledge, these results are setting

Figure 2. Top: The energy barriers of the transverse and longitudinal motions of the domain wall calculated by first principles simulations. Bottom left: Contour plots of the domain wall motion versus time, integrated differential phase contrast scanning tunnelling electron microscopy images of the dark (N polarity) and light (metal polarity) regions. Bottom right: Regulation of wake-up effect and the coercive electric field.

a new benchmark for ferroelectric properties and crystal quality.

Our work establishes a universal framework for optimising polarisation switching in wurtzite ferroelectrics. It is a particularly timely advance, offering a solution for addressing the growing demand for energy-efficient computing architectures in the AI era, and providing a clear pathway from fundamental research to industrial applications in memory, logic, and sensing devices.

It's worth noting that ferroelectric domain walls have been regarded as nanoscale functional interfaces, exhibiting reduced dimensionality and a different symmetry from the host material. Due to this, they give rise to physical properties that do not exist in the surrounding uniformly polarised domains.

We will now pivot our research, switching our focus to harnessing conductive domain walls as programmable functional elements that could enable precise control over multi-level resistance states and emulate memristive behaviours that are critical for neuromorphic computing. Success will not only pave the way for sub-nanometre device scaling, but also revolutionise integration, by merging memory and computation at the atomic interface. By leveraging domain wall conductivity for synaptic weight modulation, we foresee a new generation of ultra-dense neuromorphic architectures - they could finally bridge the gap between traditional systems and biological brain efficiency. The ability to engineer intelligent nanointerfaces may well define the next frontier in post-Moore's-law electronics.

### FURTHER READING

M. Liu et al. "Low-Field-Driven Domain Wall Motion in Wurtzite Ferroelectrics" Adv. Mater. 37 2505988 (2025)

# Progressing the PCSEL towards high-volume production

By developing and refining the PCSEL, manufacturers of optoelectronic device are laying the foundations for the commercial success of this very promising class of laser

### BY RICHARD STEVENSON, EDITOR, CS MAGAZINE

TAKING a device from its inception to lucrative, high-volume production is a lengthy, complex journey. Following the eureka moment that spawns a promising idea for a new class of device, there's the fabrication of the first chip and then its development, demanding many years of funding, often secured by identifying a potentially 'killer' application. Design and processing must then improve, so that this device satisfies a long list of requirements, including those related to performance, yield, cost and reliability, prior to the commercial launch of a competitive product that will net significant sales. That last step is particularly tricky to navigate if the fledgling device will only succeed in the marketplace by displacing an incumbent, as then it's critical that the new contender outperforms its rival by significant margins to win over the wavering minds of system engineers that are responsible for placing orders.

Against this backdrop, how much progress has been made by the PCSEL, the surface-emitting single-mode laser with a photonic structure that's renowned for its exceptional beam profile, incredibly narrow divergence, and a power that scales with the size of the emitting region?

While it's never possible to offer a definitive answer to this crucial question, those attending the recent second International Workshop on the PCSEL could offer an informative, well-considered answer. At that gathering, held on 10-12 November in Glasgow, UK - and co-located with the 14th International Symposium on Photonic and Electromagnetic Crystal Structures – a number of companies and universities detailed advances in the performance of the PCSEL. And during networking events, including a delightful visit to a local distillery, a number of low-profile delegates disclosed that they were also pursuing the development this promising surface-emitting laser, either at a company looking to diversify its laser portfolio or a new start-up formed to champion this device. So, what's clear is that there's tremendous momentum

➤ The second International Workshop on the PCSEL, held on 10-12 November, was co-located with the 14th International Symposium on Photonic and Electromagnetic Crystal Structures. Some talks were held at Glasgow University, while others, along with two posters session, took place at the nearby Grosvenor Hotel.

behind the PCSEL, with much effort directed at preparing the ground for commercial success.

Laying much of the foundation for progress to date is Susumu Noda, the leader of PCSEL development at Kyoto University, and a co-author of the first ever paper outlining this device, published back in 1999 in Applied Physics Letters. Since that groundbreaking conception, Noda's group has made a great deal of progress on many fronts, including the production of numerous devices, featuring higher powers and an expansion of material systems and spectral ranges.

Noda delivered the keynote session at the joint conference, with a presentation describing many potential applications for the PCSEL. They include using this device as the optical source for lidar employed in automobiles, farm machinery and robots; the deployment of PCSELs in material processing; and using this source for free-space communication, both underwater and over vast distances in space. In fact, there are so many applications where the PCSEL could serve that this situation may be viewed as an embarrassment of riches - with such a vast number of opportunities, it can be a challenge to know quite where to focus.

As one would expect in a keynote presentation, Noda covered a great deal of ground, highlighting key milestones from more than two decades of trailblazing research. While much of this would be familiar to many in the audience, the latest results, yet to be published, would be new to them. Building on powerful sources with an emission diameter of

3 mm, Noda and co-workers have just introduced variants with a diameter of 10 mm, emitting at around 940 nm. Initially, these sources produced more than 500 W of optical power when driven with pulses of 1000 A, and very recently continuous-wave outputs of 500-1000 W have been developed, with the PCSEL's thermal management benefitting from its bonding to a submount.

Today, the most efficient PCSELs have a wall-plug efficiency of around 25-30 percent. Noda suggested that far higher values, potentially up to 60 percent, might be realised by turning to multi-junction PCSELs.

Offering a tantalizing glimpse into the future, the PCSEL pioneer claimed that it may be possible to produce 15-20 kW devices with an emission diameter of 3 cm. Such sources would be a very attractive alternative to today's  $CO_2$  lasers, which are bulky – typical dimensions are around 1.5 by 0.4 m by 0.5 m – and have an efficiency of about 10 percent.

A key member in Noda's group, Takuya Inoue, focused on one of the applications mentioned in the keynote address, giving a presentation on the dynamic control of PCSELs for satellite communication. Inoue explained that satellite communication involves transmission over distances of more than 1000 km at data rates between 1 Gbit s<sup>-1</sup> and 100 Gbit s<sup>-1</sup>. As only a fraction of the light leaving the transmitter will hit the detector, due to beam divergence, the source must produce an optical power of at least 1 W.

Outlining the requirements for the transmitter, Inoue remarked that "the size, weight and power must be as small as possible". But these are not the attributes of a conventional transmitter, which incorporates an erbium-doped fibre amplifier that's large and heavy. This transmitter also features a number of components, hindering reliability.

PCSELs have much promise for this application, thanks to their high power and incredibly narrow beam divergence. But what modulation speeds are possible?

Inoue and colleagues have been investigating this matter for a few years, with initial efforts determining watt-class

operation with a direct bandwidth of more than 3 GHz. Turning to quadrature amplitude modulation has enabled transmission of 256 QAM signals at 2 Gbaud.

More recently, this team has investigated coherent free-space optical communication, realised with two-section PCSELs featuring a pair of photonic crystals with slightly different lattice constants in their gain sections. By injecting an anti-phase modulation current with the same bias current in both sections, the team have generated watt-class frequency-modulated signals with supressed amplitude modulation. This success provided the foundation for employing this PCSEL as a coherent free-space optical transmitter delivering Gbit s<sup>-1</sup> signal transmission, even when laser power is attenuated by 80 dB. Success with such a degree of attenuation, corresponding to the link loss in satellite communication, allows Inoue to claim that the team's directly modulated PCSELs have the potential to provide compact free-space optical transmitters for tomorrow's satellite communication systems.

As well as running the world's leading group on PCSEL development, Noda has inspired and supported a number of Japanese optoelectronic manufacturers in their development of this device. They include Hamamatsu Photonics, which launched the first commercial PCSEL in 2017 (a data sheet for this product, the L13395-04, can be found on the internet, but there is no price, suggesting it's been discontinued).

Hamamatsu is continuing to develop its PCSELs, targeting applications requiring a patterned light source. During development of its lasers, one of the issues that's been addressed is what's described as 'mesh noise' – this arises from an anti-crossing of photonic bands between the fundamental mode and higher modes in the layer direction.

At the PCSEL workshop, company spokesman Yoshitaka Kuorsaka told delegates that these modes have now been eliminated. Details surrounding the solution were scant, but involved changes to the epitaxial structure. Another issue that's been addressed is zero-order noise, removed by modifying the photonic crystal structure to introduce an additional phase. Recent efforts by Kurosaka and co-

workers have focused on a structure with two embedded regions in the same square lattice. The team have produced horizontal stripe patterns with a phase difference of 90° that have a stripe intensity ratio for each pattern region that changes continuously when the beams are superimposed. Based on this demonstration, Kurosaka claims that this work paves the way to a dynamically changeable light pattern consisting of multiple channels. In related work, Kurosaka's colleague Kazuyoshi Hirose detailed micro-pattern projection from a PCSEL-based on-chip pattern generator. These projections could be deployed for 3D profilometry - that's the measurement of surface profiles – with high-quality patterns needed for practical application.

### InP PCSELs

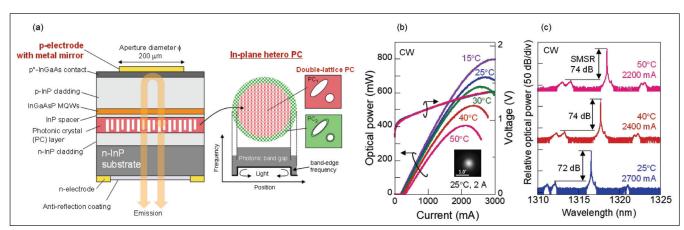

Another Japanese optoelectronics powerhouse that is partnering with Noda's team for PCSEL development is Sumitomo Electric Industries. This firm is directing efforts at improving the performance of InP PCSELs emitting at 1.3  $\mu$ m and 1.55  $\mu$ m, viewing such devices as promising candidates for sensing, free-space communication and sources for optical communication networks.

The power of Sumitomo's PCSELs has increased significantly over the last few years. Back in 2022, designs featuring a double-lattice produced an optical output of 200 mW. The introduction of a metal mirror the following year doubled output, and the latest PCSELs are emitting 700 mW, thanks to the introduction of an in-plane heterostructure.

> On the first evening of the conference, delegates were offered a guided tour of Clydeside Distillery.

Sumitomo spokesman Yuhki Itoh told delegates that the team began by switching from a single-lattice to a doublelattice to increase vertical radiation and hit 200 mW. This refinement produced a 25-fold hike in slope efficiency.

Introducing a metal mirror provided the next jump in output power, with this move enhancing carrier injection and reducing emission in unwanted directions. Thanks to these benefits, InP PCSELs emitting at around 1330 nm produce: a slope efficiency of 0.4 W A-1; output powers of more than 400 mW and 150 mW at 25°C and 70°C, respectively; a wall-plug efficiency of more than 24 percent at 25°C; and a side-mode suppression ratio exceeding 70 dB. Variants with the same design emitting at 1.5 µm produce a continuous-wave output of 300 mW at 25°C, and a peak power of 32 W when driven with short pulses.

To address limitations associated with self-heating that led to the leaking of light, Itoh and co-workers have recently introduce an in-plane heterostructure. This refinement is accomplished by reducing the size of the air holes near the device periphery, a change that leads to a lowering of the photonic band-edge frequency and ultimately an enhanced in-plane optical confinement. With this modification, output power climbs to 700 mW, and wall-plug efficiency is 27 percent at 25°C.

Itoh and co-workers have also investigated the reliability of their PCSELs. Results are encouraging, with no degradation observed when driving these devices for 2,500 hours at 105°C.

Benchmarking these PCSELs against high-power DFB lasers also leads to promising findings, including a superior wall-plug efficiency, a higher side-mode suppression ratio and a much narrower beam divergence.

### Into the blue

Most of the development of the PCSEL has involved GaAs and InP material systems. But to reach shorter wavelengths, these emitters must be formed with the GaN-based material system.

In Japan, much effort has been devoted to the development of surface-emitting lasers based on GaN and its alloys. More than a decade ago, Nichia made a number of early breakthroughs in GaN VCSEL performance, including the first device producing more than a milliwatt. And more recently, other Japanese leaders in optoelectronics have grabbed the headlines, with impressive output powers of 15.4 mW and 22.2 mW, announced at Photonics West 2019 by Sony and Stanley Electric, respectively. Later that year, Stanley followed this up with a paper in Applied Physics Express, detailing a Watt-class blue-emitting array of 16 by 16 VCSELs.

Given how hard it is to make progress with GaN-based VCSELs, mainly due to issues associated with producing the mirrors - there's no ideal latticematched pairing with a high refractive index contrast and good electrical conductivity - it's not that surprising that Stanley Electric has also started to develop GaN-based PCSELs. Efforts on this front were presented in Glasgow by Mei Emoto, who described the progress of a collaboration between

researchers at Stanley Electric and Kyoto University.

Emoto began by putting recent efforts in context, explaining that Noda's group produced the first ever GaN-based PCSEL, reporting that success in 2008. That breakthrough emitter, featuring a triangular lattice and air holes, had a very high threshold of around 70 kA cm<sup>-2</sup>. Weaknesses of that pioneering PCSEL included insufficient resonance, a large scattering loss and a low slope efficiency.

To produce a higher-performance device, Emoto and co-workers switched to a square lattice to enhance optical confinement, optimised the size of the resonator, and developed a SiO<sub>2</sub>-free fabrication method. In addition, they have worked to improve crystal quality, aided by the use of GaN substrates. With these changes, PCSELs with a period for the holes of around 200 nm have a threshold current of around 2.6 kA cm<sup>-2</sup>.

Further improvements have resulted from the introduction of a double lattice that enhances vertical emission and inplane resonance. With this refinement the team produced a single-mode PCSEL with an output of 1 W, emitting at 431 nm from a circular region with a diameter of 300 µm.

Even higher powers have come from an increase in the emission area to a diameter of 500 µm. With this change, output power exceeds 2 W, realised with a slope efficiency of 0.5 W A-1. Emoto revealed that one of the issues with that generation of PCSELs is that as the current through the device is cranked up, there is a slight widening of

Sumitomo Electric Industries has been developing InP PCSELs emitting at 1.3 µm and 1.55 µm. (a) Schematic of these InP-based PCSELs. (b) Light-current-voltage characteristics with far-field pattern (inset) and (c) lasing spectra under continuous-wave operation.

the beam divergence angle. To address this, the team modified the design of its high-power PCSELs, increasing destructive interference to cut off the higher modes. With this optimisation, PCSELs have a stable fundamental mode, a threshold current of around just 1.8 kA cm<sup>-2</sup>, a slope efficiency of 0.6 W A<sup>-1</sup>, and an output power of more than 2 W.

The most recent results may be even more impressive. While Emoto failed to divulge many details, emitting area has increased to a diameter of 1 mm, and the divergence angle is just 0.5°.

Emoto concluded his talk by showing how the team's PCSELs can be used for underwater lidar, operating in systems with a 10 m range, and revealing that they have just started to collaborate with Nichia on the development of these devices.

### **UK efforts**

Within the UK, the host nation for the workshop, there are efforts at developing PCSELs. This includes engineers at Huawei investigating these devices at the legendary facility in Ipswich, previously owned by BT and Corning, and recently renamed as the Bragg Research Centre. Here, efforts are focused on InP PCSELs, primarily for optical communication.

Speaking on behalf of PCSEL efforts at Huawei, Samir Rihani argued that the communication sector has fuelled laser innovation for many decades, driving the development of distributed Bragg reflector lasers in the 1970s; and in the data era that started in the 1990s, the first killer application of the VCSEL. And now with the growth of machine learning and AI, applications that demand massive parallel data transfer, there's an opportunity for a compact, high-power laser, ideally operating at multi-wavelengths – and these requirements could be fulfilled by the PCSEL.

Working towards this, Rihani and co-workers have developed an InP-based multi-wavelength PCSEL with four channels, operating at around 1330 nm. This source has a wall-plug efficiency of 16 percent, and a power-per-channel of 45 mW at a drive current of 250 mA channel. Operating at up to 85°C, the slope efficiency for this PCSEL is 0.24 W A-1.

According to Rihani, the team's quad-PCSEL has good channel uniformity, with a channel flatness of less than 1 dB, meeting the requirement for a multi-wavelength light source. The researchers have demonstrated a channel spacing of 0.6 nm, laying the foundations for a 32-channel PCSEL.

Rihani's colleague, David Moodie, outlined the development of a 1550 nm PCSEL with a hetero-lattice design, created in collaboration with researchers at the University of Nottingham. Moodie explained that the motivation behind this design is an increase wall-plug efficiency, realised by reducing in-plane loss.

In addition, Moodie and co-workers have tried to optimise the round-trip phase from the photonic crystal to the *p*-metal reflector. This investigation involved etching of the *p*-type InP by either 0 nm, 61 nm, 122 nm or 183 nm, prior to addition of *p*-contact layers.

To produce the hetero-lattice PCSEL, the team defined an inner lattice, occupying a 200  $\mu m$  square area, and featuring a double-lattice design — one lattice is shifted vertically and horizontally by a quarter of the 477 nm pitch. In addition to this inner lattice that has a 12.6 percent fill factor, the engineers formed a second photonic crystal that occupied the remainder of the 300  $\mu m$  by 300  $\mu m$  area. For this photonic crystal, there's a 15.5 percent fill factor, and circular holes with half the pitch of the inner fill factor.

According to Moodie, the best results came from PCSELs with no *p*-type etching. For these devices, the introduction of the hetero-lattice increased the slope efficiency by 34 percent, boosted the output power, improved linearity, and ensured that the laser continued to operate in single-mode at higher current densities.

Hetero-lattice PCSELs produced single-mode lasing at up to 85°C.

Measurements of these PCSELs recorded powers of 249 mW and 145 mW at 25°C and 55°C. Driven at 2.5 A, side-mode suppression ratio exceeded 65 dB at both these temperatures. Moodie told the delegates in Glasgow that the team are also developing 1300 nm PCSELs, and getting "good" results.

Given the location of the workshop - it's in the backyard of Vector Photonics, a pioneer of the PCSEL - an absence of any presentations from the start-up, including any posters, will have raised a few eyebrows, particularly as this company initially had a very public profile. Over its first five years it has undergone major changes, including the departing of two of the four co-founders, including the CEO, as well as a Sales and Marketing Director. While such an upheaval might suggest a company in turmoil, it would be wrong to read too much into these developments. Vector is taking on new staff, with some at the conference, and it is making progress. As efforts are commercially sensitive, this restricts opportunities to details successes, accounting for the restricted engagement in Glasgow.

### State of play

The second International Workshop on the PCSEL concluded with a discussion between all delegates on potential stumbling blocks to the commercial success of this laser. There are no major concerns related to the manufacturability of this device, and when its production moves to larger substrates, this will enable the use of better tools that increase yield and performance.

Proving reliability may not been a significant stumbling block either. Initial results are encouraging. As well

The biggest issue facing the PCSEL is what will be its 'killer' application. But rather than identifying this, maybe there's a need to walk before running – that is, find a market that will allow a ramp to relatively modest volumes, providing a platform to targeting bigger successes.

> A converted church, now known as Òran Mór, provided the setting for the conference dinner.

as findings by Sumitomo, already described in this conference report, investigations by Changchun Institute of Optics, Fine Mechanics and Physics are encouraging – they determined an extrapolated lifetime of just over 8.000 hours, based on pulsed operation at 25°C (10 kHz, 4.75 ns); and an accelerated aging lifetime test at 85°C

using the same pulse conditions led to no obvious degradation over 240 hours, indicating a life span of 3,288 hours. However, there is no standard for lifetime testing, an issue that may hamper commercial success.

In many applications, the wall-plug efficiency is a critical metric. For PCSELs, the best efforts have been around 30 percent. In contrast, for GaAs-based laser diodes, this figure is above 70 percent. For that class of laser, efficiencies increased about 20 years ago, spurred on by a DARPA-funded programme known as SHEDS – super high-efficiency diode sources. This effort, which included identification and quantification of loss mechanisms, provided funding for US companies to increase efficiencies from around 50 percent to 65 percent within 18 months. If successful, further funding followed, for an 80 percent target. Maybe a similar focus on the origins of losses in PCSELs. and addressing them, could spur improvements in this area? Offering hope, Noda revealed that his team have recently delivered a substantial hike in efficiency, with results soon to be published.

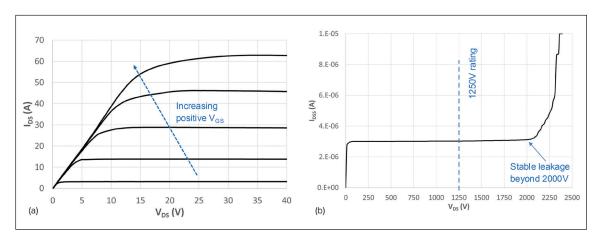

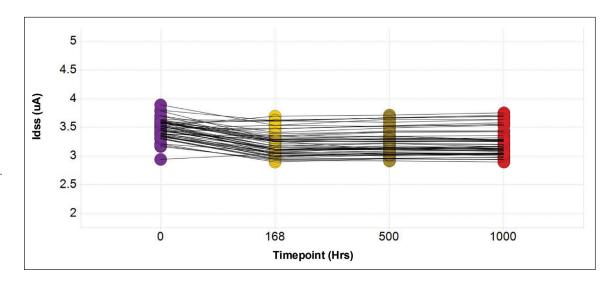

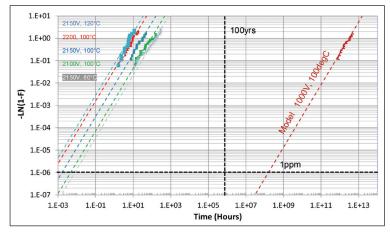

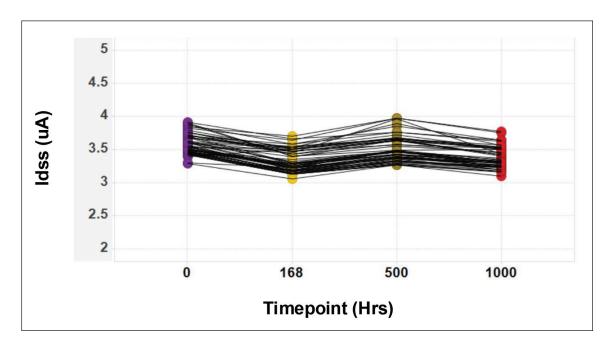

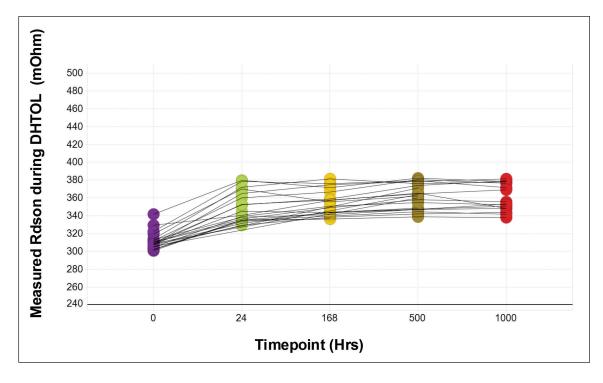

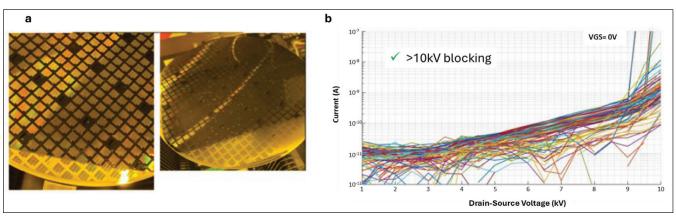

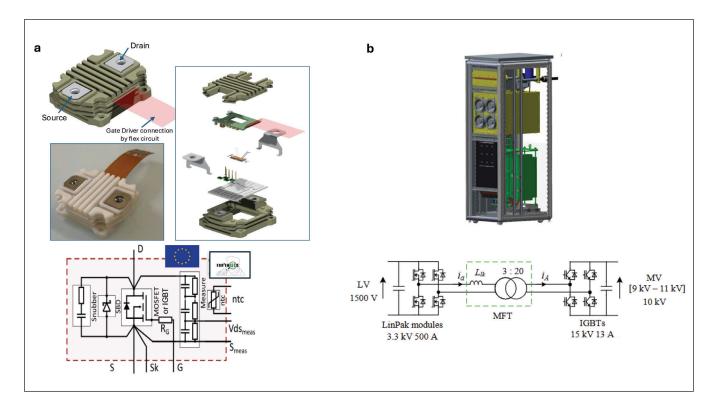

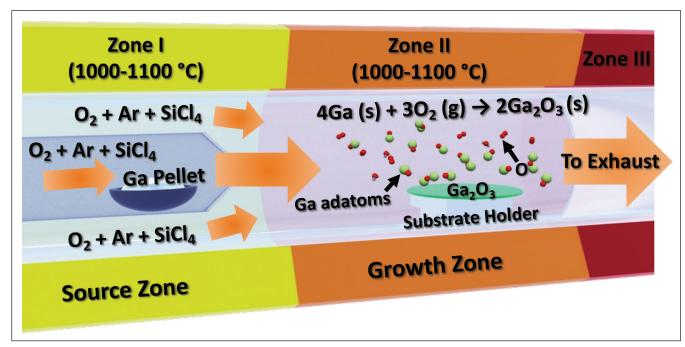

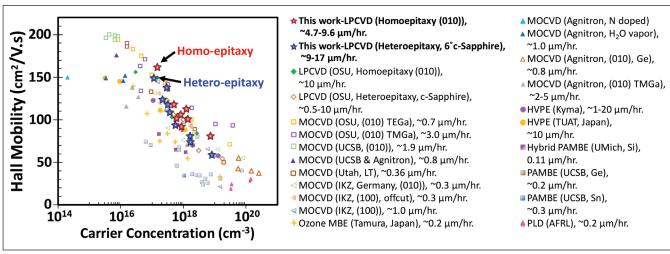

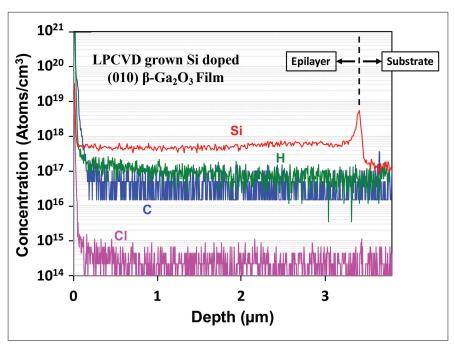

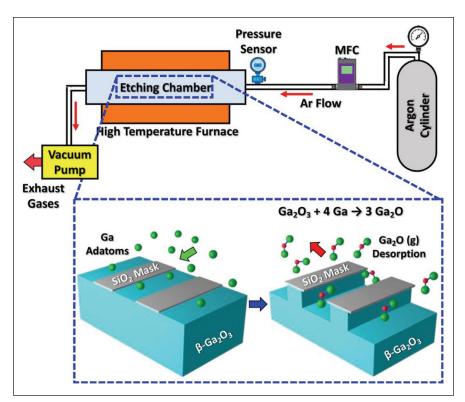

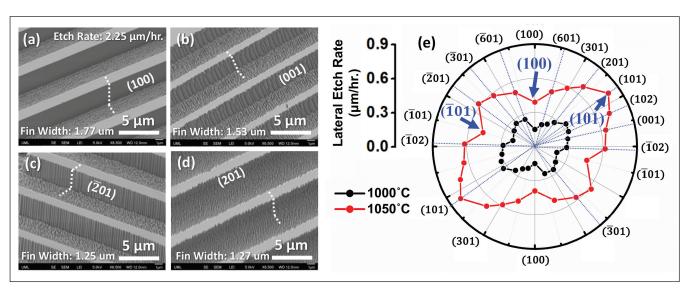

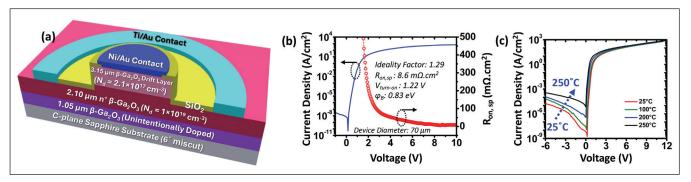

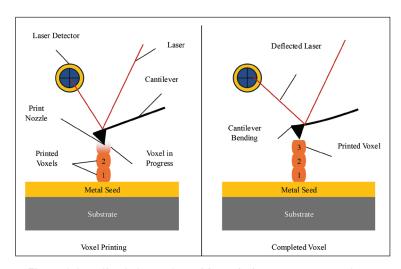

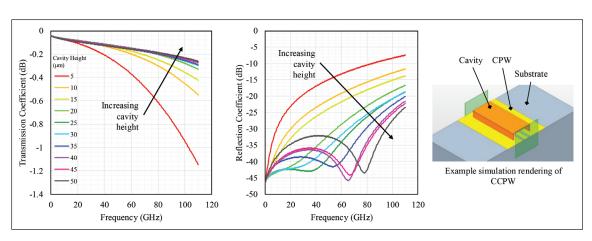

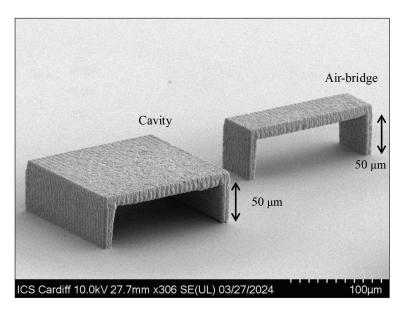

The biggest issue facing the PCSEL is what will be its 'killer' application. But rather than identifying this, maybe there's a need to walk before running - that is, find a market that will allow a ramp to relatively modest volumes, providing a platform to target bigger successes.