# CONPOUND SENICONDUCTOR Connecting the Compound Semiconductor Community

Volume 23 Issue 5 JULY 2017

🔰 @compoundsemi

www.compoundsemiconductor.net

### Understanding the low efficiency of GaN lasers

MicroLED displays: How good are their prospects?

Bridging the green gap with novel substrates

GaN-on-silicon devices get the green light

CS Mantech: Refining GaN HEMT production

Inside News Review, News Analysis, Features, Research Review, and much more... Free Weekly E News round up go to: www.compoundsemiconductor.net

### YOU THINK, GLOBAL MEGA TRENDS REQUIRE BEST PERFORMANCE III-V MATERIALS WE THINK THAT TOO. THE AIX2800G4-TM

3D-SENSING J AUGMENTED REALITY AUTONOMOUS DRIVING CLOUD COMPUTING INTERNET OF THINGS/5G NEXT GENERATION DISPLAYS

### DISCOVER THE AIX2800G4-TM.

Tool of Record for all AsP-based materials for next generation applications.

Market leading technology delivering best yield combined with highest productivity in the industry.

AIXTRON SE info@aixtron.com · www.aixtron.com

# Viewpoir

By Dr Richard Stevenson, Editor

### Lighting with lasers?

SEVERAL EXPERTS have suggested that the GaN-based laser will supersede the LED as the dominant source for solid-state lighting.

The most famous figure indicating that this could happen is Shuji Nakamura. In the lecture he gave for winning the Nobel Prize for Physics in 2014, he pointed out that GaN lasers operating at high current densities could create white light sources with a staggering light output.

Others enthused by the potential of laser-based lighting include Jonathan Wierer and Jeffrey Tsao from Sandia National Labs. They have evaluated the capability of a white light source that mixes several lasers emitting at different wavelengths. Their calculations suggest that the resultant source, which would include GaN lasers emitting in the blue and green, could be very attractive, partly due to its freedom from droop.

Commercialisation of white-light, GaN-based laser sources is already underway, with headlights of high-end cars, such as premium models made by BMW, providing the bestknown success. In this application, the laser's directionality enables illuminated of the road far ahead with a carefully chosen beam.

Editor Richard Stevenson Contributing Editor Rebecca Pool News Editor Christine Evans-Pughe Editor Richard Stevenson Sales Executive Jessica Harrison USA Representatives Tom Brun Brun Media Janice Jenkins Publisher Jackie Cannon Director of Logistics Sharon Cowley Design & Production Manager Mitch Gaynor

richardstevenson@angelbc.com editorial@rebeccapool.com chrise-p@dircon.co.uk richardstevenson@angelbc.com +44 (0)1291 629640 jessica.harrison@angelbc.com tbrun@brunmedia.com jjenkins@brunmedia.com jackie.cannon@angelbc.com sharon.cowley@angelbc.com

+44 (0)2476 718209 +001 724 539-2404 +001 724-929-3550 +44(0)1923690205+44 (0)1923 690200 +44 (0)1923 690214 mitch.gavnor@angelbc.com

+44 (0)1291 629640

So, given the progress made to date, is laser-based lighting of homes and offices just around the corner? Well, probably not, according to theorist Joachim Piprek from the NUSOD Institute.

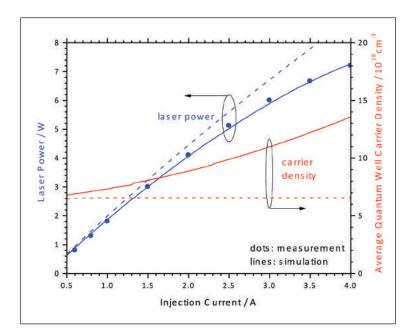

In this month's issue, in his piece entitled What is to blame for the low efficiency of GaN-based lasers? (see p.34), Piprek presents the results of calculations that suggest that lasers may never get close to the efficiency of LEDs - so there is no change in the status quo on the horizon.

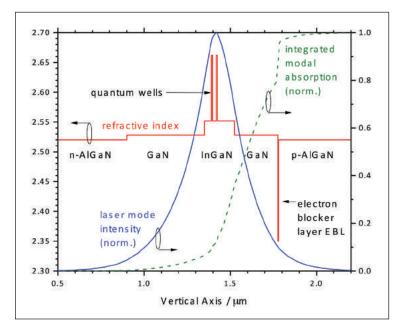

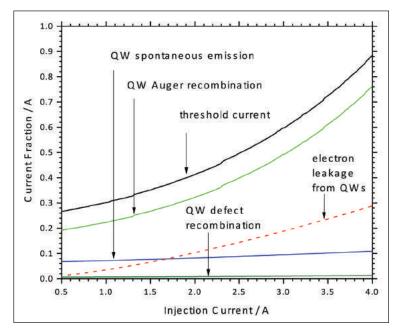

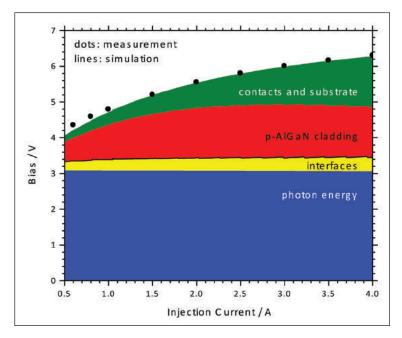

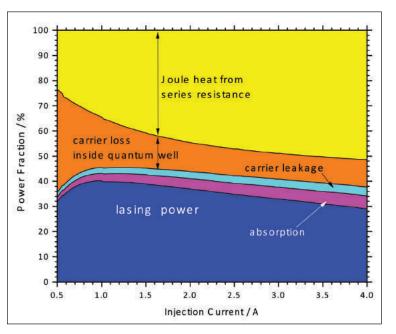

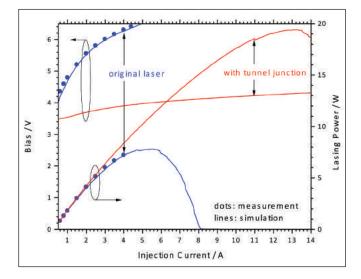

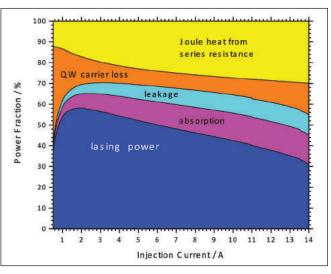

According to Piprek, the best blue LEDs can now hit an efficiency of 84 percent, while lasers are limited to just 43 percent. The latter is held back by various loss mechanisms: Joule heating, due to a high series resistance; losses inside

the quantum well, predominantly resulting from Auger recombination; electrical leakage; and optical absorption.

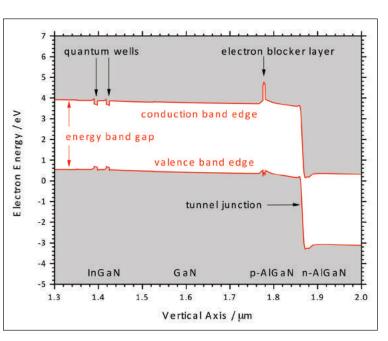

Piprek points out that higher laser efficiencies could be reached with a novel architecture that has been pioneered by Nakamura and co-workers.

Out goes the *p*-doped cladding, replaced with a tunnel junction and a highly conductive *n*-doped layer. Turning to this unconventional design slashes cladding and contact resistances on the *p*-side, leading to far lower bias and selfheating. Fewer carriers are then needed for lasing, reducing Auger recombination and delivering a three-fold hike in peak power. Another benefit is a narrowing of the efficiency gap with the LED, but the difference is still significant - so it would appear that LEDs bulbs are safe for the foreseeable future.

Circulation Director Jan Smoothy +44 (0)1923 690200 jan.smoothy@angelbc.com Chief Executive Officer Stephen Whitehurst stephen.whitehurst@angelbc.com +44 (0)2476 718970 Directors Bill Dunlop Uprichard - EC, Stephen Whitehurst - CEO, Jan Smoothy - CFO, Jackie Cannon, Scott Adams, Sharon Cowley, Sukhi Bhadal, Jason Holloway

Published by Angel Business Communications Ltd, Hannay House, 39 Clarendon Road, Watford, Herts WD17 1JA, UK. T: +44 (0)1923 690200 E: ask@angelbc.com

Accounts & Multi Media Angel Business Communications Ltd, Unit 6, Bow Court, Fletchworth Gate, Burnsall Road, Coventry CV5 6SP, UK, T: +44 (0)2476 718 970 E: info@angelbc.com

Compound Semiconductor is published eight times a year on a controlled circulation basis. Non-qualifying individuals can subscribe at: £105.00/e158 pa (UK & Europe), £138.00 pa (air mail), \$198 pa (USA). Cover price £4.50. All information herein is believed to be correct at time of going to press. The publisher does not accept responsibility for any errors and omissions. The views expressed in this publication are not necessarily those of the publisher. Every effort has been made to obtain copyright permission for the material contained in this publication. Angel Business Communications Ltd will be happy to acknowledge any copyright oversights in a subsequent issue of the publisher. The paper used within this magazine is produced by chain of custody certified manufacturers, guaranteeing sustainable sourcing. US mailing information: Compound Semiconductor, ISSN 1096-598X, is published 8 times a year, Jan/Feb, March, April/May, June, July, August/September, October, November/ December by Angel Business Ctd, Unit 6, Bow Court, Fletchworth Gate, Burnsall Rd, Coventry CV5 6SP UK. The 2017 US annual subscription price is \$198. Airfreight and mailing in the USA by agent named Air Business Ltd, c/o Worldnet Shipping Inc., 156-15, 146th Avenue, 2nd Floor, Jamaica, NY 11434, USA. Periodicals postage paid at Jamaica NY 11431. US Postmaster: Send address changes to Compound © Copyright 2017. Air Business Ltd, c/o Worldnet Shipping Inc., 156-15, 146th Avenue, 2nd Floor, Jamaica, NY 11434, USA. Printed by: The Manson Group. ISSN 1096-598X (Print) ISSN 2042-7328 (Online) © Copyright 2017.

Volume 23 ISSUE 4 JULY 2017

Self-driving mode Program: oncoming driv Front camera Real time scan

### **COVER STORY**

### 16 Building better low-light detectors

A stack of alternating layers of GaN and AIN creates an avalanche photodiode with high sensitivity and excellent controllability

## 22 Is the microLED the next display revolution?

Displays based on microLEDs combine exceptional contrast with a vast colour gamut, tremendous brightness and a great deal of ruggedness, but will production be held back by their complexity?

# 28 Bridging the green gap with a new foundation

Relaxed InGaN substrates open the door to high quality lighting and full colour displays based on III-nitride LEDs

### 34 What is to blame for the low energy efficiency of GaN-based lasers?

24

Why is the power conversion efficiency of the leading GaN lasers just half of that of the best LEDs?

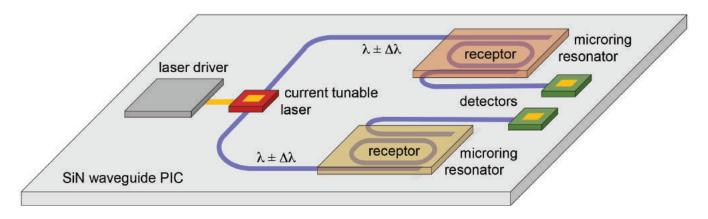

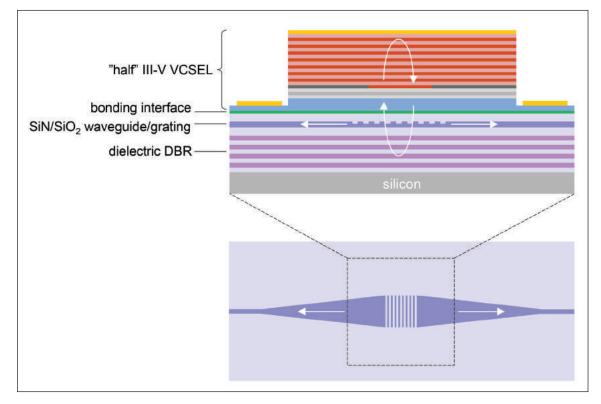

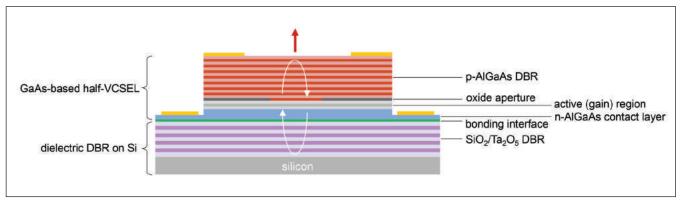

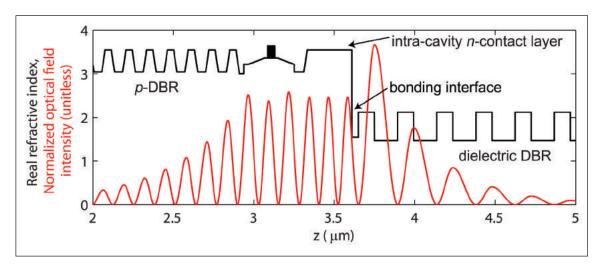

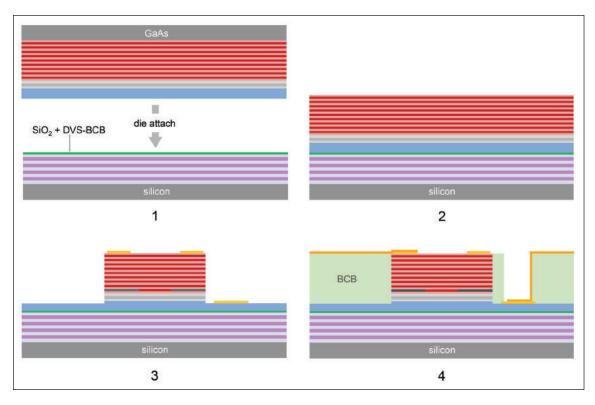

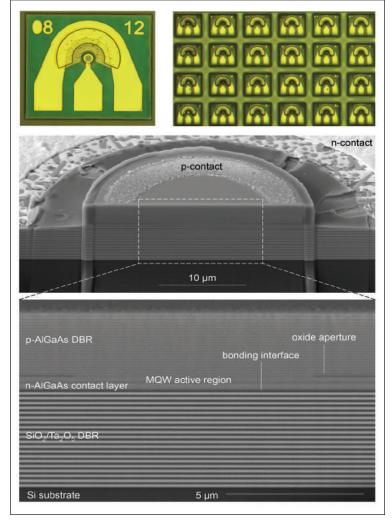

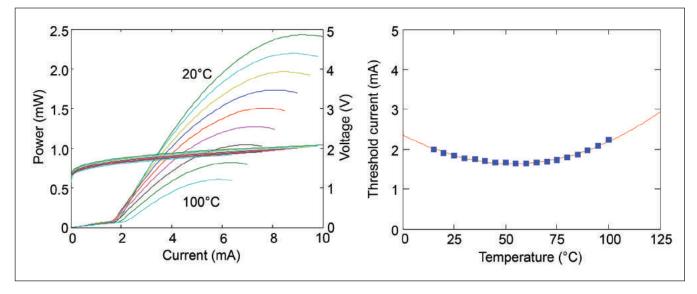

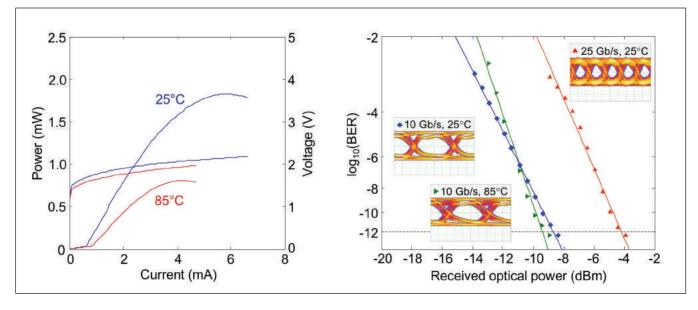

### 40 Empowering silicon with vertical-cavity lasers

Bringing the advantages of the VCSEL to silicon photonics with vertical-cavity lasers

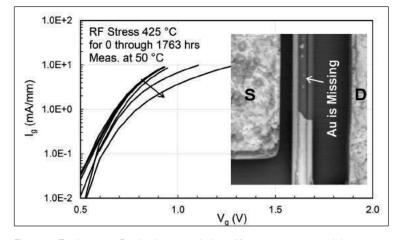

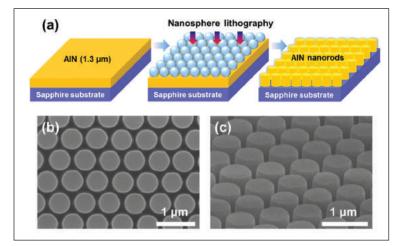

# 46 Refining production of the GaN HEMT

At CS Mantech, engineers revealed how to build GaN HEMTs with greater gain, higher efficiency and increased mobility

### news

- Compound semi market growing 8 percent CAGR

- Raytheon GaN radar surpasses1000 operational hours

- 38 Sofradir designs supersize short wave IR detector

- Imec announces GaN-on-silicon breakthrough

- TI GaN design drives 200 V AC servo drives with 99 percent efficiency

### news analysis

12

- 12 Green light for GaN devices

- 14 Infineon: SiC modules and more

### research review

- 51 Deep UV LEDs: Increasing extraction with nanoscale patterns

- 52 Exposing oxygen defects in GaN HEMTs

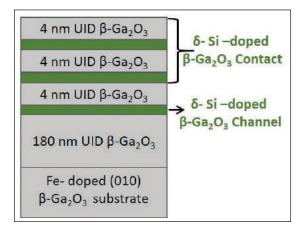

- 53 Gallium oxide transistors target RF

### Compound semi market growing 8 percent CAGR

IN A NEW REPORT covering 2017 to 2021, market research analysts at Technavio predict that the global compound semiconductor market will grow at a CAGR of over 8 percent by 2021.

This market research identifies the rising global adoption of smartphones as one of the primary growth factors, driven by the availability of low-cost smartphones and the increased penetration of the Internet.

An increase in mobile devices drives the market for components such as GaAs amplifiers and switches. Additionally, says Technavio, smartphone manufacturers are trying to develop solar-powered smartphones by using GaAs. This will drive the production of smartphones powered by GaAs-based solar cells, which will subsequently drive the growth of the compound semiconductor market.

Growth in industry automation will also drive the market in the coming years, according to the report, because compound semiconductors (such as

GaN and SiC) are playing a key role in increasing the efficiency of power consumption.

The report identifies leading vendors in the market as Broadcom, Skyworks Solutions, Cree, and Qorvo. Other prominent vendors include Analog Devices, Osram Opto Semiconductors, GaN Systems, Infineon Technologies, NXP Semiconductors, Advanced Wireless Semiconductor, STMicroelectronics, Microsemi, Texas Instruments, WIN Semiconductors, and AXT. APAC will be the major revenue contributor to the market by 2021.

This is due to the increased demand for power applications and the economic growth in developing countries such as South Korea, China, India, Taiwan, and Malaysia. Additionally, the increasing demand for wireless infrastructure will also boost the growth of the compound semiconductor market in this region.

The report also considers the growth of similar markets such as epi wafers and semiconductor chip packaging, which are expected to grow at a CAGR of 12 percent and 31 percent, respectively, for the forecast period of 2017 to 2021.

In another new report, Technavio predicts that the SiC market will grow steadily at a CAGR of over 14 percent between 2017 and 2021, driven by the growing demand for power inverters for electric vehicles.

Automotive inverters and advanced semiconductor devices based on SiC FETs can save low energy losses and result in improved electric vehicle performance, says Technavio.

### New Lumileds CoBs deliver up to 30000 lumens

LUMILEDS has announced the addition of three new products to its Luxeon CoB Core Range to satisfy high lumen output applications such as streetlights, stadium lights and high bay and low bay fixtures.

"We now have the ability to address not only 40 and 50 W applications but up to 100 W and 120 W applications with these high lumen packages, at the same high efficacy as our Luxeon CoB Core Range (Gen 3) products," said Eric Senders, product line director for the Luxeon CoB Family.

The high lumen extension of the Luxeon CoB Core Range (Gen 3) features light emitting surfaces (LES) of 23, 29 and 32 mm, nominal fluxes of 8,800, 11,000 and 16,000 lm at drive currents of 1.2, 2.1 and 2.2 A, plus efficacy up to 161 lm/W. The arrays are offered over a colour temperature range of 2700K to 5700K and CRI of 70, 80 or 90, with an efficient 70 CRI solution in warmer 3000K for outdoor lighting as well as a special colour requirement for studios and stadiums where cool colour temperatures and high (>90) CRI are required.

The CoBs are mounted on square Metal Core PCBs (MCPCBs), which are claimed to provide the industry's lowest thermal resistance, enabling smaller heat sinks and optics for lower overall system cost.

"Feedback from many CoB customers indicates that heat sinks alone make up a substantial portion of system cost. By keeping the LES as small as possible and having a low thermal resistance substrate, a smaller heat sink can be used and a good portion of the cost has been removed from the system," said

Senders. The Luxeon CoB Core Range (Gen 3) CoBs are compatible with an existing ecosystem of optic, drivers and holders.

# Raytheon GaN radar surpasses 1000 operational hours

RAYTHEON has announced that its GaNpowered Active Electronically Scanned Array (AESA) proposed upgrade to the Patriot Air and Missile Defense has surpassed more than 1,000 hours of operation in just over a year – half the time of a typical testing program.

"We achieved this milestone so quickly because of our successful experience developing and maturing GaN for programs like the US Navy's Air and Missile Defense Radar," said Doug Burgess, director of AESA programs at Raytheon's Integrated Defense Systems business. "We're ready to take the next step and get this radar into the hands of our customers."

During the course of the 1,000 hours, Raytheon's GaN-based AESA prototype radar routinely demonstrated 360-degree capability by working together with a second GaN-based AESA antenna that was pointed in a different direction.

As targets flew out of one array's field of view and into another, the two arrays seamlessly passed information back and forth, tracking the target continuously. The main array also detected and tracked tactically manoeuvring fighter jets and thousands of other aircraft, according to the company.

"Raytheon's GaN technology is backed by 19 years of research and \$300 million in investment, while our competitors are either new to the market or primarily build GaN for commercial applications," said Ralph Acaba vice president of Integrated Air and Missile Defense at Raytheon's Integrated Defense Systems business. Raytheon's GaN-based AESA radar will work with the Integrated Air and Missile Defense Battle Command System and other open architectures. It maintains compatibility with the current Patriot Engagement Control Station and full interoperability with NATO systems.

A number of current and expected future Patriot Air and Missile Defense System partner nations in Europe and Asia have expressed interest in acquiring GaNbased AESA. Poland submitted a Letter of Request for GaN-based AESA Patriot on March 31. Raytheon's GaN-based AESA technology also meets Germany's requirements for the German Taktisches Luftverteidigungssystem, or TLVS, tactical air and missile defence system.

### Dowa to massproduce high Output UV LEDs

DOWA ELECTRONICS MATERIALS has developed a deep ultraviolet LED chip it says features the industry's highest output power, with a peak wavelength of 280 nm, output of 75 mW and dimensions of 1 mm x 1 mm. The company will be massproducing these new products, with capacity equivalent to one million LED chips per month.

Since deep ultraviolet lights with a wavelength of 280 nm have a high efficiency of disinfestation, replacing the conventional mercury lamps with these LEDs enables facilities to be smaller and mercury-free. With other advantages, such as power saving, this product is expected to find new smart applications.

Combining an AIN template with crystal growth technology, Dowa Electronics Materials successfully began to mass-produce robust, deep ultraviolet LED chips in 2010.

Its development of what it believes is the world's highest output power deep UV LED chip is thanks to better luminous efficiency, by applying improved crystal growth technology together with an optimised LED chip design of dimension and structure.

The new UV products may provide light source manufacturers with a greater flexibility for selection of package formats, such as lamps and chip-on-board (COB). Dowa will also supply some finished products such as various kinds of the surface mount device (SMD) and conventional TO-Can package.

### Sofradir designs supersize short wave IR detector

IR DETECTOR specialist Sofradir has announced it is developing its first very large format (2048x2048) 15 µm-pitch near infrared detector.

The supersize IR detector is designed for future scientific space observation equipment and state-of-the-art Extremely Large Telescopes (ELT) for ground observation aimed at tackling major scientific challenges.

The ALFA 2Kx2K (Astronomy Large Focal Array) 15µm pitch short-wave infrared detector will provide the highest levels of performance in Quantum Efficiency (QE), dark current and noise in order to optimize IR observations for astrophysicists.

The NIR detector is based on a compound semiconductor material, HgCdTe, as the absorbing material. It includes a readout circuit (ROIC) with a source follower per detector (SFD) at the input stage.

Sofradir is collaborating with leading French research centres CEA-Leti in Grenoble and CEA-IRFU in Paris to develop the ALFA near-infrared detector through an ESA initiative. Sofradir plans to deliver a fully characterized low-flux, low-noise ALFA prototype in Q1 2019.

"Sofradir is pleased to work with partners CEA-Leti and CEA-IRFU in developing a truly evolutionary very large-format infrared detector that will contribute to the detailed study of matter in the universe," said Philippe Chorier, space activities manager at Sofradir.

"Sofradir has a long and successful track record for delivering IR detectors with proven performance, robustness and reliability. We believe ALFA 2Kx2K will enable OEMs to build new instruments, opening up new opportunities for us in astronomy and other sciences, where every single infrared application needs very low flux and low noise compatibility."

Large format infrared detectors, greater than 1024x1024, are highly complex devices that only a handful of manufacturers in the world can produce to space-grade standards. This new low-flux, low-noise near infrared (NIR) 2Kx2K detector for space astrophysics is the result of developments the ESA initiated several years ago, under its Near Infrared Large Format Sensor Array (NIRLFA) program. This is a program that Sofradir, CEA-Leti and CEA-IRFU have been working on since 2009.

The development of the detector will benefit from Sofradir's

experience as one of the leading worldwide manufacturers for IR detectors deployed in space; totaling more than 82 flight models to date. Space programs include: Sentinel 2 and Sentinel 5 (Copernicus), MTG (Meteosat Third Generation) and Exomars, among others.

"Thanks to ALFA detector, Sofradir will be able to offer a new up-to-date solution for applications in space, science and astronomy," Chorier added. Details of the development were presented in the paper 'Development and Characterization of MCT Detectors for Space Astrophysics at CEA' at the International Conference on Space Optics in 2014.

Sofradir and its subsidiaries ULIS and Sofradir-EC exhibited a selection of top-of-the-line infrared detectors for airborne, naval, ground vehicle and space applications at the Paris Air Show.

### Advanced Compound Semiconductor Foundry Services

MOCVD · Fabrication · Testing

Advanced III-V semiconductor solutions for optoelectronics application in the biotechnology, telecommunications, energy, industrial, and defense industries.

MasimoSemiconductor.com | 603-595-8900

# your EPITAXIAL GROWTH partner

InGaM

# Enabling advanced technologies

nA GaN

World leading technology

nGaP

**IGaAs**

- Complete materials range

- ⊜MÓCVD, MBÉ, CVD

- Advanced semiconductor wafer products

- Advanced R&D capabilities

- Multiple, manufacturing sites (Europe, Asia, USA)

www.iqep.com

# Imec announces GaN-on-silicon breakthrough

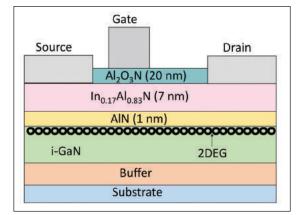

BELGIAN research company Imec has announced that it has developed 200 V and 650 V normally-off/ enhancement mode (E-mode) power devices on 200 mm/8-inch GaN-onsilicon wafers, achieving a very low dynamic R<sub>on</sub> dispersion (below 20 percent) and state-of-the-art performance and reproducibility.

Imec says it technology is ready for prototyping, customised low-volume production as well as for technology transfer. Imec's GaN-on-Silicon device technology is Gold-free and compatible with the wafer handling and contamination requirements for processing in a silicon fab. A key component of the GaN device structure is the buffer layer, which is required to accommodate the large difference in lattice parameters and thermal expansion coefficient between the AlGaN/GaN materials system and the silicon substrate.

Imec says it has achieved a breakthrough development in the buffer design (patent pending), allowing it to grow buffers qualified for 650 V on large diameter 200 mm wafers. This, in combination with the choice of the silicon substrate thickness and doping increased the GaN substrate yield on 200 mm to competitive levels, enabling low-cost production of GaN power devices.

Cleaning and dielectric deposition conditions have been optimised too, and the field plate design (a common technique for achieving performance improvement) has been extensively studied. As a result, the devices exhibit dynamic  $R_{on}$  dispersion below 20 percent up to 650 V over the full temperature range from 25°C to 150°C. This means that there is almost no change in the transistor on-state after switching from the off-state, a challenge typical for GaN technology.

"Having pioneered the development of GaN-on-silicon power device technology on large diameter substrates (200mm/8-inch), imec now offers companies access to its normally-off/ E-mode GaN power device technology through prototyping, low-volume manufacturing as well as via a full technology transfer," stated Stefaan Decoutere, program director for GaN technology at Imec.

# Osram announces multi-chip LED with lens for camera flash

OSRAM OPTO SEMICONDUCTORS has integrated two LED chips and a lens into a single module for camera flash applications. With its brightness of 125 lux, the Oslux S 2.1 is designed to provide uniform illumination of photos and video recordings from mobile devices such as smartphones.

The Oslux S 2.1 for camera flash applications combines two chips of different colour temperatures: a cold white chip with 6,000 K, and a warm white chip with 2,250 K (Dual-CCT), providing both a multi-chip LED and a lens for the first time. This not only makes manufacturing easier by saving a step, but also produces excellent results. The chip has a maximum deviation of 300 K, resulting in good colour fidelity and uniformity across the target scene. While dimensions of 5.0 mm x 5.0 mm x 1.15 mm make the Oslux S 2.1 with its lens slightly taller than previous models, it requires less space on the board and has a smaller exposed aperture than two single LEDs, making it overall a more compact solution.

The silicone lens also allows this module to be reflow solderable, allowing the module to be easily integrated into standard manufacturing flows."With the new Oslux S 2.1 we were able to achieve

### Northrop Grumman introduces 5G MMIC range

NORTHROP GRUMMAN has announced that a range of MMICS produced by its MPS (Microelectronics Products and Services) division meet the Federal Communications Commission's (FCC) 5G frequency allocations at the International Microwave Symposium (IMS) 2017.

"MPS's low noise and high power technologies and products provide a differentiating advantage that allows operators the ability to maximize the number of users and revenue generation, "said Chris Brown, general manager, Northrop Grumman MPS.

"The Northrop Grumman power amplifiers provide the high-linearity performance near peak output power levels required for complex modulations, which optimizes the data throughput within the FCC allocated bandwidth" said Brown. "This same performance advantage is realised in the 5G receivers using the Northrop Grumman low noise amplifiers utilising our GaAs and InP technologies. Between the power amplifiers, the low noise amplifiers and the mixers, we can address all of the 5G frequency bands."

Also at IMS 2017, Northrop Grumman engineers presented on high power and high efficiency chipsets for Ku-Band, Ka-Band, V-Band, Q-Band, E and W-band communications, and on optimising ground, airborne and space-based communication links using Northrop Grumman's advanced semiconductor products and technologies.

very high quality. We have subjected it to both electrical and optically demanding testing and are very happy with the results. It definitely meets our high quality standards," said Russell Willner, product marketing manager at Osram Opto Semiconductors.

news review

# TI GaN design drives 200V AC servo drives with 99% efficiency

TEXAS INSTRUMENTS has introduced a three-phase, GaN-based inverter reference design that helps engineers build 200 V, 2 kW AC servo motor drives and next-generation industrial robotics with fast current-loop control, higher efficiency, more accurate speed, and torque control.

The reference design features TI's newest LMG3410 600 V, 12 A GaN power module with an integrated FET, gate driver and protection, announced last year. The GaN module allows the design to switch up to five times faster than silicon FETs, while achieving efficiency levels greater than 98 percent at 100 kHz and greater than 99 percent at 24 kHz pulse width modulation (PWM) frequency.

With GaN, designers can optimise switch performance to reduce power loss in the motor, and downsize the heat sink to save board space. Operating the inverter at 100 kHz significantly helps improve torque ripple when used with low-inductance motors. According to TI,

the reference design will help engineers design 200 V, 2 kW AC servo motor drives and next-generation industrial robotics with fast, more precise torque control and 99 percent efficiency.The GaN inverter power stage interfaces with microcontrollers (MCU), including TI's TMS320F28379D drive control systemon-chip to help dynamically adjust voltage frequency and achieve ultra-fast current loop control.

TI has also introduced its new Design DRIVE Fast Current Loop software with innovative sub-cycle PWM update techniques that help push current-loop performance in servo drives to less than 1 microsecond, potentially tripling motor torque response. The Fast Current Loop software outperforms traditional MCUbased current-loop solutions, and is available free with controlSUITE software. In addition to the GaN module, the reference design relies on TI's AMC1306 isolated delta-sigma modulators with current sensing to increase motor control performance. TI's ISO7831 digital isolator also provides reinforced isolation between the MCU and the design's six PWMs.

### news analysis

# GREEN LIGHT FOR GAN DEVICES

Exagan and X-Fab prepare for mass production after delivering GaN-on-silicon devices with a 200 mm CMOS process. Rebecca Pool investigates.

### news analysis

IN A BREAKTHROUGH for GaN-on-silicon device markets, industry partners X-Fab and Exagan have produced transistors with a 200 mm, CMOS process.

With substrate fabrication taking place at Exagan's 200 mm epi-manufacturing facility in Grenoble, France, followed by device processing at X-Fab's CMOS foundry in Dresden, Germany, prototype 650 V G-FETs are currently with first customers.

Crucially, plans to ramp production are underway, with mass production well within the companies' sights.

"We are the first to transfer and produce devices on 200 mm wafers, with manufacturing quality, in a CMOS fab using standard silicon production equipments and process steps," claims Frédéric Dupont, president and chief executive at Exagan.

"Importantly, we have established our technology and products on the most competitive wafer size; taking advantage of the mature, 200 mm, and highly productive, manufacturing environment."

"Once our product is established on the market, we will be able to work with X-Fab to ramp up capacity very quickly," he adds.

Exagan's GaN-on-silicon technology has been under development since the late 1990s. Researchers at France-based hetero-epitaxy research centre, CNRS-CRHEA spent more than a decade grappling with the different thermal coefficients of silicon and GaN that cause materials stresses, and ultimately cracking, when a GaN film is grown on silicon. By 2003, a GaN-buffer - for the growth of thick, high-quality GaN layers on silicon – had been developed and patented by wide bandgap semiconductor business, Picogiga, France, later acquired by semiconductor material manufacturer, Soitec, also of France. In 2012, Soitec joined forces with electronics research institute, CEA-Leti, France, to develop a 200 mm, CMOS-compatible GaN-based FET process for 650 V power switching devices, with the technology then being transferred to Exagan for commercialisation.

Collaboration with X-Fab began in 2015 and in just two years several barriers to 200 mm CMOS process success have been overcome. Importantly, says Dupont, Exagan has developed its so-called G-Stack material technology, based on the CNRS-CRHEA buffer layer and including GaN insulating layers and strain management layers. These layers relax the GaN crystal stresses, improving crystal quality and yielding crack-free, flat wafers for CMOS manufacture.

"The larger the diameter, the more challenging it is to get a perfectly flat wafer, and managing cracks and bowing has been a huge challenge," he says. "But G-Stack has addressed this and we can manufacture wafers that are fully compliant with the CMOS process."

Frédéric Dupont, President, CEO and Co-Founder of Exagan (right) with X-Fab chief technology officer, Jens Kosch (left).

The GaN-on-silicon fabrication process adheres to the strict contamination rules of a standard CMOS process. "We also use fully-automated, epitaxy equipment for our eight inch process – including automated wafer handling – to avoid any contact and wafer contamination," says Dupont.

Crucially, not a single, additional processing step or tool is required to support GaN-on-silicon device fabrication. "We really wanted full compatibility with the CMOS line with no extra process steps of specific tools," highlights Kosch. "Our common goal from day one was to avoid additional capital expenditure and we can now use a standard CMOS manufacturing line, running at volume production levels, for this new GaN material."

Right now, Exagan is sampling 650 V G-FETs to its first customers. Devices have been described as having a high breakdown voltage, low vertical leakage and a high operating temperature, although according to Dupont, specific performance figures cannot yet be revealed. The company has also been working with Germany's certification services business, TÜV Nord, to achieve product qualification meeting automotive and aerospace industry standards.

Electric vehicle charging will be amongst the initial targeted applications for Exagan's 650 V G-FETs; a growing market already under scrutiny from other SiC and GaN suppliers. "There are many companies working on GaN but our technology and business model are unique; we control the full technology flow from the epitaxy to system level," asserts Dupont.

"Critically, our partnership with X-Fab gives us the capacity to ramp very quickly to high volumes and with very cost competitive devices," he adds. "I believe we will soon be recognised as the GaN market accelerator."

# **Infineon:** SiC modules and more

With volume production of SiC devices underway, what next for Infineon and compound semiconductors asks Rebecca Pool.

IT'S NO SECRET that higher efficiency, increased power density and a smaller footprint are just a few advantages that SiC MOSFETs offer over the silicon IGBTs. So as photovoltaic inverter, uninterruptible power supply and electric vehicle charging markets finally look set to adopt the technology, industry players have a raft of products ready.

Rohm recently unveiled an all-SiC, 1200 V, 600 A power module optimised for inverters and converters in solar power conditioners, UPS, and industrial power applications, just as Wolfspeed claimed its all-SiC 1200 V power model had met harsh environment qualification tests.

In the last two years, STMicroelectronics has delivered a series of 650 V and 1200 V SiC MOSFETs. And last month Infineon revealed it had started volume production of its full-SiC module while delivering new module platforms and topologies for its 1200 V CoolSiC MOSFET family.

For Peter Friedrichs, Senior Director of Silicon Carbide at Infineon, the time is right to ramp up production. As he puts it: "We are definitely seeing a tipping point for certain applications – solar power conversion, UPS and electric vehicle charging – thanks, in part, to a very attractive total system cost."

According to Friedrichs, inductive components make up a relatively large part of the bill of materials in many applications, including solar power conversion. However, SiC enables higher switching frequencies, allowing the use of smaller external components, including inductors and capacitors, saving board space and overall component cost.

"This reduction in the bill of materials was the tipping point for the use of SiC Schottky diodes more than fifteen years ago," highlights Friedrichs. "And these SiC devices were extremely highly priced at the time."

But looking beyond system costs, the time is also right to ramp up production as the industry transition

from 100 mm to 150 mm SiC wafers is well and truly underway.

In May, last year, STMicroelectronics announced it was scaling up its production of SiC MOSFETs and diodes on 150 mm wafers, predominantly to drive down manufacturing costs and deliver volume to the automotive industry. Now Friedrichs confirms that Infineon has made the transition from 100 mm to 150 mm wafers for SiC diode production.

From word go, the company has also developed its SiC MOSFETs on 150 mm wafers, forging a strong connection between technology development and wafer availability. And right now, the company is sourcing its 150 mm wafers from a handful of vendors worldwide – 'the known companies' says Friedrichs – that can offer volume capability.

"The move from 100 mm to 150 mm is a major change and as always, some customers are more reluctant than others to change their products, but we are nearly there," he says.

"For 150 mm, we still see slight quality differences from supplier to supplier, whereas with 100 mm wafers quality is comparable," he adds. "But we believe we will move beyond this very soon and it isn't a sticking point at all."

#### Chasing markets

Infineon now intends to ease its first full-SiC module based on 1200 V MOSFETs – Easy 1B – into volume production this year. This module will target solar, UPS and charging applications.

Meanwhile, a larger module – Easy 2B – will follow. This version is designed for higher power ratings in target applications. Friedrichs reckons the latest module configurations will also soon be used in industrial drives, medical applications and auxiliary power supplies for the railway sector.

### "We are definitely seeing a tipping point... thanks, in part, to a very attractive total system cost."

Peter Friedrichs, Senior Director of Silicon Carbide at Infineon:

"We have already seen our hybrid modules – which combine silicon IGBTs with silicon carbide diodes – being used in solar power conversion applications, and these will now be partially replaced with the silicon carbide switch," explains Friedrichs. "Silicon carbide is also going to be highly appreciated in the emerging electric vehicle fast-charging infrastructure market, but we do not expect to see modules in actual electric vehicles until at least 2020."

For now, customer acceptance is not a huge issue. According to Friedrichs, some customers are more conservative than others and wish to see field data first, which can be difficult with a new technology. And while faster switching devices bring EMC issues, the Senior Director is confident the necessary support can be offered here. Crucially, Friedrichs reckons the company can keep pace with future leaps in demand. "We expect market growth to be around 20 percent [year-on-year], which is a lot greater than total power semiconductor growth," he says. "But we have good flexibility regarding volume manufacturing. We already have three-and-a-half-million SiC modules in the field – hybrid modules dominate so far – but we expect similar figures for the full-SiC modules as well."

Manufacturing aside, Friedrichs is also certain that SiC very much has its place amongst the rise of silicon semiconductor alternatives. "We believe, for example, that the playground for GaN HEMTs is very much 600 V while SiC can compete with silicon IGBTs at 1000 V and above," he says.

And looking to the future, Infineon has a roadmap in place for higher voltage systems; Friedrichs expects demand for 1700 V full SiC MOSFET modules to be driven by solar power conversion and traction applications, and eventually 3.3 kV modules will follow. "We have frequent discussions about 10 kV and 15 kV parts but are still in 'observation mode' for such devices," he says. "We want to understand that there is a real market here, and that this [development] wouldn't be an academic exercise to simply achieve a world record."

CoolSiC<sup>™</sup> MOSFET Easy 2B

Easy2B in half-bridge topology targets solar inverters, quick-charging systems and uninterruptible power supply applications.

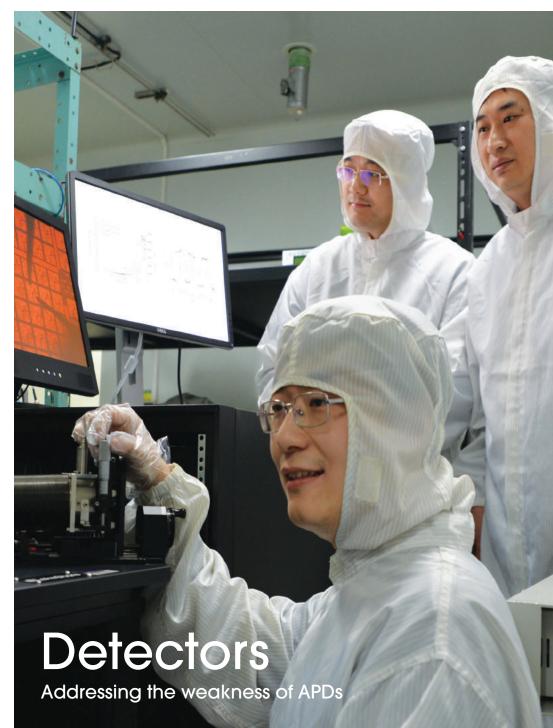

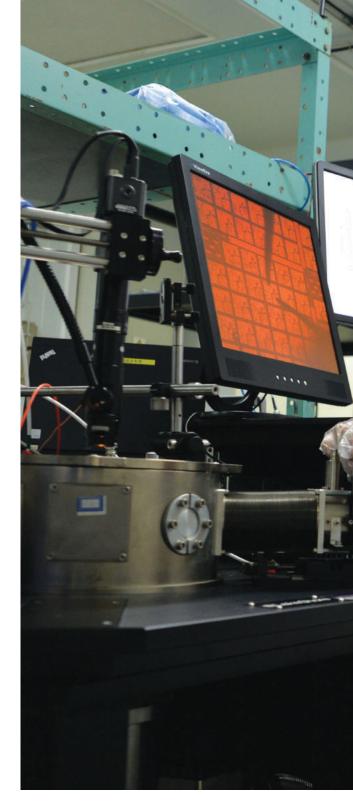

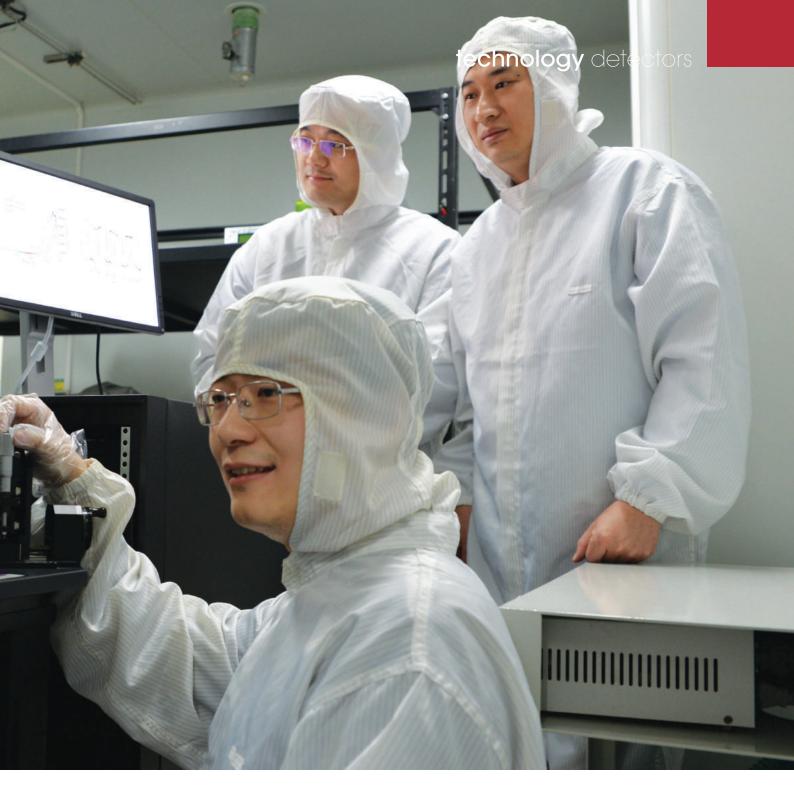

### technology detectors

# Building better low-light detectors

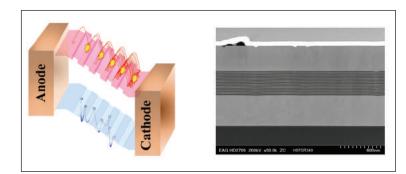

A stack of alternating layers of GaN and AIN creates an avalanche photodiode with high sensitivity and excellent controllability

BY LAI WANG, JIYUAN ZHENG, ZHIBIAO HAO AND YI LUO FROM TSINGHUA UNIVERSITY

> IF YOU NEED to measure incredibly low light signals, you have to make a compromise. If you want the best performance, you must select a photomultiplier tube. However, it is fragile and bulky. The alternative, addressing these weaknesses, is the avalanche photodiode (APD), but it is let down by its poor controllability.

The good news, however, is that this lack of controllability will not be plaguing the APD for much longer, thanks to a recent breakthrough by our group at Tsinghua University, working in partnership with researchers at CNRS-CRHEA, France, and the Chinese Academy of Sciences. Together we have developed a novel APD that delivers a record-breaking stable linear gain of over 10<sup>4</sup> under constant bias –

that's almost two orders of magnitude higher than that of silicon APDs.

With conventional APDs, producing high multiplication gain requires operation under extremely high bias. When controlled in this manner, there is a drastic rise in the response current, known as 'breakdown'. This breakdown will not stop until the bias is reduced below its breakdown value.

What this means in practice is that when using an APD, it needs to be periodically quenched below its breakdown bias, with photons only detected when these diodes are under breakdown. It is a compromise between high gain and sustainable detection, and requires the use of complex control circuits. This

intrinsic limitation has been plaguing researchers for years, who want an APD that works like a PMT, with a controllable avalanche and the opportunity to operate the device under a simple constant bias with high gain. This is what you get with our device.

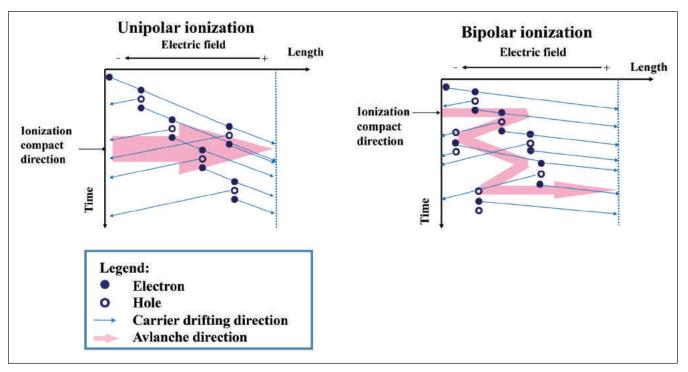

It is important to note that avalanche and breakdown are actually two completely different concepts. Breakdown is a compromise, used to ensure that a conventional APD delivers high gain. In this type of device, a significant proportion of the carrier energy that's drawn from the electric field is thermalized by intense scattering. As a result, these diodes have to work under extremely high bias, because this enables electrons and holes to both trigger ionization (see Figure 1(a)). Multiplication proceeds along two opposite directions, forming positive feedback chains that lead to a drastic rise in the response current.

A better approach would be for just one kind of carrier to trigger ionization, leading to an avalanche march in just one direction (see Figure 1 (b)). If that were the case, the avalanche could stop by itself when all the carriers move out of multiplication region. Thanks to this, the APD could provide a suitable response to the signal when it is operated under constant bias, simplifying its use and the accompanying circuitry.

Our device works on this principal, as do several others. In fact, in general, there are three conventional approaches to improving the sensitivity of linearmode APDs: using materials with a great difference in

Figure 1. Unipolar ionization and bipolar ionization. (a) In a unipolar ionization APD, only one kind of carrier can trigger ionizations. Avalanche proceeds unidirectionally. (b) In a bipolar ionization APD, all carriers can trigger ionization. Avalanche proceeds bi-directionally. The solid and hollow circles represent electrons and holes, respectively; and the small and large arrows represent the carrier drifting direction and the avalanche direction, respectively.

conduction band and valence band profiles, narrowing the ionization region, and turning to impact ionization engineering.

With the first of these, suitable materials are silicon, InAs and HgCdTe. For these semiconductors, the first energy valley of the conduction band is very deep, and electrons traversing it can increase in energy, triggering ionizations without inter-valley scattering. This means that the ionized electrons have far higher energies than the holes in this material. In these devices, gain is relatively high - but it is not high enough. If the APD is made from silicon, the effective mass for the conduction band is relatively large, innervalley scattering cannot be ignored, and the efficiency of electron-triggered ionization is not high enough; and if this device is made from InAs or HgCdTe, the narrow bandgap leads to a risk of Zener breakdown, particularly under high electric fields. What's more, the gain is not that high.

The second option, narrowing the ionization region, can be accomplished with the 'dead space' effect. By localizing the position for ionization, triggering of ionization is restricted to just one type of carrier. There is a price to pay, however – limited ionisation time, and ultimately diminished gain.

The third approach is impact ionization engineering, a technique that involves deploying periodic doping layers and heterojunctions. Here, the challenge is that the active region for ionization is so thick that it is hard to grow many cycles. Gain is limited to around 1000.

If commonly used semiconductors are adopted to construct APDs with either a conventional homojunction or an impact ionization engineering architecture, inter-valley scattering disrupts the transport of carriers. This prevents them from hitting the ionization threshold energy, resulting in a low ionization coefficient.

However, it is possible to overcome scattering and realise a high gain with the GaN material system. For both GaN and AIN, there is a deep  $\Gamma$  valley with a depth of about 2 eV in the first conduction band, and no such valley in the valence band. Due to this, electrons transporting within the  $\Gamma$  valley of either GaN or AIN experience a relatively weak scattering.

When using GaN to make an APD, the ionization threshold energy for electrons is 5.3 eV. Although this is significantly higher than the depth of the  $\Gamma$  valley, the conduction band offset between GaN and AlN is 2 eV. So, when electrons travel from GaN to AlN, along the (0001) direction, they enter into the  $\Gamma$  valley of AlN and are given an increase in energy to more than 4.0 eV. As this is quite close to the ionisation threshold, only moderate electric fields can trigger ionization impact.

We are pioneering the development of this APD architecture, using a GaN/AIN periodically stacked structure to realize controllable electron multiplication

### technology detectors

(see Figure 2 (a) for the bandstructure of our device). To kick-start this effort, we used Monte Carlo simulations based on first-principle theory to model the behaviour of both a conventional GaN-based heterojunction APD and our novel variant – it has a periodic structure, containing alternating AIN and GaN layers with a thickness of 10 nm.

Simulations suggest that our new device delivers a tremendous hike in the ionization coefficient for electrons, while realising a negligible increase for holes. When the electric field exceeds 2.8 MV/cm, the electron ionization saturates at around  $3.96 \times 10^5$  cm<sup>-1</sup>. Under these conditions, the probability of electrontriggered ionization within each 20 nm-thick GaN/AIN period is nearly 80 percent. Such a high ionization coefficient has never been realized in APDs with either heterojunction or impact ionisation engineering structures.

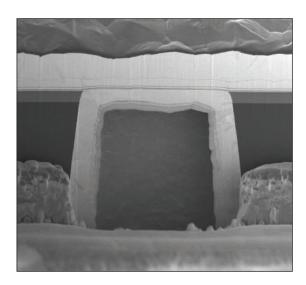

To validate the capability of this APD, we have built a prototype that features 20 periods of 10 nm-thick GaN and AIN layers. This replaces the conventional multiplication layer in a GaN-based, *p-i-p-i-n* device with separate absorption and multiplication regions.

A Riber 32 P MBE reactor was used to grow this structure on a 2-inch, *c*-plane template produced by Suzhou Nanowin Science and Technology. On this foundation, a 4 µm-thick AIN layer on sapphire, we grew a 50 nm-thick AIN layer, followed by a silicondoped 500 nm-thick GaN layer, 20 periods of GaN (10 nm) and AIN (10 nm), a magnesium-doped 10 nm-thick GaN layer, a 300 nm-thick non-intensivelydoped GaN layer and 100 nm-thick magnesiumdoped GaN. Cross-sectional transmission electron microscopy reveals that the layers are uniform, with a thickness that coincides with the designed value (see Figure 2 (b)).

To prevent edge leakage and breakdown, we create a double-mesa architecture, using inductively-coupled-plasma, dry etching. The mesa has an outer diameter of 35  $\mu$ m, and an inner diameter of 25  $\mu$ m that

Figure 2. (a) Applying a relatively weak field to an APD with a periodically stacked GaN/AN structure allows electrons to reach the ionisation threshold of 5.3 eV. (b) Transmission electron microscopy reveals the high quality of this MBE-grown structure.

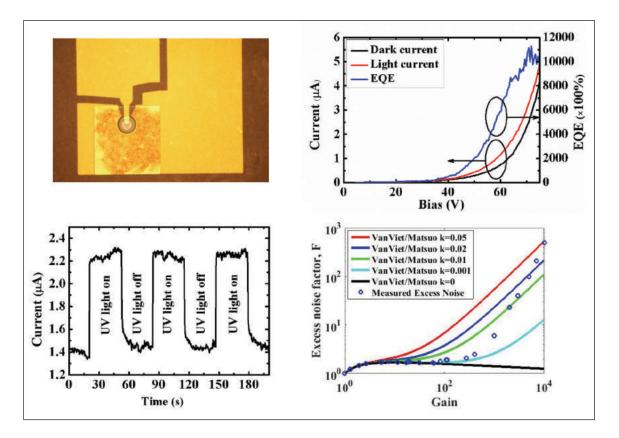

provides the light absorption surface. A layer of  $SiO_2$  is added by plasmas-enhanced CVD to passivate the device. A *p*-type transparent ohmic contact is formed from Ni (2.5 nm)/Au (8 nm), and an *n*-type ohmic contact is created with Cr (25 nm)/Au (200 nm). A 100 nm-thick layer of gold provides the electrode pads that complete device fabrication (see Figure 3 (a)).

We have evaluated the performance of our APDs by measuring current-voltage curves, in the dark and under illumination, with an Agilent Type 4155C semiconductor analysis meter. Illumination of the front of our chip comes from a 350 nm source, with emission from a xenon lamp directed through a monochromator. The light power density is 51  $\mu$ W/cm<sup>2</sup>, equating to 250 pW of power coupled into the chip.

Unlike conventional APDs, the external quantum efficiency of our device increases steadily with bias voltage (see Figure 3 (b)). Gain saturates at  $1 \times 10^4$ . This number can be expressed as about  $2^{14}$ , implying that photon-generated electrons are repeatedly multiplied at least 14 times during a single-pass transport. From this data we can determine that the probability for electron-triggered ionization at each period of the APD is about 70 percent. This is quite close to the simulation result of 80 percent at the

This collection of results demonstrates that electron-triggered ionisation in our GaN/AlN APDs is highly-efficient and controllable. What's more, even better performance is possible. Since the electron ionization coefficient is extremely high, and the multiplication performance is determined by the number of GaN/AlN stacks, simply increasing the number of periods of GaN and AlN, or optimising their thicknesses, should yield a higher gain

### technology detectors

Figure 3. (b) The GaN/AIN periodically stacked APD features a double-mesa design. (b) I-V curves and external quantum efficiency (EQE) of the device. (c) Response of the device under constant bias. (d) Excess noise of the APD under different values of gain.

saturation electric field.

To confirm that our APD can work under constant bias with high gain, we have recorded the roomtemperature response under a constant bias of 65 V (see Figure 3(c)). This current responds well with the switching on and off of the incident ultraviolet light, while the external quantum efficiency hits 10<sup>4</sup>. This result showcases the superiority of our APD, as conventional devices working under constant bias cannot reach such high gain.

This collection of results demonstrates that electrontriggered ionisation in our GaN/AIN APDs is highlyefficient and controllable. What's more, even better performance is possible. Since the electron ionization coefficient is extremely high, and the multiplication performance is determined by the number of GaN/ AIN stacks, simply increasing the number of periods of GaN and AIN, or optimising their thicknesses, should yield a higher gain. An additional insight into the

#### **Further reading** J. Zheng et. al. Appl. Phys. Lett. **109** 241105 (2016) J. Zheng et. al. Sci. Rep. **6** 35978 (2016)

workings of the APD is provided by analysing excess noise (see Figure 3 (d)). Evaluating the ionization coefficient ratio k, by comparing the excess noise with data calculated by the VanVliet/Matsuo model, using different fitting parameters of k, shows that ionization originates purely from electrons – that conclusion can be drawn, because the excess noise factor fits well with the curve for a value of k of zero, when the gain is below 100.

For a gain that is higher than 100, there is a slight feedback from holes during the ionization process. However, even when the gain is as high as 10,000, the value of k is still just 0.05, which is comparable to the value for a silicon APD working under linear mode. That's not to say, however, that performance is similar: our APDs deliver a better linear performance, because their gain is over 10,000, while for silicon it is only about 100. When gain is 10,000, the excess noise factor is only 500.

Our results are very encouraging for the future of lowlight signal measurements. They show that there will come a time when there is no need to select between fragile, bulky photomultiplier tubes and APDs that are difficult to control, thanks to our development of highperformance, periodically stacked structures based on the pairing of AIN and GaN.

# SERVICION ® SEPT 13-15, 2017 | TAIPEI NANGANG EXHIBITION CENTER CONNECT

### **Register Online FREE**

### Get Access to the World's Largest Semiconductor Equipment and Materials Market

SEMICON Taiwan integrates an exhibition, forums, and networking events to provide a complete platform for you to explore unlimited possibilities in the Taiwan high-tech industry.

- AOI

- CMP

- Compound Semiconductors

- Flexible Hybrid Electronics

- High-Tech Facility

- Lasers

- Materials

- MEMS & Sensors

- Micro LEDs

- Opto Semiconductors

- Precision Machinery

- Secondary Equipment

- Smart Manufacturing & Automation

- Circular Economy

### **Co-Location**

DESPITE THE RAPID GROWTH in solid-state lighting, the backlighting of displays remains a substantial market for the LED. For more than a decade, screens have been illuminated with these devices – initially housed in a traditional package, and more recently the chip-scale package – and they are now the omnipotent lighting source in LCDs.

A related success story for the packaged LEDs is as the illumination source in large video billboards, which are a common sight in stadiums, malls and video facades. Here, discrete-packaged LEDs containing red, green and blue chips form individual pixels, with pitches typically ranging from 1 mm to 40 mm, depending on the size of the display and its resolution.

As of today, LEDs have never been used as the direct emissive element – that is the pixel – in smallpitch consumer displays. Many issues prevent this from happening, including concerns related to cost and manufacturability. However, the idea of building a display with microLEDs and sub-millimetre pixel pitches can be traced back to the time when the LED was in its infancy.

# **Is the microLED** the next display revolution?

Displays based on microLEDs combine exceptional contrast with a vast colour gamut, tremendous brightness and a great deal of ruggedness, but will production be held back by their complexity?

BY ERIC VIREY FROM YOLE DÉVELOPPEMENT During the last five years, interest in developing microLED-based displays has taken off. In 2014, excitement in the tech and display communities skyrocketed after Apple acquired Luxvue, a microLED display start-up. Last October, Oculus, the augmented reality/virtual reality (AR/VR) arm of social networking behemoth Facebook, bought microLED start-up InfiniLED and this May, Sharp, now part of the Hon Hai Foxconn group acquired eLux, another microLED outfit.

Given these acquisitions, the technology is not just a lab curiosity. What is driving this tremendous interest by consumer electronic OEMs and leading brands? It is that this technology, which features individual red, green and blue sub-pixels as independently controllable light sources, is capable of forming displays with high contrast, high speed, and wide viewing angles – attributes also found in the pricey OLED displays.

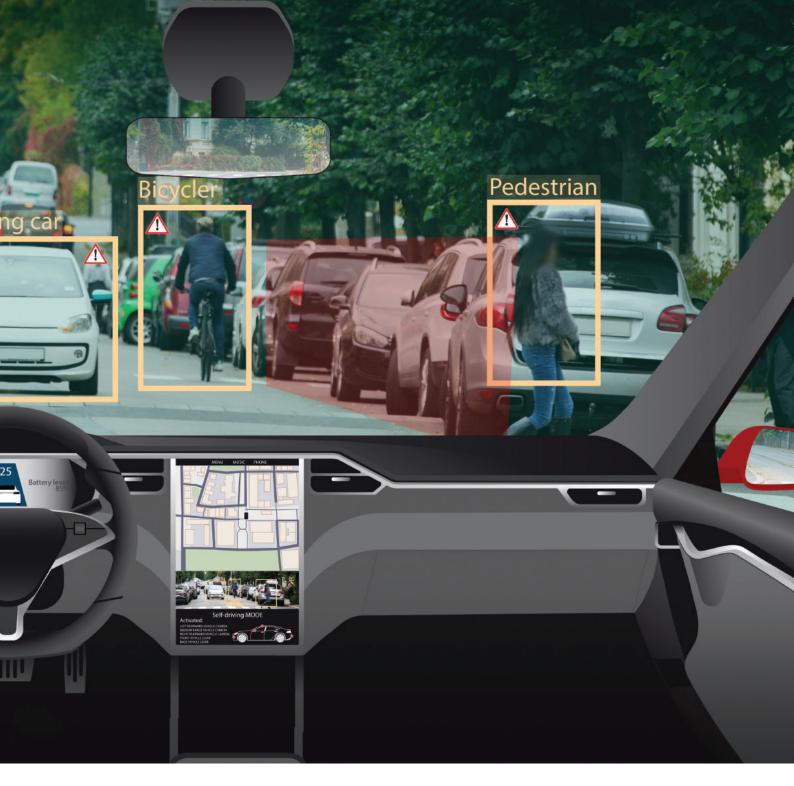

**Self-driving mode** Program: oncoming drive **Front camera** Real time scan

In fact, microLED displays should have the upperhand over OLED rivals, thanks to a wider colour gamut, a brightness that is orders of magnitude higher, a significantly reduced power consumption, a longer lifetime, greater ruggedness and superior environmental stability. What's more, as illustrated by Apple's recent patent filings, microLEDs could allow the integration of sensors and circuits, enabling thin displays with embedded sensing capabilities, such as fingerprint identification and gesture control.

Although microLEDs are still to reach the market, they are far more than just an idea on a drawing board. Back in 2012, at the Consumer Electronic Show, Sony showcased a full HD 55-inch television that featured microLEDs. This display, which received rave reviews from video enthusiasts walking by the booth, contained 6.2 million sub pixels – each an individually controllable microLED chip. However, Sony was noncommittal regarding a commercialisation timeline, and as of today, no microLED TV has ever made it into market.

#### An inherently complex technology

Today, there isn't a commonly accepted definition for microLEDs. However, in general, they are considered to be LED die with a total surface less than 2500  $\mu$ m<sup>2</sup>. This corresponds to a 50  $\mu$ m x 50  $\mu$ m square, or a circular die with a diameter of 55  $\mu$ m. Based on this definition, microLEDs are on the market today – they were unveiled again by Sony, in 2016, in the form of a small-pitch, large LED video wall, with traditional packaged LEDs replaced by microLEDs.

The big question for both the LED and display industries is this: how far off is the small-pitch,

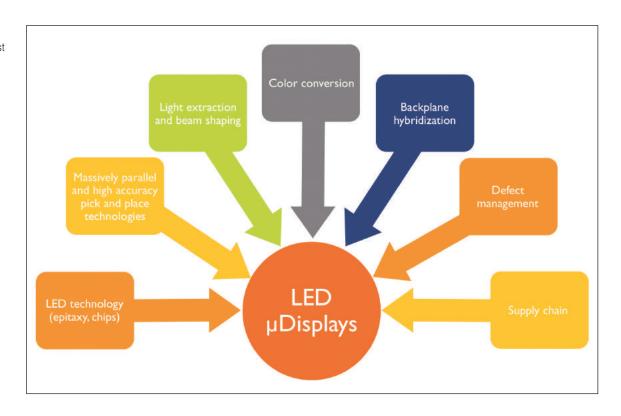

Multiple challenges must be overcome before it is possible to realise the potential of microLEDs.

consumer microLED display? It is this that can target cell phones, smartwatches, TVs, laptops and, more recently, virtual, augmented, and mixed reality, headmounted devices.

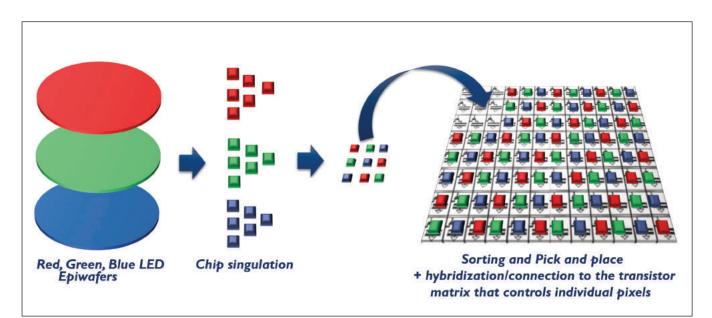

Getting there will not be easy. The art of making microLED displays involves processing of a bulk LED substrate into an array of microLEDs that are poised for pick-up and transfer to a receiving substrate, for integration into a heterogeneously integrated system: the display, which integrates LEDs, pixeldriving transistors, optics and so on. The epiwafers accommodate hundreds of millions of microLED chips, compared to just thousands for traditional LEDs.

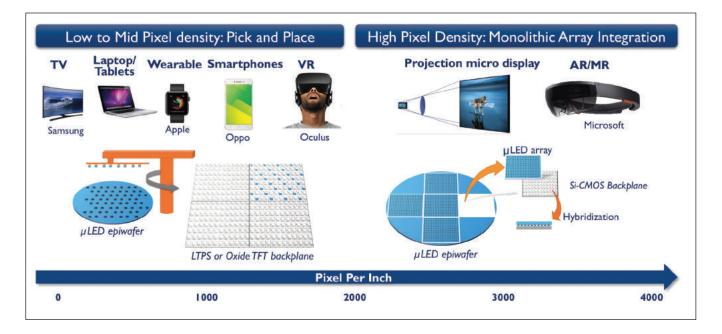

There are two leading options for realising a display with microLEDs. One is to pick up and transfer the microLEDs individually, or in groups, onto a thin-film transistor driving matrix that is similar to the ones already used in OLED displays; and the other is to unite a full monolithic array of hundreds of thousands of microLEDs with a CMOS driving circuit.

If the first of these two approaches is adopted, assembling a 4K display requires picking up, positioning and individually connecting 25 million microLED chips (assuming no pixel redundancies) to the transistor backplane. Manipulating such small devices with traditional pick and place equipment produces a processing speed of around 25,000 units per hour. That's far too slow – assembling a single display would take over a month.

To address this concern, companies such as Apple, X-Celeprint and dozens of others have developed

massively parallel pick and place technologies. They can process tens of thousands to millions of microLEDs simultaneously. However, when microLED sizes are just 10  $\mu$ m, handling and positioning them with sufficient accuracy is very challenging.

There are also issues to overcome with the LED chip. When its dimensions are very small, its performance is held back by nefarious sidewall effects related to surface and subsurface defects, such as open bonds, contamination and structural damages. These imperfections lead to a hike in non-radiative carrier recombination. Sidewall effects can extend over distances similar to the carrier diffusion length, typically 1  $\mu$ m to 10  $\mu$ m: that's not a big deal in conventional LEDs, which have sides of hundreds of microns, but it's a killer in microLEDs. In these devices, it can limit the efficiency of the entire volume of the chip.

Due to these flaws, the peak efficiency of a microLED is often below 10 percent – and it can be less than 1 percent when device dimensions are below 5  $\mu$ m. That's far lower than the best traditional blue-emitting 'macro' LEDs, which can now produce peak external quantum efficiencies exceeding 70 percent. Making matters even worse, microLEDs often have to be operated at very low current densities. They are typically driven way below the 1-10 A cm<sup>2</sup> peak efficiency region, where traditional mid-power LEDs operate, because even at this low efficiency the LEDs are incredibly bright. If a cell phone had microLEDs operating at their peak efficiency, its display would deliver a brightness up to tens of thousands of nits, which is more than an order of magnitude higher than

the brighter phones on the market today. The screen would be so bright that it would dazzle any user bold enough to look at it.

When LEDs operate at a very low current density, their efficiency is so low that the technology cannot fulfil its promise of trimming energy consumption. Consequently, addressing this issue is a key priority for companies involved in microLEDs. Options for increasing efficiency include the introduction of new chip designs and improved manufacturing technologies. Both approaches could reduce sidewall defects and keep electrical carriers away from the edges of the chip.

Developers of microLEDs also face challenges related to colour conversion, light extraction and beam shaping. All are subjects of intense research, licensing, and merger and acquisition activities.

Another requirement for modern displays is the elimination of dead or defective pixels. It is nothing short of utopia to realise a 100 percent combined yield in epitaxy, chip manufacturing and transfer. So microLED display manufacturers must develop effective defect management strategies. They could include pixel redundancies and individual pixel repair, with the approach governed by the characteristics and the economics of the display.

#### Low hanging fruits

MicroLED are capable of being deployed in any display application, from the smallest to the largest. In many cases, they would be even better than the ultimate combination of LCD and OLED displays. But feasibility and economic realities will initially limit the reach of displays to devices where they offer a significant or disruptive gain in performance and functionality, at a cost that is acceptable to the product. Examining in detail the strengths, weaknesses, opportunities and threats for every single application that the microLED display could serve is well beyond the scope of this article. However, detailed analysis indicates that smartwatches and other wearables, such as microdisplays for AR/MR applications, are the most likely applications to initially showcase the capability of microLED displays.

Of these, it is the smartwatch that represents the lowest hanging fruit: it has a relatively small number of pixels and a mid-range pixel density. These characteristics lead to high cost efficiency at the chip and the assembly level. Due to this, displays are nearly within reach of the current technological development status of the microLED – and they have potentially differentiating features, including a reduced power consumption that allows for a longer battery life, and a higher brightness that enables outstanding outdoor readability.

If these displays start to take off, the technology may advance, with the introduction of various sensors within the display front-plane, such as those that can read fingerprints and provide gesture recognition.

Another major opportunity for microLEDs is in augmented- and mixed-reality headsets. Unlike virtually reality, where the user wears a fully enclosed head-mounted display that visually isolate them from the outside world, AR and MR applications overlay computer-generated images onto the real world.

One of the requirements for these applications is that the overlaid image is bright enough to compete with ambient light, especially in outdoor applications. Another criterion is that the display must not be physically located in front of the eye – there it would obstruct the user's vision of the real world. To satisfy these conditions, the display must be MicroLED displays are made by dicing wafers into tiny devices, and tranferring them with a parallel pick-and place technology to a transitor backplane.

MicroLEDs can target a range of applicatrons, which require different pixel densities. located in an unobtrusive location, with the image projected onto the eye, using either complex projection or waveguide optics with an optical efficiency of less than 10 percent. These requirements dictate that the display brightness ranges from 10,000 to 50,000 Nits, which is more than 10 times to 50 times that of the brightness of the best cell phone on the market.

Today, the microLED is the only candidate that has the potential to offer these levels of brightness while maintaining a reasonable power consumption and compactness. Encouragingly, the same reasoning can be applied to head-up displays in automotive and other environments – this class of display can be considered as a form of AR.

A market where the microLED will struggle to make an impact is that of the smartphone. Here OLED displays are already delivering outstanding performance at a very competitive cost. If microLEDs are to be in the game, the size of the subpixel must be reduced to just a few microns. That will make it even harder to deliver acceptable efficiencies, and implement a parallel transfer approach. Success could come more easily in the TV. In this case, the drawback is that pixel densities are relatively low, with a spacing of around 100  $\mu$ m in a 4K, 55-inch set. The low density

hampers the efficiency of the transfer technology, because each cycle needs to move several thousand chips, rather than the hundreds of thousands needed for smartphones or smartwatches. Thriving in this market requires the development of alternative highthroughput assembly techniques.

#### But where's the supply chain?

There are many large companies and multiple startups working on microLEDs, from LED makers such as Epistar, Nichia and Osram; to display makers like Sony, AUO, BOE and CSOT; and original equipment manufacturers such as Apple and Facebook/Oculus. Undertake a thorough patent search and analyses and you'll find more than a hundred companies that have filed for patents related to microLEDs.

Success in this market requires three major disparate technologies and supply chain elements to be brought together: LEDs, thin-film transistor backplanes and chip transfer. This creates a supply chain that is more complex and involved, compared to that of traditional displays. Each process is critical, and it will be challenging to manage every aspect effectively.

No single player is going to solve all the issues, and it's unlikely that a fully integrated manufacturer will emerge. In the smaller markets, such as augmented

A market where the microLED will struggle to make an impact is that of the smartphone. Here OLED displays are already delivering outstanding performance at a very competitive cost. If microLEDs are to be in the game, the size of the subpixel must be reduced to just a few microns. That will make it even harder to deliver acceptable efficiencies, and implement a parallel transfer approach

reality, small companies could bring together the different technologies needed for the product. But that's unlikely to happen in high-volume consumer applications, such as mobiles or TVs, where a strong push from a leading OEM is probably needed to establish a supply chain. Today, Apple has enough leverage and financial strength to be able to bring all partners together. Others that might also be capable of doing this include Oculus, which has invested in microLEDs, with a focus on AR/MR applications.

Within the supply chain, each player will try and capture as much added value as possible. For LED makers, two requirements particular to the microLED – very low levels of defects and high-resolution features – imply large investments in new clean room and lithography equipment. These are criteria that might be better suited to CMOS foundries. Traditional display makers will also come up against new challenges. They are used to manufacturing back and front planes in an integrated fashion, before delivering finished panels to OEMs.

A move to microLEDs could result in these players just providing a thin-film transistor backplane to producers of the final display assembly: either OEMs or outsourced semiconductor assembly and test players. There will be some winners from the introduction of

microLED displays, regardless of the shape of the supply chain. Equipment manufacturers, including makers of MOCVD equipment, will increase their sales, as will suppliers of wafers.

How long will we have to wait until we see the first consumer applications? The science is established, but the microLED is an inherently complex display technology, with cost drivers different to those of incumbents, namely LCD and OLED displays. Based on the latest developments, and the level of maturity in the supply chain, it will be 2019 at the very earliest before a high-volume application hits the market.

There is a good chance that the microLED will succeed in various sectors. However, it is still too early to say whether it will take the industry by storm, or will crash and burn like many other 'promising' technologies of the past. In any case, the vast accumulated and ongoing research and development on the topic should bear fruit and cross pollinate into other applications. It should lead to better, more efficient LEDs; high speed Li-Fi communication; and micro-device transfer technologies that aid other industries.

• Market trends and figures have been extracted from the Yole Développement report MicroLED Displays (Feb. 2017)

### The most cost effective method to excellent quality.

III/V-Reclaim Wald 10 84568 Pleiskirchen / Germany Telefon: +(49) 8728-911093 Telefax: +(49) 8728-911156

E-Mail: sales@35reclaim.com

Internet: www.35reclaim.com

- We recycle your GaAs and InP wafer (all formats and sizes)

- One and double side polished wafer

- Best surface quality for direct use in Epitaxy

- Backside thinning of fully structured wafer

- O Thin wafer (60 μm)

"Now offering Germanium Reclaim"

- Single wafer processing possible

- We buy used wafer and sell recycled wafer

# Bridging the **Green gap** with a new foundation

Relaxed InGaN substrates open the door to high quality lighting and full colour displays based on III-nitride LEDs

BY AMÉLIE DUSSAIGNE FROM CEA/LETI AND DAVID SOTTA FROM SOITEC

THE MAJORITY of commercial white LEDs are based on a blue-emitting chip that pumps a phosphor. This combination has generated tremendous sales, but it does have two major weaknesses: an energy loss of typically 25 percent, associated with the phosphor down conversion; and a colour rendering index that is not that high.

Both these drawbacks can be addressed by direct colour mixing, using LEDs with a variety of emission wavelengths. The ideal way to accomplish this is to use one material system that spans the blue to red, because this simplifies colour control. Do this, and the technology could also find deployment in high-brightness displays.

Fulfilling this dream is not easy, however. The main issue is the material. Although the InGaN alloy can theoretically cover the whole visible range, its quantum efficiency plummets above 500 nm as emission shifts from green to red. Switching to the AlGaInP material family allows the production of high-performance amber and red LEDs, but in this case efficiency takes a nose dive as emission stretches to wavelengths shorter than 570 nm.

The 500 nm to 570 nm spectral range, where it is difficult to realise efficient emission, has its own name: the green gap. For GaN-based LEDs, lack of success stems from a reduction in material quality with increasing indium content in the InGaN alloy. This issue can be traced back to low miscibility of indium in GaN, and the high lattice mismatch between the GaN buffer layer and the InGaN quantum wells.

Our team at CEA/Leti and Soitec has tackled this issue head on with a novel substrate technology that allows InGaN quantum wells to combine a high indium content with great material quality. This is accomplished with substrates that are better suited to the growth of InGaN than the most common one used for nitride LEDs, sapphire.

Growth of GaN-based LEDs on sapphire often begins with the deposition of a GaN buffer layer. That's not a great start, as the buffer layer leads to strong compressive strain. Making matters worse, when InGaN quantum wells are added, the strain gets even higher. Compounding these

Figure 1. The fabrication process for making InGaNOS substrates helps to increase the emission wavelength of InGaN-based quantum wells. issues, internal electric fields in the InGaN/GaN heterostructures hamper LED efficiency when wells are widened, or indium content increased.

The electric field can be eliminated by switching to non-polar GaN planes. But it's not a great solution, as more indium is needed to realise the same emission wavelength.

If concerns over electric fields are put to one side, and the focus placed on limiting the strain, one way forward is to insert AlGaN layers in an InGaN buffer or an InGaN active zone. This has been tested, but no reports of highly efficient LEDs have followed.

Our idea is to grow the LED on a relaxed InGaN substrate, as this reduces the strain between well and buffer. Additional merits of this platform are an increase in the indium incorporation rate and a reduction in the internal electric field for the same emission wavelength.

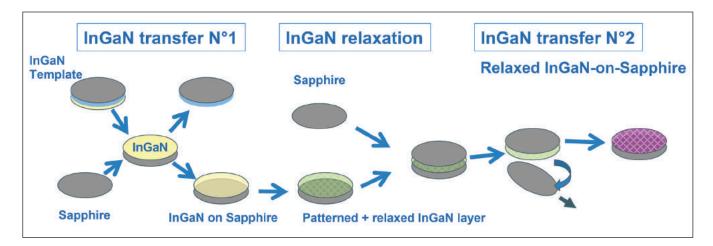

This particular substrate is not available - but we have something similar, an InGaN pseudo-substrate called InGaNOS, based on Soitec's Smart Cut technology. Development of this foundation, formed by transferring a thin layer of InGaN to a sapphire

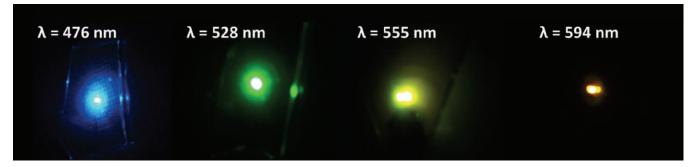

substrate, has been motivated by efforts to reduce the efficiency droop in high-brightness blue LEDs. However, through our work, led by CEA-LETI, we are showcasing the capability of this platform in another arena – its potential to form the base for structures emitting at long wavelengths. Emission can span blue to amber when InGaN LEDs are grown on an InGaNOS substrate, thanks to the increase in the indium incorporation rate.

#### Forming the foundation

Our starting material for making InGaN pseudosubstrates is an InGaN donor template. This template is formed by growing a 3  $\mu$ m-thick GaN buffer layer on a 100 mm sapphire substrate, followed by an In<sub>x</sub>Ga<sub>1,x</sub>N layer that is typically 200 nm-thick and has an indium content, x, of between 1.5 percent and 8 percent. This InGaN donor template, which is strained due to lattice mismatch between GaN-on-sapphire and the In<sub>x</sub>Ga<sub>1,x</sub>N layer, is hydrogen implanted. In parallel, a compliant layer is deposited onto a sapphire substrate, before molecular bonding unites the InGaN donor template and sapphire handle substrate.

The next step is to transfer the donor strained  $\ln_x Ga_{1,x}N$  layer to the compliant layer of the sapphire handle substrate, using Smart Cut technology. Photolithography and dry etching follow to create strained patterns, which are then relaxed, thanks to the compliant layer. This relaxation process proceeds via successive thermal annealings (see Figure 1 for an overview of the entire process).

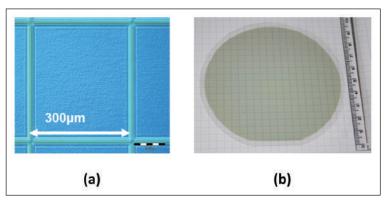

It is not easy to produce a uniform relaxed  $\ln_x Ga_{1,x} N$  layer while maintaining a flat surface. A competitive relaxation mechanism is at play that can cause buckling, and lead to wavy, cracked surface. But we can avoid this by optimising the process, to produce flat patterns from 100 x 100  $\mu m^2$  up to 1000 x 1000  $\mu m^2$  and a partially relaxed  $\ln_x Ga_{1,x} N$  layer with a value of x of up to 8 percent. It is also possible to process patterns down to 10 x 10  $\mu m^2$  with this technology.

The relaxation process produces  $ln_xGa_{1,x}N$  patterns with N-face polarity. That's not ideal, as a top Ga-

face is needed for standard GaN growth. So the full patterned wafer is bonded to a second sapphire handle substrate by molecular bonding, before laser lift-off removes the first sapphire substrate.

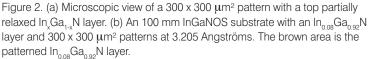

To evaluate the roughness of our partially relaxed  $ln_xGa_{1,x}N$  layers, we have inspected them with atomic force microscopy. This reveals that the roughness is equivalent to that of the donor (see Figure 2(a) for a microscopic view of a 300 x 300  $\mu$ m<sup>2</sup> pattern with a top partially relaxed  $ln_xGa_{1,x}N$  layer).

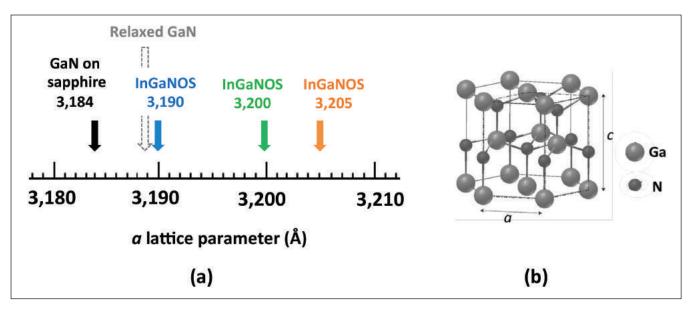

In the relaxation process, a key characteristic is the lattice parameter of the  $\ln_x Ga_{1,x}$  N layer. The GaN buffer fixes the strained  $\ln_x Ga_{1,x}$  N layer *a* lattice parameter of the donor at 3.184 Angström. According to the indium content of the donor and the relaxation process, the InGaNOS *a* lattice parameter can be tuned up to 3.205 Angström, with a uniformity within the wafer of +/- 0.0005 Angström.

We have used our technology to produce wafers that feature partially relaxed  $ln_xGa_{1,x}N$  square patterns on a sapphire substrate. The thickness of the  $ln_xGa_{1,x}N$ layer in each pattern is 100 nm, and it has a standard deviation of 4 nm. This level of uniformity ensures a continuous seed layer for LED growth within the pattern. The surface is epi-ready, and it has the preferred Ga-face polarity (see Figure 2 (b) for an example). Note that at Soitec, there is a lnGaNOS pilot line for 100 mm and 150 mm wafers, and the technology can be scaled to 200 mm.

### **Multicolour** emission

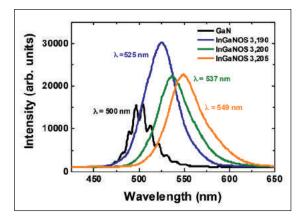

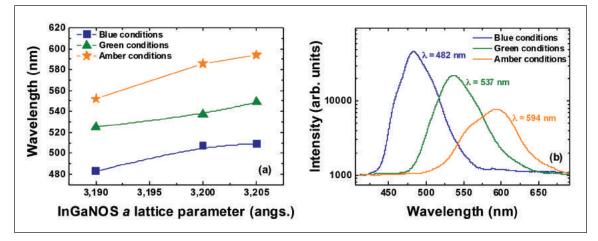

To evaluate the benefits of the relaxed InGaN substrate, we have characterized full InGaN structures that are grown on the InGaNOS substrates by MOCVD. The impact of lattice mismatch on indium incorporation in InGaN quantum wells is assessed with three different InGaNOS substrates – they have a lattice parameters of 3.190 Å, 3.200 Å, and 3.205 Å (see Figure 3). Note that no surface preparation is

needed, as InGaNOS substrates are epiready.

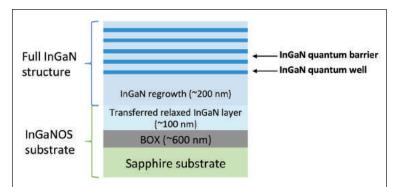

The structure that we have grown consists of a 200 nm-thick  $\ln_y \text{Ga}_{1,y}$ N buffer layer, followed by  $\ln_z \text{Ga}_{1,z}$ N/ $\ln_y \text{Ga}_{1,y}$ N (with z > y) active region with five quantum wells (see Figure 4).

In order to assess the impact of a relaxed InGaN substrate on the indium incorporation rate, it is imperative to apply exactly the same growth conditions to all three InGaNOS substrates. To achieve this, we co-load all the samples in the same run.

We have selected an indium content in the InGaN buffer layer of 4 percent, because this equals the average indium content in the three InGaNOS substrates. Three different growth conditions are then employed for the active region: those that we use in a conventional structure, as well as those with a higher InGaN growth rate and a lower growth temperature. The latter two variants increase indium content, and ultimately shift emission to longer wavelengths. To provide a benchmark for this study, we compare the results with a reference sample – a conventional structure that is grown on a GaN template and features GaN barriers.

Figure 4. The full InGaN structure on InGaNOS that is used to highlight the capability of this substrate for long-wavelength emission.

Figure 5. Photoluminescence spectra at room temperature of full InGaN structures (green conditions) grown on InGaNOS 3.190 Å (blue curve), InGaNOS 3.200 Å (green curve), and InGaNOS 3.205 Å (orange curve). The reference sample on a GaN template has been added for comparison (black curve).