# COMPOUND SEMICONDUCTOR SENSON

CONNECTING THE COMPOUND SEMICONDUCTOR COMMUNITY

VOLUME 31 ISSUE III 2025

COMPOUNDSEMICONDUCTOR.NET

THE TANTALISING PROMISE OF WIDER BANDGAPS

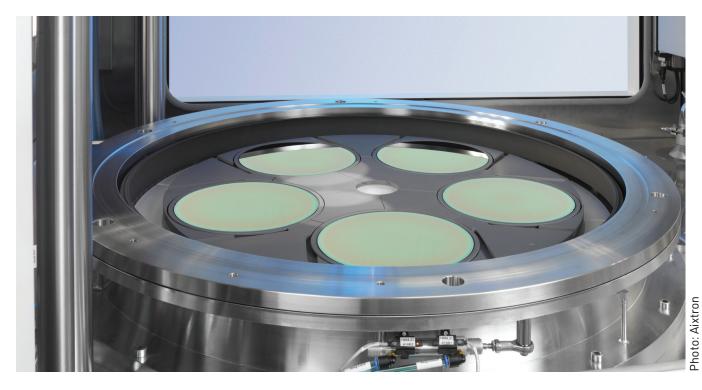

# AIXTRON

# THE NEW G10 SERIES

Your Productivity Solution for All Advanced Epitaxy Materials

## G10-SiC

- ▶ 9x150 mm (6") or 6x200 mm (8")

- New hardware & process surpassing Single Wafer Reactor uniformities

- ► +50% productivity per fab area with large batch technology & small footprint

#### **End Markets/Products:**

EV inverters & charging infrastructure

# G10-GaN

- ▶ 8x150mm (6") or 5x200mm (8")

- ▶ 1st fully automated compact GaN MOCVD cluster designed 100% for Si Power fabs

- Novel hardware solution for unmatched barrier uniformities and device yields

#### **End Markets/Products:**

Power Electronics & Wireless communication

# G10-AsP

- ▶ 8x150 mm (6") or 5x200 mm (8")

- ▶ 1<sup>st</sup> fully automated AsP MOCVD system enabling 10x lower defect density

- Unmatched wavelength uniformity on all wafer sizes

#### **End Markets/Products:**

Micro LED, Optical Data communication, 3D-sensing & LiDAR

# BY RICHARD STEVENSON EDITOR

# **Tumultuous tariffs**

This April, CS International celebrated its 15<sup>th</sup> anniversary. You'll not be surprised that I have been to them all, and I still really look forward to attending. As well as hearing plenty of talks, providing an excellent overview of how our industry is progressing on all key fronts, I enjoy the numerous networking opportunities.

Often my conversations with delegates from all around the world focus on matters related to the commercialisation of new technologies, such as microLEDs and ultra-wide bandgap devices. But this year, global events dominated our conversation, as the Trump administration had just announced details of its tariffs, which sent stock markets into a tailspin.

I failed to find anyone who is supportive of these measures. That's hardly surprising, as working with other countries is the norm for our industry. Raw materials are mined in one location and shipped elsewhere to produce boules, which are sliced and polished into substrates, possibly using equipment made in other countries. And then there's the growth of epiwafers, chip production, and packaging, activities that may involve goods transported over borders. The thought of high tariffs at every stage threatens a snowballing of prices for compound semiconductor devices, which will be used in products subjected to additional tariffs.

However, while widespread tariffs are not popular, and are viewed as a blunt instrument that will harm our industry – and the world at large – they are being introduced against the backdrop of an unlevel playing field. Understandably, governments all around the world have always taken steps to support their own industries. But there's no agreement on what's fair and what oversteps the mark.

I'm aware that Washington has a strong desire to bring manufacturing back to the US, to generate wealth for the nation. It's a laudable aim, involving replacing global

supply chains with sovereign capability. However, it's hard to imagine the introduction of packaging houses in the US, a move that would struggle to generate good wages for workers or competitive products for the domestic market

Since my return from CS International, the US has started to tinker with its tariffs. Initially, Washington watered them down to many countries, a move that's helped turbulent stock markets recover some of their losses. And more recently, there has been a slashing of the whopping 125 percent tariff imposed on China for a range of products, including smartphones, electronic devices and components, such as semiconductors, solar cells and memory cards.

I'm almost certain that by the time you read this there will have been more adjustments to Trump's tariffs. These changes might be good or bad, but what's sure is that we are living in an era of uncertainty – and that's a headwind to both the compound semiconductor community and the global economy.

Free weekly e-news roundup go to: compoundsemiconductor.net

# 14 The tantalising promise of wider bandgaps

Producing power devices with ever wider bandgaps is far from easy, but realising success slashes on-resistance while boosting blocking capability

# 20 Power semiconductors for carbon neutrality

Advances in semiconductor and power electronics technologies, led by increasing deployment of wide-bandgap power devices, are essential for reducing greenhouse gas emissions and developing a carbonneutral energy system by 2050

# 22 Improving GaN with a dash of oxygen

Depositing a partial monolayer of oxygen between a silicon substrate and GaN device layers trims defect density and improves material quality

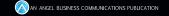

# 26 Exposing SiC defects

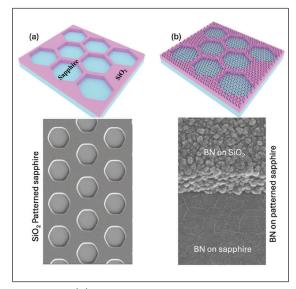

Conductance and optical excitation measurements offer unique insights into interfacial defects in SiC devices

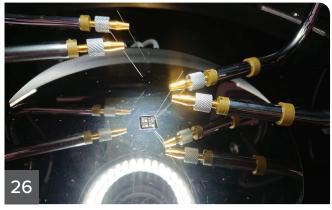

# 32 Cutting the cost of InP-based devices

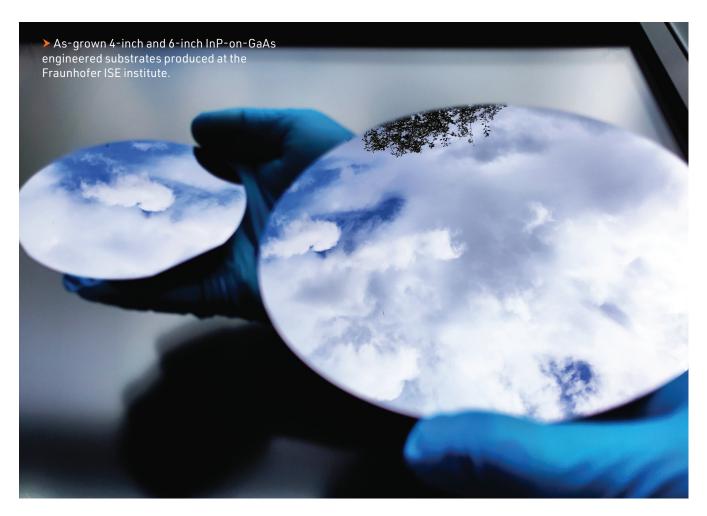

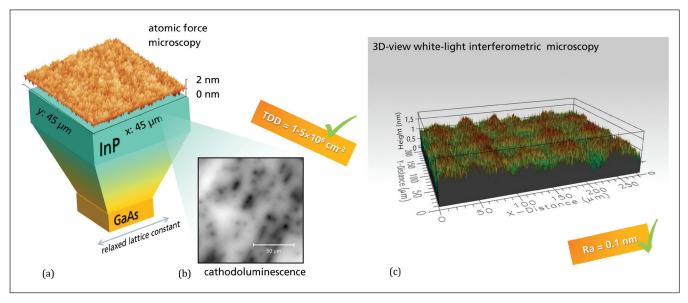

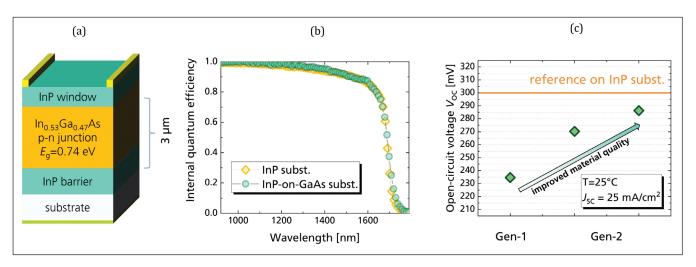

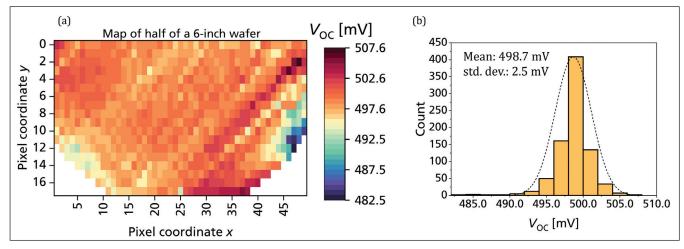

Engineered InP-on-GaAs substrates with diameters up to 200 mm provide a rigid, low-cost platform that can be rapidly ramped to production volumes

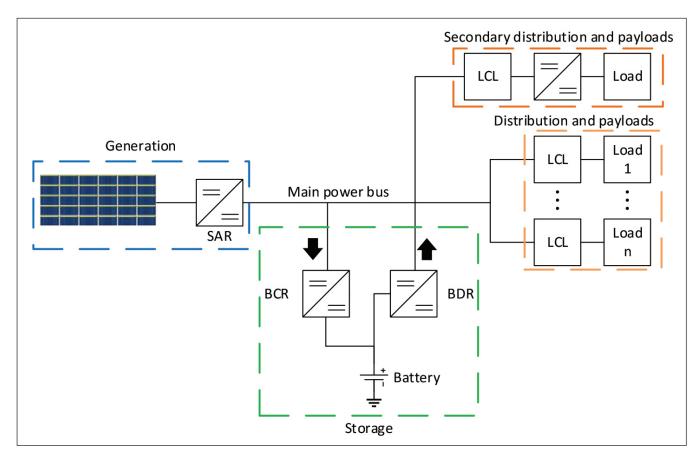

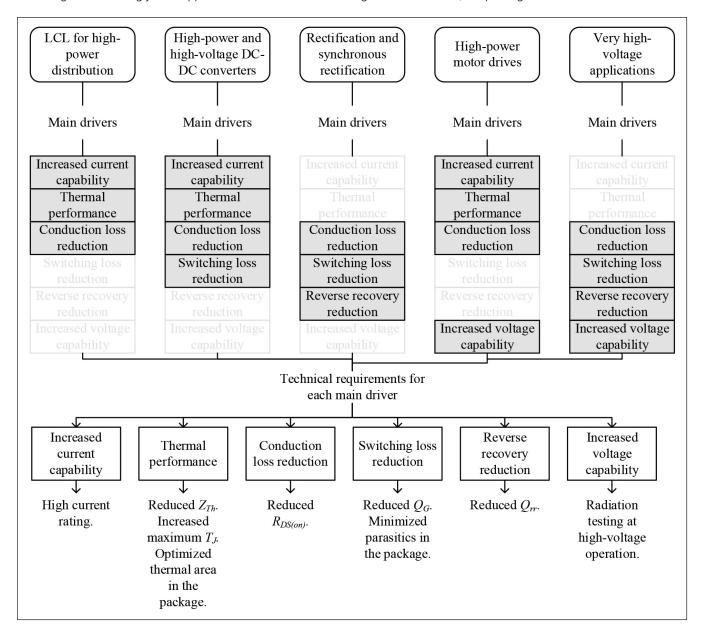

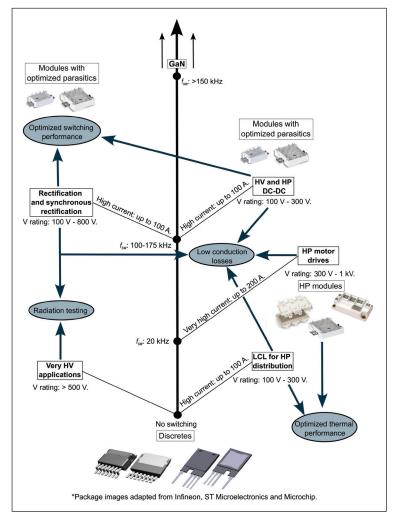

# 36 Launching SiC into space

For future space missions, makers of electrical systems need better power devices, a requirement that's met by SiC

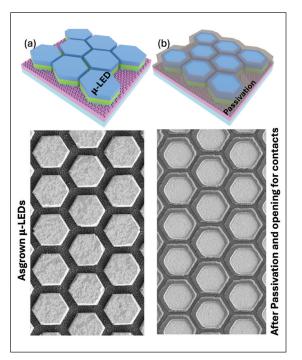

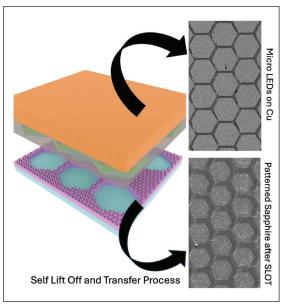

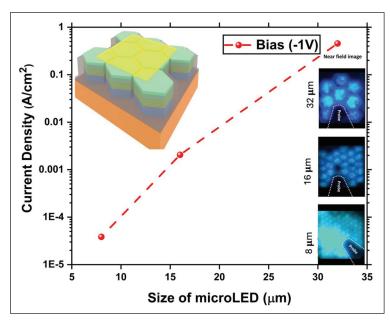

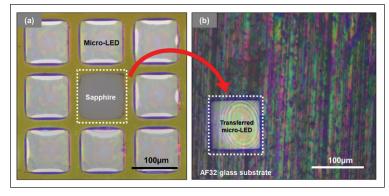

# 44 Transferrable vertical microLEDs arrays

It's not easy to transfer arrays of incredibly small, vertical GaN-based microLEDs to another platform. But there is a promising solution: selective-area growth of these emitters on hexagonal boron nitride

## **NEWS ANALYSIS**

#### 18 Innocent Innoscience?

The latest ruling from the US Patent Office draws jubilation from Innoscience, while EPC claims to have strengthened its key patent. But aside from the lawyers, will there ever be a winner in this long-running dispute?

# RESEARCH REVIEW

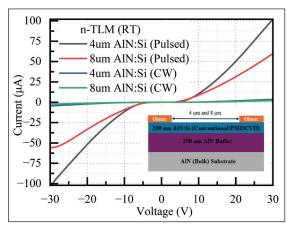

## 50 MOCVD improves n-type AIN

Switching from conventional MOCVD to a pulsed variant enables a hike in the conductivity of *n*-type

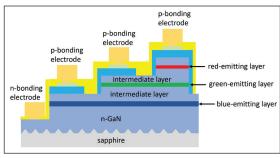

# 51 InGaN full-colour monolithic microLED displays

A full-colour passive matrix display with almost 1,000 pixels is formed from a single wafer

## 52 Turbocharging AIN/GaN HEMTs

A selective etching process for heavily doped *n*-type contacts enables the scaling of AIN/GaN HEMTs

# **NEWS**

- 06 SiC slowdown is only short term, says Yole

- 07 £250 million to turbocharge Welsh cluster

- 08 Aixtron delivers InP tool to Nokia

- **09** Wolfspeed appoints new CEO amidst funding crisis

- 10 Lumentum shows InP advances at OFC

- 11 Navitas Partners with Great Wall for 400 V-DC power

- 12 4-inch gallium oxide facility established in Swansea

- 13 Polar signs GaN-on-silicon agreement with Renesas

Editor Richard Stevenson News Editor Christine Evans-Pughe **Design & Production Manager** Mitch Gaynor

mitch.gaynor@angelbc.com Director of Logistics Sharon Cowley **Event & Media Sales Executive**

Ranjodh Shergill Circulation Scott Adams Publisher Jackie Cannon

richardstevenson@angelbc.com christine.evans-pughe@angelbc.com

sharon.cowley@angelbc.com ranjodh.shergill@angelbc.com

scott.adams@angelbc.com jackie.cannon@angelbc.com +44 (0)1291 629640

+44 (0)1923 690214 +44 (0)1923 690200

+44 (0)2476 718970

+44 (0)1923 690205

Chief Executive Officer Sukhi Bhadal sukhi.bhadal@angelbc.com Chief Technical Officer Scott Adams scott adams@angelbc.com Directors Jackie Cannon, Sharon Cowley

Published by Angel Business Communications Ltd 6 Bow Court, Fletchworth Gate, Burnsall Road, Coventry CV5 6SP, UK T: +44 (0)2476 718970 E: info@angelbc.com W: angelbc.com

+44 (0)2476 718970

+44 (0)2476 718970

Compound Semiconductor is published nine times a year on a controlled circulation basis. Non-qualifying individuals can subscribe at: £115.00 per annum (UK), €165 per annum (Europe), \$198 per annum (air mail) (USA). Cover price £4.50. All information herein is believed to be correct at time of going to press. The publisher does not accept responsibility for any errors and omissions. The views expressed in this publication are not necessarily those of the publisher. Every effort has been made to obtain copyright permission for the material contained in this publication. Angel Business Communications Ltd will be happy to acknowledge any copyright oversights in a subsequent issue of the publication. Angel Business Communications Ltd (Copyright 2025, All rights reserved. Contents may not be reproduced in whole or part without the written consent of the publishers. The paper used within this magazine is produced by chain of custody certified manufacturers, guaranteeing sustainable sourcing. US mailing information: Compound Semiconductor, ISSN 1096-598X, USPS Permit Number 25366, is published 9 times a year, Combined Jan/Feb, March, Combined April/May, June, July, Combined August/September, October, November, December by Angel Business Communications Ltd, Unit 6, Bow Court, Fletchworth Gate, Burnsall Rd, Coventry CV5 65P, UK, Airfreight and mailing in the USA by agent named World Container INC 150-15, 183rd St, Jamaica, NY 11413, USA. Periodicals Postage Paid at Brooklyn, NY 11256. POSTMASTER: Send address changes to Compound Semiconductor, Air Business Ltd, c/o World Container INC 150-15, 183rd St, Jamaica, NY 11413, USA. Periodicals Postage Paid at Brooklyn, NY 11256. POSTMASTER: Send address changes to Compound Semiconductor, Air Business Ltd, c/o World Container INC 150-15, 183rd St, Jamaica, NY 11413, USA. Periodicals Postage Paid at Brooklyn, NY 11256. POSTMASTER: Send address changes to Compound Semiconductor, Air Business Ltd, c/o World Container INC 150-15, 183rd St, Jamaica, NY 11413, USA. Periodicals Posta

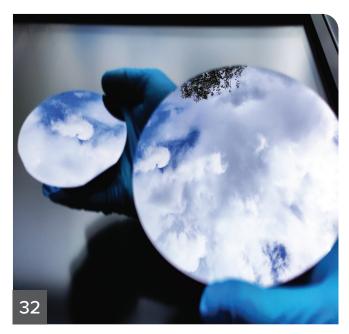

# SiC slowdown is only short term, says Yole

BEV slowdown is delaying short-term expansion, but the \$10 billion future remains on track

DESPITE a temporary slowdown in BEV shipments, the SiC market remains on a long-term growth trajectory, according to the Yole Group.

Its analysts forecast the power SiC market will exceed \$10 billion by 2029, driven by a strong rebound in 2026 with CAGR between 2024 and 2029 close to 20 percent.

"SiC adoption has accelerated since 2018-2019, primarily led by Tesla, the early disruptor in automotive electrification. In 2024, Tesla continued to dominate the SiC-based BEV segment with nearly two million units shipped, although that figure is down 5 percent from 2023," said Poshun Chiu, senior technology and market analyst at Yole Group.

Meanwhile, other OEMs, especially from China, are gaining ground. BYD, Nio, Geely, and Xiaomi are expanding their SiC-based BEV portfolios.

Despite these positive trends, the overall market deceleration has impacted the revenue growth of key SiC suppliers such as STMicroelectronics and onsemi, though Infineon Technologies continues to grow, supported by its diversified applications across both automotive and industrial sectors.

While many players are expanding capacity, especially in transitioning from 6-inch to 8-inch wafers, current endsystem demand may not yet justify this scale.

Ezgi Dogmus, activity manager, Compound Semiconductors at Yole Group says: "Industry feedback suggests that total announced capacity could outpace short-term SiC device consumption. Suppliers are now adjusting production volumes on a per-order basis and slowing down some expansion plans to match market realities for 2024 and 2025."

Key factors to monitor include wafer quality, yield, and supply chain efficiency. As competition intensifies, vertical integration becomes more critical. Leading companies, including STMicroelectronics, onsemi, Wolfspeed, and Infineon Technologies, are doubling down on internal wafer manufacturing and module production to meet their billion-dollar revenue targets.

Yole identifies STMicroelectronics' approach as one of the most ambitious moves among non-Chinese semiconductor players. Faced with rising competition and China's push for local sourcing, the leading semiconductor company has adopted a unique 'become Chinese in China' strategy.

Yole Group's analysts spotlight three key partnerships underpinning this approach: a \$3.2 billion joint venture with Sanan Optoelectronics for SiC devices, a manufacturing collaboration with Hua Hong Semiconductor for 40 nm automotive MCUs, and a strategic investment in GaN leader Innoscience. These moves are designed to localise production, support Chinese OEMs, and secure long-term market share in China's EV and industrial sectors.

This detailed analysis, based on the Power SiC/GaN Compound

Semiconductor Market Monitor, Q1 2025, suggests that these bold moves could significantly boost STMicroelectronics' growth from 2026 while also shaping the competitive landscape in SiC markets.

Yole says although the short-term outlook has cooled, analysts remain confident in SiC's long-term momentum, especially as BEV demand recovers and industrial applications continue to expand.

Despite these positive trends, the overall market deceleration has impacted the revenue growth of key SiC suppliers such as STMicroelectronics and onsemi, though Infineon Technologies continues to grow, supported by its diversified applications across both automotive and industrial sectors

# £250 million to turbocharge Welsh cluster

Vishay's investment in UK's largest semiconductor fab will be vital to EV production and support hundreds of highly-skilled jobs

WALES is set to benefit from a £250 million investment from the semiconductor company Vishay Intertechnology, that will be vital to the production of electric vehicles, supporting the UK government's Plan for Change in delivering more skilled jobs, and turbocharging the economy.

The Chancellor Rachel Reeves is welcoming Vishay Intertechnology's intention to invest in the Newport plant – the UK's largest semiconductor facility – as part of plans to develop large-scale compound semiconductor manufacturing in the country.

The investment will boost production at the factory where it will make advanced SiC semiconductors. Vishay's investment is expected to directly support over 500 high value, high skilled jobs in the region and indirectly support hundreds more in the wider supply chain.

It comes after the Chancellor Rachel Reeves' Spring Statement where she vowed to bring about "new era of security and national renewal" to kickstart economic growth, protect working people and keep Britain safe.

Supported by the government's Automotive Transformation Fund (ATF), the investment will help secure domestic supplies of semiconductors critical to the UK automotive industry, and other key industries including renewable energy and defence.

This funding also strengthens the UK's position in a competitive, global semiconductor landscape, supporting long-term growth for the UK economy.

Through the ATF, delivered in partnership with the Advanced Propulsion Centre (APC), the UK government continues to unlock private investment in UK automotive design,

development, and manufacturing as the sector transitions to zero emission technology. To date, the ATF and APC funding programmes have leveraged over £6 billion of investment from the private sector.

The UK's Autumn Budget confirmed over £2 billion for capital and R&D funding over five years for zero emission vehicle manufacturing and their supply chains. Mike Hawes, SMMT (Society of Motor Manufacturers and Traders) CEO, said: "This significant investment in compound semiconductors is a huge contribution to the innovation and advanced technology necessary to drive the future of UK Automotive. British-made next-generation semiconductors will create jobs, support supply chains and enhance the UK's strategic capabilities."

Secretary of State for Wales, Jo Stevens, said: "This massive investment by Vishay and the UK Government is a huge boost for Wales's world-leading semiconductor industry. Earlier this month I was at Vishay to see the work they do on advanced manufacturing, renewable energy and defence industries – all key sectors in the Welsh economy."

Wyn Meredith, chair of CSconnected, the Welsh Semiconductor Cluster, said: "Since the launching the Welsh Semiconductor Cluster in 2015, our partners have invested heavily in creating a world-leading research and innovation ecosystem, with a highly skilled talent pipeline to address a semiconductor market opportunity which is set to surpass \$1 trillion per annum by 2030. Global semiconductor players like KLA, Microchip, IQE, Vishay, and recently announced Cadence, have recognised the value of our proposition and have committed in excess of £600 million investment to fuel the continued growth of semiconductor manufacturing in South Wales."

Roy Shoshani, COO Semiconductors and CTO for Vishay, said: "This is an exciting moment, and the start of our plans for growth in the UK. We can see through the development of the Industrial Strategy and the skilled workforce in Newport that there is a real opportunity to play to the UK's strength in advanced semiconductors, delivering greater economic security and supporting Net Zero."

# Aixtron delivers InP tool to Nokia

G10-AsP system will allow company to produce 6-inch InP wafers for next gen photonics

AIXTRON SE will supply Nokia with its G10-AsP system to enable the company to produce 6-inch InP wafers, marking the next step in the evolution of photonic integrated circuits (PICs).

This follows Nokia's completion of its \$2.3 billion acquisition of InP specialist Infinera, in late February 2025.

The G10-AsP system is designed to provide precise and uniform processes that PICs require in contrast to traditional transceivers, as demonstrated in particular on 6-inch InP wafers.

For example, thanks to an innovative injector and advanced temperature control the platform offers up to 4 times superior on-wafer-uniformity for critical layers compared with the previous generation, according to Aixtron.

Combined with in-situ cleaning, the company says these new levels of uniformities can be consistently reproduced without the need for

hardware exchange or calibration between the different growth steps of the complex circuits. The automated cassette-to-cassette wafer loading ensures highest operator efficacy for the MOCVD tool.

"We are thrilled to support Nokia's innovation in photonic integrated circuits with our G10-AsP system. The ability to produce 6-inch InP wafers will significantly enhance their manufacturing and technology capabilities and drive the adoption of next-generation optical technologies," said Felix Grawert, CEO and president of Aixtron SE.

Steve Stockman, who leads Nokia's InP-based PIC manufacturing added: "The acquisition of Aixtron's stateof-the-art G10-AsP platform is a strategic investment in our production capabilities. This advanced technology will enable us to meet the growing demand for high-performance photonic integrated circuits and expand our leadership in the industry."

# CrayoNano puts assets up for auction

IN A SAD STORY of an innovative firm running into funding problems, CrayoNano, the Norwegian UVC LED company, has filed for bankruptcy and recently auctioned its assets.

Back in August 2024, the company announced record shipments to the drinking water disinfection market in North America, and around the same time raised \$1.5 milion (16.2 million NOK) capital in a private placement.

But there continued to be liquidity problems, despite the company's management and board working hard to raise capital to sustain operations and facilitate the long-term business plan.

Early December 2024, despite interest from several investors in a subscription for a Convertible Loan to raise a minimum of around \$1.4 milion (15 million NOK), CrayoNano did not receive enough subscriptions to cover it.

The company continued discussions with potential industrial partners but eventually exhausted all options to secure short-term financing. In January this year, it came to the end of the line and filed for bankruptcy.

The auction to acquire CrayoNano's complete technological assets took place on March 17. It included patents, research materials, hard disks and servers.

# Wolfspeed appoints new CEO amidst funding crisis

Chip veteran Robert Feurle takes the helm of SiC specialist at time of great uncertainty over \$750 million expected CHIPS Act Funding

US SiC specialist Wolfspeed has appointed Robert Feurle as CEO, effective May 1, 2025. Feurle succeeds Thomas Werner, who is serving as interim executive chairman and will return as chairman of the board following the transition.

Feurle brings more than 20 years of leading organisations that develop advanced power semiconductor solutions in automotive and other highvoltage applications, including both silicon and SiC. However, he arrives at a difficult time for Wolfspeed, whose shares on the 28th March 2025 lost half their value (hitting their lowest level since 1998), as funding through a Joe Biden-era legislation that promised subsidies for chip making in the United States remains uncertain.

Wolfspeed is waiting on about \$750 million in federal funding under the US CHIPS Act, the 2022 bipartisan law which promised \$52.7 billion in subsidies for domestic semiconductor chips manufacturing and production. But earlier this month. President Donald Trump said US lawmakers should get rid of the law and use the proceeds to pay debt.

"Wolfspeed's CHIPS Act grant ended up being the highest-dollar CHIPS grant

to not be officially awarded before Biden's exit, leaving it particularly vulnerable to being pulled under the new administration," Brooks Idlet, senior analyst at CFRA Research told the news agency Reuters.

Without the grant, Wolfspeed would face devastating consequences requiring major restructuring to preserve cash, Idlet added. The chipmaker has revealed that it accrued \$865 million in tax credits, using which it intends to strengthen its capital structure.

Feurle previously served as executive VP and general manager of the Opto Semiconductors Business Unit at Ams Osram AG, where he was responsible for managing more than 10,000 employees in sites and factories around the world. There, he expanded market

share and accelerated the introduction of cutting-edge LED and laser products into automotive and new advanced LED applications.

During his tenure at Infineon, Feurle became familiar with the SiC industry. He said: "I believe we have just begun to scratch the surface of the vast potential of SiC. Wolfspeed's world-class facilities, exceptional talent, and robust intellectual property, position us to maintain and expand our market leadership".

At Infineon, he spearheaded new product introductions in the field of IGBT and SiC technologies and increased focus on competitive differentiation and profitable growth.

He was also part of the team at Infineon supporting the proposed acquisition of the Wolfspeed operations in 2016.

A citizen of both the United States and Germany, Feurle will be returning to the United States where he previously spent a decade in executive roles at Micron Technology and will be relocating to the company's headquarters in Durham, North Carolina, where he will work closely with Werner to ensure a smooth transition.

# Private Treaty Sale

**ALTADEVICES**

Complete, Late-Model (2018), **High-Tech Solar Cell Equipment** and Intellectual Property from **Specialty (GaAs) PV Manufacturer**  Flexible Thin-Film GaAs Solar Cell Manufacturing and Fabrication Equipment Including — PVD Sputter, MOCVD, Surface Preparation, ELO, Plating Lines, Wet Processing, Test and Measurement, Inspection, Analysis Lab, Plant Support/IT Equipment, plus much more. All equipment was running production in the fab prior to shutdown, and professionally decommissioned in 2022.

Now accepting offers.

**Kevin Shows** kshows@gesemi.com 480-433-1866

**Chris Jenness** cjenness@gesemi.com 602-284-7870

In conjunction with TIGER

# Lumentum shows InP advances at OFC

Company demonstrates readiness for 400G-per-lane Al data centres

AT THE RECENT OFC 2025 exhibition in San Francisco, Lumentum announced a number of advances in its InP photonic chip technologies for delivering higher bandwidth and more power efficiency in next-generation Al data centres.

The InP innovations enable future 400 Gbps-per-lane optical links, more efficient 200 Gbps-per-lane optical links, and co-packaged optics.

"Building on decades of InP expertise, Lumentum is driving industry technology leadership and volume production readiness for the future 400G per lane generation of optical interconnects, along with more efficient 200G per lane optical interconnects, to enable data centre compute capacity scaling," said Matt Sysak, Lumentum CTO of Cloud and Networking.

"Lumentum InP technology is also enabling new co-packaged optics solutions to significantly reduce power consumption in Al data centre networks, supporting larger Al installations and accelerating the

transition from copper to photonic interconnects." For example, Lumentum demonstrated two key 400 Gbps-perlane photonic technologies which will enable the 3.2T generation of optical transceivers at OFC 2025.

These included a 448 Gbps data transmission using a 224 GBaud PAM4 externally modulated laser technology in collaboration with Keysight Technologies and NTT Innovative Devices. And a 450 Gbps PAM4 distributed feedback (DFB) laser with an integrated Mach-Zehnder modulator for 400 Gbps-perlane technologies.

To address power challenges in bandwidth scaling, Lumentum

engineers presented a technical paper at OFC 2025 detailing results from Lumentum's new 200 Gbps-per-lane differential drive electro-absorption modulated laser. These lasers operate at a lower drive voltage, reducing power dissipation while offering excellent signal integrity and cross-talk immunity.

Lumentum also highlighted its ultrahigh power (UHP) 1310 nm DFB lasers designed for co-packaged optics to support higher-density optical interconnects.

The UHP platform is based on InP pump lasers for Raman amplification applications.

# 5N Plus gives GaN IP back to Allos

5N Plus Inc, a Canada-based producer of specialty semiconductors and materials, has entered into an agreement, through its subsidiary, Azur Space Solar Power GmbH, with Dresden-based microLED and GaN-onsilicon expert Allos Semiconductors.

The aim is to complete the development and commercialisation of a GaN IP portfolio that 5N Plus has provided to Allos Semiconductors for a nominal value in exchange for future royalties.

Prior to becoming part of 5N Plus in 2021, Azur had acquired a package of technology and patents for High Power

Electronics (HPE) and RF applications from Allos Semiconductors in 2020. This package will now be transferred back to Allos, along with additional GaN IP.

"This transaction allows 5N Plus to focus on its core business while benefiting from the growth of the HPE market through royalties. With Allos, we have found the strongest possible partner to commercialise the technology over time," said Gervais Jacques, president and CEO, 5N Plus.

"With this acquisition we are further strengthening our IP position," said Burkhard Slischka, co-founder and CEO of Allos Semiconductors. The company specialises in 200 mm and 300 mm epiwafers for microLED applications that can be processed in standard silicon fabs. Allos' customers are microLED and display companies, working with silicon foundries to achieve the yield and unit cost breakthroughs that are critical to turning microLED display prototypes into mass consumer products.

Slischka added: "We remain focused on our successful microLED technology while exploring synergies with the rapidly growing HPE market. We are open to new partnerships in GaN HPE and our now expanded IP portfolio remains available for licensing."

# Navitas Partners with Great Wall for 400 V-DC power

GaNSense technology boosts 8-times power in ultra-high power density DC-DC converters

GaN and SiC specialist Navitas Semiconductor has announced that its GaNSense power ICs will power GreatWall's latest 2.5 kW ultra-high power density DC-DC converter for Al data centres.

Great Wall has developed a 2.5 kW DC-DC converter in 1/4 brick outline with what it claims is the world's highest power density of 92.36W/cm<sup>3</sup>, up to 8 times higher than the output power of traditional silicon designs.

With a high half-load efficiency of 97.9 percent and a wide input range of 320-420  $V_{\rm DC}$ , this solution achieves the increasingly stringent efficiency guidelines and regulations from Open Compute Project and can be widely used in applications from Al data centres, telecommunications, and industrial equipment.

The DC-DC converter is powered by Navitas' GaNSense NV6169. The 650 V, 45 m $\Omega$  device is claimed to deliver 50 percent more power than prior designs, in an industry-standard,

low-profile, low-inductance,  $8\times8$  mm PQFN package for high-efficiency, high-density power systems.

GaNFast power ICs with GaNSense technology have features such as loss-less current sensing and fast short-circuit protection, with a 'detect-to-protect' speed of only 30 ns, six times faster than discrete solutions.

NV6169 is rated at 650 V for nominal operation plus an 800 V peak-rating for robust operation during transient events. The GaN gate is fully-protected and the whole device rated at 2 kV.

"With its faster switching frequency and higher efficiency, GaN has become a key factor in unlocking the next generation of power supplies," said Michael Zhang, head of DC Product Line at Greatwall Power. He added: "We are very pleased to collaborate with Navitas, an industry leader in GaN technology, and successfully enable this industry-leading ultra-high-power density and ultra-high efficiency DC-DC converter."

# MoD to put £200 million into UK compound semi fab

THE UK's MoD will put a further £200 million into Octric Semiconductors, the re-named GaAs fab in Newton Aycliffe, County Durham which the Ministry of Defence (MoD) bought in September 2024 for £27 million.

According to a report in *Electronics Weekly*, the investment will be used to produce GaAs and GaN chips for military systems, radars and power electronics. Octric aims to expand with further processes: it is looking for engineers with experience in a range of compound semiconductors, including InP.

Most recently owned by US company Coherent, the UK fab was bought by the MoD as a crucial supply chain to UK defence.

The site is said to be the only secure facility in the UK with the skills and capability to manufacture GaAs semiconductors, vital for a number of military platforms, including to boost fighter jet capabilities.

# 4-inch gallium oxide facility established in Swansea

University centre to become national hub for thin film gallium oxide R&D

RESEARCHERS at the Centre for Integrated Semiconductor Materials (CISM) at Swansea University have established the first 4-inch thin film gallium oxide ( $Ga_2O_3$ ) capability in the UK.

This advance was achieved using a newly commissioned Aixtron close-coupled showerhead deposition system that can precisely grow high-quality crystalline thinfilm gallium oxide on 4-inch substrates. These have been tested and shown to be uniform and of high quality.

This capability is housed in the new Oxide and Chalcogenide MOCVD Laboratory at CISM, which is now set to become a national hub for thin-film gallium oxide research and development in areas such as power electronics, deep-UV photodetectors and transparent conductive oxide applications.

Dan Lamb, research lead at the Oxide and Chalcogenide MOCVD Centre said: "This new facility represents a major step forward for our research, and I'm incredibly excited about the possibilities it unlocks for novel

materials and device development. With this advanced equipment, we can push the boundaries of our existing work while also creating new opportunities for collaboration with research groups across the UK and beyond."

John Heffernan of the National Epitaxy Facility, which supports semiconductor research in UK universities, said: "Swansea University's MOCVD capability is now accessible to researchers through direct collaboration. Researchers can also gain access to feasibility studies through Swansea partnering with the UK National Epitaxy Facility's Pump Priming scheme. This initiative ensures that academic and industrial partners can leverage Swansea's expertise

in epitaxial thin-film growth to accelerate their research and technology development.'

The achievement follows the recent announcement of a £250 milion investment by Vishay supported by the UK Government's Automotive Transformation Fund in it's Newport plant to dramatically expand advanced wide band gap power semiconductor component manufacturing.

Sam Evans, director of quality assurance and external affairs, Vishay Newport, said: "This is a major step forward for wide band gap materials innovation in our South Wales Semiconductor Cluster, underpinning efforts to grow regional manufacturing in advanced power electronics such as Vishay's recently announced £250 million investment in SiC component expansion."

The deposition system was funded by a £2.7 million grant from the Engineering and Physical Sciences Research Council (EPSRC – Strategic Equipment Programme), reinforcing the UK's commitment to advancing semiconductor innovation.

#### **KEY FEATURES**

- · Spit-Free Deposition up to 70Å/s

- · 200 mm Wafers

- · Exceptional Uniformity

- $\cdot$  Suitable for Round and Square Bumps

- · High Lift-Off Yield

- · Bumps from 1 μm to 40 μm

www.intlvac.com

# Polar signs GaN-on-silicon agreement with Renesas

Partnership to make 650 V GaN-on-silicon devices in Minnesota aims to strengthen the US supply chain

POLAR SEMICONDUCTOR, a US-owned merchant foundry, has sighed a deal with Renesas Electronics to license the Japanese firm's GaN-on-silicon D-Mode GaN-on-silicon technology.

As part of this agreement, which is to ensures the US has a reliable, domestic source for this semiconductor technology, Polar will fabricate high-voltage 650 V class GaN-on-silicon devices for Renesas and other customers in its 200 mm automotive quality high-volume manufacturing facility in Minnesota.

Polar and Renesas will work together to scale commercial production of GaN devices, expanding its use across automotive, data centre, consumer, industrial, and aerospace and defence markets. The agreement ensures the US has a reliable, domestic source for this cutting-edge semiconductor technology.

Surya lyer, president and COO of Polar Semiconductor said: "This licensing and commercial production agreement underscores our commitment to strengthening the domestic semiconductor ecosystem. GaN is a game-changing technology for power and RF, and with Renesas as our partner, we are well-positioned to ramp commercial production, secure key defence programs, and drive the next wave of semiconductor innovation."

"We are excited to partner with Polar to scale our proven GaN technology to 200 mm wafers and leverage our knowhow across broad power conversion

markets ranging from infrastructure and AI to energy and industrial to e-Mobility and xEVs to high-value IoT," said Chris Allexandre, SVP nd GM, power products group, at Renesas. "This collaboration ensures a strong, US-based manufacturing capability for GaN products, provides multi-sourcing to our customers, and meets the growing demand for high-performance power solutions."

# Navitas and GigaDevice announce partnership

NAVITAS SEMICONDUCTOR has announced a partnership with GigaDevice, a Chinese maker of microcontrollers and flash memory, to create a joint-lab for integrating and tailoring Navitas' GaNFast ICs and GigaDevice's microcontrollers for Al data centres, EVs, solar, and energy saving systems.

As GaN and SiC power technologies transition power conversion to faster, lighter, and more compact solutions, such as single-stage BDS converters, MCUs need to be optimised to maximise fast switching characteristics, such as high processing speeds and fast I/O capabilities.

A co-developed solution of Navitas' power and GigaDevice's control will further accelerate the adoption of GaN and SiC into higher-power markets, according to the companies.

The joint R&D laboratory will integrate both company's technical product and

system-level application expertise to develop power management solutions. Integrating Navitas' GaNFast technology with GigaDevice's advanced MCU products will enable a new level of integration, performance, and high-power-density digital-power solutions. GigaDevice has been widely adopted across diverse sectors including power systems, industrial automation, automotive electronics, and motion control, with cumulative shipments exceeding 2 billion units.

GigaDevice's GD32 MCU series has been designed for applications including industrial automation, photovoltaic energy storage, graphic displays, digital power supplies, and motor control.

"Digital power stands as one of GigaDevice's core strategic markets. MCUs play a pivotal role in advancing the intelligence of digital power systems, enhancing energy efficiency, and ensuring operational security," said Vincent Li, GigaDevice SVP, CTO, and general manager of MCU business unit. "By working with Navitas, we will deeply integrate GigaDevice's advanced MCU with Navitas' leading GaNFast technology to develop competitive solutions for industrial automation and new energy vehicles. This collaboration is not only technological synergy but also a critical step toward greener, more efficient industry development."

"Navitas continues to innovate our GaNFast power IC technology to achieve our mission to 'Electrify Our World", said Charles Zha, SVP and GM of Navitas Asia-Pacific. "The joint lab with GigaDevice will amplify our complementary strengths in IC design, manufacturing, and ecosystem development and accelerate R&D for next-gen, high-efficiency power solutions, reinforcing our 'Smart + Green' strategic vision. We look forward to delivering faster, energy-saving innovations to global customers and pioneering a new era of collaboration in power electronics."

# The tantalising promise of wider bandgaps

Producing power devices with ever wider bandgaps is far from easy, but realising success slashes on-resistance while boosting blocking capability

### BY RICHARD STEVENSON, EDITOR, CS MAGAZINE

ONE OF THE primary purposes of CS International is to provide a detailed overview of the latest trends with our industry. To fulfil this goal, the key themes of this conference have evolved over the last 15 years. While progress in GaAs RF electronics played an important role in the first few meetings, this has subsequently taken a back seat, with CS International now focusing on optoelectronics and power electronics, with the latter accounting for the lion's share of the 40 or so presentations.

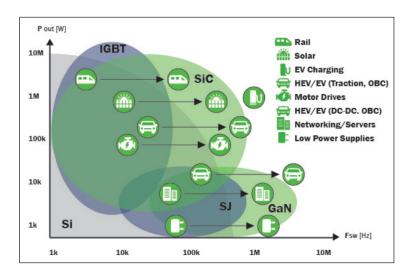

Today, SiC accounts for the majority of the revenue generated by compound semiconductor power electronics, and sales are forecast to continue to climb, as many of the leading suppliers expand their production capacities, enhance their portfolios, and ship more products for deployment in electric vehicles.

At this year's CS International – held at the Sheraton Hotel, Brussels, from 8-9 April – two leading chipmakers, Navitas and Infineon, detailed the strengths of their approaches in a session entitled *Optimising opportunities for SiC success*.

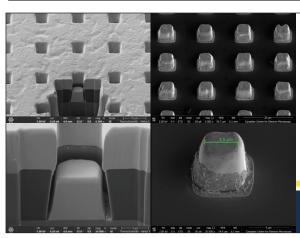

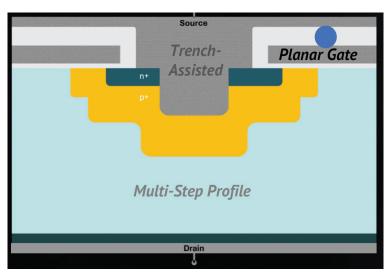

➤ The Navitas trench-assisted planar MOSFETs

Speaking on behalf of Navitas, Senior Director for Product Management and Marketing for SiC and GaN, Llewellyn Vaughan-Edmunds, discussed the company's novel trench-assisted planar technology for SiC MOSFETs.

Vaughan-Edmunds argued that while the traditional planar architecture offers repeatable high-yield, low-cost manufacture, and has a high level of reliability that benefits from a rugged gate oxide, which ensures a stable threshold voltage, these strengths come at the expense of slow switching and high values for the drain-source on-resistance, both as a function of area and as a change in temperature.

According to Vaughan-Edmunds, the SiC trench MOSFET also has some significant weaknesses. While this design addresses the shortcomings of the traditional SiC MOSFET, this class of transistor suffers from an inconsistent trench etch that hampers yield and leads to higher production costs. What's more, reliability is impaired by failures from the non-uniform gate oxide, and the device is held back by a lower short-circuit capability.

Offering the best of both worlds, says Vaughan-Edmunds, is the trench-assisted planar SiC MOSFET. It is claimed to combine the manufacturing merits of the planar MOSFET with the performance of its trench-based cousin, while excelling in reliability — this design has excellent avalanche capability, a long short-circuit withstand time, and features a rugged gate oxide that ensures a stable threshold voltage.

To benchmark the performance of Navitas' trenchassisted planar MOSFETs, Vaughan-Edmunds presented a plot of the key figure-of-merit – the product of the drain-source on-resistance and area – for currents up to 100 A. The Navitas device delivers the most impressive performance, with the next-best values coming from the planar devices produced by Toshiba and General Electric.

# NEWS ANALYSIS | CS INTERNATIONAL

Vaughan-Edmunds also discussed the pros and cons of various architectures from a production perspective. Standard trench MOSFETs have a complex structure, with their production requiring 40 percent more process steps than planar architectures. For planar designs, the trenchassisted architecture that features a novel source contact on the side wall enables a smaller cell pitch and an increased power density.

Some of the advantages of the trench-assisted planar SiC MOSFET over both the traditional planar and standard trench designs are attributed to a multi-step profile that: smooths the electric-field distribution, leading to an increase in long-term reliability; and improves currents spreading, leading to a lower drain-source on-resistance. The latter can be up to 20 percent lower at elevated temperatures, leading to lower conduction losses and a cooler performance.

Another strength of Navitas' trench-assisted planar technology is its reduction in switching losses by up to 15 percent. Thanks to this, the trench-assisted planar SiC MOSFET ensures faster, efficient high-frequency switching, enabling a higher power density, according to Vaughan-Edmunds.

#### **Expanding SiC capacity**

Among the chipmakers increasing production capacity, Infineon is attracting much attention for its construction of a colossal facility in Kulim, Malaysia.

Offering an update on this project, the company's Vice President of SiC, Peter Friedrichs, explained to delegates at CS International that Infineon has had a presence in Malaysia since 1974, initially with backend manufacturing, and in 2006 it added 200 mm silicon front-end processing in Kulim. The Kulim facility has undergone several expansions, including in 2022 the addition of Kulim 3.1, supported by more than  $\mathfrak{C}2$  billion, that's enabled the introduction of SiC and GaN production. Now capacity is now being increased with Kulim 3.2, via a second phase of investment that totals up to  $\mathfrak{C}5$  billion. Helping to support this venture are design wins worth around  $\mathfrak{C}5$  billion, and customer pre-payments of around  $\mathfrak{C}1$  billion.

Friedrichs explained that Infineon has designated its Villach facility as its competence centre for wide bandgap materials, with its GaN and SiC power

> Alan Dolittle from Georgia Tech gave a presentation entitled A solution to doping AlN enabling a new era of nitride semiconductors in the session Ultra-wide bandgap materials: The ultimate devices.

electronics technologies developed at this Austrian site. When these technologies enter large-scale production, they are introduced at the Kulm site, a move that is said to enable high-volume production, alongside supply chain stability, quality and efficiency.

According to Friedrichs, the opening of Kulim 3 is ensuring that Infineon is on track to become the industry's most cost-competitive provider of SiC technology. Supporting this endeavour is: the qualification of more than six SiC wafer and boule suppliers; what's claimed to be a superior trench technology that yields 30 percent more chips per wafer than its planar counterpart, along with unmatched reliability and zero field returns; in-house packaging technologies that are said to be best-inclass; and a deep system understanding, drawing on decades of experience.

## The allure of Ga<sub>2</sub>O<sub>3</sub>...

One of the materials for the future that has a significantly wider bandgap than SiC is  $Ga_2O_3$ . At this year's CS International, Xiaohang Li from

Ga<sub>2</sub>O<sub>3</sub> ICs and devices are promising candidates for operation in a range of extreme environments, such as space, quantum applications and the petrochemical and geothermal industries. By 2035, the number of transistors/diodes in space might exceed 10<sup>20</sup>, according to a report produced by McKinsey and company and General Electric.

# NEWS ANALYSIS | CS INTERNATIONAL

Another recent advance by Doolittle and his team has been the first ever AIN *p-i-n* diodes, which produced a nearly ideal turn-on of around 6 V. This diode is held back by a high series resistance associated with the n-contacts.

KAUST discussed the prospects for this oxide in ICs, after outlining the strengths and weaknesses of this material – its downsides include a low thermal conductivity and poor *p*-type doping, but it has strengths that include a high value for the tunnelling effective mass, excellent radiation hardness, the capability to operate at high temperatures, and the potential to produce low-cost substrates in high volume.

Li argued that  ${\rm Ga_2O_3}$  ICs and devices are promising candidates for operation in a range of extreme environments, such as space, quantum applications and the petrochemical and geothermal industries. By 2035, the number of transistors/diodes in space might exceed  $10^{20}$ , according to a report cited by Li and produced by McKinsey and company.

The common approach to producing ICs is to use two building blocks – nMOS and pMOS – but forming highly dense, stacked circuits is costly and complex. Ambipolar transistors can overcome this difficulty by trimming costs, reducing the number of logic gates and delay, and decreasing energy consumption by between 30 percent and 70 percent.

Until recently, ambipolar transistors have been limited to narrow bandgap material, but Li has broken down this barrier by pairing  ${\rm Ga_2O_3}$  with NiO. To ensure good gate control, the team from KAUST employs a gate-all-around architecture. According to benchmarking against state-of-the-art ambipolar transistors, those made by Li and his team have the highest on-off ratio, and a sub-threshold swing that's competitive.

#### ... and AIN

Offering an even higher bandgap than  ${\rm Ga_2O_3}$  is AIN. Thanks to a bandgap of 6.1 eV, this nitride has a critical electric field five times higher than SiC, and when judged against major performance predictors, it's the best or a close second. However, its major weakness has been its lack of doping.

To overcome this issue, Alan Doolittle and his coworkers from Georgia Tech have recently shown that it's possible to produce *n*-type and *p*-type AIN by metal-modulated epitaxy.

Speaking at this year's CS International, Doolittle revealed that additional motivation for his development of AIN materials and devices has come from theoretical work by Emmanouil Kioupakis' group at the University of Michigan, with calculations revising the peak mobility for this material from around 400 cm² V¹ s¹ to more than double this value. According to Doolittle, if this holds up, AIN will surpass c-BN and diamond as the transistor material with the highest potential. Note that those at Georgia Tech have already measured mobilities of more than 500 cm² V¹ s¹ in AIN.

Another recent advance by Doolittle and his team has been the first ever AIN *p-i-n* diodes, which produced a nearly ideal turn-on of around 6 V. This diode is held back by a high series resistance associated with the *n*-contacts.

While this effort is in its infancy, progress on materials with very wide bandgaps is gathering pace, and will feature at the next CS International, to be held on 21-22 April, 2026.

# **Connecting Semiconductors and Electronics**

#### About SEMI:

SEMI connects more than 2,500 member companies and 1.3 million professionals worldwide to advance the technology and business of electronics design and manufacturing. The breadth and depth of our events, programs and services help members accelerate innovation and collaboration on the toughest challenges to growth.

WORKFORCE DEVELOPMENT

**Global** ADVOCACY

Sustainability

1000+ STANDARDS

THOUGHT LEADERSHIP

**TECH**COMMUNITIES

**SEMI** UNIVERSITY

**Cyber** Security

# Innocent Innoscience?

The latest ruling from the US Patent Office draws jubilation from Innoscience, while EPC claims to have strengthened its key patent. But aside from the lawyers, will there ever be a winner in this long-running dispute?

#### BY RICHARD STEVENSON, EDITOR, CS MAGAZINE

THE GaN IP war raging between EPC and Innoscience is now entering a new phase, following rulings from the US Patent and Trademark Office (USPTO) this past month.

As is often the case in complex matters that involve IP, both sides are talking up the positives, while glossing over the negatives.

Innoscience, on its back foot since the imposition of a ban on importation into the US, is now incredibly upbeat. It is claiming it achieved an 'ultimate victory' in what it describes as EPC's meritless two-year-long patent war, and says that the USPTO ruling shows that EPC's allegations relating to enhancement-mode GaN transistors are 'completely unfounded'.

Unsurprisingly, US firm EPC has a different take on these matters. As well as emphasising a strengthening of its key patent, it is planning to appeal the USPTO's cancellation of its claims.

#### From four patents to only one

When EPC initiated its legal action against Innoscience back in May 2023, it claimed infringement of four patents, all associated with enhancement-mode GaN HEMT technology. The fabless chipmaker subsequently decided to drop two patents in the case directed to HEMTs with a self-aligned gate having 'ledges'. This left two patents being asserted against Innoscience: US Patent No. 8,350,294 (directed to a FET made with a 'compensated' GaN layer); and US Patent No. 8,404,508 (directed to a multi-step process for fabricating a self-aligned gate E-mode HEMT).

Relating to the '508 patent: EPC went to trial at the International Trade Commission (ITC) in July 2024, with the Administrative Law Judge (ALJ) deciding that the '508 patent was not infringed by Innoscience.

While Innoscience did not enjoy a full victory, having failed to convince the ALJ that the '508 patent was invalid, there is no doubt that it was pleased with the result, according to patent attorney David Radulescu, who is an expert in GaN IP. Radulescu, who is the head of the patent litigation boutique firm Radulescu LLP and has been litigating semiconductor patents in

courts throughout the US for three decades, points out that EPC is now suffering from an undeniable loss on the '508 patent: "EPC has no right to an injunction (or any compensation) with its lawyers being unsuccessful in establishing use of its patented fabrication process."

However, EPC may draw some comfort from Innoscience's unsuccessful invalidity challenge before the patent office, where a final determination recently went in its favour. "For Innoscience, it was a complete loss at the USPTO, because all five claims were found to not be invalid," remarks Radulescu.

Relating to the '294 patent: In contrast to the ITC finding of no infringement on the '508 patent, EPC was successful in obtaining an infringement ruling on the '294 patent, which resulted in the ITC issuing an importation ban. The impact of the adverse ruling, however, was blunted when Innoscience claimed to have changed the design of its products to sidestep the ban. "Even so, the redesign had to be painful, particularly when lawyers are involved in device design decisions based on a patent landscape that is so fraught with traps," says Radulescu.

#### The 'compensation' conundrum

The on-going dispute is now focused on the '294 patent, related to the use of a 'compensated' GaN layer in a FET. Innoscience has widely reported that its devices use *p*-type GaN, but it is not disclosing whether transistor production includes an extra step to expel hydrogen, an approach widely used in the manufacture of GaN LEDs.

During the intentional doping of any semiconductor material with impurities, there will always be some degree of compensation, because no semiconductor is 'perfectly' doped with one type of impurity without other defects/impurities in the crystal lattice. With GaN grown by MOCVD, a number of factors are at play following the addition of magnesium, the common *p*-type dopant. One is that magnesium may be complexed with hydrogen, leading to compensation, because this impurity fails to create a hole. A second factor is that lattice defects and vacancies, of which there are many in GaN grown by MOCVD on lattice-mismatched substrates, could lead to compensation. Lastly, unintentional impurities, such as carbon and oxygen,

## NEWS ANALYSIS | Gan PATENT WARS

could also lead to compensation. Due to all these possibilities, characterising magenesium-doped GaN as 'compensated' or 'not compensated' is complicated to apply when that concept is written into a patent claim, says Radulescu. "It's not so simple as focusing on if hydrogen is present while ignoring other impurities or defects."

This complication hampered the efforts of EPC's lawyers, who needed to demonstrate that the patent is both infringed and not invalid.

"If you represent the patentee, the job of the lawyers is to walk the line between infringement and invalidity," explains Radulescu. "If you want to argue your claims are broad to show infringement, then you could be stepping over into invalidity territory and you could have the patent invalidated."

Although Innoscience was successful in having the all asserted claims of the '294 patent recently invalidated, EPC was successful in having two new 'substitute' claims added to its patent that escaped Innoscience's invalidity challenge. Both claims are directed to GaN-based enhancement-mode transistors with more specificity to distinguish from the prior art. In particular, these new claims require that 'no two-dimensional electron gas (2DEG) region exists below the gate at zero volts applied gate voltage' and refer to a 'semi-insulating III-N layer', which includes a 'compensated GaN layer containing acceptor-type dopant atoms passivated with hydrogen'. These claims continue to not only refer to the hotly contested phrase 'compensated', but add a further complication by referring to a

'semi-insulating' layer (without any quantification of how insulating/conducting). "With all this added language, the claim scope is rich with opportunity to allow a lawyer with GaN experience to argue on either side of the dispute," Radulescu believes.

#### What happens next?

How both parties proceed from here will depend on a number of factors, some unknown. For EPC, if it wants to continue its battle with Innoscience, it will have to focus on appeals, attempting to overturn unfavourable decisions - which is always an uphill battle. In addition, it could file a new infringement action using other patents or the '294 patent with the new claims that have been litigation-hardened. Meanwhile, Innoscience may decide to direct its efforts at removing the import ban, given that the infringed '294 patent claims were recently ruled as invalid. So far, there has been silence on this matter, but it's possible private negotiations are underway.

What the future holds is anyone's guess. Even those with tremendous expertise in these matters, such as Radulescu, can only speculate – and they will only do so after reeling off a string of caveats. Radulescu surmises that among a number of possible scenarios, one that would not surprise him is a sudden truce in this battle between EPC and Innoscience, with cross-licencing following. And if that were to happen, he would expect all the details to be confidential, with both companies just issuing a press release stating that they have cross-licensed their technology. Motivation for such a move would include avoiding paying more in legal fees, which may already total \$15-20 million for each side.

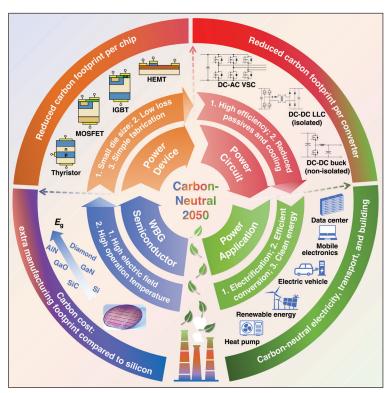

# Power semiconductors for carbon neutrality

Advances in semiconductor and power electronics technologies, led by increasing deployment of wide-bandgap power devices, are essential for reducing greenhouse gas emissions and developing a carbonneutral energy system by 2050

#### BY YUHAO ZHANG FROM THE UNIVERSITY OF HONG KONG

THE LAST decade has witnessed an increase in the adoption of wide-bandgap power devices, led by those based on GaN and SiC. Both these materials have enabled improvements to the performance of power electronics systems in numerous applications. But beyond performance, what impacts are these advanced semiconductors having? Are they set to play a major role in driving down greenhouse gas emissions? And are they critical to reaching carbon neutrality?

Recently, I have been digging into these important questions, working with departmental colleagues at the University of Hong Kong, and collaborators from Virginia Tech and the University of Cambridge. Together, we published our findings earlier this year in Nature Reviews Electrical Engineering. Our paper traverses the full material-device-circuit-application spectrum, to scrutinise the combined impacts of wide-bandgap semiconductors and power electronics on greenhouse gas emissions. This thorough investigation has led us to conclude that wide-bandgap power semiconductors are critical enablers to carbon neutrality.

Since 2015, 195 countries have joined the Paris Agreement, signing up to mitigate their greenhouse gas emissions and strive towards the goal of carbon neutrality by 2050. Currently, energy generation and energy use accounts for around three-quarters of greenhouse gas emissions, mainly associated with four sectors: electricity generation, transportation, industrial processes, and the cooling and heating of buildings. Power electronics are utilised ubiquitously in all these sectors for electrical energy conversion, such as stepping up and down the current and voltage, as well as converting between AC and DC forms.

Crucial to determining the efficiency, power density and form factor of power electronics systems are the power semiconductors, in conjunction with the circuit topology and control. While it is well known that the adoption of GaN and SiC devices can bring significant performance advances, their environmental impact on carbon emissions is less researched. Filling the gap between semiconductor technology and carbon footprint demands a multidisciplinary approach, covering the full spectrum of material, device, circuit and application.

The uptake of GaN and SiC power devices cuts carbon footprints on many fronts. At the device and circuit level, these wide bandgap diodes and transistors can potentially have smaller carbon footprints than their silicon cousins, due to their smaller die size and superior performance. These strengths enable: a lower per-chip carbon footprint for the same energy and chemicals used in manufacturing a wafer; reduced energy loss, associated with an increased converter efficiency; and dematerialisation, that is, a reduction in the volume of materials used for passive and cooling components.

At the application level, wide bandgap semiconductors cut carbon emissions on three key fronts. First, they reduce energy loss in power conversion and trim the energy consumed by cooling systems; for example, these devices and cooptimised circuits increase the efficiency of electrical conversion from grid edge to the processors in data centres from below 80 percent to over 90 percent. Second, power devices and circuits aid the use of renewable energy in electricity generation, for example, through the use of solar photovoltaics, wind power generation, electric vehicles and heat pumps. Third, power electronics with a fast dynamic response, high switching frequencies and a high-power density promotes the electrification of transportation and buildings, for example, by boosting an electric vehicle's driving range, its charging time and its energy efficiency.

We have analysed and quantified the potential reduction of carbon emission across four pivotal sectors - renewable energy systems, electric vehicles, data centres, and heat pumps - from the perspectives of electrification and energy conversion efficiency. This led to a number of interesting findings, such as the replacing of 80 percent of fossil-fuel electricity generation with GaN/SiCbased photovoltaic systems could lead to an annual reduction in US greenhouse gas emissions of at least 1,236 million tonnes – that's equivalent to the annual emissions of 245 million gasoline passenger vehicles.

According to our study, substantial savings in US greenhouse gas emissions can also be realised with other significant initiatives, such as a reduction by 390 million tonnes by replacing 80 percent of gasoline cars with GaN/SiC-based electric vehicles. Meanwhile, in data centres, if silicon devices were replaced with those made from GaN and SiC, this could reduce US greenhouse gas emissions by at least 1.7 million tonnes per year; and if US homes currently heated by natural gas switched to heat pumps powered by photovoltaic systems, this could slash greenhouse gas emissions by around 260 million tonnes per year.

To ensure rigour in our findings, we considered the extra carbon emissions associated with GaN and SiC production, compared with those for legacy silicon manufacturing. Despite the smaller size of wide bandgap devices, the raw materials, chemicals

and energy used in their production could be very different from those for silicon.

For this part of our analysis, we surveyed the normalised carbon emission by corporate revenue for GaN, SiC and silicon manufacturing, based on data disclosed from third-party-verified sustainability reports from major power semiconductor companies. From the survey, we estimated the extra carbon footprint for GaN/SiC manufacturing. We found this to be marginally small compared with the system-level carbon saving.

We hope that our recent paper, offering the first quantitatively analysis of the impact that widebandgap power semiconductors could have in realising carbon neutrality, will become a useful reference for researchers, engineers, and policymakers. Despite their potential to deliver significant change, the consequences of increasing the deployment of SiC and GaN devices have not been considered in detail, such as their impact on sustainability. But what we do know is that further innovation across materials, devices, circuits and systems, as well as a shift to designing power electronics based on the principles of reuse, remanufacturing and recycling, is essential to fulfil the potential of wide-bandgap power electronics for carbon neutrality.

> Figure 1. The role of wide-bandgap semiconductors in achieving carbon neutrality.

#### **FURTHER READING / REFERENCE**

Y. Zhang et al. "Wide-bandgap semiconductors and power electronics as pathways to carbon neutrality" nature reviews electrical engineering 2 155 (2025)

# Improving GaN with a dash of oxygen

Depositing a partial monolayer of oxygen between a silicon substrate and GaN device layers trims defect density and improves material quality

#### BY ROBERT MEARS FROM ATOMERA

THROUGHOUT the semiconductor industry, those working in R&D look to new materials to push the boundaries of technology, with a focus on enhancing performance and reducing power consumption. Progress on these fronts is imperative for developing the next generation of mobile devices, consumer electronics and data centres - all require devices that draw less power without compromising performance. These objectives may be meet by advancing devices made from silicon, but compound semiconductors such as GaN are beginning to play a role, particularly in enabling more-efficient power delivery.

At Atomera, a semiconductor materials and technology licensing company based in California, we are supporting efforts to develop efficient, high-performance devices produced with a number of different materials with our novel epitaxial technology.

Initially, we developed a unique epitaxially grown silicon material technology, which we refer to as Mears Silicon Technology, or simply MST. We describe this epitaxial technology as 'silicon with a twist.' It's variant on conventional silicon epitaxy, with the novelty being the interruption of growth at intervals, during which time there is the deposition

of a partial monolayer of oxygen, or sometimes other elements. Crucially, the conditions for this deposition ensure that there are sufficient silicon atoms available on the surface to allow high-quality silicon epitaxy to continue.

Over the years, we have discovered that MST can be used to define a diffusion-blocking layer, enabling abrupt junctions and the shielding implants from point defects, which are the main source of dopant diffusion. By creating a thin undoped region that is maintained throughout the silicon manufacturing process, our growth technology enables the engineering of a variety of desirable transistor characteristics, including enhanced carrier mobility, reduced threshold voltage mismatch, and improved short-channel effects. It's also possible to improve junctions and contacts with MST. What's more, further benefits may be realised in some forms of scaled silicon devices, including reduced surface roughness scattering and improved wafer-level reliability metrics, such as bias temperature instability and time-dependent dielectric breakdown.

Recently, we have expanded the application of MST to a wider range of devices. It's now applied to a variety of silicon technologies, from CMOS and

DRAM to power and RF devices, and it's also being used to improve the process for growing GaN on silicon.

We have been working on silicon power devices since 2016. Over that timeframe we have proven that our technology enables unique device-doping profiles. Key merits of the MST layer are the suppression of diffusion below the film, as well as localising doping in the vicinity of the film to enhance conduction.

Initially, we applied our MST technology to 5 V power devices, with our novel MST Smart Profile design used to produce an asymmetric device with higher localised shallow *p*-body doping. Thanks to this doping profile, these power devices combine an expanded safe-operating area with industry-leading values for the specific on-resistance as a function of breakdown voltage for a given silicon process node.

Over time we have extended the reach of our technology to designs covering the 7-48 V range. This work has involved additional doping profile engineering of the drift region. Such success has helped us to showcase the capability of our MST technology, which we licensed to STMicroelectronics in 2024 for its Smart Power products.

#### From silicon to GaN

GaN technology, a newcomer compared with silicon, has matured considerably since its introduction into power devices. While yet to receive as much attention as SiC for high-voltage, high-power applications in the automotive and industrial sectors, GaN has inherent advantages over both silicon and SiC in terms of its high mobility – and hence its higher frequency. In addition, compared with silicon, it offers a markedly better on-resistance as a function of blocking voltage. Due to its superior efficiency at high frequencies, GaN is well-suited to deployment in DC-DC converters and various lower-power converters.

Today, the majority of sales of GaN devices are associated with fast-charging for consumer electronics. However, GaN could serve in many more applications, as these devices are capable of operating in units with power capabilities of up to tens of kilowatts, and frequencies from tens of kilohertz to tens of megahertz.

Helping to expand the opportunities for this wide bandgap semiconductor will be advances in GaN material growth quality, alongside a reduction in cost that could come from the introduction of 300 mm wafers. It's anticipated that consumer electronics products, such as laptop chargers and mobile phone fast chargers, will continue to drive the majority of the demand for GaN, while increases in revenue will be driven by the automotive segment, with GaN a strong candidate for onboard chargers and ADAS systems.

Note, though, that the automotive market is not the only one that promises growth for GaN. Artificial intelligence and machine learning will benefit from GaN, as the GPU and memory processors in this high-performance compute application require high power.

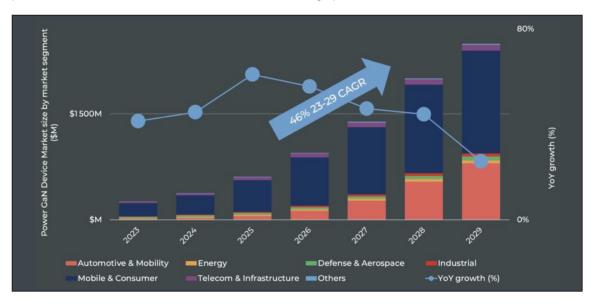

Figure 2. Growth of GaN power device market by market segment. Source: Power SiC & GaN Compound Semiconductor Market Monitor, Q1, 2024, Yole Intelligence.

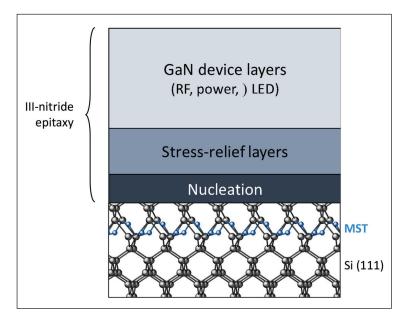

Figure 3. GaN on MST on silicon (111).

When market analyst Yole Group considered all the opportunities for GaN, they forecast that annual revenue will total more than \$2 billion by the end of this decade (see Figure 2).

#### Unlocking the potential of GaN

Our current licensing of MST is directed towards improving the electrical characteristics of a wide application space of silicon products, from power and RF through memory to the most-advanced logic nanosheet applications. So, what can MST offer GaN? In short, a more compliant lattice for the growth of lower-defectivity GaN-on-silicon (see Figure 3). In this sense, MST offers chemical and mechanical advantages, as opposed to the previously characterised electrical benefits.

In our early days, we devoted much effort to the fundamental ab initio modelling of the inserted partial monolayers of oxygen in the silicon lattice, as well as detailed experimental characterisation. Back then we often considered a ball-and-stick model, with a silicon-silicon bond bending to enable a stable Si-O-Si bond that retained the silicon lattice. As oxygen is introduced, the stability of the overall structure increases via the proximity of adjacent oxygen. We discovered that over a characterised temperature range, stability improves with oxygen

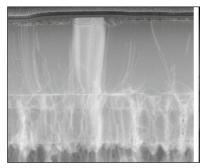

Figure 4. Defect reduction using MST. Same epi recipe and crosssectional transmission electron microscopy imaging conditions for both samples.

density, according to a power law with a factor of roughly 2.5.

Another insight from this work is that due to the electronegativity of oxygen, charge transfer occurs from adjacent silicon atoms. Due to this, nextnearest silicon neighbours have a smaller opposite charge, and the charge spatial 'wave' dissipates over about four atomic spacings. Related to this is a local distortion of the lattice to accommodate oxygen, again with dissipation over about four atomic spacings.

According to our theoretical simulations, this modified silicon lattice is better at accommodating lattice mismatch. This observation provided our starting point for virtual substrate work and, in particular, our development of GaN-on-silicon technology.

#### Growth on silicon

The conventional growth of GaN-on-silicon begins by taking (111) orientated silicon wafers with nominally zero-degree off-cut and loading them into a reactor for epitaxial growth. In contrast, silicon epitaxy for electronic applications typically involves (100) orientated wafers with a 4° offcut.

Removing the off-cut presented us with a challenge. Based on conventional epi wisdom, zero-degree growth is too slow and can be defective. Addressing these issues has taken some time, but we have been able to overcome these challenges and apply our MST technology to silicon (111) substrates.

Assisting us in this endeavour, in late 2023 we started to engage with Wayne Johnson, a veteran in GaN technology. Johnson had previously worked at Nitronix, a pioneer in the GaN space, before working for Kopin and then IQE. Through Johnson, we were introduced to another GaN pioneer, the academic Edwin Piner of Texas State University. These introductions led us to sponsor a programme at Texas State University to grow baseline GaN HEMT material.

The first phase of this project focused on the physical characterisation of GaN grown on MST substrates. For this investigation, Piner's team compared results with their stable process-ofrecord GaN baseline stack, consisting of AIN buffer layers followed by GaN of around 2 µm thickness, a heterostructure suitable for RF applications. For the first phase dataset, the process-of-record recipe was kept constant, and various MST structures were grown to start to explore how our technology interacts with the baseline. To everyone's delight, the first set of wafers showed very promising results.

This promise is clear in side-by-side transmission electron microscopy images, comparing the process-of-record GaN-on-silicon stack with the same stack on the MST (111) wafers. Images at the microscopic level reveal that the MST wafers have fewer defects, both in the AIN buffer and in the top GaN layer.

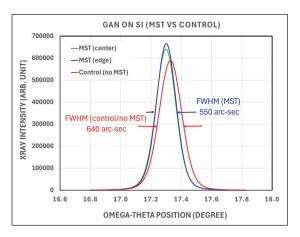

While the transmission electron microscopy images are encouraging, they have the potential to mislead, because they only consider a very small region. To cater for this concern, we turned to X-ray diffraction to examine crystal quality, considering the width of the diffracted beam.

The benchmark for this is the X-ray diffraction spectra from the process-of-record GaN-on-silicon stack produced by Piner and his co-workers that's been characterised over a number of years. Diffraction peaks from this material, considering the (002) and (114) diffraction directions, have typical values for the full-width at half-maximum of 650 +/-30 arcsec. Such values are considered to be good for industry-grade 2  $\mu m$  GaN.

X-ray diffraction spectra for the MST design has confirmed the promise provided by transmission electron microscopy. X-ray diffraction peaks for the (002) and (114) directions are narrower (see Figure 5), with different trends observed in the composition and spacing of the MST layers.

#### Collaborating with Sandia Labs

Recently, we announced a collaboration with Sandia National Labs – a Department of Energy, Office of Science, Nanoscale Science Research Center – with this partner performing electrical tests on our MST-supplied silicon (111) substrates, with GaN epilayers grown at Texas State University. The purpose of this

Figure 5.

Example

of X-ray

diffraction

(XRD) fullwidth at

half-maximum

(FWHM)

improvement

with MST.

project is to validate MST's mechanical and electrical benefits for GaN-on-silicon epiwafers. This effort will build upon improvements already observed at the materials level in GaN/MST-on-silicon wafers.

While GaN is helping to usher in a new era of electronics, challenges persist. However, many of them can be addressed by leveraging our innovations in material science, which open the door to even higher efficiencies, greater power handling, and enhanced stability. Such gains will help to enable electrification in many fields. By providing a cost-effective alternative to SiC, our MST technology is expanding the limits of GaN chip performance.

# kSA 400 for RHEED Analysis

# Exploit the power of RHEED!

- The industry's most powerful analytical RHEED tool

- Growth rate, lattice spacing, surface coherence, time evolution and more at your fingertips

- Plus the best support in the industry

- Learn more by visiting our website: k-space.com

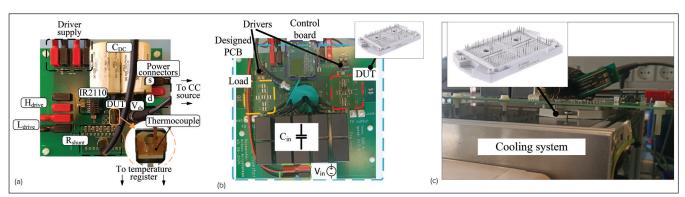

# **Exposing SiC defects**

Conductance and optical excitation measurements offer unique insights into interfacial defects in SiC devices

## BY PIYUSH KUMAR, MANUEL BELANCHE AND ULRIKE GROSSNER FROM ETH ZURICH

SILICON CARBIDE is transforming the future of semiconductor devices. Strengths of this wide bandgap matertial include low conduction and switching losses, a high blocking-voltage capability, fast switching, and high operating temperatures. It's a set of attractive properties that make SiC a compelling candidate for high-power, hightemperature electronics, and radiation-hard applications.

One crucial driver behind the development of SiC power electronics is its similarity to mature silicon transistors, in terms of the manufacturing processes and the device structure – both technologies employ the native oxide SiO<sub>2</sub>. Thanks to extensive understanding of this dielectric, SiC enjoys a significant advantage over other wide bandgap

semiconductors, with its development drawing on existing fabrication processes established for producing silicon devices.

#### The devil in the defects

Unfortunately, unlocking the promise of SiC demands addressing a number of key challenges. A major one is an imperfect interface between SiC and SiO<sub>2</sub> that prevents SiC technology from reaching its full potential. Growth of this dielectric, a thin layer of SiO<sub>2</sub>, involves thermal oxidation of SiC at high temperatures. During this step many unwanted electrically active defects, commonly referred to as traps, form at the SiO<sub>2</sub>-SiC interface. These defects drag down channel mobility and capture charges, which cause threshold voltage instabilities, a major concern in the development of SiC MOSFETs.

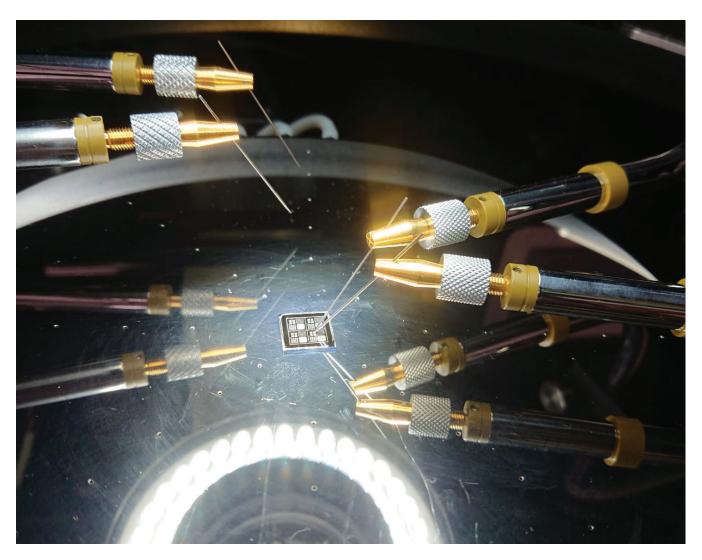

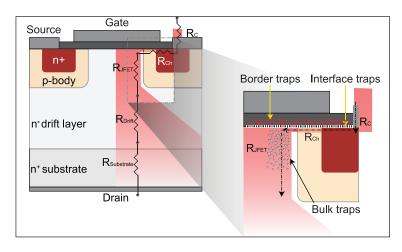

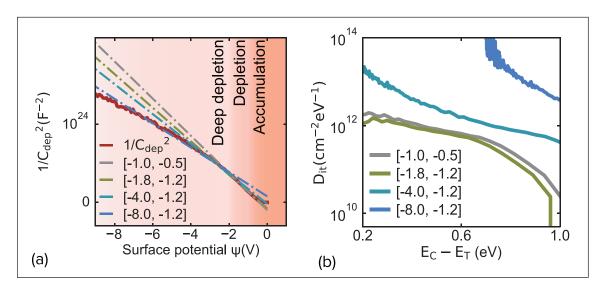

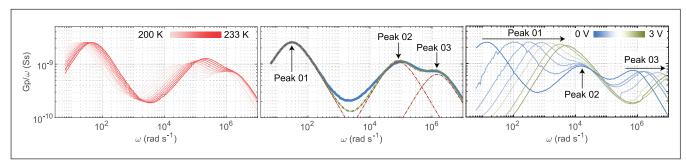

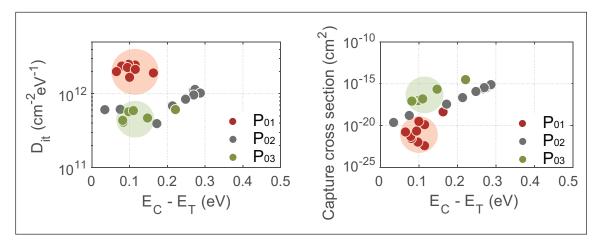

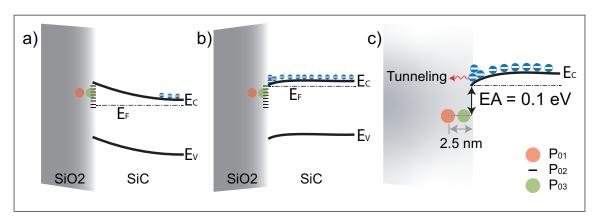

To address these issues, it is essential to understand the nature of these electrically active defects. Knowing them is the first step to avoiding them.