# COMPOUND SEMICONDUCTOR

CONNECTING THE COMPOUND SEMICONDUCTOR COMMUNITY

VOLUME 30 ISSUE IV 2024

COMPOUNDSEMICONDUCTOR.NET

#### **INSIDE**

News, Analysis, Features, Editorial View, Research Review and much more

## A new approach to education

Compound semiconductor innovation requires an overhaul of engineering education and talent development

## Monolithic power integration

Sapphire substrates with ultrathin buffer layers hold the key to 1200 V GaN-based monolithic power integration

## Silicon's positive influence

Sales to silicon fabs are behind the greatest gain in share price within the compound semiconductor industry

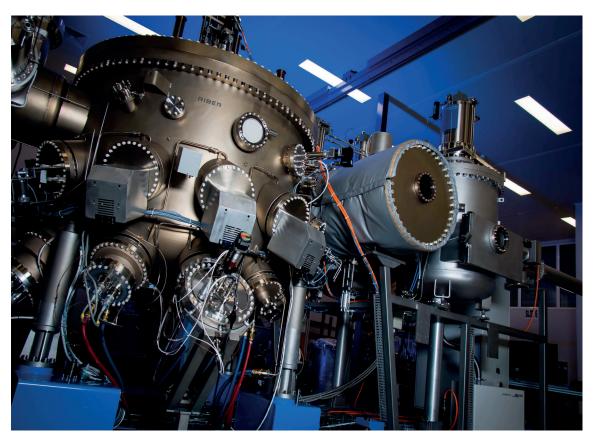

## AIXTRON

## THE NEW G10 SERIES

Your Productivity Solution for All Advanced Epitaxy Materials

#### G10-SiC

- ▶ 9x150 mm (6") or 6x200 mm (8")

- New hardware & process surpassing Single Wafer Reactor uniformities

- ► +50% productivity per fab area with large batch technology & small footprint

#### **End Markets/Products:**

EV inverters & charging infrastructure

#### G10-GaN

- ▶ 8x150mm (6") or 5x200mm (8")

- ▶ 1st fully automated compact GaN MOCVD cluster designed 100% for Si Power fabs

- Novel hardware solution for unmatched barrier uniformities and device yields

#### **End Markets/Products:**

Power Electronics & Wireless communication

#### G10-AsP

- ▶ 8x150 mm (6") or 5x200 mm (8")

- ▶ 1<sup>st</sup> fully automated AsP MOCVD system enabling 10x lower defect density

- Unmatched wavelength uniformity on all wafer sizes

#### **End Markets/Products:**

Micro LED, Optical Data communication, 3D-sensing & LiDAR

## **VIEWPOINT**

By Richard Stevenson, Editor

#### Green credentials?

What have you done to help to tackle climate change? It's a question rarely asked today.

However, fast-forward a decade or more and we can expect interrogation from younger generations, demanding an answer, possibly along with an apology.

If you are limiting foreign travel, trimming meat consumption, or are an early adopter in electric vehicles (EVs), you may avoid the harshest criticism. And you might also defend yourself by pointing out that you have been involved in an industry that's introduced new technologies, which are playing a valuable role in slashing carbon dioxide emissions.

Within the compound semiconductor industry, there are certainly some great success stories involving substantial energy savings.

Arguably the biggest to date is in general illumination. The incumbent of the twentieth century, the incandescent bulb, is notoriously inefficient, with around 90 percent of electricity converted into heat. It's initial rival, the fluorescent, has the upper hand in this regard, but takes time to warm up and fails to light a room with flattering form of white. Accounting for the demise of both of these forms of lightbulb is that based on the LED. It has no major weaknesses and delivers hikes in efficiency and lifetime.

The other example easily coming to mind of compound semiconductor chips giving a helping hand to the environment is role that they play in EVs. Power semiconductors based on SiC are increasing the efficiency with which the energy from the battery provides transportation. As well as reducing the energy per mile, the uptake of SiC is increasing the driving range, and ultimately helping to accelerate adoption of a new generation of automobiles through reduced range anxiety.

While EVs are helping to tackle climate change, there are concerns over the production of their batteries. Mining the key ingredients for their manufacture is detrimental to the environment, and production is energy intensive.

Studies suggest it takes 30-55 kWhr of energy for every kWhr of battery. This soon adds up, given that EVs can be powered by batteries with a total energy capacity of 100 kWhr.

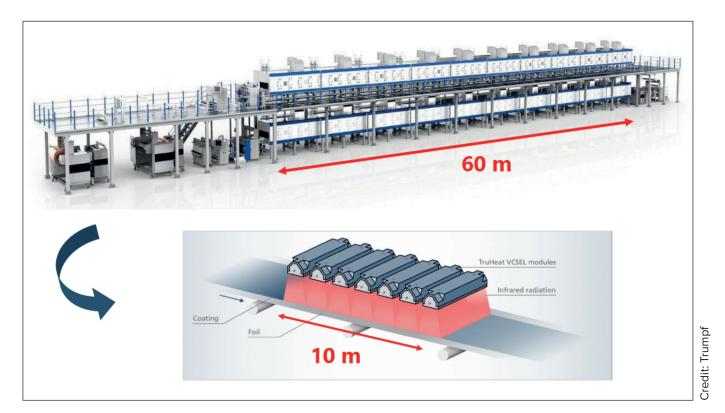

Within the battery production process, nearly half of all the energy that's consumed is involved in a heating process, with ovens employed to dry a thick, wet, lithium-containing slurry that's applied to a metal foil during the production of electrodes.

At this year's CS International, CTO of Trumpf Photonics, Roman Koerner, revealed that energy savings could come from heating with vast arrays of VCSELs. According to Koerner, the established oven-based process has an efficiency of

10-20 percent, while laser drying is more than 40 percent efficient (for more details, see "New vectors for the VCSEL" on p 28).

This opportunity for the VCSEL is yet another example of how compound semiconductors are positioned to play an increasing role in tackling climate change. While our community's devices are only a small part of the solution, all contributions are welcome in the struggle to prevent overheating of our planet.

#### 20 Overhauling engineering education

To ensure the future of compound semiconductor innovation, a new approach is needed to engineering education and talent development

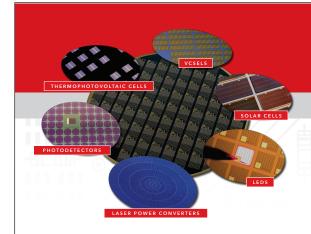

#### 28 New vectors for the VCSEL

The VCSEL is assured of a promising future, with growth in established markets to continue alongside success in new applications

#### 34 Silicon's positive influence

While most players in the CS industry are suffering from significant falls in their share prices over the last 12 months, a few companies have risen in valuation, in one case due to opportunities within the silicon industry

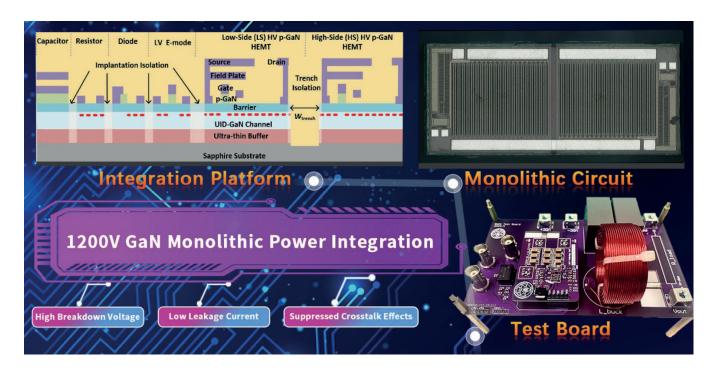

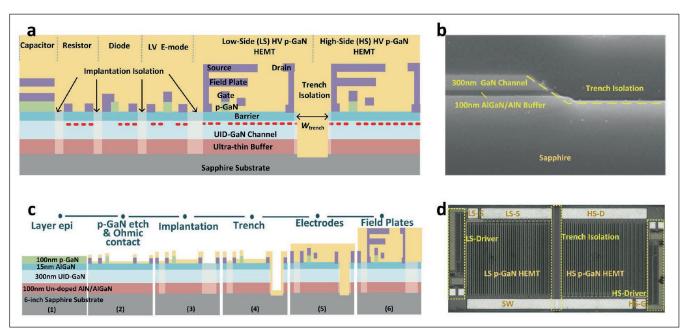

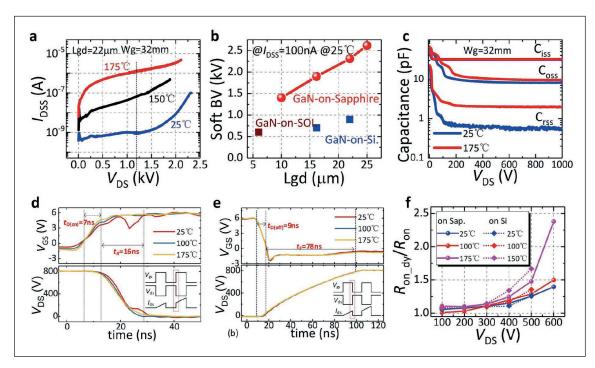

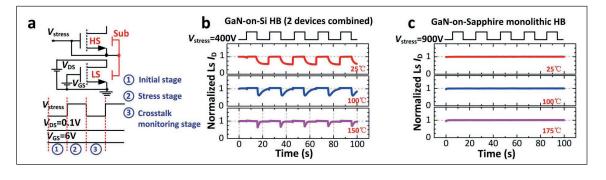

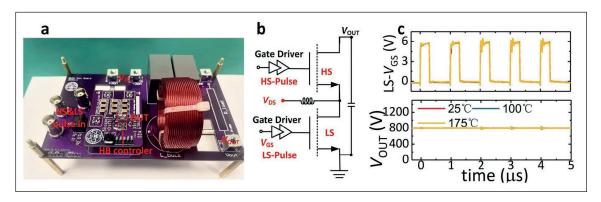

## 40 1200 V GaN monolithic power integration

Sapphire substrates with ultra-thin buffer layers provide a foundation for fabricating systems offering 1200 V GaN-based monolithic power integration while supressing crosstalk

#### 44 Gate to the future

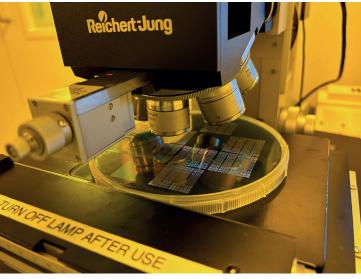

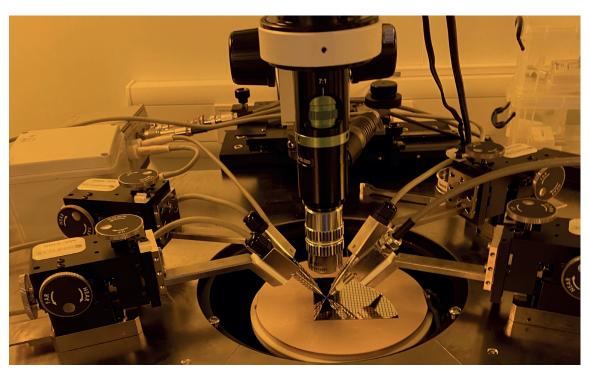

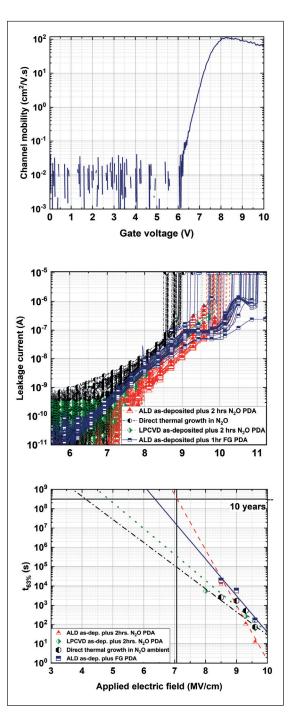

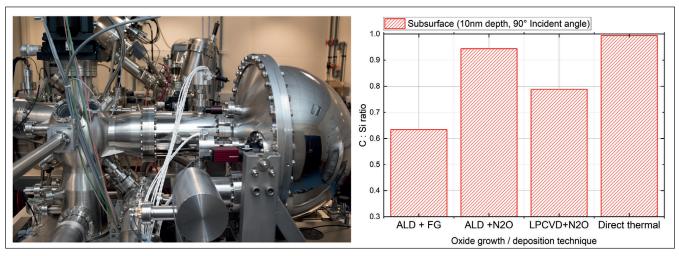

Reliability benefits from deploying deposited gate oxides in SiC MOSFETs

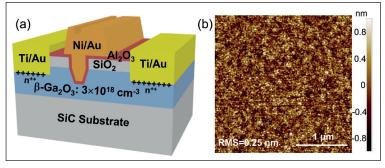

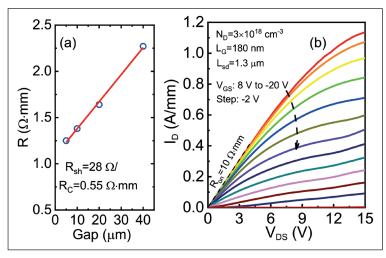

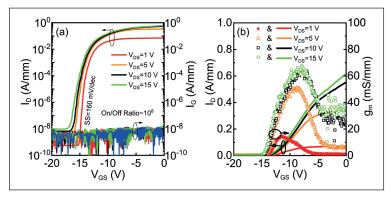

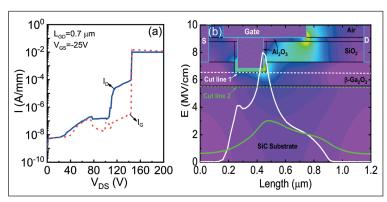

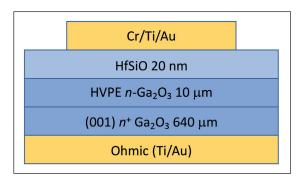

#### 52 β-Ga<sub>2</sub>O<sub>3</sub> RF power FETs

A promising candidate for tomorrow's high-voltage, high-power RF applications, the  $\beta\text{-}Ga_2O_3\text{-}on\text{-}SiC$  RF power FET is already amplifying signals up to 8 GHz with an output power density approaching 1 W/mm

#### **NEWS ANALYSIS**

## 14 CS International champions a green agenda

Compound semiconductors are the driving force behind the more efficient use of electricity, reduced energy consumption for battery manufacture, and photovoltaic systems with integrated energy storage

#### 18 A wise investment in the GaN IC

French start-up Wise-Integration has raised an additional €15 million to expand its commercialisation of the GaN IC

#### RESEARCH REVIEW

- 58 GaN VCSELs: Refining the production process

- 59 Realising a low contact resistance on N-polar GaN surfaces

- **60** Ga<sub>2</sub>O<sub>3</sub>: Improving the gate dielectric

#### **NEWS**

- 06 What's next for SiC?

- **07** Q-Pixel debuts highest resolution colour display

- **08** Vishay chooses Aixtron SiC tech for Newport fab

- **09** MicroLED firm Kubos raises \$2 million

- 10 SiCrystal and ST expand SiC wafer agreement

- 10 Arizona State University to explore potential of AlN

- 11 China's IP office validates EPC GaN patents

- 12 Infineon SiC modules to power Xiaomi EV

- 12 UK's CSConnected appoints new managing director

Editor Richard Stevenson richardstevenson@angelbc.com +44 (0)1291 629640

**News Editor** Christine Evans-Pughe christine.evans-pughe@angelbc.com

**Design & Production Manager**Mitch Gaynor

mitch.gaynor@angelbc.com

+44 (0)1923 690214

**Director of Logistics** Sharon Cowley sharon.cowley@angelbc.com

+44 (0)1923 690200

Senior Sales Executive

Jacob Caulfield jacob.caulfield@angelbc.com +44 (0)2476 718979

Marketing & Logistics Executive

Eve O'Sullivan +44 (0)2476 823 123 eve.osullivan@angelbc.com Circulation Scott Adams

scott.adams@angelbc.com

Publisher Jackie Cannon jackie.cannon@angelbc.com +44 (0)1923 690205

Senior B2B Event & Media Sales USA

Catherine Sayers catherine.sayers@angelbc.com +44 (0)2476 718 975 Chief Executive Officer

Sukhi Bhadal sukhi.bhadal@angelbc.com +44 (0)2476 718970

Chief Technical Officer Scott Adams scott.adams@angelbc.com

+44 (0)2476 718970

**Directors**Jackie Cannon, Sharon Cowley

Published by

Angel Business Communications Ltd 6 Bow Court, Fletchworth Gate, Burnsall Road, Coventry CV5 6SP, UK.

T: +44 (0)2476 718 970

E: info@angelbc.com

Compound Semiconductor is published nine times a year on a controlled circulation basis. Non-qualifying individuals can subscribe at: £105.00 per annum (UK), €158 per annum (Europe), \$198 per annum (air mail) (USA). Cover price £4.50. All information herein is believed to be correct at time of going to press. The publisher does not accept responsibility for any errors and omissions. The views expressed in this publication are not necessarily those of the publisher. Every effort has been made to obtain copyright permission for the material contained in this publication. Angel Business Communications Ltd © Copyright 10 publishers reserved. Contents may not be reproduced in whole or part without the written consent of the publishers. The paper used within this magazine is produced by chain of custody certified manufacturers, guaranteeing sustainable sourcing. US mailing information: Compound Semiconductor, ISSN 1096-598X, is published 9 times a year, Jan/Feb, March, April/May, June, July, August/September, October, November, December by Angel Business Communications Ltd, Unit 6, Bow Court, Fletchworth Gate, Burnsail Rd, Coventry CV5 659. UK.Airfreight and mailing in the USA by agent named World Container INC 150-15, 183rd St, Jamaica, NY 11413, USA. Periodicals Postage Paid at Brooklyin, NY 11256. POSTMASTER: Send address changes to Compound Semiconductor, Air Business Ltd, c/o World Container INC 150-15, 183rd St, Jamaica, NY 11413, USA. We strive for accuracy in all we publish; readers and contributors are encouraged to contact us if they recognise an error or omission. Once magazine edition is published [online, in print or both), wed not update previously published articles to align old company names, branding, marketing efforts, taglines, mission statements or other promotional veribiage, images, or logos to newly created or updated names, images, typographic renderings, logos (or similar) when such references/images were accurately stated, rendered or displayed at the time of two reiplane, business objective

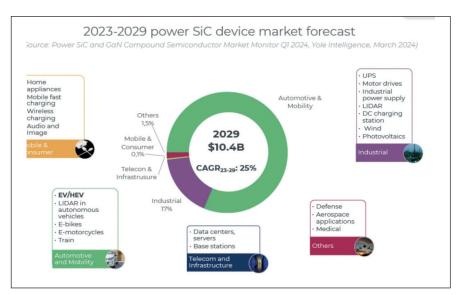

#### What's next for SiC?

Shipments are slowing down due to the weakness of the global economy, according to Yole

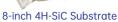

POWER ELECTRONICS based on SiC is on track to reach \$10 billion in revenue by the end of this decade, and the strong growth in 2023 was a crucial step in multiple applications, according to the market research firm Yole Group.

BEV remains the key market driver, with Tesla's 1.8 million cars shipped in 2023, while major OEMs such Hyundai, BYD, Xpeng, Nio and many others are increasingly launching 800 V BEVs. All the major SiC device players are supplying this application, helping it achieve record revenue in 2023.

In the meantime, other applications, such as EV chargers, power supplies and photovoltaics, are waiting for sufficient volume at a competitive cost for the next generation of SiC device designs. It was the same in the SiC wafer and epiwafer businesses, with record 2023 revenues.

However, Yole says there is a concern that shipments are slowing down due to the weakness of the global economy. Many players are re-evaluating the timing of the return to growth;

could it be in Q3 of 2024 or later? The SiC supply chain is closely monitoring it, as 2024 results will be highly impacted.

In the meantime, the supply chain is reshaping. This is seen in the ranking of players by revenue in 2023: currently, Yole sees at least two Chinese companies ranked in the top five in SiC wafer and epiwafer. This also indicates the maturity of equipment supply

supporting this rapidly growing SiC market. Another critical consideration is the demand-supply issue. In the past years, SiC wafer was in tight supply; a long-term agreement with a wafer supplier being essential to secure access to SiC wafers. However, following significant capacity expansion in the past two years, the discussion is moving to price and the risk of overcapacity, says Yole.

#### Power Integrations to acquire Odyssey assets

POWER INTEGRATIONS has agreed to acquire the assets of Odyssey Semiconductor Technologies, a developer of vertical GaN transistor technology. The transaction is expected to close in July 2024, after which all key Odyssey employees are expected to join Power Integrations.

The acquisition supports the company's ongoing development roadmap for its proprietary PowiGaN technology, which is featured in many of the company's product families, including InnoSwitch ICs, HiperPFS-5 power-factor-correction ICs and the recently launched InnoMux-2 family of single-stage, multiple-output ICs.

The company introduced 900 V and 1250 V versions of PowiGaN technology and products in 2023.

According to Radu Barsan, Power Integrations' vice president of technology, Pl's roadmap is to achieve cost parity with silicon MOSFETs and expand the voltage and power capabilities of PowiGaN.

Barsan said: "Our goal is to commercialise a cost-effective high-current and high-voltage GaN technology to support higher-power applications currently served by SiC, at a much lower cost and higher performance enabled by the fundamental material advantages

of GaN over SiC. The experience of the Odyssey team in high-current vertical GaN will augment and accelerate these efforts, and we are delighted to add them to our team."

Richard Brown, Odyssey co-founder and CEO said: "The Odyssey team and I are excited to join Power Integrations in accelerating their GaN technology roadmap. As the first company to commercialise high-voltage GaN, Power Integrations continues to lead the industry in driving the technology forward in terms of cost, voltage and current, as well as the design of system-level products that take full advantage of the capabilities of GaN."

## Q-Pixel debuts highest resolution colour display

Q-Pixel believes it has produced the highest resolution, active-matrix colour display in the world

Q-PIXEL'S breakthrough display boasts 6,800 pixels-per-inch (ppi), far surpassing current state-of-the-art displays, such as the Apple Vision Pro (around 3,380 ppi). The display is made entirely using microLED pixels.

Unlike most advanced VR displays, which use micro-organic LEDs (micro-OLEDs), Q-Pixel's displays consist entirely of III-V compound microLED pixels. Synthesised from inorganic materials, III-V microLEDs offer many advantages over OLEDs, including a faster response time, higher brightness, longer lifetime, and superior energy efficiency. From a physics perspective, inorganic III-V microLEDs have long been considered the ideal display technology, but have lacked a clear path to commercial viability.

The main challenges to commercialising microLED displays arise from the traditional approach of assembling full colour pixels using individual monochromatic red, green, and blue (RGB) LEDs. For high-resolution displays requiring small (less than 50 μm) pixels, the assembly, testing, and repair of millions of RGB microLED subpixels is a complicated, labour-intensive, and expensive process. Moreover, the physical space required for three RGB subpixels restricts the display's pixel density, posing an obstacle to realising high-resolution displays. Q-Pixel's overcomes both hurdles by replacing three RGB subpixels with individual, fully colour-tunable pixels.

The enabling technology is based on a disruptive tunable polychromatic LED (TP-LED) pixel: a single pixel capable of emitting light across the full colour spectrum, without any use of subpixels, quantum dots, colour filters, polarisers, or mechanical stacking. In addition to possessing all the benefits inherent to III-V LED technology, Q-Pixel's single TP-LED greatly simplifies display assembly,

reduces manufacturing costs, and enables world-record pixel densities.

In May 2023, Q-Pixel unveiled its world-record 5,000 ppi full-colour microLED display, and in November 2023 surpassed its world record with the simultaneous announcement of a passive 10,000 ppi microLED display made from the world's smallest full-colour pixels (1 µm diameter), all based on its TP-LED technology.

Now by delivering the world's highest resolution (6,800 ppi) active-matrix colour display, Q-Pixel has accomplished two major milestones. First, it has proved that it is possible to produce ultra high-resolution, active displays based on the microLED technology. Secondly, it has shown that its TP-LED pixel technology surpasses more mature display technologies, such as OLEDs, to attain world-record breaking pixel densities.

With these latest achievements, Q-Pixel says that it has established itself as a trailblazer in the microLED field and will embark on the commercialisation of dazzling displays.

Q-Pixel demonstrated its technology and prototype at the Society for Information Display's annual symposium and tradeshow, SID Display Week, held on May 14-16, 2024. We cordially invite you to join the Institute of Novel Semiconductors at Shandong University

#### 1. About Us

The Institute of Novel Semiconductors is a key academic special zone supported by Shandong University. Leveraging the solid foundation of Shandong University in the field of semiconductor material research, the institute aims at the future development direction of semiconductor material technology. It focuses on the major demands in energy, information, rail transit, and other fields, cultivating the development of new generation wide bandgap and ultra-wide bandgap semiconductor single crystal materials, enhancing breakthroughs in key technologies of semiconductor devices, and promoting application demonstrations in typical application fields.

#### 2. Application Conditions

#### (A) Basic Conditions

- 1. Born after January 1, 1969 (inclusive);

- 2. In principle, should have a Ph.D. degree;

- 3. Have obtained a formal teaching or research position at overseas universities, research institutions, or corporate R&D institutions;

- 4. Have-obtained researchor

- technical-achievements recognized-by peers in the field,and havethepotential-to-becomea leading-academic-or-outstanding-talent-inthefield.

#### (B) Research Directions and Professional Fields

Growth of new generation semiconductor single crystal materials such as silicon carbide, gallium nitride, gallium oxide, diamond, aluminum nitride, boron arsenide, thin film growth, substrate processing, advanced laser technology; fabrication of power devices, optoelectronic functional devices, acoustic devices, microwave devices; and the related technology fields of packaging testing, modules, etc.

#### 3. Compensation and Benefits

- (A) High Starting Point for Career Development: Eligible for appointment as a professor and doctoral supervisor:

- (B) Competitive Salary: Comprehensive annual salary not less than 600,000 RMB, with no cap on total income:

- (C) Sufficient Research Funding: Research funding ranging from 3 to 10 million RMB during the employment period;

- (D) Excellent Working and Living Conditions: Offers a settling-in and housing subsidy of 2.5 million RMB for the National talents;

- (E) High-Quality Team Resources: Provides full quotas for recruiting PhD students and postdoctoral researchers during the employment period;

- (F) Additional Support: Offers first-class medical and healthcare services for talents, and provides leading domestic basic education for the children of talents. Assistance in resolving spouse employment issues.

#### 4. Contact Information

C.P.: Ms. Wang | Tel: 86-531 883 66003 Email: dpt@sdu.edu.cn | https://dpt.sdu.edu.cn Add: No. 27, Shanda South Road, Licheng District, Jinan City, Shandong Province, China

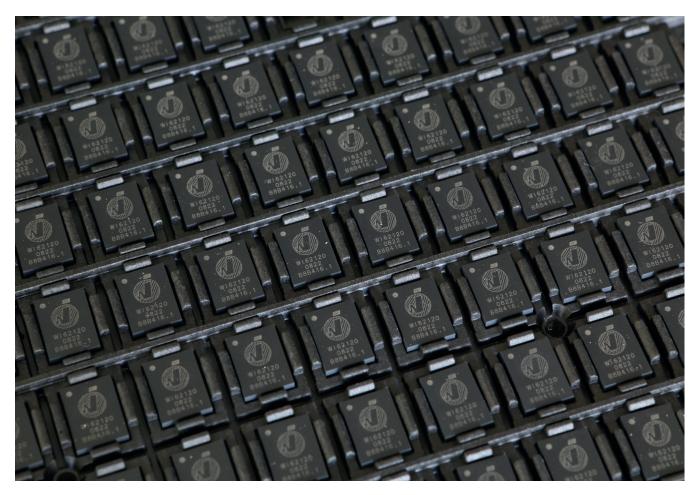

### Vishay chooses Aixtron SiC tech for Newport fab

G10-SiC epitaxy production platform supports transition between 150 mm and 200 mm wafers

VISHAY INTERTECHNOLOGY has chosen Aixtron's G10-SiC epitaxy production platform for the automotive-certified Newport fab in South Wales, UK, which it has recently acquired.

With its flexible dual wafer size configuration of 9 x 150 mm and  $6 \times 200$  mm, the G10-SiC supports the transition between the wafer diameters.

"The new G10-SiC epi production tool delivers a leading cost structure for 200 mm epitaxy, which meets Vishay's productivity goals. This, in combination with an excellent uniformity performance on 200 mm wafers, has made us choose Aixtron technology,"

said Danilo Crippa, senior director R&D for SiC development, Vishay Intertechnology.

"The Aixtron team has developed a unique solution for the tightest control of doping levels and uniformity on 200 mm SiC wafers. This performance is maintained across the entire 6 x 200 mm wafer batch with an impressive run- to-run stability," said Frank Wischmeyer, VP SiC, Aixtron SE.

He added: "We are very grateful for the opportunity to partner with Vishay and deliver our state-of-the-art epi production system with flexible 150 mm and 200 mm SiC wafer configuration

for Vishay's automotive-certified Newport fab in South Wales. Our strong customer service team in the South Wales Compound Semiconductor Cluster is dedicated to fully support the production ramp of Vishay's SiC inhouse epitaxy to the highest productivity within a short period of time."

#### SweGaN announces strategic partnership with RFHIC

SweGaN AB, a European semiconductor manufacturer that develops and produces engineered high-performance GaN-on-SiC epitaxial wafers, has announced it has entered strategic partnership with South-Korea-based RFHIC Corporation. RFHIC is a global leader in designing and manufacturing GaN RF and microwave semiconductors for communications and defence applications. The new, pivotal agreement encompasses an undisclosed equity investment from RFHIC. The two companies will focus on joint R&D and product development moving forward.

Over the last decade, SweGaN has been developing and producing high-performance GaN-on-SiC epitaxial solutions for RF and power devices that can be used in various applications such 5G telecommunications infrastructure, defence radars, satellite communications, on-board chargers, and data centres.

The new strategic investment by RFHIC is said to manifest the recognition of SweGaN's QuanFINE epitaxial solutions as a standout differentiator among GaNon-SiC materials available on the market. In partnership with RFHIC, SweGaN gains

additional resources to expedite market penetration and to achieve its business goals.

RFHIC Corporation believes that the partnership with SweGaN and its investment strategy will strengthen RFHIC's GaN semiconductor supply chain and further fortifying its competitiveness of RF and microwave products within the compound semiconductor arena.

Jr-Tai Chen, CEO and Founder at SweGaN, remarked: "With the accelerating demand for high-performance semiconductor materials to power a multitude of applications and increase the efficiency in an energy-conscious world, the new equity investment will support SweGaN's capacity expansion plan of its best-inclass GaN-on-SiC epitaxial wafers and tap joint product developments with RFHIC."

He added: "We are very proud to partner with RFHIC, a leading RF GaN innovator who has the passion and commitment to amplify the world by providing top-efficiency and cuttingedge GaN solutions." As market requirements for highpower, highly efficient semiconductors are spurred by the rapid growth of a wide array of applications such as 5G communications, defence radars and data centers, SweGaN is moving swiftly to address the growing demand by expanding its in-house manufacturing capacity and R&D capability.

The new strategic partnership with RFHIC has the potential to significantly invigorate SweGaN's position in multiple geographical areas important for the company as it aims to lead a transition from legacy material solutions to its innovative GaN semiconductors.

Samuel Cho, CTO and co-founder of RFHIC Corporation, said: "As RFHIC maps its future strategy for GaN semiconductors, including accelerated market demand for products in 5G, 6G, satellite communication and more, SweGaN's high-performance 6-inch GaN epiwafers for RF and power semiconductors – with exemplary high-power efficiency – provide a strong fit for our technological roadmap and diversification of gallium nitride epitaxial wafer suppliers."

### MicroLED firm Kubos raises \$2 million

UK-based firm to use funding to double red microLED efficiency for AR/VR displays

KUBOS SEMICONDUCTORS, a UKbased microLED material technology company, has raised \$2 million to accelerate development of its cubic GaN technology, which can double the efficiency of red microLEDs.

It brings the company's total funding to \$5.5 million and will enable Kubos to enter the microLED display market within three years through IP licensing.

Kubos says its technology will enable clearer, brighter, more efficient displays to be manufactured for augmented reality and virtual reality (AR/VR) applications.

The company has secured support from three of the most prolific and experienced veterans of the (UK) compound semiconductor industry and three strategic investors. Martin Lamb, Drew Nelson, and Geoff Haynes have a combined tenure of over 100 years in compound semiconductor materials development. Strategic investors are the Development Bank of Wales, FOV Ventures, and S4C Digital Media.

Caroline O'Brien, CEO of Kubos. commented: "Any UK compound semiconductor business would be thrilled to have just one of these movers and shakers in the industry supporting it and Kubos can now draw on the experience of all three. In addition, the strategic investor group that we have assembled brings vital insight into how the metaverse, digital content and AR/ VR products drive display and microLED requirements. This, coupled with our unrivalled experience in compound semiconductors means that Kubos is now fully equipped and ready to deliver."

Martin Lamb, formerly CEO of Wafer Technology (acquired by IQE in 2000) and an angel investor with several successful exits, was instrumental in the formation of Kubos, and an early investor, and has guided and shaped the team. He has served as chairman since its inception and will continue in this role.

Drew Nelson, founder of IQE who stepped down as CEO in January 2022, has invested in Kubos and joins the board of directors.

Geoff Haynes also participated in this investment round and is a GaN semiconductor expert. A company he co-founded in 2008 to address the power semiconductors market. GaN Systems, was acquired by Infineon for \$830 million last year.

The Development Bank of Wales has a track record of supporting breakthrough technologies and compound semiconductor businesses. FOV Ventures is focussed on spatial computing and S4C Digital Media plays a key role in the delivery of

digital content to consumers. This investor group brings experience and knowledge that touches on all aspects of the AR/VR opportunity that Kubos aims to exploit.

Carl Griffiths, fund manager in the Technology Venture Investments team at the Development Bank, said: "Kubos' proprietary technology has the potential to improve the user experience for lighting and displays and accelerate the adoption of microLEDs across a wide range of applications. We are proud to be working with this exciting company of highly acclaimed engineers and scientists, and to have helped them re-locate to Wales to make use of the compound semiconductor expertise and infrastructure in the region."

Any UK compound semiconductor business would be thrilled to have just one of these movers and shakers in the industry supporting it and Kubos can now draw on the experience of all three. In addition, the strategic investor group that we have assembled brings vital insight into how the metaverse, digital content and AR/VR products drive display and microLED requirements 🧾

## SiCrystal and ST expand SiC wafer agreement

A multi-year agreement with STMicroelectronics is helping to drive an increase in SiCrytals' production of SiC substrates manufactured in Nuremberg

ROHM and STMicroelectronics have expanded an existing multi-year, long-term 150 mm SiC substrate supply agreement involving SiCrystal, a Rohm group company.

The new agreement governs the supply of larger volumes of SiC substrates manufactured in Nuremberg, Germany, for a minimum expected value of \$230 million.

Geoff West, EVP and chief procurement officer, STMicroelectronics, commented: "This expanded agreement with SiCrystal will bring additional volumes of 150mm SiC substrate wafers to support our devices manufacturing capacity ramp-up for automotive and industrial customers worldwide. It helps strengthen our supply chain resilience for future growth, with a balanced mix of in-house and commercial supply across regions."

"SiCrystal is a group company of Rohm, a leading company of SiC, and has been manufacturing SiC substrate wafers for many years. We are very pleased to extend this supply agreement with our longstanding customer ST. We will continue to support our partner to expand SiC business by ramping up 150 mm SiC substrate wafer quantities continuously and by always providing reliable quality," said Robert Eckstein, president and CEO of SiCrystal, a Rohm group company.

#### US SiC R&D facility celebrates topping out

THE UNIVERSITY OF ARKANSAS has celebrated a milestone with the topping-out of the Multi-User SiC Research and Fabrication Facility. The new semiconductor facility will enable the federal government — via national laboratories — businesses of all sizes and other universities to prototype with SiC, a capability that does not presently exist elsewhere in the United States.

Work at the facility is intended to bridge the gap between traditional university research and the needs of private industry. The aim is to accelerate technological advancement by providing a single location where chips can go from developmental research to prototyping, testing and fabrication. The 21,760-square-foot facility, located next to the National Center for Reliable

Electrical Power Transmission at the Arkansas Research and Technology Park, will feature approximately 8,000 square feet of clean rooms for fabrication and testing.

Education and training within the facility will also accelerate workforce development, helping supply the next generation of engineers and technicians in semiconductor manufacturing.

## Arizona State University to explore potential of AIN

ARIZONA STATE UNIVERSITY'S Houqiang Fu, an assistant professor of electrical engineering, has received a US 2024 National Science Foundation Faculty Early Career Development Program (CAREER) Award to explore the potential of the ultrawide bandgap semiconductor AIN in power electronics.

Fu aims to develop AIN power FETs that control power flow with greater efficiency and can handle higher temperatures and more voltage than those made with silicon, SiC or GaN.

While AIN has promising properties, a lack of knowledge regarding how to effectively use the material for power electronics prohibits it from reaching its full capabilities.

Fu will lead a five-year investigation to determine how best to overcome the main problems facing the use of AIN.

This will focus on how best to grow the crystals needed for manufacturing AIN, refine it, fabricate it into power electronic devices and integrate the devices into electrical systems.

"The new AIN power electronics can offer superior performance and significantly impact grid modernisation, transportation electrification and greenhouse gas emissions," Fu says.

"The electronics will also dramatically increase the current grid infrastructure's resilience, reliability and efficiency. They will also help mitigate power disruptions' health and economic impact and improve energy security."

## China's IP office validates GaN patents filed by EPC

EPC delights in the ruling of two foundational patents by the China National Intellectual Property Administration

US GaN company Efficient Power Conversion Corp (EPC) has announced that the China National Intellectual Property Administration (CNIPA) has validated the claims of an EPC patent titled Compensated gate MOSFET and method for fabricating the same (Chinese Patent No. ZL201080015425.X) for enhancement-mode GaN semiconductor devices.

The decision on April 30, 2024 follows an April 2, 2024 announcement from the CNIPA that confirmed the validity of key claims of EPC's Chinese patent titled *Enhancement mode GaN HEMT device and method for fabricating the same* (Chinese Patent No. ZL201080015388.2).

Both EPC patents were challenged by the Chinese company Innoscience.

Chinese Patent No. ZL201080015425.X covers the fundamental design and configuration of EPC's proprietary enhancement-mode GaN FETs with reduced gate leakage.

Most industry participants employ the GaN gate technology covered by this patent.

"These are two of the foundational patents supporting our broad portfolio of innovations, and we are pleased that the CNIPA has again confirmed the validity of our valuable intellectual property," said Alex Lidow, CEO and co-founder of EPC. "Quick, fair and efficient decisions such as these reinforce the confidence in legal systems that companies need to operate globally."

In May 2023, EPC filed complaints in the US federal court in Los Angeles and in the US International Trade Commission, asserting that Innoscience and its affiliates infringe patents of its foundational patent portfolio, which include the US counterparts of EPC's Chinese Patent Nos. ZL201080015425.X and ZL201080015388.2. In response, Innoscience had petitioned the CNIPA to invalidate the two Chinese patents.

#### Toyoda Gosei develops high output UVC LEDs

TOYODA GOSEI has used its expertise in crystallisation and design of blue LEDs for lighting to develop UVC LEDs with a light output of 200 mW from a single chip driven by 350 mA.

Toyoda Gosei says these performance figures mean the LEDs can be used as a future alternative to mercury lamps.

By improving the LED structure and composition, the company says it has quadrupled the amount of light that can be extracted. Disinfecting capability is said to be about three times higher than previously available UVC LEDs.

## **Advanced Compound Semiconductor**Foundry Services

MOCVD · Fabrication · Testing

Advanced III-V semiconductor solutions for optoelectronics application in the biotechnology, telecommunications, energy, industrial, and security industries.

MasimoSemiconductor.com | 603-595-8900

### Infineon SiC modules to power Xiaomi EV

SiC power modules and bare die products will be used in new SU7 until 2027

INFINEON will provide SiC power modules HybridPACK Drive G2 CoolSiC and bare die products to Xiaomi EV for its recently announced SU7 until 2027.

Infineon will provide two HybridPACK Drive G2 CoolSiC 1200 V modules for the Xiaomi SU7 Max. In addition, Infineon is also supplying Xiaomi EV with a broad range of other products per car, including EiceDRIVER gate drivers and more than ten microcontrollers in various applications.

The two companies have also agreed to further cooperate on SiC automotive applications using Infineon's SiC portfolio.

Zhenyu Huang, VP of Xiaomi EV and general manager of the supply chain department, said: "Infineon is an important partner with leading technologies and resilient manufacturing capabilities in power semiconductors as well as a highly scalable microcontroller product portfolio. The cooperation

between the two companies will not only help stabilise the supply of SiC for Xiaomi EV, but also help us build a highperformance, safe and reliable luxury car with leading-edge features for our customers."

Peter Schiefer, president of Infineon's automotive division, said: "We are very pleased to work with dynamic players such as Xiaomi EV and provide them with SiC products designed to enhance the performance of electric cars even further. As the leading partner to

the automotive industry, we are well positioned with our broad product portfolio, system understanding and multi-site manufacturing base to shape the mobility of the future."

According to the latest data from TechInsights, Infineon is the largest semiconductor supplier to the automotive industry. In addition to its number one position in automotive power semiconductors, Infineon also took the lead in the field of automotive microcontrollers last year.

#### UK's CSConnected appoints new managing director

HOWARD RUPPRECHT will take over as managing director of CSconnected with effect from 1 June 2024. Rupprecht will take over from Chris Meadows who has led CSconnected Ltd since its formation in 2017.

Meadows will continue to support a number of committed activities during the remainder of the year and will remain on the CSconnected board as a non-executive director.

Rupprecht has been working as a director of CSconnected since January; he brings a wealth of semiconductor industry and business development experience from both the public and private sectors.

Rupprecht said: "I would like to thank Chris for his relentless efforts in developing CSconnected and ultimately building a strong and highly recognised global brand for the Welsh Compound Semiconductor Cluster. It's good to be building on such a solid foundation as the team introduces new initiatives to support future cluster growth".

Wyn Meredith, chair of CSconnected,

commented: "We are entering a new phase of expansion of the South Wales Semiconductor Cluster driven by the rapid growth of our industrial partners and a global semiconductor industry forecast to surpass \$1 trillion per annum by 2030."

Meredith added: "Howard's appointment heralds an expansion of the CSconnected team to support the Welsh position in UK semiconductor initiatives such as the £160 million South Wales Investment Zone, and the £1 billion UK Semiconductor strategy."

CSconnected represents organisations

who are directly associated with research, development, innovation and manufacturing of compound semiconductor related technologies as well as organisations along the supply chains whose products and services are enabled by compound semiconductors.

## SEMILAB Metrology Solutions for Wide Bandgap Materials Characterization

## EIR-2300

SiC, EPI thickness measurement

Reflection measurement

SiC buffer layer

Higher dopant concentration SiC

Implanted SiC characterization

## **SEMILAB**

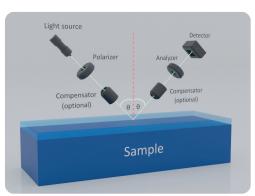

#### **Microspot Spectroscopic Ellipsometry**

Thin film thickness and surface characterization

Al content measurement for GaN HEMTs Layer thickness and homogeneity Dielectric characterization Bow/warp monitoring

#### **Photomodulated** Reflectometry

Pre-anneal implantation characterization Ion implantation dose monitoring Ion implant tilt angle monitoring Implant temperature monitoring

#### NEWS ANALYSIS | CS INTERNATIONAL

### CS International champions a green agenda

Compound semiconductors are the driving force behind the more efficient use of electricity, reduced energy consumption for battery manufacture, and photovoltaic systems with integrated energy storage

#### BY RICHARD STEVENSON, EDITOR, CS MAGAZINE

TACKLING CLIMATE CHANGE understandably gets less media attention these days, with the focus shifting to the coverage horrendous conflicts around the globe. But the need to cut carbon footprints and get a grip on global warming is still of vital importance – and got the justifiable prominence it deserves at this year's CS International.

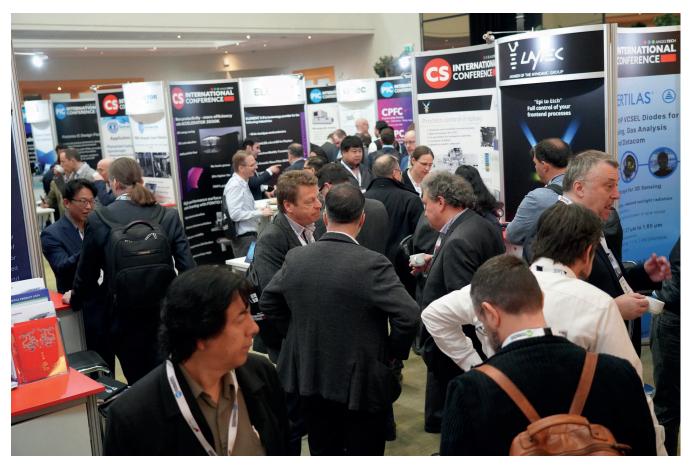

At this conference, held in Brussels on 16 and 17 April, many speakers detailed efforts to streamline the production and increase the volume of energy-efficient wide bandgap devices, while others outlined how optoelectronic devices can play their part in tackling climate change.

Significant progress in cutting emissions can come from increasing the electrification of our world, greater adoption of renewable forms of generation, and improving electrical efficiency. Around half of the world's electrical energy is used to drive motors, a proportion that's only going to increase.

Here there is a tremendous opportunity to boost efficiency, according to the International Energy Authority: this body claims that if energy is used more effectively in motors, around 25 percent of global electricity use could be saved, a goal that would be helped through increased adoption of devices with a wider bandgap.

#### NEWS ANALYSIS | CS INTERNATIONAL

> Delegates at Angeltech, which includes CS International, Power Electronics International and Photonics Integrated Circuits (PIC) International, benefitted from discussions in the exhibition hall, packed with around 80 sponsors.

Assisting in this endeavour is the ramp in worldwide production of SiC and GaN power devices, a trend that will continue, thanks to efforts by many manufacturers to increase their capacity. These chipmakers include STMicrolectronics, which has plans for expansion that were outlined at CS International by Mario Saggio, Company Fellow and R&D Design Director.

Saggio extolled the "outstanding characteristics" of SiC, arguing that while this class of device costs more than silicon rivals, it still delivers savings at the application level.

ST is a well-established player in the SiC industry. It started investing in SiC more than 25 years ago, and last year sales of its SiC devices generated \$1.14 billion. The company dominates the SiC MOSFET market, with a share of more than 50 percent, according to Saggio.

This global player in the power industry has an incredible degree of vertical integration, stretching from raw materials to the design and manufacture of SiC products. It has a SiC substrate plant in Norrköping, Sweden, which manufactures 150 mm substrates and produces 200 mm variants with industrial quality and yield; and a new integrated plant in Catania, Italy, producing devices from 150 mm substrates. In Catania, pilot production started this year, and big plans for this plant include volume production in 2024, the migration to manufacture on 200 mm wafers, and the addition of 700 staff.

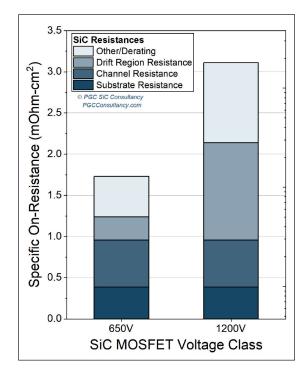

ST continues to evolve its SiC planar MOSFET technology. Second-generation devices were launched in 2017, followed by third and fourth generations that have benefitted from a reduced JFET and improved epitaxy, followed by an optimised edge alongside additional improvements to epitaxy. ST's fifth generation of SiC MOSFET, now in development, will benefit from reduced contact dimensions.

Comparing the second generation of MOSFET to that in development, specific on-resistance for the 650 V and 1200 V variants are lower by almost 40 percent and 50 percent, respectively. Additional improvements, supporting further energy savings, may come from the introduction of a superjunction design, which Saggio said is under consideration. Another company with big plans for SiC is Sanan Semiconductor, which is better known as the biggest producer of LED chips and epitaxial wafers in China.

Speaking on behalf of this company, Ajay Poonjal Pai, Director of Wide Bandag Innovation and Applications Engineering, told delegates that Sanan started developing SiC technology in 2014,

and has become China's first vertically integrated manufacturer of these devices. The company has control of the complete supply chain, from SiC crystal growth to the packaging of power devices.

Backed by \$2.3 billion of investment, Sanan is building what Pai describes as a state-of-the-art mega-fab. It's first phase is now complete, enabling a ramp in production to 200,000 wafers per year. Following further work, capacity is expected to increase to 500,000 wafers per annum. Current production is on 150 mm SiC, but the company will switch to 200 mm wafers by the end of this year.

Sanan entered the SiC power device market with the diode, and shipped more than 100 million in 2022. Based on its third generation of diode, the company has recently released a fourth generation that majors on a low forward voltage, and a fifth that boasts high surge-current capability.

Later this year Sanan will launch its first range of SiC MOSFETs. This automotive-qualified product portfolio will offer blocking voltages of 650 V, 1200 V and 1700 V.

Another champion of SiC is Wolfspeed. Speaking on its behalf at CS International, Pranjal Srivastava, who is responsible for strategic business development at the global level, detailed benefits realised by using SiC devices, rather than those made from silicon, in 25 kW three-phase motor drives.

This opportunity, which offers "immense market potential", can trim losses by up to 50 percent.

To arrive at that figure, Srivastava and colleagues compared the efficiency of power-factor-correction units with a silicon IGBT design, operating at 20 kHz and having a power density of 3.5 kW/litre, with a design using SiC MOSFETs operating at 45 kHz and providing a power density of more than 4.6 kW/litre. The unit using devices with a wider bandgap enables an increase in peak efficiency from 97.2 percent to

> Over the 16 and 17 April, delegates at CS International could hear from more than 40 presenters, covering a wide variety of topics within the compound semiconductor industry.

#### NEWS ANALYSIS I CS INTERNATIONAL

98.5 percent. In addition, the team have considered gains in the performance of an inverter, with SiC providing a 1.1 percent improvement in efficiency.

Taken together, the efficiency gains total 2.4 percent, equating to 600 watts. Srivastava has calculated that this enables a financial saving of more than €7,000, based on today's electricity costs in Germany and assuming that this motor runs almost continuously for 15 years.

#### Galloping GaN

While SiC attracted the greatest coverage at CS International, it could be argued that GaN offers at least as much promise in the long term.

> CS International is co-located with Power Electronics International and Photonics Integrated Circuits (PIC) International a trio that proceeds the Executive Summit.

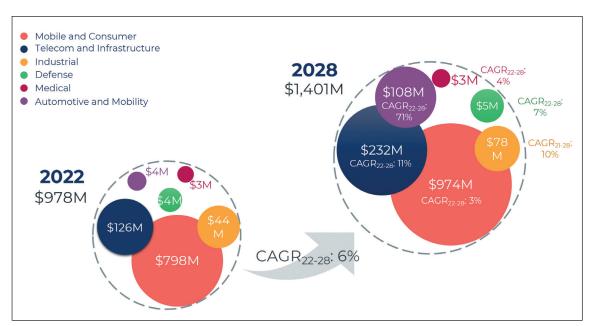

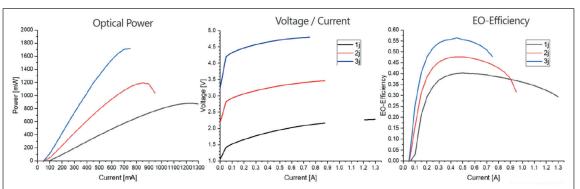

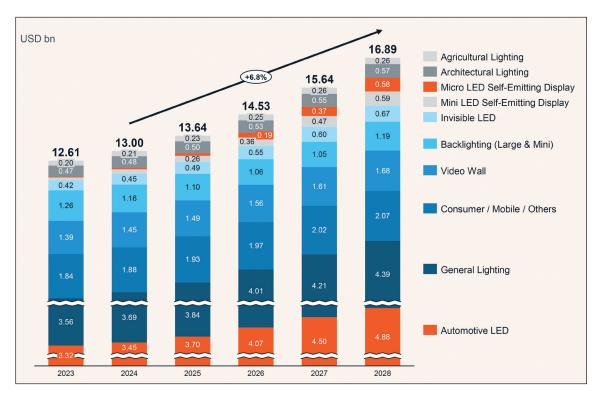

Covering both technologies is market analyst Richard Eden from Omdia. He explained that his forecasts for the GaN market are getting more and more positive. Back in 2020, he forecast this market to be worth about \$1.5 billion by 2029 - and in 2021 and 2023, he revised this figure to just over \$2 billion and then just over \$3 billion.

What applications will account for all these sales by the end of this decade? Eden expects deployment to be broad, seeing opportunities in power supplies, electric vehicles, and a number of industrial applications. Offering detail, he suggested that GaN will win sales in telecom power supplies, such as those used for cell phones and cellular base stations, as well as power supplies used in TVs, consumer audio, data centres and Al servers. In the electric vehicle sector, Eden has identified opportunity in niche powertrains, such as those involving 96 V batteries and 48 V mild hybrid vehicles, as well as on-board chargers. GaN may also find deployment in motor drives for the likes of delivery drones, robotic lawn mowers and vacuum cleaners, as well as power tools and precision motors for surgical robots.

The phenomenal growth of GaN, now tipped by Eden to climb to more than \$6 billion in 2032

from this year's base of below \$1 billion, may be even faster if QPT impacts the market. Its CEO, Rupert Baines, argued that his company is offering revolutionary technology that will stop GaN being limited to low powers and soft switching. Pointing out that faster switching saves more energy, he championed a future that combines kilowatt powers with gigahertz switching frequencies.

Baines believes that QPT's technology can deliver energy savings for motors of at least 5 percent. This translates to a cut in global CO<sub>2</sub> emissions by 400 million tonnes per year and a trimming of electricity bills by \$66 billion per annum.

#### Optoelectronic opportunities

Two of the consequences of greater electrification are an increase in the demand for batteries, and the need to supply more electrical energy when it is needed. Compound semiconductors have a role to play on both fronts, with opportunities outlined at CS International.

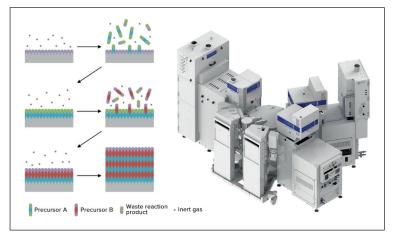

Battery production is an energy-intensive process, with 47 percent associated with the drying of a thick, wet, lithium-containing slurry that's applied to a metal foil. The incumbent approach for drying this slurry involves convection, in ovens 60 m long.

One promising alternative, described by the CTO of Trumpf Photonics, Roman Koerner, is to turn to vast arrays of VCSELs. He explained that this could reduce the heating system for battery manufacture to just 10 m in length, while improving efficiency (for more details, see "New Vectors for the VCSEL", p. 28.)

For the generation of renewable energy, concentrated photovoltaics has much promise. Tremendous falls in the price of silicon panels around the time of the global credit crunch thwarted the success of the first generation of pioneers, but now more than a decade on, this technology is seeing a resurgence, thanks to important innovation by RayGen of Australia. Detailing its novel approach to CPV, Kira Rundel, Head of Strategic Projects, explained that the key to success is supplying energy when it's needed, rather than just when the sun is shining. That's realised by combining electricity generation with thermal energy, with the later coming from the cell's cooling water that's used to heat a thermal store. This store can then generate electricity when it's needed, via a turbine. A 4 MW plant has now been built with this technology, and bigger projects are in the pipeline.

While the likes of RayGen, Trumpf and the producers of wide bandgap power devices will gain the plaudits for enabling compound semiconductor devices to green our planet, they need the support of strong supply chains. Such companies also featured at CS International, with manufacturers of epitaxial growth and metrology systems updating delegates via conference presentations and discussions in the exhibition hall, acommodating around 80 sponsors.

Solutions for Compound semiconductor epitaxy

In situ real time curvature

RIBER EZ-CURVE®

Tool for process monitoring: yield enhancer

- In situ measurements of bow, stress and curvature

- Real time detection of growth events

- Comparison with reference curvė

RIBER

INNOVATIVE SOLUTIONS FOR SEMICONDUCTOR INDUSTRY

#### NEWS ANALYSIS | POWER ELECTRONICS

### A wise investment in the GaN IC

French start-up Wise-Integration has raised an additional €15 million to expand its commercialisation of the GaN IC

#### BY RICHARD SATEVENSON, EDITOR, CS MAGAZINE

OVER THE LAST FEW YEARS, GaN has become more familiar with the general public than ever, thanks to its success in fast chargers for mobile devices. Products on sale trumpeting the use of this wide bandgap material are widely promoted, such as the Anker 120 W GaN Charger and the Wavlink 100 W GaN Charger. There is no doubt that the fastcharging market has been great for growing sales of GaN devices, but commoditisation has now kicked in, creating a need for diversification.

To open up new opportunities for the GaN transistor, its producers need to increase its powerhandling capability, a move that would enable the introduction of this material in power supplies in telecom, industrial and electric vehicle markets. Another strategy is to enhance the functionality of GaN - gains on this front will also drive its deployment, and help it displace the incumbent, silicon.

One company that's simultaneously pursuing both these opportunities - higher powers and greater functionality - is Wise-Integration, the fabless spin-off of CEA-Leti. An initial funding round of €2.5 million led to the development and commercialisation of two product families: a GaN IC; and a silicon-based control chip, which can drive GaN with digital signals. And this February Wise-Integration raised an additional €15 million to expand its commercial activities.

"We are now moving to market, and we need to push the technology to customers," claims company CEO Thierry Bouchet, who says that while the level of recent investment may not be that high by US standards, it is significant, and will fund Wise-Integration until the middle of 2026.

One of the company's primary objectives is to win sales for its digital control technology, a goal that

#### NEWS ANALYSIS | POWER ELECTRONICS

will be targeted by supporting customers with application engineers. The French start-up has developed embedded software that's implemented on standard microcontrollers, and it aims to use this to promote digital control of GaN devices in the power supply market.

"It's a differentiation versus the competition," argues Bouchet. "We are not only providing GaN – we also leverage all the GaN performance with digital control."

The company's other big plan is to drive its technology into higher-power applications.

"Today we target consumer, low-power applications," says Bouchet. "We need to move now to industrial, server, telecom and also automotive products."

While GaN ICs are not as mature as their discrete cousins, they are on the market, with suppliers limited to not just Wise-Integration. There is also Navitas, the first company to introduce the GaN IC, in the form of a charger for the smartphone. For all, the challenge is to now produce successful products providing far higher powers.

What distinguishes Wise-Integration from its competitors is its approach to integration. "We focus on the digitalization," remarks Bouchet, pointing out that rivals drive GaN with analogue signals.

Benefits of a digital drive include the opportunity to turn to very high frequencies, and to produce incredibly thin power supplies with a low bill of materials.

"A key targeted market for us is the power supply for monitors and TVs," says Bouchet. "You have a very small, very thin display, and all the OEMs are looking to introduce power supplies inside the panel, so they need to have a very thin power supply. Our technology allows this requirement, thanks to digital."

Wise-Integration has produced a demonstration board for a 300 watt TV power supply that involves switching GaN at 1 MHz. Such high frequencies threaten to produce electromagnetic interference and noise, potential problems that have already been addressed.

#### Supply chains

To produce its products, Wise-Integration partners with TSMC, one of the first open foundries for GaN technology. TSMC's expertise includes the epitaxial process, allowing fabless firms to use a relatively short supply chain. For Wise-Integration, alongside TSMC it uses AEC for packing and testing and Alter, a French firm, for device qualification.

Bouchet and colleagues are now trying to secure a second source for chip production, to increase

While GaN ICs are not as mature as their discrete cousins, they are on the market, with suppliers limited to not just Wise-Integration. There is also Navitas, the first company to introduce the GaN IC, in the form of a charger for the smartphone. For all, the challenge is to now produce successful products providing far higher powers

the robustness of their supply chain. This would allow Wise-Integration to cater for all eventualities, including unforeseen production problems at TSMC, or a decision by this giant to devote its capacity to other companies.

"The second source could be far closer to home, with options including a European GaN foundry," says Bouchet.

While working on that, Wise-Integration plans to ship a million GaN devices this year, and then a million digital controls. These products will be offered as bundles, which will accelerate sales, by enabling the company's digital controller to be sold alongside up to four of its GaN ICs.

The company clearly has many exciting plans for the next year or so that could open the door to a new era for GaN power devices.

> Thierry Bouchet. CEO and co-founder of Wise-Integration, previously led Adis Innovation, a manufacturer of highperformance discrete and integrated power devices.

#### Overhauling engineering education

To ensure the future of compound semiconductor innovation, a new approach is needed to engineering education and talent development

#### BY RODNEY PELZEL FROM IQE

MUCH HAS BEEN WRITTEN about compound semiconductor innovation and the vital role it plays in shaping the devices that underpin modern life. However, there is little substantive information on the most critical component of this innovation - technical people who are also adept at critical thinking. Few would deny that the single most important factor for successful innovation is maintaining a world-class talent pipeline that fosters teamwork while supporting diversity, equity and inclusion.

During my career in compound semiconductor technology, which spans more than 20 years, I have been responsible for hiring and managing all levels of operational and technical staff, from operators to Ph.D. engineers and scientists. This experience has imparted within me a universal truth that may surprise you - it's not possible to rely upon a person's educational background to predict their technical proficiency and their effectiveness. These findings have led me to conclude that the problem does not lie with any individual, but is deeply rooted in the way we train our technical workforce. And the solution? Without doubt, it has to be a radical overhaul of our education system.

All this may sound rather strange, given the success I've enjoyed from following the 'traditional' educational path. I hold a B.S. and Ph.D. (both in chemical engineering) from established, reasonably prestigious universities, a foundation that has served me well in steadily progressing my career as a technologist.

Throughout this time, I have been passionate about progressing technology. Advances on this front depend on people equipped with the right skills, a requirement that can only be ensured through change. So that I avoid any confusion, let me state my position in simple terms: the educational system is too formulaic, and it fails to foster the type of innovative mindset that's required to make a person a top-notch technical thinker. The unfortunate reality is that we are not teaching students how to become effective problem-solvers, or how to think about open-ended situations.

To truly break the above-noted paradigm requires a complete change in how we educate future generations, with a shift in focus from strictly linear to lateral thinking.

Note, though, that I'm not saying that there is no place for fundamental science and engineering education. In fact, the opposite is true. My point is that by teaching fundamentals in isolation, students fail to gain the required proficiency to use

information in real-world situations. This is an issue for all levels of education, from school through to Ph.D. programmes. What's needed is an overhaul in how we teach the fundamentals. The downside of the current approach is that people are leaving formal education ill-prepared to make a true impact in innovation.

Fixing this will require a significant change in our technical education programmes. It is essential that they are revolutionised to incorporate close collaboration between industry and academia.

What I am envisioning is an extreme version of collaborative on-the-job training, with book-learning supporting real problem solving, rather than problem solving following book-learning.

Let me be clear that I am talking about more than internships, or short placements in industry. Rather, I am advocating a radical overhaul to the entire programme, with a shift in focus.

In an extreme scenario, a person might attend Company X University, who has partnered with an academic institution to provide the fundamentals. To be fair, pockets of such programmes already exist. However, they are far from the norm, with formal school education entrenched as the more prestigious/accepted credential.

Shifting the training of engineers along the lines I recommend would have a number of interesting 'side effects'. One is fostering team-work, as the approach I am championing would demand this to ensure that

a member of a team succeeds. Today, teamwork is neither required nor rewarded, and one can obtain an extremely prestigious degree without understanding how to effectively collaborate. Using my own Ph.D. education as a reference, I was rewarded for getting to the answer as quickly as possible on my own – and experience has shown that this is not unique to me.

Another side-effect of my proposal is that it would impact the designation of degrees, causing them to become more 'general'. For example, students would work towards an engineering degree with a focus on semiconductors, rather than an electrical engineering degree. This shift would also alter what is meant by advanced degrees, such as the MS and Ph.D., and their level of applicability to a differently educated workforce.

One great benefit of what I'm suggesting is that it would lead to improvements in diversity, equity and inclusion. This would stem from lowering barriers to entry for the educational system. What's more, it could accommodate those with a different background, or a different style of learning that does not fit well within the current system. Such students may even thrive and flourish in a system rewarding an 'out of the box' approach.

As we seek to push the frontiers of innovation, there is no doubt that we need a different type of technical workforce. Real innovation hinges on collaborative lateral thinking, and the ability to solve ill-defined, open-ended problems. To excel in this regard, there must be significant change in how the technical workforce is trained and educated.

Uncovering the secrets of

SiC epilayers

Comprehensive characterisation of SiC layers is accomplished with an enhanced form of Fourier transform infra-red spectroscopy

#### BY ESZTER ÉVA NAJBAUER FROM SEMILAB

TECHNOLOGY continues to progress, influencing our daily lives and impacting humanity's efforts to preserve our environment. Against this backdrop, one force for good is the electric vehicle (EV), which benefits from modern power devices; these vehicles are six times more energy-efficient than those incorporating a combustion engine. But not all

advancing technologies are good for the ecosystem. The acceleration in the data that is generated online every second contributes significantly to carbon dioxide emissions. Here, power supplies are required to run continuously, while demanding efficient cooling and significant storage space.

At first glance, these two domains – EVs, and the power supplies for maintaining the internet – appear to be disparate. But they share common imperatives, which are the pursuit of a higher efficiency and greater reliability through further improvement to one key component: SiC.

For high-power applications, SiC is superior to silicon on several fronts. Thanks to its high performance-to-size ratio, its greater energy

efficiency, its low switching losses and its long lifetime, systems based on SiC are lighter, charge faster, and have fewer components. All these factors are valued by the EV industry. Additional benefits include high operating frequencies and temperatures, a low thermal expansion and a high thermal conductivity that reduces cooling requirements. These are strengths that deliver a huge advantage when SiC devices are deployed in data centres.

EVs and server parks are just two examples of the many ways in which SiC is making an important contribution to our daily lives. Due to its remarkable properties, there is an ever-growing demand for these compelling devices, which are amplifying waves of continuous technological improvement.

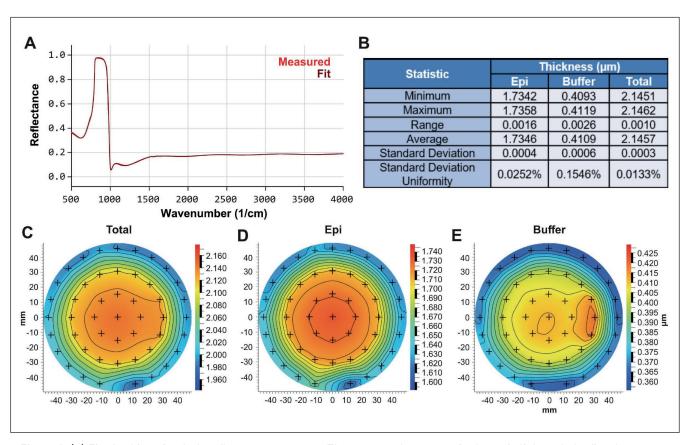

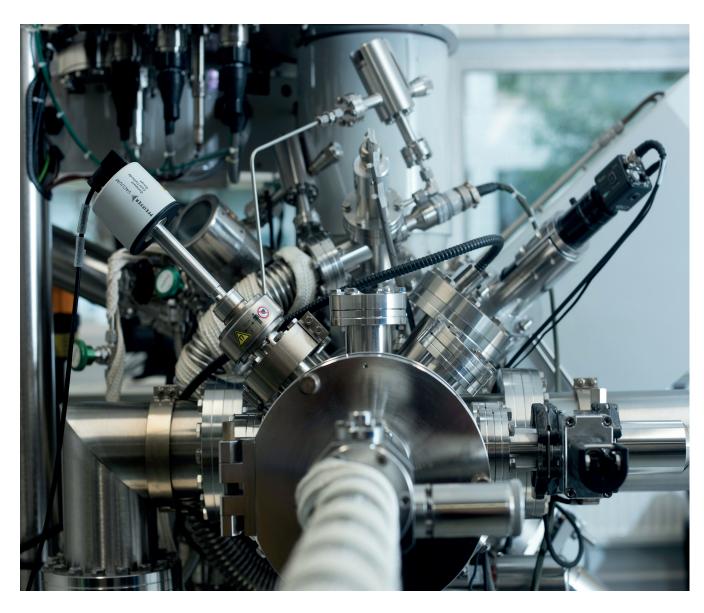

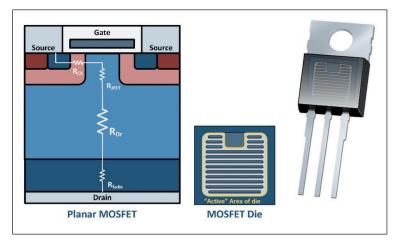

➤ Above: Semilab's EIR-2300 FTIR-based metrology system Price, however, is still a bottleneck in many SiC applications. Based on figures from May 2023, the cost of a single SiC MOSFET inverter is double that of a silicon IGBT with an equivalent performance (that is for transistors capable of withstanding 1200 V and delivering 200 A). Accounting for the lion's share of the cost of the SiC MOSFET is its native substrate, indicating that high value is added early in the process. Due to this, it is vital to closely monitor each step in the process flow while developing highly stable production technologies. It is the norm for substrates to undergo rigorous inspection steps focusing on geometric properties, resistivity, defect assessment, surface roughness, and crystal orientation, and for epi wafers to be monitored for their epilayer thickness, doping concentration, level of defects, degree of surface roughness, and for any presence of contamination.

A critical determinant of performance and functionality is the thickness of the epitaxial layer. This directly governs crucial electrical parameters, such as junction capacitance, and impacts several parameters in the fabrication process, including etch rates. As one of the key roles for the epilayer is to isolate the current-carrying components of the device, even small variations in epilayer thickness can have profound repercussions on the performance of diodes and MOSFETs.

To fulfil the growing demand for SiC power electronics, while executing high yields and retaining competitiveness, manufacturers of these devices are having to address the challenge of migrating from 150 mm to 200 mm wafers while maintaining uniformity in both layer thickness and electrical properties.

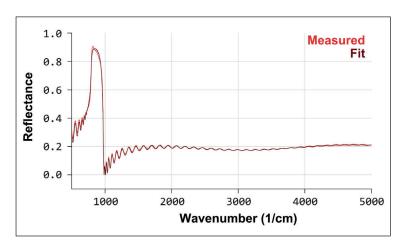

Often optical monitoring techniques are chosen for measuring the thickness of SiC epitaxial layers. They include Fourier-transform infrared (FTIR) reflectometry, a non-destructive technique that provides fast and accurate values for epitaxial thickness from the sub-micron to several-hundred-micron range, while avoiding risks of additional defects and contamination.

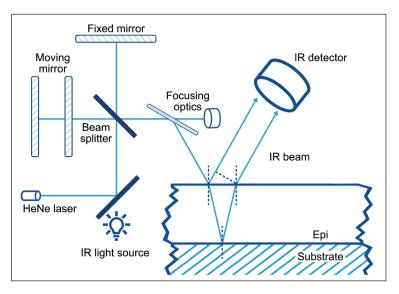

> Figure 1. Measurements with a Michaelson interferometer involve reflection of infra-red light from an epitaxial sample. Infrared light is reflected off the top of the epilayer as well as the interface between two layers (epi-substrate or epi-buffer). Interference of these two rays enables the epitaxial layer thickness to be calculated.

#### Principles of FTIR

FTIR is a non-contact measurement technique that provides the the semiconductor industry with a wealth of information. Its capabilities include industry-standard rapid interferogram measurements of epitaxial thickness, reflectance spectrum measurements for multilayer analysis and dielectric composition measurements, and transmission measurements for absorption peak analysis.

At the heart of every FTIR spectrometer is a Michaelson interferometer (see Figure 1), which consists of a beam splitter and two mirrors: one is moveable and the other static. The position of the moving mirror is changed gradually when measuring a sample. Measurements are made of the light transmitted through and reflected from the sample. Detected signals create interferograms,

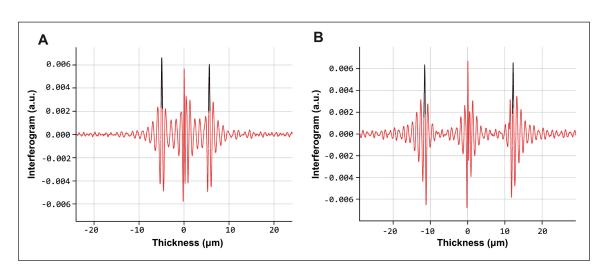

> Figure 2. Interferogram of 5  $\mu$ m (a) and 12  $\mu$ m (b) SiC episamples. Fits of the sideburst maxima are shown in black.

#### COVER STORY | SEMILAB

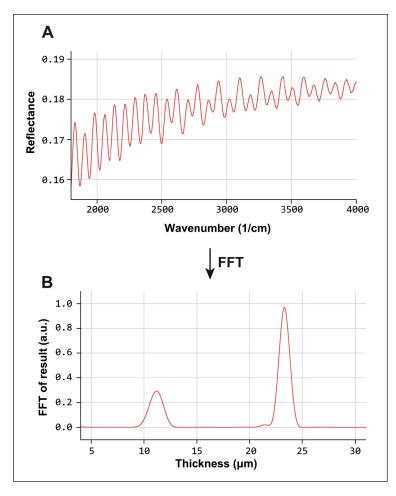

> Figure 3. Baseline fringes in the reflectance spectrum of a SiC epi-sample (top), and the thickness peak obtained by FFT (bottom). Spectra were measured on a regrown epi-sample in collaboration with Fraunhofer IISB, Erlangen. The FFT result shows two peaks: a total thickness peak at around 23 µm, and a peak at the thickness of the top epilayer, at around 11 um. The thickness of the bottom epilayer, around 12 µm, can be obtained as a difference of the two.

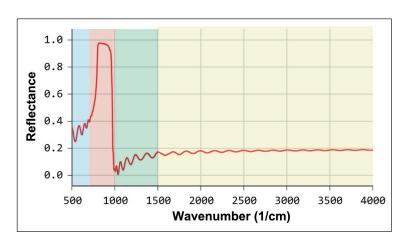

Figure 4. Reflectance spectrum of a SiC epi sample, with the four spectral regions marked with different colours. Blue: 500-700 cm<sup>-1</sup> shows thickness oscillations. This region is most sensitive to the effect of dopant concentration. Red: 700-1000 cm<sup>-1</sup> is the reststrahlen band, a highly absorptive region. Green: 1000-1500 cm<sup>-1</sup> is a transient region between an absorptive and a transparent region. 1500- cm<sup>-1</sup> is a transparent region showing thickness oscillations.

with the intensity of outcoming light a function of the moving mirror's position. For every point in the interferogram, all wavelengths in the spectrum are monitored simultaneously.

#### Metrology methods

Although a typical SiC epitaxial structure consists of only a high-resistivity SiC epilayer and a buffer layer on a low-resistivity substrate, there can still be large variations in layer thickness, dopant concentration, and the number of layers. When analysing any sample, its architecture will influence the most suitable method of analysis, which will also be governed by the most important characteristics to uncover.

At Semilab, we produce FTIR-based Enhanced Infrared (EIR) systems that offer a choice of three different analysis methods. Each has different capabilities and advantages for SiC epitaxial thickness measurements. We now consider, in turn, these three methods: interferogram subtraction, fast Fourier transformation (FFT), and optical modelling.

Interferogram subtraction is a widespread, robust method for determining the thickness of the epilayers. Quick and easy to set up, this approach provides information on a single layer's thickness. Analysis is based on determining the position of the interferogram's secondary maxima, known as sidebursts. These arise when the optical path difference between the interferometer's mirrors matches the path difference of the rays reflected from the top of the epilayer and the epi-substrate interface. The thickness of the epilayer is proportional to the sidebursts' position, and is easy to calculate by taking into account the sideburst position, the incidence angle of the infra-red light, the wavelength of the laser, and the refractive index of the sample.

It should be noted that it is more challenging to analyse interferograms for SiC than silicon. Due to wavelength dispersion in SiC, there are several secondary maxima in the interferogram. So, to ensure reliable analysis, there is a need for postprocessing of the interferograms.

Our software is more than up to this task, providing advanced SiC interferogram analysis features, including filtering, as well as various algorithms for finding and fitting maxima/minima. Depending on the sample structure, our tools for interferogram analysis may also be used to determine the total thickness of the layers for multilayer samples. However, we advise validation of the results by other analysis methods. An example of interferogram analysis of two epi structures to determine the total thickness of the buffer and the epilayer is shown in Figure 2.

More details of the epi structure can be uncovered in reflectance spectra by considering details in characteristic baseline oscillations, also referred

to as fringes, that arise from interference of light reflected from each layer's surface. It is these baseline fringes that 'encode' thickness information in the reflectance spectrum. Thickness values can be extracted from reflectance spectra in a fast and unambiguous manner by undertaking FFT of these fringes. As a result, we obtain the frequencies present in the signal. These can easily be converted into thickness values using the refractive index of the layer in question. For a one-layer epistructure, FFT produces a single peak that reveals the layer thickness, while measurements on multi-layer samples may produce several peaks, including those uncovering the total thickness of the stack.

To illustrate this point, see the FFT analysis of a twolayered regrown epi-sample (see Figure 3). There are two peaks, corresponding to the total thickness and the thickness of the top layer. Subtracting one from the other provides the thickness of the bottom layer.

While FFT is great way to get quick information on epiwafer thickness, using analysis that's easy to undertake, this technique has some limitations. For samples with several layers, the result is ambiguous, in terms of the order of the layers. Another downside is that the baseline curvature in the SiC reflectance spectra causes a strong artefact to appear close to zero thickness that may obscure peak(s) of interest. Due to this issue, FFT analysis has to be restricted to samples with relatively thick epilayers, such as more than 2-3 µm.

Compared with the other two techniques, interferogram subtraction and FFT, optical modelling is the most comprehensive. This approach begins by making assumptions of a structure, using estimated thicknesses and dopant concentrations. From this starting point, a reflectance spectrum is predicted, using physical laws. Depending on the modelling approach, this may involve the use of the Drude dispersion law, employed to model the effect of free-carrier concentration and using Lorentzians to model the background. By changing input parameters, one can fit the predicted spectrum to the measured reflectance spectrum, and extract important information related to the characteristics of the epilayers.

SiC epi (Phase 2) Thickness = 1735.2 nm SiC buffer (Phase 1) Thickness = 412.2 nm

> Figure 5. Structure of a typical SiC epi-sample with a  $0.4 \,\mu m$  buffer layer (phase 1) and a  $1.7 \,\mu m$ epi layer (phase 2).

#### From a seed of an idea to state-ofthe-art metrology solutions

**GLOBAL DIGITALIZATION and** technological transformation are fuelled by the semiconductor industry,

and its evolution and further development is heavily dependent on cutting-edge measurement and testing equipment. A key supplier of these critical metrology tools is Semilab, which continues to invest in research and development.

Founded in 1990 in Budapest, Hungary, by a handful of researchers, Semilab is drawing on more than 30 years of scientific expertise and know-how in electrical and optical measurement methods to create a strong portfolio of industrial metrology systems. These widely used systems, which provide advanced process control, are narrowing the gap between industry requirements and metrology capabilities.

Semilab is pursuing the development of measurement techniques based on a deep understanding of the key processes and requirements for microelectronics production. It is already providing state-of-the-art metrology solutions to leading wafer manufacturers. IC device makers in the more-than-Moore market segment, and solar and display industries worldwide. These instruments are contributing to more efficient production and

At Semilab, key industry needs are met by creating solutions, going from an original idea to a finished product that transforms new ideas into reality. Through an in-depth analysis of the methodology, intricacies of instrumentation, and nuanced data analysis techniques, Semilab works to unveil the transformative potential of this innovative approach within the compound semiconductor landscape. A smarter future beckons, thanks to these initiatives.

There are four distinct regions in the SiC reflectance spectrum, each sensitive to different layers and parameters (see Figure 4). Between 400-700 cm<sup>-1</sup> there are thickness oscillations associated with the epitaxial structure, and this is the region most sensitive to free-carrier absorption. Next to this is a spectral domain known as the reststrahlen region, spanning 700-1000 cm<sup>-1</sup>, where high levels of absorption occur for wide bandgap semiconductors. This part of the SiC reflectance spectrum is most sensitive to the top layer of the sample. Beyond this, from 1000-1500 cm<sup>-1</sup>, is a transient region, positioned between a highly absorptive and a transparent one. In the transparent region above 1500 cm<sup>-1</sup> thickness oscillations dominate the spectrum.

If FTIR measurements are to differentiate between different layers, there has to be sufficient contrast between their optical properties. Often this contrast stems from a difference in doping – according to the Drude model, a layer's absorption coefficient changes linearly with free-carrier concentration.

> Figure 6. (a) Fit of a thin epiwafer's reflectance spectrum. The measured spectrum is shown in light red, the fitted spectrum in dark red. The goodness of fit is R<sup>2</sup>=0.9995. (b) Statistics of a 15-fold centre repeat measurement. Wafer maps with (c) total, (d) epi, and (e) buffer thickness obtained by optical modelling.

However, contrast can also come from partial amorphization of a layer, originating from ion implantation. Depending on the sample's optical characteristics, optical modelling can extract multiple layer thicknesses, such as those of the buffer and multiple epilayers, as well as higher dopant concentrations from the reflectance spectrum.

Another strength of optical modelling is that, unlike the other two methods outlined, this technique can

> Figure 7. Optical modelling of an ion-implanted epiwafer. The thickness of the top layer is 0.6095  $\mu$ m, and the goodness of fit, R<sup>2</sup>, is 0.9969.

accurately measure layers as thin as a few hundred nanometres. Care is needed, however, since in a simultaneous fit of multiple parameters correlation may appear between them, so models must be validated with repeatability and map measurements.

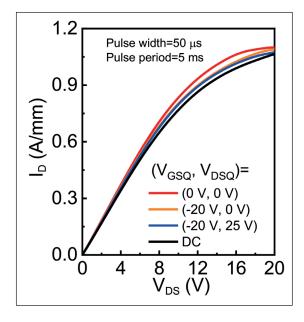

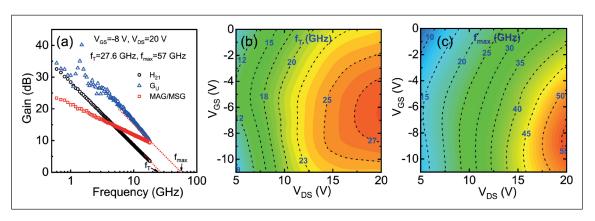

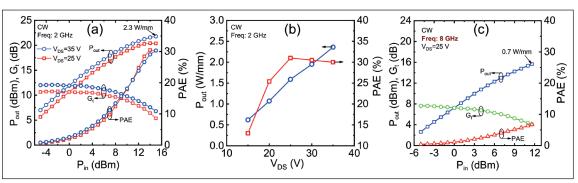

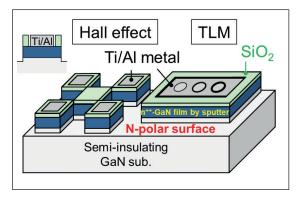

To illustrate the capability of optical modelling, let us take a look at results obtained with a typical SiC epi structure (see Figure 5 for the structure, and Figure 6 for: (a), the reflectance spectrum's fit; (b), the statistics of a centre repeat measurement; and (c), thickness maps). For this thin two-layered sample, optical modelling provides the only way to accurately determine the thickness of both the layers.