# **CONNECTING THE COMPOUND SEMICONDUCTOR COMMUNITY**

## ACCELERATED ALD SEAMLESS PRODUCTION PATHWAY

OXFORD

ENO

VOLUME 30 ISSUE IX 2024

## INSIDE

News, Analysis, Features, Editorial View, Research Review and much more

## Promoting the PCSEL

There is no question that the PCSEL has a wonderful set of attributes. But can it find its killer application?

AN ANGEL BUSINESS COMMUNICATIONS PUBLICATION

## Solar cells: The hunt for 50 percent

Lattice-matched solar cells with five or six junctions look to surpass the conversion efficiency of 50 percent

#### COMPOUNDSEMICONDUCTOR.NET

## Producing vertical GaN power devices

Tuning wafer bow by laser patterning enables the growth of thick epitaxial layers for vertical high-voltage devices

## RIXTRON

# **THE NEW G10 SERIES**

## Your Productivity Solution for All Advanced Epitaxy Materials

## G10-GaN

- 8x150mm (6") or 5x200mm (8")

- 1<sup>st</sup> fully automated compact GaN MOCVD cluster designed 100% for Si Power fabs

- Novel hardware solution for unmatched barrier uniformities and device yields

#### End Markets/Products:

Power Electronics & Wireless communication

*BIXTRON*

## - **G10-SiC**

- > 9x150mm (6") or 6x200mm (8")

- New hardware & process surpassing Single Wafer Reactor uniformities

- +50% productivity per fab area with large batch technology & small footprint

End Markets/Products: EV inverters & charging infrastructure

## G10-AsP

- ▶ 8x150mm (6") or 5x200mm (8")

- 1<sup>st</sup> fully automated AsP MOCVD system enabling 10x lower defect density

- Unmatched wavelength uniformity on all wafer sizes

## End Markets/Products:

Micro LED, Optical Data communication, 3D-sensing & LiDAR

## **VIEWPOINT** By Richard Stevenson, Editor

## Milestones in time and space

There are a number of ways we can measure the growth of our industry. We can consider the annual revenue of all the devices we produce, or their total number, which is phenomenal. Or we could consider how dependent the world is on what we produce, or the number of people that our industry employs.

There are also simpler ways, involving less calculation and rigour, that offer a way to tell compelling stories about our industry's expansion. And while they are a little anecdotal, that doesn't stop them from making the point that the compound semiconductor industry is going from strength to strength.

In this issue you can read about how our industry continues to advance in time and space. There's a piece detailing the history of Riber, now celebrating its 60th anniversary, and another about Agnit Semiconductor, the nascent pioneer of GaN chipmaking in India.

Back in 1964, when four French engineers started Riber, the compound semiconductor industry did not exist. So, it's hardly a surprise that in the very early days, this firm focused on stainless steel fabrication and welding for vacuum applications, before diversifying, initially with Joule-effect evaporators and vacuum chambers. From there, the portfolio expanded to analytical instruments, such as Auger spectroscopes.

The defining moment came ten years after founding, when Klaus Ploog, a legend in MBE, called on Riber to build him a system for the epitaxial growth of films of GaAs. This first system paved the way for many more, first for research communities in academia and industry – still significant markets for Riber – and over the last few decades, for chip manufacturers.

While I'm sure Riber is well-known to you, you may not have heard to Agnit. It's a spin-out of the Indian Institute

of Science, which provides an incubator for producing GaN epiwafers and power and RF devices.

Agnit has just raised \$3.5 million, which will help increase the yield of its die, improve their reliability and enable the company to win qualification in a number of markets.

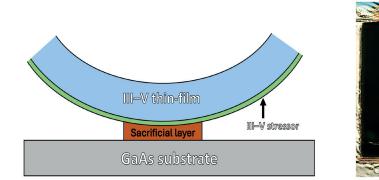

Within the GaN power market, IP is crucial. Agnit is strong on this front, drawing on technology developed by and licensed from the Indian Institute of Science. It also has more than 20 patents, which could prove useful, should the company ever need to defend itself or take action against infringement of its own IP.

In fact, patent filing is another way to track the growth of our industry, reflecting the vast sums that can be made from employing great technology in many devices. They include GaN power and RF chips, as well as various structures made by MBE, where Riber has played a key role for many decades.

Happy anniversary, Riber.

Free weekly e-news roundup go to: compoundsemiconductor.net

## CONTENTS

## VOL. 29 ISSUE IX 2024

## 18 ALD: Speeding the pathway from development to production

Oxford Instrument's suite of ALD tools ensures a reliable process transfer from development to production

## 24 Riber celebrates 60 years of success

With a pedigree in vacuum technology stretching back 60 years, Riber has an enviable track record in MBE innovation that shows no signs of abating

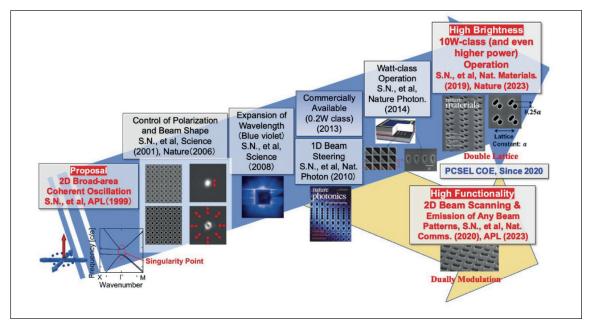

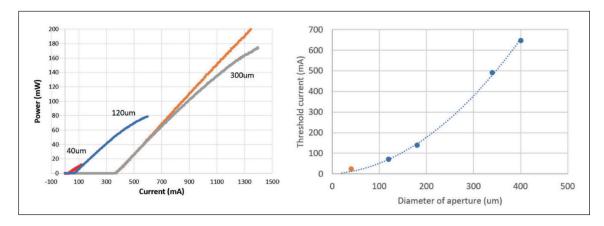

## **30** Promoting the PCSEL

There's no question that the PCSEL has a wonderful set of attributes. But can it find its killer application?

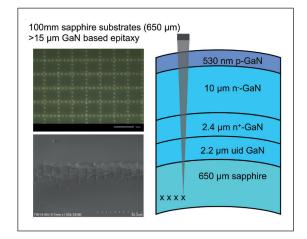

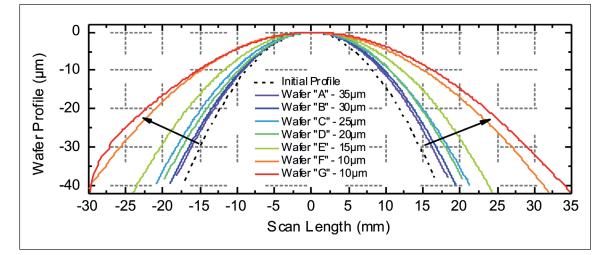

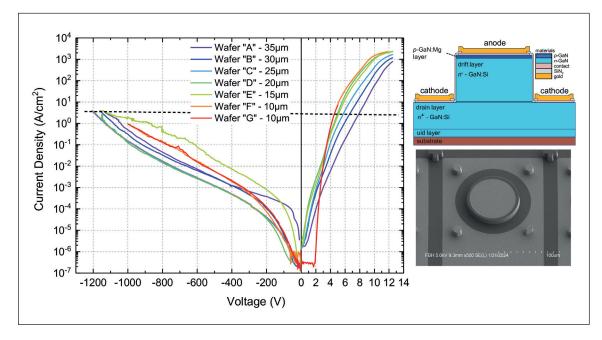

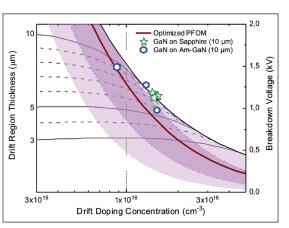

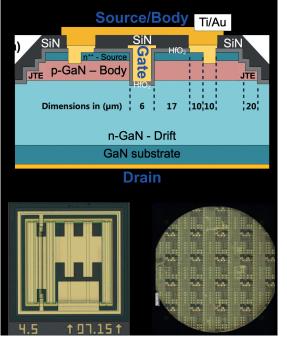

## 36 Producing thick GaN layers on sapphire for vertical power devices

Tuning of wafer bow by stealth laser patterning enables the growth of thick epitaxial layers of GaN on sapphire for vertical high-voltage devices

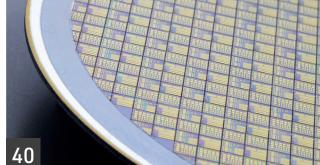

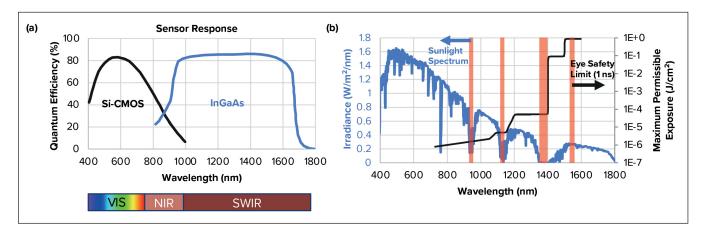

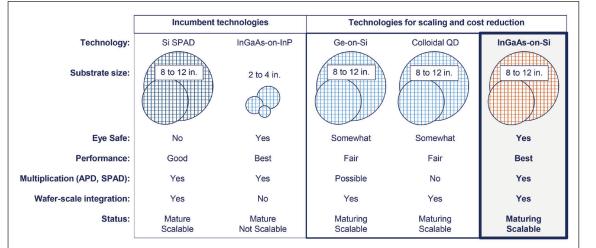

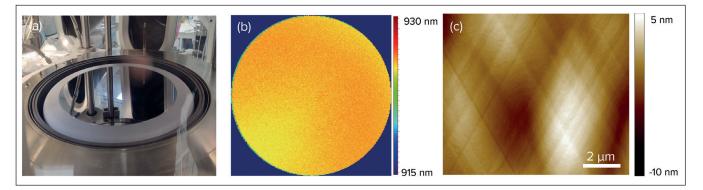

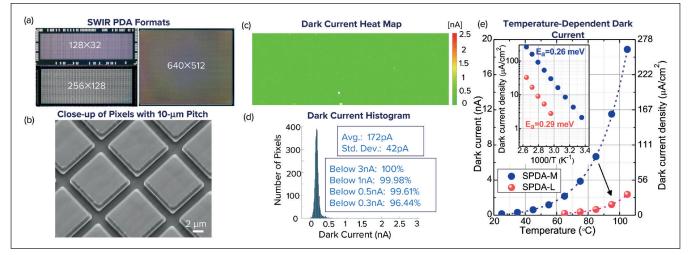

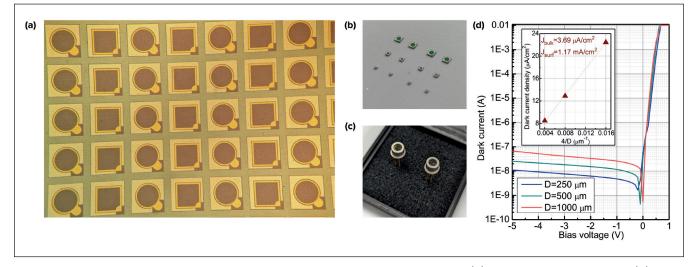

## 40 Realising high-performance sensors with heterogeneous integration

Manufacturing InGaAs photodetectors directly on CMOS silicon revolutionises shortwave infrared sensors for consumer markets

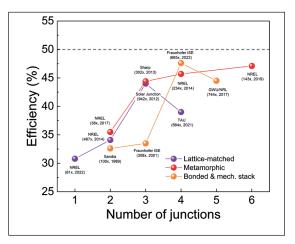

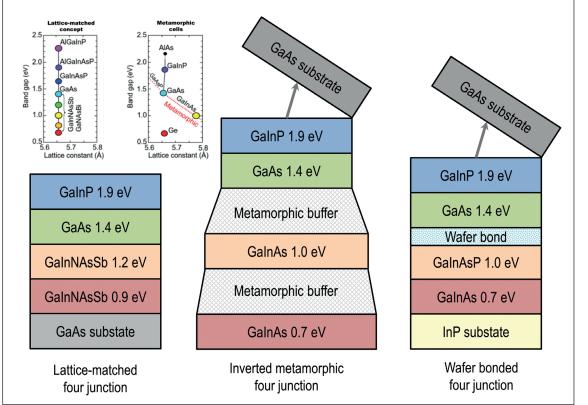

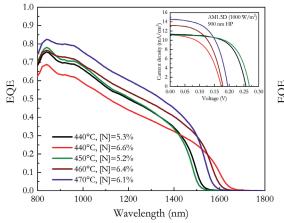

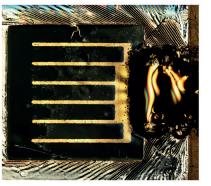

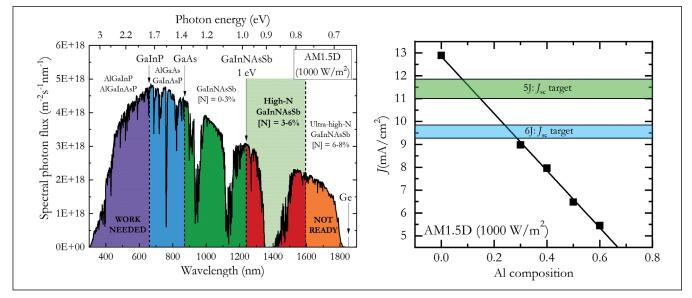

## 46 Multi-junction solar cells: The hunt for 50 percent

Lattice-matched solar cell with five or six junctions look to surpass the landmark conversion efficiency of 50 percent

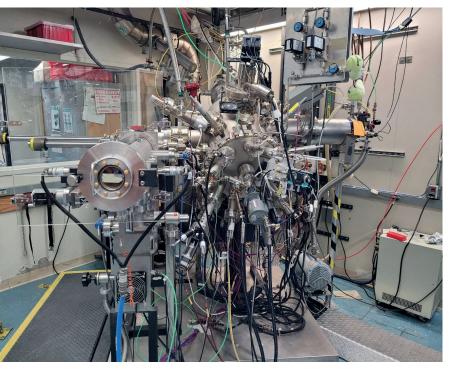

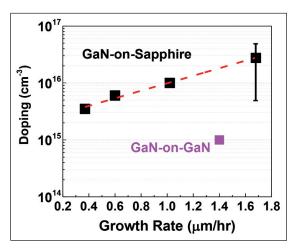

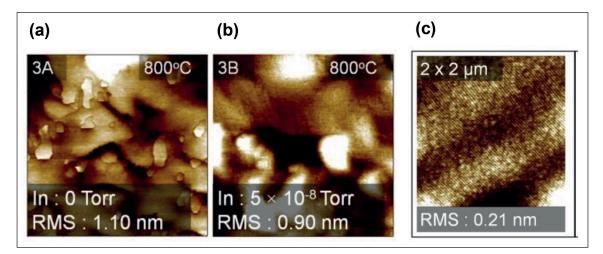

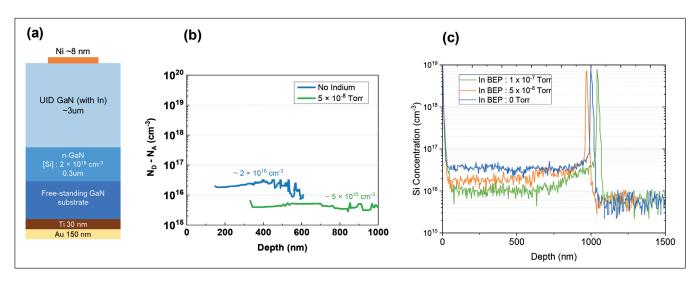

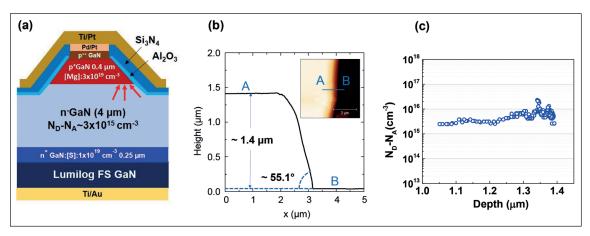

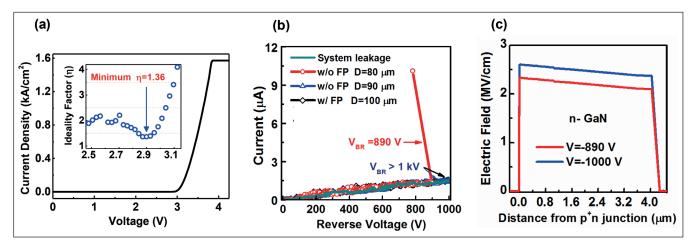

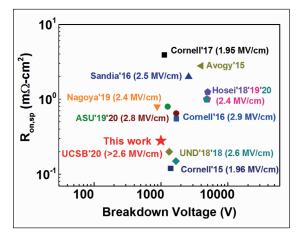

## 54 Advancing GaN power devices with ammonia MBE

Operating in the kilovolt regime, GaN vertical *p-n* high-power diodes produced by ammonia MBE combine a fast growth rate with an ultra-clean thick drift layer and a smooth surface morphology

## **NEWS ANALYSIS**

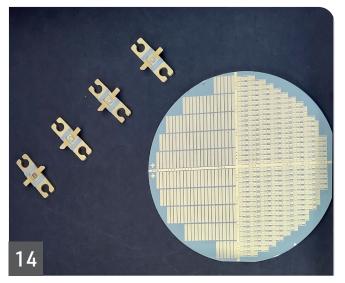

## 14 Putting India on the global GaN stage

University spin-out Agnit has just secured funding to grow its GaN portfolio, a combination of epiwafers and power and RF devices

## 16 MicroLEDs: Eliminating etching

Pyramidal microLEDs on patterned SiC deliver a great performance, even when their dimensions approach the nanoscale

## **RESEARCH REVIEW**

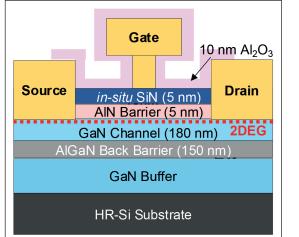

- **59** Double heterostructure HEMTs for handsets

- **60** Turbocharging the GaN trench MOSFET with a  $HfO_2$  gate

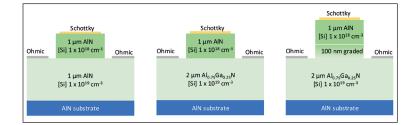

- **61** Transforming the current density of AlN Schottky barrier diodes

## NEWS

- 06 SICC shows first 300 mm SiC wafer

- **07** Samsung to exit LED business

- **08** GaN and SiC 'first' for data centre PSU

- 09 GlobalFoundries confirms \$1.5B CHIPS Act funding

- **10** X-FAB and SMART Photonics partner on micro-printing

- 11 IQE announces departure of CEO

- 12 Smartkem and AUO collaborate on rollable microLED displays

- 13 'All-GO-HEMT' to develop β-gallium oxide heterostructures

Editor Richard Stevenson richardstevenson@angelbc.com +44 (0)1291 629640

News Editor Christine Evans-Pughe christine.evans-pughe@angelbc.com

Design & Production Manager Mitch Gaynor mitch.gaynor@angelbc.com +44 (0)1923 690214 Director of Logistics Sharon Cowley sharon.cowley@angelbc.com +44 (0)1923 690200

Senior Sales Executive Jacob Caulfield jacob.caulfield@angelbc.com +44 (0)2476 718979

Senior Logistics Executive Eve O'Sullivan +44 (0)2476 823 123 eve.osullivan@angelbc.com Circulation Scott Adams scott.adams@angelbc.com

Publisher Jackie Cannon jackie.cannon@angelbc.com +44 (0)1923 690205

Chief Executive Officer Sukhi Bhadal sukhi.bhadal@angelbc.com +44 (0)2476 718970 Chief Technical Officer Scott Adams scott.adams@angelbc.com +44 (0)2476 718970

Directors Jackie Cannon Sharon Cowley Published by

Angel Business Communications Ltd 6 Bow Court, Fletchworth Gate, Burnsall Road, Coventry CV5 6SP, UK. T: +44 (0)2476 718 970 E: info@angelbc.com

Compound Semiconductor is published nine times a year on a controlled circulation basis. Non-qualifying individuals can subscribe at: £115.00 per annum (UK), £165 per annum (Europe), \$198 per annum (air mail) (USA). Cover price £4.50. All information herein is believed to be correct at time of going to press. The publisher does not accept responsibility for any errors and omissions. The views expressed in this publication are not necessarily those of the publisher. Every effort has been made to obtain copyright permission for the material contained in this publication. Angel Business Communications Ltd will be happy to acknowledge any copyright oversights in a subsequent issue of the publication. Angel Business Communications Ltd © Copyright 2024. All rights reserved. Contents may not be reproduced in while he appy to acknowledge any copyright oversights in a subsequent issue of the publication. Angel Business Communications Ltd © Copyright 2024, All rights reserved. Contents may not be reproduced in while he appy to acknowledge any copyright of 6. Bow Court, Fletchworth Gate, Burnasal Rd, Coventry CV5 65P, UK. Alfrieght and mailing in the USA by agent named World Container INC 150-15, 1837d St, Jamaica, NY 11413, USA. Periodicals Postage Paid at Brooklyn, NY 11256, POSTMASTER: Send address changes to Compound Semiconductor, Air Business Ltd, c/0 World Container INC 150-15, 1837d St, Jamaica, NY 11413, USA. We strive for accuracy in all we publish; readers and contributors are encouraged to contact us if they recognise an error or omission. Once a magazine edition is publication about, we do not update previously published articles to align old company names, branding, marketing efforts, taglines, mission statements or other promotional verbiage, images, or logos to newly created or updated names, images, typographic renderings, logos (or similar) when such reference/images were accurately stated, rendered or displayed at the time of the original publication. When companies change their names or the images/ tox

## **INDUSTRY NEWS**

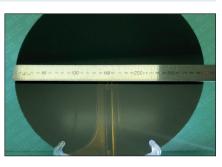

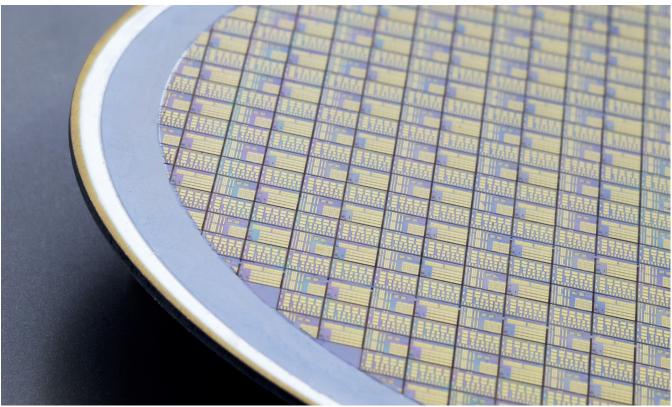

## SICC shows first 300mm SiC wafer

#### Chinese SiC wafer company exhibits first 300 mm n-type SiC substrate at Electronica 2024

AT ELECTRONICA 2024, Chinese SiC wafer company SICC will exhibit what is thought be the first 300 mm *n*-type SiC substrate.

SICC already makes 150 mm and 200 mm *n*-type conductive SiC, and high-purity semi-insulating substrates.

The company has also developed largesize *p*-type SiC substrates.

But the 300 mm *n*-type substrate, it says, is an industry breakthrough that highlights SICC's ability to push the boundaries of semiconductor technology. For example, in its 200 mm conductive 4H-SiC single crystal substrates, SICC says it has achieved near-zero threading screw dislocation and extremely low basal plane dislocation densities, which significantly enhances yields.

For its high-purity semi-insulating SiC substrates, SICC claims zero micro pipe density. (Micro pipes are SiC crystal defects that can cause electronic devices to short circuit and fail).

The company puts its success down to the ability to precisely control the

crystal growth process, ensuring consistent wafer quality .

The company, which has headquarters in Jinan, is currently further expanding its 200 mm SiC wafer manufacturing capacity at its Shanghai plant.

## All change at Wolfspeed as CEO steps down

WOLFSPEED has announced that Gregg Lowe, who has led the company's transition to a pure-play SiC company, will depart this month from his roles as president and CEO and as a member of the board.

In the meantime, Thomas Werner, chairman of the board, has been appointed as executive chairman while the board works to identify Wolfspeed's next CEO.

"On behalf of the full board, I would like to thank Gregg for his service and dedication to Wolfspeed," Werner said. "Since joining the company as CEO in 2017, Gregg has spearheaded our transition into a leading, pure-play SiC company well-positioned to capture the long-term opportunities ahead."

"The board has always been focused on driving long-term value, and at this inflection point in Wolfspeed's journey, the board agreed that this is the right time for a leadership transition."

Werner added: "As we look ahead, we are firmly committed to our key strategic initiatives, which includes executing against the milestones outlined in our recent CHIPS PMT agreement, completing our restructuring initiatives to lower our break-even point and accelerate our path towards profitability, and delivering sales growth on a consistent basis. Wolfspeed is materially undervalued relative to its strategic value and I will focus on driving the company's priorities and working with the finance committee of the board to explore options to unlock value."

Lowe said, "I am honoured to have had the opportunity to lead Wolfspeed and work alongside such talented and dedicated colleagues. Over the past seven years, we have transformed Wolfspeed into the only pure-play and vertically integrated SiC operator in the country to capitalise on the structural and long-term demand for nextgeneration semiconductor technology."

"While there is work still to be done, I have every confidence that Wolfspeed will execute on its strategic priorities and extend its SiC leadership in the years to come."

Werner will oversee the continued execution of Wolfspeed's strategy in close alignment with Wolfspeed's senior leadership team, the board and the board's operations and finance committees. Following Werner's appointment as executive chairman, board member Stacy Smith was appointed as lead independent director.

Werner has been a member of the board since March 2006, and chairman since October 2023. He has served as the executive chairman of SunPower Corporation, a publicly traded solar cells and solar panel company, since February 2024, and as principal executive officer of SunPower from February 2024 until August 2024.

Werner was Sunpower's chairman from June 2010 to November 2021 and its CEO from June 2003 to April 2021. Prior to SunPower, he was CEO of Silicon Light Machines Corporation, an optical solutions subsidiary of Cypress Semiconductor, from July 2001 to June 2003.

Earlier, Werner was VP and general manager of the Business Connectivity Group of 3Com Corporation, a network solutions company.

## Samsung to exit LED business

Korean giant to focus on areas with better growth prospects, including power semis and Micro LED technology, says TrendForce

ACCORDING TO market research firm TrendForce, Samsung Electronics has begun restructuring its business, with the semiconductor division deciding to withdraw from the mainstream LED business, due to the group's performance falling short of expectations.

The division will instead focus on core areas with better growth prospects, including power semiconductors and microLED technology

Samsung Electronics' preliminary unaudited financial results released on 8 October for the third quarter of 2024, showed that the company's profit and revenue for the quarter fell below market expectations. Sales were 79 trillion KRW (around \$57 billion), a 17.2 percent year-on-year increase but lower than the market estimate of 81.57 trillion KRW (\$59 billion). Operating profit was 9.1 trillion KRW (\$6.6 billon), a 274.5 percent year-onyear increase but down 12.8 percent from the previous quarter, and also below analysts' estimate of 11.5 trillion KRW (\$8.3 billion).

At the beginning of 2023, Samsung established a special task force for power semiconductors, and by the end of the year, it further reorganised its operations, transforming the LED division into the Power Semiconductor Division.

In July 2023, Samsung announced that it would launch 8-inch GaN power

semiconductor foundry services by 2025, targeting applications in consumer electronics, data centres, and automotive markets. As part of this plan, Samsung introduced German company Aixtron's MOCVD system into its Giheung 8-inch wafer foundry, during the second quarter of this year.

## Macom gets CHIPS Act funding for GaN-on-SiC project

US SEMICONDUCTOR company Macom Technology has been selected to lead a development project to establish advanced GaN-on-SiC process technologies for RF and microwave applications.

Funded by the CHIPS and Science Act through the United States Department of Defense (DoD), the project will focus on developing semiconductor manufacturing processes for GaN-based materials and MMICs operating efficiently at high voltages and at millimetre-wave frequencies.

Macom is a member of the Commercial Leap-Ahead for Wide Bandgap Semiconductors Microelectronics Commons Hub and will work with North Carolina State University, Adroit Materials and the Naval Research Laboratory on this project.

The year 1 value of this award is \$3.4 million. This award expands

upon a series of GaN technology development activities with the DoD, including a 2021 Cooperative Research and Development Agreement with the United State Air Force Research Laboratory, where Macom successfully transferred AFRL's 0.14 µm GaN-on-SiC MMIC process to its Massachusettsbased US Trusted Foundry.

This was followed in 2023 by a \$4 million AFRL contract to develop

GaN technologies for millimetre-wave applications and a Defense Advanced Research Projects Agency award valued at up to \$10.1 million aimed at improved heat dissipation for high power applications.

Earlier this year, Macom was awarded a separate CHIPS-funded GaN technology development contract worth up to \$11.4 million.

"Our strategy is to increase domestic production of state-of-the-art RF and microwave power technologies to support our military's radar and sensing applications and to enable next generation telecommunications networks," said Stephen Daly, Macom president and CEO.

"We believe the technologies and products developed under these contracts will help keep the United States and Macom on the leading edge."

## **INDUSTRY NEWS**

## GaN and SiC 'first' for data centre PSU

#### Navitas announces 98 percent efficient 8.5 kW AI data centre PSU

NAVITAS SEMICONDUCTOR has announced what it claims is the world's first 8.5 kW power supply unit (PSU), powered by GaN and SiC technologies to achieve 98 percent efficiency, for next-generation AI and hyperscale data centres.

The Al-optimised 54 V output PSU complies with Open Compute Project and Open Rack v3 specifications and uses high-power GaNSafe and Gen-3 Fast SiC MOSFETs configured in 3-phase interleaved PFC and LLC topologies.

The company says that the PSU's shift to a 3-phase topology for both the PFC and LLC (compared with 2-phase topologies used by competing PSUs) enables the industry's lowest ripple current and EMI. Furthermore, the PSU reduces the number of GaN and SiC devices by 25 percent compared with the nearest competing system, which reduces the overall cost.

The PSU has an input voltage range of 180 to 264  $V_{\rm AC}$  a standby output

voltage of 12 V, and an operating temperature range of -5°C to 45°C. Its hold-up time at 8.5 kW is 10 ms, with 20 ms possible through an extender.

The 3-Phase LLC topology is enabled by high-power GaNSafe, which integrates control, drive, sensing, and critical protection features. GaNSafe has short-circuit protection (350 ns maximum latency), 2 kV ESD protection on all pins, elimination of negative gate drive, and programmable slew rate control. All these features are controlled with 4-pins, allowing the package to be treated like a discrete GaN FET, requiring no VCC pin.

The 3-Phase interleaved CCM TP-PFC is powered by Gen-3 Fast SiC MOSFETs with 'trench-assisted planar' technology.

"This complete wide bandgap solution of GaN and SiC enables the continuation of Navitas' AI power roadmap, which enables this 8.5 kW and plans to drive to 12 kW and higher in the near-term", said Gene Sheridan, CEO and co-founder of Navitas. "As many as 95 percent of the world's data centres cannot support the power demands of servers running NVIDIA's latest Blackwell GPUs, highlighting a readiness gap in the ecosystem. This PSU design directly addresses these challenges for AI and hyperscale data centres."

Navitas displated the PSU for the first time at Electronica 2024 (November 12th– 15th).

As many as 95 percent of the world's data centres cannot support the power demands of servers running NVIDIA's latest Blackwell GPUs. This PSU design directly addresses these challenges for AI and hyperscale data centres

## GlobalFoundries confirms \$1.5B CHIPS Act funding

## Funding supports GF's Vermont GaN facility modernisation and New York expansion plans

GLOBALFOUNDRIES and the US Department of Commerce have announced an award of up to \$1.5 billion in direct funding to GF through the CHIPS and Science Act.

The award follows the previously signed preliminary memorandum of terms announced in February 2024 and will enable GF to expand its chip manufacturing and technology development in the US, across a range of end-markets including automotive, smart mobile devices, IoT, data centres, and aerospace and defence.

One of the key project's GF's CHIPS award will support is modernisation of GF's existing fab in Essex Junction, Vermont, to expand production capacity and create one of the world's leading facilities capable of high-volume manufacturing of next-generation GaN semiconductors for use in electric vehicles, data centres, IoT, smartphones and other critical applications.

Money will also go towards expansion of GF's existing Malta, New York, fab by adding technologies already in production at GF's Singapore and Germany facilities, to enable a secure and reliable supply of domestically manufactured essential chips for the US auto industry.

Funding may also go towards the construction of a new state-of-art fab on GF's Malta, New York, campus to meet expected demand for US-made essential chips across a broad range of markets and applications including automotive, AI in the data centre and at the edge, as well as aerospace and defence.

"The idea of strengthening US semiconductor manufacturing has been five-plus years in the making. With bipartisan support, that idea evolved into the CHIPS and Science Act," said Thomas Caulfield, president and CEO of GF. "GF's essential chips are at the core of US economic, supply chain and national security. We greatly appreciate the support and funding from both the US Government and the states of New York and Vermont, which we will use to ensure our customers have the American-made chips they need to succeed and win."

In aggregate, these projects represent more than \$13 billion of investment

over the next 10-plus years across GF's two US sites. This investment includes the \$1.5 billion CHIPS and Science Act award, more than \$550 million in support from the New York State Green CHIPS Program, as well as funding and support from Vermont, GF ecosystem partners and key strategic customers, and other incentives.

Combined, these investments are expected to create close to 1,000 direct manufacturing jobs and more than 9,000 construction jobs over the life of these projects.

GF's fabs in New York and Vermont are both Trusted Foundry accredited and manufacture secure chips in partnership with the US government.

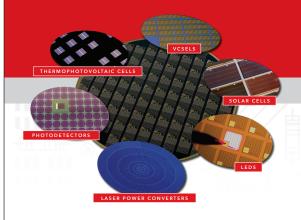

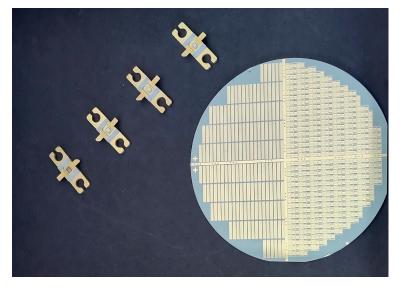

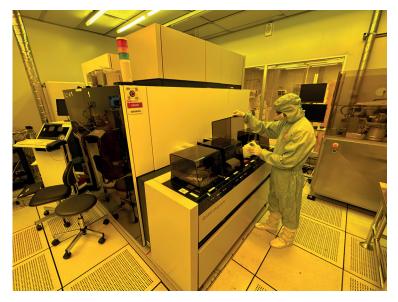

## **Advanced Compound Semiconductor** Foundry Services

MOCVD • Fabrication • Testing

Advanced III-V semiconductor solutions for optoelectronics application in the biotechnology, telecommunications, energy, industrial, and security industries.

MasimoSemiconductor.com | 603-595-8900

## **INDUSTRY NEWS**

# X-FAB and SMART Photonics partner on micro-printing

Companies to use X-Celeprint's micro-transfer printing to build next-generation transceivers with silicon photonics and InP integration

SPECIALIST FOUNDRY X-FAB and InP photonics foundry SMART Photonics have announced a collaboration to integrate X-FAB's silicon photonics platform with SMART Photonics' InP chiplets.

They aim to use use micro-transfer printing (MTP), licensed from X-Celeprint, for heterogeneous integration, enabling new capabilities for datacom and telecom applications.

InP technology supports modulator bandwidths exceeding 120 GHz, making it a good solution for next-generation multi-terabit telecom and datacom standards – pushing transceiver speeds far into the terabit realm. In contrast, silicon photonics technologies hit a performance ceiling at around 70 GHz.

The collaboration aims to deliver scalable, high-volume solutions that combine the best of both technologies.

By co-optimising silicon photonics, InP, and MTP technologies to fulfill customer requirements, the collaboration will enable new

functionalities and improved system performance while reducing integration costs through relaxed photonics packaging requirements.

The MTP technology enables a broad degree of freedom for the system and product designers, by providing flexible integration of various material system chiplets into the product design.

Johan Feenstra, CEO of SMART Photonics, explains: "As the demand for integrated photonics rapidly increases, thanks to the growth of AI and data transfer, our joint solutions will enable much faster data rates while reducing overall power consumption, and therefore the environmental footprint." Rudi De Winter, CEO of X-FAB, adds: "Through heterogeneous integration, we are combining the best of the InP and silicon photonics worlds."

"This will allow our customers to develop innovative solutions addressing the societal challenges of our times such as decarbonization. It is also a great opportunity to build a strong European value chain."

This collaboration builds upon the PhotonixFAB EU funding project, which aims to provide a path to scalable high-volume manufacturing for SOI and SiN silicon photonics, MTP-ready InP chiplets and micro-transfer printing of chiplets.

X-FAB and SMART Photonics recently signed a Memorandum of Understanding to formalise their collaboration.

The aim is to support lead customers with industrial prototyping by 2026, with risk production readiness by 2027.

Early customer engagements can be supported within the ongoing PhotonixFAB project framework.

## India's DRDO announces GaN and SiC milestones

INDIA'S Defence Research and Development Organisation (DRDO) has announced a significant milestone in semiconductor technology by developing indigenous methods for producing 4-inch SiC wafers and fabricating GaN HEMTs up to 150 W.

A statement from the Indian Ministry of Defence said that these advancements, achieved by the DRDO's Solid State Physics Laboratory (SSPL), also include MMICs with power capabilities up to 40 W, suitable for applications extending to X-band frequencies.

The establishment of indigenous GaN-on-SiC-based MMIC production has been successfully implemented at GAETEC (Gallium Arsenide Enabling Technology Centre) in Hyderabad.

These technologies are considered essential for modern combat systems, radar technologies, electronic warfare,

aerospace, satellite communications, and green energy initiatives.

## IQE announces departure of CEO

### Americo Lemos leaves the company, with Jutta Meier taking up the position of interim CEO

IQE PLC, a supplier of compound semiconductor wafer products, has announced that Americo Lemos, CEO, has left the company.

Mark Cubitt, who recently joined the IQE board as chair-elect, will become the executive chair of IQE. He is currently non-executive chair at AIM-Listed Beeks Group and Concurrent Technologies.

Jutta Meier will take up the position of IQE's interim CEO in addition to her CFO role. Meier joined IQE in January 2024 from Intel Corporation.

Phil Smith, who has been chair of IQE since 2019, will step down from his role but remain on the IQE board as a non-executive diirector.

IQE says it will begin the search for a permanent CEO immediately.

Phil Smith, chairman of IQE, said: "Whilst IQE continues to navigate the semiconductor market recovery, we are confident that the company's renowned technical expertise is well aligned to long-term growth market vectors."

He continued: "In Mark and Jutta we have two excellent individuals with the necessary sector and leadership skills to capture that growth in partnership with our customers, employees and broader stakeholders. Their immediate priorities will include a focus on executing on the near-term pipeline as well as cash generation across the group and on unlocking embedded value by pursuing the IPO of our Taiwan business. They will examine other efforts to optimise our asset base and ensure that resources are centred around IQE's strategic areas of expertise."

Following the departure of Lemos, IQE revealed that revenue for the full year 2024 is expected to be broadly flat year-on-year, resulting in around £115 million. In line with the rest of the industry, the company says it is continuing to see a slower than anticipated recovery in key sectors driven by weak consumer demand in end markets. The group expects this to result in an adjusted EBITDA of at least £5 million.

In light of the results, IQE has announced a strategic review.

## Driving tomorrow's technologies

Compound semiconductors provide the key enabling technologies behind many new and emerging applications. CSconnected represents the world's first compound semiconductor community based in and around South Wales in the UK

## cs connected

## **INDUSTRY NEWS**

# Smartkem and AUO collaborate on rollable microLED displays

#### Collaboration marks first microLED display product in development using Smartkem's technology

SMARTKEM, a UK developer of organic thin-film transistors (OTFTs), has partnered with AUO, the largest display manufacturer in Taiwan, to jointly develop the world's first advanced rollable, transparent microLED display.

Smartkem's chairman and CEO Ian Jenk says its technology has the potential to take today's microLED TVs from highend market prices of \$100,000 down to mass market prices.

"Because our transistors are processed at such a low temperature compared to other technologies, we are able to pour them directly on top of the microLEDs, completely eliminating the problematic mass transfer and laser welding processes required with other technologies," explained Jenks.

He adds: "The key feature that enables the development of this microLED display is our unique low-temperature process that allows the use of lowcost, flexible plastic rather than glass. We believe that, if successful, this collaboration will be a significant milestone for Smartkem in its road to commercialisation, and for microLED display product development using our technology."

Wei-Lung Liau, CTO of AUO, commented, "AUO has dedicated years to developing the ultimate microLED display technology, forging alliances with ecosystem partners to enable mass production. In this collaboration, AUO has developed groundbreaking technologies that

boost the high transparency and freeform in applications of microLED. With proprietary materials from Smartkem and the OTFT production process from ITRI, we are collaboratively developing the world's first rollable microLED display for potential commercialisation with cost advantage. We believe this will create new opportunities for the display industry and continue to expand value chain partner cooperation and influence."

Display analyst and DSCC (Display Supply Chain Consultants) CEO, Ross Young, commented, "This is an exciting project that, if successful, will demonstrate the cost effectiveness of Smartkem's technology in the most demanding of microLED applications, and could generate substantial market interest." The project between Smartkem and AUO will commence on January 1, 2025. The collaboration has been awarded a grant from the 2024 Taiwan-UK Research & Development Collaboration, supported by The Taiwanese Ministry of Economic Affairs and Innovate UK, part of UK Research and Innovation.

The 2024 UK-Taiwan Collaborative R&D Initiative has invested more than £10 million this year to promote bilateral industrial technology research and development cooperation.

The nine award-winning projects will promote the joint development of advanced technologies in fields such as electrical information communication, biomedicine, and electromechanical by Taiwan-UK enterprises.

The key feature that enables the development of this microLED display is our unique low temperature process that allows the use of low-cost, flexible plastic rather than glass. We believe that, if successful, this collaboration will be a significant milestone for Smartkem in its road to commercialisation, and for microLED display product development using our technology

# 'All-GO-HEMT' to develop β-gallium oxide heterostructures

#### €2 million German-funded project aims to increase in efficiency in power electronics

A €2 MILLION German-funded project called All-GO-HEMT aims to increase efficiency in power electronics and make a significant contribution to sustainable energy generation.

Led by Andreas Fiedler of the Leibniz-Institut für Kristallzüchtung (IKZ), the project aims to develop modulation-doped  $\beta$ -(Al<sub>x</sub>Ga<sub>1-x</sub>)<sub>2</sub>O<sub>3</sub>/ Ga<sub>2</sub>O<sub>3</sub> heterostructures that exhibit high electron mobility.

Compared to established materials such as silicon, GaN and SiC,  $Ga_2O_3$  offers potential for increasing efficiency that has not yet been fully exploited.

"We believe that the development of more efficient materials can make a significant contribution to the energy transition and enable the industry to successfully master the challenges of the future," explains Fiedler.

Even though power electronics based on  $Ga_2O_3$  promise to be more efficient, the material is inferior to established materials in terms of charge carrier mobility. "Gallium oxide behaves to the established materials in the same way as ten metres of dirt road to one kilometre of freeway. Due to the shorter distance, your car consumes less, and despite the lower speed, you reach your destination faster - all thanks to a more compact design," explains Fiedler.

The central aim of the project is to overcome the material limitation of  $Ga_2O_3$  in terms of charge carrier mobility with the help of the innovative design of an aluminium-alloyed heterostructure and thus eliminate this disadvantage.

Fiedler emphasises: "We are convinced that the efficiency of power electronics can be significantly increased through a combination of a more compact design and higher charge carrier mobility in our newly developed materials."

Another goal of All-GO-HEMT is to create a reliable material basis of  $Ga_2O_3$ and the newly developed alloy with aluminum of the highest crystalline Compared to established materials such as silicon, GaN and SiC, Ga<sub>2</sub>O<sub>3</sub> offers potential for increasing efficiency that has not yet been fully exploited

quality for research and industry. This basis is necessary because the development of high-performance devices with compact design and optimised manufacturing processes is currently limited by the insufficient availability of high-quality material.

The project partner Ferdinand-Braun Institut (FBH) will use this material basis to develop new prototypes for power electronic devices. These prototypes will then be tested by ZF Friedrichshafen AG, the industrial application. In addition, the entire value chain, from crystal growth to the finished device, will be analysed by the industrial mentors Aixtron SE and Siltronic AG in order to quantify and evaluate the economic and ecological benefits of this technology at an early stage.

Enabling Process Control Solutions for Compound Semiconductor Manufacturing

## **CELERO<sup>™</sup> PL** SYSTEM

Onto Innovation combines four-channel defect inspection with photoluminescence, imaging and classification for surface/sub-surface defectivity and contamination inspection across a range of wafer sizes in both R&D and production environments for silicon carbide (SiC) and gallium nitride (GaN) based wafers and compound semiconductor materials.

COMPOUNDSEMICONDUCTOR.NET | ISSUE IX 2024 13

## Putting India on the global GaN stage

University spin-out Agnit has just secured funding to grow its GaN portfolio, a combination of epiwafers and power and RF devices

## BY RICHARD STEVENSON, EDITOR, CS MAGAZINE

THERE ARE a number of ways to measure the growth of an industry.

For GaN electronics, which serves both the power and RF sectors, evidence of its rapid rise is seen in its double-digit rises in revenue, which will swell this market to several billion dollars by the end of this decade. But that's not the only way to track success. The growth of GaN is also seen in the geographical expansion of its chipmakers. As well as big the names in the US, Europe, Japan and China – such as Navitas, EPC, Transphorm, Infineon, Toshiba and Innoscience – smaller players are cropping up all over the world, including in unfamiliar locations, such as India.

Breaking new ground on this sub-continent is Agnit, a spin-out of the Indian Institute of Science that has just raised another US \$3.5 million to advance its GaN portfolio, a mix of epiwafers and power and RF devices.

Company co-founder and CEO, Hareesh Chandrasekar cannot lay claim to Agnit being the sole trailblazer for compound semiconductor manufacturing in India, because it's just possible that there is another maker of such devices hiding from view. But he is adamant that Agnit is the first to use indigenous technology, rather than getting it from somewhere else.

Introducing semiconductor manufacturing in India could be crucial to the growth of this nation's economy, says Chandrasekar. "If India is going to be a 5, 7, \$10 trillion economy in the next decade or so, there's no way this is happening without us having a presence in the electronics manufacturing ecosystem."

While there are a number of options for gaining a foothold in the semiconductor industry, some are more attractive than others, with cutting-edge CMOS having a formidable financial barrier to entry.

"We felt that gallium nitride was a nice sweet spot," says Chandrasekar, who argues that while this technology is not as complex as state-of-the-art CMOS, and doesn't demand fabs with price tags of several billion dollars, it's up and coming, and there is a local pull for products.

#### An academic heritage

Founded in late 2019, but initially impeded by the global pandemic that stalled the start of this company's operations until January 2021, Agnit receives tremendous support from the Indian Institute of Science, in terms of both facilities and expertise.

This institute is a great incubator for Agnit, having constructed a pilot production line for GaN that has a peak capacity of about ten 6-inch wafers per day. Supporting this is a very good characterisation suite.

Another asset of this institute is its extensive development of GaN technology, creating a strong IP base that draws on many, many years of research.

Imparting expertise from the Institute to Agnit is seamless, as four of the seven founders, all still involved, are academics with complementary capabilities related to the fabrication, operation and reliability of GaN devices. The other three co-founders, now the core management team, have PhDs in the field of GaN, but bring a different skillset, partly thanks to time spent working in the semiconductor industry. Strengthening this team are a growing number of employees, now totalling 16.

In terms of the commercialisation of its GaN device portfolio, Agnit has initially focused on the RF, before more recently expanding into the power domain.

## NEWS ANALYSIS | POWER ELECTRONICS

Agnit's RF devices are marketed to the telecom and the strategic sector. Products from rival suppliers are already being deployed in base stations, encouraging the Bangalore start-up to pursue more niche applications associated with 5G networks. "It could be things like private networks," says Chandrasekar.

For the power market, which Chandrasekar describes as "pretty hot now", there are many players with unique business models. To carve out a space in this sector, he and his colleagues are trying to address a particular set of problems associated with the unique, local market. Prototyping is underway.

To support its device development, Agnit is packaging its die in-house. But this will change when it moves into production, with this final manufacturing step outsourced, using the strong local ecosystem.

"We are also exploring global partnerships to see how we can actually leverage the global packaging capacity for the GaN chips that we make," says Chandrasekar.

The third string to Agnit's bow is its supply of GaN epiwafers to chipmakers.

"We had already supplied to academia," says Chandrasekar, adding that the new additional capacity is enabling Agnit to expand its horizons and build foundry relationships for the global supply of GaN-based power and RF epiwafers.

One of the issues hampering the GaN industry for many years is that epi is a "black box," according to Chandrasekar. "When you buy a batch of wafers, you never know if they're the right ones to begin with for your process or not. That has always been a big stumbling block."

Agnit is addressing this concern by offering the capability to adjust the epitaxial process based on internal device feedback. This helps customers target particular performance specifications.

#### Patents and IP

Agnit has a strong IP portfolio, supported by technology developed from the Indian Institute of Science, which it licences exclusively. The start-up has more than 20 patents, of which 15 or so are global patents.

Like the leaders of many foundries, those calling the shots at Agnit have thought very carefully about what IP requires patenting, and what is best left undisclosed. Such decisions are guided by whether patents have the potential to expose and demonstrate infringement. "If you can't do that, then it makes very little sense to patent your IP," argues Chandrasekar.

Highlighting the need for defendable IP are the patent battles being fought between Innoscience and EPC and Infineon. While such skirmishes may

alarm some chipmakers within the GaN industry, they are not a major concern to those leading Agnit. "Everything that we commercialise has our own patents as a backing, or our trade secrets and knowhow as a backing," says Chandrasekar. "We are quite careful about that."

#### Investing in its future

The US\$3.5 million raised this Autumn came from a seed round led by 3one4 Capital and Zephyr Peacock.

This investment will help to increase production yields for 4-inch GaN-on-SiC epiwafers for RF devices, and for 6-inch GaN-on-silicon wafers for the power sector.

In addition, the funding will be used improve device reliability, an issue that Agnit takes very seriously. "This will help our devices be qualified for various reliability standards that we are targeting based on the markets that we choose to go after," remarks Chandrasekar.

As well as advancing yield and reliability, the seed funding will support prototype development – in particular, power devices for the domestic market, as well as RF devices for the telecom sector.

Two big goals for the next 12 months are to get RF products in the market, in both the telecom and strategic sectors, and to grow the epiwafer supply business, supporting these customers with device data.

"In 24 months, we'll also have the first alpha samples available on the power devices that we're working on, which will be sampled to customers for integration into their systems," adds Chandrasekar.

The CEO expects the majority of its sales over the next few years to come from domestic markets, but 30 percent will be overseas. If such success follows, that will surely help to grow the role of India on the global GaN stage. > Agnit produces GaN power and RF devices at the incubator at the Indian Institute of Science.

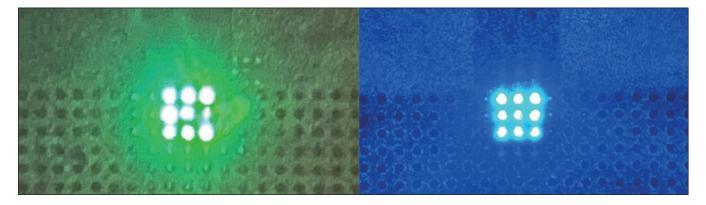

## MicroLEDs: Eliminating etching

Pyramidal microLEDs on patterned SiC deliver a great performance, even when their dimensions approach the nanoscale

## BY RICHARD STEVENSON, EDITOR, CS MAGAZINE

IDEALLY, when producing compound semiconductor devices, every process adds functionality without introducing compromise. For example, the addition of an anti-reflection coating should increase the efficiency of a multi-junction solar cell without limiting its lifetime; and when mirrors are added to a laser, they should boost reflectivity without introducing light-quenching defects.

On the whole, processing epiwafers into devices follows this formula, with a succession of positive steps creating a high-performance chip. But there is an exception: the microLED. When crafting such a smaller emitter, its dimensions are typically defined by etching, a step that creates imperfections, including dangling bonds that drag down efficiency. It's possible to restore this device's performance through passivation, using techniques such as plasma-enhanced CVD and atomic layer deposition. But wouldn't it be better to never damage these miniature marvels, rather than having to repair them?

> Polar Light Technologies has produced blue and green pyramidal microLEDs, and is working on red-emitting varaints.

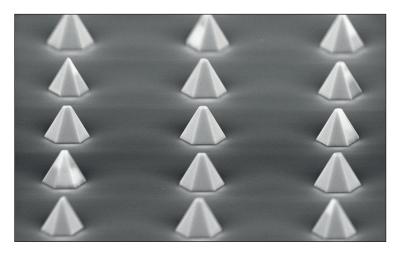

Pursuing this attractive approach with vigour is the Swedish start-up Polar Light Technologies. This spin out of Per Olof Holtz's group at Linköping University has been gathering pace this year as it looks to increase the spectral coverage of its devices, engage with other companies, and win further funding to support its shift from development to production. The core technology of Polar Light Technologies is its pyramidal LEDs, formed by growth of GaN-based structures on patterned SiC substrates by MOCVD.

According to the company's Chief Product Officer and co-founder, Ivan Martinovic, the initial target market for these novel emitters is the light source for augmented-reality headsets. Martinovic views his company's technology as a competitive candidate for making monochrome panels in products made by the likes of Jade Bird Display, with full-colour images formed with an optical system that combines the output of red, green and blue sources.

Looking further ahead, Martinovic expects microLEDs, including those he is helping to pioneer, to penetrate the automotive industry, due to their high level of robustness. MicroLEDs may also take market share from OLEDs in the smartwatch sector, where they promise to enable a battery life of several days.

For the first of these target markets, augmentedreality headsets, displays should have a pixel size approaching two microns, says Martinovic. "The subpixel should be even smaller, and with the spacing, it's a sub-micron game at that point."

As well as increasing the fidelity for the user of the headset, microLEDs that are small enough to meet this requirement deliver cost benefits.

## NEWS ANALYSIS | OPTOELECTRONICS

"Whether it's for micro-displays, where you monolithically integrate onto silicon, or mass transfer for large-area displays, you want to have really, really small LEDs," argues Martinovic. "You can't have five- or ten-micron microLEDs, even for big panel displays. You will use too much epi for your display."

Note that it's not possible to produce conventional microLEDs as small as this that deliver high performance. "You're in the area where damage caused by the etching is getting so out-of-hand that it's almost not controllable anymore," says Martinovic.

While the pyramidal microLEDs excel at such small dimensions, they do incur a substrate cost penalty compared with more conventional LEDs, due to the use of SiC. However, this expense is overshadowed by etching-related issues, argues Martinovic, who points out that the size of SiC substrates is increasing while their price is staying the same. "So, in that case, you can say that the price is coming down."

The pyramidal shape of Polar Light Technologies' microLEDs delivers a number of benefits, including an increase in the light extraction efficiency and an emission profile that leads to better utilisation of light.

So far, demonstrations of the company's technology have focused on devices emitting in the blue and green, but evidence of capability in the red is in the pipeline.

Propelling the emission of GaN-based LEDs to the red is not easy. Success requires increasing the indium content in the quantum wells, but that leads to significant strain that spawns nonradiative defects. Switching to wider wells can alleviate this strain, but at the expense of a fall in the recombination efficiency, due to a reduction in the overlap of electrons and holes, which are pulled towards opposite edges of the wells by internal electric fields.

These problems diminish with pyramidal LEDs. Due to their geometry, they are semi-polar and thus enjoy a reduction in the strength of the internal electric fields that hamper radiative recombination.

Polar Light Technologies has been honing its pyramidal microLEDs over many years. The company formed in 2014, with much initial effort devoted to research and filing patents.

Funding for the start-up, which comes from a number of local venture capital firms, only began in 2021.

"We've gathered a really nice network of Swedish and Nordic VCs. We've chosen to focus on them. We want to keep it here," says Martinovic, who is now

working on a "medium-sized" round that is slated to close at the end of this year.

"At the end of next year, we're gearing up to bring in a more serious level of funding - let's say the A round for Polar Light."

So far, the company has carried out all the process steps in house, including the fabrication of the silicon chips that are used to drive the microLEDs.

"We're using a cold bonding approach to hybridise, to put together gallium nitride LEDs with silicon CMOS," says Martinovic. He explains that a bonding approach involving heating is not permitted, because slight differences in thermal expansion coefficients would lead to a misalignment that exceeds the pitch of the display.

This in-house *modus operandi* is unlikely to continue, as Martinovic and his colleagues are looking to start working with partners. "We're much more active right now and much more open to collaborations than we've ever been. That's part of that direction of going towards product. We're not going to do this ourselves."

It's a good move, as more collaboration will be key to driving the success of microLEDs in a number of displays, where bright, miniature emitters that are free from etching look to shine.

Whether it's for micro-displays, where you monolithically integrate onto silicon, or mass transfer for large-area displays, you want to have really, really small LEDs. You can't have five- or ten-micron microLEDs, even for big panel displays. You will use too much epi for your display

>The triangular shape aids light extraction and is behind the semipolar active region that helps increase radiative recombination.

# **ALD:** Speeding the pathway from development to production

Oxford Instruments' suite of ALD tools ensures a reliable process transfer from development to production

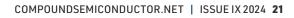

## BY GRANT BALDWIN AND AILEEN O'MAHONY FROM OXFORD INSTRUMENTS PLASMA TECHNOLOGY

IN ANY MANUFACTURING ENVIRONMENT, engineers face a critical challenge when moving a process on from prototype or development to volume production. Reproducing results obtained in a compound semiconductor device development lab at scale is not straightforward, due to the fundamental design of development systems tending to differ from that of production systems.

During the device development process, developers want as many options and capabilities as possible, as this widens their process window, while allowing them the opportunity to pull many levers when trying to nudge the process toward a desired result. But having the opportunity to play with superfluous parameters and process knobs is a double-edged sword, threatening to introduce risk in production environments, where more options mean more components to monitor, control and maintain. What's really needed is to find a way that allows process engineers to benefit from system flexibility in development, without having to compromise production transferability.

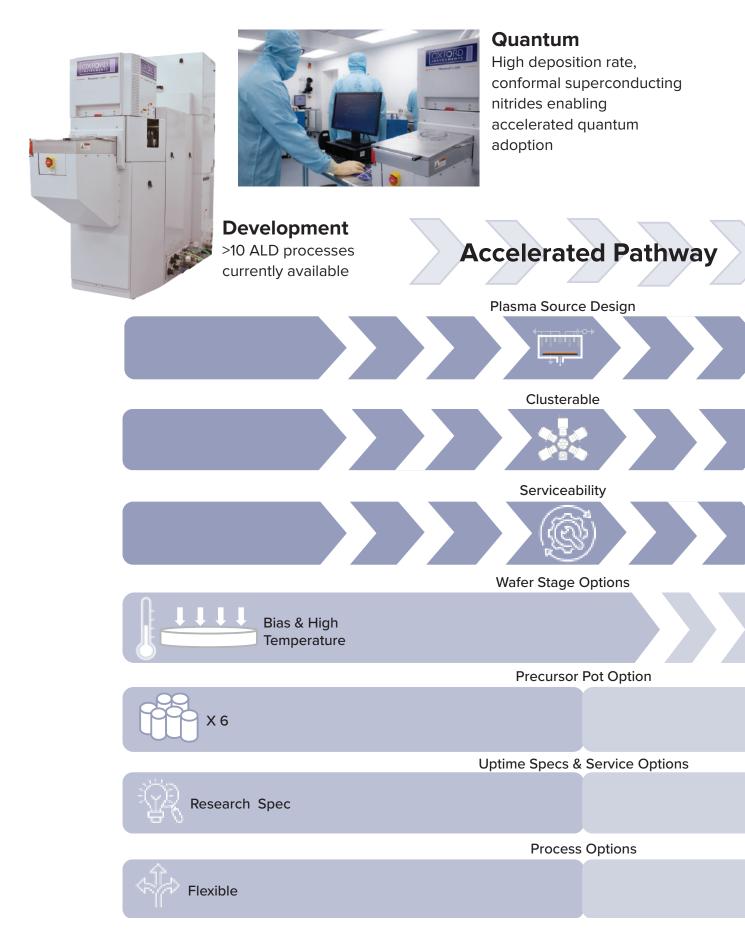

At Oxford Instruments Plasma Technology, located on the outskirts of Bristol, UK, we offer a solution to this problem for those using atomic layer deposition (ALD). We have a complementary pair of systems within our ALD product range that combine, in a very innovative way, development flexibility with high-volume

> Oxford Instruments Plasma Technology's PlasmaPro ASP and Atomfab suite of atomic layer deposition systems

## COVER STORY I OXFORD INSTRUMENTS

manufacturing repeatability and throughput. Read on to discover how we fulfil these disparate goals.

#### Development with PlasmaPro ASP

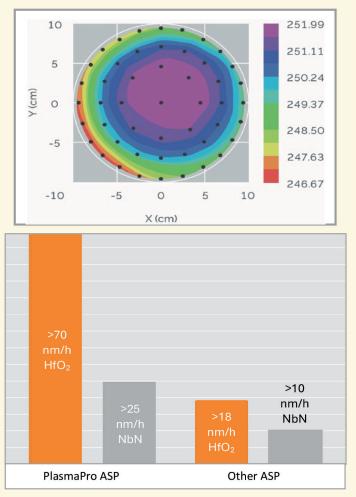

Our PlasmaPro ASP, launched in the last 18 months, is designed to give process engineers all the flexibility and capability to develop the industry's most advanced high-quality ALD layers for research and development, with incredibly high rates and low damage.

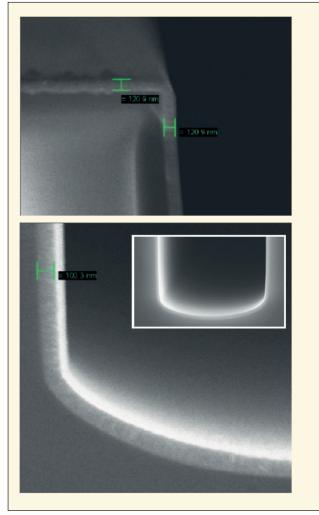

Initially, we launched our PlasmaPro ASP into the quantum market. Here it offers a deposition rate that is 2-3 times higher than comparable ALD systems, and provides a process solution for superconducting nitrides, such as NbN and TiN. For those using rival tools, depositing superconducting thin films can take up to 12-15 hours, slowing down implementation in certain quantum applications.

When targeting deposition of these superconductors, we identified an ideal set of processes to launch our PlasmaPro ASP. Our new ALD system offers deposition rates of more than 25 nm hr<sup>1</sup> for NbN, and in excess of 35 nm hr<sup>1</sup> for TiN. Our PlasmaPro ASP provides the capability to tune film properties, such as stress and crystallinity, enabling engineers to dial in the desired properties of their deposited material.

After launching the PlasmaPro ASP with a suite of the most challenging thin films required for any application, we developed additional ALD films. By adding to this repertoire, we are able to give our customers a truly unique platform for ALD development.

#### Production with the Atomfab

Although high deposition rates provided by the PlasmaPro ASP enable a crucial breakthrough for quantum applications, such rates are not usually a critical requirement for ALD process development systems. So why did we design the PlasmaPro to deliver such high rates?

The answer is found in the innovative way that our development and production ALD systems – Atomfab – work together. This duo share the same genetics, including the same patented plasma source design and user interface, referred to as PTIQ. Thanks to this holistic product range concept, our PlasmaPro ASP benefits from a high deposition rate with process flexibility, as well as ease of process transferability from development to our Atomfab production-proven ALD system. By design, this transfer is incredibly straightforward and negates the need for process requalification at the production level.

> 130 nm conformal superconducting NbN deposited in 8:1 aspect ratio trench using PlasmaPro ASP. Trench etched using PlasmaPro 100 Estrelas in cryogenic mode.

## COVER STORY | OXFORD INSTRUMENTS

## COVER STORY | OXFORD INSTRUMENTS

Production >7,000 wafers per month at 200 mm

AR / VR

Low temperature processing with excellent conformality for mechanical protection

Silicon Carbide Enabling enhanced SiC MOSFET performance with high quality oxides and trench conformality

0

**Gallium Nitride** Productionqualified GaN HEMT passivation with low CoO, validated at global install base

Roadmap for Future Production Qualification

Production Spec

**Optoelectronics** High quality moisture barrier

for lasers. Passivation of VCSEL & LED devices.

| <image/>                        | <b>Quantum</b><br>High deposition rate,<br>conformal superconducting<br>nitrides enabling<br>accelerated quantum<br>adoption |                                      |  |

|---------------------------------|------------------------------------------------------------------------------------------------------------------------------|--------------------------------------|--|

| Development   >10 ALD processes | ccelerated Pathway                                                                                                           | Production                           |  |

| currently available             |                                                                                                                              | >7,000 wafers<br>per month at 200 mm |  |

|                                 | Plasma Source Design                                                                                                         |                                      |  |

|                                 |                                                                                                                              |                                      |  |

|                                 | Clusterable                                                                                                                  |                                      |  |

|                                 |                                                                                                                              |                                      |  |

|                                 | Serviceability                                                                                                               | 2                                    |  |

|                                 |                                                                                                                              |                                      |  |

| Wafer Stage Options             |                                                                                                                              |                                      |  |

| Bias & High<br>Temperature      |                                                                                                                              | Roadmap for Future                   |  |

|                                 | Precursor Pot Option                                                                                                         |                                      |  |

| X 6                             |                                                                                                                              | X 4                                  |  |

|                                 | Jptime Specs & Service Options                                                                                               |                                      |  |

| Research Spec                   |                                                                                                                              | Production Spec                      |  |

|                                 | Process Options                                                                                                              |                                      |  |

| Flexible                        |                                                                                                                              | Dedicated                            |  |

## COVER STORY I OXFORD INSTRUMENTS

## AR / VR

Low temperature processing with excellent conformality for mechanical protection

SNI

## **Silicon Carbide**

Enabling enhanced SIC MOSFET performance with high quality oxides and trench conformality

## **Gallium Nitride**

Productionqualified GaN HEMT passivation with low CoO, validated at global install base

## **Optoelectronics**

High quality moisture barrier for lasers. Passivation of VCSEL & LED devices.

## COVER STORY | OXFORD INSTRUMENTS

We have demonstrated that processes developed on PlasmaPro ASP are easy to transfer and replicate on the Atomfab. This feature is tremendously beneficial to engineers who begin by developing a process to deposit an ALD film, before having to quickly ramp up production.

Since 2020 our Atomfab has been productionqualified throughout the world for ALD passivation of GaN HEMTs. When optimised to run a single plasma ALD process on up to 200 mm wafers, this tool provides a monthly throughput of more than 7,000 wafers for oxide passivation, and over 9,000 wafers for a nitride interface layer on GaN HEMTs for each ALD chamber on a cassette handler.

While throughput is crucially important for device fabrication, quality is also vital. Due to this, we are as innovative in our process development as we are in our product development. Our efforts in GaN HEMT device fabrication highlight this broad outlook. Here we have established a market-leading position in both ALD and atomic layer etch, as well as demonstrating a range of processes to control and optimise material interfaces to improve device performance.

> Process flexibility data for PlasmaPro ASP and production quality data for Atomfab below for ALD

One technique that we have developed, yielding excellent results by optimising the material interface, involves a pre-ALD plasma surface treatment, prior to oxide or nitride interfacial layer deposition. The processes work together to reduce the interface trap density and improve the GaN HEMT performance at a significantly reduced cost of ownership – it is more than four times lower in cost than the incumbent ALD solution. All this is accomplished whilst meeting our customers' expectations in terms of system uptime, mean time to repair, mean time to clean, mean time between cleans, and mean time between assists.

#### Accelerated development

Having the capability, to carry out ALD at high rates on a development system, opens up a world of new opportunities for applying ALD where previously not possible. As well as speeding up development, thicker ALD layers that were previously not thought possible can be developed, and ALD can be considered for new applications with a wider process application window. Once developed on the PlasmaPro ASP, processes can be seamlessly transferred to the Atomfab and ramped to production to enable ALD in high-volume device manufacturing. It is such an advantage to have a suite of products designed to achieve continuity between development and production phases, and arguably this kind of innovation is unique in its category, and with it being available in our technology portfolio, will now be accessible to all ALD users worldwide.

3 inches

Possibilitiy of substrate support with cavity and washer, on request and according to drawings

- Stock of platens blanks for all types of MBE from various manufacturers.

- « Usable in clean rooms » Platens and washers produced according to drawings.

Cleaning and Dégassing

Avenue Louis Armand • B.P. 31 • 74301 Cluses Cedex FRANCE T. +33 (0)4 50 98 15 18 • info@raboutet.fr www.raboutet.fr

## INDUSTRY I EPITAXY

## Riber celebrates 60 years of success

With a pedigree in vacuum technology stretching back 60 years, Riber has an enviable track record in MBE innovation that shows no signs of abating

## BY CLAUDINE PAYEN FROM RIBER

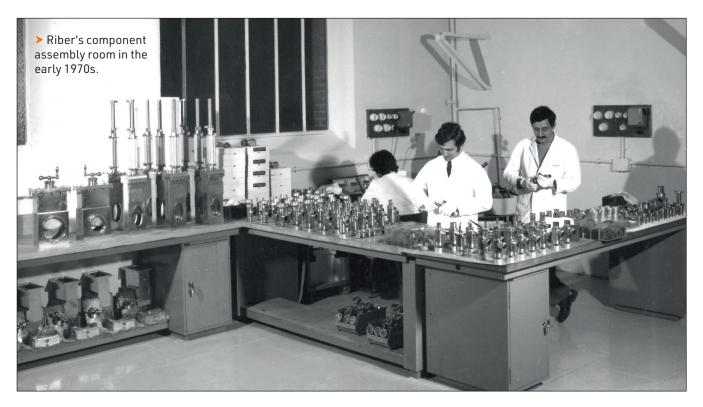

ENGINEERING COMPANIES operating at the cutting edge of technology are renowned for their precision. Such firms are built on calculation, with every alteration accounted for. There's little room, if any, for uncertainty.

So it's almost unthinkable that given all this attention to detail, one such outfit is shrouded in a mystery since its conception. But that's the case for Riber, our company that's a pioneer of MBE, and now celebrating its 60th anniversary.

What, you may ask, is the nature of this mystery? Well, it is the reason behind the name of the company, founded by four engineers in 1964. There is no apparent connection between any of them and the name of our company.

Looking back on those formative years, what is known is the initial focus, a combination of stainlesssteel fabrication and tungsten-inert-gas welding for high-vacuum applications, an emerging technology of the time. Alongside this, we distributed Americanmade micro-welders and ion pumps.

Like many small and successful start-ups, we quickly

expanded our portfolio. Three years in, we started to make Joule-effect evaporators, vacuum chambers and a series of accessories. It's a direction of travel that continued into the 1970s, when our design office would draw plans for increasingly complex chambers. Such work drove our first technological shift, as we moved into the production of analytical instruments, such as Auger spectroscopes and lowenergy electron diffraction systems.

During this time of transition, our clientele expanded from research laboratories to include industrial companies. We also developed new accessories, such as valves, ultra-high vacuum (UHV) linear and rotary feedthroughs, and many other components.

#### **Pioneering MBE**

A major milestone came in 1974, when we created a unique system at the request of the now legendary pioneer of MBE, Klaus Ploog, who had just started leading a group at the Max Planck Institute for Solid-State Research in Stuttgart, Germany. Using the UHV chamber we provided, Ploog and his coworkers were able to deposit arsenic and gallium via evaporation. Their efforts led to the development of the first Knudsen cells, comprising a graphite

## INDUSTRY I EPITAXY

crucible 2 cm<sup>3</sup> to 3 cm<sup>3</sup> in size, accompanied by a thermocouple and a heating element spiralled around machined alumina. Samples produced in this chamber were just 10 mm in size.

Our driving force behind these fledgling MBE tools is Pierre Bouchaïb, the product manager during our formative years. While the nature of the growth in this chamber was yet to be christened MBE, this work marked the beginning of increasing interest in this technology from laboratories like IBM, Bell Labs, NEC, Rohm and Sony. All would go on to play a key role in the development of this class of epitaxy.

From these early days onwards, MBE has advanced in both its capability and the performance of the growth tools. Critical to this progress are the partnerships that we have formed with our users. We have a deep commitment to collaboration, which is part of our core values. As Bouchaïb used to say: "Our only limit is the imagination of our clients."

As interest in MBE expanded throughout the 1970s and beyond, with research groups keen to explore the mechanisms behind the growth of material, we shipped more and more systems. Often designed for research, they could accommodate substrates up to 2 inches in diameter, but would often be used to produce epilayers on smaller platforms.

During the 1980s, we reached a manufacturing milestone, passing the production of 100 systems sold in 1984, and we also received a strong endorsement from a master of MBE, AI Cho. Often referred to as the father of this particularly growth technology for his trailblazing work at Bell Labs, Cho visited our headquarters on the outskirts of Paris during the 1980s, and paid tribute to the key features of our MBE tool. He argued that the best MBE machines should exclusively feature a liquidnitrogen cooling unit, cells and a manipulator, as anything else was a source of contamination. Our systems are built around these core principles.

#### From research to industrialisation

Inspired by scientific discoveries, many new commercial applications related to compound semiconductor devices have emerged since the 1990s. To support this, we have expanded our portfolio, introducing more industrial machines. This includes the MBE 49, our first fully automated industrial prototype, unveiled in 1990. Developed for the company Bandgap in the US, this reactor broke new ground by enabling several substrates to be grown simultaneously.

We have also advanced our effusion cell technologies. A great deal of progress has been made with valve cells for cracking group V elements, enabling a significant increase in the arsenic incorporation on substrates; and we have also improved cells for group III elements, which now offer capacities of several hundred cubic centimetres.

A key juncture in our history came in 1994, when we decided to focus exclusively on producing MBE systems. At this point in time we divested our instrumentation division, now known as the company Cameca. Back in the early 1990s, our portfolio included secondary ion mass spectrometers, instruments for Auger spectroscopy, and low-energy electron diffraction systems.

Our focus on MBE has helped us in our efforts to develop new tools. In 1997 we launched the MBE 6000, which offers double the capacity of the MBE 49. This hit the market at a time when production systems in an industrial setting were gaining substantial traction, with around 50 already operating worldwide.

Throughout our history, we have continued to innovate, never resting on our laurels. This willingness to keep pursuing excellence and questioning what might be best has led us to some fundamental changes. Through a project called ANISET, named after a spirit that's well known and

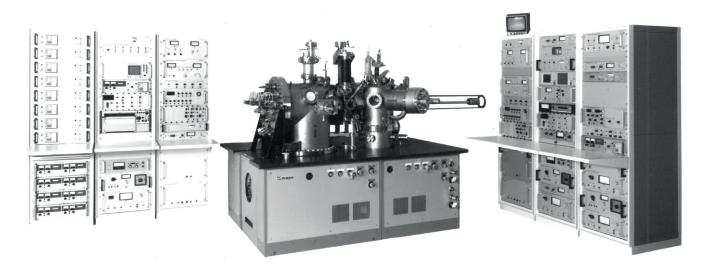

Riber's first

MBE system.

Photo from

1980.

## INDUSTRY I EPITAXY

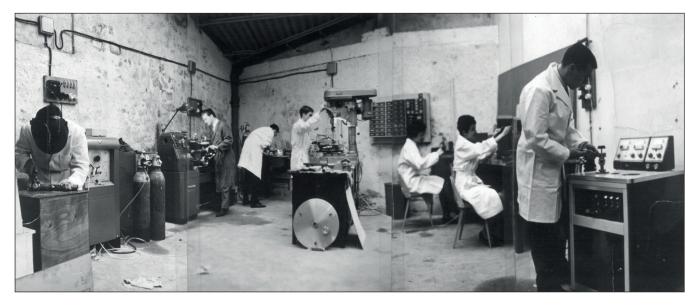

> The starting assembly room. Photo from 1964.

appreciated in the south of France and has the taste of aniseed, we worked with Jean Massies and his team at CRHEA in the late 1990s to transition MBE reactors from a horizontal to a vertical design. Since then, this new geometry has become the standard for MBE growth.

Today we offer an extensive range of MBE reactors for research and production. Our focus is on improving the reproducibility, stability and uniformity of our machines, goals that we are helping to fulfil through sustained work on manipulators and cells. Through our acquisition of Addon in 2008, we have expanded our product range to include RF cells, as well as cells designed specifically for corrosive materials, such as antimony, magnesium and tellerium. Another advance is our introduction

> Today's cleanroom at Riber, featuring an MBE 6000 system.

of a 'cluster' version of our machines, providing full flexibility and automation. This move has been motivated by the emergence of centres of excellence, and the pooling of machines by multiple working groups.

#### Silicon photonics and quantum materials

Last year, we launched the highest capacity machine on the market: the MBE 8000. This highlights how we have come full circle, from the most advanced research machine to the most demanding production system.

Today, as well as selling state-of-the-art MBE tools, we also offer the hardware to support exceptional epitaxy. We provide our clients with real-time, *in-situ* control, featuring feedback loops on all growth parameters, thanks to a range of optical instruments called EZ-Tools that are compatible with our entire product range.

The capability of our instrumentation never stands still, thanks to ambitious development at Epicentre, a joint laboratory between ourselves and LAAS-CNRS.

We are also playing a key role in emerging technologies, such as silicon photonics. We are developing a platform called ROSIE - Riber oxide silicon epitaxy – that will enable the growth of barium titanate on 300 mm silicon substrates. It's a project that's addressing the challenge of the adoption of this technology in high-volume silicon fabs.

Alongside this, we are finalising the validation of a quantum platform that combines standard epitaxy with 120 K epitaxy to produce superconducting materials. Over the coming months we shall start to offer this opportunity to the MBE community.

Like the compound semiconductor industry, we have come through some challenging periods. But drawing on 60 years of success, we continue to be a key player, ready to tackle the challenges that will lie ahead for the next 60 years.

## **Sheraton Brussels Airport Hotel**

To find out more about our sponsor and speaker opportunities contact us today on:

+44 (0)2476 718970

or email: info@angel-tech.net

# CONFERENCE ANGELTECH

## 7 - 9 APRIL 2025 BRUSSELS BELGIUM

## **CONNECTING, EDUCATING & INSPIRING THE CS INDUSTRY**

## THEMES AND SPEAKERS ANNOUNCED

**CS INTERNATIONAL** is part of the AngelTech series of events, which has produced for over 15 years, a portfolio of insightful, informative, and highly valued chip-level conferences.

Attracting more than 800 delegates and 80+ exhibitors consisting of co-located AngelTech Executive Strategy Summit, PIC International, and PE International, plus a single exhibition area, delegates can dip in and out of every session to put together their own tailor-made programme by selecting from over 130+ invited talks, delivered by leaders of the most innovative global companies of today.

With a significant overlap between the three conferences, attendees and exhibitors are exposed to the full relevant supply chains and customer and supplier bases.

## **KEY THEMES FOR 2025**

#### **GaN: Going Beyond Fast Charging**

To ramp the revenue of GaN transistors, their deployment must extend beyond the fast charging of mobile devices. But where are the most lucrative opportunities?

#### Maintaining Momentum for the microLED

Apple's decisions to terminate its venture with Osram has sent shockwaves through the microLED industry. But this emitter still has tremendous potential that will be set free with the introduction of novel technologies.

#### **Optimising Opportunities for SiC success**

As sales of electric vehicles stutter, SiC revenues could face some bumps in the road ahead. So, what's the best approach to optimising returns in these uncertain times?

#### **Expanding the Emission Envelope**

What strategies will extract an even better performance from the various classes of lasers and LEDs? And what applications could benefit from these superior sources?

#### Ultra-wide Bandgap Materials: The Ultimate Devices

Higher bandgaps promise to propel the performance of power devices to a new level. But which materials have the greatest potential? And what's must be done to unlock this promise?

#

ESS EXECUTIVE STRATEGY SUMMIT

PIC INTERNATIONAL CONFERENCE

## Sponsorship / Exhibition / Speaker OPPORTUNITIES AVAILABLE!

Sponsorship, exhibition, and speaker opportunities at CS International, enable and empower you to educate and penetrate the global compound semiconductor industry using a plethora of marketing tools.

Demand is high, with sponsorship, exhibition and speaking slots already being secured for 2025, so to avoid disappointment, please get in touch today.

## **Earlybird Discount:**

**Register before 31 December and get 10% off!** Registration to AngelTech allows you to access both days of **CS International** and the co-located **PIC International** and **PE International**.

## PLATINUM SPONSORS

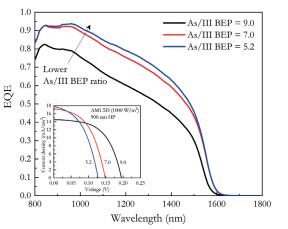

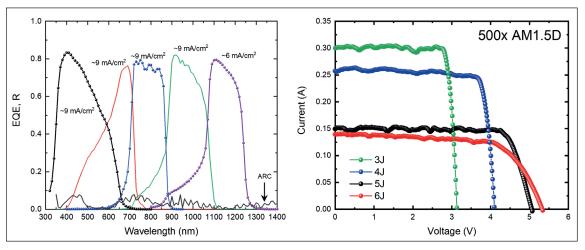

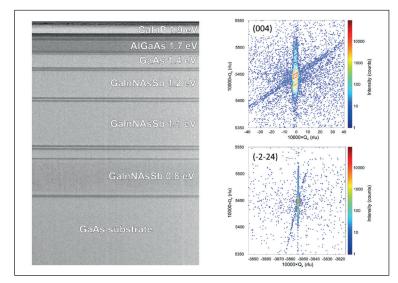

| PLATINUM SPONSORS                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |  |  |