## POWER ELECTRONICS INTERNATIONAL

**DESIGN + MATERIALS + PACKAGING + PERFORMANCE**

## RIXTRON

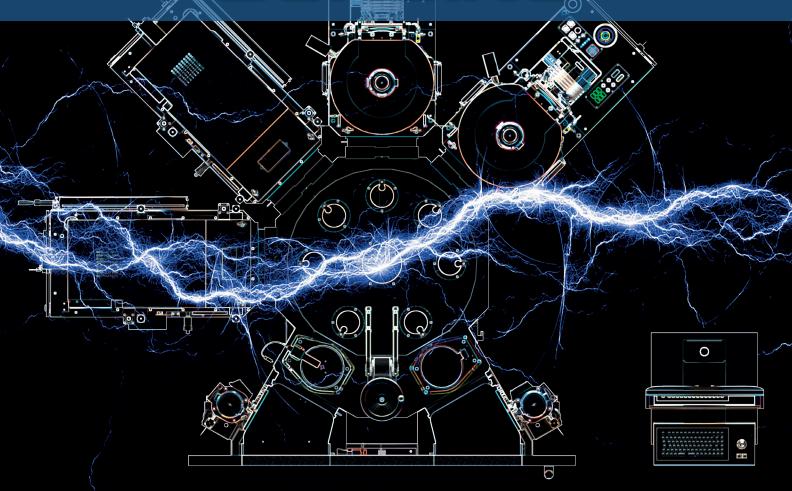

## THE NEW G10 SERIES

Your Productivity Solution for All Advanced Epitaxy Materials

## G10-SiC

- ▶ 9x150 mm (6") or 6x200 mm (8")

- New hardware & process surpassing Single Wafer Reactor uniformities

- ► +50% productivity per fab area with large batch technology & small footprint

#### **End Markets/Products:**

EV inverters & charging infrastructure

## G10-GaN

- ▶ 8x150mm (6") or 5x200mm (8")

- ▶ 1<sup>st</sup> fully automated compact GaN MOCVD cluster designed 100% for Si Power fabs

- Novel hardware solution for unmatched barrier uniformities and device yields

### **End Markets/Products:**

Power Electronics & Wireless communication

## G10-AsP

- ▶ 8x150 mm (6") or 5x200 mm (8")

- ▶ 1<sup>st</sup> fully automated AsP MOCVD system enabling 10x lower defect density

- Unmatched wavelength uniformity on all wafer sizes

#### **End Markets/Products:**

Micro LED, Optical Data communication, 3D-sensing & LiDAR

## Power electronics at a tipping point

The past decade has been defined by incremental gains in efficiency and miniaturisation. But if the past few months of research breakthroughs are any indication, power electronics is now entering a true inflection point - one that could reshape everything from consumer devices to national grids.

At Northeastern University, scientists have made plastics behave like metals. Their 3D-printed plastic-ceramic composite conducts heat better than stainless steel while remaining electrically insulating - an extraordinary combination.

From data centres to EV batteries, this could mean cooler, safer systems without the weight or short-circuit risks of metal. In parallel, teams in Japan and the US are redefining how we manufacture and manage wide-bandgap semiconductors. Sumitomo Chemical's quartz-free HVPE GaN wafers and Nagoya University's first functional gallium oxide pn diodes suggest that long-standing bottlenecks in scalability and material science are finally breaking.

Even existing materials like SiC are being 'reinvented'. Osaka researchers have found a way to anneal devices without compromising reliability, while the US National Renewable Energy Laboratory's ULIS module demonstrates how clever design can yield fivefold energy density gains.

Meanwhile, recycling silicon sludge into SiC crystals at Tohoku University hints at a future where performance and sustainability go hand in hand.

Yet perhaps the most striking development is who is now steering the field. Nvidia -better known for graphics chips than power semiconductors - is dictating architectures

for 800V AI data centres. Like Tesla's push for SiC in EVs, Nvidia's endorsement of GaN could accelerate adoption across the supply chain. Suddenly, the conversation is not about if GaN and SiC will dominate, but how quickly.

Meanwhile, the geopolitical dimension is impossible to ignore. China continues to expand its dominance in traction inverters. The UK eyes leadership in solid-state transformers for smart grids. US labs are racing to develop DC circuit breakers and modular, stackable power movers. Europe is investing in talent pipelines. Power electronics, once a niche materials science pursuit, is now industrial strategy.

What ties these advances together is not simply better chips, but systems thinking. Materials, design, manufacturing, and sustainability are converging. The sector is no longer asking whether it can catch up with demand from AI, EVs, and renewable grids - it is beginning to define the pace of that demand itself. We are witnessing the foundations of a new energy infrastructure, built not just on silicon, but on imagination,

## **COVER STORY**

# Infineon reports strong earnings as Smart Power fab advances

Rising power semiconductor revenues boost Infineon while Dresden expansion heads towards 2026 production

## 14 How AI will drive growth in power semiconductors, from the (data) centre to the edge

he industry is facing a challenge to keep up with the ever-evolving demands of the big Al players. This is a challenge we should all embrace

## 16 Infineon reports strong earnings as Smart Power fab advances

Rising power semiconductor revenues boost Infineon while Dresden expansion heads towards 2026 production

## 18 Reshaping gate drivers for next-gen electrification

As the need for higher performance, precision, and efficiency mounts, gate driver technology is becoming more essential than ever

## 22 Harnessing the sun: semiconductors in solar inverters

The shift toward GaN and SiC technologies not only improves the size, weight, and cost-effectiveness of solar inverters but also enhances their efficiency, potentially breaking through the 99% efficiency barrier

## 26 Wide-bandgap power semiconductor device dynamic characterisation

This article outlines the technologies and techniques required for performing dynamic characterisation of SiC and GaN power semiconductor devices

## 34 Metrology for the 2 nm era and beyond

Infinitesima bets on high-speed atomic force microscopy to keep advanced silicon on track

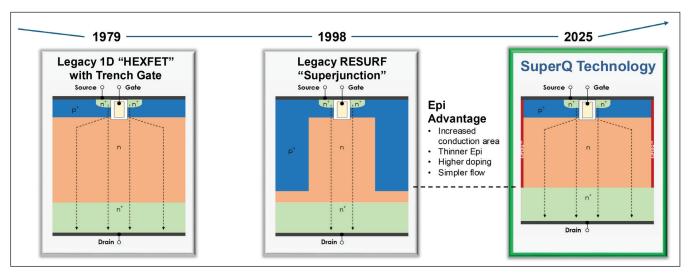

## 36 iDEAL charts a new course for silicon

Will the latest MOSFET from iDEAL Semiconductor redefine silicon chip performance?

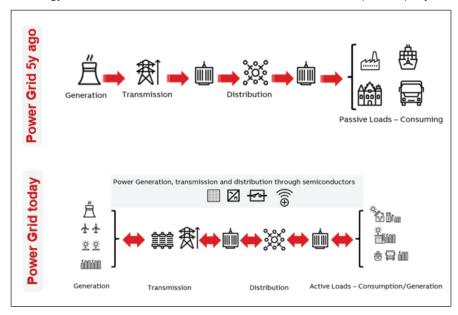

## 38 Power semiconductors – the silent heroes in the power grid

Exploring the pivotal role of power semiconductors in the evolving landscape of the power grid

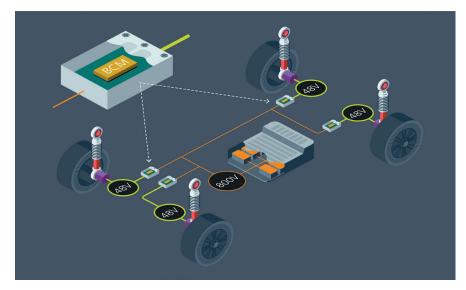

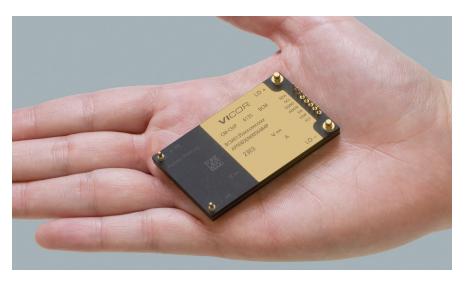

## 42 Bidirectional power and transient speed enable scalable active suspension

Sine Amplitude Converter™ modules offer a unique combination of bidirectionality and transient response that unlocks new possibilities for active suspension

## 46 How Network-on-Chip architectures are powering the future of microcontroller design

Microcontrollers (MCUs) are no longer the humble workhorses of embedded systems. Today's MCUs rapidly evolve into compact, high-performance computing platforms, integrating artificial intelligence (AI), advanced security features, and real-time processing into power-constrained environments

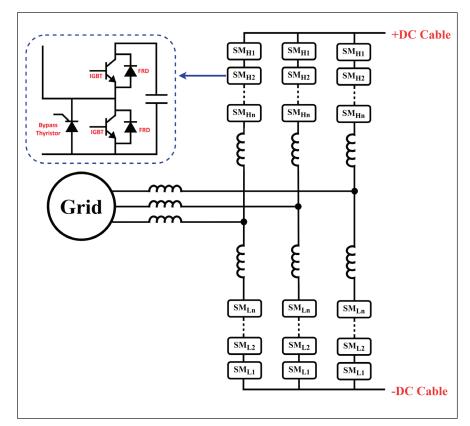

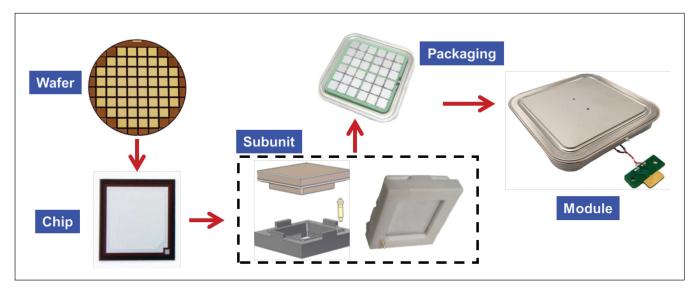

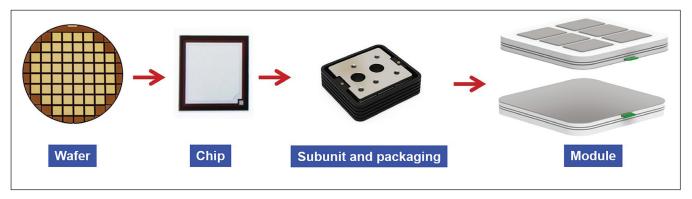

## 48 Enhancing MMC VSC HVDC system performance with Press-Pack IGBT technology

By adopting Press-Pack IGBTs, operators can significantly reduce component-level failure risks while improving overall system efficiency and lifetime economics — a decisive advantage in today's utility-scale energy infrastructure

## **NEWS**

- **06** Heat-conductive plastic could help cool power chips

- **07** Scaling quartz-free HVPE of GaN-on-GaN epiwafers

- **08** USTC team develops ultrafast junction temperature mapping of GaN PiN diode

- 09 Scientists make first gallium oxide pn diodes

- 10 NREL team constructs record-beating SiC module

- 11 UK can lead modern grid technology, says new report

- 12 RNL team develops fast circuit breaker for the modern grid

## POWER ELECTRONICS INTERNATIONAL DESIGN + MATERIAS + PACKAGING + PERFORMANCE

#### Editor

Phil Alsop phil.alsop@angelbc.com +44(0)7786084559

#### News Editor

Christine Evans-Pughe christine.evans-pughe@angelbc.com

#### Technology Editor Rebecca Pool

#### Contributing Technical Editor Richard Stevenson

richard.stevenson@angelbc.com +44 (0)1923 690215

#### Sales & Marketing Manager

Shehzad Munshi shehzad.munshi@angelbc.com +44 (0)1923 690215

#### Design & Production Manager

Mitch Gaynor mitch.gaynor@angelbc.com

+44 (0)1923 690214

#### Sales and Product Manager

James Cheriton james.cheriton@angelbc.com +44 (0)2476 718970

#### Publisher

Jackie Cannon jackie.cannon@angelbc.com +44 (0)1923 690205

CEO Sukhi Bhadal sukhi.bhadal@angelbc.com +44 (0)2476 718970

CTO Scott Adams scott.adams@angelbc.com +44 (0)2476 718970 Power Electronics international Magazine is published six times a year on a controlled circulation basis. Non-qualifying individuals can subscribe at: £105.00/e158 pa (UK & Europe), £138.00 pa (air mail), \$198 pa (USA). Cover price £4.50. All information herein is believed to be correct at time of going to press. The publisher does not accept responsibility for any errors and omissions. The views expressed in this publication are not necessarily those of the publisher.

Every effort has been made to obtain copyright permission for the material contained in this publication. Angel Business Communications Ltd will be happy to acknowledge any copyright oversights in a subsequent issue of the publication. Angel Business Communications Ltd © Copyright 2024. All rights reserved. Contents may not be reproduced in whole or part without the written consent of the publishers. The paper used within this magazine is produced by chain of custody certified manufacturers, guaranteeing sustainable sourcing.© Copyright 2024.

We strive for accuracy in all we publish; readers and contributors are encouraged to contact us if they recognise an error or omission. Once a magazine edition is published [online, in print or both], we do not update previously published articles to align old company names, branding, marketing efforts, taglines, mission statements or other promotional verbiage, images, or logos to newly created or updated names, images, typographic renderings, logos (or similar) when such references/images were accurately stated, rendered or displayed at the time of the original publication.

When companies change their names or the images/text used to represent the company, we invite organizations to provide Angel Business Communications with a news release detailing their new business objectives and/or other changes that could impact how customers/prospects might recognise the company, contact the organisation, or engage with them for future commercial enterprise.

**Published by** Angel Business Communications Ltd 6 Bow Court,

Fletchworth Gate, Burnsall Road, Coventry CV5 6SP, UK.

T: +44 (0)2476 718 970 E: info@angelbc.com

W: angelbc.com

## Heat-conductive plastic could help cool power chips

3D printing allows a new, lightweight plastic-ceramic composite to be tailored to specific shapes and sizes

NORTHEASTERN UNIVERSITY researchers have developed a new, lightweight plastic-ceramic composite that conducts heat and can be used to more efficiently cool advanced power electronics in phones, data centres and cars.

"Managing heat is a big challenge for power electronics and devices like radar antennas," says Northeastern Randall Erb, head of the university's Directed Assembly of Particles and Suspensions (DAPS) Lab and lead researcher on the project.

"When electronics overheat, you either have to slow them down or turn them off. That might be fine for a phone, but not for critical systems like radar."

Northeastern researchers, in collaboration with the US Army Research Laboratory, developed the material that combines ceramics, polymers and additives into a 3D-printable plastic composite. It has a unique internal structure, ordered down to the nanoscale, that lets heat move through it easily.

"Plastics are normally terrible at conducting heat," says Daniel Braconnier, a former PhD student in Erb's lab. "Adding ceramic particles helps a bit, but the plastic still slows heat flow too much."

The breakthrough was finding a way to precisely organise the material at every scale — from molecules all the way up to the printed part. Using 3D printing, the team carefully positioned ceramic particles, then used special heating steps to grow tiny bridges of crystalline polymer between them.

This connected network allows heat to travel efficiently, making the material

even more thermally conductive than stainless steel, while being four times lighter.

"These properties can enable much higher performance in many systems," Erb says.

While metal materials like stainless steel can short out electronics if they touch them, the new material is an electrical insulator. It also doesn't block radio frequency signals, which means it won't interfere with 5G or radar systems.

"These new materials can cover and protect circuits without causing electrical shorts," Erb continues. "They help pull heat away from advanced telecommunication devices without blocking their signals."

"Industry keeps pushing for higher power in smaller packages, which means devices keep getting hotter," Braconnier says. For example, he notes that an iPhone processor often doesn't run at full speed in hot conditions to avoid overheating.

The team also sees potential far beyond phones.

"Data centres generate huge amounts of heat, and industry doesn't have a sustainable solution yet," Erb says. "Our material won't solve it alone, but it could help by providing a better thermal interface with chips and other cooling systems."

They're also looking at electric vehicles, where overheating batteries can cause dangerous fires.

"Our material could be used around battery cells to spread out and remove heat, helping prevent thermal runaway events," Erb says.

The team is now working to scale up production of the material in partnership with the US. Army Research Laboratory.

## Scaling quartz-free HVPE of GaN-on-GaN epiwafers

Sumitomo Chemical targets the epiwafer market with 6-inch material produced in a quartz-free HVPE reactor that's designed for mass production

k increase the adoption of GaN power devices via a reduction in production costs, Sumitomo Chemical has developed a quartz-free HVPE reactor for mass production that can accommodate 6-inch substrates. This latest triumph builds on previous successes by the Japanese company, which has shown that quartz-free HVPE can grow GaN layers with record room-temperature mobilities. Epilayers also feature very low background concentrations of silicon, oxygen and carbon.

Spokesman for the team, Ryota Ito, told Compound Semiconductor that the quartz-free HVPE technology is now very close to full optimisation. "The mobility at room temperature is close to theoretical values, and the impurity concentration is below the detection limit as measured by secondary ion mass spectrometry."

To underscore the capability of their new tool, engineers from Sumitomo Chemical have used their reactor to produce 4-inch and 6-inch GaN epiwafers. This involved the growth of a silicon-doped GaN layer, subsequently scrutinised by various characterisation techniques.

The 4-inch substrate employed in this study was produced internally, using the void-assisted separation method. This substrate had a uniform threading dislocation density of 1-3 x 106 cm-2 and an off-angle of 0.4°, tilted from the exact + c-plane towards the m-direction. "The off-cut angle is intentionally used to prevent the occurrence of hillocks," explains Ito.

For growth on 6-inch wafers, the team at Sumitomo Chemical turned to a GaN-on-sapphire template. Note, though, that 6-inch free-standing GaN substrates are under development.

Growth conditions employed included atmospheric pressure, a growth rate of approximately 1 mm min-1, the use of ammonia and gallium monochloride as source gases, and a mixture of hydrogen and nitrogen for the carrier gas.

According to Fourier transform infrared spectroscopy, the silicondoped GaN epilayer on the 4-inch native substrate has a thickness of 14.1 mm, with a standard deviation of 3.4 percent. Commenting on this, the team remarked in their paper that whereas conventional HVPE-grown GaN tended to exhibit a large thickness variation, the optimised quartz-free HVPE system led to a uniform distribution, similar to that of an MOCVD-grown epitaxial film. For the growth of epiwafers on 6-inch templates, the thickness uniformity is a little higher, with a standard deviation of 4.4 percent.

To evaluate doping, the engineers at Sumitomo Chemical considered the difference between the density of donors and acceptors, determined by a non-contact capacitance-voltage instrument. For MOCVD-grown GaN on 100 mm free-standing GaN, the standard deviation is 14.3 percent – and for GaN grown by quartz-free HVPE on 100 mm free-standing GaN it's just 3.0 percent.

The team also conducted photoluminescence measurements on their latest GaN epilayers, and compared the spectra with that obtained for an equivalent sample produced with a prototype reactor. The film grown with the more recent reactor, designed for mass-production, produces stronger near-band-edge emission, thanks to suppression of carbon contamination. Also encouraging is a reduction in green luminescence, indicative of a reduction

in the density of point defects – this is attributed to a superior reactor design that supresses the leakage of gas from/ into the growth area.

To demonstrate carrier control in their quartz-free HVPE reactors, the engineers at Sumitomo Chemical varied the silicon source rate, with a step change for every 600 nm of GaN growth. Analysing the doping profile via secondary ion mass spectrometry determined that the doping level is constant in each layer, and at the interfaces there is a steep change in silicon concentration.

This investigation also showed that with the latest quartz-free HVPE reactor there is linear doping with silicon concentration, over a wide range from 1  $\times$  1014 cm<sup>-3</sup> to 1  $\times$  1018 cm<sup>-3</sup>.

As many power devices operate in the kilovolt range, controlling the carrier concentration in the range below 1 x 1016 cm-3 is critical. Excelling in this regard, Sumitomo Chemical's latest quartz-free HVPE reactor offers the capability to produce devices with breakdown voltages of 10 kV or more. Sumitomo Chemical does not intend to produce and sell its quartz-free HVPE reactors. "We are a GaN substrate vendor, and we are planning to sell GaN-on-GaN epitaxial wafers produced by quartz-free HVPE," says Ito.

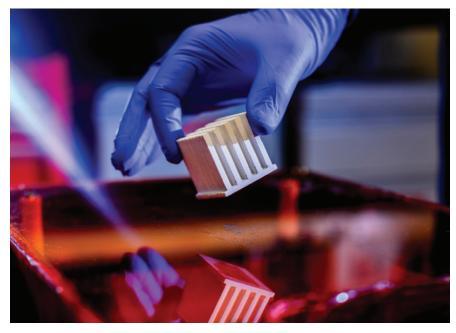

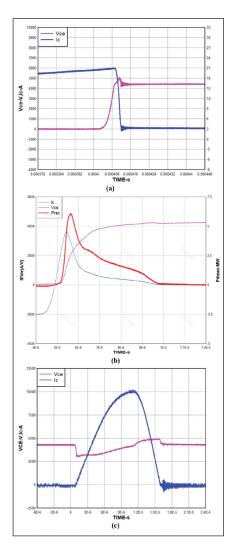

## USTC team develops ultrafast junction temperature mapping of GaN PiN diode

Confocal thermoreflectance microscopy approach achieves time-resolved Tj measurement during extreme stress transients

RESEARCHERS from University of Science and Technology of China (USTC) have achieved dynamic junction temperature (Tj ) mapping of a vertical GaN PiN diode during extreme stress transients up to 10000 A/cm², using ultrafast confocal thermoreflectance microscopy (CTRM) featuring a sampling rate of 105 Sa/s.

The approach, they say, enables time-resolved Tj measurement during extreme stress transients, enabling the identification of degradation/failure mechanisms.

When operating at high-frequency and high-power levels, the elevated Tj presents a critical challenge for GaN power devices. In particular, power devices are usually required to withstand extreme stress such as surge current, in which the heat generation during the high-power transient within a short duration (10-5~10-2 s) would cause rapid Tj rise or even device failure.

However, conventional Tj monitoring techniques (e.g., thermocouple, infrared imaging) with relatively long response delay over milliseconds are unable to capture the abrupt change of Tj, which is an obstacle towards the identification of device degradation/ failure under extreme stress.

The USTC researchers say that thanks to the ultrafast Tj mapping with CTRM, they have identified device failure mechanisms under surge current stress, during which

the dynamics of heat spreading/ accumulation is revealed. Moreover, to enhance the heat dissipation during surge current stress, they have developed thermal management with a bonded diamond heatsink, which can further boost the surge energy density from 323 J/cm² (without diamond heatsink) up to 390 J/cm² in a 10-ms surge current test.

The ultrafast Tj mapping and thermal management techniques in this work are valuable towards high-ruggedness GaN devices for high-power and

high-temperature power electronics applications.

The figures above show the (a) Challenge in ultrafast Tj monitoring during extreme stress transient (e.g., surge current/voltage, short circuit, etc). (b) Tj mapping platform featuring time-resolved CTRM with synchronously triggered surge current excitation circuit. (c) Time-resolved Tj in vertical GaN PiN diode during surge current up to 10000 A/cm². (d) Measured peak Tj at the centre and the edge of vertical GaN PiN diode during surge current stress transient.

## Dedicated webinars for the power electronics (PEI) industry

Using our 30+ years' experience in B2B vertical technical markets, and as the publisher of PEI Magazine, we offer effective webinars, ZOOM interview and virtual events. We help you get your message, to your desired audience, by marketing to over 53,000 PEI professionals.

In addition to organising and managing your webinar, we can also market your webinar to our specialist databases.

Reach Educate Influence

- Brand Awareness

- Lead Generation

- Thought Leadership

Contact: Jackie Cannon jackie.cannon@angelbc.com +44 (0)1923 690205

## Scientists make first gallium oxide pn diodes

New method uses standard industrial processes to achieve higher voltage, increased stability, and energy efficiency

RESEARCHERS at Nagoya University in Japan have created the first functional pn diodes using Ga<sub>2</sub>O<sub>2</sub>.

Their method '*P*-type layer formation study for Ga<sub>2</sub>O<sub>3</sub> by employing Ni ion implantation with two-step oxygen plasma and thermal annealing' was published in the Journal of Applied Physics.

SiC-based Schottky barrier diodes are replacing silicon devices in inverter applications. However, high production costs due to SiC substrates being deposited by PVD and high device processing temperatures are barriers to increasing their market scale. SiC also faces another difficulty in that it tends to degrade when used in bipolar pn junction devices.

${\rm Ga_2O_3}$  is a potential alternative because it is less expensive to produce than SiC as a result of its compatibility with meltgrowth methods such as the film-fed growth or Czochralski method. Schottky

barrier diodes based on  ${\rm Ga_2O_3}$  are under development; however, practical bipolar pn diodes have not yet been achieved.

The problem is that Ga<sub>2</sub>O<sub>3</sub>'s crystal structure easily accepts the atoms needed to create n-type layers but rejects the atoms required for p-type layers. Previous methods to force them in either failed or required temperatures that destroyed the material. Without both types working together, Ga<sub>2</sub>O<sub>3</sub> remained limited for practical applications.

To address this, the researchers injected nickel atoms into the  ${\rm Ga_2O_3}$  layer by shooting individual atoms at high speed into the surface of the material. They then heated the material twice, first at 300°C with activated oxygen radicals (oxygen atoms that have been given extra energy using proprietary plasma treatment) and then at 950°C in oxygen gas. This converted

the embedded nickel into nickel oxide and properly integrated it with the Ga<sub>2</sub>O<sub>3</sub> crystal structure.

"Since this method uses standard industrial equipment and processes, it can be scaled up for mass production," Masaru Hori from the Center for Low-Temperature Plasma Sciences at Nagoya University highlighted. "The implications for future energy efficiency and costs are substantial, particularly for electric vehicle and renewable energy industries."

Nagoya University spin-off company NU-Rei is now working to bring these advances to market.

Pictured above: Illustration of the new fabrication process: ion implantation of nickel atoms, followed by low-temperature plasma treatment and high-temperature annealing (heating) to create stable p-type layers in  ${\rm Ga_2O_3}$ .

## Novel annealing process improves SiC devices

RESEARCHERS at the University of Osaka in Japan have developed a novel technique to enhance the performance and reliability of SiC MOS devices.

This breakthrough uses a two-step annealing process involving diluted hydrogen, to eliminate unnecessary impurities and significantly improve device reliability.

SiC power devices offer superior energy efficiency compared to traditional silicon-based devices, making them ideal for applications like electric vehicles and renewable energy systems.

However, previous attempts to improve SiC MOS device performance relied on introducing impurities like nitrogen, which unfortunately compromised

reliability and limited operating voltage range.

This necessitated strict gate drive design, hindering wider adoption. The team discovered that a two-step high-temperature hydrogen annealing process, performed before and after gate oxide deposition, could drastically improve both performance and reliability without the need for these

problematic impurities.

This process effectively removes defects at the oxide/SiC interface, resulting in a lower interface state density and higher channel mobility. The devices demonstrated improved immunity against both positive and negative bias stress, expanding their operational voltage range.

"SiC MOS devices, despite being in mass production, haven't yet reached their full potential in terms of performance and reliability," explains Takuma Kobayashi, the lead researcher. "Our findings offer a solution to this long-standing challenge and open up exciting new possibilities for SiC power devices. We overcame many hurdles during this research, and I'm grateful to all my co-authors for their contributions."

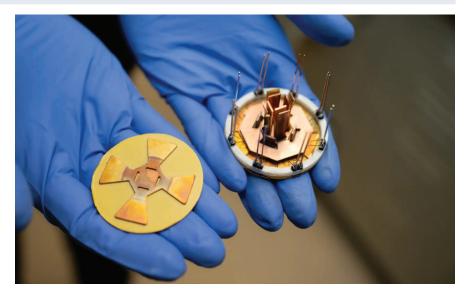

## NREL team constructs record-beating SiC module

Ultra-Low Inductance Smart (ULIS) module can achieve five times greater energy density than predecessor designs

NREL has developed an Ultra-Low Inductance Smart (ULIS) SiC power module with a parasitic inductance seven to nine times lower than any current state-of-the-art SiC power module.

The 1200V, 400A module is capable of achieving five times greater energy density than predecessor designs in a smaller package, making it possible for to build and power more efficient, compact, and lighter technologies for applications such as data centres, power grids, microreactors, and even heavy-duty vehicles such as next-generation aircraft and military vehicles.

"We consider ULIS to be a true breakthrough," said Faisal Khan, NREL's chief power electronics researcher and the principal investigator for the project. "It's a future-proofed, ultrafast power module that will make the next generation of power converters more affordable, efficient, and compact." Furthermore, Khan explained, ULIS is uniquely suited for high-intensity applications, like aviation and military operations, because the powerful, lightweight module also monitors its own state of health and can predict component failure before it occurs.

Unlike a typical brick-like power module, ULIS winds its circuits around a flat, octagonal design. The disk-like shape allows more devices to be housed in a smaller area, making the overall package smaller and lighter. At the same time, novel current routing allows for maximum magnetic flux cancellation, contributing to the power module's clean, low-loss electrical output—in other words, its ultrahigh efficiency.

"Our biggest concern was that the device switches off and on very quickly, and we needed a layout that wouldn't create a chokepoint within the design," said Shuofeng Zhao, an NREL power electronics researcher who designed ULIS' flux cancellation architecture. One of the original layouts, Zhao said, looked like a flower with a semiconductor at the tip of each petal.

Another idea was to create a hollow cylinder with components wired to the inside. Sarwar Islam, another NREL power electronics researcher on the ULIS team, came up with the 2D structure, which made it possible to build the module balancing complexity with cost and performance.

"We squished it flat, like a pancake," Zhao said, "and suddenly we had a low-cost, high-performing design that was much easier to fabricate."

Where conventional power modules rely on bulky and inflexible materials,

also ULIS takes a new approach. Instead of dissipating excess heat by bonding copper sheets directly to a ceramic base, ULIS bonds copper to a flexible polymer, called Temprion, to create a thinner, lighter, more configurable design.

Because the material bonds easily to copper using just pressure and heat, and because its parts can be machined using widely available equipment, ULIS can be fabricated quickly and inexpensively, according to the NREL team. Manufacturing costs total hundreds, rather than thousands, of dollars.

A further breakthrough allows ULIS to function wirelessly, as an isolated unit that can be controlled and monitored without external cables. A patent for this low-latency wireless communication protocol is pending. ULIS can scale to accommodate advancements in semiconductor devices using SiC, GaN, and even gallium oxide.

Our biggest concern was that the device switches off and on very quickly, and we needed a layout that wouldn't create a chokepoint within the design

## UK can lead modern grid technology, says new report

UK's CSA Catapult highlights potential of solid-state transformers in providing a more intelligent and flexible energy grid

THE UK has all the ingredients to take advantage of a promising new semiconductor technology that will make our energy grids smarter, more reliable and less prone to blackouts, according to a new report published by Compound Semiconductor Applications (CSA) Catapult.

Solid state-transformers (SSTs) are an advanced type of transformer that use power electronics and high-frequency components to convert and control electricity.

They are extremely useful for integrating renewable energy sources and energy storage systems into the grid, as well as managing surges and disturbances, reducing the likelihood of blackouts.

In April this year, a major blackout occurred across Spain and Portugal, disrupting power for more than 10 hours and causing economic losses of an estimated \$1.6 billion.

Compound semiconductors such as SiC and GaN, are the material of choice for this application as they can handle higher voltages, operate at higher frequencies, and perform better at higher temperatures.

Even though SSTs are still a nascent technology, the SST market is projected to grow at a double-digit compound annual growth rate (CAGR) through to 2030. Similarly, the market for SiC power devices is expected to grow at over 20 percent CAGR over the same period. The total global investment in power grid technology was projected to peak at nearly \$400 billion in 2024, whilst global spending on renewables hit a record \$735 billion in 2023.

In the UK alone, there are over 500,000 substations that could benefit from

new SST upgrades. Between 2020 and 2023, over 100,000 traditional dielectric transformers were sold in the UK, generating over £90 million in revenue. Compared to traditional transformers, SSTs are much smaller and lighter, better at regulating voltage and more flexible—they can also convert between AC and DC electricity and help send electricity back into the grid.

Outside of the energy grid, SSTs can also be used to manage power in EV chargers, data centres, and electric rail, marine and aerospace applications. SSTs will modernise EV charging by providing compact, efficient systems that support high-power, ultrafast charging solutions and a seamless link into renewable energy sources. Global companies are already developing SiC-based SSTs that can achieve up to 96.5 percent efficiency and reduce carbon footprint by 40 percent, weighing up to 70 percent less.

The report estimates that between 300,000 and 800,000 EV charges could be installed in the UK by 2030, providing a market opportunity of between £570 million and over £4.5 billion.

To overcome the hurdles facing the commercial development of SSTs, the report calls for a more coordinated between academia, industry, and government, improved funding and regulatory frameworks, and the development of large-scale pilot projects to test the technology in the real world.

Nick Singh, chief technology officer at CSA Catapult said: "As the energy landscape evolves and we introduce more renewables into the grid, SSTs have the potential to modernise our infrastructure and transform the way we move electricity around the system.

"Their ability to integrate seamlessly with distributed energy resources, bidirectional power flow, and real-time monitoring will place them at the heart of smart grids and create a whole host of new and advanced applications.

"The UK is in a strong position to take this technology forward with a flourishing power electronics and compound semiconductor ecosystem that is needed to take this technology from concept into real world applications."

## ORNL team develops fast circuit breaker for the modern grid

Medium-voltage thyristor-based circuit breaker could help reduce future electricity costs and expand capacity

RESEARCHERS at the US Department of Energy's Oak Ridge National Laboratory (ORNL) have developed medium-voltage solid state circuit breakers capable of handling increasing levels of direct current at a lower cost, an advance that can help reduce future electricity costs and expand capacity in an overburdened US grid.

"The lack of medium-voltage circuit breakers for direct current has been an obstacle to flexibility in delivering electricity," said Prasad Kandula, lead researcher. "Developing this technology helps keep the grid working safely and reliably while keeping more energy available to support our growing population and economy."

"Once you go to DC, that 'zero current' moment is gone - and without it, a mechanical switch isn't fast enough to stop a fault before heat builds up and a fire starts," said Kandula, who leads ORNL's Grid Systems Hardware group. To tackle this problem, ORNL researchers are designing and scaling up the capacity of a seminductor-based circuit breaker, which can operate a hundred times faster than mechanical switches. This enables wider use of DC in the electric grid as it becomes more attractive to energy system designers for its efficiency, flexibility and compatibility with modern energy sources and loads.

Until now, semiconductor breakers have been too expensive to either compete economically with mechanical breakers for AC, or to facilitate expanded use of DC grids. No type of commercial breaker can handle DC above 2,000 volts, and most can't achieve half that. Kandula and his team set out to find a cost-effective solution and chose a thyristor. Thyristors cannot be directly 'switched' off, so the team also had to design an external circuit

> Prasad Kandula and Marcio Magri Kimpara set up testing of ORNLdeveloped medium-voltage circuit breakers

to forcibly reduce the current. In ORNL's Grid Research Innovation and Developmentcentre, or GRID-C, engineers built and tested a circuit breaker prototype to interrupt a current at 1,400 volts in less than 50 microseconds – four to six times faster than had been demonstrated with thyristors previously. To prove the technology could be scaled up to handle higher voltages, researchers connected the breakers in a series. This approach comes with several technical challenges: First, the voltage must be shared evenly across all breakers, to prevent any single device from becoming overloaded and failing. Second, creating a series of breakers must not delay the system's rapid reaction time.

ORNL researchers designed solutions and tested them in a series of breakers operating up to an 1,800-volt testing capacity. They are already working on adding to the series for eventually scaling up to 10,000 volts, anticipating the larger energy demands of future DC grids. The project is part of a larger ORNL initiative to develop a menu of stackable medium-voltage building blocks for expanding new power applications in U.S. transportation, manufacturing and data centres.

## UW-Madison opens ultra wide bandgap lab

THE University of Wisconsin-Madison has opened an Ultra-Wide Bandgap Semiconductor MOCVD Laboratory, a facility that will focus on the emerging class of ultra wide bandgap III-nitride semiconductors such as AlGaN and AlN.

At the moment, fabricating and characterising ultra-wide bandgap semiconductors is challenging because they require expensive equipment and deep expertise in MOCVD or other advanced commercialisation- friendly deposition techniques.

Shubhra Pasayat (pictured above centre), who oversees the new facility as the lab's principal investigator, set up a commercial Aixtron MOCVD reactor for research when she first joined UW-Madison in 2021.

The new facility takes this to the next level with an Agnitron Agilis 100 system that can handle higher temperatures and lower pressures.

This will allow Pasayat and her students to design and precisely synthesise high-quality two-inch diameter wafers of high-aluminium content ultra-wide bandgap materials.

The lab is described as being at the centre of UW-Madison's rising Ill-nitride ecosystem. The onsite faculty's broad expertise in chip design and architecture, materials characterisation, fabrication, advanced packaging, and systems integration means these ultra-wide bandgap semiconductors can go from the drawing board to the motherboard all on one campus – streamlining and improving the research process.

# IGCT highest power density for most compact equipment

The IGCT is the semiconductor of choice for demanding high-power applications such as wind power converters, medium-voltage drives, pumped hydro, marine drives, cogeneration, interties and FACTS. Hitachi Energy's range of 4500 to 6500 V asymmetric and reverse conducting IGCTs deliver highest power density and reliability together with low on-state losses.

## How AI will drive growth in Power Semiconductors, from the (data) centre to the edge

The industry is facing a challenge to keep up with the ever-evolving demands of the big Al players. This is a challenge we should all embrace.

#### BY CALLUM MIDDLETON, PRINCIPAL ANALYST: POWER SEMICONDUCTORS AT OMDIA

THE ONE certainty that seems to come with AI is that it will change the world around us in uncertain ways. Beyond the chatbots that many now interact with daily, AI is being applied in unseen ways to improve efficiencies in processes as mundane as planning applications and as exciting as drug discovery.

Taking the former example, local councils in the United Kingdom have been using Al to scan and analyse historical planning documents which were typically handwritten and contained hand-drawn sketches.

The Al tools then produce digitised copies, which can be easily queried and cross-compared against other documents, speeding up decision

making. What took two hours, now takes 3 minutes.

If all of this seems incredibly dull, that's probably because it is! When people imagine the Al future they often picture a dystopian world of miracle drugs and humanoid robots moving through neon drenched metropolises, but not necessarily how efficient the planning process must be to achieve that future. The reach of Al will go far beyond the headlines.

There is currently a very significant build out in data center capacity to allow for AI to touch as many applications as possible. Data centers are critical in the training of foundational AI models. These models form the basis of AI capability and new generations

are often the result of months or even years work of development. Training foundational models is incredibly energy intensive, using the latest generations of GPUs and huge amounts of data.

Once these foundational models have been trained, secondary level models can be developed which provide the utility. They can be optimised for different applications whether that is through training on specific datasets, or for optimising efficiency. They can be specific to certain fields or certain companies and are often also trained in data centers via the cloud, although it is also possible to achieve this through servers located at the edge.

The final rung in the ladder is inference - how we all interact with AI regularly. This may be by asking questions of a chatbot, generating an image, or analysing data. This is the least computationally intensive aspect of the process and can be performed in the cloud (i.e a data center), or at a secure edge server.

Secondary models can be designed to be loaded and compute at the extreme edge, such as on a phone or laptop, allowing for no data transfer, improved security, and personalisation.

This spectrum of energy usage, from the beating heart of foundational training to the capillaries of inference at the edge will be demanding. The challenges will be different but the fundamental nature of one those challenges, how do we do this as efficiently as possible, will remain

consistent. Power semiconductors of all flavours will have a part to play. Data centers have been constrained by what came before. Prior to the launch of ChatGPT in November 2022 very few server racks operated at above 30 kW. From 2023 onwards 50 kW became the baseline for an Al server rack operated by the likes of Meta, AWS or Oracle. Google pushed things to 100 kW, and the race to higher power continues.

To meet the need for rapid deployment these AI server racks were often upgraded versions of traditional racks and new infrastructure was based on existing standards. Two core architectures were used, one with dedicated AC-DC power supplies in each shelf of the rack, and one with a shelf housing all AC-DC power supplies and a bus taking power to neighbouring shelves containing compute functions. To increase the power in a rack it is possible to use more power supplies, but this is not desirable as it takes away precious compute space.

The alternative is to increase the power density of each power supply – an approach that brings power semiconductors to the forefront. Prior to ChatGPT, a standard form factor power supply rated at 3.3 kW was considered high performance, with 5.5 kW representing the cutting edge. As of time of writing, reference designs are available for power supplies at 8 kW and even 12 kW levels in the same form factor, representing a more than doubling of power density.

This can only be achieved through the adoption of wide bandgap semiconductors. Both silicon carbide and gallium nitride have their advantages. Silicon carbide can be used effectively in totem pole configurations in the PFC front end of the power supply. GaN is suited to resonant LLC converters in the back end. Whilst it is possible to just use one of these materials, using both in concert delivers the highest performance.

Eventually, this process of upgrading existing infrastructure and designs will reach its limit. A step change is required and this has been outlined by Nvidia who have suggested that data centers should use a high voltage (800 V, +/-400 V) DC bus with power supplies replaced by a sidecar – an entire rack dedicated to converting voltage to an

intermediate 48 V DC bus which is taken to the server racks. This provides three options for wide bandgap power semiconductors – silicon carbide in solid state transformers to achieve the 800 V DC bus, silicon carbide or gallium nitride in the sidecar to convert to the 48 V DC bus, and then gallium nitride in conversion of 48 V to 12 V or to point of load.

Wide bandgap semiconductors have gone from complementary to cornerstone. It is no coincidence that Nvidia, when naming their semiconductors partners for future data center architectures, referenced leaders and specialists in silicon carbide and gallium nitride devices. Beyond power density, wide bandgap-based data center power distribution will reduce running costs.

This positive story comes at a critical time for the power semiconductor industry. Omdia finds that revenue from discrete power components dropped by 9.9% in between 2023 and 2024. For power modules this drop was 5.0% and for power IC's it was 3.5%. The post pandemic period gave several years of growth kick started by spending on home work and entertainment during lockdown periods and was then powered forward by renewable energy and electric vehicles. Investment poured into the industry, but as these applications faltered one by one, the classic semiconductor cycle appeared. Over-capacity occurred, inventories built up, and several components faced severe ASP pressure.

There are signs that inventories are being digested, and demand is picking back up. For the most part wide bandgap semiconductors managed to withstand the headwinds in the wider market. However the emergence of a dynamic growth market is certainly welcome. Silicon carbides rise has been closely tied to the EV industry whilst gallium nitride has been not expanded beyond power adaptors as rapidly as expected.

Whilst the numbers for data center investments are eye-catching, it is worth providing perspective. The compute components within the server are absorbing an ever-greater proportion of the investment and all systems are becoming more complex. At Omdia we have estimated that demand for

high voltage (600-1200 V) devices for Al data centers can hit 120-150 million shipments by 2030, made up of a mixture of silicon carbide, gallium nitride, and silicon solutions. Based on current forecasts this is expected to be an order of magnitude lower than the equivalent shipments in electric vehicle applications, which is the market that will dominate power semiconductors in the future. Data centers provide a high-quality secondary market that aids diversification and pushes innovation.

Some worry that once the next big foundational models are trained, the demand for compute will dry up and with it the demand for high performance power distribution.

However as discussed earlier there is always another rung on the ladder of Al. Compute is a scarce resource and so will be quickly distributed to secondary models or inference applications, increasing the reach of Al and making it more affordable.

Away from the data center, the main target for improving efficiency in edge AI is within the models themselves. High performance power management ICs will be needed to ensure power is delivered when and where it is needed. The biggest impact will be in convincing consumers to part with their hard-earned cash. With many countries facing cost-of-living difficulties, and many consumers having upgraded their tech during the pandemic, the refresh time on items such as phones and laptops has been getting longer and longer.

Power semiconductor manufacturers should use data centers as their moonshot. Developing devices that can match the incredible demands placed here will surely mean better devices across a range of complimentary applications. EVs may provide the scale, but partnering with and suppling the likes of Nvidia will add to brand recognition and value.

Much like those hyper efficient planning decisions we are promised, power semiconductors are essential if not celebrated. The industry is facing a challenge to keep up with the everevolving demands of the big Al players. This is a challenge we should all embrace.

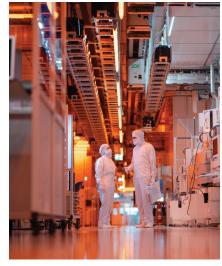

## Infineon reports strong earnings as Smart Power fab advances

Rising power semiconductor revenues boost Infineon while Dresden expansion heads towards 2026 production.

## BY REBECCA POOL, TECHNOLOGY EDITOR

AMID geopolitical turbulence from US tariff concerns, Germany-based chipmaker Infineon recently raised its profit outlook. In the company's Q3 earning call, CEO Jochen Hanebeck, noted that rising revenues in Green Industrial Power and Power & Sensor Systems segments, in particular, delivered strong quarterly earnings.

According to Hanebeck, key applications such as power infrastructure, renewable energy, as well as automation and drives contributed to 'sequential improvement'. Meanwhile rising demand for energy-efficient power semiconductors in Al

servers for data centres also drove growth.

Hanebeck also revealed how Infineon's semiconductor modules will be used in a China-based power project combining large-scale, 400 MWh energy storage with photovoltaics to supply around 270,000 homes. And he noted Infineon's recent collaboration with Nvidia to develop 'the industry's first' 800V high-voltage, direct current power delivery architecture for Al data centres.

"In a very volatile environment, Infineon has again produced sound results," he said. "Semiconductor markets are recovering slowly from a long downturn... that affected different markets at different times, [but] there are signs of an upward trend at last." "Because of US tariffs, customers are ordering at short notice and we are seeing inventories being built up – so we're also encountering a headwind for our business development," he added.

#### Dresden expansion

Buoyed by the strong quarterly earnings and following final approval from the German government, Infineon is now pressing ahead with its long-term plan to construct a Smart Power Fab in Dresden. The facility, "The Smart Power Fab is more than just a construction project – it is a strong commitment to Dresden as a location and to the future of European microelectronics."

Infineon Dresden Site Manager, Raik Brettschneider

designed to produce 300 mm siliconbased wafers, is intended to meet the growing demand for analog/ mixed-signal technologies and power semiconductors across renewable energy, data centre, and electromobility applications – the same sectors driving Infineon's latest results. Public funds total €1 billion, coming from the European Chips Act and EU's important project of common European interest in microelectronics and communications, while Infineon is investing more than €5 billion in capital at the site.

In a recent update to Power Electronics World, Infineon confirmed shell construction is complete, with the first tools to be brought online soon. Production is set to start during 2026 and ramp according to market demand. While traditional fabs can take weeks or even months to reconfigure product lines, the company also also highlighted that innovative prediction systems in the Smart Power Fab promise to enable technology changes in mere days.

"Close and trusting cooperation with the authorities, politicians and our partners has been and remains a key factor in the impressively rapid implementation of this gigantic project," commented Infineon Dresden site manager, Raik Brettschneider. Once up and running, the new fab is expected to create around 1000 highly-qualified jobs. It will also be closely linked to Infineon's Villach site, home to 300 mm wafer production, which the company says will give it the flexibility to very quickly supply chips to customers.

But it's not just about manufacturing chips. The Dresden expansion will undoubtedly contribute to the European Commission's objective of reaching a 20 percent share of global semiconductor by 2030, as part of the Chip Act. Indeed, Infineon itself is clear that the new fab will be critical to strengthening the European semiconductor supply chain.

Infineon has claimed that every third chip in Europe is already manufactured at its existing Dresden site, and the expanded fab will better help to secure value chains in the key European industries – with its ability to react rapidly to market segment changes helping to ensure resilient supply. "The Smart Power Fab is more than just a construction project – it is a strong commitment to Dresden as a location and to the future of European microelectronics" says Raik Brettschneider

So as the Smart Power Fab in Dresden

> Construction site of Infineon's Smart Power Fab in Dresden. [Infineon]

➤ Dresden cleanroom, 300 mm cleanroom at Infineon Dresden's existing site. [Infineon]

readies for production, the outlook for Infineon remains strong. In his recent earnings call, Hanebeck noted that 70% of its 2024 revenue related to power discretes and modules, based on silicon, silicon carbide and gallium nitride materials, as well as analog semiconductors and sensors, including smart power switches. And continued growth is expected.

Revenues for the September quarter are predicted to reach around €3.9 billion, equating to about 5% sequential growth, which as Hanebeck said: "[makes] our fourth quarter the strongest as usual." Hanebeck also pointed out how his company is "taking advantage of opportunities in strategic growth areas" including power supply solutions for AI data centers, rapidly increasing investment in energy infrastructure, and software-defined vehicles - strengthened by the firm's upcoming acquisition of Marvell's Automotive Ethernet business. "In these areas, semiconductor demand is increasing in the long term," he said. "Infineon, with its portfolio... is ideally positioned to play a role in shaping these markets."

## Reshaping gate drivers for next-gen electrification

As the need for higher performance, precision, and efficiency mounts, gate driver technology is becoming more essential than ever. Advancing the technology to overcome traditional limitations will be key to truly unlocking this next generation of electrification.

#### BY EMMANUEL ONYEMA, AUTOMOTIVE PRODUCT LINE MANAGER AT SKYWORKS.

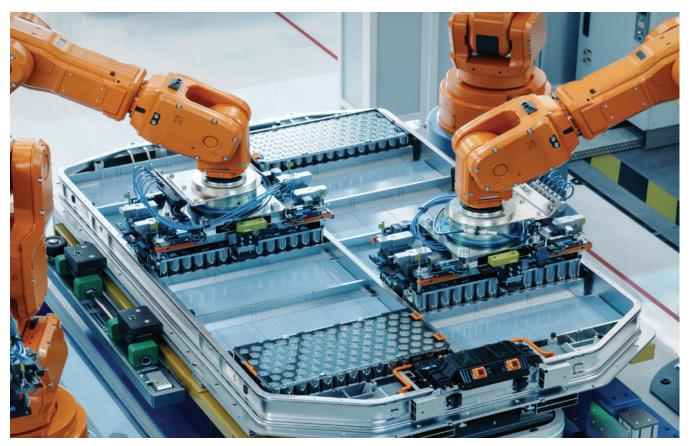

INDUSTRIAL ROBOTICS and renewables applications are at the leading edge of electrification and automation, yet they are only as effective as their underlying power and control circuitry.

Reports suggest that the power electronics global market for EVs alone will grow at a CAGR of 17% from 2025 to 2035. Gate drivers play a pivotal role in meeting this sustainably, yet currently, traditional gate driver architectures face significant shortcomings in power loss and adaptability.

As the need for higher performance, precision, and efficiency mounts, gate driver technology is becoming more essential than ever. Advancing the technology to overcome traditional limitations will be key to truly unlocking this next generation of electrification.

#### What is a Gate Driver?

Taking a step back, power electronics circuits are responsible for controlling the movement of electrical current through a system, utilizing three components: power switches, called Field Effect Transistors (FETs); gate drivers and MCUs.

The FET specifically is responsible for enabling or disabling the flow of current, equipped with on/off switching

behavior. This allows it to turn on when gate voltage exceeds a certain amount and turn off when it falls below a certain amount. From there, the FET's gate acts as a sensor that builds up a charge to turn it on. The speed and strength at which the gate driver sends its control signal determines the efficiency of the FET and, in turn, the entire system. Meanwhile, the MCU is running the entire operation by providing signals to control the gate driver's movement.

#### Traditional Gate Drivers: Consistent but Inflexible

Traditional voltage mode drivers (TVMDs) have historically been the preferred architecture for engineers because they are simple. They function as a voltage source able to activate and turn off the FET quickly. However, the demands of modern power electronics today have revealed TVMD's limitations in performance and efficiency.

Take today's EVs, for example; onboard chargers often operate in varied conditions where the gate driver may need to adjust its behavior depending on temperature or output. With TVMDs, once the resistor values are set, they cannot be changed, hindering the ability to optimize currents for differing temperatures. This is a fundamental

lack of flexibility in TVMDs that could mean significantly shorter battery range and slower charging. As demand for longer ranges and faster charging increases, automakers simply can't afford these operational shortcomings. Additionally, limits in slew rate, the maximum speed at which a voltage can change in a circuit, have become a great design consideration. Advanced gate driver designs are largely in two camps: high-current drivers that can handle more power but require careful resistor tuning, or multi-output drivers, which boost current capacity by splitting the load across multiple paths, thus improving switching speed but can be costly and complicate the design.

Each approach introduces its own unique set of benefits but also challenges: either a risk of oscillations or lower efficiency.

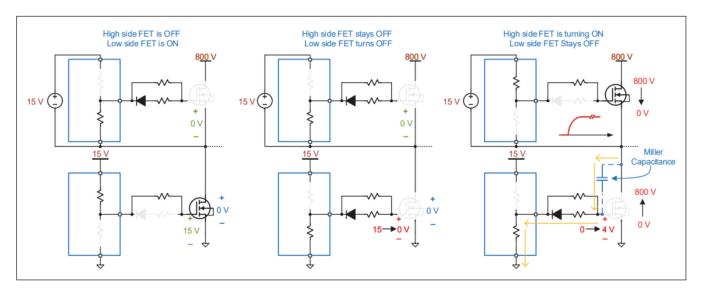

Outside of this, the Miller Effect, which is essentially the unintended electric charge caused by the small space between two circuit components, can trigger unintended FET turn-on and potentially result in system failure. When looking at the full picture, it's clear that power loss has become a major hurdle to overcome within the gate driver architecture. Next-

generation applications require gate drivers that provide strong current, respond quickly and precisely to triggers, and are adaptable to different environmental setups. They also need to be highly resistant to electrical noise to ensure they work reliably in any environment, no matter what the strain. Leading industry players have integrated active Miller clamp functionality to suppress the unintended gate turn-on, which improves immunity against these events.

To address these challenges, the industry is tasked with creating an architectural solution that allows designers to select optimal drive profiles without external resistors, streamlines thermal and electrical tuning, and integrates active Miller clamp functionality to suppress unintended gate turn-on and improve immunity against DV/DT events.

## Enter Current-Mode Controlled Gate Drive Solutions

Current-mode gate drive solutions may be the exact solution the industry is looking for. These updated architectures offer programmable gate current with a ±10% tolerance across PVT, enabling dynamic gate current control through SPD pin configuration,

Each approach introduces its own unique set of benefits but also challenges: either a risk of oscillations or lower efficiency. Outside of this, the Miller Effect, which is essentially the unintended electric charge caused by the small space between two circuit components, can trigger unintended FET turn-on and potentially result in system failure

## TECHNOLOGY I GATE DRIVERS

matched to system conditions without discrete component tuning.

The technology offers features including programmable drive strength, which allows engineers to choose how fast or slow the switch turns. This balances the speed and efficiency necessary for different environments and tasks. Additionally, built-in protections like Miller clamps prevent accidental switching, i.e., the Miller Effect.

This is the type of flexibility needed in programming and power optimization, especially in applications like EVs, where power systems are exposed to harsh and varied conditions depending on weather, load variability, and temperature fluctuations. A current mode gate driver's ability to monitor and adjust its performance unlocks a level of system control that a TVMD would not be able to offer.

#### What's next?

While future integration paths are being

explored, next-generation electrification technological advancements seem to be going in the direction of fully integrated gate drivers into the power switches, making systems smaller and more reliable. These drivers are set to support more automotive systems alongside industrial and renewable energy applications, with their greater adaptability to harsher temperatures and conditions.

Maintaining efficient switching performance across varying temperatures and supply voltages remains a common challenge in EV and industrial power systems. Technology like current-mode controlled gate drive addresses this by providing programmable gate current, which is configured via the SPD pin to tune drive strength per application need. This eliminates reliance on fixed external resistors and ensures consistent switching behavior across power, voltage, and temperature variations. Additionally, integrated features like active Miller clamp and

output discharge enhance robustness against noise and unintended turn-on, which streamline reliability under stress.

As power needs across the industry continue to accelerate, adaptive control will become a must-have in power electronics architecture. Having the ability to diagnose, control, and adjust your power systems will become the new normal for optimal performance, efficiency, and safety in EVs and all power electronics.

## HIGH-VACUUM BONDING

## EVG® ComBond®

Oxide-free, covalent wafer bonding High-vacuum process environment Room-temperature process

**GET IN TOUCH** to discuss your manufacturing needs **www.EVGroup.com**

## Harnessing the sun: semiconductors in solar inverters

The shift toward GaN and SiC technologies not only improves the size, weight, and cost-effectiveness of solar inverters but also enhances their efficiency, potentially breaking through the 99% efficiency barrier.

#### BY MATHIS FLANDRIN, GLOBAL BUSINESS DEVELOPMENT SPECIALIST, NEXPERIA.

ACCORDING to the International Energy Agency's (IEA) latest research, 77% of renewable capacity additions in 2028 will be solar energy, with an impressive 640 gigawatts (GW) of capacity added annually. As one of the most abundant and sustainable sources of power, solar energy harnesses the sun's energy and converts it into electricity using photovoltaic (PV) systems. At the heart of these systems is the solar inverter, a critical component that transforms the direct current (DC) generated by solar panels into alternating current (AC) suitable for use in homes and on the grid. Semiconductors play a pivotal role in the operation of solar inverters, and we explore their functions, benefits, and latest advancements.

Solar inverters are essential for the functioning of PV systems, acting as the

bridge between solar panels and the electrical grid or home power systems. The conversion process involves two main stages:

- ODC/DC conversion stage: where the Maximum Power Point Tracking (MPPT) algorithm optimizes the power output from the solar panels by adjusting the voltage to ensure maximum efficiency.

- DC/AC conversion stage: the optimized DC power is then converted into AC electricity, making it suitable for household use or feeding into the grid.

This dual-stage process ensures that the power generated by the solar panels is efficiently converted, minimizing energy losses and enhancing overall system performance.

# DC/DC Conversion DC/DC Conver

> Simplified block diagram of a hybrid solar inverter.

## Inverter topologies and functionality

Solar inverters utilize various topologies to achieve the best efficiencies, with two-level and three-level topologies being the most common. Two-level inverters, which are simpler and widely used in smaller systems, switch between two voltage levels to produce AC power. Three-level topologies provide a more refined output by introducing an additional voltage level, resulting in lower harmonic distortion, reduced stress on components, and improved overall efficiency. That makes them ideal for larger, more demanding solar systems. These topologies allow solar inverters to cater to a wide range of applications, from small residential setups to large-scale solar farms. To maximize the efficiency of the solar power system, inverters use Maximum Power Point Tracking (MPPT) algorithms, ensuring that the solar panels operate at their peak power output.

In grid-tied systems, inverters manage the interaction with the electrical grid, ensuring synchronization and safe operation, while also having the capability to shut down automatically during grid outages to protect utility workers. Additionally, modern inverters often come equipped with monitoring and communication features, allowing users to track their system's performance and receive alerts in case of issues, further enhancing the reliability and convenience of solar energy systems.

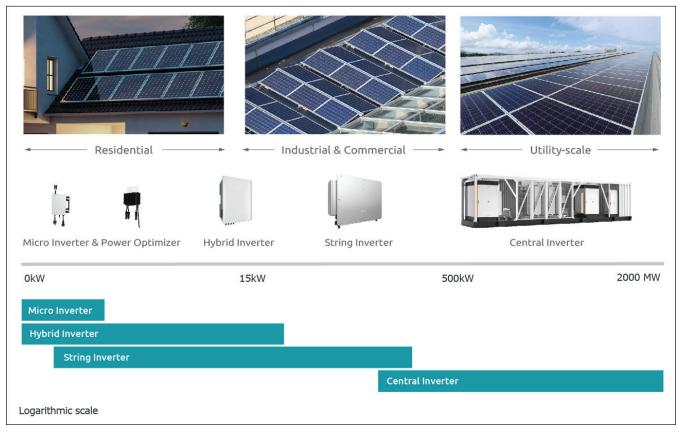

> Four main inverter types cover all installations.

## Different inverters for different applications

Since photovoltaic installations come in different sizes ranging from small residential units to grid-tied solar power plants there are different types of inverters for every application case.

- The smallest inverter, mainly used for residential installations, is the micro solar inverter. Power conversion is performed at the individual PV panel level, and they can handle power from 200 W up to 3 kW. Having a microinverter on each panel allows MPPT per panel, resulting in higher efficiency and flexibility particularly in installations with shading issues.

- Another inverter commonly used in households is the hybrid solar inverter. These devices are designed to integrate solar electricity along with battery energy storage systems and EV charging infrastructure, managing all power conversion bi-directionally. To cover today's residential purposes, the current power range for hybrid inverters typically goes from 1 kW up to 50 kW.

- Often the preferred option for larger residential installations as well as commercial projects is the

- photovoltaic string inverter. This connects multiple panels in series (string) and converts the combined DC output into AC. These systems typically operate in a power range of a few kilowatts up to several hundred kilowatts.

- For the biggest utility and grid-tied solar projects one central inverter is at the heart of the solar power conversion process. These large box-shaped devices handle output power ranges from a few hundred to several thousand kilowatts.

## Semiconductors in solar inverters

Semiconductors are the backbone of solar inverters, playing a crucial role in the conversion and management of electrical energy within PV systems. Key semiconductor components like IGBTs, MOSFETs, diodes and bipolar transistors are integral to the inverter's operation.

IGBTs are widely used in solar inverters for their ability to efficiently handle high voltages and currents, making them ideal for power conversion tasks. They offer the benefits of both high-speed switching and low conduction losses,

- which are essential for both MPPT and DC-AC conversion processes

- MOSFETs, on the other hand, are mainly employed in lower power applications within solar inverters due to their superior switching speeds and lower gate drive power requirements, which contribute to overall efficiency improvements, especially in smaller, high-frequency inverter designs.

- Bipolar Junction Transistors (BJTs) are vital in small signal control applications within solar inverters, where they ensure precise switching and amplification of signals, maintaining stable inverter operation by efficiently controlling low-level currents and voltages in various circuits

- Diodes, another critical component, facilitate the smooth flow of electricity by allowing current to flow in a single direction, preventing backfeed that could potentially damage the inverter and other connected components.

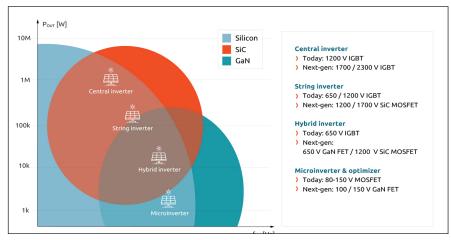

Wide bandgap a game changer The introduction of wide bandgap (WBG) semiconductors, specifically Silicon Carbide (SiC) and Gallium Nitride

## TECHNOLOGY | SOLAR INVERTERS

Co-existence of power technologies addressing different solar inverters.

(GaN), has revolutionized solar inverter technology by offering significant advantages over traditional siliconbased semiconductors. GaN High Electron-Mobility Transistors (HEMTs) and SiC MOSFETs provide superior electrical properties, including lower on-resistance, faster switching capabilities, higher breakdown voltages, and the ability to operate at elevated temperatures.

These characteristics lead to significantly lower power losses, higher efficiency, and more compact designs due to reduced cooling and passive component requirements.

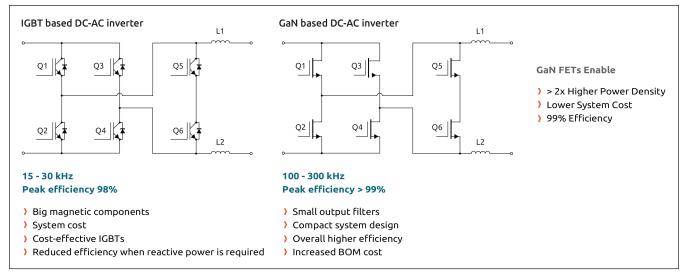

In solar inverter applications, especially in small-scale photovoltaic (PV) systems for homes and commercial buildings, GaN and SiC devices enable more efficient energy conversion and higher power densities. For instance, GaN-

based designs, such as those using Nexperia's GAN041-650WSB, can achieve switching frequencies between 100 kHz and 300 kHz, which is a substantial increase compared to the 15 kHz to 30 kHz range of traditional IGBT-based solutions.

This increase in frequency allows for smaller and lighter output filters, reduced harmonic distortion, and an overall more compact and cost-effective design with power densities that have increased from

$0.5~W/in^3~with~IGBT~modules~to~as~much~as~4~W/in^3~with~the~latest~WBG~devices.$

In single-phase string inverter configurations, where PV panels are connected in series to generate a DC voltage, the higher efficiency of GaN and SiC technologies is critical. These configurations typically involve a DC/DC boost circuit controlled by a

microcontroller or system-on-chip (SoC) that also manages maximum power point tracking (MPPT).

The output feeds DC link bulk capacitors, which can then supply power to an energy storage system (ESS) or a DC/AC inverter to provide single-phase AC for local use or the grid.

The future is bright for solar inverters The shift toward GaN and SiC technologies not only improves the size, weight, and cost-effectiveness of solar inverters but also enhances their efficiency, potentially breaking through the 99% efficiency barrier.

This leap in performance makes solar energy systems more accessible and viable, ultimately lowering the total cost of ownership and paving the way for the next generation of highly efficient and resilient renewable energy solutions.

In the future, we can expect inverters to integrate even more advanced features like smart grid compatibility, enhanced monitoring, and Al-driven energy management. These advancements will enable greater energy optimization, accelerate response times, and improve integration with energy storage systems.

Further transforming the landscape for distributed energy generation and accelerating the transition to clean, efficient solar power. All enabled by advances in power semiconductor technology.

➤ Comparing IGBT-based and GaN-based DC/AC inverters.

# Find your way in thin film technology for Power Devices with Evatec

From 300mm silicon processing to Wide Band Gap (WBG) applications on SiC or GaN, Evatec is your partner for thin film production in power devices.

Process know-how including secure thin or bonded wafer handling combined with management of wafer stress and temperature keeps you on the right track.

Visit evatecnet.com/markets/power-devices to find out how you can power ahead in your own production or contact your local Evatec Office at evatecnet.com/about-us/sales-service

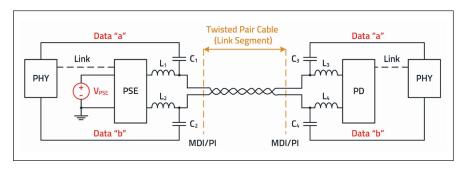

## Wide-bandgap power semiconductor device dynamic characterisation

This article outlines the technologies and techniques required for performing dynamic characterisation of SiC and GaN power semiconductor devices.

#### BY RYO TAKEDA, SOLUTIONS ARCHITECT, KEYSIGHT

WIDE-BANDGAP (WBG) power semiconductor devices, such as Silicon Carbide (SiC) and Gallium Nitride (GaN), are rapidly replacing traditional silicon-based MOSFETs and IGBTs in a wide range of power-conversion applications, including electric vehicles, solar inverters, data center power supplies, and compact chargers. Its superior material properties (wide bandgap, high breakdown voltage, high electron mobility, and excellent thermal performance) enable higher switching frequencies, lower conduction and switching losses, and smaller passive components.

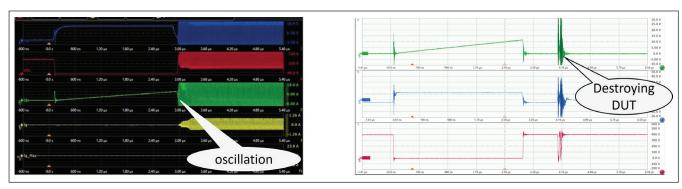

However, these benefits also come with new challenges such as extremely fast switching transitions (high di/dt and dv/dt) which intensify the effects of parasitic inductance and capacitance in test circuits, leading to waveform distortion, ringing, unintended turn-on events, and potentially damaging surge currents.

Accurate and repeatable dynamic characterisation is therefore a critical first step in designing robust power-electronic circuits using SiC or GaN devices.

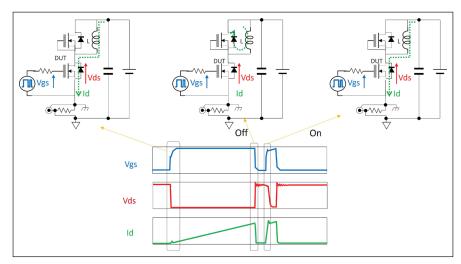

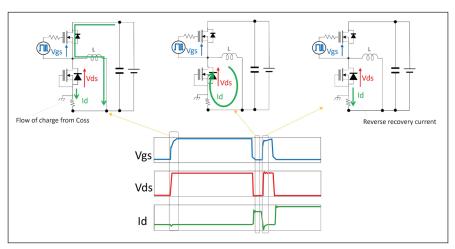

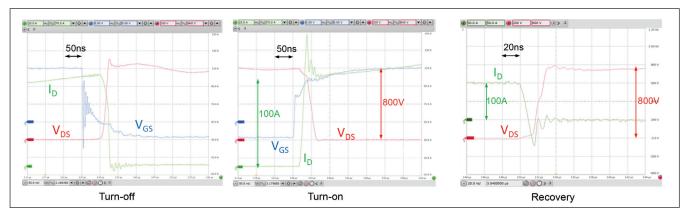

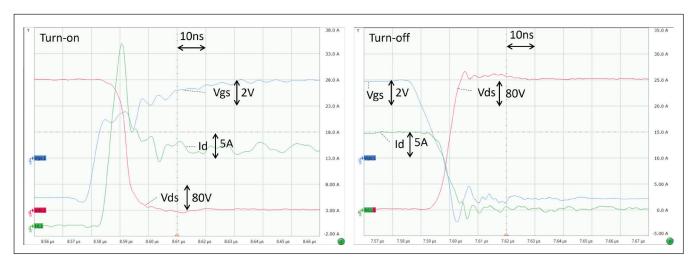

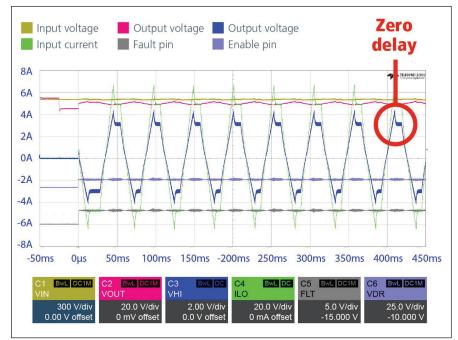

## Fundamentals of dynamic characterisation: The double pulse test

Both SiC and GaN devices are typically characterized dynamically using a double-pulse test (DPT). In this method, a half-bridge configuration of Field-Effect Transistors (FETs) is used, and two pulses are applied to the Device Under Test (DUT). When the first pulse is applied, the current begins to rise gradually due to the load inductor placed between the power supply and the DUT. The current increases linearly, with a rate inversely proportional to the inductance value. By adjusting the width of the first pulse, the target current for the switching event can be controlled. When the first pulse ends, the DUT turns off

and can no longer conduct current. However, the current continues to circulate through the loop formed by the load inductor and the body diode (or freewheeling diode) of the high-side FET. When the second pulse is applied, the DUT turns on again, and current flows through it to the ground.

This two-pulse sequence produces the waveform shown in Figure 1. The falling edge at the end of the first pulse corresponds to the turn-off characteristics, while the rising edge at the beginning of the second pulse represents the turn-on characteristics. In this way, both turn-on and turn-off switching behaviors can be conveniently captured in a single measurement.

Reverse recovery characteristics can also be measured using the doublepulse test. In this setup, the load inductor is connected between the neutral point of the half-bridge and ground. Two pulses are applied to the high-side device. By adjusting the width of the first pulse, the current is ramped up to the desired target value. When the first pulse ends, the highside device turns off, and the current continues to flow through the loop formed by the load inductor and the body diode (or freewheeling diode) of the low-side FET. During this conduction phase, charge carriers accumulate in the PN or PIN junction of the diode.

When the second pulse is applied to the high-side FET, the current commutates, abruptly turning off the diode. The stored carriers in the junction are released instantaneously and appear as a reverse-recovery

> Figure 1: Double pulse test for switching characterisation.

current, which is measured during this transition.

The DPT enables the capture of both turn-off and turn-on transitions in a single measurement cycle, making it a convenient method for quantifying switching losses (EOFF, EON) and reverse-recovery behavior. However, because SiC and GaN devices switch with sub-10 ns edges (or even sub-5 ns in GaN), parasitic inductance (Lpar) and capacitance (Cpar) in the test circuit, probes, and measurement equipment can introduce significant measurement errors such as:

- Voltage Overshoot:  $\Delta V = Lpar \cdot (di/dt)$  during turn-on or turn-off.

- Current Spikes: Ispike = Cpar·(dv/dt).

- Ringing: Fast switching edges interacting with parasitic can cause ringing.

- Probe Skew: Nanoseconds of timing mismatch between voltage and current probes can lead to inaccurate switching-loss calculations.

Minimizing these parasitics and ensuring sufficient bandwidth throughout the measurement is therefore essential for obtaining repeatable and reliable results.

## Minimizing parasitics and ensuring measurement fidelity

PCB layout and power-loop inductance When designing a PCB for a double-pulse test, maintaining a compact half-bridge layout is essential. Additionally, the forward and return current traces should overlap as much as possible to cancel mutual magnetic fields. A parallel-plane layout (i.e., placing the trace over a ground plane) helps reduce

➤ Figure 2: Double pulse test for reverse recovery characterisation.

loop inductance (see Figure 3).

One key parameter that indicates the performance of the test system is the power loop inductance, which can be calculated using the following equation. Here, VDS,droop represents the voltage dip at the drain when the drain current (Id) ramps up. This value is easily derived from the turn-on waveform and provides a practical estimate of loop inductance—unlike source or drain stray inductances, which are more difficult to isolate individually.

$$L_{powerloop} = \frac{V_{ds,droop}}{dI_d/dt}$$

Oscilloscope and probe requirements Because wide-bandgap (WBG) power devices have fast edge times—typically 8–15 ns for SiC and 2–5 ns for GaN—a bandwidth of 350 MHz or higher is required for the oscilloscope. In practice, a 500 MHz (or higher) oscilloscope is recommended for

capturing the edges of both SiC and GaN devices. To ensure accurate waveform reconstruction, the sampling rate should be at least 5 to 10 times the highest frequency component. Therefore, an oscilloscope with a sampling rate of at least 5 GS/s is recommended. For voltage probes, it is advisable to use the same or higher bandwidth as the oscilloscope, since the overall system bandwidth is determined using the following equation:

$$system\ bandwidth = \frac{1}{\sqrt{\left(\frac{1}{BWprobe}\right)^2 + \left(\frac{1}{BWoscilloscope}\right)^2}}$$

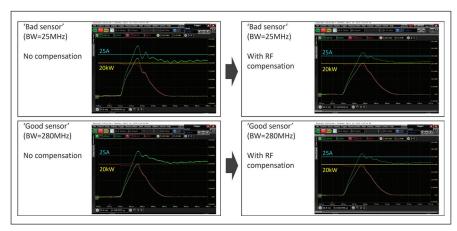

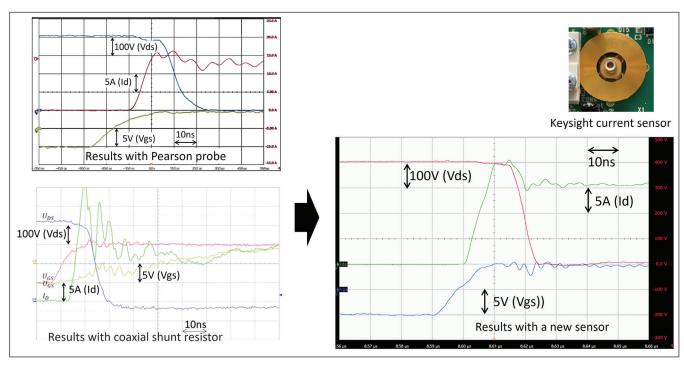

For the current sensor, since SiC devices can have edge times of approximately 8–15 ns and GaN devices as short as 2–5 ns, the sensor must capture frequency components up to at least the knee frequency ( $\approx$  90 MHz for 8 ns edges,  $\approx$  350 MHz for 2 ns edges). To meet this requirement, coaxial shunt resistors are suitable for SiC, while even

> Figure 3: Layout example & power loop calculation.

## **TECHNOLOGY I TESTING**

> Figure 4: Id and power measured with different BW sensors (Left) and adjusted results with RF compensation (Right).

higher-bandwidth current sensors are necessary for GaN.

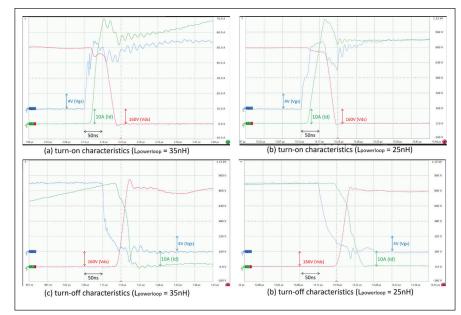

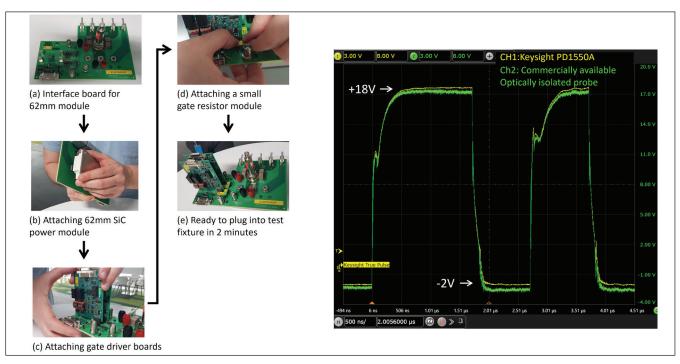

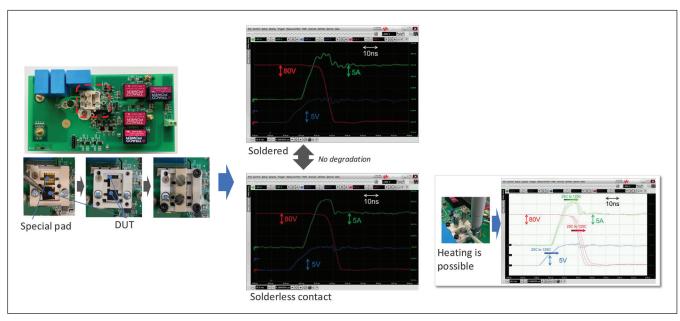

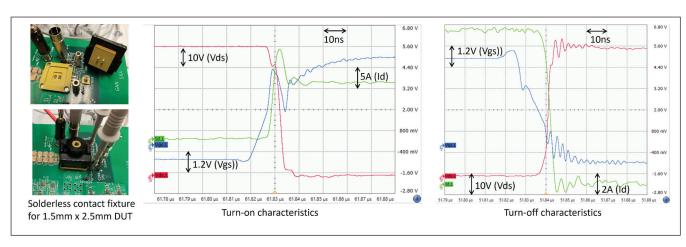

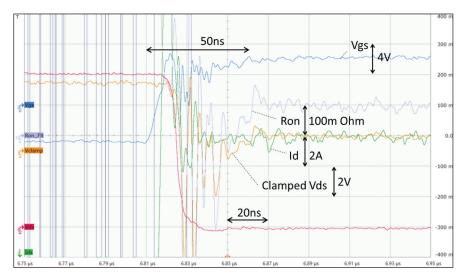

## SiC power device dynamic characterisation

Characterising SiC devices presents a unique set of requirements compared to traditional silicon devices. Due to its high voltage and current capabilities and fast switching performance, both the test methodology and equipment need to be optimized to ensure accurate, repeatable results. The following sections outline the specific challenges and technological considerations involved in reliably testing SiC devices.

#### Unique challenges for SiC

SiC MOSFETs often operate at voltages up to 1 kV and currents of