PEI

# POWER ELECTRONICS INTERNATIONAL

DESIGN + MATERIALS + PACKAGING + PERFORMANCE

ISSUE IX 2025

AN ANGEL BUSINESS COMMUNICATIONS PUBLICATION

POWERELECTRONICSMAGAZINE.NET

## ADDRESSING THE PROTECTION CHALLENGES OF 48V AI SERVERS USING HOT-SWAP CONTROLLERS

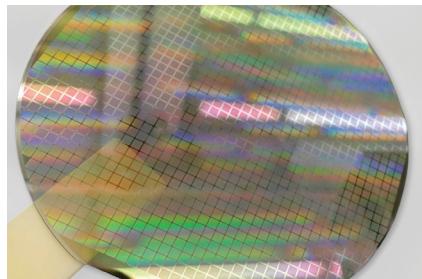

## THE NEW G10 SERIES

Your Productivity Solution for All Advanced Epitaxy Materials

### G10-SiC

- ▶ 9x150 mm (6") or 6x200 mm (8")

- ▶ New hardware & process surpassing Single Wafer Reactor uniformities

- ▶ +50% productivity per fab area with large batch technology & small footprint

#### End Markets/Products:

EV inverters & charging infrastructure

### G10-GaN

- ▶ 8x150mm (6") or 5x200 mm (8")

- ▶ 1<sup>st</sup> fully automated compact GaN MOCVD cluster designed 100% for Si Power fabs

- ▶ Novel hardware solution for unmatched barrier uniformities and device yields

#### End Markets/Products:

Power Electronics & Wireless communication

### G10-AsP

- ▶ 8x150 mm (6") or 5x200 mm (8")

- ▶ 1<sup>st</sup> fully automated AsP MOCVD system enabling 10x lower defect density

- ▶ Unmatched wavelength uniformity on all wafer sizes

#### End Markets/Products:

Micro LED, Optical Data communication, 3D-sensing & LiDAR

## Research community delivers some seasonal successes

THE PAST SEVERAL WEEKS have delivered some significant research breakthroughs across the wide-bandgap landscape — a reminder, perhaps, that power electronics is not merely an industry of incremental advancement but one continually reinventing its scientific foundations. Something of a genuine research renaissance, spanning materials, devices, packaging, metrology, and manufacturing infrastructure?

Nowhere is this more evident than in gallium nitride, where a collaboration led by North Carolina State University has achieved a nine-orders-of-magnitude reduction in the specific on-resistance of magnesium-implanted vertical p–n diodes. By boldly revisiting one of GaN's thorniest issues — realising high-quality p-type contacts after implantation — the team demonstrated performance on par with epitaxial devices. Their clever use of magnesium deposition and annealing to eliminate the parasitic Schottky barrier is not just a process optimisation; it reopens the viability of selective-area doping for advanced vertical GaN architectures. For designers of vertical MOSFETs, JBS diodes and next-generation high-voltage GaN devices, this work is strategically enabling.

IMEC's record-breaking >800 V GaN HEMT on Shin-Etsu's 300 mm QST substrate is another milestone that signals GaN's steady march into large-diameter, CMOS-compatible manufacturing. By solving the historic warpage and cracking problems that plagued GaN-on-silicon scaling, QST may become a cornerstone substrate technology — arriving just in time as AI data centres and electrified mobility demand cheaper, higher-performance GaN power devices.

SiC research, meanwhile, is undergoing its own transformation. The University of Osaka's two-step hydrogen/argon anneal — notably without nitrogen — is a decisive step forward in resolving the long-standing mobility-reliability trade-off at the SiC/SiO<sub>2</sub> interface. Achieving high mobility while suppressing threshold-voltage drift is precisely the combination needed to support 600–1200 V MOSFETs in EV and renewable-energy inverters. In tandem, NREL's Ulis

module demonstrates that SiC innovation is not confined to materials: packaging engineering can still rewrite the performance envelope. With parasitic inductance cut by nearly an order of magnitude and a design that is both lightweight and health-monitoring-capable, Ulis hints at a new breed of intelligent power modules for aviation, microgrids and defence.

If GaN and SiC dominate the headlines, gallium oxide and aluminium nitride are proving that the materials frontier remains wide open. Nagoya University's demonstration of the world's first Ga<sub>2</sub>O<sub>3</sub> p–n diodes, using industry-standard implantation and annealing steps, marks a pivotal advance for this ultra-wide-bandgap contender. Likewise, new MOVPE-grown Si-doped AlN films with tunable properties for high-temperature Schottky devices highlight how research is expanding the palette of viable power-semiconductor materials.

Even fundamental heat transport science is being rewritten. The University of Houston's discovery that ultra-pure boron arsenide can exceed 2,100 W/mK, potentially outperforming diamond, could redefine thermal management for power electronics and high-power computing alike — a rare case where theory is being forced to catch up with experiment. Crucially, this surge in research is being matched by investment in infrastructure and standards. The University of Arkansas' MUSiC facility gives the U.S. its first open-access SiC MPW fab — a powerful lever for accelerating prototyping and training. The TRACE-Ga initiative signals strategic recognition of gallium's geopolitical importance. And the ITRI–NPL partnership reflects a global push toward metrology leadership in compound semiconductors.

Wishing all our readers a happy and relaxing festive season and here's to the power electronics industry enjoying a successful 2026.

## COVER STORY

### Addressing the protection challenges of 48V AI servers using hot-swap controllers

Enabling the design of a reliable input protection solution for a 48V AI server

26

#### 14 MIT engineers develop a magnetic transistor for more energy-efficient electronics

A new device concept opens the door to compact, high-performance transistors with built-in memory

#### 16 Small material, big impact

Dr Conor O'Brien, Senior Technology Analyst at IDTechEx, explores graphene in electronic applications

#### 18 Powering the AI era: how Infineon Technologies' SiC solutions are shaping the future of data centre power supplies

As artificial intelligence (AI) continues to redefine the frontiers of computational performance, the supporting infrastructure particularly the power conversion within data centers must evolve rapidly to meet new performance and density benchmarks

18

#### 32 The rise of 800V High Voltage DC: Can collaboration drive NVIDIA's AI infrastructure vision?

NVIDIA's transition to an 800 VDC architecture for AI data centres isn't just a technological shift – it's a call for industry-wide alignment on power delivery, semiconductors and standards

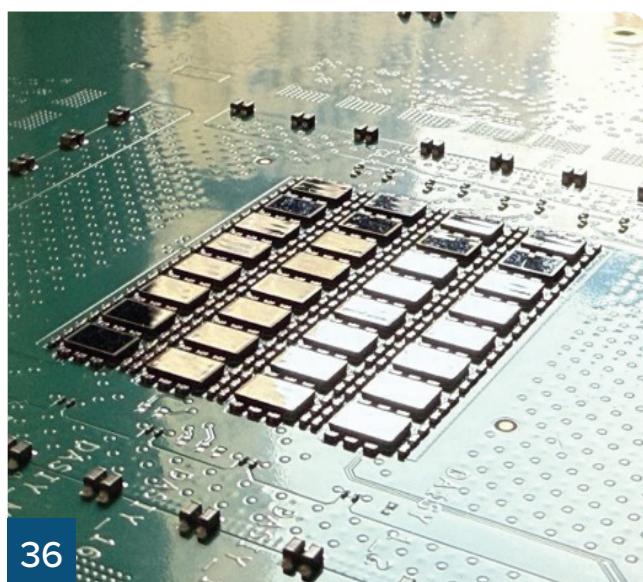

#### 36 Ferric brings power efficiency to the heart of AI chips

As power-hungry AI processors strain energy systems, Ferric's integrated voltage regulators promise more efficient power delivery

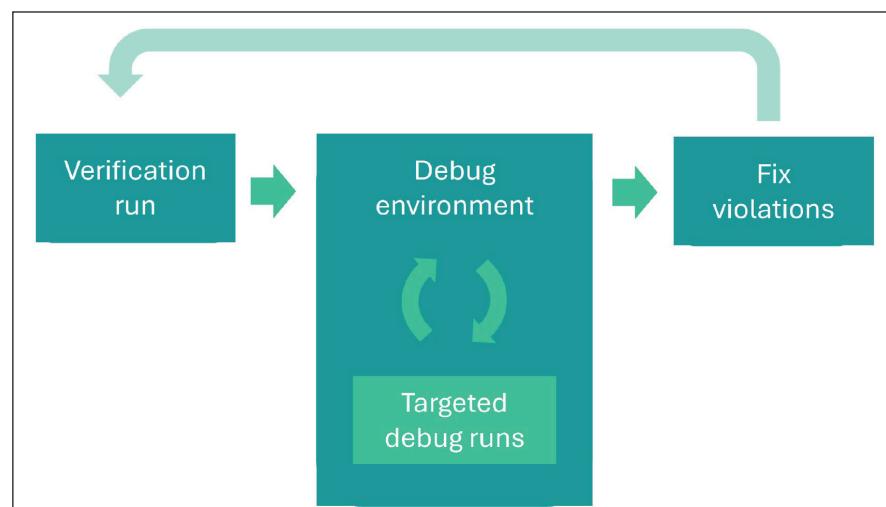

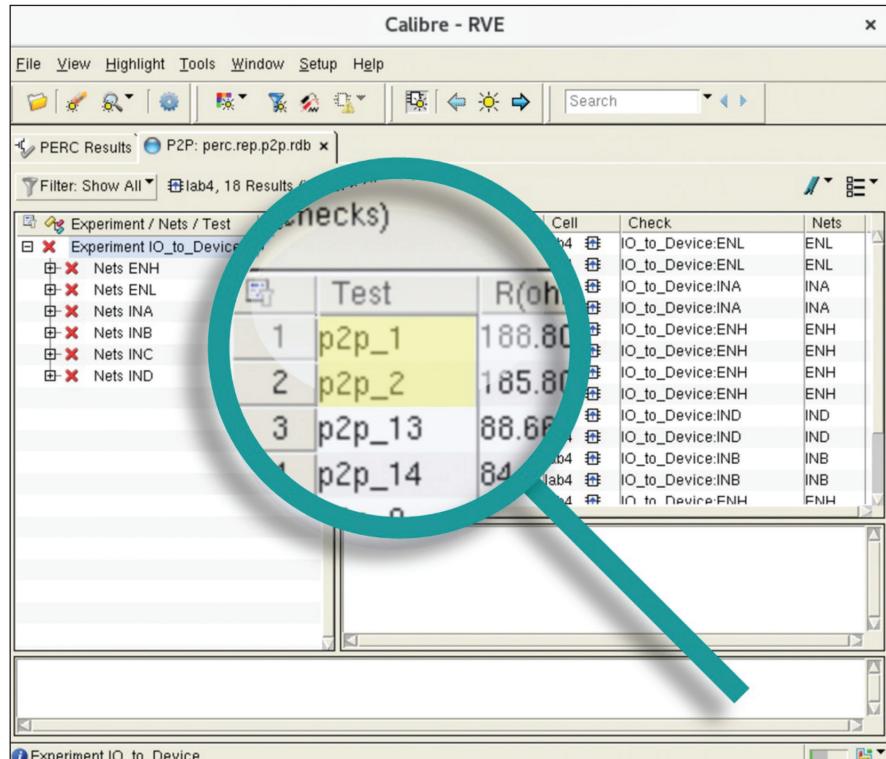

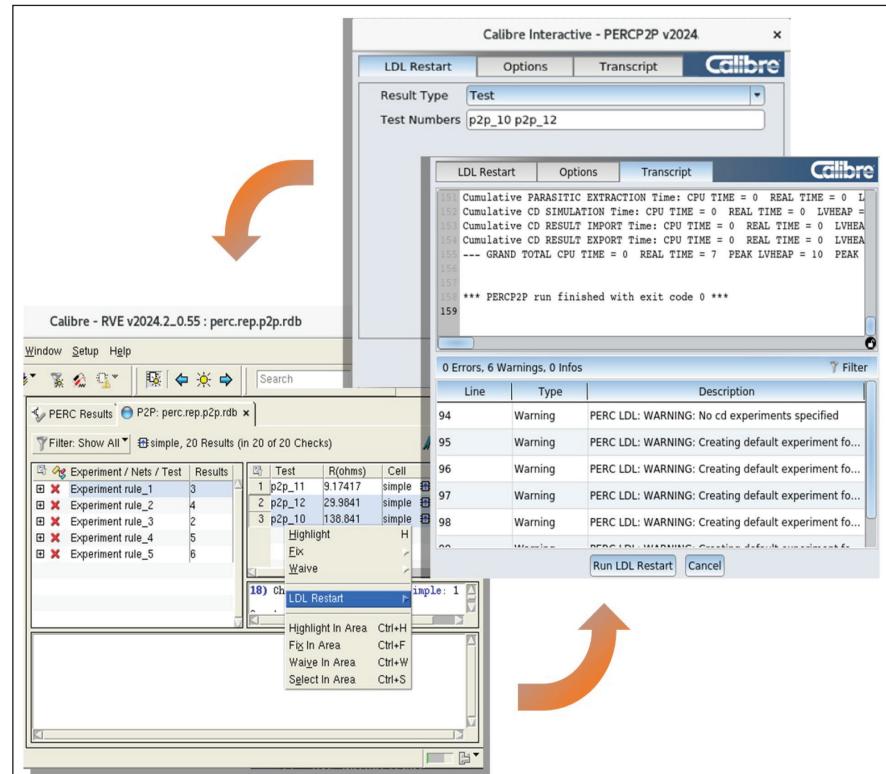

#### 40 Efficient debugging workflow in chip circuit verification - A targeted simulation approach

Chip circuit verification is a vital to the semiconductor industry, ensuring that integrated circuits meet design specifications and quality standards

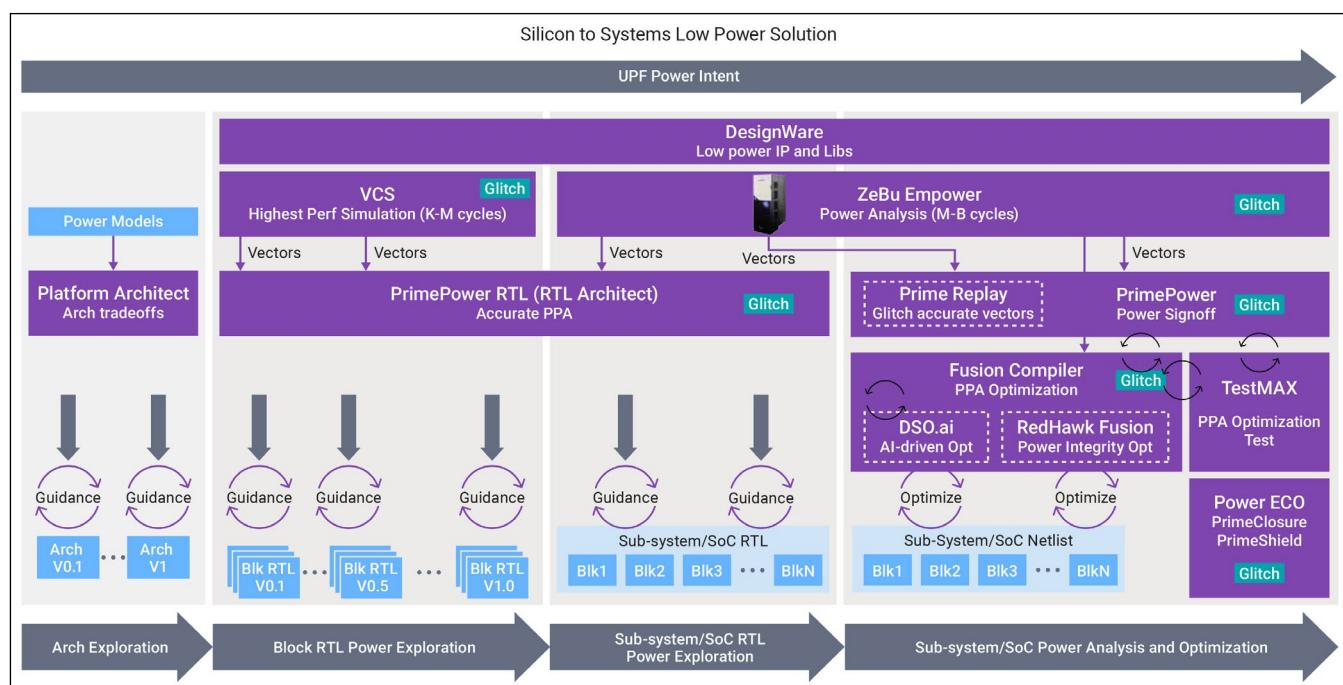

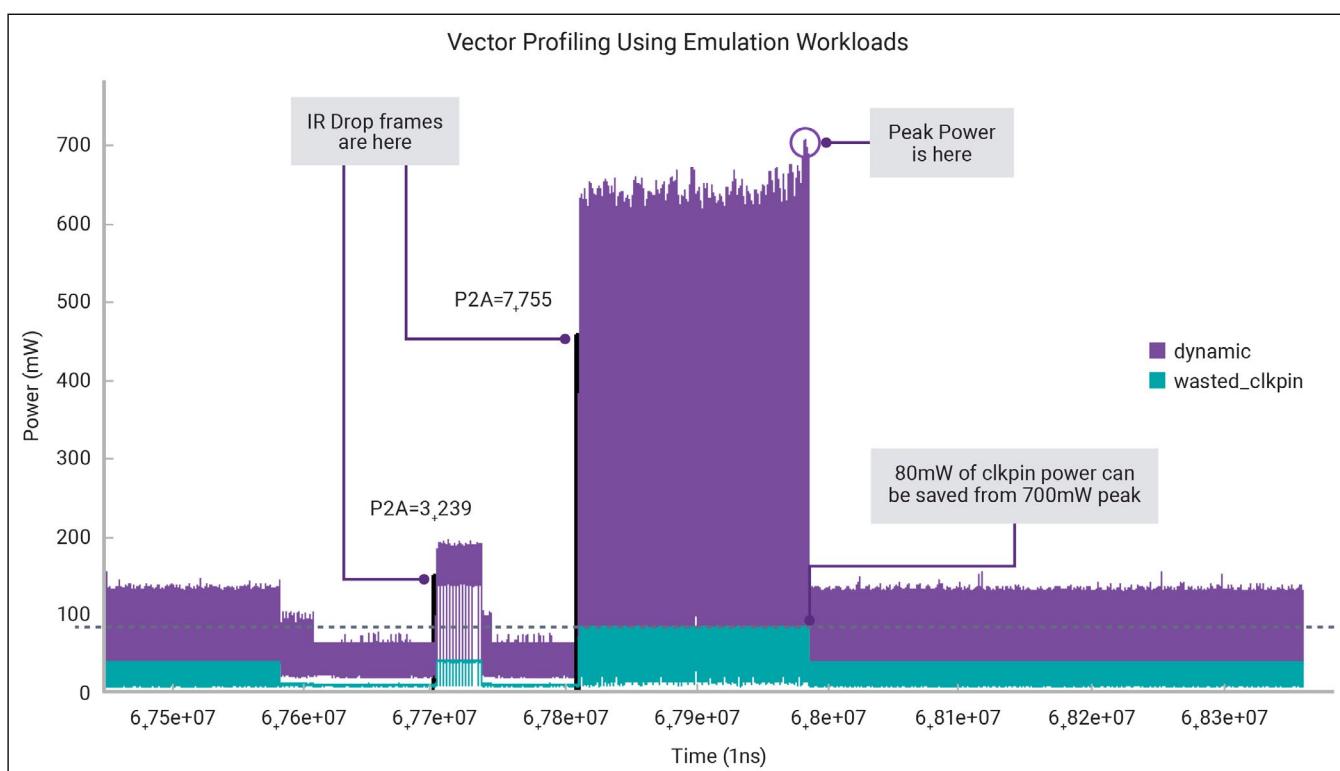

#### 44 The criticality of performance per watt optimisation for AI chip development

AI workloads create an urgent need for compute and power efficiency improvements from the architecture stage forward

#### 48 Taking SiC switches to new highs

How APC Electronics and Luminus aim to reshape high-power, high-frequency design with next-generation silicon carbide technology

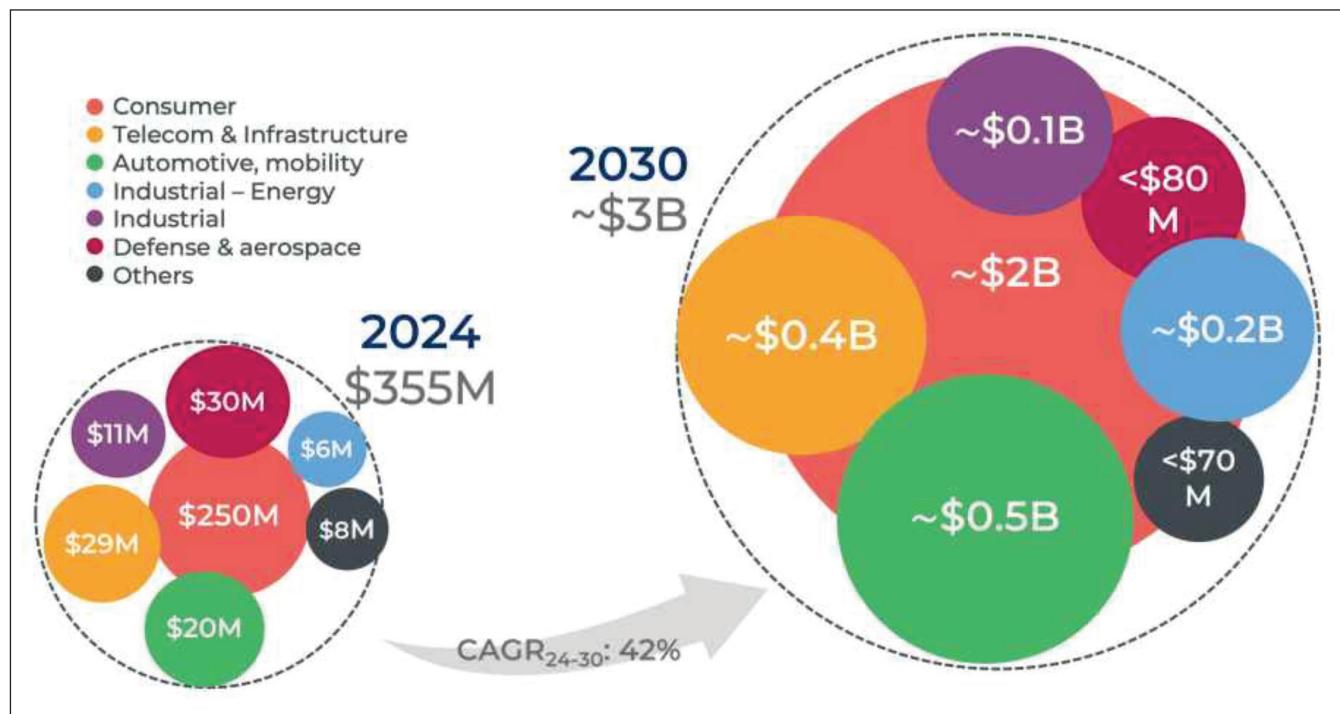

## 52 From chargers to data centres: power GaN market set for rapid sixfold expansion by 2030

Power GaN 2025, powered by Yole Group, provides a detailed look at the market growth, technology trends, and strategic shifts shaping the gallium nitride power device industry

## 54 New CEO to lead Wise Integration's global growth

Ghislain Kaiser, the recently appointed Chief Executive Officer of Wise Integration, explains how his main task is to transition the company from a CEA Leti spinout into a pioneering force in GaN and digital power management innovation with strong growth potential

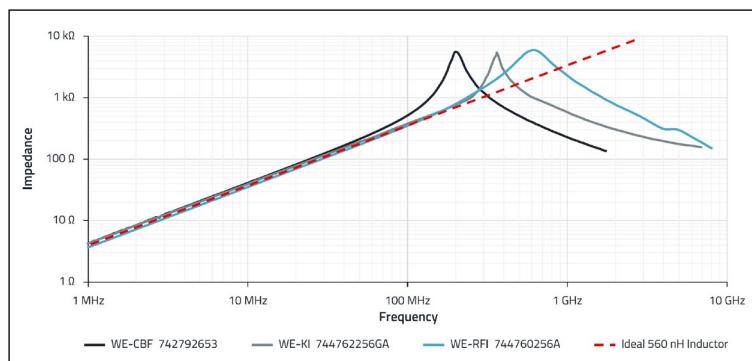

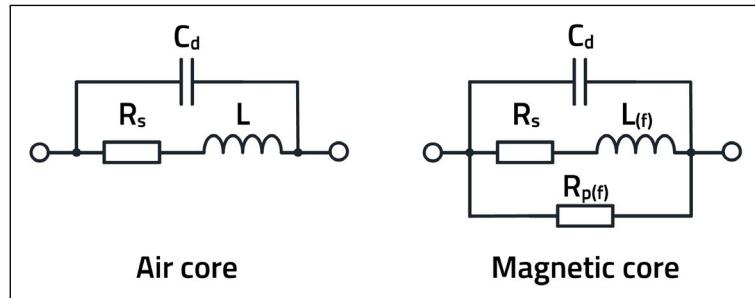

## 58 SMT Inductors - Coils and ferrites - selection made easy

How do you choose the right inductor for your application? This article compares the differences between three inductive SMT components: ceramic inductors, SMT ferrites, and wire-wound ferrite inductors

36

## NEWS

06 SemiQ launches Gen3 1200V modules

07 STMicroelectronics unveils e-fuse automotive smart switch

08 VisIC announces \$26M investment backed by Hyundai

09 X-FAB speeds time-to-market for SiC MOSFET solutions

10 European DC-Power projects to boost collaboration

11 Wolfspeed receives nearly \$700m in tax refunds

12 Wise, Powernet and KEC to co-develop AI power supplies

### PEI POWER ELECTRONICS INTERNATIONAL

#### Editor

Phil Alsop

phil.alsop@angelbc.com

#### News Editor

Christine Evans-Pughe

christine.evans-pughe@angelbc.com

#### Technology Editor

Rebecca Pool

#### Contributing Technical Editor

Richard Stevenson

richard.stevenson@angelbc.com

+44 (0)1923 690215

#### Sales & Marketing Manager

Shehzad Munshi

shehzad.munshi@angelbc.com

+44 (0)1923 690215

#### Design & Production Manager

Mitch Gaynor

mitch.gaynor@angelbc.com

+44 (0)1923 690214

#### Sales and Product Manager

James Cheriton

james.cheriton@angelbc.com

+44 (0)2476 718970

#### Publisher

Jackie Cannon

jackie.cannon@angelbc.com

+44 (0)1923 690205

#### CEO

Sukhi Bhadal

sukhi.bhadal@angelbc.com

+44 (0)2476 718970

#### CTO

Scott Adams

scott.adams@angelbc.com

+44 (0)2476 718970

Power Electronics International Magazine is published six times a year on a controlled circulation basis. Non-qualifying individuals can subscribe at: £105.00/e158 pa (UK & Europe), £138.00 pa (air mail), \$198 pa (USA). Cover price £4.50. All information herein is believed to be correct at time of going to press. The publisher does not accept responsibility for any errors and omissions. The views expressed in this publication are not necessarily those of the publisher.

Every effort has been made to obtain copyright permission for the material contained in this publication. Angel Business Communications Ltd will be happy to acknowledge any copyright oversights in a subsequent issue of the publication. Angel Business Communications Ltd © Copyright 2025. All rights reserved. Contents may not be reproduced in whole or part without the written consent of the publishers. The paper used within this magazine is produced by chain of custody certified manufacturers, guaranteeing sustainable sourcing. © Copyright 2025.

We strive for accuracy in all we publish; readers and contributors are encouraged to contact us if they recognise an error or omission. Once a magazine edition is published [online, in print or both], we do not update previously published articles to align old company names, branding, marketing efforts, taglines, mission statements or other promotional verbiage, images, or logos to newly created or updated names, images, typographic renderings, logos (or similar) when such references/images were accurately stated, rendered or displayed at the time of the original publication.

When companies change their names or the images/text used to represent the company, we invite organisations to provide Angel Business Communications with a news release detailing their new business objectives and/or other changes that could impact how customers/prospects might recognise the company, contact the organisation, or engage with them for future commercial enterprise.

Published by Angel Business Communications Ltd

6 Bow Court,

Fletchworth Gate,

Burnsall Road, Coventry CV5 6SP, UK.

T: +44 (0)2476 718 970

E: info@angelbc.com

W: angelbc.com

Angel

BUSINESS COMMUNICATIONS

# SemiQ launches Gen3 1200V modules

Family includes 608A half-bridge module with 2.4mΩ RDSON and best-in-class thermal resistance

SEMIQ INC, a developer of SiC solutions, has announced an expansion of its third-generation QSiC MOSFET product line, including devices with what it claims are industry-leading current density and thermal resistance.

Seven devices have been launched, including high-current S3 half-bridge, B2T1 six-pack and B3 full-bridge packages.

This expansion addresses the growing demand for ultra-efficient conversion in high-power systems, and features devices engineered for current capabilities of up to 608A and a junction-to-case thermal resistance of 0.07°C/W (in the 62 mm standard S3 half-bridge format).

The six-pack modules integrate the three-phase power stage into a compact housing and have an RDSON range of 19.5 to 82mΩ. They are designed to optimize layout and minimise parasitics in motor drives and advanced AC-DC converters.

The full-bridge modules deliver high current capabilities of up to 120A and an ultra-low on-resistance down to

8.6mΩ. This combination, coupled with a low thermal resistance of 0.28°C/W, maximises power density and efficiency in single-phase inverters and high-voltage DC-DC systems.

All parts are screened using wafer-level gate-oxide burn-in tests to guarantee the gate oxide quality. They are also breakdown voltage tested to over

1350 V. Modules using these third-generation chips operate at lower gate voltages than previous generations as a result of the 18 V-4.5 V gate voltage of the third-generation chips.

SemiQ's Gen3 technology reduces both RONsp and turn off energy losses (EOFF) by up to 30 percent versus previous generations, according to the company.

## Mitsubishi adds to high-voltage IGBT range

MITSUBISHI ELECTRIC launching new standard-isolation (6.0kVrms) and high-isolation (10.2kVrms) modules in its 4.5kV/1,200A XB Series of high-voltage HVIGBTs.

These new high-capacity power semiconductors achieve high moisture resistance for more efficient and reliable inverters used in large industrial equipment, such as railcars, operating in diverse environments including outdoors.

Mitsubishi Electric will exhibit the new modules at the 40th Nepcon Japan R&D and Manufacturing show in Tokyo

from January 21 to 23, 2026, as well as other exhibitions in North America, Europe, China, India and additional locations.

The new modules use IGBT elements that incorporate Mitsubishi Electric's proprietary relaxed field of cathode (RFC) diode and carrier-stored trench-gate bipolar transistor (CSTBT) structure.

New structures for electric field

relaxation and surface charge control enabled Mitsubishi Electric to reduce the chip's termination region size by about 30 percent while also achieving about 20 times greater moisture resistance than existing products.

In addition, the module reduces total switching loss by approximately 5% compared to previous models, and reverse-recovery safe-operating area (RRSOA) tolerance is about 2.5 times greater than that of compared to previous models.

# STMicroelectronics unveils e-fuse automotive smart switch electrification strategy

New addition to STi2Fuse family reacts within 100µs

STMICROELECTRONICS' VNF1248F automotive e-fuse MOSFET controller combines ST's fast-acting, advanced e-fuse features for harness protection and enhanced flexibility, enabling power saving and advanced performance in automotive functional-safety systems.

A new addition to the STi2Fuse family, the VNF1248F reacts within 100µs, which is faster than a conventional wire fuse and ensures flexible and robust protection to avoid fault propagation inside the vehicle.

The VNF1248F integrates the new capacitive charging mode (CCM) functionality to ensure proper driving of large capacitive loads with high inrush current. In addition, an enhanced Standby-ON mode with current capability up to 600mA and current consumption lower than 75µA enhances the vehicle's efficiency when in park mode, helping increase autonomy. An optional external supply pin for logic reduces power consumption by 0.4W in 48V systems and battery-undervoltage shutdown compatible with the automotive LV124 standard ensures system stability.

The chip facilitates reaching high safety-integrity levels (ASIL) in ISO 26262 functional-safety applications thanks comprehensive dedicated features like advanced fault detection and reaction, fail-safe mode and limp-home mode. There are also built-in self tests for automatic diagnosis and a dedicated pin for direct hardware control of the external MOSFET gate in case of a microcontroller fault.

Suitable for 12V, 24V, and 48V boardnets, the VNF1248F handles power distribution in zonal vehicle electrical architectures and general

fuse and relay replacement. Other uses include as an ECU main switch and active supply for always-on circuitry in parking mode.

Joining ST's STi2Fuse family of smart switches for wire harness protection and dynamic power distribution, the VNF1248F has an SPI port to interact with a host microcontroller. Configuring the device using SPI saves conventional external programming components and allows flexible control of settings including hard short-circuit (HSC) latch-off, current-vs-time latch-off in fuse emulation, and MOSFET-desaturation shutdown. With non-volatile memory (NVM) also on-chip, the VNF1248F can additionally store an immutable default configuration to ensure consistent behavior in failsafe or locked states.

The associated EV-VNF1248F evaluation board, pre-assembled and ready to connect directly to the load, power supply, and microcontroller, simplifies integration of ST's intelligent fuse protection into prototype circuitry. A software package, STSW-EV-VNF1248F, is also available and provides a graphical user interface and control firmware to configure and monitor the VNF1248F using an EV-SPC582B microcontroller board.

The VNF1248F MOSFET controller is in production now in a 5mm x 5mm 32-lead QFN32 package, from \$2.63 for orders of 1000 pieces.

## Infineon GaN powers Enphase solar microinverters

ENPHASE ENERGY, a leading supplier of microinverter-based solar and battery systems, is using Infineon's CoolGaN bi-directional switch (BDS) technology for its next-generation of solar microinverters.

According to Infineon, its GaN technology enables significant enhancements in power output, energy efficiency, and system reliability for Enphase's IQ9 Series Microinverters. For the new IQ9N-3P Commercial Microinverter, it will also help simplify design complexity and lower installation and balance of system costs.

CoolGaN bi-directional switch technology replaces two or four unidirectional switches with a single bi-directional switch. This allows power flow in both directions, and enables significant cost savings, while enabling the design of smaller, more efficient power devices, according to Infineon. The BDS technology has also demonstrated a reduction in power loss, outperforming conventional silicon switches by 68 percent and GaN unidirectional switches by 42 percent. By achieving higher power output and efficiency, Enphase's new microinverters can now service not only the residential solar market, but also a much larger portion of the commercial market.

"Utilising Infineon's CoolGaN bi-directional switch technology allows us to service a much larger segment of the commercial market with our IQ9 Series Microinverters," said Ron Swenson, SVP of operations at Enphase Energy.

# VisIC announces \$26 million investment backed by Hyundai

Hyundai and Kia join as strategic investors with a commitment to integrate GaN tech into mass-production EV platforms

GaN POWER chip company VisIC Technologies has announced the successful second closing of its Round B funding, securing \$26 million.

The round was led by a global semiconductor leader, with car companies Hyundai and Kia (HKMC) joining as a strategic investor.

The lead investor's focus on advancing critical semiconductor technologies complements VisIC's proprietary D<sup>3</sup>GaN platform, designed to deliver efficiency, scalability, and reliability for automotive drivetrains. HKMC's participation underscores its commitment to integrating GaN technology into mass-production EV platforms.

VisIC says the new capital will accelerate its roadmap, including: optimisation, qualification, and release of Gen3 750V GaN dice and power modules; development of Gen4 1350V GaN technology, supporting the full spectrum of EV designs; stabilisation of the supply chain and ramp-up of GaN product delivery for EV traction inverters; and expansion into emerging 800V data centre power requirements,

leveraging the same advanced GaN platform.

Tamara Baksht, CEO of VisIC Technologies said: "This investment marks a major milestone for VisIC and the global EV industry. Our D<sup>3</sup>GaN technology is redefining power electronics for electric vehicles, and the support of our strategic partners accelerates our mission to deliver high-efficiency, scalable solutions for the

next generation of mobility."

Hyundai Motor Company and Kia (HKMC) said: "Hyundai Motor Company and Kia are committed to advancing sustainable mobility. Partnering with VisIC enables us to integrate cutting-edge GaN power technologies into our EV platforms, enhancing efficiency, reliability, and performance as we shape the future of electric transportation."

## Company's SiC technology to help advance Toyota's electrification strategy

WOLFSPEED has announced that its automotive SiC MOSFETs will power onboard charger systems for Toyota's battery electric vehicles (BEVs).

"Toyota is known for its uncompromising approach to quality and reliability, and we're honoured to be supporting their next wave of electrification," said Robert Feurle, CEO,

"Wolfspeed's US-based supply chain and domestic SiC manufacturing

footprint ensure the stability and continuity they need to achieve their electrification goals."

"Our work with Toyota is built upon years of trust in engineering expertise, supply reliability, as well as a shared obsession with quality," said Cengiz Balkas, Wolfspeed's chief business officer, "This reinforces our role in driving electrification with SiC technology that delivers performance, efficiency and safety."

# X-FAB speeds time-to-market for SiC MOSFET solutions

XbloX platform gives easy access to a standardised SiC process technologies

SPECIALTY foundry X-FAB is offering easy access to a standardised yet flexible set of SiC process technologies that accelerate the development of advanced power devices.

From rapid prototyping to full production, the modular and scalable XbloX platform is said to help SiC device developers to expedite engineering assessments and technology release, with production starts achieved up to nine months faster than traditional methods.

The XbloX WBG discrete foundry model has two major benefits, according to the company. Firstly, X-FAB takes on process development activities with the introduction of a Process Installation Kit (PIK), where design and implant recipes provide key differentiators.

Secondly, the use of XbloX ensures wafer manufacturing at X-FAB becomes a highly scalable activity in line with application requirements, differing considerably from the less scalable production provided by a traditional foundry model for customer-specific SiC technologies.

“Thanks to a PIK, qualified SiC process development modules, and an automated onboarding process, customers need do little more than access our global hotline for support on block selection and deployment,” explains Brian Throneberry, business director SiC Foundry at X-FAB.

“We have robust rules in place to help guide design, mask tooling, engagement, and so on. Once the selection is finalised, XbloX automatically generates the process flow, which subsequently integrates quality systems, business functions, and commercial aspects for the customer. It’s a highly expedited way of providing customers with the flexibility required to build custom SiC MOSFET technologies at an accelerated rate.”

## SK Keyfoundry ramps up SiC activity

SK KEYFOUNDRY, an 8-inch pure-play foundry in Korea, is accelerating the development of SiC-based power semiconductor technology with the acquisition of SK Powertech, a key SiC player.

“The acquisition of SK Powertech, a specialist in SiC, marked a pivotal step for SK Keyfoundry in securing its own distinctive technological edge in the compound semiconductor field,” said Derek D. Lee, CEO of SK Keyfoundry. “By combining the core development capabilities of both companies and

launching high-efficiency SiC power semiconductor process technologies and products, SK Keyfoundry aims to establish differentiated technological leadership in the rapidly growing global market for high-voltage and high-efficiency compound semiconductor applications.”

Building on this foundation, SK Keyfoundry aims to provide SiC MOSFET 1200V process technologies by the end of 2025 and launching SiC-based power semiconductor foundry business in the first half of 2026.

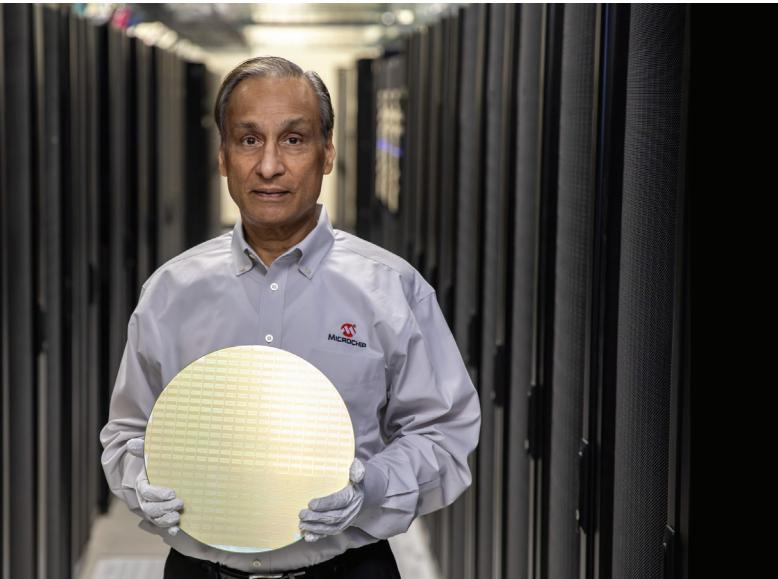

## Coherent 300mm SiC platform addresses AI needs

COHERENT has announced that its next-generation 300mm SiC platform will address the increasing higher power density, faster switching, and thermal efficiency demands in AI data centre infrastructure.

“AI is transforming the thermal-management landscape in data centres, and SiC is emerging as one of the foundational materials enabling this scalability,” said Gary Ruland, SVPt and general manager at Coherent.

“Our 300mm platform, which we plan to ramp in high volumes, delivers new levels of thermal efficiency that translate directly into faster, more power-efficient AI data centres.”

The platform’s conductive SiC substrates provide low resistivity, low defect density, and high homogeneity, enabling low-dissipation, high-frequency, and good thermal stability.

In AI and data infrastructure, these properties boost energy efficiency and thermal performance in next-generation data centre systems.

In addition, the company says the technology brings benefits for AR/VR devices, enabling thinner and more efficient waveguides for AR smart glasses and VR headsets, improving reliability in compact immersive display modules.

# European DC-Power projects to boost collaboration

THEUS, DC-POWER, InterSCADA, FLAGCHIP, PROSECCO and SAFEPower look towards building a coherent European DC and hybrid AC/DC innovation ecosystem

EARLIER this month, seven European projects in DC and hybrid AC/DC grid technologies held a joint coordination meeting to strengthen cooperation and identify synergies.

The participating projects which include THEUS, DC-POWER, InterSCADA, FLAGCHIP, PROSECCO and SAFEPower, aim to create a more modern, flexible, and efficient electricity system, capable of supporting increased renewable integration, sector coupling, and the EU's long-term climate and energy security goals.

During the meeting, each project presented its objectives, activities, and expected outcomes. A dedicated discussion session was held to explore common challenges, shared research priorities, and opportunities for joint actions across technology development, demonstration activities, and dissemination efforts.

This first collective exchange represents an important step toward building a more coherent and collaborative European DC and hybrid AC/DC innovation ecosystem. By aligning efforts and sharing expertise, the projects aim to accelerate progress toward more efficient, resilient, and sustainable electricity systems.

"The DC-Power project has developed a solution for the cost-efficient distribution of electricity for MW scale appliances, such as datacenters, electrolyzers, fast charging stations of electric trucks and cars.

Key is the use of medium voltage DC grids which has been found to be an optimal solution for electro intensive industry", says Jens Merten, the coordinator who is with CEA, a large scale technology developer in France.

Carlos Pérez Montero, THEUS Coordinator: "Our synergy call showed that the challenges we face in hybrid AC/DC grids are shared across projects, and that by aligning our methods and sharing use cases we can accelerate the deployment of next-generation grid solutions across Europe".

Eduardo Garcia Martinez, FLAGCHIP Coordinator: "By sharing our objectives, innovations, and approaches, we gained a clearer collective picture of where the field is heading."

Dirk Van Hertem, PROSECCO Coordinator: "Hybrid AC/DC grids introduce new protection, control, and system engineering challenges that no single project can solve alone. This exchange allows us to align our approaches, share insights, and accelerate solutions that will support a resilient and interoperable European grid."

## About the projects:

- **DC-POWER:** Medium-voltage DC grid solutions for industrial and utility applications.

[dcpower.tech](http://dcpower.tech)

- **InterSCADA:** Open-source SCADA platform for hybrid AC/DC monitoring and control.

[interscada.eu](http://interscada.eu)

- **THEUS:** Tools and methodologies for planning and operating hybrid AC/DC networks across all voltage levels.

[theus-project.eu](http://theus-project.eu)

- **FLAGCHIP:** High-efficiency power electronics using wide-bandgap and ultra-wide-bandgap semiconductors.

[flagchip-project.eu](http://flagchip-project.eu)

- **PROSECCO:** Enhanced protection, congestion management, and system engineering for HVDC and hybrid grids.

[prosecco-project.be](http://prosecco-project.be)

- **SAFEPower:** Next-generation MVDC converters with advanced semiconductors and AI-enabled condition monitoring.

[safepowerproject.eu](http://safepowerproject.eu)

# Wolfspeed receives nearly \$700m in tax refunds

Cash injection gives company more financial flexibility as it ramps its 200mm SiC line

WOLFSPEED has received \$698.6m in cash tax refunds from the US Internal Revenue Service (IRS) from the Advanced Manufacturing Investment Credit (AMIC) under Section 48D of the Internal Revenue Code. The company says this refund represents a significant step in getting back the approximately \$1 billion of Section 48D cash tax refunds. In fiscal 2025, the company received \$186.5m in cash tax refunds related to its 2023 and 2024 federal tax filings.

Following receipt of these funds, Wolfspeed's cash balance is approximately \$1.5b, positioning the company with more financial flexibility as it ramps its 200mm SiC line.

"This substantial cash infusion further strengthens our liquidity position at a critical phase in Wolfspeed's strategic evolution," said Wolfspeed CFO, Gregor Van Issum. "It provides us with the financial agility to support long-term growth, manage our capital structure responsibly, and continue driving innovation across the SiC value chain for our customers."

Over the past several years, Wolfspeed has made significant investments to establish a vertically integrated, US-based, and highly resilient supply chain

for SiC materials and power devices. Section 48D support has helped accelerate the company's transition from 150mm (6-inch) to 200mm (8-inch) wafer technology, a critical next-generation platform for increasing efficiency and expanding global adoption of SiC.

As per the agreement with the senior secured lenders, the company plans to allocate \$192.2m of the refund toward retiring approximately \$175m of outstanding debt, with the remaining funds for general corporate purposes.

Over the past several years, Wolfspeed has made significant investments to establish a vertically integrated, US-based, and highly resilient supply chain for SiC materials and power devices

**POWER ELECTRONICS INTERNATIONAL**

DESIGN • MATERIALS • PACKAGING • PERFORMANCE

- Based around a hot topic for your company, this 60-minute recorded, moderated zoom roundtable would be a platform for debate and discussion

- Moderated by editor, Phil Alsop, this can include 3 speakers

- Questions prepared and shared in advance

**Cost: €5995**

**Contact:** Jackie Cannon

[jackie.cannon@angelbc.com](mailto:jackie.cannon@angelbc.com)

# Wise, Powernet and KEC to co-develop AI power supplies

French digital GaN pioneer and Korean power supply specialists join forces as Korea accelerates AI data centre build-out

FRENCH GaN company Wise Integration has signed a memorandum of understanding (MoU) with Korean power firms Powernet and KEC to co-develop next-generation switched-mode power supply (SMPS) solutions for AI server applications in South Korea.

Under the agreement, Wise Integration will supply its GaN power devices, digital-control expertise and technical support. Powernet Technologies will lead development of new SMPS designs using Wise's WiseGan and WiseWare technologies. KEC will manage backend manufacturing, including module integration and system-in-package production tailored to the thermal and reliability demands of AI-server racks.

In addition to accelerating the design and development of competitive AI-server power supply solutions and creating business opportunities in Korea's AI server market, the project aims to shorten the solutions' time-to-market using WiseGan and WiseWare technologies. The collaboration builds on an earlier partnership between Wise Integration and Powernet, launched to serve OEMs that require compact, digitally controlled power-supply systems for faster, smaller and more energy-efficient electronic equipment.

AI servers draw extensive power, generate intense heat, and depend on SMPS designs capable of converting high-voltage input (e.g., 400 V) to

stable 48 V rails with minimal loss. GaN devices with digital control are uniquely suited for that task: they enable higher switching frequencies, greater efficiency, and more precise management of fast, high-current load transients.

The South Korean government's investments in AI-dedicated data centres includes high-performance GPU clusters and digital infrastructure that supports demand for more efficient, compact, and scalable power-conversion systems.

"Korea is moving quickly to build the next generation of AI data centres, and power architecture is a critical piece of that effort. Working with Powernet and KEC lets us bring GaN-based digital control into server-grade designs at scale—delivering the efficiency, thermal performance, and responsiveness that modern AI hardware depends on," said Ghislain Kaiser, CEO of Wise Integration.

Beyond the MoU, Wise has been widening the foundation that supports strategic partnerships. As Korea accelerates AI-ready data centre development, the demands on power-conversion systems intensify — higher switching frequencies, tighter thermal budgets and more aggressive efficiency targets. Wise has been expanding its GaN + digital-control portfolio to meet those constraints, ensuring the technologies Korea aims to deploy at scale already have a maturing, production-validated base behind them.

## Wolfspeed to power Toyota BEVs

Wolfspeed has announced that its automotive SiC MOSFETs will power onboard charger systems for Toyota's battery electric vehicles (BEVs).

"Toyota is known for its uncompromising approach to quality and reliability, and we're honoured to be supporting their next wave of electrification," said Robert Feurle, CEO.

"Wolfspeed's US-based supply chain and domestic SiC manufacturing footprint ensure the stability and continuity they need to achieve their electrification goals."

"Our work with Toyota is built upon years of trust in engineering expertise, supply reliability, as well as a shared obsession with quality," said Cengiz Balkas, Wolfspeed's chief business officer. "This reinforces our role in driving electrification with SiC technology that delivers performance, efficiency and safety."

For example, the company recently launched WiseWare 1.0 for totem-pole PFC and LLC topologies, its newest fully digital controller. While aimed today at gaming, displays and industrial systems, it shares the same architecture—high-frequency GaN operation, compact form factor, digitally managed efficiency—that naturally scales into the server-class designs targeted under the Korea-focused collaboration.

WÜRTH ELEKTRONIK MORE THAN YOU EXPECT

# ULTRA LOW LOSSES

---

## WE-MXGI

---

© elSos

With the WE-MXGI Würth Elektronik offers the newest molded power inductor series. It combines an innovative iron alloy material that provides high permeability for lowest  $R_{DC}$  values combined with an optimized wire geometry.

Ready to Design-In? Take advantage of personal technical support and free samples ex-stock.

[www.we-online.com/WE-MXGI](http://www.we-online.com/WE-MXGI)

### Highlights

- Extremely high power density

- Ultra low  $R_{DC}$  values and AC losses

- Magnetically shielded

- Optimized for high switching frequencies beyond 1 MHz

#UltraLowLosses

# MIT engineers develop a magnetic transistor for more energy-efficient electronics

A new device concept opens the door to compact, high-performance transistors with built-in memory.

BY ADAM ZEWE, MIT NEWS OFFICE

TRANSISTORS, the building blocks of modern electronics, are typically made of silicon. Because it's a semiconductor, this material can control the flow of electricity in a circuit. But silicon has fundamental physical limits that restrict how compact and energy-efficient a transistor can be.

MIT researchers have now replaced silicon with a magnetic semiconductor, creating a magnetic transistor that could enable smaller, faster, and more energy-efficient circuits. The material's magnetism strongly influences its electronic behavior, leading to more efficient control of the flow of electricity. The team used a novel magnetic material and an optimization process that reduces the material's defects, which boosts the transistor's performance.

The material's unique magnetic properties also allow for transistors with built-in memory, which would simplify circuit design and unlock new applications for high-performance electronics.

"People have known about magnets for thousands of years, but there are very limited ways to incorporate magnetism into electronics.

We have shown a new way to efficiently utilize magnetism that opens up a lot of possibilities for future applications and research," says Chung-Tao Chou, an MIT graduate student in the departments of Electrical Engineering and Computer Science (EECS) and Physics, and co-lead author of a paper on this advance.

Chou is joined on the paper by co-lead author Eugene Park, a graduate student in the Department of Materials Science and Engineering (DMSE); Julian Klein, a DMSE research scientist; Josep Inglá-Aynés, a postdoc in the MIT Plasma Science and Fusion Center; Jagadeesh S. Moodera, a senior research scientist in the Department of Physics; and senior authors Frances Ross, TDK Professor in DMSE; and Luqiao Liu, an associate professor in EECS, and a member of the Research Laboratory of Electronics; as well as

others at the University of Chemistry and Technology in Prague. The paper appears in *Physical Review Letters*.

## Overcoming the limits

In an electronic device, silicon semiconductor transistors act like tiny light switches that turn a circuit on and off, or amplify weak signals in a communication system. They do this using a small input voltage. But a fundamental physical limit of silicon semiconductors prevents a transistor from operating below a certain voltage, which hinders its energy efficiency.

To make more efficient electronics, researchers have spent decades working toward magnetic transistors that utilize electron spin to control the flow of electricity. Electron spin is a fundamental property that enables electrons to behave like tiny magnets. So far, scientists have mostly been limited to using certain magnetic materials. These lack the favorable electronic properties of

semiconductors, constraining device performance.

"In this work, we combine magnetism and semiconductor physics to realize useful spintronic devices," Liu says. The researchers replace the silicon in the surface layer of a transistor with chromium sulfur bromide, a two-dimensional material that acts as a magnetic semiconductor.

Due to the material's structure, researchers can switch between two magnetic states very cleanly. This makes it ideal for use in a transistor that smoothly switches between "on" and "off."

"One of the biggest challenges we faced was finding the right material. We tried many other materials that didn't work," Chou says.

They discovered that changing these magnetic states modifies the material's electronic properties, enabling low-energy operation. And unlike many other 2D materials, chromium sulfur bromide remains stable in air.

To make a transistor, the researchers pattern electrodes onto a silicon substrate, then carefully align and transfer the 2D material on top. They use tape to pick up a tiny piece of material, only a few tens of nanometers thick, and place it onto the substrate. "A lot of researchers will use solvents or glue to do the transfer, but transistors require a very clean surface. We eliminate all those risks by simplifying this step," Chou says.

**“** People have known about magnets for thousands of years, but there are very limited ways to incorporate magnetism into electronics. We have shown a new way to efficiently utilize magnetism that opens up a lot of possibilities for future applications and research,” **”**

### Leveraging magnetism

This lack of contamination enables their device to outperform existing magnetic transistors. Most others can only create a weak magnetic effect, changing the flow of current by a few percent or less. Their new transistor can switch or amplify the electric current by a factor of 10.

They use an external magnetic field to change the magnetic state of the material, switching the transistor using significantly less energy than would usually be required.

The material also allows them to control the magnetic states with electric current. This is important because engineers cannot apply magnetic fields to individual transistors in an electronic device. They need to control each one electrically.

The material's magnetic properties could also enable transistors with built-in memory, simplifying the design of logic or memory circuits.

A typical memory device has a magnetic cell to store information and

a transistor to read it out. Their method can combine both into one magnetic transistor.

"Now, not only are transistors turning on and off, they are also remembering information. And because we can switch the transistor with greater magnitude, the signal is much stronger so we can read out the information faster, and in a much more reliable way," Liu says.

Building on this demonstration, the researchers plan to further study the use of electrical current to control the device. They are also working to make their method scalable so they can fabricate arrays of transistors.

This research was supported, in part, by the Semiconductor Research Corporation, the U.S. Defense Advanced Research Projects Agency (DARPA), the U.S. National Science Foundation (NSF), the U.S. Department of Energy, the U.S. Army Research Office, and the Czech Ministry of Education, Youth, and Sports. The work was partially carried out at the MIT.nano facilities.

## VACUUM SOLDERING SYSTEM

UNCOMPROMISING QUALITY,

EFFICIENT DESIGN

VADU core

- Standardized, efficient system design

- Individually expandable to solve complex soldering tasks

- Soldering with preforms or solder pastes

- Proven and tested in series production for 25 years

**PiNK®**

productronica

18. – 21. November

Trade Fair Munich

Booth A4.255

# Small material, big impact

Dr Conor O'Brien, Senior Technology Analyst at IDTechEx, explores graphene in electronic applications

GRAPHENE was initially celebrated as a sci-fi material destined to transform electronics, quantum devices, and futuristic sensors. While expectations soared, commercial reality proved more modest. Rather than enabling transparent phones or levitating trains, graphene first succeeded in practical roles such as enhancing polymer composites in tires, coatings, and sporting goods through improved strength and conductivity. Now, with advances in manufacturing and renewed interest from major electronics and energy companies, the question resurfaces: are we finally approaching the breakthrough era once promised?

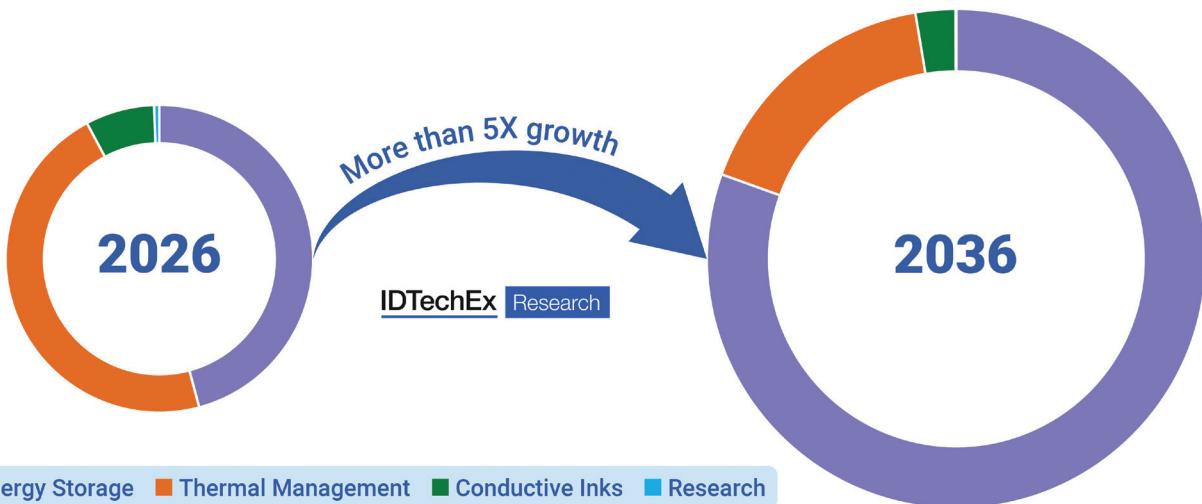

IDTechEx has covered the graphene market since 2012, providing a unique perspective on technological progress, commercialization strategies, and the long-term market outlook for the material. A new report has been released, "Graphene & 2D Materials

2026-2036: Technologies, Markets, Players", which includes granular 10-year graphene market forecasts, based on profiles of 90+ key players and leverages extensive in-depth coverage of many end-use markets for graphene.

Graphene is increasingly used in consumer electronics for thermal management, leveraging its exceptional heat conductivity to improve device cooling and reliability. Beyond passive materials, its high surface area and conductivity also make it a strong candidate for energy storage applications, particularly in next-generation batteries and supercapacitors, where faster charging and longer lifetimes are sought.

## Material requirements

Pristine graphene produced via chemical vapor deposition (CVD) offers exceptional electronic performance but is costly and complex to scale. As

a result, it's primarily reserved for high-end sensing applications. Most other uses such as thermal management films or battery additives can rely on lower-grade, bulk graphene materials without requiring perfect atomic structure.

IDTechEx believes that thermal management applications is a key early area for graphene adoption. There is increasing demand for high-performance heat spreaders, and the graphene properties and morphology are well-suited. The thermal conductivity of carbon materials tend to be higher than that seen in metals, with graphene oxide (GO) reporting a thermal conductivity in excess of 3,000 W/m-K. For anisotropic materials such as graphene, achieving through-plane alignment is key for a thermally efficient system, capable of minimising material usage and enabling cost savings. Multiple routes exist based on the material to be

## Small Material, Big Impact: Graphene in Electronic Applications

The **electronic applications of graphene** have received a lot of hype and bordered on science fiction over the past two decades. Tangible success is now being achieved in **thermal management**, while the **next generation of energy storage** devices could be unlocked by graphene. The sector is set to grow by a factor **more than 5X** over the coming decade.

aligned, including mechanical methods and dielectrophoresis. This need for alignment to enhance thermal conductivity is mirrored in applications leveraging the electrical conductivity of graphene, such as when using graphene dispersions as conductive inks.

Overview of the growing importance of graphene in electronic applications over the coming decade. Source: IDTechEx market report "Graphene & 2D Materials 2026-2036: Technologies, Markets, Players".

### China leads the way for consumer electronics

For some years the centre of gravity for graphene has been shifting towards China. This trend has shown up in several indicators including investment levels, patent filing trends, academic publication and in the number and size (at least nominal size) of graphene companies. Key players include The Sixth Element, Leadernano and SCF Nanotech.

The use of graphene for thermal management has increasingly been observed across the leading Chinese smartphone manufacturers as higher performances are demanded. This varies from acting as very localised heat spreader, a larger heat spreader or replacing a vapor chamber. A cooling

system, such as vapor chamber (VC) technology, manages a phone's heat by using evaporation and condensation to dissipate warmth from internal components. This prevents overheating, enhances performance, and extends battery life.

Huawei has taken this concept further with the Mate X6 by incorporating graphene sheets. Other leading smartphone players including Realme, ZTE, Xiaomi and OnePlus have reported use of graphene in various heat spreading technologies.

Other consumer electronics to have adopted graphene heat spreaders include gaming-grade laptops and monitors with Acer, ViewSonic and Samsung Display active in this area. Beyond heat spreaders, adoption of graphene has also been seen in headphones with players reporting that coating audio drivers with graphene can reduce vibrations and allow powerful bass with enhanced mid- and high-range frequencies.

Household names have released graphene-enhanced headsets, including Logitech, and LG, with graphene typically featuring in high-end headsets. Philips bucked this trend when the mid-range H8000E was launched in January 2025, featuring graphene-coated 40 mm drivers.

### Will graphene achieve success in energy storage?

The term "graphene battery" is widely misused. In reality, graphene is more likely to be one of several conductive additives selected based on cost, morphology, and performance, potentially used at the electrode, current collector, or pack level. Today, it is rarely found in commercial lithium-ion cells, with limited success mainly in high C-rate consumer devices. In contrast, carbon nanotubes are already established in current cathode formulations with well-established supply chains for lithium-ion batteries.

Looking ahead, graphene's best opportunity within energy storage lies in enabling next-generation technologies such as silicon anodes, which are expected to scale commercially. However, it is only one contender in an intensely competitive, well-funded landscape where many alternatives also offer effective conductive networks. If graphene is the enabling technology that unlocks silicon anodes, then strong and significant growth will be seen for this material.

For more details on the graphene market, including granular 10-year forecasts for 18 different application areas, see the IDTechEx market report "Graphene & 2D Materials 2026-2036: Technologies, Markets, Players".

# Powering the AI era: how Infineon Technologies' SiC solutions are shaping the future of data centre power supplies

As artificial intelligence (AI) continues to redefine the frontiers of computational performance, the supporting infrastructure particularly the power conversion within data centers must evolve rapidly to meet new performance and density benchmarks

BY DEEPAK VEEREDDY, DIRECTOR OF TECHNICAL MARKETING, INFINEON TECHNOLOGIES AND ALEKSEI CHERKASOV, SENIOR MANAGER PRODUCT MARKETING, INFINEON TECHNOLOGIES

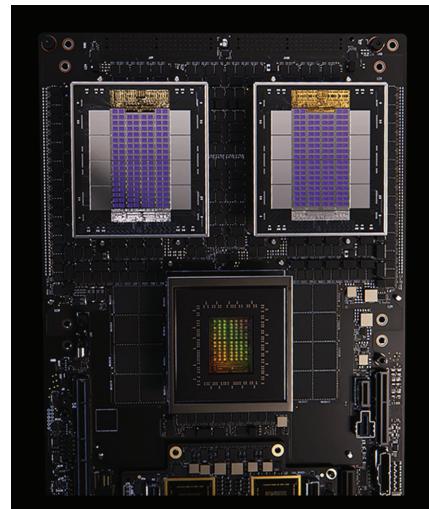

WITH data center power levels rising exponentially due to the proliferation of GPU- and TPU-based processing systems, it is crucial to use new semiconductor materials like silicon carbide (SiC) and gallium nitride (GaN) to complement a well-established silicon (Si) infrastructure.

Today Infineon Technologies is leading the charge to future-proof power conversion infrastructure by deploying its latest generations of all three

technologies making the most of each to support the extreme demands of AI-driven data center architectures.

Each technology has its own strengths and hence is positioned for power supply design as follows [1]:

**Silicon is:**

- Perfect for legacy or conventional designs

- Optimized cost / performance solutions

- Suitable for traditional topologies up to 150 kHz switching

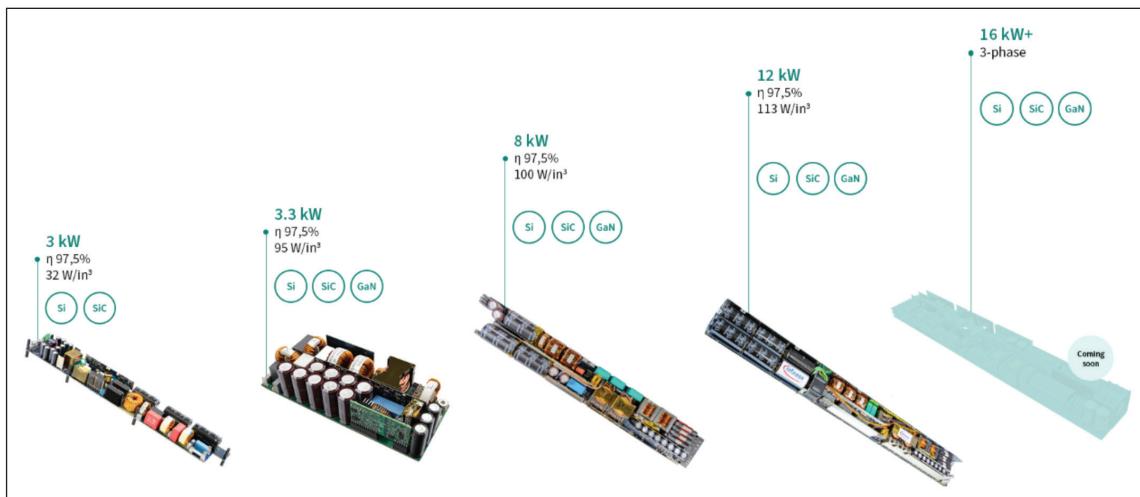

► Figure 1.

Infineon

Technologies'

PSU reference

designs span

across a wide

range of data

center needs.

#### Silicon carbide is:

- Perfect for half-bridge (HB) hard-switching topologies like totem-pole PFC requiring high voltages ( $\geq 400\text{V}$ ) and high temperature operating conditions

- Suitable for resonant topologies like LLC up to 500 kHz

#### Gallium nitride is:

- Perfect for soft-switching topologies such as LLC, for very high frequency ( $\geq 500 \text{ kHz}$ ) operation

- Best in efficiency x power density FOM

As we consider the diverse needs of various topologies, it becomes apparent that a single technology is not sufficient to meet all requirements. This is where the value of a hybrid approach comes into play, combining the strengths of Si, SiC, and GaN devices in a single system to create a tailored solution.

By leveraging this hybrid approach, engineers can achieve rapid scaling and optimal performance, making it an attractive option for developing modern power supply unit (PSU) designs for AI data centers. Having access to a broad portfolio of technologies

and expertise, such as that offered by Infineon Technologies, is crucial to create innovative and efficient PSU designs that meet the unique demands of AI data centers.

Infineon's AI centric SMPS demo solutions roadmap (Figure 1) reflects such approach that is engineered to factor in the rugged realities of 24/7 data center operation, offering full turn-key solutions. They are a blueprint for achieving the highest efficiency and density targets.

While a hybrid approach combining Si, SiC, and GaN devices is essential for meeting the diverse needs of AI data centers, silicon carbide CoolSiC™ MOSFETs are a critical component in this ecosystem, and in this article, we will discuss their specific applications and benefits in modern power supply unit (PSU) designs.

The AI revolution is reshaping the design criteria of data center power systems. Unlike conventional server environments that were CPU-centric and operated in relatively predictable load conditions, AI servers operate in highly dynamic states with rapid current surges and higher sustained power demands.

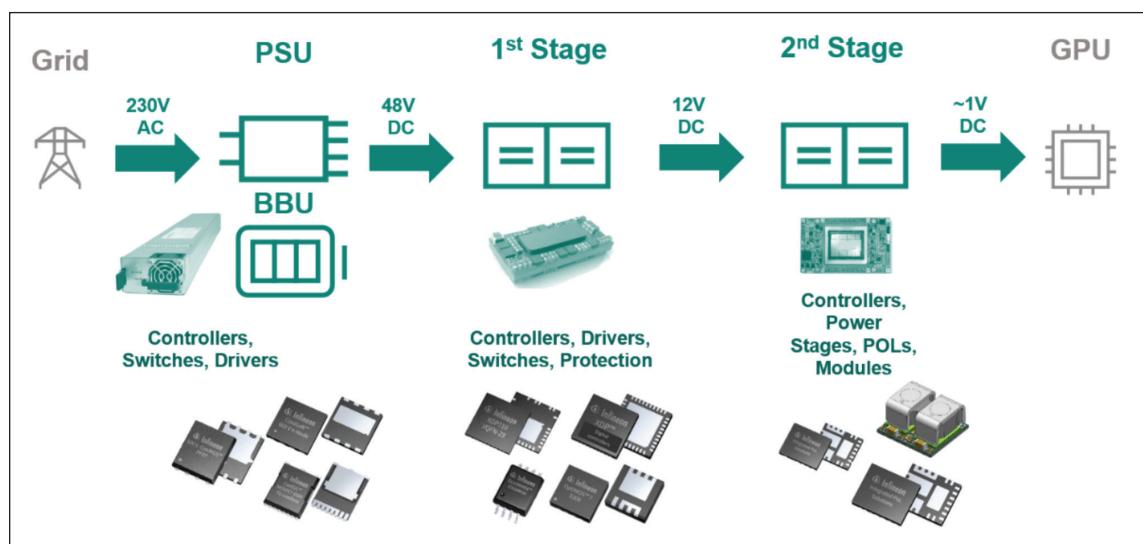

► Figure 2.

Server power

flow and

Infineon

Technologies'

comprehensive

product

portfolio to

address each

stage from

grid to core

in 48V bus

architecture.

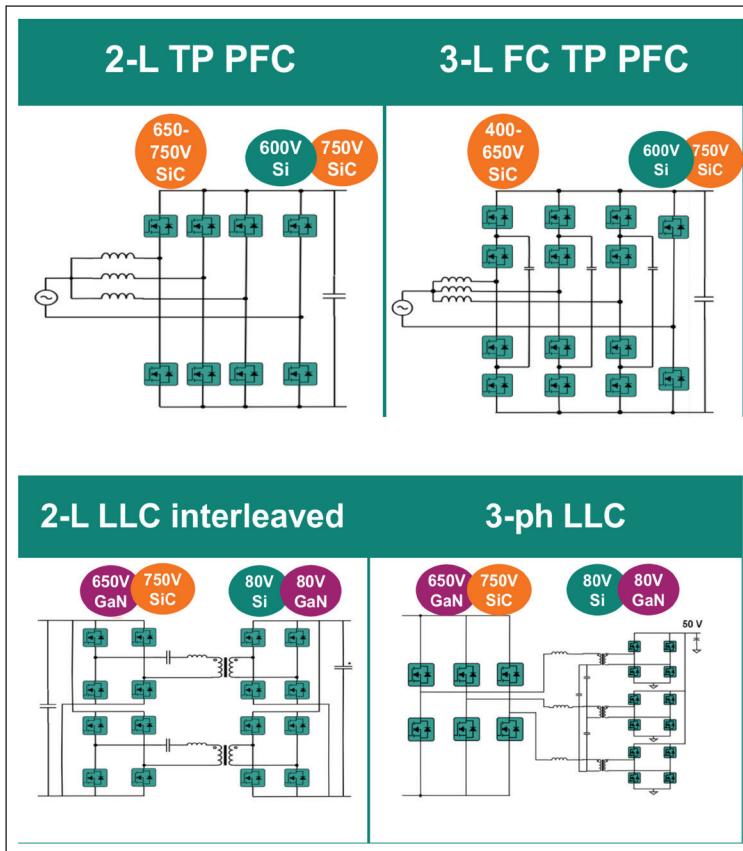

► Figure 3. Common PFC and LLC topologies addressed with SiC MOSFETs.

In fact, racks that once consumed under 10 kW are now pushing beyond 300 kW per rack and even above 500 kW in specialized training clusters. SiC based semiconductor solutions are the undisputed choice for such high power rack designs.

And here comes the question – why silicon carbide?

SiC devices are built on a wide bandgap semiconductor material with a bandgap of 3.26 eV—more than three times that of silicon. This physical characteristic provides the following intrinsic advantages for SiC based MOSFET:

- High breakdown field strength allowing for thinner drift regions and thereby reducing

- specific on-resistance

- High thermal conductivity (3-5x better than Si) improving heat dissipation

- Low switching losses allowing high frequency operation and reducing magnetics size

The low reverse recovery charge ( $Q_{rr}$ ) of the intrinsic body diode of SiC MOSFET is a decisive differentiator in fast commutation legs, particularly in bridgeless totem pole PFC. The combination of low gate charge ( $Q_g$ ) and reduced output charge (QOSS) broadens zero voltage switching (ZVS) windows in resonant topologies like LLC, enabling operation in the 200–250 kHz range without disproportionate penalties in magnetics or EMI.

From reliability standpoint, SiC MOSFETs exhibit robust avalanche and short circuit capability and a relatively lower positive temperature coefficient of  $R_{DS(on)}$  than Silicon MOSFETs. These features simplify current sharing mechanisms in parallel configurations common to multi kilowatt shelves. All these device level benefits align directly with the system level objectives of AI power design: higher efficiency across the load range, smaller and lighter passives, predictable thermal behavior under elevated coolant temperatures, and resilience to abnormal events without compromising on quality and reliability.

From an economic standpoint, SiC enables:

- Smaller power stages and fewer passive components, reducing BOM and footprint

- Higher reliability, minimizing service costs and extending product life

- Superior performance under extreme conditions

The growth of SiC in AI is very well supported by Environmental, Social, and Governance regulations as well as performance and total cost of ownership metrics:

- Hyperscalers like Google, Meta, and Microsoft have set aggressive energy efficiency targets for AI workloads

- Open Compute Project (OCP) standards, such as ORV3, require modular, high-efficiency PSUs

- EU and U.S. energy regulations (e.g. Ecodesign Directive, DOE Level VI) demand stringent

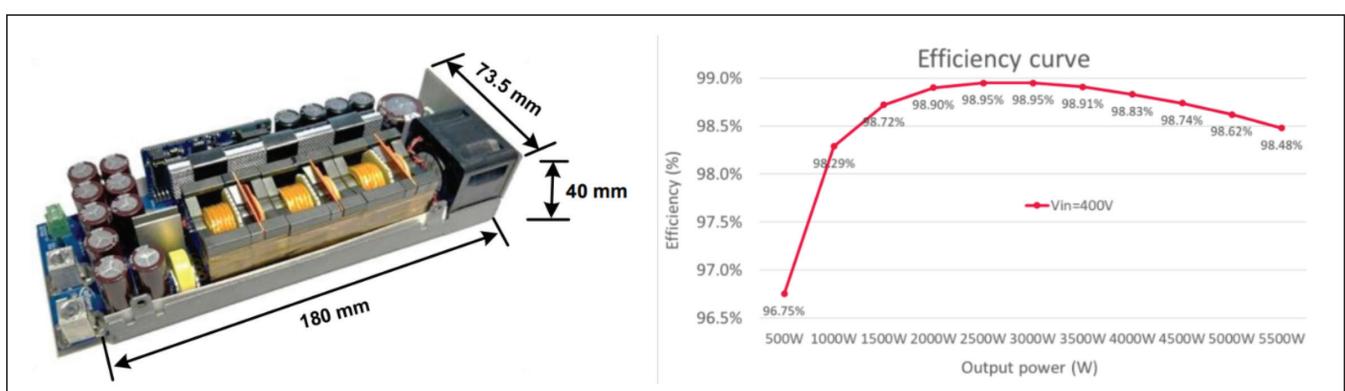

► Figure 4. 5.5 kW three-phase interleaved LLC converter: reference design and efficiency curve.

efficiency curves across load ranges

- Edge data centers and modular deployments favor compact, high-density designs achievable only with wide bandgap (WBG) semiconductors

This explosive growth poses an immediate and long-term engineering challenge: how to efficiently convert and distribute power from high-voltage AC grid inputs to ultra-low voltage rails (often under 1V) that feed modern AI processors. Moreover, in future, these conversions may happen within space-constrained, thermally stressed environments like liquid-cooled environments.

To meet the current demands of 48V architecture (Figure 2), Infineon Technologies has comprehensive offerings that addresses every node of the power path – from the power grid interface all the way to the processor core. The building blocks of this ecosystem include power switches, gate drivers, controllers, power stages, points of load, and power modules.

With PSUs being at the frontier of power conversion flow in servers, Infineon Technologies' CoolSiC™ MOSFET families provide the building blocks to support most advanced AI data center architectures.

PSU manufacturers have been widely adopting SiC in Totem Pole Power Factor Correction (TP PFC) designs, where SiC's fast recovery possible by low Qrr characteristics eliminate the need for slow, lossy boost diodes. Compared to traditional bridged PFC, TP PFC offers 1-1.5% higher peak efficiency in continuous conduction mode (CCM) operation.

The TP PFC stage of the PSU design could involve a 2-level or a 3-level flying capacitor (FC) topology (Figure 3) with or without interleaved approach. 2-level TP PFC is relatively simpler to implement than a 3-level FC design. However, the 3-level FC TP PFC boosts efficiency and density further compared to 2-level approach [2].

In ~400input systems, LLC converters (Figure 3) using SiC MOSFET can operate at up to 500 kHz frequency leading to minimal system loss for the following reasons.

The conduction losses of primary FET are the dominant portion of its overall loss. SiC MOSFET's relatively lower Rds(on) temperature co-efficient results in relatively lower conduction losses at high temperature operation.

The second dominant loss in the primary FET of LLC is the turn-off loss. SiC MOSFET, being a fast-switching device, enables lower turn-off losses. In addition to the above, the gate driving loss contribution of SiC MOSFET is low due to its lower gate charge compared to Si MOSFETs.

For instance, Infineon Technologies' 5.5 kW LLC reference design [3] using Gen 2 650V CoolSiC™ MOSFETs in TOLT package achieves almost 99% peak efficiency (Figure 4).

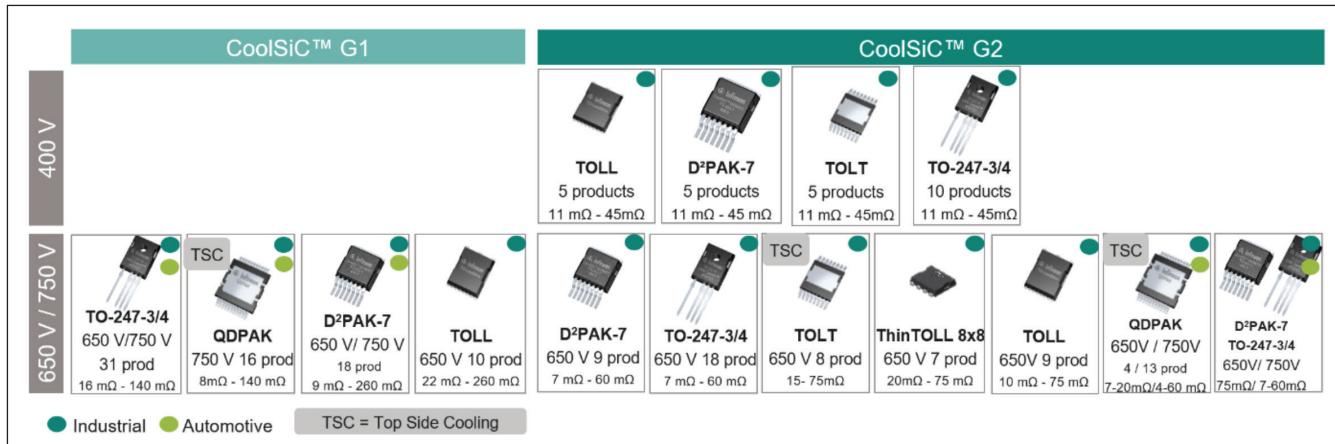

Today Infineon Technologies offers one of the most comprehensive SiC MOSFET offerings in the market and recently has expanded the product families with Generation 2 across 400 V, 650 V, and 750 V voltage classes (Figure 5).

Thus, 400 V CoolSiC™ MOSFET family shows its advantages the best in the multilevel topologies [4]. In 3L Flying Capacitor Continuous Conduction Mode

► Figure 5.

Infineon

Technologies'

CoolSiC™

MOSFET

400-750V

product

families.

The AI revolution is reshaping the design criteria of data center power systems. Unlike conventional server environments that were CPU-centric and operated in relatively predictable load conditions, AI servers operate in highly dynamic states with rapid current surges and higher sustained power demands. In fact, racks that once consumed under 10 kW are now pushing beyond 300 kW per rack and even above 500 kW in specialized training clusters

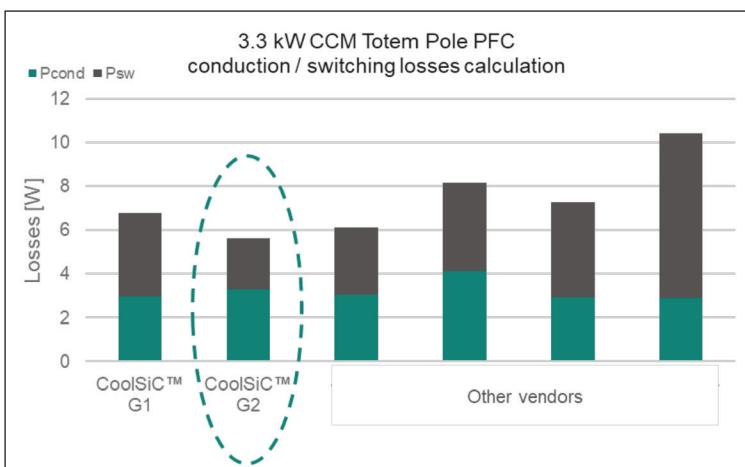

► Figure 6. 650 V CoolSiC™ MOSFET Gen 2 conduction/swapping losses in 3.3 kW CCM TP PFC.

(CCM) Totem Pole topology 400 V SiC provides:

- Lower PFC ripple current leading to lower Root Mean Square (RMS) currents and Total Harmonic Distortion (THD) compared to Triangular Current Mode (TCM) mode.

- Easier control, sensing and electromagnetic interference (EMI) filter design with fixed-frequency operation compared to variable-frequency operation in TCM mode

- Effective frequency on the 3L-PFC inductor is double that of the device switching frequency. Due to the multi-level voltage output of the HF-leg, volt-seconds on the inductor is further reduced. This leads to a potential 4x shrink in PFC-inductor size

- HF-leg switches block half the DC-link voltage, leading to lower switching losses and lower dv/dt swings for a reduced EMI emissions enabling a reduction in the EMI filter size

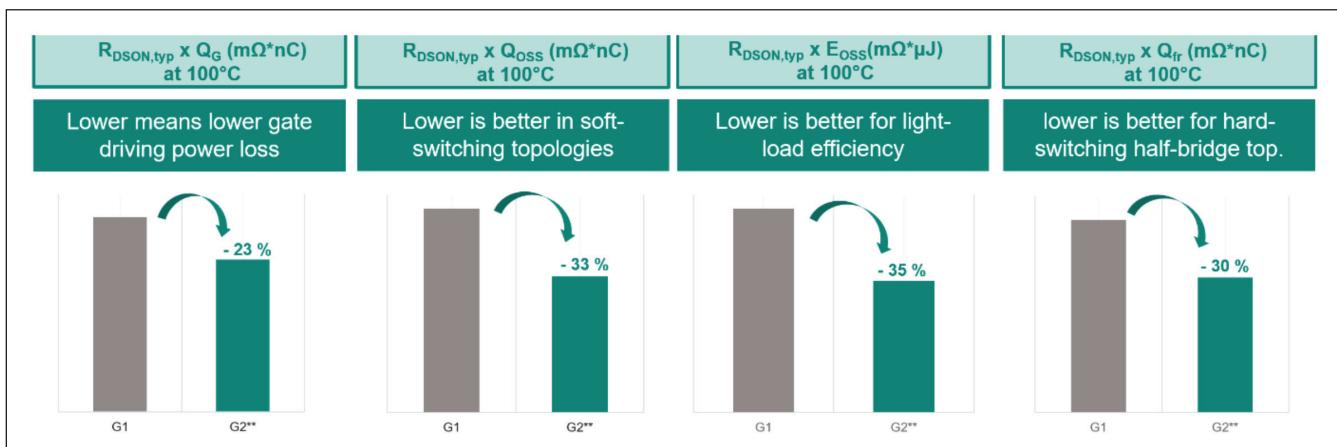

650 V CoolSiC™ MOSFET Gen 2 devices (when compared to Gen1) are engineered for higher switching speeds, lower gate charge, reduced reverse recovery charge and output capacitance/charge values [5] — making them ideal for demanding hard-switching topologies (Figure

6). These enhancements directly translate into improved efficiency and thermal behavior.

For hardware design manufacturers, the benefit lies in reduced cooling requirements, greater design freedom, and the ability to hit higher power density targets without compromising on system reliability.

In short, the CoolSiC™ 650V Gen 2 family fits well in the building blocks to support today's most advanced AI data center power supply architectures encompassing both hard-switching (PFC) and soft-switching (LLC) topologies as described before. Infineon Technologies' 750V CoolSiC™ MOSFET portfolio is engineered for higher voltage and harsher operating conditions, making it ideal for both industrial and high-end server PSU applications [6]. Gen 1 MOSFETs offer excellent switching performance and ruggedness, while Gen 2 pushes the performance frontier even further.

With RDS(on) values as low as 4 mΩ, these MOSFETs deliver ultra-low conduction losses, essential for efficient high-power systems. Available in through-hole (THD), surface mount device (SMD), as well as SMD top-side cooled (TSC) like Q-DPAK package, this portfolio offers design flexibility.

Gen 2 devices have industry leading lowest specific on-resistance, lower gate charge (QG), output capacitance (QOSS), and output capacitance stored energy (EOSS), translating into faster switching and reduced switching losses. These characteristics are critical for high-frequency, soft-switching topologies where fast transition speeds and minimal dead time improve both efficiency and system density.

Moreover, these devices are being adopted in everything from electric vehicle fast chargers to AI data center PSUs. Their robustness, efficiency, and thermal characteristics are redefining what's possible at the 8 – 30 kW PSU level.

One of the key features that brings CoolSiC™ Gen 2 on top is the .XT [7] interconnection technology offered across all voltage classes, which marks

► Figure 7. 750 V CoolSiC™ MOSFET Gen 2 figures of merit vs 750 V Gen 1.

## From reliability standpoint, SiC MOSFETs exhibit robust avalanche and short circuit capability and a relatively lower positive temperature coefficient of RDS(on) than Silicon MOSFETs

a significant leap in packaging and thermal performance.

Traditional solder-based interfaces exhibit limitations in thermal resistance and mechanical robustness under high current cycling. The .XT uses a diffusion solder process to create a highly thermally conductive bond between the die and the lead frame. This reduces RthJC (thermal resistance junction-to-case) by up to 25%—significantly enhancing thermal performance and allowing for more compact and reliable system designs.

This advancement is particularly critical in AI data centers where power density is climbing up and thermal margins are shrinking. The .XT also improves reliability under power cycling, reducing the risk of joint fatigue or thermal cracking over time. For system designers, this means longer operational life, less frequent maintenance, and fewer cooling constraints. The powerful combination of CoolSiC™ MOSFETs and .XT technology enables PSUs that are not just smaller and cooler, but also significantly more robust—exactly what's needed in mission-critical AI infrastructure.

Nowadays environmental impact of power efficiency improvements is often overlooked. However, deploying 650V CoolSiC™ Gen 2 in the PFC stages of all global data centers would save approximately 2.9 terawatt-hours of electricity over five years [1]. That equates to 1.35 million metric tons of CO<sub>2</sub> emissions avoided—the same as removing nearly 300,000 cars from the road.

These calculations are not based on optimistic projections; they are grounded in real operating profiles, mission loads, and validated efficiency gains from production-ready reference boards of Infineon Technologies. As global electricity prices tend to rise with power hungry data centers, and carbon regulation intensifies, these savings become more than a “nice to have”—they are operational imperatives. Today Infineon Technologies helps customers meet Environmental, Social and Corporate Governance targets while also enhancing their bottom line.

Through energy-efficient CoolSiC™ MOSFETs, we contribute to a cleaner, greener digital infrastructure. Sustainability and performance no longer need to be tradeoffs—they go hand in hand. The data centers are no longer a passive utility—it is the active brain of the digital economy. As AI accelerates toward exascale compute, the infrastructure behind it must evolve. Silicon carbide MOSFETs provide the building blocks for that evolution. With unmatched performance in efficiency, density, and reliability, 400V, 650V, and 750V SiC devices are now essential for AI server power conversion stages of the existing 48V and the upcoming 800V or ±400V bus architectures.

Infineon Technologies' full stack SiC strategy, supported by industry partnerships and deep application expertise, ensures that power electronics keep pace with computing demands. In this new era of power-hungry, thermally constrained, and environmentally conscious compute, the message is clear: AI cannot run without SiC MOSFETs.

## FURTHER READING

- [1] A. Cherkasov; “SiC-based power solutions for AI: Enabling next-generation server power supplies with unparalleled efficiency and reliability”; Power Electronics International, 2025

- [2] 3.3 kW high-frequency, high-density PSU with three-level flying capacitor PFC for server and data center applications, Application note, 2025 - <https://www.infineon.com/assets/row/public/documents/24/42/infineon-reference-design-ref-3k3w-3lfc-psu-applicationnotes-en.pdf>

- [3] 5.5 kW three-phase interleaved LLC converter with 650 V CoolSiC™ TOLT, Application note, 2025 - <https://www.infineon.com/assets/row/public/documents/24/42/infineon-evaluation-board-eval-5k5w-3ph-llc-sic2-applicationnotes-en.pdf>

- [4] CoolSiC™ MOSFET 400 V and 440 V G2 - <https://www.infineon.com/content/dam/infineon/row/restricted/documents/24/296/disti/infineon-coolsic-mosfet-400-v-g2-customerconnector-en.pptx>

- [5] CoolSiC™ MOSFET discrete 650 V G2 Industrial, 2025 - <https://www.infineon.com/content/dam/infineon/row/restricted/documents/24/156/customer/infineon-coolsic-mosfet-650v-g2-productpresentation-en.pptx>

- [6] CoolSiC™ 750 V G2 Industrial MOSFET, Application note, 2025 - <https://www.infineon.com/assets/row/public/documents/24/42/infineon-coolsic-750v-g2-industrial-mosfet-applicationnotes-en.pdf>

- [7] .XT interconnection technology - <https://www.infineon.com/technology/xt>

# INTERNATIONAL CONFERENCE

ANGELTECH

20-22 APRIL 2026

BRUSSELS

BELGIUM

CONNECTING, EDUCATING & INSPIRING THE POWER ELECTRONICS INDUSTRY

## REGISTER NOW: [PEINTERNATIONAL.NET/REGISTER](http://PEINTERNATIONAL.NET/REGISTER)

Power Electronics International 2026 returns for its 4th edition as part of the leading series of senior-level chip level conferences for the global power electronics industry, bringing together executives, end users and technology experts for two days of insight, discussion and collaboration. The conference will focus on four key themes:

- Putting the Automotive Industry in Pole Position

- Ensuring a Renewable, Sustainable Future

- Delivering AI-driven Data Centre Densification

- Engineering Innovation with WBG Devices, Circuits and Materials

Co-located with **CS International**, **PIC International** and **Advanced Packaging International**, the event features four focused conference programmes and a shared exhibition hall.

With over **800 attendees** and more than **80 exhibitors**, the event also includes two evening networking drinks receptions, providing valuable opportunities for conversation, collaboration and business development.

PLATINUM

STARTUP

SUPPORTING PARTNER

OPENING RECEPTION

REGISTRATION

## POWER ELECTRONICS SPONSORS

DATACENTRE SOLUTIONS

SUPPORTING PARTNER

OPENING RECEPTION

REGISTRATION

## MEDIA PARTNERS

## 2026 SPEAKERS INCLUDE

## ORGANISERS

# ANGELTECH

**CS** INTERNATIONAL CONFERENCE

**PIC** INTERNATIONAL CONFERENCE

**PE** INTERNATIONAL CONFERENCE

**AP** INTERNATIONAL CONFERENCE

**AIS** ANGELTECH INNOVATE SUMMIT

## Sponsorship / Exhibition / Speaker OPPORTUNITIES AVAILABLE!

Sponsorship, exhibition, and speaker opportunities at PE International, enable and empower you to educate and penetrate the global power electronics industry using multiple marketing tools.

Demand is high, with sponsorship, exhibition and speaking slots already being secured for 2026, so to avoid disappointment, please get in touch today.

**10% off registration offer by scanning the code**

**10% OFF**

## Key Themes for 2026

### Putting the Automotive Industry in Pole Position

What are the most effective ways to improve reliability, efficiency, and fast-charging for electric vehicles while managing thermal and wide bandgap challenges?

### Ensuring a Renewable, Sustainable Future

Can greater efficiency in power conversion and better integration of renewables lead to a more stable and low-carbon energy grid?

### Delivering AI-driven Data Centre Densification

What solutions will deliver reliable, high-density power for AI data centres as space and thermal demands grow?

### Engineering Innovation with WBG Devices, Circuits and Materials

Will advances in SiC and GaN technologies finally break through technical and supply chain barriers for wide bandgap adoption?

To find out more about our sponsor and speaker opportunities, contact us today on:

+44 (0) 2476 718970

[info@peinternational.net](mailto:info@peinternational.net)

[peinternational.net](http://peinternational.net)

ANGEL EVENTS

## Addressing the protection challenges of 48V AI servers using hot-swap controllers

Enabling the design of a reliable input protection solution for a 48V AI server.

BY AVISHEK PAL, POWER SWITCHES AT TEXAS INSTRUMENTS AND RAKESH PANGULOORI, POWER SWITCHES AT TEXAS INSTRUMENTS

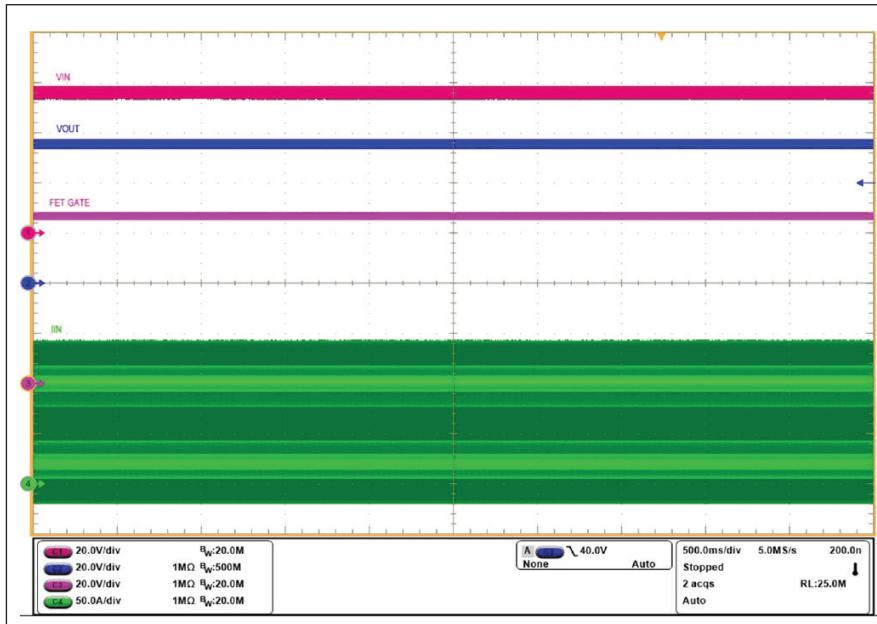

WITH ADVANCEMENTS in artificial intelligence (AI) and machine learning, enterprise servers have become extremely power-hungry as they simultaneously process a large amount of data and storage. The steady-state power rating of each server

motherboard has gone up to 5kW or 6kW, in contrast to 1kW or 2 kW for general servers. The form factor remains the same, however, which imposes system design challenges given the increased power density. The load amplitude, slew rate and frequency

of transient loads on AI servers have increased three to four times compared to general servers.

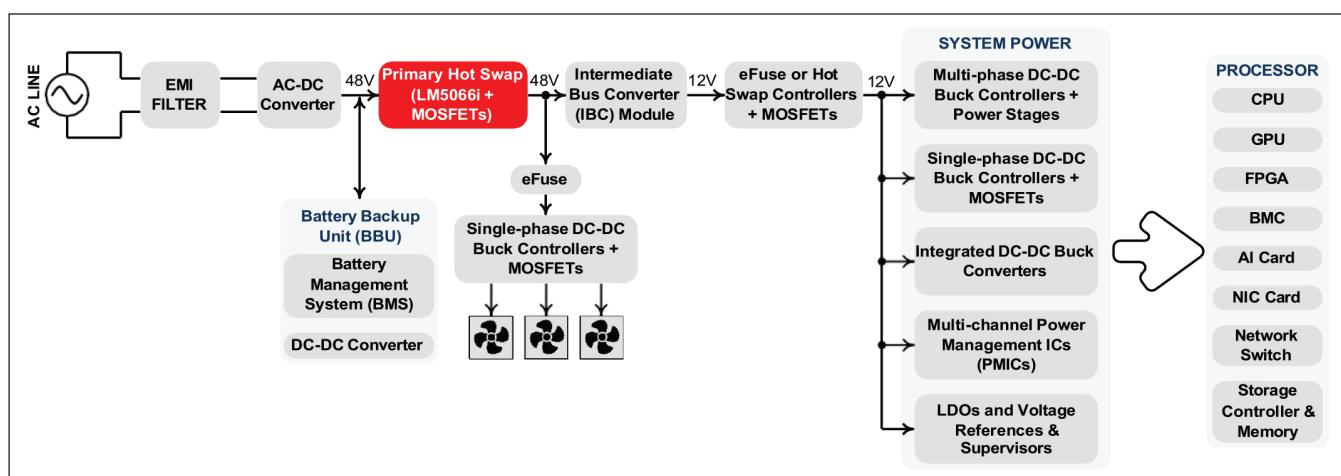

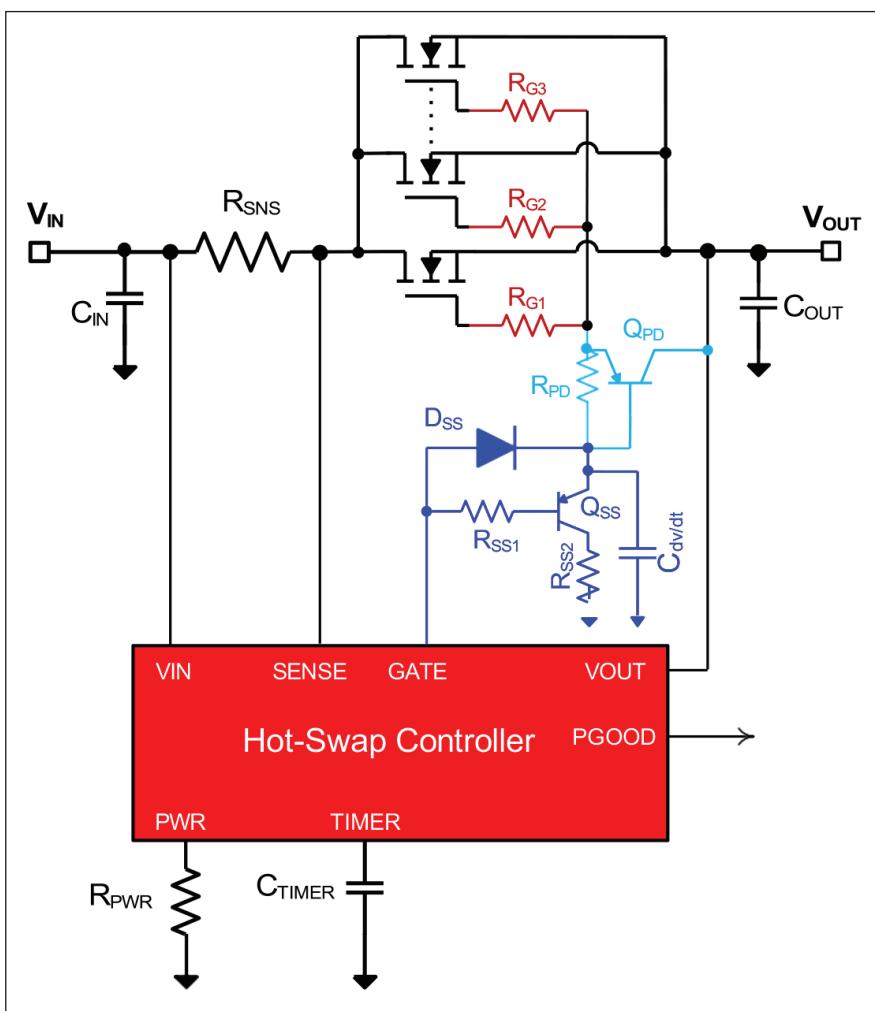

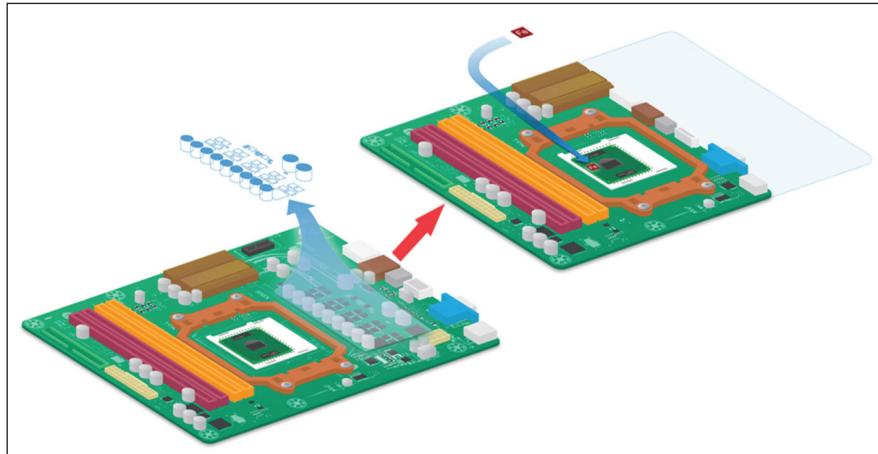

Figure 1 shows a typical power distribution in a 48V rack server where the input is protected by the hot-swap

► Figure 1. Typical block diagram of a 48V rack server power distribution.

circuit - and then distributed to all downstream system loads.

In this article, we'll discuss various challenges that AI-based processors bring into 48V server designs, along with design guidelines and important tips and tricks for the design and layout to achieve a reliable hot-swap solution for the system specifications outlined in Table 1.

Challenges in designing a hot-swap circuit for a 48V AI server

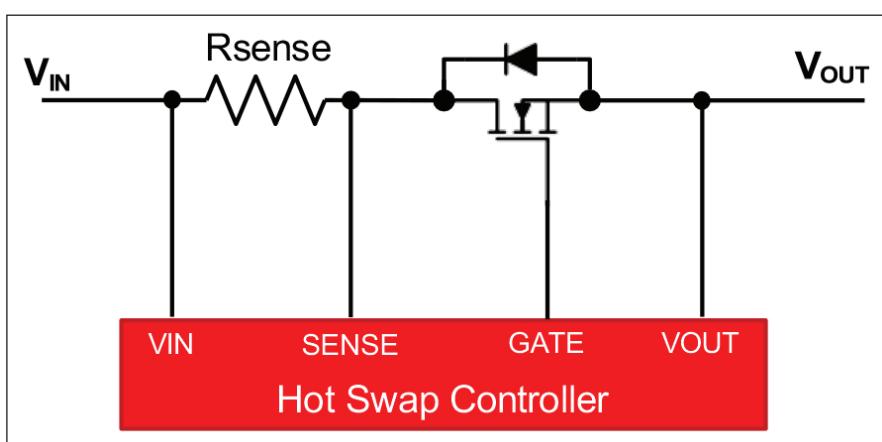

It's interesting to look at how hot-swap circuit configurations have evolved over the years. A hot-swap solution consists of three main components: a N-channel metal-oxide semiconductor field-effect transistor (MOSFET) that serves as the main power control switch; a sense resistor that measures the current; and the hot-swap controller, which includes a current-sense amplifier completing the loop to control the MOSFET's pass current.

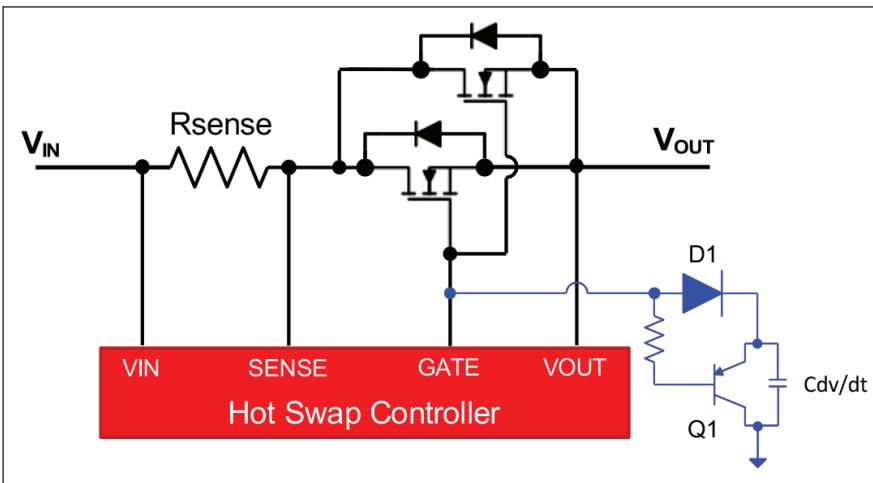

As shown in Figure 2, you can use a single MOSFET-based hot-swap solution for low-power designs. Fundamentally, the hot-swap controller comes with current- and power-limiting functionalities to limit the inrush and fault currents while ensuring the MOSFET's safe operating area (SOA). These functionalities are good enough to design low-power (<500W) hot-swap solutions.

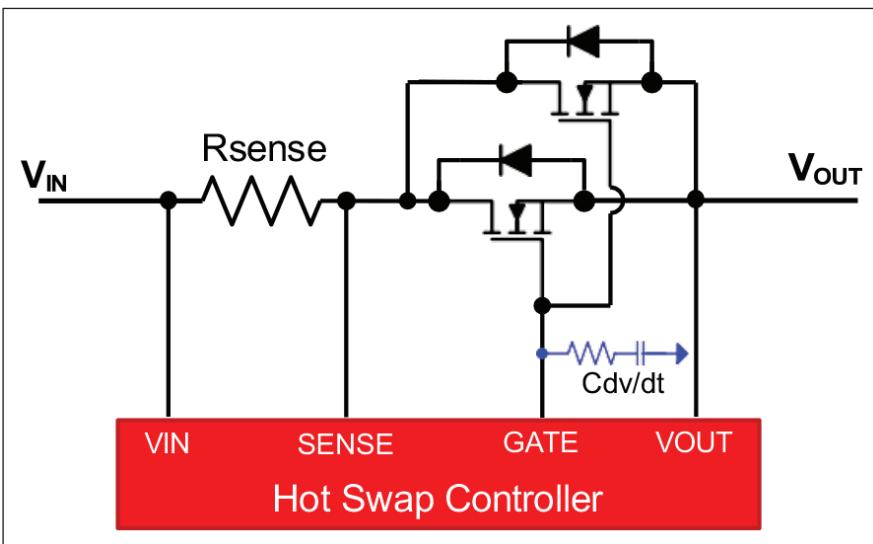

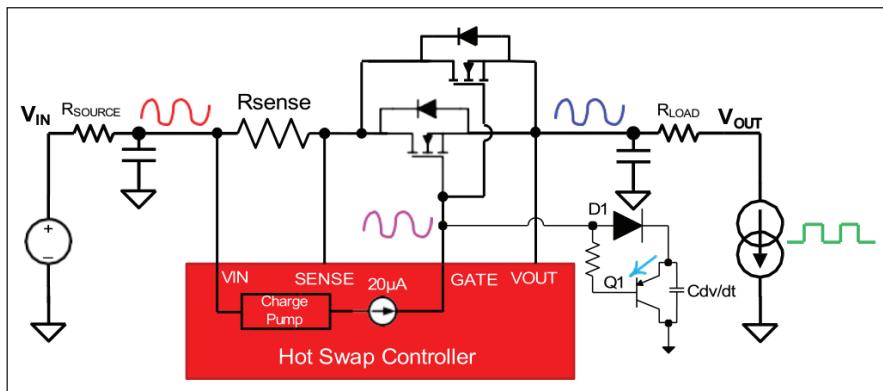

With the increase in digital load, the system needs a higher output capacitance (>470 $\mu$ F), requiring parallel MOSFETs to support steady-state current and the adoption of output-voltage slew-rate control [1] to keep the MOSFET within its SOA.

In the output-voltage slew-rate control method, capacitor C<sub>dv/dt</sub> placed across GATE-GND (see Figure 3) limits the slew-rate of the gate and output voltages, which limits the inrush current. MOSFETs can handle more energy

| Design Parameter                         | Value                                                           |

|------------------------------------------|-----------------------------------------------------------------|

| Input voltage range                      | 40V to 60V                                                      |

| Output capacitance                       | 4.2mF                                                           |

| Steady-state thermal design power rating | 6kW                                                             |

| Transient power rating                   | 8kW at 400 $\mu$ s                                              |

| Transient load profile                   | 15% to 100% of the transient power rating with a 10% duty cycle |

| Load slew rate                           | >2A/ $\mu$ s                                                    |

| Frequency of transient load              | >1kHz                                                           |

► Table 1. Typical system specifications.

► Figure 2. Traditional power-limiting hot-swap circuit.

when the power dissipation in them is reduced and spread over longer durations. Therefore, as the output capacitance increases, you need a higher C<sub>dv/dt</sub> to reduce both the inrush current and power dissipation in the MOSFET during startup.

A higher C<sub>dv/dt</sub> interferes with the turnoff process, however, the hot-swap controller has limited pulldown strength. This necessitates a local P-channel N-channel P-channel (PNP)-based discharge circuit for C<sub>dv/dt</sub>, as shown in Figure 4. During startup, C<sub>dv/dt</sub>

controls slew-rate in the same way, but during a turnoff event, the Q1 PNP transistor activates and discharges C<sub>dv/dt</sub> locally. Diode D1 blocks the discharge of C<sub>dv/dt</sub> into the GATE pin, which reduces the stress on the GATE pin and also ensures proper operation of the controller.

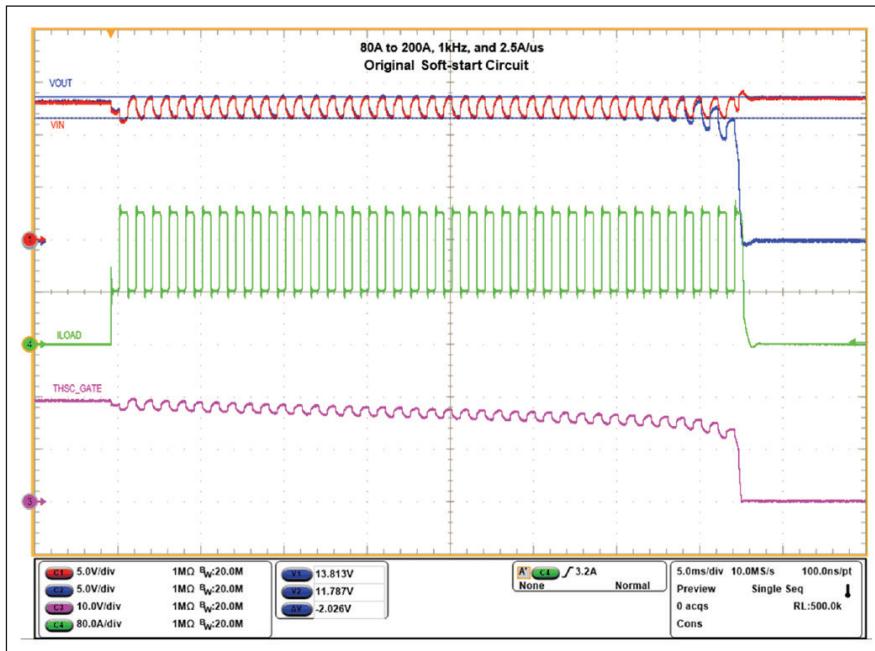

In AI-powered graphics processing unit applications, the hot-swap solution has to support currents around 150A and must support high-frequency, high slew-rate load transients, which present three new challenges.

The hot-swap gate node is decoupled from the MOSFET gate terminal by placing the DSS diode between them. This modification helps eliminate the reflection of output voltage ripple to the hot-swap controller GATE node and avoids false turn-on of the soft-start PNP transistor, Qss.

► Figure 3. Hot-swap circuit with GATE slew-rate control.

► Figure 4. Hot-swap circuit with local discharge path for  $C_{dv/dt}$ .

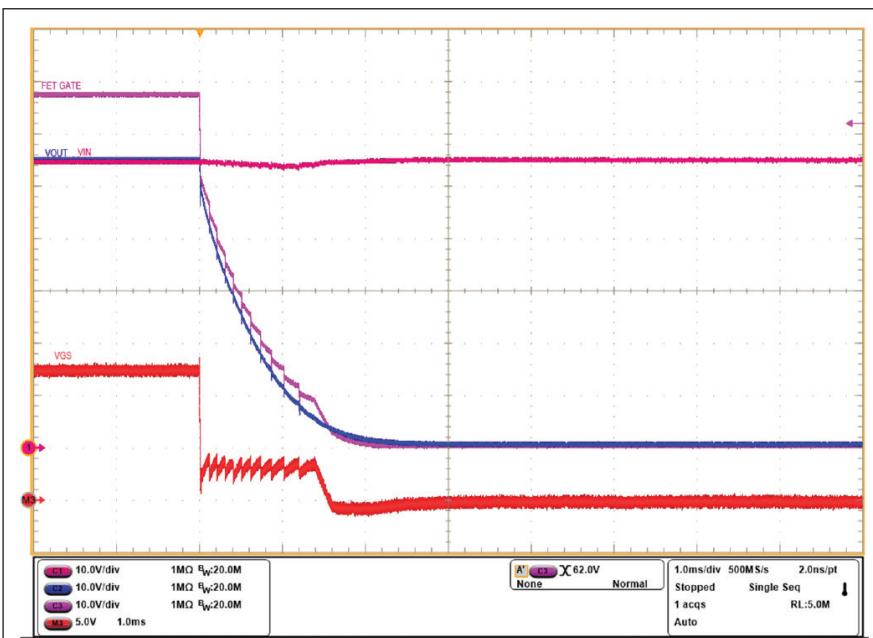

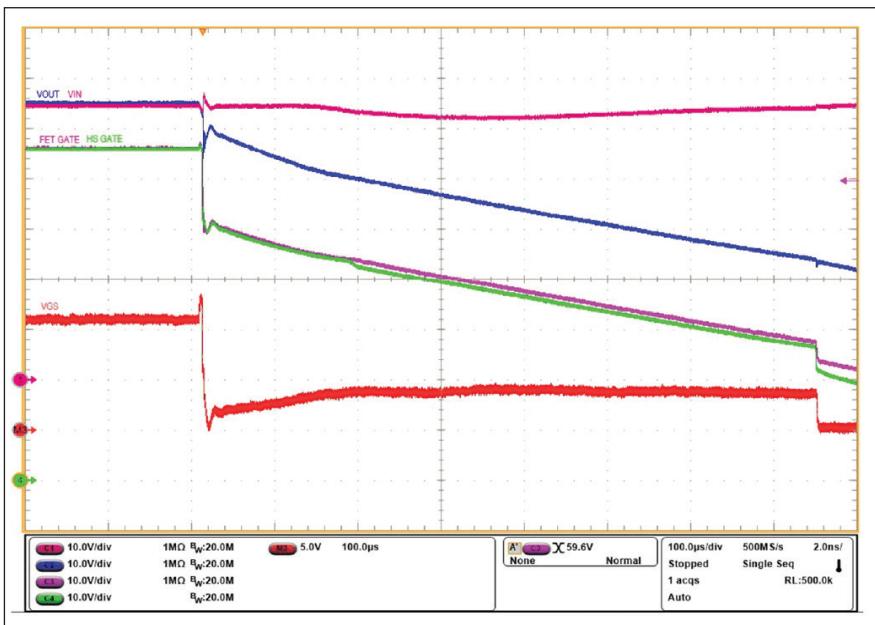

► Figure 5. Short-circuit response of the LM5066I controller with eight MOSFETs.

### Challenge No. 1: Turnoff delay during an output short-circuit

With the increase in load current, more MOSFETs need to be parallel to limit the maximum steady-state MOSFET junction temperature to a safe value (100°C to 125°C).

For example, to support a steady-state load current of 150A at an ambient temperature of 70°C, eight Texas Instruments (TI) CSD19536KTT MOSFETs need to be in parallel to limit the steady-state MOSFET junction temperature to 100°C. Paralleled MOSFETs help thermally, but increase the effective capacitance on the GATE pin of the hot-swap controller and impact the turnoff response.

During an output short-circuit, the MOSFETs need to turn off fast enough to prevent further buildup of fault current and avoid damage to the MOSFETs, input power supply, or printed circuit board (PCB). The gate pull-down strength of the TI LM5066I hot-swap controller is limited to 160mA, which is not enough to turn off all eight MOSFETs completely during a short-circuit event, as shown in Figure 5.

### Challenge No. 2: False gate turn-off during a load transient