## **INSIDE**

News Review, Features News Analysis, Profiles Research Review and much more...

## Splitting hairs to ten to the power of four

14ACMOS: EU project for the next technology node in semiconductor manufacturing

## High-voltage SiC for storage & MV-Grid conversion

As reliance on renewable energy continues to increase, a threelevel converter architecture built using high-voltage SiC MOSFETs

## **Cost-effective** SiC substrate manufacturing

Silicon Carbide (SiC) power devices are seen as a gamechanger in the automotive industry.

## AIXTRON

## THE NEW G10 SERIES

Your Productivity Solution for All Advanced Epitaxy Materials

## G10-SiC

- ▶ 9x150 mm (6") or 6x200 mm (8")

- New hardware & process surpassing Single Wafer Reactor uniformities

- ► +50% productivity per fab area with large batch technology & small footprint

### **End Markets/Products:**

EV inverters & charging infrastructure

## G10-GaN

- ▶ 8x150mm (6") or 5x200mm (8")

- ▶ 1<sup>st</sup> fully automated compact GaN MOCVD cluster designed 100% for Si Power fabs

- Novel hardware solution for unmatched barrier uniformities and device yields

## **End Markets/Products:**

Power Electronics & Wireless communication

## G10-AsP

- ▶ 8x150 mm (6") or 5x200 mm (8")

- ▶ 1<sup>st</sup> fully automated AsP MOCVD system enabling 10x lower defect density

- Unmatched wavelength uniformity on all wafer sizes

## **End Markets/Products:**

Micro LED, Optical Data communication, 3D-sensing & LiDAR

## **VIEWPOINT**

By Phil Alsop Editor

## Power electronics can provide a sustainable, digital future

Having arrived in the semiconductor industry by way of, most recently, the data centre industry, it's fascinating to compare and contrast these two technology sectors and, not least, to understand that they are, in essence, two key parts of the same overall ICT supply chain. Asked what I do for a living, folks' eyes tend to glaze over when I tell them that I work on data centre and digital transformation publications – magazines, newsletters and websites.

Until, that is, I am given the chance to explain that, like it or not, there's almost no activity undertaken in today's digital world without some reliance on a data centre somewhere in the background. I won't say that my audience becomes engrossed with thoughts of servers, routers and storage hardware, let alone power and cooling technology, but there is certainly some recognition of this truth and maybe a grudging understanding of just how important are data centres in our digital lifestyles.

And now, of course, I can add to my party conversation, the fact that I also work in the semiconductor industry – focusing on both silicon semiconductors and power electronics. Once again, I can explain to whoever wants to listen that semiconductors and, in particular, power electronics, are an equally essential part of the digitalisation process.

Conversations about the digital world often move on to contemplation of sustainability and the inevitable discussion as to whether a truly digital and sustainable world is actually achievable. We'll leave that debate for another day, but let us recognise the vital role that the power electronics world has to play when it comes to improving energy efficiency in so many applications and in so many ways:

- Power generation (especially when it comes to renewables and energy storage)

- Industrial automation, drives and controls

- Information and communications (ICT)

- Emobility and etransportation

- Smart/connected homes

As this issue of PEW demonstrates, there's a great deal of innovation in the power electronics sector to develop new materials and solutions with the major focus of providing significantly more sustainable power however, wherever and whenever required.

I don't have anything more complicated to add – other than to recommend that, every now and then, it's good to view the industry in which you work from an outsider's perspective. To understand the fantastic work that's often taken for granted and to maybe take

## 18 Splitting hairs to ten to the power of four

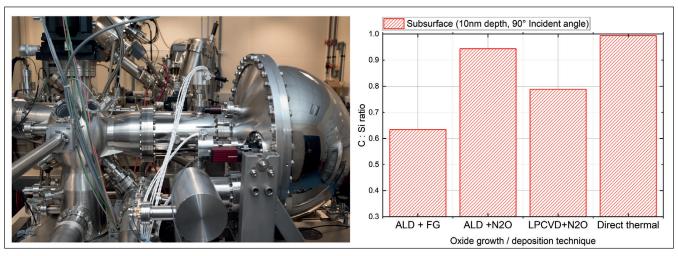

14ACMOS: EU project for the next technology node in semiconductor manufacturing

## 22 Cost-effective SiC substrate manufacturing for power devices enabled by oxide-free wafer bonding

Silicon Carbide (SiC) power devices are seen as a game-changer in the automotive industry

## 28 High-voltage SiC for storage & MV-grid conversion

As reliance on renewable energy generation continues to increase, a three-level converter architecture built using high-voltage SiC MOSFETs enhanced with an integrated MPS diode boosts efficiency and reliability in the storage-to-grid connection

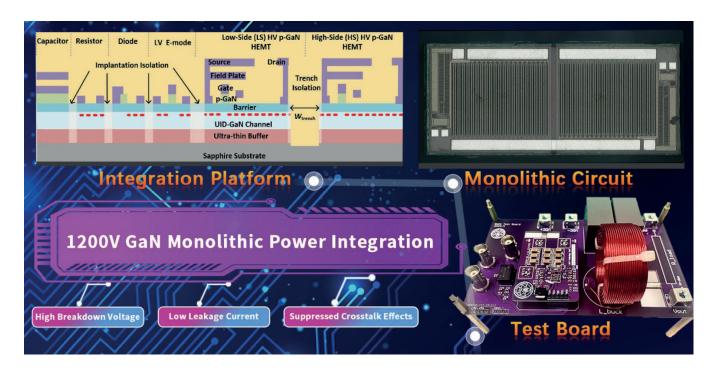

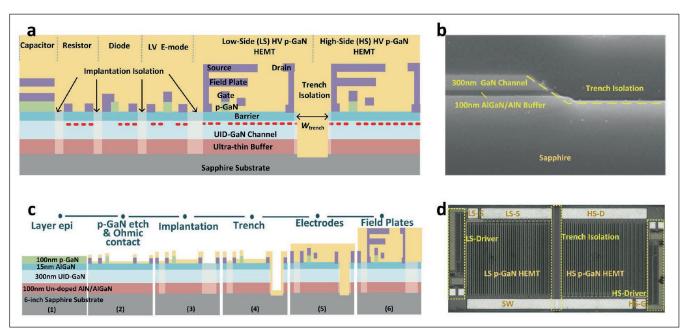

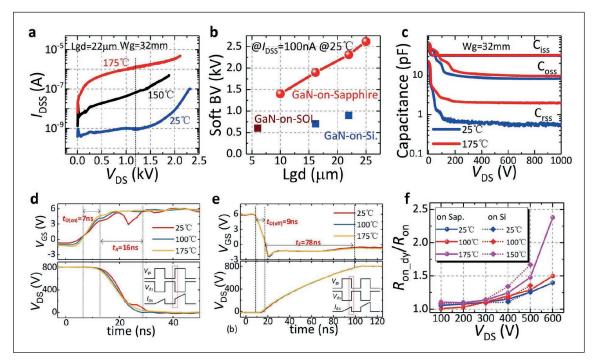

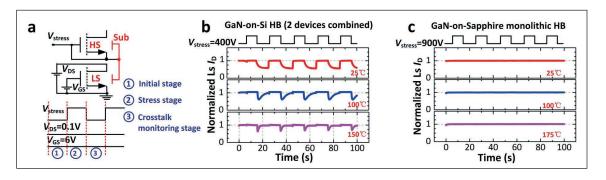

## 32 1200 V GaN monolithic power integration

Sapphire substrates with ultra-thin buffer layers provide a foundation for fabricating systems offering 1200 V GaN-based monolithic power integration while supressing crosstalk

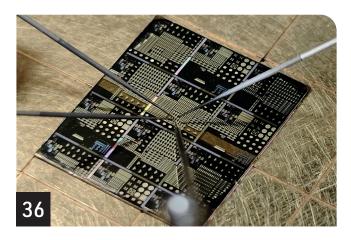

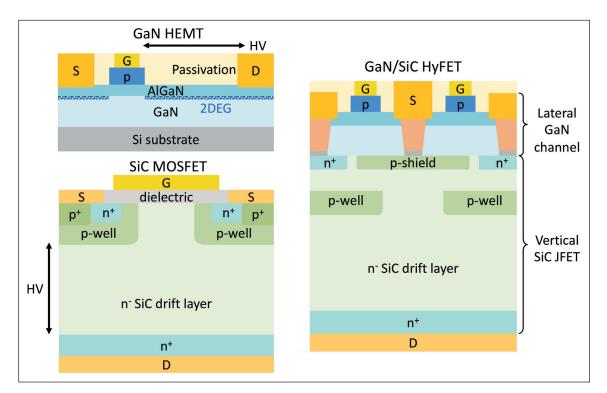

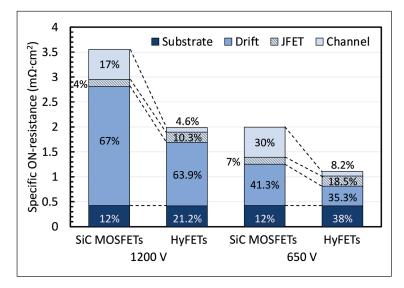

## 36 A mighty marriage

A monolithic architecture combines the complementary merits of GaN lateral heterojunctions and SiC vertical power devices

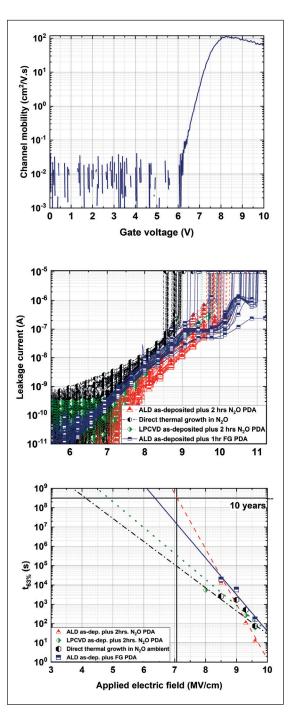

## 44 Gate to the future

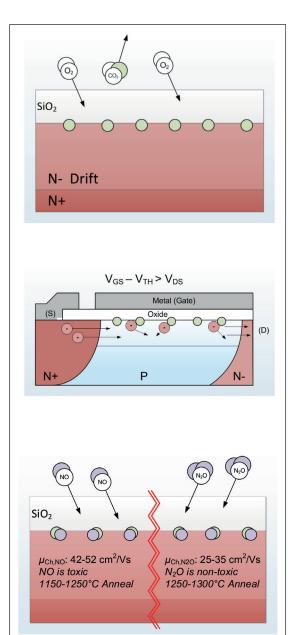

Reliability benefits from deploying deposited gate oxides in SiC MOSFETs

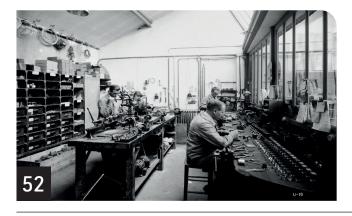

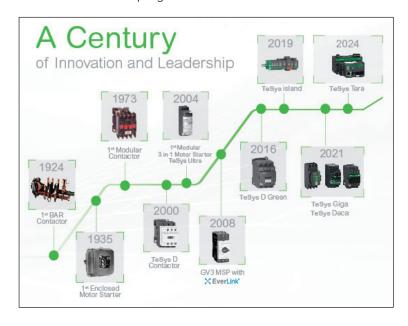

## 52 Celebrating a century of innovation in power electronics: Schneider Electric

Schneider Electric, the industrial technology leader of energy management and automation, have been at the forefront of innovation for over 100 years

## **NEWS**

**06** GaN transistors: An escalating patents war

08 Almost 42 million EV cars worldwide

- **09** Scientists use waste RF to power electronics

- 10 Russian venture targets SiC power

- 11 German research cluster announces AlN success

### Editor

Phil Alsop phil.alsop@angelbc.com +44(0)7786084559

### News Editor

Christine Evans-Pughe christine.evans-pughe@angelbc.com

### Contributing Technical Editor

Richard Stevenson richard.stevenson@angelbc.com +44 (0)1923 690215

## Sales & Marketing Manager

Shehzad Munshi shehzad.munshi@angelbc.com +44 (0)1923 690215

### Design & Production Manager

Mitch Gaynor mitch.gaynor@angelbc.com +44 (0)1923 690214 Senior Event and Media Executive for Power Electronics International

James Cheriton james.cheriton@angelbc.com +44 (0)2476 718970

## Publisher

Jackie Cannon jackie.cannon@angelbc.com +44 (0)1923 690205

CEO Sukhi Bhadal sukhi.bhadal@angelbc.com +44 (0)2476 718970

CTO Scott Adams scott.adams@angelbc.com +44 (0)2476 718970 PEW Magazine is published four times a year on a controlled circulation basis. Non-qualifying individuals can subscribe at: £105.00/e158 pa (UK & Europe), £138.00 pa (air mail), \$198 pa (USA). Cover price £4.50. All information herein is believed to be correct at time of going to press. The publisher does not accept responsibility for any errors and omissions. The views expressed in this publication are not necessarily those of the publisher.

Every effort has been made to obtain copyright permission for the material contained in this publication. Angel Business Communications Ltd will be happy to acknowledge any copyright oversights in a subsequent issue of the publication. Angel Business Communications Ltd © Copyright 2024. All rights reserved. Contents may not be reproduced in whole or part without the written consent of the publishers. The paper used within this magazine is produced by chain of custody certified manufacturers, guaranteeing sustainable sourcing.© Copyright 2024.

We strive for accuracy in all we publish; readers and contributors are encouraged to contact us if they recognise an error or omission. Once a magazine edition is published [online, in print or both], we do not update previously published articles to align old company names, branding, marketing efforts, taglines, mission statements or other promotional verbiage, images, or logos to newly created or updated names, images, typographic renderings, logos (or similar) when such references/images were accurately stated, rendered or displayed at the time of the original publication.

When companies change their names or the images/text used to represent the company, we invite organizations to provide Angel Business Communications with a news release detailing their new business objectives and/or other changes that could impact how customers/prospects might recognise the company, contact the organisation, or engage with them for future commercial enterprise.

Published by Angel Business Communications Ltd 6 Bow Court, Fletchworth Gate, Burnsall Road, Coventry CV5 6SP, UK. T: +44 (0)2476 718 970

E: info@angelbc.com W: angelbc.com

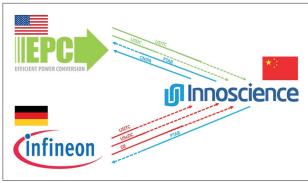

## GaN transistors: An escalating patents war

The battle over intellectual property surrounding the GaN power transistor is intensifying, with EPC and Infineon attacking Innoscience over patent infringement that it vigorously denies.

WITHIN OUR INDUSTRY, last summer will be remembered as the start of a global war surrounding the intellectual property (IP) of the GaN power transistor. Back then, Efficient Power Corporation fired the first shots, accusing Innoscience of infringing four of its patents. In only a matter of days Innoscience shot back, denying any wrongdoing. More recently, another company has entered the fray, with Infineon claiming that Innoscience is also not respecting its IP. And again, Innoscience is pleading innocence.

As claims and counterclaims are launched in courtrooms around the world, there is much value in hearing from those that combine expertise in this area with a neutral standpoint. Offering all this and more is David Radulescu, head of the patent litigation boutique firm Radulescu, who has been litigating semiconductor patents in courts throughout the US for three decades. More significantly, Radulescu also holds a PhD in compound semiconductor HEMTs and has previously devoted much effort to representing global companies fighting over IP associated with GaN-based LEDs.

In late July, Radulescu spoke for a second year in a row about the escalating IP war in a highly insightful webinar covering various patents that hold the key to deciding the outcome of the many court cases.

Before delving into details, Radulescu summarised the shots that had been fired to date: a pair of actions taken by both EPC and Innoscience in their battle, plus three fired by Infineon and another by Innoscience in their more recent skirmish.

This all kicked off last summer, when EPC announced it took legal action

against Innoscience for infringing four of its patents. In the intervening months, EPC dropped two patents in its International Trade Commission (ITC) case, while initial rulings have been released on the other two this July. According to the administrative law judge (ALJ) in the ITC, both of EPC's patents are not invalid, but significantly, he determined that one of them is infringed.

What's also worth noting is that in the last couple of months action taken by Innoscience in China has also led to rulings that counterpart Chinese EPC patents were not invalid.

"We have Innoscience on its own turf losing in the Chinese Patent Office," remarked Radulescu, who added that the US Patent and Trademark Office (USPTO) is still considering the validity of the patent found to be infringed by the ALJ, although the claims and prior art at issue are identical. Radulescu offered a closer look at the key patents after highlighting the recent stockpiling of US patents issued to Innoscience. In the past year-and-a-half, the Chinese chipmaker was issued 45 US patents, while EPC was issued only one, leading Innoscience to outpace EPC in the total number of US patents by 58 to 57.

### Gate designs

Focusing on the shape of the gate structure is EPC's '508 patent, which the ALJ found to be not invalid but

also not infringed. To put this patent in context, over the last few decades, a number of different gate structures have been used to produce GaN transistors, including: those that are self-aligned, with the gate and the insulator underneath having the same dimension (length); and those that have a T-shape or an inverted T-shape.

The '508 patent describes a multistep process involving the use of three different photoresist patterns to produce a self-aligned gate. For the claims brought by EPC concerning this patent, the key issue, according to Radulescu, is whether "etching away the doped GaN layer, except a portion of the doped GaN layer beneath the gate contact," describes the Innoscience process.

"When you visually look at the [Innoscience] device, you see a gate ledge that is not co-extensive with the gate contact layer," said Radulescu, who is not surprised that the ALJ viewed this transistor as being different from that of EPC, and thus concluding that there was no infringement. The other important matter relating to the '508 patent is that Innoscience has asserted that it is invalid, an argument that was rejected by the ALJ.

## Doping and compensation

Radulescu believes that those involved in ruling on the EPC-Innoscience battle will have a more difficult decision to make when it comes considering claims surrounding the '294 patent entitled 'Compensated Gate MISFET'. In his view, what's crucial is to understand what is meant by 'compensated', against the backdrop of the difficulties that have had to be overcome to realise p-type doping in GaN, key to producing LEDs with this material system.

The key claim by EPC is whether the phrase 'compensated GaN layer' describes the GaN layer in Innoscience's devices that is presumed to be p-type based on its own publications.

It's important to note, argued Radulescu, that EPC's patent does not say anything about the GaN layer's carrier type or its resistivity, characteristics that can be measured. Instead, it just uses the word 'compensated', a characteristic far harder to judge. This is because a picture or image of the device material is not determinative, but requires an understanding of semiconductor material science. The other key point that Radulescu emphasised is that the '294 patent covers simply a transistor, and makes no reference to enhancement-mode or depletionmode devices. Many are assuming that the GaN employed by Innoscience is p-type. "They introduced magnesium, and I will be willing to bet that the hydrogen is intentionally removed after growth," remarked Radulescu, whom added that secondary ion mass spectrometry (SIMS) plots have been disclosed during the case. "Whether or not you can call it 'compensated' depends upon how you define what compensation is," added Radulescu.

Innoscience has argued that they do not employ a compensated GaN layer because they use a Schottky gate, as well as claiming that SIMS data reveals dopant activation, and testing confirms p-type conductivity. According to Radulescu, all these arguments were rejected by the ITC staff due to procedural errors of its counsel. For example, Innoscience offered evidence of the nature of the GaN through the testimony of an employee, an account viewed as problematic due to self-interest.

"Unfortunately for Innoscience, I don't think their best arguments were put forward," commented Radulescu, who explained that the full Commission will now review the ALJ's initial determination of infringement and issue a final decision on the investigation called a Final Determination, which is expected to issue in early November 2024.

Both Innoscience and EPC have tried to claim victory from the initial determination. Innoscience argues that it has won, because one of the patents was determined to not be infringed, while EPC is focusing on a finding of infringement.

The view of Radulescu is that while, in theory, EPC lost on three patents out of four, what really matters is that they have a ruling of a violation of the ITC statute against unfair competition by importing products that infringe US patents. And he believes that given how Innoscience's lawyers argued their defences, it will be far from easy to get the ALJ's determination reversed or modified, although not impossible.

Looking ahead, in March 2025, the US Patent Office will rule on the validity of the four patents asserted by EPC against Innoscience (which are also still at issue in EPC's District Court case against Innoscience in California). If the '294 patent is determined to be invalid, this decision could be appealed, dragging the case on for a couple more years. Significantly, under this scenario, the ITC's final determination will likely not matter as any potential importation ban would be expected to be stayed pending appeal. On the other hand, if the '294 patent is determined to not be invalid, and at the same time the full Commission agrees with the ALJ on infringement of the '294 patent, Innoscience's products found to infringe would presumably be subject to some form of importation ban as that is a typical remedy available to patent owners in these type of ITC investigations.

Infineon versus Innoscience

Infineon's actions against EPC began

in March this year, when they brought

a suit in San Francisco for a patent

associated with high-voltage packages

featuring so-called 'source sensing'.

Innoscience response to this has been

to file a petition this June with the US

Patent Office, arguing for invalidation of

every single claim.

Meanwhile in Germany, Infineon has also filed several cases, as well as obtaining a preliminary injunction that prevented a small fraction of Innoscience's high-voltage GaN transistors from being promoted at PCIM. Commenting on this, Radulescu remarked: "Infineon outmanoeuvred Innoscience's lawyers, because they got that injunction without Innoscience actually being heard on any of the issues. It was a surprise, but not unusual for parties to go to Germany to try to get these preliminary injunctions and mess up trade shows."

Within the last few weeks, Infineon has stepped up its action, adding three more patents to the San Francisco case, and filing its own complaint with the ITC. On the merits, the first of four Infineon patents that have been asserted involves an additional connection to the source of the power transistor, so that the parasitic elements associated with the packaging and connections have a reduced impact on overall system performance.

Infineon's accusations centre on Innoscience's use of a Kelvin source that it claims practices the patented source sensing functionality, as well as an identical pin layout. Like Infineon's products, those in question from Innoscience have 8 pins, including one that's a Kelvin source sensor.

Regarding the three other patents, one is concerned with the thickness of a titanium nitride capping layer in an electrode stack. The other two concern so-called 'merged cascode transistors', with one patent concerned with adding curvature to inter-digitated fingers to trim the electric field strength at the edge of the electrodes, and the other associated with combining a depletion-mode transistor with an enhancement-mode transistor to make a circuit. If the case is not settled beforehand, the ALJ's initial rulings on these patents are not expected until autumn 2025.

While it is impossible to predict the rulings of all the asserted claims to date in the GaN patent war, there is no doubt that substantial time and money will be spent over the next few years trying to defend IP and the products based on them. There are many different outcomes that could emerge, including licensing deals and import bans – but what is for sure is that interesting times lie ahead.

## Almost 42 million EV cars worldwide

## Trend in electromobility continues, according to German research organisation ZSW

14.8 MILLION new electric vehicles were registered worldwide in 2023 (EVs running on battery power alone, plug-in hybrids and vehicles with range extenders), according to new research by ZSW's Centre for Solar Energy and Hydrogen Research Baden-Württemberg, Germany.

China is in the lead with over nine million electric cars while the USA has claimed second place ahead of Germany. The number of new registrations of electric cars in Germany last year was almost 700,000. This brings the current tally of electric cars on German roads to 2,330,400 but this is not enough to achieve the goal set by the German government of 15 million electric vehicles by 2030. The annual level of new registrations would have to double or triple in order to achieve the target.

The global count of electric cars in circulation at the end of 2023 was almost 42 million. More than half of these vehicles are registered in China, ahead of the USA in second place with 4.8 million electric cars and Germany in third place. Setting aside the Chinese figures, the highest growth rates in circulation were seen primarily in smaller markets like Belgium with 71 per cent (192,400 vehicles) or Portugal with 54 per cent (65,000 vehicles).

In terms of new registrations, the EU is the second largest market in the world after China. Around 2.5 million new electric cars were registered here in 2023, with the USA following in third place with 1.5 million vehicles. Electric cars still have the highest share of the total vehicle market in Norway where four in every five new vehicles are powered by electricity.

Germany, by contrast, is seeing a significant slowdown in the momentum gathered in 2022, when the figures rose by 22 per cent on 2021, and is now reporting that new registrations actually fell by 16 per cent in the past year.

One of several factors accounting for this development, says ZSW, is that sales of plug-in hybrids have fallen sharply since the government subsidy scheme ended on 31 December 2022. It is also evident, however, that an 11 per cent growth in cars run entirely on battery power did not fully compensate for this decline.

The higher initial outlay on the purchase of an electric vehicle remains a frequently cited point of criticism. The relatively weak overall economic situation in Germany has probably also had a dampening effect on the development of electromobility, as have falling fossil fuel prices after the phase of high prices in 2022.

"There is a need for new incentives in the market in order to achieve the electromobility targets in Germany – 15 million electric vehicles in circulation by 2030 – and to encourage new momentum in climate action in the transport sector. The initiative for growth proposed by the German government in greater support of electric company cars cannot amount to anything more than an initial step," said ZSW staff member Andreas Püttner.

"In view of the strict austerity budgets choking the public finances, there can be a major impetus in abolishing privileges for conventional vehicles — aka subsidies having an adverse impact on climate targets. Examples of steps which could be taken to come much closer to a 'level playing field', with the same conditions for cars with combustion engines and electric cars, would be to abolish tax breaks for

fossil diesel fuels and for company cars with conventional engines, known as the diesel concession and company car concession respectively, or to limit incentives strictly to company cars powered by electricity."

Despite the weakness of the German domestic market, German manufacturers are successful on the international stage where VW, BMW and Mercedes all rank among the top 10 manufacturers and where VW has even moved up to third place in the statistics on new registrations, having sold just over one million cars overall, according to ZSWI.

Compared to the industry leaders BYD (China) and Tesla (USA), however, there is still a large gap in terms of numbers, with Chinese company BYD reporting sales of over three million electric cars and therewith another significant increase of 68 per cent in the number of new registrations compared to last year, thereby maintaining a confident lead in the rankings over the other manufacturers, while Tesla holds on to second place with 1.8 million sales.

The most successful model in the world by far last year was again the Tesla Model Y, which was sold over 1.2 million times. Tesla enjoys further success with its Model 3 in third place. The other electric cars in the top 10 worldwide all come from China, with the manufacturers BYD, GAC Group and SAIC increasingly widening their range of vehicles.

"If Germany is to achieve its climate control goals, there is an urgent need for attractive vehicles in the lower and middle segments in order to appeal to a larger customer base. If the German and European manufacturers do not fill this gap, there is a risk that other manufacturers, especially those in China, will seize this opportunity in spite of the introduction of punitive tariffs at European level in a bid to prevent this," added Andreas Püttner.

## Scientists use waste RF to power electronics

## Singapore University team leads development of novel energy harvesting module

UBIQUITOUS wireless technologies like Wi-Fi, Bluetooth, and 5G rely on RF signals to send and receive data. Now a team led by scientists from the National University of Singapore (NUS) has developed a prototype energy harvesting module that can convert these ambient RF signals into DC voltage to power small electronic devices.

RF energy harvesting technologies face challenges due to low ambient RF signal power (typically less than -20 dBm), where current rectifier technology either fails to operate or exhibits a low RF-to-DC conversion efficiency. While improving antenna efficiency and impedance matching can enhance performance, this also increases on-chip size, presenting obstacles to integration and miniaturisation.

To address these challenges, a team of NUS researchers, working in collaboration with scientists from Tohoku University (TU) in Japan and University of Messina (UNIME) in Italy, has developed a compact and sensitive rectifier technology that uses nanoscale spin-rectifier (SR) to convert ambient wireless radio frequency signals at

power less than -20 dBm to a DC voltage.

The team optimised SR devices and designed two configurations: 1) a single SR-based rectenna operational between -62 dBm and -20 dBm, and 2) an array of 10 SRs in series achieving 7.8 percent efficiency and zero-bias sensitivity of approximately 34,500 mV/mW. Integrating the SR-array into an energy harvesting module, they successfully powered a commercial temperature sensor at -27 dBm.

"Harvesting ambient RF electromagnetic signals is crucial for advancing energy-efficient electronic devices and sensors. However, existing energy harvesting modules face challenges operating at low ambient power due to limitations in existing rectifier technology," explained Yang Hyunsoo from the Department of Electrical and Computer Engineering at the NUS College of Design and Engineering, who spearheaded the project.

Yang added, "For example, gigahertz Schottky diode technology has remained saturated for decades due to thermodynamic restrictions at low power, with recent efforts focused only on improving antenna efficiency and impedance-matching networks, at the expense of bigger on-chip footprints. Nanoscale spin-rectifiers, on the other hand, offer a compact technology for sensitive and efficient RF-to-DC conversion."

Elaborating on the team's breakthrough technology, Yang said, "We optimised the spin-rectifiers to operate at low RF power levels available in the ambient, and integrated an array of such spin-rectifiers to an energy harvesting module for powering the LED and commercial sensor at RF power less than -20 dBm. Our results demonstrate that SR-technology is easy to integrate and scalable, facilitating the development of large-scale SR-arrays for various low-powered RF and communication applications."

The experimental research was carried out in collaboration with Shunsuke Fukami and his team from TU, while the simulation was carried out by Giovanni Finocchio from UNIME. The results were published in Nature Electronics, on 24 July 2024.

# FLEXIBLE SINTERING SYSTEM SIN 200+ modular For extraordinarily reliable, highly thermally conductive bonds Easy expansion of productivity or functionality by adding modules Patented softool suited for multilayout use and multilayer designs without tooling changes Quasi-isostatic pressure distribution even with different sintering heights Highly flexible and adjustable control of sintering atmosphere Sintering process under inert or reducing atmosphere Individual and free programmable sintering profiles Low energy and media consumption PINK GmbHThermosysteme Am Kessler 6 • 97877 Wertheim info@pink.de • pink.de

## Russian venture targets SiC power

Element and St. Petersburg Electrotechnical University form joint power chip company

RUSSIAN MICROELECTRONICS company PJSC Element and St. Petersburg Electrotechnical University LETI (ETU LETI) have formed a joint venture called Letiel LLC, according to a story on Interfax, a news agency covering Russia.

"We plan to actively develop the area of high-tech power semiconductor devices and in future take leading positions among global manufacturers of SiC devices," Element president Ilya Ivantsov told Interfax.

"The objective of the joint venture with LETI will be to develop and research technologies to produce SiC devices, on the basis of which we will be able to build a modern and competitive power electronics product and technology line for various sectors of industry," Ivantsov said.

The new company will do research and development on SiC based power devices, which are used on production of modern electric vehicles, aircraft navigation systems and other sectors.

The venture, which is 51 percent owned by Element and 49 percent by LETI, also plans to study and design promising Photonic integrated circuits.

These components are used in equipment for cellular networks, satellite systems and radiolocation.

"Mass production of solutions in the area of the electronic component base for power electronics and photon integrated circuits will be rolled out at the facilities of Element Group's new plant in Zelenograd," the company said.

The partners have not specified how much they are investing in the venture, which is headed by Element technology

development director Konstantin Okunev.

Element was formed in 2019 with 19 microelectronics design, development and manufacturing assets belonging to investment group Sistema PJSFC and state corporation Rostec. Element's key portfolio companies are chip factory Mikron and microchip, molecular electronics research institute NIIME and electronics research institute NIIET. The group now includes about 30 enterprises.

## Project to develop EV-grade 1.2 kV SiC MOSFETs

OXFORD INSTRUMENTS will be working with Hitachi Energy Switzerland and the University of Warwick to improve SiC power MOSFET gate technology through the use of ALD oxides.

This is one of 26 new projects intended to enhance UK and Swiss collaboration on innovation and technology, supported by £7.8 million funding from Innovate UK and similar figure from Innosuisse, the Swiss innovation agency.

Hitachi Energy Switzerland (Hitachi) has a proven track record of developing automotive grade SiC power MOSFETs with a reputation for products with novel MOS interfaces. Oxford Instruments Plasma Technology (OIPT) has developed a novel oxide deposition process that uses a remote plasma source in a commercial atomic layer deposition (ALD) system. This process is suitable for the formation of gate oxides in wide bandgap semiconductors.

A research team at the University of Warwick (UoW) has recently developed an ALD SiO2 deposition process on SiC that has the potential to be commercialised.

This project will bring together the three groups and their relative expertise to demonstrate the potential of ALD oxides in the formation of EV-grade 1.2 kV SiC MOSFETs.

The aim is address one of the most pressing issues in the adaptation of this

technique by fundamentally changing the way of forming a crucial part of the device, the gate oxide. Conventional dielectric and SiC interfaces are suffering from high density of defect states, hampering the further uptake of this technology.

This proof-of-concept project will demonstrate the viability and advantages of utilising ALD deposited oxides (SiO2 and high-k dielectrics such as aluminium oxide, Al2O3 in a commercial SiC MOSFET device.

The partners aim to deliver the first demonstration of a commercially relevant planar 1.2 kV SiC MOSFET that contains OIPT's remote plasma ALD-deposited SiO2 and high-k dielectric (for example Al2O3) gate oxides.

## German research cluster announces AIN success

German partners demonstrate practical implementation of AIN-based value chain for power semiconductors

A NEW semiconductor technology based on AIN for power electronic transistors as well as mmWave radio-frequency circuits has the potential to significantly reduce losses in electrical energy conversion and high frequency transmission, according to German research partners.

Devices on single-crystal AIN wafers reach a higher power density and efficiency compared to GaN technology. They also show lower dynamic parasitic effects and a higher reliability.

At the same time, the high thermal conductivity of AIN enables good heat dissipation of the devices.

In order to make AIN technology accessible to industry in the medium term, the related existing activities in Germany have been combined in a strategic cluster,.

The aim is to establish a German value chain for AIN-based technology and to build up an international leadership position in this increasingly economically important field.

The Ferdinand-Braun-Institut (FBH), the Fraunhofer Institute for Integrated Systems and Device Technology IISB and the company III/V-Reclaim PT GmbH drive this initiative together.

They cover the entire value chain, starting with the growth of AIN crystals using the Physical Vapor Transport (PVT) process, to wafering and polishing of epi-ready AIN-wafers, and the epitaxy of the functional device layers, up to the fabrication of transistors for power electronics and mmWave applications.

For the first time, the consortium has now successfully demonstrated the practical implementation of a value

chain for AIN devices in Germany and Europe.

To this end, AIN crystals were grown at Fraunhofer IISB and sliced into AIN wafers with a diameter up to 1.5 inches.

The company III/V-Reclaim has developed a polishing process for epitaxial wafer production. Functional epitaxial layers were then applied to these wafers at the Ferdinand-Braun-Institut, and AIN/GaN HEMTs were successfully processed on them.

The first transistor generations produced with these wafers already show promising electrical properties, such as a breakdown voltage of up to 2200 V and a power density superior to SiC as well as GaN-based powerswitching devices.

Compared to established silicon devices, AIN/GaN HEMTs, as successfully produced on AIN wafers, offer up to three thousand times less conduction losses than with silicon and are around ten times more efficient than SiC transistors.

These research breakthroughs were supported by funding from the German Federal Ministry of Education and Research (BMBF) within the ForMikro-LeitBAN and Nitrides-4-6G projects.

## Samsung backs next gen GaNFast

NAVITAS GaN power ICs now fastcharge Samsung's Galaxy Series-A, Galaxy Z Fold6 and Galaxy Z Flip6 phones

Navitas Semiconductor has announced that Samsung had expanded adoption of Navitas' GaNFast ICs from the original Galaxy S22, S23 and S24 to the mainstream Galaxy A, and also the new Galaxy Z Fold6 and Galaxy Z Flip6 smartphones with Galaxy Al features.

GaN runs up to 20x faster than legacy silicon and enables chargers up to 3x more power and 3x faster charging in half size and weight. Navitas says that its GaNFast power ICs enable high-frequency, high-efficiency power conversion, achieving up to a 50 percent shrink vs. prior designs.

The new 25W charger (EP-T2510) features new energy-saving technology to reduce standby losses by 75 percent to only 5 mW, which aligns with Navitas' environmental advances, where every GaNFast IC saves 4 kg of CO2 vs. legacy silicon chips. "Since enabling the world's first production GaN charger in 2018, Navitas has pioneered and leads the adoption of GaN to replace legacy silicon chips," noted David Carroll, SVP Worldwide Sales for Navitas. "Our production partnership with Samsung dates back to the Galaxy S22 Ultra, and today's announcement reflects the dramatic expansion of GaN from niche, flagship designs to adoption in highvolume, mainstream phones."

## 7 - 9 APRIL 2025 BRUSSELS BELGIUM

CONNECTING, EDUCATING & INSPIRING THE POWER ELECTRONICS INDUSTRY

## THEMES AND FIRST SPEAKERS ANNOUNCED

With soaring sales of silicon devices and explosive growth in SiC and GaN technologies, the industry is filled with optimism. Attendees will enjoy two days of insightful talks and panel discussions, where we will delve into the factors driving this industry boom and address emerging challenges.

In addition to enlightening conference sessions, Power Electronics International offered ample networking opportunities to connect with industry leaders. In our exhibition hall, providers of process equipment, materials, and metrology tools showcased cutting-edge innovations.

Power Electronics International is part of AngelTech, a renowned event hosting chip-level conferences. With three conferences, 800+ delegates, 80+ exhibitors, 120+ presentations, and extensive networking possibilities, AngelTech is the premier global event for compound semiconductor, photonic integrated circuit, and power electronic technologies.

Benefit from the synergy between these conferences, expanding your customer and supplier networks across comprehensive supply chains.

## **Key Themes for 2025**

## Next-Generation Semiconductor Materials: Beyond SiC and GaN

Explore the latest advancements in semiconductor materials beyond silicon carbide (SiC) and gallium nitride (GaN), including emerging options like gallium oxide (Ga2O3) and diamond semiconductors. Understand their potential applications and performance enhancements, shaping the future of power electronics.

## Sustainable Power Conversion Technologies: Eco-Friendly Solutions

Delve into sustainable power conversion technologies, focusing on eco-friendly solutions for reducing environmental impact. Discuss innovations in energy-efficient designs, materials recycling, and renewable energy integration, addressing the growing demand for environmentally conscious power electronics solutions.?

## **Smart Grid Integration: Enhancing Resilience and Flexibility**

Examine strategies for enhancing the integration of power electronics in smart grids, emphasizing resilience and flexibility. Discuss advanced grid control algorithms, distributed energy resource management, and cybersecurity measures to ensure reliable and secure operation in dynamic grid environments.

## Power Electronics for Electric Mobility: Accelerating Electrification

Explore the role of power electronics in accelerating the electrification of transportation, including electric vehicles (EVs), hybrid electric vehicles (HEVs), and charging infrastructure. Highlight advancements in powertrain technologies, battery management systems, and fast-charging solutions to meet the evolving needs of the automotive industry.

## **Artificial Intelligence in Power Electronics: Optimizing Performance**

Investigate the integration of artificial intelligence (AI) and machine learning techniques in power electronics systems for optimizing performance and efficiency. Explore Al-driven control algorithms, predictive maintenance strategies, and adaptive power conversion architectures, enabling intelligent and autonomous operation in diverse applications.

## **Energy Harvesting and Wireless Power Transfer: Enabling Autonomous Systems**

Examine the latest developments in energy harvesting and wireless power transfer technologies, enabling autonomous and self-powered systems. Discuss advancements in harvesting energy from ambient sources, wireless charging techniques, and their applications in IoT devices, wearable electronics, and remote sensing platforms.

To find out more about our sponsor and speaker opportunities, contact us today on:

+44 (0) 2476 718970 info@peinternational.net peinternational.net

## Sponsorship / Exhibition / Speaker OPPORTUNITIES AVAILABLE!

Sponsorship, exhibition, and speaker opportunities at PE International, enable and empower you to educate and penetrate the global power electronics industry using multiple marketing tools.

Demand is high, with sponsorship, exhibition and speaking slots already being secured for 2025, so to avoid disappointment, please get in touch today.

## **Delegate Earlybird Discount:**

Register before 31 December and get 10% OFF!

Registration to AngelTech allows you to access both days of **PE International** and the co-located **CS International** and **PIC International**.

## **PLATINUM SPONSORS**

## **GOLD SPONSOR**

### **MEDIA PARTNERS**

## **2025 SPEAKERS INCLUDE**

**ORGANISERS**

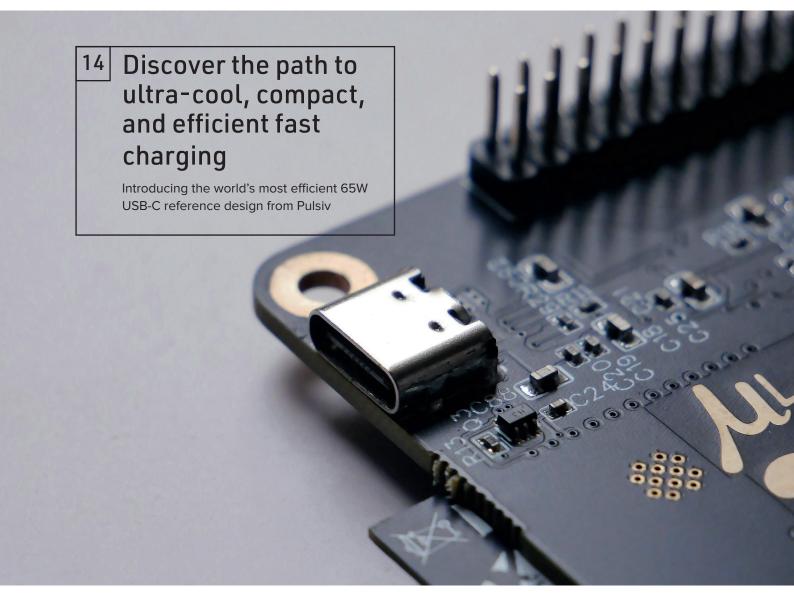

## Discover the path to ultra-cool, compact, and efficient fast charging

Introducing the world's most efficient 65W USB-C reference design from Pulsiv.

## **BY PULSIV**

THE DEMAND for USB-C is forecast to surge over the next decade, fuelled by the migration from USB-A to USB-C and a growing market of portable devices that require fast charging. As power requirements increase, the need to deliver more power in a confined space adds challenges with thermal management and heat dissipation which impact safety and reliability.

The PSV-RDAD-65USB reference design has been developed to demonstrate how Pulsiv OSMIUM technology reduces component temperatures, enabling products to consume less power and reduce overall size. It represents the first in a series of designs aimed at pushing the boundaries of power conversion to create a sustainable platform for the USB-C standard.

In this design, the Pulsiv OSMIUM microcontroller PSV-AD-65EG-Q24IV has been combined with OnSemi's NCP1342 Flyback controller and GaN devices from Innoscience to deliver a world leading specification:

- Input Voltage Range 90 265VAC (no input voltage derating)

- Output Voltage: 5 20VDC supporting PD3.0, QC4.0, BC1.2, & PPS (Fast Charging)

- Output Power: 65W max

- Transformer Temperature: 30.3°C above ambient

- Operating Frequency: 125kHz

- Peak Efficiency: 96%

- Average Efficiency: 95%

- O Half-Active Bridge: Included

- Line Currents: 0.5A max

- Inrush Current: Eliminated

- GaN Optimised: Yes

- DC-DC Converter: Quasi-Resonant (QR) Flyback

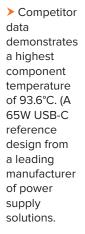

## Taking ultra-cool operation & fast charging to a whole new level

Critical components in conventional designs will often reach temperatures of over 100°C, so measures must naturally be taken to dissipate heat or limit output power. This means compromising cost, performance, or physical size to mitigate impact safety and reliability issues.

The Pulsiv OSMIUM reference design demonstrates a significant improvement in thermal performance and reduces critical component temperatures by more than 30% compared to other designs. At full load, the Flyback transformer reaches an impressive 33.9°C at 230VAC and 30.3°C at 265V above an ambient temperature of 26.1°C. This incredible achievement is likely to set a new benchmark and

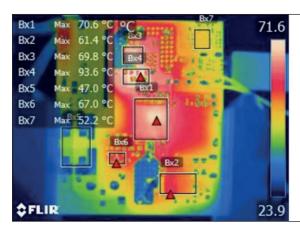

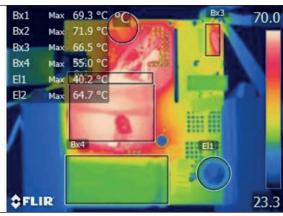

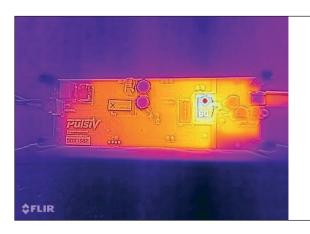

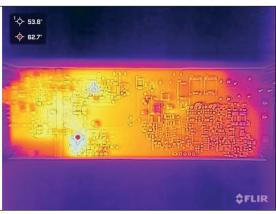

Thermal measurement of the Pulsiv PSV-EBAD-65USB evaluation board demonstrates the hottest component temperature :of 62.7°C.

enables 65W fast charging in space constrained environments and/or heat sensitive applications such as in-wall plug sockets that incorporate USBC connectivity.

Setting a new benchmark in power conversion Pulsiv OSMIUM technology is a patented AC to DC front-end conversion method that applies intelligence to an active valley fill approach and delivers a combination of game changing benefits in power electronics designs. It significantly improves performance at low loads to increase overall average efficiency, reduce energy consumption, and deliver a totally flat efficiency profile across all load conditions.

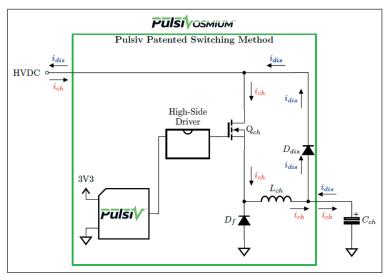

The Pulsiv AC to DC conversion method intelligently regulates the charging current and voltage on the storage capacitor using a high-side architecture to switch Qch. This allows the use of 200V or 160V capacitors (selectable) to support a universal mains input. The valley-fill period is broadly similar to a 2C3D architecture; but the charging period of the capacitor is significantly longer and more variable.

### Reducing system losses

Figure 1 shows a simplified circuit implementation to illustrate the basic operation of Pulsiv OSMIUM technology in this design. A MOSFET, Qch, is used to control the charging of Cch to generate a configurable highvoltage DC output (HVDC) and a blocking diode Db ensures that Cch does not discharge through the body diode of Qch while avoiding stray conduction through the inductor. This approach allows the use of smaller and lower cost 200V or 160V capacitors to support a universal mains input.

Losses during the charging phase are typically between 0.5% and 2%, resulting in a peak efficiency of up to 99.5%. The circuit converts just enough energy to maintain capacitor voltage and delivers consistent efficiency over the full power range. In a traditional valley-fill design, AC to DC conversion involves a full-wave diode bridge.

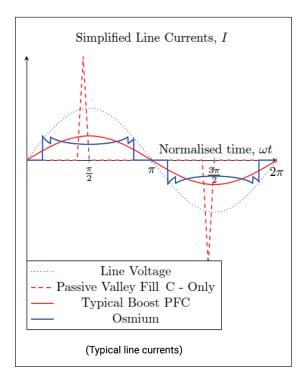

Diode losses are mainly determined by the average current, RMS current, the forward voltage drop, and

the resistance during conduction. Conventional systems without power factor correction exhibit large peak currents, resulting in higher RMS currents and greater diode bridge losses. Power factor correction improves RMS current and results in a current waveform with a crest factor of  $\sqrt{2}$ .

Pulsiv OSMIUM designs typically have a crest factor of 1.3, which is lower than that of a sinusoid, leading to lower RMS values and reduced losses. Peak line currents are reduced by up to 90% as a direct result of the way Pulsiv OSMIUM controls capacitor charging, and inrush current is also eliminated.

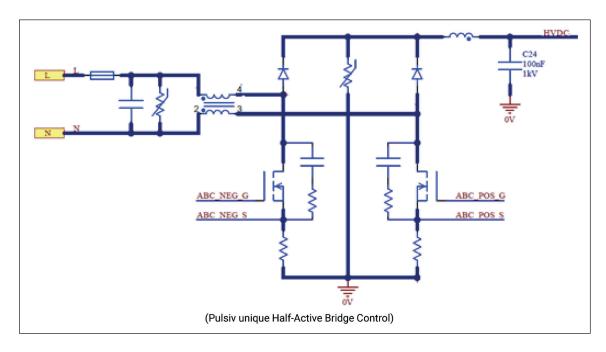

## Optimize efficiency and space with a half-active bridge

Pulsiv OSMIUM technology senses AC line voltage and frequency to adjust capacitor charging time, therefore the circuit draws no line current at the AC zero voltage crossing. This enables a simple halfactive bridge implementation to increase efficiency, especially at low line conditions.

MOSFETs in the lower half of the AC to DC bridge are carefully controlled, in combination with highside diodes. The half-active bridge in this design strikes the delicate balance between efficiency, cost, and complexity and supports universal input with

> Figure 1: Pulsiv OSMIUM high side architecture.

Typical line currents.

efficiency gains of 0.7% at full load from a 115V AC supply.

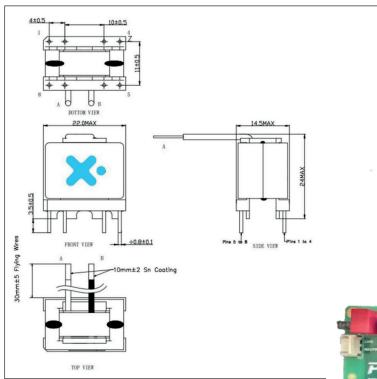

## Innovation in magnetics design reduces transformer size by 20%

Pulsiv OSMIUM technology generates a HVDC output that varies between the peak AC input and 150V (with a 230V input) to drive the QR Flyback at maximum efficiency. The wide voltage range it generates requires a significantly reduced primary side inductance which enables the use of an EQ20 transformer. This was developed in partnership with magnetics experts Frenetic where a 20% size reduction was achieved compared to the typical RM8 used in other designs.

## Minimizing losses with GaN optimization

GaN transistors from Innoscience were used to lower the RDSon which reduced conduction losses, but this naturally increased parasitic capacitance. The INN700DA240B was the optimum device which provided the necessary balance between the two losses. An additional Innoscience GaN transistor INN150FQ032A was also selected to provide the most suitable match for operating with the synchronous rectifier controller and output current from the transformer.

In this design, GaN lowered the overall energy consumption, reduced component size, and improved cost compared to conventional MOSFET's. Innoscience also provided outstanding support, delivering samples within 48hrs, and demonstrating the most competitive pricing.

## Design package & evaluation boards

The PSV-RDAD-65USB document package is available to download free from the Pulsiv website and includes a Datasheet, Schematics, Bill of Materials, & Altium files. The PSV-EBAD-65USB evaluation board enables rapid lab testing and can be pre-ordered now for delivery in the 2nd half of August through a network of franchised distribution partners including global stockist Digikey.

## **Summary**

The PSV-RDAD-65USB reference design showcases a truly sustainable approach to efficient power conversion, ultra-cool thermal performance, and reduced energy consumption in USB-C applications. It demonstrates how the unique Pulsiv OSMIUM technology can influence magnetics design while supporting GaN to minimize overall losses. Its gamechanging thermal measurements enable USB-C to be adopted quickly and safely while paving the way for fast charging within virtually any application.

➤ Pulsiv unique Half-Active Bridge Control.

PS V-E BAD65USB Evaluation Board.

> Far Left Duo: Innoscience INN700DA240B and right: Innoscience INN150FQ032A.

| Value            | Wind | Start             | End  | Short | Conditions             | Test | Nom    | Tol(%) | Min   | Max    | Unit |

|------------------|------|-------------------|------|-------|------------------------|------|--------|--------|-------|--------|------|

| Inductance       | W1&3 | 1                 | 3    |       | 25ºC, 0.1Vrms @ 100kHz | 1    | 97.00  | 15.00  | 82.45 | 111.55 | uН   |

| Inductance       | W2   | Α                 | В    |       | 25ºC, 0.1Vrms @ 100kHz | 2    | 6.06   | 15.00  | 5.15  | 6.97   | uH   |

| Lk<br>Inductance | W1&3 | 1                 | 3    | A,B   | 25ºC, 0.1Vrms @ 100kHz | 3    |        | 15.00  |       | 3.00   | uH   |

| Inductance       | W4   | 7                 | 6    |       | 25ºC, 0.1Vrms @ 100kHz | 4    | 26.62  | 25     | 19.97 | 33.28  | uH   |

| Inductance       | W5   | 6                 | 5    |       | 25ºC, 0.1Vrms @ 100kHz | 5    | 2.50   | 25     | 1.88  | 3.13   | uH   |

| Inductance       | W4&5 | 7                 | 5    |       | 25ºC                   | 6    | 44.98  | 15.00  | 38.23 | 51.73  | uH   |

| DC<br>Resistance | W1&3 | 1                 | 3    |       | 25ºC                   | 7    | 187.50 | 15.00  |       | 215.63 | mOhm |

| DC<br>Resistance | W2   | Α                 | В    |       | 25ºC                   | 8    | 12.00  | 15.00  |       | 13.80  | mOhm |

| DC<br>Resistance | W4&5 | 7                 | 5    |       | 25ºC                   | 9    | 360    | 15.00  |       | 414.00 | mOhm |

| Hi-Pot           |      | W1,<br>3,4,<br>&5 | W2   |       | 3000VAC, 60s           | 10   |        |        |       | 5.00   | mA   |

| Hi-Pot           |      | W2                | Core |       | 3000VAC, 60s           | 11   |        |        |       | 5.00   | mA   |

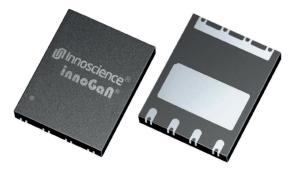

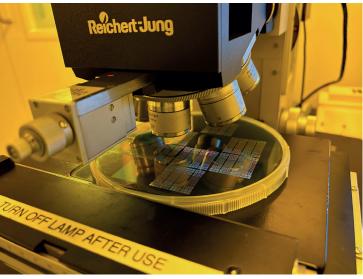

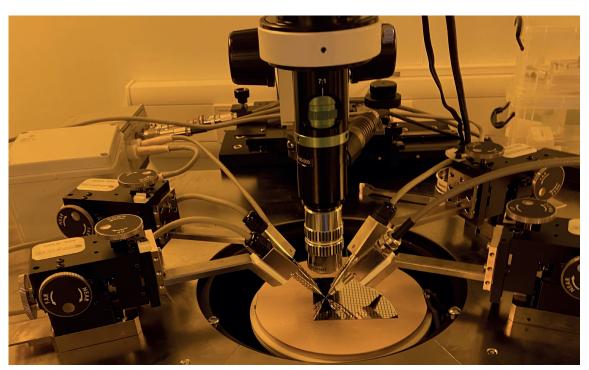

## Splitting hairs to ten to the power of four

14ACMOS: EU project for the next technology node in semiconductor manufacturing

BY MATHIAS WINTER, HEAD OF PIEZO DRIVES & SYSTEMS TECHNOLOGY, GLOBAL RESEARCH AND MARKUS WIEDERSPAHN, CORPORATE COMMUNICATIONS, PHYSIK INSTRUMENTE L.P. (PI)

THE 14ACMOS project is part of Horizon Europe, the EU's key funding program for research and innovation for the period of 2021 to 2027 with a volume of more than  $\in$  95 billion. It tackles climate change, helps to achieve the UN's Sustainable Development Goals, and boosts the EU's competitiveness and growth.

Horizon is divided into six clusters, of which cluster 4 addresses "Digital, Industry & Space", funded with more than € 15 billion. With a total of currently 127 projects cluster 4 aims to strengthen the competitiveness of European companies in semiconductor and photonics industries.

The 14ACMOS project (14ACMOS = 14 Angstroem Complementary Metal-Oxide-Semiconductor) within Horizon aims to develop solutions for the 1.4 nm process technology node. Project activities address four key pillars: lithography, metrology, mask-infrastructure, and process technology.

Lithography solutions will be pushed to meet 1.4 nm capability, and extreme UV plasma physics will be studied to optimize optics transmission and lifetime. In the metrology pillar, advanced methods will be

developed to improve measurement sensitivity and uncertainty and to assess reticle degradation induced by extreme UV light. Mask-infrastructure will cover the development of mask repair strategies based on particle removal technology and will assess durability. Process technology involves the development of patterning solutions, active device selection, and new interconnect technology, which are suitable for the 1.4 nm technology node.

The 14ACMOS project started in December 2022 and is set to end in November 2025. Total cost of the project sums up to € 94.6 million with an EU contribution of € 21.8 million. The project is coordinated by ASML. Participants are among others Carl Zeiss SMT, Trumpf, Applied Materials, KLA, Physikalisch-Technische Bundesanstalt (PTB). European players like ASML, Carl Zeiss SMT, and PI have contributed to every step of miniaturization in semiconductor manufacturing along the way from several microns down to the 1.4 nm node. To reach precision of 1.4 nm, new actuator and motor concepts, sensors and (control) algorithms for the drives must be developed, besides advancements in process technology, improved optics, and materials.

This project is co-funded by the European Union under grant agreement No 101096772 and is supported by the Chips Joint Undertaking and its members.

"Funded by the European Union. Views and opinions expressed are however those of the authors only and do not necessarily reflect those of the Chips Joint Undertaking. Neither the European Union nor the granting authority can be held responsible for them."

PI offers 50 years of experience in piezo technology and nano positioning, a broad technological spectrum, and a high level of vertical integration in order to develop and provide components and systems that are optimally tailored to the respective process: From the very beginning, the basis for this consisted of mechanical motion systems (actuators and motors) and the appropriate bearing technology, sensors for recording the distance traveled and for determining the absolute position, algorithms for the firmware and an extensive collection of software interfaces and control technology. As a decade-long system partner of semiconductor equipment manufacturers and in particular the main participants in the 14ACMOS project, PI contributes its expertise and experience to the development of innovative motion solutions. The focus here is on very demanding motion and positioning tasks that require precision in the nanometer and sub-nanometer range. A particularly important aspect of some of the applications is the need to operate the systems under vacuum conditions. Pl also offers suitable technologies and options for this.

## A wide range of drive technologies

The field of semiconductor manufacturing, and the 14ACMOS project in particular, presents a unique challenge for motion systems: the combination of long travel distances (up to hundreds of millimeters) with high dynamics, speed, and precision down to the nanometer range. PI meets these challenges head-on with a comprehensive portfolio of drive technologies.

## **Electromagnetic drives**

In the class of electric motors, PI offers rotating electric motors such as DC or stepper motors. These are used in connection with screw or worm

drives. Stepper motor systems with high-resolution encoders can perform minimum incremental motions of 10 nm with high reliability and repeatability.

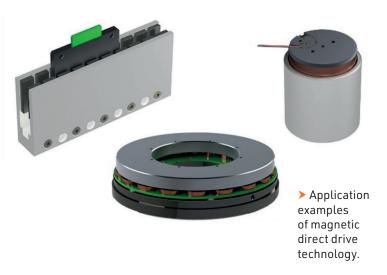

Also, in the field of magnetic direct drives, a wide range of technologies is at hand, namely voice coil motors, iron-core and ironless linear motors, and torque motors.

### Piezo-based actuators and drives

The motion of piezo actuators is based on solid-state effects, giving them unlimited resolution in principle. Their stiffness is very high, enabling high force generation and dynamics. Their rapid response time in the microsecond range is a result of their high resonant frequency which can reach more than one hundred kilohertz. Actuator travel in the range of several ten micrometers can be mechanically amplified to reach more than 1 mm. The combination of extremely high resolution and small travel ranges requires the use of suitable guiding elements which are typically flexures that enable highest accuracy by avoiding friction, play and backlash.

## TECHNOLOGY | 14ACMOS PROJECT

➤ The PIOne optical nanometrology encoder from PI offers resolution down to 20 picometer RMS and better.

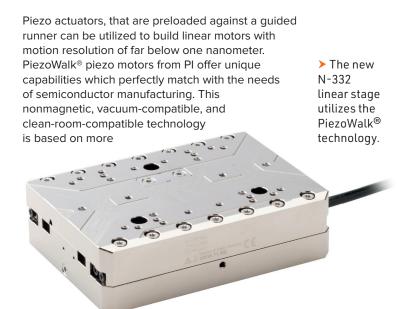

than 30 years of experience with the development and production of piezoceramic components. PI received the SEMI Technology Innovation Showcase Award for the PiezoWalk® technology in 2005. The drives are continuously developed further, and a large number of variants are now available for different areas of application.

Resolution of these drives goes down to 30 picometer, travel ranges are scalable due to scalable runner length. Feed forces are in the range of 50 N to several 100 N. These drives are self-locking when switched off thus saving energy and reducing the generation of heat.

The latest addition to this product family, the N-332 linear stage, is configurable for use in multi-axis setups involving the X, Y, Z axes, and the XY, XZ, and XYZ planes. For applications that require operation in vacuum, the N-332 stages are available in configurations suitable for pressures as low as 10-9 hPa. The PICMAWalk piezo motor inside the N-332 stage is based on PI's proprietary PICMA® piezo actuators.

A highly specialized application of piezo-based components are so-called PIRest actuators. With a load capacity of up to 4000 N per actuator and micrometer displacement with nanometer resolution, these components are ideally suited for drift compensation in machines, for alignment of optical components and static precision positioning.

Sometimes it is even necessary to combine motion systems that enable long-stroke movements, such as linear drives or piezo motors, with piezo-based

➤ Magnetic levitation is a promising technology for high-precision motion in six degrees of freedom.

actuators. Actuator and drive technologies are only one aspect considering the overall system properties. Optimal performance as required in applications targeted in the 14ACMOS project can only be achieved by implementing new and sophisticated control algorithms and the next generation of high-resolution sensor technology.

## The right position sensor technology

Position sensing systems are required to provide feedback to the motion controller. Linearity and repeatability of motion and positioning tasks are not possible without highest-resolution measuring devices. Accuracies in the range of a few nanometers and below require a position measurement method that can also detect motion in this range. PI can also draw on extensive experience and a comprehensive portfolio of technologies developed in-house in this discipline. Examples comprise capacitive sensors and optical nanometrology encoders. The latter achieve a resolution of 20 picometer and better due to their small signal period of 500 nm and the optimized signal processing.

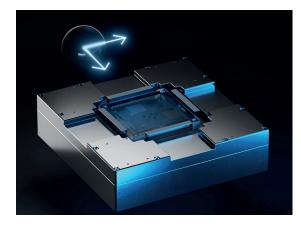

## New magnetic levitation stages

The PI Group is committed to meeting the demanding objectives of the 14ACMOS project through the enhancement of existing technologies and the creation of novel and transformative new solutions. PI is also engaged in the development of new technologies beyond the scope of the 14ACMOS project. One illustrative example is that of magnetic levitation (maglev) stages with six degrees of freedom. One major benefit of this technology is the avoidance of any friction in the process chamber, eliminating the risk of particle contamination.

To employ this principle for the execution of highprecision movements, the magnets in the base are designed as electrically controllable coils. In order to enable movements in all six degrees of freedom, a corresponding number of magnet pairs is required. In a multitude of practical applications, Halbach arrays are employed to reduce energy consumption, augment load capacity, and diminish heat dissipation.

The combination of magnetic guidance and dedicated high-precision drive and sensor technologies provides high dynamics and the highest resolutions down to the picometer range. Active control and definition of guiding characteristics in up to six degrees of freedom can enable additional correction tasks such as focusing in Z or adjusting tip/tilt during operation. The frictionless guiding principle, which is free of rolling elements, lubrication, and air flow, will ensure the highest precision over the entire service life and allows use in cleanroom environments.

### Controller technology

As demands on the precision, dynamics, and speed of mechanical motion systems increase, so too does the complexity of the control systems. The selection

of an appropriate control technology is therefore of paramount importance. In particular, the control of piezo actuators and piezo-based positioning systems requires a high degree of specialization. Pl has gained extensive experience in this field over decades. The characteristic properties of piezo actuators include the generation of large forces and fast response. In electrical terms a piezo element corresponds to a capacitance. A rapid change to the operating voltage brings about a rapid displacement of the actuator and thus a change in position.

When the control voltage suddenly increases, the piezo actuator can achieve its nominal displacement in only a few microseconds. A prerequisite for this is that the power supply provides sufficient current to charge the capacitance. For steady state operation, i.e., when holding a certain position, the stability of the power supply is crucial, as the piezoelectric actuators already respond with motion to the slightest voltage changes. Noise or drifting must therefore be avoided as far as possible.

With all these special features, PI benefits from more than 30 years of experience in the manufacture of piezo elements and the development of piezo-based positioning systems. PI is one of the few companies in the world with access to the entire value chain: from piezo development and production to the development of piezo-based motion systems and control technology.

PI can also look back on an even longer history of innovation in electric motor control technology. In addition to own cutting-edge solutions, PI leverages the expertise of ACS Motion Control, a wholly owned member of the PI Group based in Israel. Magnetic levitation stages exemplify the necessity for sophisticated control technology. In this context, the linear stage platform is not constrained by mechanical bearings, allowing for unimpeded movement within a single degree of freedom. Consequently, a robust multi-axis controller with a high bandwidth is essential to maintain control over all other degrees of freedom.

### Conclusion

The 14ACMOS project presents completely new challenges and tasks for all involved. Precise positioning plays a key role in many processes. For example, in the manufacture, inspection (quality control) and repair of lithography masks. In wafer inspection, it supports the detection of structural failures, defects and particles. Precise positioning is also essential in the lithography process, and in wafer metrology, for example for measuring layer thicknesses and overlay offsets.

With a comprehensive portfolio of precision positioning technologies and complementary expertise in sensor, control, motion and force transfer technologies, PI is well positioned to support this technology node.

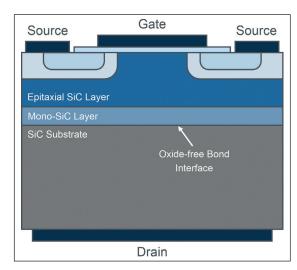

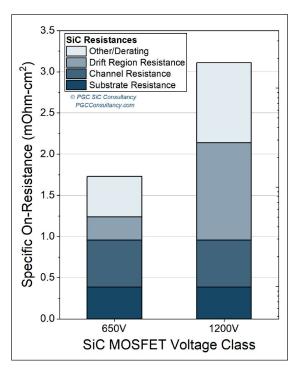

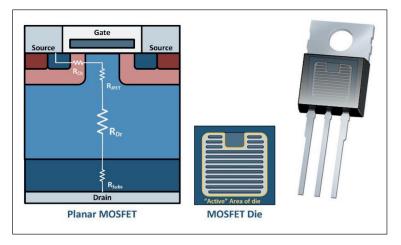

## Cost-effective SiC substrate manufacturing for power devices enabled by oxide-free wafer bonding

Silicon Carbide (SiC) power devices are seen as a game-changer in the automotive industry.

## BY BERND DIELACHER AND PETER KEREPESI, EV GROUP

THESE ADVANCED semiconductor devices offer superior device performance compared to conventional silicon-based devices. SiC as a material has a 3x wider bandgap, 10x higher breakdown voltage and a 5x higher thermal conductivity.

These properties ultimately translate into faster EV charging and more efficient and reliable automotive fleets. Large investments in new SiC wafer fabs underline the high interest from the automotive sector. However, SiC manufacturing processes are far from being as mature as silicon processes. Significant developments along the entire process chain are needed to pave the way for a SiC-based future of the EV industry.

Challenges include the high costs associated with substrate manufacturing, the complex processing of SiC, limited economies of scale and overall yield issues. In particular, the substrate is a major concern as it accounts for the largest share of production costs. Many routes are currently being explored to address this issue including improvements of crystal growth or novel wafer slicing technologies. The transition to 8-inch manufacturing is also expected to reduce substrate costs. This will only pay off in the long term as the processes for this scale are more complex and still need to be established and optimized. Another way of reducing substrate costs is the use of wafer bonding to utilize the expensive high quality SiC material more efficiently.

Wafer bonding is an established process in power device manufacturing, in particular temporary bonding is commonly used to support substrates during device thinning. Wafer bonding is not only used for device manufacturing, but also enables new types of substrates. In the case of SiC MOSFET power devices, the main structure is built into a thin epitaxial SiC layer, commonly grown on monocrystalline SiC wafers. SiC crystal growth

defects can be minimized or eliminated during the epitaxial process and epi-layers can be efficiently electrically tuned by doping.

However, only high-quality monocrystalline SiC substrates provide the required electrical device performance but contribute significantly to the overall chip cost. Since this material is mainly required as a seed layer for the epitaxial process, using only a thin layer and substituting the bulk material with a polycrystalline or lower quality monocrystalline substrate is seen as a viable route to address this cost issue (Figure 1).

Such a process generally involves wafer bonding of the two materials as well as a method to produce a thin layer from the high-quality monocrystalline substrate and reuse the remaining substrate multiple

> Figure 1. SiC power MOSFET structure using a cost-effective engineered substrate (thin high quality monocrystalline SiC layer bonded on a less-expensive SiC substrate).

ComBond®

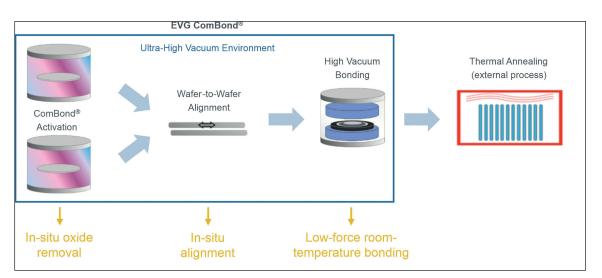

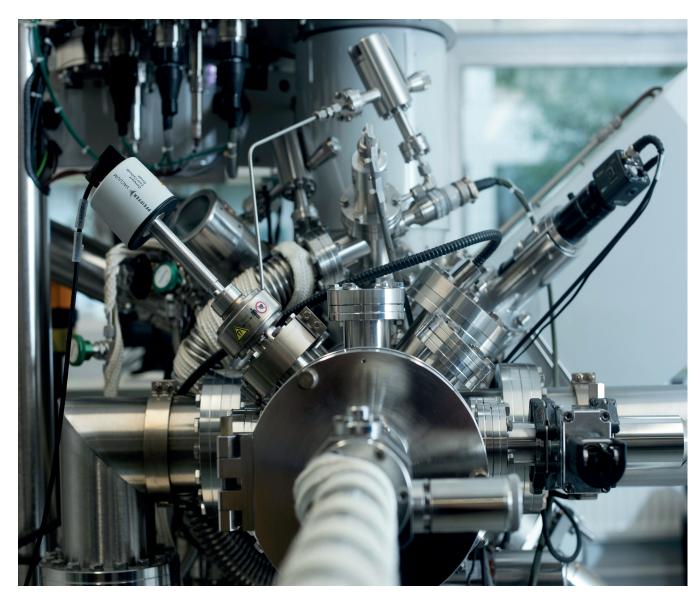

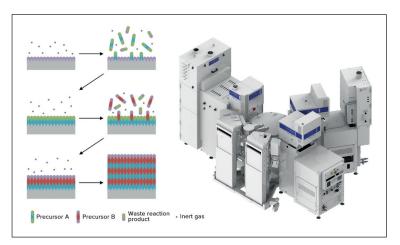

times. Several methods for the thin layer generation have been demonstrated, including the well-known ion-implantation and splitting process. This article focuses on the wafer bonding process and presents the latest developments for this application using EVGs high-vacuum ComBond® cluster system.

The ComBond® system (Figure 2) offers covalent fusion bonding at room temperature, enabling heterogenous integration of various materials with different lattice constants and thermal expansion coefficients. Processing at room temperature does not induce additional stress in the materials, thus initial wafer bow is not increased. While classical fusion bonding is based on oxide-oxide bonding, the ComBond® process relies on a surface activation process called ComBond Activation Process, which is based on oxide removal by ion beam sputtering. Any re-oxidation is prevented by wafer handling and bonding the wafers in an ultrahigh vacuum environment. The result is a seamless transition between the two bulk materials without any intermediate layer. Table 1 summarizes the key differences between the two technologies. Oxide-free wafer bonding enables electrically conductive interfaces, which is the most important requirement for engineered substrates with respect to the

## Oxide-free SiC-SiC wafer bonding optimisation and characterization

structure of vertical SiC power MOSFETs.

SiC bonding has been investigated using monocrystalline 4H SiC wafers, including incoming metrology, characterization of the activation process and analysis of the final bonded wafer pairs. The bonding process (Figure 3) starts with oxide removal from both wafer surfaces using an ion beam sputtering process (ComBond® Activation), followed by wafer-to-wafer alignment and transfer to the bonding chamber without breaking the ultrahigh vacuum (< 5·10-8 mbar). Finally, the wafers are bonded at room temperature with low force.

External annealing allows further optimization of the bond interface.

A general prerequisite for fusion bonding is a very low surface roughness of the incoming wafers (< 0.5 nm). The initial values of the SiC wafer were well below this requirement and it was confirmed that ion beam sputtering does not lead to a significant increase in surface roughness during the activation process, thus a good bond quality can be expected with respect to this parameter. Nevertheless, the activation process leads to numerous surface effects (see Table 1), which need to be well understood and controlled. Figure 4 illustrates different stages of surface activation and their optimization in terms of bonding energy.

Figure 2.

EVG

ComBond®

- Automated

High-Vacuum

Wafer Bonding

System

➤ Figure 3. Oxide-free wafer bonding process of SiC using EVG ComBond® technology.

| Parameter           | Plasma Activated Fusion Bonding | ComBond® Technology                |

|---------------------|---------------------------------|------------------------------------|

| Pre-treatment       | RF plasma                       | lon beam sputtering                |

| Surface effects     | * Surface energy modification   | * Oxide removal                    |

|                     | * Surface microroughness        | * Dangling bonds generation        |

|                     | reduction                       | * Chemical functionalization       |

|                     | * Oxide layer growth            | * Stoichiometry modification       |

|                     | * Chemical Functionalization    | * Amorphous layer generation       |

|                     | * Contaminant removal           | (few nm range)                     |

| Environment         | Ambient air                     | Ultrahigh vacuum                   |

| Post-bond annealing | Commonly yes (<400 °C)          | Commonly no                        |

| Bond type           | Covalent                        | Covalent                           |

| Bond interface      | Oxide-Oxide                     | Oxide-free (same as bulk material) |

| EVG equipment       | GEMINI® FB                      | ComBond®                           |

➤ Table 1. Comparison between plasma activated fusion bonding and ComBond® technology.

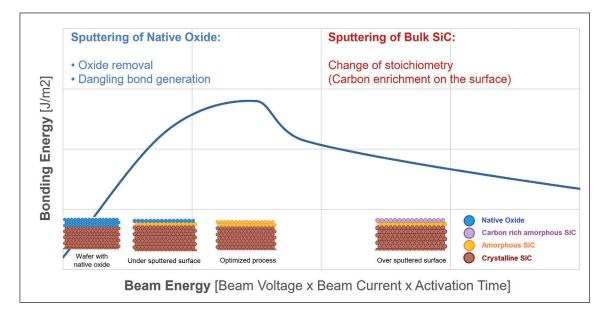

In the initial phase, ion beam treatment leads to a sputtering of the native oxide, which is gradually removed. At the same time, dangling bonds are formed. During this process, an increase in bonding energy is observed, reaching a maximum after complete oxide removal. The ion beam treatment also generates a thin amorphous SiC layer in the range of a few nm. Due to a preferential sputtering of carbon compared to silicon, this amorphous SiC layer becomes enriched with carbon over time, changing the stoichiometry of the material.

SiC bonding energies of 1.4 J/m² were observed with optimized activation parameters. This value is still below the theoretical maximum but much higher than minimum bonding energies required for further processing (0.5 J/m²). The bonding energies were measured using the Mazara test at 4 locations on the wafer.

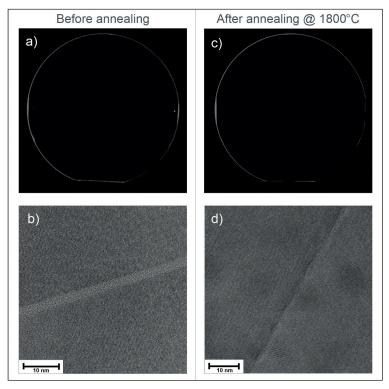

The bond interface across the wafer was investigated by Confocal Scanning Acoustic Microscopy (C-SAM). No scratches, delamination or particle related voids were detected, confirming a high quality bonding process (Figure 5a). Cross-sectional analysis of the interface by Transmission Electron Microscopy (TEM) shows a thin amorphous SiC layer (2.1 nm) produced by the sputtering process (Figure 5b). Amorphous layers are generally not of any concern, but they can affect the electrical or thermal conductivity across the interface.

Finally, the bonded SiC wafers were annealed in an external furnace at 1800 °C (kindly supported by centrotherm international AG). While the C-SAM images showed a similar high quality bond interface without any outgassing effects (Figure 5c), the TEM measurements revealed an interesting result. The amorphous layer disappeared completely and a

> Figure 4. Bonding energy optimization with respect to surface activation.

**WURTH ELEKTRONIK** MORE THAN YOU EXPECT

## ULTRA LOW LOSSES

## WE-MXGI

With the WE-MXGI Würth Elektronik offers the newest molded power inductor series. It combines an innovative iron alloy material that provides high permability for lowest R<sub>DC</sub> values combined with an optimized wire geometry.

Ready to Design-In? Take advantage of personal technical support and free samples ex-stock.

www.we-online.com/WE-MXGI

## **Highlights**

- Extremely high power density

- Ultra low R<sub>DC</sub> values and AC losses

- Magnetically shielded

- Optimized for high switching frequencies beyond 1 MHz

## TECHNOLOGY | SUBSTRATES

Figure 5.Bonding quality and interface characterization with C-SAM (a, c) and TEM (b, d) before and after thermal annealing.

Higher temperatures and full recrystallization is not necessarily needed to achieve best electrical performance.

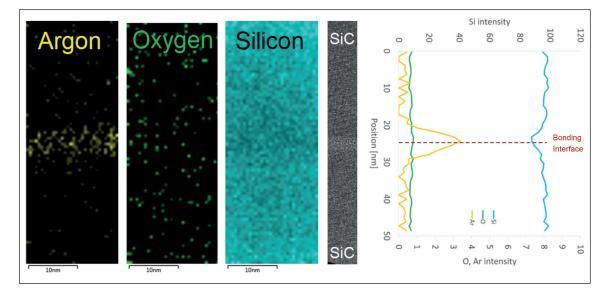

Finally, Energy Dispersive X-ray (EDX) analysis was used to confirm an oxide-free interface (Figure 6). This measurement also shows reduced Si content at the bond interface due to the preferential sputtering of silicon over carbon.

Since characterization of carbon is challenging in the case of EDX, the enrichment of the carbon at the interface was proved by XPS measurements.

High quality SiC wafer bonding has been demonstrated using EVG ComBond® technology. The developed oxide-free bonding process can be used for the volume production of engineered SiC substrates for advanced, cost-efficient vertical power device architecture.

The extensive characterization in this work has been carried out on 4-inch monocrystalline SiC substrates. Successful bonding with similar results and quality has also been demonstrated on the ComBond® system with 6- and 8-inch wafers by now, both mono-to-mono- and mono-to-polycrystalline SiC bonding.

full recrystallization of the interface was observed (Figure 5d). During the annealing, the electrical characteristic is improving. In addition, the bonding energy increased significantly and reached the fracture energy of bulk SiC. Engineered SiC substrates produced by this oxide-free bonding technique are therefore ideally suited for SiC power MOSFETs.

Recrystallization begins at temperatures as high as 1400 °C. As substrates for this application are processed at high temperatures during epitaxy, no additional annealing is usually required.

## **REFERENCE**

P. Kerepesi et al, Oxide-Free SiC-SiC Direct Wafer Bonding and Its Characterization, 2023 ECS Trans. 112 159

> Figure 6. EDX analysis of the bond interface confirms oxidefree wafer bonding.

## Selective Laser Annealing for Ohmic Contact Formation

## microPRO™ XS OCF

- » Best-in-class throughput (up to 17 WPH)

- » Wide and stable process window

- » Reduced particle generation due to process routine and chamber layout

- » Thin-wafer handling available

Visit us at ICSCRM 2024 Booth 80

Contact us:

Tel: +49 371 40043-222

sales@3d-micromac.com

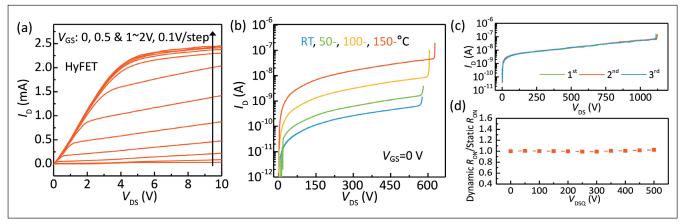

## High-voltage SiC for storage & MV-grid conversion

As reliance on renewable energy generation continues to increase, a three-level converter architecture built using high-voltage SiC MOSFETs enhanced with an integrated MPS diode boosts efficiency and reliability in the storage-to-grid connection.

## BY RANBIR SINGH, EVP GENESIC, NAVITAS SEMICONDUCTOR AND LLEW VAUGHAN-EDMUNDS, SENIOR DIRECTOR PRODUCT MANAGEMENT AND CORPORATE MARKETING, NAVITAS SEMICONDUCTOR

BALANCING THE FLOW of energy into and out of the grid is a perennial challenge for operators, now made tougher as an increasing proportion of energy must come from renewable sources. Historically, pumped hydro-electric has dominated, representing more than 82% of grid-connected storage capacity. It is well suited to providing a long-lasting boost at times when high demand is expected, such as in the early evening.

Wind and solar, which are intermittent and unpredictable, demand storage with different

characteristics including faster response time, low/medium energy capacity, easy scalability, and compact size. Battery energy-storage systems (BESS), typically built with Li-ion batteries, can meet these demands. BESS currently represents almost 17% of storage in the US, with about 16 GW of installed capacity in 2023.

Another 15 GW is planned for 2024. In addition to helping balance energy flow, BESS can also help improve the performance of the transmission and distribution network by compensating

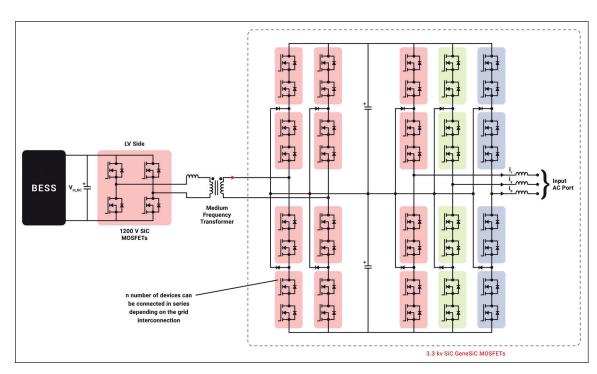

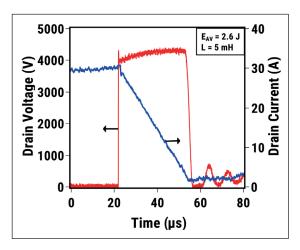

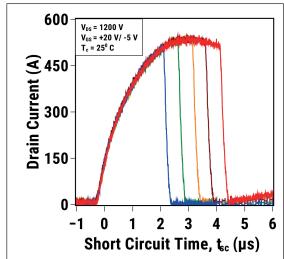

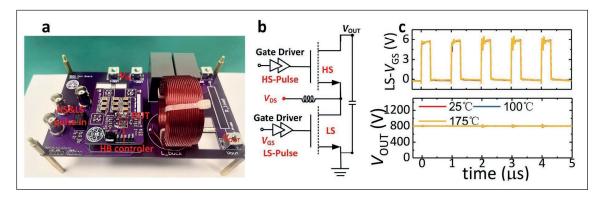

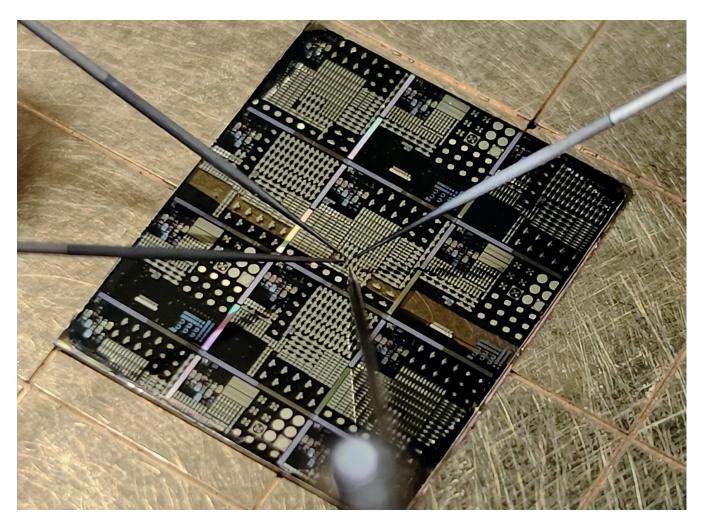

Figure 1. Isolated BESS feed-in to MV grid with DAB and AFEC.

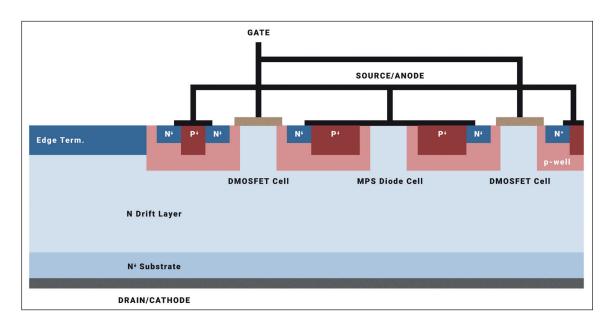

Figure 2. 3.3kV SiC MOSFET and monolithically integrated MPS diode.

for disturbances such as voltage fluctuations, frequency variations, phase shifts, harmonics, and interruptions.

## **BESS** to grid connection