### Key criteria for power MOSFETs in harsh linear mode applications

### INSIDE

News Review, Features News Analysis, Profiles **Research Review** and much more...

### **BATTERIES TO CHANGE POWER** INDUSTRY

Bbenefits of new Vanguard Si 1.5kWh battery and what it brings to the growing power rental market

### **A GAN DEVICE FOR ALL** MARKETS

Half-bridge power IC will deliver the high powers and efficiencies that we all need

### THE CHAMPION **FOR POWER ELECTRONICS?**

What's to stop cubic SiC from playing a major role in tomorrow's power electronics industry?

### Best performance for next generation SiC power electronics to address global mega trends

## AIX G5 WW C

- Electric vehicles: on board chargers, power inverters

- Infrastructure: charging stations

- Renewables: solar and wind

- Industrial: motor drives, power supplies

- Power distribution: HVDC

Discover our SiC epi production batch tool with single wafer performance

Made in Germany

### VIEWPOINT By Mark and rews Technical Editor

## Tech evolution, new discoveries drive the future of Power Electronics

A FASCINATING aspect of semiconductor manufacture is its rapid, sometimes breakneck pace of innovation. Power electronics enjoys an ample share of new and evolving technologies that are rapidly becoming the future of high performance, high power systems.

The bulk of this Power Electronics World edition focuses on the new, the evolving and the unexpected. We'll save the 'unexpected' for last... In an article from STMicroelectronics, we look at high power MOSFET devices that are often considered system workhorses due to their wide versatility and power handling. Achieving linearity and maintaining versatility when current surges, peaks or plummets is challenging. STMicroelectronics explains how its new device family is ideal for linear power in harsh conditions.

Power electronics developers, designers and researchers have sought to bring the wide bandgap benefits of gallium nitride (GaN), silicon carbide (SiC,) and GaN on Silicon into wider applications. A Navitas news analysis explores how GaN is mainstreaming, bringing greater power density, smaller form factors, and greater power handling to more commercial and consumer applications.

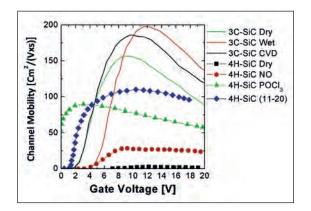

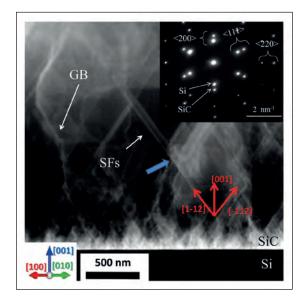

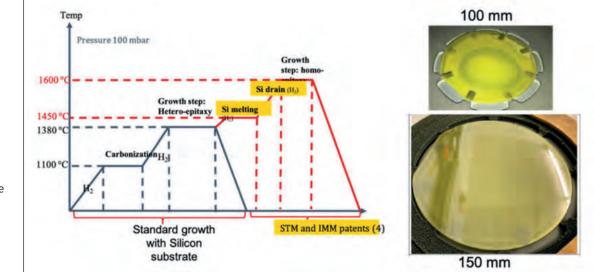

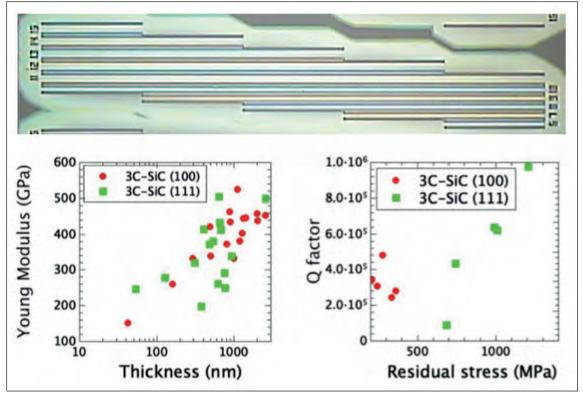

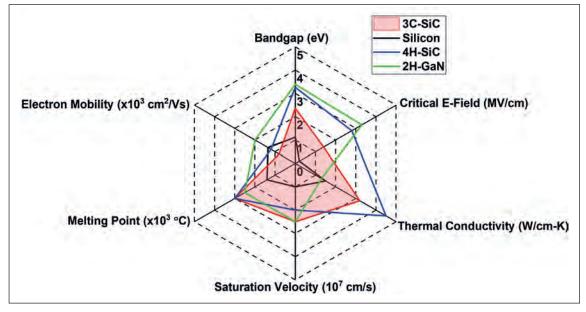

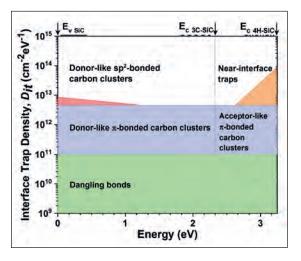

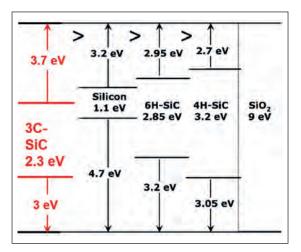

We have an interesting GaN article from researchers at Virginia Tech (USA) that have stretched high performance GaN-based devices to 10 kV. Another rapidly evolving power technology – Silicon Carbide – is explored in an article from the Institute for Microelectronics (Swansea University) that focuses on the allure of 'cubic' SiC, the 3C-SiC

polytype, not today's most-manufactured technology: 4C-SiC. While some aspects of 3C-SiC are less robust than 4C-SiC, cubic SiC offers fabrication advantages including more streamlined (read 'simpler') fabrication of the device interface, be it metal or an insulator; 3C-SiC also shines reliably in the field. The authors championing 3C-SiC argue a performance trade-off is preferable if 4C-SiC remains tougher to manufacture while suffering more frequent failures.

Now the unexpected. ClassOne Technology provides a case study that explores what happens when manufacturers of new equipment find their latest and greatest is outperformed by older equipment. What engineers found was startling, including the realization that electroplating technology has not evolved nearly as far as other processing techniques like those supporting Dennard scaling. See how engineers 'broke' with established electroplating practices and techniques to achieve an astounding 4x performance increase.

### CONTENTS

### VOL. 28 ISSUE IV 2022

### 14

### KEY CRITERIA FOR POWER MOSFETs IN HARSH LINEAR MODE APPLICATIONS

MOSFET devices are often

thought of as the 'workhorses' of powerelectronics due to their wide-ranging applications

### 20 A case study reveals unconventional electroplating techniques can improve performance

Almost six decades ago Intel cofounder Gordon Moore postulated that processors would evolve regularly to double their transistor count, thereby enabling better performance and lower costs.

### 26 Swappable batteries set to revolutionise the power industry

What are the benefits of the new Vanguard Si 1.5kWh battery and what it brings to the growing power rental market.

### 28 A GaN device for all markets

GaN power device maker, Navitas, believes its latest half-bridge power IC will deliver the high powers and efficiencies that mobile phone chargers, electric vehicles, photovoltaics and data centres need

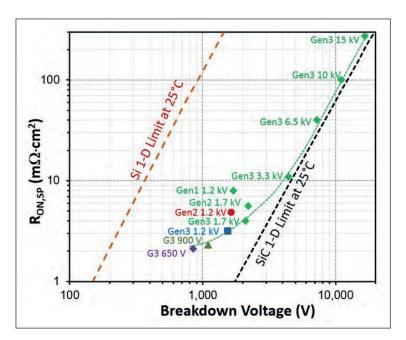

### **30** Stretching GaN power devices to 10 kV

GaN power rectifiers and transistors combine a breakdown voltage beyond 10 kV with a specific on-resistance that's below the SiC limit.

### 36 The allure of cubic SiC

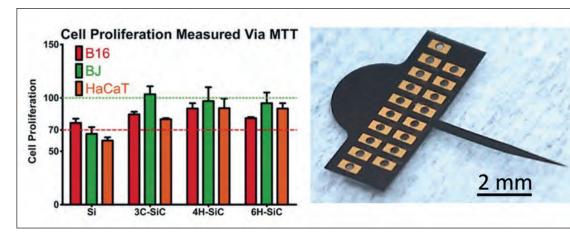

The exceptional electronic and mechanical properties of the cubic form of SiC are enabling this polytype to take rapid strides towards serving in medical devices, MEMS and power electronic applications.

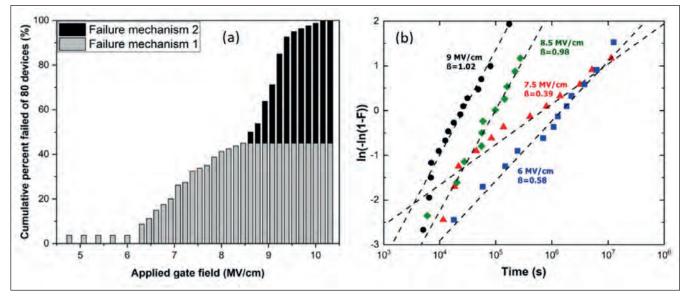

### 42 The glorious gate oxide

Should one worry about the lifetime of the gate oxide of the SiC power MOSFET under negative gate stress?

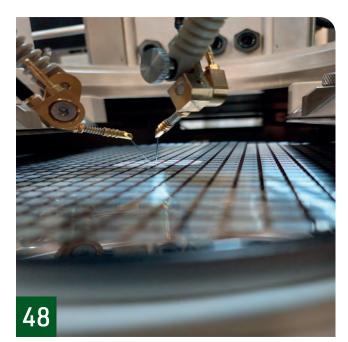

### 48 Cubic SiC: Tomorrow's champion for power electronics?

Offering the same crystal structure as silicon, alongside a wider bandgap and the potential for high reliability, what's to stop cubic SiC from playing a major role in tomorrow's power electronics industry?

### NEWS

- 06 Tech partnership with BMW Group

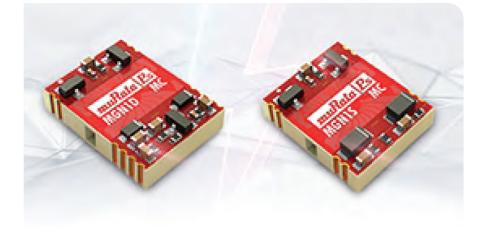

- **07** Murata DC-DCs optimised for GaN gate drivers

- 08 EasyPACK4B enables single module 352 kW PV string inverter

- 08 Hunan Sanan secures \$524M SiC order from NEV brand

- 09 Rohm, Mazda, and Imasen sign SiC e-Axle deal

- **10** Pulsiv raises £1.5m in latest funding round

- 11 Nexperia launches new hotswap ASFETs

- 12 BorgWarner to invest \$500M in Wolfspeed

Technical Editor Mark Andrews mark.andrews@angelbc.com +44 (0)1291629640

Contributing Technical Editor Richard Stevenson richard.stevenson@angelbc.com +44 (0)1923 690215

Sales & Marketing Manager Shehzad Munshi shehzad.munshi@angelbc.com +44 (0)1923 690215 Sales Executive Jessica Harrison jessica.harrison@angelbc.com +44 (0)2476 718209

Design & Production Manager Mitch Gaynor mitch.gaynor@angelbc.com +44 (0)1923 690214

Publisher Jackie Cannon jackie.cannon@angelbc.com +44 (0)1923 690205 CEO Sukhi Bhadal sukhi.bhadal@angelbc.com +44 (0)2476 718970

CTO Scott Adams scott.adams@angelbc.com +44 (0)2476 718970

T: +44 (0)2476 718 970

E: info@angelbc.com

Published by Angel Business Communications Ltd 6 Bow Court, Fletchworth Gate, Burnsall Road, Coventry CV5 65P, UK.

PEW Magazine is published four times a year on a controlled circulation basis. Non-qualifying individuals can subscribe at: £105.00/e158 pa (UK & Europe), £138.00 pa (air mail), \$198 pa (USA). Cover price £4.50. All information herein is believed to be correct at time of going to press. The publisher does not accept responsibility for any errors and omissions. The views expressed in this publication are not necessarily those of the publisher. Every effort has been made to obtain copyright permission for the material contained in this publication. Angel Business Communications Ltd will be happy to acknowledge any copyright oversights in a subsequent issue of the publication. Angel Business Communications Ltd <sup>®</sup> Copyright 2022. All rights reserved. Contents may not be reproduced in whole or part without the written consent of the publishers. The paper used within this magazine is produced by chain of custody certified manufacturers, guaranteeing sustainable sourcing.<sup>®</sup> Copyright 2022.

We strive for accuracy in all we publish; readers and contributors are encouraged to contact us if they recognise an error or omission. Once a magazine edition is published [online, in print or both], we do not update previously published articles to align old company names, branding, marketing efforts, taglines, mission statements or other promotional verbiage, images, or logos to newly created or updated names, images, typographic renderings, logos (or similar) when such references/images were accurately stated, rendered or displayed at the time of the original publication. When companies change their names or the images/text used to represent the company, we invite organizations to provide Angel Business Communications with a news release detailing their new business objectives and/or other changes that could impact how customers/prospects might recognise the company, contact the organisation, or engage with them for future commercial enterprise.

### Tech partnership with BMW Group

### EAS Batteries accelerates development of cylindrical battery cells

EAS BATTERIES has supported the BMW Group's "Battery Cell Competence Centre" in the development of its first cylindrical battery cells.

The round cells have a diameter of 46 mm and will be used for the purely electric drive of future BMW models. The BMW Group officially presented the cylindrical cell format in September 2022.

The aim of the partnership between the BMW Group and EAS Batteries was to accelerate the development of the battery cells and thus give BMW a time advantage. "EAS Batteries provided us with excellent support in the early phase of round cell development, for example by supplying prototype cells, and significantly shortened the development time for the BMW cell," says Peter Lamp, head of Battery Cell Technology at the BMW Group.

EAS Batteries provided BMW with both mechanical and electrochemical support, enabling BMW to pull forward decisions on design and cell chemistry of the new cell to an earlier stage and to define the corresponding processes in a timely manner.

BMW will continue to rely on its technology partnership with EAS in the future. Michael Deutmeyer,

managing xirector of EAS Batteries GmbH, emphasises the contacting: "By licensing our patented contacting technology, the 'tab-less contacting', we are making a decisive contribution to securing the high-current capability of the new BMW cell design".

EAS Batteries has positioned itself in the automotive market within a very short time. The automotive industry first turned to the highly specialised niche supplier for large format round cells in September 2020, at which time interest in co-developments with the EAS Innovation Factory skyrocketed.

The Nordhausen-based producer of innovative cell and battery solutions now supports a wide range of cell development projects for automotive companies worldwide. "EAS know-how is of great importance to the automotive industry," says Michael Deutmeyer. "The targeted charging currents require cells with high current capability. EAS has already perfected these."

## Murata DC-DCs optimised for GaN gate drivers

DC-DCs target EV fast charging infrastructure, battery storage converters, smart grid implementations and renewables

USING PROPRIETARY PCB electrical and mechanical design topologies, Murata has introduced a new series of compact DC-DC converters that are aligned with the increasing prevalence of wide bandgap technology.

The new MGN1 series of 1W output DC-DC converters are designed to deliver the voltages needed by the gate drivers of GaN devices.

These units provide low-profile, small footprint, surface-mount solutions that can be easily integrated into spacelimited systems. They also have the advantage of being lightweight, which opens up even greater deployment opportunities. The output voltages offered are +8V, +12V and +6/-3V.

One of the key attributes of MGN1 series DC-DC converters is their ultralow isolation capacitance of 2.5pF (typical). Through this, the coupling of transients across the isolation barrier is minimised, thereby preventing signal distortion.

In addition, it means that system EMI problems can be mitigated. The >200kV/µs common mode transient immunity (CMTI) of these units makes them well suited to the elevated switching speeds of GaN-based systems, further ensuring gate driver signal integrity. Thanks to their partial discharge performance, reliable operation is maintained in high voltage conditions.

The DC-DC converters in Murata's MGN1 series support a continuous isolation barrier withstand voltage of 1.1kV, with UL62368 conformance pending for 650VDC basic insulation and 240VAC reinforced insulation.

These converters have 6.5mm creepage and clearance figures. A -40°C to +105°C working temperature range allows them to be installed into extremely challenging environments. In addition, reverse polarity and short circuit protection mechanisms are both incorporated.

There are a wide range of GaN-based applications that the new DC-DC converters can be used for. These include EV fast charging infrastructure, battery storage converters, smart grid implementations, solar inverters, solid-state switching breakers, ICT and data centre, wind turbines and motor drives.

### Toshiba MOSEFT wins AspenCore Award

TOSHIBA has won the 'Power Semiconductor/Driver of the Year' category in the World Electronics Achievement Awards (WEAA) 2022.

US-based technology media grou AspenCore gave the award for 'Power Semiconductor/Driver of the Year' to Toshiba's XPQR3004PB MOSFET.

The XPQR3004PB is an N-channel, 40V low-voltage MOSFET for automotive applications. It is suitable for battery switches in eco-friendly vehicles and driving assist motors in mild hybrids. It is Toshiba's most advanced UMOS IX die and is clipped to L-TOGL package. AspenCore noted its high current, high heat dissipation capability and high reliability.

Tsutomu Nomura, president of Toshiba Devices & Storage (Shanghai) said: "We are delighted to be recognised by the prestigious WEAA. This is the fifth year in a row one of our products has taken an award. Toshiba is determined to continue to lead the way in providing the automotive industry and other sectors with power electronics that improve the operating efficiency of equipment and advance carbon neutrality."

### **INDUSTRY NEWS**

## EasyPACK4B enables single module 352 kW PV string inverter

Module enables simple more powerful inverter design with higher power density and reduced system costs

INFINEON TECHNOLOGIES has recently added EasyPACK 4B to its Easy power module family. Targeting applications in photovoltaic string inverters, the module can achieve up to 352 kW.

According to Infineon, it allows a significant increase in output power of about 40 percent compared to last generation PV inverter of 250 kW using EasyPACK 3B. The module aims to enable a simpler but more powerful inverter design with higher power density and reduced system costs. The device is ideal for 1500 V DC solar string inverters.

With the introduction of the F3L600R10W4S7F\_C22 lead-type, EasyPACK 4B is now the largest package in the Easy family with three DCB substrates.

Nevertheless, it still features a nobaseplate design, 12 mm height, PressFit pins and flexible pinout, and more. Like the other Easy packages, it offers flexibility in platform-based solutions. The package extends the EasyPACK 3B hold-down concept to ensure low thermal resistance (R th) and to increase robustness and quality.

Just like the existing Easy family members, the new

EasyPACK 4B has optimised stray inductance for reduced design efforts.

The lead-type power module F3L600R10W4S7F\_C22 features an advanced three-level NPC (ANPC) topology that combines the latest generation of 1200 V CoolSiC Schottky diode with the latest 950 V TRENCHSTOP IGBT7 chip technology for up to 600 A. ANPC is a popular topology in solar string inverters and ensures high efficiency as well as low power losses. This combination of topology and chip optimises the usefulness of the power semiconductor.

The EasyPACK 4B F3L600R10W4S7F\_ C22 can be ordered now. The new Easy 4B package will be available for additional typologies, current ratings and voltage classes.

### Hunan Sanan secures \$524M SiC order from NEV brand

HUNAN SANAN, a subsidiary of Sanan Optoelectronics, will supply SiC chips to a prominent automaker's new electric vehicle product line in the next few years.

Tony Chiang, general manager of Hunan Sanan, said: "Our agreement with this strategic partner further demonstrates the automotive industry's commitment to providing innovative electrification experience to the market and leveraging the advantages of wide bandgap semiconductors to improve overall vehicle performance. The agreement ensures a longterm supply of SiC to our customer to help them realise their promise of low-carbon, smart mobility. "

The SiC chips in the agreement will be manufactured in the Hunan Sanan's mega fab in Changsha, said to be the first vertically integrated SiC wafer manufacturing service platform in China, providing in-house supply chain from SiC crystal, substrate, epitaxy, chip manufacturing, packaging and testing, with a committed annual production capacity of 500,000 SiC 6-inch wafers. Hunan Sanan has recently obtained IATF 16949 system certification while the automotive-grade SiC MOSFETs have been verified with the cooperation of strategic partners, and are expected to be released in production in 2024.

Sike Semiconductor, a company jointly established by Hunan Sanan and Li Auto, also officially started construction this past August and is expected to start production in 2024 with a planned annual production capacity of 2.4 million half-bridge SiC power modules. Hunan Sanan's SiC technology will provide energy for the NEV power system for medium and high voltage platforms.

### Rohm, Mazda, and Imasen sign SiC e-Axle deal

Through the collaboration, Rohm will develop further SiC MOSFETs and modules by working backwards from the finished vehicle

ROHM has signed a joint development agreement with Mazda Motor Corporation and Imasen Electric Industrial for inverters and SiC power modules to be used in the electric drive units of electric vehicles, including e-Axle.

As the 'heart of the EV', e-Axle integrates a motor, reduction gearbox, and inverter into a single unit that plays a large part in determining the driving performance and power conversion efficiency of electric vehicles. SiC MOSFETs in particular are expected to improve efficiency even further.

Rohm will carry out joint inverter development for e-Axle by participating in a 'cooperative framework for the electric drive units development and production' with companies such as Imasen and led by Mazda. At the same time, Rohm will contribute to the creation industry-leading compact, high efficiency electrical units by developing and supplying advanced SiC power modules that provide improved performance.

Through this collaboration, Rohm will develop even more competitive SiC MOSFETs and modules by working backwards from the finished vehicle to understand the performance and optimal drive method required of power semiconductors.

Besides creating new value through mutual understanding between car and device manufacturers, the three companies also support technical innovation in the automotive field and contribute to a sustainable society by leveraging extensive knowledge, technologies, and products garnered on a global basis.

Ichiro Hirose, director and senior managing executive officer; Oversight of R&D, Cost Innovation and Innovation, Mazda Motor Corporation said: "We are pleased to collaborate on the development and production of e-Axle with Rohm, who hopes to create a sustainable mobility society through outstanding semiconductor technologies and advanced system solution development capabilities, to co-create a new value chain that directly links semiconductor devices and vehicles in both directions as electrification brings us closer to carbon neutrality. By partnering with likeminded companies, Mazda is committed to injecting 'driving pleasure' into every product - including electric vehicles."

Katsumi Azuma, director and senior managing executive officer and COO, Rohm: "We are extremely pleased to work together on the development and production of e-Axle with Mazda, who is committed to providing 'driving pleasure' that expresses the inherent appeal of cars. Through this partnership, we hope that by reflecting the true demands and requests in our products we can develop automotive systems that contribute to decarbonization while allowing We are extremely pleased to work together on the development and production of e-Axle with Mazda, who is committed to providing 'driving pleasure' that expresses the inherent appeal of cars

us to gain a deeper understanding of Mazda's goal of creating cars that are sustainable with the earth and society. As the role of semiconductors in the automotive market continues to grow, Rohm will strive to manufacture high quality products and contribute to the creation of a sustainable mobility society by offering a wide range of solutions."

### Pulsiv raises £1.5m in latest funding round

Pulsiv Limited, a UK-based cleantech company announces that it has raised £1.5m through an equity funding round supported by existing shareholders, including management and Frontier IP Group plc (a founder of the business), and new angel investors. The round remains open.

PULSIV'S unique technology aims to conserve every watt of power that needs converting when consumer devices are run from a mains supply, when batteries are being charged, when LED lights are illuminated or when electricity is generated from solar panels. Products under the Pulsiv OSMIUM brand are designed for always-efficient power supplies. Pulsiv HORIZON technology has been developed for advanced solar micro-inverters and power optimizers. The company sells a range of system controllers that intelligently manage power conversion. Our proven reference designs will enable seamless integration by OEMs and accelerate industry adoption.

The Pulsiv OSMIUM architecture can be used in a broad range of OEM products that demand high efficiency, compact design and a low-cost bill of materials. Pulsiv OSMIUM technology exceeds the highest Energy Star standards, eliminates inrush current, reduces overall component cost/count and delivers consistent performance from no-load through to full power. Our scalable solution promotes a platform approach and economies of scale – most components remain unchanged across different designs.

Pulsiv HORIZON employs patented methods for extracting more energy from solar panels than alternative solutions, and our innovative prototype uses a unique split architecture to maximize the power generated by solar micro-inverters and power optimizers under all operating conditions.

Standard reference designs will create greater competition, ensuring that future solar installations will generate maximum returns and accelerate the transition towards renewable energy. The investment raised during this round supports the commercialization of Pulsiv OSMIUM and the ongoing development of Pulsiv HORIZON: • Pulsiv OSMIUM development

systems are currently being manufactured to support customer evaluations and product integration.

- Pulsiv OSMIUM reference designs will simplify the customer journey and drive mass-market adoption.

- Pulsiv HORIZON reference designs will demonstrate our new architecture for power optimiser and microinverters with best-on-class CEC/EU efficiency and power delivery.

Pulsiv's original concept for more efficient power conversion between AC and DC was developed by Zaki Ahmed and spun-out of the University of Plymouth.

It is protected through multiple patent families and trademarks. A global energy transition is underway to phase out fossil fuels and reduce greenhouse gas emissions. IRENA (International Renewal Energy Agency) reports that 90% of the required carbon reductions can be achieved by switching to renewable energy sources and implementing a range of efficiency measures. Rising energy prices, concerns about energy security and inflationary pressures are also driving the need for Pulsiv technology.

Pulsiv CEO Darrel Kingham commented: "We are delighted to have secured this funding given the challenging fundraising environment and full credit goes to my leadership team and our strategic partners. This shows confidence in our progress over the last 18 months, with Pulsiv OSMIUM far exceeding the original design goals and the Pulsiv HORIZON prototype producing best-in-class results. The many benefits of our technology will challenge conventional thinking and give customers an opportunity to differentiate their products in a number of markets."

### Nexperia launches new hotswap ASFETs

Optimised RDS(on) and SOA manage in-rush currents in 12 V hotswap and soft start applications

NEXPERIA has extended its range of Application Specific MOSFETs (ASFETs) for Hotswap and Soft Start with the introduction of ten new 25 V and 30 V fully optimised devices.

According to the company, these combine enhanced safe operating area (SOA) performance with low RDS(on), making them suitable for use in 12 V hotswap applications including data centre servers and communications equipment.

The PSMNR67-30YLE ASFET delivers 2.2x stronger SOA (12 V @100 mS) than previous technologies while having an RDS(on) (max) as low as  $0.7 \text{ m}\Omega$ .

The Spirito effect (represented by the steeper downward slope found on SOA curves at higher voltages) has been eliminated, while exceptional performance is maintained across the full voltage and temperature range (compared to unoptimised devices).

Nexperia further supports designers by removing the need to thermally de-rate designs, by fully characterising these new devices at 125 °C and providing hot SOA datasheet curves. With eight new devices (three 25 V and five 30 V) available in a choice of LFPAK56 & LFPAK56E packages with RDS(on) ranging from 0.7 m $\Omega$  to 2 m $\Omega$ , the majority of hotswap and soft

start applications are addressed. Two additional 25 V products (which will have an even lower RDS(on) of 0.5 m $\Omega$ ) are planned for release over the coming months.

### **kSA BandiT for MBE** Go where pyrometers can't!

- Ideal for low- and high-temperature MBE deposition monitoring

- Flexible viewport mounting geometries

- Insensitive to changing viewport transmission

Learn more by visiting our website: **k-space.com**

**Putting Light to Work** Since 1992

### BorgWarner to invest \$500M in Wolfspeed

Agreement ensures BorgWarner has a reliable supply of SiC devices for its inverter growth plans

SiC specialist Wolfspeed and e-mobility firm BorgWarner have announced a strategic partnership that calls for BorgWarner to invest \$500 million in Wolfspeed's financing transaction in exchange for SiC device capacity.

Under the multi-year agreement between BorgWarner and Wolfspeed, BorgWarner will be entitled to purchase up to \$650 million of devices annually as BorgWarner requirements increase.

"SiC-based power electronics play an increasingly important role for our customers as our electric vehicle business continues to accelerate," said Frédéric Lissalde, president and CEO of BorgWarner.

"We believe this agreement helps ensure that BorgWarner will have a reliable supply of high-quality SiC devices, which are significant to the company's inverter growth plans."

BorgWarner's Charging Forward strategy targets \$4.5 billion of electric vehicle revenue for 2025, compared to less than \$350 million in 2021. Based on new business awards and acquisitions announced as of the Company's third quarter earnings release, BorgWarner believes it is already on track to achieve approximately \$4 billion of electric vehicle revenue by 2025.

"Today's announcement demonstrates the creative solutions two collaborative and strategic partners are pursuing to better support the growing demand for SiC devices. BorgWarner has been a strong partner with Wolfspeed for many years, and we are pleased to secure the investment from them which will be used to support our capacity expansion efforts and ensure we have a steady supply of product for their customers," said Gregg Lowe, president and CEO for Wolfspeed.

"This agreement, combined with our most recent announcement of a multibillion-dollar materials expansion in North Carolina, confirms the industry

transition from silicon to SiC is well underway."

Last month at the company's Investor Day, Wolfspeed outlined a multiyear, \$6.5 billion capacity expansion effort which included the installation of additional tools at the company's state-of-the-art, 200mm Mohawk Valley fab and the construction of a 445-acre SiC materials facility in North Carolina, which will expand the company's existing materials capacity by more than 10x. The first phase of construction is slated to be complete by the end of FY2024.

In addition to a portfolio of more than 2000 standard articles. Wurth Elektronik offers various possibilities to tailor the products to your specific requirements. Personalized modifications of standard terminal blocks are available for small to medium quantities within a few days as a special service. Fully customized products in high quantities are possible within a few weeks. In house design, tooling and prototyping ensures all customer specific requirements are met.

#### #TailoredTBL

WE are here for you! Join our free webinars on

# A webinar without the right audience is worthless!

### Dedicated webinars for the power electronics industry:

Using our 30+ years' experience in B2B vertical technical markets, and as the publisher of Power Electronics portfolio we now offer effective webinars, webcasts and virtual events. We help you get your message, to your desired audience, by marketing to over 53,000 power electronics professionals.

We offer access to the right audience at the right time.

In addition to organising and managing your webinar, we can also market your webinar to our specialist Power Electronics database.

### We deliver the audience!

In a dedicated 6 week program we will promote through our magazine, newsletters, LinkedIn group and website.

We can also provide the webinar moderator, from our team of highly respected editors and researchers.

Not sure what to say? Let our editors work with you and help you with the content.

### Harness the power of a webinar

#### **O** Brand Awareness

Increase global awareness by running sponsored webinars, webcasts and virtual events which also have the possibility of generating revenue

• Lead Generation

Generate and mature leads through the use of online events. Then analyse, qualify, and understand their buying behaviour

#### O Thought Leadership

Become the voice of knowledge by generating compelling content via online events

**POWER** ELECTRONICS WORLD CONNECTING THE GLOBAL COMMUNITY Find out how Angel Webinar can help you organise and run a webinar within the power electronics industry, contact:

jackie.cannon@angelbc.com +44 (0)1923 690 205 angelwebinar.co.uk

## Key criteria for Power MOSFETs in harsh linear mode applications

MOSFET devices are often thought of as the 'workhorses' of power electronics due to their wide-ranging applications. But as the experts at STMicroelectronics advise, key criteria are essential to follow when selecting devices for harsh linear mode applications.

### BY GIUSY GAMBINO, STMICROELECTRONICS, CATANIA, ITALY

NEW ADVANCED trench MOSFETs are increasingly requested with improved linear mode ruggedness to provide excellent performance in telecom, server and industrial applications. They play a key role in safety switches for battery insulation and power distribution, in-rush current limiters, electronic fuses, linear motor controllers, load switches and hot swap applications. These devices exhibit excellent performance in terms of conduction and switching figure of merit (FoM), offering an optimal efficiency and thermal behavior at high switching speed. STMicroelectronics released new MOSFETs with a wide SOA capability able to outperform advanced planar technology in linear mode operation, being thermally stable for a wider range of operating conditions into the safe operating area (SOA). Depending on the gate-source voltage ( $V_{GS}$ ) levels at which the MOSFET is driven, different areas of the device with specific gate threshold voltage (Vth) and current gain values are involved in the drain current (ID) flow with a trade-off between linear mode and switching performance. With this improved design,

### MOSFETs

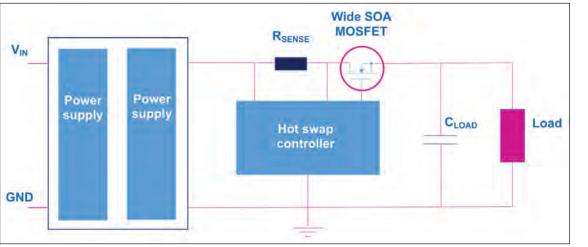

➤ Fig. 1. Hot swap system block diagram.

the new trench power MOSFETs are ideal for rugged forward biased SOA (FBSOA) applications, where high-power levels with high drain-source voltage (VDS) drops are required, ensuring both a high surge current capability in linear mode and low static on-resistance ( $R_{DS(on)}$ ) in fully on conditions.

#### Linear Applications in Power Electronics

Linear mode operation is widely used in power electronics systems and applications that require safe and reliable devices with high ruggedness and thermal stability. High current handling for soft start under significant voltage drops, as well as limiting inrush peaks and any potential failure mechanism are all crucial for hot swap systems. In telecom applications, they are used to charge the bulk capacitor, which powers the entire loading system, such as server, rack and each load connected to the main power supply (Fig. 1).

Since system maintenance is performed in most cases once it is permanently functional, by connecting the replaced parts to the rest of the live system, the capacitor may initially be completely discharged and then a huge current of up to hundreds of amperes can flow through the circuit.

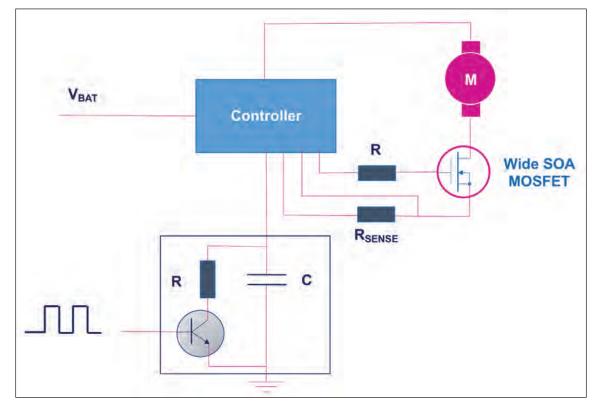

Linear mode working conditions are also requested in fan motion control for heating, ventilation and air conditioning (HVAC) systems (Fig. 2).

According to the below motion control system, the VGS voltage of the MOSFET can be changed by tuning the duty cycle of the bipolar transistor driving voltage and then it is possible to control

➤ Fig. 2. HVAC system block diagram.

### **MOSFETs**

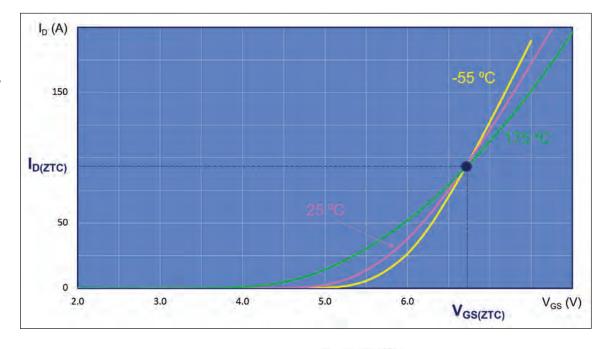

Fig. 3.

Power

MOSFET

transfer

characteristics

at different

temperatures.

the current through the motor and its speed. The current is set by the equivalent resistance provided by the MOSFET when biased under FBSOA working conditions.

To meet the harsh requirements of linear mode applications, a dedicated MOSFET technology has to be considered with a special focus on the key parameters, such as the thermal coefficient, threshold voltage ( $V_{th}$ ), transconductance ( $G_{fs}$ ) and thermal resistance ( $R_{th}$ ).

#### **Thermal Coefficient**

The key parameter to define the linear mode performance of a MOSFET is the thermal coefficient (TC) of the ID current. This coefficient represents the ability of the device to self-balance the current control at both high temperatures and voltages and can be calculated with the following equation (Eq. 1):

$$TC = \frac{\delta I_D}{\delta T}$$

(1)

where: ID is the drain current and T the temperature of the MOSFET.

The heat developed inside the junction is due to the electrical power dissipation (PD) in linear mode (Eq. 2):

$$P_{D} = V_{DS} \times I_{D} = \frac{\Delta T}{Z_{thJA}}$$

(2)

where:  $\mathbf{Z}_{_{thJA}}$  is the junction-to-ambient thermal impedance.

When the temperature increases, the ID current changes according to the thermal coefficient and

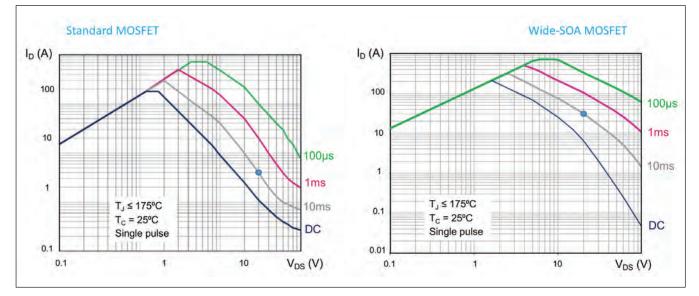

> Fig. 4. SOA diagram for the standard trench MOSFET and wide-SOA device.

### MOSFETs

the device can manage the power until the failure point is reached. The maximum limit of the power is set by the following equation (Eq. 3):

$$V_{DS} \times \frac{\delta I_D}{\delta T} < \frac{\delta \Delta T}{\delta T} \times \frac{1}{Z_{thJA}}$$

(3)

The above equation shows that:

when TC is zero or negative, when the temperature increases, the drain current decreases, then the device works in thermal stability conditions;

when TC is positive, the device can work without failing if the Z<sub>thJA</sub> impedance is low enough to dissipate the heat generated by the applied power.

The thermal coefficient is a technology-dependent parameter, linked to the transfer characteristics of the power MOSFET (Fig. 3).

The three transfer curves intersect at a crossing point, called zero temperature coefficient or zero tempco (ZTC):

- For  $V_{GS} = V_{GS(ZTC)}$ , the device current remains stable with temperature;

- For V<sub>GS</sub> > V<sub>GS[ZTC]</sub>, as the device temperature increases, the drain current tends to decrease, reaching conditions of thermal stability;

- For V<sub>GS</sub> < V<sub>GS(ZTC)</sub> it is vice versa, as the device temperature increases. The drain current continues to increase thanks to the lower threshold voltage, which has a negative coefficient versus temperature. Consequently, when a small area of the die becomes hotter than the adjacent zone, it conducts more drain current, thus creating more heat and pushing the device to failure (thermal runaway), if the appropriate limitations are not set.

Once fixed the thermal coefficient, the device becomes potentially more unstable at high  $V_{DS}$  level. The thermal instability condition can be written also as follows (Eq. 4):

$$V_{DS} \ge \frac{1}{TC \times Z_{m10}}$$

(4)

When the V<sub>DS</sub> voltage increases, the temperature distribution at die level in fact becomes much less uniform, focusing in some small zones of the device. Hot spots determine a localized reduction of the V<sub>th</sub> voltage and an increase of the ID current, which generates more heat further reducing the V<sub>th</sub>. This condition could cause the thermal runaway and the failure of the device.

#### **Technology Design Optimization**

The wide SOA MOSFET technology is the result of a design compromise between  $R_{DS(on)}$  and ZTC point. The device shows different areas, having two different gate threshold voltages (Patent proposal 19-CT-0299 registered in USA in Nov. 2020). When the gate-source voltage  $V_{GS}$  reaches the first threshold voltage and is lower than the second threshold voltage, the first device portion starts to switch on even while the second device portion is still turned off. In this condition, the overall behaviour of the device substantially coincides with the saturation mode of the first portion, showing a low current value and a good thermal stability.

When the gate-source voltage VGS exceeds the second threshold voltage, both the first and second device portions are active, therefore the total current has a second value equal to the sum of the current of the two portions. In this condition, both portions operate in the ohmic region with a low

When the  $V_{\rm DS}$  voltage increases, the temperature distribution at die level in fact becomes much less uniform, focusing in some small zones of the device

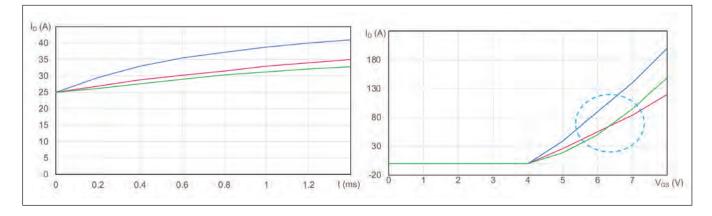

Fig. 6. Measured waveforms for standard trench MOSFET and wide-SOA device at a fixed drain current. value of on-resistance  $R_{\rm DS(on)}$ . Moreover, the high values of the  $V_{\rm GS}$  voltage are fixed in order to be higher than the ZTC point of the power MOSFET, which therefore does not present any thermal drift issue.

As a result, the wide SOA MOSFET (Model: STH200N10WF7-2,) offers superior performance compared to an equivalent standard trench device for higher current capability under the same operating conditions, as shown in Fig. 4.

The standard trench MOSFET is able to withstand a current of 3A at 20V with a 10ms pulse time, while the new wide SOA device can handle a current of 30A at the same conditions. The improved performance is the result of a technology optimization aimed at ensuring quite flat ID current curves at high  $V_{\rm DS}$  voltage values.

The main benefit of the technological improvement is the self-limiting current over time, which is crucial for the thermal stability of the MOSFET over a wider range of operating conditions in linear mode.

### **FURTHER READING**

- [1] A. Consoli, F. Gennaro, A. Testa, G. Consentino, F. Frisina, R. Letor and A. Magrì, "Thermal instability of low voltage power MOSFET's", IEEE Transaction on Power Electronics, vol. 15, no. 3, May 2000.

- [2] G. Consentino and G. Bazzano, "Investigations on Electro-Instability of Low Voltage Power MOSFETs: Theoretical Models and Experimental comparison results for different structures", PET 2004 Conference, Chigaco 2004.

- [3] A Raciti, F. Chimento, S. Musumeci, G. Privitera, "A New Thermal Model for Power MOSFET Devices Accounting for the Behavior in Unclamped Inductive Switching", Special Issue on Reliability Issues in Power Electronics (Si and Wide Band Gap Devices, Interconnections, Passives, Analysis and Applications) on Microelectronics Reliability, ELSEVIER Editor 58 (2016) Conf. Rec. 2019 21st European Conference on Power Electronics and Applications (EPE '19 ECCE Europe), 3-5 Sept. 2019, Genova, Italy.

Simulation results show the current stability and transfer characteristics of the wide SOA device compared to the standard trench MOSFET and the best competitor's device available on the market (Fig. 5).

As a result of the design trade-off, the wide SOA MOSFET features a low current gain at lower gate-source voltage ( $V_{GS}$ ), thus limiting the current increase and, consequently, the thermal runaway in linear mode operation; at higher VGS values, the current gain increases, thereby reducing the on-resistance ( $R_{DS(ON)}$ ) under switching conditions. Thanks to this feature, after limiting the inrush current pulse in linear mode at start up, the wide SOA device can also be driven in PWM (Pulse Width Modulation) mode.

#### **Measurement Results**

The ruggedness of the wide SOA MOSFET with respect to the standard device was experimentally verified by testing the following condition:

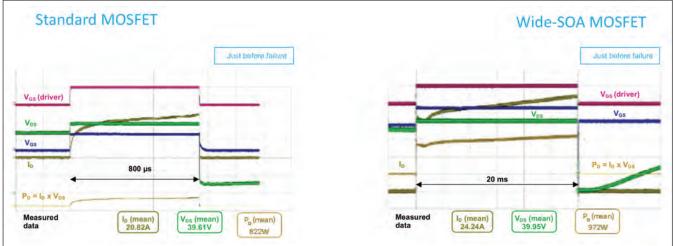

• With a fixed ID current of 20A, the pulse duration was increased until the device failure.

The measured waveforms just before failure are shown in Fig. 6.

Experimental data highlight the high ruggedness of the wide SOA MOSFET, which survives for 20ms under the stressful linear mode conditions whereas the standard device can only work for 800µs before failing.

#### Conclusions

The wide SOA MOSFET exhibits good performance in linear mode working conditions thanks to high ruggedness and thermal stability that prevents thermal runaway. In addition, the new device driven in fully saturation region (linear resistive behavior) is also suitable for switching applications, particularly where the linear mode occurs during the transition phases only. The STH200N10WF7-2 is an ideal choice to design safe and reliable electronics systems.

### FROM INDUSTRIAL AUTOMATION TO HOME AUTOMATION

PowerCoils is an Italian company specialized in the design and production of customised magnetic components for electronics applications for over 20 years.

### WHAT MAKE US ALL DIFFERENT

- Co-design

- Prototype

- Pre-serie

- Mass Production

| POWER       | RAILWAY AND | HOME       | INDUSTRIAL |  |

|-------------|-------------|------------|------------|--|

| ELECTRONICS | MEDICAL     | AUTOMATION | AUTOMATION |  |

## www.powercoils.it

# A case study reveals unconventional electroplating techniques can improve performance

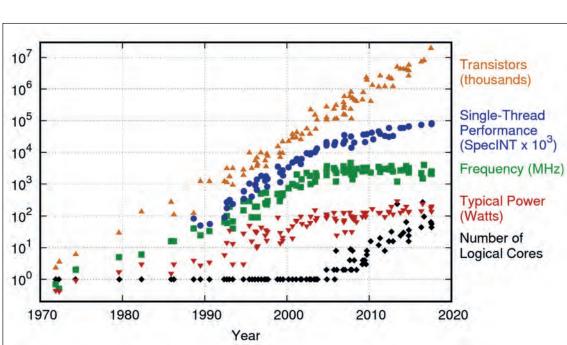

Almost six decades ago Intel cofounder Gordon Moore postulated that processors would evolve regularly to double their transistor count, thereby enabling better performance and lower costs. While traditional Dennard scaling held true for decades, its theoretical limit is fast approaching. The electroplating experts at ClassOne Technology demonstrate a new 'More than Moore' pathway.

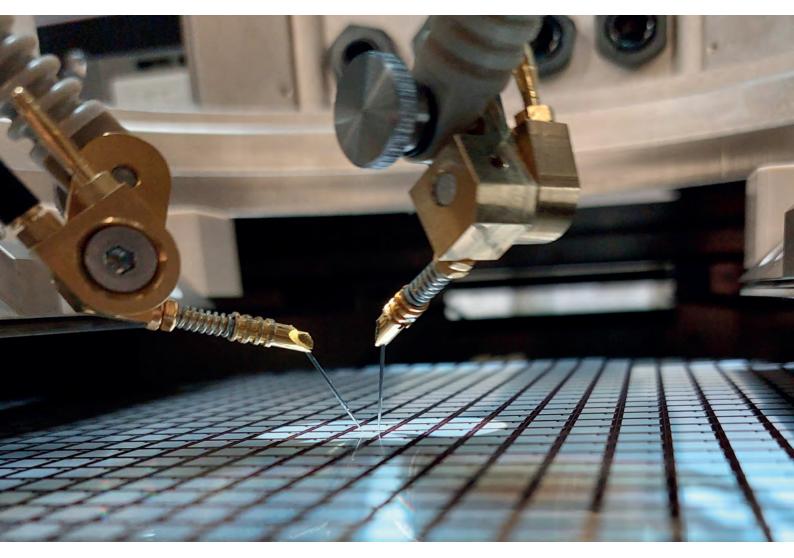

### BY CODY CARTER, PRODUCT ENGINEER, CLASSONE TECHNOLOGY AND STAN WRIGHT, MANAGER, COMPOUND SEMICONDUCTOR-WLP, MACDERMID ALPHA

CLASSONE TECHNOLOGY has built its business around electroplating innovation, demonstrating that

'More than Moore' next-generation technologies

do not require ever-shrinking node sizes and

exceedingly complex metallization schemes. Today, the company is rethinking fundamental

requirements. Its latest discovery reveals that

industry has just scratched the surface of what

electroplating can do for power ICs and many other

electroplating design to address emerging

> Cody Carter

≻ Stan Wright

> Figure 1. The rate of many device performance metrics has stagnated in recent years.

#### The Past & Present of IC Tech

The dawn of Moore's Law in the 1960s recognized a trend in the semiconductor industry – namely, that MOSFET devices doubled in performance every year. Moore then predicted that they would continue to do so at least for the next decade. As semiconductors grew in use and value, manufacturers were able to exponentially improve performance through scaling ever-smaller, further increasing their use and value; this pace of advancement would continue for decades to come,

applications.

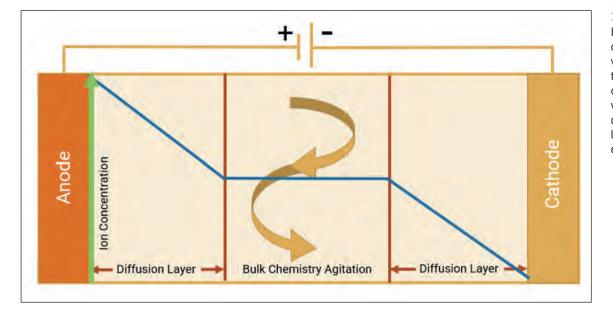

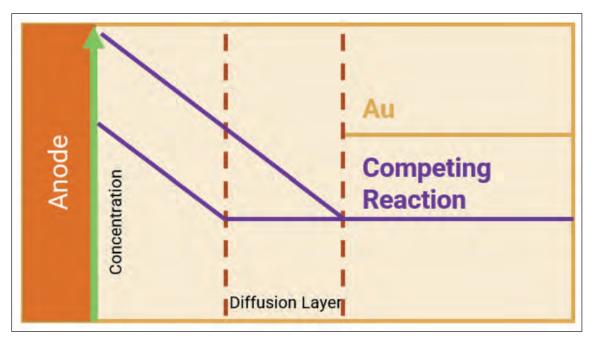

➤ Figure 2a. Ion concentration varies from the bulk chemistry within the diffusion layer during electroplating.

Figure 2b. Increasing agitation at the anode or cathode shortens the diffusion layer, improving ion concentration curves.

creating two key development trends that have not necessarily been as beneficial to the rest of the semiconductor industry.

The first trend is the way in which technology was driven to development. Because device manufacturers have been primarily focused on scaling logic and memory devices, technology development was dedicated to the specific bottlenecks that hindered this scaling. As a result, certain technologies, such as lithography, received intensive development; other technologies considered adequate for use in this type of manufacturing received less development; and technologies not involved in logic and memory (like gold electrochemical deposition) received significantly less development.

The second trend, specifically for equipment manufacturers, was that complexity was added to the systems to appease this particular corner of the industry. On electroplating systems, for instance, hot entry and multiple anodes were developed for damascene electroplating to counteract the effects of the high resistance of a very thin seed layer. In the past decade, however, Moore's Law has been approaching what appears to be its practical limit in terms of making smaller nodes, as seen in Figure 1. Simultaneously, the compound semiconductor industry has exploded in diversity with the advent of high-voltage power devices based on gallium nitride (GaN) and silicon carbide (SiC) and high-frequency devices based on indium phosphide (InP). This has led equipment manufacturers, chemistry vendors, and process engineers to revisit these trends to (1) focus on underdeveloped technologies and (2) question whether the technologies they made to enable the frenzied growth of Moore's Law are best suited for this diversity.

To this end, ClassOne Technology and MacDermid Alpha have partnered with their mutual customer, a leading U.S.-based leader in RF device manufacture, to revisit the fundamental reactions occurring in

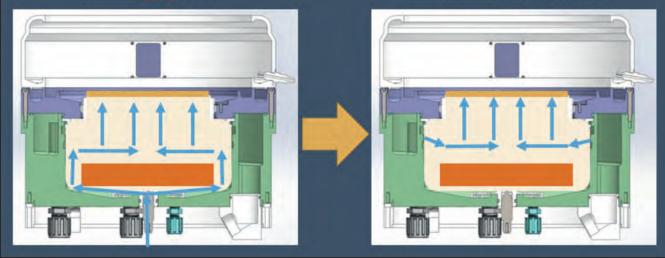

#### Solstice AuPro Reactor

Modified Solstice AuPro Reactor

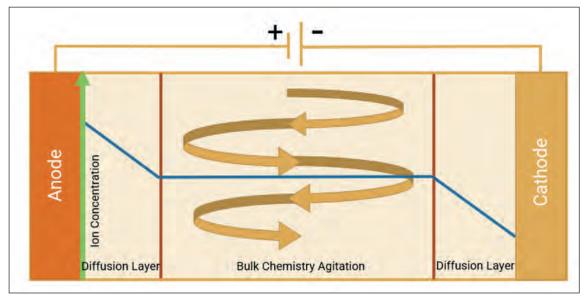

> Figure 3. By flowing above the anode, the boundary layer at the anode on the Solstice is increased. an electroplating system with the goal of attaining better performance from their current process. The outcome was a simple, counterintuitive modification to an existing electroplating reactor.

#### **Getting Moore from Less**

Like equipment vendors, chemical vendors were focused on improving their chemistry performance in order to keep up with the incredible growth of the semiconductor market. For electroplating, copper has been the primary metal choice for interconnect applications, and for that reason it has historically been one of the technical bottlenecks for successive technology nodes. By plating physics alone, faster deposition will occur at areas with shorter diffusion distances. Because of this, additives were developed and refined to enable varied plating rates dependent on the topography of the wafer surface. Suppressors move through solution slowly but attach guickly to the wafer surface. Accelerators move quickly but attach slowly. When paired together, suppressors quickly adhere to the higher

topography of the plating surface, preventing accelerators from doing so. However, diffusing faster, accelerators can move quickly into the lower topography of a damascene structure or a via and attach to the plated surface there. Levelers then prevent undesirable bumps from forming on the plated surface. These additives have overcome the natural physics and now allow faster plating in areas with greater diffusion distances. The result is uniform deposition on non-uniform seed.

This has been an enabling approach for copper electroplating baths, but other processes, such as gold electroplating baths, have not benefited from this development. Additionally, gold electroplating faces other disadvantages in that it is difficult to stabilize in solution and has very slow diffusion rates. Cyanide-based baths have been the historical standard for gold electroplating. The gold-cyanide complex is relatively stable but does not substantially benefit from high concentrations of gold in solution. More recently, gold sulfite baths

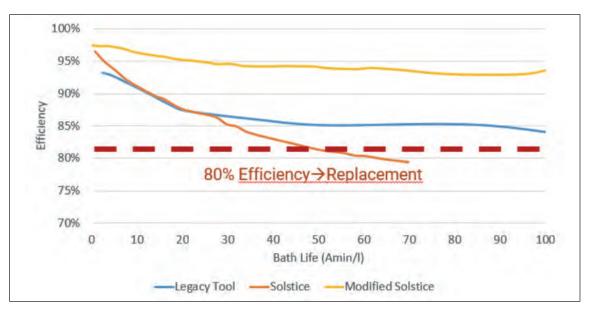

Figure 4. Modifying the Solstice reactor to affect the anode diffusion layer greatly improved performance over that of the initial Solstice GoldPro reactor configuration, as well as the previously existing tool.

have become more popular due to safety concerns with cyanide-based baths and because they allow for higher gold concentrations (and, therefore, faster plating rates). Gold sulfite baths have their own disadvantage, as the sulfite that complexes the gold ion in solution slowly oxidizes over time, making it less stable than its cyanide predecessor.

Compared with copper plating, gold plating is very expensive. The integration of both electroplated metals depends on uniformity to increase throughput in downstream processes (such as CMP). Since gold is very expensive, not only does non-uniform deposition require longer downstream processes, but costs add up in loss of the metal itself, and metal losses are especially egregious when gold is involved. While slower deposition rates can provide better uniformity, it can also cost semiconductor manufacturers by lowering throughput of their electroplating process.

#### **The Problem**

For the customer in our case study, electroplating throughput is essential. Years ago, the company developed a process using a legacy cyanide-based soft gold chemistry from MacDermid Alpha that allowed them to meet throughput by running the bath at a current density four times higher than nominal by using semiconductor style fountain plating equipment vs. a traditional rack plating wet bench. One downside of running the bath in this manner is that the bath efficiency (that is, the amount of gold deposited per ampere) would rapidly decrease, then stabilize for a period of time before it needed to be replaced. Since the efficiency is measured by the amount of gold plated per amp, the current was increased so that the plating time for each wafer did not change as the efficiency decreased. This method, though unconventional, proved to be a stable solution. When the customer decided to replace their existing electroplating equipment with ClassOne's Solstice single-wafer platform, an issue arose in which the electroplating baths now experienced an even more rapid decline in efficiency. Instead of six months, the bath now only lasted two weeks - an unsustainable rate for production purposes.

Several potential solutions were deemed impossible from the outset. Reducing the deposition rate into a lower current density range of the chemistry would require the company to quadruple their electroplating tools to make up for the lack of throughput. Moving to a sulfite-based bath, which would allow them to maintain throughput without detriment to the chemistry, would require an extensive requalification process. The last option, then, was for the three companies to collaborate to determine the root cause of this incongruity between the two electroplating systems.

#### **The Process**

The first step was creating a model in which we could account for all differences between the two

systems - not only physical differences, but even the way they were used in the fab. This included any detail that would pertain to the electroplating reaction, such as the power supply used, fluidics, possible contamination, the way the bath is managed, the product splits between each tool, and even the geometry of the reactors. Overall, 39 individual possible differences were identified, initiating months of troubleshooting to eliminate these possibilities through deliberate testing. What we found would challenge our assumptions regarding fundamental electroplating reactions. The particular electroplating fundamental in this case is that of the diffusion layer. The liquid immediately proximal to the wafer surface is stagnant relative to the wafer. As agitation of the liquid near the wafer surface is increased (by wafer spin, flow, or paddles), this diffusion layer thins, but

Since gold is very expensive, not only does non-uniform deposition require longer downstream processes, but costs add up in loss of the metal itself, and metal losses are is especially egregious when gold is involved

it does not disappear. Since this liquid is stagnant, the only way for ions to cross it is by diffusion. The rate of diffusion of a particular ion is dependent on its size and the electromotive force applied by the electric field.

Figure 2a shows the impact of ion concentration at the electrode due to the diffusion layer. The closer to the anode, the higher the concentration of ions; the inverse is true for the cathode. Figure 2b shows how agitation reduces the size of the diffusion layer and therefore affects the availability of ions at the electrode surface for a given current density (depletion rate of ions).

In an electroplating reactor, both the cathode and the anode have critical diffusion layers. As electrochemical reactions occur at the surface of these two components, plating performance (in terms of rate, efficiency, deposited metal uniformity, etc.) is highly reliant on the thickness of the diffusion layer. At the wafer (cathode), a thinner boundary layer allows better access of the ions in the bulk of the fluid with the surface of the wafer, thus allowing faster deposition rate performance. The anode side

> Figure 5. The competing reaction becomes less efficient with the increased diffusion layer at the anode.

of the electrochemical cell has its own challenges. In electrochemical processes like traditional acid copper, the anode is soluble, meaning the ions in the bath are supplied by the oxidation reactions on the anode. As the metal atoms from the anode surface oxidize and go into solution, removing them from the anode surface more quickly is desirable as it allows more sites for the oxidation process to occur.

When comparing this example to the customer's electroplating process, we assumed that an insoluble anode used in gold electroplating processes (where the ions to be replenished are supplied as a soluble salt, not by the anode) would follow similar logic. Since ion concentration within the anode diffusion layer for an insoluble anode is not a controlled parameter (overlooking other reactions at the anode, such as evolution of hydrogen or reactions with electrolyte salts), we thus deprioritized one item that had been on our model since the beginning: the fluid path at the anode.

#### The Solution

The Solstice electroplating system flows chemistry into the reactor directly under the anode. It then flows around it and up to the wafer. On the legacy tool, however, flow comes into the reactor well above the anode and then up to the wafer. By traditional understanding, this was undesirable and not worth putting energy into when there were so many other possibilities.

However, having eliminated all more likely possibilities, we were left with this one difference. We stuck to our problem-solving protocol and made a simple modification to the Solstice reactor to flow the chemistry into the reactor above the anode, as shown in Figure 3. The result was not only a remediation of the short bath life on the Solstice, but a dramatic improvement over the legacy tool's performance, as shown in Figure 4. While a traditional understanding of the diffusion at the wafer remains intact, this testing has greatly challenged our understanding of its role for inert anodes. The leading theory as to why this change worked is that in the absence of gold metal oxidation at the insoluble anode, there are still other byproduct reactions at the anode.

The reduced diffusion layer at the anode does make the desired reaction more efficient, but it also makes the byproduct reaction more efficient at an even greater rate. When the diffusion layer at the anode was increased with the new flow path, the byproduct became less efficient while the desired reaction efficiency remained intact (Figure 5). What this tells us, beyond this particular instance, is that a renewed fundamental understanding of electroplating is available to inform the semiconductor industry going forward.

#### **Looking Forward**

What this documented experimentation means for semiconductor manufacturers is that the way things have been done is not the way they should be done when new and improved tool configurations are introduced. Electroplating tools have acquired immense capability over the years through complexity demanded by a particular market, while other technologies have not received adequate attention.

What if that complexity is not needed for every corner of the semiconductor field? Can we rethink the way we design equipment to provide the capability that is needed by often-neglected chip producers without added complexity? By revisiting fundamental plating principles, we believe that the era of 'More than Moore' will better serve the diverse compound semiconductor and overall power electronics market.

### HITACHI Inspire the Next

## SiC RoadPak – New levels of power density

No matter if high torque requirement in vehicles, efficient charging for e-busses and e-trucks or smallest footprint within train converters is needed, Hitachi Energy's new generation of e-mobility SiC power semiconductor modules are the best choice.

Hitachi Energy

## Swappable batteries set to revolutionise the power industry

Paul Bramhall, Director Electrification & Rental EMEA, from Briggs & Stratton discusses the benefits of the new Vanguard Si 1.5kWh battery and what it brings to the growing power rental market.

#### Powering the rental market

THE BATTERY MARKET is growing swiftly with demand across multiple industries increasing. Driven by the need to reduce carbon emissions and work towards a "greener future", the push for electrification is affecting businesses of all sizes. With the cost of battery powered equipment on the rise compared to traditional combustion engines, users can face the uncomfortable situation of having to choose between meeting sustainability goals or boosting profit margins. This is when the option of rental equipment can provide a workable solution that avoids large upfront fees and reduces costs.

can access the best products on the market for a reduced fee without putting their own capital at risk. This is particularly beneficial for businesses new to the market, which do not yet have the capacity to take on expensive equipment and therefore need to find alternative solutions that still meets their needs. Whilst rental equipment offers great benefits for the end user, there can be difficulties when it comes to battery powered applications. Recent market trends have seen OEMs try to offer an all-in-one solution approach that leads to sub-par batteries and creates further issues for the end user. To make the rental market more inviting, more needs to be done to limit the number of batteries required to get the job done, ultimately making things easier for the end user. Rather than multiple batteries, each requiring its own power cable, charging facility and user manual, solutions that can be integrated across multiple machines will vastly improve accessibility and efficiency.

To achieve this, OEMs need to work with power suppliers to develop equipment solutions that meet these growing needs. With multiple machines in use across construction sites, manufacturing plants and landscaping grounds, renters could otherwise be forced to accommodate an untenable number of batteries, each with individual charging systems. This would put more pressure on space requirements and overheads, pushing higher costs on the renter and making the move to rental equipment an inefficient and undesirable option.

As battery power becomes the increasing norm, OEMs will need power suppliers capable of providing a power-agnostic approach whereby their power solutions can be used across a wide range of machines to better serve the growing rental market. The newly launched Vanguard 48V Si 1.5kWh Swappable Battery pack from Briggs & Stratton aims to serve this need by providing a battery that can be easily moved from application to application on active jobsites, reducing downtime for the end user and therefore boosting efficiency and productivity.

### Making use of effective swappable batteries

With the ability to be used across multiple machines, rental users can easily move the Si 1.5kWh between applications. The integrated battery management system (BMS) and CANbus J1939 communicate with the application to adjust the discharge rate and ensure effective power output without damaging the battery. This helps to reduce reliance on multiple batteries and streamlines rental company service offerings. Rather than sending out numerous pieces of equipment, each with their own charger and charging recommendations, rental companies can supply one type of charger to charge one type of battery and still power multiple applications.

As different machines used by renters will each have different power requirements, it is important that they are powered by scalable batteries. These battery formats are ideal as they can be stacked in parallel to achieve the desired input required to power each of the individual applications. The Si 1.5kWh battery has been designed with this in mind, with the option for up to 10 batteries to be used in parallel to achieve an overall power of 15kWh. As not all applications will require ten batteries, those not in use can be charged to ensure that the user has access to battery power as and when it is needed.

The resulting process is far more streamlined compared to fixed solutions, which require downtime to replenish energy capacity. Batteries will always require charging, this is unavoidable, but the availability of multiple units will maximise equipment usage in the rental period, delivering the most value by providing more efficient working operations and enabling users to deliver effective results more easily. With the easy latch system on the Swappable Battery, users can swiftly replace a battery when it runs out of charge. This system also allows users to move the battery between applications to tackle a wide range of tasks.

Moving towards standardised power will reduce reliance on traditional combustion engines and enable end users to move closer to their environmental targets. It will require OEMs to work collectively with power providers and rental companies to find solutions suited to multiple machines, while ensuring power requirements are met and equipment is user-friendly for efficient and effective application.

#### Current factors affecting the market

Currently, there is a growing focus from OEMs to develop their own in-house batteries to power their equipment. With the intention of creating all-inone packages, this fast-paced movement towards electrification is seeing many OEMs race to develop power solutions and failing to meet the demands of the end user. Instead, OEMs need to look outwards to power specialists who can advise on the right solution for the unique power capabilities of each application in development. Power specialists, such as Briggs & Stratton, have vast experience in developing power solutions that meet the needs of the end user. As an independent power provider, they can work with a wide range of OEMs to develop power solutions suited to the equipment in question. By working with an independent power specialist, rental companies can select from a wide range of manufacturers to meet customer needs, safe in the knowledge that they will not need to rent out multiple batteries and chargers to each user.

Instead, the renter themselves can reduce their space costs by streamlining their equipment to run off one type of battery. The rental company can offer equipment from a range of OEMs, but the power source for each machine will be the same. This helps to reduce manufacturing pressure and, in turn, reduce the need for mining new materials.

#### Next steps for OEMs

When it comes to developing unique applications to meet the demands of the growing electrification market, it is important to engage collaboratively with effective power providers. That way OEMs can develop unique applications that will improve efficiency and execution for your target audience. With the growing opportunities that the rental market offers, connecting with companies like Briggs & Stratton will enable OEMs to capitalise on the growing demand for electrified equipment.

As companies continue to explore ways to reduce their emissions quotas to meet growing customer demand and reduce their overall environmental impact, it is important to find power solutions that can meet demand without compromising overall performance. To achieve this, agnostic power specialists who understand your power needs and deliver a bespoke solution will provide the best way forward.

This has never been a more pressing issue for the rental hire market, where diverse ranges of equipment are available to customers. In a traditional, fossil fuel-led approach, end users can easily make use of the same petrol source in each machine. However, as manufacturers look to move to battery power, there are growing concerns over the different battery platforms that rental companies will need to deal with.

Overcoming these concerns requires an agnostic power solution that can be used across multiple brands and a wide range of machines. Breaking away from closed-off battery platforms to work collectively with other OEMs using the same battery platform will help to reduce the number of batteries in production – a vital step towards the ultimate goal of a greener future.

\*study by Grand View Research: <u>https://www.</u> grandviewresearch.com/industry-analysis/ construction-equipment-rental-market

### NEWS ANALYSIS I NAVITAS

### A GaN device for all markets

GaN power device maker, Navitas, believes its latest half-bridge power IC will deliver the high powers and efficiencies that mobile phone chargers, electric vehicles, photovoltaics and data centres need, reports **REBECCA POOL**

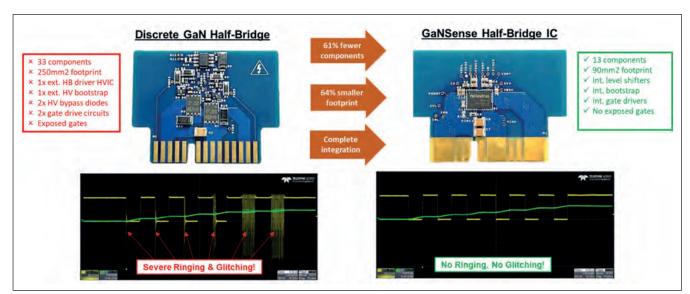

IN EARLY September this year, California-based GaN power device manufacturer, Navitas, released 'GaNSense', a half-bridge power IC that the company reckons provides a 'new level' of megahertz switching frequencies whilst slashing system cost and complexity compared with discrete half-bridge GaN ICs.

As Llew Vaughan-Edmunds, senior director of marketing at Navitas, points out: "The difference between Navitas and other gallium nitride companies is that we integrate the gate driver monolithically with the gallium nitride power and integrate real-time sensing and autonomous protection – that's the secret of our success and why we're number one in this field."

Following industry's relentless demand for more power and higher switching frequencies, Vaughan-Edmunds is certain that GaN ICs are going to be instrumental to the power devices of the future. Looking at mobile device chargers, right now Apple and Samsung wireless fast charge power adapters are currently rated to around 45W, but this is quickly changing. "These chargers are going to 65 W and 100 W now, and ultra-fast chargers have just been released at 200 W so you can charge your phone within 10 minutes," says Vaughan-Edmunds.

At the same time, data centres are striving for higher efficiencies to reduce electrical and cooling costs, as are electric vehicles to reduce battery recharge times. "[Industry] needs half-bridge topologies to meet these higher power, higher switching frequency and higher efficiency market demands, and this is why we've released our half-bridge IC now," he adds.

Navitas' half-bridge power IC integrates two GaN FETs with drive, control, sensing, autonomous protection and level-shift isolation in a single package. GaN is notorious for its sensitive gate structure, so from word go, Navitas has set out to deliver GaN power ICs with robust GaN gate protection. Given this, autonomous protection is a key feature of the latest chips. As Vaughan-Edmunds points out, gate driver and sensing protection is now imperative given the noise generated at higher frequencies and powers. At the same time, temperature protection and over-current protection

### NEWS ANALYSIS I NAVITAS

will autonomously shut down the chip to prevent device and system failure.

The Navitas director also points out how this set-up requires 61 percent fewer components and has a 64 percent smaller footprint than a typical discrete GaN half-bridge IC. "By eliminating all the [associated] circuitry, we're reducing circuit parasitics – this does give us nice, clean switching," he adds. "We are the first company to release a half-bridge power IC with this level of integration and rich feature set."

#### Market-driven

Importantly, these latest half-bridge power ICs are already in mass production in Europe. "Strategically, we wanted to be first to market in key growth segments," says Vaughan-Edmunds. This sentiment is clearly in line with past product launches.

Navitas power ICs have been in production since 2018, and just last year industry analyst TrendForce indicated that this west-coast chipmaker held the greatest market share amongst GaN power device suppliers.

According to Navitas, its technology is now in well over 150 different charging products from different companies – key partnerships include Lenovo, Xiaomi, Dell, Oppo, LG and Amazon. And, in a recent *Compound Semiconductor* interview, Navitas vice president Stephen Oliver estimated that the company was working with more than 90 percent of OEMs that are supplying phones, laptops and tablets.

Beyond mobile chargers, the company is gearing up for solar, datacentre and electric vehicle applications, and anticipates these markets to start bringing in revenue within the next 3 years. "The fast mobile charging market is our bread and butter right now, but beyond charging, our strategy includes looking at solar, electric vehicle and data centre markets," says Vaughan-Edmunds. "The electric vehicle and data centre markets take longer in Navitas power ICs have been in production since 2018, and just last year industry analyst TrendForce indicated that this west-coast chipmaker held the greatest market share amongst GaN power device suppliers

design cycles and qualification, however these are key strategic markets for Navitas and where we are focusing.

"If we look at the mobile charging market alone – right now GaN only has a few percent of the total market so we've still got a lot of room to grow," he adds.

#### **Bringing in SiC**

Yet despite the company's clear advocacy towards GaN, it acquired SiC developer GeneSiC Semiconductor for \$100 million in late August. At the time, Navitas chief executive, Gene Sheridan, said GeneSiC will help his company to accelerate growth in the high-power solar, datacentre and electric vehicle markets.

For his part, Vaughan-Edmunds highlights how rugged, vertical SiC devices are better suited to traction inverters, which provide enormous amounts of torque and acceleration in electric vehicles. "We're not a gallium nitride company trying to convince customers to use gallium nitride instead of silicon carbide. We realise that silicon carbide has its place in the market, and it's a big market that we want to go after," he says. "On gallium nitride alone, we've already shipped more than 50 million pieces, with zero field failures – and that's only just scratching the surface."

> Discrete GaN halfbridge IC versus Navitas' latest half-bridge IC.

### Stretching GaN power devices to 10 kV

GaN power rectifiers and transistors combine a breakdown voltage beyond 10 kV with a specific on-resistance that's below the SiC limit

### BY YUHAO ZHANG FROM VIRGINIA TECH

> Yuhao Zhang holding a GaN power transistor wafer in front of the 10 kV probe station ONE OF THE KEYS to getting carbon emissions to net zero is to increase the efficiency of electrical energy processing. This can be accomplished through the introduction of semiconductor-based power devices with a lower on-resistance, a faster switching speed and a high breakdown voltage. It is a roll-out that must include devices operating between 1 kV and 35 kV, a range that's often known as medium-voltage, but also referred to as highvoltage in many contexts. Devices operating in this range are ubiquitously used in electrical grids, renewable energy processing, industrial motor drives and electrified transportation. Driven by this widespread deployment, the market size for medium-voltage power devices has already topped \$10 billion and is increasing at pace.

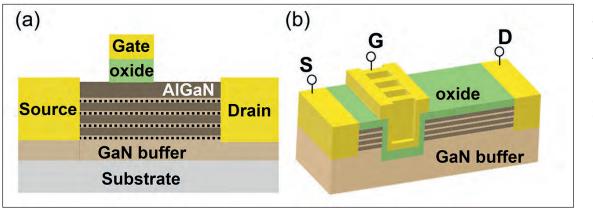

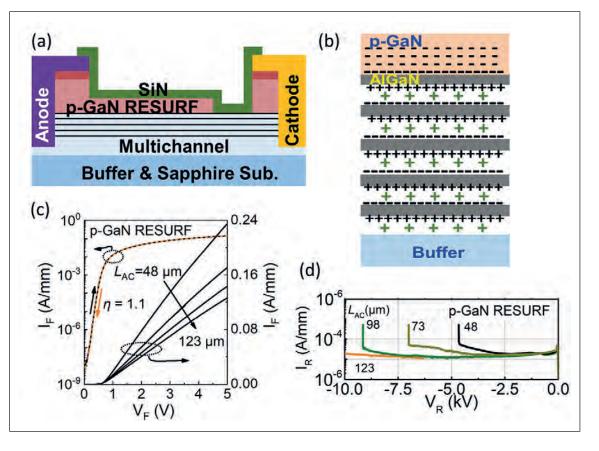

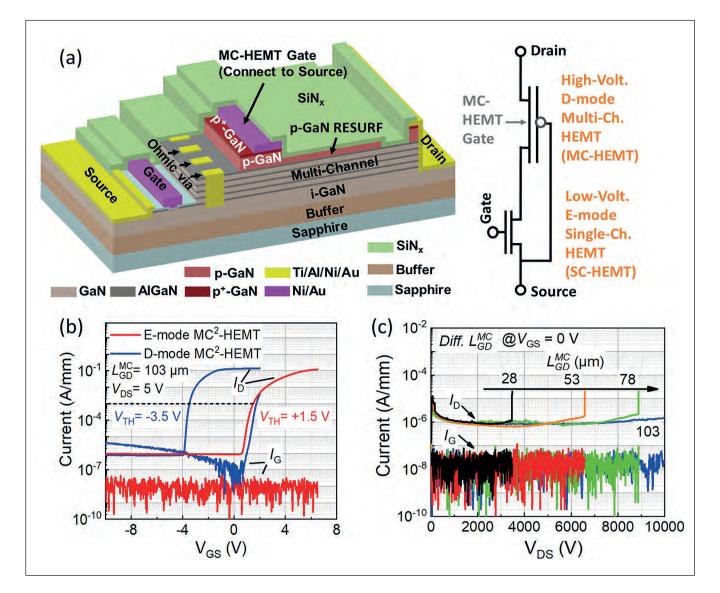

Figure 1. The multichannel AlGaN/GaN HEMT with a planar gate (a) and a trigate architecture (b).

Dominating today's medium-voltage power device market are a pair of silicon devices: the insulatedgate bipolar transistor; and the *p*-*n* diode, up to a voltage class of 6.5 kV. Both suffer from a slow switching speed, stemming from bipolar operation – as electrons and holes contribute to current conduction, both forms of carrier must be removed or supplied during device switching.

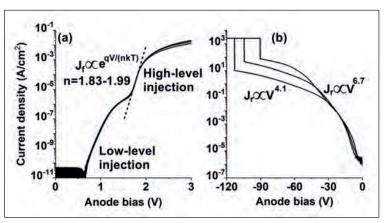

A superior performance can be realised by turning to the unipolar SiC MOSFET and the SiC junction barrier Schottky diode. These alternatives, which enable faster switching speeds, are covering an increasingly broad range of voltages. They have been commercialized up to 3.3 kV, and industrial R&D devices are available up to 10 kV.

But that's not the ultimate solution, as even better results are possible with SiC's wide bandgap rival, GaN. Providing a higher critical electric field and a higher electron mobility, GaN enables the fabrication of devices with a lateral or a vertical architecture. Lateral GaN HEMTs operating at up to 900 V are already on the market, and industrial vertical GaN transistors have been demonstrated at the 1.2 kV class. Progress has also been made at far higher voltages. Some groups are reporting GaN devices with blocking voltages close to 10 kV. However, specific on-resistances are much higher than those of SiC counterparts, leading many to conclude that GaN is only advantageous in the low-voltage range.

But those of us at Virginia Polytechnic Institute and State University – better known as Virginia Tech – beg to differ. Working in collaboration with engineers at the University of Southern California, the University of Cambridge, Enkris Semiconductor and Qorvo, we have developed a new generation of lateral medium-voltage devices that are based on a multi-channel GaN platform and outperform their silicon and SiC counterparts.

We produce our devices from multi-channel AlGaN/ GaN wafers that consist of vertically-stacked heterostructures, which enable the fabrication of diodes and HEMTs that feature a high mobility twodimensional electron gas (2DEG) channel. These devices offer a high-power handling capability, thanks to the stacked channels (see Figure 1(a)), and can leverage some of the benefits of vertical devices, such as a spatially distributed current. By drawing on a series of device innovations we have demonstrated 10 kV GaN Schottky barrier diodes and normally-off HEMTs that exceed the onedimensional SiC unipolar limit, in terms of the tradeoff between the specific on-resistance and the blocking voltage.

#### Challenges of multi-channel devices

It is easy to understand why the introduction of multiple channels reduces the on-resistance of a device. Using the 4-inch multi-channel GaN wafer grown by Enkris Semiconductor, the devices that we fabricate feature five channels, leading to a sheet resistance of just 120  $\Omega$ /sq – that's about a third-to-a-quarter of that of today's commercial GaN HEMTs formed from single-channel wafers. The upshot is that a switch to multiple channels enables a dramatic decrease in specific on-resistance.

Unfortunately, enjoying this benefit is far from trivial. There are two fundamental challenges associated with multi-channel devices.

The first arises because when the device is blocking voltage, there is a large volume of charge in the stacked channels that can lead to a fast drop in the electric field. This is a fundamental issue, expected from the simple Poisson equation. Due to this large

By drawing on a series of device innovations, we have demonstrated 10 kV GaN Schottky barrier diodes and normally-off HEMTs that exceed the one-dimensional SiC unipolar limit, in terms of the trade-off between the specific on-resistance and the blocking voltage

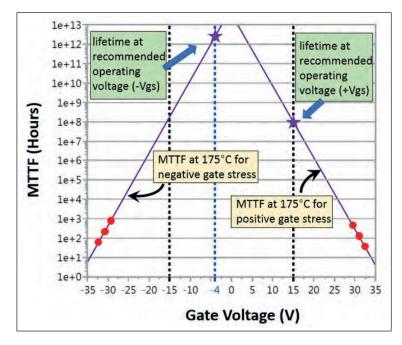

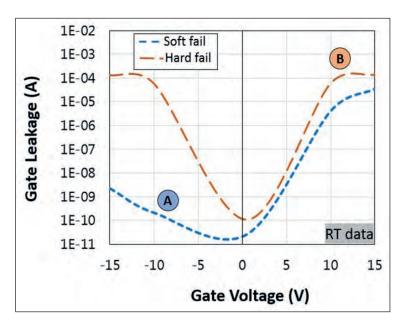

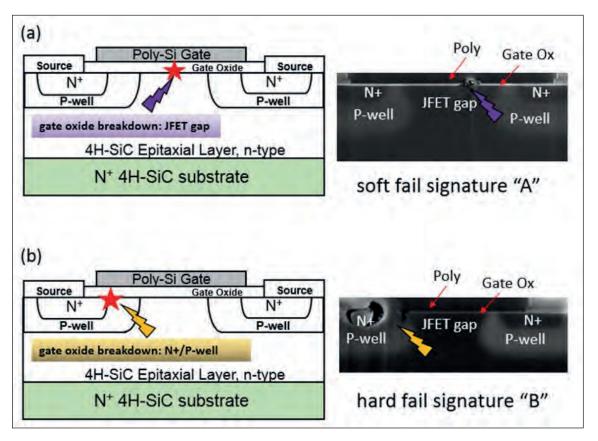

volume of charge, there is a low average electric field across the device length, and increasing this dimension does not ensure an upscaling of the blocking voltage. Note that with these net charges, even if there is a good edge termination that enables a large peak electric field at the device edge region (see *Compound Semiconductor* 27 **3** 44), the blocking voltage of a multi-channel device tends to be much lower than that of a single-channel counterpart with the same length.