## NEW SILICON CARBIDE MOSFETS AND DIODES ENABLE HIGHER EFFICIENCY IN HIGH-VOLTAGE APPLICATIONS

#### ISSUE IV 2024

INSIDE

News Review, Features

News Analysis, Profiles

**Research Review**

and much more...

AN ANGEL BUSINESS COMMUNICATIONS PUBLICATION

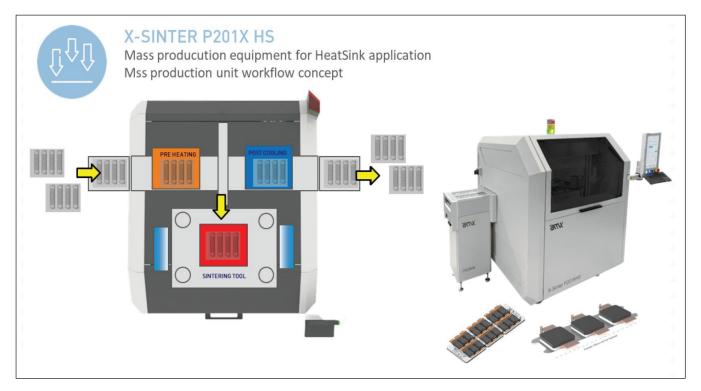

#### Large-Area Sintering for High Power Modules

Examining the benefits of large-area sintering, including thermal resistance and reliability improvements

### Innovative Approaches to IGBT Production

Manufacturers of power semiconductor devices often grapple with high breakage rates and significant financial losses

#### POWERELECTRONICSWORLD.NET

### Overcoming DC Bias and Size Challenges in Quantum

Quantum computing, with its promise of efficient calculations in challenging applications, is rapidly advancing in R&D

# RIXTRON

# **THE NEW G10 SERIES**

## Your Productivity Solution for All Advanced Epitaxy Materials

## G10-GaN

- 8x150mm (6") or 5x200mm (8")

- 1<sup>st</sup> fully automated compact GaN MOCVD cluster designed 100% for Si Power fabs

- Novel hardware solution for unmatched barrier uniformities and device yields

#### End Markets/Products:

Power Electronics & Wireless communication

*BIXTRON*

## - **G10-SiC**

- > 9x150mm (6") or 6x200mm (8")

- New hardware & process surpassing Single Wafer Reactor uniformities

- +50% productivity per fab area with large batch technology & small footprint

End Markets/Products: EV inverters & charging infrastructure

## G10-AsP

- ▶ 8x150mm (6") or 5x200mm (8")

- 1<sup>st</sup> fully automated AsP MOCVD system enabling 10x lower defect density

- Unmatched wavelength uniformity on all wafer sizes

#### End Markets/Products:

Micro LED, Optical Data communication, 3D-sensing & LiDAR

# VIEWPOINT By Phil Alsop Editor

## EV market running out of revs?

WHICH COMES FIRST – the EV or the charging station? In simple terms, that's the dilemma facing the EV industry right now. Should there be a massive roll out of charging infrastructure (and just think what's required to replicate the re-fuelling capacity of every single service station across the globe, before local infrastructure is even considered), which will then encourage more and more people to purchase an EV – build it and they will come? Or, do you keep trying to sell EVs until some kind of unstoppable momentum is achieved, and there's then the rush to build out the necessary supporting charging infrastructure? Either way, I think it's all but impossible to achieve success without major intervention from governments. And we're not just talking about the launch of policies and the encouragement of sustainability in general. No, we need billions and billions of state investment to kick start the EV success story. Which is maybe why China would seem to be a shining light in an otherwise slightly dimming market?

If we're being brutally honest, the global automotive industry is in danger of losing its way. Governmental pressure is telling them what is expected, but there's no clear roadmap – companies are being asked to drive forwards in the dark. And then being castigated for not moving forwards quickly enough. And consumers are picking up on this uncertainty, even if they have not been put off by the hefty price tag of going electric. And, as I've mentioned before, there are plenty of smart folks who genuinely believe that (green) hydrogen may well be the automotive industry's final destination fuel of choice.

Where some times one looks at an industry or individual companies who have simply mis-read their market, and

suffered as a result, in the case of the automotive sector, they really are being handed so many mixed messages by individual governments, and very little concrete help or advice, that there's plenty of sympathy for them. And there's no sign of this disruption clearing any time soon.

The good news, such as it is, is that there's still a massive market when it comes to adding intelligence to vehicles, whatever their fuel source, so the semiconductor market has plenty of room for growth here. Whether or not this will end up with the 'nirvana' of autonomous vehicles is anyone's guess.

However, the quest for intelligence, whatever the market size, will not disguise the EV 'chaos'. Sorry if that sounds like a gloomy message on which to end the year. On the bright side, the speed at which technology is developing almost certainly means that there will be other major opportunities ahead. And the AI market shows no signs of slowing down any time soon. And maybe renewables opportunities will outpace expected demand?

#### A happy festive season to you all.

## CONTENTS

VOL. 28 ISSUE IV 2024

#### 14 Combining a CMOS driver and a GaN power switch on 300 mm silicon

Intel's DrGaN technology, involving the monolithic integration of GaN and silicon CMOS on 300 mm wafers

# 22 Bipolar p-FETs enable all-GaN power integration

Bipolar transport overcomes the inherent barriers of GaN p-FETs to pave the way to higher current densities

### 28 Crushing MOSFETs one tipping point at a time

The growth of GaN is inevitable as it displaces the MOSFET in one application after another

### 32 Unlocking the Internet of Everything with flexible chips

An Internet of Everything has long been promised, but progress has been hindered by semiconductor availability, cost, and concerns around sustainability

# 34 Unleashing the performance of 1200V SiC devices: driving the future of electrification

As the world accelerates toward electrification, driven by the electrification of transport, the global transition to renewable energy, and the growing demand for energy-efficient industrial systems, the role of advanced power semiconductor devices has become more critical than ever

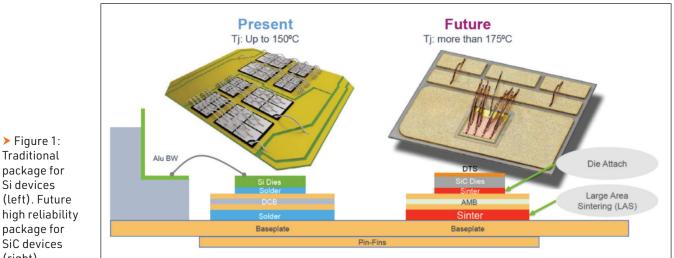

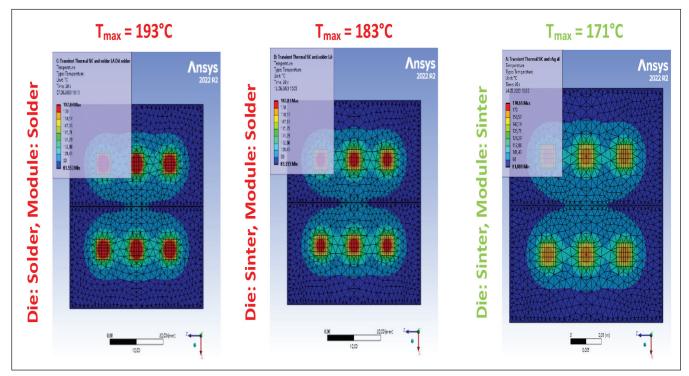

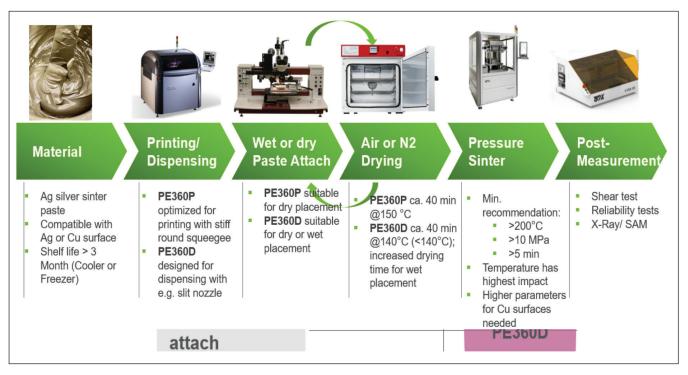

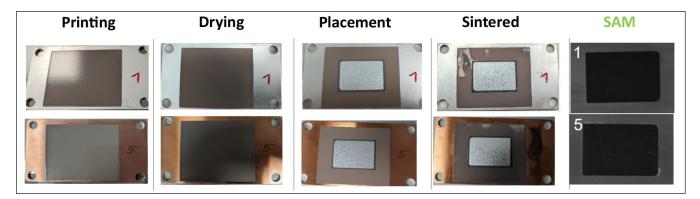

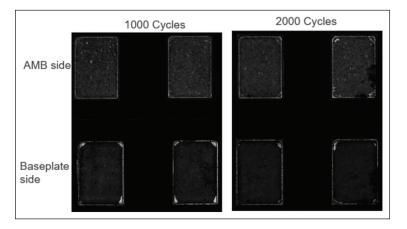

### 40 Large-area sintering for highperformance power module packaging

Examining the benefits of large-area sintering, including thermal resistance and reliability improvements

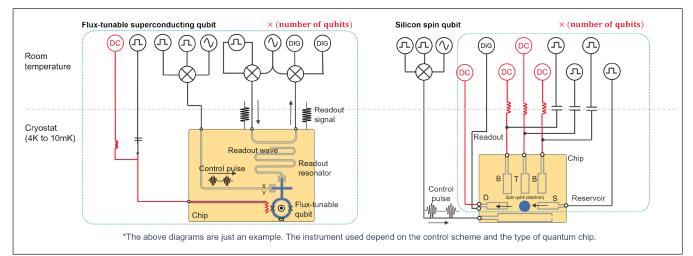

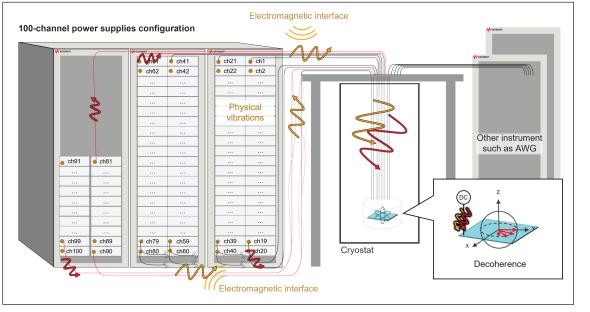

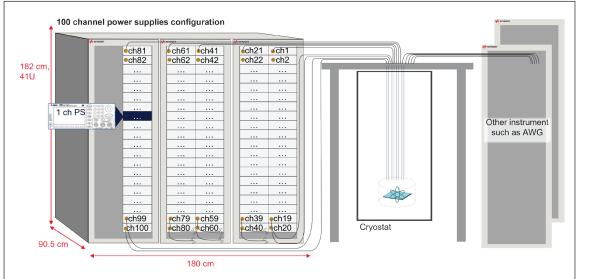

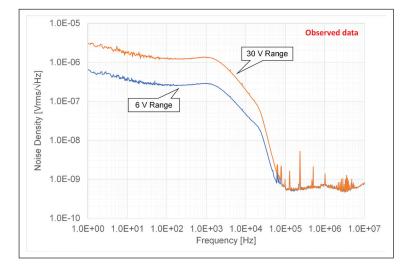

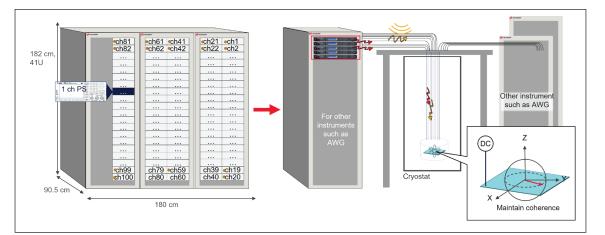

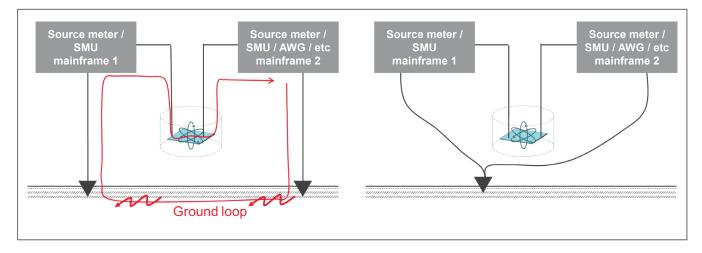

### 46 Controlling the qubits: Overcoming DC bias and size challenges in quantum

Quantum computing, with its promise of efficient calculations in challenging applications, is rapidly advancing in research and development

### 50 Breaking the cycle of breakage: Innovative approaches to IGBT production

Manufacturers of power semiconductor devices often grapple with high breakage rates and significant financial losses due to stress-related damages during production

### 52 New semiconductor material: AlYN promises more energyefficient and powerful electronics

With aluminum yttrium nitride (AIYN), they have succeeded in producing and characterizing a new and promising semiconductor material using the MOCVD process

### 54 New Silicon Carbide MOSFETs and Diodes Enable Higher Efficiency in High-Voltage Applications

Sanan Semiconductor, an emerging leader in wide bandgap power semiconductor materials, components, and foundry services has expanded its SiC power product portfolio with the introduction of 1700V and 2000V devices

## NEWS

- **06** Atomera/Sandia project to address GaN/Si challenges

- 07 UK announces sustainable electronics centre

**08** 'All-GO-HEMT' to develop β-gallium oxide heterostructures

- **09** Infineon unveils world's thinnest silicon power wafer

- **09** Mitsubishi to invest \$64m in new power module plant

- **10** US DOE announces \$481.5m loan to SK Siltron CCS

- 10 SICC shows first 300mm SiC wafer

##

Editor Phil Alsop phil.alsop@angelbc.com +44(0)7786084559

News Editor Christine Evans-Pughe christine.evans-pughe@angelbc.com

Contributing Technical Editor Richard Stevenson richard.stevenson@angelbc.com +44 (01923 690215

Sales & Marketing Manager Shehzad Munshi shehzad.munshi@angelbc.com +44 (0)1923 690215

Design & Production Manager Mitch Gaynor mitch.gaynor@angelbc.com +44 (0)1923 690214 Senior Event and Media Executive for Power Electronics International James Cheriton james.cheriton@angelbc.com +44 (0)2476 718970

Publisher Jackie Cannon jackie.cannon@angelbc.com +44 (0)1923 690205

CEO Sukhi Bhadal sukhi.bhadal@angelbc.com +44 (0)2476 718970

CTO Scott Adams scott.adams@angelbc.com +44 (0)2476 718970 PEW Magazine is published four times a year on a controlled circulation basis. Non-qualifying individuals can subscribe at: £105.00/e158 pa (UK & Europe), £138.00 pa (air mail), \$198 pa (USA). Cover price £4.50. All information herein is believed to be correct at time of going to press. The publisher does not accept responsibility for any errors and omissions. The views expressed in this publication are not necessarily those of the publisher.

Every effort has been made to obtain copyright permission for the material contained in this publication. Angel Business Communications Ltd will be happy to acknowledge any copyright oversights in a subsequent issue of the publication. Angel Business Communications Ltd @ Copyright 2024. All rights reserved. Contents may not be reproduced in whole or part without the written consent of the publishers. The paper used within this magazine is produced by chain of custody certified manufacturers, guaranteeing sustainable sourcing.@ Copyright 2024.

We strive for accuracy in all we publish; readers and contributors are encouraged to contact us if they recognise an error or omission. Once a magazine edition is published [online, in print or both], we do not update previously published articles to align old company names, branding, marketing efforts, taglines, mission statements or other promotional verbiage, images, or logos to newly created or updated names, images, typographic renderings, logos (or similar) when such references/images were accurately stated, rendered or displayed at the time of the original publication.

When companies change their names or the images/text used to represent the company, we invite organizations to provide Angel Business Communications with a news release detailing their new business objectives and/or other changes that could impact how customers/prospects might recognise the company, contact the organisation, or engage with them for future commercial enterprise.

Published by Angel Business Communications Ltd 6 Bow Court, Fletchworth Gate, Burnsall Road, Coventry CV5 6SP, UK. T: +44 (0)2476 718 970

E: info@angelbc.com W: angelbc.com

### **INDUSTRY NEWS**

# Atomera/Sandia project to address GaN/Si challenges

Collaboration aims to create first GaN transistors from wafers using Atomera's Mears Silicon Technology (MST)

ATOMERA, a US semiconductor materials and technology licensing company, has announced a project at Sandia National Laboratories (a US Department of Energy, research centre), to address the challenges of growing GaN films on silicon.

The project, which is a collaboration with the Centre for Integrated Nanotechnologies (CINT) at Sandia, aims to create the world's first GaN transistors and test data from wafers employing Atomera's Mears Silicon Technology (MST). The effort will build upon improvements already observed at the materials level in GaN/MST on silicon wafers.

MST consists of layers of a nonsemiconductor, such as oxygen inserted into a semiconductor material, such as silicon so that epitaxial growth is preserved. These layers can be used to modify or enhance the basic semiconductor properties and device attributes in a number of ways, including: diffusion blocking, variability, mobility, gate leakage, and reliability, among others.

"Atomera's MST represents a tremendous opportunity to improve GaN on Si manufacturing and provide speed, efficiency and cost-saving benefits to a wide range of industries including electronics, RF/microwave electronics and even MicroLEDs. This user project will test the effectiveness of the MST solution quickly using CINT's highly specialized tools and technology and give Atomera access to our team of scientists and researchers," said Jeffrey Nelson, director of CINT.

Due to the limited availability and size of native substrates, most GaN devices have been grown heteroepitaxially on sapphire, SiC or Si substrates.

Although impressive performance has been achieved with each of these, Si substrates offer a clear pathway to large wafer size, low cost and compatibility with well-established CMOS wafer fabrication lines.

However, there are significant challenges, including wafer warping or cracking, associated with the growth of thick GaN films on Si (GaN/Si),

Atomera's MST represents a tremendous opportunity to improve GaN on Si manufacturing and provide speed, efficiency and costsaving benefits to a wide range of industries including electronics, RF/ microwave electronics and even MicroLEDs particularly at large wafer sizes. "Over the past approximately 25 years, GaN has transformed multiple industries, including lighting, RF/ microwave and power electronics, but manufacturing limitations have hindered the widespread adoption of GaN for modern power electronics," said Shawn Thomas, vice president of Marketing & Business Development at Atomera. "This user project with Sandia Labs will allow Atomera to fabricate devices and collect data to validate the mechanical and electrical benefits of MST-enhanced GaN on Si."

Managing stress is the most important aspect of growing thick GaN epi on Si. Commercially available GaN on Si power electronics (PE) devices are currently limited to a ~650V rating due to the maximum epi thickness (and thus breakdown voltage) that can be grown on Si without excessive wafer curvature, micro-cracking or poor yield. MST can improve the growth of GaN epitaxy on Si substrates by relieving biaxial tensile stress.

## UK announces sustainable electronics centre

Four year project involves universities of Glasgow, Edinburgh, and Heriot-Watt with the Compound Semiconductor Catapult in Scotland

A NEW £5.5 million initiative aims to establish Scotland's Central Belt as a leader in sustainable electronics manufacturing and design.

The University of Glasgow will lead and coordinate the four-year project in collaboration with the University of Edinburgh, Heriot-Watt University, and The Compound Semiconductor Catapult in Scotland.

The Responsible Electronics and Circular Technologies Centre (REACT) is one of five new centres announced across the UK which will share in £25M from UKRI's Accelerating the Green Economy programme.

It will drive the transition to netzero electronics, addressing both the environmental and economic challenges faced by the industry, while promoting the adoption of green technologies through collaboration between academia, industry, and policymakers.

The Compound Semiconductor Catapult in Scotland will providi access to cutting-edge equipment and world-class expertise to support start-ups, SMEs, large organisations, and academia in advancing compound semiconductor technology integration. The electronics industry is primarily driven by technical and economic considerations, often neglecting sustainability principles.

This has led to significant challenges, including large amounts of Waste Electrical and Electronic Equipment (WEEE), high emissions across the supply chain, and widespread use of Critical Raw Materials (CRMs) such as gold, palladium, and indium—materials with limited reserves.

In Scotland, the electronics industry is vital to the regional economy, with over 130 companies and 10,300 employees

contributing to an annual turnover of more than £2.8bn. However, as more prominent manufacturers and buyers increasingly demand that suppliers commit to decarbonising their products, alongside growing legislative pressure, it is clear that the industry must adapt. Jeff Kettle from the University of Glasgow, who will lead and coordinate the REACT Hub, said:

"The Centre will unite leading researchers to drive the industry's transition toward a net-zero economy. Its primary focus will be developing solutions to reduce electronic waste, minimise reliance on critical raw materials (CRMs), and reduce carbon footprints."

The REACT team brings extensive expertise across various areas, including electronic materials, design, manufacturing, and assembly, environmental impact, supply chain management, and business modelling. Bing Xu of Heriot-Watt University said: "REACT will leverage its partnerships to translate research into practical applications, boosting both the region's and the UK's global competitiveness in the sector."

REACT will collaborate with SMEs in the region to develop demonstrators and market-led solutions and provide skills training.

Jason Love of the University of Edinburgh said: "REACT will bring together industrial partners as well as the supply chain of companies and proactively communicate to the wider public, driving change at a governmental level."

REACT's work will offer key benefits, including reductions in e-waste, improved energy efficiency, and cost savings by adopting greener manufacturing processes. Additionally, REACT will play a crucial role in

fostering public-private partnerships to drive these innovations, focusing on cocreation, outreach, and advocacy.

Through conferences, workshops, and applied research projects, the centre aims to reshape the electronics industry in Scotland's Central Belt, transforming it into a sustainability model for the global market.

The University of Glasgow is also playing a key role in the Centre for Net-Zero High Density Buildings, another centre supported by the Accelerating the Green Economy funding.

Gioia Falcone of the University's James Watt School of Engineering will lead the University's contribution to the centre, which is setting out to investigate how densely-populated urban areas can be made more energy-efficient. The University of Glasgow-led centre has received £4.5m from UKRI, with a further £1.1m in support from industry, education, the public sector and the community.

The programme is part of UKRI's Building a Green Future strategic theme, which aims to accelerate the green economy by supporting research and innovation that unlocks solutions essential to achieving net zero in the UK by 2050.

#### **INDUSTRY NEWS**

# 'All-GO-HEMT' to develop β-gallium oxide heterostructures

€2 million German-funded project aims to increase in efficiency in power electronics

A €2 MILLION German-funded project called All-GO-HEMT aims to increase in efficiency in power electronics and make a significant contribution to sustainable energy generation. Led by Andreas Fiedler (pictured above) of the Leibniz-Institut für Kristallzüchtung (IKZ), the project aims to develop modulation-doped  $\beta$ -(Al<sub>x</sub>Ga<sub>1-x</sub>)<sub>2</sub>O<sub>3</sub>/Ga<sub>2</sub>O<sub>3</sub> heterostructures that exhibit high electron mobility.

Compared to established materials such as silicon, GaN and SiC, Ga<sub>2</sub>O<sub>3</sub> offers potential for increasing efficiency that has not yet been fully exploited. "We believe that the development of more efficient materials can make a significant contribution to the energy transition and enable the industry to successfully master the challenges of the future," explains Fiedler.

Even though power electronics based on  $Ga_2O_3$  promise to be more efficient, the material is inferior to established materials in terms of charge carrier mobility. "Gallium oxide behaves to the established materials in the same way as ten metres of dirt road to one

kilometre of freeway.

Due to the shorter distance, your car consumes less, and despite the lower speed, you reach your destination faster - all thanks to a more compact design," explains Fiedler. The central aim of the project is to overcome the material limitation of  $Ga_2O_3$  in terms of charge carrier mobility with the help of the innovative design of an aluminium-alloyed heterostructure and thus eliminate this disadvantage.

Fiedler emphasises: "We are convinced that the efficiency of power electronics can be significantly increased through a combination of a more compact design and higher charge carrier mobility in our newly developed materials." Another goal of All-GO-HEMT is to create a reliable material basis of Ga<sub>2</sub>O<sub>3</sub> and the newly developed alloy with aluminum of the highest crystalline quality for research and industry.

This basis is necessary because the development of high-performance devices with compact design and optimised manufacturing processes is currently limited by the insufficient availability of high-quality material.

The project partner Ferdinand-Braun Institut (FBH) will use this material basis to develop new prototypes for power electronic devices. These prototypes will then be tested by ZF Friedrichshafen AG, the industrial mentor, for their suitability for industrial application.

In addition, the entire value chain, from crystal growth to the finished device, will be analysed by the industrial mentors Aixtron SE and Siltronic AG in order to quantify and evaluate the economic and ecological benefits of this technology at an early stage.

## SYNERGIES THROUGH EXPERIENCE

In collaboration with Heraeus Electronic's Engineering Services and VisIC we are actively involved in the development and testing of GaN module prototypes in accordance with the automotive standard AQG 324. Leverage our expertise in the GaN sector with our small scale, vacuum assisted sintering system SIN 20 for extraordinarily reliable and highly thermally conductive bonds.

Together, we are driving innovation in the EV market.

**PiNK**

PINK GmbH Thermosysteme · Am Kessler 6 · 97877 Wertheim · sales@pink.de · pink.de

## Infineon unveils world's thinnest silicon power wafer

Company first to master handling and processing of ultra-thin  $20 \mu m$  power semiconductor wafers

INFINEON has announced a breakthrough in handling and processing the thinnest silicon power wafers, with a thickness of only  $20\mu ms$  and a diameter of 300mm, in a high-scale semiconductor fab.

According to the company, this innovation will significantly help increase energy efficiency, power density and reliability in power conversion solutions for applications in Al data centres as well as consumer, motor control and computing applications. Halving the thickness of a wafer reduces the wafer's substrate resistance by 50 percent, reducing power loss by more than 15 percent in power systems, compared to solutions based on conventional silicon wafers.

For high-end Al server applications, where growing energy demand is driven by higher current levels, this is particularly important in power conversion: Here voltages have to be reduced from 230 V to a processor voltage below 1.8 V. The ultra-thin wafer technology boosts the vertical power delivery design, which is based on vertical Trench MOSFET technology and allows a very close connection to the Al chip processor, thus reducing power loss and enhancing overall efficiency.

"The new ultra-thin wafer technology drives our ambition to power different Al server configurations from grid to core in the most energy efficient way," said Adam White, division president Power & Sensor Systems at Infineon. "As energy demand for Al data centres is rising significantly, energy efficiency gains more and more importance. For Infineon, this is a fast-growing business opportunity. With mid-double-digit growth rates, we expect our Al business to reach one billion euros within the next two years."

To overcome the technical hurdles in reducing wafer thickness to the order of  $20\mu m$ , Infineon engineers had to establish an innovative and unique wafer grinding approach, since the metal stack that holds the chip on the wafer is thicker than  $20\mu m$ . This significantly influences handling and processing the backside of the thin wafer. Additionally, technical and production-related challenges like wafer bow and wafer separation have a

major impact on the backend assembly processes ensuring the stability and first-class robustness of the wafers. The technology has been qualified and applied in Infineon's Integrated Smart Power Stages (DC-DC converter) which have already been delivered to first customers.

With the current ramp up of the ultra-thin wafer technology Infineon expects a replacement of the existing conventional wafer technology for low voltage power converters within the next three to four years.

## Mitsubishi to invest \$64m in new power module plant

MITSUBISHI ELECTRIC will invest approximately \$64m (10 billion yen) to construct a new facility for the assembly and inspection of power semiconductor modules at its Power Device Works in Fukuoka Prefecture, Japan.

The plant, which was originally announced on March 14, 2023, is scheduled to begin operations in October 2026.

As the primary facility for assembling and inspecting power semiconductor modules, the plant will consolidate previously dispersed assembly and inspection production lines within the site to streamline production, from the incoming of components through manufacturing and final shipment.

New systems will be implemented to automate the management of manufacturing processes and the transportation of products for improved productivity. In addition, the company's integrated system covering everything from design, development and production technology verification to manufacturing will be strengthened to enhance product development.

Mitsubishi Electric says it expects the new plant to support its rapid and stable supply of products to meet market needs in response to the anticipated increases in demand for power semiconductors.

### **INDUSTRY NEWS**

## US DOE announces \$481.5m loan to SK Siltron CCS

#### Company to use funds to expand manufacturing of SiC wafers for EVs

AS PART of the Biden-Harris Administration's Investing in America agenda, the Department of Energy (DOE) has announced a \$544 million loan to SK Siltron CCS, LLC to expand American manufacturing of high-quality SiC wafers for electric vehicle (EV) power electronics.

The project — located at SK Siltron CSS facility in Bay City, Michigan — is expected to be among the top-five manufacturers of SiC wafers globally, boosting America's manufacturing competitiveness.

This project is forecast to create up to 200 construction jobs in the buildout phase and up to 200 skilled, good-paying operations jobs at full production.

SK Siltron CSS sells directly to device manufacturers which make power electronics used across many industries, not just EVs and high-speed EV charging. Market demand is currently being driven by

transportation, next generation cellular (i.e., 5G), artificial intelligence and cloud computing end uses. SiC is also becoming increasingly common in other mid to high voltage applications such as solar photovoltaic, inverters and DC converters, and industrial chargers and adapters. The loan is offered through LPO's Advanced Technology Vehicles Manufacturing (ATVM) Loan Program, which supports domestic manufacturing of advanced technology vehicles, qualifying components, and materials that improve fuel economy.

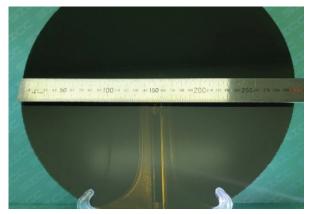

## SICC shows first 300mm SiC wafer

AT ELECTRONICA 2024, Chinese SiC wafer company SICC exhibited what is thought be the first 300mm N-type SiC substrate.

SICC already makes 150mm and 200mm N-type conductive SiC, and high-purity semi-insulating substrates. The company has also developed largesize P-type SiC substrates.

But the 300mm N-type substrate, it says, is an industry breakthrough that highlights SICC's ability to push the boundaries of semiconductor technology.

For example, in its 200mm conductive 4H-SiC single crystal substrates, SICC says it has achieved near-zero threading screw dislocation (TSD) and extremely low basal plane dislocation (BPD) densities, which significantly enhances yields.

For its high-purity semi-insulating SiC substrates, SICC claims zero micro pipe density. (Micro pipes are SiC crystal defects that can cause electronic devices to short circuit and fail).

The company puts this success down to the ability to precisely control the crystal growth process, ensuring

consistent wafer quality.. The company, which has headquarters in Jinan, is currently further expanding its 200mm SiC wafer manufacturing capacity at its Shanghai plant.Semiconductor value per car to reach \$1k by 2029

# Si, SiC & GaN 'Power ahead' in Power Devices

#### **Frontside processes**

- Ohmic contacts

- Surface protection for SiC

- Trench filling including high aspect ratio

- Sputtered AIN seed layer for MOCVD GaN growth

- Solderable top metal stack

#### **Backside processes**

- Etching / surface cleaning

- Ohmic contacts

- Thick metal stack

Choosing Evatec's CLUSTERLINE<sup>®</sup> family of 200 or 300mm tools is a sure way to "power ahead" of the competition. Our thin film process know-how on Silicon and WBG materials ensures the best device performance while our wafer handling and stress management for thin wafers delivers the best production yields.

Visit **evatecnet.com/markets/power-devices** to find out how you can power ahead in your own production or contact your local Evatec Office at **evatecnet.com/about-us/sales-service**

SEMICONDUCTOR & ADVANCED PACKAGING • COMPOUND & PHOTONICS • THE THIN FILM POWERHOUSE www.evatecnet.com

### SiC MOSFETs

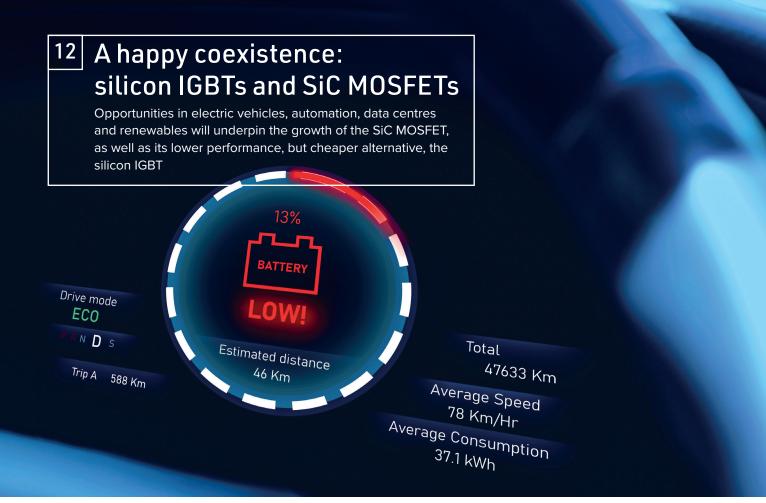

# A happy coexistence: silicon IGBTs and SiC MOSFETs

Opportunities in electric vehicles, automation, data centres and renewables will underpin the growth of the SiC MOSFET, as well as its lower performance, but cheaper alternative, the silicon IGBT

#### BY CALLUM MIDDLETON AND PAUL PICKERING FROM OMDIA

THOSE OF YOU owning vehicles powered by a battery will know that, in many ways, the driving experience is no different from that provided by a car consuming petrol or diesel. But there are some notable differences.

One of the first of these you'll encounter is that rather than having a traditional fuel gauge, you'll get a figure for the estimated range. And unfortunately, it will not take you long to discover that what this figure lacks in accuracy, it makes up for in optimism.

Driving range often tops the list of considerations of those looking to purchase an electric vehicle in an ever more competitive marketplace. Helping to maximise this range is the SiC MOSFET, which draws on its superior efficiency over the silicon IGBT. Having the upper hand on this front is the primary justification for OEMs to opt for the SiC solution. While the efficiency of the SiC MOSFET is a major selling point, that's not the only benefit it offers over the silicon IGBT. Additional merits are a doubling of thermal conductivity and a far higher switching frequency, which allows the use of smaller passives and cheaper systems. It's also worth noting that many of the advantages of SiC are greater at higher voltages, allowing the wider bandgap transistor to shine in higher-voltage systems, such as 800 V electric vehicles and 1500 V photovoltaic inverters. The only significant downside of the SiC MOSFET is that it's pricey, but that concern is diminishing, as wafer sizes expand and material prices fall. So, is there much of a future for the silicon IGBT?

Well, one should not dismiss the importance of its lower price. The best engineering solution is not always the best solution, and there is no reason to expect the SiC MOSFET to ever reach price parity with the silicon IGBT, due to its higher inherent costs that are associated with the manufacturing process. While turning to SiC can drive down system costs, offsetting some of the difference in die cost, this can be a challenging proposition to make, and it is likely that users will always face a choice between performance and cost.

In the traction inverter market, after weighing up the pros and cons, many automotive OEMs and tier ones are deciding to deploy SiC. Tesla introduced SiC to this sector to distinguish its vehicles from its competitors, and in the process became the leading BEV manufacturer in the world. Now many automotive companies are following suit in an attempt to close the gap. This is driving a ramp in SiC device sales, which climbed by 75 percent in 2023. However, today's BEVs are primarily in the 'luxury' and 'midrange' categories, where consumers are willing to pay a little more for improved performance. As the BEV market expands, makers of these vehicles will have to penetrate the economy end of the market, where price matters much more. For customers who tend to use their vehicles for short journeys in urban settings, cars fitted with IGBTs will appeal.

It's quite feasible that even the more expensive vehicles will not solely use SiC. The Tesla model that pioneered SiC featured 48 MOSFETs. But in March 2023, that trailblazer of the BEV surprised many when it announced it would be trimming usage of these wide bandgap chips by 75 percent. Arguably, this decision should not have raised that many eyebrows, as one should expect that innovations in device design and inverter design would lead to a reduction from 48 MOSFETs, alongside a possible move to a blend of SiC MOSFETs and silicon IGBTs.

As already mentioned, BEVs are renowned for their optimistic range. This is partly due to difficulties in estimating this critical distance, which is influenced by numerous factors, including driving style and ambient temperature. The mission profile of the traction inverter within a BEV can vary greatly depending on where it is located, who the owner is, and even the day of the week. Due to these considerations, what's needed is a varied internal solution that allows the system to operate in the most efficient manner, irrespective of what is asked of it, without over-engineering. It remains to be seen whether this blended solution comes from vehicle designers deploying multiple inverters within a vehicle, or the use of power modules containing both SiC MOSFETs and silicon IGBTs.

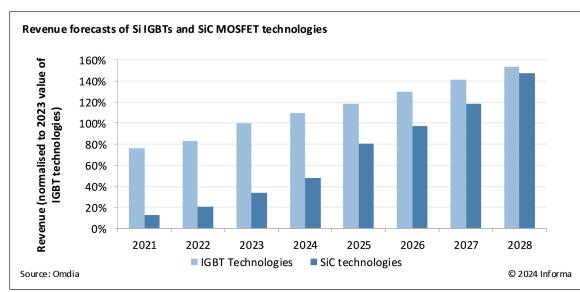

When considering these factors, it is clear that the rise of the electric vehicle provides a great opportunity for both SiC MOSFETs and silicon IGBTs. At Omdia, we are forecasting a compound annual growth rate of 32.6 percent for SiC device revenue between 2023 and 2028, and over that time frame an equivalent figure of 10.8 percent for power modules based on the silicon IGBT. Our forecast growth in SiC is eye-catching, justifying the level of investment in this technology, while the growth in the silicon IGBT offers a compelling reason to continue investing in device research and development to help companies claim more of this growing pie.

Outside the automotive sector, many of the same trade-offs apply. However, the absence of a key performance metric, such as range, makes it harder to justify a transition to SiC. We are living in a time of high energy costs and increased automation, factors that encourage investment in motor drives and grid infrastructure – and present opportunities for both SiC MOSFETs and silicon IGBTs. As SiC capacity expands, this should trim costs, but capacity is closely tied to the automotive sector. This tie-in may encourage equipment manufacturers in other sectors to stick with silicon until there's greater maturity in the SiC industry. Whilst improved efficiency is a big benefit at a time of increased energy costs, it still may not be enough to offset the extra chip cost. Therefore, it is most likely that the greatest penetration will come in applications where space savings are highly desirable, such as microinverters for photovoltaic systems, or power supplies for data centres.

There's no question that SiC growth is a huge opportunity for the power semiconductor industry, but it's not easy to see MOSFETs getting to the price of silicon IGBTs. Instead, they offer another option for the power electronics engineer, who has the opportunity to use the SiC MOSFET and the silicon IGBT concurrently. Thanks to overarching growth trends of electrification, electric vehicles, and renewable energy, there is the potential for a significant growth in sales of both device types; and industry should continue to develop IGBT technologies to aid the green transition.

> The historical and forecast revenue for the silicon IGBT and the SiC MOSFET. Data has been normalised to the 2023 revenue of IGBT technologies.

# Combining a CMOS driver and a GaN power switch on 300 mm silicon

Intel's DrGaN technology, involving the monolithic integration of GaN and silicon CMOS on 300 mm wafers, will support power delivery in tomorrow's data infrastructure and communication networks

#### BY HAN WUI THEN FROM INTEL CORPORATION

THE NUMBER of power-hungry applications involving massive computation is on the rise, due to growth in datacenters, AI, wafer-scale compute, supercomputers and 5G/6G networks. Due to this, there is a need for the ICs that power these applications to combine a superior level of performance with greater energy efficiency and higher densities.

Our team at Intel Technology Research has anticipated these trends and has already devoted many years to addressing them. Back in 2019 we developed the industry's first enhancement-mode (E-mode) GaN transistor, enabled by high- $\kappa$  dielectric metal gate technology; and we pioneered monolithic three-dimensional stacking integration of GaN and silicon transistor technology, all using 300 mm silicon wafers. During these efforts, we pursued the use of GaN because this high-mobility wide-bandgap semiconductor can operate at high frequencies and high power densities. These assets make this particular technology the best-in-class for power delivery and RF applications. We have focused on combining the advantages of GaN and silicon CMOS

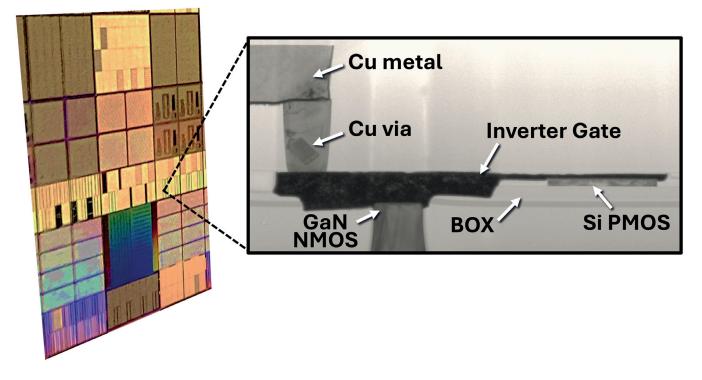

Above. Intel's CMOS DrGaN Technology on a single chip to realise best-in-class performance, high efficiency and high density (small form-factor), as well as to integrate functionalities beyond what is possible with an *n*-channel only GaN technology.

Recently, we have taken our research a step further, employing an improved version of this process. At the most recent *International Electron Devices Meeting*, held last December in San Francisco, we unveiled what we refer to as 'DrGaN': it is a largescale integrated CMOS driver-GaN power switch technology, realised on a 300 mm GaN-on-silicon wafer.

#### A single die solution

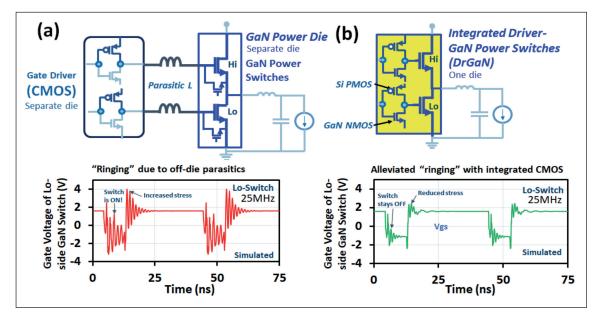

Our DrGaN technology breaks new ground. It is the first time that a GaN power transistor technology has been enhanced with an integrated CMOS driver on the same die. In comparison, other state-of-theart GaN technologies of today employ a separate CMOS driver die that accompanies a GaN die, with the driver signal from the CMOS die routed through the package to the GaN die. This routing through the package incurs parasitic inductance

> Figure 1. (a) A typical state-of-the-art solution involves a co-packaged two-die implementation: a separate CMOS driver die and power GaN die, where the driver signal from the CMOS die is routed through the package (represented by parasitic inductance, L) to the power GaN die. One downside of this approach is that it causes extreme ringing, visible in the simulation (inset). (b) A new approach facilitated by DrGaN, with a fully integrated CMOS driver on the power GaN die, enables a low-inductance path from the CMOS driver output to the GaN power switches. This technology suppresses the large ringing in (a).

(see Figure 1(a)), which limits performance, with extreme 'ringing' at high switching speeds (this is visible in the simulation trace, shown in the inset of Figure 1(a)).

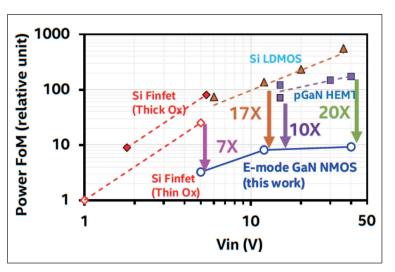

This ringing is detrimental, limiting the switching speed and the performance, in terms of the conversion efficiency. Due to this ringing, it's not possible to exploit a key advantage of the GaN transistor, which can switch far faster than its silicon sibling, evidenced by a figure-of-merit around 10-20 times higher (see Figure 2).

In addition, pairing a GaN die with a CMOS die leads to voltage 'overshoot'. Two issues result from this: an increase in the stress subjected to both the CMOS and GaN transistors; and inadvertent activation of the GaN power switch during the off-interval.

There is no doubt that a two-die solution fails to realise the full potential of the figure-of-merit gains offered by GaN. Overcoming this limitation is our DrGaN technology. By offering a fully integrated CMOS driver on the GaN die, our approach enables the realisation of a low-inductance path from the driver output to the GaN power gate, thereby suppressing the substantial ringing. The upshot is higher frequency operation, alongside a higher efficiency and improved reliability. The higher switching frequencies are cherished, as they open the door to smaller passives, such as smaller inductors. Shrinking the size of the power delivery unit follows, enabling higher power densities - that is, power delivery occupies less spaceper-unit-power delivered, while maintaining high

performance. Note that what we have just described is an instance of Moore's law in action for the power delivery solutions provided by DrGaN technology.

Our company has a long and strong track record in driver and MOSFET integration. Back in 2004 we introduced 'DrMOS' – driver and MOSFET integration for the silicon MOSFET. Our motivation for this breakthrough came from the need to keep pace with increasing microprocessor power density

▶ Figure 2. Benchmarking the power figure-of-merit ( $R_{ON}xQ_{GG}$ ) of the GaN transistor of this work shows: a performance that's around a 20-fold better than the *p*GaN HEMT and around a 30-fold better than silicon LDMOS at 40 V; a 10-17-fold better performance than silicon LDMOS and a *p*GaN HEMT at 12-15 V, and 7-fold better performance than a silicon finFET at 5 V.

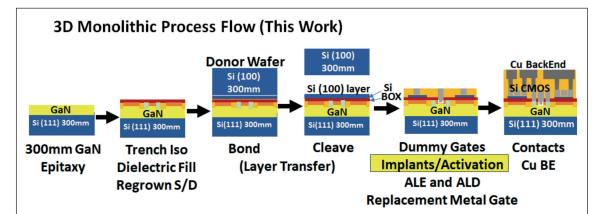

► Figure 3. The process flow used for DrGaN technology, which involves threedimensional monolithic integration of GaN and silicon CMOS by layer transfer on 300 mm silicon wafers.

and efficiency demands associated with the leading PCs and laptops of that era. Since then, DrMOS has become the gold standard for point-of-load power delivery solutions for CPUs and GPUs.

One of the trailblazers for GaN is Navitas Semiconductor, which introduced integrated enhancement-depletion (E-D) mode *n*-channel drivers for high-voltage GaN power ICs. This particular architecture has been adopted because standard GaN processes cannot produce *p*-channel or CMOS devices.

The E-D mode driver is suitable for high-voltage scenarios. However, this form of driver is far too leaky – and thus not efficient enough – for lower voltage, point-of-load applications, such as those below 48 V. Turning to CMOS addresses this, while enabling efficient, high-density integration of other functionalities, including control logic and telemetry circuitries, such as current and temperature sensors. It is a broad range of features, challenging to realise with a standard GaN *n*-channel only process.

With our DrGaN technology, we accomplish the monolithic integration of GaN and silicon CMOS with a new process flow (see Figure 3), using a technique called layer transfer. We begin by bonding a donor silicon wafer to a GaN wafer. Upon separation, the silicon donor wafer cleaves along a weakened crystal plane throughout the wafer, to leave a thin layer of silicon channel material bonded onto the GaN wafer.

Our latest approach involves introducing implants and high-temperature activation steps, for the fabrication of the silicon CMOS transistors, prior to formation of the high- $\kappa$  gate dielectric of the GaN transistors. From there onwards, we only perform low-temperature steps. That's critical, because high temperatures threaten to degrade the quality and reliability of the high- $\kappa$  gate dielectric used for GaN transistors. By arranging our process flow in such a manner, this truly gate-last process overcomes a major hurdle in three-dimensional monolithic integration of GaN NMOS and silicon CMOS transistors.

#### **Proven superiority**

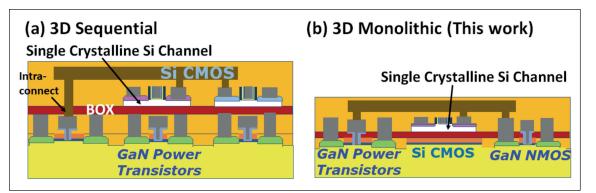

The benefits of our latest process are seen in the measurements of silicon PMOS transistors fabricated by both approaches (see Figure 4). Previously, PMOS transistors were fabricated sequential, only after the GaN transistors were completed. This sequence exposed the gate dielectric of the GaN transistor to the high-temperature steps of silicon transistor processing.

Another downside of our previous approach is that this sequential process flow employed intra-connects to establish electrical connectivity between the silicon and GaN transistors. As well

> Figure 4. (a) Intel's prior work involved the three-dimensional sequential monolithic integration of GaN and silicon CMOS by a layer transfer process, with silicon PMOS/NMOS transistors fabricated after completing fabrication of the GaN transistors. (b) For Intel's latest work, DrGaN technology, GaN and silicon PMOS/NMOS transistors are fabricated in such a way that the high-temperature activation steps are completed before the deposition of the gate dielectric of the GaN transistors.

as necessitating additional fabrication steps and masks, these intra-connects added path resistance when accessing the underlying GaN transistors. In contrast, our latest process for producing GaN and silicon CMOS transistors leads to a shared backend copper interconnect stack, eliminating the need for additional intra-connects and masks.

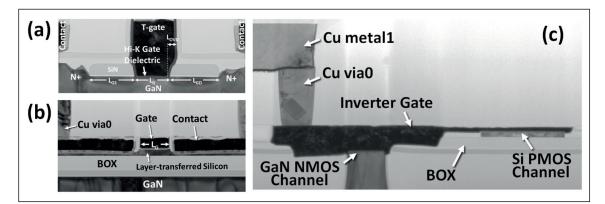

To inspect our completed devices – the GaN transistor, silicon PMOS transistor and hybrid GaN/silicon CMOS inverter – we have used a transmission electron microscope (see Figure 5). These devices, fabricated with our latest process on a 300 mm wafer, are used to construct the DrGaN.

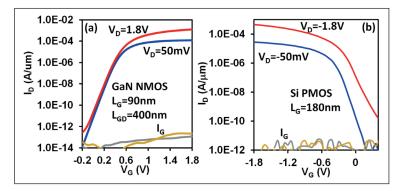

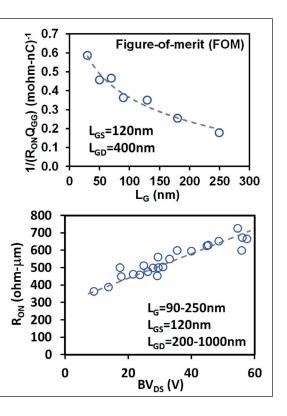

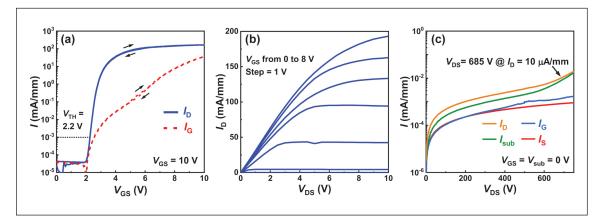

We have undertaken a number of electrical measurements on our devices. Transfer currentvoltage (I-V) characteristics for a typical GaN transistor with a channel length of 90 nm are shown in Figure 6 (a). Strengths of this device include an excellent on-off ratio of around 10<sup>10</sup>, a low onresistance of 422  $\Omega$  µm, a high drain-current drive of 1.2 mA µm<sup>-1</sup>, and gate leakage below 1 pA µm<sup>-1</sup>. Equally impressive are the I-V characteristics of our silicon PMOS transistor, which has a channel length of 180 nm (see Figure 6(b)). In this case the on-off ratio is around 10<sup>6</sup>, the on-resistance 1780  $\Omega$   $\mu$ m, the drain current drive 0.43 mA  $\mu$ m<sup>-1</sup>, and the gate leakage around 1 pA  $\mu$ m<sup>-1</sup>. Note that these are some of the best numbers ever reported for GaN and silicon PMOS transistors at comparable channel lengths. In particular, the GaN transistors show a best-in-class figure-of-merit for the reciprocal of the product of on-resistance and gate charge of  $0.59\ m\Omega^{\text{-1}}\ nC^{\text{-1}},$  measured from the shortest channel length of 30 nm (see Figure 7).

Through judicious selection of gate-to-drain separation, which can be varied from 200 nm to 1000 nm, we can obtain a breakdown voltage of up to around 60 V for our GaN transistor (see Figure 7). This enables us to target a range of use cases and application voltages.

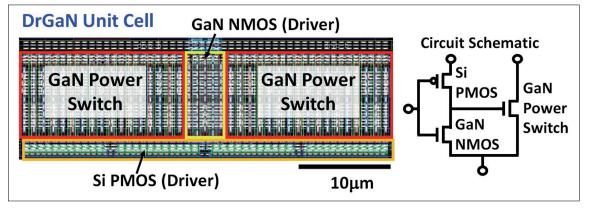

Our DrGaN technology enables the construction of a large-scale IC from a massive array of repeated unit cells. Each of these cells, 40  $\mu$ m by 10  $\mu$ m in size, consists of four blocks: a silicon PMOS driver block, a GaN NMOS driver block, and two symmetrical GaN power switch blocks. The layout for these cells is

outlined in Figure 8, along with a circuit schematic that illustrates the electrical connections between the silicon PMOS, GaN NMOS and GaN power switch transistors.

The DrGaN unit cell is arrayed over an area of 0.8 mm<sup>2</sup> to realise a desired total width of 421.1 mm for the GaN power switch, 49.54 mm for the GaN NMOS (driver) and 27.19 mm for the silicon PMOS (driver). The aggregate total width of all the transistors is 497.83 mm.

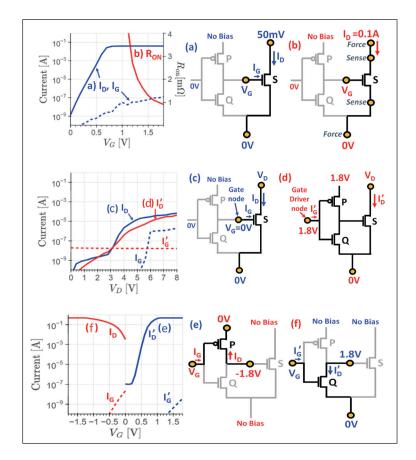

To demonstrate the full functionality of this 497.83 mm wide DrGaN, we have measured its steady-state electrical characteristics. To record the transfer characteristics of the GaN power switch S, which has a total width of 421.1 mm, in DrGaN, we use a probe to apply a bias voltage to the gate node of this switch (see Figure 9(a)). For this GaN power switch we have measured an on-resistance of  $1 \text{ m}\Omega$  and determined leakage characteristics, with the switch turned off by applying a bias voltage of either (c) 0 V directly at the gate node of S; or (d) 1.8 V at the gate driver node of P and Q. Drain and gate leakage currents are well below 0.1 mA for the 421.1 mm-wide power switch. Also shown in Figure 9 are the transfer characteristics of silicon PMOS, P (width of 27.19 mm) (e) and the leakage characteristics of GaN NMOS, Q (width of 49.54 mm), in the gate driver (f).

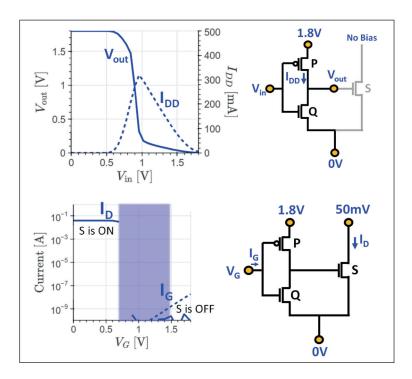

We have also assessed the inverting characteristics of the combined GaN-silicon CMOS driver

Figure 6. The current-voltage (I-V) characteristics of (a) GaN transistor, and a (b) silicon PMOS transistor produced by the DrGaN process.

► Figure 7. (a) The figureof-merit  $1/(R_{ON}Q_{GG})$ for the GaN transistors produced by the DrGaN process, for channel lengths, L<sub>c</sub>, ranging from 30 nm to 250 nm. (b) The onresistance,  $R_{oN}$ , and breakdown voltage, BV<sub>DS</sub>, for GaN transistors produced by this process. Gate-to-drain lengths, L<sub>gp</sub>, are between 200 nm and 1000 nm.

(P and Q). Figure 10 shows the steady-state transfer characteristics with DrGaN. Modulation of the GaN power switch, S, is driven by the integrated GaN-silicon CMOS driver (P and Q).

This final measurement completes full functionality testing of our DrGaN technology, which has multiple merits. We view our realisation of a large-scale, 497.83 mm-wide DrGaN is an important milestone towards demonstrating the viability of our 300 mm GaN-on-silicon process with three-dimensional monolithically integrated GaN and silicon CMOS, brought together by layer transfer. Our efforts break new ground, showing for the first time that this process can produce large-scale integrated circuits comprising GaN and silicon CMOS transistors on the same chip.

Our development of DrGaN demonstrates that the monolithic three-dimensional integration of GaN NMOS and silicon PMOS transistors is a powerful way to integrate two dissimilar best-in-class semiconductor technologies on the same silicon and deliver optimal performance, improved density, and more functionalities. Our accomplishments include the industry's first CMOS DrGaN technology fabricated in 300 mm GaN-on-silicon technology. Through the use of enhancement-mode high- $\kappa$  dielectric GaN MOSHEMT technology for the GaN transistor, our DrGaN ICs set new benchmarks for performance and leakage. Another significant advance is the new improved truly gate-last process flow, resolving a major hurdle in three-dimensional monolithic integration of GaN NMOS and silicon CMOS transistors.

Thanks to our efforts, there has been a significant advance in 300 mm GaN-on-silicon technology. But that's far from all that the demonstration of DrGaN has accomplished. This technology holds the key to tomorrow's efficient, highly integrated, highdensity point-of-load power delivery solutions for future high-performance compute in datacenters, AI and 5G/6G networks. DrGaN is clearly destined to deliver many great things.

- The author, Han Wui Then, would like to thank team members and contributors:

- M. Radosavljevic, S. Bader, A. Zubair, H. Vora,

- N. Nair, P. Koirala, M. Beumer, P. Nordeen,

- A. Vyatskikh, T. Hoff, J. Peck, R. Nahm,

- T. Michaelos, E. Khora, R. Jordan, C. Hoffman,

- N. Franco, A. Oni, S. Beach, D. Garg, D. Frolov, A. Latorre-rev. A. Mitaenko, J. Ranaaswamv.

- S. Sarkar, S. Ahmed, V. Rayappa, H. Chiu,

- A. Hubert, S. Brophy, N. Arefin, N. Desai,

- H. Krishnamurthy, J. Yu, K. Ravichandran, and P. Fischer.

> Figure 8. The layout of a 40  $\mu$ m by 10  $\mu$ m DrGaN unit cell consisting of silicon PMOS and GaN NMOS driver blocks, and two GaN power switch transistor blocks. The inset shows the circuit schematic of the electrical connections between the silicon PMOS, GaN NMOS and GaN power switch transistors. In the driver block, the silicon PMOS has a channel length, L<sub>g</sub>, of 180 nm, and a total width per unit cell of 19.76  $\mu$ m, while the GaN NMOS has the same channel length of 180 nm and total width-per-unit-cell of 36  $\mu$ m. The GaN power switch transistors have a similar channel length of 180 nm, but a larger total width-per-unit-cell of 306  $\mu$ m, and a longer gate-to-drain length, L<sub>gp</sub>, of 400 nm, in order to withstand a higher operating voltage.

WURTH ELEKTRONIK MORE THAN YOU EXPECT

# ULTRA LOW LOSSES WE-MXGI

With the WE-MXGI Würth Elektronik offers the newest molded power inductor series. It combines an innovative iron alloy material that provides high permability for lowest R<sub>DC</sub> values combined with an optimized wire geometry.

Ready to Design-In? Take advantage of personal technical support and free samples ex-stock. **www.we-online.com/WE-MXGI**

### WE are here for you!

Join our free webinars on: www.we-online.com/webinars

#### **Highlights**

- Extremely high power density

- Ultra low R<sub>DC</sub> values and AC losses

- Magnetically shielded

- Optimized for high switching frequencies beyond 1 MHz

► Figure 9. (Top) the transfer characteristics of the GaN power switch S with a total width of 421.1 mm in DrGaN, demonstrating transistor operation. The normalized  $R_{DSON}$  is 0.8 mΩ mm<sup>2</sup>. (Middle) The leakage characteristics,  $I_D - I_G - V_D$  and  $I_D' - I_G' - V_D$  of the GaN power switch S in DrGaN, in the off-state accomplished by either applying a bias voltage,  $V_G$ , of (c) 0 V directly at the gate node of S; or (d) 1.8 V at the gate driver node of P and Q. (Bottom) The I-V transfer characteristics of the (e) silicon PMOS, P, and (f) GaN NMOS, Q, in the gate driver of DrGaN.

#### **FURTHER READING / REFERENCE**

- H.W. Then et al. "DrGaN: an Integrated CMOS Driver-GaN Power Switch Technology on 300mm GaN-on-Si with E-mode GaN MOSHEMT and 3D Monolithic `Si PMOS," IEDM 9.7.1-9.7.4. (2023)

- H.W. Then, "Stacking GaN and Silicon Transistors on 300 mm Silicon", Compound Semiconductor, May 2020.

- H.W. Then et al. "3D heterogeneous integration of high performance high-K metal gate GaN NMOS and Si PMOS transistors on 300mm high-resistivity Si substrate for energy-efficient and compact power delivery, RF (5G and beyond) and SoC applications," IEDM 17.3.1-17.3.4 (2019)

- N. Desai et al. "A 32A 5V-Input, 94.2% Peak Efficiency High-Frequency Power Converter Module Featuring Package-Integrated Low-Voltage GaN NMOS Power Transistors," 2021 Symposium on VLSI Circuits pp. 1-2 (2021)

- H. W. Then et al., "Scaled Submicron Field-Plated Enhancement Mode High-K Gallium Nitride Transistors on 300mm Si(111) Wafer with Power FoM (R<sub>on</sub> xQ<sub>GG</sub>) of 3.1 mohm-nC at 40V and f<sub>r</sub>/f<sub>MAX</sub> of 130/680GHz," IEDM 35.1.1-35.1.4 (2022)

- G.Moore, "Cramming more components onto integrated circuits", Electronics 38 114 (1965) Intel, DrMOS Technical Specifications Rev.1.0, Nov 2004.

- N. Fichtenbaum, "GaN Integrated Circuits for Power Electronics," 2019 Device Research Conference pp. 1-26 (2019)

- H. W. Then et al. "Gallium Nitride and Silicon Transistors on 300 mm Silicon Wafers

Enabled by 3-D Monolithic Heterogeneous Integration," IEEE Trans. Electron Devices

67 5306 (2020)

> Figure 10. (Top) Transfer characteristics,  $V_{out}-V_{in}$ , of the GaN-silicon CMOS driver, P and Q, in DrGaN technology. (Bottom) The steady-state transfer characteristics of DrGaN. The switching of the GaN power switch, S, is driven by the integrated GaN-silicon CMOS driver (P and Q). Turning on involves a driver pull-up to a V<sub>g</sub> rail of 1.8 V, and turning off involves a driver pull-down to a V<sub>g</sub> rail of 0 V.

dsPIC33A 200 MHz 32-bit CPU with FPU 10x Faster Analog

## **Next Generation dsPIC® Digital Signal Controller**

### **Driving Innovation and Precision in Real-Time Control**

Progressive real-time control systems demand enhanced optimization, greater computational efficiency and broader functionality. Microchip's latest dsPIC33A DSC tackles the complexities of executing highperformance system designs. This advanced controller boasts improved efficiency and integration capabilities, allowing for the execution of multiple functions through a single device. It facilitates the integration of code from model-based design tools with increased focus on safety and security.

microchip.com/dsPIC33A

rene output name and open internet Microchip Technology porated in the U.S.A. and other countries. All other marks are the property of their registered owners 2024 Microchip Technology Inc. All rights reserved MEC2585A-UK-09-2e

- Moderated by editor, Phil alsop, this can include 3 speakers

- Questions prepared and shared in advance

Cost: €5995

Contact: Jackie Cannon jackie.cannon@angelbc.com

# Bipolar *p*-FETs enable all-GaN power integration

Bipolar transport overcomes the inherent barriers of GaN *p*-FETs to pave the way to higher current densities

# BY MENGYUAN HUA FROM SOUTHERN UNIVERSITY OF SCIENCE AND TECHNOLOGY

GaN POWER DEVICES have many attributes. They are renowned for their exceptional switching efficiency and high power density, strengths that are driving the development of miniaturised, energysaving power systems. Thanks to a wide bandgap and stable material properties, GaN-based power devices are also capable of maintaining a good performance in challenging environments, such as extreme temperatures and irradiation conditions. And in addition to these capabilities, GaN power devices are revolutionising power systems towards higher levels of integration and intelligence. Given all this, it's of no surprise that GaN-based HEMTs have rapidly surpassed traditional silicon devices to play an indispensable role in a number of fields, ranging from consumer electronics to industrial power supplies.

However, while much progress has been made to date, there is still much more to do. In this regard, one important area for improvement is the GaN power IC - today there is a significant challenge in realising the seamless integration of power devices with low-voltage peripheral circuits. In the latest approaches to hybrid integration, the siliconbased circuits that are used for driving, sensing and protecting functions, are integrated with GaN power devices through packaging. This results in non-negligible parasitic inductance, which can lead to gate ringing, particularly during high-power fast-switching transients. Two downsides of this are a limited switching speed and a compromised system reliability. What's more, the silicon devices in these hybrid designs fail to handle extreme environments as well as GaN devices, narrowing the

application scope. Consequently, moving to an all-GaN integration strategy has much appeal, including liberation from parasitic issues and the constraints of silicon-based devices, as well as the opportunity to unleash the full potential of GaN power ICs.

There are several straightforward approaches for all-GaN integration, such as leveraging established *n*-channel device technology, resistor-transistor logic and direct-coupled FET logic. However, all these methods are impaired by excessive power consumption, due to a significant static current that diminishes the efficiency of the power IC and necessitates enhanced heat dissipation strategies.

A promising solution to effectively blocking the static current is the GaN-based complementary logic IC, incorporating both the *p*-FET and the *n*-FET. In this design, the existing *p*-GaN layer on the E-mode GaN HEMT platform is used to fabricate the *p*-FET.

The simplicity of this approach has attracted much attention, leading to efforts directed at boosting *p*-FET performance via strategies that include reducing interface trap states, downscaling the device, and engineering the gate dielectric. But even with these refinements, the current density of the *p*-FET falls far short of that of the GaN HEMT. This gap in current density between the GaN *p*-FET and its *n*-FET sibling poses a significant hurdle for progressing GaN CMOS technology.

Limiting the current density of the GaN *p*-FET is the low conductivity of the *p*-GaN layer. Due to a considerable effective mass and strong scattering, the mobility of holes is nearly two orders of magnitude lower than it is for electrons. Compounding this issue, magnesium is the only effective dopant available for *p*-type GaN. Unfortunately, it's far from an ideal dopant, being held back by a low activation ratio and a deep energy level that restricts the hole concentration in the *p*-GaN layer to  $10^{18}$  cm<sup>-3</sup>. While innovative epi-structure designs involving N-polar GaN, AIN and GaN heterostructures, superlattices, and InGaN insert layers are able to enhance hole mobility or density, these approaches are incompatible with the existing commercial p-GaN gate HEMT platform.

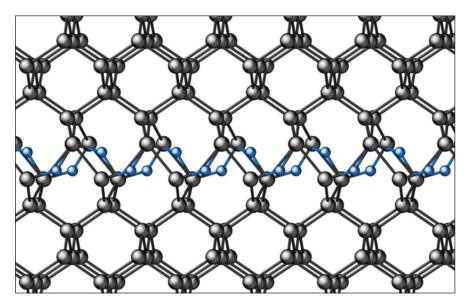

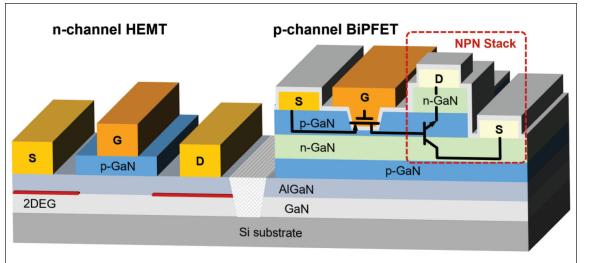

To overcome this challenge, our team at the Southern University of Science and Technology is pursuing an innovative GaN *p*-FET architecture endowed with a bipolar transportation capability (see Figure 1). This bipolar *p*-FET (BiPFET) features a conventional *p*-FET gate for maintaining *p*-type control logic, as well as an additional *n-p-n* GaN stack, which functions as a bipolar junction transistor that amplifies the current density. Operating in the on state, the *p*-channel turns on with a gate voltage below the threshold voltage. In this state, a minor hole current flows through the *p*-channel, and is injected into the base region of the *n-p-n* stack, initiating a substantial electron current. With electrons serving as majority carriers, the current density of the BiPFET is no longer confined by holes.

In addition to its remarkable conduction capability, the BiPFET inherently ensures a more stable threshold voltage and a higher drain-to-source breakdown voltage. When in the off-state, the bottom *n*-GaN region acts as a back-side field plate, extending the depletion region from the *p*-FET gate to the drain side. Thanks to this there is a more uniform electric field distribution, alleviating stress on the *p*-FET gate and improving the off-state breakdown voltage.

Another advantage of the BiPFET technology is that it is ready for integration with GaN HEMTs, thereby demonstrating outstanding compatibility and feasibility. The *n-p-n* stack can be realised through MOCVD growth, and the process flow of the BiPFET aligns well with that of the standard *p*-GaN gate HEMT. These strengths underscore the promising potential of the BiFET for the development of all-GaN ICs.

#### Demonstrating the concept

We have investigated the capability of our BiPFETs by producing these devices from a commercial

➤ Figure 1. A promising option for GaN integration is the combination of the p-GaN gate HEMT and the bipolar p-FET.

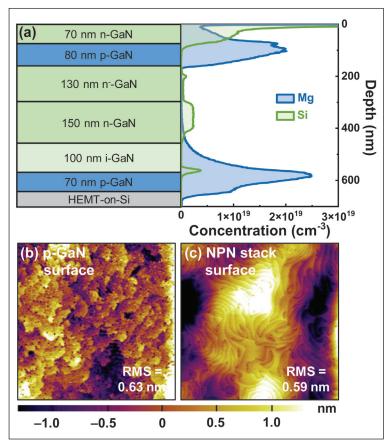

*p*-GaN HEMT platform featuring a 4.2 µm-thick GaN buffer layer, a 420 nm-thick undoped GaN channel layer, a 15 nm-thick  $AI_{0.25}Ga_{0.75}N$  barrier layer, and a 75 nm-thick *p*-GaN layer with magnesium doping at a concentration of  $2.5 \times 10^{19}$  cm<sup>-3</sup>. Using this platform, our partners at Suzhou Institute of Nano-tech and Nano-bionics, Chinese Academy of Sciences, led by Qian Sun, selectively grew the *n-p-n* stack by MOCVD. This stack comprises

Figure 2. (a) An n-p-n epi-structure on the conventional p-GaN HEMT platform and a secondary ion mass spectrometry depth profile of magnesium and silicon dopants. Atomic force microscopy images of the (b) initial p-GaN surface and (c) GaN surface after n-p-n stack growth on the E-mode GaN HEMT platform. a 150 nm-thick bottom *n*-GaN collector layer with a silicon doping concentration of  $3 \times 10^{18}$  cm<sup>-3</sup>, a 130 nm-thick *n*-GaN layer with a silicon doping concentration of  $5 \times 10^{17}$  cm<sup>-3</sup> to enhance voltage blocking capability, an 80 nm-thick *p*-GaN base layer with a magnesium doping concentration of  $2 \times 10^{19}$  cm<sup>-3</sup>, and a 70 nm top *n*-GaN emitter layer with a silicon doping concentration of  $10^{19}$  cm<sup>-3</sup> (see Figure 2(a)).

Note that we insert a 100-nm undoped GaN layer between the bottom n-GaN and p-GaN layers to mitigate the impact of the magnesium memory effect. Encouragingly, this n-p-n epi-stack preserves the favourable surface morphology of the original p-GaN, with clear atomic steps (see Figure 2(b) and (c)).

The fabrication of our BiPFETs starts with two-step etching, using a chlorine-based inductively coupled plasma recipe. The first step involves etching the collector region to remove the *n*-GaN layer, part of the *p*-GaN base layer, and then the hard mask  $SiO_2$  in the *p*-FET region. During the second step, we simultaneously etch the top *n*-GaN in the *p*-FET region and the remaining *p*-GaN in the collector region until we reach the target depth. After removing the hard mask, we activate dopants in the *p*-GaN layer by annealing our samples under nitrogen gas at 750°C for 30 minutes.

Following dopant activation, we add p- and n-ohmic contacts. To ensure an excellent p-ohmic contact on the etched p-GaN surface, we sputter a 50 nm-thick layer of magnesium on the contact region, prior to annealing at 600 °C, to diffuse this metal into the GaN layer. After removing the annealed magnesium layer, we form p-ohmic contacts with conventional evaporation and annealing processes.

According to electrical measurements, the contact and sheet resistance for our *p*-ohmic contacts are  $57 \Omega$  mm and  $65 k\Omega/sq$ , respectively. These values are comparable to those for a fresh bare *p*-GaN layer without any etching.

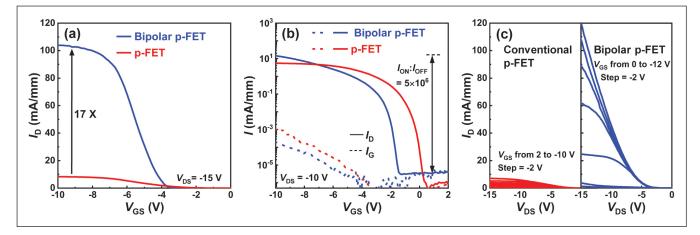

Figure 3. (a) Linear-scale transfer, (b) log-scale transfer and gate leakage current, and (c) output characteristics of BiPFETs compared with conventional p-FETs.

Our next step is to form *n*-ohmic contacts on upper and lower *n*-GaN layers through photolithography, evaporation, lift-off, and annealing.

Following contact formation, we undertake slow inductively coupled plasma etching to gradually recess the gate trench. By going slow, we minimise plasma-induced damage. Then, using atomic layer deposition, we add a layer of  $Al_2O_3$  that is approximately 22 nm-thick and serves as the *p*-FET gate dielectric. Evaporation of the gate electrodes follows, before we finalise the fabrication by defining contact vias and probing pads.

#### Improved current density ...

By integrating the *n-p-n* stack into the *p*-FET, we realise a substantial increase in the current density of the GaN *p*-FET. With identical MIS-gate dimensions as the *p*-FET, our BiPFET delivers a 17-fold hike in current density to more than 100 mA mm<sup>-1</sup> (see Figure 3). This enhancement in current density is particularly pronounced when comparing output characteristics.

It's worth noting that this substantial increase in current density is realised without compromising the performance of the MIS-gate. Our BiPFET maintains a high current on-off ratio and exhibits a low gateleakage current, signifying the well-preserved performance of the MIS gate (see Figure 3(b)). With moderate device scaling, we anticipate an increase in current density.

#### ... and enhanced stability

As well as significantly enhancing the current density, the incorporation of the *n-p-n* stack offers the additional advantage of mitigating the voltage drop on the *p*-channel MIS-gate. When operating in the off-state, a depletion region forms in the reversely biased *p*-GaN/bottom *n*-GaN junction, creating a depletion region that homogenises the electric field distribution and alleviates stress on the MIS gate. The introduction of the *n-p-n* stack elevates the off-state breakdown voltage from 22 V to 68 V (see Figure 4(a) and (b)).

The strengths of our BiPFET extend to exhibiting a more stable threshold voltage under pulsed drain-bias stress, a merit that's attributed to a reduced voltage stress on the *p*-channel MIS gate. Pulsed tests, conducted on both the *p*-FET and BiPFET, show that the latter has a significantly lower drain-induced threshold voltage shift (see Figure 4(c) and (d)). In the BiPFET, the *n-p-n* stack shares

> Figure 4. (a) Off-state leakage current and breakdown characteristics of (a) the conventional p-FET and (b) bipolar p-FET. Plots of pulsed drain current as a function of gate-source voltage ( $I_p$ - $V_{GS}$ ) of (c) the p-FET and (d) the BiPFET measured with various drain-source stress voltages ( $V_{DS \ stress}$ ).

the drain stress and safeguards the gate region. Even under a high drain stress of up to 20 V, we do not uncover any degradation in our pulsed transfer curves.

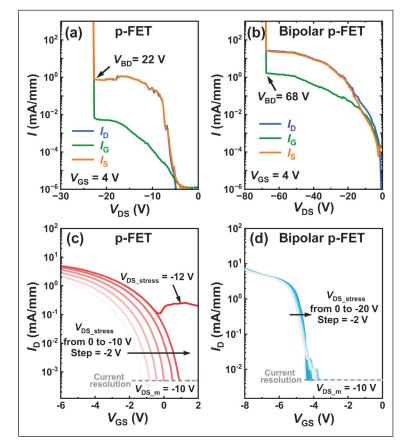

#### Integration capability

To assess the integration capability of our BiPFET, we concurrently fabricated a p-GaN gate HEMT on the same epitaxial wafer. This p-GaN gate HEMT demonstrates E-mode operation and a high on-off ratio, confirming the continued activation of the p-GaN layer after regrowth of the n-p-n stack (see Figure 5(a)).

We measure a saturation drain current density for our fabricated *p*-GaN gate HEMT of 200 mA mm<sup>-1</sup>,

The strengths of our BiPFET extend to exhibiting a more stable threshold voltage under pulsed drain-bias stress, a merit that's attributed to a reduced voltage stress on the *p*-channel MIS gate. Pulsed tests, conducted on both the *p*-FET and BiPFET, show that the latter has a significantly lower drain-induced threshold voltage shift

Figure 5. (a) Transfer and gate leakage, (b) output and (c) off-state leakage characteristics of the E-mode p-GaN gate HEMT on the same platform with the BiPFET.

a value comparable to that of conventional p-GaN gate HEMTs (see Figure 5(a) and (b)). This robust conduction capability indicates that the 2DEG channel is not significantly impacted by regrowth of the n-p-n stack.

Another encouraging finding is that after regrowth,

#### FURTHER READING / REFERENCE

➤ J. Tang, et al., 'Bipolar *p*-FET with Enhanced Conduction Capability on E-mode GaN-on-Si HEMT Platform', in 2023 IEEE International Electron Devices Meeting the buffer and channel layers still exhibit excellent blocking capability (see Figure 5(c)). The off-state breakdown voltage of the fabricated *p*-GaN gate HEMT achieves 685 V, validating the feasibility of integrating *n*-channel devices with BiPFETs for the realisation of GaN CMOS and power ICs.

The key strengths of our BiPFET are its exceptionally high current density and its enhanced stability, attributes that enable this class of transistor to be a very promising candidate for seamless integration with GaN HEMTs. This breakthrough paves the way for the design and fabrication of GaN CMOS and power ICs, laying the foundation for tomorrow's advanced power systems.

## Dedicated webinars for the power electronics industry

Using our 30+ years' experience in B2B vertical technical markets, and as the publisher of Power Electronics World, we offer effective webinars, ZOOM interview and virtual events. We help you get your message, to your desired audience, by marketing to over 53,000 power electronic professionals.

In addition to organising and managing your webinar, we can also market your webinar to our specialist databases.

In a dedicated 6 week program we will promote through our magazine, newsletters, LinkedIn group and website. We can also provide the webinar moderator, from our team of highly respected editors. Let our editors work with you and help you with the content.

#### **Reach Educate Influence**

#### Brand Awareness

Increase global awareness by running sponsored webinars, Zoom interviews and virtual events

#### Lead Generation

Generate and mature leads through the use of online events. Then analyse, qualify, and understand their buying behaviour

#### Thought Leadership

Become the voice of knowledge by generating compelling content via online events

Find out how Angel Webinars can help you organise and run a webinar within the power electronics industry.

> Contact: Jackie Cannon jackie.cannon@angelbc.com +44 (0)1923 6<u>90205</u>

ESS EXECUTIVE STRATEGY SUMMIT PIC INTERNATIONAL CONFERENCE

ANGELTECH

PE INTERNATIONAL CONFERENCE

# SAVE THE DATE 07-09 APRIL 2025

# Sheraton Brussels Airport Hotel

To find out more about our sponsor and speaker opportunities, contact us today on: +44 (0) 2476 718970

> or email: info@csinternational.net info@picinternational.net info@peinternational.net

## Crushing MOSFETs one tipping point at a time

The growth of GaN is inevitable as it displaces the MOSFET in one application after another

#### BY ALEX LIDOW FROM EFFICIENT POWER CONVERSION

GaN POWER TRANSISTORS are at a tipping point. It's a juncture where any small change or action leads to significant and often irreversible effects, and the future of these devices has reached a point of no return, where the dynamics of the situation shift dramatically.

This tipping point is following more than a decade of volume production of the GaN transistor. Since our company, Efficient Power Conversion (EPC), starting producing them in March 2010, they have repeatedly been touted as the replacement for the aging power MOSFET. Fourteen years on, the promise that GaN will crush silicon is now being realised.

To understand the changing rate of adoption of GaN, one can draw lessons from the 45-year-old power MOSFET. It's a device I know intimately, having been one of its first developers, as well as an instrumental player in the launch of the first product in November 1978. Back then the bipolar transistor was the incumbent power transistor. Despite being ten times slower, it was much cheaper than the MOSFET.

MOSFETs eventually crushed bipolar transistors. This did not occur overnight, but one application at a time. The first tipping point came from desktop computers, with Apple and IBM turning to the MOSFET for their AC-DC power supplies.

By adopting the superior transistor of the day, these tech giants could shrink their power supplies enough to fit inside desktop housings, a breakthrough that played a crucial role in widespread adoption of these computers.

Following this breakthrough, our MOSFETs continued to increase their deployment in highperformance applications while we focused on reducing costs and accelerating the learning curve as quickly as possible. Initially adoption took time, but jumps occurred whenever a new application ramped successfully. With each new tipping point for an application, the benefits to the business would extend beyond this individual triumph to trim the time and increase the likelihood of subsequent successes. Motor drives for high-speed plotters ramped in 1982. Anti-lock brakes ramped in 1985.

By 1988, thanks to higher volumes and significant capital investments, the manufacturing cost for the MOSFET had plummeted to below that of the bipolar transistor. Since then, the world never looked back. At that point in time the MOSFET had officially reached its tipping point. And that's exactly where GaN stands today.

GaN has already been adopted in several disruptive technologies, to the point where MOSFETs are no longer even considered for new designs. Each novel application for GaN can be thought of as having crossed an individual tipping point. This roadmap for ever-expanding adoption includes lidar, fast chargers, satellite electronics, AI, DC-DC power supplies, and humanoid robots.

With nearly fifty years of experience to guide us, we can identify four key factors that have played a crucial role in ensuring that GaN reaches its tipping point and finally surpass the MOSFET. These four factors, which exist in addition to all the cost, performance, and reliability requirements, are as follows: the design community now clearly understands the large value derived from GaN; the targeted application is facing a changing landscape that leads to many open design windows; the adoption of GaN is being pursued by user community leaders, who are enjoying subsequent business success; and the existence of well-trained technical talent has emerged, which is capable of working with GaN and efficiently extracting its benefits.

For GaN technology, lidar provided the first application for crossing the tipping point. The simple reason behind this success is that GaN is capable of operating at far faster speeds than the MOSFET. Dave Hall, the visionary founder of Velodyne and the father of modern lidar, fully appreciated this benefit, realising that GaN technology enables a car sensor to see farther and with higher resolution than radar. Hall developed a spinning lidar system using EPC's first-generation GaN transistors, sparking the birth of the autonomous car.

Considering lidar from the perspective of tipping point elements, one can conclude that: Hall had a clear understanding of the substantial value derived from GaN; lidar opened many new design windows as it became an essential sensor for autonomous vehicles; Velodyne had huge success, attracting lots of customers and competitors; and Hall, with some assistance from EPC's engineers, knew how to extract the maximum performance from of these transistors.

The second application to reach a tipping point is the satellite power supply. As well as outperforming the MOSFETs, GaN is virtually immune from degradation caused by radiation in space. The key champion in helping to reach this particular tipping point is Dan Sable, CEO and founder of VPT. Today, just four years after initial deployment in this application, GaN transistors account for 30 percent of the satellite market for MOSFETs, and are on track to take the final 70 percent as legacy designs become obsolete or uneconomical.

Providing the third tipping point for GaN is the fast charger. Here the standout is Gene Sheridan, CEO and co-founder of Navitas Semiconductor. Today, virtually all fast chargers use GaN, thanks to its

knowledge in overlapping sectors

Specialists with 30 year+ pedigree and in-depth

capability to deliver high powers and recharge power-hungry cell phones, tablets and laptops in a fraction of the time that silicon-based chargers would take.