**ISSUE V 2025**

POWERELECTRONICSWORLD.NET

# RIXTRON

# THE NEW G10 SERIES

Your Productivity Solution for All Advanced Epitaxy Materials

### G10-SiC

- ▶ 9x150 mm (6") or 6x200 mm (8")

- New hardware & process surpassing Single Wafer Reactor uniformities

- ► +50% productivity per fab area with large batch technology & small footprint

#### **End Markets/Products:**

EV inverters & charging infrastructure

### G10-GaN

- ▶ 8x150mm (6") or 5x200mm (8")

- ▶ 1<sup>st</sup> fully automated compact GaN MOCVD cluster designed 100% for Si Power fabs

- Novel hardware solution for unmatched barrier uniformities and device yields

#### **End Markets/Products:**

Power Electronics & Wireless communication

### G10-AsP

- ▶ 8x150 mm (6") or 5x200 mm (8")

- ▶ 1<sup>st</sup> fully automated AsP MOCVD system enabling 10x lower defect density

- Unmatched wavelength uniformity on all wafer sizes

#### **End Markets/Products:**

Micro LED, Optical Data communication, 3D-sensing & LiDAR

### GaN's ascent, SiC's stumble?

The global semiconductor landscape seems to be undergoing a significant shift, with Gallium Nitride (GaN) emerging as a strategic front-runner while there appears to be a corresponding slowing in the momentum of Silicon Carbide (SiC).

Add in recent US reshoring investments and regional innovation hubs, and 2025 is proving to be a significant year for the industry's future.

GaN technology, once niche, has now solidified its status as a critical enabler for the next generation of power and RF applications. KnowMade's Q1 patent report reflects this momentum, documenting over 500 new GaN patent families. These filings, spanning gate design to advanced packaging, signal not just technical innovation but geopolitical positioning. Chinese players like Xidian University and Innoscience lead in filings, but the U.S. is responding with manufacturing muscle.

GlobalFoundries, for instance, just committed an additional \$3 billion to GaN and photonics R&D, as part of a \$16 billion initiative to onshore chip manufacturing with partners like Apple and SpaceX. Similarly, Texas Instruments is putting more than \$60 billion into expanding US production, setting the record for the largest domestic semiconductor investment ever. These moves are as much about technological leadership as they are about national security and supply chain resilience.

Meanwhile, Singapore has launched its National GaN Innovation Centre, its first foundry capable of both GaN-on-Si and GaN-on-SiC wafer production. This gives the city-state a firm foothold in the future of semiconductors, especially as the industry veers toward higher frequencies and more power-dense applications like AI datacentres and satellite communications.

But while GaN surges, SiC is maybe facing some growing pains. Renesas seems to have abandoned its SiC chip

production plans amid collapsing prices and an oversupply driven by aggressive Chinese competition (in fairness, something not too dissimilar is happening when it comes to GaN, as it seems that TSMC is planning to leave this space – seemingly reluctant to compete with Chinese competition). This follows signs of instability from Wolfspeed, once considered a SiC pioneer, now reportedly heading for bankruptcy. Although companies like Rohm are pushing ahead - its 4th-gen SiC MOSFETs are now in Toyota's new bZ5 EV – it seems fair to say that market volatility is forcing a rethink on how and where SiC

Radiation damage studies by ETH Zürich and ANSTO further underscore the technical limitations of SiC, particularly for space-based applications. Issues like single-event leakage currents threaten long-term reliability in extreme environments, complicating its value proposition against more robust GaN alternatives.

Strategic partnerships are now playing a crucial role in accelerating GaN's climb. Navitas has partnered with Taiwan's Powerchip to transition to high-volume 200mm GaN production, targeting fast-growing markets like Al infrastructure and EVs. Europe, too, is stepping up: Silvaco's collaboration with Fraunhofer ISIT aims to push the frontiers of GaN chip design through advanced simulation and cooptimization tools.

In this fast-evolving semiconductor race, GaN is no longer just the future - it's the present. Its rapid ascent, backed by patents, partnerships, and political capital, contrasts with SiC's progress, at least for now. As national governments, corporate giants, and research institutes converge on GaN

innovation, the message is clear: the material war is far from over, but the momentum is unmistakably shifting.

### 14 Smart GaN HEMT + IGBT = EV success?

Cambridge GaN Devices is targeting the powertrain of electric vehicles with the combination of IGBTs and its proprietary integrated circuit enhancement GaN technology

### 16 Infineon's expanding 2 kV portfolio

Joining Infineon's 2kV MOSFETs are Schottky barrier diodes with identical voltage ratings

### 18 Thermally conductive silicones

From electric vehicles (EVs) and electric bikes (e-bikes) to electric trains, trucks and buses, demand for e-mobility solutions is rising.

### 22 Compact, low-power receiver could give a boost to 5G smart devices

Researchers designed a tiny receiver chip that is more resilient to interference, which could enable smaller 5G "internet of things" devices with longer battery lives

# 28 Can an unassuming electrical component help unlock limitless energy?

The global push for clean, sustainable energy is driving efforts to unlock fusion as a transformative power source

### 30 Vertical power takes centre stage on AI chips

As Al accelerators from AMD, Google, and Nvidia push beyond 1 kW power consumption, Empower Semiconductor is overhauling how power reaches these high-performance chips

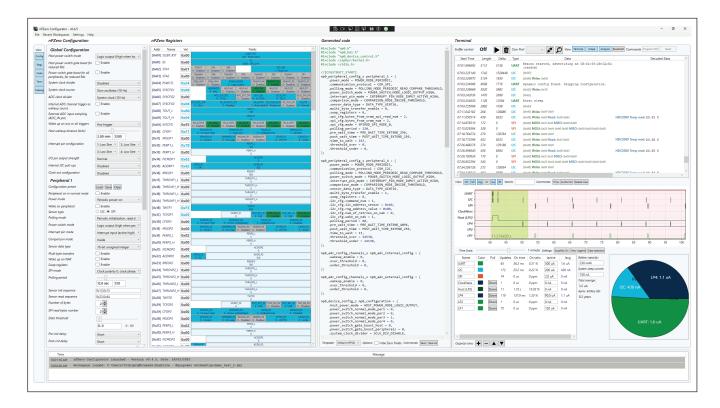

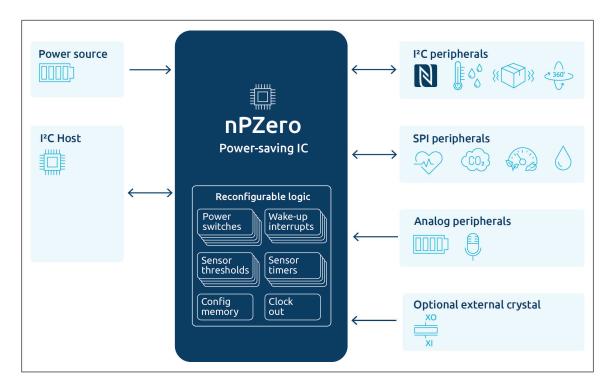

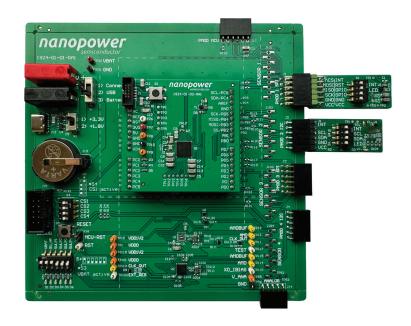

### 32 A step change in low-power circuit design

How the nPZero power-saving IC enables sensor system operation at the nanoamp level

### 36 Thick homoepitaxy on 200 mm SiC

The cost of SiC substrates needs to come down. But are we going to hamper these efforts by imposing limits on the thickness of this foundation?

### **40 Scrutinising SiC MOSFETs**

Efforts by chipmakers to improve the SiC MOSFET include investigations to understand how the design of the trench influences ruggedness, the role of the substrate on device quality, opportunities for superior screening, and the origin of shifts in threshold voltage

### 49 A GaN-on-silicon foundation for Ga<sub>2</sub>O<sub>3</sub> transistors

GaN buffer underpins high-voltage, normally-off Ga<sub>2</sub>O<sub>3</sub> transistors

### **NEWS**

- 06 GaN companies strengthen patent portfolios

- 07 GlobalFoundries boosts 're-shoring' investment

- 08 Texas Instruments to invest more than \$60 billion in the US

- 09 Renesas to abandon SiC production

- 10 Understanding the impact of radiation on SiC devices for space

- 11 Navitas plans 200mm GaN production with PSMC

- 12 Silvaco and Fraunhofer ISIT collaborate on GaN chip design

### POWER ELECTRONICS WORLD

Phil Alsop phil.alsop@angelbc.com +44(0)7786084559

#### News Editor

Christine Evans-Pughe christine.evans-pughe@angelbc.com

#### Contributing Technical Writer

Rebecca Poole

#### **Contributing Technical Editor**

Richard Stevenson richard.stevenson@angelbc.com +44 (0)1923 690215

#### Sales & Marketing Manager

Shehzad Munshi shehzad.munshi@angelbc.com +44 (0)1923 690215

### **Design & Production Manager**

Mitch Gaynor mitch.gaynor@angelbc.com +44 (0)1923 690214

#### Senior Event and Media Executive for **Power Electronics International**

James Cheriton james.cheriton@angelbc.com +44 (0)2476 718970

#### Publisher

Jackie Cannon jackie.cannon@angelbc.com +44 (0)1923 690205

#### CFO Sukhi Bhadal sukhi.bhadal@angelbc.com +44 (0)2476 718970

CTO Scott Adams scott.adams@angelbc.com +44 (0)2476 718970

PEW Magazine is published six times a year on a controlled circulation basis. Non-qualifying individuals can subscribe at: £105.00/e158 pa (UK & Europe), £138.00 pa (air mail), \$198 pa (USA). Cover price £4.50. All information herein is believed to be correct at time of going to press. The publisher does not accept responsibility for any errors and omissions. The views expressed in this publication are not necessarily those of the publisher.

Every effort has been made to obtain copyright permission for the material contained in this publication. Angel Business Communications Ltd will be happy to acknowledge any copyright oversights in a subsequent issue of the publication. Angel Business Communications Ltd © Copyright 2024. All rights reserved. Contents may not be reproduced in whole or part without the written consent of the publishers. The paper used within this magazine is produced by chain of custody certified manufacturers, guaranteeing sustainable sourcing.© Copyright 2024.

We strive for accuracy in all we publish; readers and contributors are encouraged to contact us if they recognise an error or omission. Once a magazine edition is published [online, in print or both], we do not update previously published articles to align old company names, branding, marketing efforts, taglines, mission statements or other promotional verbiage, images, or logos to newly created or updated names, images, typographic renderings, logos (or similar) when such references/images were accurately stated, rendered or displayed at the time of the original publication.

When companies change their names or the images/text used to represent the company, we invite organizations to provide Angel Business Communications with a news release detailing their new business objectives and/or other changes that could impact how customers/prospects might recog the company, contact the organisation, or engage with them for future commercial enterprise.

Published by Angel Business Communications Ltd 6 Bow Court, Fletchworth Gate, Burnsall Road, Coventry CV5 6SP, UK. T: +44 (0)2476 718 970 E: info@angelbc.com W: angelbc.com

### GaN companies strengthen patent portfolios

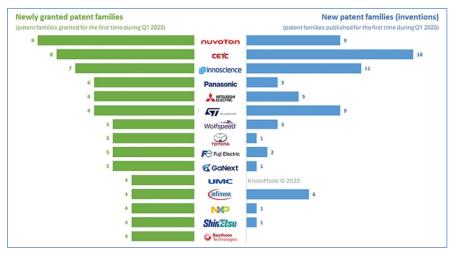

KnowMade Q1 IP patent report shows companies are addressing critical aspects of GaN technology.

KNOWMADE has published its Q1 2025 IP report on GaN electronics, highlighting robust patenting activity across both power and RF segments, amid on-going patent disputes between power GaN companies.

Recent patent filings emphasise critical aspects of power GaN technology such as gate design and packaging, resulting in sustained patent portfolio growth. Meanwhile, key RF market players keep expanding their IP activities in the RF GaN landscape, underlining the technology's role in next-generation wireless applications.

During the first quarter of 2025, a total of 540 new patent families were published, with Xidian University and major Chinese entities such as CETC and Innoscience leading the patent filings, followed by contributions from Nuvoton, STMicroelectronics, and Toshiba. Over 330 patent families were granted for the first time, notably reinforcing portfolios at Innoscience, STMicroelectronics, Infineon, Navitas, and EPC, alongside significant grants to Panasonic and TSMC. The guarter also saw more than 110 patents abandoned and over 70 patents expired, primarily from well-established patent holders including Wolfspeed, Infineon, and Fujitsu.

Approximately 10 IP collaborations (patent co-filings) were recorded, most partnerships formed between industry and academic organisations. For instance, Safran published a patent application with CNRS, CNAM and several universities in Paris, for an on-board aeronautical power circuit with active filtering. Also, Volkswagen cooperated with the University of Tennessee on GaN-based three-level active neutral point clamped power module designs, resulting in joint patent publications in Q1 2025. Nearly 40 patent transactions took place this

quarter, predominantly within China, such as the transfer of several RF GaN patents from Xidian University to Huawei and power module company Macmic Science & Technology's acquisition of a GaN device patent from UESTC. In addition, a new lawsuit was initiated in February 2025 when Innoscience appealed to the US Court of Appeals to challenge the US International Trade Commission's ruling in last November on EPC's patent US 8,350,294.

Toshiba, Texas Instruments (TI), and Rohm each published more than six new inventions. In particular, Rohm introduced multiple innovations aimed at enhancing the reliability of normallyoff GaN devices by leveraging p-GaN gate layer techniques and superlattice buffer structures. TI unveiled a novel gate structure incorporating a p-type poly-Si layer to decouple parasitic capacitances and improve gate depletion behavior, alongside trench-based substrate-to-source connections for GaN power devices and a HEMT design featuring a doped barrier to boost threshold voltage stability and drain current stability. Moreover, TI disclosed a packaging solution wherein a GaN FET is copackaged with its driver for optimised

half-bridge modules. Leading RF GaN Developments

Sony, Sumitomo Electric, and Macom disclosed six, five, and four RF-focused inventions, respectively. While Sumitomo Electric and Sony were focused on RF GaN device designs, Macom's patenting activity related to RF amplifier circuitry and advanced packaging techniques.

Interestingly, Sumitomo Electric focused on RF GaN-on-SiC devices fabricated on nitrogen-polarity GaN epitaxial structures. Academic research also made a significant contribution on this topic with UCSB publishing an invention that improves the linearity of deep-recess GaN MIS-HEMTs through corrugation of N-polar structures. MONDE Wireless, a UCSB spin-off, also mentioned N-polar GaN HEMTs grown on miscut substrates in another Q1-2025 patent publication.

New entrants to the GaN electronics IP landscape were predominantly Chinese, with LED manufacturer Anhui GaN Semiconductor filing several epiwafer patent applications for both power and RF uses, and battery manufacturer CATL submitting its first GaN-related invention targeting battery management systems.

### GlobalFoundries boosts 're-shoring' investment

Company commits to a further \$3b on next-generation GaN tech, packaging innovation, and silicon photonics.

GLOBALFOUNDRIES says it is working with the Trump Administration, with support from tech companies Apple, SpaceX, AMD, Qualcomm, NXP and GM, to onshore critical components of the supply chain with a total \$16 billion investment in expanding chip manufacturing and packaging across its facilities in New York and Vermont.

This latest announcement builds on the company's existing US expansion plans of more than more than \$13 billion funding to both advance manufacturing of 200mm GaN on silicon semiconductors at its facility in Essex Junction, Vermont; and for its recently launched New York Advanced Packaging and Photonics Center. GF is committing an additional \$3 billion, which includes advanced research and development initiatives focused on next-generation GaN technologies, packaging innovation, and silicon photonics.

The company says its investment is a strategic response to the explosive growth in Al, which is accelerating demand for next-generation semiconductors designed for power efficiency and high-bandwidth performance across data centres, communications infrastructure and Alenabled devices.

Tim Breen, CEO of GlobalFoundries said: "The Al revolution is driving strong, durable demand for GF's technologies that enable tomorrow's data centres – including GF's leading silicon photonics, as well as GaN for power applications. Meanwhile at the edge, GF's proprietary FDX technology is uniquely positioned to support Al functionality with low power consumption. With all these technologies and more manufactured right here in the US, GF is proud to play its part in accelerating America's semiconductor leadership."

"GlobalFoundries investment is a great example of the return of United States manufacturing for critical semiconductors," said US Secretary of Commerce, Howard Lutnick. "President Trump has made it a fundamental objective to bring semiconductor manufacturing home to America. Our partnership with GlobalFoundries will secure US semiconductor foundry capacity and technology capabilities for future generations."

"GlobalFoundries has supplied semiconductors for Apple products since 2010 and we're excited to see them expand right here in the United States. These chips are an essential part of Apple products like iPhone, and they're a powerful example of American manufacturing leadership," said Tim Cook, Apple's CEO Gwynne Shotwell, president and COO at SpaceX said: "Advanced semiconductors are critical to the advanced satellite capabilities which SpaceX has been pioneering for over two decades. We are excited by the expansion of GlobalFoundries' manufacturing base right here in the US, which is core to Starlink's growth and our commitment to manufacturing in the US, as well as our mission to

deliver high-speed internet access to millions of people around the world." "As a strategic supplier of Qualcomm, GlobalFoundries shares our vision for strengthening US chip production capacity. This commitment from GlobalFoundries will help secure a resilient semiconductor supply chain to support the next wave of US technology innovation, especially in areas vital to enabling power efficient computing, connectivity, and edge intelligence," said Cristiano Amon, president and CEO of Qualcomm Incorporated "This collaboration allows us to scale efficiently, expand production in the US and continue delivering for our customers. It's a strong step forward in building a resilient, high-performing semiconductor supply chain in the United States, "said Kurt Sievers, CEO of NXP Semiconductors.

"Semiconductors are critical to the future of vehicles, and their importance will only grow. GlobalFoundries' investment supports our work to secure a reliable, US-based chip supply – essential for delivering the safety, infotainment and features our customers expect," said Mark Reuss, president of General Motors.

# Texas Instruments to invest more than \$60 billion in the US

More than \$60 billion investment includes seven U.S. semiconductor fabs across three manufacturing mega-sites in Texas and Utah supporting more than 60,000 new US jobs.

Texas Instruments plans to invest more than \$60 billion across seven U.S. semiconductor fabs, making this the largest investment in foundational semiconductor manufacturing in U.S. history.

Working with the Trump administration and building on the company's nearly 100-year legacy, TI is expanding its U.S. manufacturing capacity to supply the growing need for semiconductors that will advance critical innovations from vehicles to smartphones to data centers. Combined, TI's new manufacturing mega-sites in Texas and Utah will support more than 60,000 U.S. jobs.

"TI is building dependable, low-cost 300mm capacity at scale to deliver the analog and embedded processing chips that are vital for nearly every type of electronic system," said Haviv llan, president and CEO of Texas Instruments. "Leading U.S. companies such as Apple, Ford, Medtronic,

NVIDIA and SpaceX rely on TI's world-class technology and manufacturing expertise, and we are honored to work alongside them and the U.S. government to unleash what's next in American innovation."

"For nearly a century,

Texas Instruments has been a bedrock American company driving innovation in technology and manufacturing," said U.S. Secretary of Commerce, Howard Lutnick.

"President Trump has made it a priority to increase semiconductor manufacturing in America – including these foundational semiconductors that go into the electronics that people use every day. Our partnership with TI will support U.S. chip manufacturing for decades to come."

Today, TI is the largest foundational semiconductor manufacturer in the U.S., producing analog and embedded processing chips that are critical for smartphones, vehicles, data centers, satellites and nearly every other electronic device. In order to meet the steadily growing demand for these essential chips, TI is building on its legacy of technology leadership and expanding its U.S. manufacturing presence to help its customers pioneer the next wave of technological

Based around a hot topic for your company, this 60-minute recorded, moderated zoom roundtable would be a platform for debate and discussion

breakthroughs.

- Moderated by editor, Phil Alsop, this can include 3 speakers

- Questions prepared and shared in advance

Cost: €5995

Contact: Jackie Cannon jackie.cannon@angelbc.com

ANGEL EVENTS

### Renesas to abandon SiC production

Japanese giant halts SiC chip plans amid Chinese price war and Wolfspeed uncertainty.

RENESAS is abandoning plans to produce SiC chips for EVs. according to TrendForce, citing a report by Nikkei, This move by the Japanese semiconductor firm has apparently been prompted by slow growth in the EV market, coupled with a SiC chip supply glut driven by Chinese manufacturers. It follows news that Renesas' SiC partner Wolfspeed is preparing to file for Chapter 11 bankruptcy within weeks.

In July 2023, Renesas announced its entry to the power SiC market through a ten year partnership with Wolfspeed. The deal included a \$2 billion deposit from Renasas to secure supply for both 150mm and 200mm SiC wafers.

Renesas had initially planned to begin manufacturing SiC power chips for EVs in early 2025 at its Takasaki plant in Gunma Prefecture. However, the company has since disbanded the SiC team at the facility, according to Nikkei. The latest research from TrendForce. shows

weakening

demand in the

automotive

and industrial

sectors and

slow shipment

growth for SiC

substrates in

2024.

Simultaneously, intensifying competition and sharp price

declines have driven global revenue for N-type SiC substrates down 9 percent year-over-year to \$1.04 billion.

Chinese vendors TanKeBlue and SICC have risen to prominence, capturing 17.3 percent and 17.1 percent of the global market share, respectively. Price competition with Chinese rivals is expected to intensify over the medium to long term, making it more difficult for a late arrival like Renesas

to generate profits from SiC chip production.

TrendForce adds that while Renesas has reportedly decided to halt inhouse production of SiC power chips, the company does not plan to exit the market entirely. Instead, it may continue to develop its own SiC designs while outsourcing manufacturing to foundries, then selling the finished products under its own brand.

### Singapore opens GaN innovation centre

SINGAPORE has opened the National Semiconductor Translation and Innovation Centre for GaN; the country's first national facility dedicated to GaN semiconductors.

The centre addresses common challenges faced by companies and researchers – such as limited local access to advanced facilities and the need for closer collaboration.

NSTIC (GaN) is the first facility in Singapore to host both 6-inch GaN-on-SiC and 8-inch GaN-on-silicon wafer fabrication lines.

It will also offer advanced GaN technology with gate lengths below 0.1µm and operation frequencies above 100GHz suitable for chips

used in satcoms and a range of future communication and instrumentation technologies. NSTIC (GaN) will begin offering commercial foundry services from mid-2026.

First set up in 2023 as the National GaN Technology Centre (NGTC), NSTIC (GaN) is a partnership between the Agency for Science, Technology and Research (A\*STAR), DSO National Laboratories (DSO), and Nanyang Technological University, Singapore (NTU Singapore).

NSTIC (GaN) is part of the broader National Semiconductor Translation and Innovation Centre (NSTIC) initiative led by A\*STAR, which supports national efforts to deepen semiconductor R&D and innovation across priority domains such as photonics and advanced packaging.

The semiconductor industry contributes nearly 6 percent of GDP to Singapore's economy and supports around 35,000 skilled jobs across R&D, design, and advanced manufacturing.

"NSTIC (GaN) is not just a facility — it is a national platform for innovation and a catalyst for future technologies," said Cheong Chee Hoo, chairman of the NSTIC (GaN) Steering Committee. "Our goal is to build deep capabilities in GaN manufacturing and research, so that Singapore can help define the future of high-performance semiconductors."

# Understanding the impact of radiation on SiC devices for space

ETH Zürich and ANSTO collaboration reveals mechanisms of single event leakage current radiation damage in MOSFETs and JBS diodes

THE FIRST results have been reported on a collaboration between ETH Zürich and Australia's Nuclear Science and Technology Organisation (ANSTO), looking at the impact of radiation on SiC devices for space.

The results are covered in two articles both in IEEE Transactions on Nuclear Science. Corinna Martinella (pictured above), formerly a senior scientist at ETH Zurich, said in a LinkedIn post that the research advances an understanding of the basic mechanisms of radiation damage in SiC power devices exposed to heavy ions.

One paper describes how commercial SiC power devices, including MOSFETs and Junction Barrier Schottky (JBS) diodes, respond to space-like radiation at a microscopic level. By using a highly focused beam of particles at the Centre for Accelerator Science, that either travel deep or stay near the surface, Martinella and her team studied how different kinds of radiation affect the devices.

They found that short-range particles could cause a type of damage called single event leakage current (SELC) in both older and newer versions of these devices.

Monte Carlo simulations performed at ANSTO helped explain how particle depth affects the damage. In particular, when particles strike certain areas of a diode, they increase the electric field and trigger a chain reaction of ionisation, which may lead to lasting defects.

Some parts of the devices, such as the source and the gate metal lines showed no signs of damage. However, there were differences in how the devices reacted depending on whether the

particle beam hit directly on the source pad or off to the side.

A protective polyimide layer reduced how deeply ions could penetrate in offpad areas.

The second paper investigated the relation between single event effects (SEEs) caused by heavy-lon Irradiation and defects in SiC devices.

First author student Helton De Medeiros used heavy-ion irradiation with different linear energy transfers and ion penetration ranges to investigate the radiation tolerance of SiC power diodes.

Single event leakage current degradation was observed for ion ranges shorter than the top crystalline layer. Other techniques were applied to explain the root cause of the observed radiation effects.

### TSMC to exit GaN production

ACCORDING to various reports, Taiwanese chip giant TSMC will wind down its GaN wafer foundry services by July 31, 2027, with related production lines at its Hsinchu Science Park fabs ceasing operations.

The reason for the decision is thought to be rising price pressure from Chinese rivals.

TrendForce says that TSMC plans to repurpose its Hsinchu Fab 5, which handles GaN production, for advanced packaging.

By reusing existing cleanroom facilities, TSMC can accelerate expansion with minimal effort, addressing demand for Chip-on-Wafer-on-Substrate, Wafer-on-Wafer (WoW), and Wafer-Level System Integration (WLSI) technologies, the report says.

### Navitas plans 200mm GaN production with PSMC

Partnership will support GaN's ramp into Al data centres, EVs, solar, and home appliances.

NAVITAS SEMICONDUCTOR has announced a strategic partnership with Powerchip Semiconductor Manufacturing Corporation (PSMC or Powerchip), to start production and continue development of 200mm GaN-on-silicon technology.

Navitas' GaN IC portfolio is expected to use Powerchip's 200mm in Fab 8B, located in Zhunan Science Park, Taiwan. The fab has been operational since 2019 and supports various high-volume manufacturing processes for GaN, ranging from micro-LEDs to RF GaN devices.

Powerchip's capabilities include an improved 180nm CMOS process, offering smaller and more advanced geometries, which bring improvements in performance, power efficiency, integration, and cost. "200mm GaNon-silicon production on a 180nm

process node enables us to continue innovating higher power density, faster, and more efficient devices while simultaneously improving cost, scale, and manufacturing yields", said Sid Sundaresan, SVP of WBG Technology Platforms at Navitas.

Powerchip is expected to manufacture Navitas' GaN portfolio with voltage ratings from 100V to 650V, supporting the growing demand for GaN for 48V infrastructure, including hyper-scale Al data centers and EVs. Qualification of initial devices is expected in Q4 2025. The 100V family is expected to start production first at Powerchip in 1H26, while the company expects 650V devices will transition from Navitas' existing supplier, TSMC, to Powerchip over the next 12-24 months.

Navitas recently made several announcements in the Al data center,

EV, and solar markets, including its collaboration with NVIDIA to support GaN and SiC technologies for 800V HVDC architectures for 1 MW IT racks and beyond. Enphase announced that its next-generation IQ9 would include Navitas' 650 V bi-directional GaNFast ICs, and Changan Automobile announced its first commercial GaNbased OBC (on-board charger) using Navitas' GaNSafe technology.

"We are proud to partner with Powerchip to advance high-volume 200 mm GaN-on-silicon production and look forward to driving continued innovation together in the years ahead", said Gene Sheridan, CEO and co-founder of Navitas. "Through our partnership with Powerchip, we are well-positioned to drive sustained progress in product performance, technological evolution, and cost efficiency."

### Toyota 'bZ5' uses Rohm SiC MOSFETs

TOYOTA is using a power module equipped with Rohm's 4th generation SiC MOSFET bare chip in the traction inverter of its new crossover BEV 'bZ5' aimed at the Chinese market.

The power module has started mass production shipments from Chinese module-maker Haimosic, a joint venture between Rohm and Zhenghai Group.

The bZ5 has a driving range of 550 km for the lower grade model and 630 km (CLTC mode) for the higher grade.

Reservations for the car began on April 22, 2025, the day before the opening of the 2025 Shanghai Motor Show, attracting significant attention.

Rohm says it aims to complete the construction of the production line for

the next-generation 5th generation SiC MOSFET by 2025, and is also

accelerating the market introduction plans for the 6th and 7th generations.

Picture source: JustAnotherCarDesigner, CC0, via Wikimedia Commons

# Silvaco and Fraunhofer ISIT collaborate on GaN chip design

Project aims to explore and optimise the performance of GaN devices with greater depth and efficiency.

EDA company Silvaco has announced an R&D collaboration with Fraunhofer Institute for Silicon Technology (ISIT) to accelerate development of nextgeneration GaN devices.

Fraunhofer ISIT's Power Electronics division (which develops prototypes for power electronic and sensor systems) will use Silvaco's design tools — including the Victory TCAD platform, Utmost IV, and SmartSpice — to perform Design Technology Co-Optimisation (DTCO) for device development.

The idea is that Silvaco's DTCO platform will accelerate prototyping in Fraunhofer ISIT's post-CMOS process environment, which is set up to explore emerging processes for both GaN and MEMS technologies on 8-inch wafers. In addition, Silvaco's Victory Design of Experiments (DOE) solution will streamline development workflows and support rapid innovation during the evaluation of novel process modules and emerging device concepts.

"We are excited to expand our GaN design capabilities with Silvaco's Victory products," said Michael Mensing, head of the Advanced Devices Group at

Fraunhofer ISIT. "By using Silvaco's advanced TCAD solutions, our teams can explore, understand, and optimise the performance of GaN devices with greater depth and efficiency. Especially during our current development of high voltage lateral and vertical GaN devices based on engineering substrates, like Qromis Substrate Technology, we see many physical effects that require accurately calibrated process and device models.

This collaboration marks a significant

step forward in strengthening Europe's semiconductor capabilities and driving the global evolution of GaN devices," said Eric Guichard, SVP and general manager of Silvaco's TCAD Division.

"Institutes like Fraunhofer ISIT are instrumental in pushing the boundaries of innovation in device and process technology. By collaborating with Fraunhofer ISIT, we not only accelerate their development efforts but also enhance our own TCAD tools to meet the demands of future device design."

## Dedicated webinars for the power electronics (PEW) industry

Using our 30+ years' experience in B2B vertical technical markets, and as the publisher of PEW Magazine, we offer effective webinars, ZOOM interview and virtual events. We help you get your message, to your desired audience, by marketing to over 53,000 PEW professionals.

In addition to organising and managing your webinar, we can also market your webinar to our specialist databases.

Reach Educate Influence

- Brand Awareness

- Lead Generation

- Thought Leadership

**SEP 10-12, 2025 | TAINEX 1&2, TAIPEI**

STRONGER TOGETHER

Register at www.semicontaiwan.org

## **SEMICON®WEST**

OCTOBER 7-9, 2025 | PHOENIX, ARIZONA

STRONGER TOGETHER

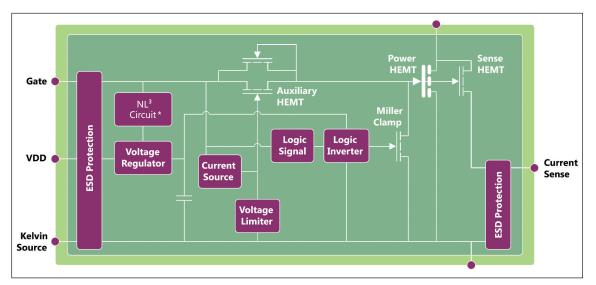

### Smart GaN HEMT + IGBT = EV success?

Cambridge GaN Devices is targeting the powertrain of electric vehicles with the combination of IGBTs and its proprietary integrated circuit enhancement GaN technology.

#### BT RICHARD STEVENSON, EDITOR, CS MAGAZINE

TODAY'S DESIGNERS of power trains for electric vehicles face a difficult choice. Should they view cost as paramount and select silicon IGBTs; or should efficiency be the priority, and they deploy SiC MOSFETs? Whichever they choose, a significant compromise will be made.

But now there's the promise of a third way, pioneered by a handful of producers of GaN — they are claiming that they could offer products with a price close to that of silicon solutions, while delivering an efficiency similar to that of SiC, by pairing a GaN HEMT with a silicon transistor.

Amongst these trailblazers, Cambridge GaN Devices (CGD) claims that it is standing out from the crowd with its proprietary integrated circuit enhancement GaN technology, which it refers to as ICeGaN. The company is championing the combination of its 'intelligent' GaN HEMTs, which feature an enhancement-mode *p*-GaN HEMT rated at 650 V, and an IGBT. It's a patent-pending pairing with the moniker Combo ICeGaN.

According to Daniel Murphy, Director of Technical Marketing at CGD, the company's ICeGaN is its core technology, as well as its unique selling point. "This is what we're building the company around. The DNA of CGD, if you like."

One of the primary strengths of ICeGaN is that it provides ease of use. "You can essentially treat a GaN transistor like a MOSFET," says Murphy. Due to this, it's possible to use a very simple, low-cost driver to accompany the GaN HEMT.

Another great attribute of ICeGaN is that it facilitates zero-voltage switching, thanks to the inclusion of a Miller clamp. "There's no need for a negative voltage to be applied to switch the device," says Murphy, explaining that this refinement allows the driver to be simpler and cheaper. What's more, the Miller clamp ensures a very efficient turn-off of the GaN HEMT.

In addition to these valuable assets, absent in conventional GaN HEMTs, CGD's ICeGaN

> IceGaN is a form of smart power HEMT that features advanced sensing and protection capabilities.

technology has a slightly higher threshold voltage for the transistor.

"We've shifted it up to about three volts," says Murphy, explaining that this adjustment brings ICeGaN technology in line with standard silicon devices. "Hence, you can use standard silicon drivers."

The slight increase in threshold voltage also eliminates the danger of spurious turn-on.

With Combo IceGaN, higher efficiencies are realised by drawing on the complementary benefits of both classes of transistor.

"GaN comes into play at light loads, where you have very low switching losses. It brings increased efficiency," enthuses Murphy, who adds: "At high loads, and in some fault conditions, the robustness of the IGBT comes into play."

While the levels of efficiency provided by Combo IceGaN are not quite as high as they are with a full SiC solution, it provides a cost saving of around 40 percent to 50 percent, according to Murphy. And compared with only IGBTs, efficiency is 3 percent higher, based on measurements that consider the Worldwide Harmonised Light Vehicles Test Procedure cycle. "That obviously translates into either a less expensive battery or extended range," remarks Murphy.

As well as targeting the power train, CGD is pursuing opportunities in on-board chargers and DC-to-DC converters in electric vehicles, as well as industrial data centres, through the development of more innovative approaches. In this sector, power densities and power levels tend to increase year-on-year. "So, we're needing to improve the form factor all the time, and investigate different ways to address the packaging to meet the thermal requirements," says Murphy.

As all these applications involve very high power

levels, the increase in chip area associated with additional features of ICeGaN, such as advanced sensing and the protection function, is relatively modest. Thanks to this, CGD is able to produce highly functional, competitively priced products.

Like many players in GaN power electronics, CGD is fabless, with chips produced at TSMC. This world-renowned Taiwanese foundry is responsible for the growth of epiwafers and their processing into devices. Packaging is undertaken at another partner, ASE.

As the Combo GaN technology can incorporate a range of IGBTs, CGD is planning to operate at the chip level within the supply chain. "We're looking for module partners, we're looking for car makers, tier ones that are interested to adopt this approach, and then we would support them with the sale of bare die," says Murphy.

One of the reasons why CGD is focusing on the traction inverter within the electric vehicle market is the volume of GaN that's required. "It is so much higher, because the power level is so much higher," claims Muphy, who adds that the other big draw is the substantial technical challenge. "We're a company with lots of smart people, and we're very ambitious. So that's why we're targeting traction."

Given the conservative nature of the automotive industry, it will take time for CGD to penetrate this market. The plan is to begin by launching discrete products for on-board chargers and DC-to-DC converters in 2026.

"The idea is for traction to try and enter a carmaker platform around 2028 timescale, and sooner than that with on-board chargers and DC-to-DCs," says Murphy.

So, while the makers of SiC MOSFETs are going to face stiff challenge from other wide bandgap devices, the competition is not going to begin immediately.

### Infineon's expanding 2 kV portfolio

Joining Infineon's 2kV MOSFETs are Schottky barrier diodes with identical voltage ratings

#### BY RICHARD STEVENSON, EDITOR, CS MAGAZINE

HIGH ON THE AGENDA of many design engineers in increasing the electrical efficiency of their systems. Gains on this front trim carbon dioxide emissions and utility bills, while reducing heating, which simplifies thermal management and enhances reliability.

Today, two well-trodden routes may be taken to increase the efficiency of electrical systems. One of these proven pathways is to replace silicon power electronics with those that have a wider bandgap, as this reduces resistance. And the other common approach is to increase the voltage of the electrical system, and this enables a reduction in current and ohmic heating.

While both approaches pay dividends, rather than picking one over the other, it's better to adopt both practices. And helping to do just that is the trailblazer of the SiC Schottky barrier diode (SBD), Infineon Technologies: it added a 2kV SiC SBD last October, and has just introduced a sibling, rated at the same voltage and housed in a different

package. This pair of diodes complement Infineon's 2 kV MOSFET, launched in March 2024.

Infineon has been refining the SiC SBD for decades, having brought the first commercial device to market back in 2001. Major revisions to this diode since its debut include a new backside die metallisation and die attach technology, and more recently, the introduction of thin wafer technology, making an earance in the fifth-generation portfolio.

appearance in the fifth-generation portfolio. With these SBDs, the thickness of the die is slashed from 350  $\mu$ m to just 110  $\mu$ m.

In 2018, the European powerhouse introduced a sixth-generation of SiC SBDs, featuring an electrochemical barrier between the metal and

semiconductor that reduces the knee voltage by around 0.1 volts.

"For 650 volts, this is a big advantage, but not so much for other blocking voltages," remarks Peter Friedrichs, Infineon's Vice President of SiC. "For that reason, Gen 6 remained at 650."

By offering fifth-generation 2 kV SiC SBDs in two different packages – initially TO-247PLUS-4-HCC, and now the TO-247-2 package – Infineon is giving design engineers the opportunity to select between a diode that majors on clearance and on creepage. The former metric is related to the physical distance between the pins, with a higher value reducing the chances of arcing, while creepage considers the conductance pathway along the package surface.

"[With the TO-247PLUS-4-HCC] there's an extra gap in the plastics that forms a longer creepage," says Friedrichs.

It's not clear which of the two variants will prove more popular. "We can scale both of them according to customer needs," says Friedrichs.

Infineon is mainly targeting two markets with its expanding portfolio of 2 kV power devices: the solar sector and the charging of electric vehicles.

To provide high-power, fast charging of electric vehicles, bus voltages as high as 1,500 V are employed. So, to ensure reliability in this application, power devices are ideally rated at 2 kV.

Within the solar market, one of the trends has been an increase in the output voltage of the panels. "Today, 1,500-volt panels are state-of-the-art, but there are already first solutions with 2 kV and even higher," says Friedrichs.

While it is theoretically possible to serve both these applications with silicon devices related at 2 kV, the electrical losses are unacceptable. So wide bandgap

➤ Infineon's

barrier diode

in a TO-247-

2 package

majors on

clearnace.

2kV SiC

Schottky

By offering fifth-generation 2 kV SiC SBDs in two different packages – initially TO-247PLUS-4-HCC, and now the TO-247-2 package – Infineon is giving design engineers the opportunity to select between a diode that majors on clearance and on creepage

devices with a low voltage rating have been adopted, using what is referred to as a multi-level topology.

"You stack components with a lower blocking voltage in series to manage the higher voltage," explains Friedrichs, illustrating this point by suggesting that rather than using a 2 kV device, two 1.2 kV devices may be used in series. However, as well as doubling the number of devices, multilevel topology designs increase the complexity for controlling the circuit and magnify cost at the system level.

As one would expect, Infineon's 2 kV devices are more expensive than their 1.2 kV siblings.

"2 kV comes at a higher price, since we need a thicker epitaxial layer, a thick drift zone and a larger area. This, of course, contributes to cost, but it's still more affordable than putting two 1.2 kV in series," explains Friedrichs.

For SiC devices, the substrate accounts for a significant proportion of device cost, especially for SBDs, even though they are smaller than MOSFETs. However, substrates costs are falling, with a significant reduction in the last 12 to 15 months, according to Friedrichs.

For both of the applications that Infineon is targeting humidity is an issue, as electric vehicles and solar panels operate outdoors. Friedrichs says that humidity is a particularly significant concern for solar applications, due to the low night-time temperatures that leads to condensation in the system. It's not possible to address these concerns with a perfect hermetic seal, and if moisture enters the power devices, this can impact long-term reliability.

Infineon has been aware of this issue for many years, having been supplying devices to makers of solar systems since 2010. "From that point onwards, we have integrated special measures to protect the silicon carbide chips against any moisture-related degradation." says Friedrichs.

degradation," says Friedrichs.

Two sites for production of its SiC portfolio have been established by Infineon: Villach, Austria; and Kulim, Malaysia.

"In Kulim, we are just starting to ramp silicon carbide front-end production," says Friedrichs. "We start with the MOSFET. So, at the moment, all the diodes are produced in Villach."

But with demand for SiC power devices set to rise, it will potentially not be long before the Kulim fab is serving customers all around the world with a broad and expanding portfolio that includes high-voltage SBDs.

Thanks

to an extra

gap in the

plastics, the

TO-247PLUS4-HCC suits

engineers

requiring a

high degree of

creepage

# Dedicated webinars for the power electronics (PEW) industry

Using our 30+ years' experience in B2B vertical technical markets, and as the publisher of PEW Magazine, we offer effective webinars, ZOOM interview and virtual events. We help you get your message, to your desired audience, by marketing to over 53,000 PEW professionals.

In addition to organising and managing your webinar, we can also market your webinar to our specialist databases.

#### **Reach Educate Influence**

- Brand Awareness

- Lead Generation

- Thought Leadership

Contact: Jackie Cannon jackie.cannon@angelbc.com +44 (0)1923 690205

### Thermally conductive silicones

From electric vehicles (EVs) and electric bikes (e-bikes) to trucks and buses, demand for e-mobility solutions is rising.

### BY LUC DUSART, MARKETING MANAGER FOR MOBILITY & TRANSPORTATION ELECTRONICS AT DOW

ACCORDING to the International Energy Agency (IEA), the global EV fleet is expected to grow 12-fold by 2035. Current and evolving e-mobility solutions depend on advances in power electronics that facilitate effective conversion and control of increasing amounts of electrical energy. E-mobility goals such as greater range and performance require new power electronics devices with higher efficiency, smaller formats and better thermal management properties. However, several factors present roadblocks to achieving these improvements. Advanced siliconebased materials can help address these challenges.

## Managing heat, boosting reliability and streamlining production

When designers add more, and increasingly powerful components to printed circuit board (PCB) assemblies used in signal flow and power transfer, their additional generated heat can reduce the capacity, lifespan and performance of power electronics devices. Excessive heat can also

increase the risk of thermal runaway in battery cells. These are two reasons why designers are seeking e-mobility materials, such as thermally conductive silicones, that can resolve heat-related issues with better thermal management. Designers are also looking for solutions to performance, safety and reliability concerns. For example, e-mobility power electronics applications like electronic control units (ECUs), inverters, converters and onboard chargers face environmental and mechanical challenges. Resistance to moisture, humidity, salt spray, shock and vibration is critical for e-mobility technologies that operate on roads or railways. Moisture, humidity and salt can lead to corrosion in PCB traces, while shock and vibration can cause solder joints to crack and PCB substrates to warp or bend.

There are also assembly issues to consider. Manufacturers of mass-produced e-mobility technologies such as EVs prefer materials that help facilitate high-volume production. For example, silicone-based materials can be applied quickly and precisely with

automated mixing and dispensing equipment to reduce cycle times, labor costs and material waste. When curing is required, a material's curing method can also affect cycle times and operational expenses such as energy costs.

### Advantages of advanced silicones

For thermal management, assembly and protection of electronic components, E-mobility designers have a choice of materials including silicone-based solutions and organics such as epoxies and urethanes. Compared to organics, advanced silicone-based materials provide important advantages. For example, silicones withstand higher temperatures than organics and provide longer-lasting heat resistance without a significant loss in mechanical properties.

Temperature fluctuations also pose a challenge for e-mobility power electronics. When materials used in PCB components have different coefficients of thermal expansion (CTEs), they expand and contract at different rates. Advanced silicones can absorb some of the stress that results from inconsistent temperature changes. By contrast, epoxies and urethanes may crack because they have a higher modulus than silicones and relieve stress less effectively, due to their rigidity after curing.

With their low modulus, silicones can also absorb shock and vibration associated with operating an e-bike or EV. As mentioned previously, epoxies and urethanes are prone to cracking under stresses such as vibration. The hydrolytic stability of advanced silicones is also an advantage because it helps protect EVs from moisture related damage.

For productivity, silicones support high-volume, automated assembly and can cure at room temperature or with ultraviolet (UV) light instead of energy-intensive ovens. Dual-cure systems combine UV light with moisture to reach shadowed areas.

While epoxies and urethanes also support automated assembly and various curing methods, they cannot match silicones' other advantages.

Silicones offer a range of benefits for power electronics and one particularly beneficial application is thermal management. To leverage the benefits of these materials in thermal management, silicone materials are supplied in a variety of formulations and formats.

### Thermally conductive silicones

Thermal conductivity (TC) is measured in Watts per meter Kelvin (W/m·K). Because air has a relatively low TC of 0.024 W/m·K, it is not efficient at dissipating heat from electronics. Therefore, filling the air gaps between heat sinks or heat spreaders and other components and substrates with a thermally conductive material is essential to optimize heat dissipation.

Silicones are inherently thermally insulating; however, with the addition of specialized fillers they can become thermally conductive. By conducting heat from power electronics, these silicones help prolong the life of power electronics, reduce energy consumption and prevent damage to surrounding components on a PCB. Depending on the application,

operational requirements and preferred dispensing method, manufacturers can choose from silicone gap fillers, gels, greases/compounds, adhesives, and encapsulants.

- O Gap Fillers: Thermally conductive silicone gap fillers fill large gaps (0.5-5mm) between components on a PCB. These materials are available with a wide range of thermal conductivity values up to 12 W/mk. Some applications may need materials with a TC of 6 W/m⋅K, while other electronics may require a higher or lower TC.

- Greases: Thermally conductive silicone greases create a path between a heat source and a heat spreader. They are easy to dispense with automated equipment and do not require curing. These materials come in a range of thermal conductivities. Applications include heat dissipation from insulated-gate bipolar transistors (IGBTs) used with inverters. Importantly, thermally conductive silicone greases support thin bond lines for improved heat transfer.

- Adhesives: Thermally conductive silicone adhesives bond electronic components within a heat-generating assembly such as an ECU. They also are used to bond metal heat sinks to PCB substrates. They are available in one- and two-part formulations that are easy to dispense and can cure at room temperature. Thermally conductive silicone adhesives have TC values that range from 0.8 to 3.3 W/m·K.

- Gels: Thermally conductive silicone gels are highly conformable and reworkable, making them especially valuable for complex geometries

- of some e-mobility power electronics. These materials also have significantly lower viscosities than other thermally conductive products such as gap fillers because of their semi-solid state. Low viscosity makes gels easier to pump and mix, and flow more freely. Thermally conductive silicone gels cure at a wide range of temperatures and are easy to process.

- Encapsulants: Thermally conductive silicone encapsulants can cure at room temperature or with added heat. They flow easily and, after mixing, have viscosities ranging from 3,000 to 25,000 millipascal second (mPa·s). Products with a TC from 1.0 to 4 W/m·K are available. Applications include battery chargers where the small feature size of onboard-charger inductors need to be filled to ensure efficient heat transfer.

### Other advanced silicone products

Unlike thermally conductive silicones, thermally insulating silicones prevent or reduce the spread of heat due to their low thermal conductivity and unique molecular structure. Some also meet specific flame ratings or provide electrical conductivity and shielding against electromagnetic interference (EMI).

As designers add more electronics to e-mobility vehicles, EMI shielding is becoming increasingly important because electronic noise or crosstalk can affect performance and safety.

Thermally insulating silicone products for e-mobility applications include encapsulants, conformal coatings, adhesives and greases.

### TECHNOLOGY I EVs

- Silicone Encapsulants play a crucial role in protecting inverters, converters and e-motors from various environmental and operational hazards. They are also used with IGBT modules, highvoltage resistor packs, sensors, connectors, wires and LED lighting. These advanced silicone materials are waterproof, stress relieving, electrically insulating, vibration damping and flame resistant. Transparent silicone encapsulants also provide visibility of protected electronics during inspection or repair.

- Silicone Conformal Coatings are thin films that are applied to PCB substrates in one or more layers to resist moisture, dust, abrasion and mildew. Depending on their formulation, these materials may have UL94 V-0 or UL94 V-1 flame rating. Silicone conformal coatings are used in the automotive industry

- to replace potting or encapsulating materials that result in a brick-like structure, which can be bulky and heavy. By using conformal coatings instead, e-mobility designers can support light weighting without sacrificing performance.

- Silicone Adhesives are a broad category of materials with variations that are thermally insulating. They are used for assembly of inverters, converters, on-board battery chargers, e-motors and ECUs. Thixotropic silicone adhesives, featuring a thick, paste-like consistency, are used for gasketing, typically as lid seals or covers. Silicone adhesives with high tensile strength are recommended for e-mobility applications that need to resist significant pulling forces, such as power electronics that are subjected to significant vibrations. Another option is adhesive sealants, which combine strong bonding with reliable sealing. These are well suited for e-motors due to a combination of their chemical, thermal, and mechanical properties. Silicones can withstand extreme temperatures, they are excellent electrical insulators and their elasticity help absorb shocks and vibrations, reducing wear and tear on components.

- Electrically conductive silicone Adhesives can be used in several formats such as a die attach adhesive, EMI gasketing, and grounding adhesives to maintain electrical connection. Depending on the application the EC silicone

- can provide electrical connection across a wide range of application temperatures and over a wide variety temperature, both low and high. of The EMI shielding provided by electrically conductive silicone adhesives can protect sensitive e-mobility electronics across frequencies in the 1 KHz to 70 GHz range.

- O Silicone Greases can provide thermal protection but may also be used for protection against electrical arcing and voltage drop. Such dielectric greases protect electrical connections from dirt, water, moisture and contaminants.

Importance of the right supplier Finding the right materials for e-mobility power electronics is only part of any solution.

Partnering with a leading supplier can help designers improve e-mobility performance, reliability, safety and durability. Dow takes a collaborative approach to help customers advance e-mobility technologies.

Hands-on collaboration is paired with Dow's scientific research, data generation and testing under real-world conditions to ensure quality and reliability of silicone-based products.

By leveraging advanced silicones and support services, designers can confidently drive innovation in power electronics and shape the future of e-mobility.

- Based around a hot topic for your company, this 60-minute recorded, moderated zoom roundtable would be a platform for debate and discussion

- Moderated by editor, Phil Alsop, this can include 3 speakers

- Questions prepared and shared in advance

Cost: €5995

Contact: Jackie Cannon jackie.cannon@angelbc.com

**WURTH ELEKTRONIK** MORE THAN YOU EXPECT

# ULTRA LOW LOSSES

# WE-MXGI

With the WE-MXGI Würth Elektronik offers the newest molded power inductor series. It combines an innovative iron alloy material that provides high permability for lowest R<sub>DC</sub> values combined with an optimized wire geometry.

Ready to Design-In? Take advantage of personal technical support and free samples ex-stock.

www.we-online.com/WE-MXGI

### **Highlights**

- Extremely high power density

- Ultra low R<sub>DC</sub> values and AC losses

- Magnetically shielded

- Optimized for high switching frequencies beyond 1 MHz

# This compact, low-power receiver could give a boost to 5G smart devices

Researchers designed a tiny receiver chip that is more resilient to interference, which could enable smaller 5G "internet of things" devices with longer battery lives.

### BY ADAM ZEWE, MIT NEWS

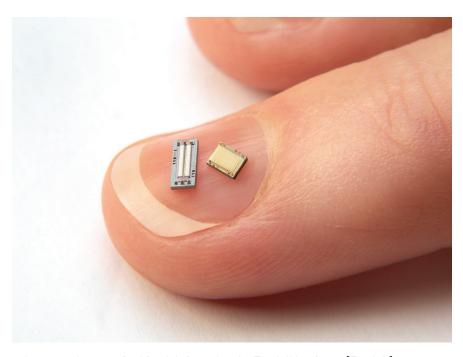

MIT researchers have designed a compact, low-power receiver for 5G-compatible smart devices that is about 30 times more resilient to a certain type of interference than some traditional wireless receivers.

The low-cost receiver would be ideal for battery-powered internet of things (IoT) devices like environmental sensors, smart thermostats, or other devices that need to run continuously for a long time, such as health wearables, smart cameras, or industrial monitoring sensors.

The researchers' chip uses a passive filtering mechanism that consumes less than a milliwatt of static power while protecting both the input and output of the receiver's amplifier from unwanted wireless signals that could jam the device.

Key to the new approach is a novel arrangement of precharged, stacked capacitors, which are connected by a network of tiny switches. These miniscule switches need much less power to be turned on and off than those typically used in IoT receivers. The receiver's capacitor network and amplifier are carefully arranged to leverage a phenomenon in amplification that allows the chip to use much smaller capacitors than would typically be necessary.

"This receiver could help expand the capabilities of IoT gadgets. Smart devices like health monitors or industrial sensors could become smaller and have longer battery lives. They would also be more reliable in crowded radio environments, such as factory floors or smart city networks," says Soroush Araei, an electrical engineering

and computer science (EECS) graduate student at MIT and lead author of a paper on the receiver.

He is joined on the paper by

Mohammad Barzgari, a postdoc in the

MIT Research Laboratory of Electronics

(RLE); Haibo Yang, an EECS graduate

student; and senior author Negar

Reiskarimian, the X-Window Consortium

Career Development Assistant

Professor in EECS at MIT and a member

of the Microsystems Technology

Laboratories and RLE. The research

was recently presented at the IEEE

Radio Frequency Integrated Circuits

Symposium.

#### A new standard

A receiver acts as the intermediary between an IoT device and its environment. Its job is to detect and amplify a wireless signal, filter out any Our chip also is very quiet, in terms of not polluting the airwaves.

This comes from the fact that our switches are very small, so the amount of signal that can leak out of the antenna is also very small

interference, and then convert it into digital data for processing.

Traditionally, IoT receivers operate on fixed frequencies and suppress interference using a single narrow-band filter, which is simple and inexpensive. But the new technical specifications of the 5G mobile network enable reduced-capability devices that are more affordable and energy-efficient. This opens a range of IoT applications to the faster data speeds and increased network capability of 5G. These next-generation IoT devices need receivers that can tune across a wide range of frequencies while still being cost-effective and low-power.

"This is extremely challenging because now we need to not only think about the power and cost of the receiver, but also flexibility to address numerous interferers that exist in the environment," Araei says.

To reduce the size, cost, and power consumption of an IoT device, engineers can't rely on the bulky, off-chip filters that are typically used in devices that operate on a wide frequency range.

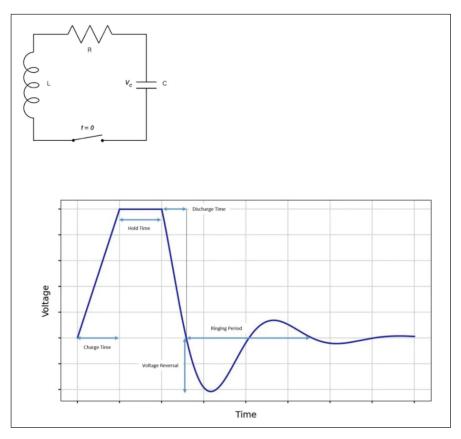

One solution is to use a network of on-chip capacitors that can filter out unwanted signals. But these capacitor networks are prone to special type of signal noise known as harmonic interference.

In prior work, the MIT researchers developed a novel switch-capacitor network that targets these harmonic signals as early as possible in the receiver chain, filtering out unwanted signals before they are amplified and converted into digital bits for processing.

#### Shrinking the circuit

Here, they extended that approach by using the novel switch-capacitor network as the feedback path in an amplifier with negative gain. This configuration leverages the Miller effect, a phenomenon that enables small capacitors to behave like much larger ones.

"This trick lets us meet the filtering requirement for narrow-band IoT without physically large components, which drastically shrinks the size of the circuit," Araei says.

Their receiver has an active area of less than 0.05 square millimeters.

One challenge the researchers had to overcome was determining how to apply enough voltage to drive the switches while keeping the overall power supply of the chip at only 0.6 volts.

In the presence of interfering signals, such tiny switches can turn on and off in error, especially if the voltage required for switching is extremely low.

To address this, the researchers came up with a novel solution, using a special circuit technique called bootstrap clocking. This method boosts the control voltage just enough to ensure the switches operate reliably while using less power and fewer components than traditional clock boosting methods.

Taken together, these innovations enable the new receiver to consume less than a milliwatt of power while blocking about 30 times more harmonic interference than traditional IoT receivers.

"Our chip also is very quiet, in terms of not polluting the airwaves. This comes from the fact that our switches are very small, so the amount of signal that can leak out of the antenna is also very small," Araei adds.

Because their receiver is smaller than traditional devices and relies on switches and precharged capacitors instead of more complex electronics, it could be more cost-effective to fabricate. In addition, since the receiver design can cover a wide range of signal frequencies, it could be implemented on a variety of current and future IoT devices. Now that they have developed this prototype, the researchers want to enable the receiver to operate without a dedicated power supply, perhaps by harvesting Wi-Fi or Bluetooth signals from the environment to power the chip. This research is supported, in part, by the National Science Foundation.

Reprinted with permission of MIT News http://news.mit.edu

### Industry eyes integrated magnetics for AI chips

With power-hungry Al chips on the rise, Apple, Intel and others are turning to magnetics-on-silicon, pioneered by Ireland's Tyndall National Institute, to dramatically raise energy efficiency

#### BY REBECCA POOL, TECHNICAL WRITER, PEW MAGAZINE

EARLIER THIS YEAR, Apple filed a US patent application for an inductor that uses magnetic films, designed to save board space and ultimately improve power supply efficiency in high performance portable computers.

The filing follows a series of applications relating to integrated magnetics on silicon spanning eight years, with listed inventors including Apple engineers as well as Professor Cian O'Mathuna, Director of Integrated Power and Energy Systems Research, and colleagues, at Ireland's Tyndall National Institute.

Such patent activity stems from nearly three-decades' worth of research on integrated magnetics at Tyndall, and comes at a time when the likes of Nvidia, AMD, Google and Intel are rolling out the hungriest of AI chips. Packed with hundreds of thousands - or more - processing units, vast on-chip memory and advanced interconnects, these chips easily eat up hundreds of watts, and then some, for massive parallel computations.

So how can integrating magnetics onto silicon chips help? It's largely about minimising the footprint and energy

losses of DC-DC power supplies. Breakthroughs in both magnetic thin films on silicon and PCB-embedded magnetics have enabled the miniaturization of magnetic inductors that can replace bulky, wire-wound magnetic components. As O'Mathuna puts it: "For me, the best way to get the ultimate miniaturisation was always with integrated magnetics and magnetics-on-silicon technology."

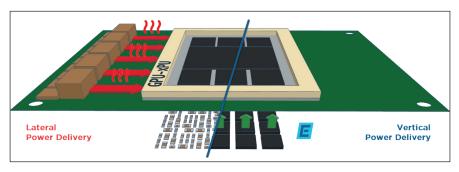

Smaller inductors can be integrated, alongside power management ICs (PMICs ) and capacitors, onto a single chip, forming an advanced integrated voltage regulator or DC-DC converter. This serves as the final stage in the power supply system for a processor, and can be placed underneath the processor chip, either in the package substrate or embedded in the interposer, in a vertical configuration. Vertically integrating the power supply with the processor chip minimises parasitic losses and provides a faster transient response, dramatically enhancing the efficiency of power delivery. Critically, a large array of power supplies can deliver fast, efficient granular power, from directly beneath the compute die.

"When we build the inductor on silicon, we can make it really really small - we would even say we make the magnetics disappear onto the silicon chip, which is why we call this technology MaglC. We also have an array of inductors associated with an array of DC to DC converters," says O'Mathuna. "So now I can control the current going into each core or each part of the processor, while minimising interconnect losses."

➤ Professor Cian O'Mathuna is Director of Integrated Power and Energy Systems Research at Ireland's Tyndall National Institute. [Tyndall]

### TECHNOLOGY I MAGNETICS-ON-SILICON

The Tyndall Director also believes an integrated magnetics approach makes manufacturing sense for the Al chips of tomorrow. "We're introducing a new component but not a new manufacturing technology per se, as the magnetic disc-head industry has been using this type of technology for thirty years," he points out. "So this is not a massive leap of faith."

Indeed, integrated magnetics have already found their way into commercial chips, as part of a vertical power delivery set-up, to enable high performance computing. Intel, for one, has integrated coaxial magnetic composite core inductors to its processor chips. Meanwhile Apple uses magnetic thin-film inductor technology from TSMC. In late 2021, the tech-giant released its MacPro computers with an array of 140 integrated, thin-film coupled inductors fabricated on five silicon PMICs, which delivered vertical power to the processor, through the package substrate and interposer. According to reports, this integrated magnetics technology enabled Apple's MacPro to last for 18 hours from a single battery charge, compared with between 6 to 9 hours for previous models. "We do hold a patent with Apple in this space," confirms O'Mathuna.

#### Reaching out

At the start of this year, O'Mathuna and Tyndall colleagues were also granted a patent for a novel thin-film vertical inductor, again designed to boost power efficiency in Al applications. In the coming year, they will be working on proof-of-concept studies and then intend to licence the associated technology to Tyndall industry partners. This is an extension of their ongoing industry activities - various integrated magnetics technologies have already been licenced to multiple international companies.

While all license deals are confidential, Tyndall has published the results of collaborative research with many international companies including Global Foundries, Infineon, Intel, Murata (formerly IPDIA), Taiyo Yuden, Texas Instruments and Wurth Electronics. O'Mathuna highlights the Global Foundries silicon-based Ultimate Miniature Magnetic Inductors and Transformers (SUMMIT) platform. As part of this, 3mm² solenoid-type inductors and transformers can be

> Integrated magnetic chips fabricated at the Tyndall Institute. [Tyndall]

monolithically integrated onto silicon substrates for power supply on chip (PwrSoC) DC/DC or integrated voltage regulator applications for Al accelerators and other highperformance computing systems. "Wurth Elektronic [Germany] has also been designing its own inductors, with fabrication through an external foundry, with some really impressive results," he adds.

Along the way, chip inductor firms, including Taiyo Yuden, as well as Murata and TDK have also been developing their own high temperature magnetic materials for compact and very low profile PCB-embedded magnetics. For example, Taiyo Yuden's LSCN series of multilayer power inductors has a thickness of only 0.2 to 0.3 mm, which according to O'Mathuna, meets the demands of high-end PCB suppliers, such as AT&S. Austria, keen to embed components in the circuit board. "You could imagine these companies saying; 'So what can we do to stay competitive here - Intel is using soft magnetic composites in PCBs – could we put our inductors into the PCB? Yes we can but they need to be very thin," he says.

Other industry players, including Atlas Magnetics, Empower Semiconductor, Ferric and Texas Instruments, have taken a different approach, and have been manufacturing entire PMIC

modules, (Power Supply in Package – PsiP), which include integrated magnetics. These modules typically include a small ASIC with multiple DC to DC converters and inductors, have a very low profile of some 0.6 mm, and are assembled using conventional surface mount assembly technology.

O'Mathuna highlights how Ferric, for one, manufactures a multi-phase output module and had previously been working with TSMC on thin film magnetics - but has since moved onto an alternative, undisclosed technology. "These companies set out to fit within the existing surface mount assembly supply chain and so developed PSiP modules," points out O'Mathuna. "It's pretty cool to see how [these companies] can get the power management, magnetics and possibly capacitors all into 0.6 mm thickness," he says. "This indicates that there is a lot of innovative routes to creating integrated inductor solutions."

#### Commercial moves

As more and more of their developments edge closer to commercialisation, Tyndall researchers continue to work with myriad magnetic materials. For example, as part of their magnetics-on-silicon development, they currently deposit thin films of cobalt-based and Fe-based alloys on silicon as well as cobalt-based thin magnetic films on vertical copper structures.

### TECHNOLOGY | MAGNETICS-ON-SILICON

To drive magnetics-on-silicon fabrication forward, Tyndall researchers are currently part of the EU-funded FD-SOI FAMES Pilot Line, funded under the Chips for Europe initiative. With project partners CEA-LETI, in Grenoble, the researchers are developing a miniaturised DC-DC converter in which a PMIC and thin-film inductor will be flipchipped or micro-transfer printed onto a high density trench capacitor interposer substrate. "For granular power, you could have a number of these chiplets in an array, so you can deliver power to multiple loads in a processor," says O'Mathuna.

Apple processors developed by TSMC already have high density trench capacitors attached to the interposer. "With the Apple product, TSMC has demonstrated that it can put the magnetics on top of the silicon PMIC," says O'Mathuna. "So I would suggest that the commercial application of FAMES technology, is not a million miles away – it could be three to five years away."

O'Mathuna also highlights how global firms began to show significant interest in Tyndall's magnetic-on-silicon technology more than a decade ago, prompting him and colleagues to start working on technology transfer.

"These companies had various levels of success in taking the technology forward – this isn't an easy thing to do," he says. "But now TSMC and Global Foundries have magnetics-on-silicon technology, it's going to be much easier for the industry to progress." "You could say that after thirty years of research, magnetics-on-silicon has become an overnight success," he adds.

We've got a complexity here that needs to be worked out in terms of who owns what, who's going to be responsible for reliability issues that may arise in manufacture and whose problem is it

#### Supply chain complexities

But is the integrated magnetic supply chain ready for commercial-scale manufacturing? Not quite yet. Right now, only a handful of firms are operating in the integrated magnetics-on-silicon, PCB-embedded magnetics, and PMIC/magnetics modules spaces. For example, only two industry players appear to be offering magnetic-on-silicon technology right now; TSMC in volume production and Global Foundries, which is currently sampling to customers.

O'Mathuna is well aware of the supply chain complexities that lie ahead, highlighting how magnetic components have yet to be built into the CAD EDA tools used by IC designers. "There is work to be done here... and who should be working on it? Should it be, say, TSMC?" he asks. "Or could the OSATs (Outsourced Semiconductor Assembly and Test) vendors do this? They take the wafers from companies and package them, so this could give them a significant competitive advantage to add integrated power delivery to their capabilities."

He also points to Intel's involvement in PCB embedded soft magnetic composites, and wonders if the technology is Intel-specific and therefore proprietary. "Even PCB embedding of chip inductors becomes complicated as you now have a package substrate but need to talk to the Taiyo Yudens of the world and ask them to work with a package substrate supplier on embedding the chip inductors," he says. "We've got a complexity here that needs to be worked out in terms of who owns what, who's going to be responsible for reliability issues that may arise in manufacture and whose problem is it?" Yet despite the complexities, O'Mathuna is optimistic that given recent industry developments, supply chain issues will be ironed out in the near-term. Reiterating how TSMC has Apple as its customer for magnetic thin-film inductor technology while Wurth Electronik's interest in the technology can only drive business for the foundries, he asserts: "The future of integrated power is about making magnetics disappear."

"All of these power companies are trying to get into the Al chiplet space and Al power delivery, and from a sustainability point of view you could save dramatic amounts of energy if you adopt a vertical power approach," he says. "Some Al companies have said, we can do the power management chips but our problem is the magnetics... This is the bottleneck, which means there's a big opportunity here"

# Find your way in thin film technology for Power Devices with Evatec

From 300mm silicon processing to Wide Band Gap (WBG) applications on SiC or GaN, Evatec is your partner for thin film production in power devices.

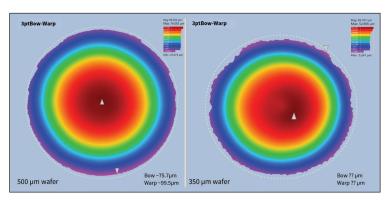

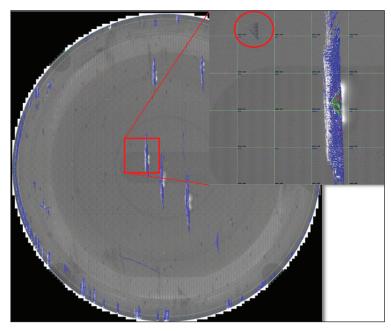

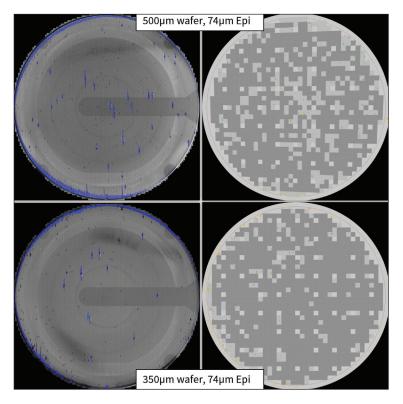

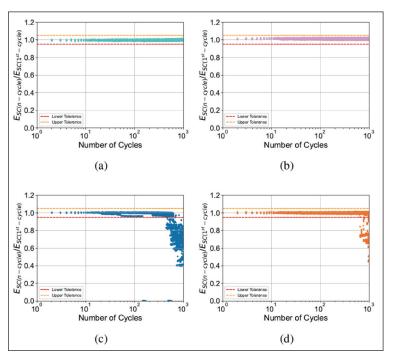

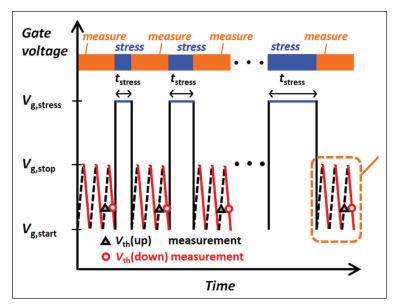

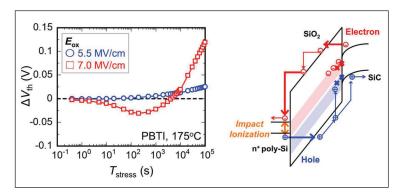

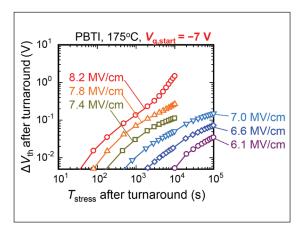

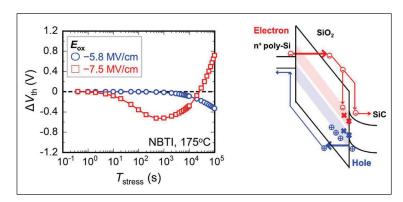

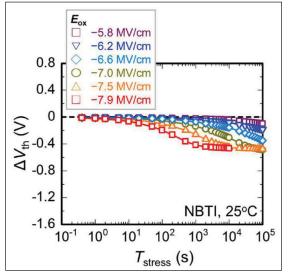

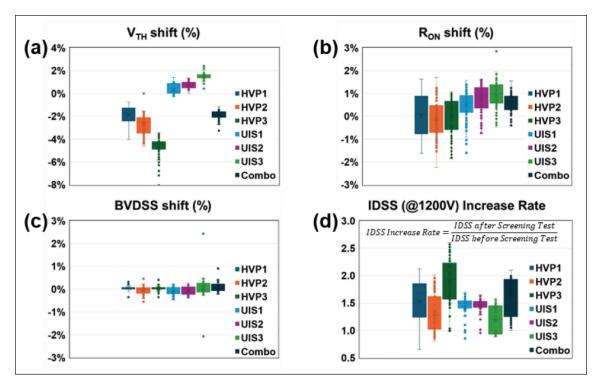

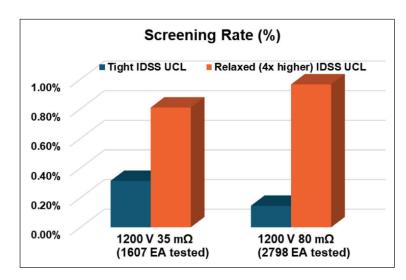

Process know-how including secure thin or bonded wafer handling combined with management of wafer stress and temperature keeps you on the right track.