**ISSUE 1 2020**

#### WWW.POWERELECTRONICSWORLD.NET

Smart manufacturing in the sub-fab

### Steer tech for car, power applications

#### Better etching enhances selective area doping

### IEDM improvements in power electronics

# KLA steers tech for power applications

### Photoluminescence captures carbon contaminants in GaN

By researchers at Tohoku University and SCIOCS

News Review, News Analysis, Features, Research Review and much more.

### Best performance for next generation SiC power electronics to address global mega trends

RIXTRON

# AIX G5 WW C

- Electric vehicles: on board chargers, power inverters

- Infrastructure: charging stations

- Renewables: solar and wind

- Industrial: motor drives, power supplies

- Power distribution: HVDC

Discover our SiC epi production batch tool with single wafer performance

www.aixtron.com

By Jackie Cannon, Publisher & Editor

### Powering into 2020: IEDM new technologies, dealing with defects

THE NEW YEAR got off to a roaring start across the power electronics industry with announcements from all supply chain sectors pointing to greater innovation and more capable products backed by R&D programmes filling product pipelines.

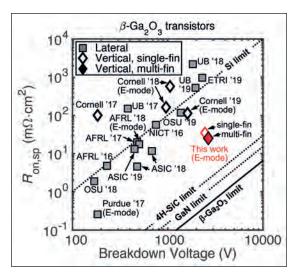

In this edition we profile some of the most exciting power electronics advances including an article from the editor of Compound Semiconductor magazine, Dr. Richard Stevenson in his profile of the recent International Electron Devices Meeting (IEDM). He explores methods to enhance today's mainstay of non-silicon MOSFET transistors and Schottky diodes: Silicon Carbide (SiC). Dr. Stevenson details ways to further enhance SiC performance while exploring new wide bandgap technologies including gallium oxide  $(Ga_2O_3)$ . While the first commercial GaO devices will soon debut, high volume is years away as researchers seek to improve stability and yield – issues that typically impact the adoption of all technologies.

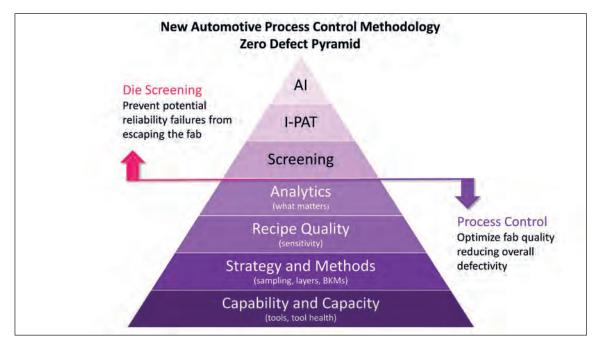

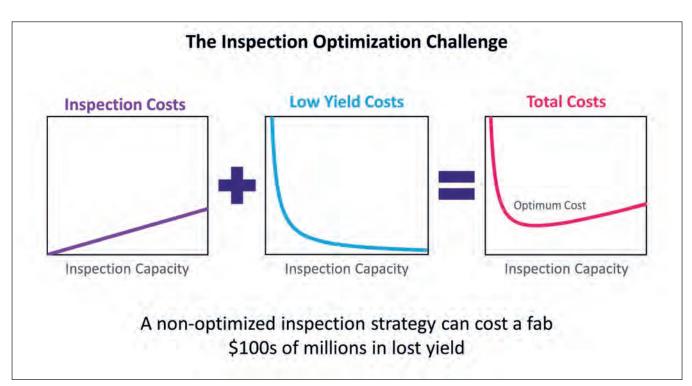

Whether at IEDM or other major industry events, ideas enabling cost reduction, defect elimination and auto sector design wins were common themes. In this edition we hear from KLA Corporation, a global leader in metrology, device inspection, packaging and emerging automotive IC applications. KLA demonstrates how to meet stringent vehicle quality and lifetime requirements that can be a decade or more compared to consumer electronics lifetimes that sometimes shrink to months.

In this Power Electronics World we also speak with Onto Innovation CEO Mike Plisinski who dives into the customercentric advantages his team is engineering as leaders of the recently merged Rudolph Technologies and Nanometrics. We also highlight the work being undertaken by Edwards Vacuum in its quest to enhance sub-fab performance through 'Industry 4.0' preventative maintenance systems that are elevating cost savings and uptime to new and exciting levels.

Explore the latest advances in power device technologies at the Compound Semiconductor International Conference held in conjunction with the Sensor Solutions and PIC International Conferences, 31 March-1 April in Brussels. Visit: www.csinternational.net for more information.

Editor & Publisher Jackie Cannon jackie.cannon@angelbc.com +44 (0)1923 690205 Technical Editor Mark Andrews mark.andrews@angelbc.com Sales Manager Shehzad Munshi +44 (0)1923 690215 shehzad.munshi@angelbc.com USA Representatives Tom Brun Brun Media tbrun@brunmedia.com +001 724 539-2404 Janice Jenkins jjenkins@brunmedia.com +001 724-929-3550 Director of Logistics Sharon Cowley +44 (0)1923 690200 sharon.cowley@angelbc.com Design & Production Manager Mitch Gaynor mitch.gaynor@angelbc.com +44 (0) 1923 690214 Circulation Director Scott Adams scott.adams@angelbc.com +44 (0)2476 718970 Chief Executive Officer Stephen Whitehurst stephen.whitehurst@angelbc.com +44 (0)2476 718970

Joint Managing Director Sukhi Bhadal sukhi.bhadal@angelbc.com Joint Managing Director Scott Adams scott.adams@angelbc.com Directors Jackie Cannon, Sharon Cowley

ngelbc.com +44 (0)2476 718970 gelbc.com +44 (0)2476 718970

Published by Angel Business Communications Ltd, Unit 6, Bow Court, Fletchworth Gate, Burnsall Road, Coventry CV5 6SP, UK. T: +44 (0)2476 718 970 E: info@angelbc.com

PEW Magazine is published four times a year on a controlled circulation basis. Non-qualifying individuals can subscribe at: £105.00/e158 pa (UK & Europe), £138.00 pa (air mail), \$198 pa (USA). Cover price £4.50. All information herein is believed to be correct at time of going to press. The publisher does not accept responsibility for any errors and omissions. The views expressed in this publication are not necessarily those of the publisher. Every effort has been made to obtain copyright permission for the material contained in this publication. Angel Business Communications Ltd will be happy to acknowledge any copyright oversights in a subsequent issue of the publisher. Step and the publication. Angel Business Communications Ltd will be happy to acknowledge written consent of the publishers. The paper used within this magazine is produced by chain of custody certified manufacturers, guaranteeing sustainable sourcing.© Copyright 2020.

We strive for accuracy in all we publish; readers and contributors are encouraged to contact us if they recognise an error or omission. Once a magazine edition is published [online, in print or both], we do not update previously published articles to align old company names, branding, marketing efforts, taglines, mission statements or other promotional verbiage, images, or logos to newly created or updated names, images, typographic renderings, logos (or similar) when such references/images were accurately stated, rendered or displayed at the time of the original publication. When companies change their names or the images/ket used to represent the company, we invite organizations to provide Angel Business Communications with a news release detailing their new business objectives and/or other changes that could impact how customers/prospects might recognise the company, contact the organisation, or engage with them for future commercial enterprise.

### 24 COVER STORY

#### Photoluminescence captures carbon contaminants in GaN

Omidirectional photoluminescence offers a non-contact, non-destructive method for measuring the density of carbon contaminants in GaN

#### 12 Better etching enhances selective area doping for vertical GaN power devices

Multi-step etching slashes the leakage current in regrown GaN p-n junctions for selective area doping

#### 18 Enabling Smart Manufacturing in the Sub-Fab

The Industry 4.0 movement is rapidly becoming the *de facto* means to optimize cost-effective manufacturing. Power electronic device makers want to leverage any practical idea

## 26 IEDM details improve in power electronics

Supressing degradation in SiC p-i-n diodes and IGBTs, enhancing channel mobility in SiC MOSFETs, and improving the blocking voltage and on-resistance of  $Ga_2O_3$  transistors all featured at the most recent IEDM meeting

#### 32 KLA steers tech for automotive IC, power applications

Silicon Semiconductor technical editor Mark Andrews speaks with Robert Cappel, Senior Director of Marketing, about advances that KLA Corporation has made to enable defect reduction and quality improvement processes for automotive applications

#### 38 Rudolph Technologies, and Nanometrics merge to form Onto Innovation

Silicon Semiconductor technical editor Mark Andrews recently asked Onto Innovation's CEO Mike Plisinski about the merger of Nanometrics and Rudolph Technologies that formed a new company

#### news

- 06 ib vogt sells and constructs 180 MWp PV plant in Badajoz, Spain

- 07 Octopus electric vehicles and EO charging launch EV charging solution

- 08 Controllis introduces high capacity rectifiers with solar integration

- 09 Next steps towards miniature power supplies

- 10 Opel to build plant manufacturing battery cells in Kaiserslautern

news review

# ib vogt sells and constructs 180 MWp PV plant in Badajoz, Spain

ib vogt has announced the sale and start of construction of the 180 MWp "Bienvenida" photovoltaic project in Badajoz, Spain. The Talanx Group, one of the major European insurance groups and institutional investor, has acquired the plant. ib vogt has set up an innovative long-term power purchase agreement (PPA) for the project with Shell Energy Europe and will perform all operational contracts for the project delivery and operation.

The Bienvenida project was initially acquired as an early stage development project by ib vogt in 2017 and developed to achieve a capacity of 180 MWp on only 175 hectares of land located in Extremadura, one of the sunniest places in Spain. With a fully wrapped EPC contract and full lifetime operation for the client, ib vogt provides a one-stop service to meet the investors needs whilst removing interface risks otherwise widely common in the market.

ib vogt has developed and successfully implemented an innovative power contracting structure with Shell Energy Europe, who will buy the produced energy. The agreement between the parties includes an attractive price

hedging that balances price volatility while remaining exposed to opportunities in the Spanish power market.

"The solar park 'Bienvenida' represents an excellent fit with our direction and strategy," explained Dr Thomas Mann, Chief Investment Officer of Talanx. "The investment allows us to diversify our asset portfolio and this enables us to manage the volatility in our portfolio in a more controlled way, since we will benefit equally from wind and solar power.

"Moreover, the sheer size of the solar park allows us to better support the environmental transformation to a zero-carbon emission society – in this case by means of industrially generated green energy," he added. "Furthermore, it helps us to counteract the low-interest phase with higher returns on investment." Anton Milner, CEO of ib vogt GmbH, stated: "This project is the culmination of a number of years of development work and is the first of a series of major "grid parity" projects that we are developing in Southern Europe.

{Importantly, these will help drive the penetration of clean electricity in Europe on a stand-alone economic – unsubsidised – basis. We are delighted and proud to be working with the Talanx Group and to be able to support their sustainability and portfolio objectives.

"In Talanx we have a partner that shares our objectives and approaches in driving the implementation of this important technology in the fight against climate change. We would also like to thank all of our partners in this complex project and especially the local commune where we will be creating long term employment opportunities."

### Littelfuse board helps designers try out SiC chips

Littelfuse has announced the Gate Drive Evaluation Platform (GDEV)to help designers evaluate SiC MOSFETs, SiC Schottky diodes, and other peripheral components like gate driver circuitry, so that they can better understand how SiC technologies will behave in converter applications under continuous operating conditions.

The GDEV offers quick connect header pin terminals that allow for rapid and consistent comparison of different gate drive circuits, unlike most other SiC evaluation platforms. The GDEV supports an 800 V DC link input voltage and up to 200 kHz switching frequency. Typical markets and applications for the GDEV include automotive EC/HEV charging stations, industrial powersSupplies, data centre servers, telecom case stations and solar / wind power inverters.

"The Gate Drive Evaluation Platform (GDEV) is a critical addition to our SiC technology portfolio because SiC is still relatively new and there are some unknowns surrounding the operating characteristics under various conditions," said Corey Deyalsingh, director, Power Control at Littelfuse.

"The GDEV helps engineers understand the operating characteristics of SiC devices. By utilszing this evaluation platform, designers will be better informed about the incredibly energy efficient opportunities that SiC technologies present. Equipped with that knowledge, we anticipate that designers will be more likely to incorporate SiC into their future designs."

The Gate Drive Evaluation Platform from Littelfuse enables users to evaluate continuous operation of SiC power MOSFETs and diodes under rated voltage and rated current, delivering real power to the load. It also lets them analyse system-level impacts associated with SiC-based designs including efficiency improvements, EMI emissions and passive components (size, weight, cost). Other features are include the ability to compare the performance of different gate driver solutions under well-defined test conditions, and to test gate driving circuits under continuous working conditions to evaluate thermal performance and EMI immunity.

news review

### Octopus electric vehicles and EO charging launch EV charging solution

OCTOPUS ELECTRIC VEHICLES and EO Charging launch an all-in-one EV home charging bundle to help consumers take advantage of the electric driving revolution – at hugely discounted rates.

The EO Mini Smart Home is the smallest smart electric vehicle charger in the world and is now available through Octopus Electric Vehicles in conjunction with Octopus Energy's EV energy tariff, Octopus Go.

Founded in 2015, EO has set the bar for EV charging solutions, and to date has shipped over 20,000 chargers to more than 30 countries around the world. It has released a sleek and stylish smart charger that is designed to be inconspicuous when installed at an EV owner's home. It is smaller than an A5 piece of paper, making it the most compact at-home electric vehicle charger in the world.

Octopus Electric Vehicles is an independent EV advisory and leasing business that has helped thousands of people find the right combination of vehicle, charger and tariff. It works alongside Octopus Energy's Go EV tariff, which uses dynamic time of use pricing to allow drivers to charge their car when it's cheapest or greenest – including at 5p/Kw overnight. That's 70% cheaper than legacy suppliers' equivalent tariffs and is ten times cheaper than fossil fuel cars – at just 1p per mile driving.

From April 2020, changes to Benefit In Kind taxation mean employees can get electric vehicles tax-free, via salary sacrifice schemes, at no cost to their employers. This launch anticipates a huge increase in demand for effective home charging solutions for savvy drivers looking to go electric.

Currently, many electric vehicles are sold in silo without the home charging technology and the green energy tariff. This collaboration integrates all the key components that are required for customers planning to transition to an electric vehicle.

The game-changing compact charger is available for an introductory price of £369.00. For an initial leasing cost plus £271 ongoing, customers who take advantage of the OEV bundle will get the Nissan Leaf with 8,000 miles per year, the EO Mini Smart Home charger including installation, plus the Octopus GO tariff, offering charging for just 1p per mile. The bundle is available for a limited time only.

Fiona Howarth, CEO of Octopus Electric Vehicles comments:

"Octopus Electric Vehicles is delighted to partner with EO to be able to offer this incredibly sleek, stylish and smart charger to customers. We want to make electric vehicles the go-to option for anyone considering a new car.

At-home charging technology can be a stumbling block for people looking at transitioning to EVs, as previous models available are often large and clumpy.

"The EO Mini Smart Home makes this a

problem of the past. We are incredibly proud to partner with a business that has similar values to ours, one that breaks the mould and is constantly looking to innovate within the electric vehicle market to deliver affordable, convenient electric vehicle solutions."

Charlie Jardine, CEO of EO comments:

"Getting a charger installed at home should be hassle-free - and that's why we've partnered with Octopus Electric Vehicles to create the ultimate electric vehicle package."

"Electric vehicle chargers are more than 'just a plug'. They're the first piece of the puzzle in giving people energy autonomy and the future of mobility relies on the smart charging technology we're developing.

"Together with Octopus Electric Vehicles, we're making the process of getting a charger installed at home and using the government grant as simple as shopping online."

# Controllis introduces high capacity rectifiers with solar integration

CONTROLLIS, a leading global supplier of low carbon and carbon neutral hybrid power solutions has added the Smart48 DC power system to its portfolio. An efficient and highly scalable power platform, the Smart48 DC power system will help telecoms, mobile and tower companies provide more reliable, efficient and green power for their networks. Operators looking to reduce their carbon footprint now have the option of combining mains rectification and solar power using a single integrated solution.

The Smart48 DC power system can provide 2kW to 300kW of power from a single 19"" rack which can be split between MPPT solar inputs and mains rectifiers. The system can also prioritise solar power over mains power, saving energy and massively reducing an operator's carbon footprint. The Smart48 can be deployed in any part of the network, from small mobile cell sites to large data centres, and will allow operators to quickly and easily upgrade their networks to run on both mains and / or solar power.

The compact system includes highly efficient hot swappable rectifier and solar modules, n+1 redundancy, intelligent fan cooling and advanced battery monitoring and management. The system also includes a controller module, multichannel Low Voltage Disconnects and circuit breakers to protect the batteries and the site as a whole.

"The Smart48 DC power system provides the ideal solution for telecoms operators looking to save energy costs and reduce their carbon footprint." says Lee Johnson, Head of Sales and Marketing at Controllis. "It allows operators to incrementally upgrade the power to any part of their network infrastructure and easily add solar power where and when required, all from a single compact shelf."

He continues "Because we are able to prioritise solar power over mains power, operators benefit from reducing their power costs and having greener, more efficient and reliable networks."

The Smart48 DC power system is the latest offering in a series of initiatives from Controllis to provide highly efficient, reliable and green site power solutions to the telecoms industry. Alongside their low carbon and carbon neutral DC generator based hybrid power systems, Controllis provide lithium ion telecoms batteries and a range of solar power solutions.

As a data driven company, all Controllis products have comprehensive remote management with data analytics capabilities. The Controllis Smart48 DC power system is globally available along with its comprehensive portfolio of DC hybrid power solutions.

#### Maserati starts testing its first 100% electric powertrain

IMPLEMENTING its plans for the electrification of its range, as previously announced, Maserati has started the testing phase of its new full electric propulsion systems that will equip the future models of the brand.

Some experimental vehicles have now been built equipped with the new innovative powertrain, 100% electric with 100% Maserati technology, developed at the new Innovation Lab in Modena. During this experimental phase, the sound that will characterise the electric engine will also be developed. The next full electric models will have a distinctive signature sound, already a unique attribute of all Maserati cars equipped with traditional combustion engines.

Customers will therefore benefit from 100% electric propulsion vehicles that will combine driving pleasure, comfort and performance with a unique and unmistakable sound.

Thanks to the tests conducted in various conditions of use on both road and track, important data will be acquired for the development and definition of the new electric powertrains, which will be used for future models in the Maserati range. The new Maserati GranTurismo and GranCabrio will be the brand's first cars to adopt 100% electric solutions and will be built at the Turin production hub.

### Next steps towards miniature power supplies

INFINEON TECHNOLOGIES AG is taking the next step towards smallest power supply devices for automotive electronics. As first chipmaker, the company set up a dedicated production process for flip-chip packages that is fully aligned with the high quality requirements of the automotive market. Infineon now launches the first respective product: the linear voltage regulator OPTIREG<sup>™</sup> TLS715B0NAV50.

With flip-chip technology, the ICs are installed upside down in the package. With the heated part of the IC facing the bottom of the package and being closer to the PCB, thermal inductance can be improved by a factor between 2 and 3. The higher power density enables a significantly smaller footprint than conventional package technologies. The footprint of Infineon's new linear voltage regulator (TSNP-7-8 package, 2.0 mm x 2.0 mm) is more than 60 percent smaller than that of an established reference product (TSON-10 package, 3.3 mm x 3.3 mm) while the thermal resistance stays the same. This makes the new device particularly suitable for applications with very limited board space, such as radar and cameras. The OPTIREG TLS715B0NAV50 provides 5 V with a maximum output current capability of 150 mA.

Flip-chip technology has been used in consumer and industrial markets for several years. Due to increasingly strict space requirements, particularly in the growing number of radar and camera systems, also automotive electronics require smaller power supply solutions – albeit with much higher quality requirements. In order to offer bestin-class flip-chip quality Infineon does not rely on a subsequent qualification

of existing consumer and industrial products but rather on a dedicated production process for automotive devices.

In the future, flip-chip technology will strengthen Infineon's overall portfolio of automotive power supply products in the OPTIREG family. The chipmaker is planning to apply it also to its switch mode voltage regulators and power management ICs.

# MOSFET driver for synchronous rectification from diodes incorporated

DIODES INCORPORATED announced the introduction of the APR348 secondary-side, multi-mode synchronous rectification MOSFET driver, designed for AC-DC rectification circuits in general consumer applications, notebooks, and USB adapters.

The APR348 is capable of driving the external MOSFET in both high-side and low-side secondary-side synchronousrectifier configurations. This flexible and efficient device supports secondary-side output voltages up to 20V in continuous conduction mode (CCM), discontinuous conduction mode (DCM), and quasiresonant (QR) flyback modes. These options give development teams total freedom over how they implement synchronous rectification.

Manufacturers often choose an external MOSFET when implementing synchronous rectification as it provides greater efficiency converters. As the APR348 requires very few additional external components, engineers can still realize extremely small and efficient power supply designs that meet the

demands of the consumer sector. A key design feature of the APR348 is fast turn-on and turn-off times, which reduces power loss and ensures safe operation when in CCM mode. The device also features a blanking period to set the minimum turn-on period for the MOSFET; this significantly improves performance by limiting the impact of voltage ringing. The APR348 also features a light load (LL) mode, which uses an internal timer to skip cycles when there is no load or only a light load detected at the output. This design delivers lower standby power at no load. In addition, high-side switching does not require an additional transformer winding, further minimizing the bill of materials cost. news review

# Opel to build plant manufacturing battery cells in Kaiserslautern

SUPPORTED by the Federal Government and the state of Rhineland-Palatinate, the largest battery cell production for electric vehicles in Germany is to start at the traditional Opel location from 2024. According to Opel CEO Michael Lohscheller, around € billion (\$2.22 billion) will be invested in the future project.

Around 2,000 jobs are to be created at the location. The Mayor of Kaiserslautern, Klaus Weichel, and the Chairman of the Opel Works Council in Kaiserslautern, Thorsten Zangerle, also paticipated in the working meeting.

Federal Minister for Economic Affairs Peter Altmaier expressed his pleasure on the European Commission reviewing and approving the first major battery project for Europe in just a few weeks. Kaiserslautern will be a part of this first joint battery project. Together with the parent company Groupe PSA and Total's

subsidiary, Saft, Opel wants to found a joint venture called ACC (Automotive Cell Company) that produces battery cells for electric cars.

From 2023, the automaker wants to gradually build three blocks with a capacity of 8GWh each. Around half a million vehicles per year can thus be supplied with battery cells that will be 'Made in Kaiserslautern'. A total of two plants with a total capacity of 48 GWh are to be built – in addition to Kaiserslautern in the Hauts de France region.

This would correspond to a production of about 10 to 15% of the expected European market. The total investment volume for this project is almost €5 billion (\$5.55 billion).

# ABB wins \$30m power equipment order to bolster Germany's renewable energy integration

ABB has won an order worth around \$30 million from Amprion GmbH, a German transmission grid operator that provides electricity to more than 29 million people, from the Alps in South of Germany to Lower Saxony, to supply phase-shifting transformers (PSTs) that will optimize power flow in the German electricity network and help in the integration of renewable resources. These transformers have the potential to offer savings of more than \$110 (€00 million), over 3 years.

Power generated by windfarms is unpredictable. To keep the grid stable, electricity produced in conventional power plants must be increased or decreased at very short notice, which is both inefficient and costly. For these so-called redispatch costs Germany is paying about \$1.7 billion (€.5 billion(1)) annually. To better control the flow of power in the existing grid infrastructure, ABB is supplying two PSTs with 2,494 megavolt amperes (MVA) capacity each, from its transformer factory in Bad Honnef, Germany.

These PSTs, amongst the

most powerful in the world will enable Amprion to integrate wind power more efficiently.

ABB has been at the forefront of developing PST technology. First developed by Westinghouse Electric Corporation T&D in the 1950s and acquired by ABB in 1989, PSTs require a deep evaluation of the power system to define their optimum application and location. Their demanding size and complexity require advanced design

and manufacturing skills along with stringent quality control. "Phase-shifting transformers are a specialized solution that carry out the complex task of controlling power flow in the electricity grid. This enables our customers to optimize grid investments and avoid costs when integrating renewable power like offshore wind while improving their economic viability" said Bruno Melles, Managing Director of ABB's Transformers business line, part of ABB's Power Grids business.

ISS INDUSTRY STRATEGY SYMPOSIUM

### 1-3 APR 2020 BRUSSELS, BELGIUM

#### SEMICONDUCTORS ENABLING A DIGITAL, SECURE AND SUSTAINABLE FUTURE

A POWERFUL FORUM FOR IDENTIFYING COLLABORATION OPPORTUNITIES TO STRENGTHEN EUROPE'S COMPETITIVE ADVANTAGE IN THE DIGITAL ECONOMY.

LOCATION Steigenberger Wiltcher's

Steigenberger Wiltcher's Avenue Louise 71 1050 Brussels, Belgium

#### SEMI EUROPE CONTACT

Pantelitsa Markus, Senior Program Manager E-mail: pmarkus@semi.org

www.semi.org/eu

### Better etching enhances selective area doping for vertical GaN power devices

Multi-step etching slashes the leakage current in regrown GaN *p-n* junctions for selective area doping.

#### BY HOUQIANG FU, KAI FU AND YUJI ZHAO FROM ARIZONA STATE UNIVERSITY

GaN IS A VERY ATTRACTIVE material for making power electronics. It has a bandgap that is three times wider than the incumbent, silicon, and a critical electric field that is more than ten times higher. Thanks to these attributes, devices made from GaN can realise higher breakdown voltages when they have the same thickness as those made from silicon, or a similar breakdown voltage with less material.

|                                             | Si   | 4H-SiC | GaN   |

|---------------------------------------------|------|--------|-------|

| E <sub>g</sub> (eV)                         | 1.2  | 3.2    | 3.4   |

| 3                                           | 11.9 | 9.7    | 10.4  |

| μ (cm²/Vs)                                  | 1240 | 980    | 1000  |

| K (W/mK)                                    | 145  | 370    | 253   |

| V <sub>sat</sub> (×10 <sup>7</sup><br>cm/s) | 1    | 2      | 3     |

| E <sub>c</sub> (MV/cm)                      | 0.3  | 3.1    | 4.9   |

| BFOM                                        | 1    | 710    | 3,200 |

| BHFFOM                                      | 1    | 84     | 215   |

| JFOM                                        | 1    | 20     | 49    |

Table 1. Material properties and power electronics figures-of-merit (FOMs) for silicon, SiC and GaN. E<sub>g</sub>: bandgap;  $\epsilon$ : permittivity;  $\mu$ : mobility; K: thermal conductivity; V<sub>sal</sub>: saturation velocity; E<sub>c</sub>: critical electric field; BFOM: Baliga's FOM; BHFFOM: Baliga's high frequency FOM; JFOM: Johnson's FOM. The FOMs of silicon are normalised to 1 to ease comparison.

Additional strengths of GaN devices are a low onresistance and a high switching speed, merits that are reflected in outstanding values for various figures-ofmerit (see table 1).

However, these excellent material properties are of no practical benefit unless they are harnessed in electronic devices that excel on many fronts, and lead to efficiency gains in the likes of the power grid, electric vehicles, renewables, data centres, wireless charging, and consumer electronics.

Building great GaN devices is far from trivial, with success hinging on the use of the best geometry. Early development focused on lateral GaN power devices, such as HEMTs, grown on foreign substrates. With this architecture, breakdown voltages are held laterally, and currents flow laterally. That's not ideal. Part of the problem is that there are issues associated with surface states that can lead to performance degradation, and also result in reproducibility and reliability concerns. In addition, the heat that is generated concentrates in a very narrow region, causing device temperature to rise; and the higher breakdown voltages require a larger chip area, an impediment to scalability.

To tackle these issues, our research team at Arizona State University has been developing highperformance vertical GaN power devices on bulk GaN substrates. One merit of this architecture is that it employs homoepitaxial growth, significantly reducing the density of defects, which can deteriorate breakdown voltages and increase leakage currents.

What's more, the vertical device geometry offers: higher voltages and forward currents, without

#### technology processing

sacrificing chip area; better scalability and heat dissipation; and freedom from the effects of surface states.

This approach may raise a few eyebrows, given the high cost of GaN substrates. However, volumes have been steadily growing over the years, large size substrates with diameters of up to 6 inch are starting to emerge, and the substrate price is expected to continue to decrease, due to further expansion of both the power electronic market and that for GaN optoelectronic devices, such as laser diodes.

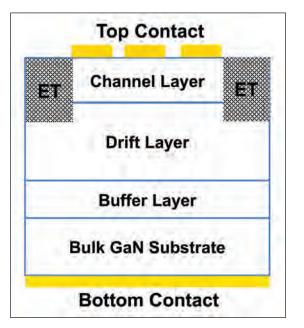

Vertical GaN power devices can be divided into four regions: the buffer layer, the drift layer, the channel layer and the edge-termination region (see Figure 1). We have strategies for improving each of these, leading to a boost in device performance. For the channel layer we are pursuing selective-area doping, an ongoing hot topic.

#### Doping challenges

Selective-area doping remains a huge hurdle for realising the full potential of GaN power electronics. The purpose of this form of doping is to create laterally patterned *p*-*n* junctions (see Figure 2(a)). This type of junction is needed for the fabrication of various GaN power devices, including: junction barrier Schottky diodes or merged *p*-*n*/Schottky diodes (see Figure 2(b)); and vertical junction FETs (see Figure 2(c)). These structures have been produced in silicon and SiC by ion-implantation, but not in GaN.

There are two reasons why it is very challenging to realise ion-implantation in GaN, especially for the production of *p*-type material. One issue is related to the subsequent thermal annealing process, needed to activate implanted atoms and recover crystal damage caused by ion-bombardment. To anneal, often the temperature has to exceed 1200 °C, but GaN begins to decompose at only 900 °C.

The second concern relates to the success of approaches to overcome this decomposition. To alleviate GaN decomposition at high temperatures, researchers have turned to capping layers such as AIN, multi-cycle rapid thermal annealing, and ultrahigh pressure, but in all cases the conductivity of the implanted *p*-GaN is still very low – and judged from the perspective of power devices, it is far from satisfactory.

To overcome this particular hurdle, we have developed a re-growth method that realises selectively doped p-n junctions. With our approach, we can produce high conductivity p-GaN without having to worry about high annealing temperatures and associated GaN decomposition. This process currently remains one of the most important and promising methods for selective-area doping.

Figure 2. a) schematics of selectively doped *p-n* junctions. (b) JBS diodes or MPS diodes. (c) VJFETs.

Figure 1. A crosssectional diagram of the simplified structure of vertical GaN power devices on heavily doped bulk GaN substrates. ET indicates edge terminations

#### technology processing

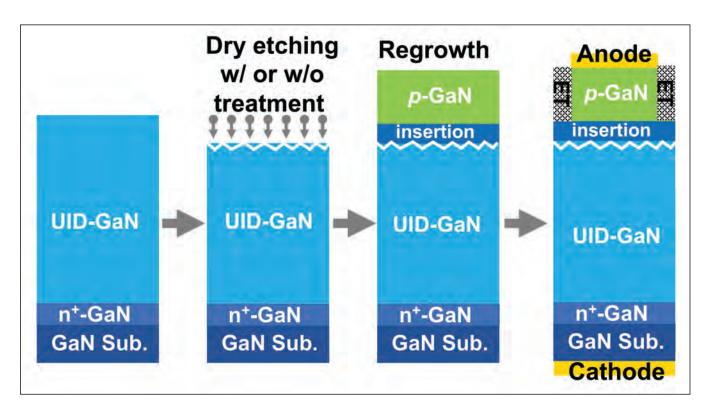

Figure 3. The growth and fabrication process of regrown p-n junctions formed by MOCVD. The structure is homoepitaxially grown on (0001) bulk GaN substrates. It is formed by the growth of an  $n^+$ -GaN buffer layer and an unintentionally doped (UID) GaN drift layer, before undertaking ICP dry etching and surface treatments, followed by the regrowth of a thin insertion layer and p-GaN. Diode fabrication includes the deposition of metal stacks for anodes and cathodes, mesa isolation and edge termination.

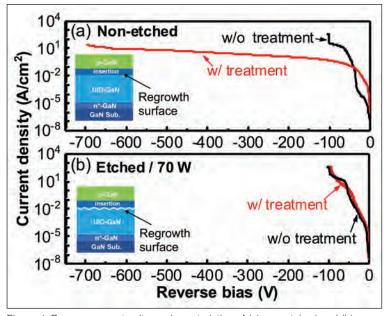

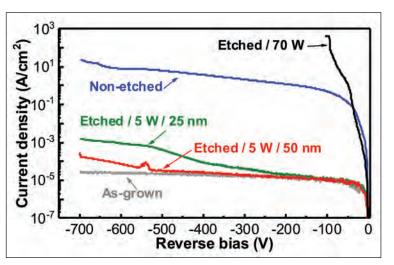

Figure 4. Reverse current-voltage characteristics of (a) non-etched and (b) etched samples with and without surface treatments. The non-etched sample was not subject to ICP plasma etching before regrowth. The etched sample was subject to ICP plasma etching, using a power of 70 W. Etching proceeds at around 200-300 nm/min, a reasonable rate for most device fabrication processes. A high etching power results in stronger ion-bombardment and more severe etching damage.

When we undertake our regrowth process, it is essential to ensure that the subsequent devices are not impaired by large reverse leakage currents, which can limit the ultimate breakdown voltage and increase power conversion losses in power electronics. Our research has uncovered two contributors to large leakage currents: surface contaminations at the regrowth interface, caused by impurities such as silicon, oxygen and carbon, all identified by secondary ion mass spectrometry; and etching damage, often caused by inductively coupled plasma etching, which is a widely used dry etching technique during GaN device fabrication.

To obtain selectively doped p-n junctions (as shown in Figure 2(a)), we could selectively remove part of n-GaN by inductively coupled plasma etching. This step would form trenches for subsequent p-GaN regrowth. However, this process would complicate experiments and analysis, because when two interfaces are exposed there is the possibility that leakage currents will flow in two directions. What's more, this approach is time-consuming.

To avoid these complications and speed turnaround, we begin by making planar regrown p-n junctions (see Figure 3). These junctions, regrown by MOCVD, have provided us with a test vehicle for obtaining fundamental knowledge on regrowth, such as the impact of inductively coupled plasma etching and surface treatments.

#### Evaluating etching damage

For our first set of experiments, we co-load two samples into the MOCVD reactor and regrow without any surface treatment. With this approach, we compared a non-etched sample and one etched with an inductively coupled plasma etching power of 70 W. Both samples suffer from large reverse leakage currents, highlighting the need to properly treat the surface prior to regrowth.

To realise this, we adopt a combination of UV-ozone and acid surface treatments. The former utilises powerful oxygen radicals to oxidize the surfaces and organic residue contaminants. The beauty of this treatment is that it is purely chemical, and thus free from plasma discharging. Note that with inductively coupled plasma etching, ion-bombardment takes place that can lead to charging damage and deterioration of the device's electrical characteristics. After the UV-ozone treatment, both samples are immersed in hydrofluoric acid and hydrochloric acid to remove oxidised materials and future clean the surface.

Electrical measurements reveal a massive reduction in the reverse leakage current in the non-etched sample. But that's not the case in the etched sample (see Figure 4). Our hypothesis for explaining this stark difference is that in the etched sample, etching damage is so severe that it cannot be repaired by surface treatments.

To put this theory to the test, we have carried out another set of experiments involving a lower etching power. This is reduced to just 5 W, a condition that slows the etching rate. We compare the reverse leakage currents in an as-grown sample with three samples that are first subjected to the aforementioned surface treatments. Two samples are etched with a power of 5 W, with an insertion layer thickness of 25 nm and 50 nm, respectively, and a third is etched at 70 W.

Results indicate that slow etching dramatically reduces the reverse leakage currents, and that an insertion layer helps to move the junction away from the regrowth interface, further reducing the reverse leakage current (see Figure 5). For the etched sample with an inductively coupled plasma etching power of 5 W and a 50 nm insertion layer, the reverse leakage current is lower than that in the non-etched sample and similar to the as-grown sample. The key conclusion from this experiment is that the combination of slow etching and proper surface treatments is very effective for regrowth.

Our findings prompt this question: What really drives the difference in reverse leakage currents between these samples? To find out, we have taken a closer look at the regrowth interface.

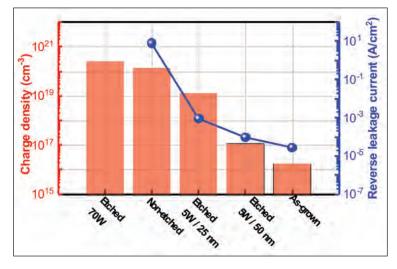

One of its characteristics that can have a significant impact on the regrowth interface, and ultimately reverse leakage currents, is the charge density. Our

Figure 5. Reverse current-voltage characteristics of the non-etched sample and different etched samples. The power indicates the ICP etching power, and the thickness indicates the insertion layer thickness. An etching power of 5 W corresponds to an etching rate of around 20 nm/min.

Figure 6. Charge density at the regrowth interface (histogram) and leakage current (line-shape) at -600 V for the five samples measured in Figure 5. The charge density is extracted from capacitance-voltage measurements.

measurements show that the higher the interface surface density, the larger the leakage current (see Figure 6). The as-grown sample has a low, constant charge distribution, on the order of  $10^{16}$  cm<sup>-3</sup>, while the regrown sample has a peak charge density at the regrowth interface in the range  $10^{17}$ - $10^{21}$  cm<sup>-3</sup>. Measurements also show that a reduction in the etching power lowers the charge density at the regrowth interface, and trims the leakage current.

It is not surprising that a high density of surface charges has profound physical consequences. These charges will create a large electric field at the regrowth interface, and help carriers to tunnel through the potential barrier in the p-n junction and make a significant contribution to the leakage current.

#### technology processing

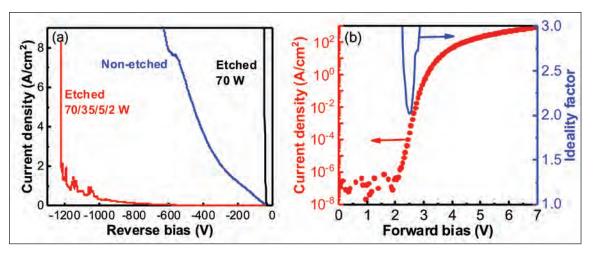

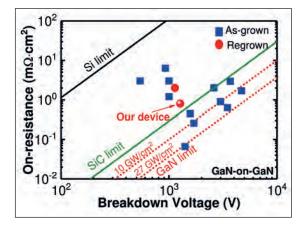

Figure 7. (a) Reverse current-voltage characteristics of the non-etched sample, the sample with the single-step etching, and the sample with the multi-step etching. All samples are subject to the aforementioned surface treatments. (b) Forward current-voltage characteristics and ideality of the sample with the multi-step etching.

Figure 8. Benchmark plot of on-resistance versus breakdown voltage for reported asgrown and regrown GaNon-GaN *p-n* diodes.

#### Multi-step etching

Although slow etching delivers the best results, it's not always practical. It can be very time-consuming, a significant impediment for some device structures with deep trenches and mesas.

To address this concern, we have evaluated multi-step etching, decreasing the ICP power from 70 W to 35 W, and then down to 5 W and finally 2 W. The four-step etching process pays dividends, producing samples with significantly reduced reverse leakage currents and the highest breakdown voltage – it can be over 1.2 kV (see Figure 7(a)).

Another benefit of this multi-step etching process is that it produces a good regrowth surface. We have

#### Further reading

- K. Fu et al. Appl. Phys. Lett. **113** 233502 (2018)

- K. Fu et al. IEEE Electron Device Lett. 40 1728 (2019)

- H. Fu et al. Appl. Phys. Express **11** 111003 (2018)

- H. Fu et al. IEEE Electron Device Lett. 39 1018 (2018)

- H. Liu et al. Appl. Phys. Lett. 114 082102 (2019)

compared two etched samples, both subject to a 70 W etching power. Subsequent slow etching steps, using multi-step etching, produce significant improvements in surface quality. We postulate that during multistep etching, slow etching probably plays a role in recovering the plasma etching damage caused by previous high-power etching steps. In other words, slow etching is more like healing than etching.

Before we can herald multi-step etching as a great success, we need to make sure that it doesn't degrade the forward characteristics of regrown *p-n* junctions. Our measurements are encouraging. Samples exhibits excellent forward rectifying behaviours, with an on-off ratio of around  $10^{10}$  and an on-resistance of  $0.8 \text{ m}\Omega \text{ cm}^2$ . The ideality factor, which can be used to evaluate the performance of a *p-n* junction, is also promising. Its value is around 2.0, a figure that compares favourably with previously reported values for regrown *p-n* junctions, and is close to that of our as-grown samples – they are in the range 1.5-1.8.

Baliga's figure-of-merit provides another opportunity for us to benchmark our regrown p-n diodes. For these devices, it is 2.0 GW cm<sup>-2</sup>. That's very close to the SiC limit, and even comparable to some values reported for as-grown p-n diodes. Given that this work is still in its infancy, we are very encouraged by this result. We anticipate improvements in inductively coupled plasma etching, surface treatments and device fabrications, spurring the performance of GaN regrown p-n junctions towards the GaN limit.

In short, our results show that it is possible to produce high performance regrown p-n junctions via epitaxial regrowth. Our next step is to apply the obtained fundamental knowledge on regrowth to selective area doping. When progress follows, it will make a significant contribution to improving the performance of advanced GaN power electronics, and helping this class of device to create a greener planet.

# 10000 SEMI STANDARDS & COUNTING

Industry counts on SEMI standards.

SEMI is the global industry association serving the product design and manufacturing chain for the electronics industry.

Check out our new standards on SMT & PCB Manufacturing Equipment Communication, Panel Level Packaging & Energetic Materials at:

www.semi.org/collaborate/standards

## Smart manufacturing enabled in the sub-fab

The Industry 4.0 movement is rapidly becoming the de facto means to optimize cost-effective manufacturing. Power electronic device makers want to leverage any practical idea. The experts at Edwards Vacuum point their customers to proven methods that can rapidly reduce costs while improving uptime by focusing on a part of the fab that manufacturers don't always think of first in the quest for a healthier bottom line.

#### BY ALAN IFOULD, ERIK COLLART, ANTONIO SERAPIGLIA, AND MICHAEL MOONEY, EDWARDS VACUUM

IN THE BROADEST TERMS, smart manufacturing refers to collecting data from all aspects of the manufacturing process and by using advanced analytical and modeling capabilities, like artificial intelligence and machine learning, process performance and productivity are improved. It has been embraced by manufacturers in all industries and hailed as the fourth industrial revolution (Industrie 4.0). Semiconductor manufacturers have a long history of collecting and analyzing process data, a key smart manufacturing concept, to improve performance in the fab. Now semiconductor manufacturers are realizing the potential benefits of extending smart manufacturing technologies to the support systems housed in the sub-fab.

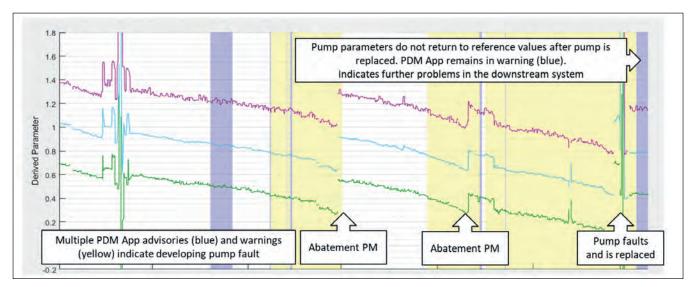

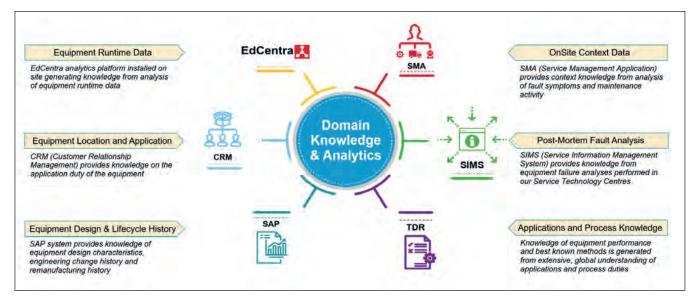

Figure 1: Output from a predictive maintenance application (PdM app) monitoring a vacuum pump

Driven by recent developments in the fields of sensors, data management, analytics and artificial intelligence, a new vision for manufacturing has emerged. This vision includes integrating supply chains; creating virtual factories with cyber-physical systems and digital twins; using big data techniques to interrogate tool, process, yield and facility data; and accumulating and applying critical domain knowledge. Smart manufacturing is a broad concept that is perhaps best generally described as combining technologies and solutions to optimize operations by reducing and/or managing risk and uncertainty. In more practical terms, it is using big data infrastructure and information technology to provide advanced analytics and create a knowledge network of subject matter expertise and operational excellence models. It connects people, machines and processes in a more effective way.

Semiconductor manufacturers have been using advanced automation and statistical control techniques for a long time. As fabs have become more expensive and the cost of unexpected downtime has increased, they have enhanced their capabilities using smart manufacturing concepts. They are also extending them to the critical process support systems found in the sub-fab. The sub-fab has evolved dramatically over the years, from what was originally simply a location outside the fab in which to house supporting equipment, to an environment that is in many ways as sophisticated as the fab itself. A typical HVM fab, starting 40,000 wafer per month, may have 1,500 process tools. It's sub-fab will have 2,000 vacuum pumps and 1,000 abatement systems plus other ancillary systems. Most of the critical steps in a chip manufacturing process require high vacuum conditions and the unexpected failure of a pump can bring significant disruption to the manufacturing process, imposing heavy penalties in lost productivity and scrapped product.

Smart manufacturing in the sub-fab enhances vacuum security with comprehensive monitoring of process critical vacuum and abatement equipment. Using specifically designed models and algorithms, it can predict catastrophic failure modes related to hazardous process chemicals, high flowrates of flammable gases, ingestion of solid materials and condensation of liquids and solids.

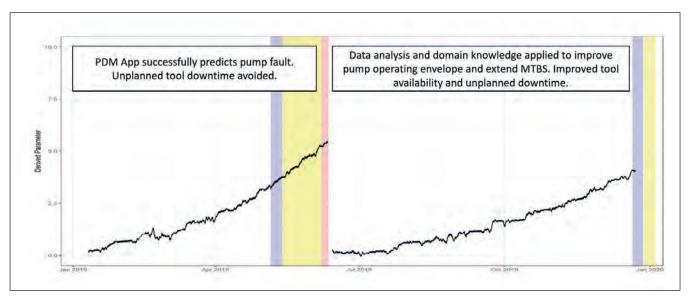

It can also deliver rapid root cause analysis for new and harsh process steps and materials, provide real-time intelligence on critical process vacuum state, accelerate yield ramp by correlating vacuum behaviour with wafer yield, and support fast installation of new sub-fab equipment. Figure 2: PdM data from a process tool in an HVM environment was delivering only 10% of the wafer throughput of other comparable tools

Figure 3 Vibration signal from a pump on an atomic layer deposition tool (left) and a photo of material deposited on internal components.

Figure 4: Dry pump power (orange) and temperature (green), and vibration data (blue) taken from a pump supporting an LP-CVD  $Si_3N_4$  batch deposition process

#### A systems approach to the sub-fab

There is a growing understanding that vacuum pumps and abatement systems are not isolated, selfcontained pieces of equipment. They react to each other and to the wider vacuum system that includes forelines, gate valves, other vacuum components and fab process tools. Monitoring pump parameters can reveal the health of individual pumps and also the health of up- and downstream components, including forelines, gate valves, and process chambers. Data acquired at the pump or abatement system can help determine the size and location of vacuum system leaks.

Algorithms based on vacuum science and thermodynamics can lead engineers to problems that, over time, can have a significant impact on yield. Figure 1 shows output from a predictive maintenance application (PdM app) monitoring a vacuum pump in an HVM environment. The plotted parameter is derived from a multivariate analysis and is responsive to various fault types.

The downward trend in this plot indicates gradual degradation, interrupted by a temporary re-setting. Comparing sub-fab maintenance records with parameter time stamps showed a one-to-one

correspondence between reset events and preventive maintenance procedures performed on the abatement system for the same process tool, indicating that the degradation was connected to the state of the abatement equipment, rather than the health of the pump itself. This was corroborated by other pump parameters not part of the PdM app. The evolution over time further suggested that the abatement PM's themselves did not fully address the issue at hand: the derived parameters did not return to their default values and the downward trend resumed immediately. Ultimately, successful diagnosis of pump faults, combined with the successful segmentation of external downstream issues, resulted in reductions in unscheduled tool down time.

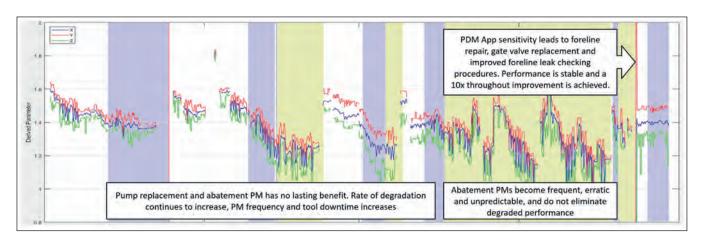

Figure 2 illustrates a case where a process tool in an HVM environment was delivering only 10% of the wafer throughput of other comparable tools. A multivariate PdM App was monitoring the vacuum pump health. The time-series plot of derived parameters clearly showed degradation over time, interrupted by abatement PM-driven re-sets. Initially, the degradation was not as severe and abatement PMs re-set the pump health as indicated by the multiple step changes. But degradation resumed almost immediately after each step improvement.

As time went on this degradation worsened, in spite of the increasing frequency of preventive maintenance on pumps and abatement units. Multiple PdM App alerts were issued. This and other indicators pointed to leaks in the upstream vacuum system. Ultimately a thorough review and repair of forelines and gate valves resolved the issue and resulted in an improved, integrated vacuum system leak check procedure. The wafer throughput gradually returned to match the throughput of peer systems, a 10x improvement for this particular tool.

#### Sensorization

One of the key requirements for smart manufacturing is the development and implementation of sensors to collect and record new signals, beyond the power and temperature sensors typically used to monitor pump health and performance. An innovative vibration sensor (EdCentra Vision, Edwards Vacuum) illustrates some of the requirements and challenges encountered in this "sensorization".

Measuring vibration to monitor the health of rotating machines has a long and successful history. Intrinsic bearings frequencies can be calculated from rotation speeds, and wear-generated perturbations of these frequencies can indicate bearings faults. However, these methods do not translate well to a semiconductor environment where process-induced failure modes are more common than wear-induced. The effects of process-induced failure modes on standard vibration spectra is largely unknown and analysis is complicated by high noise levels.

The new method unlocks key predictive information from vibration data and can detect failure modes that cannot be seen by conventional vibration detectors. It uses a retrofittable "edge" sensor module that includes both sensing and data processing capability to reduce bandwidth requirements on the communications network. Its innovative data analytics methodology translates the complex, noisy vibration signal into a single dynamic coefficient that is easy to compare with existing predictive maintenance parameters. Further vibrational sub-band analysis can provide specific failure mode identification and root-cause analysis, thus providing valuable fault classification (FC) capability.

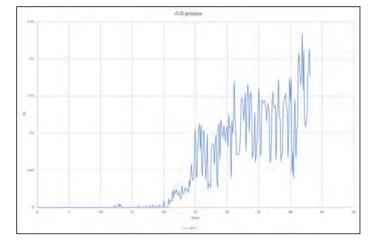

Compared to conventional methods, the new approach increases sensitivity and provides extended, and in some cases unique, predictive maintenance capability for mechanical pump failure modes. Figure 3 shows the vibration signal from a pump on an atomic layer deposition tool. This pump was pro-actively removed from service based on the progression and value of some of the vibration parameters, even though the next calendar-based maintenance was not imminent.

Other pump parameters (not shown), failed to indicate pump deterioration. A detailed analysis of the pump after removal indicated that it was very close to faulting. The picture on the right in figure 3 shows part of the internal pump mechanism with significant process deposition and confirming the vibrationbased prediction. Early replacement prevented unscheduled process downtime and potential losses from wafer scrap. The data management system used to collect this data can combine it with other pump and abatement data in a multi-variate analysis to significantly enhance predictive power and accuracy.

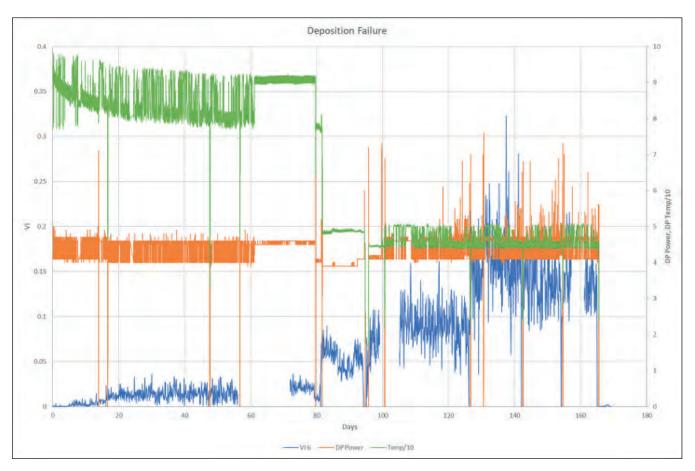

Figure 4 demonstrates the sensitivity of vibration analysis in tandem with traditional pump parameters used historically to monitor conditions. The figure shows an example of pump parameters, dry pump power (orange) and temperature (green), and vibration data (blue). The failure mode in this case was deposition related. As shown in Figure 4, from day 80 onward changing process conditions caused a step-change in temperature. The power curve shows developing patterns at around the 120-day mark, indicating a predictive time horizon of about 40

Figure 5: Information sources for domain knowledge

Figure 6: Application of domain knowledge improves pump operating envelop and extends MTBS days. An important observation to make here is that the vibration data (blue curve) reacted immediately to the modal change and the increased impact of condensable process by-product adversely affecting the operation of the pump.

The heightened sensitivity of vibration gave a pointof-detection time period of around 75 days, 25 days greater than traditional pump parameters. Although vibration analysis is not a new technique, the new vibration sensor detected anomalies otherwise missed by traditional monitoring techniques. Importantly, it has added considerably to the ability to detect process-induced changes to the vacuum pump. Its implementation of edge computation reduces data volume, enables real time analytics and shortens detection latency.

#### Safety

No discussion of smart manufacturing can be complete without considering its potential impact on safety in the sub-fab. The sub-fab is a dangerous place, and safe working practices must be maintained alongside new business processes enabled by smart manufacturing. Examples of potential benefits include: providing advance notice of required equipment interventions so that activities can be better planned, thereby reducing risk and uncertainty associated with the time pressure of urgent activities; using technology to deliver safe standard operating procedures (SOP) and best known methods (BKM) for equipment installation; and incorporating safety data and observations along with asset performance data in the domain knowledge that drives a holistic approach to reducing risk and uncertainty.

#### Domain knowledge is central

Domain knowledge and subject matter expertise are key in providing the right context for any type of machine learning and data science application within smart manufacturing. They are key for several reasons, including the complexity of the manufacturing process, the dynamic nature of dayto-day operations and the general unavailability of large, unambiguous and consistent data sets. People will manage, operate and optimize machines with the

Domain knowledge and subject matter expertise are key in providing the right context for any type of machine learning and data science application within smart manufacturing. They are key for several reasons, including the complexity of the manufacturing process, the dynamic nature of day-to-day operations and the general unavailability of large, unambiguous and consistent data sets

help of digital technologies. Processes will define the interaction of machine to machine, people to machine, and people to people. This constitutes a domain knowledge supply chain essential to enabling smart manufacturing.

For sub-fab vacuum and abatement equipment, domain knowledge encompasses multiple areas of know-how, ranging from specific knowledge of how a process or a piece of equipment works to all the ways the process interacts with the world in which it exists. Vacuum science and thermodynamics provide the basic laws governing critical parameters such as pressure, flow, temperature, and pumping speed. These all display linear and non-linear responses, instantaneous changes, and long-term trends that need to be considered.

Equipment behavior is also ruled by the details of electronic sub-assemblies and mechanical construction. This specific domain knowledge is, for instance, required to distinguish between normal, instantaneous power spikes from pump-vent cycles or powder ingestion and abnormal power spikes from gradual film deposition over long periods of time. A third area relates to the sequence of wafer processing vs. idle and how it affects parameter behavior over time.

The last areas of domain knowledge, measured and inferred alert states and measured degradation states, relate to quantifying and calibrating the progression of abnormal behavior against PdM alert states. Depending on process and equipment type different parameter sets and thresholds may be needed to accurately capture this.

Figure 5 summarizes sources of information that provide critical input for developing domain knowledge.

Figure 6 shows a practical example of domain knowledge at work. PdM Apps, built using domain knowledge, were used to monitor the condition of the pump. The first blue/yellow/band indicates a successful fault prediction that eliminated an unscheduled tool down event. Domain knowledge was then applied to change the operating envelope of the vacuum system. Note the right-hand side of the graph shows a much slower degradation of performance before a second successful fault prediction. This delivers the additional benefit of a longer MTBS and thus tool availability.

#### Tying it together - operational excellence

Smart manufacturing connects people, machines and processes. The full benefit of any smart manufacturing strategy is only realized once these three elements work effectively together to reduce and/or manage risk and uncertainty. Considering the examples discussed, a PdM App may provide a good indication of a fault Equipment behavior is also ruled by the details of electronic subassemblies and mechanical construction. This specific domain knowledge is, for instance, required to distinguish between normal, instantaneous power spikes from pump-vent cycles or powder ingestion and abnormal power spikes from gradual film deposition over long periods of time

condition, but further action is needed to eliminate the root cause of the problem and design out the cause of faults from machines or the processes that support them. New sensors provide more information than ever, but processes are needed to bring new learning to fruition. It is always worth reiterating safety: safe working practices must be maintained alongside new business processes enabled by smart manufacturing. A strong subfab management strategy includes a strong operational excellence model to drive safe and stable operations. Operational excellence incorporates four key areas: standards and procedures; team competency and capability; operational models; and knowledge systems. This is the holistic approach required to provide the solid foundations from which data-driven decision making and improvement activities can be achieved.

#### Summary

Smart manufacturing in the sub-fab combines realtime data with specific domain knowledge to optimize equipment performance. Improved performance enables significant improvements in productivity and yield. A successful implementation of smart manufacturing requires that sub-fab vacuum and abatement systems be treated as a whole as well as individually. Application of big data techniques, data mining, artificial intelligence and machine learning will certainly reveal new relationships within the data, especially as the number and types of sensors grows and data is integrated across the fab, sub-fab and entire manufacturing ecosystem. Operational excellence models will provide the safe and solid foundations needed to realize the full benefits of new learning.

#### photoluminescence

### Photoluminescence captures carbon contaminants in GaN

Omidirectional photoluminescence offers a non-destructive method for measuring the density of carbon contaminants in GaN

CARBON IMPURITIES limit the performance of GaN devices. They create deep levels in the material, leading to leakage currents.

To reduce the levels of carbon contaminants, the first step is to quantify this impurity in the nitrides. Unfortunately that's not easy, because conventional approaches are slow, destructive, and limited in sensitivity. But all these issues can be overcome, according to recent work by a collaboration in Japan between researchers at Tohoku University and SCIOCS.

Spokesperson for this partnership, Kazunobu Kojima from Tohoku University, claims that the team have shown that omidirectional photoluminescence spectroscopy offers a non-contacting, non-destructive, high-sensitivity technique for detecting carbon levels in GaN. Kojima says that even when they examine some of the world's purest GaN crystals, they can measure their carbon content.

#### photoluminescence

The established approach for determining the concentration of elements in compound semiconductor materials is a destructive method known as secondary ion mass spectrometry (SIMS). Using standard depth profiling, this technique has a detection limit for carbon of 3 x  $10^{15}$  cm<sup>-3</sup>. This limit falls to 5 x  $10^{14}$  cm<sup>-3</sup> by switching to a raster change approach.

In comparison, the limit for omidirectional photoluminescence spectroscopy is far lower. A conservative estimate is 10<sup>14</sup> cm<sup>3</sup>.

Another strength of omidirectional photoluminescence spectroscopy is its capability to detect very deep levels formed by point defects. "[These levels are] too deep to detect by deep-level transient spectroscopy, a popular method to detect impurity and defect levels in semiconductors," says Kojima.

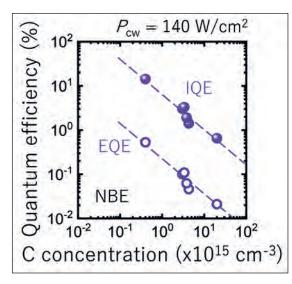

The team have studied six samples – four grown by MOCVD, and the other two by HVPE. Measurements with a SIMS tool with a detection limit of  $7 \times 10^{14}$  cm<sup>-3</sup> reveal that these samples provide a range of carbon impurities. One of the HVPE-grown samples has a carbon concentration below the detection limit, another a value of 2 x 10<sup>16</sup> cm<sup>-3</sup>, and MOCVD-grown materials have values between 3 x 10<sup>15</sup> cm<sup>-3</sup> and 4.3 x 10<sup>15</sup> cm<sup>-3</sup>.

In addition to measuring the external quantum efficiency of the samples, Kojima and co-workers have calculated the internal quantum efficiency by using a streak camera to record the photoluminescence lifetime.

Under excitation, the GaN samples produce photoluminescence over wavelengths ranging from 1.5 eV to 3.5 eV. For the near band-edge emission, which is related to carbon impurities, both the internal and external quantum efficiencies monotonically increase with carbon concentration (see figure). As the

Internal and external quantum efficiencies of near band edge (NBE) photo-;luminescence provide a method to measure carbon concentrations in GaN.

near-band edge external quantum efficiency is only 1 percent at a carbon concentration of  $4 \times 10^{14}$  cm<sup>-3</sup>, it is possible that concentrations below  $10^{14}$  cm<sup>-3</sup> could be measured with this technique.

Measurements of photoluminescence lifetime show that this decreases from 0.78 ns to 0.32 ns as the carbon concentration falls from  $2 \times 10^{16}$ cm<sup>-3</sup> to  $3 \times 10^{15}$  cm<sup>-3</sup>. For lower concentrations, the photoluminescence lifetime plateaus. To try and understand the reason for this, Kojima and co-workers have plotted the radiative and non-radiative lifetimes as a function of concentration – the former has a steady increase with concentration, while the latter mirrors the photoluminescence lifetime. This led the team to postulate that samples contain vacancyrelated intrinsic non-radiative recombination centres, with an estimated density of 2.1 x 10<sup>15</sup> cm<sup>-3</sup>.

#### conference report IEDM

### IEDM details improvements in power electronics

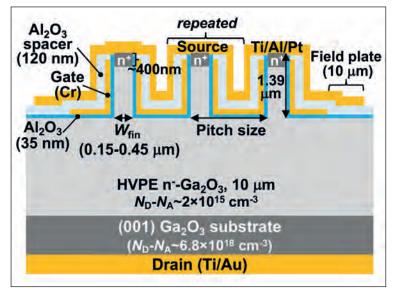

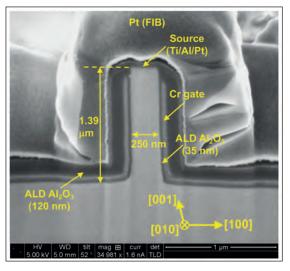

Techniques for supressing degradation in SiC *p-i-n* diodes and IGBTs, enhancing channel mobility in SiC MOSFETs, and improving the blocking voltage and on-resistance of  $Ga_2O_3$  transistors were all unveiled at the most recent IEDM meeting

#### BY RICHARD STEVENSON

TURN ON THE NEWS and there's a good chance you'll hear a story related to climate change. Recently the focus has been on the devastating fires in Australia, but in the last few months you may also have read of accelerated ice-melting in Greenland, demolition of homes in Rwanda to protect citizens from flooding, and the breaking of global temperature records.

For those of us that see climate change as man-made, our challenge is to modify our lifestyle, so that we help to curb carbon emissions. Some of the changes that we could consider may not be to our liking, such as switching to a more plant-based diet and taking fewer flights to sunny climes. But there is one change that we will applaud: far greater deployment of moreefficient power electronics, based on devices made from alternatives to silicon.

Leading this charge is SiC. Sales of diodes and transistors made from this material are ramping fast, as the uptake of these devices branches out from their

deployment in power supplies and inverters to electric vehicles, where they enable an extension to the driving range. Far behind, but with even greater promise, is gallium oxide, a material with an even wider bandgap. It will not be long before the first commercial  $Ga_2O_3$  devices appear on the market, but significant sales are still some years away.

For both SiC and  $Ga_2O_3$ , long-term success hinges on making the devices better and better. Performance must improve, alongside reliability. To succeed, more research is needed to understand the behaviour of the diodes and transistors, and how modifications to designs impact device behaviour.

Presentations detailing progress of this nature were detailed at the latest International Electron Devices Meeting (IEDM). Held in San Francisco between 7 and 11 of December, researchers at IEDM 2019 described techniques to suppress bipolar degradation in SiC *p-i-n* diodes and IGBTs, improve the characteristics of the channel in SiC MOSFETs,

and a Ga<sub>2</sub>O<sub>3</sub> transistor architecture that sets a new benchmark for breakdown voltage.

#### Supressing bipolar degradation

Sales of SiC power devices are dominated by Schottky barrier diodes and MOSFETs. Within this commercial product portfolio there are devices designed to operate between 600 V and 3.3 kV. Higher voltages are possible, but for values of 10 kV and above, SiC *p-i-n* diodes and IGBTs appear to be better alternatives. However, if this pair of devices are to fulfil their potential, a condition known as bipolar degradation must be addressed. This degradation occurs when current passes through these devices and stacking faults arise, leading to an increase in forward voltage. Note that a solution to this impediment could have wider implications, as this type of affliction may also occur in body *p-n* diodes of SiC MOSFETs.

The origin of stacking faults in bipolar devices is basal plane dislocations in the substrate. This form of imperfection comprises two partial dislocations, on either side of a narrow single Shockley stacking fault. Fortunately, during the growth of the epilayer, most of basal plane dislocations are converted into threading edge dislocations. However, a few propagate into the epilayer – most of them are in the form of screw-type basal plane dislocations.

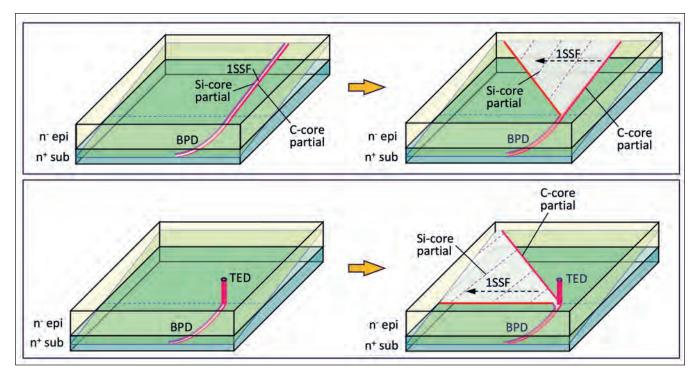

When basal plane dislocations are in the epilayers, once the carrier density exceeds a threshold, there is an expansion of single Shockley stacking faults (see Figure 1). Eventually, right-angled triangular single Shockley stacking faults are formed across the current pass of the device, leading to an increase in forward voltage.

At IEDM several approaches to combat bipolar degradation were described by Hidekazu Tsuchida from Japan's Central Research Institute of Electric Power Industry (CRIEPI).

Tsuchida, who is working with colleagues at CRIEPI, the National Institute of Advanced Industrial Science and Technology and Fuji Electric, says that it is unrealistic to expect a complete elimination of basal plane dislocations through refinements in bulk growth technology. "The average basal plane dislocation density on 'good substrates' has decreased a lot in the last decade. However, we still have a large variation in the quality of commercial SiC substrates." In his opinion, the way forward is to eliminate basal plane dislocations in the epilayers by growing well-chosen heterostructures on good commercial substrates.

Back in 2018, Tsuchida and co-workers reported a study involving the fabrication of SiC *p-i-n* diodes. This effort involved using electroluminescence to determine the threshold current associated with the expansion of single Shockley stacking faults. By measuring the charge in the drift layer during turn off, the researchers converted the current density to a hole density. This revealed that the threshold for the hole density in an *n*-type layer is  $1-2 \times 10^{15}$  cm<sup>-3</sup>.

#### conference report IEDM

Figure 1. Basal plane dislocations (BPDs) in the substrate can propagate into the epilayer (top left), or be converted into threading edge dislocations (TEDs). Most of the BPDs in the epilayer contain a pair of partial dislocations – one with a silicon core, and the other with a carbon core – with a single Shockley stacking fault (1SSFs) between them. Once the carrier density exceeds a threshold, there is an expansion of 1SSFs from the BPDs in the epilayers to create a right-angled triangular 1SSF (top right). This expansion forms across the current pass of the device, leading to an increase in forward voltage. There can also be an expansion of 1SSFs, involving bar-shaped 1SSFs to expand from the BPD segment below the BPD-TED conversion point (bottom right). This can be caused by the injection of minority carriers into a region below the BPD-TED conversion point solution and substrate interface, and also in substrates with a high density of BPDs.

Based on this insight, Tsuchida and co-workers argue that two criteria must be met to ensure the suppression of bipolar degradation. They are the elimination of basal plane dislocations from the region where minority carriers are injected, and the reduction in the minority carrier density to a level below threshold in the region where basal plane dislocations exist.

According to Tsuchida, both these requirements are needed because even if basal plane dislocations in the substrate are perfectly converted to threading edge dislocations at the interface between the epilayer and the substrate, minority carriers are still injected into the substrate. Here, the danger is that the density of these carriers exceeds the local threshold, triggering conversion of the basal plane dislocations in the substrate into stacking faults.

The solution, according to Tsuchida, is to insert a buffer layer with a short carrier lifetime between the substrate and drift layer. This addition reduces the injection of minority carriers into the substrate region.

Initially, the team turned to nitrogen doping to reduce the carrier lifetime in the buffer. However, when the nitrogen concentration exceeded  $1-2 \times 10^{19} \text{ cm}^3$ , this introduced an imperfection known as a double Shockley stacking fault. Keeping the nitrogen concentration low enough to avoid this shortened the carrier lifetime to around 40 ns.

To further reduce this lifetime, Tsuchida and coworkers have recently switched to doping with vanadium, a deeper dopant. When present at a concentration of just 7 x  $10^{14}$  cm<sup>-3</sup>, room-temperature carrier lifetime is shortened to just 13 ns.

The benefit of vanadium doping has been assessed by comparing two sets of SiC p-*i*-n diodes. Controls features a 10 mm-thick, nitrogen-doped drift layer grown on an n-type substrate, and modified variants have an additional buffer, doped with vanadium and nitrogen, inserted between the substrate and drift layer.

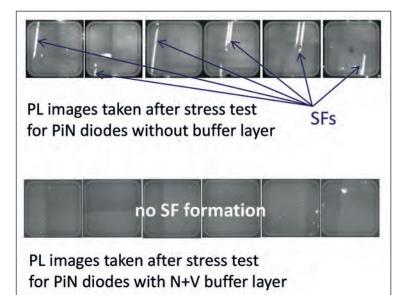

To evaluate the impact of the buffer, measurements were made on 16 controls and 16 variants. Initial forward voltages, recorded at a 18 A drive current, were compared with values after one stress test and then another. The first involved driving diodes at 300 A cm<sup>-2</sup> for an hour, and for the second, devices were run at 600 A cm<sup>-2</sup> for an hour. Analysis of the results showed that the buffer layer leads to a substantial reduction in variation of forward voltage after operation.

#### conference report IEDM

Further insight into the difference between standard devices and those with a doped buffer has come from photoluminescence measurements. This optical technique exposed single Shockley stacking faults in the conventional diode, and the absence of these faults in the modified design (see Figure 2).

Buffer layers may also benefit SiC IGBTs. This type of device would require a *p*-type buffer layer with a short carrier lifetime. Aluminium, which forms a shallow acceptor, is a candidate for doping, as increases in its concentration reduce carrier lifetime. Tsuchida and co-workers suggest that this might be combined with boron, which greatly shortens carrier lifetime.

One of the goals for the team is to map, with precision, the locations across a wafer where basal plane dislocations are converted into threading edge dislocations. Such a study promises to enable a more detailed, quantitative understanding of the expansion of single Shockley stacking faults, and could also aid the development of drift and buffer layers that improve the performance of bipolar devices.

Another target for the researchers is the development of a fast growth technique for making 4H SiC that will trim the density of basal plane dislocations and threading dislocations. The team have already made much progress, realising a growth rate of 3 mm/hour. "[That's] about ten times higher than a typical PVT growth," says Tsuchida.

#### **MOSFET** modifications

The introduction of a new dopant is also behind the improvements made to the performance of SiC MOSFETs. This success, realised by a team from Mitsubishi, involved the introduction of oxygen doping. It led to a significant reduction in channel resistance and an increase in the threshold voltage.

Both of these attributes are highly desired by the designers of power electric systems. Reducing resistance cuts energy losses, and a higher threshold voltage makes it easier to control the system. Normally these improvements are realised by nitridation. However, if the threshold voltage exceeds 3 V, this comes at the expense of a hike in channel resistance.

The team from Mitsubishi have previously addressed this weakness by switching to sulphur. And at IEDM they revealed the results of using another alterative, oxygen, which is a far deeper donor. Spokesman for the team, Munetaka Noguchi, claims that there are no downsides to the use of deep donors. He arrived at this conclusion after considering the results of pulsed measurements that enable an estimate of threshold voltage stability.

Noguchi and co-workers have produced vertical and lateral SiC MOSFETs with oxygen doping. For commercial sales, vertical MOSFETs are preferred.

Figure 2. Photoluminescence measurements on *p-i-n* diodes that have been subjected to a stress test show that the addition of a buffer layer (bottom set of devices) eradicates the formation of single Shockley stacking faults.