CONNECTING THE GLOBAL COMMUNITY

**ISSUE II 2020**

WWW.POWERELECTRONICSWORLD.NET

Best performance for next generation SiC power electronics to address global mega trends

# AIX G5 WW C

- Electric vehicles: on board chargers, power inverters

- Infrastructure: charging stations

- Renewables: solar and wind

- Industrial: motor drives, power supplies

- Power distribution: HVDC

Discover our SiC epi production batch tool with single wafer performance

Made

Germany

www.aixtron.com

# Viewpoin

By Mark Andrews, Technical Editor

#### Power Electronics and the 'New Normal' of 2020

IT WASN'T SO LONG AGO that new work-from-home-office solutions created about as much media excitement as rearranging one's sock drawer on a rainy afternoon. That was before the word 'pandemic' entered daily conversations and more than one-third of worldwide tech employees were in fact working from home. Welcome to the New Normal of summer 2020.

While many of us are still trying to achieve balance between many important and sometimes conflicting objectives, the pandemic has given us all a new perspective on what is important, like our health, families, and our collective futures, and what isn't worth our time or worry.

Throughout all that is happening to us and around us, technology continues to fill the gaps and enable all types of work and life scenarios that didn't necessarily cross our minds just six short months ago. I'm reminded of a former colleague, a poster child for Old School business, who couldn't quite get the knack of email protocol - more than once he hit 'reply all' with comical results. How trivial thoughts like this sound today compared to the global health emergencies we have all experienced. Even though tech industries face unprecedented challenges and opportunities, there are solutions and means to help tomorrow be better than what we have experienced last week or the month before that.

In this issue of Power Electronics World we look at ways that industry leader KLA Corporation is addressing the changing needs for power device inspection, test and metrology. We look

at more efficient, highly accurate wafer singulation technologies from Panasonic that reduce waste and increase throughput, while exploring new thermal interface materials from ABB that enable faster, more consistent module installations. We also delve into the potential of graphite to create new generations of SiC power modules while exploring monolithically integrated GaN ICs. We also consider different GaN possibilities being advanced by UK startup Porotech.

'Business Unusual' has challenged us like never before. But we have also seen the resilience of individuals across the globe who have demonstrated how we can live and work safely and productively even amidst a very changed world. Stay safe!

Editor & Publisher Jackie Cannon Technical Editor Mark Andrews Sales Manager Shehzad Munshi USA Representatives Tom Brun Brun Media Janice Jenkins Director of Logistics Sharon Cowley

Circulation Director Scott Adams

jackie.cannon@angelbc.com mark.andrews@angelbc.com shehzad.munshi@angelbc.com tbrun@brunmedia.com jjenkins@brunmedia.com sharon.cowlev@angelbc.com Design & Production Manager Mitch Gaynor mitch.gaynor@angelbc.com scott.adams@angelbc.com Chief Executive Officer Stephen Whitehurst stephen.whitehurst@angelbc.com

+44 (0)1923 690205

+44 (0)1923 690215 +001 724 539-2404 +001 724-929-3550

+44 (0)1923 690200 +44 (0)1923 690214

+44 (0)2476 718970 +44 (0)2476 718970 Joint Managing Director Sukhi Bhadal Joint Managing Director Scott Adams Directors Jackie Cannon, Sharon Cowley sukhi.bhadal@angelbc.com scott.adams@angelbc.com

+44 (0)2476 718970

Published by Angel Business Communications Ltd, Unit 6, Bow Court, Fletchworth Gate, Burnsall Road, Coventry CV5 6SP, UK, T: +44 (0)2476 718 970 E: info@angelbc.com

PEW Magazine is published four times a year on a controlled circulation basis. Non-qualifying individuals can subscribe at: £105.00/e158 pa (UK & Europe), £138.00 pa (air mail), \$198 pa (USA). Cover price £4.50. All information herein is believed to be correct at time of going to press. The publisher does not accept responsibility for any errors and omissions. The views expressed in this publication are not necessarily those of the publisher. Every effort has been made to obtain copyright permission for the material contained in this publication. Angel Business Communications Ltd will be happy to acknowledge any copyright oversights in a subsequent issue of the publication. Angel Business Communications Ltd © Copyright 2020. All rights reserved. Contents may not be reproduced in whole or part without the written consent of the publishers. The paper used within this magazine is produced by chain of custody certified manufacturers, guaranteeing sustainable sourcing. © Copyright 2020.

We strive for accuracy in all we publish; readers and contributors are encouraged to contact us if they recognise an error or omission. Once a magazine edition is published [online, in print or both], we do not update previously published articles to align old company names, branding, marketing efforts, taglines, mission statements or other promotional verbiage, images, or logos to newly created or updated names, images, typographic renderings, logos (or similar) when such references/images were accurately stated, rendered or displayed at the time of the original publication. When companies change their names or the images/elxet used to represent the company, we invite organizations to provide Angel Business Communications with a news release detailing their new business objectives and/or other changes that could impact how customers/prospects might recognise the company, contact the organisation, or engage with them for future commercial enterprise.

## Rohm and Leadrive establish joint lab for SiC automotive modules

JAPANESE electronics firm Rohm and Leadrive, a Chinese maker of automotive power devices, have established a joint research lab in Shanghai to develop power modules and inverters for vehicles around Rohm's SiC MOSFET bare chips and isolated gate drivers.

Rohm and Leadrive have been collaborating on automotive applications using SiC power devices since 2017. Establishing a joint research lab is designed to give both companies the opportunity to further accelerate the development of innovative power solutions.

"The adoption of power modules that integrate SiC chips for new energy vehicles will become an industry trend over the next couple of years. Commercialising mature SiC-equipped devices by collecting resources from around the world and carrying out R&D gives us a competitive edge as an automotive Tier 1 manufacturer," says Jie Shen, chairman and general manager at Leadrive Technology.

"Rohm has been a strong partner since Leadrive was founded. This joint research

laboratory will allow us to deepen our collaboration," Shen continues. "As a pioneer and leading supplier of SiC power devices, Rohm has a proven track record for providing high quality power solutions that combine industryleading device technology with driver ICs, and we are committed to promote the use of SiC for xEV applications," adds Kazuhide Ino, CSO, and senior director of power device business at

"Understanding customer needs and market trends is extremely important when developing SiC power device technology. Leadrive plays an important role in the applied research of SiC as a manufacturer of automotive power modules and inverters. Through this joint research lab, we can strengthen our partnership and contribute to the technical innovation of automotive power solutions centred on SiC," Ino concludes.

#### Heraeus launches new bonding ribbon for SiC modules

HERAEUS has announced a copper bonding ribbon called PowerCuSoft Ribbon that it has optimised for surface contacting on SiC semiconductors.

Copper offers better thermal, electrical and mechanical properties compared to aluminium wire and ribbons. The material heats up less than aluminium and can withstand higher module temperatures this improves the lifespan and reliability of power modules, according to the company.

PowerCuSoft Ribbon can withstand module temperatures of up to 250degC. In tests, copper ribbons show a ten to twenty times longer service life than comparable products made of

aluminium, while at the same time increasing the energy density in the module.

"SiC semiconductors are in the fast lane due to their high power density," says Christian Kersting, product manager power bonding wires at Heraeus Electronics. "In order to be able to use the advantages of these products, module manufacturers need high-performance packaging and interconnection technologies."

Compared to copper wires, ribbons also offer cost advantages, as one ribbon replaces several copper wires. Manufacturers are thus able to optimise the manufacturing costs per module

as output increases. Depending on the module design, even twice the number of modules per hour can be produced.

### GaN and SiC power semi markets to pass \$1B in 2021

WORLDWIDE revenue from sales of SiC and GaN power semiconductors is projected to rise to \$854 million by the end of 2020, up from just \$571 million in 2018, according to Omdia's SiC & GaN Power Semiconductors Report - 2020. Market revenue is expected to increase at a double-digit annual rate for the next decade, passing \$5 billion by 2029. These long-term market projection totals are about \$1 billion lower than those in last year's edition of this report. This is because demand for almost all applications has slowed since 2018. Moreover, device average prices fell in 2019. A note a caution: The equipment forecasts used to create this year's forecast all date from 2019, and do not take account of the impact of the COVID-19 pandemic.

SiC Schottky diodes have been on the market for more than a decade, with SiC metal-oxide semiconductor field-effect transistors (SiC MOSFETs) and junctiongate field-effect transistors (SiC JFETs) appearing in recent years. SiC power modules are also becoming increasingly available, including hybrid SiC modules, containing SiC diodes with Si insulatedgate bipolar transistors (IGBTs), and full SiC modules containing SiC MOSFETs

with or without SiC diodes. SiC MOSFETs are proving very popular among manufacturers, with several companies already offering them. Several factors caused average pricing to fall in 2019, including the introduction of 650, 700 and 900 volt (V) SiC MOSFETs priced to compete with silicon superjunction MOSFETs, as well as increasing competition among suppliers.

By the end of 2020, SiC MOSFETs are forecast to generate revenue of approximately \$320 million to match those of Schottky diodes. From 2021 onwards, SiC MOSFETs will grow at a slightly faster rate to become the best-selling discrete SiC power device. Meanwhile, SiC JFETs are each forecast to generate much smaller revenues than those of SiC MOSFETs, despite achieving good reliability, price and performance. Hybrid SiC power modules, combining Si IGBTs and SIC diodes, are estimated to have generated approximately \$72 million in sales in 2019, with full SiC power modules estimated to have generated approximately \$50 million in 2019. Full SiC power modules are forecast to achieve over \$850 million in revenue by 2029, as they will be preferred for use in hybrid and electric

vehicle powertrain inverters. In contrast, hybrid SiC power modules will be used in photovoltaic (PV) inverters, uninterruptible power supply systems and other industrial applications, mainly, delivering a much slower growth rate. There are now trillions of hours of device field experience available for both SiC and GaN power devices. Suppliers, even new market entrants, are demonstrating this by obtaining JEDEC and AEC-Q101 approvals. There do not appear to be any unexpected reliability problems with SiC and GaN devices; in fact, they usually appear better than silicon.

SiC MOSFETs and SiC JFETs are available at lower operating voltages, such as 650V, 800V and 900V, allowing SiC to compete with Si Superjunction MOSFETs on both performance and price. End-products with GaN transistors and GaN system ICs inside are in mass production, particularly USB type C power adaptors and chargers for fast charging of mobile phones and notebook PCs. Also, many GaN devices are being made by foundry service providers, offering in-house GaN epitaxial crystal growth on standard silicon wafers, and potentially unlimited production capacity expansion as volumes ramp.

#### CoolSiC for ultra-fast pit stops ...

SPAIN based power conversion group Ingeteam and Infineon have teamed up for best customer experience in superfast electric vehicle (EV) charging. Rated at 400 kW, the converter INGEREV RAPID ST400 from Ingeteam is based on CoolSiC MOSFETs in an EasyDUAL 2B housing.

A single charging point implements eight of Infineon's FF6MR12W1M1\_B11 modules. Depending on the charging capabilities of the respective car, an EV now only needs to stop for a minimum of 10 minutes for an 80 percent percent battery charge. This is comparable to refueling a conventional car with internal combustion engine. The design of the INGEREV RAPID ST400 converter has proven to operate successfully at real life conditions. Already last year, the

first project integrating this technology was developed, implemented, and commissioned by IBIL, the leading recharge technology services company in Spain, for Repsol, the multienergy provider and leading spanish petrol station operator.

Located at Ugaldebieta in the Bay of Biscay region, it was commissioned in October 2019 as a lighthouse project in the field of electro mobility. The facility on the heavily frequented A-8 motorway features four ultra-fast charging points. These units guarantee optimal distribution of the available power between the four vehicles that can be connected simultaneously. More importantly, the technology is flawless and operates without any major downturns since the start.

# Panasonic Plasma Dicing

For higher throughput and increased yield per wafer

Plasma dicing addresses the challenges of dicing smaller and thinner dies.

#### BY PANASONIC

EVERY PERSON with a passing interest in electronics has heard of Moore's Law: the processing power of affordable CPUs – or the number of transistors on a chip - will roughly double every two years. It is credit to both Gordon Moore's foresight, and the technical and engineering teams around the world who continue to innovate, that the 'Law' is still even being discussed today.

Part of the reason for chip size reduction lies in the shrinking of technology nodes (process geometries). Currently the smallest node that is being manufactured in mass volume is 7nm, and even smaller sizes are under development in the industry. The increase in processing power and speed and the miniaturisation and integration of electronic functions

that continue to result from such technological advances lie at the heart of the pervasiveness of electronics in our everyday lives: the smart phones that we rely on; the uptake of artificial intelligence in smart homes and cities; driverless vehicles; remote medical home diagnostics – there is not one aspect of life that electronic products and systems have not penetrated.

But for this to continue, it is not only in the area of photolithographic processing that technology needs to keep innovating. Once a wafer has been created it must be singulated into individual dies, and as dies are becoming smaller and thinner, many products are facing difficulties caused by the singulation or dicing process.

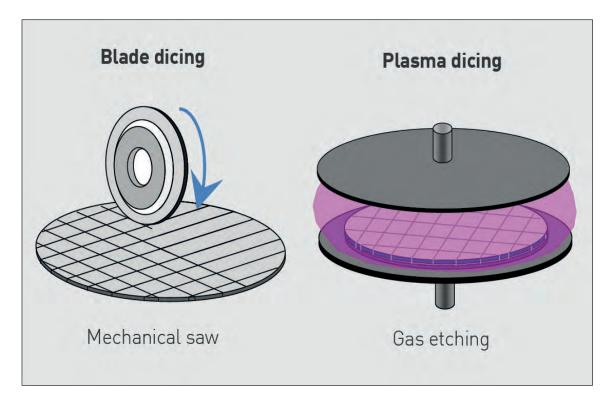

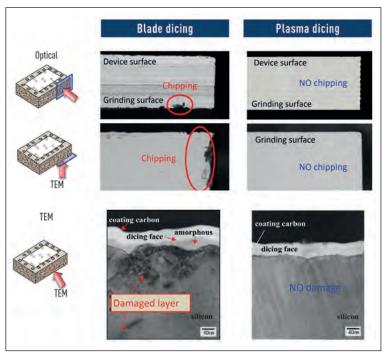

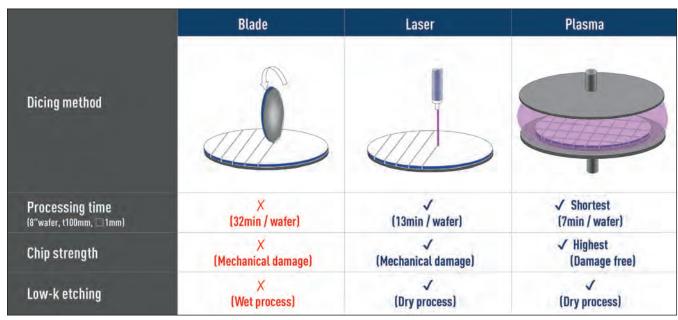

Figure 1: Blade dicing & Plasma dicing processing

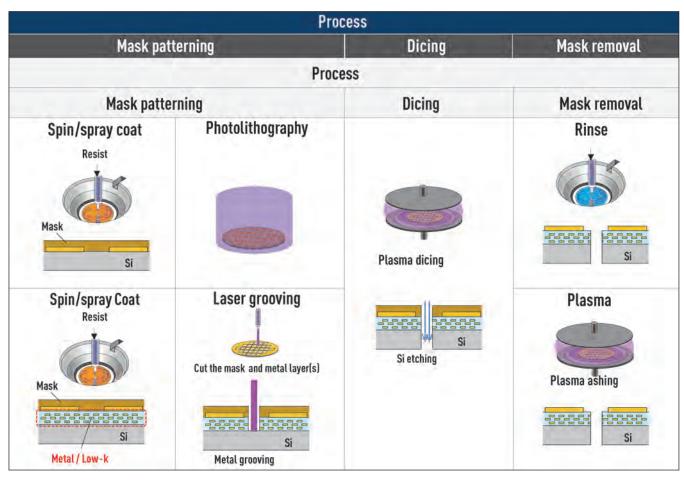

Figure 2: Panasonic's chemical etch dicing process

New challenges include: increasing material loss due to the width of the dicing street; mechanical damage such as chipping; and increasing processing time. Now, Panasonic has developed a plasma dicing process that in certain circumstances can replace mechanical dicing, which addresses these issues.

#### Types of dicing process

Traditionally, two dicing technologies have been used: scribing and breaking, and mechanical cutting using a dicing saw ("blade dicing"). Scribing and breaking causes stresses on the wafer and die and results in chipping and yield inefficiencies. Blade dicing also introduces stresses and contaminants which are more problematic as the die size and process geometries shrink. Laser dicing is another method which is faster than using a saw but can also cause cracking and damage to the chip.

Now, a new dicing process has been introduced which uses a plasma chemical etching process, where all the 'cuts' are achieved in a single batch process, with no die stressing, no contamination, and an increase in wafer dicing throughput. Also, more chips can be designed onto the wafer as narrower dicing 'streets' can be used due to mask patterning. In addition, the

Figure 3: Damage evident on chip samples using blade dicing (left); none present when plasma dicing is used

#### Panasonic Cover Story

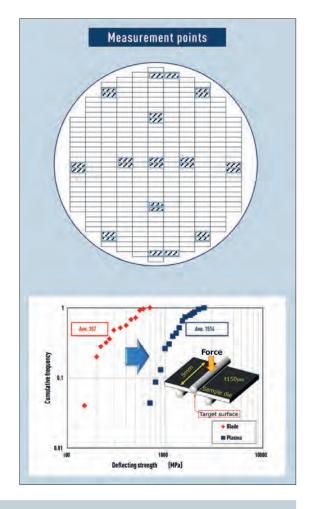

Figure 4: Strength tests prove the benefits of plasma dicing

8 7 Plasma 6 5 4 3 Blade Throughput [WPH] 2 0 0 2 3 5

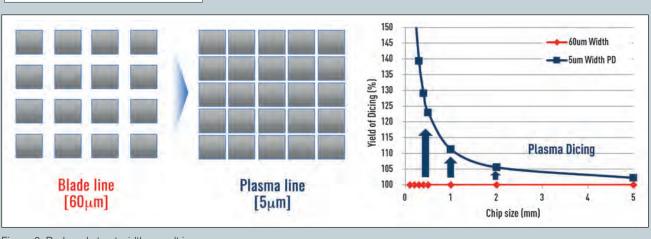

Left: Figure 5: Productivity curves show increasing benefits with smaller chip

mask pattern enables flexibility in the choice of chip sizes, shapes, positioning. The two approaches are shown in Figure 1.

Figure 2 shows Panasonic's plasma dicing process which uses a dicing mask. The plasma process etches the streets by chemical reaction. Plasma dicing uses pulsed or time-multiplexed etching, with the process cycling repeatedly between two phases: a near-isotropic plasma etch where ions attack the wafer in a near-vertical direction; followed by the deposition of a chemically inert passivation layer which protects the entire substrate from further chemical attack.

During etching, the vertically-directed ions attack the passivation layer only at the bottom of the trench (not along the walls), exposing the substrate to the chemical etch. This two-phase process results in sidewalls that increase and decrease with an amplitude of between 100 and 500nm. The cycle time is adjustable: short cycles yield smooth walls; longer cycles yield a higher etch rate.

#### Particle-free and damage-free process

The action of the saw blade during the dicing process causes mechanical damage and affects inner layers of the die. Figure 3 demonstrates damage and chipping at the edge and of the inner layers. By contrast, the micro-photographs show no damage when the individual dies are separated using the plasma dicing process. Also, unlike blade dicing which causes micro particles of the wafer (e.g. silicon) to be freed up, potentially causing devices to fail, by using plasma etching, no contaminating particles are released.

#### Greater chip strength

Chip breakage tests show the typical range of fracture strength for silicon chips to be in the range of 100MPa up to 3000MPa. Dies from several positions on a 150µm thick wafer were sampled and a Weibull plot was used to compare the statistical data for chip strengths of lots using blade and plasma dicing preparation methods.

Figure 6: Reduced street widths result in more

Figure 4 shows that the plasma dicing process results in chips that are about five times stronger than those which underwent blade dicing. With a fracture stress pressure of 600MPa, all samples of chips that had been processed using blade dicing broke due to internal micro- cracks, whereas all of the plasma diced chips shattered at a pressure close to the breakingstrength of silicon. Therefore the plasma dicing process is proven to result in dramatically higher chip strength, especially if thin wafers are being processed.

#### Higher throughput and yield

The processing time of blade dicing depends on the number of dicing lines. If the die size is small, longer dicing processing time is required and throughput is reduced. However, with the plasma dicing process, etching is performed across the whole wafer in one pass, so throughput remains constant, no matter how many dicing streets are required (see Figure 5). In addition, the plasma dicing process uses a narrower dicing street design. With blade dicing, there is always a minimum cutting street width, due to the thickness of the blade. A simulation prepared by Panasonic shows that for a 0.5mm<sup>2</sup> chip size, reducing the dicing street width from  $60\mu m$  to  $5\mu m$ , yield will be increased by 23% using the new plasma process (see figure 6). However, the method of avoiding chips contacting other chips when handling a wafer with 5µm dicing street width needs to be considered.

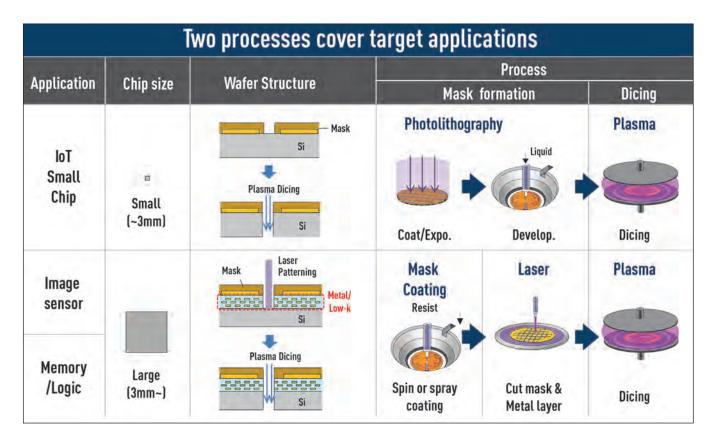

#### Suitability for different wafer processes

The Panasonic plasma dicing process can be applied to wafer dicing with mask patterning either performed

by photolithography or laser patterning methods. The appropriate process flow should be selected to fit the wafer design (Figure 7). Plasma dicing is a high quality innovation which offers different benefits depending on the end application, as shown in Figure 8. In small chips, for example, RFID tags, IoT devices or MEMS sensors, the ability to obtain a higher number of chips per wafer, plus the reduction in process time is paramount. For devices such as image sensors, the elimination of contaminating particles is essential, and the smoother, damage-free sidewalls, with no heat-affected zones or cracking, allows an increase in the active area. For makers of memory ICs, the elimination of damage is most significant.

#### Panasonic plasma dicing demo center

In order to demonstrate the plasma dicing process, Panasonic has built a customer demonstration centre Panasonic plasma dicing

Figure 7:

The processing time of blade dicing depends on the number of dicing lines. If the die size is small, longer dicing processing time is required and throughput is reduced

#### Panasonic Cover Story

| Target Application                                      | Blade issue                            | Benefit by plasma                                           |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                                   |

|---------------------------------------------------------|----------------------------------------|-------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------|

| 0.2mm I mm                                              | Wider<br>dicing lane<br>(W 60µm)       | Narrower lane<br>(W 5µm)<br>→ More chips<br>from a wafer    | Blade<br>↓60µm                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | Plasma 5µm                        |

| IoT Small chip • RF-ID tag • Chip component • MEMS etc. | Longer process<br>time in smaller dies | Shorter process time → lower COO                            | Line-by-line                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | Whole wafer                       |

| Image Sensor                                            | Particle from blading,<br>less yield   | Particle free  → improve yield                              | Blade NG chip                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | Plasma                            |

| Memory CPU Memory                                       | Chipping/die breakage<br>due to damage | Damage free chip<br>obtained<br>→ new value for<br>end user | Blade  Contract to the contrac | Plasma  Plasma  Plasma  No damage |

Figure 8: Benefits of Plasma

in Osaka, Japan. This Class 1000 facility is capable of processing 200mm and 300mm diameter wafers with a minimum thickness of 25µm. It is fully-equipped including two APX300 plasma dicing machines, laser pattern- ing equipment, polisher / grinder, lithography and measurement equipment, enabling customers to quickly and thoroughly evaluate different products and materials.

#### **Total Solutions Approach**

In addition to supplying the APX300 Plasma Dicer,

Panasonic is in close contact with vendors globally to assist our customers with the integration and selection of appropriate equipment and material, and implementation of decades of process know-how.

#### Conclusion

Panasonic's plasma dicing process achieves damagefree and particle-free dicing, resulting in inherently stronger chips and increased yield. Throughput is increased and production costs reduced.

Figure 9: Summarises the different dicing processes and the advantages of the plasma dicing process

## Power semiconductors

Perfecting the art of ultimate reliability.

Whether efficiently driving industrial motors, smoothly accelerating trains or transmitting gigawatt power over long distances and underwater – failure is not an option! That's why you need ABB Power Grids' power semiconductors that provide the ultimate in reliability and are the epitome of quality.

# KLA Corp. focuses on next-gen solutions for power applications

Power Electronics World technical editor Mark Andrews recently asked representatives of KLA Corp. to detail the ways that they are assisting customers address unique inspection and metrology requirements for power devices for automotive applications in addition to SiC and GaN technologies that seek to displace incumbent silicon technologies.

#### BY KLA CORP.

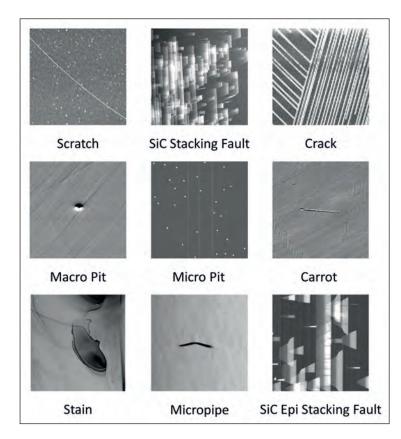

MA: Please describe KLA's specialized inspection systems for SiC substrates as well as processing within GaN-on-silicon manufacturing flows that target present and future automotive power requirements.?

**KLA:** SiC power devices pose unique yield and cost challenges in comparison to Si-based devices. Some of these challenges include:

- Much higher intrinsic material defect densities than Si-based devices

- High level of defect transference from substrate to epitaxy to device fabrication

- Variation in quality among substrate suppliers.

Wafers graded and sold by dislocation density.

- Key defect issues include both crystallographic and morphological defects (carrots, surface triangles and stacking faults)

- Defect mechanisms act in the z-direction instead of x/y-plane. KLA's Candela 8720 compound

semiconductor material surface inspection system and the 8 Series patterned wafer inspection system have been developed to address these challenges.

The Candela® compound semiconductor material surface inspection system enables GaN-related materials, GaAs substrate and epi process control with high sensitivity to critical defects for the production of power devices, communications and RF devices, and advanced LEDs (as well as upcoming micro LEDs).

With its proprietary optical design and detection technology, the Candela inspection tool utilizes signals from scatterometry, reflectometry, ellipsometry, slope and photoluminescence detectors to detect and classify yield-limiting, sub-micron defects to support production-line monitoring.

The Candela 8720 system is used to monitor the substrate IQC (incoming quality control) and OQC (outgoing quality control) processes for a variety of defect types including particles, scratches, stains, pits, micropipes, stacking faults and other crystallographic defects.

For the post epitaxial growth process step, the inspection system can detect and monitor process issues such as cracks, macro epi disturbances (such as droplets), epi pit, epi bump, crystal-oriented defects (such as single/bar stacking faults, BPDs, etc.), micropits and particles. Defects in the substrate and post epi growth can significantly impact end of the line yield, so detecting and correcting such process issues at the source - where cost is the lowest - is critical. Patterned wafer inspection of SiC semiconductor devices is important for reducing defectivity and maintaining traceability, but inspection can present several unique challenges.

Wafer thickness and warpage are outside typical SEMI standards. The transparent (SiC) substrate can create challenges for focus systems and create unwanted noise when imaging the wafer. The 8 Series patterned defect inspection tool addresses these challenges through a specialized prealignment and chuck, selectable illumination wavelengths and depth of focus for inspection, multiple inspection channels and increased wafer handling flexibility.

With simultaneous brightfield and darkfield inspection capability, it captures all types of surface defects with a multi-level defect binning solution. With optional back side inspection capability, the 8 Series system can handle and inspect both frontside and back side

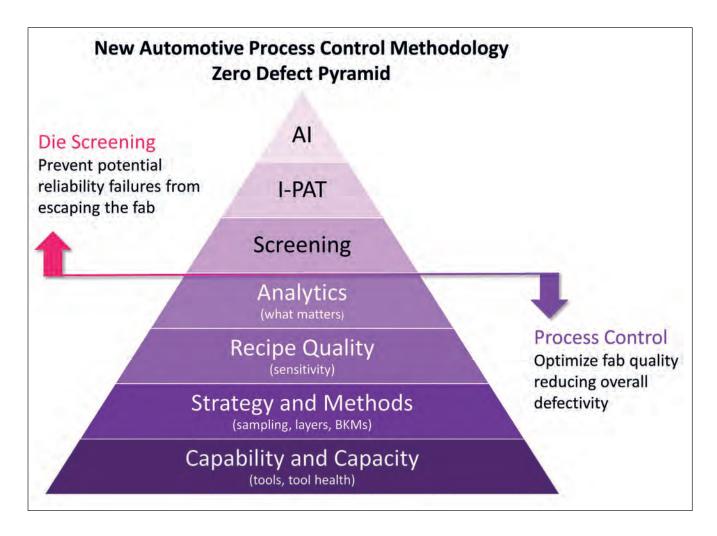

Figure 1: New automotive process control methodology Zero Defect pyramid

#### **KLA Corp**

of 6" SiC pre- and post-grind wafers offering high precision frontside to back side correlation and die inking for process-induced killer defects on both sides of the wafer.

It is important to note that beyond some of the early SiC process steps, the many remaining steps for SiC are very similar to a standard silicon chip process, so SiC fabs will utilize similar process control strategies compared to silicon IC fabs.

MA: Producing automotive ICs and packaged devices present unique challenges beyond greater reliability such as the need to produce spare parts for years longer than consumer electronics. How does KLA technology help device manufactures meet these critical needs?

KLA: Automotive fabs have faced this problem for years and they do it by maintaining the process control strategies and standards that they used successfully in the past. This is shown through the defect pyramid (see Figure 1). In order to help maintain these strategies along with the best performing tools, KLA works with our customers in two areas:

- KLA helps customers by making continuous improvements on the process control platforms through product upgrades.

- KLA provides an extensive service package that helps our customers ensure that the process control tools are performing at the highest levels.

In addition, KLA also offers metrology and inspection

tools that enable component sorting to prevent defective devices arriving at the assembly line and to keep track records of each device. Metrology helps verify whether device dimensions are within tolerance and thus confirming the quality of packaged products; inspection verifies that there are no particles, burrs or other defects present that could impact the yield.

MA: Can KLA detail its approach to supporting the power devices market and how experience in supporting other areas of the IC industry benefit their approaches to power electronics?

KLA: The company has been delivering solutions and support to the SiC and GaN power device market segment for some time. Leveraging our vast experience in developing new technology capable of solving complex inspection and metrology challenges across the IC industry to help drive yield improvements, we have developed a comprehensive portfolio of process control solutions specialized for the unique needs of power devices. In addition, through our subsidiary SPTS Technologies, we offer industry leading plasma etch, PVD and CVD wafer processing systems that are used in the manufacture of SiC and GaN devices.

There are several unique challenges in the manufacturing of power devices. Although the design rule is larger, there are special requirements beginning with the substrate and the early epitaxial process. These include, but are not limited to, thickness, wafer handling, substrate shape and quality, epitaxial dislocations, stacking faults and a number of other defect types which could limit the final device yield.

Working closely with our world-wide customers, both in development and in high volume manufacturing (HVM), KLA has engineered, delivered and improved our inspection and metrology offerings to provide the high quality inline data required to help drive yield and continuously improve cycle times.

MA: Packaging power electronics is often a challenge in and of itself. In the past, manufacturers often needed to create new package designs, especially for GaN and SiC. How does KLA support packaging requirements and what are its essential advantages?

KLA: The demand for packaging power electronics is widespread across different application types, including mobile and automotive, which results in the development of a wide variety of new packaging technologies to meet different requirements for overall performance, power, form factor and price.

The growth of 5G communication brings an increase in device power consumption, resulting in unique requirements for including more power management ICs. Therefore, development of advanced packages for these types of power devices is expected to

increase, and the resulting innovation will bring greater complexity and new process flows. Generally, IC packages are getting smaller, thinner and more complex, as seen with the integration of multiple dies and passive components into a system in package (SiP), but at the same time requiring higher power density and demanding stricter yield requirements. To meet the yield targets for new packaging technologies, more automated inspection of packages in the assembly and test processes will be required to ensure that defects are identified and sourced quickly during the manufacturing process.

Today's evolving automotive market is being driven by several key areas, most notably connectivity, electrification, and autonomous driving, which is resulting in increased IC content in every car. High reliability requirements for automotive push for Zero Defect standards in manufacturing. Because reliability affects both warranty and liability, as well as the brand image of car manufacturers - and potentially the safety of their customers - process control in packaging, from wafer level to component, will increase significantly in the coming years to find and eliminate the sources of defects and screen for costly excursions. Manufacturers must leverage every available opportunity for continuous improvement across the entirety of their manufacturing value chain to reach that goal.

and adopted. Tolerances on key features (i.e. size, thickness, warpage, interconnect size, alignment, etc.,) for these advanced packages are becoming tighter. Requirements for defect detection and classification accuracy are also increasing. Inline, nondestructive inspection and metrology characterization provide the signals required to enable customers to deliver advanced packaging innovation and differentiated solutions to the market.

High-end 3D profiling and metrology on wafer and panel can be measured with KLA's Zeta 5xx and 6xx systems. Wafer-level inspection and metrology process control with the Kronos™ wafer inspection system meets the requirements of high sensitivity and production-worthy throughput, while simultaneously addressing the challenges of wafer warpage, thin and thick substrates and numerous process variations typical of advanced packaging processes.

After dicing, the detection of hairline cracks in bare dies or in fan-in wafer-level packaging is achieved with the ICOS™ F160 die sorting and inspection system. It examines packages after wafers have been diced, delivering fast and accurate die sort based on detection of key defect types - including sidewall cracks, a new defect type affecting the yield of highend packages.

To meet the yield targets for new packaging technologies, more automated inspection of packages in the assembly and test processes will be required to ensure that defects are identified and sourced quickly during the manufacturing process

For more traditional packaging types, the focus is largely on cost. Automatic inspection is available, providing the benefit of reducing overkill and then increasing yield. ICOS™ T3/T7/T8 and MV component inspection systems provide automated inspection and metrology capabilities across all different types of packages. With modular tool architecture, KLA can offer solutions to meet the requirements of many package types with varying size and interconnect

Beyond traditional packages, mobile applications have been driving the development of smaller (dimensions below 3mm) and more complex packages. These include new technology such as fan-in wafer level packaging (FI-WLP), bare dies, fan-out wafer level packaging (FO-WLP) and SiP (system in package) for silicon-based packages.

We also expect similar levels of packaging innovations for SiC/GaN devices as they are further developed

Once packaged, the ICOS component inspectors provide higher accuracy and repeatability in characterizing key features of advanced packages. With high resolution defect detection, ICOS component inspectors enable discovery and classification of defects smaller than 10 µm in mold or substrates and below 1µm for cracks in die.

The unique process control capabilities described thus far are critical to ensure performance of power electronics, but also to ensure optimal yield. Achieving high yields and meeting cycle time goals are challenging with new complex process schemes. Smarter, faster methods of analyzing large data sets and extracting critical information quickly to make decisions is required. Deep learning methodologies paired with advanced defect detection of packages helps to optimize the classification process, reduce overkill and maximize yield. KLA has extensive experience in working with customers to solve new packaging challenges and helping them succeed in

#### **KLA Corp**

ramping new products while improving overall yield in a cost-effective manner.

#### MA: How does KLA support the unique inspection/ metrology challenges presented by SiC and GaN?

KLA: Starting with the substrate, dimensional wafer metrology systems from KLA's MicroSense offer precise, non-contact, automated geometry measurements including thickness, thickness variations, bow, warp, and 2D and 3D mapping on a wide range of substrates including sapphire, silicon, SiC, GaAs, glass, quartz, ceramics and graphene. For measurement and control of multilayer bonded wafers, our systems can measure total wafer stacks and individual layers throughout the wafer bonding, thinning and de-bonding process steps.

For metrology of power devices, our optical film thickness, overlay patterning and critical dimension instruments are successfully being deployed for inline process control at leading SiC and GaN customer fabs. We have developed a unique transparent wafer option to handle, transfer, align and measure various thin films on SiC on the F5x Pro film metrology system. The KLA Pro Archer™ overlay metrology platform enables production control of overlay and CD to help provide the data required for correcting the scanner.

For inspection, both SiC and GaN are complex material systems and each have very specific and unique process related defects that manifest in the substrate and after epitaxial growth process. Some of the similarities and differences between the two material systems include:

- Much higher intrinsic material defect densities in SiC based power devices

- Variation in quality among SiC substrate and GaN epi suppliers. SiC substrates are graded and sold by dislocation densities that are native to the substrate

- Morphological defects, crystallographic defects on SiC (such as carrots, triangles, stacking faults, basal plane dislocations), interfacial defects (such as cracks that originate at the interface of GaN and the substrate on which the epi is grown)

- Defects on SiC post epitaxy growth are directional while on GaN the defects are non-directional

KLA has developed unique solutions to meet the inspection requirements of both SiC and GaN materials systems.

The Candela® 8720 compound semiconductor material surface inspection system enables GaN-related materials, GaAs substrate and epi process control with high sensitivity to critical defects to produce GaN based power devices, communications and RF devices, and advanced LEDs (as well as upcoming microLEDs). With its proprietary optical design and detection technology, the Candela inspection tool utilizes signals from

scatterometry, reflectometry, ellipsometry, slope and photoluminescence detectors to detect and classify yield-limiting, sub-micron defects to support production-line monitoring.

The next generation of the award winning Candela® CS920 - the industry's first integrated surface and photoluminescence SiC inspection tool - is enhanced with greater sensitivity for monitoring the substrate IQC (incoming quality control) and OQC (outgoing quality control) processes for a variety of defect types including particles, scratches, stains, pits, micropipes, stacking faults and other crystallographic defects. For the post epitaxial growth process step, this inspection system can detect and monitor process issues such as cracks, macro epi disturbances (such as droplets), epi pit, epi bump, crystal-oriented defects (such as single/bar stacking faults, BPDs, etc.), micropits and particles.

Defects in the substrate and post epi growth can significantly impact end of the line yield, so detecting and correcting such process issues at the source is critical--where cost is the lowest. Patterned wafer inspection of SiC semiconductor devices is important for reducing defectivity and maintaining traceability, but this need presents several unique challenges. Wafer thickness and warpage are outside typical SEMI standards. The transparent substrate can create challenges for focus systems and create unwanted noise when imaging the wafer. The 8 Series patterned defect inspection tool addresses these challenges through a specialized pre-alignment and chuck, selectable illumination wavelengths and depth of focus for inspection, multiple inspection channels and increased wafer handling flexibility.

With simultaneous brightfield and darkfield inspection capability, the tool captures all types of surface defects with a multi-level defect binning solution. With optional back side inspection capability, the 8 Series system can handle and inspect both the front side and back side of 6-inch SiC pre- and post-grind wafers offering high precision front side to back side correlation and die inking for process-induced killer defects on both sides of the wafer. As the demand for power devices continues to grow, we are adapting our portfolio to the needs of our customers, so they have the data they need to control their process. Both SiC and GaN have unique challenges compared to silicon; inspection and metrology data can help provide valuable information required to move the process from R&D to high volume production.

#### Replies from KLA Corporation were supplied by:

Robert Cappel, Senior Director of Marketing; David P. Price, Sr. Director, Automotive Technical Solutions:

Mukundkrishna Raghunathan and Oliver Dupont, Product Marketing Managers."

**BUSINESS COMMUNICATIONS**

Specialists with 30 year+ pedigree and in-depth knowledge in these overlapping sectors:

Expertise: Moderators, Markets, 30 Years + Pedigree Reach: Specialist vertical databases

Branding: Message delivery to high level influencers via various in house established magazines, web sites, events and social media

**Future Mobility**

Publications include: TaaS Technology, TaaS News

#### P

Data Centres

**Publications include:** DCS Europe, DCS UK, SNS International

SmartSolar UK & Ireland

**Publications include:** Solar and Power Management, Solar UK and Ireland

Sensors

**Publications include:** Sensor Solutions Magazine, Sensor Solutions International

Diaitalisation

**Publications include:** Digitalisation World, Information Security Solutions, Managed Services

Photonics

Publications include: PIC Magazine, PIC Conference

#### **Expert Moderators**

Dedicated technical and time-served experts/editors

#### **MARK ANDREWS**

Mark Andrews is technical editor of Silicon Semiconductor, PIC Magazine, Solar+Power Management, and Power Electronics World. His experience focuses on RF and photonic solutions for infrastructure, mobile device, aerospace, aviation and defence industries

#### **JACKIE CANNON**

Director of Solar/IC Publishing, with over 15 years experience of Solar, Silicon and Power Electronics, Jackie can help moderate your webinar, field questions and make the overal experience very professional

#### **PHIL ALSOP**

Journalist and editor in the business to business publishing sector for more than 30 years currently focusing on intelligent automation, DevOps, Big Data and analytics, alongside the IT staples of computing, networks and storage

#### DR RICHARD STEVENSON

Dr Richard Stevenson is a seasoned science and technology journalist with valuable experience in industry and academia. For almost a decade, he has been the editor of Compound Semiconductor magazine, as well as the programme manager for the CS International Conference

#### For more information contact:

Jackie Cannon T: 01923 690205 E: jackie@angelwebinar.co.uk W: www.angelwebinar.co.uk 6 Bow Court, Burnsall Road, Coventry, CV5 6SP. UK

# New Thermal Interface Material (TIM) improves lifetime and performance of LoPak1 modules

Heat generated during the operation of IGBT switches is a constant threat to the survival of microelectronic chips within power modules. ABB has developed a new thermal interface material (TIM) that can be applied to the base plate surface; the company has demonstrated its new TIM layer can effectively extend the life and improve performance of power modules across a wide range of high voltage applications.

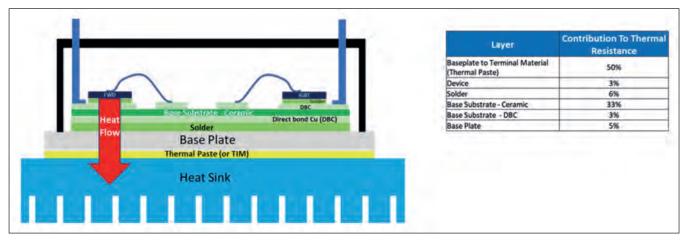

HEAT GENERATED by power losses during the operation of IGBT switches must be removed from the chip to prevent the junction temperature of semiconductor devices from rising beyond maximum allowable limits. Heat is transferred through the module to a heat sink, with the interface between the module baseplate; the heat sink typically has the highest thermal resistance and therefore contributes most strongly to the module thermal path resistance (Figure 1). The use of the TIM improves the thermal conduction across this interface ensuring more stability over long-term operation than commonly used conventional heat conductive pastes (Figure 2). The use of the

TIM can increase the amount of current that can be safely switched by the IGBT and improve the module's lifetime, since the TIM's thermal resistance does not increase with the number of switching cycles.

ABB's 1700V LoPak1 modules will be available with improved lifetime and enhanced electrical performance derived from (optional) pre-applied thermal interface material (TIM) that is deposited on the outside module base plate surface that contacts the heat sink. Module orders scheduled for delivery from June 2020 onward will be able to specify this enhancement.

Figure 1: Heat flow pathway through module and layer contributions

| Appearance                     | Paste                      | TIM                               |

|--------------------------------|----------------------------|-----------------------------------|

| Color                          | White or Grey              | Grey                              |

| Base Material                  | Silicone Fluid with filler | Phase Change Material with filler |

| Consistancy @ room temperature | Viscous                    | Hard                              |

| Thermal Conductivity (W/mK)    | 0.8 - 3.0                  | 5.2                               |

Figure 2: Comparison of materials used between base plate and heat sink

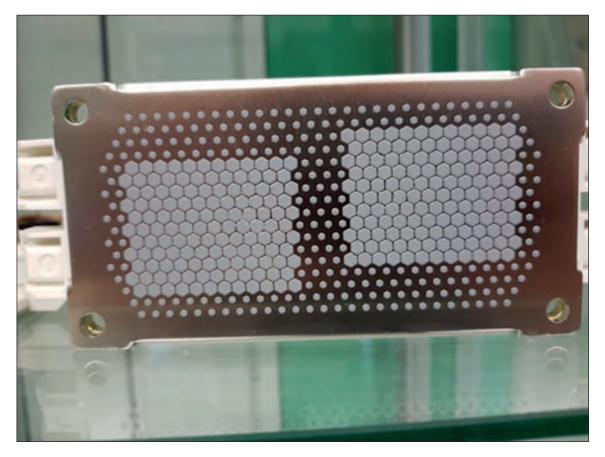

The amount of thermal material applied, and its application pattern critically affect the thermal resistance of the interface. ABB Power Grids applies the TIM in a paste form using automatic stencil printing during module fabrication. This paste transforms into a solid through the use of a curing / drying process performed after coating. The TIM layer remains solid at room temperature reducing the potential for damage to the print pattern by accidental contact. Being a solid also makes module handling and installation easier for the customer. The design of the TIM pattern takes into account the locations of highest heat generation and the module's intentional baseplate bending; it ensures that the best metal-tometal contact is made between the module baseplate and the heatsink (figure 3). The process is automated to ensure the repeatability required for volume production.

An alternative to ABB's thermal interface material involves the application of conventional heat conducting paste, which is applied by the customer manually using stencil printing. This process leads to higher variability in the amount of material applied and non-uniformity of its application across the interface area. The paste also remains viscous throughout the process.

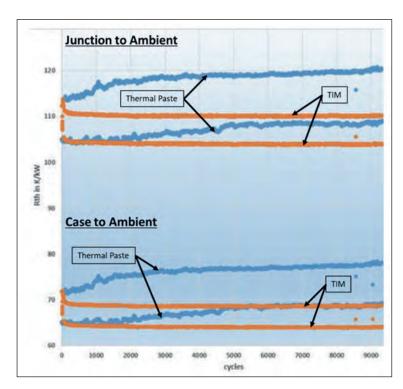

The improved thermal stability of TIM, as compared to heat conductive pastes, can be seen during power cycling (figure 4), which is a standard test to simulate the degradation of the module over its lifetime by thermo-mechanical stress. The test was run for 9,400 cycles, in line with the JESD51-14 specification, using the maximum allowable junction temperature of 150oC, with a total cycle time of 120 seconds (ton = toff = 60s), dTc = 65-75K.

Figure 3: Base plate bottom surface with TIM applied

| Thermal Resistance, Average over 9400 Cycles | Paste  | TIM    | Improvement |  |

|----------------------------------------------|--------|--------|-------------|--|

| Junction to Ambient (K/kW)                   | 114.75 | 106.66 | 7%          |  |

| Case to Ambient (K/kW)                       | 73.92  | 65.93  | 11%         |  |

Figure 4: Performance of TIM compared to heat conductive paste

#### The results of this testing showed:

- A 7 percent improvement in the average thermal resistance for the entire pathway from the IGBT junctions to ambient when the TIM is used instead of heat conductive pastes

- An 11 percent improvement in the average thermal resistance from the case to ambient when the TIM is used instead of heat conductive pastes

The impact of using ABB's TIM rather than heat conductive paste can be seen by looking at data from the cycling test (figure 5) for the partial thermal resistance from the case to the heat sink (where the TIM is located) and for the entire path between the transistor junction and the heat sink. While the initial thermal conductivity of pre-applied TIM is comparable with the heat conductive paste, the modules using TIM show no increase in thermal resistance with cycling, while those using the heat conductive paste show increasing thermal resistance during the test.

These results imply degradation of the thermal interface for the heat conductive paste and demonstrate the better long-term stability of the TIM. The improved consistency of performance is because the TIM becomes viscous when it is heated to temperatures above 45°C by the operation of the transistors. This allows it to spread out evenly across the interface during thermal cycling to provide a homogeneous coating across the base plate/heat sink

Figure 5: Comparison of TIM and heat conductive paste stability

interface while dramatically reducing material pumpout. The use of the TIM improves the thermal transfer between power module and heat sink when compared to conventional heat conductive pastes, improving the long-term reliability and performance of the module. The TIM option will be available for LoPak modules beginning in June 2020.

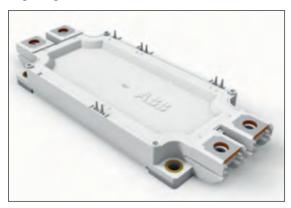

Figure 6: Image of ABB's LoPak 1.7kV 450A IGBT module

#### **About LoPak**

LoPak devices are medium power IGBT modules (figure 6) that enable extra transient overcurrent capability by taking advantage of the IGBT module's maximum operating junction temperature of 175°C, compared to the typical 150°C. The configuration is a 1700V phase-leg (half-bridge) IGBT module with a copper base plate that utilize ABB's uniquely designed SPT++ IGBT and diode devices. Current ratings of 450A, 300A and 225A are available.

The LoPak devices provide outstanding safe operating area (SOA) and over-temperature capability and benefit from ABB's expertise in ensuring robust electrical performance and high reliability. The careful design and virtual prototyping used by ABB makes the LoPak module's current distribution well-balanced during switching and ensures control under overload conditions. Extensive customer feedback confirms that LoPak modules have the same 'DNA' for high reliability and robustness as the entire family of ABB's high-power semiconductors.

Applications for LoPak modules include renewable energy and industrial sectors; LoPak plays a key role in ABB's expanding catalog of products that support existing and emerging market requirements.

# Industry counts on SEMI standards.

SEMI is the global industry association serving the product design and manufacturing chain for the electronics industry.

Check out our new standards on SMT & PCB Manufacturing Equipment Communication, Panel Level Packaging & Energetic Materials at:

www.semi.org/collaborate/standards

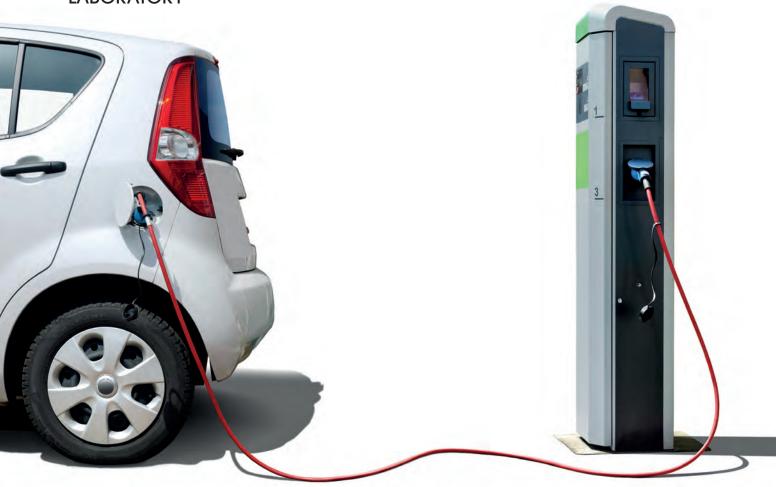

# Charging the UK to power an **EV** future

Julian Skidmore, Senior Software Engineer at embedded systems consultancy ByteSnap Design

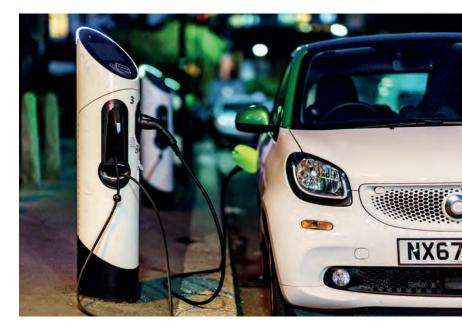

> DRIVEN BY CONCERNS over global heating and improvements in battery technology, electric vehicles are the most promising solution for emissions-free transit, but one barrier to adoption is the slowerdeveloping EV charging infrastructure which can be inconsistent and difficult to use.

> Battery electric vehicle (BEV) sales in the UK are projected to be around 100,000 during 2020 and the government has set a goal for half of all new vehicle sales by 2030 to fall into the "ultra-low" emissions category. Yet, at current growth rates over 2010 to 2019, all registered vehicles will be BEVs by the mid-2020s.

The availability of public charging points is an issue though, and charging availability and technology could potentially hold back EV adoption. While battery capabilities have grown rapidly, from a range of 100 miles to between 200 and 300 miles, EV prices are falling, consumer choice is growing and EV performance is rising, but EV charging infrastructure is not yet keeping up.

#### Charging

Rapid DC charger rollout is essential for longer journeys, because the charging rate has a much bigger impact on average speeds than battery size. If we want to put EVs on the highway, rapid

charging matters more than a large battery, but for local or urban driving there will be a market for smaller battery, slow charging EVs.

AC chargers, like those at home, with slower charging and lighter loading are best for grid management with local or urban driving. That's because most journeys are short, so their energy requirements won't change over time. Home chargers obviously keep up with EVs sold, but public ones

#### ByteSnap Design

aren't so they should be targeted, because they're cheap and cover most cases. Some of the new cars in 2020 will have modest batteries, short ranges and 7KW charging as standard.

#### User experience

EV chargers are less user-friendly than we'd expect from something that is powering our driving future. Billing mechanisms can be "nasty" and payment methods inconsistent; connections can be faulty or intermittent; systems can crash and user interfaces that are on the opposite side of the charger from the plug cause inconvenience. We wouldn't accept this lack of service at a petrol station and EV journeys shouldn't have to be that stressful.

#### Revolution

While we are at the beginning of the EV revolution, which presents an opportunity without the constraints of fossil fuel powered cars which need piping, tankers, stations and Just In Time logistics, better government support and initiatives are needed to support charging locations and a good geographical distribution of chargers. Subsidies for charging network providers may also be needed, along with consideration of load balancing, as distributed energy could cause intermittent supply.

Usage restrictions and non-standardised interfaces represent wasted engineering effort that actually slows down adoption and finally charging points are unmanned, resulting in maintenance issues. However, that could actually present an opportunity for a new service industry.

Although charger manufacturers would like a comprehensive networking protocol between the charger and the car, the IEC 61851 and 62196 specifications have led to a plethora of CAN bus, IP over Power and crude PWM communications along with incompatible plugs. Combined with that, manufacturers' reluctance to provide useful EV battery charging status (to protect their patents) will also continue to inhibit the potential for Smart EV charging. Vehicle to Grid (V2G)

Because batteries also represent a source of baseload microgeneration, EVs can be part of the energy solution. ByteSnap, in collaboration with a consortium of partners, is working on a two year project called VIGIL (Vehicle-to-Grid Intelligent Control), which will see the development of a new communication and control platform for vehicle-to-grid (V2G) and vehicleto-building (V2B) systems.

V2G technology could mean that EVs can return energy to the power grid when stationary and plugged in, increasing energy grid resilience and providing payback for EV drivers. V2G connectivity could also take advantage of the new phenomenon of renewable energy surplus. Germany is one country where consumers can experience negative energy prices,

thanks to renewable and green energy initiatives. VIGIL would promote comprehensive charging communications, in turn aiding EV adoption, with ByteSnap's smart communications controller (called RAY) managing the charge going back into the smart building, or substation. In turn, substation energy can flow into the smart building; charge EVs or return power to the grid.

#### **Future**

Appless charging, where EV owners can tap a credit or debit card on a charging post to start and stop charging is something every EV driver would like. Some Polar Ultrachargers already have a contactless payment method and Ecotricity Electric Highway plans a similar upgrade, despite the plan bringing with it higher charging costs.

Combining substations with urban car parks could help solve issues of kerb-based charging sockets which can be inaccessible or easily damaged. Secure multi-storey car parks with built-in charging facilities where the infrastructure is in one place and therefore cheaper to implement, upgrade and maintain, would clear streets of EVs and provide security.

Alongside V2G facilities, fully automated charging is the dream of every EV driver. Intuitively, robots would plug in charging cables, but this over-engineering of a human oriented interface might better be met by inductive charging, though since that requires charging mechanisms to change yet again it's more likely in the long term. EVs are the most likely technology to replace fossil fueled vehicles and the nascent world of EVs is a rapidly accelerating, disruptive market, which charging technology and infrastructure is as critical to as the vehicles themselves. Driving the deployment of EVs will come from making EV driving as effortless and attractive as petrol and diesel vehicles.

# **Qromis:** ready for business

As the GaN market gathers momentum, Qromis is serving up fab-friendly substrates and epi-wafers to ease device manufacture, reports Rebecca Pool.

> IN JANUARY THIS YEAR, Silicon Valley based Qromis revealed two developments that signal the company is on the cusp of rapid expansion.

> For starters, the fabless, wide bandgap materials business has just received an undisclosed investment from The Mirai Creation Fund, led by Japan-based investors SPARX.

At the same time, it has also signed a licensing agreement with Shin-Etsu Chemical, a Japanbased silicon wafer and materials manufacturer, to produce substrates and epiwafers for GaN power/RF electronics, LED devices and more.

Qromis' latest developments follow five years of development of its novel materials technology for substrates. And right now, chief executive, Cem Basceri, is excited.

"We've developed this unique CMOS fab-friendly substrate technology that is scalable and stressmatched to GaN," he says. "It sounds simple but it's taken years of development and investment."

"Now, a device manufacturer can take our substrate, and without any challenges, make many different device features," he adds. "This is extremely valuable."

#### Rapid progress

Qromis launched back in 2015 to commercialise its Qromis Substrate Technology, QST. Ready for GaN epi-growth, these substrates comprise an engineered coefficient of thermal expansion (CTE)-matched core onto which several engineered layers are deposited. A top thin silicon interface is also deposited onto the engineered layers.

Crucially, the CTE-matched core has a thermal expansion that closely matches the thermal expansion of the GaN-AlGaN epitaxial layers, enabling the deposition of low dislocation density, crack-free GaN epitaxy from a few microns to bulk-like thickness.

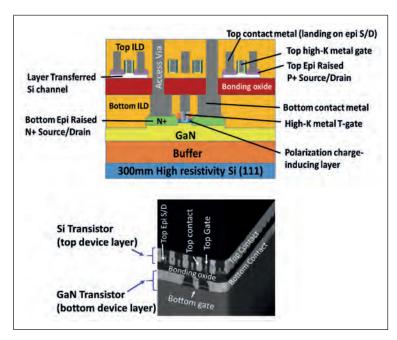

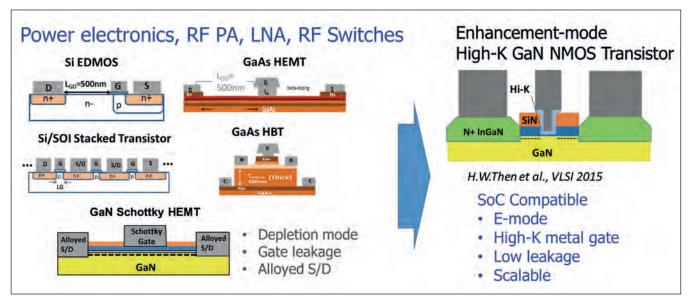

As Basceri highlights: "We did this so that the substrate would be stress-matched with GaN without any cracking or wafer breakage issue and also to prevent substrate cross-talk in integrated circuits, which is a big issue on silicon."

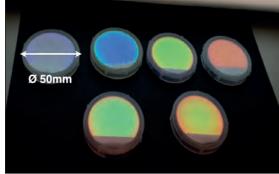

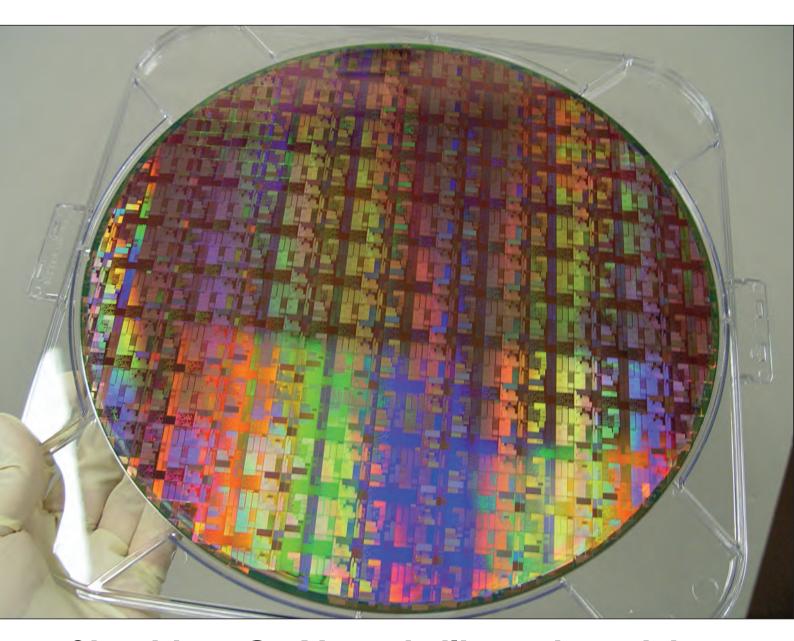

Qromis has already released 6- and 8-inch GaN-ready QST substrates as well as 6- and 8-inch 'templates' with 5  $\mu m$  and 10  $\mu m$  GaN layers. What's more, 200 V and 650 V GaN HEMT epi-wafers, based on 6-inch and 8-inch QST substrates, are being fine-tuned for commercial devices while 900 V and 1200 V GaN HEMT epi-wafers are also being developed and sampled.

The company's rapid technology development follows partnerships and collaborations with a host of industry players up and down the supply chain. Within a year of launching, the company had partnered with Vanguard International Semiconductor, licensing its key technologies to the Taiwan-based silicon foundry for manufacturing.

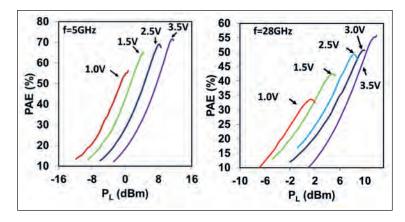

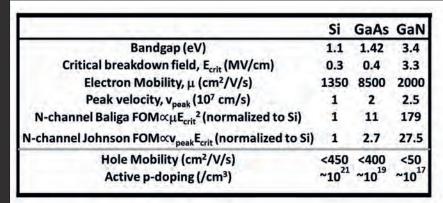

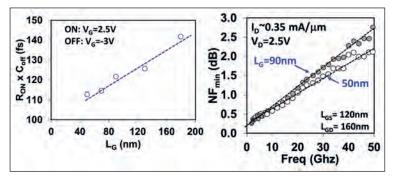

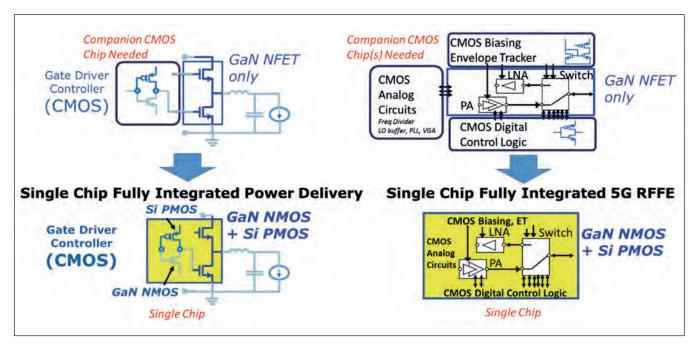

Since 2016, the company has also worked closely with microelectronics innovation hub, imec, Belgium, on device fabrication, developing GaN power devices, in discreet and monolithically-integrated ICs forms, on 200 mm QST substrates in an advanced CMOS silicon pilot line.

Imec and Qromis have also been collaborating with GaN MOCVD equipment manufacturer, Aixtron, Germany, on GaN-on-QST epitaxy development. The results have been quite remarkable.

As Basceri points out, the industry standard platform for GaN-on-silicon has been 150 mm wafers. And while imec has pioneered the development of 200 mm GaN-on-silicon wafers for HEMTs to 650 V operating voltages, thermal mismatch between the GaN/AlGaN layers and silicon has stymied device fabrication at higher voltages.

Imec and Qromis have since developed enhancement mode p-GaN discrete and IC power devices on 200 mm QST substrates with epitaxy layers grown in Aixtron's G5+ C 200 mm MOVCD platform. Crucially, imec was able to port its p-GaN e-mode power device technology to Qromis' 200 mm GaN-on-QST wafers in its silicon pilot line, and also demonstrate highperformance power devices.

"Vanguard then decided to licence imec's device technology, GaN power epitaxy and processes and the company is currently manufacturing and tuning devices to [partner's] specifications," says Basceri. "This has been a big turning point."

#### Ramping manufacture

In line with healthy GaN growth forecasts, Basceri

says Vanguard will 'open its doors to everybody' later this year, offering GaN power, and later RF, device manufacturing services on the 200 mm diameter QST platform. This has also prompted the Qromis chief executive to establish a second manufacturing source for QST substrates and GaN-on-QST epitaxy wafers, in the form of Shin-Etsu Chemical. Importantly, with this partnership, QST-based materials products will be commercially available from both Shin-Etsu and Qromis for industry players.

According to Basceri, Shin-Etsu is going to aggressively move ahead with the development of GaN-related products, supplementing its existing line-up of GaN-on-silicon, SOI and silicon wafers. As he says: "From what we hear from our partners and customers that use Vanguard, we are expecting wafer demand to reach tens of thousands of wafers in the next three-to-four years."

With its substrates, Qromis will address a range of applications starting with GaN power and RF devices and later LED devices, such as microLEDs, and sensors. One of the key markets will be electric vehicles - as Basceri points out, a significant portion of SPARX's Mirai Creation Fund comes from Toyota Motor Corporation, which is heavily entrenched in this market.

"We expect to start ramping up 200 millimetre manufacturing between 2021 and 2022, and I would also expect to see an overall demand for 300 millimetre wafers starting by 2025 for which we have already started to receive some initial inquiries," says Basceri. "Several years ago, there were missing links in the GaN business, but the tipping point is now here."

Qromis, Chief Executive, Cem Basceri

# Unlocking the potential of SiC power modules with graphite

Replacing the copper core in insulated metal substrates with highly oriented graphite boosts thermal conductivity of the SiC power module while trimming its weight

BY WEI FAN AND DAWN KRENCISZ FROM MOMENTIVE QUARTZ

TECHNOLOGIES, GARRY WEXLER FROM HENKEL CORPORATION AND

EMRE GURPINAR AND BURAK OZPINECI FROM OAK RIDGE NATIONAL

LABORATORY

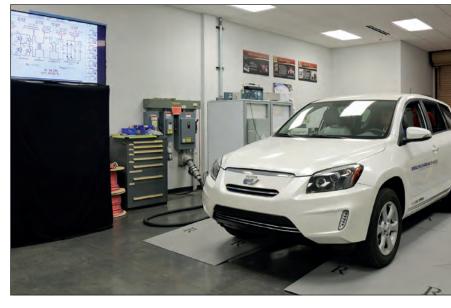

CHOOSING YOUR NEXT CAR is far from easy. As part of being environmentally responsible, you will certainly want to consider purchasing a vehicle that runs solely on battery power. While such a vehicle will undoubtedly help to curb your carbon footprint, will it have sufficient driving range? Or will your car run out of juice on one of your long trips?

To avoid agonising over this dilemma, what is needed is the development of vehicles with a longer range between recharges. Increasing energy storage in the battery will help, along with a hike in the performance of the power electronics.

Such efforts are already underway in the United States supported by a Department of Energy roadmap that details requirements for next-generation electric drive systems. Targets include: a doubling of power handling capability to allow the electric traction drive system to handle peak powers of up to 100 kW; and a hike in power density from 13.4 kW/litre in 2020 to 100 kW/litre in 2025. Research institutes and industrial partners have been pouring tremendous resources and efforts into the development of the next-generation power electronics for electrical vehicles (see Figure 1).

Increases in power density must be accompanied by improvements to the thermal management system. However, this must be accomplished without adding weight to the vehicle, as weight will negatively impact travel range. Meeting this requirement demands more advanced thermal management methods beyond traditional heat pipes, water cooling, and fans.

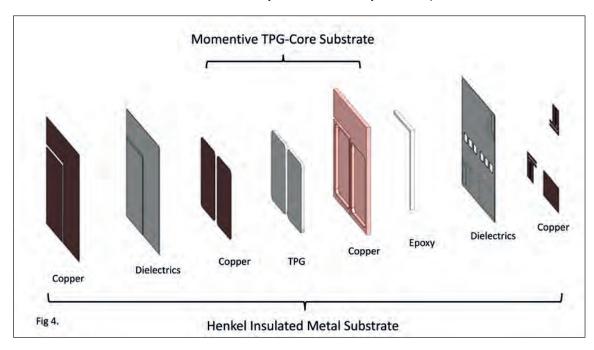

Tackling this challenge of improving the thermal management of SiC power modules while trimming their weight is the objective of a collaborative partnership between Momentive Quartz Technologies,

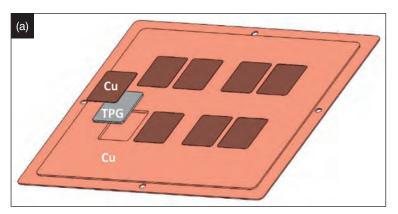

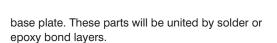

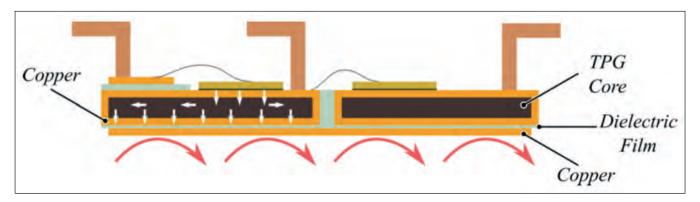

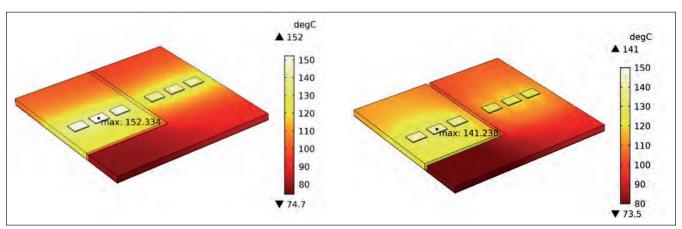

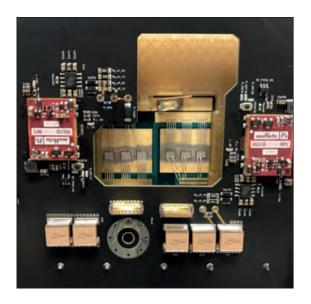

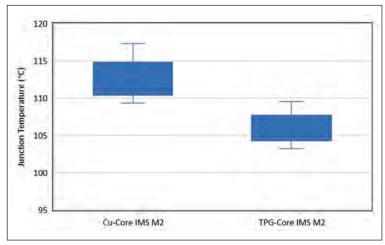

Henkel Corporation (Henkel) and Oak Ridge National Laboratory (ORNL). Working within the US Department of Energy Electric Drive Technologies Consortium, this partnership - from now on referred to collectively as the 'Group' - is redesigning the insulated metal substrate. This technology is light weight, featuring a thermally conductive graphite core. Armed with this approach, engineers can cut substrate weight by 30 percent and increase the power loading for the SiC power module by 15 percent or more, thanks to a near doubling of thermal conductivity.

Figure 1. An EV test platform at ORNL that was used to evaluate power modules for wireless charging

This technology promises to revolutionise the standard isolated multi-chip SiC power module. Today, if you cut open one of these modules you are likely to find SiC dies, on either a direct bonded copper or insulated metal substrate, mounted to a thick copper

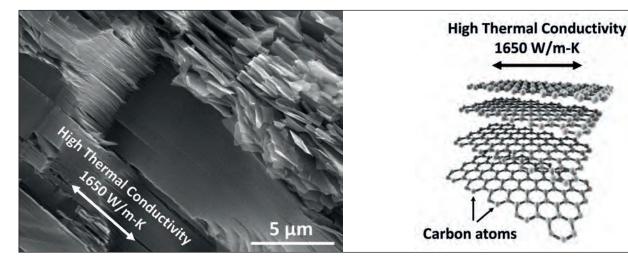

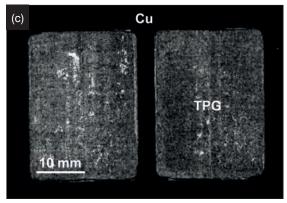

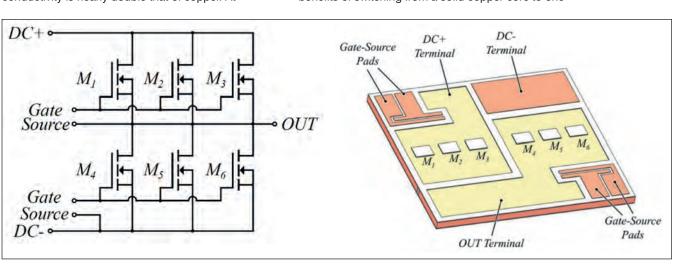

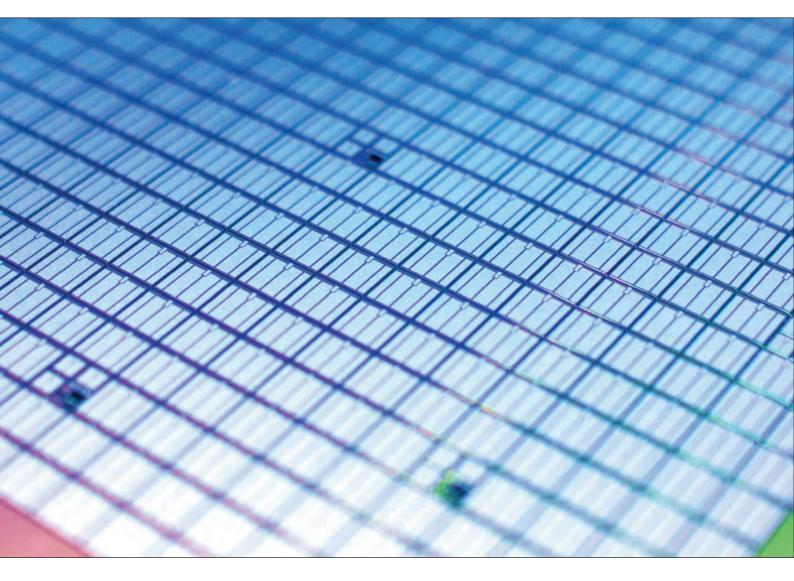

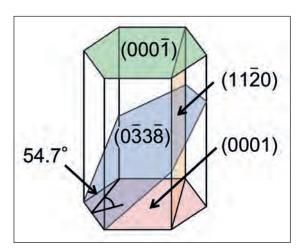

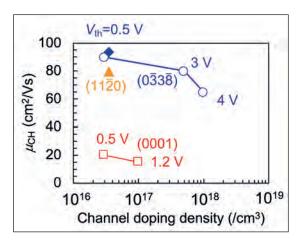

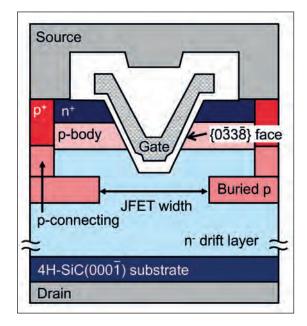

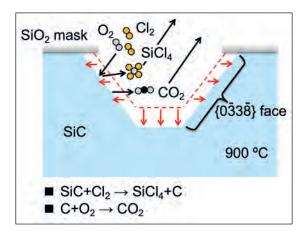

Figure 2. Cross-sectional view, provided by a scanning electron microscope, of Momentive Quartz Technologies' thermal pyrolytic graphite cores (left). An illustration of this material, showing well-aligned graphene basal planes (right).