#### **ISSUE IV 2020**

#### WWW.POWERELECTRONICSWORLD.NET

Focuses on next-gen power applications

### Evaluating new switching technologies

#### EPC launches eGaN FET for rectification

## Next-Gen Solutions for Power Applications

**KLA** Corporation

News Review, News Analysis, Features, Research Review and much more.

## Best performance for next generation SiC power electronics to address global mega trends

RIXTRON

## AIX G5 WW C

- Electric vehicles: on board chargers, power inverters

- Infrastructure: charging stations

- Renewables: solar and wind

- Industrial: motor drives, power supplies

- Power distribution: HVDC

Discover our SiC epi production batch tool with single wafer performance

www.aixtron.com

# Viewpoint

By Mark Andrews, Technical Editor

### Looking ahead to a brighter & better 2021

WE COULD ALL USE A BREAK. A pause. A respite. Take heart—the holidays are here, and the glass is half full, not half empty. Brighter days are indeed ahead.

After many grim months of infection tallies growing ever greater, the world received a much needed 'shot-in-the-arm' as COVID-19 vaccines began distribution in the UK, Europe and North America. Developing a new vaccine typically requires years, but by pooling resources, the global pharmacological community did the almost-impossible in mere months. Even as the latest surges bring more sad statistics, we at last have reason for hope. Instead of just raising our glasses to welcome a New Year, we'll soon be rolling up our sleeves.

If 2020 was plotted as a misery index, one could hardly find its equal in the past 50 years. While there were horrors aplenty, 2020 also had its heroes. These were not cape-clad Big Screen stars fighting mythical villains; 2020's heroes wore PPE, scrubs, and risked their lives each day to mend what was broken and comfort those facing their last hours without kith and kin. Each harrowing day became another, and then another—yet they prevailed. Looking for Superman? Thank a nurse. Or Wonder Woman? Hug a doctor. Iron Man? Thank the orderlies, the med techs and everyone giving their all to bring hope. Thank-you to our 2020 heroes and all who give us hope that we can soon de-mask and gather with friends (safely) while planning a future beyond living day-by-day.

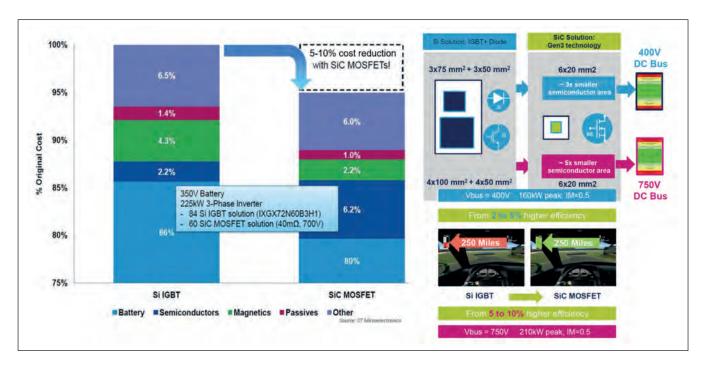

We have a great final 2020 edition of Power Electronics World to share. This year saw increasing sales of electric vehicles thanks to ever-improving SiC's in fast chargers along with range improving batteries utilizing the latest lithium tech. We take a look at Wolfspeed's ongoing SiC improvements and parent company Cree's future beyond LED lighting. We examine new switching technology, better solar cells and amazing advances in concentrated solar power cells for satellites.

Despite the seemingly impossible challenges of 2020, industry met them head-on, delivering performance that was hard to envision amidst seemingly endless pandemic challenges.

#### Here is to brighter days ahead!

| Editor & Publisher Jackie Cannon         | jackie.cannon@angelbc.com      | +44 (0)1923 690205 | Chief Executive Officer Sukhi Bhadal       | sukhi.bhadal@angelbc.com               | +44 (0)2476 718970                                              |

|------------------------------------------|--------------------------------|--------------------|--------------------------------------------|----------------------------------------|-----------------------------------------------------------------|

| Technical Editor Mark Andrews            | mark.andrews@angelbc.com       |                    | Chief Technical Officer Scott Adams        | scott.adams@angelbc.com                | +44 (0)2476 718970                                              |

| Sales Manager Shehzad Munshi             | shehzad.munshi@angelbc.com     | +44 (0)1923 690215 | Directors Jackie Cannon, Sharon Cowley     |                                        |                                                                 |

| USA Representatives Tom Brun Brun Media  | tbrun@brunmedia.com            | +001 724 539-2404  |                                            |                                        |                                                                 |

| Janice Jenkins                           | jjenkins@brunmedia.com         | +001 724-929-3550  | Published by Angel Business Communication  | ns Ltd, Unit 6, Bow Court, Fletchworth | h Gate, Burnsall Road,                                          |

| Director of Logistics Sharon Cowley      | sharon.cowley@angelbc.com      | +44 (0)1923 690200 | Coventry CV5 6SP, UK. T: +44 (0)2476 718 9 | 70 E: info@angelbc.com                 |                                                                 |

| Design & Production Manager Mitch Gaynor | mitch.gaynor@angelbc.com       | +44 (0)1923 690214 |                                            |                                        | $\mathbf{O}$                                                    |

| Circulation Director Scott Adams         | scott.adams@angelbc.com        | +44 (0)2476 718970 |                                            | Angel 📿                                | recycle                                                         |

| Chairman Stephen Whitehurst              | stephen.whitehurst@angelbc.com | +44 (0)2476 718970 |                                            | BUSINESS COMMUNICATIONS                | When you have finished with<br>this magazine please recycle it. |

PEW Magazine is published four times a year on a controlled circulation basis. Non-qualifying individuals can subscribe at: £105.00/e158 pa (UK & Europe), £138.00 pa (air mail), \$198 pa (USA). Cover price £4.50. All information herein is believed to be correct at time of going to press. The publisher does not accept responsibility for any errors and omissions. The views expressed in this publication are not necessarily those of the publisher. Every effort has been made to obtain copyright permission for the material contained in this publication. Angel Business Communications Ltd will be happy to acknowledge any copyright oversights in a subsequent issue of the publication. Angel Business Communications Ltd © Copyright 2020. All rights reserved. Contents may not be reproduced in whole or part without the written consent of the publishers. The paper used within this magazine is produced by chain of custody certified manufacturers, guaranteeing sustainable sourcing. © Copyright 2020.

We strive for accuracy in all we publish; readers and contributors are encouraged to contact us if they recognise an error or omission. Once a magazine edition is published [online, in print or both], we do not update previously published articles to align old company names, branding, marketing efforts, taglines, mission statements or other promotional verbiage, images, or logos to newly created or updated names, images, typographic renderings, logos (or similar) when such references/images were accurately stated, rendered or displayed at the time of the original publication. When companies change their names or the images/ket used to represent the company, we invite organizations to provide Angel Business Communications with a news release detailing their new business objectives and/or other changes that could impact how customers/prospects might recognise the company, contact the organisation, or engage with them for future commercial enterprise.

# CONTENTS

#### 12 COVER STORY IGBT modules interrogated acoustically

IGBT failures, because of the typically high voltage and power levels, can be both costly and dangerous. It makes sense to find internal structural defects be-fore they have an opportunity to go wrong

#### 16 KLA Corp. focuses on next-gen solutions for power applications

Power Electronics World technical editor Mark Andrews recently asked representatives of KLA Corp. to detail the ways that they are assisting customers address unique inspection and metrology requirements for power devices for automotive applications

#### 22 Enabling smart manufacturing in the sub-fab

The Industry 4.0 movement is rapidly becoming the de facto means to optimize cost-effective manufacturing. Power electronic device makers want to leverage any practical idea

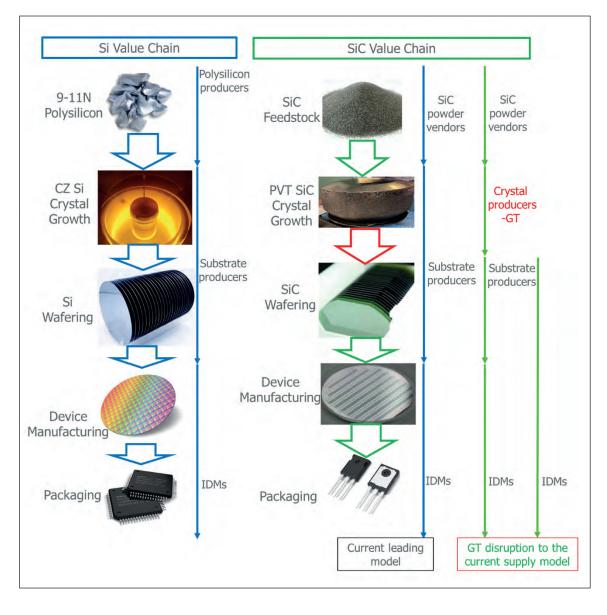

## 28 Opening up SiC substrate production

A manufacturer of crystal growth equipment pivots to materials manufacturing, creating a more competitive supply chain for the production of SiC power electronics

## 34 Evaluating switching technologies

It takes more than a change in part number to move to a wide bandgap technology; what's required is a systemic approach, considering all aspects of design

#### 40 Imec offers new wireless charging solutions for implantable, insertable and ingestible medical devices

Researchers from imec presented a novel, new system for wireless medical device communication and power at the 2020 ISSC conference

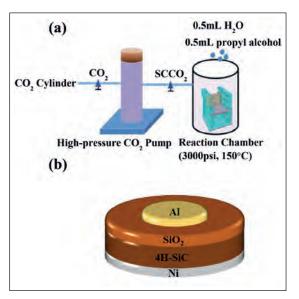

#### 44 Research review

- Supercritical CO2 spawns superior MOSFETs

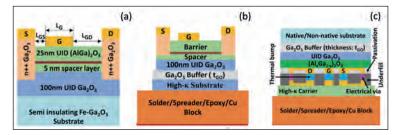

- Building better Ga2O3 transistors

- AIPN enlarges the nitride family

#### news

- 06 EPC Launches eGaN FET for 48V synchronous rectification

- 07 Infineon expands SiC supply base with GTAT

- 08 Transphorm selects Veeco platform for GaN-based devices

- 09 Tektronix releases TekDrive, groundbreaking data collaboration software

- 10 Transphorm samples first SuperGaN Gen V FET

- 11 EnergyHub and Enel X partner to expand EV charging as a grid resource

## EPC Launches eGaN FET for 48V synchronous rectification

EPC has advanced the performance while lowering the cost of off-the-shelf GaN transistors with the introduction of the EPC2059 ( $6.8m\Omega$ , 170V) eGaN FET. This device is the latest in a family of 100 to 200V solutions suitable for a widerange of power levels and price points.

They are designed to meet the increasing demands of 48 to 56V server and data centre products as well as an array of consumer power supply applications for high end computing, including gaming PCs, LCD/LED TVs, and LED lighting.

The EPC2059 is suitable for DC-DC secondary-side synchronous rectification in AC/DC adaptors, fast chargers, and power supplies with power ranges between 100 W and 6 kW. The performance advantage of GaN devices helps designers achieve the demanding efficiency requirements for 80 Plus Titanium power supplies, while providing smaller, faster, cooler, and lighter systems with lower system costs then currently available solutions.

According to Alex Lidow, EPC's cofounder and CEO: "There are very significant performance advantages gained from using GaN in the secondaryside synchronous rectification socket of AC/DC adaptors.

In a 400V to 48V conversion, switching at 1 MHz, GaN has shown to have one-sixth the losses and run 10 degrees cooler than a silicon MOSFET with equivalent on resistance. This enables designers to meet the latest stringent energy efficiency standards for high-end computing, where growth is exploding for multiple applications, such as artificial intelligence (AI), cloud computing, and high-end gaming systems."

#### Development Board The EPC9098 development board is a 170V maximum device voltage, 25/ maximum output ourroat, balf bridge

a 170V maximum device voltage, 25A maximum output current, half bridge with onboard gate drives, featuring the EPC2059 eGaN FETs.

This 50.8 mm x 50.8 mm board is designed for optimal switching performance and contains all critical components for easy evaluation of the EPC2059.

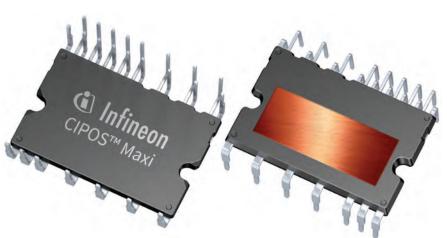

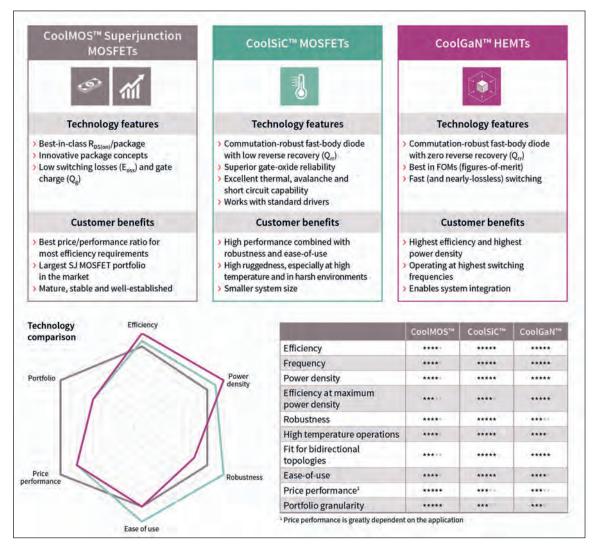

### Infineon launches CoolSiC CIPOS Maxi

INFINEON has launched a 1200 V transfer moulded SiC integrated power module (IPM) and concludes the roll-out of SiC solutions for this year.

The CIPOS Maxi IPM IM828 series is believed to be the industry's first in this voltage class. The series provides a compact inverter solution with an excellent thermal conduction and a wide range of switching speed for three-phase AC motors and permanent magnet motors in variable speed drive applications. Amongst others, these can be found in industrial motor drives, pumps drives, and active filters for heating, ventilation, and air conditioning (HVAC).

The CIPOS Maxi IPM integrates an improved 6-channel 1200 V silicon on insulator (SOI) gate driver and six CoolSiC MOSFETs to increase system reliability, optimise PCB size and system costs. The new family member is packaged in a DIP 36x23D housing. This makes it the smallest package for 1200 V IPMs with the highest power density and

best performance in its class. The IM828 series features an isolated dual-in-line moulded housing for excellent thermal performance and electrical isolation. It meets EMI requirements and overload protection of demanding designs.

The rugged 6-channel SOI gate driver of the SiC IPM provides built-in dead time to prevent damages from transients. It also offers under-voltage lockout (UVLO) at all channels and over current shutdown protection functions. With its multifunction pin, this IPM allows high design flexibility for various purposes.

Adding to the protection features, the IPM is equipped with an independent UL-certified temperature thermistor. The low side emitter pins can be accessed for phase current monitoring making the device easy to control.

## Infineon expands SiC supply base with GTAT

INFINEON TECHNOLOGIES AG and GT Advanced Technologies (GTAT) have signed a supply agreement for SiC boules. The contract has an initial term of five years. With this supply contract, the German semiconductor manufacturer adds a further element to secure its growing base material demand in this area.

Under the brand name CoolSiC Infineon now already markets a large product portfolio for industrial applications and is rapidly expanding its offerings towards consumer and automotive products.

"We are seeing a steadily increasing demand for SiC-based switches, especially for industrial applications," says Peter Wawer (pictured above), president of Infineon's Industrial Power Control Division.

"However, it has become clear that the automotive sector is quickly following suit. With the supply agreement we have now concluded, we ensure that we will be able to meet the rapidly growing demand of our customers with a diversified supplier base. GTAT's high-quality boules will provide an additional source for competitive SiC wafers fulfilling the best-in-class material standards now and in the future. This supports our ambitious SiC growth plans, making good use of our existing in-house technologies and core competencies in thin-wafer manufacturing."

"We are very excited to enter into a longterm supply agreement with Infineon," says Greg Knight, president and CEO of GT Advanced Technologies. "GTAT will enable Infineon to achieve a secure high-quality internal SiC wafer supply by applying their proprietary thin-wafer technology to GTAT's crystal. The growth of SiC device adoption is tied largely to the aggressive cost down of the substrate, and this agreement is a significant step towards achieving that goal."

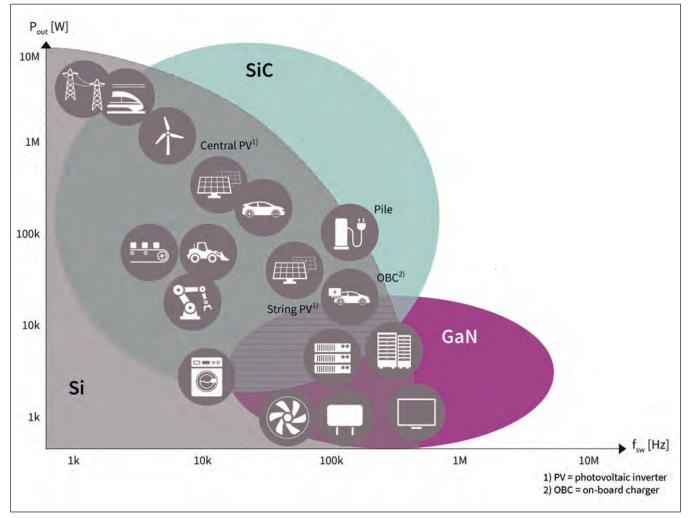

SiC has mainly been used up to now in photovoltaic inverters, industrial power supplies, and the charging infrastructure

for electric vehicles. This is where the advantages of SiC at the system level, compared to classical silicon solutions, have already come into play.

Other industrial applications such as uninterruptible power supplies and variable-speed drives are increasingly making use of the new semiconductor technology. In addition, electric vehicles show enormous potential for application options, including the main inverters for the drive train and onboard battery charging units.

### UnitedSiC introduces new SiC FETs on Gen 4 technology

UNITEDSiC, a US manufacturer of SiC power semiconductors, has launched the first four devices based on its advanced Gen 4 SiC FET technology platform. As the first and only 750V SiC FETs currently available on the market, these Gen 4 devices enable new performance levels, based on high Figures of Merit (FoM), that benefit power applications across automotive, industrial charging, telecom rectifiers, datacenter PFC, and DC-DC conversion as well as renewable energy and energy storage.

Available in 18 and 60 mohm options, these new SiC FETs deliver unmatched FoMs with reduced on-resistance per unit area, and low intrinsic capacitance.

In hard-switching applications, the Gen 4 FETs exhibit the lowest RDS(on) x EOSS (mohm-uJ) resulting in lower turn-on and turn-off loss. In soft-switching applications, their low RDS(on) x Coss(tr) (mohm-nF) specification provides lower conduction loss and higher frequency. According to the company, these devices not only surpass existing competitive SiC MOSFET performance whether running cool (25degC) or hot (125degC), but also offer the lowest integral diode VF with excellent reverse recovery delivering low dead-time losses and increased efficiency.

In expanding UnitedSiC's offering to 750V, the new devices offer more designer headroom and reduced design constraints. This higher VDS rating also makes these FETs beneficial for 400/500V bus voltage applications.

With a widely compatible gate drive of +/-20V, 5V Vth, all devices can be driven with 0 to +12V gate voltages. This means they work with existing SiC MOSFET, Si IGBTs and Si MOSFET gate drivers.

As Anup Bhalla, VP Engineering at UnitedSiC, explains: "These devices help address the challenges facing engineers working across sectors with the highest

voltage and power demands - from DC-DC conversion and on-board charging to power factor correction and solar inverters.

"We will be announcing many new Gen 4 devices over the next 9 months which will further improve on costeffectiveness, heat efficiency and design headroom. This will support all sectors in overcoming the challenges of mass adoption and to accelerate innovation." NEWS REVIEW

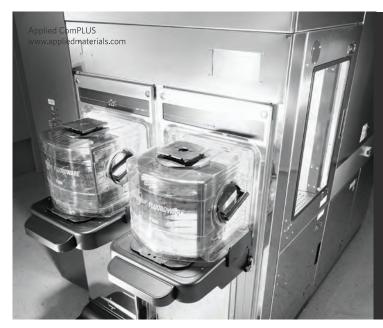

## Transphorm selects Veeco platform for GaN-based

## devices

VEECO has announced that Transphorm, a supplier of GaN chips products for high voltage power conversion applications, has selected Veeco's Propel HVM MOCVD System for highvolume production of GaN-based RF (DoD and Commercial/5G) and power electronics epiwafers. The Veeco system was purchased under a US DoD Office of Naval Research (ONR) contract N68335-19-C-0107 from an OUSD (R&E) TAM/ MINSEC program to establish a US based dedicated production source of GaN Epitaxy for high performance RF and mmwave electronics.

"Being at the forefront of GaN-based power and 5G devices that offer efficiency and high-power density, requires world-class manufacturing solutions that are capable of scaling to mass production while offering flexibility to continuously innovate," said Umesh Mishra, chief technology officer and co-founder of Transphorm. "Veeco's Propel HVM system is uniquely qualified to do that. The multi-reactor, single-

wafer technology provides flexibility and exceptional throughput at a low cost of ownership."

The Propel system's single-wafer reactor platform enables the processing of sixand eight-inch wafers or two- to four-inch wafers in a mini-batch mode. It is said to accelerate production ramping due to faster recipe capabilities up to 50 percent quicker than when using traditional tools.

In addition to Veeco's proprietary TurboDisc technology, the system also includes Veeco's IsoFlange and SymmHeat technologies, which are designed to provide homogeneous laminar flow and uniform temperature profile across the entire wafer.

"We are proud to have our MOCVD technology selected by a pioneer and recognised world leader in the GaN revolution," commented Ajit Paranjpe, Veeco's CEO. "Transphorm's decision to adopt our high-volume MOCVD technology is proof of the system's uniformity, throughput, repeatability and cost of ownership advantages over batch technology."

## Denso adopts SDK SiC epi-wafers for EVs

SiC epitaxial wafers, the main material for power semiconductors, with a diameter of six inches (150mm) and manufactured by Showa Denko, have been adopted by Denso Corporation for its latest booster power modules for fuel cell electric vehicles (FCEVs).

SDK's SiC epi-wafers, launched in 2009, have been adopted by electronic device manufacturers for various devices

including power supply for servers of cloud computing systems, quick charging stands for EVs, and railcars. DENSO adopted SDK's SiC epi-wafers for its next-generation power modules recognizing the track record of adoption by device manufacturers, highest-grade epi specifications, low density surface defects, and low frequency of basal plane dislocation. When compared with current mainstream silicon-based semiconductors, SiC-based power semiconductors can operate under high-temperature, high-voltage, and highcurrent conditions, while substantially reducing energy loss.

These features enable device manufacturers to produce smaller, lighter, more energy-efficient power control modules. SiC power semiconductors are already used in on-board battery chargers and quick charging stands for EVs, and railcars. Demand for SiC power semiconductors is expected to grow, with full scale use in power control units (PCUs) for EVs in and after 2025.

The Showa Denko Group aims to contribute to the solution of SDGs-related issues through its business activities and become "a social contribution company" that contributes to the creation of society where affluence and sustainability are harmonised. The size of the market for SiC epi-wafer, which realises efficient use of energy, is expected to be about 100 billion yen in 2025, and will grow further because of the start of its full-scale use as parts of PCUs.

As the largest independent manufacturer of SiC epitaxial wafers, and under a motto of "Best in Class," SDK will continue coping with rapid expansion of the market for SiC epitaxial wafers and providing the market with highperformance and highly-reliable products, thereby contributing to the spread of SiC-based devices.

## Tektronix releases TekDrive, groundbreaking data collaboration software

TEKTRONIX, INC. announced the availability of TekDrive, the first native oscilloscope-to-cloud software solution to facilitate global data collaboration directly on an oscilloscope, PC, phone or tablet. Created to enable ultimate ease and accuracy in data accessibility and collaboration, TekDrive provides engineers the ability to instantaneously share and recall data directly on an oscilloscope, eliminating the need for cumbersome data-sharing practices. TekDrive allows for data to automatically become accessible, usable and shareable across teams and partners, making remote work easier - all with industry-leading security practices built in.

In addition, TekDrive is the first general purpose test and measurement file system with scope-like data visualizations. The software provides ultra smooth visualization and analysis capabilities that support any modern browser, including options to view, zoom, pan, measure, decode and analyze full test and measurement data on any device without the need for any additional software. "This technology is a game changer for teams," says Tami Newcombe, president of Tektronix. "Clients tell us about insecure datasharing practices that are awkward and unreliable, and now with TekDrive, data sharing is secure and lightning fast. Launching TekDrive today marks a major expansion of our Tektronix vision to focus on relevant and cutting-edge software solutions that directly correspond to the latest industry needs."

Seventy percent of oscilloscope users have the need to transfer data off scope.

Through TekDrive, data updates are instantly saved in globally-accessible shared folders in which owners can manage secure access and permissions at a granular level.

"I joined Tektronix to help inspire the next wave of innovation in electronics engineering, and projects like this will do exactly that," says David Sulpy, chief information officer at Tektronix. "Engineers needed their own workspace in the cloud to securely manage complicated, real-time data from their oscilloscopes. TekDrive fulfills that need, whether they are working in the lab or at home." TekDrive was built with the engineer in mind, and boasts a clean, easy-to-use interface for file organization, management, search, upload and download. It's also architected for ease-of-integration with secure vendoragnostic REST APIs for scripting,

automation and analysis. Tektronix provides SDKs and examples in multiple languages, such as Python, Matlab and LabVIEW. The TekCloud Developer Program also provides a secure way for third party developers to add native TekDrive capability to their devices, instruments and software applications. With a quick integration, any vendor of hardware or software can unleash the ecosystem of TekCloud storage, streaming, visualization and analysis into their products.

TekDrive is now available in many regions worldwide and will be released globally over the coming months. All TekDrive users receive a free contributor account, which grants participation rights in shared files and folders, with the Enterprise Tier boasting unlimited contributors. A 14-day trial is also available.

### EPC adds 300W bidirectional 16th brick

EPC announces the availability of the EPC9151, a 300 W bidirectional DC-DC voltage regulator in the 16th brick format which is just 33 mm x 22.9 mm.

The EPC9151 power module features Microchip's dsPIC33CK digital signal controller (DSC) with the EPC2152 ePower Stage integrated circuit from EPC to achieve greater than 95 percent efficiency in a 300 W 48 V to/from 12 V converter design. Additional phases can be added to this scalable 2-phase

design to further increase power. Brick DC-DC converters are widely used in data centre, telecommunication and automotive applications, converting a nominal 48 V to (or from) a nominal 12 V distribution bus. Advances in GaN integrated circuit (IC) technology have enabled the integration of the half bridge and gate drivers, resulting in the EPC2152 single chip solution employed in the EPC9151 module to simplify layout, minimise area, and reduce cost for these applications.

## Transphorm samples first SuperGaN Gen V FET

TRANSPHORM has announced it is sampling of its first Gen V device under its proprietary SuperGaN brand, the TP65H015G5WS. The new Gen V device, which is for electric vehicles, is claimed to offer the world's lowest packaged on-resistance, delivering a 25 percent lower power loss over SiC in a standard TO-247-3 package.

In March 2020, Marelli, a large independent supplier to the automotive sector, announced a strategic partnership with Transphorm to collaborate on new GaN-based automotive/EV power conversion solutions including on-board chargers (OBCs), DC-DC converters and powertrain inverters for electric and hybrid vehicles. To date, Marelli has made a \$4 million equity investment in Transphorm and has committed to an additional \$1 million equity investment in Q1 2021.

Joachim Fetzer, CEO, Electric Powertrain Marelli, commented: "Transphorm's demonstration of achieving 10 kilowatts of power from a discrete packaged GaN device in a bridge configuration is further validation of the exciting promise of GaN for electric vehicle converters and inverters. As part of our previously announced partnership, we will continue to evaluate Transphorm's industryleading GaN devices and work together in support of a multi-year EV systems product roadmap."

"We continue to innovate Transphorm's SuperGaN FET technology, now offering the world's lowest on-resistance in a standard TO-247-3 package in the

market, targeted for electric vehicles and other higher power conversion applications. This allows customers to drive into double digit kilowatts with a single device, continuing to demonstrate GaN's ability to provide higher performance, lower system cost and higher power density," said Primit Parikh, COO and co-founder, Transphorm. "Our Gen V GaN platform is creating new design opportunities for power levels that previously required paralleling, while still offering the greater than 99 percent efficiency."

#### **Outperforming SiC**

According to Transphorm, the SuperGaN Gen V platform incorporates all the learnings from its Gen IV predecessor, patented reduced packaging inductance technology, ease of designability and drivability (Vth of 4 V for noise immunity), and gate robustness of +/- 20 Vmax along with a simplified and reduced assembly structure. In a recent article published in EEWorld, "Pushing the Boundaries of High Voltage GaN Power Conversion," the company's TP65H015G5WS was compared to a similar on-resistance leading-edge SiC MOSFET in a standard TO-247-3 package.

The devices were both operated up to 12 kW at 70 kHz in a half bridge synchronous boost converter, resulting in Transphorm's GaN device demonstrating up to 25 percent lower losses.

Transphorm has begun sampling the SuperGaN Gen V FET, a 15 m $\Omega$  650 V device, which is unavailable with today's single chip e-mode GaN technology due to its gate sensitivity.

Matching the lowest R available from typical SiC MOSFETs in a discrete package, the solution is capable of driving more than 10 kW depending on the target application, such as EV OBCs and powertrain inverters, power supplies for rack powered data center servers, uninterruptible industrial power applications, and renewable photovoltaic inverters.

The TP65H015G5WS will also be available for die level module solutions that enable further paralleling for even higher power.

The ompany anticipates its Gen V FET device to receive JEDEC qualification in mid-2021 with AEC-Q101 qualification expected thereafter.

### EPC Launches 40V eGaN FET

EPC, a maker of enhancement-mode GaN on silicon (eGaN) power FETs and ICs, has introduced the EPC2055 (3 m $\Omega$ , 40 V) eGaN FET.

This device is suitable for applications with demanding requirements for performance in space-constrained form factors including USB-C battery chargers and ultra-thin point-of-load (POL) converters. Other low-voltage applications benefiting from the fastswitching speeds and ultra-high efficiency of the EPC2055 include LED lighting, 12 V - 24 V input motor drivers, and lidar systems for robotics, drones, and autonomous cars.

According to Alex Lidow, EPC's cofounder and CEO: "The EPC2055 is a very good example of the rapid evolution of GaN FET technology.

This 40 volt device offers both smaller size and reduced parasitics compared

with previous-generation 40 V GaN FETs and at lower cost; thus, offering designers both improved performance and cost savings." The EPC90132 development board is a 40V maximum device voltage, 25 A maximum output current, half bridge with onboard gate drives, featuring the EPC2055 eGaN FETs. This 50.8 mm x 50.8 mm board is designed for optimal switching performance and contains all critical components for easy evaluation of the EPC2055.

NEWS REVIEW

## EnergyHub and Enel X partner to expand EV charging as a grid resource

EnergyHub has partnered with Enel X, the Enel Group's advanced energy services business line and EV charger manufacturer and service provider, to expand the availability of smart electric vehicle (EV) charging stations as a flexible distributed energy resource (DER) for utilities. Through the partnership, utilities can now manage customer-owned Enel X smart EV charging stations through EnergyHub's Mercury DERMS platform, expanding the breadth of EnergyHub's EV charging solution and increasing the EV charging resources available for utilities to manage. Utilities including Baltimore Gas & Electric (BG&E) and Eversource are the first to leverage the partnership and enroll customers with JuiceBox residential smart charging stations, with more to come.

Preparing for transportation electrification has emerged as a top priority for utilities. Bloomberg New Energy predicts EVs will account for the majority of passenger car sales by 2040. According to the same research, smart EV charging technology, which encourages customers to charge at optimal times, is estimated to save grid operators 30 to 70 percent of electrical infrastructure upgrade costs, representing hundreds of millions to billions of dollars a year in savings.

"We see managed EV charging as an important and growing piece of our DER portfolio, which we leverage not just during the hottest days of the year, but to manage demand year round," said Michael Goldman, Director of Energy Efficiency for Eversource. "We're glad to be able to allow more customers to participate by offering incentives to our customers with JuiceBox EV chargers." The partnership with Enel X, with over 60,000 consumer charging stations deployed nationwide, expands the ecosystem of EV chargers that utilities can manage with EnergyHub's Mercury DERMS.

"Working with EnergyHub and Enel X allows us to partner with our customers to manage flexible EV charging

load, preparing us for the future of transportation electrification, while also supporting the grid as whole" said Kristy Fleischman Groncki, manager of strategic programs at Baltimore Gas and Electric. "Our EV Smart program managed with EnergyHub rewards customers for contributing to the grid while using their preferred EV charging equipment."

EnergyHub and Enel X are working with electric utilities to harness the benefits of EV adoption and smart charging for the grid. The partnership enables utilities to grow their DER portfolios deployed with EnergyHub by managing enrolled Enel X JuiceBox smart charging stations in a service territory. Through the integration of EnergyHub's Mercury DERMS platform with Enel X's cloud-based JuiceNet smart EV charging software, utilities can forecast load, intelligently instruct, and monitor load results from customerowned Enel X charging stations.

Utility time-of-use (TOU) rates incentivize EV owners with Level 2 smart charging stations to utilize off-peak charging, generating bill savings for the customer and reducing strain on the grid during peak periods. In Maryland, where the state has a goal to deploy 300,000 EVs by 2025, the Public Utilities Commission authorized local utilities to install a network of 5,000 residential, workplace, and public charging stations.

To best support the rollout, BGE deployed EnergyHub's Mercury DERMS to implement an EV-TOU rate that incentives off-peak charging, through the gathering and analyzing of charging data. This charging data is provided at a 15 minute granularity from customers' Level 2 charging equipment, including Enel X JuiceBox smart chargers.

The integration of EnergyHub's Mercury DERMS plaform with Enel X's JuiceNet smart EV charging software platform is enabled by JuiceNet, which optimizes the energy consumption of the JuiceBox EV charging station to align with grid conditions, while ensuring customer mobility requirements are met. EnergyHub's Mercury DERMS platform allows utilities to monitor, coordinate, and orchestrate EV charging in concert with other DERs. EnergyHub works with utilities on multiple types of EV management solutions: time of use (TOU) enablement, peak management, and dynamic load shaping. EnergyHub and Enel X previously partnered to provide utilities with access to certain portfolios of Enel X commercial and industrial demand response assets.

#### **SONOSCAN** IGBT MODULES

## IGBT modules interrogated OCOUSTICOLY

IGBT failures, because of the typically high voltage and power levels, can be both costly and dangerous. It makes sense to find internal structural defects be-fore they have an opportunity to go wrong.

#### BY TOM ADAMS, CONSULTANT, NORDSON SONOSCAN

A GROUP of three small air voids is trapped in the solder that bonds an IGBT module to its heat sink. The voids happen to lie close enough to each other to prevent some of the heat from escaping cleanly from the area of the die just above them. Over time, the area above the voids may overheat and the die may fail electrically - and along with it the system it is part of.

IGBT failures, because of the typically high voltage and power levels, can be both costly and dangerous. It makes sense to find internal structural defects before they have an opportunity to go wrong.

X-ray and ultrasound can both perform the nondestructive imaging that is needed, but with some

differences. The first is penetration. X-ray may not ade-quately penetrate the heat sink on some IGBT modules, to deliver its data. The X-ray beam reports local differences in attenuation, and the most frequent de-fects in IGBTs are air gaps and non-bonds.

If the gaps are relatively thick, such as a void in solder, imaging may succeed, but if they are very thin, as in a non-bonded area, they may remain invisible because their impact on the beam's at-tenuation is too slight.

An Acoustic Micro Imaging tool such as a C-SAM® tool from Nordson SONOSCAN can readily penetrate the heat sink, but first it needs to solve an-other problem: the small water column that on other components couples the tool's transducer to the top

#### SONOSCAN IGBT MODULES

of the component cannot be used on the top surface of an unencapsulated IGBT module. Impure water coming in contact with the face of the module could invariably leave some residue from evaporation, and the IGBT's voltage level is so high that the residue could become a con-ductive pathway, with disastrous consequences. IGBT modules area one the few comps types the only component type having this limitation.

For this reason an inverted acoustic micro imaging tool was developed in order to image IGBTs from below, through the heat sink. The transducer and its wa-ter column both point upward at their station below the module, whose top surface remains dry. Because the bottom side of an IGBT module not covered by encapsulant, the modules can be imaged even after encapsulation.

As the tool's transducer scans back and forth along the bottom surface of the heat sink, it carries out its pulse-echo function at individual x-y locations tens of thousands of times per second, and contributes one pixel for the acoustic image with each pulse. The sequence is this:

- the transducer launches a pulse upward into the column of water.

- the pulse strikes the water-to-heat sink interface, and is in part reflected back to the transducer and in part transmitted upward into the module.

- the reflected echo reports, among other things, the distance from the transducer to the surface of the heat sink at the bottom of the module

- the transmitted portion travels through the heat sink and reaches the interface between the heat sink and the solder

- the heat sink-solder echo is reflected to the transducer, where it reports the distance and other data about the interface.

The process will continue upward through additional material interfaces until the pulse reaches the attachment of the die to the raft. But before it reaches the raft, it will report any unintended features it encounters in the solder. The unintended features consist almost entirely of air gaps, which may take the form of air bubbles in the solder or flat delaminations between two solid materials. This is when the three voids mentioned in the first paragraph would be imaged, and their distance from the heat sink surface recorded.

The air bubbles are actually the most imageable features in the module, because instead of presenting a solid-to-solid interface, they present a solid-to-gas (air) interface, which reflects more ultrasound (nearly 100%) back to the transducer than any other type of interface. Solid-to-solid interfaces tend to reflect 10 to 50 percent of the energy in an arriving pulse. No ultrasound penetrates the solid-to-air interface, so x-y locations lying directly beyond it will not be imaged. You can see these effects at work in the monochrome

Figure 1. Monochrome acoustic image made by scanning through bottom of module shows defects in one die attach.

acoustic image in Figure 1. To make this image, ultrasound was pulsed upward through the heat sink, the solder, the raft, and the die attach material, and returned to the transducer by the same route.

The rounded white feature near the upper left is an air-filled void in the layer bonding this chip to the ceramic raft in the module. There is another large void near the lower left, and several smaller ones.

This image was made by using a 'gate.' Since the pulse was launched three ma-terial layers below, to make the desired image the receiver needs to select only the echoes from the small slice of time during which echoes were reflected by this die.

At each x-y location, the transducer's receiver waits after a pulse is launched until at precisely the right nanosecond after launch it is activated to accept whatever arrives from the gated depth - anything from no echo to, as here, the strongest possible echo. Probably thousands of 'strongest possible' echoes arrived at the receiver to make the x-y shape of this void appear white. Weaker echoes produce gray. No echo at all yields black.

There seem to be a few cracks in this die, visible as dark lines; one reaches the void at upper left. The indistinct black features mostly on the right half of the die are voids in the solder layer, which is closer to the transducer. They are above the gate set for the die that is being imaged. They are black because they are shadows from voids above the gate.

Being voids, and filled with air, they sent back their own echoes when the pulses coming from the transducer struck them, but their own echoes arrived at the transducer too early to be within the collecting gate and were ignored. But by preventing pulses from reaching the die, they sent their own acoustic shad-ows to the transducer. One might also explain the same phenomenon by saying that during the brief moment when the transducer was receiving echoes

#### **SONOSCAN** IGBT MODULES

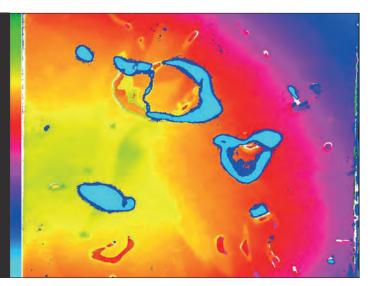

Figure 2. Light blue features are closest to heat sink, pale green are farthest above.

from the die attach, the areas beyond these voids had nothing too contribute.

Figure 2 is the acoustic image of the raft surface on one of the die on a IGBT. The colors here are reporting the vertical distance of the solder-filled space between the raft and heat sink surfaces. This figure extends vertically through the whole thickness of the solder. The raft is deepest in small areas at left center (pale green in color map at left) and highest at upper right (pale blue in color map), where there is so little solder that the raft surface probably comes close to touching the heat sink.

The key features here are the non-uniform thickness of the solder and the numerous heat-blocking voids, some of which are quite large. Collectively they may be capable of causing a region of the die just above to overheat and fail. Those voids that are light blue are likely in contact with the heat sink. But note that part of the upper right corner is the same color, because the solder in this region is very thin.

The large blue C-shaped void near the center lies above an-other large void that lies in the red-yellow depth. Non-uniform solder layers may lead to uneven heat dissipation and therefore unwanted stress. Non-uniform solder layers may lead to uneven heat dissipation and thus unwanted stress.Neither of the IGBT modules shown here would be candidates for incorporation into a product: they are simply too filled with anomalies. But in these high-power modules even a single small anomaly could lead to failure if the modules are being used close to their design specifications.

## LEADING WAFER PROCESSING EQUIPMENT for the global semiconductor, MEMS and nanotechnology markets

- Permanent Wafer Bonding

- Temporary Bonding / Debonding

- Lithography / Mask Alignment

- Photoresist Coating and Development

- Nanoimprint Lithography

- Inspection and Metrology

GET IN TOUCH to discuss your manufacturing needs www.EVGroup.com

## KLA Corp. focuses on next-gen solutions for power applications

Power Electronics World technical editor Mark Andrews recently asked representatives of KLA Corp. to detail the ways that they are assisting customers address unique inspection and metrology requirements for power devices for automotive applications in addition to SiC and GaN technologies that seek to displace incumbent silicon technologies.

#### BY KLA CORP.

MA: Please describe KLA's specialized inspection systems for SiC substrates as well as processing within GaN-on-silicon manufacturing flows that target present and future automotive power requirements.?

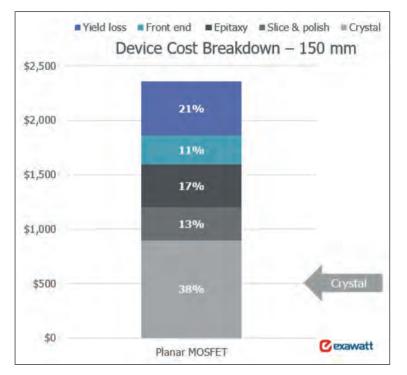

**KLA:** SiC power devices pose unique yield and cost challenges in comparison to Si-based devices. Some of these challenges include:

- Much higher intrinsic material defect densities than Si-based devices

- High level of defect transference from substrate to epitaxy to device fabrication

- Variation in quality among substrate suppliers. Wafers graded and sold by dislocation density.

- Key defect issues include both crystallographic and morphological defects (carrots, surface triangles and stacking faults)

- Defect mechanisms act in the z-direction instead of x/y-plane. KLA's Candela 8720 compound

semiconductor material surface inspection system and the 8 Series patterned wafer inspection system have been developed to address these challenges.

The Candela® compound semiconductor material surface inspection system enables GaN-related materials, GaAs substrate and epi process control with high sensitivity to critical defects for the production of power devices, communications and RF devices, and advanced LEDs (as well as upcoming micro LEDs).

With its proprietary optical design and detection technology, the Candela inspection tool utilizes signals from scatterometry, reflectometry, ellipsometry, slope and photoluminescence detectors to detect and classify yield-limiting, sub-micron defects to support production-line monitoring.

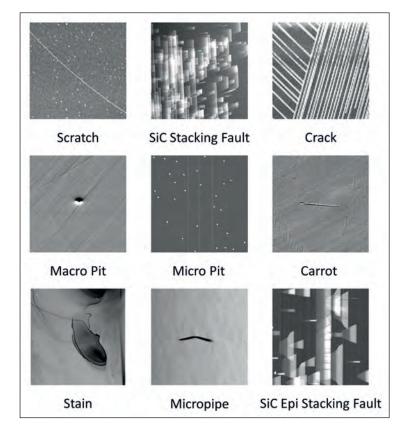

The Candela 8720 system is used to monitor the substrate IQC (incoming quality control) and OQC (outgoing quality control) processes for a variety of defect types including particles, scratches, stains, pits, micropipes, stacking faults and other crystallographic defects.

For the post epitaxial growth process step, the inspection system can detect and monitor process

issues such as cracks, macro epi disturbances (such as droplets), epi pit, epi bump, crystal-oriented defects (such as single/bar stacking faults, BPDs, etc.), micropits and particles. Defects in the substrate and post epi growth can significantly impact end of the line yield, so detecting and correcting such process issues at the source – where cost is the lowest – is critical. Patterned wafer inspection of SiC semiconductor devices is important for reducing defectivity and maintaining traceability, but inspection can present several unique challenges.

Wafer thickness and warpage are outside typical SEMI standards. The transparent (SiC) substrate can create challenges for focus systems and create unwanted noise when imaging the wafer. The 8 Series patterned defect inspection tool addresses these challenges through a specialized prealignment and chuck, selectable illumination wavelengths and depth of focus for inspection, multiple inspection channels and increased wafer handling flexibility.

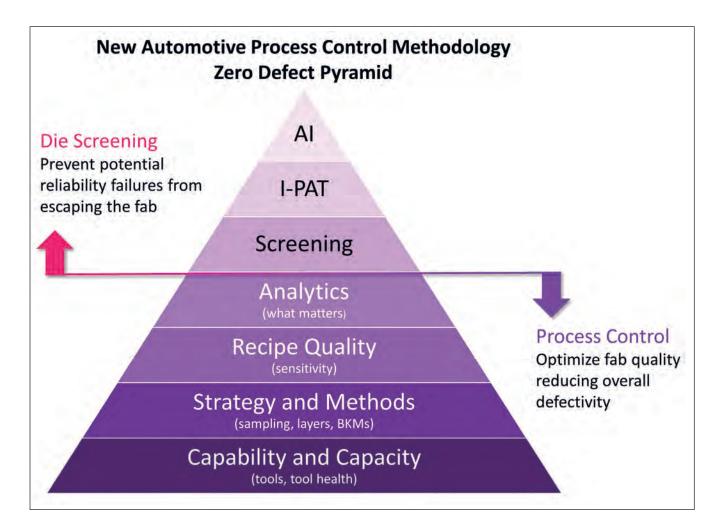

With simultaneous brightfield and darkfield inspection capability, it captures all types of surface defects with a multi-level defect binning solution. With optional back side inspection capability, the 8 Series system can handle and inspect both frontside and back side Figure 1: New automotive process control methodology Zero Defect pyramid

of 6" SiC pre- and post-grind wafers offering high precision frontside to back side correlation and die inking for process-induced killer defects on both sides of the wafer.

It is important to note that beyond some of the early SiC process steps, the many remaining steps for SiC are very similar to a standard silicon chip process, so SiC fabs will utilize similar process control strategies compared to silicon IC fabs.

MA: Producing automotive ICs and packaged devices present unique challenges beyond greater reliability such as the need to produce spare parts for years longer than consumer electronics. How does KLA technology help device manufactures meet these critical needs?

**KLA:** Automotive fabs have faced this problem for years and they do it by maintaining the process control strategies and standards that they used successfully in the past. This is shown through the defect pyramid (see Figure 1). In order to help maintain these strategies along with the best performing tools, KLA works with our customers in two areas:

• KLA helps customers by making continuous improvements on the process control platforms through product upgrades.

• KLA provides an extensive service package that helps our customers ensure that the process control tools are performing at the highest levels.

In addition, KLA also offers metrology and inspection

tools that enable component sorting to prevent defective devices arriving at the assembly line and to keep track records of each device. Metrology helps verify whether device dimensions are within tolerance and thus confirming the quality of packaged products; inspection verifies that there are no particles, burrs or other defects present that could impact the yield.

#### MA: Can KLA detail its approach to supporting the power devices market and how experience in supporting other areas of the IC industry benefit their approaches to power electronics?

KLA: The company has been delivering solutions and support to the SiC and GaN power device market segment for some time. Leveraging our vast experience in developing new technology capable of solving complex inspection and metrology challenges across the IC industry to help drive yield improvements, we have developed a comprehensive portfolio of process control solutions specialized for the unique needs of power devices. In addition, through our subsidiary SPTS Technologies, we offer industry leading plasma etch, PVD and CVD wafer processing systems that are used in the manufacture of SiC and GaN devices.

There are several unique challenges in the manufacturing of power devices. Although the design rule is larger, there are special requirements beginning with the substrate and the early epitaxial process. These include, but are not limited to, thickness, wafer handling, substrate shape and quality, epitaxial dislocations, stacking faults and a number of other defect types which could limit the final device yield.

Working closely with our world-wide customers, both in development and in high volume manufacturing (HVM), KLA has engineered, delivered and improved our inspection and metrology offerings to provide the high quality inline data required to help drive yield and continuously improve cycle times.

MA: Packaging power electronics is often a challenge in and of itself. In the past, manufacturers often needed to create new package designs, especially for GaN and SiC. How does KLA support packaging requirements and what are its essential advantages?

**KLA:** The demand for packaging power electronics is widespread across different application types, including mobile and automotive, which results in the development of a wide variety of new packaging technologies to meet different requirements for overall performance, power, form factor and price.

The growth of 5G communication brings an increase in device power consumption, resulting in unique requirements for including more power management ICs. Therefore, development of advanced packages for these types of power devices is expected to

increase, and the resulting innovation will bring greater complexity and new process flows. Generally, IC packages are getting smaller, thinner and more complex, as seen with the integration of multiple dies and passive components into a system in package (SiP), but at the same time requiring higher power density and demanding stricter yield requirements. To meet the yield targets for new packaging technologies, more automated inspection of packages in the assembly and test processes will be required to ensure that defects are identified and sourced quickly during the manufacturing process.

Today's evolving automotive market is being driven by several key areas, most notably connectivity, electrification, and autonomous driving, which is resulting in increased IC content in every car. High reliability requirements for automotive push for Zero Defect standards in manufacturing. Because reliability affects both warranty and liability, as well as the brand image of car manufacturers - and potentially the safety of their customers - process control in packaging, from wafer level to component, will increase significantly in the coming years to find and eliminate the sources of defects and screen for costly excursions. Manufacturers must leverage every available opportunity for continuous improvement across the entirety of their manufacturing value chain to reach that goal.

and adopted. Tolerances on key features (i.e. size, thickness, warpage, interconnect size, alignment, etc.,) for these advanced packages are becoming tighter. Requirements for defect detection and classification accuracy are also increasing. Inline, nondestructive inspection and metrology characterization provide the signals required to enable customers to deliver advanced packaging innovation and differentiated solutions to the market.

High-end 3D profiling and metrology on wafer and panel can be measured with KLA's Zeta 5xx and 6xx systems. Wafer-level inspection and metrology process control with the Kronos<sup>™</sup> wafer inspection system meets the requirements of high sensitivity and production-worthy throughput, while simultaneously addressing the challenges of wafer warpage, thin and thick substrates and numerous process variations typical of advanced packaging processes.

After dicing, the detection of hairline cracks in bare dies or in fan-in wafer-level packaging is achieved with the ICOS<sup>™</sup> F160 die sorting and inspection system. It examines packages after wafers have been diced, delivering fast and accurate die sort based on detection of key defect types – including sidewall cracks, a new defect type affecting the yield of highend packages.

To meet the yield targets for new packaging technologies, more automated inspection of packages in the assembly and test processes will be required to ensure that defects are identified and sourced quickly during the manufacturing process

For more traditional packaging types, the focus is largely on cost. Automatic inspection is available, providing the benefit of reducing overkill and then increasing yield. ICOS <sup>™</sup> T3/T7/T8 and MV component inspection systems provide automated inspection and metrology capabilities across all different types of packages. With modular tool architecture, KLA can offer solutions to meet the requirements of many package types with varying size and interconnect styles.

Beyond traditional packages, mobile applications have been driving the development of smaller (dimensions below 3mm) and more complex packages. These include new technology such as fan-in wafer level packaging (FI-WLP), bare dies, fan-out wafer level packaging (FO-WLP) and SiP (system in package) for silicon-based packages.

We also expect similar levels of packaging innovations for SiC/GaN devices as they are further developed

Once packaged, the ICOS component inspectors provide higher accuracy and repeatability in characterizing key features of advanced packages. With high resolution defect detection, ICOS component inspectors enable discovery and classification of defects smaller than 10 $\mu$ m in mold or substrates and below 1 $\mu$ m for cracks in die.

The unique process control capabilities described thus far are critical to ensure performance of power electronics, but also to ensure optimal yield. Achieving high yields and meeting cycle time goals are challenging with new complex process schemes. Smarter, faster methods of analyzing large data sets and extracting critical information quickly to make decisions is required. Deep learning methodologies paired with advanced defect detection of packages helps to optimize the classification process, reduce overkill and maximize yield. KLA has extensive experience in working with customers to solve new packaging challenges and helping them succeed in

ramping new products while improving overall yield in a cost-effective manner.

MA: How does KLA support the unique inspection/ metrology challenges presented by SiC and GaN?

**KLA:** Starting with the substrate, dimensional wafer metrology systems from KLA's MicroSense offer precise, non-contact, automated geometry measurements including thickness, thickness variations, bow, warp, and 2D and 3D mapping on a wide range of substrates including sapphire, silicon, SiC, GaAs, glass, quartz, ceramics and graphene. For measurement and control of multilayer bonded wafers, our systems can measure total wafer stacks and individual layers throughout the wafer bonding, thinning and de-bonding process steps.

For metrology of power devices, our optical film thickness, overlay patterning and critical dimension instruments are successfully being deployed for inline process control at leading SiC and GaN customer fabs. We have developed a unique transparent wafer option to handle, transfer, align and measure various thin films on SiC on the F5x Pro film metrology system. The KLA Pro Archer<sup>™</sup> overlay metrology platform enables production control of overlay and CD to help provide the data required for correcting the scanner.

For inspection, both SiC and GaN are complex material systems and each have very specific and unique process related defects that manifest in the substrate and after epitaxial growth process. Some of the similarities and differences between the two material systems include:

- Much higher intrinsic material defect densities in SiC based power devices

- Variation in quality among SiC substrate and GaN epi suppliers. SiC substrates are graded and sold by dislocation densities that are native to the substrate

- Morphological defects, crystallographic defects on SiC (such as carrots, triangles, stacking faults, basal plane dislocations), interfacial defects (such as cracks that originate at the interface of GaN and the substrate on which the epi is grown)

- Defects on SiC post epitaxy growth are directional while on GaN the defects are non-directional

KLA has developed unique solutions to meet the inspection requirements of both SiC and GaN materials systems.

The Candela® 8720 compound semiconductor material surface inspection system enables GaN-related materials, GaAs substrate and epi process control with high sensitivity to critical defects to produce GaN based power devices, communications and RF devices, and advanced LEDs (as well as upcoming microLEDs). With its proprietary optical design and detection technology, the Candela inspection tool utilizes signals from scatterometry, reflectometry, ellipsometry, slope and photoluminescence detectors to detect and classify yield-limiting, sub-micron defects to support production-line monitoring.

The next generation of the award winning Candela® CS920 – the industry's first integrated surface and photoluminescence SiC inspection tool - is enhanced with greater sensitivity for monitoring the substrate IQC (incoming quality control) and OQC (outgoing quality control) processes for a variety of defect types including particles, scratches, stains, pits, micropipes, stacking faults and other crystallographic defects. For the post epitaxial growth process step, this inspection system can detect and monitor process issues such as cracks, macro epi disturbances (such as droplets), epi pit, epi bump, crystal-oriented defects (such as single/bar stacking faults, BPDs, etc.), micropits and particles.

Defects in the substrate and post epi growth can significantly impact end of the line yield, so detecting and correcting such process issues at the source is critical--where cost is the lowest. Patterned wafer inspection of SiC semiconductor devices is important for reducing defectivity and maintaining traceability, but this need presents several unique challenges. Wafer thickness and warpage are outside typical SEMI standards. The transparent substrate can create challenges for focus systems and create unwanted noise when imaging the wafer. The 8 Series patterned defect inspection tool addresses these challenges through a specialized pre-alignment and chuck, selectable illumination wavelengths and depth of focus for inspection, multiple inspection channels and increased wafer handling flexibility.

With simultaneous brightfield and darkfield inspection capability, the tool captures all types of surface defects with a multi-level defect binning solution. With optional back side inspection capability, the 8 Series system can handle and inspect both the front side and back side of 6-inch SiC pre- and post-grind wafers offering high precision front side to back side correlation and die inking for process-induced killer defects on both sides of the wafer. As the demand for power devices continues to grow, we are adapting our portfolio to the needs of our customers, so they have the data they need to control their process. Both SiC and GaN have unique challenges compared to silicon; inspection and metrology data can help provide valuable information required to move the process from R&D to high volume production.

**Replies from KLA Corporation were supplied by:** Robert Cappel, Senior Director of Marketing; David P. Price, Sr. Director, Automotive Technical Solutions;

Mukundkrishna Raghunathan and Oliver Dupont, Product Marketing Managers."

## 10000 SEMI STANDARDS & COUNTING

## Industry counts on SEMI standards.

SEMI is the global industry association serving the product design and manufacturing chain for the electronics industry.

Check out our new standards on SMT & PCB Manufacturing Equipment Communication, Panel Level Packaging & Energetic Materials at:

www.semi.org/collaborate/standards

## Smart manufacturing enabled in the sub-fab

The Industry 4.0 movement is rapidly becoming the de facto means to optimize cost-effective manufacturing. Power electronic device makers want to leverage any practical idea. The experts at Edwards Vacuum point their customers to proven methods that can rapidly reduce costs while improving uptime by focusing on a part of the fab that manufacturers don't always think of first in the quest for a healthier bottom line.

#### BY ALAN IFOULD, ERIK COLLART, ANTONIO SERAPIGLIA, AND MICHAEL MOONEY, EDWARDS VACUUM

IN THE BROADEST TERMS, smart manufacturing refers to collecting data from all aspects of the manufacturing process and by using advanced analytical and modeling capabilities, like artificial intelligence and machine learning, process performance and productivity are improved. It has been embraced by manufacturers in all industries and hailed as the fourth industrial revolution (Industrie 4.0). Semiconductor manufacturers have a long history of collecting and analyzing process data, a key smart manufacturing concept, to improve performance in the fab. Now semiconductor manufacturers are realizing the potential benefits of extending smart manufacturing technologies to the support systems housed in the sub-fab.

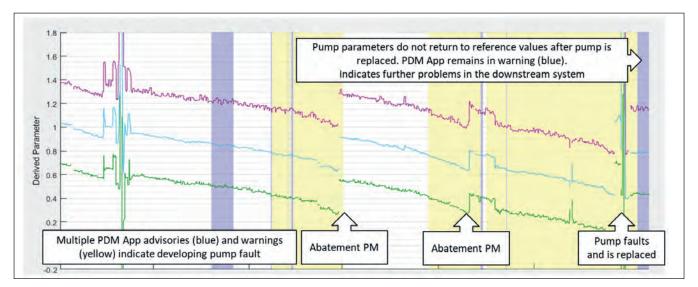

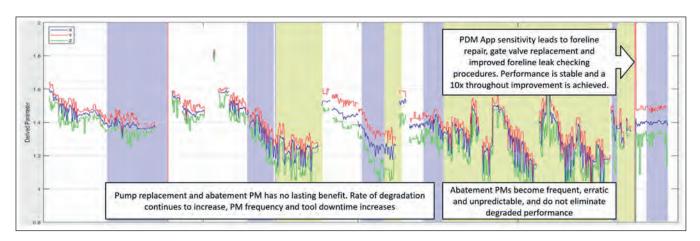

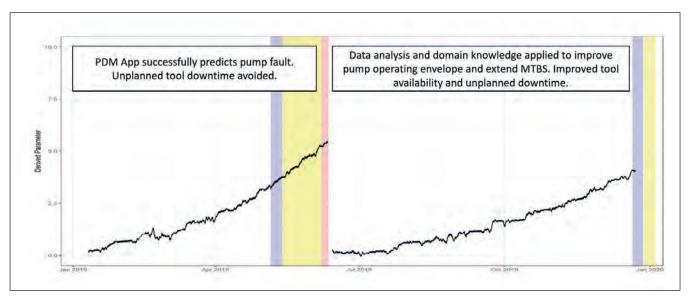

Figure 1: Output from a predictive maintenance application (PdM app) monitoring a vacuum pump

Driven by recent developments in the fields of sensors, data management, analytics and artificial intelligence, a new vision for manufacturing has emerged. This vision includes integrating supply chains; creating virtual factories with cyber-physical systems and digital twins; using big data techniques to interrogate tool, process, yield and facility data; and accumulating and applying critical domain knowledge. Smart manufacturing is a broad concept that is perhaps best generally described as combining technologies and solutions to optimize operations by reducing and/or managing risk and uncertainty. In more practical terms, it is using big data infrastructure and information technology to provide advanced analytics and create a knowledge network of subject matter expertise and operational excellence models. It connects people, machines and processes in a more effective way.

Semiconductor manufacturers have been using advanced automation and statistical control techniques for a long time. As fabs have become more expensive and the cost of unexpected downtime has increased, they have enhanced their capabilities using smart manufacturing concepts. They are also extending them to the critical process support systems found in the sub-fab. The sub-fab has evolved dramatically over the years, from what was originally simply a location outside the fab in which to house supporting equipment, to an environment that is in many ways as sophisticated as the fab itself. A typical HVM fab, starting 40,000 wafer per month, may have 1,500 process tools. It's sub-fab will have 2,000 vacuum pumps and 1,000 abatement systems plus other ancillary systems. Most of the critical steps in a chip manufacturing process require high vacuum conditions and the unexpected failure of a pump can bring significant disruption to the manufacturing process, imposing heavy penalties in lost productivity and scrapped product.

Smart manufacturing in the sub-fab enhances vacuum security with comprehensive monitoring of process critical vacuum and abatement equipment. Using specifically designed models and algorithms, it can predict catastrophic failure modes related to hazardous process chemicals, high flowrates of flammable gases, ingestion of solid materials and condensation of liquids and solids.

It can also deliver rapid root cause analysis for new and harsh process steps and materials, provide real-time intelligence on critical process vacuum state, accelerate yield ramp by correlating vacuum behaviour with wafer yield, and support fast installation of new sub-fab equipment. Figure 2: PdM data from a process tool in an HVM environment was delivering only 10% of the wafer throughput of other comparable tools

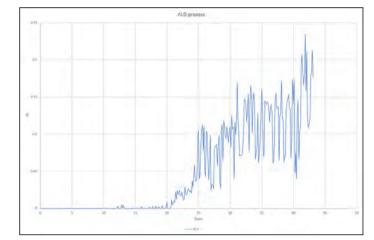

Figure 3 Vibration signal from a pump on an atomic layer deposition tool (left) and a photo of material deposited on internal components.

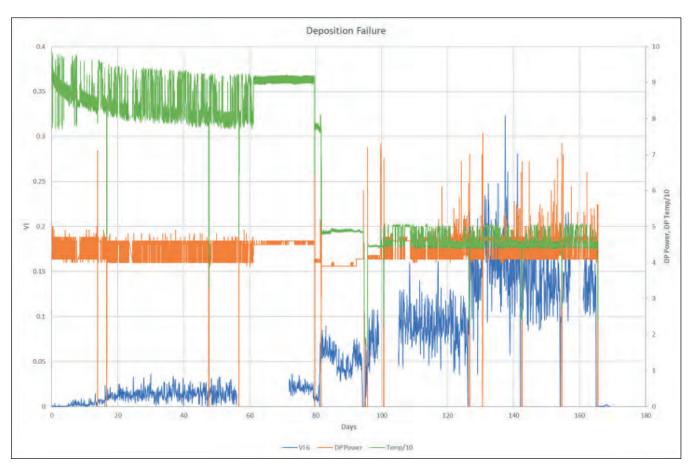

Figure 4: Dry pump power (orange) and temperature (green), and vibration data (blue) taken from a pump supporting an LP-CVD  $Si_{3}N_{4}$  batch deposition process

#### A systems approach to the sub-fab

There is a growing understanding that vacuum pumps and abatement systems are not isolated, selfcontained pieces of equipment. They react to each other and to the wider vacuum system that includes forelines, gate valves, other vacuum components and fab process tools. Monitoring pump parameters can reveal the health of individual pumps and also the health of up- and downstream components, including forelines, gate valves, and process chambers. Data acquired at the pump or abatement system can help determine the size and location of vacuum system leaks.

Algorithms based on vacuum science and thermodynamics can lead engineers to problems that, over time, can have a significant impact on yield. Figure 1 shows output from a predictive maintenance application (PdM app) monitoring a vacuum pump in an HVM environment. The plotted parameter is derived from a multivariate analysis and is responsive to various fault types.

The downward trend in this plot indicates gradual degradation, interrupted by a temporary re-setting. Comparing sub-fab maintenance records with parameter time stamps showed a one-to-one

correspondence between reset events and preventive maintenance procedures performed on the abatement system for the same process tool, indicating that the degradation was connected to the state of the abatement equipment, rather than the health of the pump itself. This was corroborated by other pump parameters not part of the PdM app. The evolution over time further suggested that the abatement PM's themselves did not fully address the issue at hand: the derived parameters did not return to their default values and the downward trend resumed immediately. Ultimately, successful diagnosis of pump faults, combined with the successful segmentation of external downstream issues, resulted in reductions in unscheduled tool down time.

Figure 2 illustrates a case where a process tool in an HVM environment was delivering only 10% of the wafer throughput of other comparable tools. A multivariate PdM App was monitoring the vacuum pump health. The time-series plot of derived parameters clearly showed degradation over time, interrupted by abatement PM-driven re-sets. Initially, the degradation was not as severe and abatement PMs re-set the pump health as indicated by the multiple step changes. But degradation resumed almost immediately after each step improvement.

As time went on this degradation worsened, in spite of the increasing frequency of preventive maintenance on pumps and abatement units. Multiple PdM App alerts were issued. This and other indicators pointed to leaks in the upstream vacuum system. Ultimately a thorough review and repair of forelines and gate valves resolved the issue and resulted in an improved, integrated vacuum system leak check procedure. The wafer throughput gradually returned to match the throughput of peer systems, a 10x improvement for this particular tool.

#### Sensorization

One of the key requirements for smart manufacturing is the development and implementation of sensors to collect and record new signals, beyond the power and temperature sensors typically used to monitor pump health and performance. An innovative vibration sensor (EdCentra Vision, Edwards Vacuum) illustrates some of the requirements and challenges encountered in this "sensorization".

Measuring vibration to monitor the health of rotating machines has a long and successful history. Intrinsic bearings frequencies can be calculated from rotation speeds, and wear-generated perturbations of these frequencies can indicate bearings faults. However, these methods do not translate well to a semiconductor environment where process-induced failure modes are more common than wear-induced. The effects of process-induced failure modes on standard vibration spectra are largely unknown and analysis is complicated by high noise levels.

The new method unlocks key predictive information from vibration data and can detect failure modes that cannot be seen by conventional vibration detectors. It uses a retrofittable "edge" sensor module that includes both sensing and data processing capability to reduce bandwidth requirements on the communications network. Its innovative data analytics methodology translates the complex, noisy vibration signal into a single dynamic coefficient that is easy to compare with existing predictive maintenance parameters. Further vibrational sub-band analysis can provide specific failure mode identification and root-cause analysis, thus providing valuable fault classification (FC) capability.

Compared to conventional methods, the new approach increases sensitivity and provides extended, and in some cases unique, predictive maintenance capability for mechanical pump failure modes. Figure 3 shows the vibration signal from a pump on an atomic layer deposition tool. This pump was pro-actively removed from service based on the progression and value of some of the vibration parameters, even though the next calendar-based maintenance was not imminent.

Other pump parameters (not shown), failed to indicate pump deterioration. A detailed analysis of the pump after removal indicated that it was very close to faulting. The picture on the right in figure 3 shows part of the internal pump mechanism with significant process deposition and confirming the vibrationbased prediction. Early replacement prevented unscheduled process downtime and potential losses from wafer scrap. The data management system used to collect this data can combine it with other pump and abatement data in a multi-variate analysis to significantly enhance predictive power and accuracy.

Figure 4 demonstrates the sensitivity of vibration analysis in tandem with traditional pump parameters used historically to monitor conditions. The figure shows an example of pump parameters, dry pump power (orange) and temperature (green), and vibration data (blue). The failure mode in this case was deposition related. As shown in Figure 4, from day 80 onward changing process conditions caused a step-change in temperature. The power curve shows developing patterns at around the 120-day mark, indicating a predictive time horizon of about 40

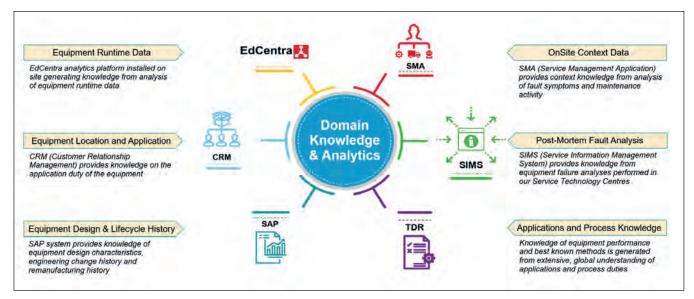

Figure 5: Information sources for domain knowledge

Figure 6: Application of domain knowledge improves pump operating envelop and extends MTBS days. An important observation to make here is that the vibration data (blue curve) reacted immediately to the modal change and the increased impact of condensable process by-product adversely affecting the operation of the pump.

The heightened sensitivity of vibration gave a pointof-detection time period of around 75 days, 25 days greater than traditional pump parameters. Although vibration analysis is not a new technique, the new vibration sensor detected anomalies otherwise missed by traditional monitoring techniques. Importantly, it has added considerably to the ability to detect process-induced changes to the vacuum pump. Its implementation of edge computation reduces data volume, enables real time analytics and shortens detection latency.

#### Safety

No discussion of smart manufacturing can be complete without considering its potential impact on safety in the sub-fab. The sub-fab is a dangerous place, and safe working practices must be maintained alongside new business processes enabled by smart manufacturing. Examples of potential benefits include: providing advance notice of required equipment interventions so that activities can be better planned, thereby reducing risk and uncertainty associated with the time pressure of urgent activities; using technology to deliver safe standard operating procedures (SOP) and best known methods (BKM) for equipment installation; and incorporating safety data and observations along with asset performance data in the domain knowledge that drives a holistic approach to reducing risk and uncertainty.

#### Domain knowledge is central

Domain knowledge and subject matter expertise are key in providing the right context for any type of machine learning and data science application within smart manufacturing. They are key for several reasons, including the complexity of the manufacturing process, the dynamic nature of dayto-day operations and the general unavailability of large, unambiguous and consistent data sets. People will manage, operate and optimize machines with the

Domain knowledge and subject matter expertise are key in providing the right context for any type of machine learning and data science application within smart manufacturing. They are key for several reasons, including the complexity of the manufacturing process, the dynamic nature of day-to-day operations and the general unavailability of large, unambiguous and consistent data sets

help of digital technologies. Processes will define the interaction of machine to machine, people to machine, and people to people. This constitutes a domain knowledge supply chain essential to enabling smart manufacturing.

For sub-fab vacuum and abatement equipment, domain knowledge encompasses multiple areas of know-how, ranging from specific knowledge of how a process or a piece of equipment works to all the ways the process interacts with the world in which it exists. Vacuum science and thermodynamics provide the basic laws governing critical parameters such as pressure, flow, temperature, and pumping speed. These all display linear and non-linear responses, instantaneous changes, and long-term trends that need to be considered.

Equipment behavior is also ruled by the details of electronic sub-assemblies and mechanical construction. This specific domain knowledge is, for instance, required to distinguish between normal, instantaneous power spikes from pump-vent cycles or powder ingestion and abnormal power spikes from gradual film deposition over long periods of time. A third area relates to the sequence of wafer processing vs. idle and how it affects parameter behavior over time.

The last areas of domain knowledge, measured and inferred alert states and measured degradation states, relate to quantifying and calibrating the progression of abnormal behavior against PdM alert states. Depending on process and equipment type different parameter sets and thresholds may be needed to accurately capture this.

Figure 5 summarizes sources of information that provide critical input for developing domain knowledge.

Figure 6 shows a practical example of domain knowledge at work. PdM Apps, built using domain knowledge, were used to monitor the condition of the pump. The first blue/yellow/band indicates a successful fault prediction that eliminated an unscheduled tool down event. Domain knowledge was then applied to change the operating envelope of the vacuum system. Note the right-hand side of the graph shows a much slower degradation of performance before a second successful fault prediction. This delivers the additional benefit of a longer MTBS and thus tool availability.

#### Tying it together - operational excellence

Smart manufacturing connects people, machines and processes. The full benefit of any smart manufacturing strategy is only realized once these three elements work effectively together to reduce and/or manage risk and uncertainty. Considering the examples discussed, a PdM App may provide a good indication of a fault Equipment behavior is also ruled by the details of electronic subassemblies and mechanical construction. This specific domain knowledge is, for instance, required to distinguish between normal, instantaneous power spikes from pump-vent cycles or powder ingestion and abnormal power spikes from gradual film deposition over long periods of time