# EMPOWER THE INTELLIGENCE REVOLUTION

Visit **ASMPT Semiconductor Solutions** at Booth # C1131

semi.asmpt.com

#### **Fabrication fragmentation**

PICS are often compared and contrasted with their traditional electronic counterparts, and for good reason. There's much to learn from the success of the established semiconductor industry and how it might be replicated with photonic chips, while also identifying the physical differences that present unique manufacturing challenges.

But the PIC industry's evolution – and its potential divergence from the path that its electronic predecessors have taken – may be influenced by more than just intrinsic technical details. After all, this industry is maturing in a notably different geopolitical atmosphere from the one in which semiconductors originally flourished.

The consolidation of manufacturing in a handful of countries occurred in a time of relative peace and liberal trade. And perhaps it was not yet clear just how vital these chips would prove to be. Now, amidst raised and rising global tensions, countries are under no illusions about how essential a resource they are, both for domestic infrastructure and for economic relevance on the world stage.

PICs, despite being in an earlier phase of development, are already recognised as part of this critical sector. And they have not been left out of the drive to build up domestic supply chains – a trend which has continued this year. In June, for instance, GlobalFoundries announced its "reshoring" investment of \$16 billion in US semiconductor production, with focus areas including silicon photonics.

But while countries seek to loosen their reliance on global supply chains for silicon, novel PIC platforms may offer an opportunity to establish a better level of independence from the get-go. For example, this year has seen major announcements from three foundries producing TFLN PICs

– which are rapidly gaining traction – on three different continents. In May, QCi officially opened a new TFLN facility in Arizona, US. The same month, CSEM announced that it had launched the spin-off CCRAFT in Switzerland, describing it as the first production-ready pure-play TFLN foundry. In June, reports emerged that CHIPX in Shanghai had officially begun producing TFLN chips, in China's first PIC pilot line.

While some consolidation may happen at a company level, we might not see a replay of the geographical concentration of manufacturing that took place with silicon. Is this a good thing for the industry? Efficiency and resilience are often conflicting imperatives. It was economic efficiency, after all, that drove the current geographical

#### **COVER STORY**

## The essential link in next-generation optical connectivity

With industry-ready 3D nano-printing solutions, Vanguard Automation is lighting the path to scalable and reliable processes for integrating active components to PICs

#### 20 A seamless PIC design workflow for datacentre interconnects

VPIphotonics' universal design automation framework empowers design teams to model and optimise PICbased optical datacentre interconnects at every level, from submicron integrated devices to kilometre-scale fibre links

### 26 Harnessing sound waves for photonic neuromorphic computing

Optical neural networks could bring about sustainable, energy-efficient AI, but fulfilling this vision requires further advances in scalability and reconfigurability

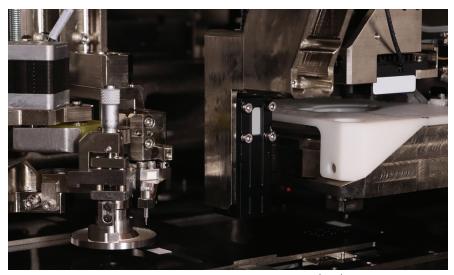

### 30 Unlocking 3D-CPO: The industry's first double-sided electro-optical wafer tester

As the telecom industry adopts co-packaged optics at scale, ficonTEC has developed a product strategy that enables volume testing of next-generation optical engines for high-performance computing in datacentres

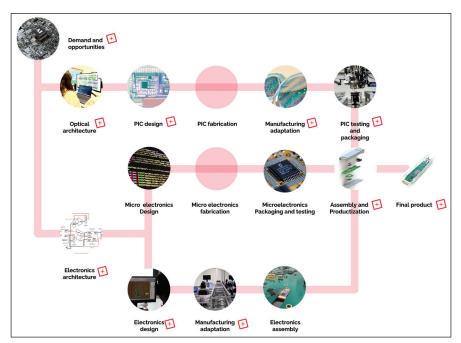

### 34 Accelerating toward the future of connectivity with photonic integration

The Al-driven surge in data traffic and disaggregated computing demand more integrated optical networking technologies

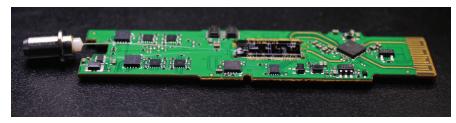

#### 38 Achieving precision for photonics with multi-chip bonding

With a focus on upcoming trends in advanced packaging, the new multi-chip bonding platform, MEGA, is the latest example of how ASMPT Semiconductor Solutions is pushing the boundaries of precision and speed in semiconductor manufacturing

#### 42 Shaping the future of cloud Al with silicon photonics

Silicon photonics is transforming Cloud AI with highspeed, energy-efficient data movement. Soitec's Photonics-SOI engineered substrates are key enablers, enhancing performance, scalability, and integration for next-gen AI infrastructures

#### **NEWS**

- 06 Terakraft and Neurophos collaborate on sustainable Al

- 07 OpenLight closes \$34 million Series A funding round

- 08 Lightmatter achieves 16-wavelength bidirectional link on standard optical

- 10 Lightium, MPI Corporation and Axiomatic Al partner on PIC testing

Laura Hiscott Contributing Technical Editor

Richard Stevenson richard.stevenson@angelbc.com Sales & Marketing Manager shehzad.munshi@angelbc.com

Shehzad Munshi Design & Production Manager

Mitch Gaynor mitch.gaynor@angelbc.com Publisher

Jackie Cannon jackie.cannon@angelbc.com

laura.hiscott@angelbc.com

+44 (0)1923 690215

+44 (0)1923 690215

+44 (0)1923 690214 +44 (0)1923 690205 Sales and Product Manager

James Cheriton james.cheriton@angelbc.com +44 (0)2476 718970

CEO Sukhi Bhadal sukhi.bhadal@angelbc.com CTO Scott Adams scott.adams@angelbc.com

Angel Business Communications Ltd, 6 Bow Court, Fletchworth Gate, Burnsall Road, Coventry CV5 6SP, UK. T: +44 (0)2476 718 970 E: info@angelbc.com W: picmagazine.net

+44 (0)2476 718970

+44 (0)2476 718970

PIC Magazine is published four times a year on a controlled circulation basis. Non-qualifying individuals can subscribe at: £105.00/e158 pa (UK & Europe), £138.00 pa (air mail), \$198 pa (USA). Cover price PIC Magazine is published four times a year on a controlled circulation basis. Non-qualifying individuals can subscribe at: £105.00/e158 pa (UK & Europe), £138.00 pa (air mail), \$198 pa (USA). Cover price £4.50. All information herein is believed to be correct at time of going to press. The publisher does not accept responsibility for any errors and omissions. The views expressed in this publication are not necessarily those of the publisher. Every effort has been made to obtain copyright permission for the material contained in this publication. Angel Business Communications Ltd © Copyright 2025. All rights reserved. Contents may not be reproduced in whole or part without the written consent of the publishers. The paper used within this magazine is produced by chain of custody certified manufacturers, guaranteeing sustainable sourcing. US mailing information: Pic Magazine, ISSN 1096-598X, is published 4 times a year, March, May, August and December by Angel Business Communications Ltd, Unit 6, Bow Court, Fletchworth Gate, Burnsall Rd, Coventry CV5 6SP, UK. The 2025 US annual subscription price is \$198. Airfreight and mailing in the USA by agent named Air Business Ltd, c/o Worldnet Shipping Inc., 156-15, 146th Avenue, 2nd Floor, Jamaica, NY 11434, USA. Periodicals postage paid at Jamaica NY 11431. US Postmaster: Send address changes to Pic Magazine, Air Business Ltd, c/o Worldnet Shipping Inc., 156-15, 146th Avenue, 2nd Floor, Jamaica, NY 11434, USA. Printed by: The Manson Group. © Copyright 2025. We strive for accuracy in all we publish; readers and contributors are encouraged to contact us if they recognise an error or omission. Once a magazine edition is published [online, in print or both], we do not update previously published articles to align old company names, branding, marketing efforts, taglines, mission statements or other promotional verbiage, images, or logos to newly created or updated names, images, typographic renderings, logos (or similar) when such references/images were accurately stated, ren

### Terakraft and Neurophos collaborate on sustainable AI

The companies plan to run a pilot in 2027, offering early access to Neurophos' ultraefficient optical chips for Al inference hosted in Terakraft's fully renewables-powered datacentre

AI DATACENTRE operator Terakraft and AI chip company Neurophos have announced that they are collaborating to provide sustainable, high performance, and energy efficient AI infrastructure.

As the Al-driven surge in demand for data continues, a major challenge is the enormous amounts of energy required to power and cool computing infrastructure. Terakraft and Neurophos seek to demonstrate that a combination of green datacentres and breakthrough hardware can meet these needs in a sustainable way.

Terakraft, which is based in Norway, says its infrastructure is fully powered by renewable hydropower and cooled with natural lake water, achieving a power usage effectiveness (PUE) below 1.1, which it says is among the best metrics in the industry. The company is repurposing an existing hydropower plant built with reinforced concrete, with the goal of avoiding additional embodied carbon and setting a new

benchmark for low-emission operations.

Meanwhile, Neurophos has developed Al hardware with proprietary optical processing units which it says are 100x more energy efficient than leading GPUs for the same workload.

The company says it has successfully fabricated, demonstrated, and characterised its miniaturisation of optical modulators by a factor of 10,000x, enabling future optical processing units to deliver the compute power of 100 GPUs while consuming the equivalent of 1 percent of the energy, validated by end-toend simulation results. According to Neurophos, its compute-in-memory architecture, which is inspired by the human brain's efficiency, allows for unprecedented processing speeds and density, making ultra-efficient, large-scale Al inference practical and scalable.

The companies plan to host a pilot as part of a commercial early access

programme in 2027 for Neurophos' accelerated Al inference platform – a project that aims to provide a real-world proving ground for sustainable, ultraefficient compute.

"By hosting Neurophos' ultra-efficient optical chips in our green datacentre for select enterprise clients, we not only reduce our carbon footprint but also raise the bar for energy-efficient Al infrastructure," said Giorgio Sbriglia, chairman of the board of Terakraft. "Our mission has always been to power the future responsibly, and this collaboration brings that vision to life."

Patrick Bowen, CEO and founder of Neurophos, added: "Terakraft's commitment to renewable energy and innovative technologies aligns perfectly with our mission to democratise high-performance Al. By deploying our 100x more efficient inference chips in Terakraft's green datacentre we're proving that Al's exponential growth can be achieved sustainably, together."

### OpenLight closes \$34 million Series A funding round

The company plans to use the new investment to expand its PDK library, which is based on the heterogeneous integration of indium phosphide and silicon photonics, and scale its team to support customers as they transition to volume production

OPENLIGHT, a company focusing on custom photonic application-specific integrated circuit (PASIC) chip design and manufacturing based on heterogeneous integration, has announced that it has closed its oversubscribed \$34 million Series A funding round.

The round is co-led by Xora Innovation and Capricorn Investment Group. Other participants include Mayfield; Juniper Networks, now part of HPE; Lam Capital, the corporate venture arm of Lam Research Corporation; New Legacy Ventures; and K2 Access.

OpenLight says that this round of financing completes its transition from a Synopsys subsidiary to a high-velocity, venture-backed company positioned to address the growing demand for faster and more energy-efficient data movement in Al datacentre networks.

As the shift from electrical to optical interconnects accelerates to support Alscale workloads, integrated photonics is emerging as a core enabler of next-generation datacentre infrastructure. Additional applications for OpenLight's technology include telecom, automotive and industrial sensing, IoT sensing, healthcare and quantum computing.

OpenLight has developed a Process Design Kit (PDK), based on the heterogeneous integration of indium phosphide and silicon photonics, which aims to give customers access to a library of passive and active components covering integrated lasers, modulators, amplifiers and detectors.

The company says its PDK has been validated at the leading photonics foundry Tower Semiconductor, ensuring designs are production-ready from day one

According to OpenLight, this enables customers to create custom PASICs using proven building blocks, simplifying advanced chip development and accelerating time to market.

The company adds that it currently holds more than 360 patents covering its PDK and the manufacturing of heterogeneously integrated III-V photonics, and that its PDK is already being used by over 20 companies to design and fabricate PASICs across a wide spectrum of applications.

With the new capital injection, OpenLight plans to expand its PDK library of active and passive photonics components, including its 400G modulator and indium phosphide heterogeneously integrated on-chip laser technology. The company also aims to ramp up its standard-based reference PICs at 1.6T and 3.2T to provide customers with the most flexible and leading-edge component design library available in the market. In addition, OpenLight says it will scale its team to support customers as they transition to volume production over the next 12 months.

"As we enter this next phase of our company's growth, we are excited to be adding such strong investors with deep roots and expertise in the semiconductor and photonics industry,"

said Adam Carter, CEO of OpenLight. "With this strong syndicate of investors, we can push the boundaries of innovation and deliver transformative solutions to our customers. This funding will allow us to scale our operations, deepen our R&D efforts and bring our groundbreaking products to market faster. We believe heterogeneous integrated silicon photonics will transform the way data is processed and transmitted, and we're excited to be at the forefront of this revolution."

Phil Inagaki, managing partner and chief investment officer at Xora, commented: "Xora has conviction that the field of photonics is going to see exponential growth in the coming years, and III-V heterogeneous integration is one of the foundational capabilities that will enable this growth."

"We see OpenLight not only as a technology leader in this field, but also as a company positioned to quickly scale manufacturing with foundry partners. One of the critical challenges for the photonics industry in the back half of this decade will be achieving scale, and we see OpenLight's PDK as an important part of the solution."

Dipender Saluja, managing partner at Capricorn's Technology Impact Funds, added: "Optical connectivity in datacentres has become critical for next-generation scale-up and scaleout Al architectures. OpenLight's heterogeneous integration delivers on all three axes of performance, reliability and cost, which will enable the explosive growth of optical IO. With the industry's leading team, open PDKs, strong foundry and customer relationships, OpenLight is best positioned to meet the scale of demand that is needed for next-generation Al hardware."

### Lightmatter achieves 16-wavelength bidirectional link on standard optical fibre

The company says this breakthrough advances chip I/O design by increasing bandwidth per fibre compared to existing co-packaged optics solutions, and enables more powerful, efficient, and scalable datacentres

LIGHTMATTER, a company focusing on photonic supercomputing, has announced it has developed a 16-wavelength bidirectional dense wavelength division multiplexing (DWDM) optical link operating on one strand of standard single-mode (SM) fibre. Powered by Lightmatter's Passage interconnect and Guide laser technologies, the company says this achievement shatters previous limitations in fibre bandwidth density and spectral utilisation, setting a new benchmark for high-performance, resilient datacentre interconnects.

With the rise of complex trillionparameter "mixture of experts" models, scaling AI workloads is increasingly bottlenecked by bandwidth and radix (I/O port count) limitations in datacentre infrastructure. Lightmatter says its Passage technology delivers an unprecedented 800G bidirectional bandwidth (400G transmit and 400G receive) per single-mode fibre for distances of several hundred metres or more. This achievement advances chip I/O design by simultaneously increasing both radix and bandwidth per fibre compared to existing co-packaged optics (CPO) solutions, the company adds

While commercial bidirectional transmission on a single fibre has been limited mainly to two wavelengths, achieving 16 wavelengths (also referred to as "lambdas") has historically required multiple or specialised fibres.

According to Lightmatter, this milestone addresses significant technical challenges related to managing complex wavelength-dependent propagation characteristics, power budget constraints, optical nonlinearity, and mitigating crosstalk and backscattering in a single fibre.

Such innovations could pave the way for the next major advances in Al model development, which demand more extensive and efficient high-bandwidth networking than exists today.

"Datacentres are the new unit of compute in the Al era, with the next 1000X performance gain coming largely from ultra-fast photonic interconnects," said Nicholas Harris, founder and CEO of Lightmatter. "Our 16-lambda bidirectional link is an architectural leap forward. Hyperscalers can achieve significantly higher bandwidth density with standard single-mode fibre, reducing both capital expenditure and operational complexity, while enabling higher 'radix' – more connections per XPU or switch."

Alan Weckel, co-founder and analyst at 650 Group, added: "Lightmatter's innovation arrives at a pivotal moment for hyperscale Al infrastructure.

The ability to dramatically increase bandwidth density on existing single-mode fibre, coupled with the technology's robust thermal performance, is a game-changer for datacentre scalability and efficiency. This solves one of the most pressing challenges in Al development and brings advanced CPO a giant step closer to market."

According to Lightmatter, the new breakthrough incorporates a proprietary closed-loop digital stabilisation system that actively compensates for thermal drift, ensuring continuous, low-error transmission over wide temperature fluctuations. In addition, architectural innovations aim to make the Passage 3D CPO platform inherently polarisation-insensitive, maintaining robust performance even when the fibres are being handled or subject to mechanical stress.

Standard SM fibre, while offering immense bandwidth potential, does not inherently maintain light's polarisation state, unlike specialised and more costly polarisation-maintaining fibre. By achieving polarisation insensitivity, Lightmatter says it enables the use of cost-effective SM fibre for its bidirectional DWDM technology.

This combination of fibre bandwidth density, efficient spectral utilisation, and robust performance makes

Lightmatter's Passage technology foundational for the industry's transition from electrical to optical interconnects in Al datacentres, the company concludes. It aims to empower customers to accelerate development of larger and more capable Al models with more powerful, efficient, and scalable datacentres.

# Double-sided Wafer-level Testing

#### with Scalable CPO Production Solutions

- Hard-dock ATE integration on the top-side of the wafer

- · High-precision alignment engine underneath the wafer

- Slotted specialty 300 mm wafer chuck with thermal & vacuum

- · Retractable slim-profile vision system for wafer referencing

- Electrical Probe tip inspection and cleaning

- Compatibility with wafer autoloader

### Lightium, MPI Corporation and Axiomatic Al partner on PIC testing

The companies say their Al-driven solution sets a new industry benchmark for efficiency, precision, and scalability, lowering the total cost of testing and accelerating time-to-market for next-generation PIC devices

LIGHTIUM AG, MPI

Corporation, and

Axiomatic\_AI Inc.

have announced they

have entered into

a memorandum of

understanding (MoU) to

jointly develop a platform

that they describe as the

world's first Intelligent,

Autonomous, and

Integrated Test Solution

(IAITS) for photonic devices.

This strategic collaboration aims to revolutionise the testing and qualification processes of PIC devices by uniting state-of-the-art AI, next-generation hardware, and deep domain expertise.

The companies say the IAITS platform will deliver breakthrough performance in testing workflows, enabling unmatched efficiency, precision, and scalability to meet the ever-evolving demands of the photonics industry.

According to the companies, this partnership is motivated by a shared commitment to deliver groundbreaking Al-driven and self-optimising solutions to the photonics industry. By combining

Axiomatic\_Al's reasoning-based Al with MPI's wafer probing systems and automation software, and leveraging Lightium's testing infrastructure and expertise in ultra-high-speed photonic device measurements, the collaboration aims to bring fully integrated, intelligent PIC test solutions to market.

Together, the three companies plan to create a unified AI platform that addresses the growing complexity and performance demands of characterising PICs – unlocking new levels of automation, precision, and scalability for next-generation applications.

The Intelligent,

Autonomous, and

Integrated Test Solution

(IAITS) aims to introduce

a new paradigm in

PIC testing, delivering

transformative value

across both technology

infrastructure and human

capital.

By automating complex test routines, minimising downtime, and optimising measurement system utilisation, the companies say IAITS significantly

accelerates test cycles and reduces iteration times, increasing throughput. Another key benefit that IAITS aims to offer is enhanced human efficiency, achieved by reducing reliance on manual operation, programming, and debugging – freeing skilled personnel to focus on high-value engineering and strategic innovation tasks.

Designed to support both R&D and high-volume production environments, IAITS will be commercially available as an advanced software add-on package for MPI Corporation's wafer probing systems.

- Partnerships with Foxconn, Luxshare, Mitsubishi, NTT, Adtran and others

- Tx and Rx optical engines for 1.6T & beyond pluggable transcievers

- · Light sources to propel Al's growth

- · Lower cost, silicon-based hybrid-integration platform

#### **POET at ECOC EXHIBITION 2025**

September 29 to October 1 | Copenhagen, Denmark

Raju Kankipati

Chief Revenue Officer

- Panelist on Market Potential for CPO

- Product Focus Presentation on POET's 1.6T Optical Engines

#### **LEARN MORE**

poet-technologies.com sales@poet.tech

@POETtech

@POETTechnologies

@POETtechnologies

**#POETpowersAl**

#### 20-22 APRIL 2026 BRUSSELS BELGIUM

#### CONNECTING, EDUCATING & INSPIRING THE PIC INDUSTRY

The 11th PIC International builds on the strengths of its predecessors, with around 40 leaders from industry and academia delivering presentations falling within four key themes:

Those attending these sessions will gain greater insight into device technologies while learning of the latest opportunities and trends within the PIC industry. Delegates will also discover significant advances in tools and processes that deliver enhanced yield and throughput.

Attendees at this two-day conference will also meet a wide variety of key players within the community, from investors and analysts to fab engineers and managers.

PIC International is part of AngelTech, which delivers a portfolio of insightful, informative, highly valued chip-level conferences. Bringing together an Innovate Summit and four conferences with more than 120 presentations, more than 700 delegates and over 80 exhibitors,

AngelTech is the premier global event covering compound semiconductors, photonic integrated circuits, power electronic technologies and advanced packaging.

With a significant overlap between the four conferences, attendees and exhibitors are exposed to the full relevant supply chains and customer and supplier bases.

#### **Key Themes for 2026**

#### Foundations of PIC design: materials, devices and processes

While PICs are well established, they still face technological limitations. How can new materials and devices improve their performance and expand their range of functionalities, and how can we accelerate these innovations to market?

#### Connectivity and scalability for secure, highspeed data networks

Data communications networks face numerous challenges, including soaring Al-driven demands, high energy consumption, and the possibility of future quantum technologies breaking current encryption methods. How can PICs help to solve these issues and underpin the high-speed, energy-efficient, quantum-secure networks of the future?

### Emerging applications: photonics for sensing, imaging and beyond Integrated photonics has a wide range of potential

Integrated photonics has a wide range of potential applications. From self-driving cars to miniaturised molecular sensors and non-invasive healthcare, how are PICs making these possibilities a reality?

### Future computing: PICs for photonic processing, quantum computers, and neural networks

Computing power is integral to the modern world, but established technologies have limits, and novel systems could herald more powerful devices. From fully photonic processing to photonics for neuromorphic and quantum computing, how are PICs transforming the way we process data?

#### Sponsorship / Exhibition / Speaker **OPPORTUNITIES AVAILABLE!**

Sponsorship, exhibition, and speaker opportunities at PIC International, enable and empower you to educate and penetrate the global photonic integrated circuit industry using a plethora of marketing tools.

Demand is high, with sponsorship, exhibition and speaking slots already being secured for 2026, so to avoid disappointment, please get in touch today.

#### **SPECIAL Event Discount:**

Register before 14 November and get 10% OFF!

Registration to AngelTech allows you to access both days of PIC International, CS International, Advanced Packaging and PE International.

#### **SPONSORS**

To find out more about our sponsor and speaker opportunities, contact us today on:

+44 (0) 2476 718970 info@picinternational.net picinternational.net

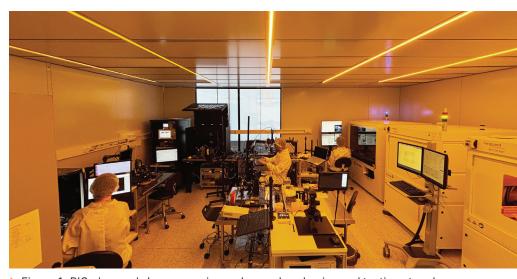

### The essential link in next-generation optical connectivity

With industry-ready 3D nano-printing solutions, Vanguard Automation is lighting the path to scalable and reliable processes for integrating active components to PICs

#### BY LAURA HORAN AND MO LU, VANGUARD AUTOMATION GMBH

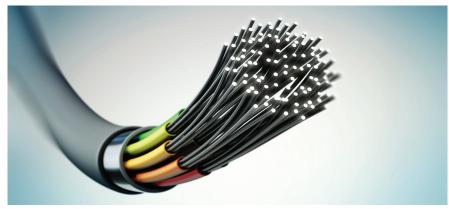

DEMAND is surging for highperformance optics and PICs, driven by AI, datacom, and quantum technologies. LightCounting's recent report on *Optics for AI Clusters* forecasts that the market for optical transceivers used in AI clusters will double from \$5 billion in 2024 to over \$10 billion by 2026 [1]. This underscores how the AI megatrend is reshaping traditional manufacturing, placing pressure on the industry to deliver optical assemblies that ensure precision, reliability, and cost-efficiency at scale.

But there's a major complication in meeting these needs: next-generation designs for photonic products often combine active and passive components in hybrid systems, fabricated on diverse material platforms such as indium phosphide (InP), silicon nitride, silicon, and thin-film lithium niobate (TFLN). Each of these materials has distinct mode-field characteristics and packaging requirements, and integrating active components like edge-emitting lasers into passive PIC materials for hybrid photonics remains a challenge for the industry.

Traditional active alignment techniques enable accuracy down to sub-micron precision, meeting the stringent requirements for mode-field matching and alignment tolerances that are needed to ensure highly efficient signal transmission. But these methods are labour-intensive and difficult to scale from single to multi-channel arrays. This means that packaging costs can amount to up to 80 percent of the cost

of the final product, representing a significant barrier to manufacturing.

At Vanguard Automation, we take a different approach; by combining passive alignment techniques and machine vision with high-precision and fully automated 3D nano-printing, we develop scalable and high-throughput manufacturing solutions for hybrid photonic integration. Headquartered in Karlsruhe, Germany, and now a part of Mycronic, a global supplier of high-precision manufacturing tools, Vanguard Automation is uniquely positioned to deliver advanced manufacturing tools to the market.

Across datacentre, telecommunication, and AI applications, a range of users [2] working on various material platforms have proven that Vanguard

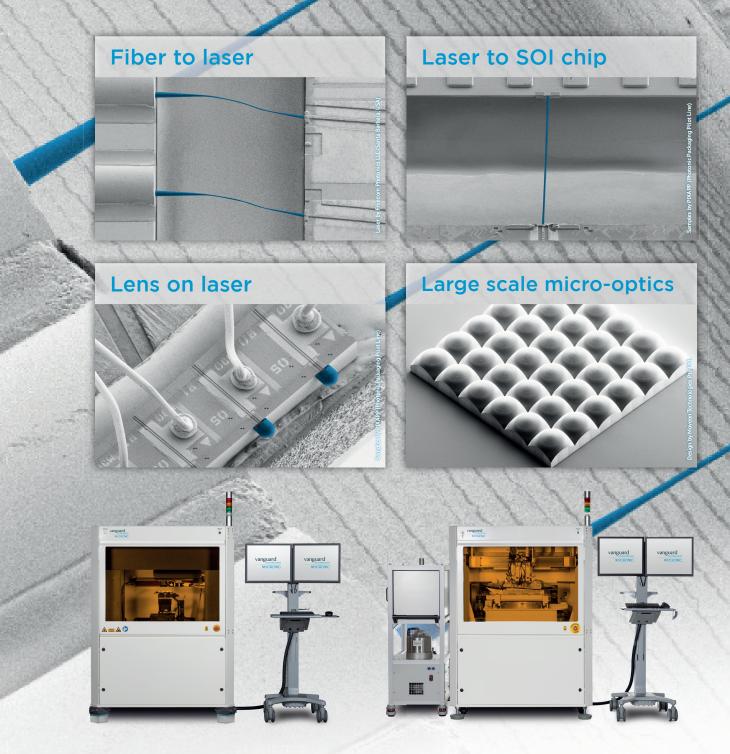

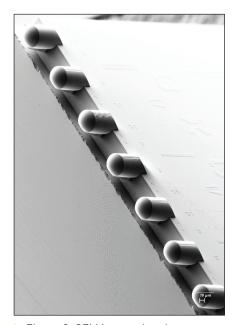

➤ Figure 1. SEM image of a single-mode fibre (SMF) array aligned to an AMF chip and integrated using Photonic Wire Bonds. This assembly type has demonstrated 100 percent yield across 180 connections, with insertion losses consistently below 2 dB and an average of 1.4 dB—highlighting the reliability of passive photonic integration packaging.

Automation's novel processes can deliver the innovation and scalability needed to unlock the full potential of hybrid photonic integration [3].

#### Automated nano fabrication

Vanguard's solution uses highly precise direct-write 3D laser lithography to print 3D freeform optics in-situ at the chip level, eliminating the need for active alignment and enabling passive pick-and-place assembly. The printed optics allow for mode-field matching between dissimilar materials and components, as well as compensating for manufacturing variations by relaxing alignment tolerances. Vanguard Automation offers a robust portfolio of photonic interconnect structures - most notably Photonic Wire Bonds and facetattached micro-lenses – engineered to support versatile and scalable photonic integration across a wide range of packaging scenarios. This empowers photonic product designers and manufacturing teams to fully leverage efficient assembly build-up in volume manufacturing.

Photonic Wire Bonds (PWBs), shown in Figure 1, are single-mode freeform optical waveguides printed between two photonic components, that compensate for misalignment of up to ±20 µm. This ensures optimal coupling between dissimilar photonic components and enables passive alignment during assembly. PWBs are increasingly recognised as the preferred solution for hybrid integration of active devices such as III-V lasers, quantum-dot lasers, and amplifiers onto passive PIC material platforms [4-6].

#### INDUSTRY | MANUFACTURING

> Figure 2. SEM image showing facet-attached micro-lenses precisely 3D-printed onto the edge of an AMF chip, demonstrating in-situ fabrication for compact, alignment-tolerant photonic integration.

In recent demonstrations, PWBs achieved insertion losses as low as 1 dB per interface and supported stable, mode-hop-free laser operation exceeding 58 hours.

Even more impressively, the Vanguard system can complete fibre-to-chip-to-laser integration in a single fabrication step. To achieve this, the system uses machine vision to detect the individual waveguide positions, and automatically calculates the optimal low-loss PWB

interconnect trajectory, including modefield matching.

Meanwhile, facet-attached microlenses (FaMLs) can perform spot size conversion and beam expansion, relaxing alignment tolerances up to ±15 µm, and beam shaping reduces sensitivity to lateral and angular misalignment. This eliminates the need for bulk optics, reducing system footprint and cost while overcoming optical and mechanical challenges in hybrid photonic packaging.

FaMLs are a key component for integration in electro-optical engines that underpin transceivers, copackaged optics, light engines, and sensing devices. A stand-out example is POET Technologies, which collaborates with Vanguard Automation to integrate 3D printed micro-lenses onto its optical interposers. This collaboration enhances coupling efficiency while preserving POET's signature wafer-level passive assembly process [7].

With its complementary technology portfolio, Vanguard Automation provides a scalable path for volume-production customers to incorporate 3D-printed optics into their production chain. Starting with hybrid approaches using 3D-printed optical elements and active alignment, the product design can evolve to leverage the full potential for photonic integration. Ultimately, customers can benefit from incorporating PWBs with standard pick-and-placing of components with very relaxed tolerances, while

simultaneously ensuring high coupling efficiency, high yields, and high package density.

And there are advantages for foundries too; since PWBs and FaMLs can work with simple inverse taper edge couplers realised by stepper lithography, the chip real estate used for sophisticated couplers can be reduced substantially, paving the way towards a novel and more universal standard for optical coupling [8]. Furthermore, the benefits of PWBs and FaMLs can be combined to form a unique offering to correct highly elliptical laser outputs [9].

This convergence of compact design, relaxed alignment tolerances, and platform versatility positions PWBs and FaMLs as foundational building blocks for scalable, cost-efficient photonic manufacturing, enabling streamlined integration and expanded design flexibility across platforms.

#### Flexible, reliable and robust

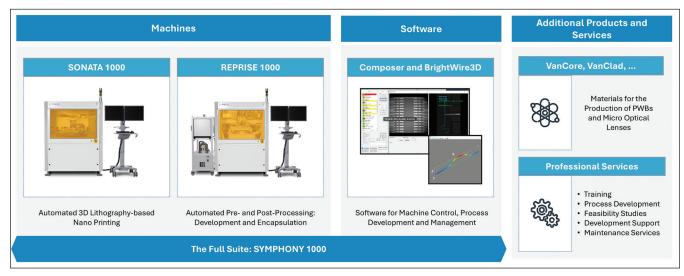

Vanguard offers a fully automated solution, the vanguard SYMPHONY, which comprises two systems: one for the fabrication of PWBs and FaMLs (vanguard SONATA 1000), and one for postprocessing of optical assemblies to complete the fully automated packaging process (vanguard REPRISE 1000). Alongside the machines, vanguard SYMPHONY incorporates Vanguard's Brightwire3D software for automated, highly precise interface detection (accurate to < 50 nm) as well as on-the-fly calculation of optimal PWB trajectories.

➤ Figure 3. Vanguard SYMPHONY: Vanguard Automation's fully automated photonic integration and packaging platform, featuring BrightWire3D software for precision interface detection and VanCore photoresists engineered for industrial reliability.

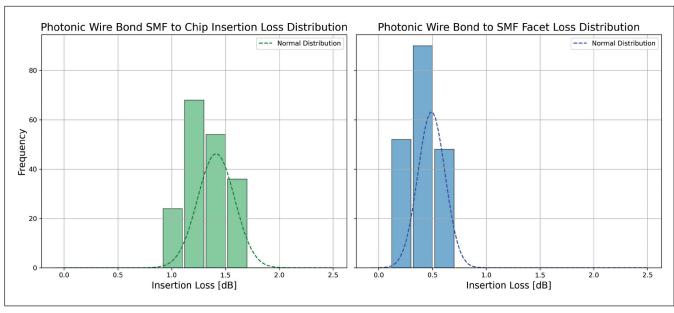

> Figure 4. Statistical overview of insertion loss performance for fibre-to-silicon PIC and SMF facet coupling using Photonic Wire Bonds, demonstrating consistent low-loss results across multiple assemblies.

Additionally, the solution includes dedicated photoresists tailored to meet strict industrial reliability requirements (vanguard VanCore series), and standard fabrication processes. Finally, customers can also take advantage of engineering services and support to advance quickly from prototyping to production, as seen in Figure 3.

Whereas traditional volume manufacturing relies on product-specific physical tooling, 3D printing operates on a software-defined model, enabling the complete removal of long lead times and expenses associated with tooling preparation. This significantly accelerates the development and production cycle of complex freeform optical components and waveguides for hybrid photonic integration.

Vanguard's solution thus enables seamless transition from prototyping to volume production, including batch and wafer-level processing with industrial-grade reliability. Designed to be flexible, the Vanguard Automation SYMPHONY systems can be easily adapted to different product requirements and production lines.

While delivering flexibility and automation for scalability, Vanguard's photonic packaging technology does not compromise on yield; indeed, it consistently delivers high yield across a range of integration scenarios and has undergone rigorous testing to validate its performance and reliability. Figure 4 highlights the high yield performance of two common assembly types used in photonic integration: SMF fibre-to-silicon PIC and SMF fibre-to-fibre.

In the case of SMF fibre-to-silicon PIC assemblies, Vanguard's PWB achieves 100 percent yield with insertion losses below 2 dB across 180 connections, with a mean of 1.4 dB. For SMF fibre-to-fibre assemblies, the technology maintains 100 percent yield with insertion losses under 0.75 dB per facet across 190 PWB to SMF facet interfaces, with a mean of 0.49 dB [3]. Even with lateral misalignments exceeding 20 µm and vertical offsets exceeding 40 μm, insertion loss remains stable demonstrating that PWBs work reliably with passive alignment at production scale.

In high-precision photonic manufacturing, consistent insertion loss performance for back-end photonic integration is critical to ensuring high yield, process control, and quality assurance. Reliable manufacturing of photonic interconnects ensures that performance metrics remain within acceptable limits across production batches. Vanguard's consistent insertion loss results highlight the robustness and repeatability of its 3D printing technologies, making them highly suitable for industrial-scale deployment. Industry users have reported a 99 percent reproducible yield in laser-to-silicon nitride assemblies, with coupling losses below 2.3 dB and a mean of just 1.7 dB, further validating the reliability of PWBs for hybrid integration.

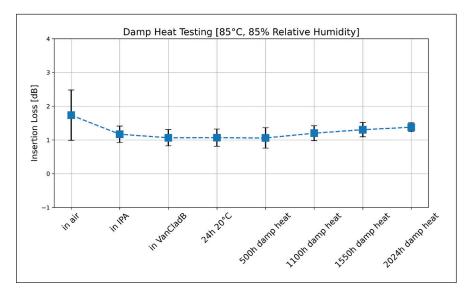

PWBs and FaMLs have also demonstrated exceptional reliability under rigorous environmental testing [3]. Assemblies with 3D-printed optics have been subjected to thermal cycling, mechanical stress, and Telcordia damp heat conditions (85 degrees C, 85 percent relative humidity), with insertion loss variation remaining within 0.5 dB

By combining fully automated system tools, Telcordia-qualified materials, and 3D-printed freeform optics, Vanguard Automation's photonic integration solution portfolio delivers industry-grade performance from prototyping to volume manufacturing

#### INDUSTRY | MANUFACTURING

over 2000 hours, as demonstrated in Figure 5. In further testing, no degradation was observed under mechanical shock or vibration, and FaMLs maintained stable performance during high-power operation at 200 mW for over 5000 hours, showing no signs of delamination or structural failure. These results confirm the robustness of Vanguard's photonic packaging technologies for demanding industrial applications.

Crucially, 3D-printed structures retain optical integrity after 260 degrees C solder reflow, ensuring compatibility with thermally demanding back-end processes. This makes the technology an ideal fit for integration into standard semiconductor workflows.

When FaMLs are printed in situ to InP modulator chips and sealed in industry-standard hermetic "gold-box" packages, they maintain stable performance – even after 500 thermal cycles, mechanical shock, vibration, and die bonding at 320 degrees C [3].

In non-hermetic applications, such as coupling silicon nitride PICs to polarisation-maintaining fibre arrays, FaMLs have demonstrated robust thermal stability, with less than 0.1 dB variation after reflow soldering [10]. This level of thermal and mechanical resilience makes FaMLs a viable solution for co-packaged optics (CPO), which demands compact, reflowtolerant, and detachable fibre-to-chip coupling.

#### A bright future

As we look ahead to ECOC 2025 and beyond, the message is clear: Vanguard Automation's Photonic Wire Bonds and facet-attached micro-lenses offer a scalable and reliable solution to one of the photonic industry's most pressing challenges – integrating active components to PICs.

By combining fully automated system tools, Telcordia-qualified materials, and 3D-printed freeform optics, Vanguard Automation's photonic integration solution portfolio delivers industrygrade performance from prototyping to volume manufacturing.

The platform-agnostic solution enables passive assembly alignment, batch and wafer-level processing, and software-defined fabrication, eliminating the

> Figure 5. Telcordia damp heat test results for SMF fibre-to-fibre connections using Photonic Wire Bonds, monitored over 2000 hours at 85 degrees C and 85 percent relative humidity. Each data point represents the average performance of 10 PWBs, demonstrating long-term environmental stability.

bottlenecks of traditional tooling and accelerating development cycles.

This approach is already empowering customers in both research and industry to develop next-generation photonic integration and packaging that combine the strengths of diverse photonic platforms into compact, high-density multi-chip modules. 3D-printed

freeform optics is more than just a packaging solution; it's a platform for innovation.

With proven yield, low-loss performance, and design flexibility, Vanguard Automation is not just solving today's integration challenges, but shaping the future of photonic manufacturing.

#### **FURTHER READING / REFERENCE**

- [1] https://opticalconnectionsnews.com/2025/02/ai-drives-demand-foroptical-transceivers-lpo-cpo-report/

- ➤ [2] https://www.aeponyx.com/lightwave-webinar

- [3] M. Lu et al., "Photonic Integration Using Industry Ready Photonic Wire Bonds & Facet Attached Micro-Lenses," in IEEE Transactions on Components, Packaging and Manufacturing Technology

- ➤ [4] Franken et. al. "High-power and narrow-linewidth laser on thin-film lithium niobate enabled by photonic wire bonding", APL Photonics 1 February 2025; 10 (2): 026107

- ➤ [5] M. De Gregorio, et al. "Fiber-coupled quantum dot single-photon source via photonic wire bonding." Quantum Computing, Communication, and Simulation IV. Vol. 12911. SPIE, (2024).

- [6] V. Deenadayalan et al., "Packaged Tunable Single Mode III-V Laser Hybrid Integrated on a Silicon Photonic Integrated Chip using Photonic Wire Bonding," 2024 IEEE ECTC, Denver, CO, USA, 2024, pp. 1387-1391

- ➤ [7] https://poet-technologies.com/news/2023-mar-6.html

- [8] Y. Mizuno et al., "Low Insertion Loss 128-Gbaud HB-CDM with 3D-Printed Spot Size Converter Integrated InP-based Modulator," 2023 Optical Fiber Communications Conference and Exhibition (OFC), San Diego, CA, USA, 2023, pp. 1-3

- > [9] OPHELLIA: On-chip PHotonics Erbium-doped Laser for Lldar Applications

- ➤ [10] Y. Mizuno, et al. "3D-printed Beam Expanding Lens for Chip to Fiber Vertical Coupling." 2024 IEEE 74th Electronic Components and Technology Conference (ECTC). IEEE, 2024.

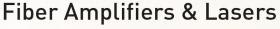

### PROFESSIONAL SIMULATION TOOLS & EXPERT DESIGN SERVICES

Integrated Devices, Waveguides & Fibers

VPIdeviceDesigner™

VPIcomponentMaker™ Photonic Circuits

VPIcomponentMaker™ Fiber Optics

Transmission Systems

VPItransmissionMaker™ Optical Systems

Lab-proven DSP Algorithms

VPItoolkit™ DSP Library

Quantum Key Distribution

VPItoolkit™ QKD

We empower you to define the cutting edge.

Request an evaluation

FROM pluggable transceivers to advanced co-packaged optics, PICs are already powering next-generation datacentre interconnects. By offering compact, low-power, and high-bandwidth solutions for wavelength-division multiplexing (WDM) and high-speed links between multiple processing units, they enhance data throughput and scalability [1], addressing an unprecedented demand for computing power in datacentres. As such, they are an indispensable technology for AI and the digital transformation.

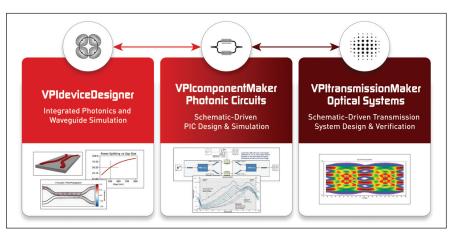

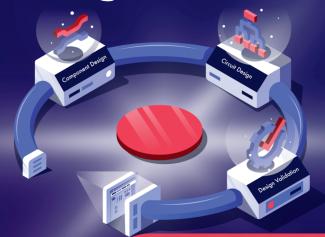

However, photonic chips are complex devices, and performance bottlenecks often emerge late in the design cycle [2]. System-level modelling of PICs is essential to optimise optical links and meet strict network specifications. This increasingly involves hybrid PIC platforms, combining diverse materials and integration strategies, which require optimisation of basic sub-components, such as modulators, splitters, and combiners. Although Process Design Kits (PDKs) with building block libraries simplify design, there is growing demand for customisation without compromising IP security [3].

This is where VPIphotonics' advanced Photonic Design Automation (PDA) framework excels, unifying PIC and optical system simulation in one environment.

This solution enables accurate modelling of photonic devices and components considering full-system behaviour – from submicron integrated devices to kilometre-scale fibre links – while supporting customisable, multi-platform PDK development. The framework supports collaboration

between designers working on different aspects of the system. Designing PIC-based systems often involves separate teams; photonic engineers focus on designing PICs and optimising components such as modulators and filters, while system engineers are responsible for the overall system architecture and performance, whether for transmitters, receivers, fibre links, or digital signal processing (DSP). While this division of expertise is necessary for such a complex, multi-stage process, it can also lead to fragmented

> Figure 1. Block description of the cross-layer photonic design framework.

workflows, relying on manual file transfers, custom scripts, and repeated tuning cycles [1].

To address this, a unified simulation framework brings together VPIphotonics Design Suite [4] and VPIdeviceDesigner [5] as presented in Figure 1. It combines device design and optimisation with flexible import and export of the component GDS, custom PDK creation, and circuit design with full optical system simulation, and export of the final circuit layout. This shared design environment facilitates seamless collaboration, allowing teams to cosimulate and optimise PICs in system-level contexts, while tailoring models to specific foundry processes.

#### **Device modelling**

The first layer of the PDA framework focuses on the level of individual devices. Here, optimising building blocks for foundry-specific, PICdedicated applications requires both adequate simulation models and the ability to import and export the equivalent layout of the building blocks. While working with foundry-specific elements, the design process typically follows layout-driven workflows. This involves importing an existing initial design as a GDS file, adding or removing fabrication-aware corrections, generating the 3D device, and optimising its simulation and geometry. On the other hand, to develop new, custom individual PIC building blocks, designers require a flexible process for creating 2D waveguide cross-sections and 3D devices.

In both scenarios, the simulation requires a combination of powerful mode solvers, which calculate light's behaviour in the device, and an efficient 3D simulation technique to optimise its geometry. A few of the most common techniques are finite difference time domain (FDTD), 3D beam propagation (BPM), and eigenmode expansion (EME) methods.

While FDTD provides the most accurate simulation results, this method has high computational and memory costs, making it unusable for larger components and more complex optimisation processes. In many cases, BPM and EME provide great alternatives with satisfying accuracy and reasonable simulation time for optimising integrated photonic devices.

> Figure 2. Block description of the layout-aware schematic-driven design methodology [7].

That, together with easy-to-use postprocessing capabilities, makes VPldeviceDesigner a practical tool for analysing integrated dielectric and plasmonic waveguides, optical fibres, and passive integrated components such as multi-mode interferometers, directional couplers, edge couplers, and photonic lanterns. VPldeviceDesigner is natively integrated in Python, offering complete flexibility in the simulation workflow and seamless integration with other Python libraries.

Additionally, users can export the performance data in a suitable format for VPIcomponentMaker Photonic Circuits [4] - the second layer of our design framework - ready to be included in the circuit-level PIC simulation. Furthermore, it is easy to systematically vary the dimensions of GDS-imported layouts, enabling geometry optimisations and parameter sweeps. Designers can then export the resulting optimised layout back to the layout tool, or write it directly into the PDK file structure. Since VPIdeviceDesigner is fully integrated into Python, all these steps can be fully automated, version-controlled, and organised as reproducible simulation recipes.

#### **PICs and PDKs**

Moving from individual devices to circuit design represents a new level of complexity, with modern PICs containing dozens of components and hundreds of devices on just a single chip. A large-scale passive PIC – which does not include any light sources or detectors – can be efficiently simulated at different frequencies as a single

assembled S-matrix, which is calculated from the schematic on the fly and fully describes transmitted and reflected signals [6]. Since these models represent steady-state behaviour without transient effects, the duration of the signal data block, or time window, can remain short; the lower limit is defined mainly by the desired frequency resolution, which is improved by a longer time window.

However, validating system performance metrics, such as symbol error rate (SER), may require the simulation of millions of symbols and thus a long time window. This means the S-matrix must be calculated at many more frequency points, making its assembly significantly more complex.

To address this, a faster, memory-efficient implementation calculates the S-matrix for a smaller number of frequency points and then interpolates the values between them. This maintains a high accuracy while significantly reducing the computation resources required.

While simulating passive linear circuits is relatively straightforward, accurately modelling active and electro-optic elements such as lasers, amplifiers, and modulators requires sophisticated circuit-level models operating in the time domain that capture nonlinear effects, bidirectional propagation, and dynamic carrier density behaviour [6].

VPIcomponentMaker Photonic Circuits addresses these requirements with its transmission-line laser model (TLM).

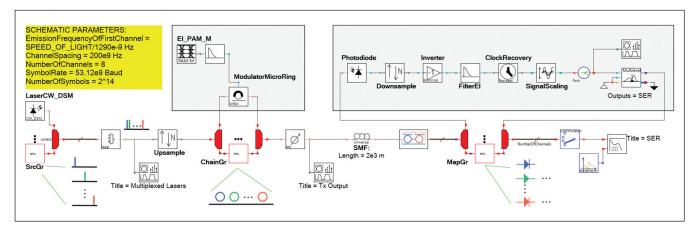

> Figure 3. 800G DWDM PAM-4 system schematic.

To further manage the complexity of large-scale circuits, circuit-level tools support hierarchical designs for block reuse, graphical structuring of serial/parallel layouts, and Python/MATLAB co-simulation for creating custom components or technologies.

Besides the many different components that make up PICs, a further complexity in simulation arises from the many photonic platforms available, including silicon, indium phosphide, lithium niobate and more. Designing highperformance PICs for optical systems often involves combining these different materials, each of which has unique advantages and integration approaches, increasing the need for customisation. While foundry-provided PDKs accelerate development by using libraries of pre-characterised building blocks, designers often face two key limitations: the difficulty of creating new building blocks and the challenge of customising existing ones without compromising foundry and company IP [3].

To address these challenges, VPI

Design Suite provides a framework

for the flexible development of new

PDKs and seamless integration of novel

components into existing libraries. This

gives designers the freedom to enrich commercial PDKs or build entirely new libraries for emerging PIC technologies, enabling innovative applications and empowering fabless companies to develop secure, IP-protected internal PDKs.

The custom PDK library is automatically created from a template and includes all necessary features of a standard PDK, including design automation macros, schematic-to-layout conversion tools [7], and fabrication tolerance analysis capabilities [8]. Custom user interface toolbars allow for streamlined usability, while building block templates with links to their corresponding layout descriptions enable the layout-aware, schematic-driven design methodology (see Figure 2). Users can further customise this process to adapt the template models to their requirements.

#### System design

Today's datacentres communicate information across multiple scales – from intra-rack and intra-campus links to inter-campus connections spanning hundreds of kilometres [9]. Each tier demands unique optical interconnect solutions, such as coherent optical interconnects with advanced modulation formats (QPSK,

16QAM) and intensity-modulated direct-detection systems utilising PAM-M. Supporting such a wide range of applications requires powerful system-level simulation tools that must include models for transmitters, receivers, fibres, modulation and coding schemes, DSP elements, and dispersion mitigation techniques. Additionally, they should enable virtual testing environments that comply with industry standards and evaluate key performance metrics such as SER, bit error ratio, optical signal-to-noise ratio, Q-factor, and others.

VPltransmissionMaker Optical Systems [4] – the third pillar of our design framework – delivers a robust solution, offering an integrated simulation environment for diverse use cases, ranging from short-reach optical interconnects to metro/core networks, free-space optics, microwave photonics, and more. Supported by comprehensive model and application example libraries as well as advanced analysis capabilities, engineers can move confidently from concept to system validation in today's dynamic datacentre landscape.

Together, VPIdeviceDesigner, VPIcomponentMaker Photonic Circuits, and VPItransmissionMaker Optical Systems offer a complete design workflow. Historically, PIC research has focused primarily on individual device or circuit optimisation. Now, with the growing adoption of PICs in commercial applications, engineers are increasingly adopting a system-level approach, starting from high-level performance targets and deriving component requirements based on the overall application. Factors like required data

Unlike simplified datasheet models, advanced architectures demand physical-level simulations. The MRM response depends on resonant wavelength, free spectral range, extinction ratio, and tuning conditions – all affected by device geometry and material properties

rate, transmission distance, and channel spacing define parameters such as desired modulator bandwidth, Q-factor, and noise tolerance. However, due to the different nature and scale of the device, circuit, and system levels, it is challenging to combine simulations for them.

Optimising device geometry is a complex task that cannot always be done by modelling the behaviours of electromagnetic fields rigorously, due to the high computational and memory demands of these methods. But neither can the problem be solved in isolation from the target circuit performance. To overcome these challenges, PIC design teams need a flexible equivalent compact model for accurate circuit-level simulation. VPIdeviceDesigner provides exactly this, by offering an automated transfer of the device simulation data into VPI Design Suite circuit-level analytical models and parametrised S-matrix representations.

The shared simulation environment also addresses the challenges that arise between the circuit and system levels.

Optical fibre models, for example, implement computationally efficient methods in the frequency domain, that only support periodic boundary conditions, where the signals display repeating patterns and the end of one segment smoothly joins up to the start of the next. However, modelling PICs often requires more complex timedomain simulations with aperiodic boundary conditions, meaning that the signal cannot be broken into a pattern of repeating segments.

To model long signal streams, as needed for system performance validation, engineers can use multirun periodic simulations, breaking the stream into different chunks.

However, this approach can create artificial signal discontinuities at the break between one chunk and the next, due to the above-mentioned inherent aperiodicity of some of the circuit-level simulations. These discontinuities do not occur in the real data stream and can falsely deteriorate the assessed performance metrics, such as the SER.

To mitigate such numerical effects, the VPI Design Suite environment provides techniques for smoothing discontinuities, such as windowing, stitching, and the overlap-save method. It also offers signal conversion functionalities like resampling. These modules are important tools that are essential to the simulation setup, but they do not have physical counterparts in an actual PIC or system.

Finally, supporting faster and more memory-efficient algorithms for S-matrix assembly and dedicated time-and-frequency domain simulations [7] with a flexible frequency grid and advanced interpolation enables the simulation of large-scale PICs in complete system scenarios.

#### **Application examples**

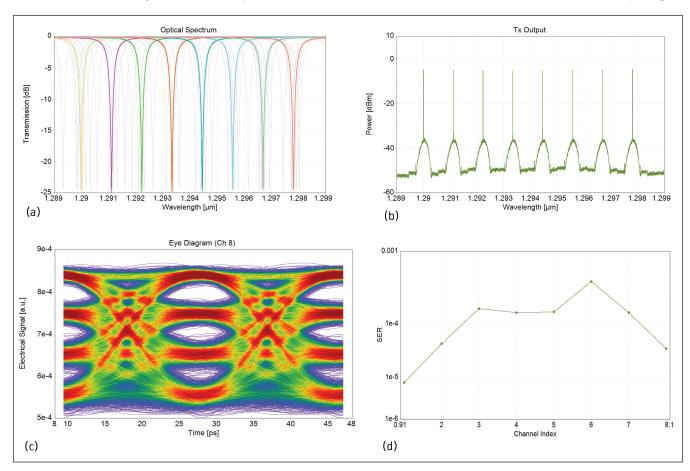

A powerful example of advanced system-level simulation is an 800G DWDM PAM-4 optical link leveraging silicon microring modulators (MRMs) and third-order microring resonator filters (MRRs) [1]. The system uses up to 8 laser channels at 200 GHz spacing,

> Figure 4. 8-channel DWDM PAM-4 transmission system simulation results: static MRM transfer functions including intermediate plots for the automated phase tuning (a), modulated optical spectrum at the transmitter output (b), eye diagram at the receiver for channel #8 (c), SER performance for all 8 channels (d).

#### TECHNOLOGY | SIMULATION

> Figure 5. 3D impression of a PPLN waveguide (a), investigated lithium niobate waveguide cross-section (b), and waveguide mode dispersion (c).

> Figure 6. Mode profile of the fundamental TE mode at 1550 nm (a), mode profile of the fundamental TE mode at 775 nm (b), and spatial distribution of the nonlinearity (c).

modulated by cascaded MRMs, transmitted over 2 km of single-mode fibre (SMF), and demultiplexed via MRRs before signal detection and SER estimation (Figure 3).

The design employs higher-orderfunction modules for scalable schematic generation, enabling quick reconfiguration (such as increasing channel count) without redrawing the circuit. Modules like SrcGr, ChainGr, and MapGr automate channel-wise source generation, modulation, and detection setup.

Unlike simplified datasheet models, advanced architectures demand physical-level simulations. The MRM response depends on resonant wavelength, free spectral range, extinction ratio, and tuning conditions – all affected by device geometry and material properties. To streamline

tuning, dedicated test benches automate characterisation, optimising parameters such as microring radius, attenuation, coupling coefficients, and phase alignment.

The simulation, conducted in VPIphotonics Design Suite, integrates VPIcomponentMaker Photonic Circuits and VPItransmissionMaker Optical Systems, completing a full-system simulation run in about 32 seconds on

- Based around a hot topic for your company, this 60-minute recorded, moderated zoom roundtable would be a platform for debate and discussion

- Moderated by an editor, Laura Hiscott, this can include 3 speakers

- Questions prepared and shared in advance

Cost: €5995

Contact: Jackie Cannon jackie.cannon@angelbc.com

NGEL EVENTS

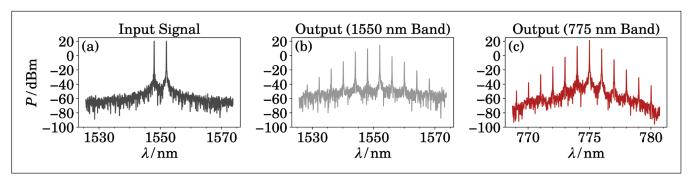

> Figure 7. Spectra of the optical signal in the simulation. In addition to the sum frequency at 775 nm and the two second harmonics, a few more lines appear due to the mutual interaction of the signals in the PPLN.

a standard desktop. Results include automatically tuned transfer spectra, eye diagrams, and SER across channels, offering insights into system performance under realistic conditions (Figure 4).

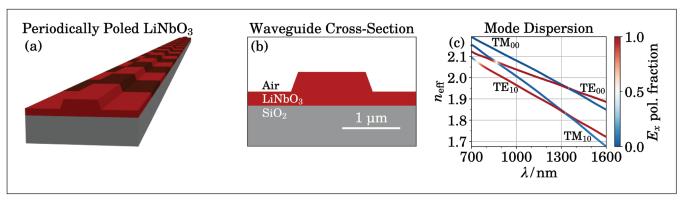

Another promising technology for datacentre interconnects is thin-film lithium niobate (TFLN). This material enables ultra-high-speed modulation with travelling-wave Mach-Zehnder modulators (MZMs), paving the way for data transmission beyond 1 Tbps.

We previously validated this through the simulation of a 2 Tbps single-polarisation DWDM 32 QAM coherent optical system for mid- and long-reach datacentre interconnects using TFLN MZMs in the IQ modulator [1]. TFLN is also an attractive platform for nonlinear conversion processes such as second-harmonic generation due to its strong second-order nonlinear coefficient.

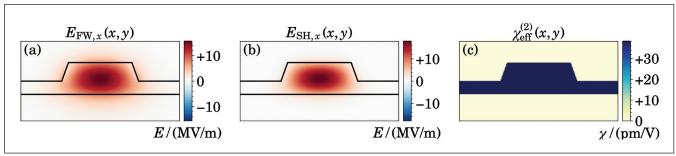

Developing the corresponding TFLN-based PDK library requires the combination of accurate devicelevel and circuit-level simulations. As an example, we have modelled a periodically poled lithium niobate (PPLN) waveguide (Figures 5a-b). While the local conversion efficiency is determined by waveguide mode overlap integrals, which must be calculated on the level of Maxwell's equation, the propagation along the PPLN waveguide can span more than several millimetres and can involve broadband signals, requiring coupled-mode or split-step methods in circuit-level models.

VPIdeviceDesigner calculates the conversion efficiency in a single line of Python code (Figure 6), utilising the fact that calculated modes are feature-rich Python objects in VPIdeviceDesigner. The wavelength-dependent effective

mode indices (Figure 5c) and conversion efficiency can be easily exported to VPlcomponentMaker Photonic Circuits.

In our simulation, the PPLN waveguide is excited with two laser lines spaced at 0.5 THz, which induce second-harmonic generation, sum frequency generation, and difference frequency generation in the PPLN. These effects are calculated using a multi-wavelength coupled-mode approach, as shown in Figure 7. This device-level data is then loaded into the circuit-level PPLN model for further use.

These are just two examples of how VPIphotonics' versatile platform can support designers in simulating and optimising various optical systems.

As the optical interconnect industry increasingly turns to heterogeneous fabrication platforms and hybrid integration technologies to meet the growing demand for high-speed components, system design is becoming increasingly complex.

There is now a critical need for integrated system and circuit codesign, in particular for scalable WDM architectures and advanced modulation schemes. By providing a complete solution for efficient device and circuit simulation, seamlessly moving from the smallest individual devices to the entire functional system, VPIphotonics is empowering designers to realise the future of optical communications.

#### FURTHER READING / REFERENCE

- [1] Sokolov, E., et al., "PIC design and custom PDKs for data center interconnects", (Invited Paper), SPIE Optics+Photonics 2025, Proc. SPIE 13601-24

- > [2] Sokolov, E., et al., "A Comprehensive Guide to Photonic Design Automation: From Devices to Systems", Photonics Spectra

- > [3] Polatynski, A., et al., "The best of both worlds: Design freedom and IP protection," in PIC Magazine, Issue 1, pages 12-14 (2024)

- [4] VPIphotonics Design Suite, https://www.vpiphotonics.com/Tools/ DesignSuite/, accessed July 15, 2025

- ➤ [5] VPIdeviceDesigner, https://vpiphotonics.com/Tools/DeviceDesigner/, accessed July 15, 2025

- ➤ [6] Mingaleev, S., et al., "Rapid virtual prototyping of complex photonic integrated circuits using layout-aware schematic-driven design methodology," Proc. SPIE 10107, Smart Photonic and Optoelectronic Integrated Circuits XIX, 1010708 (20 February 2017)

- ➤ [7] Mingaleev, S., et al., "Towards an automated design framework for large-scale photonic integrated circuits", Proc. SPIE 9516, Integrated Optics: Physics and Simulations II, 951602 (2015)

- > [8] Richter, A., et al., "Schematic-driven PIC design process considering manufacturing tolerances", Proc. SPIE 11690, Smart Photonic and Optoelectronic Integrated Circuits XXIII, 1169004 (2021)

- ➤ [9] Richter, A., et al., "Optical interconnects for datacenter links: design and modeling challenges," Proc. SPIE 11286, Optical Interconnects XX, 1128617 (28 February 2020)

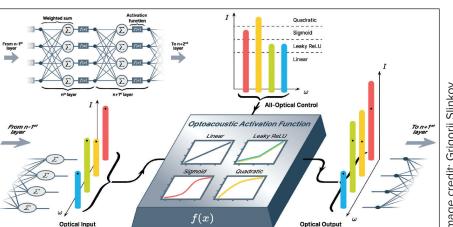

# Harnessing sound waves for photonic neuromorphic computing

Optical neural networks could bring about sustainable, energy-efficient AI, but fulfilling this vision requires further advances in scalability and reconfigurability. Using sound waves in optical fibres and PICs offers one path to flexible, configurable, photonic deep learning units.

BY BY BIRGIT STILLER, PROFESSOR AT LEIBNIZ UNIVERSITY AND GROUP LEADER AT THE MAX PLANCK INSTITUTE FOR THE SCIENCE OF LIGHT

LAST YEAR, Microsoft made headlines when it signed a deal to buy energy from Three Mile Island, a nuclear power plant infamous for the accident that took place there in 1979. And Microsoft is not the only tech company seeking new ways to fulfil its soaring energy needs. Google and Meta have also been making deals to purchase power from nuclear facilities, while Google and Microsoft have even signed long-term agreements with nuclear fusion startups to secure future fusion-generated electricity.

These actions underscore just how much energy these companies are expecting to need for their power-hungry datacentres and AI applications. Large language models such as ChatGPT have already proven extremely useful across numerous industries and in our daily lives. A technology that might have seemed far-fetched just a few years ago has been adopted remarkably quickly, and the demand for AI services will only continue to grow. But providing access to them will require new technologies that speed up data processing and reduce energy consumption.

One potential solution arises from using optical devices, such as PICs or hybrid photonic-electronic chips, as the basis for new computing architectures. By using light instead of electrical

#### TECHNOLOGY | OPTOACOUSTIC COMPUTING

signals to represent data, optical neural networks could handle large volumes of information at high speeds and with great energy efficiency, forming the backbone of future AI systems.

Electrical signals travel comparatively quickly over short distances, meaning that the speed of light itself does not necessarily offer a huge advantage for computing. A more significant gain comes from the fact that light has many more parameters that can encode information; frequency, spatial modes, optical phase, and polarisation can all carry data simultaneously — an advantage that is already being harnessed in optical communications.

To date many of the experimental approaches to implementing optical neural networks have relied on fixed components and devices configured to manipulate light in specific ways.

These components may include resonator structures on a chip, huge interferometric networks made of photonic waveguides, arrangements of diffractive phase plates, or even metamaterials. It is possible to tune and train these elements, but for many of these setups, once a structure or device is fabricated there is limited room for reconfiguration. This lack of flexibility means that some devices can usually perform the task they were designed for and cannot be adapted for broader functions – an essential feature of the most useful Al models.

Now, let's take a break from photonics and think about sound: about acoustic waves. Acoustic waves have a completely different nature from optical signals, which are electromagnetic waves. Optical waves travel at high speed through materials and also through vacuums like outer space. Acoustic waves, on the other hand. travel a million times more slowly than light in air, and they do not travel through a vacuum at all; they need a material to propagate through. Optical and sound waves also have very different frequency ranges, with the former generally oscillating millions of times more per second than the latter.

Given all these dissimilarities, it may seem unlikely that pristine optical information could be captured in such a bulky, macroscopic thing as an acoustic wave. Yet the two forms of energy can in fact interact very efficiently via the refractive index of a material.

For example, in an acousto-optic modulator, sound waves periodically distort the material and change its refractive index, scattering incoming optical waves. Additionally, in certain materials, light waves can cause charged particles in the structure to move (a physical effect called electrostriction), and the resulting deformation can produce acoustic waves. These interactions offer an opportunity to modulate and control optical signals with sound.

#### Sound as memory

In our research on neuromorphic computing at the Leibniz University Hannover and Max Planck Institute for the Science of Light, our vision is to create neuromorphic hardware based on optical fibres and photonic chips that can be built and reconfigured by acoustic waves. To this end, we use stimulated Brillouin scattering – a phenomenon by which light and sound waves affect one another via the refractive index of a material.

By bringing the waves into interaction, we have found a way to build reconfigurable building blocks based on sound waves for photonic machine learning. With optical control pulses, we can generate coherent acoustic waves, which can then be used for various functions.

For example, they can be used to store information, serving as a temporary memory, to amplify certain signals, or to enable other functionalities such as recurrency and nonlinearity. These building blocks can be implemented in hair-thin optical fibres, already used globally for fast internet connections, or in photonic chips for potential hybrid integration with electronics.

The optoacoustic memory uses the fact that acoustic waves are slow and can therefore act like a parking slot for optical information. Additionally, these waves fulfil several other key requirements for an optical high-performance random-access memory: they are coherent, they are compatible with photonic chips, they can be tuned to different frequencies, and they have a high bandwidth.

The mechanism for transferring information from light waves to sound waves involves an optical data stream being sent into the optical fibre or photonic chip, while a second optical control pulse is sent from the other side. When these two counterpropagating waves collide, they create an acoustic wave that encodes the information from the data stream. This information is preserved in the acoustic domain until a second optical control pulse enters the medium and "reads" the sound wave, creating a corresponding optical wave again.

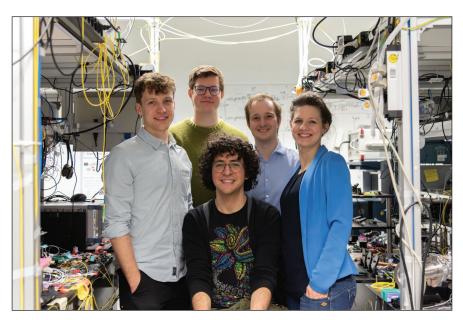

> Figure 1. Part of Birgit Stiller's research group, from left to right: Steven Becker, Niklas Braband, Jesus Humberto Marines Cabello, Andreas Geilen, Birgit Stiller. Photo: Susanne Viezens.

#### TECHNOLOGY | OPTOACOUSTIC COMPUTING

> Figure 2. In photonic systems, sound waves can serve several different purposes, such as storing data in a temporary memory, amplifying certain signals, or introducing functions like recurrency and nonlinearity.

We have demonstrated that this memory is coherent in amplitude and phase, meaning that the data does not get lost or scrambled, and provides a high bandwidth up to the GHz range. The memory can also be accessed at high speed and be operated at different frequency channels at the same time with negligible crosstalk.

Because the acoustic waves only travel in one specific direction, this type of photonic memory is nonreciprocal, meaning that it is unaffected by counterpropagating signals and only interacts with the optical control pulse intended to read it. This property also allows for the nonreciprocal manipulation and potentially storage of specific types of light beams called orbital angular momentum modes, which can carry more information than standard light signals.

#### Recurrency and nonlinearity

Being so slow, acoustic waves remain in the medium much longer than optical waves, which makes them perfect candidates for recurrent neural networks - a type of architecture that is designed to process sequential data, in which the order of the data is important. For example, in human language, the order of words in a sentence affects its meaning. The two sentences "The cat hunts the mouse" and "The mouse hunts the cat" consist of the same words but have different meanings. indicated by the word orders.

A traditional fully connected neural network on a computer faces difficulties capturing this context because it requires access to memory. But recurrent operators feed the output of one calculation back as an additional input for the next, linking a series of computational steps and thus providing context for each single calculation performed. By equipping neural networks with recurrent operations, we can give systems internal memory and enable them to capture contextual information, overcoming the challenges associated with processing sequential data.

We have now used sound waves to implement such a recurrent operator.

Our Optoacoustic REcurrent Operator (OREO) harnesses the intrinsic properties of optical waveguides, meaning we can enable recurrent operations in the existing physical structures, without needing to add an artificial reservoir or any additional components. Unique to OREO is the advantage of being entirely controlled by light, making the optoacoustic computer programmable on a pulseby-pulse basis, and eliminating the need for complicated structures or transducers to convert between signal types.

Another key ingredient of neural networks is an activation function - a nonlinear mathematical operation that takes the inputs to a particular neuron and determines its output. Examples of activation functions include ReLU, sigmoid, or tanh functions, which are commonly used to transform the weighted sum of inputs in an artificial neural network. Crucially, these functions introduce nonlinearity into the neuromorphic structure, which is essential for deep learning models to learn complex relationships between data and to be able to perform complex tasks.

In optical neural networks, nonlinear activation functions should ideally be implemented in the photonic domain, to avoid the typical conversion between optics and electronics, which would limit the benefits of using photonic hardware in the first place. When it comes to building larger optical neural networks, it might prove especially beneficial to have an all-optical activation function

> Figure 3. Nonlinear activation functions are essential for neural networks to learn complex patterns in data and to perform complex tasks. Acoustic waves can effectively mediate these types of functions in photonic architectures through their nonlinear interactions with light waves.

mage credit: Grigorii Slinkov.

#### TECHNOLOGY | OPTOACOUSTIC COMPUTING

which can also be controlled alloptically, making the system more efficient and easier to scale.

For linear operations such as the weighted sum – a matrix operator – a plethora of photonic techniques already exist. But this is not the case for nonlinear activation functions, for which few approaches have been demonstrated experimentally. Here, acoustic waves could become an enabler because the effect is intrinsically nonlinear. Indeed, we have demonstrated that sound waves can be the mediator for an effective photonic activation function.

Once again, stimulated Brillouin scattering is the key; optical input information interacts with sound waves and undergoes a nonlinear change depending on the level of optical intensity. In this mechanism, the information does not have to leave the optical domain and is directly processed in optical fibres or photonic waveguides.

Besides avoiding electro-optic conversion and any associated loss or latency, including a photonic activation function in an optical neural network also preserves the bandwidth of the optical data and maintains the coherence of the signal. The versatile control of the nonlinear activation function with the help of sound waves allows the implementation of this process in existing optical fibre systems as well as photonic chips.

#### **Future directions**

With our recent European Research Council (ERC) Consolidator funding, we hope to scale up our approach and to achieve complete, reconfigurable computing architectures that might lead to fabrication-less Al. But, while Al may be our primary focus, it is not the only promising application of optoacoustics. Another research direction that the Stiller Lab is actively investigating is the quantum domain; here too, sound waves in optical waveguides could enable technological progress.

For instance, optically controlled acoustic waves could serve as a quantum memory for quantum information processing, as well as for quantum repeaters, which enable long-distance transmission of quantum information despite signal degradation.

We have now used sound waves to implement such a recurrent operator. Our Optoacoustic REcurrent Operator (OREO) harnesses the intrinsic properties of optical waveguides, meaning we can enable recurrent operations in the existing physical structures, without needing to add an artificial reservoir or any additional components

Interactions between light and sound waves could also generate the entanglement necessary for quantum communications.

In the first experimental demonstration of its kind, we have already proven that we can achieve strong coupling between optical and acoustic waves in waveguides – a prerequisite for quantum information processing.

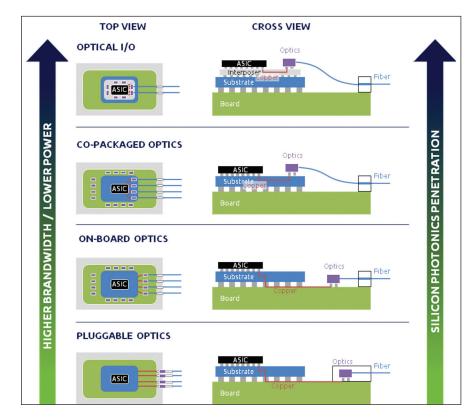

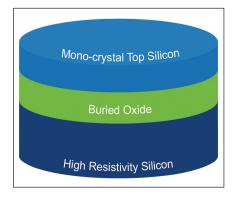

Additionally, we have shown that our system exhibits high cooling rates, meaning it can cool down very quickly between operations, suppressing thermal noise that could interfere with quantum states. These experiments will ultimately enable optoacoustic memory for quantum states and entanglement between photons and phonons — "quanta" of vibrational energy that can be thought of as the sound-wave counterparts of photons.