# INDUSTRY LEADING WAFER PROCESSING EQUIPMENT FOR PHOTONIC INTEGRATED CIRCUITS

### Scaling up PIC innovation

AS THE new Editor of *PIC Magazine*, I am pleased to introduce myself at a moment when Photonic Integrated Circuits are advancing with exceptional speed and maturity.

Stepping into this role has given me a fresh appreciation of how far the PIC community has come in refining circuit architectures, strengthening design processes, and pushing the limits of what integrated platforms can reliably deliver.

This issue comes at a time when the sector is moving forward with renewed clarity and purpose. Research results are transitioning into deployable PIC-based products at an accelerated pace, commercial timelines are tightening, and global demand for compact, high-performance integrated circuits continues to grow. Entering the field today means joining a community firmly focused on scale, efficiency, interoperability, and long-term PIC development strategies.

This edition places strong emphasis on the transition from demonstration-level PICs to full industrial readiness. Several features explore how the sector is preparing for high-volume PIC production and what this shift demands from foundries, circuit designers, process engineers, and packaging specialists. The challenges are substantial and increasingly interconnected. They include improving platform uniformity, strengthening design-for-manufacture principles, enhancing wafer-level testing, and ensuring closer alignment between PIC architectures and advanced packaging. Across the ecosystem, however, the message is one of confidence.

Contributors highlight growing investment in automation, tighter process control, improved simulation workflows, and deeper collaboration across the supply chain—efforts aimed at meeting commercial expectations for performance, yield, and scalability. We also examine how regional strategies are influencing the global PIC landscape. Europe's position is a recurring focus, especially as the region works to consolidate its PIC value chain, expand access to openfoundry services, and build a more resilient environment for PIC design, fabrication, and packaging. Policy coordination, shared infrastructure, and strategic funding programmes

continue to play a crucial role in ensuring that PIC innovation is matched by the capacity to manufacture and scale within the region.

Another central theme in this issue is the increasing importance of ecosystem-level coordination. Progress in hybrid and heterogeneous integration, advances across established material platforms such as InP, SiN, and thin-film lithium niobate, improvements in PIC test strategies, and the introduction of new packaging approaches all depend on how effectively the PIC ecosystem adapts to rapid technological change. Features in this edition underline how essential co-design, interoperability, transparent communication, and evolving standards have become for the next stage of PIC

## **COVER STORY**

## Ge Shape Engineering Unlocks Ultra-Low Back Reflection in High-Speed Ge-on-Si Photodetectors

Shape-engineered Ge-on-Si photodetectors deliver -36 dB optical return loss, ~60 GHz bandwidth, 0.95 A/W responsivity, and <30 nA dark current

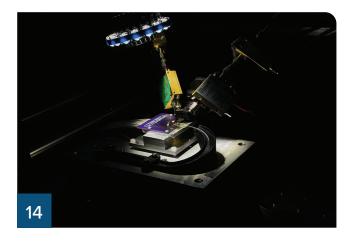

## 14 Reimagining PIC-fibre interfaces with engineered V-Groove technology

Engineered V-Groove technology is redefining fibre alignment in photonic integration, offering a cost-effective, scalable solution that bridges performance with manufacturability for next-generation optical interconnects

## 24 The race to revolutionise silicon photonics with seamless III-V integration

Growing III-V nano-ridge lasers directly on silicon sidesteps the complexities of existing integration methods and paves the way for scalable, cost-efficient PIC production

## 30 Giving AI room to grow with ultra-compact silicon modulators

Al infrastructure requires ultra-fast communications across distant processors, but conventional silicon modulators are bulky and power-hungry

## 34 Putting the UK at the forefront of silicon photonics

The CORNERSTONE foundry at the University of Southampton offers both academic and industrial users a flexible solution for fabricating silicon photonics devices

## 40 Beyond silicon: building a photonic foundation for next-gen computing

Al, quantum, and high-performance computing are outpacing the limits of traditional silicon photonics

#### **NEWS**

- 06 Photonics start-ups driving Europe's innovation surge

- 07 MicroAlign's ultra-precise fibre arrays boost PIC integration

- 08 GUC and Ayar Labs partner on co-packaged optics

- 10 High Tech Campus Eindhoven invests in facilities for TNO's 6-Inch photonic chip pilot line

- 11 LuxQuanta raises €8 million for quantum cybersecurity

Sarab Chopra

**Contributing Technical Editor** Richard Stevenson

Sales & Marketing Manager Shehzad Munshi shehzad.munshi@angelbc.com

Design & Production Manager mitch.gaynor@angelbc.com

Mitch Gaynor Publisher

jackie.cannon@angelbc.com Jackie Cannon

sarab.chopra@angelbc.com

richard.stevenson@angelbc.com +44 (0)1923 690215

+44 (0)1923 690215

+44 (0)1923 690214

+44 (0)1923 690205

Sales and Product Manager

James Cheriton james.cheriton@angelbc.com +44 (0)2476 718970

CEO Sukhi Bhadal sukhi.bhadal@angelbc.com CTO Scott Adams scott.adams@angelbc.com

+44 (0)2476 718970 +44 (0)2476 718970

Angel Business Communications Ltd, 6 Bow Court, Fletchworth Gate, Burnsall Road, Coventry CV5 6SP, UK. T: +44 (0)2476 718 970 E: info@angelbc.com W: picmagazine.net

PIC Magazine is published four times a year on a controlled circulation basis. Non-qualifying individuals can subscribe at: £105.00/e158 pa (UK & Europe), £138.00 pa (air mail), \$198 pa (USA). Cover price PIC Magazine is published four times a year on a controlled circulation basis. Non-qualifying individuals can subscribe at: £105.00/e158 pa (UK & Europe), £138.00 pa (air mail), \$198 pa (USA). Cover price £4.50. All information herein is believed to be correct at time of going to press. The publisher does not accept responsibility for any errors and omissions. The views expressed in this publication are not necessarily those of the publisher. Every effort has been made to obtain copyright permission for the material contained in this publication. Angel Business Communications Ltd © Copyright 2025. All rights reserved. Contents may not be reproduced in whole or part without the written consent of the publishers. The paper used within this magazine is produced by chain of custody certified manufacturers, guaranteeing sustainable sourcing. US mailing information: Pic Magazine, ISSN 1096-598X, is published 4 times a year, March, May, August and December by Angel Business Communications Ltd, Unit 6, Bow Court, Fletchworth Gate, Burnsall Rd, Coventry CV5 6SP, UK. The 2025 US annual subscription price is \$198. Airfreight and mailing in the USA by agent named Air Business Ltd, c/o Worldnet Shipping Inc., 156-15, 146th Avenue, 2nd Floor, Jamaica, NY 11434, USA. Periodicals postage paid at Jamaica NY 11431. US Postmaster: Send address changes to Pic Magazine, Air Business Ltd, c/o Worldnet Shipping Inc., 156-15, 146th Avenue, 2nd Floor, Jamaica, NY 11434, USA. Printed by: The Manson Group. © Copyright 2025. We strive for accuracy in all we publish; readers and contributors are encouraged to contact us if they recognise an error or omission. Once a magazine edition is published [online, in print or both], we do not update previously published articles to align old company names, branding, marketing efforts, taglines, mission statements or other promotional verbiage, images, or logos to newly created or updated names, images, typographic renderings, logos (or similar) when such references/images were accurately stated, ren

# Photonics start-ups driving Europe's innovation surge

Europe's photonics start-up scene is booming, with 240 new companies identified since 2024, bringing the total to 556 active firms, according to new data from Photonics21.

THE European Technology Platform's updated database highlights start-ups developing technologies that tackle major societal challenges, from lifesaving medical diagnostics and surgical tools to quantum communication chips, precision climate and energy sensors, and lasers powering advanced manufacturing.

Healthcare remains the leading sector, with one in five start-ups focused on medical applications such as cancer diagnostics, surgical imaging, and personalised medicine.

Other key sectors include components and advanced materials (16 percent) and Industry 4.0 (14 percent), where photonics supports automation, robotics, and digital factories.

Berlin-based start-up DiaMonTech

exemplifies the impact of these innovations. Founded in 2015, the company has developed a non-invasive glucose monitoring device using mid-infrared light, offering a pain-free alternative for millions of diabetes patients across Europe.

Catalina Plesmann, Head of Marketing, said, "Our technology uses light instead of needles to make glucose monitoring completely pain-free. Europe is where our science was born and where we want to scale."

Dr Lutz Aschke, President of Photonics21, said the growth reflects a dynamic and young ecosystem, with 35 percent of firms founded since 2020 and 84 percent under ten years old. He added that connecting founders with investors remains crucial to help these companies scale within Europe rather than overseas.

Photonics21 supports this through initiatives like Tech Tour Photonics, where EU-based entrepreneurs pitch directly to international investors. This year, 77 companies were evaluated, and 39 were selected to present, highlighting the pipeline of investment-ready photonics ventures emerging across Europe.

Europe's photonics industry, currently valued at €124.6 billion, employs over 430,000 people and is projected to reach €175 billion by 2027, reinforcing the continent's position as a global leader in photonics innovation across Al, quantum, health, green energy, and secure communications.

# MicroAlign's ultra-precise fibre arrays boost PIC integration

Eindhoven-based startup MicroAlign is making waves in the photonic integrated circuit (PIC) sector with its ultraprecisely aligned fibre arrays, tackling one of the biggest bottlenecks in chip-to-fibre integration.

THE COMPANY has developed ready-to-integrate fibre arrays assemblies of optical fibres encapsulated in glass blocks capable of tenfold higher alignment accuracy and 75 times lower fibre-to-chip coupling loss than traditional methods. These advancements are crucial for PIC developers seeking high-performance, scalable optical networks. "Every photon counts in photonic quantum computing, and these fibre arrays set a new benchmark for connectivity efficiency," says MicroAlign CEO Simone Cardarelli.

Founded in 2021 by Cardarelli and CTO Marco Fattori, the startup emerged from PhD research at TU Eindhoven. Embedded in the PhotonDelta ecosystem, MicroAlign has leveraged shared expertise and local networks to refine its technology and target high-end photonic applications. While the company initially pivoted toward

quantum computing, its fibre array solutions are broadly applicable to telecom, sensing, and other PIC-driven industries.

This year, MicroAlign delivered 100 fibre arrays to paying customers and is preparing to scale production with a 500-square-meter facility slated to open in 2026. The plant aims to produce up to 100,000 fibre arrays annually, supporting industry demand for high-precision, low-loss integration.

Cardarelli highlights the technical challenges behind their approach: "Fibre behaves chaotically when handled, so automating this delicate process requires precision engineering and deep expertise." Looking ahead, MicroAlign aims to become the gold standard for PIC fibre connectivity, potentially supporting the next generation of high-performance photonic systems.

### CITC joins TNO to strengthen chip packaging in Nijmegen

THE Chip Integration Technology Centre (CITC) will become part of TNO, marking a major step in advancing chip packaging research and innovation. The integration, effective January 1, 2026, aims to secure CITC's long-term continuity and strengthen the Netherlands' semiconductor ecosystem, connecting Nijmegen with other hubs such as Eindhoven.

CITC, founded in 2019 by TNO and TU Delft, has developed into a broad R&D hub for advanced chip packaging technologies. By joining TNO's High Tech Industry unit, CITC will expand research efforts, accelerate innovation, and maintain its presence at the Noviotech Campus in Nijmegen.

Arnaud de Jong, TNO's director

of High-Tech Industry, said,

"Integrating CITC allows us to

intensify our work in advanced

chip packaging and contribute

to a strong, future-proof

semiconductor ecosystem in

Nijmegen." Jeroen van den Brand,

CITC general manager, added

that the move strengthens CITC's

international position as a centre of

expertise.

TU Delft remains closely involved, ensuring that the collaboration continues to support the growth of chip integration and packaging technologies across the region.

## GUC and Ayar Labs partner on co-packaged optics

Global Unichip Corp. (GUC), a leading provider of advanced ASIC design services, has announced a strategic partnership with Ayar Labs to integrate co-packaged optics (CPO) into next-generation compute architectures aimed at AI, HPC and hyperscale data centre applications.

THE collaboration combines GUC's advanced packaging and ASIC design expertise with Ayar Labs' TeraPHY™ optical engines, positioning the two companies to address the growing limitations of electrical interconnects as AI model sizes and bandwidth requirements continue to surge.

According to GUC CTO Igor Elkanovich, the shift toward optical I/O is becoming unavoidable as system bandwidth demands outpace electrical signalling capabilities. "The CPO revolution is at our doorstep," he said. "Integrating Ayar Labs' optical engines into our advanced packaging flows is a critical step. Our new joint design allows us to address the architectural, power, signal integrity, mechanical and thermal challenges of CPO integration, ensuring customers have access to robust, high-bandwidth and power-efficient solutions."

At the core of the partnership is a new XPU multi-chip package (MCP) architecture that replaces traditional electrical interfaces with optical engines mounted directly onto the

organic substrate. The design delivers more than 100 Tbps full-duplex optical bandwidth, representing an order-ofmagnitude leap over current-generation XPUs.

The companies are leveraging UCle-S (64 Gbps) links between the optical engines and I/O chiplets, while UCle-A (64 Gbps) provides connectivity between the I/O chiplet and the main Al die via local silicon interconnect bridges. The MCP design includes enhancements addressing

power and signal integrity at scale, as well as thermal optimisations. A newly engineered stiffener enables detachable fibre connections while maintaining mechanical stability and warpage performance.

GUC plans to share further details on the technology during its presentation, "Advanced Packaging Technologies for Modular and Powerful Compute," at the 2025 TSMC Open Innovation Platform (OIP) Forum on November 18 in Hsinchu, Taiwan.

## Dedicated webinars for the photonic integrated circuits (PIC) industry

Using our 30+ years' experience in B2B vertical technical markets, and as the publisher of PIC Magazine, we offer effective webinars, ZOOM interview and virtual events. We help you get your message, to your desired audience, by marketing to over 30,000 PIC professionals.

In addition to organising and managing your webinar, we can also market your webinar to our specialist databases.

Reach Educate Influence

- Brand Awareness

- Lead Generation

- Thought Leadership

Contact: Jackie Cannon jackie.cannon@angelbc.com +44 (0)1923 690205

# Access the full potential of hybrid multi-chip integration

# High Tech Campus Eindhoven invests in facilities for TNO's 6-Inch photonic chip pilot line

High Tech Campus Eindhoven (HTCE) will host a new industrial pilot line for photonic chips, developed by TNO as part of the EU's PIXEurope project.

Construction of the building and cleanroom facilities will begin in February 2026 on the north side of the campus. Once operational, the facility will serve as both a testbed and fabrication site for advanced Indium Phosphide (InP) photonic chips, enabling full-scale manufacturing at a 6-inch wafer level.

The new pilot line represents a major step toward industrial-scale photonic chip production in the Netherlands and Europe. By combining research and manufacturing capabilities, the facility aims to accelerate the transition from innovative ideas to energy-efficient and reliable real-world technologies. With a capacity to produce up to 10,000 wafers per year, it will significantly increase throughput and efficiency for integrated photonic devices.

Ton van Mol, Managing Director at TNO,

described the initiative as a gamechanger for Dutch companies and a key part of the PhotonDelta ecosystem that positions the Netherlands as a leader in photonics. Otto van den Boogaard, CEO of HTCE, said the campus is proud to invest in and provide the facilities for the pilot line, reinforcing its role as a hub for breakthrough technology and innovation.

HTCE's investment reflects its commitment to projects that strengthen the region's technological ecosystem and national earning capacity.

The collaboration between TNO, PhotonDelta, and HTCE underlines the importance of local infrastructure in scaling up Europe's photonics manufacturing capabilities and supporting the growth of the integrated photonics industry.

#### Aluvia Photonics secures funding from PhotonDelta

ALUVIA PHOTONICS, a company developing aluminium oxide (AIOx) PICs, has secured new funding from PhotonDelta to expand its technology and deepen collaborations within the PhotonDelta ecosystem.

The company says this support strengthens its ability to accelerate ongoing projects and explore new opportunities with customers and suppliers in the region.

Aluvia's AlOx platform aims to bring compact, scalable waveguides and amplifiers to the photonic chip ecosystem, targeting telecom, quantum, and UV-visible applications where conventional solutions are limited. Complementary to existing photonic chip technologies, Aluvia says its platform can be combined seamlessly with other platforms, helping to give them new functionality and extend their performance. In this way, the technology aims to strengthen the ecosystem and open new opportunities for designers and manufacturers alike.

"We're delighted to have Aluvia in the PhotonDelta ecosystem and now also as one of our promising startup portfolio," said Erwin Holtland, investment manager at PhotonDelta. "We're excited about the opportunities now possible with their technology and see strong potential across our portfolio."

PhotonDelta's funding provides Aluvia with a strategic boost, the company adds, as it prepares for a new investment round in 2026 aimed at scaling up manufacturing. The support aligns with PhotonDelta's mission to strengthen the Dutch integrated photonics ecosystem and attract private co-financing for industrial-scale development.

# LuxQuanta raises €8 million for quantum cybersecurity

The company plans to use the investment to expand its teams, scale production, and advance research in integrated photonics – a key technology for developing scalable, quantum-safe solutions

LUXQUANTA, a spinoff of ICFO focusing on quantum cybersecurity, has announced the closing of its €8 million Series A funding round. Led by Big Sur Ventures, and with support of A&G as the main investor, the round also includes new investors GMV, Wayra, and the EIC Fund, alongside renewed commitments from existing investors Corning and GTD. The investment is further bolstered by the soft financing from the European Investment Committee (EIC) through the EIC Accelerator programme, following the €2.5 million grant awarded to LuxQuanta in March 2024.

The company plans to use the funding to scale production, advance research and development in quantum technologies and integrated photonics, expand its commercial, technical, and operational teams, and accelerate international market expansion.

The rise of quantum computing poses a significant risk to current encryption systems, but transitioning to quantum-safe infrastructures is a complex, long-term process. If public and private entities want to keep confidential data protected, immediate action is necessary.

LuxQuanta says its continuousvariable quantum key distribution (CV-QKD) technology is poised to democratise quantum-safe communications, delivering robust, scalable, and accessible solutions for telecommunications, governments, datacentres, financial institutions, critical infrastructures, and industrial and energy sectors.

The company's flagship product NOVA LQ, launched in its second generation in March 2025, is designed to integrate seamlessly into existing optical

networks while offering unmatched security and scalability. According to LuxQuanta, the product also offers high secret key rates, standards-based interoperability, and operational reliability.

"This Series A funding is a powerful validation of our vision to safeguard global communications in the quantum era," said Vanesa Díaz, CEO of LuxQuanta. "With this investment, we will scale our operations, enhance our technology, and expand our global footprint. The journey to quantum-safe networks is critical, and it starts now. We're committed to making quantum security accessible and reliable for organisations worldwide."

Ismael Almazán, partner at Big Sur Ventures, commented: "LuxQuanta's proven CV-QKD technology and successful deployments position it as a leader in quantum cybersecurity. Their focus on integrated photonics is a game-changer, and we're thrilled to support their mission to set a global standard for quantum-safe infrastructure."

LuxQuanta is headquartered in Barcelona with a business unit in Madrid. The company plans to relocate to larger facilities, ramp up production, and selectively expand into new markets in Europe and beyond. The funding will also fuel advancements in integrated photonics, LuxQuanta adds, a key technology for reducing costs and enhancing scalability to meet the growing global demand for quantum-safe solutions.

LuxQuanta's proven

CV-QKD technology and

successful deployments

position it as a leader in

quantum cybersecurity.

Their focus on

integrated photonics

is a game-change

## 20-22 APRIL 2026 BRUSSELS BELGIUM

#### CONNECTING, EDUCATING & INSPIRING THE PIC INDUSTRY

The 11th PIC International builds on the strengths of its predecessors, with around 40 leaders from industry and academia delivering presentations falling within four key themes:

Those attending these sessions will gain greater insight into device technologies while learning of the latest opportunities and trends within the PIC industry. Delegates will also discover significant advances in tools and processes that deliver enhanced yield and throughput.

Attendees at this two-day conference will also meet a wide variety of key players within the community, from investors and analysts to fab engineers and managers.

PIC International is part of AngelTech, which delivers a portfolio of insightful, informative, highly valued chip-level conferences. Bringing together an Innovate Summit and four conferences with more than 120 presentations, more than 700 delegates and over 80 exhibitors,

AngelTech is the premier global event covering compound semiconductors, photonic integrated circuits, power electronic technologies and advanced packaging.

With a significant overlap between the four conferences, attendees and exhibitors are exposed to the full relevant supply chains and customer and supplier bases.

#### **Key Themes for 2026**

## Foundations of PIC design: materials, devices and processes

While PICs are well established, they still face technological limitations. How can new materials and devices improve their performance and expand their range of functionalities, and how can we accelerate these innovations to market?

#### Connectivity and scalability for secure, highspeed data networks

Data communications networks face numerous challenges, including soaring Al-driven demands, high energy consumption, and the possibility of future quantum technologies breaking current encryption methods. How can PICs help to solve these issues and underpin the high-speed, energy-efficient, quantum-secure networks of the future?

## Emerging applications: photonics for sensing, imaging and beyond Integrated photonics has a wide range of potential

Integrated photonics has a wide range of potential applications. From self-driving cars to miniaturised molecular sensors and non-invasive healthcare, how are PICs making these possibilities a reality?

## Future computing: PICs for photonic processing, quantum computers, and neural networks

Computing power is integral to the modern world, but established technologies have limits, and novel systems could herald more powerful devices. From fully photonic processing to photonics for neuromorphic and quantum computing, how are PICs transforming the way we process data?

#### **SPECIAL Event Discount:**

Register before 31 JANUARY 2026 and get 10% OFF!

Registration to AngelTech allows you to access both days of PIC International, CS International, Advanced Packaging and PE International.

Engineered V-Groove technology is redefining fibre alignment in photonic integration, offering a cost-effective, scalable solution that bridges performance with manufacturability for next-generation optical interconnects.

BY: AURI RIPOLL, MARKET INTELLIGENCE & STRATEGIC MARKETING MANAGER, DIRK HAUSCHILD, SENIOR STRATEGIC MARKETING EXPERT, AND ZHICHAO HE, MARKETING MANAGER, FOCUSLIGHT

IN THE rapidly evolving world of photonics, PICs have emerged as a transformative force across industries – from ultra-fast datacentres to next-generation AI computing. But despite their potential, a fundamental challenge threatens to slow these chips' adoption: how they connect to the outside world, especially via optical fibres.

At the heart of every photonic system lies the need to align optical fibres to PICs with sub-micron precision. Even a small misalignment can drastically degrade signal quality, introduce insertion losses, or compromise system performance.

Fibre-to-chip interfaces are often overlooked but are mission-critical. They must meet the dual demands of sub-micron precision and high-volume manufacturability, a combination that traditional fabrication techniques struggle to deliver. As PICs become more complex and integrated with AI workloads, datacentres, and quantum systems, the cost of even minor inefficiencies in these interfaces increases exponentially.

This is precisely where engineered V-Groove technology steps in - a quiet innovation with far-reaching implications.

A traditional solution for connecting PICs to fibres involves blade dicing – a mature and well-understood process in which a rotating blade sequentially cuts grooves into a substrate to hold individual fibres in place. But despite its widespread use, the method presents

serious limitations for modern PIC applications.

First, there's tool wear. As the blade cuts through glass or silicon, its geometry degrades, leading to inconsistent groove depth and pitch variation, especially across large channel counts (>16). The cumulative result is misalignment between the fibre and the PIC waveguide.

Second, sequential processing, whereby each groove is cut one at a time, introduces positional errors, with tiny inconsistencies accumulating—especially over large arrays. Add to this the impact of thermal drift, substrate warping, and material flaking, and the result is a high failure rate and increased need for active alignment and inspection.

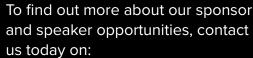

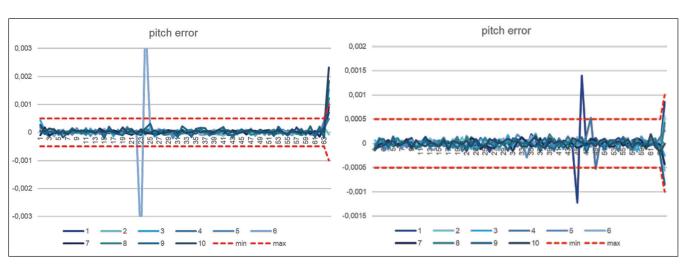

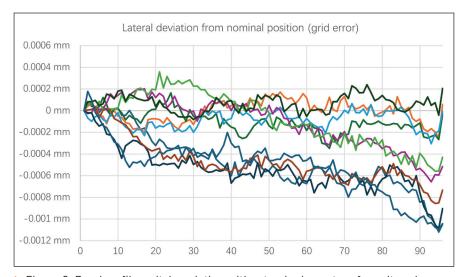

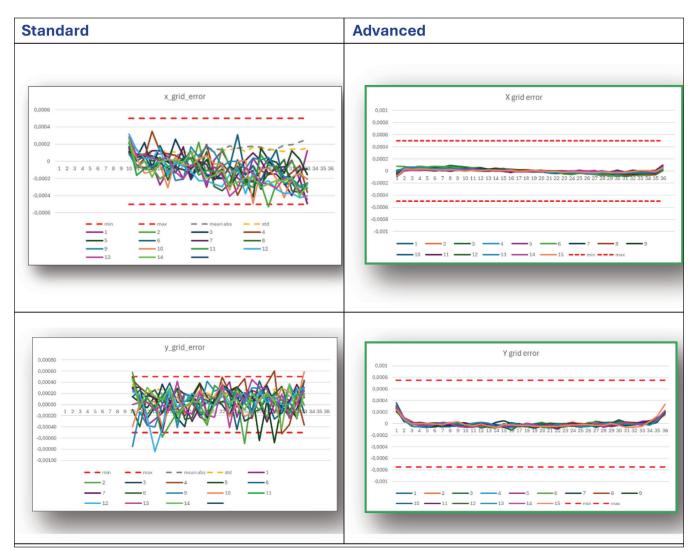

Figures 1-3 show measurements that were made with commercially available components, illustrating some characteristic problems with current methods.

#### **Cumulative errors**

The singular random pitch and position errors limit the number of channels per product and require a 100 percent test procedure (both incoming quality control and outgoing quality control) to avoid defective products at functional inspection after assembly is finished. Due to the sequential positioning of the blade, individual cutting characteristics, and degradation of the blade, achieving a defect-free product means using a selection process that will affect the yield and the resulting cost structure of the product.

During assembly of connectors and PIC-fibre interfaces, the height and roll angles – key parameters defining how well the fibre is aligned to the groove – should be reproducible across the fibre array. However, current methods offer insufficient reproducibility. Not only does this result in lower overall performance and increased variation in performance within the array of channels, but it also requires some compensation for errors, increasing the assembly time and cost.

In addition, the larger variation of parameters has implications for using reproducibility and repeatability as a basis for a good process capability index (Cpk) – a statistical measure of how consistently a process can produce output conforming to specified limits.

The combination of errors and the

distribution of functional parameters give a clear indication about the process capability and resulting yield in production. The errors and variation of parameters described above lead to a parameter distribution that is not comparable with a typical Gaussian normal distribution which is based on the variation of blade geometry and positioning during V-groove processing. Figure 3 shows a typical distribution of functional parameters of a sequential process that does not show a single "centre of gravity" value with an even distribution on either side.

This observed non-Gaussian distribution is due to the limitations inherent in sequential blade dicing; this process suffers not only from blade wear but also from cumulative 2D positioning errors and environmental temperature drift. These factors lead to systematic degradation of groove geometry, affecting reproducibility and the overall process capability index. In addition, uncontrolled sharp edges and glass flakes from the cutting process can damage delicate optical fibres, further reducing yield.

These issues also compromise compatibility with emerging copackaged optics (CPO) and multichannel transceivers, where even a 1 µm deviation can degrade link performance.

Additionally, traditional V-groove arrays are often limited by their reliance on specific materials, usually constrained to glass types that are compatible with mechanical cutting. This restricts compatibility with a broader range of

PIC materials, such as silicon, indium phosphide, silicon nitride, and lithium niobate, which are increasingly used in advanced photonic systems.

Finally, traditional blade-diced grooves often struggle to support high-density integration. As industry trends shift toward greater channel counts and denser packaging formats, the limitations of sequential processing become even more pronounced. Blade cutting is not only slower but also more likely to introduce thermal stress and microfractures, especially when pushing toward edge-to-edge array configurations.

#### Innovation unveiled

Focuslight's Engineered V-Groove technology solves these problems by rethinking the process from the ground up.

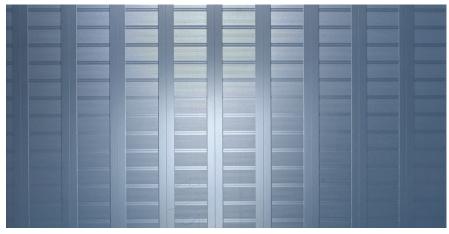

Instead of cutting grooves one by one. Focuslight uses a proprietary wafer-level simultaneous structuring approach. All grooves and alignment features are structured simultaneously across the entire wafer, processing all grooves and assembly features at the same time and thus avoiding cumulative errors inherent to sequential dicing. The process is conducted in a temperaturecontrolled environment, compatible with large substrates, and allows integration of concave/convex geometries, smooth transition zones, and customised v-angles. 100 percent in-line wafer-level testing ensures statistical reproducibility and Gaussian distribution of positional accuracy.

The benefits are immediate and profound, eliminating tool wear and

> Figure 1: Single channel errors observed in typical >16 channels blade diced v-grooves.

#### TECHNOLOGY | PIC-FIBRE COUPLING

> Figure 2: Variation of the position and orientation of fibre arrays within blade diced V-grooves.

➤ Figure 3: Random fibre pitch variation without a single centre of gravity value.

> Figure 4: Wafer-level structured substrate with engineered V-grooves.

geometric limitations of blade dicing, and reducing production time by 40 percent compared to sequential methods. Additionally, this approach offers flexibility for standard and application-adapted designs and mechanical positioning support, and allows customisation with a variable number of channels, and the potential to include assembly features to facilitate the packaging process.

Moreover, this process is fully compatible with wafer-level metrology. Focuslight inspects every unit on the wafer before dicing, ensuring quality control without needing downstream inspection.

Key performance specifications include a lateral grid error of  $\pm 0.25$   $\mu m$  in the high-accuracy version of the technology, and  $\pm 0.5$   $\mu m$  as standard, with a vertical alignment error of  $\pm 0.35$   $\mu m$  (high accuracy), or  $\pm 0.7$   $\mu m$  (standard). The single-mode fibre coupling efficiency is greater than 99.5 percent per channel. Additionally, the process is compatible with materials including fused silica, Borofloat 33, S-TIH53, N-BK7, and silicon, and supports pitches of 127  $\mu m$ , 250  $\mu m$ , and custom sizes.

In addition to standard features, Focuslight's platform enables customers to design grooves with applicationspecific mechanical or optical features. These can include thermal compensation features to reduce drift, optical blocking or guiding elements, recessed or elevated plateau areas for dual-layer packaging, and built-in fiducials for vision alignment systems.

Focuslight's platform also allows for scalable production with reduced waste, minimal edge chipping, and significantly reduced risk of microcracks, making it ideal for use in sensitive optical or high-voltage environments.

With wafer-level control, Focuslight can produce V-groove arrays scalable to 96 channels and higher, tailored to application needs, while ensuring consistency across every groove.

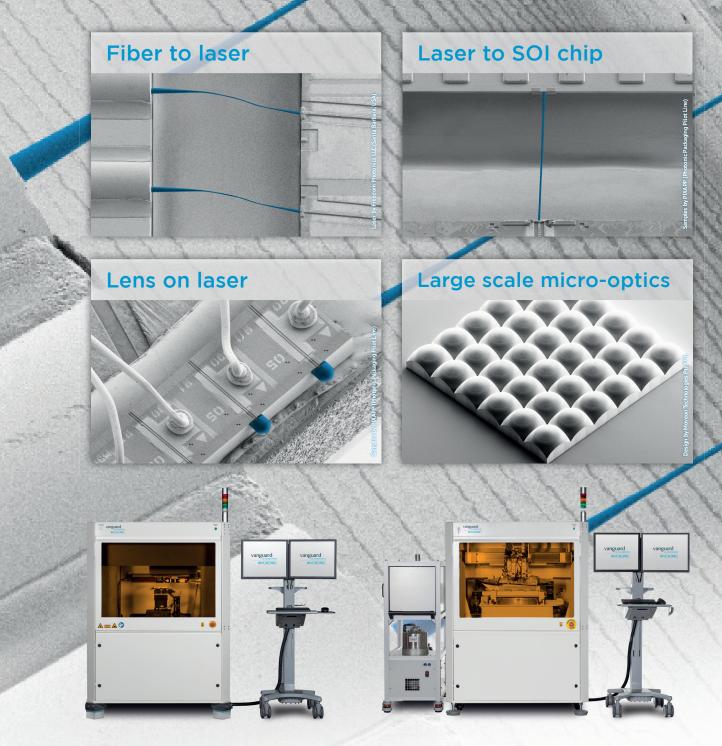

#### Designed for the real world

What truly differentiates engineered V-grooves from other high-precision technologies is their readiness for production. Focuslight's process is built on an infrastructure originally developed for high-volume micro-

Looking ahead, Focuslight continues to invest in next-generation manufacturing technology, including Al-driven process control and data-driven yield optimisation. These enhancements will further improve the consistency, cost-effectiveness, and sustainability of photonics manufacturing

optics. With substrate sizes ranging from 0.4 to 300 mm and standard thickness tolerances of  $\pm 0.05$  mm, it supports both custom and standardised product configurations.

Further capabilities include a fully customisable groove depth and step dimensions of  $\geq$ 0.1 mm  $\pm$  0.02 mm. The solution also offers edge chipping of  $\leq$ 0.1 mm on outer dimensions (minimised internally) and either a

grinded or polished surface finish, depending on optical grade.

Focuslight has also developed a wafer-level testing strategy that includes automatic quality mapping prior to back-end separation.

This ensures that 100 percent of units are tested, that the grid deviation and plateau height are within defined tolerances, and that there is no need for post-assembly active alignment.

> Figure 5: Wafer test result showing Gaussian distribution of grid error.

#### TECHNOLOGY | PIC-FIBRE COUPLING

The resulting process achieves high process capability (Cpk), low variation, and a reliable statistical distribution of performance characteristics – ideal for automation.

With its low-defect, high-throughput process and compatibility with a wide variety of substrates, Focuslight's engineered V-groove platform enables cost-effective production of high-performance optical systems across the full spectrum of commercial photonics applications.

As photonic integration continues to push the boundaries of how fibres and chips are brought together, achieving reliable coupling is no longer only about precision – it is equally about scalability, manufacturability, and long-term system stability. We are entering an era of platformisation in photonics; much like CMOS enabled the rise of ubiquitous electronics, scalable packaging and interfacing solutions will be key to the next wave of optical systems. By removing complex alignment steps

and minimising tolerance errors, Focuslight is enabling a future in which PIC modules are manufactured like electronic integrated circuits: reliably, rapidly, and affordably. By shifting from sequential blade dicing to wafer-level simultaneous structuring, the industry gains a platform that unites submicron alignment accuracy with volume production capability.

This convergence opens the door to new design freedoms, from customised geometries to integration with advanced PIC materials. These advantages will support the expansion of photonics into consumer devices, healthcare, edge computing, and satellites, where reliable and scalable interfaces are essential. Looking ahead, Focuslight continues to invest in next-generation manufacturing technology,

including Al-driven process control and data-driven yield optimisation. These enhancements will further improve the consistency, cost-effectiveness, and sustainability of photonics manufacturing.

As photonic systems evolve toward higher density and broader application spaces – from Al accelerators to quantum communication – the role of engineered V-grooves will be central in ensuring that performance and scalability advance hand in hand.

Usage Statement: All images included in this article are the intellectual property of Focuslight Technologies and are provided with full publication rights for use in PIC Magazine Issue 2025.

#### **FURTHER READING**

➤ 1. Focuslight Technologies, V-Groove Capability Guidelines 2025

#### Dedicated webinars for the photonic integrated circuits (PIC) industry

Using our 30+ years' experience in B2B vertical technical markets, and as the publisher of PIC Magazine, we offer effective webinars, ZOOM interview and virtual events. We help you get your message, to your desired audience, by marketing to over 30,000 PIC professionals.

In addition to organising and managing your webinar, we can also market your webinar to our specialist databases.

In a dedicated 6 week program we will promote through our magazine, newsletters, LinkedIn group and website. We can also provide the webinar moderator, from our team of highly respected editors. Let our editors work with you and help you with the content.

#### Reach Educate Influence

- Brand Awareness

- Increase global awareness by running sponsored webinars, Zoom interviews and virtual events

- Lead Generation

- Generate and mature leads through the use of online events. Then analyse, qualify, and understand their buying behaviour

- Thought Leadership

- Become the voice of knowledge by generating compelling content via online events

Find out how Angel Webinars can help you organise and run a webinar within the PIC industry.

> Contact: Jackie Cannon jackie.cannon@angelbc.com +44 (0)1923 690205

# OFC

The future of optical networking and communications

# Register Today

It's all here at OFC.

The brightest minds. The boldest innovations.

Technical Conference: 15 - 19 March 2026 Exhibition: 17 - 19 March 2026 Los Angeles Convention Center Los Angeles, California, USA

# Taming reflections: Ge shape engineering unlocks ultra-low back reflection in high-speed Ge-on-Si photodetectors

Shape-engineered Ge-on-Si photodetectors deliver -36 dB optical return loss, ~60 GHz bandwidth, 0.95 A/W responsivity, and <30 nA dark current - achieved through innovative Ge shaping in a 300 mm CMOS silicon photonics flow, enabling robust, IEEE-compliant solutions for Al data centers and co-packaged optics.

BY YUSHENG BIAN, SUJITH CHANDRAN,

ABDELSALAM ABOKETAF, WON SUK LEE, QIDI LIU,

MASSIMO SORBARA, BOB MULFINGER AND RYAN SPORER,

GLOBALFOUNDRIES; EDGAR HUANTE-CERON, RANOVUS

AS LINK SPEEDS surge for artificial intelligence (AI) clusters and cloud data center interconnects (DCI), back reflection from optical components has emerged as a subtle but escalating threat to link stability and signal integrity. Reflections drive standing waves, jitter, and even laser instabilities; in dense links, they also inflate bit error rate (BER) and degrade signal to noise ratio (SNR). IEEE 802.3 standards enforce tight specifications on both transmitter (TX) and receiver (RX) reflectance to ensure link stability and compliance [1] - shifting some margin from TX to RX can relieve costly TX-side constraints at 100G+/lane. From the field's perspective, ORL is the system-level sum of Fresnel reflections and Rayleigh backscatter along the light path; controlling it at the component level (including photodetectors (PDs) is essential to tame end-to-end reflection budgets in modern links..

## Our contribution: shape engineered Ge on Si PIN PDs

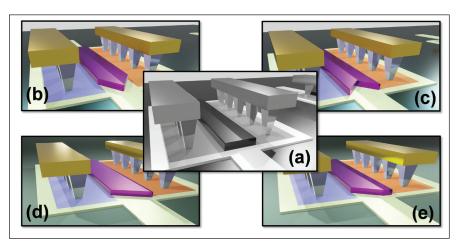

In a CMOS monolithic silicon photonics flow [2-9], we redesigned the Ge absorption geometry - moving beyond

the conventional rectangular mesa (Fig.1(a)) to angled, convex/concave, quadrilateral, and pentagon shapes that steer reflected light away from the Si waveguide taper, as shown in Figs.1(b)-(e)). The result is a family of PDs that achieve ORL down to -36 dB while preserving high responsivity (~0.95 A/W), low dark current (<30 nA median at -1 V), and ~60 GHz 3 dB optoelectrical (OE) bandwidth (BW) in the O band [10].

Why it matters: Reducing PD originated reflections relaxes upstream laser/ isolator demands and makes it easier to meet stringent ORL budgets in pluggables and future co packaged optics (CPO) - without exotic process steps.

## Design: how "shaping" suppresses reflection

**Problem:** Butt coupling a Si waveguide (WG) taper into a Ge absorption region introduces effective index discontinuities and mode profile mismatch - prime triggers for back reflection at the Si - Ge interface.

Approach: We use geometrical shaping of the Ge region (including angled tips and asymmetric facets) so any reflected field misses the incoming waveguide axis. Finite difference time domain (FDTD) optimization tuned the tip angle, facet lengths, and taper overlap to minimize coherent back coupling while sustaining absorption and contact layouts compatible with foundry design rules.

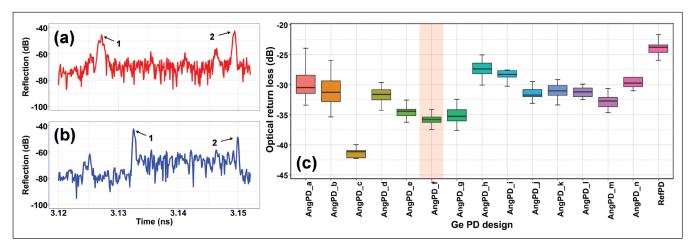

**Outcome**: Several candidates deliver ORL < -30 dB, with our lead design (Fig. 2(b) - AngPD\_c) reaching -41 dB at 1310 nm. The statistical spread across 10 dies/design remains tight, indicating process tolerance.

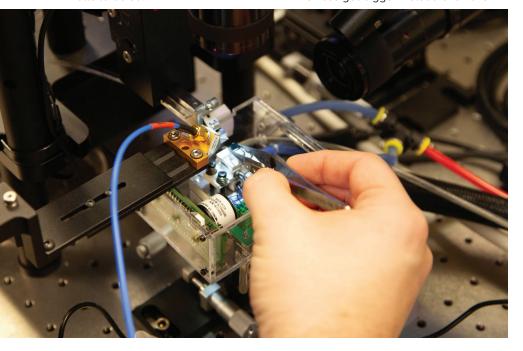

## Measurement: how we quantified ORL - and everything else

ORL characterization was performed at wafer level using grating coupler test structures and an Optical Vector Analyzer (OVA) with Optical Frequency Domain Reflectometry (OFDR) to map reflection events in the time/space domain. OFDR's micrometre scale spatial resolution is particularly useful in photonic integrated circuits (PICs) where multiple weak reflectors coexist within millimetres.

For readers less familiar with OFDR:

In a CMOS monolithic silicon photonics flow, we redesigned the Ge absorption geometry - moving beyond the conventional rectangular mesa to angled, convex/concave, quadrilateral, and pentagon shapes that steer reflected light away from the Si waveguide taper

it's an interferometric technique using a swept laser and Fourier processing to recover a reflection vs. distance profile with high dynamic range and spatial resolution, ideal for short devices and PICs; it complements Optical Time-Domain Reflectometry (OTDR) and Optical Low-Coherence Reflectometry (OLCR).

High speed response was measured on a 70 GHz lightwave component analyzer (LCA). DC metrics (I V, dark current, responsivity vs. bias/power/temperature) were gathered on temperature controlled probe stations.

#### Results at a glance

#### Optical return loss (ORL) (Fig.2(c)):

- Reference (rectangular Ge): higher reflection at PD-WG interface (time domain peaks)

- Shape engineered PDs: multi dB ORL reductions across all variants; best -36 dB => -41 dB at 1310 nm; tight lot to lot dispersion.

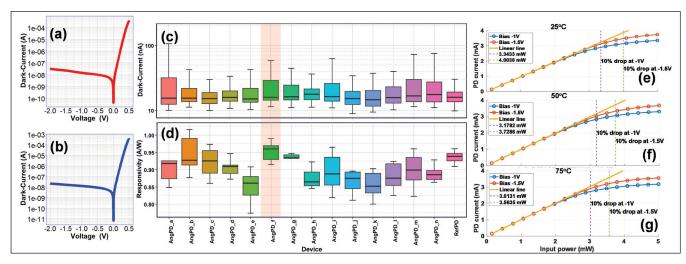

## Dark current & responsivity (-1 V) (Fig.3):

O Dark current: median <30 nA; most

- devices <100 nA, consistent with high quality Ge epitaxy and junction control (Fig.3 (c)).

- Responsivity: >0.85 A/W median; up to ~0.95 A/W, matching or exceeding the reference PD (Fig.3 (d)).

#### Linearity & high power handling:

• Photocurrent remains linear up to several milliwatts; as expected, response begins to roll off at higher powers due to carrier recombination/screening, but increasing reverse bias expands the linear region (e.g., 10% roll off point shifts from "3.35 mW to "4 mW at room temperature) (Figs.3 (e) – (g)). The power handling vs. temperature trade off follows known high carrier density dynamics in Ge PDs.

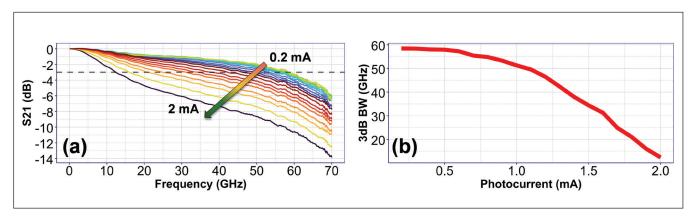

#### OE bandwidth:

• Normalized OE frequency response shows "60 GHz 3 dB bandwidth at "0.2 mA photocurrent; still >50 GHz at "1 mA (Fig.4). Bandwidth rolls off moderately at higher photocurrents, consistent with carrier screening; we're exploring implant/profile refinements to further stabilize high power bandwidth.

Figure 1. Ge-on-Si PD shape variations 3D perspective views of Ge-on-Si photodetector designs illustrating geometry-driven reflection control: (a) Reference PD with rectangular Ge; (b) convex-shaped Ge; (c) concave-shaped Ge; (d) quadrilateral-shaped Ge; (e) pentagon-shaped Ge. These alternative geometries redirect reflected light away from the Si waveguide taper to minimize ORL

> Figure 2. ORL characterization and statistical performance (a) OFDR reflection spectra comparing a reference PD with rectangular Ge and a representative angled PD. The PD-WG interface peak is strongly suppressed in the shaped design. (b) Statistical distribution of measured ORL values for all PD geometries at 1310 nm, showing consistent reductions below -30 dB and best-case performance near -41 dB.

**Key point:** Across ORL, DC, and RF metrics, no speed/responsivity penalty accompanies reflection suppression - the trade off is effectively neutralized through geometric shaping.

## System impact: cleaner receivers, simpler lasers

In Ethernet and Al interconnect roadmaps, ORL and reflectance allocations are hotly debated because every dB of reflection control buys laser stability and may reduce dependency on isolators or complex TX side strategies. By attenuating the PD's own reflection, receiver chains become easier to integrate and more robust, especially for co packaged optics and high radix fabrics where many short

optical paths amplify sensitivity to internal reflections.

This work aligns with ecosystem moves to monolithically integrate more of the optical stack and to package at scale as well as system level efforts in CPO and application specific optical engines. Minimizing PD reflection is a small change with big system level dividends.

## Where this sits in the literature - and what's next

Ge on Si PDs are a backbone device for SiPh, prized for CMOS compatibility, high responsivity, and strong bandwidth -attributes charted in review literature and sustained by ongoing advances in epitaxy and junction engineering. Our contribution specifically targets the under discussed reflection dimension, demonstrating that geometry alone can reclaim >10 dB of ORL while preserving hallmark performance.

#### Next steps include:

- Co-optimization with couplers, junctions, and electrical parasitics to further improve responsivity and bandwidth across a wider operating range.

- Integration with TIA and eyediagram analysis to assess link-level performance and confirm compliance with high-speed standards.

- Module-level validation (e.g., with isolator-free or reduced-isolation TX) to quantify system-level penalties

> Figure 3. DC characteristics and high-power behavior (a)-(b) I-V curves for reference and angled PD designs, confirming preserved diode behavior. (c) Dark current distribution at -1 V reverse bias, with median values <30 nA. (d) Responsivity at -1 V bias, exceeding 0.85 A/W for most designs and reaching  $\sim$ 0.95 A/W. (e)-(g) Responsivity versus input optical power across temperatures (25 °C, 50 °C, 75 °C) for reverse biases of -1 V and -1.5 V, highlighting improved linearity and power handling with increased bias.

> Figure 4. High-speed performance (a) Normalized opto-electric frequency response of the angled PD at varying input optical powers (photocurrent range: 0.2 mA to 2 mA). (b) Extracted 3 dB EO bandwidth as a function of photocurrent, demonstrating ~60 GHz at low photocurrent and >50 GHz at 1 mA, with moderate roll-off at higher powers due to carrier screening.

recovered by low-reflection PDs particularly in O-band pluggables and CPO engines.

## Practical design takeaways (for readers building receivers)

- Start with geometry: If you see stubborn reflection peaks at the PD-WG interface in OFDR, try angled or asymmetric Ge tips to dump eflected power off axis. This is a layout-level adjustment using the existing mask set and remains fully compatible with foundry design rules.

- Validate statistically: Measure dozens of dies; reflection is phase sensitive and can hide behind path length variations. OFDR's spatial mapping reveals true contribution.

#### O Co design bias & power:

Expect bandwidth roll off at higher photocurrent due to screening; allocate headroom in reverse bias to extend linearity and BW in deployment.

• Think system budgets: A few dB better ORL at the PD can shift margin in IEEE style allocations and de risk both RX and TX. Coordinate with optics + packaging teams early.

#### Acknowledgement

The authors would like to thank Michelle Zhang, Judson Holt, Kevin K. Dezfulian, Mankyu Yang, Brian Popielarski, Ming Gong, Shantanu Pal, Javier Ayala, Patrick Snow, Helen Wong, Mrunal Shah, Felix Beaudoin, Frank Pavlik, Crystal Hedges,

Frieder Baumann, Takako Hirokawa, Andy Stricker, Oscar Restrepo, Madhuchhanda Brahma, Brett Yatzor, Yu Zhang, Michal Rakowski, Hanyi Ding, Kate McLean, Teodor Stanev, Paul Webster-Pact, Ah Fatt Tong, Jonathan Rullan, Glyn Braithwaite, Vikas Gupta, Rick Carter, Ken Giewont, Ted Letavic, Kevin Soukup, and the rest of the GlobalFoundries team for their development engineering support for Fotonix<sup>™</sup> technologies. We also extend our sincere thanks to Hatef Shiran, Ana Villafranca, Kyle Murray, Mohammad Karimi, Akram Hajebifard, Prova Christina Gomes, John Martinho, and the rest of the Ranovus team for their invaluable support with measurements and data analysis.

#### **FURTHER READING**

- ▶ [1] IEEE 802.3, IEEE 802.3 ETHERNET

- [2] Y. Bian et al., "3D Integrated Laser Attach Technology on a 300-mm Monolithic CMOS Silicon Photonics Platform," IEEE J. Sel. Topics Quantum Electron., Invited Paper, vol. 29, no. 3, pp. 8200519, 2023. DOI: 10.1109/ JSTQE.2023.3238290

- ➤ [3] V. Stojanović et al., "Monolithic silicon-photonic platforms in state-of- the-art CMOS SOI processes," Opt. Express, vol. 26, no. 10, pp. 13106—13121, 2018.

- ➤ [4] K. Giewont et al., "300-mm monolithic silicon photonics foundry technology," IEEE J. Sel. Topics Quantum Electron., Invited Paper, vol. 25, no. 5, Sep. 2019, Art. no. 8200611.

- ➤ [5] M. Rakowski et al., "45nm CMOS silicon photonics monolithic technology (45CLO) for next-generation, low power and high speed optical interconnects," in Proc. Opt. Fiber Commun. (OFC) Conf. Exhibi., T3H.3, 2020.

- ➤ [6] Y. Bian et al., "Towards low-loss monolithic silicon and nitride photonic building blocks in state-of-the-art 300mm CMOS foundry," in Proc. Frontiers Opt. (FiO), pp. paper FW5D. 2, Sep. 2020.

- [7] T. Letavic et. al., "Monolithic Silicon Photonics," Proceedings of BCICTS, 2a.1, Invited Talk, 2023.

- ➤ [8] T. Hirokawa, et al., "Latest Progress and Challenges in 300mm Monolithic Silicon Photonics Manufacturing," in Proc. Opt. Fiber Commun. (OFC) Conf. Exhibi., Th3H.2, Invited Talk, 2024.

- ➤ [9] Y. Bian et al., "300-mm monolithic CMOS silicon photonics foundry technology," Conference on Lasers and Electro-Optics (CLEO), ATu3H.1, Invited Talk, 2024.

- ➤ [10] Y. Bian et al., "Monolithically integrated highperformance Ge-on-Si PIN photodetectors with nearly 60 GHz EO bandwidth, 0.95 A/W responsivity, <30 nA dark current and -36 dB optical return loss enabled by Ge shape optimization," in Proc. Opt. Fiber Commun. (OFC) Conf. Exhibi., Th3E.6, 2025.

# The race to revolutionise silicon photonics with seamless III-V integration

Growing III-V nano-ridge lasers directly on silicon sidesteps the complexities of existing integration methods and paves the way for scalable, cost-efficient photonic integrated circuit production

#### BY BERNARDETTE KUNERT AND JORIS VAN CAMPENHOUT FROM IMEC

IN TODAY'S data-driven world, the demand for faster and more efficient data computation and transmission is growing at an unprecedented pace. On top of the everyday expectation of instant access to high-resolution images, seamless video streaming, and immersive augmented reality experiences, the rapid expansion of Al and machine learning introduces even greater challenges. These technologies rely on massive volumes of machine-to-machine data exchange, further amplifying the need for high-speed, low-latency communication.

To keep up with these demands, optical data transmission must extend beyond traditional long-haul networks, moving closer to the chip level. This has implications for fibre-to-the-x deployments and chip-to-chip optical

interconnects, in which ultra-fast, low-power data transfer is becoming increasingly critical. As data volumes continue to surge, innovative solutions to optimise transmission efficiency are paramount. A particular focus is reducing power consumption per transmitted bit to ensure computing infrastructure is both scalable and sustainable.

One key technology in this transformation is silicon photonics, which leverages the well-established CMOS fabrication process to enable large-scale production of optical systems.

However, a longstanding barrier to the full-scale deployment of silicon photonic integrated circuits (PICs) is that they lack one critical element: the light source.

Due to its inherent material limitations, silicon cannot efficiently emit light. The industry has so far filled this gap by using III-V compound semiconductors – materials prized for their exceptional optoelectronic properties. But integrating these crystalline materials into silicon photonics has proven to be a formidable engineering challenge.

For this reason, most datacom products currently rely on III-V light sources that are separately processed on native III-V substrates and later attached to silicon photonic chips using micromounted laser packages or high-precision flip-chip assembly techniques. While these hybrid integration approaches are effective, they are also costly and tricky to scale, making PIC devices an expensive, low-volume solution.

To address this, the industry is exploring alternative integration methods. For example, micro-transfer printing, a back-end-of-line technique, involves the parallel transfer of prefabricated III-V components onto silicon photonic wafers, significantly improving throughput. Another heterogeneous integration approach employs dieto-wafer bonding of unprocessed III-V device chips onto silicon photonic wafers, followed by III-V device patterning and CMOS-based back-endof-line metal interconnect formation.

The latter method has gained commercial traction and is now available in at least two commercial manufacturing lines. Yet its dependence on complex bonding techniques and expensive III-V substrates remains a bottleneck. Additionally, the substrates are discarded as waste during the manufacturing process, raising concerns about health, safety, and environmental sustainability.

The ultimate goal is the direct monolithic growth of III-V materials on silicon wafers, which would eliminate the need for external III-V substrates and intricate assembly processes. However, silicon and III-V materials have significant differences in their lattice structures, leading to strain in the III-V layers during this monolithic growth. When this strain releases, it leads to defects such as misfit and threading dislocations forming in the III-V film

during deposition. These crystal defects do not just appear at the interface with silicon, but also penetrate the entire device stack, degrading its performance and rendering it commercially unusable.

#### Nano-ridge engineering

For decades, researchers have worked to control the inevitable strain release and block the propagation of dislocation defects through the device stack to the active layers. Some of the techniques explored include growing very thick transition buffers between the silicon and III-V, employing annealing treatments to fix some of the defects, and adding strained superlattice layers to control and isolate defects, accommodating them while limiting their wider propagation. However, these approaches have met with limited success.

A game-changing development emerged with the successful demonstration of InAs quantum dot lasers monolithically grown on silicon. These zero-dimensional nanostructures confine charge carriers, the electrons and holes, more tightly than the more common quantum wells, in which carriers can move in two dimensions. Electrons and holes in quantum dots are therefore less likely to encounter defects, meaning that quantum-dot structures exhibit greater defect tolerance than traditional lasers based on multi-quantum well gain regions.

Thanks to these properties, quantumdot lasers have achieved reliability levels that make them a promising technology for future PIC applications.

One fabrication method that has driven recent advancements in monolithic growth and in integrated photonics more broadly, is selective-area growth (SAG). This technique allows the deposition of III-V material exclusively within predefined silicon oxide patterns, minimising the need for extensive material removal during fabrication, and making the process more efficient than conventional two-dimensional growth. SAG can also leverage aspect ratio trapping (ART), which involves creating deep features that can trap relaxation defects and suppress their propagation through the device. Since only selected regions of the silicon substrate are overgrown, rather than the whole surface, this approach also reduces strain and mitigates common challenges, including crack formation and silicon wafer warpage.

Yet, despite these advantages, SAG based on ART has a drawback; the narrow deposition patterns that are critical for effective defect reduction also limit the amount of III-V material that can be integrated. This constraint restricts the range of devices that can be realised.

Enter nano-ridge engineering (NRE), a cutting-edge integration approach

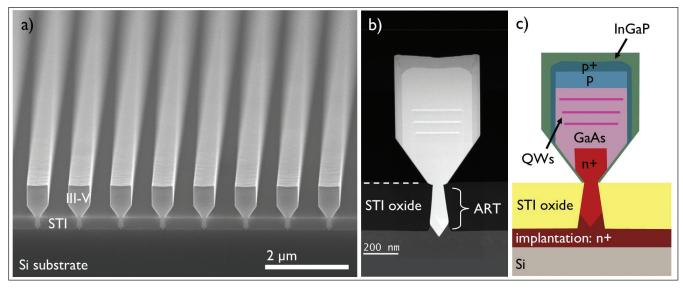

> Figure 1. (a) Scanning electron microscope image of a III-V nano-ridge array grown by MOCVD on a 300 mm patterned silicon dioxide/silicon wafer. The oxide pattern was fabricated by applying a shallow trench isolation (STI) process. (b) High-angle annular dark-field scanning transmission electron microscope image of a III-V nano-ridge laser in cross-section highlighting the different III-V material systems. (c) Schematic of the nano-ridge device stack (QW: quantum well; n\*: highly n-doped region; p: *p*-doped region; p\*: highly *p*-doped region).

pioneered by imec. By refining SAG with MOCVD – the preferred deposition technique to achieve selectivity – and enhancing ART through the use of very narrow, elongated trenches, NRE enables efficient defect suppression while significantly increasing the volume of usable III-V material. This is achieved through continuous growth beyond the trench pattern and carefully controlled nano-ridge shape engineering.

This breakthrough not only expands the design possibilities for III-V-based devices, but also redefines their functionality. The nano-ridge itself can serve as a waveguide in optoelectronic components, such as light-emitting diodes, lasers, modulators, and photodetectors. Additionally, when multiple nano-ridges are contacted in parallel, they can provide sufficient current to power a heterojunction bipolar transistor — a type of transistor that is often used as a power amplifier in RF communications.

Imec's recent milestone – the demonstration of nano-ridge lasers fully processed on 300 mm silicon in a CMOS prototyping line – marks a major step toward scalable, cost-efficient, and environmentally sustainable integration of high-quality III-V devices on silicon.

#### Fabrication challenges

To make this vision a reality, imec's researchers had to overcome three major hurdles. The first challenge was ensuring defect-free nano-ridge growth on 300 mm silicon substrates. ART has been proven effective in reducing misfit defects across various material systems, particularly for GaAs inside narrow trenches. However, for this approach to work, complete strain relaxation must occur within these trenches before uniform nano-ridge growth can extend beyond them. To achieve this, the imec team optimised the MOCVD conditions to facilitate efficient strain release at the III-V/silicon interface and gliding of the threading dislocation inside the trench.

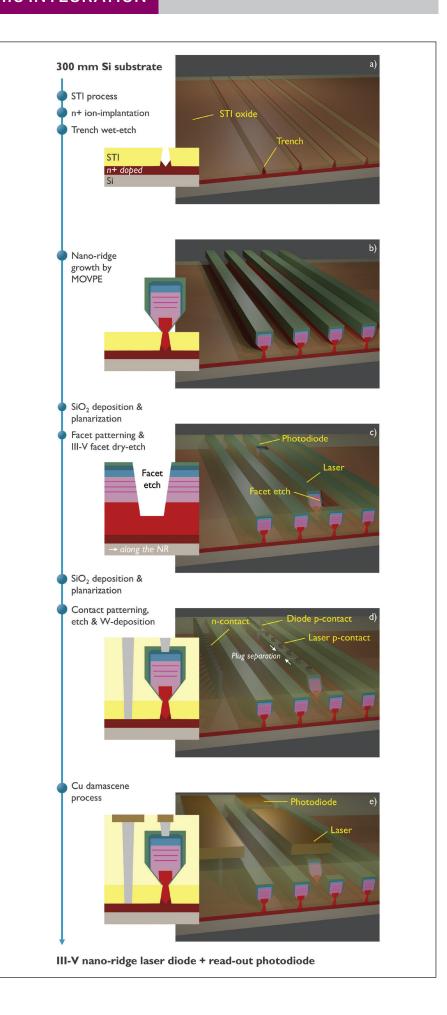

> Figure 2. Simplified schematic of the 300 mm process flow executed in imec's CMOS prototyping line (W: tungsten; Cu: copper). For more details see Y. D. Konick et al. Nature 637 63 (2025)

Once a uniform *n*-doped GaAs baseridge was established, we grew an InGaAs/GaAs multi-quantum well stack to serve as the laser's optical gain medium, followed by a *p*-doped GaAs contact layer. We then capped the final nano-ridge waveguide with an InGaP layer to enhance carrier confinement and to reduce carrier losses at the III-V surface (see Figure 1).

Measurements of the unprocessed nano-ridges (using cathodoluminescence techniques) confirmed an impressively low density of misfit defects – fewer than 6 x 10<sup>4</sup> per cm<sup>2</sup> – in the nano-ridge waveguide. This is a remarkable achievement for such a thin III-V stack.

The second challenge was designing a low-loss contact approach. It was relatively straightforward to perform electron injection via a silicon layer implanted with  $n^+$  ions and the n-doped GaAs inside the trench. However, establishing a robust p-contact on top of the nano-ridge proved more difficult. Using a continuous metal stripe on top of the nano-ridge would have led to excessive optical losses. Instead, we distributed isolated p-plugs along the nano-ridge.

To enable efficient hole injection, these metal plugs were selectively punched through the InGaP layer to reach the *p*-doped GaAs. This periodic *p*-contact design introduced a unique beating-mode formation, supporting discrete waveguide modes with minimised overlap with the metal plug array – a phenomenon that also supported single-mode laser operation. To create the Fabry-Pérot laser cavity, we etched facets into the nano-ridge using a dryetch process.

Finally, integrating and processing III-V materials within a CMOS prototyping line presented an additional set of challenges. Most semiconductor manufacturing tools are not designed to handle III-V materials, or even tolerate the risk of contamination from III-V traces on 300 mm silicon wafers. Furthermore, we had to develop many of the necessary fabrication processes from scratch. To do this, we leveraged imec's extensive expertise in III-V material processing, establishing a controlled manufacturing environment tailored to accommodate these nonstandard CMOS materials.

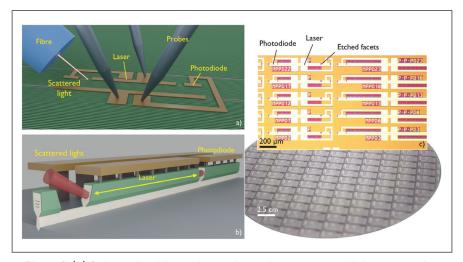

➤ Figure 3.(a) Schematic of the wafer-scale readout test setup: light scattered upwards from the left facet can be collected by a multimode fibre. The three electrical probes drive the nano-ridge laser and photodiode.(b) Schematic (ignoring the oxide) of the nano-ridge cavity formed by two etched facets with an inline photodiode collecting light emitted from the right laser facet, while the light from the left facet is scattered.(c) An optical top-view image of processed devices. A photo of a completely processed 300 mm wafer is shown in the background.

In light of the inherent uncertainties associated with novel sequential process steps and device operability, we devised a mask layout that incorporated a diverse set of physical device parameters. This included variations in laser cavity lengths, pattern trench widths, and *p*-plug separations to systematically assess their impact on device functionality and increase the probability of a successful demonstration.

To enable rapid, wafer-scale characterisation of these nano-ridge laser devices, we introduced an innovative approach: integrating a nano-ridge photodetector in line with the laser. This coupled device layout provides an elegant and efficient method for obtaining wafer-scale performance statistics, ensuring a comprehensive evaluation of device operation across the wafer. Further details on the 300 mm process flow and measurement configuration are provided in Figures 2 and 3.

#### Nano-ridge lasers

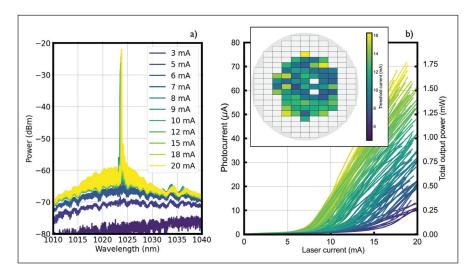

Leveraging the wafer-scale fabrication, we put thousands of GaAs nanoridge devices – including lasers, photodetectors, and test structures – to readout test, as shown in Figure 3. The results were highly promising: over 300 functional nano-ridge lasers exhibited emission at approximately 1025

nm at room temperature, as evidenced by a clear threshold behaviour in the photodiode current (see Figure 4).

This milestone is particularly noteworthy considering the challenges of pioneering a completely new 300 mm process flow. Risks such as short circuits, imperfect facet quality, and high contact resistivity could easily have hindered performance. Instead, these findings mark a major step forward, proving that nano-ridge lasers can be reliably fabricated at scale, and bringing III-V integration on silicon closer to real-world applications.

To validate these findings, we conducted additional measurements, including wafer-scale measurements detecting radiated laser light from the top of the wafer, as well as die-level analysis, for example of the emission spectra from cleaved facets of diced wafers. These tests confirmed the laser operation, revealing a threshold current as low as 5 mA, a slope efficiency of up to 0.5 W A<sup>-1</sup>, and a maximum total output power of 1.75 mW. These are encouraging values, given the nanoridge's sub-micrometre cross-section. Furthermore, the periodic grating structure formed by the *p*-contact plugs played a crucial role in stabilising single-mode operation in the Fabry-Pérot resonator, achieving a side-mode suppression ratio exceeding 30 dB.

> Figure 4. (a) Optical output spectra collected at a cleaved facet of a 1.4 mm-long laser cavity with an optical fibre for different drive currents. (b) Photodiode current (left) and related total output power (right) versus the laser drive current of a 2 mm-long device. The inset shows a wafer map of the die distribution containing the operational 2 mm-long laser devices. The colour code indicates the corresponding threshold current.

A particularly notable observation is that lasing occurred only in devices where the p-plug separation exceeded 3  $\mu$ m, highlighting that, if the plug density is too high, the absorption losses in the top metal contacts have a significant impact on the laser threshold.

However, increasing the *p*-plug separation introduced a device performance trade-off as it also led to higher current densities at each contact point. While initial reliability tests showed continuous-wave lasing for over 500 hours, further investigation revealed that the high current density at the *p*-plugs induced localised defects, ultimately leading to device failure.

A more promising observation was that, aside from the region surrounding the p-plugs, the rest of the nano-ridge waveguide retained high crystalline quality, with no additional misfit defects forming. This finding suggests that further optimisation of the contact design could significantly enhance the long-term reliability of these nano-ridge lasers, paving the way for silicon photonics applications.

#### Future focus

To the best of our knowledge, this demonstration marks the first successful realisation of a fully processed III-V nano-ridge laser on a 300 mm silicon wafer. By enabling monolithic III-V

deposition directly onto silicon, this approach eliminates the dependence on III-V substrates and complex bonding techniques, leveraging the advanced fabrication capabilities of a CMOS pilot line. This breakthrough is pivotal in facilitating high-volume scalability, improved yield, and reduced production costs – key factors for the widespread adoption of silicon photonics. However, while this achievement represents a major milestone, the nano-ridge engineering technology remains in its early development phase.

This work is part of a broader pathfinding mission at imec to advance III-V integration processes towards higher technological maturity. In the near term, the focus remains on hybrid approaches, such as flip-chip assembly and transfer printing. In the mid-term, we expect heterogeneous methods based on die-bonding techniques to

further enhance integration efficiency. Ultimately, the long-term goal is to achieve direct epitaxial growth of III-V materials on silicon – a concept that this work demonstrates is possible.

Current R&D efforts in our NRE technology focus on refining the contact approach to mitigate localised high-current injection spots, thereby extending device lifetime. Additionally, we are investigating alternative GaAsbased optical gain media to redshift the laser emission wavelength, expanding the potential range of applications.

Another promising avenue involves leveraging the waveguide nature of III-V nano-ridges to enable efficient coupling into silicon photonic waveguides. This would open up the possibility of developing external cavity lasers, further enhancing the versatility of this platform.

Beyond device-level innovations, significant work remains to optimise fabrication processes and improve throughput. Achieving full-scale commercialisation will require close collaboration with semiconductor tool suppliers to improve processing techniques and ensure compatibility with existing CMOS manufacturing infrastructure. Encouragingly, ongoing global efforts in heterogeneous integration, combined with the growing importance of III-V process technologies in CMOS environments, are set to drive continuous improvements in tool capabilities and manufacturing efficiency.

By addressing these challenges, imec aims to accelerate the development of III-V-on-silicon lasers, bringing them closer to large-scale deployment in future-generation silicon photonics applications.

#### **FURTHER READING**

- ➤ Y. D. Konick *et al.* "GaAs nano-ridge laser diodes fully fabricated in a 300-mm CMOS pilot line" Nature **637** 63 (2025)

- C. I. Ozdemir et al. "Low Dark Current and High Responsivity 1020nm InGaAs/GaAs Nano-Ridge Waveguide Photodetector Monolithically Integrated on a 300-mm Si Wafer" J. Light. Technol. 39 5263 (2021)

- Y. Shi et al. "Novel adiabatic coupler for III-V nano-ridge laser grown on a Si photonics platform" Opt. Express 27 37781 (2019)

- P.-Y. Hsieh et al. "Degradation Mechanisms of Monolithic GaAs-on-Si Nano-Ridge Quantum Well Lasers" J. Light Tech. 43 5811 (2025)

## Luceda Photonics Design Platform

## Luceda IPKISS 🌘

First-time-right photonic IC design software

Automate and integrate all aspects of your photonic design flow in one tool, using one standard language.

## **Luceda Design Kits**

Gain access to a wide range of PDKs, ADKs, and TDKs. Design and tape out to your foundry of choice.

## **Luceda Modules**

Design advanced photonic components and complement Luceda IPKISS with specialized modules.

Luceda IP Luceda AWG Manager Designer

**Link for Ansys** Lumerical

Link for Tidy3D

**Link for Dassault Systèmes** Simulia

Link for Siemens **EDA**

Link for **Check Mate** DRC

DEVICE

SIMULATION

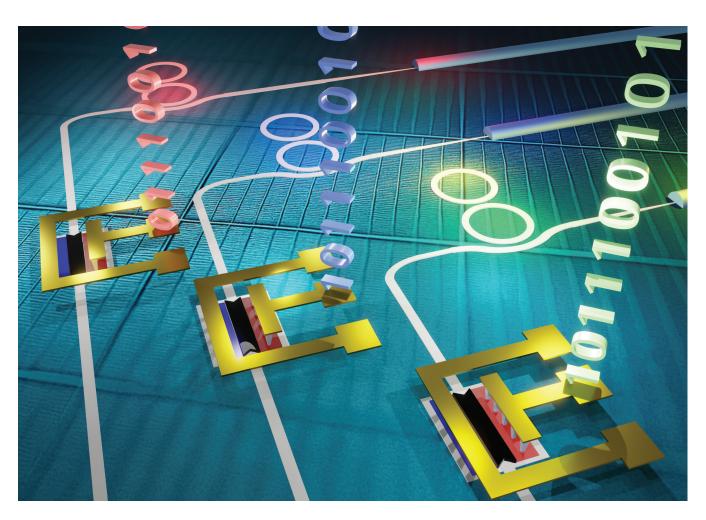

## Giving AI room to grow with ultra-compact silicon modulators

Scaling Al infrastructure requires ultra-fast communications across distant processors, but conventional silicon modulators are bulky and power-hungry. A new, ultra-compact silicon microring modulator has demonstrated record-breaking transmission speeds at low power, offering a solution that could give Al space to grow.

## BY ALIREZA GERAVAND, LESLIE A. RUSCH AND WEI SHI, CENTRE FOR OPTICS, PHOTONICS AND LASERS (COPL), UNIVERSITÉ LAVAL, CANADA

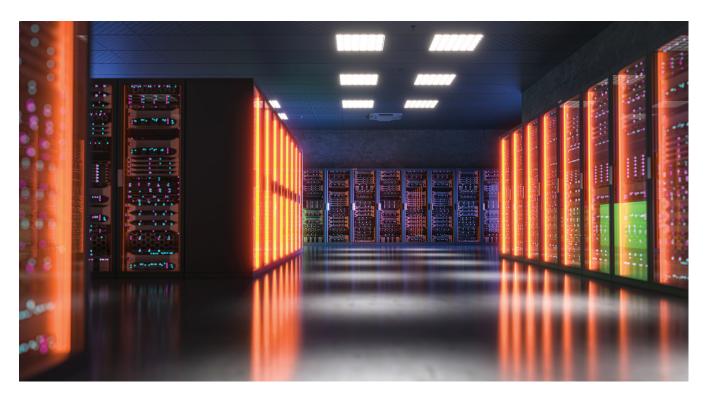

Al IS fundamentally transforming every sector, from healthcare and finance to automotive and consumer technology. This revolution is being powered by enormous computing clusters — thousands of computing nodes spread across multi-acre campuses—and as Al models grow in size, they require exponentially more processors working in parallel. OpenAl's GPT-4, for instance, used 25,000 interconnected computing nodes over 90 days for training, but next-generation clusters are projected to involve 300,000 or even a million nodes in the near future.

To operate at this scale, massive volumes of data must be exchanged rapidly and efficiently, both between compute nodes within a cluster and between clusters. Optical interconnects

form the backbone of these systems, providing high-speed, low-loss data transmission through optical fibres.

This relies on the efficient conversion of electrical data from processors into light—a process that is enabled by silicon photonics technology, which also benefits from mature manufacturing capabilities.

However, the unprecedented communication demands between Al processors are creating a performance bottleneck – one that risks slowing the pace of Al advancement. Today's optical links in Al clusters often rely on simple intensity modulation and detection – essentially turning a light on and off to send data. While costeffective, this approach faces increasing

challenges in meeting Al's soaring requirements for both speed and reach. Next-generation silicon photonics-based technologies must deliver far higher data capacity and longer reach, while scaling seamlessly as Al clusters expand. The solution is coherent optics, a technology that already dominates long-distance applications. Leveraging the coherent properties of light, we can go beyond the simple on/off flashlight approach and instead modulate both the amplitude and phase of light.

This advanced modulation dramatically increases transmission capacity, which explains its widespread adoption in long-haul networks. It also offers greater robustness to link impairments and can reach longer distances at the same signal power.

However, conventional coherent optics has so far been bulky, power-hungry, and challenging to integrate with copackaged optics (CPO). The primary culprit is the Mach-Zehnder modulator, the most commonly used modulator in coherent systems.

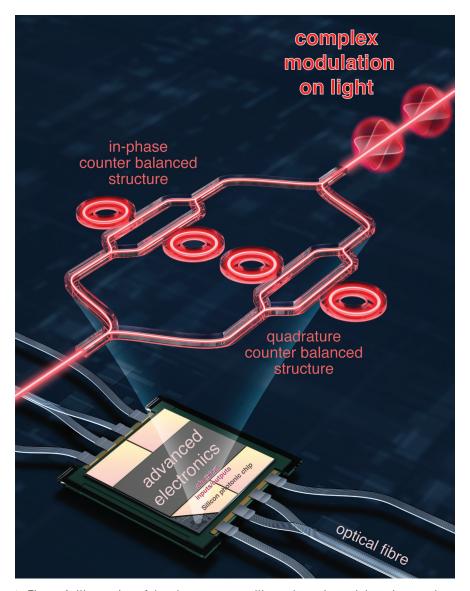

To achieve truly massive data rates, all available wavelengths must be exploited through wavelength-division multiplexing (WDM). While Mach-Zehnder modulators can handle multiple wavelengths, they require many additional components, adding complexity, size, and cost. To overcome these limitations, we have developed a transmitter for coherent optical interconnects, featuring ultra-compact, energy-efficient coherent modulators integrated directly on silicon chips.

## Rethinking coherent silicon optics

Central to our innovation is the microring modulator (MRM), a tiny structure etched onto silicon chips. Although MRMs are known for their compact size and low power operation, they have historically been considered unsuitable for coherent data transmission, because they can introduce an unwanted frequency modulation (or "chirp") that gets in the way of advanced modulation. This effect also complicates modulator biasing and operation.

Previous studies, including research from Bell Labs, have proposed mitigating the chirp through a mirrored structure in which a pair of MRMs operate in counterbalance. While promising, this approach had, until now, never been demonstrated in a complete coherent transmitter employing advanced modulation formats at high speeds.

However, the rapid growth of AI has intensified the race to deploy MRMs in the demanding datacentre environment.

To develop a better understanding of MRMs, we conducted an extensive study of their dynamics [1] to determine how to fully exploit their potential. Building on this, we have now proposed an MRM-based transmitter capable of performing complex modulation. As illustrated in Figure 1, our design nests two counter-balanced MRM structures within a higher-level Mach-Zehnder interferometer configuration. Complex

modulation encodes data in two dimensions – in phase and quadrature – with a dedicated counter-balanced MRM structure handling each data stream.