**ISSUE | 2025**

AN ANGEL BUSINESS COMMUNICATIONS PUBLICATION

POWERELECTRONICSWORLD.NET

# REWIRING THE ROAD

## RIXTRON

## **THE NEW G10 SERIES**

#### Your Productivity Solution for All Advanced Epitaxy Materials

#### G10-GaN

- 8x150mm (6") or 5x200mm (8")

- 1<sup>st</sup> fully automated compact GaN MOCVD cluster designed 100% for Si Power fabs

- Novel hardware solution for unmatched barrier uniformities and device yields

#### End Markets/Products:

Power Electronics & Wireless communication

BIXTRON

#### G10-SiC

- > 9x150mm (6") or 6x200mm (8")

- New hardware & process surpassing Single Wafer Reactor uniformities

- +50% productivity per fab area with large batch technology & small footprint

End Markets/Products: EV inverters & charging infrastructure

#### G10-AsP

- ▶ 8x150mm (6") or 5x200mm (8")

- 1<sup>st</sup> fully automated AsP MOCVD system enabling 10x lower defect density

- Unmatched wavelength uniformity on all wafer sizes

#### End Markets/Products:

Micro LED, Optical Data communication, 3D-sensing & LiDAR

# VIEWPOINT

BY PHIL ALSOP EDITOR

## A powerful year ahead

A SCAN of the news stories in this issue of PEW, alongside the many more to be found on the magazine website, provides any number of reasons to be optimistic for the power electronics sector, at a time when it is perhaps difficult to find too many reasons to be cheerful, amidst the ongoing global geopolitical uncertainties and the apparent growing momentum behind climate change push back (at least by the finance sector which bankrolls so much of the necessary investment activity).

'GaN adoption at tipping point' – Infineon believes that 2025 is the year when GaN will be a game-changing material across consumer, mobility, residential solar, telecommunication, and AI data centre industries, enabling more efficient performance, smaller size, lighter weight, and lower overall cost - substantially driving the market for GaN-based power semiconductors. Few will disagree with such an assessment – the more so as several governments have announced major AI-focused initiatives, which will require plenty of new data centres. I guess there is a slight note of caution while the 'mysteries' of the DeepSeek model are yet to be fully understood, but the direction of travel for digital transformation, with whatever level of AI-fuelled innovation, is clear for all to see.

'Medium-voltage SiC-based system developed at Fraunhofer ISE enables peak loads of several megawatts' – As the headline suggests, Fraunhofer ISE and partners have developed a SiC-based medium voltage system technology for fast charging stations that will enable peak loads of several megawatts in the future. The technology, which uses efficient SiC semiconductors and higher voltages, leads to lower material use and lower costs for fast charging stations.

At the same time, the system is very efficient and can be flexibly applied to charging stations of different sizes and different vehicle types. I have written previously about the 'chicken and egg' situation of what needs to come first – widespread EV adoption or the charging infrastructure to support EVs – and developments such as this one can only help to speed up what maybe will end up being the lockstep expansion of both EV ownership and charging station infrastructure expansion. Again, one slight note of caution – the US EV market could best be described as in something of a hiatus right now. Elsewhere, the EV commitment seems to be holding firm, if at varying rates of progress.

Perhaps the most encouraging of the news stories, alongside the innovation story above, are those which demonstrate the vibrant state of research and development work in the power electronics sector: 'EU project to develop high voltage DC WBG tech', 'UK team leads diamond-FET breakthrough', 'Transforming the current density of AIN Schottky barrier diodes', 'Turbocharging the GaN MOSFET with a HfO<sub>2</sub> gate', 'Boosting AIN-on-AIN Schottky barrier diode performance', 'Improving annealing conditions for GaN MOSFETs', 'Na flux method improves GaN device performance', 'German start-up secures finance for SiC processing tech'.

There's no doubting the huge commitment to power electronics innovation across the globe right now. However successful the attempts to 'derail' the climate change agenda, there's no doubting that energy resources, power infrastructure and power consumption will continue to remain a critical focus across all industry sectors, as well as in the domestic market. If there is one silver lining (and maybe the only one) to take out of the Ukraine/Russia conflict, it is the attention it has served to focus on all things energy and power related, with efficiency right at the top of the agenda. And the ongoing quest for more and more efficiency make sense for so many business reasons, whatever one's view on net zero.

## CONTENTS

#### VOL. 28 ISSUE I 2025

## 14 Nexperia: Expanding GaN and SiC operations

Re-fitting its Hamburg fab is laying the foundations for Nexperia to hike its production of GaN and SiC transistors and diodes on 200 mm lines

#### 16 Power GaN: The 300 mm milestone

Migrating the manufacture of GaN power devices to 300 mm lines will boost yield, improve metrology and trim costs

## 18 Putting India on the global GaN stage

University spin-out Agnit has just secured funding to grow its GaN portfolio, a combination of epiwafers and power and RF devices

## 20 Clas-SiC expands technology in its stride

Not content with opening the world's first SiC foundry that partners with power device designers, Clas-SiC Wafer Fab is evolving and adapting to grow its success

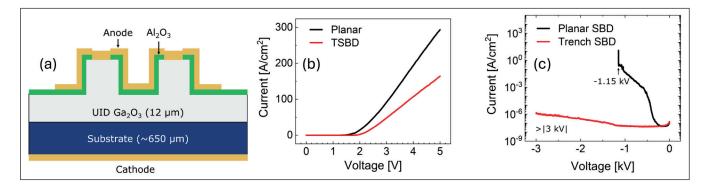

## 24 Enhancing β-Ga<sub>2</sub>O<sub>3</sub> with hetero-integration

Thanks to the introduction of a far higher thermal conductivity and p-type doping, better devices are realised when pairing  $\beta$ -Ga<sub>2</sub>O<sub>3</sub> with SiC or diamond

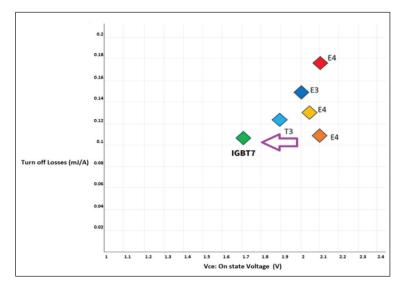

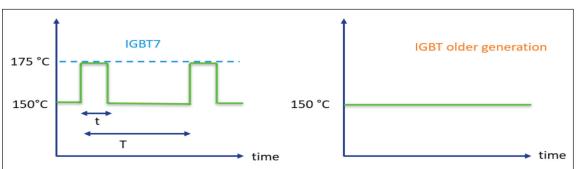

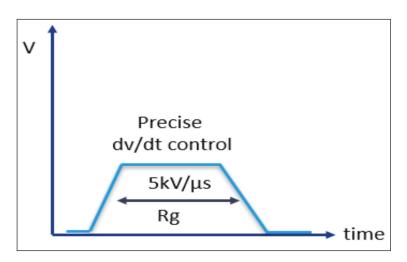

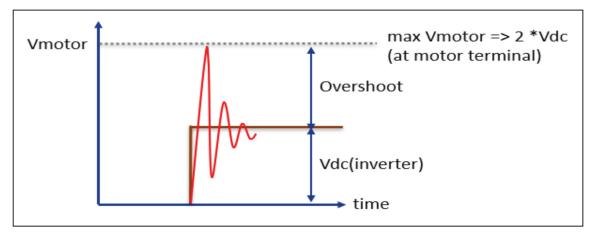

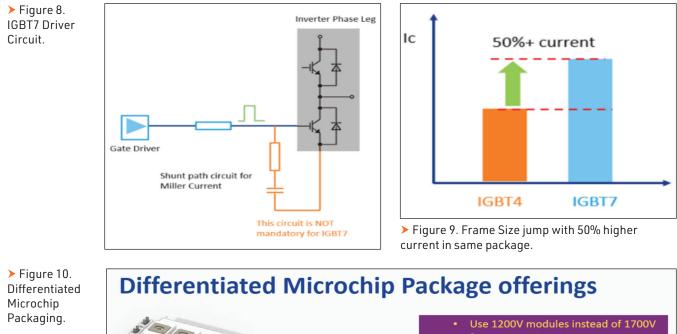

#### 30 Next-generation IGBT7 technology: versatile and simplified power management

The new IGBT7 technology has succinct differentiation in device characteristics such as lower forward voltage, higher current ratings, 175°C over-load capacity, improved dv/dt control and enhanced freewheeling diode

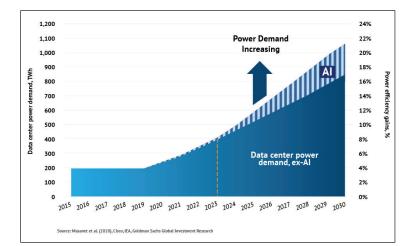

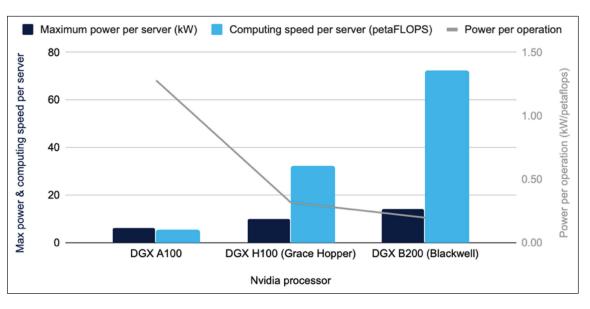

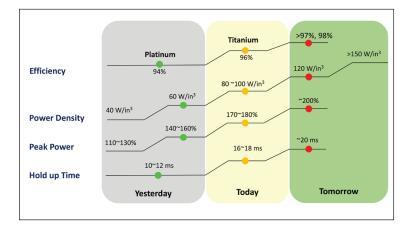

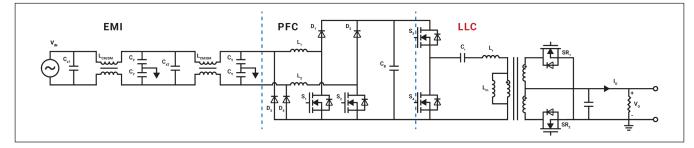

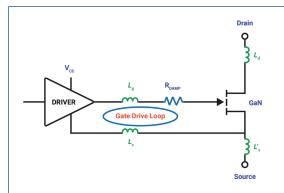

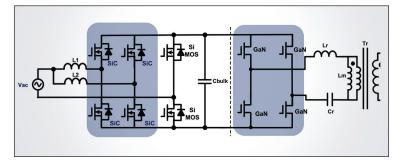

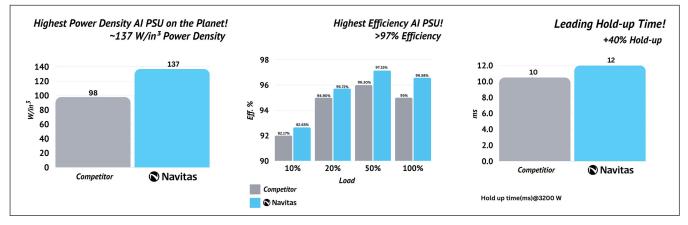

#### 36 Achieving next generation power density and efficiency for AI and hyperscale data centre PSUs

This article examines the state of the industry, the challenges it faces and outlines advances in PSUs that will take the industry to 8 kW and above, that are essential to support the next phase of generative AI

Editor Phil Alsop phil.alsop@angelbc.com +44(0)7786084559

News Editor Christine Evans-Pughe christine.evans-pughe@angelbc.com

Contributing Technical Editor Richard Stevenson richard.stevenson@angelbc.com +44 (0)1923 690215

Sales & Marketing Manager Shehzad Munshi shehzad.munshi@angelbc.com +44 (0)1923 690215

Design & Production Manager Mitch Gaynor mitch.gaynor@angelbc.com +44 (0)1923 690214 Senior Event and Media Executive for Power Electronics International James Cheriton james.cheriton@angelbc.com +44 (0)2476 718970

Publisher Jackie Cannon jackie.cannon@angelbc.com +44 (0)1923 690205

CEO Sukhi Bhadal sukhi.bhadal@angelbc.com +44 (0)2476 718970

CTO Scott Adams scott.adams@angelbc.com +44 (0)2476 718970

#### NEWS

- **06** SiC patenting strong in Q4 2024, says KnowMade

- 07 SiC MOSFETs: Understanding the benefits of plasma nitridation

- 08 Research initiative on SiN ceramic substrates

- **10** Researchers develop tech for future fast-charging stations

- 11 Mitsubishi joins Horizon Europe's FLAGCHIP project

- 12 EU project to develop high voltage DC WBG tech

PEW Magazine is published six times a year on a controlled circulation basis. Non-qualifying individuals can subscribe at: £105.00/e158 pa (UK & Europe), £138.00 pa (air mail), \$198 pa (USA). Cover price £4.50. All information herein is believed to be correct at time of going to press. The publisher does not accept responsibility for any errors and omissions. The views expressed in this publication are not necessarily those of the publisher.

Every effort has been made to obtain copyright permission for the material contained in this publication. Angel Business Communications Ltd will be happy to acknowledge any copyright oversights in a subsequent issue of the publication. Angel Business Communications Ltd @ Copyright 2024. All rights reserved. Contents may not be reproduced in whole or part without the written consent of the publishers. The paper used within this magazine is produced by chain of custody certified manufacturers, guaranteeing sustainable sourcing.© Copyright 2024.

We strive for accuracy in all we publish; readers and contributors are encouraged to contact us if they recognise an error or omission. Once a magazine edition is published [online, in print or both], we do not update previously published articles to align old company names, branding, marketing efforts, taglines, mission statements or other promotional verblage, images, or logos to newly created or updated names, images, typographic renderings, logos (or similar) when such references/images were accurately stated, rendered or displayed at the time of the original publication.

When companies change their names or the images/text used to represent the company, we invite organizations to provide Angel Business Communications with a news release detailing their new business objectives and/or other changes that could impact how customers/prospects might recognise the company, contact the organisation, or engage with them for future commercial enterprise.

Published by Angel Business Communications Ltd 6 Bow Court, Fletchworth Gate, Burnsall Road, Coventry CV5 6SP, UK. T: +44 (0)2476 718 970

E: info@angelbc.com W: angelbc.com

#### **INDUSTRY NEWS**

## SiC patenting strong in Q4 2024, says KnowMade

KnowMade's SiC Patent Monitor showed 900 new patent families and 400 newly granted patents

DURING Q4 2024, KnowMade's SiC Patent Monitor showed 900 new patent families and 400 newly granted patents. This period also saw over 100 patents expire or be abandoned and involved seven notable patent transfers.

There was no new IP litigation in the US or patent opposition in Europe. And the sector is "abuzz with ten notable patent collaborations and an influx of over 25 IP newcomers entering the field", according to KnowMade.

Innovation within the SiC industry, particularly in Bulk and bare wafers, has led to the emergence of better substrates and more reliable power devices. During Q4 2024, for example, NGK Insulators disclosed a composite SiC substrate with a biaxially oriented SiC layer that helps to reduce warpage.

Another player, SICC, published innovations improving 3D stress distribution and reducing internal stress in large diameter SiC wafers (> 150 mm). Sumitomo Electric continues to lead IP activities in epitaxial substrates, according to KnowMade, with four new inventions disclosed during Q4. One of these relates to issues in the epitaxial reactor, such as the presence of SiC particles on the susceptor, causing recesses in the rear surface of SiC epitaxial wafers.

Another invention focuses on the reduction of certain defects (bump, pit, carrot, triangular defect, downfall)

that can be imaged using a confocal scanning device.

For devices, there has been patenting activity from several Chinese automotive players, such as NIO and FAW. NIO stands out this quarter with a European patent publication related to SiC trench MOSFET. Other players from the automotive supply chain have been actively filing patents during the quarter such as Bosch (e.g., to improve the short-circuit strength of SiC FET) and Nexperia (e.g., to improve on-resistance and surge performance of SiC Schottky diodes).

In terms of modules and packaging, Onsemi has disclosed electroless plating methods and systems suitable for SiC devices, and Mitsubishi Electric has two new inventions, of which one

For circuits and application, ZF has developed a method of driving parallel-connected SiC-MOSFETs and Si-IGBTs based on the rapid detection of the current load of the active (switched-on) device. Furthermore, a collaboration between BMW with CSA Catapult and the University of Warwick in the UK has led to a new patent publication describing a monitoring device to measure temperature or current in SiC devices to suppress heat occurring in a SiC MOSFET connected in parallel with a Si IGBT, without providing a temperature detection circuit and a current detection circuit. GaN specialist Navitas Semiconductor is also looking to strengthen its patent portfolio for power SiC, with a new invention providing balanced current flow in SiC power modules.

For circuits and application, ZF has developed a method of driving parallelconnected SiC-MOSFETs and Si-IGBTs based on the rapid detection of the current load of the active (switched-on) device. Furthermore, a collaboration between BMW with CSA Catapult and the University of Warwick in the UK has led to a new patent publication describing a monitoring device to measure temperature or current in SiC devices under high current load even under rough mechanical conditions (e.g., under strong vibrations, in automotive appliances).

KnowMade closely follows SiC patenting, and has noted recently that the number of inventions disclosed in 2023 was more than 50 percent higher than it was in 2021. The number of inventions disclosed by Chinese players increased by about 60 percent between 2021 and 2023.

# SiC MOSFETs: Understanding the benefits of plasma nitridation

Annealing interfaces of SiC and SiO<sub>2</sub> formed by a process based on plasma nitridation reduces interface states and increases immunity to positive gate bias stress

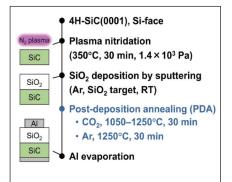

ENGINEERS from Osaka University are offering new insights into the benefits of their novel approach to forming the key interface for SiC MOSFETs. The team has just determined that its approach – involving plasma nitridation of the SiC surface, sputter deposition of  $SiO_2$ , and post-deposition annealing – reduces the interface state density near the conduction band edge by more than an order of magnitude and delivers a substantial increase in immunity to positive gate bias stress.

These valuable findings highlight the benefits of moving away from standard approaches to making SiC MOSFETs, which despite significant commercial success suffer from a high on-resistance and poor reliability, according to the team from Osaka. This team attributes those weaknesses to a high interface state density and nearinterface traps.

The Osaka University researchers say that interface nitridation with NO is widely used to reduce the interface state density and passivate defects. However, this approach is far from perfect: the reduction in the density of interface states is limited, probably due to saturation of nitrogen content at the interface; and there are reliability issues, such as a strong drift in threshold voltage with gate bias stress.

To address these concerns, the engineers from Osaka are pioneering an approach that suppresses nitrogen incorporation into  $SiO_2$  while minimising oxidation of SiC. Their three-step process involves: plasma nitridation of the SiC surface; sputter deposition of  $SiO_2$ ; and post-deposition annealing under CO<sub>2</sub>.

According to the team, one of the benefits of this approach is that SiC is directly nitrided by a high-density

plasma, enabling a high proportion of nitrogen atoms to be incorporated at the SiC surface. Additional merits of their approach include sputter deposition of SiO<sub>2</sub> in a pure argon atmosphere to minimise SiC oxidation, and a post-deposition anneal that reduces the density of defects in the SiO<sub>2</sub> dielectric. The researchers previously established that their process trebled the density of nitrogen atoms incorporated at the SiC side of the interface, lowering the density of interface states to 1 x 1011 eV<sup>-1</sup> cm<sup>-2</sup>. However, they had not investigated the impact of post-deposition annealing on device characteristics.

They have just addressed this issue with a thorough investigation of the roles played by the particular gas employed and the temperature that's adopted for the post-deposition anneal. For this work, they produced SiC metal-oxide-semiconductor capacitors. using n-type SiC (0001) epilayers with a donor density of 1 x 10<sup>16</sup> cm<sup>-3</sup>. Following wet cleaning, they nitrided the surface of SiC for 30 minutes at 350°C with a high-density nitrogen plasma at 1.4 x 10<sup>3</sup> Pa, before sputtering a 30 nm-thick film of SiO<sub>2</sub> in a pure argon atmosphere. The final step involved a post-deposition anneal for 30 minutes under either CO, or argon at a temperature between 1050°C and 1250°C. Comparing capacitancevoltage curves for annealing under  $CO_2$  at different temperatures showed that carrying out this process at 1050°C ensured sufficient electron accumulation. However, this technique led to hysteresis and stretch-out due to interface traps. Both concerns were not found in capacitance-voltage plots for devices with a 1250°C anneal, suggesting a significant reduction in interface traps.

The researchers also observed a negative shift in the capacitancevoltage curve with increasing anneal temperature, indicating the presence of positive fixed charges at the interface. Additional investigations by the team considered the trapped charge density and the energy distributions of interface states. For annealing under CO2, the trapped charge density plumets with increasing annealing temperature. Under argon, the fall in trapped charge density is notably smaller, leading the team to conclude that the reduction in charge density is not simply an annealing effect, and involves a reaction of CO<sub>2</sub> molecules with interface traps.

Studying the energy distribution of the interface state density revealed that this fell with increasing temperature when annealing under CO<sub>2</sub>. Switching to argon led to an insufficient reduction in interface state density, showing that the benefits of the team's process are not just plasma nitridation and minimised oxidation - they also include defect passivation by a CO<sub>2</sub> post-deposition anneal. The team have also carried out stress tests, applying a positive stress bias for up to 2000 s at field strength of 5-8 MV cm-1. This investigation revealed that a higher annealing temperature under CO<sub>2</sub> increases the immunity of the device.

• Reference: H. Fujimoto et al. Appl. Phys. Express 17 116503 (2024)

## Research initiative on SiN ceramic substrates

Japanese partnership to verify methods for evaluating thermal performance of ultra thin power module substrates

THE JAPANESE AIST Group (consisting of National Institute of Advanced Industrial Science and Technology and AIST Solutions) and NGK Insulators have embarked on joint research to validate methods for evaluating thermal diffusivity of SiN ceramic substrates used for power semiconductor components and modules.

SiN ceramic substrates play a pivotal role in Active Metal Brazing (AMB) substrates for heat dissipation in power modules in EV inverters and HEV motor control.

AMB substrates consist of a SiN ceramic substrate and two copper plates. The thinner the substrate and higher its thermal diffusivity, the greater the operational efficiency of the power semiconductor module.

With the increasing adoption of EVs and HEVs, there is rising demand for thinner substrates that feature substantial thermal dissipation performance. However, a lack of definitive methods for evaluating thermal diffusivity of substrates thinner than 0.5mm has given rise to challenges in ensuring consistency of measurement results.

This joint research enlists AIST and its knowledge of evaluation methods along with NGK and its ceramic substrate technologies in efforts to collect data for quantifying the preliminary process,

which affects measurement of thermal diffusivity of substrates. The aim is to verify methods for evaluating substrates that are thinner than 0.5mm, and are not yet defined under existing Japanese Industrial Standards (JIS) in order to bring about standardisation of evaluation methods in this sector.

### GaN adoption at tipping point, says Infineon

IN ITS 2025 predictions, Infineon says GaN will be a game-changing material across consumer, mobility, residential solar, telecommunication, and AI data centre industries, enabling more efficient performance, smaller size, lighter weight, and lower overall cost.

While USB-C chargers and adapters have been the forerunners, GaN is now on its way to reaching tipping points in its adoption in further industries, substantially driving the market for GaN-based power semiconductors, according to Infineon.

"Infineon is committed to driving decarbonisation and digitalisation through innovation based on all semiconductor materials Si, SiC, and GaN," said Johannes Schoiswohl, head of the GaN business line at Infineon. "The relevance of comprehensive power systems will increase with GaN manifesting its role due to its benefits in efficiency, density, and size. Given that cost-parity with silicon is in sight, we will see an increased adoption rate for GaN this year and beyond. Powering AI will be highly depending on GaN. The rapid increase of required computing power and energy demand in AI data centres will drive the need for advanced solutions capable of handling the substantial loads associated with AI servers.

Power supplies that once managed 3.3 kW are now evolving towards 5.5 kW, with projections moving towards 12 kW or more per unit.

By using GaN, AI data centres can improve power density, which directly influences the amount of computational power that can be delivered within a given rack space. While GaN presents clear advantages, hybrid approaches combining GaN with Si and SiC are ideal for meeting the requirements of AI data centres and achieving the best trade-offs between efficiency, power density and system cost.

In the home appliance market, Infineon expects GaN to gain significant traction, driven by the need for higher energy efficiency ratings in applications like

washing machines, dryers, refrigerators and water/heat pumps. In 800 W applications, for example, GaN can enable a two percent efficiency gain, which can help manufacturers achieve the coveted A ratings.

According to Infineon, GaN-based onboard chargers and DC-DC converters in electric vehicles will contribute to a higher charging efficiency, power density, and material sustainability, with a shift towards 20 kW+ systems.

Together with high-end SiC solutions, GaN will also enable more efficient traction inverters for both 400 V and 800 V EV systems, contributing to an increased driving range.

## SiC LinPak boosting the efficiency of highpower applications

Hitachi Energy extends the well-established LinPak family with devices based on SiC technology to deliver the highest current rating. Available at 1700 V and 3300 V, the SiC LinPak offers several benefits, including a massive reduction of switching losses, increased current density in the lowest inductance package of its class.

www.hitachienergy.com/semiconductors

**Hitachi Energy**

#### **INDUSTRY NEWS**

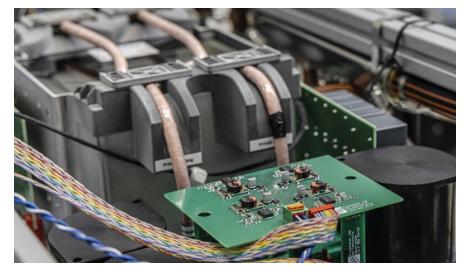

## Researchers develop tech for future fast-charging stations

Medium-voltage SiC-based system developed at Fraunhofer ISE enables peak loads of several megawatts

FRAUNHOFER ISE and partners have developed a SiC-based medium voltage system technology for fast charging stations that will enable peak loads of several megawatts in the future.

The technology, which uses efficient SiC semiconductors and higher voltages, leads to lower material use and lower costs for fast charging stations. At the same time, the system is very efficient and can be flexibly applied to charging stations of different sizes and different vehicle types, according to Fraunhofer ISE.

The system was developed in a project called MS-Tankstelle, to address the need for future charging stations along motorways, in parking lots or at logistics centres to be deliver much more power in a short space of time than they do today.

The average output of a fast-charging system for a car is 150 kW. This rises to 350 kW for buses, vans and small trucks, with higher charging capacities expected in the future. Since electric charging is slower than the refuelling process, around 15 to 25 charging points will be needed in the future

instead of the typical eight gas pumps at filling stations today.

Together these charging points will draw around 1.5 to 3.5 megawatts of power when fast charging in parallel, which means that future fast-charging stations can no longer be supplied via the low-voltage grid. Even if the charging station is underutilized, the power required would exceed 300 kW. Also the power distribution within the charging station or parking lot should not be distributed in the low voltage grid. This would lead to big installation costs and large energy losses in cables, due to the long cable runs of e.g. 100 meters or more for 25 parking spaces, coupled with the high powers. The power electronic system developed in the project with the partners Sumida Components & Modules GmbH, Infineon Technologies AG and AEG Powersolutions GmbH therefore relies on a medium voltage grid that is adapted to a voltage of 1500 VDC using a rectifier.

The higher voltage level enables a higher output at the same current without necessitating the cable cross-section to be increased. The

significantly lower copper consumption that results contributes significantly to environmental protection and resource conservation. The value of 1500 VDC was selected for this unit, as it is the boundary limit of the low voltage standard. Above this value, other standards would apply.

An electrically isolated converter couples the direct current (DC) distribution network to the vehicle battery and controls the fast-charging process. The DC converters, each with an output of 175 kW, are designed so that they can easily be connected in parallel in the system. This modular approach makes it possible to build charging stations with lower power charging points for cars and higher power charging points for trucks.

In contrast to domestic wall boxes. charging stations must be highly compatible for different vehicle types. The concept of a central rectifier and a 1500 V DC distribution. which was developed in the project, is advantageous in that the grid connection components (transformer and rectifier) can be dimensioned and scaled more independently of the charging electronics. In view of the high demand for power electronics and components, like cables and transformers, the material requirements for this system are significantly reduced compared to other current solutions. For an uncomplicated charging process, the charging station should be fully compatible with the CCS1 and CCS2 standards, which are widely established in Europe for vehicle currents up to 500 amperes and voltages up to 1000 volts. In addition, the concept also supports the Megawatt Charging System (MCS) standard. A second converter module is planned to address this. For this variant only a few components need to be adapted.

## Mitsubishi joins Horizon Europe's FLAGCHIP project

Company to develop technology for monitoring SiC power module condition

MITSUBISHI ELECTRIC'S European subsidiary Mitsubishi Electric R&D Centre Europe BV will begin developing a prototype to demonstrate a junctiontemperature estimation technology for SiC power modules, as a partner in the European Union's Horizon Europe FLAGCHIP project.

The technology will measure the condition of SiC-MOSFETs inside the power module, to provide data for accurately estimating module degradation.

FLAGCHIP (Flagship Advanced Solutions for Condition and Health Monitoring in Power Electronics)

involves 11 companies and academic institutions from nine European countries who will develop advanced power modules, condition and health monitoring technologies, and methods for calculating cost efficiency of renewable-energy power-generation systems and reducing associated costs.

The partners will demonstrate windpower and solar-power generation systems using these technologies and methods at test facilities owned by project partners in Norway and France.

Starting in October 2026, the plan is to use the Mitsubishi Electric developed prototype at a test facility in France where direct current (DC) voltage is converted to a specific DC voltage for a wind-power generation system.

#### **INDUSTRY NEWS**

## EU project to develop high voltage DC WBG tech

'MoWiLife' project to produce SiC and ultra wide bandgap devices for DC wind and solar energy applications

A NEW three-year multi-partner Horizon Europe funded project, called MoWiLife (Condition Monitoring and Wide Bandgap Power Electronics - Leading Innovations for the European Energy Sector), will be working on technology for DC wind and solar energy applications.

This includes the development of a 2.3 kV SiC MOSFET with temperature sensing and self-protection features. Additionally, the project explores the potential of ultra-high voltage and ultra-wide bandgap semiconductors, including diamonds as semiconductor materials, for energy savings.

The project features two wind energy converter pilots and two universitydeveloped pilots: a TRL 5 DC-DC converter and a TRL 5 DC circuit breaker.

The basis for the four pilots is the 2.3 kV SiC MOSFET, which will be developed by project partner Infineon. It includes a source-gate PiN diode, whose onstate voltage has a strong temperature dependence and can be read out by

AC power can only be transmitted over relatively short distances with subsea cables, and as we look increasingly to offshore wind or tidal technology to meet growing demand, solutions are needed to create high-voltage direct current (HVDC) connections and to develop an HVDC grid

the gate drive, which will be developed by Rostock University. In addition, selfprotection features will be integrated into the SiC chip for robustness and direct water cooling will be realised for higher output power.

The two wind energy converter pilots are being realised by two industrial partners. As one of the technology leaders in wind energy, Vestas – supported by University of Aalborg – will develop a TRL 6 SiC converter with +20 percent power density and digitaltwin Condition and Health Monitoring. The start-up RKL together with Rostock University will develop a TRL 5 wind energy power stack with Condition and Health Monitoring based on online chip temperature and on-state voltage measurement.

Solar medium voltage DC collection grids and meshed high voltage transmission grids will play an important role in the future. As third and fourth pilots, a TRL 5 DC-DC converter and a TRL 5 DC circuit breaker including condition monitoring are being developed by the MoWiLife university partners KTH Stockholm and University of Aberdeen. The Aberdeen HVDC research team, led by Dragan Jovcic and Xin Yuan. will be responsible for developing and validating a functional SiC MOSFET hybrid high voltage DC circuit breaker, which builds on previous research projects at Aberdeen related to DC circuit breakers and DC transmission grid development.

Jovcic said: "DC (direct current) electrical systems have not been much utilised since AC (alternating current) systems have been preferred with traditional overland power transmission and conventional electricity generation.

"However, AC power can only be transmitted over relatively short distances with subsea cables, and as we look increasingly to offshore wind or tidal technology to meet growing demand, solutions are needed to create high-voltage direct current (HVDC) connections and to eventually develop an HVDC grid.

"We will use desktop research and also develop 5 kV DC CB demonstrator based on SiC MOSFETs in our HVDC laboratory for experimental testing."

# Si, SiC & GaN 'Power ahead' in Power Devices

#### **Frontside processes**

- Ohmic contacts

- Surface protection for SiC

- Trench filling including high aspect ratio

- Sputtered AIN seed layer for MOCVD GaN growth

- Solderable top metal stack

#### **Backside processes**

- Etching / surface cleaning

- Ohmic contacts

- Thick metal stack

Choosing Evatec's CLUSTERLINE<sup>®</sup> family of 200 or 300mm tools is a sure way to "power ahead" of the competition. Our thin film process know-how on Silicon and WBG materials ensures the best device performance while our wafer handling and stress management for thin wafers delivers the best production yields.

Visit **evatecnet.com/markets/power-devices** to find out how you can power ahead in your own production or contact your local Evatec Office at **evatecnet.com/about-us/sales-service**

SEMICONDUCTOR & ADVANCED PACKAGING • COMPOUND & PHOTONICS • THE THIN FILM POWERHOUSE www.evatecnet.com

## Nexperia: Expanding GaN and SiC operations

Re-fitting its Hamburg fab lays the foundations for Nexperia to hike its production of GaN and SiC transistors and diodes on 200 mm lines

#### BY RICHARD STEVENSON, EDITOR, CS MAGAZINE

**INVESTING PHENOMENAL SUMS in infrastructure** that enables the production of SiC and GaN devices is the new norm. In this regard the likes of Infineon, Wolfspeed and Innoscience are making the biggest splashes, by building fabs of breath-taking proportions that are propelling their capacity for highvolume production of wide bandgap power devices.

But as well as constructing new fabs, chipmakers are spending a lot of money on repurposing the space within them for the manufacture of SiC and GaN diodes and transistors. And in this regard, Nexperia is not holding back – it's investing \$200 million in new tools and equipment to strengthen the development and production of its wide bandgap portfolio at its fab in Hamburg, Germany.

Nexperia has a tremendous pedigree in electronics, with a history going back 100 years, and secondgeneration parent companies that include the household name Philips. Production of vacuum tubes in Hamburg provided the first source of revenue in the 1920s, and in the decades that followed efforts extended to the research, development and production of semiconductor devices. Further milestones came in the 1980s and 1990s, including the first MOSFET and the first 150 mm line, respectively. And in this century, two

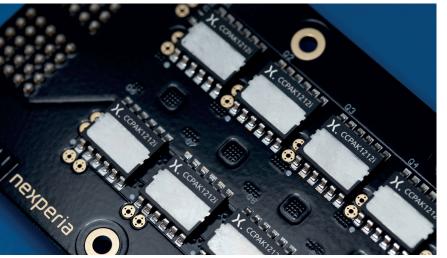

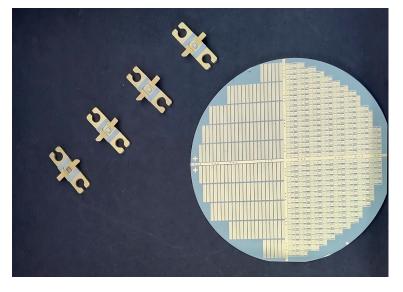

> Nexperia's proprietary CCPAK packages

These new lines will be established over the next two-to-three years at the Hamburg facility that is undergoing substantial change, as all activities unrelated to either lab or fab are relocated to

another office in the city. It's a move that's enabling an increase in the capacity of the silicon side of the business, as well as the expansion of SiC and GaN capability.

Nexperia's Senior Director Product Management for SiC, Katrin Feurle, told Compound Semiconductor that most of the \$200 million investment will be spent on new equipment and a remodelling of the fab to fit to the new machinery. Money is also allocated to increase the automation of existing infrastructure.

To scale epitaxial capabilities, Nexperia has placed orders with Aixtron. This German maker of MOCVD tools is a trusted partner that fulfils Nexperia's needs, according to Carlos Castro, Vice President and General Manager for GaN.

of the biggest moves have been carving out NXP from Philips in 2006, and in 2017, spinning out NXP's standard product division under the name Nexperia.

Today Nexperia is renowned as a major supplier of silicon power devices to automotive markets – this accounts for around half of its annual production of 100 billion discrete parts. However, over the last few years the power electronics producer has broadened its portfolio with the introduction of SiC and GaN devices.

Since 2019, GaN FETs have been part of this chipmakers' line-up. SiC products came in 2023, and now include SiC diodes and SiC MOSFETs, the latter in collaboration with Mitsubishi Electric.

An additional advance came this June, with the introduction of the production lines for high-voltage GaN D-Mode transistors and SiC diodes at the Hamburg site. And according to Nexperia, the next milestone will be modern and cost-efficient 200 mm production lines for SiC MOSFETs and GaN HEMTs.

#### NEWS ANALYSIS I NEXPERIA

As well as purchasing a range of processing tools to turn epiwafers into devices, Nexperia is making substantial investments in metrology.

Castro claims that Nexperia has a strong reputation for really high standards in production and performance, adding: "Metrology is key, because it gives you a very precise characterisation and control of materials, structures, and the process." In turn, this ensures performance, reliability, quality, and a competitive cost.

In addition to the equipment, Nexperia has recruited accompanying personal. "We have some people already on board there, experts in metrology," says Castro.

This increase in headcount is part of a pattern of long-term growth in staff at the Hamburg site. In 2017 the facility had 950 employees, a figure that now stands at 1,600, with more than 50 added in the last three years for roles solely associated with wide bandgap devices.

#### Growth in GaN...

Since launching its first wide bandgap power device in 2019, the GaN FET, Nexperia has made much progress with this class of transistor. Each new generation features a 20 percent cut in specific on-resistance.

One of the strengths of Nexperia is that it supplies both E-mode and D-mode devices.

"We are the only supplier giving the option to customers to go for D-mode technology, which we believe is more suitable for high-voltage and highpower applications, as well for E-Mode devices, which are very successful right now in the market for low-voltage or low-power applications, like, for example, fast chargers for mobile phones or notebooks," says Castro.

Another attribute of Nexperia's GaN portfolio is that it draws on the company's 20 years of expertise in copper clip technology. As well as ensuring a superior thermal performance, this packaging technology leads to better electrical performance, with a trimming of parasitics and stray inductance resulting in an increase in reliability. And that's not all – the copper clip technology enables a much more compact design that ensures a higher efficiency, as well as the opportunity to turn to higher frequencies, a strength well suited to high-power applications, such as power supplies and electric vehicles.

While GaN power devices have much appeal, they are currently attracting bad press for patent battles fought between Innoscience and EPC and Infineon.

Castro is not expecting Nexperia to be on the wrong side of such skirmishes, since it has its own IP. Back in 2017 and 2018 the company worked with a collaborator in the US, an activity that involved some licensing, and since then it has been internally and significantly growing its IP portfolio.

#### ... and SiC power portfolios

In the last year or so Nexperia has expanded its SiC portfolio, to include 650 V diodes with a current rating from 6 A to 20 A, in a range of formats that incorporate both surface mount and through-hole configurations. Additional advances are the launch of the first automotive-grade product, announced at this year's PCIM conference, and first design wins, especially in power supply applications.

Feurle describes the relationship with Mitsubishi Electric, which is key to the production of discrete SiC MOSFETs, as a strategic collaboration that's mutually beneficial for both sides. She says: "It's supporting the mission of Nexperia, but also Mitsubishi, to meet the rapidly growing demand for silicon carbide." By combining complementary expertise, both partners are reducing requirements for in-house development, and enabling them to go faster to market.

Obstructing Nexperia's plans has been its forced sale of its fab in Newport, Wales, a move dictated by the UK government. While this has caused serious disruption, it has not impacted Nexperia's compound semiconductor activities, as there were no plans to reintroduce them at the Newport site.

At the Hamburg fab, conversion of office space to clean rooms is underway, and over the next few years lines will be established for SiC and GaN production, with full production slated for 2027. "Selected key customers, of course, will receive samples in advance, to be able to qualify dedicated target applications," remarks Feurle.

The balance between the production of SiC and GaN devices will be determined by the market. Today SiC dominates, but the gap is expected to narrow, with Castro expecting that by 2028, the SiC market will be around four times that of GaN.

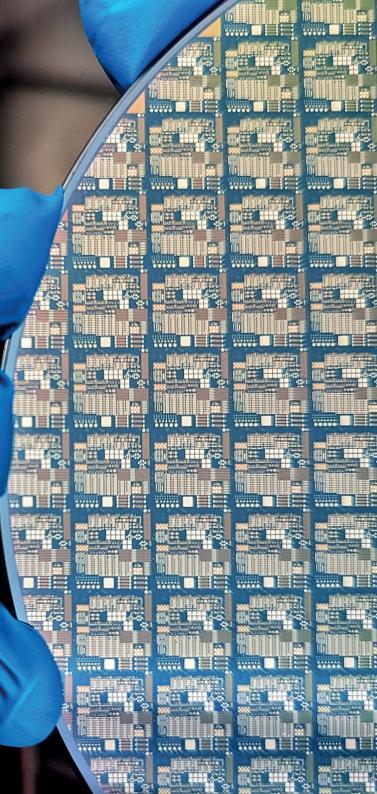

Based on this forecast, and Nexperia's substantial investment, this chipmaker is sure to be a significant supplier of a broad range of wide bandgap devices by the end of this decade.  Lithography at Nexperia's Hamburg Wafer-Fab

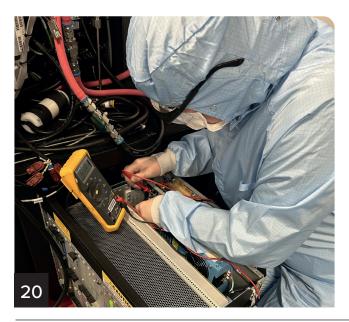

Electrical Testing in Nexperia's R&D Labs

## **Power GaN:** The 300 mm milestone

Migrating the manufacture of GaN power devices to 300 mm lines will boost yield, improve metrology and trim costs

## BY RICHARD STEVENSON, EDITOR, CS MAGAZINE

It has taken Infineon just 18 months to develop its 300 mm process, building on its 200 mm GaNon-silicon technology. A COMMON METRIC for measuring performance of any device is the bang per buck.

When it comes to GaN, there are many ways to measure that 'bang'. They include the on-resistance, the breakdown voltage, and the mobility of the two-dimensional electron gas.

But what about the 'buck'? That's a little harder to fathom, as chipmakers rarely reveal their yield, or the cost of producing their devices. But there are occasions when they will champion their efforts to trim their manufacturing costs, such as a move to larger wafers.

Claiming significant success on this front is the well-known European producer of power electronics, Infineon. It grabbed the headlines this autumn, when announcing the fabrication of the first GaN power devices on 300 mm wafers.

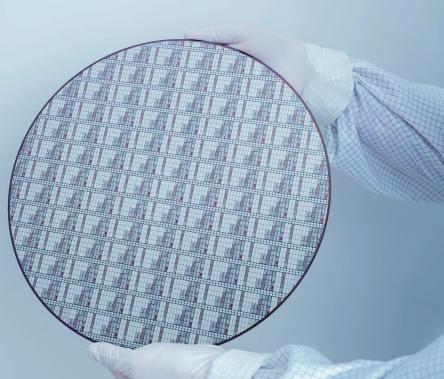

With manufacturers of GaN-on-silicon HEMTs currently carrying out production on substrates with a diameter of 200 mm, and sometimes less than that, Infineon's milestone is more than doubling the number of devices produced per wafer.

Note, though, that this gain is not the only one that will help to trim the cost of production. According to Johannes Schoiswohl, Infineon's Business Line Head for GaN, migration to larger wafers will also lead to improvements to the manufacturing process, such as a higher yield and access to superior metrology. Engineers at Infineon enjoyed these when progressing from 150 mm to 200 mm wafers, and they are seeing them again in the move to the 300 mm platform.

"We can get really great results – better than expected – because the 300-millimetre tools, from a performance perspective, from a monitoring perspective and a process control perspective, are better than the 8-inch tools," remarks Schoiswohl.

Due to these benefits, Infineon took just 18 months to develop its 300 mm process, building on its 200 mm GaN-on-silicon technology.

According to the company's projections, its GaN power devices could reach cost parity with their silicon equivalents. Helping to reach this goal will be: economies-of-scale; improvements in the technology itself, particularly the epitaxial stack; and the lower on-resistance of GaN, enabling smaller die to deliver the same performance as comparable products made from silicon.

To develop its trailblazing technology, Infineon's engineers have had to grapple with the lattice mismatch between GaN and silicon, as well as differences in thermal expansion coefficients.

"The bigger the wafer diameter, the harder it gets," admits Schoiswohl. "The wafers start to bow because of the lattice mismatch, and at a certain epithickness, they simply crack."

By developing and refining its epitaxial technology, Infineon releases strain during the growth.

#### NEWS ANALYSIS | INFINEON

Schoiswohl says that the particular epitaxial processes employed by providers of GaN power transistors are a key differentiator. According to him, the quality of the epitaxy determines the degree of early lifetime failures and often defines the device's failure mechanisms.

With Infineon's GaN power devices, a thicker epitaxial stack is needed to realise a higher blocking voltage. According to Schoiswohl, the company's engineers can see a path to progressing from 100 V to 650 V devices, but going beyond that will be more challenging. He says that one solution could be a switch to thicker wafers: "These are all details we have to figure out."

Infineon already offers wide bandgap power devices operating at a kilovolt or more, based on SiC. But that will not stop the company investigating what might be possible with GaN, which offers the tantalising possibility of a better performance at a lower cost.

Following the production of GaN-on-silicon epiwafers on dedicated MOCVD tools, processing of this material is undertaken on standard silicon lines – that's a significant merit from a CapEx perspective.

Infineon's pioneering work has been carried out at its facility in Villach, with attention paid to ensuring that processing of its GaN-on-silicon wafer in a 300 mm line did not introduce any contamination. As volume ramps, there will come a time when a 300 mm line can be devoted solely to the production of GaN devices. Infineon also has 300 mm equipment in Dresden that could be used for the production of GaN devices, and opportunities to potentially outsource due to established foundries.

At the upcoming trade show Electronica, to be held in Munich from 12-15 November, Infineon will release its next-generation G5 HV technology. The plan is to take this process and apply it to 300 mm wafers, with engineering samples reaching customers by the end of next year, and production ramping in 2026.

Today the biggest market for GaN power devices is consumer chargers. "We can see that this is now reaching points where some customers say 100 percent of their volume will move there," remarks Schoiswohl.

Additional opportunities are found in power supplies for AI, motor controls and inverters, as well as the automotive industry. While all these markets are important, Schoiswohl sees the automotive sector as an important one, due to the opportunity for higher volumes, with GaN a compelling candidate for the on-board charger.

Success will hinge on the bang-per-buck, helped by a move to 300 mm GaN-on-silicon.

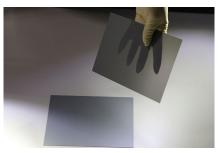

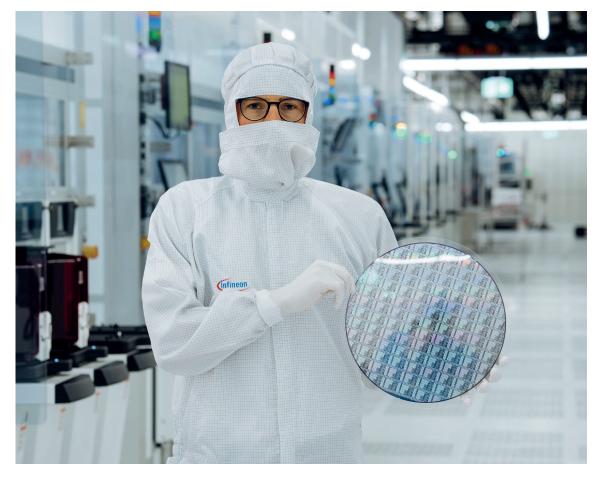

> A technical engineer in the cleanroom at Infineon Technologies in Villach, Austria, holds a 300 mm GaN-onsilicon wafer.

## Putting India on the global GaN stage

University spin-out Agnit has just secured funding to grow its GaN portfolio, a combination of epiwafers and power and RF devices

#### BY RICHARD STEVENSON, EDITOR, CS MAGAZINE

THERE ARE a number of ways to measure the growth of an industry.

For GaN electronics, which serves both the power and RF sectors, evidence of its rapid rise is seen in its double-digit rises in revenue, which will swell this market to several billion dollars by the end of this decade. But that's not the only way to track success. The growth of GaN is also seen in the geographical expansion of its chipmakers. As well as big the names in the US, Europe, Japan and China – such as Navitas, EPC, Transphorm, Infineon, Toshiba and Innoscience – smaller players are cropping up all over the world, including in unfamiliar locations, such as India.

Breaking new ground on this sub-continent is Agnit, a spin-out of the Indian Institute of Science that has just raised another US \$3.5 million to advance its GaN portfolio, a mix of epiwafers and power and RF devices.

Company co-founder and CEO, Hareesh Chandrasekar cannot lay claim to Agnit being the sole trailblazer for compound semiconductor manufacturing in India, because it's just possible that there is another maker of such devices hiding from view. But he is adamant that Agnit is the first to use indigenous technology, rather than getting it from somewhere else.

Introducing semiconductor manufacturing in India could be crucial to the growth of this nation's economy, says Chandrasekar. "If India is going to be a 5, 7, \$10 trillion economy in the next decade or so, there's no way this is happening without us having a presence in the electronics manufacturing ecosystem."

While there are a number of options for gaining a foothold in the semiconductor industry, some are more attractive than others, with cutting-edge CMOS having a formidable financial barrier to entry.

"We felt that gallium nitride was a nice sweet spot," says Chandrasekar, who argues that while this technology is not as complex as state-of-the-art CMOS, and doesn't demand fabs with price tags of several billion dollars, it's up and coming, and there is a local pull for products.

#### An academic heritage

Founded in late 2019, but initially impeded by the global pandemic that stalled the start of this company's operations until January 2021, Agnit receives tremendous support from the Indian Institute of Science, in terms of both facilities and expertise.

This institute is a great incubator for Agnit, having constructed a pilot production line for GaN that has a peak capacity of about ten 6-inch wafers per day. Supporting this is a very good characterisation suite.

Another asset of this institute is its extensive development of GaN technology, creating a strong IP base that draws on many, many years of research.

Imparting expertise from the Institute to Agnit is seamless, as four of the seven founders, all still involved, are academics with complementary capabilities related to the fabrication, operation and reliability of GaN devices. The other three co-founders, now the core management team, have PhDs in the field of GaN, but bring a different skillset, partly thanks to time spent working in the semiconductor industry. Strengthening this team are a growing number of employees, now totalling 16.

In terms of the commercialisation of its GaN device portfolio, Agnit has initially focused on the RF, before more recently expanding into the power domain.

#### NEWS ANALYSIS I INDIA

Agnit's RF devices are marketed to the telecom and the strategic sector. Products from rival suppliers are already being deployed in base stations, encouraging the Bangalore start-up to pursue more niche applications associated with 5G networks. "It could be things like private networks," says Chandrasekar.

For the power market, which Chandrasekar describes as "pretty hot now", there are many players with unique business models. To carve out a space in this sector, he and his colleagues are trying to address a particular set of problems associated with the unique, local market. Prototyping is underway.

To support its device development, Agnit is packaging its die in-house. But this will change when it moves into production, with this final manufacturing step outsourced, using the strong local ecosystem.

"We are also exploring global partnerships to see how we can actually leverage the global packaging capacity for the GaN chips that we make," says Chandrasekar.

The third string to Agnit's bow is its supply of GaN epiwafers to chipmakers.

"We had already supplied to academia," says Chandrasekar, adding that the new additional capacity is enabling Agnit to expand its horizons and build foundry relationships for the global supply of GaN-based power and RF epiwafers.

One of the issues hampering the GaN industry for many years is that epi is a "black box," according to Chandrasekar. "When you buy a batch of wafers, you never know if they're the right ones to begin with for your process or not. That has always been a big stumbling block."

Agnit is addressing this concern by offering the capability to adjust the epitaxial process based on internal device feedback. This helps customers target particular performance specifications.

#### Patents and IP

Agnit has a strong IP portfolio, supported by technology developed from the Indian Institute of Science, which it licences exclusively. The start-up has more than 20 patents, of which 15 or so are global patents.

Like the leaders of many foundries, those calling the shots at Agnit have thought very carefully about what IP requires patenting, and what is best left undisclosed. Such decisions are guided by whether patents have the potential to expose and demonstrate infringement. "If you can't do that, then it makes very little sense to patent your IP," argues Chandrasekar.

Highlighting the need for defendable IP are the patent battles being fought between Innoscience and EPC and Infineon. While such skirmishes may

alarm some chipmakers within the GaN industry, they are not a major concern to those leading Agnit. "Everything that we commercialise has our own patents as a backing, or our trade secrets and knowhow as a backing," says Chandrasekar. "We are quite careful about that."

#### Investing in its future

The US\$3.5 million raised this Autumn came from a seed round led by 3one4 Capital and Zephyr Peacock.

This investment will help to increase production yields for 4-inch GaN-on-SiC epiwafers for RF devices, and for 6-inch GaN-on-silicon wafers for the power sector.

In addition, the funding will be used improve device reliability, an issue that Agnit takes very seriously. "This will help our devices be qualified for various reliability standards that we are targeting based on the markets that we choose to go after," remarks Chandrasekar.

As well as advancing yield and reliability, the seed funding will support prototype development – in particular, power devices for the domestic market, as well as RF devices for the telecom sector.

Two big goals for the next 12 months are to get RF products in the market, in both the telecom and strategic sectors, and to grow the epiwafer supply business, supporting these customers with device data.

"In 24 months, we'll also have the first alpha samples available on the power devices that we're working on, which will be sampled to customers for integration into their systems," adds Chandrasekar.

The CEO expects the majority of its sales over the next few years to come from domestic markets, but 30 percent will be overseas. If such success follows, that will surely help to grow the role of India on the global GaN stage. > Agnit produces GaN power and RF devices at the incubator at the Indian Institute of Science.

## Clas-SiC expands technology in its stride

Not content with opening the world's first SiC foundry that partners with power device designers, Clas-SiC Wafer Fab is evolving and adapting to grow its success

#### BY JEN WALLS AND DAVID CLARK FROM CLAS-SIC

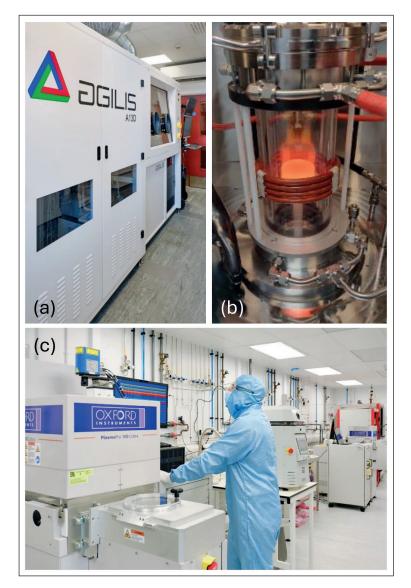

FOUNDED IN 2017, Clas-SiC Wafer Fab is the world's first open foundry dedicated to SiC. At our facility, located in Lochgelly on the outskirts of Scotland's capital city, Edinburgh, we have adopted a pureplay approach, which means that we'll never be in competition with our device customers. Instead, they draw on our standard process flows and flexible Process Design Kits (PDKs) to simply and quickly design highly customised SiC devices. By using PDK models to minimise non-recurring engineering and trim the cost and cycle time, our customers can

work with us to produce a range of competitively priced SiC transistors and diodes operating at 650 V, 1.2 kV, 1.7 kV and 3.3 kV on both conventional and engineered SiC substrates.

Our mission is to provide a low barrier to entry for all of our customers seeking to develop new products. We support them at every step, from proof-of-concept to market seeding, low-volume production, right through to high-volume production. This sets us apart, as we are the only foundry in the SiC industry that takes customers through all stages of product lifecycle. Most of our business comes from the manufacture of enhancement-mode MOSFETs, but we also produce depletion mode MOSFETs and two forms of diode – the merged p-i-n Schottky diode, and the junction barrier Schottky diode. We use PDKs to support a high level of integration, during successful customer designs for highly customised unique devices, even to the extent of including integrated sensors as part of the device design. Our customers can have confidence in these PDKs – as well as having reliability proven on our reference devices, they have been used by customers that conduct reliability trials on their own specific devices, with efforts on this front demonstrating that our foundry produces devices that satisfy AEC-Q101 using JEDEC 22 conditions.

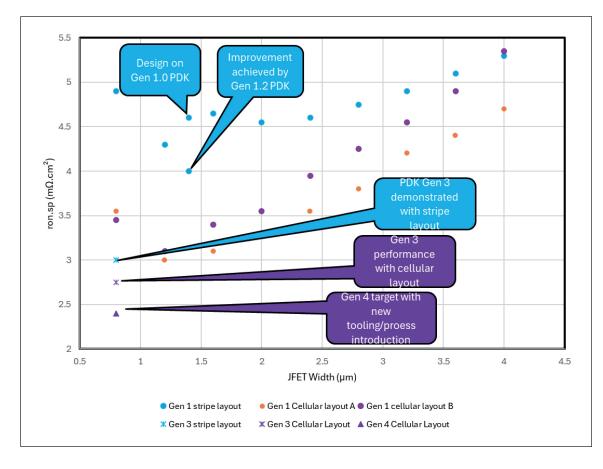

Since releasing our initial generation of PDKs in 2022, we have been working on developing Generation 3 PDKs. These successors deliver significant improvements in the performance of 1.2 kV planar MOSFETs, realised by shrinking transistor dimensions (see Figure 1). With favourable wafer-level results, Generation 3 devices are currently undergoing reliability trials, ahead of a scheduled release at the end of 2024. In parallel we are qualifying devices fabricated on engineered substrates to add to our PDK offerings.

#### TECXHNOLOGY I SiC

Figure 1. Reducing the width of the JFET is leading to a reduction in specific onresistance.

We are now starting to turn our focus to Generation 4 MOSFETs. They feature a shrinking of the transistor interconnect, a refinement that enables a further reduction in cell pitch and thus a corresponding reduction in specific on-resistance. To produce these transistors, we are investing in upgrading and expanding our tooling.

Right now, we are on the cusp of this exciting new phase, with the new tooling being identified, procured and installed ahead of interconnect technology development. Our timescales are governed by tool delivery times, and we are forecasting the introduction of our Generation 4 PDK in 2026. We plan to begin our Generation 3 and 4 technologies on 1.2 kV MOSFETs, before subsequently extending this technology to 1.7 kV and then 3.3 kV variants.

While we are currently focusing on planar MOSFET technology, this has not stopped us from conducting trench processing work for specific customer projects. As part of this effort, we are investing in process tooling to expand our trench processing capabilities, and support the possibility of developing our own trench MOSFET PDKs in the future.

We have drawn on our standard process modules that underpin our PDKs to fabricate novel trench and planar SiC MOSFETs, using heavily customised process flows. In addition, we have adopted this approach to produce *p*-*n* diodes, JFETs, and other customised devices, including both lateral and vertical device architectures.

As well as producing a wide range of SiC devices, we are active in UK innovation-based funding calls. They include APC (Advanced Propulsion Centre), DER (Driving the Electric Revolution), as well as the EU Horizon scheme. Projects in progress include an automotive BEV/FCEV project, a Solid-State Transformer project, and a project for Condition & Health Monitoring in Power Electronics. To keep close to technology advances, we are maintaining close academic links with research teams in the UK, at the University of Glasgow and Warwick, as well as overseas, such as at Purdue University.

Our innovation surrounding process development extends beyond 'normal' process advancements. We are closely involved in wafer fabrication tool development, partnering with major industrial players that advance semiconductor equipment design. This extends through to our work with substrate and epitaxy providers, to help them validate their materials for the market. Through this work we are advancing the world of SiC device processing.

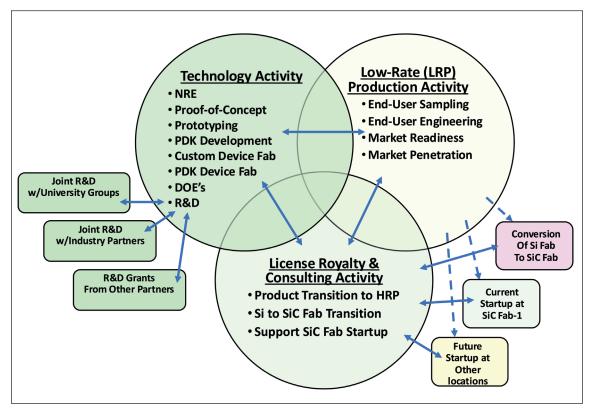

As well as technology development, which is the R&D part of our business and where we tend to begin our engagement with customers, we have another two business streams. They are Low-Rate Production (LRP), and Licensing, Royalty and Consulting (LR&C) (see Figure 2 for a summary of our business streams).

#### Views from Clas-SiC apprentices

Clas-SiC has a strong, well-established apprenticeship programme. Below, told in their own words, are the stories of three of those involved: Dani Johnston, a Modern Apprentice Manufacturing Equipment engineer (top left); and Duncan Colston (bottom left) and Kieran Healy (bottom right), both Graduate Apprentice engineers.

I AM IN MY final year as a Modern Apprentice at Clas-SiC Wafer Fab. My journey with this unique company started in 2020. I began as an operator, before I was given the opportunity to progress my career as an apprentice equipment engineer.

Starting off as an operator allowed me to gain a lot of understanding and knowledge of not only

each tools' capabilities, but also an insight into the various processes applied to semiconductors. This has benefited my ability to fulfil my role within the apprenticeship programme.

While progressing towards my HNC qualification I have gained a wide variety of experience by working alongside very knowledgeable process, equipment and facility engineers, who have guided and mentored me. My responsibilities as a equipment engineer include carrying out tasks such as preventative maintenance, fault diagnosis, and testing mechanical and electrical equipment.

I AM REALLY enjoying the second year of my apprenticeship experience with Clas-SiC. It is a challenging but rewarding environment, where I have

been surrounded by knowledgeable people to help me get the most out of my apprenticeship, both on the work side and with university.

At university I am working through my degree, which is a BEng design and manufacture (electrical) at Heriot Watt University in Edinburgh. I attend once a week and complete work-based learning tasks, and write reports on those tasks to consolidate my knowledge and complete the modules, along with gaining hands-on skills through working in the cleanroom.

I have gained a lot of relevant knowledge in the past year working in the test department, and spending some time working in the photolithography department. There has always been someone to help me when I'm stuck or confused. I started with learning the basics of operation, for example, how to run the tools and process batches. Now I am being introduced to more of the process aspects in semiconductors. I've also enjoyed the exposure I've had so far with the layout of the devices with the software we use, as I had an interest in CAD drawing at high school.

THE GRADUATE apprenticeship programme inside Clas-SiC has given me the opportunity to gain valuable industry skills whilst still having the possibility to be recognised with an educational degree (BEng – Engineering design and manufacture; electronic) that will be important for my future. Being local to me, Clas-SiC provides an easy stepping stone into the

semiconductor industry, in which I have been able to gain an appreciation for the industry and its significance in the world.

My experience at Clas-SiC has been positive, and I am now in the third year of my studies. I have been able to work alongside experienced engineers who are happy to share their knowledge with me. This has accelerated my development in both semiconductor knowledge and process engineering skills, learning different ways to carry out tasks such as data collection/presenting.

My time has been spent on a mix of day-to-day activities (monitoring SPCs, keeping batches moving etc.) and being involved in larger projects (process optimisation, development of new products), with a larger focus on the etching processes, dry and wet.

I have had support, where needed, from the Clas-SiC team. This has helped me in my university learning, where I have been able to lean on expertise to aid my understanding of topics, as well as with aspects such as time management. During my apprenticeship I have been given various opportunities to represent the company, attending schools to talk about Clas-SiC and the opportunities available, as well as events such as awards evenings.

I am looking forward to continuing my learning with Clas-SiC on their journey in SiC and hoping I can be a part of their growth.

#### TECXHNOLOGY I SiC

Our LR&C business stream enables customers with ambitious expansion plans to ramp up to high-volume/low-cost manufacture. This initiative provides support for independent foundries in low-cost manufacturing locations, such as those in Asia, to set up replicas of Clas-SiC processes. Our capacity in Scotland is limited to low-rate production, so this model allows us to access much higher volumes without Capex investment, keeping prices down for our customers.

For those that work with us under LR&C contracts, the norm is that a defined portion of their capacity is reserved for Clas-SiC customers. When our customers outgrow the capacity of Clas-SiC foundry, we outsource production to one of these associated but independent fabs. Throughout this evolution our customers maintains their partnership with us, utilising our advancing PDKs for their nextgeneration devices as they start another R&D cycle.

The first wafer fab utilising this model is now well advanced. Supported by our team, this fab has been constructed, facilities and tooling are installed, processes have been set up, and production will soon begin. We also have a number of other potential LR&C projects at the stage of advanced discussion.

Key to our success is our continual re-investment, not only in capital equipment, but also in our people. Our staff, with their advanced skill sets and out-of-the-box thinking, are our greatest asset. We now have more than 320 man-years of experience in SiC device processing, putting us in an unrivalled position for taking on the challenges of our customers. We pride ourselves in the continual development of our workforce, from our production operators through to our senior management team.

Training has been crucial to our advancing over the last year, as we have undergone exceptional growth and transitioned to a 24/7 operation for device production. More than 80 percent of our direct labour has received advanced training to fully utilise and build their skillsets, a move that has led to a more flexible and satisfied workforce. Our investment in new entrants, in the form of modern apprentices and graduate apprentices, is also well advanced. As well as ensuring that we keep the talent pipeline in a healthy state, this introduction of 'young blood' maintains a well-balanced age demographic within our workforce.

Despite the tough investment environment throughout the world, we have managed to secure equity investment from Archean Chemical Industries Ltd. We are excited to have them on our team and looking forward to the exciting times ahead. This funding will help to grow our business, supporting the launch of Gen 4.0 technology in 2026, as well as strengthening our Board of Directors.

We have been privileged to have both the financial support and the wisdom of knowledgeable investors since our foundation. One of our founding members, Carl Johnson, launched a CdTe crystal growth company just over fifty years ago that has blossomed into Coherent. By drawing on this expertise, we are well supported in our efforts that will see us take Clas-SiC to the next level and beyond.

Figure 2.The business stratergy of Clas-SiC Wafer Fab

## Enhancing $\beta$ -Ga<sub>2</sub>O<sub>3</sub> with hetero-integration

Thanks to the introduction of a far higher thermal conductivity and *p*-type doping, better devices are realised when pairing  $\beta$ -Ga<sub>2</sub>O<sub>3</sub> with SiC or diamond

#### BY ARPIT NANDI, ADITYA BHAT, INDRANEEL SANYAL, SAI CHARAN VANJARI, JAMES POMEROY, MATTHEW SMITH AND MARTIN KUBALL FROM THE UNIVERSITY OF BRISTOL

CLIMATE CHANGE and unpredictible extreme weather are impacting human life more frequently than ever. In just the last few months many in central Europe have suffered from such events, with severe flooding occuring at the same time that more than 5,000 firefighters were fighting wildfires in northern Portugal. These events underscore the urgent need to decarbonise the energy sector, an endeavour where power electronics can play a crucial role.

Within the power electronics portfolio, different materials are seeing deployment at different voltages. For low-to-medium-voltage applications, it is the silicon-based devices that dominate, due to their cost-effective manufacturing processes. But in the mid-to-higher voltage range, GaN and SiC have gained traction, with GaN-on-silicon benefiting from silicon-style manufacturing. And there is also  $Ga_2O_3$  to consider – it has emerged as a highly promising material for power electronic devices, due to its large bandgap (4.8 eV), its tolerance for high electric fields (8 MV cm<sup>-1</sup>), and the promise of cheaper production than the more established SiC.

Researchers working with this ultra-wide bandgap oxide have enjoyed tremendous success over the last decade or so, with interest ignited by the first report of a Schottky barrier diode in 2013. Spurred on by this triumph, alongside the ease of *n*-type doping and the availability of melt-grown substrates, these pioneers are now gaining further encouragement as 6-inch substrates appear on the horizon, as well as a push from multiple material vendors across the globe. There are now producers of  $Ga_2O_3$  substrates in Japan, the US, Germany, South Korea and China. Based on all this promise, commercialisation of  $Ga_2O_3$  looks inevitable for highvoltage applications.

Those developing  $Ga_2O_3$  material and devices include the UK government-funded Innovation and Knowledge Centre REWIRE, led by our team at the University of Bristol. While we acknowledge that today's  $Ga_2O_3$  devices exhibit excellent performance, with breakdown voltages that can exceed 8 kV, there are drawbacks that we are starting to address. Significant concerns preventing this material from harnessing its full potential include an on-state currents that's relatively low, and a device reliability that still needs to be established and proven.

Behind these limitations are: a lack of useable p-type doping for Ga<sub>2</sub>O<sub>3</sub>, primarily due to the flatness of the valence bands; and a low thermal conductivity. But there are ways to mitigate this through the heterogeneous integration of Ga<sub>2</sub>O<sub>2</sub> with SiC and diamond - they are materials with high thermal conductivity and *p*-type doping. Combining Ga2O3 with other materials is an increasingly popular approach to tackling the critical technological bottlenecks. For example, Ga<sub>2</sub>O<sub>2</sub> MOSFETs attached to diamond through mechanical exfoliation and bonding are showing good promise, as are devices featuring composite wafer fabrication with SiC. Still, concerns remain related to scalability, impairing manufacturing. Note that in addition to Ga<sub>2</sub>O<sub>2</sub> and its alloys, REWIRE is exploring, amongst others, SiC, AlGaN, diamond and BN device technologies, in a team with partners at Warwick University and Cambridge University.

Powered by state-of-the-art growth and clean room facilities at the University of Bristol, we are approaching heterogeneous integration of  $Ga_2O_3$  in various ways. Our goals include: optimising  $Ga_2O_3$ heteroepitaxy on SiC and diamond substrates, the latter in collaboration with Element Six Technologies and Orbray; and in partnership with Srabanti Chowdhury's Wide Bandgap Lab at Stanford University, exploring thin *p*-type diamond overgrowth on  $Ga_2O_3$ .

#### Pairing Ga<sub>2</sub>O<sub>3</sub> with diamond...

Pairing  $Ga_2O_3$  with diamond is very attractive. With a bandgap of 5.4 eV, *p*-type conductivity, a thermal conductivity of up to 2000 W m<sup>-1</sup> K<sup>-1</sup>, and a predicted critical electric field strength of 10 MV cm<sup>-1</sup>

10 III

The second

POWERELECTRONICSWORLD.NET | ISSUE 2025 25

Figure 1.(a) and (b) Ga<sub>2</sub>O<sub>3</sub> MOCVD, and (c) clean room facility at the University of Bristol. – that's even higher than that of  $Ga_2O_3$  – diamond compliments and enhances the effectiveness of  $Ga_2O_3$  when its adequately integrated.

Our initial work on this front has involved the growth of  $Ga_2O_3$  on single-crystalline diamond substrates. For this effort, we faced two underlying challenges: prevention of oxidation of the diamond surface at high temperatures during initial growth stages; and overcoming the challenge of realising good nucleation, which is plagued by the high surface energy differences between  $Ga_2O_3$  and diamond.

To address these concerns, we have pursued a twostep process, beginning with the low-temperature growth of a thin layer of  $Ga_2O_3$  that protects the diamond surface, followed by high-temperature growth of an epitaxial layer. Our detailed analysis of the microstructures and grains produced during this process has revealed two-grain variants aligned to [110] diamond and its perpendicular direction. Due to a peculiar asymmetric hexagonal (-201) face and mirror symmetry, each set has its own four equivalent subvariants (for more details see Nandi *et al.* Crystal Growth & Design **23** 8290 (2023)).

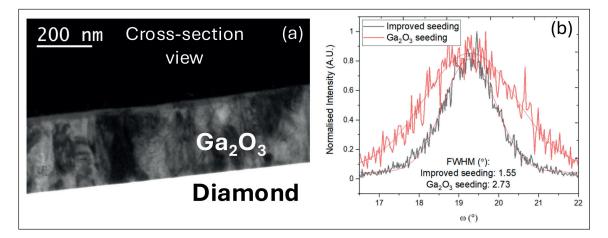

One of the important outcomes of our study is that it has helped us to identify the off-cut directions that are needed to eliminate grain variants and improve the epitaxial structure. Our approach is following in the footsteps of many other prior material systems, given that the use of off-cut substrates has a strong and well-established track record in reducing the multiplicity of grain variants. We have employed Ga<sub>2</sub>O<sub>2</sub> growth on off-cut diamond substrates to refine the quality of the epitaxial layers and eliminate one set of sub-grains. By introducing a unique, improvised seeding layer, we have produced better, smoother coalesced surfaces with larger grains and similar sets. With this approach we have grown a variety of layers, including that with a thickness of around 250 nm (see Figure 2 (a)).

Another part of this work has been the growth of an *n*-type doped  $Ga_2O_3$  cap layer on undoped material. This epistructure is a starting point for fabricating quasi-vertical power devices, currently under development. Supporting such efforts is the availability of 2-inch free-standing diamond substrates, with *p*-doping of this material set to follow.

#### ...and SiC

Composite bonded SiC- $Ga_2O_3$  substrates have also been gathering interest, due to their potential to deliver a significant reduction in the  $Ga_2O_3$  device temperature. However, the weak van-der Waals bonding at the interface between the two materials threatens to impede the mass adoption of such an approach, effectively impacting yield.

One alternative is the heteroepitaxy of  $Ga_2O_3$  on SiC; though similar to growth on both sapphire and diamond, this is a rather complex process with limited thermodynamic understanding. To try and shed new light on this, we have established a detailed thermodynamic picture that encapsulates the growth of  $Ga_2O_3$  on foreign substrates, and assumes a Volmer–Weber growth mode, where the substrate surface energy is lower than the epilayer surface energy.

Our investigations have determined that growth of  $Ga_2O_3$  on SiC is favourable at higher temperatures, a finding that falls in line with the widely adopted approach for growth on sapphire substrates. A preference for higher temperatures on both these foundations is mainly due to the comparable interface energies required for forming  $Ga_2O_3$  islands during nucleation with unit volume.

#### Heterogeneous device engineering

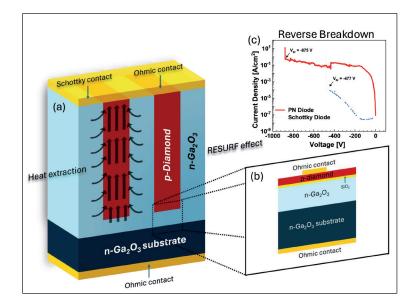

In addition to materials integration via growth, improved device engineering is critical to alleviating  $Ga_2O_3$  challenges. Diamond promises to play a role, thanks to its capability to combine excellent heat extraction with *p*-type conduction, realised

by boron doping. This conductivity opens the door to advanced device architectures that combine a low conduction loss with a high breakdown – a combination that can break through the typical trade-off between on-resistance and breakdown.

A team from Xidian University have pursued this type of approach, uniting *p*-type NiO with *n*-type  $Ga_2O_3$ . Devices with a breakdown voltage of more than 8 kV have followed, an outstanding result. However, the practical potential of these devices may be limited by the low thermal conductivity of both constituent materials, a weakness that ultimately restricts the current-carrying capacity.

Promising to overcome this limitation is the superheterojunction Schottky diode formed from *n*-type  $Ga_2O_3$  and *p*-type diamond (Figure 3 (a)). Simulations suggest that this device, which we are pursuing, can deliver off-state breakdown voltages of more than 4 kV, and an on-state resistance of just 2-3 m $\Omega$  cm<sup>2</sup>. The introduction of diamond quashes the peak temperature rise by up to around 60 percent compared with conventional Schottky diodes; and the advanced device structure aids electric field management in  $Ga_2O_3$ . We expect this superheterojunction diode to drastically outperform SiC in medium and high-voltage DC power converter applications where there is a low elevation in case temperature.