# 半导体芯科技

## SILICON SEMICONDUCTOR CHINA

ISSN 2523-1294

[www.siscmag.com](http://www.siscmag.com)

2025年 6/7月

## 半导体水管管理创新

P.15

扩展片上网络架构的创新方法

P.17

High NA EUV光刻技术的新进展

P.20

3DX射线检测解决系统性良率问题

P.26

共封装光学技术发展

P.28

ACT

INTERNATIONAL

Angel

BUSINESS COMMUNICATIONS

微信公众号

# 国际知名媒体授权 报道全球高新科技信息

免费

索阅

服务于机器视觉设计、电子制造、激光/光电子、射频/微波、化合物半导体

半导体制造、洁净及污染控制、电磁兼容等领域的专业读者及与会者

品牌会议

**ED CON** Electronic Design

Innovation Conference

电子设计创新大会

**CHIP** China

晶芯研讨会

国际代理

CQ Publishing (Japan) Chomdan (Korea) Pan Global (Europe)

Endeavor Business Media (USA) Horizon House (USA) Angel Business Communications (UK)

## ◆ 线下 ◆

### 化合物半导体&半导体芯科技 综合论坛

#### 05月·苏州 半导体先进技术创新发展和机遇大会

##### 平行论坛：Compound Semiconductor China

- 化合物半导体材料衬底、外延生长及其相关设备技术

- 超宽禁带器件：最终解决方案？

- 功率电子器件及封装和应用技术

- “AI+先进光显”引领未来

- 面向未来数据中心和6G网络下的射频器件研究进展

- 激光通信、精密加工及量测技术

- 先进半导体材料、器件的可靠性验证和故障分析

##### 平行论坛：CHIP China晶芯研讨会

- 玻璃通孔(TGV)技术创新发展和应用推动

- 面板级封装技术的崛起

- AI驱动的光电合封(CPO)新形势

- 车规级封测的挑战与解决方案

- 2.5D/3D/3.5D封装在AI趋势下大有可为

- 异构集成、芯粒(chiplet)、先进互连、混合键合、背面供电……技术发展与应用

### Compound Semiconductor China

#### 7月·广州 化合物半导体先进技术和应用大会

- 化合物半导体材料衬底、外延生长及其相关设备技术

- 能源变革大时代，功率器件及应用市场格局

- 先进显示与照明取得的进展

- 先进半导体材料、器件的可靠性验证和故障分析

- 超快通信射频器件新应用

### CHIP China晶芯研讨会

#### 10月·常州 化合物半导体先进技术和应用大会

- 化合物半导体材料衬底、外延生长及其相关设备技术

- 面向未来数据中心和6G网络下的射频器件研究进展

- 功率电子器件及封装和应用技术

- 扩大表面发射器的视野

- 激光通信、精密加工及量测技术

#### 11月·厦门 第三届-半导体先进封测产业技术创新大会

- 玻璃通孔(TGV)技术创新发展和应用推动

- 面板级封装技术的崛起

- AI驱动的光电合封(CPO)新形势

- 车规级封测的挑战和解决方案

- 2.5D/3D/3.5D封装在AI趋势下大有可为

- 异质集成·先进封装关键材料与创新

- 2.5D/3D封装设计仿真与可靠性

- 先进封装对新型装备技术的需求和挑战

- 异构集成、芯粒(chiplet)、先进互连、混合键合、背面供电……技术发展与应用

## ◆ 线上 ◆

### Compound Semiconductor China

先进半导体材料的检测/量测关键技术

GaN功率应用,厚积薄发

MicroLED取得的进展

超宽禁带材料、器件解决方案

PIC的新应用

面向未来数据中心和6G网络下的射频器件研究进展

### CHIP China晶芯研讨会

玻璃通孔(TGV)技术创新发展和应用推动

面板级封装技术的崛起

先进封装制造工艺与材料的创新

先进半导体键合集成技术

光电合封(CPO)及光电互连技术发展

2.5D/3D封装设计仿真与可靠性

## ◆ 定制专场论坛 ◆

重点依据企业需求定制化会议主题，线上直播与线下执行双向选择，垂直听众定向邀约，充分发挥资源链接优势，突破原有格局，助力泛半导体产业客户实现多元化探索路径。

线下会议

推介目的性强 会议听众垂直

议题内容聚焦 直击产品核心

\*以上主题暂定，请以会议举办议题为准

# 目录 CONTENTS

## 封面故事 Cover Story

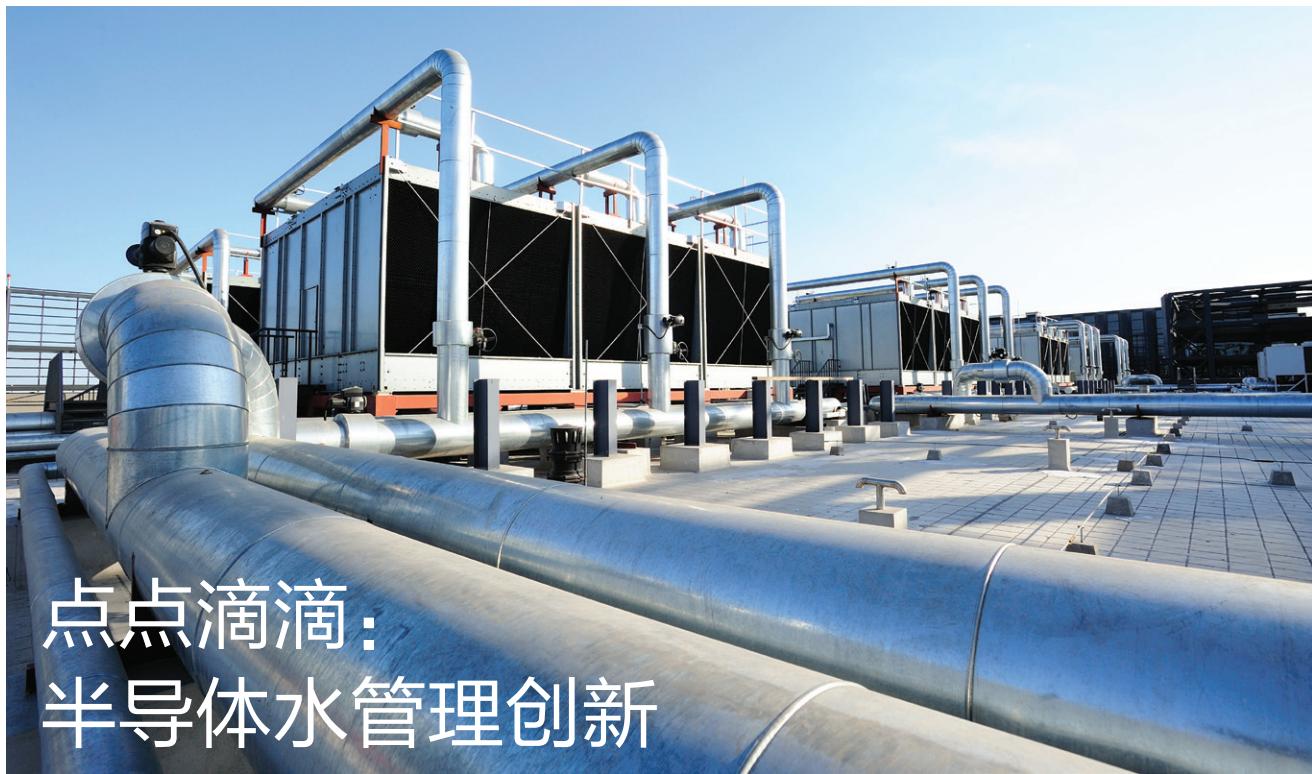

### 15 点点滴滴：半导体水管理创新

#### Drip by drip: semiconductor water management innovations

半导体制造不仅需要大量的能源、化学品和硅片，还需要大量的水。IDTechEx 预测，随着对集成电路的需求持续上升，到 2035 年，半导体制造的用水量将翻倍。

由于许多半导体晶圆厂位于水资源高度短缺的地区，因此半导体制造商需要采取行动减少这种巨大的水消耗。正在实施的水管理技术有望缓解人们对水资源短缺的担忧，同时还能降低运营成本。

15

## 编者寄语 Editor's Note

### 5 中美芯片战博弈加剧

## 行业聚焦 Industry Focus

### 6 灿芯半导体推出 28HKC+ 工艺平台 TCAM IP

### 6 中科院微电子所在碳硅三维异质集成器件上取得进展

### 7 西门子 Questa One 智能验证解决方案重新定义 IC 验证

### 7 全国首条 8 英寸 MEMS 晶圆全自动生产线投产

### 8 氮化镓进军电动汽车逆变器市场

### 9 新型蓝绿光激光二极管助力 DNA 测序功率实现五倍跃升

### 9 A-STAR 推出全球首个工业级 200 毫米碳化硅开放研发生产线

### 10 马波斯 VBI 破刀侦测：变革半导体生产的划片机

### 11 泛林集团推出突破性导体刻蚀技术

### 12 FlexEnable FlexiOM™ 有机薄膜晶体管材料

### 13 铜泰公司展出精密金基芯片贴装预成型件

### 14 面向临时键合 / 解键合的 ERS 光子解键合技术

6

10

## 关于雅时国际商讯 (ACT International)

**ACT INTERNATIONAL** 雅时国际商讯 (ACT International) 成立于1998年，为高速增长的中国市场中广大高技术行业服务。ACT通过它的一系列产品 - 包括杂志和网上出版物、培训、会议和活动 - 为跨国公司及中国企业家架设了拓展中国市场的桥梁。ACT的产品包括多种技术杂志和相关的网站，以及各种技术会议，服务于机器视觉设计、电子制造、激光/光电子、射频/微波、化合物半导体、半导体制造、洁净及污染控制、电磁兼容等领域的约二十多万专业读者及与会者。ACT 亦是若干世界领先技术出版社及展会的销售代表。ACT 总部在香港，在北京、上海、深圳和武汉设有联络处。[www.actintl.com.hk](http://www.actintl.com.hk)

## About ACT International Media Group

ACT International, established 1998, serves a wide range of high technology sectors in the high-growth China market. Through its range of products -- including magazines and online publishing, training, conferences and events -- ACT delivers proven access to the China market for international marketing companies and local enterprises. ACT's portfolio includes multiple technical magazine titles and related websites plus a range of conferences serving more than 200,000 professional readers and audiences in fields of electronic manufacturing, machine vision system design, laser/photonics, RF/microwave, cleanroom and contamination control, compound semiconductor, semiconductor manufacturing and electromagnetic compatibility. ACT International is also the sales representative for a number of world leading technical publishers and event organizers. ACT is headquartered in Hong Kong and operates liaison offices in Beijing, Shanghai, Shenzhen and Wuhan.

## 关于《半导体芯科技》

《半导体芯科技》(原半导体科技)中国版 (SiSC) 是全球最重要和最权威的杂志Silicon Semiconductor的“姐妹”杂志，由香港雅时国际商讯出版，报道最新半导体产业新闻、深度分析和权威评论。为中国半导体专业人士，提供他们需要的商业、技术和产品信息，帮助他们做出购买决策。《半导体芯科技》内容覆盖半导体制造、先进封装、晶片生产、集成电路、MEMS、平板显示器等。杂志服务于中国半导体产业，包括IC设计、制造、封装及应用等。

## About Silicon Semiconductor China

Silicon Semiconductor China is the 'sister' title to Silicon Semiconductor - the world most respected and authoritative publication, published by ACT International in Hong Kong (former SST China), reports the latest news, in-depth analysis, and authoritative commentary on the semiconductor industry. It provides for Chinese semiconductor professionals with the business and technology & product information they need to make informed purchasing decisions. Its editorial covers semiconductor manufacturing, advanced packaging, wafer fabrication, integrated circuits, MEMS, FPDs, etc. The publication serves Chinese semiconductor industry, from IC design, manufacture, package to application, etc.

## 高效、先进的成像

### EVIDENT半导体行业解决方案

**DSX2000**

数码显微镜

**MX63+AL120**

工业检测显微镜 +12 英寸晶圆搬运机

**OLS5100**

3D 测量激光显微镜

#### 用于整合的显微镜部件

##### 方便集成

特点 1：组件模块化设计非常便于与其他光学机械系统集成。

特点 2：结像透镜，暗场模块，LED 远程控制。

特点 3：独立模块，便于设计您的系统。

##### 节省观察时间

特点 1：高分辨率、长工作距离物镜

特点 2：超宽视场镜筒透镜，不断提升的显微镜相机传感器尺寸和分辨率造就了对超宽视场光学器件的需求。

##### 参数公开

专家将帮助您选择合适的组件，并为您提供诸如尺寸和透光率值等技术数据。

仪景通光学科技(上海)有限公司

EVIDENT(Shanghai)Co.,Ltd.

更多详情请咨询: 400-969-0456 / marketing.cn@evidentscientific.com

[www.evidentscientific.com.cn](http://www.evidentscientific.com.cn)

**OLYMPUS®**

# 目录 CONTENTS

## 技术 Technology

- 17** 扩展片上网络架构的创新方法

Innovative approaches to scaling network-on-chip architectures

- 20** High NA EUV 光刻技术的新进展

The new development of High NA EUV lithography technology

- 24** 真空系统：交钥匙项目指南

Vacuum systems: a guide to turnkey projects

- 26** 从实验室到晶圆厂：利用下一代 3D X 射线技术解决系统性良率问题

From lab to fab : Solving systematic yield issues with next generation 3D X-ray

- 28** 共封装光学技术发展

The evolution of Co-Packaged Optics technology

17

## 专栏 Column

- 31** 边缘 AI：物联网实施新标杆

AI at the edge: a new benchmark for IoT implementation

- 34** 人形机器人中的毫米波雷达感应和传感器融合

Millimeter wave radar sensing and sensor fusion in humanoid robots

- 36** 情境感知 AI：利用 FPGA 技术增强边缘智能

Contextual AI: Enhancing edge intelligence with FPGA technology

- 38** 物联网边缘传感器节点：超越单处理器嵌入式系统的演进

Sensor nodes at the edge of IoT: the evolution beyond uniprocessor embedded systems

26

## 广告索引 Ad Index

34

### 《半导体芯科技》编委会（排名不分先后）

|           |                                  |

|-----------|----------------------------------|

| 徐冬梅 教授级高工 | 中国半导体行业协会副秘书长兼封测分会秘书长            |

| 于大全 教授    | 厦门云天半导体创始人                       |

| 姚大平 博士    | 江苏中科智芯集成科技有限公司总经理                |

| 汤晖 教授     | 广东工业大学、精密电子制造技术与装备国家重点实验室        |

| 罗仕洲 教授    | 磐允科技总经理                          |

| 林挺宇 博士    | 广东芯华微电子技术有限公司总经理                 |

| 杨利华 院长    | 两江半导体研究院                         |

| 王文利 教授    | 西安电子科技大学电子可靠性（深圳）研究中心主任 雅时国际商讯顾问 |

| 刘功桂 教授级高工 | 中国电器科学研究院股份有限公司威凯技术中心主任          |

| 徐开凯 教授    | 电子科技大学、电子薄膜与集成器件国家重点实验室          |

| 何进 教授     | 北京大学教授、深圳系统芯片设计重点实验室主任           |

社长 Publisher

麦协林 Adonis Mak

adonism@actintl.com.hk

荣誉顾问 Honorary advisor

刘胜院士 Academician Liu Sheng

主编 Editor in Chief

赵雪芹 Sunnie Zhao

sunniez@actintl.com.hk

出版社 Publishing House

雅时国际商讯 ACT International

香港九龙 B,13/F, Por Yen Bldg,

长沙湾青山道478号 478 Castle Peak Road,

百欣大厦 Cheung Sha Wan,

13楼B室 Kowloon, Hong Kong

Tel: (852) 2838 6298

Fax: (852) 2838 2766

北京 Beijing

Tel/Fax: 86 10 64187252

上海 Shanghai

Tel: 86 21 62511200

Fax: 86 21 52410030

深圳 Shenzhen

Tel: 86 755 25988573 /25988567

Fax: 86 755 25988567

武汉 Wuhan

Tel: 86 27 82201291

UK Office

Angel Business

Communications Ltd.

6 Bow Court,

Fletchworth Gate,

Burnsall Road, Coventry,

CV56SP, UK

Tel: +44 (0)1923 690200

Chief Operating Officer

Stephen Whitehurst

stephen.whitehurst@angelbc.com

Tel: +44 (0)2476 718970

## 中美芯片战博弈加剧

2025年，中美芯片战呈现出更为复杂和激烈的态势，双方在技术、市场与规则层面的博弈持续升级，深刻影响着全球半导体产业格局。

### 美国制裁措施再升级

5月12日，美国商务部正式废除拜登政府的《AI扩散规则》，并发布《防止先进计算芯片转用行业指南》，进一步细化对AI芯片及含该类芯片产品的出口监管。新规直接将“先进的中华人民共和国芯片”列为重点管控对象，明确指出在全球任何地方使用华为昇腾芯片均违反美国出口管制规定。这一举措标志着美国对中国AI芯片的管制从限制出口转向全球禁用，试图从根本上阻断中国AI芯片在国际市场的应用与推广。

此外，美国还对中国28nm及以上成熟制程芯片发起“301调查”。尽管成熟制程芯片技术相对不那么先进，但中国在这一领域已具备强大的产能与成本优势，全球产能占比达30%。美国此举意在遏制中国在成熟制程芯片市场的主导地位，防止中国企业凭借成本优势进一步扩大市场份额，挤压美企生存空间。

### 中国的反制与突破

面对美国的全方位封锁，中国采取“双轨策略”积极应对，在技术研发与产业政策上同步发力。

在技术突破方面，国产替代进程加速推进。华为昇腾910B芯片性能达到英伟达H100的60%-80%，而价格仅为40%，极大提升了国产AI芯片在国内市场的竞争力，推动国内AI芯片市占率从5%跃升至18%。中芯国际在先进制程工艺上也取得显著进展，14nm工艺良率达75%；长江存储的232层3D NAND良率超92%；国产光刻机更是成功突破28nm节点，这些关键技术的突破为构建“去美化”供应链奠定了坚实基础。

在产业政策方面，中国利用自身在稀土等关键原材料领域的优势进行反制。2025年前4个月，中国对美的镓、锗出口锐减92%，从源头限制美国半导体产业的关键原材料供应。同时，中国积极联合金砖国家推动新结算体系，并在WTO起诉美国单边制裁行为，从国际规则层面挑战美国技术霸权，争取公平的国际竞争环境。

### 全球产业链格局正在重塑

中美芯片战的持续升级，加速了全球半导体产业链的重构。在国际市场上，各家企业为降低地缘政治风险，纷纷调整供应链布局。一些国家和地区开始重新审视与中美两国在半导体领域的合作关系，寻求更加多元化和自主可控的技术来源。

总体来看，中美芯片战已从单纯的技术与贸易摩擦，演变为一场涉及全球产业链、原材料供应、国际规则制定的全方位博弈。未来随着双方在AI、量子计算等前沿领域的竞争愈发激烈，以及更多国家和地区的参与，芯片战的走向将更加复杂多变，其对全球科技产业和经济格局的深远影响也将持续显现。

赵雪芹

## 灿芯半导体推出28HCK+工艺平台TCAM IP

一站式定制芯片及IP供应商灿芯半导体（上海）股份有限公司宣布推出基于28HCK+ 0.9V/1.8V平台的Ternary Content-Addressable Memory (TCAM) IP。该IP具有高频率和低功耗特性，随着网络设备中快速处理路由表与访问控制列表 (ACL) 等需要高效查找的场景不断增加，该IP将被高端交换机、路由器等芯片广泛采用。

灿芯半导体此次发布的TCAM IP包含全自研Bit cell，符合逻辑设计规则，良率高；在可靠性方面，这款TCAM抗工艺偏差强，具有高可靠性的特点；在功耗方面，采用match line分段控制，可节省约30%功耗；在速率方面，最高可以支持800MHz，查找速度快。另外，客户可以根据需求编译出不同尺寸的TCAM cell，具有高弹性设计的特点。

目前，该IP已成功流片，并顺利通过28HCK+工艺平台的芯片功能测试和性能测试，各项指标均达到预期标准。随着高速网络和各类智能应用等需求的不断提高，TCAM IP在这些应用里面的重要性也日益凸显，灿芯半导体可提供完整的TCAM IP和定制芯片解决方案，助力客户进行产品设计。

灿芯半导体多年来持续深耕多工艺节点IP开发及定制芯片设计服务，通过严格的设计和验证流程，确保了各类IP及定制芯片在实际应用中的可靠性和稳定性，可满足客户多层次需求。灿芯半导体的“YOU”系列IP和YouSiP (Silicon-Platform)解决方案，经过了完整的流片测试验证。其中YouSiP方案可以为系统公司、无厂半导体公司提供原型设计参考，从而快速赢得市场。

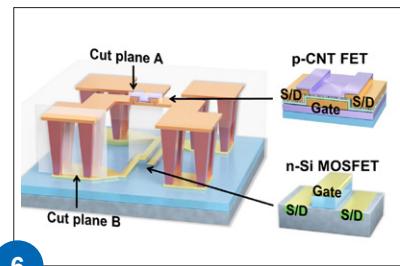

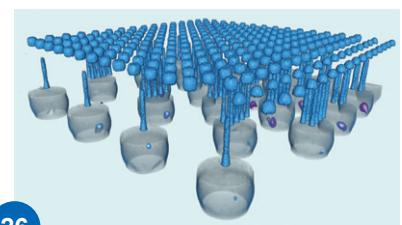

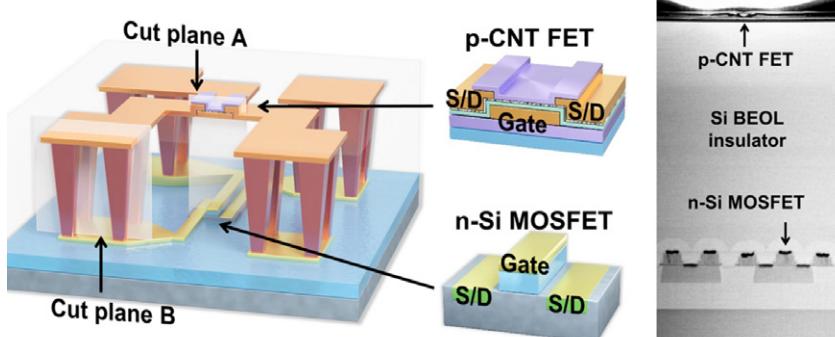

## 中科院微电子所在碳硅三维异质集成器件上取得进展

据中国科学院微电子所官网消息，随着集成电路密度不断提高，晶体管的工艺节点不断微缩，已逼近物理极限。三维互补式场效应晶体管(3D CMOS)技术成为破局的潜在路径。传统硅基3D CMOS集成技术热预算较高，导致工艺复杂成本提高，并可能引发性能退化等问题，限制了其商业应用。

针对上述问题，中国科学院微电子研究所抗辐照实验室李博研究员、陆芃副研究员团队基于碳纳米管材料低温成膜能力，提出一种碳纳米管/硅异质集成(CNT/Si Heterogeneous Integration)的3D CMOS技术，实现了180nm SOI器件后道的低温( $\leq 150^{\circ}\text{C}$ )碳纳米管器件集成。团队提出了面向高性能数字电路应用的工艺优化方案，实现了碳纳米管器件阈值电压的精准调控，可完成N、P晶体管电学特性的匹配，3D CMOS噪声容限显著提升( $\text{NMH/NML} = 0.404/0.353 \times \text{VDD}$ )，同时实现了高增益( $\sim 49.9$ )、超低功耗( $390 \text{ pW}$ )及高均一性(片间差异 $< 6\%$ )等优异性能。为论证该技术在先进工艺节点中的集成能力，团队使用TCAD仿真搭建了14nm FinFET/

CNT 3D CMOS 电路单元，理论分析显示其在噪声容限和功耗方面优于商用14nm-FinFET工艺。

基于该研究成果的论文“Low-Thermal-Budget Construction of Carbon Nanotube p-FET on Silicon n-FET toward 3D CMOS FET Circuits with High Noise Margins and Ultra-Low Power Consumption”近期发表在国际著名期刊 Advanced Functional Materials 上 (DOI:10.1002/adfm.202504068)。本工作由微电子所李博研究员团队、南京大学朱马光研究员团队、安徽大学胡海波教授团队合作完成，微电子所为第一单位。

## 西门子Questa One智能验证解决方案重新定义IC验证

西门子数字化工业软件宣布推出 Questa™ One 智能验证软件产品组合，以人工智能 (AI) 技术赋能连接性、数据驱动方法和可扩展性，突破集成电路 (IC) 验证流程限制，助力工程团队有效提高生产效率。

Questa One 提供更快引擎，可显著提升工程师的工作效率，减少工作负载，并支持从 IP 到 SoC 再到大型系统的大规模复杂设计。

Questa One 智能验证解决方案由西门子与行业领导者合作开发，具有互连性强、数据驱动、且可扩展等特点，有助于突破验证生产率差距 2.0 瓶颈。

Questa One 智能验证解决方案涵盖多项技术突破，包括：

- Questa One Coverage Acceleration 软件，通过将更高、更快的覆盖率结果和通用验证方法学 (UVM) 约束随机测试生成的优势相结合，可实现覆盖率目标速度比传统测试平台解算器快 50 倍。

- Questa One DFT Simulation Acceleration 软件，利用 Questa One Parallel Simulation，使 Gate-level DFT 串行模式仿真速度提高 8 倍，并可与 Tesson™ Streaming Scan Network (SSN) 架构紧密集成。

- Questa One Fault Simulation Acceleration 软件，性能提高 48 倍，并支持功能安全和 DFT 故障仿真应用。值得一提的是，其还针对 Tesson 用户定义的故障模型 (UDFM) 功能提供专属支持。

- Questa One Stimulus Free Verification 软件，助力工

程师达到新的生产力水平。其独特的引擎组合和应用统一的方法能够将复杂的开源 SoC 级参考设计处理时间从 24 小时以上缩短至 1 分钟以下。

- Questa One Avery Verification IP 软件，基于 Avery 的高质量 VIP 和高覆盖率合规性测试套件 (CTS)。协议感知调试和协议感知覆盖分析有助于提高生产率，加速的 VIP 使得 Questa One Sim 上的相同 CTS、测试平台和激励能够在 Veloce CS 仿真和原型系统上重复使用。

Questa One 智能验证解决方案基于以下三大核心原则：

- Questa One Connected Verification 软件能够连接工程师、EDA 工具和验证 IP，形成一体化的生态系统，从而能够在西门子的 Questa One、Tesson DFT 和 Veloce™ CS 仿真和原型系统上进行全面、无缝的验证、确认和测试。

- Questa One Data-Driven Verification 软件通过 AI 驱动的分析能力，依托数据的力量带来新的洞察并提高验证效率。生成式、规范性和预测性机器学习技术使得工程师能够以少量的资源实现高水平的验证。

- Questa One Scalable Verification 软件提供卓越的加速和自动化能力，可实现快速验证收敛，并带来高置信度。

西门子 Questa One 智能验证解决方案帮助半导体和电子系统行业向市场提供先进的 3D-IC、基于芯粒的设计和软件定义系统。

## 全国首条8英寸MEMS晶圆全自动生产线投产

安徽华鑫微纳集成电路有限公司宣布，8 英寸晶圆生产线首批产品成功串线，这标志着全国首条 8 英寸 MEMS 晶圆全自动生产线在蚌埠正式投产。

华鑫微纳 8 英寸 MEMS 晶圆生产线是一条集硅基 MEMS、压电 MEMS、CMOS-MEMS 单片集成、2.5D/3D 微系统集成于一体的灵活度高、兼容性强、体系完善研产高度协同的晶圆代工平台。其产品涵盖惯性传感器、压力传感器、光 MEMS 执行器、环境传感器、喷墨打印头等。产线规划 3 万片 / 月的 8 英寸 MEMS 晶圆制造能力，达

产后将成为国内产出最大的 MEMS 晶圆生产线。

安徽华鑫微纳副总经理丁敬秀介绍，目前累计与 50 家客户达成合作意向，意向订单总计约 21 万片，另有 3 万余片晶圆合同正在洽谈中，将有效支撑 2025 年 1 万片达产。

华鑫微纳定位为国内领先的 8 英寸 MEMS 晶圆代工企业，是开放式、定制化 MEMS 代工平台基地，可加工产品涵盖惯性传感器、压力传感器、光 MEMS 器件等，主要应用于高端装备、汽车电子等领域。

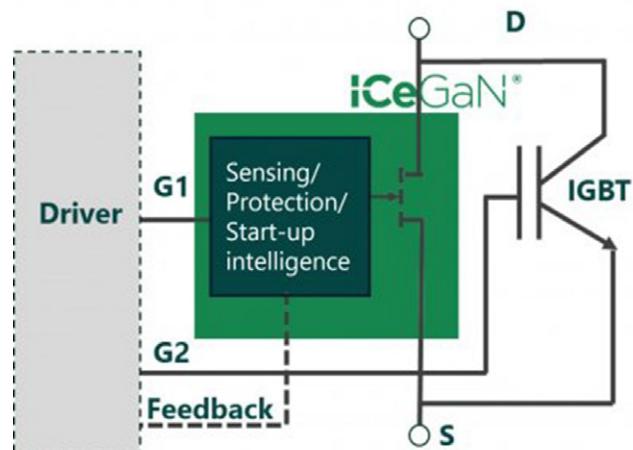

## 氮化镓进军电动汽车逆变器市场

ICeGaN HEMT与IGBT并联组合实现高效率与低成本双重优势

英国半导体公司 Cambridge GaN Devices (CGD) 专注于开发高能效氮化镓 (GaN) 功率器件，致力于简化绿色电子产品的设计和实施。近日，CGD 公布了关于 Combo ICeGaN® 的 GaN 技术解决方案的详情，该方案将助力公司进军功率超过 100kW 的电动汽车动力总成应用市场，这一市场规模预计超过 100 亿美元。

Combo ICeGaN® 通过将智慧 ICeGaN HEMT IC 与 IGBT 集成在同一模块或智慧功率模块 (IPM) 中，不仅实现了高效率，还提供一种更具有成本效益的替代方案，以取代昂贵的碳化硅 (SiC) 解决方案。

CGD 创办人兼首席执行长 Giorgia Longobardi 博士表示：目前，电动汽车动力总成的逆变器主要面临两种选择：一种是采用低成本的 IGBT，但在轻负载条件下效率较低；另一种是使用效率极高但价格昂贵的 SiC 器件。我们全新的 Combo ICeGaN 解决方案通过智慧结合氮化镓和硅技术的优势，为电动汽车行业带来革命性突破，在显著降低成本的同时实现最高效率。这将实现更快的充电速度和更长的续航里程。我们已与多家顶级电动汽车制造商及其供应链合作伙伴紧密合作，加速将这一技术创新推向市场。

独特的 Combo ICeGaN 技术解决方案充分利用了 ICeGaN 与 IGBT 器件在驱动电压范围（如 0-20V）和栅极耐受性方面的相似性，使两者能够在并联架构中高效协同工作。在实际运行中，ICeGaN 开关在较低电流（轻负载）下表现出较高的效率，具备低导通损耗和低开关损耗；而 IGBT 则在较高电流（接近满载或浪涌条件）时发挥主导作用。Combo ICeGaN 还结合了 IGBT 的高饱和电流和雪崩钳位能力，以及 ICeGaN 的高效开关特性，进一步提升了整体性能。在高温环境下，IGBT 的双极特性使其能在较低的导通电压下导通，从而有效弥补 ICeGaN 的电流损失；相反，在低温条件下，ICeGaN 将承担更多的电流。这一方案通过智慧化的感测和保护功能，优化了 Combo ICeGaN 的驱动方式，同时扩展了 ICeGaN 与 IGBT 设备的安全工作区域 (SOA)，确保系统的稳定性和可靠性。

ICeGaN 技术使电动汽车工程师能够在 DC-DC 转换器、车载充电器 (OBC) 以及未来的牵引逆变器中充分利用 GaN 技术的优势。Combo ICeGaN 进一步拓展了 GaN 技术应用范围，进入功率超过 100kW 的牵引逆变器市场。ICeGaN IC 已被验证具备极高的可靠性，而 IGBT 在牵引系统和电动汽车应用中也有着长期且可靠的应用记录。此外，CGD 还成功验证了 ICeGaN 与 SiC MOSFET 并联组合方案的可行性。在 IEDM 论文中详细介绍的 Combo ICeGaN 方案无疑是更具成本效益的选择。

CGD 预计将在 2025 年年底推出可运行的 Combo ICeGaN 演示版本，为电动汽车动力系统提供更高效、更经济的解决方案。

CGD 创始人兼首席技术长 Florin Udrea 教授说：在功率器件领域工作了三十年，这是我第一次遇到如此完美互补的技术组合。ICeGaN 在轻负载条件下表现出极高的速度和卓越的性能，而 IGBT 在满载、浪涌条件以及高温环境下展现出显著优势。ICeGaN 提供了高度集成的片上智慧功能，而 IGBT 则具备雪崩能力为系统保驾护航。两者均采用硅基底，这不仅显著降低了成本，还充分利用了基础设施和制造工艺优势。

更多信息请访问：[www.camgandevices.com](http://www.camgandevices.com)。

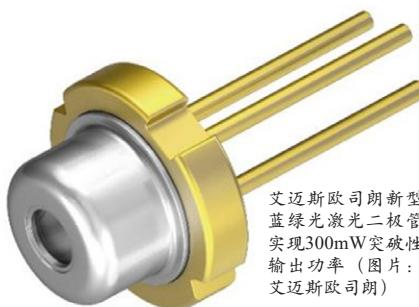

## 新型蓝绿光激光二极管助力DNA测序功率实现五倍跃升

艾迈斯欧司朗推出最新专为生命科学领域研发的蓝绿光激光二极管——PLT5 488HB\_EP，扩充其大功率激光器产品线。该二极管发射488nm波长激光，且亮度较前代产品提升五倍，在性能与能效方面较早期型号实现显著突破。这些性能指标的提升在DNA测序、流式细胞术等生命科学研究和诊断应用的可靠分析至关重要。其高性能还可助力快速精准的检测，极大拓展了大型实验室的诊断可能。该产品为半导体激光技术的突破，将助力医疗机构、医院及护理中心构建更紧凑、更具成本效益的诊断系统。

艾迈斯欧司朗研发的PLT5 488HB\_EP蓝绿光激光二极管实现300mW输出功率，其光学性能较前代产品提升五倍，电光转换效率提高逾40%。光输出功率的显著提升可实现更高测量精度，并加快生物样本处理速度。488nm激光二极管是现代诊断与科研领域的关键器件，广泛应用于血液、血清、血浆分析，以及流式细胞术和DNA测序等场景。在基因诊断应用中，依托激光穿透生物样本，利用DNA构成单元核苷酸的特异性光吸收与发射特性实现其序列精准测定。更高性能的激光二极管可显著提升分析

艾迈斯欧司朗新型

蓝绿光激光二极管

实现300mW突破性

输出功率（图片：

艾迈斯欧司朗）

结果的时效性和准确性。

蓝绿光谱段对流式细胞仪及血液检测设备等诊断设备中常用荧光染料具有高效激发效能。PLT5 488HB\_EP专为±2nm的精准波长调控与300mW的高光强输出而设计，完美契合生命科学领域对超卓显色性能与精密测量的严苛要求。其具备的高调制带宽特性可实现光强度的精细调控，大幅提升信号品质的同时能提升分析进程时效性。

新型激光二极管还具备低热阻特性，即使在高温工况下仍能保障稳定运行。该器件集成式光电二极管实现输出功率监控，内含ESD防护二极管，有效地强化产品的耐用性和高可靠性。

除生命科学研究外，该蓝绿光激光二极管在多元化应用场景中展现出卓越潜力。例如，通过扩展舞台及场馆照明的色域范围，可产生极具视觉冲击力的动态光效；在荧光显微技术领域，其488nm特定波长能显著提升成像对比度，突破传统光源对微观结构的解析极限。

目前，艾迈斯欧司朗在全球激光二极管领域拥有逾2,000项有效专利资产，始终保持行业领导地位。

## A-STAR推出全球首个工业级200毫米碳化硅开放研发生产线

新加坡科技研究局(A-STAR)推出全球首个工业级200毫米碳化硅开放研发生产线。A-STAR是新加坡政府下属的主要科研机构，成立于1991年，隶属于新加坡贸工部。

据悉，A-STAR此次推出的研发线由ASTAR微电子研究所(IME)运营，整合了从材料生长、缺陷分析到器件制造与测试的完整流程，旨在解决SiC技术开发中高成本、技术分散等挑战，加速其在电动汽车、电网及数据中心等高功率应用领域的商业化进程。该研发线将与关键设备OEM和材料供应商ASM、centrotherm，法国半导体材料公司Soite等建立密切合作。

A-STAR还公布了另外两项举措：“Lab-in-Fab”第二

阶段项目和“EDA Garage”计划。

“Lab-in-Fab”第二阶段项目的合作伙伴有意法半导体、ULVAC和新加坡国立大学，该项目专注于利用新加坡的研发生态系统来加速新的压电材料和设备的开发。

“EDA Garage”计划将为当地公司，特别是初创企业和中小企业提供具有成本效益的高级电子设计自动化(EDA)工具，促进当地的半导体公司发展。

此外，A-STAR还正式与GlobalFoundries(格罗方德半导体)和Nearfield Instruments(荷兰芯片检测设备商)建立了合作伙伴关系，以扩大先进封装的能力，并推动半导体计量技术的创新。

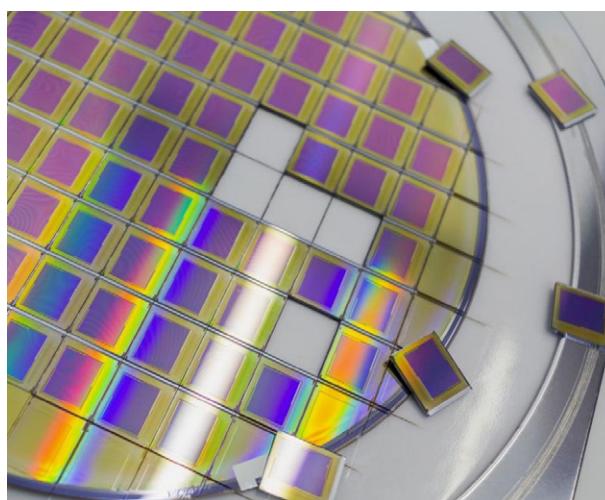

## 马波斯VBI破刀侦测：变革半导体生产的划片机

精度是半导体行业的精髓。在芯片生产中，晶圆划片工序至为关键，精度要求高，被切材料易碎，例如硅、玻璃、蓝宝石和高级复合材料，包括碳化硅（SiC）和氮化镓（GaN）。即使划片造成的缺陷十分微小，也可造成严重的生产损失。为此，马波斯成功开发了一款全新的创新方案：马波斯 VBI 破刀侦测（VBI）。这项尖端检测技术可彻底重塑划片机操作，达到更高精度和更高可靠性。

### 晶圆划片的挑战

划片机采用超薄切割刀，其芯部为粘合的金刚石耐磨材料，可达微米级高精度。切割刀的工作转速高达 30,000 至 60,000 RPM，在工作中，切割刀可发生磨损、变形和破损。主要挑战包括：

- 背面崩裂**：通常的原因是切割中含杂质，其后果是晶圆损坏或成品率降低。

- 切割刀完整性**：确保切割刀完整和无缺陷，这是切割道干净的关键。

- 形状和磨损监控**：切割刀在使用一段时间后，形状可能变成椭圆形或磨损不均匀，切削性能下降。

操作员必须确保切割刀的切削刃保持理想状况，同时最大限度缩短停机时间。然而，传统手动检测方法耗时长，且易于出错。

### 马波斯方案：马波斯VBI破刀侦测

马波斯 VBI 破刀侦测可直接应对这些挑战，实时和高精度监控切割刀。现代化的光学和数字技术提供以下特有优势：

- 全切割刀监控**：马波斯 VBI 破刀侦测测量切割刀切削刃的总伸出量、检测微观缺陷和变形，无需停止生产。

- 高速采样**：马波斯 VBI 破刀侦测在测量链中集成了数字化的光学传感器，传输实时数据，包括切割刀在高速旋转中传输。

- 综合性的切刀分析**：马波斯 VBI 破刀侦测不仅可以检测缺陷，还可以识别形状异常，监控磨损模

式，确保一致的划片质量。

- 易于集成**：马波斯 VBI 破刀侦测可检测不同类型的切割刀，通用性强，可轻松部署在不同的划片设备上。

### 变革半导体生产

马波斯 VBI 破刀侦测实时监控晶圆划片操作并配现代化的数据处理功能，为晶圆划片生产开启新的篇章。可以精确检测切割刀状况、最大限度减小切刀缺陷，例如背面崩裂，及时发现缺陷，有效缩短停机时间。马波斯 VBI 破刀侦测可将切割刀检测自动化并提供实用的信息，显著提高划片质量、工作效率并支持智能维护策略；要提高半导体生产的合格率和可靠性，这是不可或缺的工具。

### 为什么选择马波斯？

马波斯拥有 70 多年为制造业开发创新方案的丰富经验，并将继续引领精密工程技术的发展。从硅锭线切机到背面研磨机，马波斯产品可有效提高生产的工作效率和可靠性。马波斯 VBI 破刀侦测充分体现了马波斯致力于帮助客户不断优化生产的庄严承诺。

在快速发展的半导体行业，有效的检测工具，例如视觉切割刀检测器，关系到持续保持半导体生产的竞争力。马波斯 VBI 破刀侦测提供实时的划片切割刀数据、精确监控切割刀，不仅可以确保优异的划片质量，同时可以最大限度缩短停机时间和降低生产损失。马波斯 VBI 破刀侦测是您应对晶圆划片挑战不可或缺的方案。

ANGELA POSENATO

MACHINE TOOL

CUTTING PRODUCT MANAGER

## 泛林集团推出突破性导体刻蚀技术

泛林集团（Lam Research）数十年来在等离子刻蚀领域位居领先地位，不断推出革新性的等离子刻蚀技术及系统解决方案，为芯片制造商提供先进的功能和可扩展性，以满足未来的创新需求。

泛林集团于 2004 年推出的 Kiyo® 刻蚀设备在业界大获成功，经过多代发展，目前 Kiyo® 在全球已有超过 3 万个反应腔投入生产运行。

未来的器件架构将需要超越当今最先进等离子刻蚀技术的刻蚀能力才能支持 AI 时代。

新型逻辑晶体管（例如 CFET 互补型场效应晶体管）和新型存储器（例如 4F<sup>2</sup> 和 3D DRAM）架构要求刻蚀性能达到新的极限，以便塑造和形成必须在单个 300mm 晶圆上完美匹配数万亿次的、越来越精确的三维结构。为了应对形成这些三维器件的挑战，IC 制造商需要一代代持续提升其等离子刻蚀能力。

### Akara 导体刻蚀技术

近日泛林推出了先进的 Akara® 导体刻蚀系统，这是等离子刻蚀领域的一项突破性创新，也是目前最先进的导体刻蚀工具。

泛林集团凭借二十多年在导体刻蚀市场的领导地位，在 Akara® 设备实现了革命性的飞跃。Akara® 通过首次使用 DirectDrive® 固态等离子源来实现以前无法实现的刻蚀工艺控制和响应性。

DirectDrive® 能够以比以前的等离子源快 100 倍以上的速度响应来形成复杂 3D 结构所需的工艺变化。Akara® 与专利的离子能量控制和等离子脉冲系统相结合，可以提供未来 CFET 逻辑晶体管和 3D DRAM 通道所需的性能。

Akara® 继承了 Kiyo® 的传统，提供先进的技术来满足未来需求，在泛林集团的导体刻蚀创新与领导地位的历史中翻开了新的篇章。

Akara 支持环绕栅极（GAA）晶体管、6F<sup>2</sup> DRAM 和 3D NAND 器件的制程缩放，并可扩展至 4F<sup>2</sup> DRAM、

CFET 和 3D DRAM。这些器件需要极具挑战性的关键刻蚀步骤和精确的极紫外（EUV）光刻图案化，以形成复杂的三维结构。要制造出尺寸更小、纵横比更高的特征，需要达到埃级精度，这超出了当前主流等离子体蚀刻技术的能力范围。

台积电执行副总裁兼联席首席运营官 Y.J. Mii 博士表示：“随着全球对半导体的需求持续增长，需要合作伙伴的创新技术解决方案来支持更强大的新型器件架构。关键的等离子体刻蚀能力将是解决这些新器件带来的众多生产挑战的核心部分。”

#### Akara 采用了以下泛林专有的刻蚀解决方案：

- **DirectDrive**：作为业界首个固态等离子体源，其产生等离子体的响应速度比前代源快 100 倍，从而减少 EUV 光刻图案缺陷。

- **TEMPO 等离子体脉冲**：具有控制等离子体种类的独特功能，可将刻蚀选择性和微负载性能提高到新水平。

- **SNAP**：领先的离子能量控制系统，能以原子级精度塑造刻蚀轮廓。

Akara 采用全新等离子体处理技术，为 3D 芯片制造提供“无与伦比”的刻蚀精度与性能，助力芯片制造商攻克行业最严峻的制程缩放挑战。Akara® 旨在实现具有最大工艺良率的大批量生产，可提高晶圆产量并消除时间浪费，其对任何变化的响应时间均为毫秒级，能够实现行业

最先进的刻蚀均匀性控制，可提供埃米级关键尺寸下的均匀性和晶圆间可重复性。

泛林集团全球产品高级副总裁 Sesha Varadarajan 表示：基于 20 余年持续的导体刻蚀创新，我们突破性的新型 Akara 刻蚀设备借助泛林专有的 DirectDrive® 技术，以快 100 倍的等离子体响应速度，实现原子级特征的可控构建。对于

3D 芯片时代中小型复杂结构的成型来说，Akara 是导体刻蚀能力的代际飞跃。

Akara 集成在泛林的高生产率 Sense.i® 平台上，利用 Equipment Intelligence®（智能设备）解决方案自动维护以

减少整体设备维护。这些功能使芯片制造商能够从其制造设备中获得更大价值。

Akara 已被领先的器件制造商选择作为多种先进平面 DRAM 和代工 GAA 应用的生产工具。这些客户的重复订单和快速增长的安装量已经验证了它的价值。

## 泛林的高生产率 Sense.i® 平台

泛林集团全新的 Sense.i 平台提供了行业领先的产量和创新的传感技术。

泛林集团开创性的 Sense.i™ 平台基于小巧且高精度的架构，能提供无与伦比的系统智能，以实现高生产率的工艺性能，为逻辑和存储器件在未来十年的发展规划打下了基础。

以泛林集团行业领先的 Kiyo® 和 Flex® 工艺设备演变而来核心技术为基础，Sense.i 平台提供了持续提升均匀性和刻蚀轮廓控制所必需的关键刻蚀技术，以实现良率最大化和更低的晶圆成本。随着半导体器件的尺寸越来越小，深宽比越来越高，Sense.i 平台的设计旨在为未来的技术拐点提供支持。

基于泛林集团的 Equipment Intelligence® 技术，具备

自感知能力的 Sense.i 平台使半导体制造商能够采集并分析数据、识别模式和趋势，并指定改善措施。Sense.i 平台还具备自主校准和维护功能，可减少停机时间和人工成本。该平台的机器学习算法使设备能自适应以实现工艺变化的最小化，以及晶圆产量的最大化。

Sense.i 平台具有革命性的紧凑型架构，通过将刻蚀输出精度提升 50% 以上，帮助客户达成未来的晶圆产量目标。随着半导体制造商不断开发更智能、更快速、更精细的芯片，工艺的复杂性和所需步骤也在与日俱增。这需要晶圆厂拥有更多的工艺腔室，因此降低了有限空间面积条件下的总产量。Sense.i 平台的占地面积更小，无论是新建晶圆厂或是正在进行节点技术转换的现有晶圆厂都能从中获益。

泛林集团刻蚀产品事业部高级副总裁兼总经理 Vahid Vahedi 表示：Sense.i 扩展了我们的技术路线图，可以在满足客户下一代需求的同时，解决其在业务中面临的严峻成本挑战。每月有超过 400 万片晶圆采用泛林集团的刻蚀系统进行加工，这一庞大的装机数量为我们提供了丰富的经验，使我们得以研发、设计和生产出最佳的半导体制造设备。

## FlexEnable FlexiOM™ 有机薄膜晶体管材料

开发和生产用于有源光学和显示器的柔性有机电子产品领先企业 FlexEnable 宣布，其 FlexiOM™ 有机薄膜晶体管（OTFT）材料荣获国际信息显示学会（Society of Information Display, SID）颁发的“2025 年度最佳显示组件奖”。该奖项旨在表彰上一年度投放市场的最佳显示器、组件和应用。

FlexEnable 首席执行官 Chuck Milligan 表示：“我们的团队非常荣幸能够凭借 FlexEnable 高性能 FlexiOM OTFT 材料荣获享有盛誉的 2025 年度最佳显示组件奖。经过二十年的深度技术开发，其后与合作伙伴 DKE、Giantplus 和 E Ink 合作进行供应链构建计划，我们的 FlexiOM 材料和 OTFT 技术已于 2024 年投入量产，得益于我们独特的有机晶体管材料，其首款消费产品 Ledger Stax 拥有独特的 180 度曲面加固型电子纸显示屏以及独特的外形设计。”

Chuck Milligan 补充道：“OTFT 的率先量产是一个历史性里程碑，为柔性 EPD 和 LCD 显示器以及有源光学应用（包括 ePrivacy 模块、XR 像素调光器和可调镜头）的新产品设计和用例奠定了基础。”

FlexiOM 材料组合包括有机聚合物半导体和介电材料，共同构成高性能、高耐用性和高柔韧性的 OTFT，从而实现具备独特外形尺寸和功能的曲面显示器和有源光学器件。OTFT 的弯曲度可达 100 微米，甚至可以进行 3D 双轴弯曲，也丝毫不影响性能。与前面板结合时，该技术可实现独特的产品外形尺寸，例如以紧密曲面外部包裹着显示器。

FlexEnable 的 OTFT 背板制造温度不超过 100°C，与硅基 TFT 相比，可显著节省生产能耗。该制造工艺旨在沿用现有的 LCD 平板显示器工厂，利用现有设备提供高度差异化的显示器和有源光学模块。

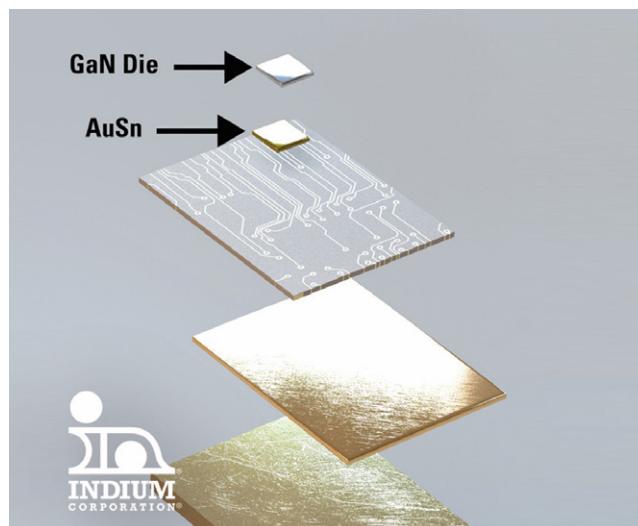

## 铟泰公司展出精密金基芯片贴装预成型件

铟泰公司（Indium Corporation）近日在美国加州旧金山举行的国际微波研讨会（IMS 2025）上展示其用于关键激光和射频应用以及 5G 通信的高可靠性金基精密芯片贴装（die-attach）预成型件。

铟泰公司是激光和光学应用领域领先的焊接材料供应商。金基合金是确保需要高熔点芯片贴装焊料的应用实现最高性能和可靠性的理想选择。除了能满足高可靠性系统苛刻的热和电要求外，它们还具有超强的抗腐蚀和抗氧化能力，使焊点持久耐用。

铟泰公司展示了特色产品 AuLTRA®75，这是一种非共晶 AuSn 预成型解决方案（75Au/25Sn），设计用于在使用金镀层较厚的芯片（如用于 5G 和其他关键军事及航空无线通信的高频率、高功率射频功率放大器器件的 GaN 芯片）的应用中提高金属间化合物可靠性。AuLTRA® 75 通过调整最终的焊料连接成分并改善润湿和气孔率，有助于提高这些关键技术的性能。

AuLTRA® 产品系列还包括 78Au/22Sn 和 79Au/21Sn 成分的产品。

AuLTRA® 芯片贴装预成型产品采用新的黄金标准，在关键的、高可靠性芯片贴装应用中提供超高的质量水平，以实现最佳性能。特点包括：

- 高精度厚度控制

- 精确的边缘质量

- 优化的清洁度

- 默认华夫饼包装方法

- 适用于基于金的合金

铟泰公司同时还展示了以下金基芯片贴装解决方案：

- AuLTRA® ThInFORMS® 是 0.00035 英寸厚 (0.00889 毫米或 8.89 微米) 80Au/20Sn 预成型件，可提高高输出激光器的整体操作效率。AuLTRA® ThInFORMS® 有助于解决短路和热传递不佳等常见的问题。

- AuLTRA® Fine Ribbon 是该公司的 Indalloy®182 级精度条带，用于大批量、全自动化激光二极管组装过程。对于这些自动供料系统，条带和卷绕的精度和高质量以及长的连续长度是最重要的。这些特性有助于减少生产停机时间并实现高效、高产量的流程，从而产生高质量的最终产品和低拥有成本。

- AuLTRA® 3.2 是一种空气或氮气回流、水溶性 AuSn 焊膏，优化用于处理金基合金的高加工温度。非常适合用于高功率 LED 模块阵列组装，确保一致且可重复的印刷性能，具有较长的钢网寿命和出色的粘性。除了满足印刷和回流需求，AuLTRA® 3.2 还提供出色的润湿性和低空洞率。

- AuLTRA® 5.1 是一种专为金基合金所需的更高温度而设计的免清洗 AuSn 焊膏。这种配方非常适合用于高功率 LED 模块阵列组装，提供了宽广的加工窗口和一致的印刷定义，即使对于超细间距也是如此。此外，AuLTRA® 5.1 在满足严格的印刷和回流标准的同时，表现出色的润湿性能和低空洞率。

**半导体芯科技**

SS SILICON CHINA

杂志、网站、公众号、

研讨会全方位服务半导体行业

**欢迎投稿 欢迎合作**

[www.siscmag.com](http://www.siscmag.com)

## 面向临时键合/解键合的ERS光子解键合技术

随着轻型可穿戴设备和先进数字终端设备的需求不断增长，传统晶圆逐渐无法满足多层先进封装（2.5D/3D堆叠）的需求。它们体积较大、重量重、且在高温和大功率环境下表现欠佳，难以适应行业的快速发展。如今，半导体制造商倾向于采用厚度小于  $100 \mu\text{m}$  的薄晶圆。然而，晶圆越薄就越容易破损，为此，行业开发了各种临时键合和解键（TBDB）技术，利用专用键合胶将器件晶圆临时固定在刚性载板上，以提升制造过程的稳定性和良率。

### 现有解键方法的局限性

完成晶圆减薄等一系列后端工艺后，如何无损地分离载板与键合胶成为关键。现有的解键方法各有优缺点：

- **热滑解键**：通过加热融化键合材料来分离晶圆和载板，但键合材料的热稳定性较低，易产生残留，影响后续加工。

- **化学解键**：使用化学溶剂溶解键合胶来确保零残留。这种方法虽然有效，大量化学品的使用不仅增加成本，也对环境造成不良影响，还可能导致晶圆翘曲。

- **机械剥离**：通过刀片施加机械应力来分离晶圆和载板。虽然避免了化学试剂和加温的过程，但外加的机械应力大大增加了超薄晶圆碎裂的风险。因此，这种方法更适用于面积较小或较厚的晶圆。

- **激光解键**：当前主流技术，利用激光透过玻璃载板照射键合胶，使其发生物理或化学变化，实现解键。然而，这种方法需特定的激光释放层（Laser release layer），工艺繁琐复杂，且玻璃载板损耗高，成本居高不下。

### 光子解键合：低成本、良率高、零应力的革新方案

为克服现有解键合技术的不足，ERS 在 2024 年推出了光子解键合机，为 TBDB 工艺带来了革命性的解决方案。该技术突破性的摒弃了传统的激光释放层，而在玻璃载板上加一层永久的光吸收反应层（CLAL，Carrier with Laser Absorbing Layer），这样做的目的是省去了激光解键合中的旋涂（Spin coating）工艺，同时也再需要昂贵的 IR 或 UV 激光器，而是采用高照射强度的闪光灯溶解载板和晶圆之间的键合胶，从而保证脱胶且无残留。

该闪光灯拥有可调控的光源波长（200 至 1100nm）以及照射强度（最高可达  $45 \text{ kW/cm}^2$ ），特殊的玻璃载板与光吸收层组合（CLAL）吸收光并将光能转化为热能，促使键合材料发生反应。由于照射时间极短，以及玻璃载板优良的光学和温度表现，不但保证了在室温下完成解键合工艺，还保护了晶圆。

作为该机器核心部件之一的玻璃载板（CLAL），通过 PVD 工艺将涂层覆盖在玻璃载板上，仅需薄薄一层就可将 55% 的光能转化为热能，并且该 CLAL 可以重复使用，大大降低了企业的耗材成本。

ERS 开创性的设计让该机器具备以下独特优势：

- 解键合无施加任何外力，无残胶

- 与传统激光解键合相比，运营成本降低超过 30%

- 可兼容多种键合材料

- 简化工艺流程：无需旋涂工艺，无需投入额外设备

- 光子解键合在工艺上的优势将大幅提高良率

此外，该机器还支持晶圆级 / 面板级先进封装，面板尺寸可达  $600 \times 600 \text{ mm}$ ，非常适合人工智能芯片、功率 IC、GPU 和 HBM 等高端应用。

ERS 光子解键合技术不仅攻克了薄晶圆解键合的技术瓶颈，更为半导体制造设定了新标准。它以低成本、高可靠性、零应力的特性，在确保高产量的同时，最大化提升良率，是推动下一代半导体先进封装工艺发展的关键一步。（来源：ERS 亚洲）

# 点点滴滴： 半导体水管理创新

IDTechEx预测，到2035年，半导体制造的用水量将翻倍。

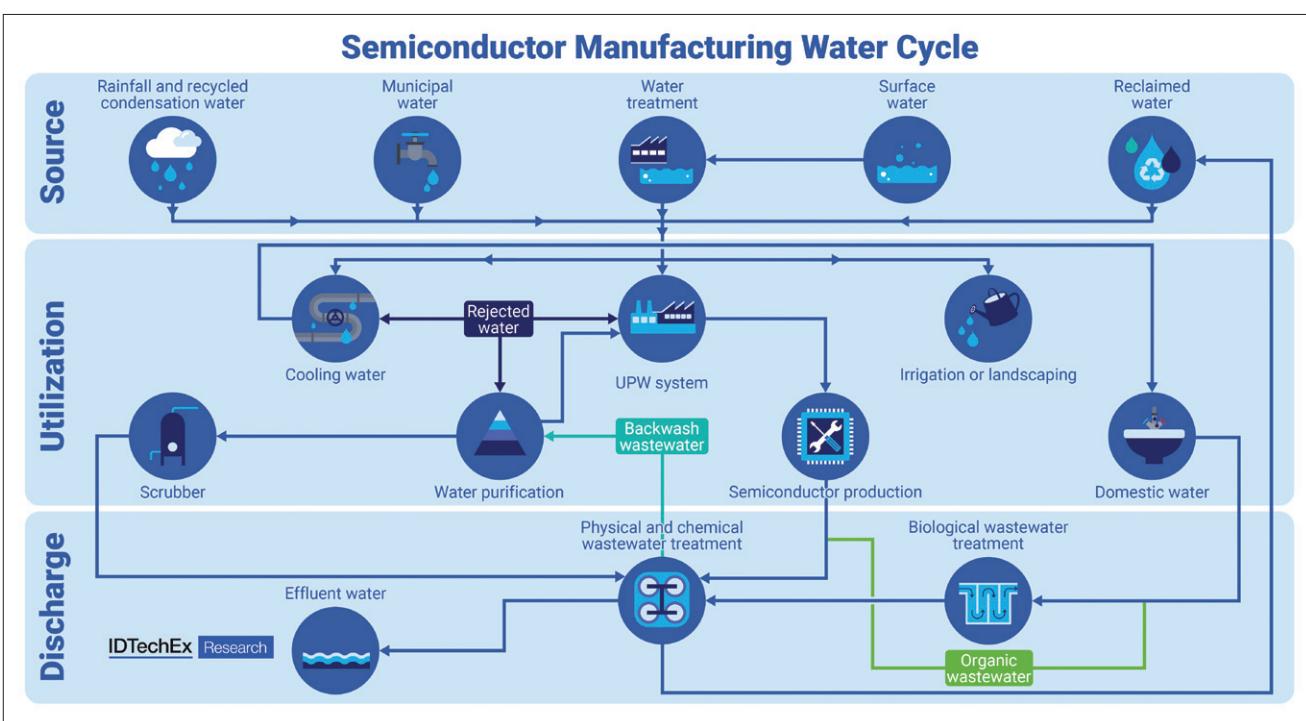

**半**导体制造不仅需要大量的能源、化学品和硅片，还需要大量的水。IDTechEx 的最新报告《2025-2035 年可持续电子产品及半导体制造：参与者、市场、预测 (Sustainable Electronics and Semiconductor Manufacturing 2025-2035: Players, Markets, Forecasts)》预测，随着对集成电路的需求持续上升，到 2035 年，半导体制造的用水量将翻倍。仅在 2023 年，半导体巨头台积电就报告其用水量达到惊人的 1.01 亿立方米，这凸显了这个快速发展的行业对水的巨大需求。

此外，随着节点技术的进步，制造工艺步骤的数量也在增加，并且单

晶圆工具的使用开始取代批量处理工具，这使得减少用水量的任务既具有挑战性，也更加关键。由于许多半导体晶圆厂位于水资源高度短缺的地区，如中国台湾地区和美国亚利桑那州，因此半导体制造商采取行动减少这种巨大的水消耗至关重要，这也是在更广泛的领域内寻求可持续电子产品的一部分。

对于半导体制造商来说，水管理是复杂的，这是由制造过程中对水的极高纯度要求所导致的，这种高纯度的水被称为超纯水 (ultra-pure water, UPW)。然而，正在实施的水管理技术有可能减轻人们对水资源短缺的担忧，同时还能降低运营成本。

## 再生水使用量增加

现在，大多数半导体制造商都在一定程度上对水进行回收或再利用，并设定了年度目标，以提高当前的水再利用水平，应对不断上升的取水率。恩智浦 (NXP)、安森美 (Onsemi) 和德州仪器 (TI) 等许多公司现在都在其冷却塔中重复利用废水。将废水再处理成超纯水的难度更大，但要实现半导体制造中的用水可持续性，就有必要采用新的水处理系统。2020 年至 2023 年间，SK 海力士 (SK Hynix) 的再生水使用量增加了 51%，部分原因是其三家晶圆厂的缺水程度被评定为“高”或“中高”。预计这还能通过减少市政用水来降低运营成本。

作者：Thomas Bithell, IDTechEx 技术分析师

## 用水效率

工艺优化也能够降低用水量。许多半导体制造商已将减少每片晶圆的用水量列为实现可持续发展的关键目标，以消除水资源短缺的风险。这对一些企业来说是个问题，因为对于中芯国际等公司而言，对晶圆的需求增加以及晶圆复杂度的提升导致每片晶圆的用水量增多。随着节点技术的进步，降低每片晶圆的用水量变得愈发困难，因为新技术往往需要更多的工艺步骤。

不过，仅仅缩短冲洗时间就能大幅节省用水。格罗方德（GlobalFoundries）将蚀刻后的冲洗时间从10分钟缩短至5分钟，每年可节水1万立方米，在IDTechEx的报告中还有许多类似的例子。

## 水源多样化

通过水资源的多样化，可以消

除水资源短缺的风险。安装雨水收集等设施可以降低运营成本，因为对市政用水的需求减少了。Tower Semiconductor公司在其位于得克萨斯州的工厂中，利用了干燥室内环境所需空气的除湿水。中芯国际也利用空调冷凝水和雨水收集来减少市政用水量和相关成本。

这些技术或许只能回收总用水量的一小部分，但仍然具有不可估量的价值。可以从海水中获取更多的水源，台积电新竹工厂就采用了海水淡化技术。对于那些靠近海岸的晶圆厂来说，利用现场海水淡化技术可以解决许多围绕可持续用水的担忧，尽管这会消耗大量能源。

## 废水分类

对废水进行分类和分离可间接提高水的再利用率。这是因为能够使处理过程更加高效。许多工艺可能会

在水中引入特定的污染物，而这些污染物可以通过较为简单的水处理方式进行处理。湿法加工设备供应商斯克林（SCREEN）公司现在能够在其设备内实现排水隔离，以便对废水进行分类。华邦电子（Winbond）使用20条不同的管道，以确保不会发生交叉污染，并能够对污染物进行单独处理。这也使得从废水中回收利用污染物成为可能，从经济角度来看，这也是有益的。

## 关于半导体可持续制造的更多见解

上述所有策略都有可能通过减少用水量，对环境和制造商的利润带来双双益处。在许多情况下，减少能源、化学品和材料的消耗，对于寻求提高可持续发展能力和降低运营成本的电子产品制造商而言，在多个方面都是可取的。◆

半导体制造过程中用水系统的简化图示。来源：IDTechEx

# 扩展片上网络架构的创新方法

云计算的演进引发了对先进解决方案的迫切需求，这些解决方案可以最大限度地提高计算效率，同时最大限度地减少物理和能源限制。现代数据中心严重依赖多核处理器，常常将100多个核集成在单个芯片中。

**这**些处理器旨在通过共享网络、内存和存储资源，将每个内核转变为可租用的处理能力单元，来处理基于云的应用程序日益增长的需求。

然而，随着处理器性能变得越来越强大，片上网络（network-on-chip, NoC）已成为扩展过程中的一个关键瓶颈。NoC 负责在 CPU 内核和内存之间路由数据，它依赖于金属互连，当按比例缩小时，金属互连会带来独特的挑战。在这些互连中，更高的电阻会增加功耗，并且需要额外的信号中继器来保持长距离传输中的性能。

此外，在保持 NoC 尺寸不变的情况下，不断增加的内核数量和高密度逻辑的扩展，也导致 NoC 面积大幅增加。这些因素都增加了设计复杂性，影响了实现更小、更高效设计的目标。

为应对这些挑战，人们提出了各种创新解决方案，但每种方案都存在权衡取舍。二维网状拓扑结构虽然简单且可扩展，但随着内核数量的增加，通信延迟也会受到影响。

其他方法，如无路由器配置或针对特定工作负载的优化，虽然可以提高性能，但对于像云计算中使用的通用系统来说，往往不太实用。虽然通过增加每个通道的信号数

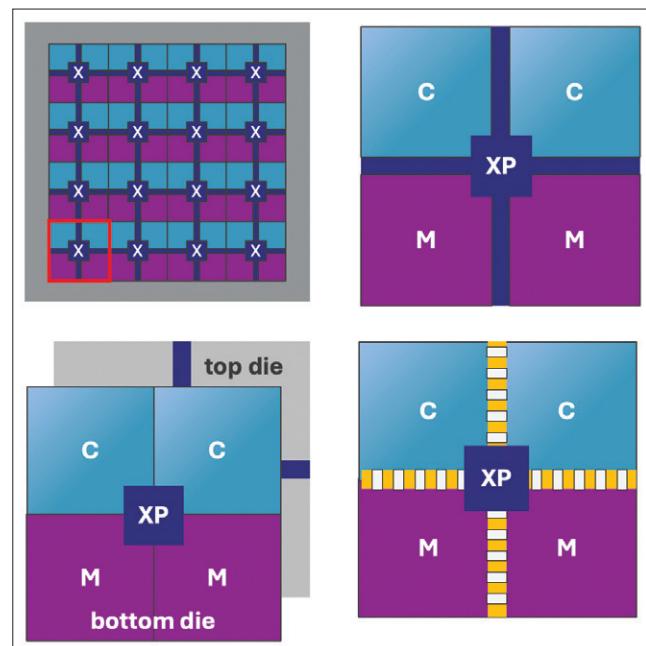

图1：二维（2D）参考系统（左上）和其中结构块（右上），展示了在单一的前段制程（FEOL）和后段制程（BEOL）堆叠内的NoC通道布线和逻辑。底部展示了两种新方法：（左）三维（3D）堆叠设计，显示将NoC通道布线分离到一个与A10逻辑芯片键合的专用布线芯片上；（右）背面集成方法，将NoC通道布线集成到BSPDN的背面金属层中。

作者：Moritz Brunion, imec公司设计-技术协同优化研究员；

James Myers, imec公司系统技术协同优化项目总监

量来扩展 NoC 链路的吞吐量可以提升数据传输速率，但这通常会导致成本上升和资源需求增加，使 NoC 的情况变得更复杂。

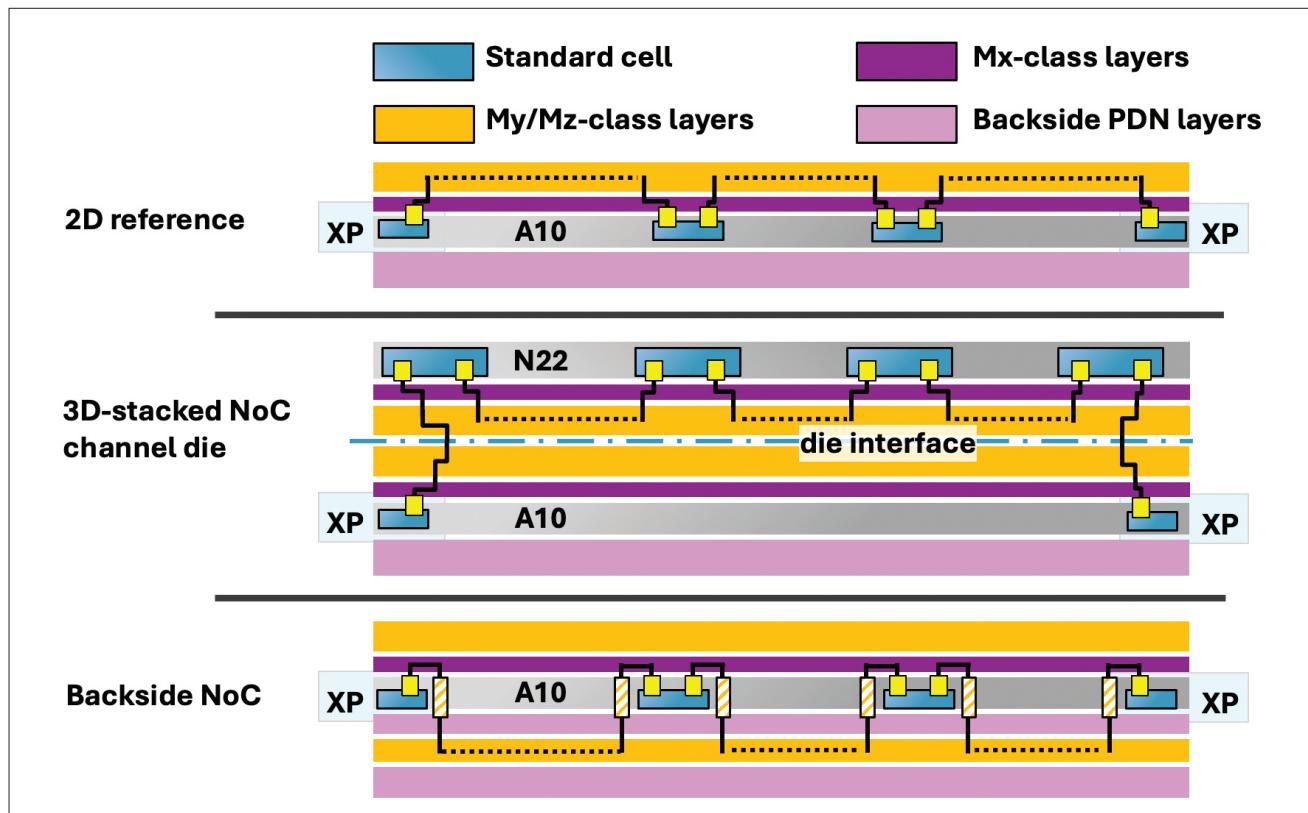

为应对这些限制，imec（比利时微电子研究中心）的研究人员率先提出了两种变革性方法：①将 NoC 通道迁移到专用芯片上，②将 NoC 通道与背面电源传输网络（BSPDN）集成。这些策略以系统 - 技术协同优化（STCO）原则为指导，旨在克服扩展限制，同时平衡成本和性能。在这些方法中，NoC 通道与 BSPDN 的协同集成，为未来设计此类高核数量系统提供了特别有前景的成果。

### 独立的NoC布线专用芯片

imec 提出的第一种新方法是将 NoC 通道布线迁移到一个独立于主逻辑层的专用芯片上。通过晶圆对晶圆的面对面混合键合技术，这种架构可以利用垂直方向上的高带宽数据传输，同时将每比特的能耗降至最低。这种 NoC 芯片可以采用 N22 等不太先进的制造工艺来制造，从而

大大降低了生产成本。

这种设计因为减少了金属层而简化了后段制程（BEOL）配置，从而优化功能集成效率。进行实时布线决策的 NoC 路由器仍保留在主逻辑芯片上，以确保延迟保持在最低水平。

然而，这种设计也并非没有挑战。功率分配变得更加复杂，因为额外的芯片需要有自己的电源基础设施。物理设计实验还表明，与传统的 2D NoC 系统相比，传输延迟增加了 8%，并且每比特跨通道链路传输的能耗上升了 15%。

### 将NoC通道与晶圆背面的BSPDN集成

第二种解决方案是将 NoC 通道与晶圆背面的 BSPDN 共同集成。BSPDN 现有的金属层经过优化，具有更宽的间距和更低的电阻，为在高时钟速度下进行长距离的 NoC 通道布线提供了理想的基础。这种集成利用了背面互连的宽松设计约束条件，以实现高效的信号传输。

图2：(上) 二维参考设计的技术堆栈横截面，显示了A10逻辑前端中的NoC通道和交叉点(XP)。(中) 将NoC布线完全卸载到一个专用芯片上，从而释放了主逻辑芯片上的布局和布线资源。在这种情况下，因为交叉点(XP)位于A10逻辑芯片中，在单独的专用芯片中的通道可以采用较旧的制程技术制造。(下) NoC通道与电源传输网络，以及位于逻辑芯片前端中的中继器共享布线资源。NoC缓存岛占用高性能CPU内核1%至2%的面积(相比之下，在二维参考设计中，NoC需要高达10%的芯片面积)，另外还为NoC通道增加了两层专用的背面金属层。

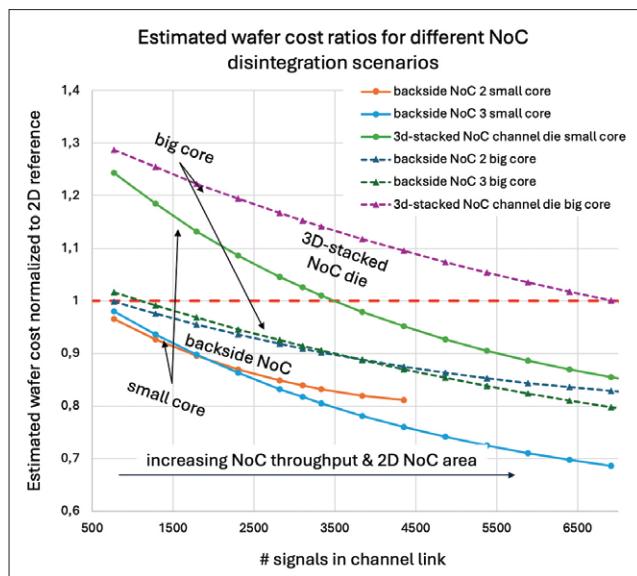

图3：不同NoC集成方案的晶圆成本比率估算，以二维基准为归一化标准。随着NoC通道宽度的增加，背面集成的成本优势变得更加明显。

为了实施这种方法，研究人员进行了一些设计调整。首先，他们设计了一种双向布线方案，使水平和垂直的NoC通道能够共享同一金属层。这就减少了所需的总层数，降低了成本和整体芯片占用面积。其次，由于BSPDN目前不支持在背面放有源器件，因此将信号中继器作为紧凑的“孤岛”放置在主逻辑芯片上。这些中继器以较小的面积开销确保了强大的信号强度，同时为其他逻辑组件腾出了主逻辑芯片中的通道布线空间。最后，将NoC通道与BSPDN集成需要解决数据传输和功率传输之间的共享布线资源问题，这增加了电阻压降（IR drop）的风险，并可能影响性能。为了应对这些挑战，研究人员在电源分布网络（PDN）间距和电阻压降（IR drop）与中继器“孤岛”的面积占用之间进行了权衡，既保持了BSPDN的优势，又确保了稳定的电压水平，同时还支持跨NoC的可靠数据传输。

## 成本效益分析支持NoC背面整合

在对这两种方法进行比较时，重要的不仅是技术上的权衡，还有成本效益，以确定满足不断增长的需求的最佳解决方案。专用芯片方法提供了更大的灵活性和定制选项，但由于需要额外的全处理晶圆，因此制造成本较高。相比之下，将NoC通道与BSPDN集成可以重复利用现有的基础设施，仅需添加几层额外的金属层。这大大降低了成本，并优化了正面硅片的使用，使其成为云服务器CPU等需

要高内核密度的应用的一个有吸引力的选择。

背面集成还具有出色的可扩展性。随着每个处理器中的内核数不断增加，对更宽NoC通道的需求也随之增加。通过利用背面金属层，这种方法可最大限度地减少拥塞，并能够在不显著增加硅片占用面积的情况下，实现更高的数据吞吐量。这些特性使其成为下一代芯片架构的理想解决方案。

## 更广泛的影响和未来发展方向

尽管背面NoC集成在云服务器CPU上具有很高的适用性，但它与其他应用（如具有粗粒度、规则拓扑结构的GPU和加速器）的相关性仍在探索之中。然而，这项技术的广泛应用依赖于电子设计自动化（EDA）工具的进步。目前，实现背面NoC通道需要专门的工作流程，这既耗费人力又成本高昂。随着电子设计自动化工具的发展，预计它们将简化设计流程，使背面集成在各种应用场景中更容易实现且更具实用性。

总之，NoC通道与BSPDN的集成是芯片设计领域的一项重大突破。通过同时解决布线和功率传输方面的难题，这种方法体现了系统-技术协同优化（STCO）原则的强大作用。随着对可扩展、高性能架构的需求持续增长，像背面NoC集成这样的创新将在塑造半导体技术的未来以及推动下一波计算技术进步方面发挥关键作用。◆

**Moritz Brunion**

Researcher Design-Technology Co-optimization

Moritz Brunion received the M.Sc. degree in electrical and computer engineering from the University of Bremen, Germany, in 2022. He is currently a researcher at imec, Leuven, Belgium, and his research focuses on design-technology co-optimization for fine-grained 3D systems.

**James Myers**

Program Director System Technology Co-optimisation

James Myers holds a MEng degree in Electrical and Electronic Engineering from Imperial College in London. He spent 15 years at Arm, leading research from low power circuits and systems, through printed electronics, to DTCO activities. He joined imec in 2022 to lead the System Technology Co-optimisation program, with the aim of building upon established DTCO practices to overcome the numerous scaling challenges foreseen for future systems. James holds 60 US patents, has taped out 20 SoCs, has presented at ISSCC and VLSI Symposium, and has published in IEDM and Nature.

# High NA EUV光刻技术的新进展

近期关于 High NA EUV（高数值孔径极紫外）光刻技术发展和应用的报道很多。在 2025 年 SPIE 先进光刻与图形化（Advanced Lithography+Patterning）会议上，一些顶尖的芯片厂商也报告了 EUV 光刻技术的一些应用进展，显示 EUV 技术的商用应用及发展进一步加速，进入了新的阶段。EUV 技术一直以来面临着多重挑战，包括高成本、复杂的光学系统以及需要在高精度下制造光罩等。然而，随着技术不断发展成熟，EUV 逐渐突破了制程限制，尤其在 10nm 及以下的制程中展现出了其不可替代的优势。

## 英特尔：High NA EUV一次曝光即可实现低至8nm的分辨率

英特尔是第一家购买 High NA EUV 光刻机的芯片厂商，据悉，每台机器价值高达 3.5 亿欧元。英特尔工程师 Steve Carson 在 SPIE 先进光刻与图形化会议上透露，英特尔去年在其位于俄勒冈州希尔斯伯勒附近的 D1 开发工厂安装并开始使用两台 ASML High-NA Twinscan EXE:5000 EUV 光刻工具，目前已使用这些系统在一个季度内处理了多达 30,000 片晶圆。

英特尔工厂的早期结果显示，高 NA 机器仅用一次曝光和“个位数”的处理步骤就能完成早期机器需要三次曝光和大约 40 个处理步骤才能完成的工作。英特尔正在使用其 18A 制造技术来测试高 NA 工具，并计划于今年晚些时候与新一代 PC 芯片一起进行量产。

英特尔计划在未来几年使用这些机器生产其 14A (1.4nm 级) 芯片。ASML 的 Twinscan EXE High NA EUV 光刻工具只需一次曝光即可实现低至 8nm 的分辨率，与单次曝光即可提供 13.5nm 分辨率的低 NA EUV 系统相比，这是一个显著的改进。虽然当前一代的低 NA EUV 工具仍可通过双重图案化实现 8nm 分辨率，但这会延长产品周期并影响产量。与低 NA EUV 系统相比，高 NA EUV 工具将曝光场减少了一半，这需要芯片开发人员更改其设计。考虑到高 NA EUV 光刻系统的成本和特性，不同芯片制造商对其采用会有不同的策略。

## imec：基于High NA EUV单次曝光获得的20nm间距金属线良率达90%

在本次 SPIE 先进光刻与图形化会议上，imec 展示了其在基于 High NA EUV 光刻设备的单次曝光图案化工艺获得的 20 纳米间距金属线结构上进行的首次电气测试 (e-test) 结果。

imec 展示对 20 纳米间距金属线的首次电气测试结果，对于验证 High NA EUV 图案化生态系统在下一代半导体制造中的应用具有重要意义。

imec 展示对 20 纳米间距金属线的首次电气测试结果，对于验证 High NA EUV 图案化生态系统在下一代半导体制造中的应用具有重要意义。

经过电气测试后，imec 的研究表明，蛇形和叉形金属线的良率超过了 90%，这意味着其在生产过程中出现的随机缺陷较少。电学测试结果证实了，High NA EUV 光刻扫描仪及其周边生态系统能够对如此小尺寸的线宽 / 线距 (lines/spaces) 进行图形化处理。这一进展对于验证 High NA EUV 技术在下一代半导体制造中的应用具有重要意义。

2024 年 8 月，imec 曾率先展示了在单次 High NA EUV 光刻曝光步骤中形成的具有行业相关性的逻辑和动态随机存取存储器 (DRAM) 结构。作为下一个关键步骤，imec 这次展示了，使用金属氧化物 (MOR) 负性光刻胶经过单次 High NA EUV 图形化处理后获得的 20 纳米间距金属线结构，其良率超过 90%。这一性能指标是在两种不同的测试结构上获得的，即蛇形 (或曲折形) 结构和叉形

结构，这些结构旨在揭示随机缺陷方面的信息。

imec 研发高级副总裁 Steven Scheer 表示：“这是首次展示通过单次 High NA EUV 图形化处理获得的 20 纳米间距金属线路的电学良品率。这些结果初步验证了 High NA EUV 光刻技术及其周边生态系统的功能，包括先进光刻胶和底层材料、光掩模、计量技术、(变形) 成像策略、光学邻近效应校正 (OPC)，以及集成图形化和蚀刻技术。我们将继续与图形化生态系统合作伙伴合作，开展相关工艺工作，以进一步提高良品率，并将这些技术转移给我们的制造合作伙伴。”

imec-ASML 的 High NA EUV 生态系统包括领先的芯片制造商、材料和光刻胶供应商、掩模供应商以及计量专家等合作伙伴，他们共同致力于为亚 2 纳米节点的下一代半导体制造开发和优化 High NA EUV 光刻技术，包括进一步优化光刻胶性能，减少缺陷，从而确保该技术能够顺利应用于低于 2 纳米节点的半导体制造中。

imec 先进图形化部门总监 Philippe Leray 补充道：“电学测试是 High NA EUV 技术验证的关键一步。这些电学测试结果也为我们指明了前进的方向。当与电子束检测相结合时，对金属化蛇形和叉形结构的电导率测量能够提供有关导致良品率降低的随机缺陷（即分别为断路和短路）的信息。这些见解有助于我们的生态系统合作伙伴制定减少随机缺陷的策略。我们正在进行的工作之一是专注于优化光刻胶性能，在对随机失效影响最小的情况下降低达到良品率所需的剂量，我们正与光刻胶领域的合作伙伴密切合作开展这项工作。”

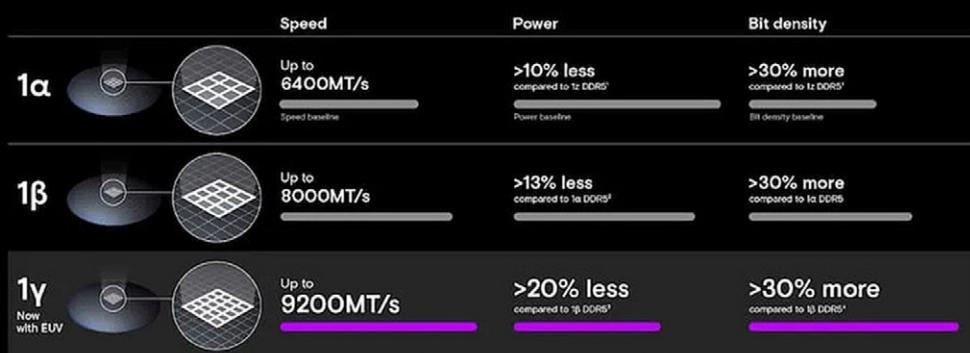

## Gen-over-gen DRAM technology leadership

Micron continues to lead the industry, advancing from 1 $\alpha$  (1-alpha) and 1 $\beta$  (1-beta) to 1 $\gamma$  (1-gamma) technology

<sup>(1)</sup> 1 $\beta$  is the previous version of DRAM technology before 1 $\alpha$ . <sup>(2)</sup> Based on calculations comparing 24Gb density DDR5. <sup>(3)</sup> Based on calculations comparing 16Gb density DDR5. <sup>(4)</sup> Calculated based on overall bits per wafer comparing 1 $\beta$  and 1 $\gamma$  process.

<sup>(5)</sup> © 2024 Micron Technology Inc. All rights reserved. Micron, the Micron logo, the Nitro logo, NitroSense™, and other Micron trademarks are the property of Micron Technology Inc. All other trademarks are the property of their respective owners.

总之，这项研究标志着 High NA EUV 技术在先进半导体制造中的商业化应用迈出了关键一步，具有重要的行业意义。

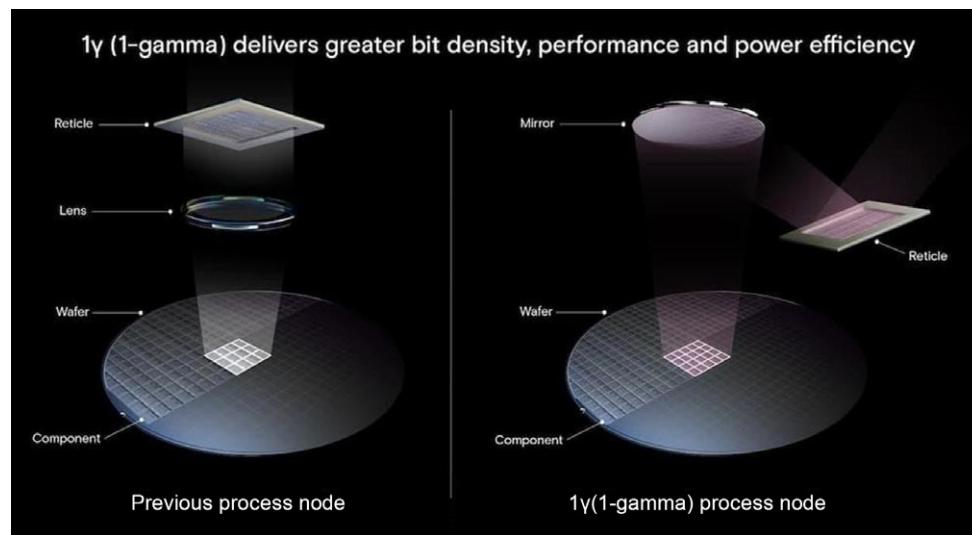

## 美光：采用EUV曝光技术推出基于1 $\gamma$ 制程的DRAM

2025 年 2 月 25 日，美光 (Micron) 正式推出基于全新 1 $\gamma$  (1-gamma) 制程技术的 16Gb DDR5 存储器，这是美光首次采用极紫外光 (EUV) 曝光技术。新存储器不仅比前代产品具备更高效能、更低功耗，制造成本也有望进一步下降。此外，美光表示，其 1 $\gamma$  制程技术（第六代 10nm 级节点）未来将应用于其他 DRAM 产品。

美光基于 1 $\gamma$  制程的主力产品为 16Gb DDR5 存储器，在业界标准电压 1.1V 下运行时，资料传输速率达 9200 MT/s。与前代 1 $\beta$  制程的 16Gb DDR5 存储器相比，新款存储器耗电量降低 20%，位元密度提升 30%，当新芯片的良率达到 1 $\beta$  16Gb DRAM 的水平时，制造成本预计将下降。

美光指出，1 $\gamma$  DRAM 是继领先业界的 1 $\alpha$  (1-alpha) 和 1 $\beta$  (1-beta) DRAM 制程节点之后，再次树立的重大里程碑，并将有效赋能云端、工业与商业消费端及边缘 AI 设备（如 AI PC、智能手机及汽车等）等未来运算平台。

美光 1 $\gamma$  制程是该公司首次采用 EUV 光刻技术，其他领先的存储器制造商数年前就已导入 EUV。虽然美光较晚采用，但 1 $\gamma$  制程相较于现有产品线具备显著优势。

美光并未透露 1 $\gamma$  制程使用多少层 EUV，但推测主要是在关键层导入 EUV 技术，这些层若使用传统的多重曝

光 (multi-patterning) 技术，将延长生产周期并影响良率。美光表示，1 $\gamma$  制程采用 EUV 搭配深紫外光 (DUV) 多重曝光技术，并引入新一代高介电常数金属栅极 (High-K Metal Gate) 与全新后段制程 (BEOL) 电路。

目前美光 1 $\gamma$  DRAM 主要在日本晶圆厂生产，该厂于 2024 年安装美光首套 EUV 设备。

随着 $1\gamma$ 存储器产量提升，美光计划在日本与中国台湾的晶圆厂增加更多EUV设备。

### 台积电：开发EUV薄膜技术

台积电去年曾在相关技术会议上介绍了其在EUV光刻技术方面的成功经验：通过增加EUV光刻机的数量、提高晶圆产量以及优化防护薄膜的使用，台积电实现了生产效率的显著提升。

薄膜（pellicle）在芯片制造中用于减少图案缺陷，薄膜位于光刻机内部，位于光罩或掩模（很像包含要印在晶圆上的图案蓝图的模板）正下方，其作用是捕捉微小颗粒，否则这些颗粒会粘附在光罩上并最终印在晶圆上，导致芯片故障。

作为全球第一大晶圆代工厂，台积电已经开发出自己的EUV薄膜技术，以最大程度地提高生产效率。

值得注意的是，ASML曾是首家成功开发出可用于EUV光刻系统的商业薄膜供应商，2019年，ASML将相关技术许可授权给了三井化学，使其成为全球唯一的EUV薄膜商用供应商。三井化学正投资于用于芯片光刻的纳米管薄膜技术。该公司计划在日本南部的岩国大竹工厂建设一座新厂，每年生产5,000片基于纳米管的薄膜。三井化学表示，这些纳米管薄膜在抵抗EUV光刻的严苛条件下，比目前的硅基薄膜更具优势。

此外，三星、FST和S&S Tech等韩国公司也在积极开发EUV薄膜，推动EUV薄膜的国产化。而且，三星的“EUV协同任务组”部门目前正在致力于开发下一代碳纳米管（CNT）薄膜，以期解决现有薄膜的限制。

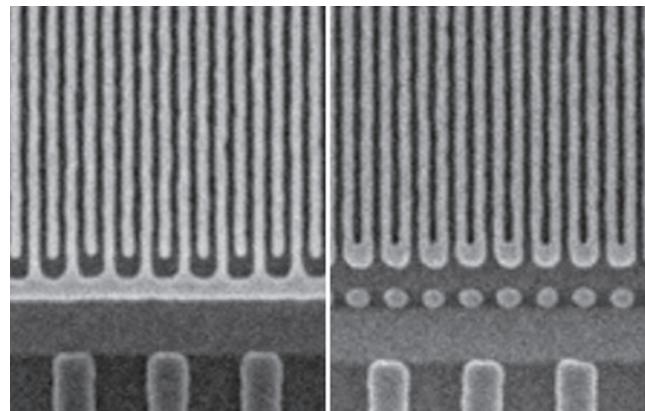

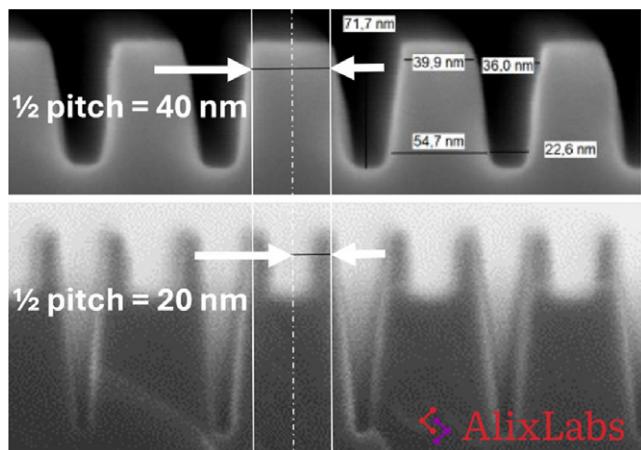

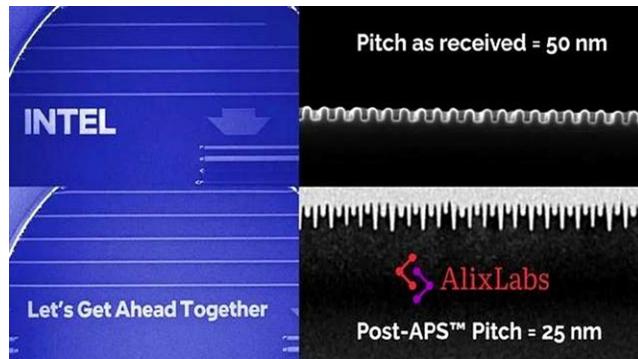

### 创新技术：原子层蚀刻（ALE）间距分割

瑞典公司AlixLabs AB开发了一种创新技术——原子层蚀刻（ALE）间距分割技术（简称APS），用以降低7纳米以下半导体制造中光刻工艺的成本和提高效率。该技术通过蚀刻来分割晶圆上的纳米结构，从而实现线宽减半，他们去年已在德国Fraunhofer IPMS的300毫米晶圆上验证了APS技术。

使用APS生成的结构可以用于制造FinFET晶体管的鳍片等。该技术适用于逻辑和存储器件工艺，并有潜力通过蚀刻过程替代双重或四重掩模步骤，将掩模层的成本降低多达40%。

使用APS也成功在英特尔提供的测试硅片上蚀刻出与商用3nm半导体工艺相对应的结构。该公司在SPIE先进光刻与图案化展上分享了这一成果。

该公司CEO Suyatin表示：APS可以帮助行业减少对多重图案化解决方案的依赖，同时降低成本和环境影响。我们的技术能够在硅片上生产10nm以下级别的特征。在英特尔测试平台计划的帮助下，我们已经证明，只需蚀刻，就可以在量产硅片上生产5nm以下级别的特征。

APS提供了一种按照摩尔定律继续缩小芯片组件尺寸的方法，同时降低成本并提高产量。因为它允许制造商实现更小、更密集的组件，而无需多个复杂的光刻步骤，这些步骤既昂贵又耗费资源。APS工艺减少了半导体生产

的资本投资、能源消耗和总体环境影响，因此，APS 在半导体制造中极有价值。

## 未来趋势

随着 EUV 光刻技术，尤其是 High NA EUV 从研发走

向量产，EUV 光刻技术将成为推动摩尔定律延续的核心动力。英特尔、imec 等厂商的技术突破，美光、三星在存储领域的应用，以及薄膜、APS 等相关配套技术的成熟，标志着 EUV 进入规模化商用的关键阶段。未来，随着生态系统的完善和成本优化，EUV 将进一步推动芯片向更小、更高效的方向发展，重塑全球半导体产业格局。◆

## 参考资料

- [https://siliconsemiconductor.net/article/121229/Imec\\_demonstrates\\_electrical\\_yield\\_for\\_20nm\\_pitch\\_metal\\_lines\\_obtained\\_with\\_High\\_NA\\_EUV\\_single\\_patterning](https://siliconsemiconductor.net/article/121229/Imec_demonstrates_electrical_yield_for_20nm_pitch_metal_lines_obtained_with_High_NA_EUV_single_patterning)

- <https://baijiahao.baidu.com/s?id=1826902271335653956&wfr=spider&for=pc>

- <https://etn.se/index.php/nyheter/71382-lunds-halvledarbolag-ett-steg-narmare-300-mm.html>

## 电动汽车电池测试解决方案

Seica S.p.A. 作为电子测试解决方案的全球领导者最近宣布 PILOT BTP 的全球首发，这是 Seica 电池测试机 Pilot BT 系列的最新解决方案。

电动汽车市场快速发展带来的主要挑战之一是确保电动汽车模块的可靠性和安全性，而电动汽车电池单元之间电气连接的质量和可靠性是确保其性能和安全性的基础。新款 Pilot BTP 专用于小批量原型或 NPI（新产品导入制造）生产场景的电气连接测试，同时也适用于电池单元以非重复几何形状排列的电池测试。PILOT BTP 是一个自动化水平系统，配有四个飞行测试头，提供真正的全尺寸并联电动汽车电池组测试。其测试区域面积为 1050 x 865 毫米，具有较高的灵活性，能够处理不规则布局，操作速度超过每分钟 600 次测试，是原型测试的理想解决方案。

PILOT BTP 是 Seica 为电池制造商提供的各类飞针测试解决方案的又一补充，这些解决方案包括 Pilot BT 和 Pilot BTV，它们具有出色的灵活性，能够处理各种类型的电池，包括目前使用的最大规格的电池。Pilot BT 能够同时对超过 32 个电池进行精确的并行开尔文测试，测试速度接近每分钟 4,800 个电池，其超大的测试区域（1200 x 1200 毫米）和重型处理系统确保了自动化生产线

中电池组的高效管理。对于需要从多面进入的复杂配置，Seica 的 Pilot BTV（立式电池测

试机）提供自动三面进入功能，使其成为“双层”电池组的理想选择，此种类型的电池组需要在两面进行连接测试以及从顶部进入测试。凭借其创新的三维探测结构和全面的测试能力，Seica 于 2024 年荣获著名的墨西哥技术奖。

Seica 的 MINI80-ACIR 测试机是另一款专为电动汽车领域开发的创新测试解决方案。该解决方案的研发旨在提供一种简单有效的方法来进行 ACIR 和电压测试，使电池组制造商能够在工厂检验时直接在 OEM 包装中对电池进行测试，以及进行生产测试，以确保组装电池组中的电流正确分布。该解决方案包含 Seica 的 Mini 80 系统，该系统可确保高效、精确的测量，并能满足严格的内阻 (IR) 测试要求，包括交流内阻 (ACIR) 测量，通常以 1kHz 和 100mA 电流进行测量，以及每个电池的 4 线开尔文测量。MINI80-ACIR 的最大扩展能力为 640 个非复用通道，可同时测试多达 160 个电池，并可配置手动夹具或集成到自动化系统中进行在线生产测试。◆

# 真空系统：交钥匙项目指南

在工业环境中实施真空系统时，您所选择的途径会对项目的效率、成本和成功产生重大影响。交钥匙项目提供了一种简化的解决方案，由一家公司负责从概念构思到完成交付的整个过程。

**尽**管交钥匙真空系统项目有许多优点，但也要考虑其潜在的弊端以及如何加以缓解。本指南将探讨如何在提升交钥匙真空系统项目优势的同时，降低其潜在弊端的影响。

## 交钥匙项目的优势

### 一站式服务

交钥匙项目为客户提供便利，客户只需与一家公司合作，无需协调多个供应商和承包商。这节省了时间，减少了混乱，并简化了项目流程。在交钥匙项目中，供应商应作为唯一的联系点，确保从项目开始到结束都能提供连贯、无缝的体验。

### 降低成本

交钥匙项目通常成本较低，因为解决方案提供商通常拥有良好的供应商关系和更强的购买力，能够协商到更优惠的价格。此外，固定成本的交钥匙项目有助于缓解财务上的不确定性。寻找能够以固定费用处理项目所有方面，从而提供经济高效解决方案的供应商。

### 缩短交付周期

交钥匙项目通常完成速度更快，因为设计、采购和施工可以同时进行。这使客户能够更快地从投资中受益。具备全面项目管理能力的供应商将有助于缩短项目时间，高效地交付任务。

交钥匙真空系统 - 由一家公司负责从概念构思到完成交付的整个过程，为寻求优化运营的企业提供了一种实用而有效的方法。（来源：Busch）

作者：BUSCH

### 提高质量

交钥匙项目通常能提高质量，因为负责的公司对设计和施工都有控制权，最大限度地减少了涉及多个供应商时经常出现的误解或错误。通过这种全面的控制，最终的系统不仅能够始终满足客户的期望，而且往往能够超越客户的期望，提供质量卓越的真空系统。

### 单一责任点

由一家公司对最终产品负责，降低了相互推诿的风险。供应商应对项目结果负全责，让客户安心，并提供可靠的联系点，以便在出现任何问题时获得服务保障。

## 关于交钥匙项目的常见担忧和误解

### 控制力有限

客户可能会觉得在交钥匙项目中对设计和施工过程的控制力有限。有能力的供应商应通过进行详细的咨询和分析来解决这一问题，以确保理解所有需求，然后进行协作设计过程，由本地工程师与客户密切合作设计解决方案。

### 灵活性降低

交钥匙项目的灵活性可能较低，项目一旦启动，进行更改就会很困难。为了缓解这一问题，寻找具有优先考虑灵活性的项目理念的供应商，该供应商应提供及时的反馈，并为任何变更请求提供选项，以保持项目高效推进。

### 依赖交钥匙解决方案提供商

客户依赖交钥匙提供商提供高质量、可靠的解决方案。如果提供商未能交付，客户可能会面临不理想的结果，或需要完全重启项目。为确保真空系统的最佳性能，选择拥有高技能专家、先进选型工具，并且在客户所在的应用领域和行业中有成功安装记录的供应商。这将确保整个过程的可靠性和安全感。

### 分包项目管理的性价比

虽然内部处理项目似乎更具成本效益，但重要的是要考虑这样做的隐性成本。选择内部管理关键项目可能会使员工偏离其核心工作，有可能降低企业核心业务领域的生产力。此外，内部团队可能缺乏有效处理复杂真空系统项目所需的专业技能、经验和资源。将项目管理分包给经验

丰富的供应商，他们可以利用其专业知识、工具和特定行业的经验，最终实现更简化的项目流程和更少的意外问题。

### 难以实现理想的项目范围

如果供应商不愿意定制解决方案，交钥匙项目可能会限制范围选择。双方协作的方法可确保客户在定义项目范围、优化价值和根据特定需求定制解决方案方面拥有控制权。此外，客户通常会发现为自己的需求选择最佳解决方案具有挑战性。供应商需要能够通过投资回报率计算展示所提供的任何选项的价值，从而展示每个选项的效率和有效性，客户才会考虑选择这样的供应商。

### 设计和施工过程中缺乏透明度

交钥匙项目有时可能缺乏透明度，使客户难以了解进展情况。协作的项目方法包括在所有阶段进行清晰的沟通和定期更新，尤其是在设计和施工过程中。

### 结论

总之，对于寻求优化运营的企业来说，交钥匙真空系统提供了一种实用且高效的方法。通过简化流程、降低成本和提供单一责任点，交钥匙解决方案解决了与复杂工业项目相关的许多挑战。然而，交钥匙项目的成功在很大程度上取决于选择一个能够在效率与灵活性、协作和质量承诺之间取得平衡的合作伙伴。

作为交钥匙真空解决方案的领导者，服务全球的普旭集团（Busch Group）在兑现这些承诺方面独具优势。从初始设计咨询到安装以及后续服务，Busch 拥有一套涵盖整个项目生命周期的综合方法，确保每个细节都符合客户的需求和行业标准。凭借丰富的经验、先进的工程工具，以及在全球范围内成功实施项目的良好记录，Busch 能够确保交付高质量的成果，满足客户的运营需求并超越预期。选择 Busch 集团（包括 Busch Vacuum Solutions、Pfeiffer Vacuum+Fab Solutions 和 centrotherm clean solutions 三大品牌），客户不仅能够获得交钥匙解决方案，更能拥有专业的合作伙伴，可以最大限度地提高真空系统项目的效率、可靠性和整体价值。◆

# 从实验室到晶圆厂 利用下一代3D X射线技术解决系统性良率问题

随着2.5D和3D集成电路在半导体制造中的应用日益广泛，封装设计的复杂程度不断提升，这凸显了在将这些复杂架构推向市场时，实施稳健的质量保证措施的重要性。

随着小型化等趋势，以及围绕人工智能的持续热潮，推动了对更高性能的需求，下一代芯片正在日益紧凑的体积内突破功能极限。这种转变给制造商带来了一系列新的挑战，不仅是在竞争激烈的市场中保持领先所需的速度，还包括管理与更复杂结构相关的更高的制造和材料成本。为了解决这一问题，制造商必须采用全面的检测策略以保持竞争优势。在整个设计和制造阶段及时发现并解决问题，对于高效扩大生产规模、提高良率和加快市场进入至关重要。

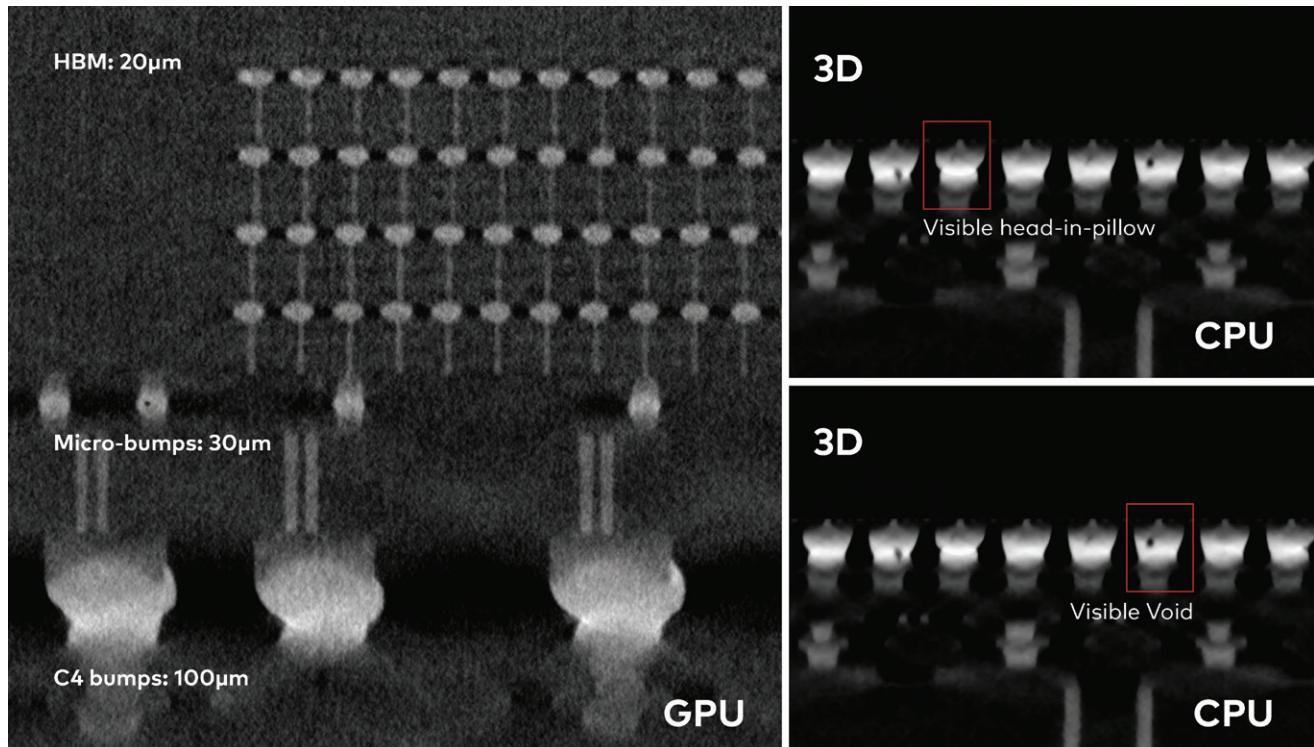

一直以来，二维（2D）X射线等无损检测方法，在先进封装的高度专业化参数范围内，特别是在面向量产的应用中，发现缺陷的速度和分辨率，都无法满足需求。然而，在人工智能驱动的缺陷识别技术的支持下，新一代三维（3D）X射线技术即将改变这一状况。

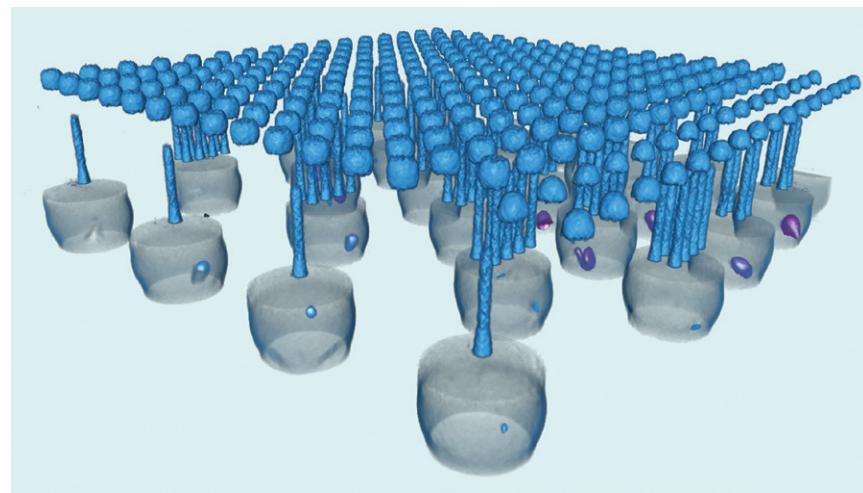

## 3D X射线与人工智能驱动的缺陷识别相结合

3D X射线技术及其支持软件（如Comet Yxlon CA20所示）的进步，有望彻底改变3D IC的检测过程。

该技术能够精准、快速地检测出哪怕是微小的缺陷，为制造商提供有价值的洞察，以提高良率和质量，同时不牺牲生产线的时间。

从捕获的图像中提取的详细信息远远超出了目视检查的范畴，使制造商能够做出明智的决策，并在系统性问题（如焊球空洞或“枕头效应”缺陷）形成之前就加以解决。

图1是通过Comet Yxlon CA20拍摄的CPU示例，展示了现代3D X射线技术揭示复杂细节的能力，包括直径小至10微米的缺陷。这些扫描能够快速完成，凸显了该技术在提供快速准确结果方面的效率。

此外，对于GPU等多层芯片，通过重建其3D体积生成“虚拟切片”的能力，使用户能够可视化不同层的横截面，例如C4凸点、中介层凸点和高带宽内存（HBM）凸点。由于各层的堆叠特性会遮挡底层特征，传统的光学检测或2D X射线方法很难达到这种细节水平。

尽管捕捉高分辨率图像很重要，但当今3D X射线技术的真正优势在于其人工智能驱动的软件功能。像Comet Yxlon的CoS Insights软件包等工具可以快速识别和评估缺陷，如

图1：市售CPU的效果图，展示了带有可见空洞的C4凸点（直径：65微米）、硅通孔（TSV）和微凸点（直径：20微米）。所有图像版权归Comet Yxlon所有，请勿复制或传播。

作者：COMET YXLON

图2：左图为市售GPU的重建X射线扫描虚拟切片，该GPU具有100 $\mu\text{m}$ 的C4凸点、30 $\mu\text{m}$ 的微凸点和20 $\mu\text{m}$ 的高带宽内存（HBM）凸点。右图为市售CPU的重建X射线扫描虚拟切片，该CPU有大约65 $\mu\text{m}$ 的C4凸点。所有图像版权归Comet Yxlon所有，不得复制或传播。

焊球错位和枕头效应问题，并分析其大小和严重程度。通过评估凸点偏移、芯片倾斜和缺陷发生概率等关键参数，该技术可对元件状态进行全面评估。

### 将3D X射线技术集成到Fab环境中

所有这些高度详细的信息都能为芯片的潜在性能提供深刻洞察。然而，在新产品导入（NPI）的背景下，即使是流程早期的微小优化，也可能对后续的良率产生显著影响。因此，将任何关于产品质量的洞察直接反馈到生产流程中以进行改进至关重要。

这正是下一代Comet Yxlon CA20的用武之地。如今，CA20通过集成EFEM装载机实现了自动上下料功能的升级，确保了平稳连续的操作，无需人工干预。通过无缝集成到

晶圆厂（Fab）生产线中，CA20为制造商提供了生产质量的实时监控，能够尽早发现趋势和潜在问题，使制造商能够采取主动措施，确保产品质量的一致性。

借助向导引导功能和自动检测工作流程（包括一键式操作），操作人员可以快速学会有效使用该系统。同时，先进的硬件确保了即使在最短的扫描时间内也能提供可靠的测量结果，并以机器可读格式输出结果，便于数据分析和解读。然后，系统会使用符合SECS/GEM标准的强大AI软件自动分析这些结果中的关键缺陷参数，确保缺陷识别和报告的一致性和准确性。

此外，软件方面也有进一步的创新。

除了缺陷识别外，CA20还配备

了智能工具，例如我们的批次管理器软件包（Batch Manager package），它能够同时扫描多个芯片，并根据部件ID灵活组织扫描结果；而剂量管理器软件包（Dose Manager package）则持续监控和跟踪样品所承受的X射线剂量，同时考虑管功率和样品距离，以避免损坏敏感组件。

### 主要启示

在当今复杂的芯片领域，要保持竞争力、降低管理成本并加快产品上市速度，必须依靠全面的检测策略。通过引入3D X射线检测等先进技术，尤其是与人工智能驱动的缺陷识别技术相结合，制造商不仅可以在整个设计和研发阶段，甚至在生产线上都能提高良率、质量和效率。◆

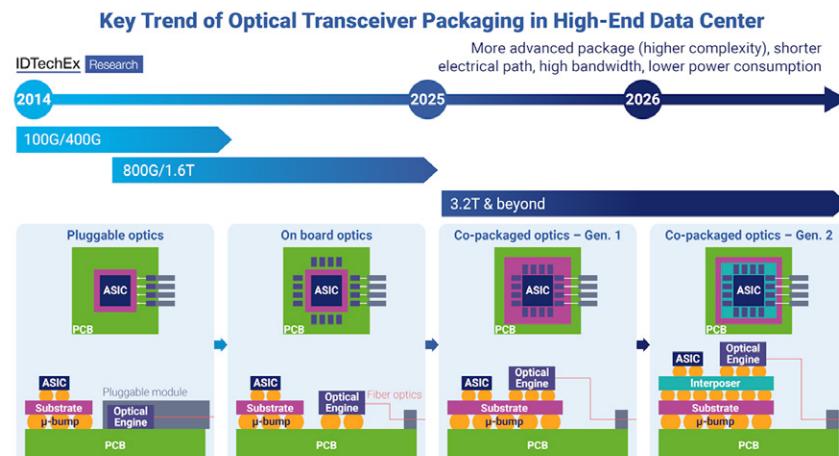

# 共封装光学技术发展

## 共封装光学（CPO）的兴起

在过去十年中，在 $64 \times 400$  Gbps 或 $32 \times 800$  Gbps 可插拔光收发模块应用的推动下，数据中心以太网交换机的容量已从 $0.64$  Tbps 飙升至 $25.6$  Tbps。然而，这些现有外形规格的高速模块面临着多种挑战，包括所需的电气和光连接器密度问题，以及不断攀升的功耗问题。

为实现支持每个模块 $800$  Gbps 及以上速率的下一代光引擎，通信速率必须翻倍，达到每通道至少 $100$  Gbps。这一提升在交换机插座、主板和边缘连接器上引入了严重的信号完整性问题，导致串行器 / 解串器 (SerDes) 接口的功耗大幅增加。在未来的以太网交换中，这些信号完整性问题可能导致 I/O 功耗超过交换机核心的功耗。此外，标准可插拔模块的集成密度受限于 QSFP/OSFP 外形规格，需要尚未广泛普及的先进热管理解解决方案。

共封装光学 (Co-Packaged Optics, CPO) 或共封装光学器件为解决这些挑战提供了一个有前景的方案。与传统可插拔模式不同，CPO 将光模块直接集成到交换机 ASIC 基板上，缩短了电气传输距离，有效解决了信号完整性问题。这一方法已获得了主要数据中心的关注。然而，优化 CPO 的封装策略仍是行业持续讨论和发展的话题。IDTechEx 的最新报告《共封装光学 2025-2035：技术、市场与预测》(Co-Packaged Optics 2025-2035: Technologies, Market, and

Forecasts) 探讨了 CPO 技术的这些进展，以及推动其应用的封装技术。

## 英伟达推出基于CPO的新型网络交换平台

在 2025 年全球图形技术大会 (GTC 2025) 上，英伟达 (NVIDIA) 基于 CPO 技术，发布了两款新型网络交换平台——“光谱 -X 光子学平台” (Spectrum-X Photonics) 和“量子 -X 光子学平台” (Quantum-X Photonics)。

国际技术研究与咨询公司 IDTechEx 首席技术分析师 Yu-Han Chang 介绍了相关情况。

“光谱 -X” 瞄准基于以太网的架构，将于 2026 年推出，其配置范围从 128 个 $800\text{Gb/s}$  端口到 2048 个 $200\text{Gb/s}$  端口，总带宽达到 $400\text{Tb/s}$ 。“量子 -X” 支持无限带宽互连技术 (InfiniBand)，计划于 2025 年底推出，采用 $200\text{ Gb/s}$  的串行器 / 解串器 (SerDes)，可提供多达 144 个 $800\text{ Gb/s}$  的端口。

这两个平台都采用了台积电 (TSMC) 的 3D 混合键合技术来实现其 CPO 技术，它们将成为世界上首个 3D 堆叠硅光子学引擎 (3D-stacked silicon photonics engine)。这两个平台都是与台积电及其供应链中的光学、光纤和模块合作伙伴合作开发的，其中包括相干公司 (Coherent)、鲁门特姆公司 (Lumentum)、康宁公司 (Corning)、富士康 (Foxconn) 和日月光集团 (ASE)。这些研发旨在解决以人工智能为核心的数据中心的带宽扩展和能源效率问题。

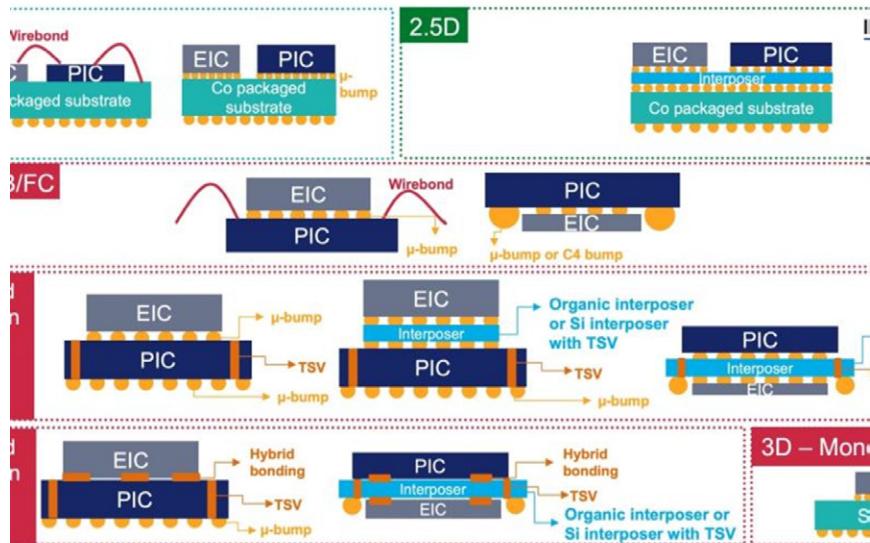

## 先进半导体封装是CPO的关键推动因素

传统的可插拔光模块由于较长的电气走线，在信号损耗和延迟方面存在局限性。相比之下，CPO 使光模块更靠近交换硅芯片。CPO 的成功依赖于先进的半导体封装技术，这些技术能够实现光子集成电路 (PIC)

图1：高端数据中心光模块发展趋势。来源: IDTechEx

和电子集成电路 (EIC) 的高密度集成，以及光模块与交换专用集成电路 (ASIC) 或加速处理器 (XPU) 的无缝集成。为实现这一目标，采用了各种封装方法，包括 2.5D 中介层、硅通孔 (TSV)、扇出型晶圆级封装 (FOWLP)，以及越来越多采用的带有混合键合的 3D 集成技术。

其中一项领先的创新技术是铜 - 铜无凸点混合键合技术 (Cu-Cu bumpless hybrid bonding)，与间距为 40-50 微米的传统微凸点相比，它能够实现间距小于 10 微米的芯片间互连。这减少了寄生效应和热阻，同时提高了带宽密度和输入 / 输出扩展能力。硅通孔通过增强功率传输和实现堆叠芯片之间的垂直通信，带来了额外的优势。然而，这些方法增加了制造的复杂性，需要精确的对准、先进的材料以及热管理解决方案。

在数据中心中，CPO 的集成旨在提升 I/O 带宽并降低能耗。PIC 与 EIC 及交换 IC 的结合方式，会显著影响面积和边缘带宽密度，以及封装寄生效应。这些因素直接关系到收发器的 I/O 带宽和能效，不当的集成可能抵消硅光子学的优势。

对于 CPO 而言，光子与电子组件的集成可通过多种方法实现，每种方法均具备独特优势与挑战：

**- 3D 单片集成：**这是最先进且仍处于研发阶段的技术，它通过最小化工艺改动，将光子组件嵌入现有电子工艺节点中，使有源光子器件与驱动电子器件共置于同一芯片内。这种方式可减少寄生效应，并省去接口焊盘和凸点，简化封装。但单片集成通常采用较旧的 CMOS 节点，导致光子性能欠佳且能耗较高。尽管存在这些局限，其阻抗失配极小且封装简洁。

图2: CPO的基本结构

**- 2D 集成：**将 PIC 与 EIC 并排置于 PCB 上，通过引线键合或倒装芯片连接。该方法操作简单且成本较低，但会产生很大的寄生电感，并由于单边连接而限制了总 I/O 带宽。虽然 2D 集成易于封装，但其对引线键合的依赖会制约收发器带宽并增加能耗，使其在高性能应用中效率较低。

**- 3D 混合集成：**通过硅通孔、高密度扇出、铜 - 铜混合键合、有源光子中介层等先进半导体封装技术，将 EIC 堆叠在 PIC 上方，大幅降低寄生效应。在 3D 集成中，先进封装技术的应用支持细间距能力，提升性能。然而，散热仍是挑战——EIC 产生的热量会影响 PIC，需搭配先进热管理方案。尽管存在散热难题，3D 混合集成因封装寄生效应最小化，可实现更高性能。

**- 2.5D 集成：**作为折中方案，将 EIC 和 PIC 倒装焊至带 TSV 的无源中介层上。该方式可保持与 3D 集成相近的寄生效应控制和细间距能力，但因需要中介层走线，复杂度增加。2.5D 集成在性能、成本与制造周期之

间取得平衡，但其寄生效应高于 3D 混合集成。

综上所述，每种集成方法均需在性能、复杂度与成本之间权衡，具体选择需基于应用场景的特定需求与约束条件。

关于先进半导体封装技术的更深入技术见解，IDTechEx 公司提供了一系列全面的报告。《2025-2035 年先进半导体封装：预测、技术、应用》(Advanced Semiconductor Packaging 2025-2035: Forecasts, Technologies, Applications) 涵盖了技术趋势、市场预测和主要参与者。《2025-2035 年共封装光学：技术、市场和预测》(Co-Packaged Optics (CPO) 2025-2035: Technologies, Market, and Forecasts) 则专注于共封装光学特定的封装挑战和集成策略。关于材料和工艺方面，《2025-2035 年先进半导体封装的材料和工艺：技术、参与者、预测》(Materials and Processing for Advanced Semiconductor Packaging 2025-2035: Technologies, Players, Forecasts) 研究了 2.5D 流程和铜 - 铜混合键合等创

新技术，以及对有机介电模块的10年预测。

### 台积电的3D混合键合技术及其在共封装光学中的作用

台积电的系统集成芯片（SoIC）技术，为英伟达“光谱-X”和“量子-X”中CPO所使用的3D集成奠定了基础。SoIC-X 变体是台积电先进的无凸点混合键合工艺，能够垂直堆叠逻辑芯片，或间距小于10微米互连的异构组件，显著缩短了互连长度、降低了电阻和延迟。

基于这项技术，台积电的紧凑型通用光子引擎（COUPE™）平台将电子集成电路（EIC）直接堆叠在光子集成电路（PIC）之上，最大限度地缩短了它们之间的电气路径。这种配置提高了能源效率并降低了延迟，这是高速人工智能网络中光互连的两个关键要求。

COUPE™还可以集成硅通孔，以便在各层之间垂直传输功率和信号。硅通孔有助于减少电压降（IR drop）和电感，支持高效功率传输和密集垂直通信。然而，将有源EIC堆叠在对热敏感的PIC上带来了散热方面的挑战。需要像液冷、热通孔和散热片等先进的热管理解决方案来缓解这一问题。

在英伟达的应用中，“光谱-X”和“量子-X”平台都采用了COUPE™技术，利用台积电的SoIC-X技术将一个65纳米的EIC与一个PIC相结合。台积电预计到2025年完成对支持小尺寸连接器的COUPE平台的验证，并计划到2026年将其全面集成到CoWoS封装中。

展望未来，COUPE平台的未来版本旨在通过将光学器件直接集成到

图3：2025年与2035年CPO市场的增长情况。来源：IDTechEx

交换机或处理器封装中，支持6.4 Tb/s的带宽，并最终达到12.8 Tb/s的带宽。这是满足人工智能工作负载不断增长的数据需求的必要发展，因为传统的可插拔光模块在功率和密度方面正逐渐达到极限。

日前，台积电负责业务开发及全球业务的资深副总经理兼副联席COO张晓强在公司2025年技术论坛欧洲场上表示，台积电暂无为先进制程导入High-NA EUV的必要。他表示，台积电最新公布的1.4nm级逻辑制程A14，即便未采用High-NA EUV图案化设备，其性能提升依然显著。台积电技术团队正持续通过工艺优化，在现有基础上进一步拓展Low-NA EUV技术可覆盖的制程范围。只要该路径仍能持续推进，就没有必要在量产中采用成本高昂的High-NA EUV设备。

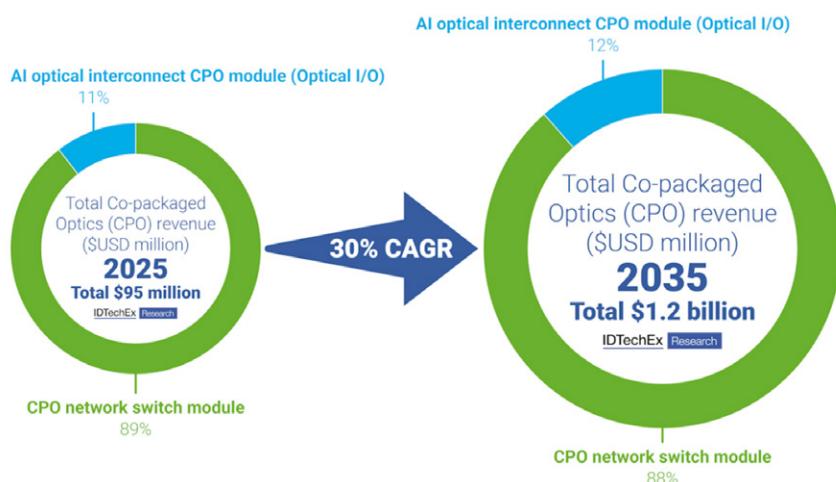

### 2035年CPO市场将超过12亿美元

共封装光学（CPO）的应用仍处于早期阶段。像英伟达和台积电这样的公司正在推动其发展，同时得到了不断发展的封装和光子学供应商生态系统的支持。预计这种光子和电子组

件的集成将在解决未来数据中心架构中的带宽和功率挑战方面发挥越来越重要的作用。

根据IDTechEx公司的数据，到2035年，CPO市场预计将超过12亿美元，从2025年到2035年的复合年增长率（CAGR）为28.9%。CPO网络交换机预计将在收入方面占据主导地位，这是因为每个交换机可能最多集成16个共封装光学PIC。IDTechEx评估，通过CPO集成，在高性能网络交换机中有实现25%效率提升的潜力。人工智能系统的光互连预计将占市场的20%，每个人工智能加速器通常使用一个光互连PIC，以满足先进计算应用中对高速数据处理和通信不断增长的需求。

IDTechEx的报告对CPO技术的最新进展进行了广泛的探讨，深入研究了关键技术创新和封装趋势，全面分析了整个价值链。该报告的核心是认识到先进的半导体封装是CPO技术的基石。报告对主要行业参与者的活动进行了详尽的评估，并提供了详细的市场预测，预测了CPO的应用将如何重塑未来数据中心架构的格局。

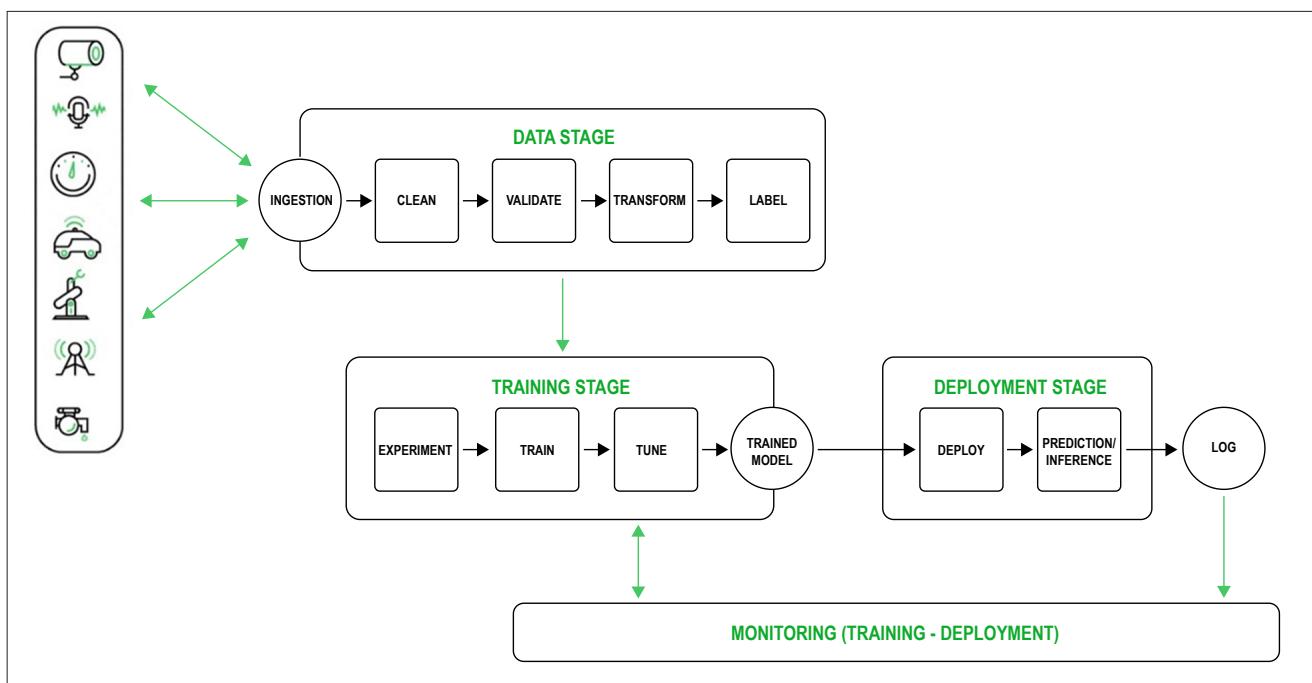

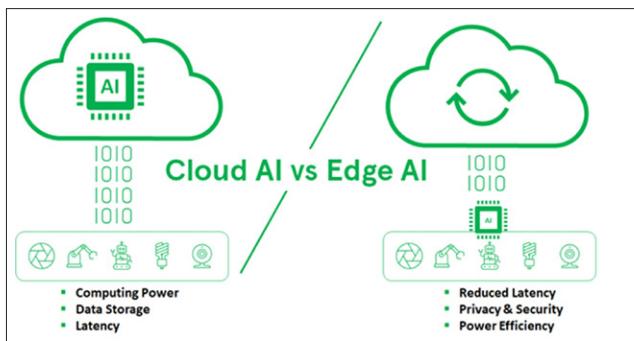

# 边缘 AI：物联网实施新标杆

**A**I与物联网系统的融合改变了数据的处理、分析与使用方式。多年以来，各种AI解决方案始终基于云端部署，而如今边缘AI的兴起，在提升运行效率、增强安全性和改善运营可靠性方面提供了颇有潜力的解决方案。本文旨在深入剖析边缘AI的复杂性，探究其构成要素、应用优势及其快速演进的硬件支持体系。

## AI 演变：从云端到边缘

传统物联网设备直接依赖云端基础设施进行AI处理。边缘设备传感器产生的数据需要传输至云端进行分析和推理运算。然而，随着物联网应用对网络边缘实时决策需求的激增，这种模式面临着严峻挑战。涉及到海量的数据规模、延迟问题以及带宽限制，这让云端处理模式在许多应用场景中难以为继。

边缘AI的出现，将处理能力更靠近数据源——也就是物联网设备本身。这样的转变减少了持续将数据传输到云端的需求，并实现了一种对许多应用至关重要的实时处理方式，例如自动驾驶汽车、工业自动化和医疗保健等领域。

## 边缘AI系统的核心组件

边缘AI系统由专用硬件与软件组件构成，具备本地化采集、处理和分析传感器数据等核心能力。边缘AI模型通常包含以下要素：

- **数据采集硬件**：若未配备专用传感器并集成处理单元及存储器，数据采集将无法实现。现代传感器内置数据处理能力，可对数据进行初步筛选与转换。

- **训练与推理模型**：边缘设备需搭载预训练的专用场景模型。由于边缘设备的计算资源有限，可在训练阶段根据特征选择和转换对模型进行训练，以提升其性能表现。

- **应用软件**：边缘设备上的软件通过微服务触发AI处理，微服务通常基于用户请求来调用；此类软件可运行训练阶段就已具备定制化功能和聚合特性的AI模型。

## 边缘AI的优势

与传统云端模型相比，边缘AI具有许多显著优势：

作者：e络盟技术团队

- **安全性提升**：本地数据处理降低了敏感信息在云端传输过程中的泄露风险。

- **运行可靠性增强**：边缘 AI 系统减少了对网络连接的依赖，在间歇性或低带宽的网络环境下仍能保持稳定运行。

- **灵活性**：边缘 AI 支持根据具体应用需求定制模型与功能，这对需求各异的多样化物联网环境至关重要。

- **低延迟**：该模式将数据处理与决策时间降至最低限度，是契合自动驾驶和医疗诊断等实时应用的关键特性。

## 实施边缘 AI 所面临的挑战

尽管边缘 AI 具备诸多显著优势，其实施仍面临多重挑战。为边缘设备开发机器学习模型，意味着需要处理海量数据、选择合适的算法，并优化模型以适应受限的硬件环境。对于许多制造商，尤其是专注于大规模生产低成本设备的制造商而言，从头开发这些功能所需的投入可能令人望而却步。

这种困境催生了对可编程平台的需求。当前，业界正加速向专用 AI 架构转型，支持在广泛的功耗性能区间实现弹性扩展。这些架构在保持通用设计灵活性的同时，又能满足特殊的处理需求。

## 专用硬件在边缘 AI 中的作用

随着 AI 和机器学习应用场景的不断拓展，市场对定制化硬件的需求与日俱增，这类专用硬件能够有效应对 AI 技术领域的独特需求。然而，传统的通用处理器在满足 AI 特殊需求，特别是神经网络处理方面表现乏力，尽管其在制造工业和通用工具链方面仍具重要价值。

为填补这一空白，半导体制造商纷纷推出新型 AI 加速器，既能提升通用处理器的性能，又可保留其优势。此

类加速器专为神经网络所需的并行处理而设计，为 AI 运算提供更高效的执行路径。

- **并行架构和矩阵处理器**：这些并行架构（比如图形处理器中的架构）对神经网络训练非常奏效。矩阵处理器正是基于此原理设计而成，比如谷歌的张量处理单元专为加快神经网络处理的核心环节——矩阵运算而开发。

- **存内计算**：这项创新技术通过可变电阻器与存储单元的互联，将内存阵列直接转化为神经网络结构，这样有效规避了传统内存访问的瓶颈问题，从而在运算速度和能效方面实现重大突破。

## 边缘 AI 的未来：创新与机遇

随着边缘 AI 领域的持续进化，为应对日益增长的 AI 处理需求，新技术与新架构不断涌现。其中，微型机器学习 (TinyML) 的进展尤为瞩目，它将 AI 能力延伸至超低功耗设备。虽然 TinyML 并非适用于所有应用场景，但它无疑推动了 AI 在更广泛设备中的普及。

- **现场可编程门阵列 (FPGA)**：FPGA 具备动态可重构架构，完美契合 AI 技术的快速发展。相较于 GPU 和 CPU，FPGA 赋予设计者快速构建和测试神经网络的能力，并能针对特定应用需求定制硬件。这种灵活性在航空航天、国防装备、医疗设备等高风险领域至关重要，这些领域的产品生命周期通常较长，且需要支持现场部署新算法。

- **图形处理器 (GPU)**：尽管 GPU 拥有强大的并行计算能力，但其能效与散热管理代价不菲。即便如此，在虚拟现实、机器视觉等需要强劲算力的应用中，GPU 仍是首选方案。

- **中央处理器 (CPU)**：尽管 CPU 在并行处理方面存在固有缺陷，但仍被广泛集成于各类设备中。Arm 推出的单指令多数据 (SIMD) 架构等创新技术，虽提升了 CPU 运行 AI 算法的性能，但与 GPU、FPGA 等其他计算设备相比，通常存在速度较慢、功耗较高的局限性。

## 结语

从云端 AI 到边缘 AI 的转型，正在深刻改变物联网系统处理与运用数据的方式。边缘 AI 通过将 AI 处理能力部署至数据源头，显著提升了安全性、可靠性和灵活性，因

而得到广泛的应用。然而，边缘 AI 的实施需要全面考量硬件与软件组件的协同，并妥善解决在资源受限环境中部署 AI 的特殊挑战。

随着 AI 普及程度的提高，市场愈发需要擅长解决边缘计算特殊问题的专用硬件。从矩阵处理器、存内计算到 FPGA 和 TinyML，这些新兴技术将重塑新一代边缘 AI 解决方案。如此一来，应用工程师得以紧跟技术发展浪潮，从而充分释放边缘 AI 的潜力，打造更具创新性和竞争力

的解决方案。

在 AI 技术日新月异的发展环境中，工程师与开发者必须持续跟进最新技术趋势。如需深入探索 AI、掌握核心要素，并学习如何在实际项目中应用 AI 技术，欢迎访问我们的 AI 中心 (AI Hub)。无论是图像分类、语音与手势识别，还是状态监测与预测性维护，AI 中心都能提供全方位支持，为您提供全面的产品解决方案、技术资源和专业知识，助您充分解锁 AI 技术的最大潜能。◆

## 艾迈斯欧司朗优化红外激光技术提升3D传感技术

当今工业机器人环境传感、多模态人脸识别、物体检测及机器视觉等现代应用对 3D 传感技术的需求持续增长。艾迈斯欧司朗基于垂直腔面发射激光器 (VCSEL) 核心技术，正式推出两款创新产品——BIDOS® P3435 Q BELAGO 1.2 点斑投射器与 BIDOS® P2433 Q/V105Q121A-850 泛光投射器。

得益于 BIDOS® P3435 Q BELAGO 1.2 点斑投射器与 BIDOS® P2433 Q/V105Q121A-850 泛光投射器的协同作用，3D 传感技术现可实现更高精度的三维感知（图片：艾迈斯欧司朗）

艾迈斯欧司朗 BIDOS® P3435 Q BELAGO 1.2 点斑投射器采用 940 纳米波长光源，通过集成红外垂直腔面发射激光器 (VCSEL)、先进光学元件及工业级防护结构，为基于主动立体视觉 (ASV) 与结构光 (SL) 技术的 3D 传感系统提供核心解决方案。该器件生成的高密度点斑图案 (15,000 个独立光点) 可实现精准深度图构建，赋能工业机器人或无人运输系统，使其能够在所有光照条件下实现自主障碍物检测与规避，并支持实时目标追踪功能。相较于前代产品，艾迈斯欧司朗最新迭代版本在 3D 传感精度方面实现了重大突破。其紧凑型封装尺寸 (4.2mm × 3.6mm × 3.3mm) 为客户提供兼具空间效率与功

能扩展性的 3D 传感解决方案。

BIDOS® P2433 Q V105Q121A-850 泛光投射器是一款集成化 VCSEL 组件，主要应用于飞行时间 (ToF) 测距方案以及需要均匀环境照明补光的 3D 传感方案。通过将 VCSEL 发射器与人眼安全专用光电二极管集成至尺寸仅 3.3mm × 2.4mm × 1.2mm 的超微型封装内，艾迈斯欧司朗在确保简易组装性的同时，为客户提供极大的设计自由度。此次发布的 850nm 波长版本可显著提升相机灵敏度，进一步完善 BIDOS® P2433 Q 泛光投射器产品矩阵，从而实现更精准的检测性能。集成的光电二极管可轻松实现人眼保护。

BIDOS® P2433 Q V105Q121A-850 泛光投射器：用于采用飞行时间 (ToF) 测量技术的 3D 传感系统，并可提供均匀场景照明（图片：艾迈斯欧司朗）

## 艾迈斯欧司朗近红外 (NIR) 波段垂直腔面发射激光器 (VCSEL) 解决方案

垂直腔面发射激光器 (VCSEL) 是推动 3D 传感技术市场高速增长的核心器件。艾迈斯欧司朗的解决方案专注于汽车电子、工业自动化及移动设备 / 可穿戴设备领域的高精度传感应用，凭借卓越的光束质量、优异的性价比与精简的架构设计，为各类场景提供高性能技术支撑。艾迈斯欧司朗提供覆盖裸片、封装及模块的完整 VCSEL 产品矩阵，满足多元化应用需求。

艾迈斯欧司朗通过持续的创新来稳固技术领导地位，其在 VCSEL 与 3D 传感技术领域已构建强大的知识产权布局，积累超过 1,000 项专利及其他知识产权成果。◆

# 人形机器人中的毫米波雷达感应和传感器融合

人形机器人具有自动执行任务、做类似人类的动作和参与社交互动，因此在各行各业都备受关注。这些机器人的应用范围广泛，从医疗保健、人形机器人辅助患者，到工业自动化、教育和研究，不一而足。人形机器人的开发面临着多项挑战，包括复制人类的复杂动作、实现自主决策以及创建能够适应非结构化环境的系统。

## 传感在人形机器人中的重要性

人形机器人的一个重要方面是探测和解读物理环境的能力；正如人类依靠感官进行导航和与世界互动一样，人形机器人也需要复杂的传感系统来自主有效地执行任务。人形机器人中使用的常见传感器类型包括视觉系统（摄像头）、雷达和激光雷达（导航和感知）、触觉传感器（模拟触控）以及使机器人能够了解自身姿势和平衡的听觉系统（麦克风）。本应

图1：现代人形机器人。

用简报探讨了毫米波(mmWave)雷达传感器在导航、识别以及将雷达与摄像头传感器集成方面的优势，从而实现人形机器人中的传感器融合。

## 毫米波雷达传感器简介

远距离功能、高运动灵敏度和隐私功能使基于雷达的传感器集成电路(IC)成为位置和接近传感设计的常用技术。雷达传感器具有高精度，在汽车和工业市场中也很受欢迎，用于检测盲点、碰撞、人员和运动。

60GHz和77GHz雷达传感器具有更高的分辨率、更高的精度和更小的外形尺寸，正在取代24GHz雷达传感器。60GHz和77GHz雷达频带支持新的应用，例如工业机器人中的物体存在检测以及工厂或家居移动机器人应用。

## 毫米波传感器相较于激光雷达和摄像头的优势

由于雷达能够在恶劣天气条件下良好运行，因此通常选择毫米波雷达技术而不是激光雷达、摄像头和其他光学传感器，以节省成本；摄像头可能会受到光线不足和天气的影响。雷达还具有较宽的距离和覆盖范围，使传感器能够检测100米以外的物体。由于移动机器人应用需要节省功耗，因此用户经常使用低至1.7mW的雷达进行存在检测。但是，在各种用例场景中，可使用雷达和激光雷达、摄像头或替代光学传感器类型组合。

从功能安全的角度来看，TI工程师在设计IWR6843等非接触式雷达传感器之前，已进行了大量的硬件和软件开发工作，并获得了(TÜV)SÜD的器件认证。所有TI雷达传感器均包含内置的功能安全机制，可提供IEC61508所要求的必要诊断覆盖范围，可在元件级别满足高达安全完整性等级(SIL)2的硬件功能。

可以通过诊断软件库、编译器资质审核套件、第三方操作系统、开发工具和其他文档在线获取功能安全配套资料，从而让工程师简化安全设计流程和系统级认证。

## 传感器融合

在人形机器人中使用一种类型的传感器存在明显的局限性，包括数据收集不完整或不准确。例如，摄像头在深度感知、光线不足或探测非视觉元素时会遇到困难，而激光雷达传感器则会因为机器人移动时激光上下跳动而导致

图2：嵌入在工业机器人中的毫米波传感器。

致读数不准确。数据收集限制可能会导致导航、物体操作和环境交互方面的错误。

传感器融合技术通过集成来自多个传感器的数据，更准确、可靠和全面地了解机器人环境，从而解决这些问题。通过结合来自各种传感模式的输入，人形机器人可以做出更明智的决策，从而增强执行复杂任务的能力，例如在不平坦的地形中导航、抓取不同形状和大小的物体，以及在动态的真实世界环境中进行交互。传感器融合的优势包括：

1. 通过合并不同传感器的数据来提高精确度。

2. 冗余，以便在一个传感器发生故障时确认功能正常。

3. 通过更全面地了解周围环境提高环境感知能力。

4. 能够更好地适应动态环境。

### 雷达和摄像头传感器融合

雷达在恶劣条件下经久耐用，而且在探测移动物体时非常可靠，因此是经常集成到系统中的主要传感器之一。为了弥补单一传感器系统的不足，TI 为希望更大限度提高机器人精度和感知能力的用户提供了各种产品。TI 提供摄像头和雷达传感器模块以及 IMX219 摄像头和 IWR6843ISK EVM 毫米波雷达传感器。该模块实现了一

图3：采用 IMX219 和 IWR6843ISK 构建的摄像头和雷达传感器模块。

种物体级融合方法，该方法应用了注重物体聚类和跟踪的摄像头 - 视觉处理链和雷达处理链，使用户能够跟踪和探测三维环境中的物体。用户演示了传感器融合在机器人 SDK 中的诸多潜能和功能。

### 总结

本文探讨了毫米波感应、安全和传感器融合在实现精确检测人形机器人周围的物体和运动方面的优势。毫米波传感技术在昏暗或灰尘等低能见度条件下尤为重要，因为在这些条件下，传统的

视觉传感器可能不可靠。毫米波雷达成本低、功耗更低，而且能在恶劣天气条件下工作，因此成为机器人应用的潜在选择。

本应用简报还介绍了功能安全和传感器融合技术，这些技术对于人形机器人在复杂环境中的可靠运行至关重要。凭借 (TÜV) SÜD 内置的功能安全机制和器件安全认证，TI 雷达器件可提供 IEC 61508 所需的必要诊断覆盖范围，可在元件级别满足高达 SIL 2 的硬件功能。将支持安全功能的雷达与激光雷达、摄像头或其他光学传感器相结合，有助于提高物体探测的准确性、故障冗余性、决策能力以及机器人行为的实时调整，从而提高人形机器人系统的自主性和安全性。◆

## 中微公司目标5到10年内覆盖60%高端设备

2025年5月27日，中微公司举行2024年度暨2025年第一季度业绩说明会。

中微公司董事长、总经理尹志尧表示，在等离子体刻蚀领域，中微基本可以全面覆盖（不同应用），包括成熟及先进逻辑器件、闪存、动态存储器、特殊器件等，并且已经有95%到99%的应用都有了批量生产的数据或客户认证的数据。

工艺精度上，中微公司ICP刻蚀机Twin-star两台的加工精度已经进入皮米数量级，达到100皮米以下水平；双台刻蚀机实现原子、亚原子水平刻蚀控制，达到全球先进水平。目前业内量产所用刻蚀机的深宽比在60:1，中微公司正

在突破90到100:1的深孔刻蚀。

除刻蚀设备外，中微公司自2010年开始不断开始扩大在薄膜设备领域的开发应用。中微公司规划了近40种导体薄膜沉积设备的开发。其中9种设备已经完成开发，6款实现量产运转1年，今年计划将完成7种设备开发。尹志尧称，很快将会把国际对国内禁运的20多种薄膜设备开发完成，预计到2029年完成所有开发。

据尹志尧介绍，目前中微可以覆盖30%的集成电路设备。而在今后五到十年内，中微公司将与合作伙伴共同覆盖60%的集成电路高端设备，包括刻蚀、薄膜及量检测的全部设备，以及一部分湿法设备，成为平台式的集团公司。◆

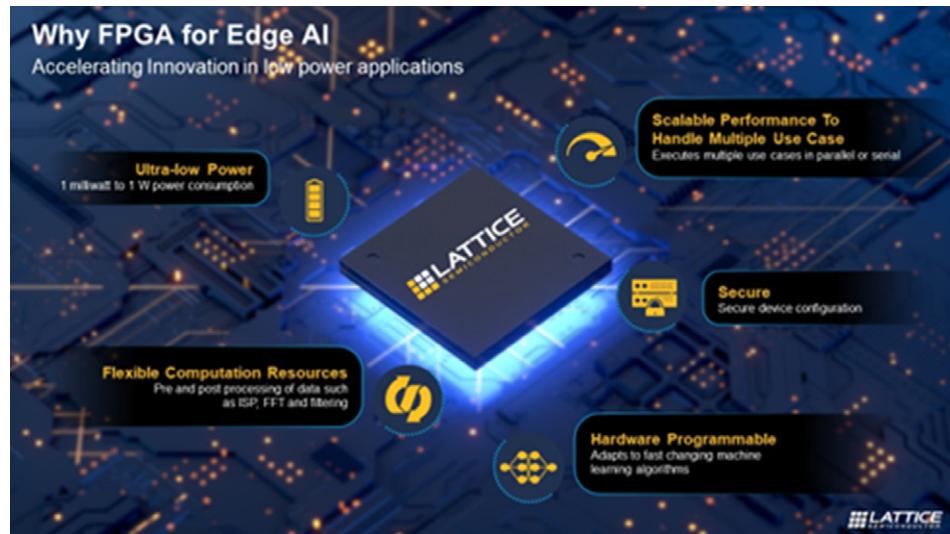

# 情境感知AI： 利用FPGA技术增强边缘智能

网络边缘人工智能——即在边缘设备端部署 AI 模型进行本地化算法处理，而非依赖云端等集中式计算平台——已成为人工智能领域发展最快的方向之一，受到业界高度关注。据测算，2024 年网络边缘 AI 市场规模约为 210 亿美元，预计到 2034 年将突破 1430 亿美元。这一增长态势表明各行业将持续加大基于 AI 的边缘系统研发投入。

网络边缘 AI 的应用前景广阔且充满创新机遇，涵盖自动驾驶汽车、智能家居设备、工业自动化机械等多个领域。但开发者在实践中需要应对硬件限制、功耗优化和处理复杂度等独特挑战。例如，设计人员必须确保嵌入式 AI 模型在保持紧凑体积的同时具备足够算力，能够直接在边缘设备端解析实时情境信息。这要求系统在延迟控制、带宽效率、运算精度和可持续性等性能指标上达到最优平衡，同时还要保障数据隐私安全并降低网络威胁风险。

网络边缘应用的演进正与情境智能的发展同步推进。情境智能旨在从数据所处的环境、关联关系及交互场景中理解其含义，这就催生了情境边缘 AI。该技术通过在网络边缘设备端运行 AI 模型，使系统能够处理环境数据、持续学习并优化性能。例如，智能设备通过视觉、听觉等

多种感知模态理解周边环境，这种对情境数据的高效处理能力，是实现网络边缘设备功能目标和提升用户体验的关键。随着边缘端处理的数据量激增，这些设备需要更高算力支撑。

现场可编程门阵列（FPGA）的灵活性、现场升级能力和互操作性，结合其低功耗、低延迟和并行处理能力，使其成为开发者克服挑战并优化情境边缘 AI 应用的关键工具。

## 实现情境感知边缘 AI 的挑战

通过直接分析网络边缘设备上的情境数据，系统可以做出更智能的实时决策，推动用户与设备之间建立更紧密的共生关系。例如，智能电脑显示器可以利用视觉传感器安全收集的用户存在数据，在用户转向屏幕时打开，在用户离开时关闭，从而优化电源使用时长。智能蜂窝设备同样可以利用面部或指纹识别技术，安全地检查生物特征或用户视觉数据，访问用户凭证，登录安全应用程序。

虽然用户已经开始期待借助情境边缘 AI 实现这些无缝、

The diagram illustrates the concept of programmable intelligence at the edge across four main industries: Industrial, Automotive, Computing, and Communications. Each industry is represented by a vertical stack of icons. To the right, a central column lists nine specific applications or features that benefit from this intelligence:

- Predictive Maintenance

- Human Machine Interface

- User & Object Identification

- User, Gesture, & Gaze Detection

- Presence & Defect Detection

- 3D Audio with Headtracking

- Adaptive Security

- Network Optimization

Lattice Semiconductor logo is visible at the bottom right of the diagram area.

个性化的体验，但开发人员可能会面临各种开发挑战。这些挑战包括：

### 1. 复杂性

随着企业尝试进一步简化人机界面，边缘传感器收集的情境数据也变得越来越复杂。这就要求 AI 模型和硬件既能处理更高的工作量，又能保持效率。网络边缘 AI 还需要灵活性，因为模型和硬件可能需要定期更新，以应对不断变化的情境数据。边缘人工智能还可能涉及 TinyAI 模型的使用，其压缩算法更适合在网络边缘场景下实现高性能，包括可穿戴设备、环境监测远程传感器、工业物联网应用中的质量控制等。即便如此，TinyAI 模型也需要足够的电源和系统支持才能有效运行。

### 2. 互操作性

为了获得尽可能多的相关情境智能，边缘网络通常包括各种传感器、处理器、网关和服务器。这些组件都需要有效地相互通信来支持实时结果。网络边缘设备必须能够处理不断增长的 AI 工作负载，同时还能与网络中的其他设备（无论是现有组件还是第三方硬件和软件）协同运行。如果没有灵活的硬件，传感器、边缘设备和数据分析接收者之间的连接将变得不可靠。

### 3. 功耗

先进的人工智能模型需要大量能源才能运行，研究人员预计，从 2023 年到 2030 年，人工智能相关的耗电量预计每年将增长高达 50%。因此稳定、节能地向模型输送能源至关重要。如果在配置时不考虑效率，边缘部署很可能会出现能源消耗过剩、成本上升，并导致网络边缘 AI 操作的执行与结果之间出现较大延迟。

只有考虑到这些挑战，并积极主动地加以克服，开发人员才能利用情境边缘 AI 改善用户体验。

## 利用莱迪思FPGA轻松实现情境边缘AI

克服复杂性、互操作性和功耗挑战是一项多方面的工作，需要灵活应用硬件和软件。针对 AI 优化的低功耗莱迪思 FPGA 和面向人工智能应用的解决方案集合 Lattice sensAI™ 非常适合应对实施挑战和实现情境感知边缘 AI 应用。

莱迪思 FPGA 经配置可执行特定的 AI 任务，使开发人员能够根据不同的环境定制应用，并处理特定的边缘数据。这有助于优化边缘 AI 应用，实现最高的效率和可靠性，同时保持 FPGA 的灵活性，支持不断发展的 AI 模型。FPGA 还配备了可定制的 I/O 接口，支持跨设备和环境（如摄像头、雷达、环境传感器）连接到各种边缘人工智能应用，并实现更简化的互操作性。

莱迪思 sensAI 解决方案集合还进一步支持和加强了这种定制化。莱迪思 sensAI 能够采用在行业标准 AI 框架（如 TensorFlow、Caffe 和 Keras）中训练的模型，通过模型量化、修剪和稀疏性利用等技术，使其能够在 FPGA 资源上运行。然后，莱迪思的神经网络编译器可以分析模型，并根据电路和片上网络的类型提出最高效的运行建议。此外，莱迪思 Propel 和莱迪思 Radiant 设计软件可用于创建合适的电路组合，以尽可能高能效的方式加速这些模型的运行。

莱迪思 FPGA 还极大降低了传感器数据采集和处理之间的延迟，为用户带来更快的响应和更高的性能。在传输到 AI 模型或中央计算引擎之前，数据可以在 FPGA 上完成预处理和聚合任务，这有助于减少网络边缘设备的压力，进而降低功耗。

各行各业都可以利用莱迪思 FPGA 克服资源限制、功耗、连接性和可扩展性方面的挑战。这些可编程器件实现的实时数据处理和预测，对于工业设备、医疗设备、汽车和机器人领域的应用至关重要。FPGA 的适应性可以量身定制人工智能解决方案，满足各种环境的特定需求，确保最佳性能和可靠性。◆

# 物联网边缘传感器节点： 超越单处理器嵌入式系统的演进

## 互联网连接推动处理需求

嵌入式系统正以越来越快的速度继续其技术演进；我们家庭、车辆和工作场所中的设备功能正在突飞猛进地发展。这一进步的一个关键驱动因素是，即使是最小的电子设备也能够连接到我们的现代网络基础设施。Wi-Fi®、蓝牙®和其他连接选项使得现场更新和维护变得更加容易，同时增加了人工智能和机器学习算法的优势。这种增加的连接性有效地使这些设备成为物联网边缘节点——但这带来了处理需求增加和内存子系统增大的代价。

## 系统挑战

大多数嵌入式系统还“连接”到其直接环境——也就是说，它们提供了某种类型的环境传感、机械驱动或人机界面的功能。例如，智能恒温器除了配备一系列按钮或电容传感器用于人机输入外，还连接到本地温度和湿度传感器网络。大多数嵌入式系统都与它们所处的环境“连接”——也就是说，它们具备某种环境感知、机械控制或人机交互的功能。举个例子，智能恒温器除了配备按钮或触摸传感器用于人机交互外，还连接到一个本地的温度和湿度传感器网络。再比如，联网的烹饪设备的主要目标是理解你对食物温度的期望，并将其转化为精确的热量控制。这些以“模拟”信号为主的系统，正逐渐进入快节奏的云通信世界，这就带来了一个难题：你是为模拟世界的缓慢输入设计系统，还是为了提升速度和整体功能而牺牲模拟信号的精确度？为了更深入地理解这个问题，我们可以看一个常见且简单的例子——物联网边缘传感器节点。

## 模拟子系统

物联网边缘传感器节点需要一些模拟子系统来测量和监控环境条件，例如温度、湿度、运动等。模拟子系统通常包括一个单片机（MCU），用于读取传感器数据，进

行某种形式的处理，并通过网络进行通信。通常情况下，环境数据变化较为缓慢，因此大多数边缘节点不需要处理连续、不间断的数据流。由于边缘节点通常依靠小型电池运行数年，它们大部分时间处于低功耗的“休眠”模式，仅定期唤醒以检测环境变化。在唤醒期间，节点会收集数据并通过网络传输。之后，它会再次进入休眠状态，直到需要进行下一次测量。在我们这个高度互联的世界中，随着边缘节点数量和收集数据的增加，电源效率和低功耗运行成为延长模拟子系统电池寿命的关键设计考虑因素。

## 嵌入式系统的分段设计

为了实现高效的嵌入式系统，通常需要将系统划分为不同的“速度域”，并通过桥接器将快速主处理器与模拟子系统连接起来。这种分区设计可以让模拟子系统专注于处理变化较慢的任务，而快速主处理器则负责处理那些需要高速运算的复杂任务。这样一来，每种处理器都能发挥其最大的优势。随着越来越多的设备需要联网，I3C® 成为了下一代串行通信接口，专门用于支持高速芯片之间的通信。作为 I2C 的升级版，I3C 不仅速度更快，还具备更智能的接口和更强大的控制功能。重要的是，I3C 仍然兼容现有的 I2C 器件，这使得它能够轻松集成到现有的硬件平台中。此外，I2C 器件可以与运行在 12.5 MHz 的 I3C 控制器共存，这意味着现有的 I2C 总线设计可以逐步过渡到 I3C 标准。举个例子，一个支持 I3C 和传统通信接口（如 I2C、SPI 或 UART）的单片机可以作为桥接设备。这个桥接器通过单片机将快速处理器与传感器连接起来。单片机负责读取传感器的数据，进行计算，并将结果高效地传输出去。这种设计不仅保持了 I3C 总线的高性能，还能通过单片机实现 I3C 控制器与 I2C/SPI 器件之间的通信。通过将嵌入式系统进行合理的分区设计，并利用 I3C 接口，可以更高效、更稳定地实现系统设计。

作者：Greg Robinson，Microchip Technology Inc. 负责 MCU 业务部的公司副总裁

**PIC18-Q20 MCU**

Microchip 推出了 PIC18-Q20 产品系列，专门为现代分布式处理器嵌入式系统设计。这些单片机（MCU）提供了先进的串行通信接口，包括多达两个 I3C 外设，能够高速连接到多个总线，极大地增强了系统的灵活性。此外，它们还内置了传统的通信协议，如 UART、SPI、I2C 和 SMBus，可以作为桥接设备无缝集成到系统中，并将 I2C/SPI 设备与纯 I3C 总线隔离开来。这种设计不仅保持了 I3C 总线的高性能，还能通过单片机实现 I3C 控制器与 I2C/SPI 器件之间的通信。PIC18-Q20 还支持多个电压域，这意味着它可以轻松连接不同工作电压的组件，从而省去了电平转换器的需求，降低了材料成本并简化了系统设计。此外，PIC18-Q20 单片机集成了片上独立于内核的外设（CIP），这些外设可以在不需要 CPU 持续干预的情况下独立运行，并直接与其他外设通信。这些基于硬件的功能模块功耗极低，几乎不需要编写代码，并且占用更少的 RAM 和闪存资源，却能实现与软件相同的功能。此外，单个 MCU 可以同时启用多个功能模块。设计人员可以通过 MPLAB® 代码配置器（MCC）——一个简单的图

形用户界面（GUI）工具——轻松定制包括 I3C 外设在内的 CIP 组合，生成应用程序代码，而无需深入研究数据手册。通过使用 CIP，工程师可以将每个系统任务进行分区管理，从而简化功能实现，减少组件数量、代码量、开发时间和功耗。

**结论**

在我们这个快速变化的世界中，技术的进步要求设备具备更快的处理速度、更高效的连接性以及更小的体积。虽然现代电子设备越来越多地与外部世界连接，但在这些互联系统中，仍然需要小型化且节能的模拟子系统来感知和测量“现实世界”的数据。由于环境数据的变化通常比较缓慢，设计时需要在速度和精度之间找到一个平衡点。

为了实现高效的嵌入式系统，通常需要将系统划分为不同的“速度域”，并通过桥接器将快速处理器与模拟子系统连接起来。随着 I3C 逐渐成为高速芯片间通信的主流接口，工程师们需要选择能够全面支持高性能数字处理需求的高级单片机（MCU），同时还要确保这些 MCU 在下一代设计中保持对模拟信号的高精度处理能力。◆

## xMEMS发布超轻薄Sycamore-W 扬声器

2025 年 5 月 27 日 - 全球先进压电 MEMS 音频创新企业、先锋级全硅微型扬声器创造者、xMEMS Labs 今日发布 Sycamore-W，这是公司的 Sycamore 近场 MEMS 扬声器系列的最新成员，该产品专为智能手表、运动手环及其他腕戴设备而打造。

在 2024 年底首度推出 Sycamore 微型扬声器获得广大成功后，Sycamore-W 延续 xMEMS 致力于在空间受限的移动设备中提供 μFidelity™ 高保真音效的承诺。Sycamore-W 外形尺寸为 20 x 4 毫米，厚度仅为 1 毫米，对比传统设计，扬声器封装体积减少了 70%，是设备更轻薄简约，同时仍可提供高品质、全音域的音效表现。

xMEMS 营销与业务开发副总裁 Mike Housholder 表示：“Sycamore-W 重新定义了智能手表的音频，将紧凑的设计与强大的性能相结合，以满足下一代可穿戴设备的需求，随着手腕成为免耳机、免提 AI 互动的关键界面，

Sycamore-W 使制造商能够打造更小、更轻、更耐用的设备中提供优质音频”。

**专为腕戴式设备而优化**

Sycamore-W 专为腕戴型可穿戴设备的特殊需求设计。其 4 毫米宽度与 1 毫米薄的外型可大幅降低对表壳内部空间的占用，为设计师腾出更多空间集成生物传感器和更大容量电池。与传统线圈扬声器（通常厚 3-4 毫米、重达 3 克）相比，Sycamore-W 仅重 150 毫克，大幅减少佩戴压力，提升舒适度，是穿戴式设备的理想选择。

**硅基耐用性与坚固设计**

Sycamore-W 延续 xMEMS 扬声器一贯的固态结构与高耐用性，具有元件级 IP58 防护等级和坚固耐用的 10,000g 机械抗冲击性能。这些特性使其成为运动生活可穿戴设备以及户外型智能手表和健身手环的理想选择。◆

| Advertiser                    | 广告商名称 | 网址                           | 页码  |

|-------------------------------|-------|------------------------------|-----|

| APSME2025亚洲国际功率半导体、材料及装备技术展览会 |       | www.powersemi-expo.com       | IBC |

| 仪景通光学                         |       | www.evidentscientific.com.cn | 3   |

## 欢迎投稿

《半导体芯科技》(Silicon Semiconductor China, SiSC) 是面向中国半导体行业专业媒体，已获得全球知名权威杂志《Silicon Semiconductor》的独家授权。本刊针对中国半导体市场特点遴选相关优秀文章翻译，并汇集编辑征稿、采编国内外半导体行业新闻、深度分析和权威评论等多方面内容。本刊由香港雅时国际商讯（ACT International）以简体中文出版发行。

本刊内容覆盖半导体制造工艺技术、封装、设备、材料、测试、MEMS、mini/Micro-LED 等。文章重点关注以下内容：

### FAB (Foundry, IDM, OSAT, R&D)

四个环节：晶圆制造(wafer 后道)、芯片制造、先进封装、洁净室；深入报道与之相关的制造工艺、材料分析，工艺材料、工艺设备、测试设备、辅助设备、系统工程、关键零备件，以及与 particle (颗粒度) 及 contamination (沾污) 控制等厂务知识。

### FABLESS

芯片设计方案、设计工具，以及与掩膜版内容和导入相关的资讯。

### 半导体基础材料及其应用

III-V 族、II-VI 族等先进半导体材料的科学研究成果、以及未来热门应用。

《半导体芯科技》欢迎读者、供应商以及相关科研单位投稿，已甄选中稿件将在印刷版杂志以及网上杂志刊登；IC 设计及应用等半导体相关内容将酌情予以网络发表（微信推送、杂志网站）。本刊优先刊登中文来稿（翻译稿请附上英文原稿）。

### 技术文章要求

- 论点突出、论据充分：围绕主题展开话题，如工艺提升、技术改造、系统导入、新品应用，等等。

- 结构严谨、短小精悍：从发现问题到解决问题、经验总结，一目了然，字数以 3000 字左右为宜。

- 文章最好配有 2-4 幅与内容有关的插图或图表。插图、图表按图 1、图 2、表 1、表 2 等依次排序，编号与文中的图表编号一致。

- 请注明作者姓名、职务及所在公司或机构名称。作者人数以四人为限。

- 文章版权归作者所有，请勿一稿多投。稿件一经发表如需转载需经本刊同意。

- 请随稿件注明联系方式（电话、电子邮件）。

### 新产品要求

- 新产品必须是在中国市场新上市、可在中国销售的。

- 新产品稿件的内容应包含产品的名称、型号、功能、主要性能和特点、用途等。

- 新产品投稿要求短小精悍，中文字数 300~400 字左右。

- 来稿请附产品照片，照片分辨率不低于 300dpi，最好是单色作为背景。

- 来稿请注明能提供进一步信息的人员姓名、电话、电子邮件。

电子邮箱：sunniez@actintl.com.hk

viviz@actintl.com.hk

## 行政及销售人员 Administration & Sales Offices

### 行政人员 Administration

#### HK Office (香港办公室)

#### ACT International (雅时国际商讯)

Unit B, 13/F, Por Yen Building, No. 478 Castle Peak Road, Cheung Sha Wan, Kowloon, Hong Kong

Tel: 852 28386298

#### Publisher (社长) - China

Adonis Mak (麦协林), adonism@actintl.com.hk

#### General Manager-China (中国区总经理)

Floyd Chun (秦泽峰), floydC@actintl.com.hk

#### Editor in China (中国版编辑)

Sunnie Zhao (赵雪芹), sunniez@actintl.com.hk

Vivi Zhang (张雨薇), viviz@actintl.com.hk

#### London Office

Hannay House, 39 Clarendon Road

Watford, Herts, WD17 1JA, UK.

T: +44 (0)1923 690200

#### Coventry Office

Unit 6, Bow Court, Fletchworth Gate

Burnsall Road, Coventry, CV5 6SP, UK.

T: +44 (0)2476 718 970

#### Publisher & Editor-SiS English

Jackie Cannon, jackie.cannon@angelbc.com

+44 (0)1923 690205

### 销售人员 Sales Offices

#### China (中国)

#### Wuhan (武汉)

Mini Xu (徐若男), minix@actintl.com.hk

Tel: 86 187 7196 7314

Mandy Wu (吴漫), mandyw@actintl.com.hk

Tel: 86 156 2304 9536

Ron Wang (汪毓翀), ronw@actintl.com.hk

Tel: 86 186 9404 8156

#### Shenzhen (深圳)

Samuel Zhou (周伟林), samuelz@actintl.com.hk

Tel: 86 186 8201 0368

#### Shanghai (上海)

Hatter Yao (姚丽莹), hattery@actintl.com.hk

Tel: 86 139 1771 3422

Shohan Shen 沈璟晓, Shohans@actintl.com.hk

Tel: 86 176 2122 8315

#### Beijing (北京)

Cecily Bian (边团芳), cecilyB@actintl.com.hk

Tel: 86 135 5262 1310

#### Hong Kong (香港特别行政区)

Floyd Chun (秦泽峰), floydC@actintl.com.hk

Tel: 852 2838 6298

#### Asia (亚洲)

#### Japan (日本)

Masaki Mori, masaki.mori@ex-press.jp

Tel: 81 3 6721 9890

#### Korea (韩国)

Lucky Kim, semieri@semieri.co.kr

Tel: 82 2 574 2466

#### Taiwan, Singapore, Malaysia

(台湾, 新加坡, 马来西亚)

Regional Sales Director

Floyd Chun (秦泽峰), floydC@actintl.com.hk

Tel: 852 2838 6298

#### US (美国)

Janice Jenkins, jjenkins@brunmedia.com

Tel: 724 929 3550

Tom Brun, tbrun@brunmedia.com

Tel: 724 539 2404

#### Europe (欧洲)

Shehzad Munshi, Shehzad.Munshi@angelbc.com

Tel: +44 (0)1923 690215

Jackie Cannon, Jackie.cannon@angelbc.com

Tel: +44 (0) 1923 690205

## 亚洲国际功率半导体、材料及装备技术展览会 同期举办：第三代功率半导体器件及应用技术展览会

2025年11月20日 - 22日

广州保利世贸博览馆

功率器件IGBT/MOSFET

第三代半导体材料

功率半导体设备

外延片/衬底材料

设计和开发

封装测试

散热管理

可靠性测试及认证

### 同期活动：

- ◆ 汽车电子创新技术国际论坛

- ◆ 中国半导体制造封装技术论坛

- ◆ 国际嵌入式创新技术大会

- ◆ 线束加工技术国际论坛

- ◆ 中西部电子制造技术周

- ◆ 电子生产智能工厂国际论坛

- ◆ 国际自动驾驶技术论坛

同期展览：AUTO TECH China 2025 广州国际新能源汽车功率半导体技术展览会

### 组委会联系方式：

参展咨询：李经理 132 6539 6437 (同微信)

邮箱：lilin@jswatsonexpo.com

参观咨询：杨女士 131 7886 7606 (同微信)

邮箱：lisayang@jswatson-expo.com

# 化合物半导体

CS COMPOUND SEMICONDUCTOR CHINA

MicroLED 超级

显示

红外激光光谱仪

手持式

激光测距仪

面向高效的星载电

子波发射器

高温电子技术的发

展与挑战

ACT

2022年4/5期

[www.compoundsemiconductorchina.net](http://www.compoundsemiconductorchina.net)

# 化合物半导体

CS COMPOUND SEMICONDUCTOR CHINA

确保高频率下的可靠性

5G & 6G

GaN: 通往窄带E场

或HEMT的桥梁

超深结碳化硅超

禁带器件

电动汽车发展的新

动力: Soitec的

SmartSiC™ 技术

ACT

2022年8/9期

免费索阅

[www.compoundsemiconductorchina.net](http://www.compoundsemiconductorchina.net)

# 化合物半导体

CS COMPOUND SEMICONDUCTOR CHINA

Micro-LED技术研

究进展

氮化镓外延处理的

最新进展

碳化硅垂直

发光二极管

基于聚酰亚胺高导热

封装技术

碳化硅辐射晶管

半绝缘导体电阻

率、迁移率的非

接触测量

ACT

2023年12月/2024年1月

微射流激光技术基于大尺寸

金刚石材料分片的研究

[www.compoundsemiconductorchina.net](http://www.compoundsemiconductorchina.net)

ISSN 2789-2735

## 全球知名权威杂志

## Compound Semiconductor的中国版

### 化合物半导体

CS COMPOUND SEMICONDUCTOR CHINA

中文版，双月刊，全方位报道化合物半导体行业的发展，是化合物半导体材料和器件业专业人士重要的信息源。2025年，将主要报道开发超宽禁带材料，基于SiC、GaN和 $\text{Ga}_2\text{O}_3$ 的功率电子；5G和6G的射频器件；光子学领域的突破，包括新的VCSEL设计；以及在射频领域的功率、效率和频谱范围的进步。

CS 2025

CHINA CON 化合物半导体

先进技术及应用大会

由雅时国际商讯主办，会议专注搭建全球化合物半导体行业范围内产、学、研、政信息交流和商务合作的精准交流平台，着眼行业前沿议题，洞悉行业最新需求，汇集国内外领先跨国科技，与专家学者共探行业发展方向，共同探讨化合物半导体产业开拓创新的解决之道。

[www.compoundsemiconductorchina.net](http://www.compoundsemiconductorchina.net)

ACT

INTERNATIONAL