## SILICON SEMICONDUCTOR

Connecting the Silicon Semiconductor Community

Volume 40 Issue III 2018

www.siliconsemiconductor.net

#### New defect reduction strategies

Resolving thermal management issues

Self-folding 3D cell grippers

Real-time air quality sensor

News Review, News Analysis, Features, Research Review, and much more...

Free Weekly E News round up go to: www.siliconsemiconductor.net

## LASER DEBONDING SOLUTIONS FOR ADVANCED PACKAGING

- High-throughput equipment solution for low-temperature debonding of wafers and panels

- Laser system with minimal consumable costs combined with proprietary optical design for excellent beam reproducibility

- Open adhesive platform laser debonding solution compatible with several material systems

**GET IN TOUCH** to discuss your manufacturing needs **www.EVGroup.com**

EVG®850 DB

## editor's view

By Mark Andrews, Technical Editor

## Opportunities drive new defect reduction strategies

THE SEMI trade group recently announced that semiconductor fab equipment sales were up 30 percent compared to 1Q 2017. While device and process tool sales are setting records. forward-looking supply chain vendors are already addressing challenges that need solutions for positive growth beyond 2018.

According to IC Insights researchers, one of the fastest growing markets and forecast upside darlings is the automotive sector. Cars and light trucks that today utilize somewhere between 400 and 700 semiconductors are forecast to become rolling 'data centers' as manufacturers automate many functions to increase safety and fuel economy. Indeed, many major auto makers are forecasting all electric vehicle (EV) fleets by 2050. If fully-autonomous vehicles move from test tracks to daily commuting, onboard semiconductors could top 5,000.

IC Insights reported that the automotive chip market has seen extraordinary performance cycles since its double-digit 2014 upswing. 2015 saw markets actually shrink, followed by nearly 11 percent growth in 2016. The 2017 auto chip market was worth (USD) \$27.2 billion. But future growth depends on a number of 'what-if' scenarios, including whether manufacturers can deliver self-driving vehicles.

One of the important challenges that the semiconductor supply chain needs to face is how to effectively transition to serving auto manufacturers who have substantially different requirements than consumer device makers. As our cover feature article from Linde Electronics points out, existing auto supply chain chip providers are a tight-knit group able meet very tough performance requirements year after year. Vendors entering that space to facilitate on-board artificial intelligence or other highly advanced applications face a tough road. Smartphone chips, for example, are typically expected to operate two to five years;

manufacturers accept a 10 percent failure rate. But on the automotive side, semiconductors have to operate up to 15 years with a zero percent target failure rate. Linde shares its strategies for success in the automotive jungle.

Also addressing the critical need for defect reduction in next-generation technologies is Brewer Science that advocates utilizing the latest tool and analytical techniques to meet manufacturer's requirements for defect elimination in devices below 10 nm.

With ample evidence of growth across both manufacturing equipment and end use sectors, it is easy to adopt a business-as-usual attitude. However, future success at challenging new geometries under tough standards requires vigilance and the rigorous application of lessons learned at 10 nm and above. Getting smaller is not getting any easier.

Publisher & Editor Jackie Cannon Technical Editor Mark Andrews Sales & Marketing Manager Shehzad Munshi USA Representatives Tom Brun Brun Media

**Director of Logistics** Sharon Cowley Design & Production Manager Mitch Gaynor Circulation Director Jan Smoothy Chief Executive Officer Stephen Whitehurst

Janice Jenkins

jackie.cannon@angelbc.com +44 (0)1923 690205

shehzad.munshi@angelbc.com +44 (0)1923 690215 tbrun@brunmedia.com +001 724 539-2404 iienkins@brunmedia.com +001 724-929-3550 +44 (0)1923 690200 sharon.cowlev@angelbc.com mitch.gaynor@angelbc.com +44 (0)1923 690214 jan.smoothy@angelbc.com +44 (0)1923 690200

stephen.whitehurst@angelbc.com +44 (0)2476 718970

Directors Bill Dunlop Uprichard - EC, Stephen Whitehurst - CEO, Jan Smoothy - CFO, Jackie Cannon, Scott Adams, Sharon Cowley, Sukhi Bhadal, Jason Holloway

Published by Angel Business Communications Ltd, Hannay House, 39 Clarendon Road, Watford, Herts WD17 1JA, UK. T: +44 (0)1923 690200 E: ask@angelbc.com

Angel Business Communications Ltd, Unit 6, Bow Court, Fletchworth Gate, Burnsall Road, Coventry CV5 6SP, UK. T: +44 (0)2476 718 970 F: +44 (0)2476 718 971 E: info@angelbc.com

Silicon Semiconductor is published four times a year on a controlled circulation basis. Non-qualifying individuals can subscribe at: £50.00/€60 pa (UK & Europe), £70.00 pa (Outside Europe), \$90.00 pa (USA). Cover price £4.50. All information herein is believed to be correct at time of going to press. The publisher does not accept responsibility for any errors and omissions. The views expressed in this publication are not necessarily those of the publisher. Every effort has been made to obtain copyright permission for the material contained in this publication. Angel Business Communications Ltd will be happy to acknowledge any copyright oversights in a subsequent issue of the publication. Angel Business Communications Ltd © Copyright 2018. All rights reserved. Contents may not be reproduced in whole or part without the written consent of the publishers. The paper used within this magazine is produced by chain of custody certified manufacturers, guaranteeing sustainable sourcing. US mailing information: Silicon Semiconductor is published four times a year for a subscription of \$90.00 by Angel Business Communications Ltd, Hannay House, 39 Clarendon Road, Watford, Herts, WD17 1 JA, UK. Periodicals postage paid at Rahway, NJ. POSTMASTER: send address changes to: Silicon Semiconductor, c/o Mercury International Ltd, 365 Blair Road, Avenel, NJ 07001. Printed by: The Manson Group. © Copyright 2018. ISSN 2050-7798 (Print) ISSN 2050-7801 (Online).

# CONTENTS

## **16** COVER STORY

### Driving growth, safety, and quality in automotive electronics

Sophisticated electronic systems continue to increase their impact across today's automotive sector. Radar, LiDAR, and a host of new artificial intelligence (Al)-based systems are becoming the norm as vehicle makers seek to improve safety, performance and efficiency on the road to fully autonomous vehicles. Linde Electronics describes ways that the automotive manufacturing supply chain can meet tight performance standards in pursuit of global market opportunities.

## 22 Future nodes require new defect strategies

Existing defect reduction protocols have proven less than ideal for reducing waste and speeding production as transistor geometries shrink and process complexity increases

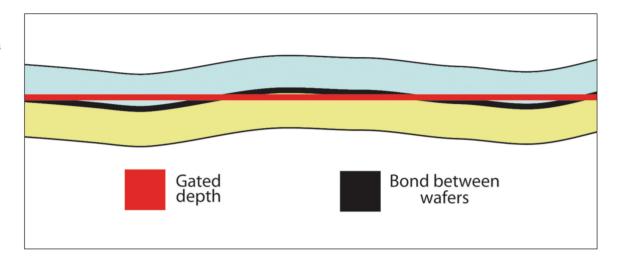

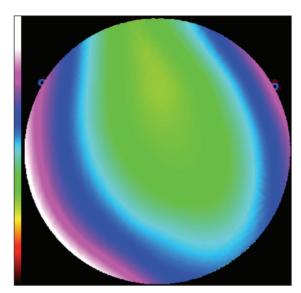

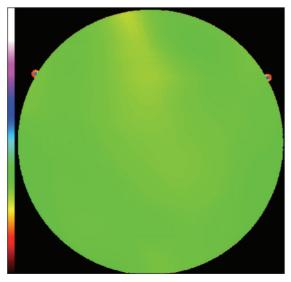

# 26 Flat wafers and warped wafers imaged acoustically

If a wafer can be imaged as though it were flat, devices with defects can be removed after dicing and the warping of individual wafers can be measured

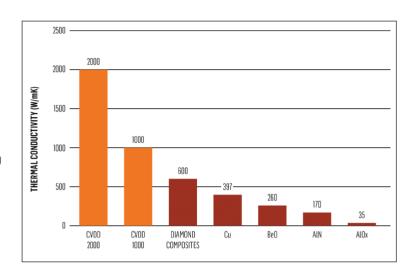

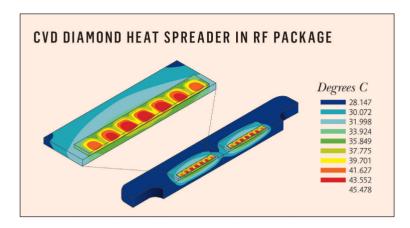

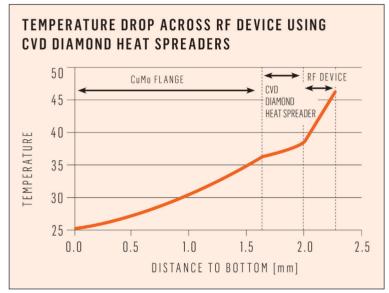

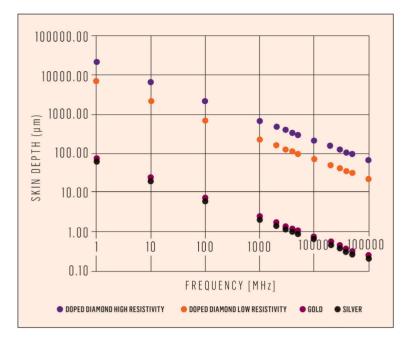

## 30 CVD diamond resolves thermal management issues

Gallium nitride (GaN) and advanced silicon technologies offer sizeable power density enhancements compared to legacy solutions

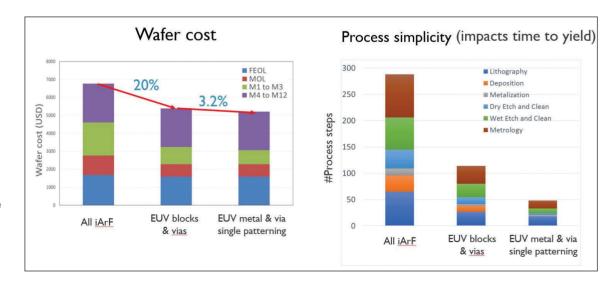

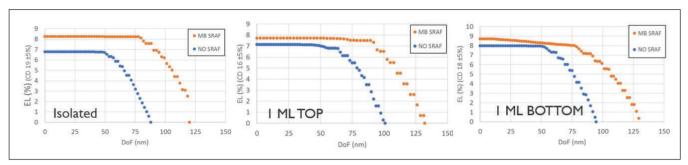

# 34 Imec pushes the limits of EUV lithography single exposure

Imec has made considerable progress towards enabling extreme ultraviolet (EUV) lithography single exposure of N5 32 nm pitch metal-2 layers and of 36 nm pitch contact holes

#### news

- 06 Infineon gears up for stronger long-term growth

- O7 Applied Materials breakthrough accelerates chip performance

- 08 Teledyne E2v awarded second phase of €42 million for custom image sensors

- 09 ASM Amicra looks to a new era

- 10 Imec demonstrates cooling solution for high performance chips

### research

- 12 Origami for cells: self-folding 3D cell grippers for recording

- 14 AFRL-AFLCMC collaborate on real-time air quality sensor

## Infineon gears up for stronger long-term growth

INFINEON TECHNOLOGIES is seeing strong long-term growth drivers in its target markets - automotive, industrial. IoT and security applications - where business momentum is gathering pace. As part of its long-term planning process, Infineon is realigning its target operating model, which sets target values for revenue growth, segment result margin and the investment-to-sales ratio over the cycle.

On 12 June 2018, Infineon held a Capital Markets Day for investors and analysts in London, during which its strategy and realigned target operating model will be explained in more detail.

"A broad range of structural trends will drive growth in the coming years: electro-mobility, renewable energies, factory automation, data centers and a steadily increasing number of batterypowered, connected devices," points out Reinhard Ploss, CEO of Infineon.

"Thanks to our leading technologies and differentiated manufacturing expertise. we have established an excellent position in the markets in which we operate. We are determined to exploit the opportunities that result from this and, accordingly, apply a rigorous approach to investing.

"Our current plans are aimed at providing the necessary level of manufacturing capacity to meet expected growth. It is currently forecast that, by the middle of the coming decade, more than half of the power semiconductors produced by Infineon will be manufactured on 300 mm wafers (in Dresden/Germany and Villach/ Austria). This will enable us to improve our profitability further, despite higher

depreciation expense".

In view of the current strength of the order book and based on a euro/US dollar exchange rate of 1.20, Infineon expects revenue to grow at least in the coming 2019 fiscal year by a minimum of 10 percent. For the fiscal years following this accelerated growth period, Infineon assumes that revenue will grow at an average annual rate of 9 percent (previously 8 percent).

Given that this superior growth is being driven in particular by strong demand for power semiconductors – an area in which Infineon's in-house manufacturing capabilities provide a competitive advantage - it is necessary to adjust the investment-to-sales ratio: On average, annual investments are

expected to amount to 15 percent (previously: 13 percent) of revenue. Approximately 2 percentage points of this figure will continue to relate to the capitalisation of development costs in accordance with IFRS, with the vast bulk of the remainder relating to manufacturing and IT equipment.

Any increase/decrease in revenue growth compared to the above-stated 9 percent will - for each percentage point - result in a slightly less pronounced change in the investment-to-sales ratio.

In addition to the investment-tosales ratio described above, further investments in the low three-digit million euro range in total are planned over the coming years to enable Infineon to exploit additional business opportunities and react appropriately to structural changes. Furthermore, Infineon intends to invest a total of approximately €700 million in front-end cleanrooms and certain larger-scale office buildings during the coming five-year planning horizon. Of the investments in Villach (Austria) that have recently been announced, this figure includes the 300 mm cleanroom and the research and development building.

Implementation of these measures on the stated scale will temporarily result in an investment-to-sales ratio well above the ratio envisaged in the target operating model. Due to the increased investment activity, Infineon expects depreciation of property, plant and equipment in relation to revenue to increase by approximately three percentage points over the next five fiscal years. However, by increasing the share of cost-efficient 300 mm manufacturing and further measures, the gross margin is projected to be maintained at the level of the 2018 fiscal year.

In addition, Infineon plans to gradually improve the segment result margin from its current target level of 17 percent by ensuring that operational expenses rise at a lower rate than revenue. Selling expenses are expected to increase by 90 percent of the rate of revenue growth, while general and administrative expenses are expected to increase by 60 percent of the rate of revenue arowth.

## SemiGen announces new foundry capabilities

US-BASED SemiGen has announced that after moving into a new state-of-the art facility it has increased its foundry and screening capabilities. It now offers wafer processing of 100 to 150 mm silicon wafers, as well as alumina and aluminium nitride substrates up to just over 100mm (4.25 inches). Services provided include any combination of photolithography, wet etch, dry etch, metallisation, grinding, polishing, as well as in-process metrology.

Recent investments in RF Test and Hi-Reliability environmental

test capabilities has also enabled SemiGen to offer solutions for High-Reliability screening of amplifiers, FETs, MMICs, transistors, diodes, and other active and passive circuits and components.

Tests are performed and are delivered with full documentation in accordance with MIL-PRF-19500, MIL-PRF-38534, and MIL-PRF-38535 requirements. Element evaluation and screening options from Class H, Class K, TX, TXV, S-level, as well as custom SCD driven requirements are available.

## Applied Materials breakthrough accelerates chip performance

APPLIED MATERIALS has announced a breakthrough in materials engineering that accelerates chip performance in the big data and Al era.

In the past, classic Moore's Law scaling of a small number of easy-to-integrate materials simultaneously improved chip performance, power and area/ cost (PPAC). Today, materials such as tungsten and copper are no longer scalable beyond the 10nm foundry node because their electrical performance has reached physical limits for transistor contacts and local interconnects.

This has created a major bottleneck in achieving the full performance potential of FinFET transistors. Cobalt removes this bottleneck but also requires a change in process system strategy. As the industry scales structures to extreme dimensions, the materials behave differently and must be systematically engineered at the atomic scale, often under vacuum.

To enable the use of cobalt as a new conducting material in the transistor contact and interconnect, Applied has combined several materials engineering steps - pre-clean, PVD, ALD and CVD - on the Endura platform. Moreover, Applied has defined an integrated cobalt suite that includes anneal on the Producer platform, planarization on the Reflexion LK Prime CMP platform and

e-beam inspection on the PROVision platform. Customers can use this proven, Integrated Materials Solution to speed time-to-market and increase chip performance at the 7nm foundry node and beyond.

"Five years ago, Applied anticipated an inflection in the transistor contact and interconnect, and we began developing an alternative materials solution that could take us beyond the 10nm node," said Dr. Prabu Raja, senior vice president of Applied's Semiconductor Products Group. "Applied brought together its experts in chemistry, physics, engineering and data science to explore the broad portfolio of Applied's technologies and create a breakthrough Integrated Materials Solution for the industry. As we enter the big data and Al era, there will be more of these inflections, and we are excited to be having earlier and deeper collaborations with our customers to accelerate their roadmaps and enable devices we never dreamed possible."

While challenging to integrate, cobalt brings significant benefits to chips and chip making: lower resistance and variability at small dimensions; improved gapfill at very fine dimensions; and improved reliability. Applied's integrated cobalt suite is now shipping to foundry/ logic customers worldwide.

## ZEISS half-year figures: High-tech drives growth

CARL ZEISS has announced positive results for first half of financial year. The company attributes growth in the semiconductor manufacturing segment thanks to future-oriented EUV technology.

The first six months of fiscal year 2017/18 (ended 31 March 2018) saw its revenue rise by 9 percent to EUR 2.773 billion (1st six months of 2016/17: EUR 2.550 billion), and as much as 13 percent after adjustments for currency effects.

At EUR 380 million, the earnings before interest and tax (EBIT) were high despite clearly negative currency effects compared to the previous year (EUR 384 million). The EBIT margin is at 14 percent. Incoming orders hit EUR 2.839 billion (1st six months of 2016/17: EUR 2.743 billion).

"It is our business in the high-tech fields of semiconductor manufacturing technology, industrial metrology and medical technology in particular that are enabling our growth and helping further advance the ZEISS Group," said Prof. Dr. Michael Kaschke, President and CEO of ZEISS. "We are benefitting once again from our balanced and future-oriented portfolio and our broad global footprint."

## Orbotech and IME to develop advanced packaging solutions

ORBOTECH a global supplier of yield-enhancing and processenabling solutions for the manufacture of electronics products, and A\*STAR's Institute of Microelectronics (IME), have announced a joint lab agreement confirming Orbotech as a partner in IME's FOWLP joint lab and as a member of the IME FOWLP development line consortium.

Orbotech's Emerald UV Laser Drilling solution is one of the key processes available in the FOWLP joint lab development line. The Emerald delivers advanced UV drilling performance for today's most challenging IC substrate and assembly applications, including 3D packages, stacking and package on package. The FOWLP development line at IME's facilities at Singapore Science Park II, and its new facilities at Fusionopolis Two, will allow IME and its partners to develop technologies

that will serve a wide range of markets including consumer electronics, healthcare and automotive. "Orbotech is honored to be part of IME's FOWLP development joint lab and FOWLP development line consortium," said Dr. Abraham Gross, Corporate Executive Vice President, Chief Technology Officer and Head of Innovation of Orbotech. "This collaboration builds on the long-term relationship that IME has with Orbotech's SPTS Technologies, a leading supplier of advanced packaging solutions. We are always pleased to cooperate with technology and process innovation initiatives that push the electronics packaging industry forward and enable solutions for complex challenges. The Emerald UV Laser Drilling system is just one of the building blocks that we, at Orbotech, provide to enhance the quality and efficiency of the production process for 3D IC and other complex high density packaging structures."

## Teledyne E2v awarded second phase of €42 million

for custom image sensors

THE EUROPEAN SPACE AGENCY (ESA) has awarded Teledyne e2v, a division of Teledyne Technologies, with the second phase of a €42M (\$47M) contract to produce high-end Charge Coupled Device (CCD) visible light image sensors for the PLATO (Planetary Transits and Oscillations of stars) mission. PLATO is a planet hunting spacecraft that will seek out and research Earth like exoplanets around Sun like stars.

About 100 Teledyne e2v large area CCDs will allow the mission to detect minute changes in the apparent brightness of stars, orbited by planets.

Teledyne e2v completed the first manufacturing phase of the contract, including the production of high end CCD wafers and the procurement and production of other key items.

After a successful review of the first phase, Teledyne e2v has been authorised to start work on phase two of this prestigious contract. This includes

manufacturing the wafers and the assembly, test and delivery of 114 CCDs. Together, they will form the biggest optical array ever to be launched into space (currently planned for 2026).

During its lifetime, PLATO will precisely measure the size, mass and age of planets, survey a large area of the sky and study the full diversity of thousands of stars and planetary systems across our galactic neighbourhood. To date, astronomers know of several thousand exoplanets orbiting distant stars.

Many of them were discovered by the Kepler and CoRoT space missions, which were also equipped with Teledyne e2v's CCD image sensors. PLATO is expected to discover many more exoplanets, which will then be further investigated and analysed by ground based telescopes, generating a huge amount of follow up activity by the astronomy community.

PLATO will be made up of 26 telescopes mounted on a single satellite platform.

Each telescope will contain four 20Mpixel Teledyne e2v CCDs in both full-frame and frame-transfer variants, for a full satellite total of 2.12 Gpixels. This is over twice the equivalent number for GAIA, the largest camera currently in space. As with GAIA, all ofthe PLATO CCD image sensors will be designed and produced in Chelmsford, UK.

## GLOBALFOUNDRIES 180UHV tech platform enters volume production

GLOBALFOUNDRIES has announced that its 180 nm Ultra High Voltage (180UHV) technology platform has entered volume production for a range of client applications, including AC-DC controllers for industrial power supplies, wireless charging, solid state and LED lighting, as well as AC adapters for consumer electronics and smartphones.

The increasing demand for highly costeffective systems requires integrated circuits (ICs) that achieve significant area savings while reducing bill-ofmaterials (BOM) and printed circuit board (PCB) footprint by integrating discrete components onto the same die. GF's 180UHV platform features a 3.3 V LV CMOS baseline, with options for HV18, HV 30 and 700V UHV, that delivers

significant area savings for both digital and analog circuit blocks, compared to the traditional 5V bipolar CMOS DMOS (BCD) technologies.

"GF's leadership in providing high voltage solutions makes the company a perfect strategic partner for On-Bright's power supply technologies," said Julian Chen, CEO of On-Bright, the leading market player in AC-DC switch mode power supply products.

"GF's new 180UHV process integrates UHV components into the same IC with 180 nm digital and analog by incorporating On-Bright know-how in the design. The technology has reduced On-Bright's switched-mode power supply cost and footprint to give our AC-DC switch mode power supply products

additional system-level benefits." As part of a modular platform based on the company's 180 nm process node, GF's 180UHV process technology delivers a 10x increase in digital density compared to previous generations for integrated AC-DC conversion.

For AC-DC conversion, the platform integrates high voltage transistors with precision analog and passive devices to control high input and output voltages of AC-DC SMPS circuits.

The process is qualified up to 150°C to accommodate the high ambient temperatures of power supply and LED lighting products.

news review

## ASM Amicra looks to a new era

AMICRA Microtechnologies, a vendor of back-end processing equipment for advanced packaging applications and silicon photonics assembly, is entering a new era of growth and market capitalization by becoming a part of ASM Pacific Technology Ltd. (ASMPT). Effective April 2018, the company was renamed ASM AMICRA Microtechnologies GmbH. The wellknown AMICRA management team, consisting of Dr. Johann Weinhaendler, Rudolf Kaiser and Horst Lapsien, remains in place.

The acquisition of 100% of the shares of AMICRA Microtechnologies GmbH by Singapore-based ASM Pacific Technology Ltd. (ASMPT) will considerably expand and strengthen AMICRA's strategic position. ASMPT, as an innovative and quality-driven strategic investor in the electronics manufacturing industry having a welldeveloped distribution network in Asia, complements AMICRA's technology position and worldwide business activities very well. The transaction will especially serve the fast growing silicon photonics assembly equipment market but also the general high-precision flipchip and die bonding markets.

ASMPT, headquartered in Singapore and listed on the Hong Kong Stock Exchange, is the world's largest backend semiconductor equipment supplier and SMT solutions provider. ASM AMICRA Microtechnologies GmbH will be integrated into ASMPT's back-end equipment segment. AMICRA's corporate structure and global organization will remain in place, as well its long-time proven management team.

AMICRA started out in 2001 with five employees. In the mean time, it has developed into an internationally known vendor and leading supplier of highprecision die bonders for the advanced packaging and photonics assembly market. AMICRA now employs 130 at its headquarters in Regensburg, Germany, and in twelve sales and tech support offices around the world. AMICRA products will now constitute an important growth factor for the global leader in back-end equipment. ASMPT's commanding market position is based on

its continued technological innovation, its foresight in investing ahead of the curve, commitment to quality, and strong valueadding services to customers.

ASMPT currently invests about ten percent of its revenues in R&D. This makes it an ideal partner for an innovation and technology leader in photonics and optical device packaging such as AMICRA.

Following its successful penetration of the worldwide markets for high-precision die-attach equipment, especially in the rapidly growing silicon photonics assembly segment, AMICRA saw a perfect opportunity to merge with a strong strategic partner to better support its growing international customers base. With ASMPT's economic scale and well established supply chains and customer support capabilities, this will allow AMICRA to take the next step in the development of its business.

Dr Johann Weinhaendler, a member of the AMICRA executive management team, stated: "We are delighted to work with ASMPT. The expanded operational base offered by ASMPT is very important to us. We will continue to be a reliable partner to our existing and new customers focused on their specific needs and requirements. We will continue to offer excellent support, as well as innovative solutions. AMICRA's sub-micron high-accuracy die bonder product is complementary to the ASMPT group's existing portfolio and the AMICRAs leading position in the photonics assembly market, gives a high growth potential for AMICRA and ASMPT. We are confident that this joining of forces will further strengthen our growth opportunities and deliver even higher added value to our common customers.'

## Imec and Unisantis unveil ultra-scaled **EUV-enabled** surrounding gate transistor

imec, the research and innovation hub in nano-electronics and digital technology, and Unisantis Electronics Singapore Pte Ltd (Unisantis), a developer of Surrounding Gate Transistor (SGT) semiconductor technology, have announced significant progress in the joint development of a process flow targeting an SGT 6T-SRAM cell with areas between 0.0184 and 0.0205 square micrometre, meeting or exceeding the dense cell area in a N5 technology node. Studies show that the vertical gate-all-around SGT-based cells have a 20-30% reduced area compared to horizontal gate-all-around FETs, while also outperforming these in terms of operating voltage, standby leakage and stability. The Surrounding Gate Transistor is a vertical gateall-around architecture that was developed at Unisantis as the basis for a universal silicon technology platform for DRAM, NAND, Flash, and SRAM.

"SGTs have all the advantages of horizontal gate-all-around transistors, allowing a near-perfect electrostatic control of the transistor channel," says Professor Fujio Masuoka, Director and CTO at Unisantis and inventor of the SGT concept. "But because the channel is a vertical pillar, the concept has the potential for a significant area reduction compared to horizontal nanowire-based transistors."

Imec and Unisantis worked out the key process flow and steps for a 6T-SRAM cell using SGT. Through a novel Design process Technology Co-Optimization (DTCO), the researchers were able to develop an SRAM bit-cell area of 0.0205 square micrometer, using a minimum pillar pitch of 50 nm. This is a 24 percent improved scaling factor compared to the smallest SRAM designs to date, and makes the design ready for N5 technology node.

## Imec demonstrates cooling solution for high performance chips

IMEC, leading research and innovation hub in nano-electronics and digital technology, announced that it has demonstrated for the first time a low-cost impingement-based solution for cooling chips at package level. This achievement is an important innovation to tackle the ever-increasing cooling demands of high-performance 3D chips and systems.

High performance electronic systems are coping with increasing cooling demands. Conventional solutions realize cooling through combining heat exchangers that are bonded to heat spreaders that are then attached to the chip backside.

These are all interconnected with thermal interface materials (TIM) that create a fixed thermal resistance that can't be overcome by introducing more efficient cooling solutions. Direct cooling on the chip backside would be more efficient, but current direct cooling microchannel solutions create a temperature gradient across the chip surface.

The ideal chip cooler is an impingementbased cooler with distributed coolant outlets. It puts the cooling liquid in direct contact with the chip and sprays the liquid perpendicular to the chip surface.

This ensures that all the liquid on the chip surface has the same temperature and reduces the contact time between coolant and chip. However, current impingement coolers have the drawback that they are silicon-based and thus expensive, or that their nozzle diameters and use processes are not compatible with the chip packaging process flow.

Imec has developed a new impingement chip cooler that uses polymers instead of silicon, to achieve a cost-effective fabrication. Moreover, imec's solution features nozzles of only 300µm, made by high-resolution stereolithography 3D printing. The use of 3D printing allows e customization of the nozzle pattern design to match the heat map and the fabrication of complex internal structures. Moreover, 3D printing allows to efficiently print the whole structure in one part, reducing production cost and time.

"Our new impingement chip cooler is actually a 3D printed 'showerhead' that sprays the cooling liquid directly onto the bare chip," clarifies Herman Oprins, senior engineer at imec. "3D prototyping has improved in resolution, making it available for realizing microfluidic systems such as our chip cooler. 3D

printing enables an application-specific design, instead of using a standard design."

Imec's impingement cooler achieves a high cooling efficiency, with a chip temperature increase of less than 15°C per 100W/cm<sup>2</sup> for a coolant flow rate of 1 I/min. Moreover, it features a pressure drop as low as 0.3 bar, thanks to the smart internal cooler design. I

t outperforms benchmark conventional cooling solutions in which the thermal interface materials alone already cause a 20-50°C temperature increase. Next to its high efficiency and its cost-effective fabrication, imec's cooling solution is much smaller compared to existing solutions, matching the footprint of the chip package enabling chip package reduction and more efficient cooling.

## SCREEN signs MoU with National Tsing Hua University

SCREEN Semiconductor Solutions has signed a memorandum of understanding (MoU) with National Tsing Hua University (NTHU) in a ceremony commemorating the launch of the massively E-beam direct write lithography for 12-inch Si wafers (MEB12) program.

NTHU combined with international semiconductor equipment and software suppliers will establish the first massively electron beam direct writing (MEBDW) innovative semiconductor industryuniversity alliance to develop the state-ofthe-art maskless lithography technology.

The MEBDW lithography technology enables "on-chip security", making Taiwan the world's first development and pilot production for security chips with

unique IDs, providing information security for the Internet, AI, electronic payment and automotive chips.

The MEB12 program participants include the world's only commercial MEBDW lithography equipment manufacturer, Mapper Lithography B.V., from the Netherlands and U.S. design software supplier Synopsys, Inc. SCREEN will support the MEB12 program with both DUO lithography coat/develop track and SU-3200 single wafer cleaning systems.

As one of the MEB12 project initiators, Professor Po-Wen Chiu of NTHU's Department of Electrical Engineering and chairman of the Centre for Nanotechnology, Materials Science, and Microsystems, pointed out: "This project

is a successful case to use Taiwan's strong penetration capability in the semiconductor manufacturing sector, to form an alliance with international semiconductor giants and build up the most advanced commercial 12 inch MEBDW lithography process line in the campus, making NTHU the world's first university to have this unique R&D capability."

"We are very pleased to be supporting NTHU in Taiwan as they pioneer the MEB12 alliance," noted Tadahiro Suhara, president of SCREEN Semiconductor Solutions. "This is a testament to the value our SCREEN equipment technology and resources bring to innovative IoT applications."

## Imec 's cooling solution for high performance chips

IMEC, leading research and innovation hub in nano-electronics and digital technology, announced that it has demonstrated for the first time a low-cost impingement-based solution for cooling chips at package level. This achievement is an important innovation to tackle the ever-increasing cooling demands of high-performance 3D chips and systems.

High performance electronic systems are coping with increasing cooling demands. Conventional solutions realize cooling through combining heat exchangers that are bonded to heat spreaders that are then attached to the chip backside. These are all interconnected with thermal interface materials (TIM) that create a fixed thermal resistance that can't be overcome by introducing more efficient cooling solutions. Direct cooling on the chip backside would be more efficient, but current direct cooling microchannel solutions create a temperature gradient across the chip surface.

The ideal chip cooler is an impingementbased cooler with distributed coolant outlets. It puts the cooling liquid in direct contact with the chip and sprays the liquid perpendicular to the chip surface. This ensures that all the liquid on the chip surface has the same temperature and reduces the contact time between coolant and chip. However, current impingement coolers have the drawback that they are silicon-based and thus expensive, or that their nozzle diameters and use processes are not compatible with the chip packaging process flow.

Imec has developed a new impingement chip cooler that uses polymers instead of silicon, to achieve a cost-effective fabrication. Moreover, imec's solution features nozzles of only 300µm, made by high-resolution stereolithography 3D printing. The use of 3D printing allows e customization of the nozzle pattern design to match the heat map and the fabrication of complex internal structures. Moreover, 3D printing allows to efficiently print the whole structure in one part, reducing production cost and time.

"Our new impingement chip cooler is actually a 3D printed 'showerhead' that sprays the cooling liquid directly onto the bare chip," clarifies Herman Oprins, senior

engineer at imec. "3D prototyping has improved in resolution, making it available for realizing microfluidic systems such as our chip cooler, 3D printing enables an application-specific design, instead of using a standard design."

Imec's impingement cooler achieves a high cooling efficiency, with a chip temperature increase of less than 15°C per 100W/cm² for a coolant flow rate of 1 I/min. Moreover, it features a

pressure drop as low as 0.3 bar, thanks to the smart internal cooler design. It outperforms benchmark conventional cooling solutions in which the thermal interface materials alone already cause a 20-50°C temperature increase. Next to its high efficiency and its cost-effective fabrication, imec's cooling solution is much smaller compared to existing solutions, matching the footprint of the chip package enabling chip package reduction and more efficient cooling.

## RELIABILITY IS EVERYTHING WHEN MEASUREMENT MATTERS

We're so confident in the reliability of our laser technology inside our 0.1 µm particle counters that we're offering the industry's best laser warranty coverage-EVER.

#### LEARN MORE

See us at SEMICON West, July 10-12, Booth 843 or visit www.tsi.com/semi

# SEMICON<sup>®</sup> EUROPA

# SEMICONDUCTORS DRIVE SMART

13-16 Nov 2018, Messe München, Munich, Germany

# The Largest European Electronics Platform connecting Industry Leaders across the entire Manufacturing Supply Chain

As a **SEMICON Europa Attendee**, you'll have the unique opportunity to connect to a vital market and companies driving innovation in electronics. Join one of our conferences and technical sessions (Material, 2018FLEX Europe - be flexible Conference, Advance Packaging, TechARENAs, TechLOUNGE, Executive Networking events ...)

As a **SEMICON Europa Exhibitor**, you'll have access to every event attendee while strengthening your position as a leader in the electronics manufacturing supply chain and supporting the programs and initiatives that SEMI sponsors worldwide.

#### **2018 EXHIBIT OPTIONS**

**Raw Space**

SEMI Member EUR 295/sqm

Non-member\* EUR 395/sam

Reserve your booth today! Get in touch with our Tradeshow Operations: Annette Niedballa, aniedballa@semi.org Don't miss a variety of sponsorship opportunities. Contact SEMI Europe Sales, Denada Hodaj, dhodaj@semi.org

## Origami for cells:

## self-folding 3D cell grippers for recording

Imec develops self-folding microgrippers that wrap around cells and function as a recording shell for better cell-contact and higher signal quality.

> Many cell types in our body have the ability to generate electrical signals, the most prominent of which include heart and brain cells. It is through the coordinated activity of these so-called electrogenic cells that the brain is capable of highly intricate information processing, and the heart can efficiently perform its function. In order to gain more profound understanding of these processes, electrophysiologists are interested in eavesdropping on the cell's electrical

conversations. Microelectrode arrays (MEAs) are the method of choice since this technology can comprise up to tens of thousands of electrodes that can pick up small electrical signals, enabling parallel recording of a large number

of cells.

But cells whisper. The tiny signals are often only a few microvolts in amplitude and disappear in the noise. The key way to achieve high signal quality is to maximize the cell-electrode contact and electrical coupling. Current MEA-technology, however, has reached its limitation, as it is inherently 2D because of the wafer-based fabrication paradigm. Bridging the gap with more complex 3D interfacing, imec presents a novel multi-electrode chip with self-folding electrodes.

#### A tale of two labs

Grippers are not new. Notably, the Gracias Lab at Johns Hopkins University (JHU) in Baltimore (USA) has a long-standing experience researching new methods to fabricate micro- and nanoscale devices with integrated structures. For example, the lab designed self-folding microgrippers for a wide range of applications, including life sciences, such as mobile microgrippers for encapsulating red blood cells or even to take small cell biopsies from living tissue. It was the ability of the self-folding structures to grasp single cells that sparked the idea for a new project between JHU and imec.

> The Cell and Tissue Technologies (CTT) team of imec has built up extensive expertise regarding in vitro recordings of electrogenic cells using MEAs.

However, with the traditional, flat electrode layouts the cell-electrode contact area is limited. It became increasingly clear that 3D-interfacing is the way to go. And so the idea arose to incorporate tiny electrodes in the panels of Gracias' microgrippers. The collaboration between imec and JHU materialized in a JHU-summer internship and continued in the PhD-

topic of Jordi Cools, main imec-researcher on this project: "The question is: can we improve the interface by wrapping the electrodes around the cell and obtain better recordings that way? The collaboration with the Gracias Lab was the ideal way to find out because it is a perfect match between their expertise in self-folding materials and our state-of-the-art nanotechnology knowledge and cleanroom infrastructure."

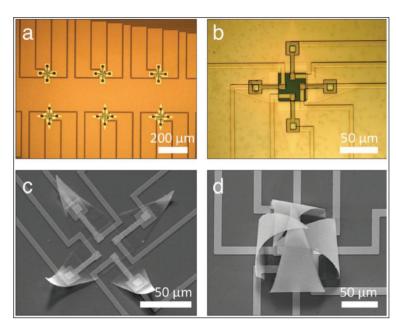

... The result is a first-of-its-kind chip with self-folding electrodes, that takes a leap forward from 2D planar recording to 3D cell interfacing...

#### It takes two layers

Each of the four arms of the microgripper contains a patterned and individually addressable electrode, allowing parallel and simultaneous readout from all sides of the cell. The secret to the folding lies in the hinges that are composed of a nanoscale SiO/SiO2 bilayer. Because of the lattice mismatch between these two layers, the thin film is intrinsically stressed.

"This is how it works: the microgrippers are first patterned on top of a dissolvable sacrificial layer. When the sacrificial layer is dissolved by the cell culture medium, the intrinsic stress of the bilayer is released and the panels with the embedded electrodes subsequently fold towards the middle, capturing any cell laying on top," Jordi explains. "The majority of the fabrication was performed in imec's III/V lab clean room, except for the deposition of the bilayer for which we could count on the expertise of CMST, an imec research group at Ghent University."

The bilayer is not only critical for the correct functioning of the grippers, but also for their performance. Jordi continues: "Using an ultrathin bilayer, we could make the panels flexible and curve during folding, so that they conformed to the shape of the cell. At the same time the panels are soft enough not to damage the cells. We demonstrated this by culturing primary heart cells on the grippers. The soft shell wrapped tightly around them, and - more importantly - the cells remained viable and functional, maintaining their electrical activity.

...Because the panels were literally pressing the electrodes against all sides of the cell, the measured signal amplitudes proved to be two times stronger than on a traditional 2D planar MEA configuration, simulated by unfolded grippers...

Moreover, our gripper design allowed for simultaneous recordings of every electrode on each of the four folded arms, making it possible to track signal propagation in the cells contained within the shell. The fact that this chip is capable of recording 3D spatiotemporal electrical signatures from captured cells is a unique advantage over traditional MEAs."

Fig 1: a) An array and b) a single planar micro-fabricated gripper with open panels, electrodes, and interconnects. Scanning electron microscopy (SEM) pictures of c) a semi-closed shell structure, illustrating the transition from the open to the closed configuration, and d) a completely closed shell with four individually addressable electrodes.

#### A firm grip on the future

The microgrippers herald the start of a new generation of MEAs, where dynamic cell-electrode interfacing and recording substitutes the traditional static electrode designs. Dynamic electrodes 'work' instead of trusting on a coincidental interface. Accordingly, future research efforts will focus on the next major step of combining these cell-sized multi-electrode shells with microelectromechanical systems (MEMS) in order to have precise control over the position and force of the gripper arms. Furthermore, future electrodes could be equipped with small needles to enable intracellular recordings or coated with drugs for drug screening or discovery.

"A large contributor to the success of this project was the excellent collaboration with the Gracias Lab in JHU," comments Dries Braeken, R&D manager Life Sciences and supervisor of Jordi's PhD. "It underlines the importance of fostering research ties with our partners. One of these joint efforts is the summer internship program in which we host every year three to five JHU students to work in the imec labs.

While they learn about our facilities and know-how, in turn we get familiar with the expertise of the JHU labs. That is how new science ideas take shape. The gripper-project is a successful illustration of this: what started off as a 10-week summer program, turned into a long-lasting collaboration. And it is only the beginning. As we continue with the program, I am convinced more new collaborative research opportunities will arise."

### research AFRI-AFI CMC

TO DATE, there have been no instances that link air quality to PEs, but that doesn't remove it from the list of variables to continue to research and consider. This is where highly advanced sensors come into play, sensors designed and developed by a team of scientists and engineers in both the Air Force Research Laboratory and the Air Force Life Cycle Management Centre. Although still in the research and development phase, this team is working together to complete a second-generation sensor package called the Real-Time Air Quality Sensor, or RTAQS, that will sense and assess cockpit air quality in real-time on high performance aircraft during flight.

"Most of the information to determine unexplained PEs is collected post-flight so much of the evidence is likely gone," explained Doug Hopkins, 711th Human Performance Wing chief engineer. "RTAQS is intended to close the gap so that we know what happens during the flight."

The first version of this sensor package was developed in 2015 and was a collaborative effort between the Airman Systems Directorate and the United States School of Aerospace Medicine, both within the 711th Human Performance Wing of AFRL. Researchers at the NASA-Glenn Research Center were also part of this collaboration.

## **AFRL-AFLCMC**

## collaborate on real-time air quality sensor

WHEN MOST THINK of hypoxia-like physiological events (PEs) some pilots have experienced in the cockpits of aircraft such as the recent propellerdriven T-6, the common assumption is an issue with the on-board oxygen generating system supplying oxygen to the pilot. But there are several other variables to consider, one being air quality.

> "We had a first-generation sensor package that we flight-tested at Edwards Air Force Base in an F-16, we got some results, and then came back to the lab to look for ways we could enhance that sensor with additional capabilities," said Jennifer Martin, a 711HPW research chemist.

The team is now testing sensors that could be put on the next version of that original package in order to improve the performance of its air quality testing. "We're in the early stages - just moving from the first generation sensor package design to the next," explained Martin. "These sensors could enable us to

rule out air quality as a root cause and they can focus on other variables such as equipment malfunction, bleed air and environmental control systems to try to figure out the driving force for physiological events." This team's research is part of the military's on-going effort to find what Air Force Chief of Staff Gen. David Goldfein calls "the smoking gun" in regards to PEs. Part of this research is looking at what other work has been done that could be leveraged with Air Force research. "RTAQS contains several embedded sensors, some of which were originally developed by NASA for use aboard the International Space Station," explained Martin. "NASA collaborated with us and

### research AFRI-AFI CMC

Makel Engineering, the technical integrator for the electronics and packaging. We're also leveraging the AFRL Small Business program via a Phase II Small Business Innovation Research award with Makel to help mature this technology."

Another part of this research is the testing phase, where these developmental sensors are put in

namely their accelerometer validation for this testing. David Ryerse, biomedical

test technician with AFLCMC, explained that this equipment has the capability to give different vibration profiles of aircraft and vehicles.

"We were contacted by 711HPW to use our vibration tables," stated Ryerse. "This table is able to do various aircraft profiles such as a jet or a high-vibration vehicle such as an Army Humvee. Whatever profile they wanted to see, we were able to produce the proper vibration profiles. They wanted to be able to see how each of these affected the accelerometer and the data."

Future versions of RTAQS are planned to sense accelerometry data in addition to air quality, said Mike Brother, 711HPW research scientist.

While the team wants to be able to see what chemicals are in the air, another goal is to be able to link those chemicals to a certain event during flight in order to inform the Root Cause Corrective Action teams from AFLCMC, who are responding to the physiological event.

"With this type of real-time sensing capability, we're trying to correlate maneuvers, aircraft parameters, as well as environmental conditions to possible conditions that could affect air quality," said Michael Brothers, a research scientist with 711HPW These sensors could also contribute to the life cycle maintenance needs of the aircraft, which could possibly improve resource efficiency, explained Grant Slusher, who is also a research scientist with 711HPW. "There's a distribution in how the aircraft's parts wear out," explained Brothers. "Maybe it's two months or maybe it's eight months, but if a maintainer has to go in and check everything after four months, it wouldn't be known if the part went bad at two months or if it's still good and might go another four months. So to have a sensor that could automatically indicate that would reduce manpower needs, reduce down time, and maximize resources."

The team of collaborators has funded studies to test operational aircraft at numerous Air Force bases,

said Martin. "We're also working to design a smaller version of the sensor that's specific to various cockpit space constraints and that could meet the longer-term vision of fleet-wide integration."

The team explained that they plan to have a number of different versions of this sensor to plug-and-play with various weapon systems and the program office needs in both the AF and US Navv. They also discussed the importance of their collaborations with academics and small businesses to see if down the line, some of their research can be more easily transitioned to other Department of Defense manned airborne platforms.

"The long term vision of this research is both to develop a sensor package for use in both PE root cause investigations and to integrate air quality sensors into all of our manned airborne platforms." explained Claude Grigsby, technical advisor for 711HPW's Human-Centered ISR Division. "These types of sensors could ultimately be utilized for immediate autonomous activation of back-up oxygen systems if an issue with the air supply is detected. When this work was initiated, as follow-up to previous PE investigations supported by the 711th Human Performance Wing, our goal was to create a capability where the pilot no-longer has to function as the sensor in the system."

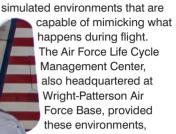

Jennifer Martin, research chemist with the 711th Human Performance Wing, displays the first generation version of the real-time air quality sensor (RTAQS) package. This sensor is the culmination of a collaborative effort between the 711HPW, NASA-Glenn, and Makel Engineering, Inc. to measure air quality during flight. (U.S. Air Force photo/Gina M. Giardina

# Driving growth, safety, and quality in automotive electronics

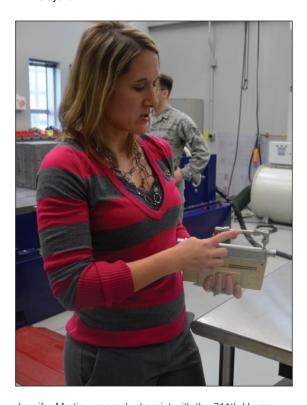

Sophisticated electronic systems continue to increase their impact across today's automotive sector. Radar, LiDAR, and a host of new artificial intelligence (AI)-based systems are becoming the norm as vehicle makers seek to improve safety, performance and efficiency on the road to fully autonomous vehicles. Linde Electronics describes ways that the automotive manufacturing supply chain can meet tight performance standards in pursuit of global market opportunities.

In 1913, Henry Ford revolutionized manufacturing with the inauguration of the first assembly line to produce automobiles, which reduced the time to make a new car from 12 hours to 2.5 hours, and more importantly, drove down the cost by 65%. Semiconductor manufacturing has been a beneficiary of this approach, as increasing automation has been complementary to the geometry shrinking forces responsible for Moore's Law. Both industries manufacture on a very high volume: there were approximately 87 million passenger vehicles and 87 million 300mm equivalent wafers fabricated in 2017. Today, robotics drives both industries to further cost reduction and improved quality.

More and more, these industries are connected, as electronic systems and semiconductors become a larger part of the total automotive bill of materials, and automotive applications become a larger percentage of the total semiconductor market. At the same time, electronics are responsible for a larger portfolio of car functions, progressing rapidly towards an anticipated revolution of fully automated driving vehicles. While electronics become more safety critical in vehicle operation, the quality requirements of the semiconductor components are increasing in ways the industry has not seen before. We can see in the daily financial news the competing headlines between large strategic plays in automated driving investments and developments punctuated by reports of crashes by test vehicles and private owners pushing their cars into uncharted levels of self-driving.

In this article, we look first at the expanding market and drivers that are linking the growth of the semiconductor and automotive businesses. Next, we evaluate the status of automotive semiconductor quality requirements and the developing needs for further specifications. Finally, we look further into the supply chain to examine the role that semiconductor process materials play in enhanced requirements for safety and quality.

#### Market overview

Electronic systems and passenger vehicles are both significant contributors to the global economy, representing about 2% each of global GDP, and their growth is increasingly interdependent. According to NXP, electronic systems represent more than one-third of the bill of materials for new cars. The chips themselves, including OSDs (optical, sensors, and discretes) now average nearly (USD) \$500 per vehicle. From the semiconductor industry perspective, automotive ICs and OSDs are 13% of application sales, and growing almost twice as fast as the overall industry. Just like PCs and smartphones, we expect the chip value of the overall electronics assembly to increase as the applications become a more critical part of vehicle operation.

This growth potential has attracted attention from many of the major players in semiconductor manufacturing as they try to both directly benefit from the higher multiples of the automotive sector, and to influence what kinds of chip designs will control future vehicles.

Many recent mergers and acquisitions have been viewed through the lens of increasing the acquirer's position in automotive applications: NXP's acquisition of Freescale, which had a larger share of automotive chip sales, and Qualcomm's pending takeover of NXP. Likewise, On Semiconductor increased its share by acquiring Fairchild, and Infineon has bought Wolfspeed and International Rectifier for silicon carbide technology important for power control in electrified vehicles.

Figure 1: Growth of automotive, semiconductor and vehicle markets [adapted from IC Insights]

Even more strategic plays have been pursued in the past year by Intel and Samsung. Intel has made a portfolio of automotive acquisitions, capped recently by the \$15 billion purchase of Mobileye for chip designs that support assisted and autonomous driving for customers like Tesla and BMW. For its part, Samsung purchased Harman for \$8 billion, Known best for its premium car audio offerings. Harman's products also include automotive navigation. communication, and cybersecurity. It brings with it a customer portfolio of most of the major vehicle manufacturers in Europe, Japan, and the United States.

**Primary drivers**

While we may think of semiconductors as being rather recent introductions, associated with many of the comfort, convenience, and infotainment options now available, computer chips have long been an integral, if unseen, part of the cars we drive.

Operations and environmental controls

In 1968, just ten years after the modern IC industry was born, Volkswagen introduced an electronic control unit (ECU) manufactured by Bosch for regulation of fuel injection. As emission and fuel efficiency requirements became more stringent, ECUs were made standard on most vehicles manufactured. Controllers have proliferated in cars ever since: engine temperature, electronic steering and braking, automatic transmissions, as well as controls for smaller parts like wipers, mirrors, and illumination. Airbag sensors/actuators and anti-lock brakes have made driving safer.

O Convenience, comfort and infotainment

More obvious in modern cars are the proliferation of many electronic functions, which have a higher density than our connected offices and homes. Conveniences and comfort functions are almost everywhere accessible in the vehicle: power windows, climate control, charging ports, remote operations, as well as those actually related to

driving like cruise control and passive seatbelt use indicators. More recently, infotainment offerings have also quickly advanced from radio and recorded media players to include multiple display screens for indicators, controls, navigation, and entertainment in addition to connectivity for the vehicle and the devices we bring inside it. As a safety feature, the US National Highway Traffic Safety Administration has required rear-view cameras for vehicles less than 4500 kg sold after May 2018.

#### ADAS to full autonomy

The basics of ADAS (advanced driver assistance systems) are already in premium vehicles today: adaptive cruise control, lane departure warnings, and drowsy driver detection are just a few of the controls and sensors available. However, these are just the beginning of what is anticipated to be a rapidly advancing revolution in driving technology, which will transform the operation of driving from one where the driver is assisted passively by various electronic information and controllers, to one where the vehicle operates fully autonomously, that is independently, of any occupant in the vehicle.

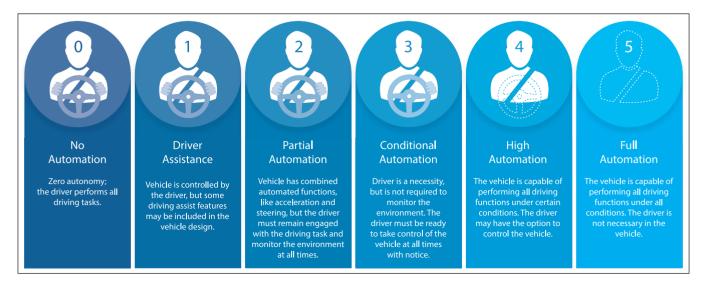

The roadmap to full autonomous driving is populated not only with significant developments in technology, but also with safety protocols. Various automotive authorities have created stages on this roadmap, such as the SAE (Society of Automotive Engineers) characterization in Figure 2. Common protocols among autonomous vehicles will need to be agreed to benefit from information sharing between vehicles.

To achieve fully autonomous driving, sensors and controllers are just the beginning of the electronics requirements. Extreme amounts of data will need to be received, prioritized, analyzed, and shared in real time. Intel estimates that cars will generate data at a rate of nearly 0.75 Gb/s, or around

Figure 2: SAE designated level of autonomous driving capability

4 Tb per average 90-minute usage per day, rivaling the fastest broadband connections available today. Processors like emerging GPUs for artificial intelligence are thought to be the likely means of dealing effectively with data-rich processing, which gives companies like Nvidia and AMD and the foundries that supply them access to this emerging application. And autonomous vehicles will need to receive and share relevant data with each other, which will require new levels of cloud connectivity and capacity, explaining the strong early investment in ADAS from cloud giants like Baidu, Google, and Microsoft.

#### Electrification

In a development roadmap roughly parallel to autonomous driving, electrification of powertrains will also transform the automotive industry and become a new growth application for semiconductors. Already available from established and new automobile manufacturers either as fully electric vehicles or as hybrid electric motor-combustion engine models, electrified vehicles have roughly double the semiconductor content per vehicle. The adoption of electric vehicles is driven by environmental concerns - the reduction of greenhouse gas, NOx, and particle emissions - as well as improvement of vehicle performance and maintenance. Bolstering adoption is the future ban of sales of combustion engines by major economies like India, China, and much of Europe by 2040. Already, 3% of vehicles sold in 2017 were electric.

#### Diverse electronics content

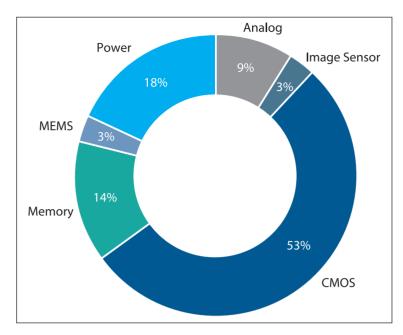

Automotive electronics is an application that cannot be defined by specific technologies or applications, which benefits almost all sectors of the semiconductor industry. Currently, it is characterized by a very large portfolio of products based on mostly mature technologies, spanning from discrete, optoelectronics, MEMS and sensors, to integrated circuits and memories.

Figure 3 shows the distribution of silicon content from an analysis of an early electrified car in 2014. Important to note is that this car has no autonomous driving capability. If all vehicles made today had the same level of electronics intensity as this example car, the semiconductor content would require the equivalent of 600,000 wafer starts per month of 300mm fab capacity.

#### **Enhanced quality**

Until now, the automotive electronics market has been the preserve of specialized semiconductor manufacturers with long experience in this field. The reason for this is the specific know-how required for quality management. As applications proliferate, become safety critical, and progress towards leadingedge processes, enhanced quality protocols will be required.

Figure 3: Semiconductor content in BMW i3 in relative silicon area [adapted from Applied Materials]

A component failure that appears harmless in a consumer product could have major safety consequences for a vehicle in motion. Furthermore, operating conditions of automotive electronics components (temperature, humidity, vibration, acceleration, etc.), their lifetime, and their spare part availability are differentiators to what is common for consumer and industrial devices.

Currently, some of the most technologically advanced vehicles integrate around 450 semiconductor devices. As they become significantly more sophisticated, the semiconductor content will drastically increase, with many components based on the most advanced semiconductor technology available. Introducing artificial intelligence will require advanced processors capable of computing a massive amount of data stored in high-performance and high capacity memory devices. This implies that not only the most advanced semiconductor processes will be used, but that these will need to achieve the highest degree of reliability to allow a flawless operation of predictive algorithms.

It is expected that smart vehicles capable of fully autonomous driving will employ up to 7,000 electronic components. In this case, even a failure rate of 1ppm, already very low by any standard today, would lead to 7 out of 1.000 cars with a safety risk. This is simply unacceptable. The automotive electronics industry has therefore introduced quality excellence programs aimed at a zero-defect target. Achieving such a goal requires a lot of effort and all constituents of the supply chain must do their part.

The automotive electronics industry is one of the most conservative in terms of change management. Long established standards and documentation procedures

| Typical operating conditions for different electronics market segments |                |               |                    |  |  |  |

|------------------------------------------------------------------------|----------------|---------------|--------------------|--|--|--|

|                                                                        | Consumer       | Industrial    | Automotive         |  |  |  |

| Temperature                                                            | 0 to 40°C      | -10 to 70°C   | -40 to 160°C       |  |  |  |

| Operation time                                                         | 2 to 5 years   | 5 to 10 years | Up to 15 years     |  |  |  |

| Humidity                                                               | Low            | Environment   | 0% to 100%         |  |  |  |

| Supply                                                                 | Average 1 year | 2 to 5 years  | Up to 30 years     |  |  |  |

| Tolerated failure rate                                                 | <10%           | <<1%          | Target: 0% failure |  |  |  |

Figure 4: Typical operating conditions for different semiconductor applications ensure traceability of design and manufacturing deviations. Qualification of novel or modified products is generally costly and lengthy. This is where material suppliers can offer competence and expertise to provide material with the highest quality standards.

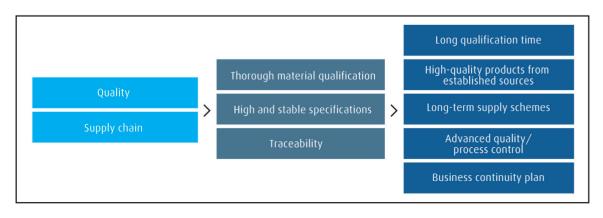

## What does this mean for a material supplier?

As a direct contact to its customer, the material supplier is responsible for the complete supply chain from the source of the raw material to the delivery at the customer's gate. The material supplier is also accountable for long-term supply in accordance with the customer's objectives.

There are essentially two fields where the material supplier can support its customer: quality and supply chain.

Given the constraints of the automotive electronics market, material qualification must follow extensive procedures. While a high degree of material purity is a prerequisite, manufacturing processes are actually more sensitive to deviations of material quality, as they potentially lead to process recalibration. Before qualification starts, it is critical that candidate materials are comprehensively documented. This includes the manufacturing process, the transport, the storage, and, where appropriate, the purification and transfill

operations. Systematic auditing must be regularly performed according to customers' standards. As a consequence, longer qualification times are expected. Any subsequent change in the material specification, origin, and packaging must be duly documented and is likely to be subject to a requalification process.

Material quality is obviously a critical element that must be demonstrated at all times. This requires the usage of high-quality products with a proven record. Sources already qualified for similar applications are preferred to mitigate risks. These sources must show long-term business continuity planning, with process improvement programs in place. Purity levels must be carefully monitored and documented in databases.

State-of-the-art analysis methods must be used. When necessary, containment measures should be deployed systematically. Given the long operating lifetime of automotive electronic components, failure can be related to a quality event that occurred a long time before.

Because of the necessary long-term availability of the electronics components and the material qualification constraints, manufacturers and suppliers will generally favor a supply contract over several years. Therefore, the source availability and the supply chain must be guaranteed accordingly.

Material suppliers are implementing improved quality management systems for their products to fulfill the expectations of their customers, in terms of quality monitoring and traceability. Certificate of analysis (COA) or consistency checks are not sufficient anymore: more data is required. In case deviation is detected, the investigation and response time must be drastically reduced and allow intervention before delivery to the customer. Finally, the whole supply chain must be monitored.

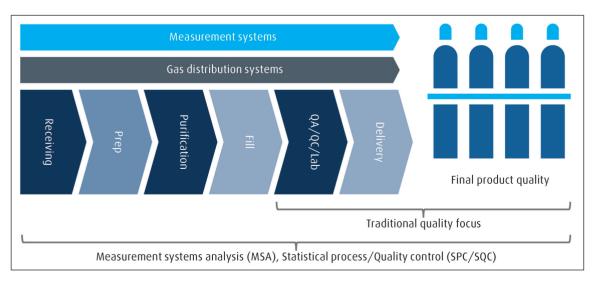

Several tools must be implemented to maintain a reliable supply chain of high-quality products: statistical process and quality controls (SPC/SQC), as well as measurement systems analysis (MSA), allow systematic and reliable measurement and information recording for traceability. Implementing these tools particularly at the early stages of the supply chain allows an "in-time" response and correction before the defective material reaches the customer's premises. Furthermore, some impurities that were ignored before may become critical, even below the current detection limits. Therefore, new measurement techniques must be continuously investigated to enhance the detection capabilities.

Finally, a robust supply chain must be ensured. It is imperative for a material supplier to be prepared to handle critical business functions such as customer orders, overseeing production and deliveries, and other various parts of the supply chain in any situation. Business continuity planning (BCP) was introduced several years ago to identify and mitigate any risk of supply chain disruption.

Analyzing the risks to business operations is fundamental to maintaining business continuity. Materials suppliers must work with manufacturers to develop a business continuity plan that facilitates the ability to continue to perform critical functions and/ or provide services in the event of an unexpected interruption. The goal is to identify potential risks and weakness in current sourcing strategies and supply chain footprint and then mitigate those risks.

Because of the efforts necessary to qualify materials, second sources must be available and prepared to be shipped in case of crisis. Ideally, different sources should be qualified simultaneously to avoid any further delay in case of unplanned sourcing changes. Material suppliers with a global footprint and worldwide sourcing capabilities offer additional security. Multiple shipping routes must be considered and planned to avoid disruption in the case, for instance, of a natural disaster or geopolitical issue affecting an entire region. Material suppliers need to be aware and monitor regulations specific to the automotive electronics industry such as ISO/TS16949 (quality management strategy for automotive industries). This standard goes above and beyond the more familiar ISO 9001 standard. By understanding the expectations of suppliers to the automotive industry, suppliers can ensure alignment of their quality systems and the documentation requirements for new product development or investigations into non-conformance.

#### Future of automotive electronics

With the increasing automation of future vehicles, new and more advanced semiconductor technologies will be used and vehicles will become supercomputers and data centers on wheels. Most of these components (logic or memory) will be built by manufacturers relatively new to the automotive electronics world-either integrated device manufacturers (IDM) or foundries.

In order to comply with the current quality standards of the automotive industry, these manufacturers will need to adhere to more stringent standards imposed by the automobile industry. They will find support from materials suppliers like Linde that can deliver highquality materials associated with a solid global supply chain with acquired global experience in automotive electronics.

Figure 6: Enhancing material quality requires expanding traditional quality focus

## Future nodes require new defect reduction strategies

Existing defect reduction protocols have proven less than ideal for reducing waste and speeding production as transistor geometries shrink and process complexity increases. Brewer Science offers insights into tools and analytical techniques that can improve defect elimination in devices below 10 nm

### By Darin Collins, Director of Metrology, Brewer Science

AS THE SEMICONDUCTOR INDUSTRY migrates to advanced lithography at the 10-nm node and beyond, standard best practices for defect reduction will be insufficient. Contamination levels will need to be measured in parts per trillion (ppt). Defect reduction at this level requires improvements in analytical tools, quality control (QC) and quality engineering (QE). Semiconductor manufacturers looking to reduce defect levels for advanced nodes must carefully control and characterize their entire supply chain, starting with raw materials. Raw materials suppliers typically provide data on the purity levels

Total scrap to revenue 2015 Continuous improvements have helped to reduce scrap cost year over year

Figure 1: Brewer Science's scrap cost as a percentage of revenue, showing reduction each year.

of their chemicals, but purity is insufficient to give semiconductor manufacturers confidence that the material will enable them to meet their yield requirements. They need data on the detailed impurity profiles at the level of parts per billion (ppb) or ppt. This requires either going to their materials suppliers' sub-suppliers or conducting extensive testing on all materials received.

What can raw materials suppliers do to differentiate themselves and gain the confidence of potential customers in the semiconductor industry? Quite a bit. At least three primary opportunities exist for companies developing materials and processes to support semiconductor and microelectronic device fabrication: data collection and analysis; factory automation; and a cultural emphasis on quality.

Although it is not yet standard industry practice, some suppliers provide mass spectrometry data on their chemicals. Such data describe levels of multiple metal impurities at the ppb or ppt level, and can track the history of these impurity levels. Brewer Science, for example, monitors levels of at least 10 common metal contaminants, with detection levels ranging from 4 to 13 ppt, and provides the resulting data to customers. Semiconductor manufacturers can work with a certain level of impurities, so long as values are consistent and manufacturers understand how different impurities are affecting their yields. By continuously tracking data on metal impurities, chemical precursors and other contaminants, any deviation from the baseline shows up. The better manufacturers understand how these deviations affect device yield, the better they

### nodes defect reduction

can optimize their process to keep yield as high as possible. The approach must be collaborative in order for these slight deviations to be understood. Suppliers can incorporate several techniques to decrease the level of impurities in their products and improve consistency in impurity profiles. These practices include factory automation, closed-loop systems and failure mode effects analysis (FMEA).

Factory automation improves production quality in several ways. In the world of manufacturing, there should ideally be no such thing as employee error, and factory automation is a necessary step toward decreasing it. Factory automation that improves product consistency can dramatically reduce the volume of product scrapped, even as production quantities increase (Figure 1).

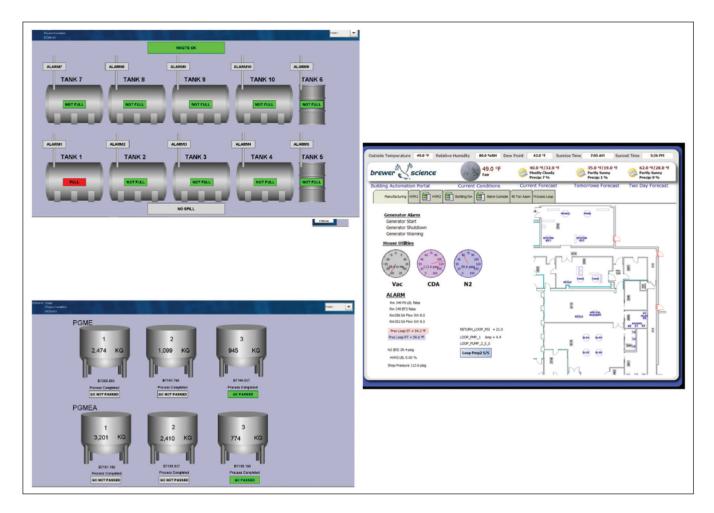

An optimized factory automation setup (Figure 2) will allow employees to see every part of the manufacturing process on a single screen, enabling them to easily monitor those and act immediately if anything is out of specification. Alarms and alerts in real time can be sent via text and email, allowing employees to monitor systems remotely via their smartphones.

An automated factory creates a massive stream of data. Quality engineers can analyze these data to continuously improve their processes. These results allow employees to understand the impact of quality improvements, and empower them to focus on product quality. Having a history of the impurity profile of a product makes it easier to know where to tighten processing specifications to produce a more consistent result.

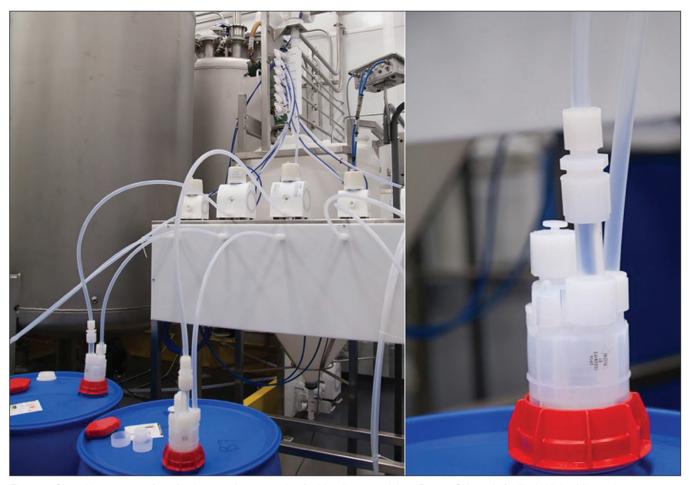

Factory automation also reduces the possibility of contamination. At Brewer Science, the blending and bottling of chemicals occurs in a closed-loop system (Figure 3). What is today a competitive advantage will soon be necessary to attract customers. As their own defect requirements tighten, semiconductor manufacturers will begin demanding higher levels of cleanliness, automation and characterization from their raw materials suppliers. The traditional advanced on-wafer defect instrumentation isn't able to detect the impact of raw materials in the supply chain. Typical solutions are found in the sub-supplier detection capability and process stabilization.

QE plays an important role in achieving continuous improvement. While FMEA is a standard tool in many manufacturing environments, it isn't always used optimally. The ideal approach to FMEA is to evaluate all possible failure modes together and incorporate lessons learned to avoid repeating mistakes. FMEA is useful at many stages of product development: when

Figure 2: Factory automation portal. In this example, tank 1 has an issue that needs to be addressed).

### nodes defect reduction

Figure 3: Closed-loop system from feed stream in preparation for blending materials at Brewer Science's facility in Vichy, Missouri.

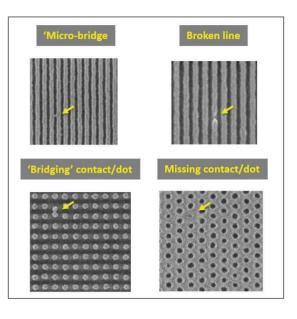

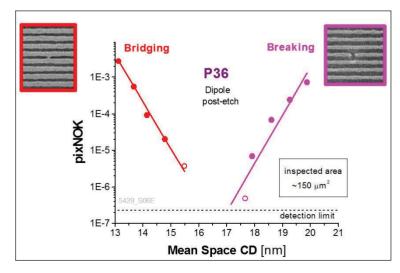

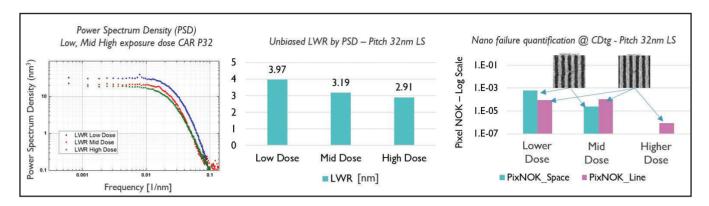

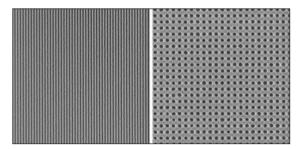

a product or process is first being designed; when it is being applied in a new way; or when analyzing failures or planning improvements for an existing product or process.