## SENICONDUCTOR Connecting the Silicon Semiconductor Community

Volume 41 ISSUE III 2020

🄰 @siliconsemi

www.siliconsemiconductor.net

#### Implementing smart manufacturing

ACM is passionate about cleaning wafers

#### Enabling smaller, lowerpower IoT & wearables

#### Rely on SAM for 3D package device analysis

#### Structural defects in TO-22

**Inside** News Review, News Analysis, Features, Research Review, and much more... Free Weekly E News round up go to: <a href="https://www.siliconsemiconductor.net">www.siliconsemiconductor.net</a>

### ACCELERATING HETEROGENEOUS INTEGRATION

VG

EV Group establishes Heterogeneous Integration Competence Center<sup>™</sup> to accelerate new product development fueled by heterogeneous integration and advanced packaging

Open access innovation incubator for EVG customers and partners across the microelectronics supply chain, guaranteeing the highest IP protection standards

Combining EVG's world-class wafer bonding, thin-wafer handling and lithography products and expertise, as well as pilot-line production facilities and services

Leveraging the state-of-the-art cleanroom facilities at EVG's headquarters in Austria, supported by EVG's worldwide network of process technology teams

**GET IN TOUCH** to discuss your manufacturing needs HeterogeneousIntegration@EVGroup.com

## editor'sview

By Mark Andrews, Technical Editor

#### IC manufacturing during 2020's new normal

AS THIS ARTICLE IS WRITTEN, our industry is a week away from SEMICON West – If this were a 'business-as-usual' time I would be packing, updating my interview schedule for a week in San Francisco, and doing all those other pre-trip things that an industry veteran undertakes before taking to the road. But not in 2020.

SEMICON West 2020 is a virtual event, so meetings will be attended using video conferencing platforms; our magazine trade show booth will be built of electrons in cyberspace. More changes amongst the many that all of us have had to deal with at a time when we are still trying to achieve balance between important and sometimes conflicting objectives.

Even as we think of how our school age children will attend class this fall, or the many other things that continue to change almost daily, the SEMI trade group reported that North Americabased manufacturers of semiconductor equipment posted \$2.35 billion in May billings worldwide, which is 2.9 percent higher than the final April 2020 level of \$2.28 billion, and a whopping 13.1 percent higher than May 2019 billings. It seems that no matter what happens around us, technology continues to be a societal 'glue' that enables all types of work and life scenarios that were unimaginable mere months ago.

In this pre-SEMICON West edition, Linde Electronics reports on new innovations that the company has developed to radically speed ion implantation for the manufacture of advanced ICs. ACM Research describes ways that its latest wafer cleaning system additions have combined the benefits of wet bench and single chamber cleaning systems to speed cleaning while

dramatically reducing the amount of sulfuric acid used to eliminate contaminants in advanced node wafer processing. Edwards Vacuum also provides an update on ways its smart manufacturing techniques are transforming the sub-fab to enable more uptime while cutting overall costs.

'Business Unusual' continues to challenge our industry. But we have also seen resilience and growth that demonstrate how we can productively live and work safely, even within our very changed world. Stay safe – I hope to see you (virtually) at SEMICON West.

Publisher & Editor Jackie Cannon jackie.cannon@angelbc.com +44 (0)1923 690205 Technical Editor Mark Andrews mark.andrews@angelbc.com Sales & Marketing Manager Shehzad Munshi +44 (0)1923 690215 shehzad.munshi@angelbc.com USA Representatives Tom Brun Brun Media tbrun@brunmedia.com +001 724 539-2404 +001 724-929-3550 Janice Jenkins jjenkins@brunmedia.com Director of Logistics Sharon Cowley sharon.cowley@angelbc.com +44 (0)1923 690200 Design & Production Manager Mitch Gaynor mitch.gaynor@angelbc.com +44 (0)1923 690214 Circulation Director Scott Adams scott.adams@angelbc.com +44 (0)2476 718970 Chief Executive Officer Stephen Whitehurst stephen.whitehurst@angelbc.com +44 (0)2476 718970 Joint Managing Director Sukhi Bhadal Joint Managing Director Scott Adams Directors Jackie Cannon, Sharon Cowley

sukhi.bhadal@angelbc.com scott.adams@angelbc.com

+44 (0)2476 718970 +44 (0)2476 718970

Published by Angel Business Communications Ltd, Unit 6, Bow Court, Fletchworth Gate, Burnsall Road, Coventry CV5 6SP, UK. T: +44 (0)2476 718 970 F: +44 (0)2476 718 971 E: info@angelbc.com

Silicon Semiconductor is published four times a year on a controlled circulation basis. Non-qualifying individuals can subscribe at: £50.00/€60 pa (UK & Europe), £70.00 pa (Outside Europe), \$90.00 pa (USA). Cover price £4.50. All information herein is believed to be correct at time of going to press. The publisher does not accept responsibility for any errors and omissions. The views expressed in this publication are not necessarily those of the publisher. Every effort has been made to obtain copyright permission for the material contained in this publication. Angel Business Communications Ltd vill be happy to acknowledge any copyright oversights in a subscenuent issue of the publication. Angel Business Communications Ltd © Copyright 2020. All rights reserved. Contents may not be reproduced in whole or part without the written consent of the publishers. The paper used within this magazine is produced by chain of custody certified manufacturers, guaranteeing sustainable sourcing. US mailing information: Silicon Semiconductor is published four times a year or a year or a specific or \$90.00 by Angel Business Communications Ltd, Unit 6, Bow Court, Fletchworth Gate, Burnsall Rd, Coverity CVS 65P. UK. Periodicals postage paid at Rahway, NJ. POSTMASTER: send address changes to: Silicon Semiconductor, c/o Mercury International Ltd, 365 Blair Road, Avenel, NJ 07001. Printed by: The Manson Group. © Copyright 2020. ISN 2050-7798 (Print) ISN 2050-77801 (Online).

We strive for accuracy in all we publish; readers and contributors are encouraged to contact us if their recognise an error or omission. Once a magazine edition is published [online, in print or both], we do not update previously published articles to align old company names, branding, marketing efforts, taglines, mission statements or other promotional verbiage, images, or logos to newly created or updated names, images, typographic renderings, logos (or similar) when such references/images were accurately stated, rendered or displayed at the time or the original publication. When companies change their names or the images/ket used to represent the company, we invite organizations to provide Angel Business Communications with a news release detailing their new business objectives and/or other changes that could impact how customers/prospects might recognise the company, contact the organization, or engage with them for future commercial enterprise.

#### VOLUME 41 ISSUE III 2020

# CONTENTS

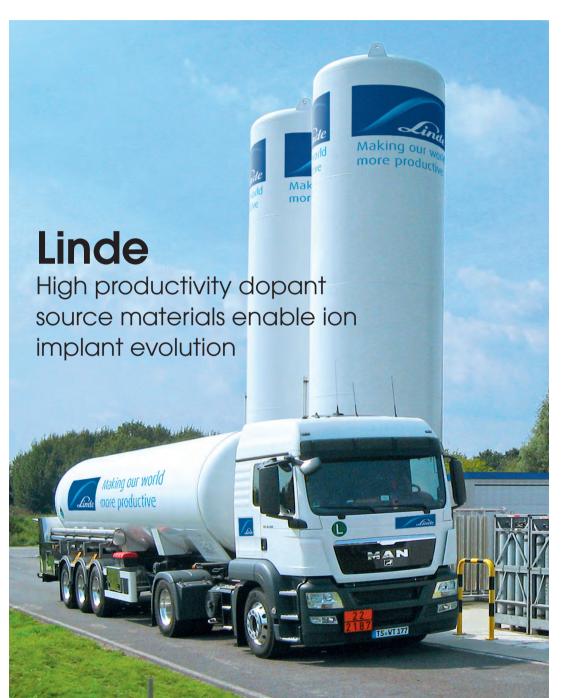

#### 10 COVER STORY High productivity dopant source materials enable ion implant evolution

Ion implantation has become a key enabling process in semiconductor fabrication. However, some of the newest implant species present challenges that can slow production. Linde Electronics has pioneered new technology to accelerate species implantation and help ensure high quality.

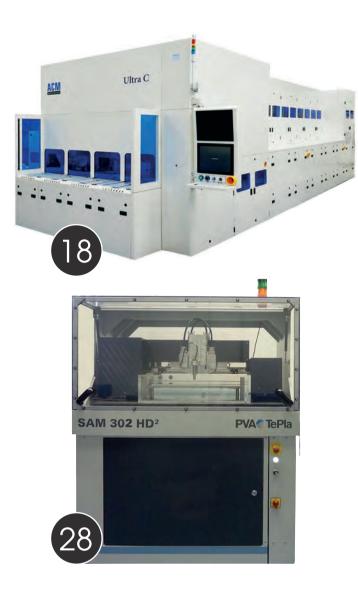

#### 18 ACM Research is passionate about cleaning wafers

The critical importance of wafer cleaning grows with each new semiconductor node. As geometries shrink, even minute contaminants have outsized impacts. Particles that didn't effect performance at the 28nm node can become 'killers' at 10nm and below.

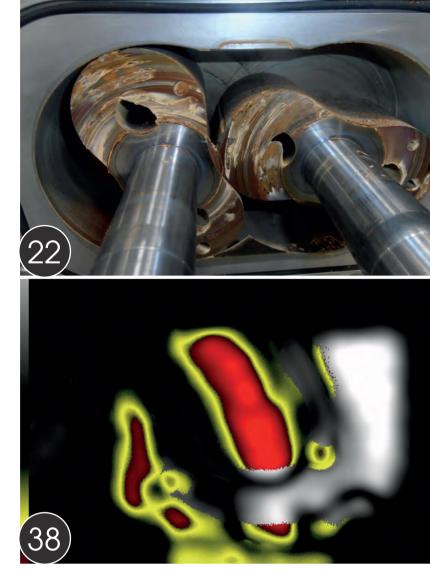

22 Implementing smart manufacturing in the sub-fab through operational excellence

> Silicon Semiconductor recently explored methods for implementing smart manufacturing and Industry 4.0 concepts in the sub-fab through a webinar presented by Edwards Vacuum.

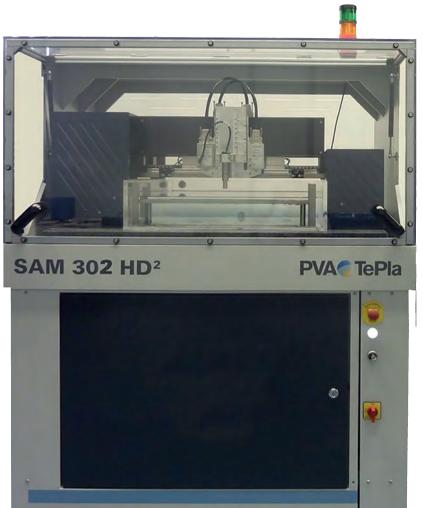

## 28 Rely on SAM for 3D package device analysis

The emergence of highly accurate wafer bonding and die stacking has enabled new generations of 3D semiconductors.

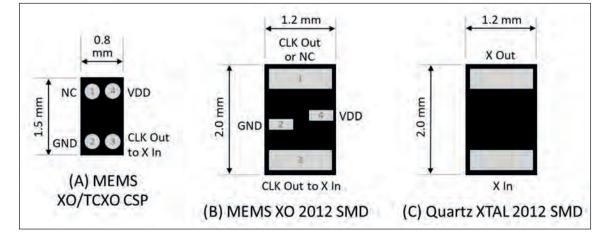

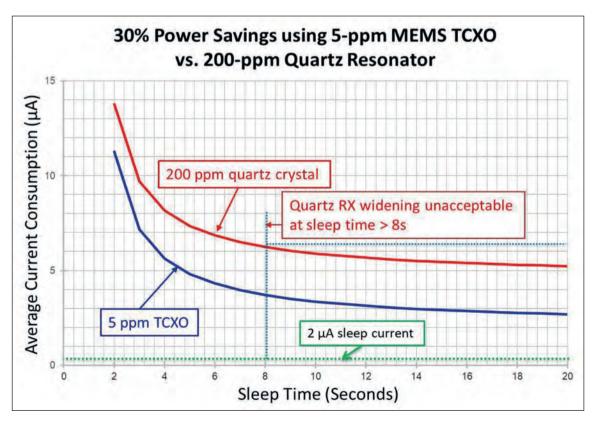

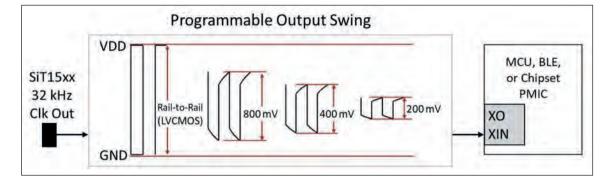

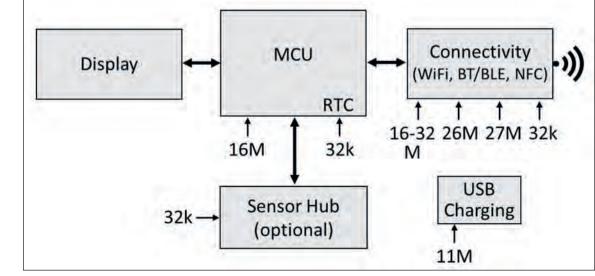

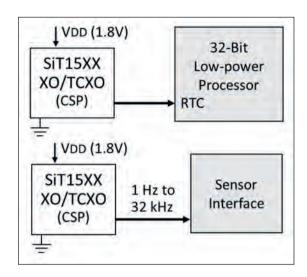

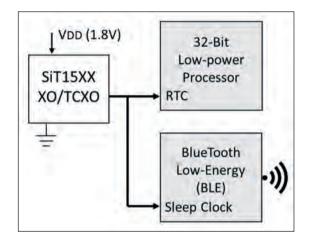

#### 32 MEMS oscillators: enabling smaller, lowerpower IoT & wearables

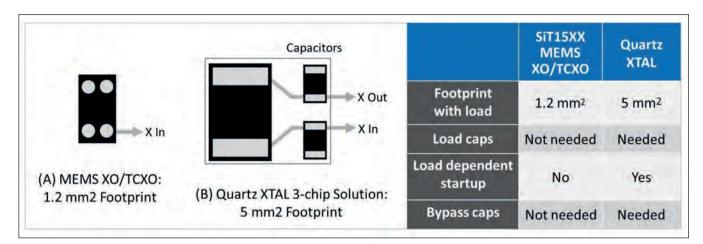

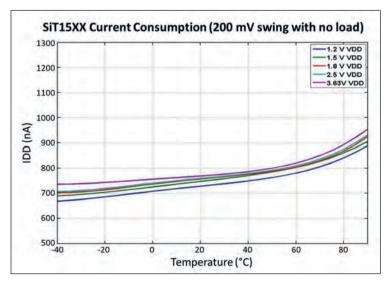

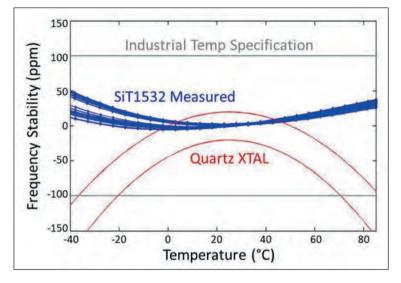

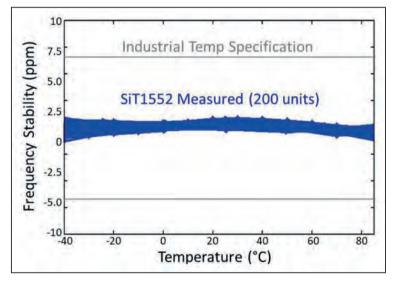

SiTimes makes a case for MEMS oscillators versus quartz-crystal-based clocking sources.

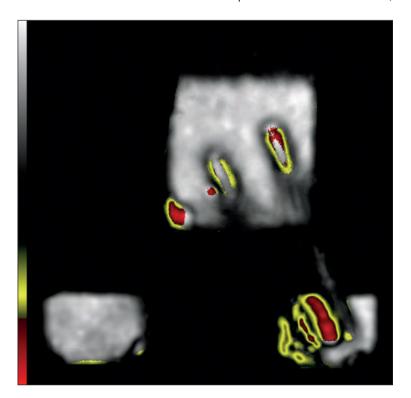

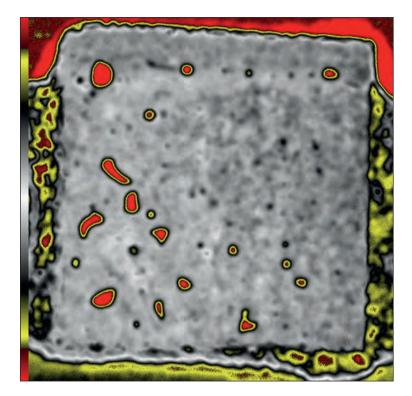

#### 38 Structural defects in TO-22

Ultrasound and X-ray work together to image and evaluate harmless anomalies and potential field failures in a TO-220 package.

42 The vertical ferroelectric FET: a new contender for 3D-NAND Flash memory and machine learning

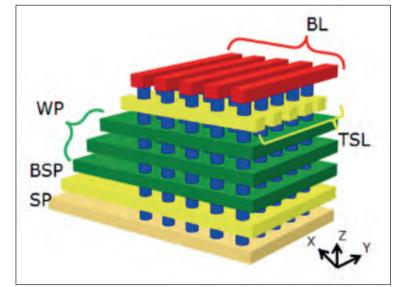

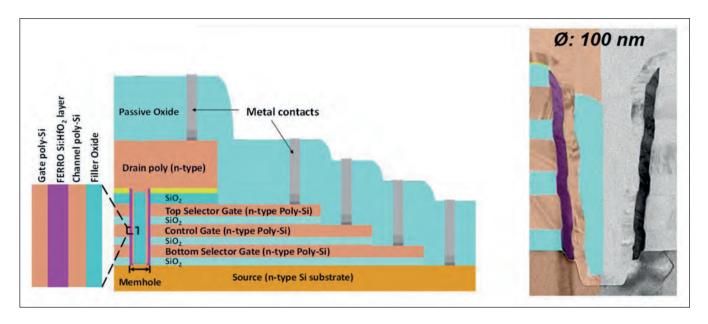

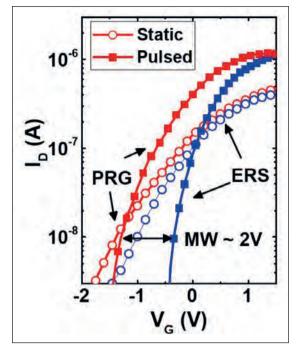

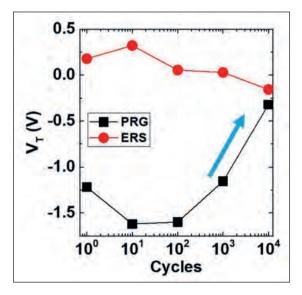

> Jan Van Houdt, Scientific Director at imec, explains how the FeFET works and how this exciting 'newcomer' might fit in the next-generation memory landscape.

#### news

- 06 130 years of Pfeiffer Vacuum

- 07 Canon launches FPA-8000iW semiconductor lithography system

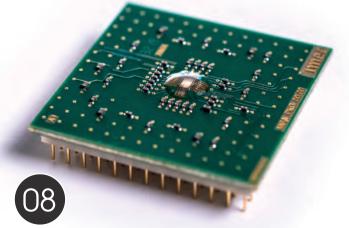

- 08 Imec and GLOBALFOUNDRIES announce breakthrough in AI chip

### 130 years of Pfeiffer Vacuum

PFEIFFER VACUUM has been influencing developments in vacuum technology for 130 years. Science and industry have benefited equally from the numerous innovations developed and successfully brought to the market by this longestablished company.

A key example being the turbomolecular pump, which was developed by the company in 1958 and has been integral to the market ever since. Thanks to its expertise, Pfeiffer Vacuum is still considered one of the world's market and technology leaders in this field.

When Arthur Pfeiffer founded the company in Wetzlar, Germany, in 1890, he initially devoted his attention to the production of remote ignition systems for gas lamps. Once electric light bulbs had established themselves on the market, the company founder quickly turned his attention to the new lighting technology that led him to look at the vacuum technology used in its production.

Arthur Pfeiffer quickly recognized the significance that vacuum technology could have in practically all areas of industry and research – and he subsequently concentrated entirely on this field. Since then, Pfeiffer Vacuum has played a key role in shaping vacuum technology.

Today, customers include the Max Planck Institute, CERN, XFEL and EADS - vacuum pumps made by the Asslarbased manufacturer are even in use in the ISS space station.

There, as in many other applications, the customer's requirements are often verv complex - not only with regard to the vacuum requirement itself, but also to the specifics of the system in question, the materials and products used or to be processed, and the process conditions. Automotive components, smartphones, pacemakers, textiles - vacuum technology is used for all these products and its solutions play an important role in both food production and in the pharmaceutical industry. Products and solutions from Pfeiffer Vacuum are developed for the fields of analytics. industry, research and development, coating systems and semiconductors.

Dr. Eric Taberlet, Chief Executive Officer of Pfeiffer Vacuum Technology AG: "With our durable products and customized vacuum solutions, we

are able to satisfy practically every customer requirement and to establish relationships that will endure for years to come.

At Pfeiffer Vacuum, 'sustainability' is not just an empty word. We are aware of our responsibility. And this is why, at all our locations around the world, we establish the necessary conditions to make sure that our staff enjoy working for Pfeiffer Vacuum.

We are socially committed, because we want to give something back, and we produce our products in the most energy-efficient and environmentally compatible manner possible. We have been living and breathing sustainability – by tradition – for 130 years.

#### Rohm announces LEDs for colour universal design

ROHM recently announced the 1608-size high accuracy blue-green chip LEDs, SMLD12E2N1W and SMLD12E3N1W. These products support the adoption of Colour Universal Design (CUD) in a variety of applications, such as fire alarm system indicator lights, industrial equipment warning lamps and public transportation information displays.

Colour is considered to be one of the most important means of communication and is used in a variety of ways – daily. However, approximately over 200 million people with P-type and D-type colour deficiencies around the world find it difficult to distinguish between red and green, possibly resulting in information being inaccurately conveyed – depending on the combination of colours used. Furthermore, since colour vision can vary from person to person, it is difficult to perceive how different people see certain colours, which can be very inconvenient and also problematic as other people may not notice this deficiency.

As a result, there is a growing need in the society to implement Colour Universal Design that takes into account the various types of colour vision in order to deliver information accurately to as many people as possible.

Rohm succeeded in developing blue-green chip LEDs with special wavelengths. These products are ideal for implementing colour Universal Design in a wide range of devices, using a vertically integrated production system from the element fabrication stage and leveraging Rohm's strength thorough quality control. The SMLD12E2N1W and SMLD12E3N1W are the first 1608 size LEDs to be certified by the Japanese NPO (Non-Profit Organisation), Colour Universal Design Organisation (hereafter referred to as CUDO) – making it possible to achieve colour schemes and designs that can be easily discernible by everyone, including those who cannot distinguish differences in colour.

In addition, adopting a new resin allows Rohm to significantly extend the LED lifetime while reducing the degradation of light intensity compared to conventional epoxy resins and improving the mold strength compared to the silicone resins while providing superior reliability. Rohm also offers AEC-Q102 qualified products that ensure worry-free use in automotive systems and industrial equipment demanding extreme reliability.

### Canon launches FPA-8000iW semiconductor lithography system

CANON INC. announced the launch in Japan of the FPA-8000iW, the first Canon semiconductor lithography system to support manufacturing using large panels that are common in back-end processing.

Integrating a proprietary projection optical system, the FPA-8000iW i-line stepper\* offers a wide exposure field and fine 1  $\mu$ m<sup>+</sup> pattern resolution.

The FPA-8000iW was designed to meet the needs of manufacturers aiming for high production efficiency through the use of  $515 \times 510$  mm organic panel substrates for Panel Level Packaging (PLP) applications.

PLP processes typically involve mounting and processing a large number of semiconductor chips on large panels in order to produce packages that can increase communication bandwidth while reducing the power consumption of highperformance computing systems, ideal for such products as CPUs and GPUs utilized by data centers.

Future PLP requirements include cost reduction and further shrinking of semiconductor packaging that protects delicate internal semiconductor circuity from outside environments and electrically connects to external components.

The FPA-8000iW supports PLP cost reduction and package scaling by

providing high productivity panel processing with a large exposure field and high resolution. In response to packaging processes that use panel substrates, Canon developed a new stepper platform capable of handling large 515 x 510 mm panel substrates.

Severe warpage is also common in large panel substrates and the new platform and panel-feeding system can overcome up to 10 mm of panel warpage. As a result, the FPA-8000iW can help customers realize high-productivity and efficiency for PLP production of large packages.

Canon's original projection optical system supports a wide 52 x 68 mm exposure field while achieving 1.0  $\mu$ m resolution—the finest resolution‡ among packaging exposure systems that support panel substrate processes. These advantages enable state-of-the-art PLP technology that supports thin substrates with high-integration, enabling flexibility in electronic system design.

#### Presto Engineering moves to new facility

PRESTO ENGINEERING, an ASIC design and outsourced operations provider to semiconductor and Internet of Things (IoT) device manufacturers, announced today the grand opening of its new Caen Hub in France. The facility will provide IC test, qualification, and test production services primarily for communications, automotive, IoT, and industrial applications.

"Despite the recent world-wide

economic challenges, at Presto, we are experiencing a high demand for new product industrialization and ramp production in Europe," said Michel Villemain, CEO, Presto Engineering.

"This move to a modernized facility in Caen will enable us to support the growing customer demand."

The 1,850m2 factory in the Caen area runs 24/7. It features a 400m2class ISO7

cleanroom and all of the necessary equipment to support the stringent qualifications of the JEDEC (Joint Electron Device Engineering Council) and AEC (Automotive Electronics Council) standards. The two-story facility houses Presto's advanced capabilities for test, qualification, and failure analysis.

The new hub is located at 5 esplanade Anton Philips, 14460 Colombelles, France.

## Imec and GLOBALFOUNDRIES announce breakthrough in AI chip

IMEC, a research and innovation hub in nanoelectronics and digital technologies, and GLOBALFOUNDRIES, the specialty foundry, today announced a hardware demonstration of a new artificial intelligence chip. Based on imec's Analog in Memory Computing (AiMC) architecture utilizing GF's 22FDX solution, the new chip is optimized to perform deep neural network calculations on in-memory computing hardware in the analog domain.

Achieving record-high energy efficiency up to 2,900 TOPS/W, the accelerator is a key enabler for inference-on-the-edge for low-power devices. The privacy, security and latency benefits of this new technology will have an impact on Al applications in a wide range of edge devices, from smart speakers to selfdriving vehicles

Since the early days of the digital computer age, the processor has been separated from the memory. Operations performed using a large amount of data require a similarly large number of data elements to be retrieved from the memory storage. This limitation, known as the von Neumann bottleneck, can overshadow the actual computing time, especially in neural networks – which depend on large vector matrix multiplications.

These computations are performed with the precision of a digital computer and require a significant amount of energy. However, neural networks can also achieve accurate results if the vectormatrix multiplications are performed with a lower precision on analog technology. To address this challenge, imec and its industrial partners in imec's industrial affiliation machine learning program, including GF, developed a new architecture which eliminates the von Neumann bottleneck by performing analog computation in SRAM cells.

The resulting Analog Inference Accelerator (AnIA), built on GF's 22FDX semiconductor platform, has exceptional energy efficiency. Characterization tests demonstrate power efficiency peaking at 2,900 tera operations per second per watt (TOPS/W). Pattern recognition in tiny sensors and low-power edge devices, which is typically powered by machine learning in data centers, can now be performed locally on this power-efficient

accelerator.

"The reference implementation not only shows that analog in-memory calculations are possible in practice, but also that they achieve an energy efficiency ten to hundred times better than digital accelerators. In imec's machine learning program, we tune existing and emerging memory devices to optimize them for analog in-memory computation. These promising results encourage us to further develop this technology, with the ambition to evolve towards 10,000 TOPS/W".

Looking ahead, GF will include AiMC as a feature able to be implemented on the 22FDX platform for a differentiated solution in the AI market space. GF's 22FDX employs 22nm FD-SOI technology to deliver outstanding performance at extremely low power, with the ability to operate at 0.5 Volt ultralow power and at 1 pico amp per micron for ultralow standby leakage.

#### Analog Devices announces collaboration with Maxim

ANALOG DEVICES and Maxim Integrated Products has announced that they have entered into a definitive agreement under which ADI will acquire Maxim in an all stock transaction that values the combined enterprise at over \$68 billion. The transaction, which was unanimously approved by the Boards of Directors of both companies, will strengthen ADI as an analog semiconductor leader with increased breadth and scale across multiple attractive end markets.

Under the terms of the agreement, Maxim stockholders will receive 0.630 of a share of ADI common stock for each share of Maxim common stock they hold at the closing of the transaction. Upon closing, current ADI stockholders will own approximately 69 percent of the combined company, while Maxim stockholders will own approximately 31 percent. The transaction is intended to qualify as a tax-free reorganization for U.S. federal income tax purposes.

"Today's exciting announcement with Maxim is the next step in ADI's vision to bridge the physical and digital worlds. ADI and Maxim share a passion for solving our customers' most complex problems, and with the increased breadth and depth of our combined technology and talent, we will be able to develop more complete, cutting-edge solutions," said Vincent Roche, President and CEO of ADI. "Maxim is a respected signal processing and power management franchise with a proven technology portfolio and impressive history of empowering design innovation. Together, we are well-positioned to deliver the next wave of semiconductor growth, while engineering a healthier, safer and more sustainable future for all."

"For over three decades, we have based Maxim on one simple premise – to continually innovate and develop high-performance semiconductor products that empower our customers to invent. I am excited for this next chapter as we continue to push the boundaries of what's possible, together with ADI.

Both companies have strong engineering and technology know-how and innovative cultures. Working together, we will create a stronger leader, delivering outstanding benefits to our customers, employees and shareholders," said Tunç Doluca, President and CEO of Maxim Integrated.

## Traditional PC shipments continue to grow amid global slowdown

THE SECOND quarter of 2020 (2Q20) ended well for the Traditional PC market, comprised of desktops, notebooks, and workstations, with global shipments growing 11.2% year over year reaching a total of 72.3 million units, according to preliminary results from the International Data Corporation (IDC) Worldwide Quarterly Personal Computing Device Tracker. As restrictions around the world tightened in the first few weeks of the quarter, demand for notebooks continued to grow to maintain continuity of business and schooling for many communities.

Despite logistics issues early in the quarter, the cost and frequency of both air and sea freight inched closer to normal (i.e. pre-COVID levels). This, combined with PC production ramping up (and in some cases surpassing previous levels), meant that retailers and other distributors around the world had ample supply and were ready to fulfill the surge in demand.

"The strong demand driven by workfrom-home as well as e-learning needs has surpassed previous expectations and has once again put the PC at the center of consumers' tech portfolio," said Jitesh Ubraniresearch manager for IDC's Mobile Device Trackers. "What remains to be seen is if this demand and high level of usage continues during a recession and into the post-COVID world since budgets are shrinking while schools and workplaces reopen."

## CyberOptics will launch a WX3000 system for 12" and 8" wafers

CYBEROPTICS, a developer and manufacturer of high-precision 3D sensing technology solutions, will unveil the new Multi-Reflection Suppression (MRS)-enabled 3D and 2D WX3000 Metrology and Inspection systems for wafer-level and advanced packaging applications at the virtual SEMICON West show, July 20-23rd.

Incorporating the NanoResolution MRS sensor, the WX3000 Metrology and Inspection systems enable the ultimate combination of high speed, high resolution and high accuracy for wafer-level and advanced packaging, to improve yields and productivity.

Performing two to three times faster than alternate technologies at data processing speeds in excess of 75 million 3D data points per second, the NanoResolution MRS sensor-enabled WX3000 systems deliver throughput greater than 25 wafers per hour. 100% 3D and 2D metrology and inspection can be completed simultaneously at high speed, as compared to an alternate, slow method that requires two separate scans for 3D and 2D and only a sampling of a few die. The proprietary NanoResolution MRS sensor, deemed best in class, meticulously identifies and rejects multiple reflections caused by shiny and mirror-like surfaces. Effective suppression of multiple reflections is critical for highly accurate measurements.

"With the growing complexity and variety of advanced packaging, the need for highly accurate, 100% 3D and 2D metrology and inspection continues to increase," said Dr. Subodh Kulkarni, President and CEO, CyberOptics,

WX3000 systems are designed specifically for various wafer-level and advanced packaging applications including wafer bumps, solder balls and bumps, gold bumps and copper pillars.

The systems provide superior measurement and inspection performance for features down to 25-micron, including bump height, coplanarity, diameter and shape, relative location and a variety of other measurements.

#### Entegris acquires GMTI

ENTEGRIS has announced it has acquired Global Measurement Technologies Inc. (GMTI), an analytical instrument provider for critical processes in semiconductor production, and its manufacturing partner Clean Room Plastics, Inc. Located in Chandler, Arizona, GMTI is now part of the Advanced Materials Handling (AMH) Division of Entegris.

GMTI is a market leader in the design and production of high precision analytical instrumen ts for Chemical Mechanical Planarization (CMP) slurries and formulated cleaning chemistries used in the semiconductor manufacturing process. GMTI's technology is designed to ensure precise consistency of complex blended chemistries to enable high yields in the CMP and formulated cleaning processes.

"The acquisition of GMTI enhances Entegris' position as the premier supplier for yield enhancement solutions for the semiconductor market. Greater materials intensity and greater materials purity will be the primary defining factors of the next generation of semiconductor performance." said Bertrand Loy, President and CEO of Entegris. With the combination of GMTI's cuttingedge measurement systems and our extensive portfolio of filtration and other contamination control solutions, we bring a complete suite of solutions that allow our customers to achieve process stability and high yields in the complex CMP environment. We are very excited about joining Entegris. The combined portfolio, global infrastructure and operational resources will allow us to deliver significant value to our customers.," said Bryan LaFlam, President of **Global Measurement Technologies** Inc.

Entegris acquired Global Measurement Technologies Inc. for an aggregate amount of approximately \$36 million in cash, subject to customary post-closing adjustments.

## High productivity dopant source materials enable ion implant evolution

Ion implantation has become a key enabling process in semiconductor fabrication. However, some of the newest implant species present challenges that can slow production. Linde Electronics has pioneered new technology to accelerate species implantation and help ensure high quality.

#### BY DR. ASHWINI SINHA, ASSOCIATE DIRECTOR R&D, LINDE ELECTRONICS

THE INTRODUCTION of ion implantation for IC device fabrication can arguably be regarded as a pivotal development which enabled economic viability and eventually ubiquitousness of electronics in our lives. Its ability to place desired atoms in a substrate with a very precise location, dose and depth control enabled high manufacturing yield and product reliability that were critical to achieving the desired economy of scale and unit cost reductions. Today, the ion implant process is used to implant over 15 different atomic species for a variety of applications.

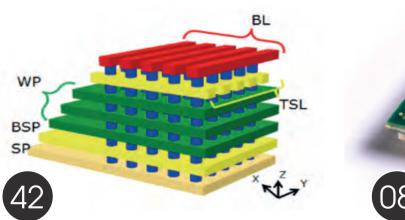

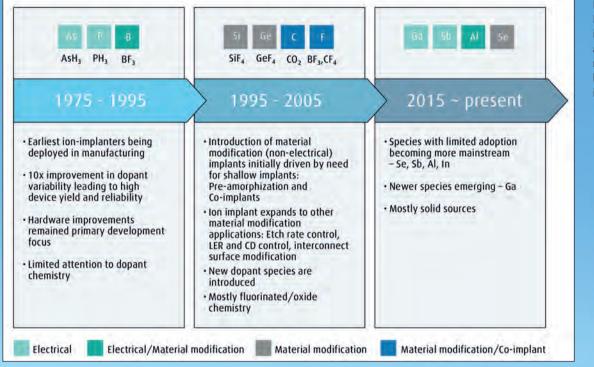

Figure 1 illustrates the evolution of implant species as they entered high volume manufacturing.

Boron, phosphorus and arsenic have been long standing choices for *p* and *n* type dopant species primarily used to modify electrical properties of

the doped substrate. Continuous shrinkage of device sizes and evolution of more complex device architecture brought the need for thinner films with shallow implant depths, higher dosing, and non-electrical material modifications. This led to the introduction of several new implant species in the product mix. Most notable among the second generation of species included germanium, carbon, silicon, and fluorine. However, these new implant species and tighter process windows in turn revealed challenges with tool operation that impacted final device performance and process line productivity.

Recently, a third generation of implant species are either becoming mainstream or are candidates for next-generation process flows. Selenium is being explored to reduce contact resistance while aluminum and antimony are finding more use with the growth

Linde

Making our wo

more productiv

10 WWW.SILICONSEMICONDUCTOR.NET | ISSUE III 2020 | COPYRIGHT SILICON SEMICONDUCTOR

in the power devices segment. Gallium is emerging as a potential *p*-type dopant for shallower junctions. a tool productivity killer Fluorinated gases are preferred for implant dopant

Call 1-800-772-9247

Industrial, Medical and Specialty Gases

www.linde.com

Service States &

Coincidentally, the traditional sources for all these new entrants are solids, which presents a new set of issues in material handling and ion-beam optimization. In this article, we describe the productivity challenges associated with conventional sources for these new generation dopant species. Both chemistry and physics inside the tool must be addressed to resolve these challenges and deliver commercially viable implant processes. We Illustrate this approach through two case studies describing high productivity performance enabled via new dopant source materials.

「「「「「「「「」」」である。

d

#### Fluorinated species and solid sources -

sources due to their favorable ionization behaviors and volatilities. Hence it was natural to adopt a fluorinated version of the dopant element to serve as the dopant source. However, the fluorinated products generated in the arc chamber plasma strongly react with the components of an arc chamber that is primarily made of tungsten or molybdenum. The interplay of fluorinated chemistry with the arc chamber leads to whisker-like growth of tungsten on arc

Figure 1. Evolution of implant species and source materials for beamline ion implant.

COPYRIGHT SILICON SEMICONDUCTOR | ISSUE III 2020 | WWW.SILICONSEMICONDUCTOR.NET 11

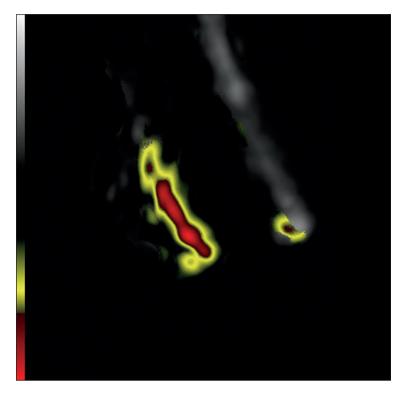

Figure 2. Examples of adverse effects of halogen cycle on the arc chamber components of the ion implant tool

chamber components such as the cathode, repeller and aperture [Figure 2], and on other components of the ion source such as the extraction electrodes and isolation components. This phenomenon is also known as Halogen-Cycle. Oxide species present very similar sets of issues due to the formation of tungsten oxide in the arc chamber. Eventually this leads to the failure of the ion source; tool operation is halted, and the ion-source has to be rebuilt before resuming operation. This phenomenon is the cause of the most common failure modes experienced during operation of implant tools, which we list below.

- 1. **Beam glitches:** Deposition on cathode, repeller and electrodes

- Defects: Undesirable W growth in ion-source / beamline, compounded by beam glitches

- 3. Beam non-uniformity: Deposition on aperture

- 4. Electrical shorts: Deposition in isolation bushing

Previously, applications were equally weighted towards fluorides ( $BF_3$ ) and hydrides ( $AsH_3$  and  $PH_3$ ) as the dopant source materials. Implant engineers were able to alternate between hydride and fluorinated species, and the hydrides acted as cleaning agents to reverse the adverse effects of fluorinated species. However, now the application mix is heavily weighted towards fluoride and oxide processes, and this solution is no longer possible. The introduction of these second-generation implant source materials emerged as a tool productivity killer with a halogen cycle as the leading cause. The engineers were finding it difficult to deploy these new applications without addressing this serious issue.

Increasing demand for the new entrants like antimony, aluminum, selenium and gallium (etc.) in the product mix is adding a severe burden on tool productivity. Coincidently, currently available options for all these implant species are solids at ambient conditions. Reliably transporting dopant material to the arc chamber thus becomes a key factor affecting implant productivity.

A typical gas base source material is packaged in a cylinder and connected to the ionization chamber using a tubing manifold - a convention for process tools in IC fabrication. When the dopant gas is demanded to start the implant process, the gas-based dopant material can be readily transported to the arc chamber precisely controlled using a mass flow controller (MFC).

| Metric                    | Gas Sources            | Solid Sources                      | emical Additional hardware required<br>ion Added PM steps<br>5X – 15X longer beam transitions |  |

|---------------------------|------------------------|------------------------------------|-----------------------------------------------------------------------------------------------|--|

| Material delivery<br>mode | Standard<br>cylinders  | Thermal or chemical<br>evaporation |                                                                                               |  |

| Flow control              | MFC based -<br>Precise | Limited                            |                                                                                               |  |

| Tool flexibility          | High                   | Poor                               | Likely dedicated operation                                                                    |  |

Figure 3: Productivity challenges with solid sources

| Implant<br>species | Traditional impant<br>sources           | Optimized source<br>mixtures and molecules                     |  |

|--------------------|-----------------------------------------|----------------------------------------------------------------|--|

| Alte               | ernatives for fluoride and oxide s      | sources                                                        |  |

| B, BF <sub>2</sub> | BF <sub>3</sub>                         | BF <sub>3</sub> /B <sub>2</sub> H <sub>6</sub> /H <sub>2</sub> |  |

| Ge                 | GeF <sub>4</sub>                        | GeF <sub>4</sub> /Xe/H <sub>2</sub>                            |  |

| Si                 | SiF <sub>4</sub>                        | SiF <sub>4</sub> /Si <sub>2</sub> H <sub>6</sub>               |  |

| C.                 | CO <sub>2</sub>                         | CO, CO/Xe/H <sub>2</sub> , CO/CF <sub>4</sub>                  |  |

| A                  | ternatives for traditional solid sc     | ources                                                         |  |

| Sb                 | $Sb_2O_3$ (s), $SbF_3$ (s)              | SbF <sub>5</sub> (I)                                           |  |

| Se                 | SeO <sub>2</sub> (s), H <sub>2</sub> Se | $SeF_{6}(g)$                                                   |  |

Figure 4. New UpTime® products improving fab productivity

Unfortunately, solid sources need new hardware to enable delivery of the dopant material to the arc chamber. This includes a complex integration of hardware like thermal vaporizers or chemical volatilization of a solid target placed inside the arc chamber. Low productivity implications associated with such approaches are listed in figure 3.

Switching to an implant recipe using a gas dopant source involves a simple step of initiating its desired flow fed into the arc chamber. On the other hand, switching to a solid implant source must undergo several additional sequence steps. First, the material needs to be heated to the desired temperature and a stable vaporization rate must be achieved. Beam tuning needs an additional feedback sequence with the vaporizer because vaporization rates vary as a function of the mass of the solid source in the vaporizer.

These sequences can take between 40 to 80 minutes, which is usually achieved in less than 10 minutes for a typical gas source. The implant tool needs to switch between different implant recipes involving different dopants. Evidently, a long transition time between a solid dopant source and another dopant source is highly undesirable. Additionally, once vaporized, the vapors tend to redeposit as solid form in cold spots, which necessitates long preventive maintenance procedures at regular intervals. On average, a solidsource based implant process exhibits 20%-30% lower productivity compared to a gas-source based process. Low implant productivity associated with solid sources has been the primary reason for their low adoption. The tool productivity bottleneck must be addressed for these new species to be a viable process to enable economical process scale-up of these emerging devices.

#### Developing implant chemistry

During the first generation of tools and processes, ion implant development was driven primarily by physics: ionization, ion selection, and strength, energy, and shape of the ion beam. With the second generation of processes and source materials, the heavy load of fluorinated chemistry in the recipe mix became an issue, as demonstrated above by the problems with the halogen cycle. In this section, we describe our approach to develop optimized source materials which addresses both the physics and chemistry requirements of newer ion implant processes to enable high tool productivity and device performance.

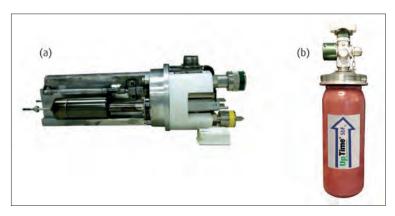

Figure 5. Advancing from (a) solid vaporizer to (b) preferred gas cylinders

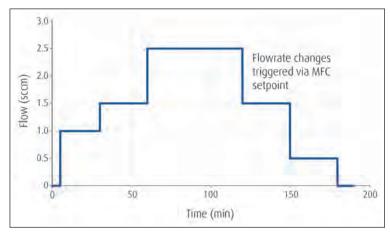

Figure 6: SbF<sub>5</sub> flow via MFC control

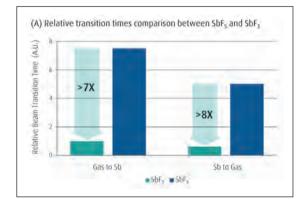

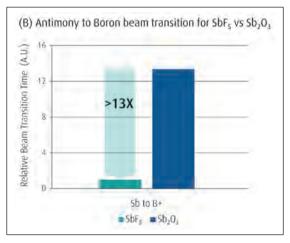

Figure 7: Faster beam transitions and startup time with  $\text{SbF}_{5}$ .

> We will also present our efforts to develop alternate gas-like dopant sources to offset the shortcoming displayed by conventional solid dopant sources.

It is important to note that because deposits continue to build up during the halogen cycle, it is not effective to implement a post-implant clean solution to remove the previously formed deposits. Not only does such a cleaning option result in unacceptable variability between cleaning cycles, but they also incur additional equipment downtime while post implant cleaning is being performed. The more effective approach is to implement in situ measures to abate the active fluorine ions/neutrals generated during initiation and disrupt the halogen cycle. This can be achieved by co-mixing a suitable chemistry with the fluorinated implant source materials.

While addressing the chemical problem, one must also retain the physics performance of the tool, as indicated by the key metric of beam current. Hence, the overall challenge is to solve and optimize both sets of variables: identifying a gas chemistry which extends tool uptime and reduces variability while maintaining high beam current. Appreciating the challenge, Linde designed and built an ion-implant test stand to develop novel gas chemistry solutions to enable high productivity for the implant process. With the deep understanding of both implant process physics and gas-phase chemistry, we invented novel dopant source solutions that not only mitigate the halogen cycle or oxygen attack but also increase the beam currents to further improve the implant tool throughput. The test system is designed to rapidly screen and optimize different gas chemistries, and thus significantly reduce the cycle time for implant process owners to deploy the best-in-class solutions. Figure 4 lists several new dopant sources currently offered by Linde that are driving implant tool productivity by delivering high marks on all the key metric listed in the section above. The two case studies presented below showcase the benefits implant process owners derive by implementing these novel solutions.

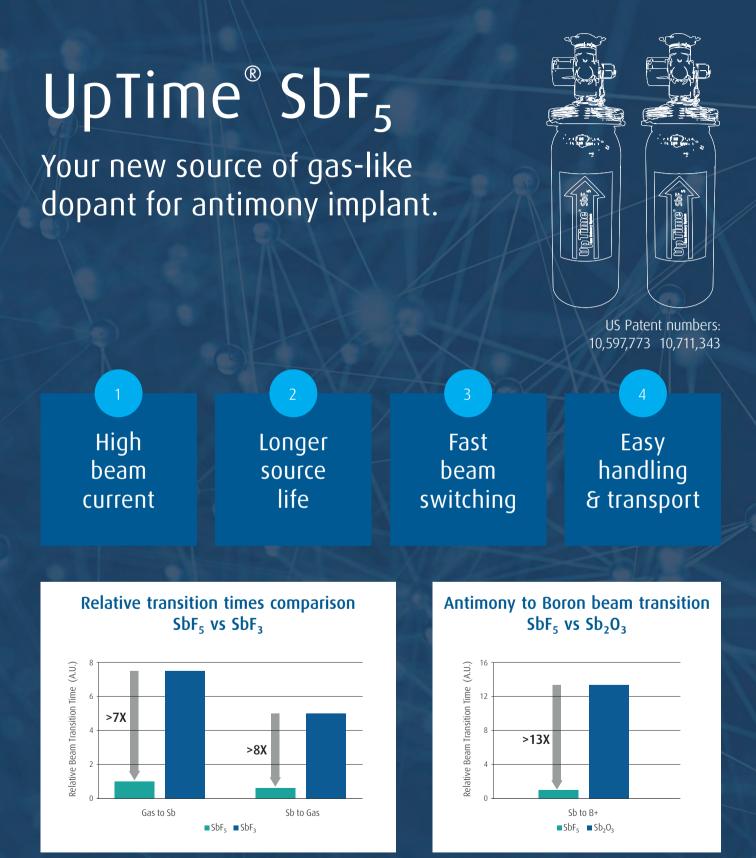

#### Case study 1 – Gas-like dopant source for antimony implant

Antimony (Sb) is another candidate for n-type doping besides arsenic and phosphorus. Antimony in fact has superior transports characteristics due to low diffusion coefficient and is a choice dopant candidate for Si based power devices. However, its adoption has been limited due to unavailability of a gas-based source. Traditionally, only solid sources like SbF<sub>3</sub>, Sb<sub>2</sub>O<sub>3</sub> or metallic Sb have been used as a dopant source. Solid sources are usually delivered via a vaporizer assembly where solid dopant sources are placed in a crucible very close to the arc chamber. The crucible is heated to an elevated temperature ( $250^{\circ}C - 1,000^{\circ}C$ ) to volatilize the solids kept in the crucible and then transported via a carrier gas flowing over the hot crucible.

This delivery approach suffers from several limitations which are nearly absent for a gas-based source.

- Long recipe / beam transition times: Long heat-up/ cool down of vaporizers for every transition. Typical transition times are in the range of 60-80 mins

- Limited crucible lifetime: ~60-100 hrs

- Limited flow control: Poor dose control

- Redeposition of solids on colder surfaces: Defects and frequent preventive maintenance requirements

Beam transitions from Sb to B is particularly so difficult that it can take up to 60 mins just to stabilize to a desired beam specification. This phenomenon is often referred to as "Antimony-Sickness." Currently implant engineers' only option to avoid these long beam transitions is to dedicate the implant tool solely

for antimony implant – a significant reduction of manufacturing flexibility and tool productivity.

Taken together, these limitations have prevented a wider adoption of Sb doping processes despite superior device properties like a shallower implant profile and reduced auto-migration in comparison to As. Linde recently introduced a gas-based source for Sb in the form of antimony pentafluoride (SbF<sub>5</sub>) packaged in a Linde proprietary cylinder [Figure 5]. This new Sb-source not only replaces the very cumbersome vaporizer operation but also offers several favorable properties:

- 7-10 torr vapor pressure at ambient conditions: can be easily dispensed as a gas via standard ionimplant gas stick

- Flow control via mass-flow controllers: instant flow change response

- Favorable ionization behavior: high Sb<sup>+</sup> and Sb<sup>++</sup> generation

- Compatibility: operates with standard gas manifold components

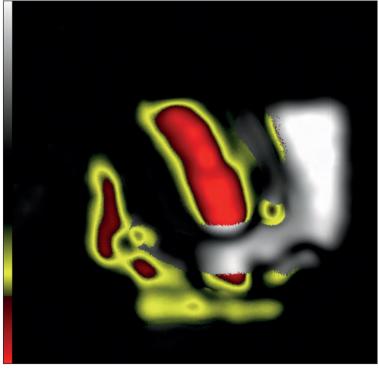

Figure 6 shows delivery of SbF<sub>5</sub> at different flows controlled via MFC. SbF<sub>5</sub> is delivered via a standard cylinder stored under ambient condition. A desired flow of Sb containing SbF, can be established instantly when the implant engineer needs to start a Sb beam. Similarly, the flow of Sb can be instantly shut-off by isolating the MFC and setting the target value to zero when the recipe needs to transition from Sb to any other species. The ability to deliver Sb dopant species to the arc chamber instantly in a reliable and controlled manner offers the engineers a powerful lever for improving the implant tool productivity. Implant users can use SbF<sub>2</sub> just like any other gas source and eliminate the productivity loss associated with incumbent solid source-based Sb implant process.

Figure 7 illustrates the relative improvement in beam transition time achieved using  $SbF_5$  as the dopant source for Sb implant.

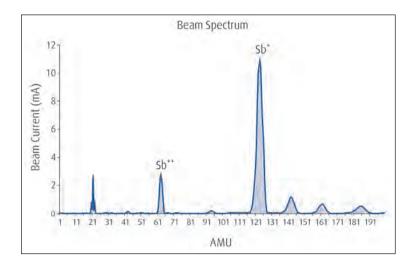

As noted before, retaining the physics performance of the beam current is equally important to the chemistry improvements. Figure 8 displays the excellent ionization behavior of SbF<sub>5</sub> resulting in high Sb<sup>+</sup> and Sb<sup>++</sup> ion intensity. Finally, SbF<sub>5</sub> has also been demonstrated to deliver long source lifetime of over 300 hours across different implant tool platforms. H<sub>2</sub>, or a mixture of H<sub>2</sub> with rare gases like Ar, Kr or Xe, dispensed along with the SbF<sub>5</sub> vapor, serves as a robust mitigant for the halogen cycle and enable the desired source lifetime [Figure 9]. Full product qualification is currently underway at several device manufacturers.

#### Case Study 2 – Novel dopant source mixture for high dose low energy boron implant

Boron is the most widely implanted specie in an IC device and is usually doped in the form of  $B^+$  and  $BF_2^+$  ions. However, the dosing and implant energy

required varies widely among the application device types and specific process applications.

Figure 8. SbF<sub>5</sub> ionization performance

Continuously shrinking device dimensions and the advent of FinFET architectures pushed certain boron recipes into the very high dose (E15 – E16 atom/cm<sup>2</sup> and low energy (sub 1 keV) implant regime. These high-dose, low-energy implants are much more challenging than other boron recipes. First, the implant tools are usually beam current limited at these low energies, significantly reducing the

Figure 9. Clean operation: 300<sup>+</sup> hours dedicated operation.

BF.

B2H5 Trimix

wafer throughput. While the average throughput for other recipes are in the range of 50 -100 wph, the throughput for these recipes can be limited to 15-30 wph. Secondly, these low energy implant layers are usually very sensitive to beam glitches and defects. It is not uncommon that the ion-source failure may happen due to the inability of the implant tool to achieve beam spec requirements for one of these high-dose, low-energy recipes. There was a clear need to develop solutions to improve beam current (equipment throughput) and ion-source lifetimes for tools running these recipes.

Linde has developed a patented mixture of  $B_2H_6$ ,  $H_2$  and  $BF_3$  (Boron Trimix) which is being widely adopted by IDMs to improve the productivity of their boron implant. Linde also utilized the advantage of its UpTime<sup>®</sup> based sub-atmospheric delivery system to package the mixture in a single container and avoid the need for a separate gas manifold to deliver this mixture to the ion-source chamber. Detailed mechanism behind improved performance with this novel gas mixture is described in US Patent 9,570,271.

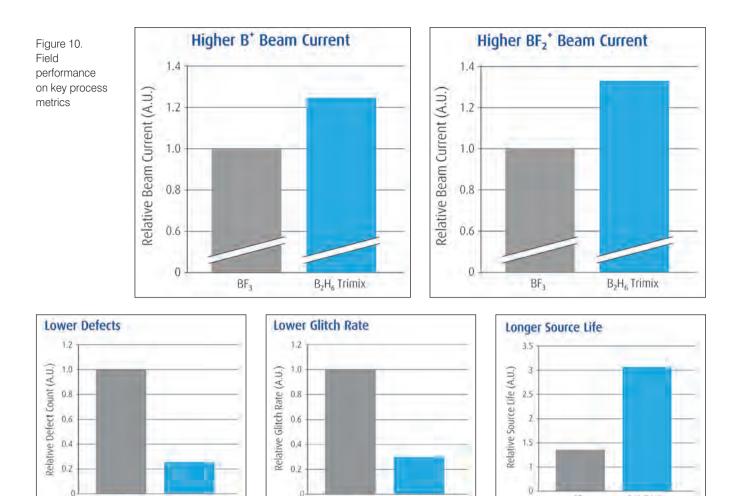

Figure 10 shows the summary of benefits that customers have been able to realize by use of Boron Trimix in their fabs. These benefits continue to enable implant engineers to meet stringent process requirements for these evolving high-dose, low-energy boron implants and to deliver on fab productivity targets.

BF,

B<sub>2</sub>H<sub>4</sub> Trimix

#### Conclusion

B<sub>2</sub>H<sub>6</sub> Trimix

BF3

As technology roadmaps evolve and more varied and complex thin films are required, ion implantation will undoubtedly be employed extensively to introduce new dopant species to meet developing device requirements. To support these new applications, innovation creating new material sources will also be required. As illustrated in the above case studies, both physics and chemistry of the dopant sources must be co-optimized to achieve a viable commercial offering and process scale-up.

Linde has pioneered development of novel dopant sources that has enabled implant process users to increase their equipment throughput, reduce equipment failures and improve process yields. By using Linde's proprietary screening test stand and protocols, we have rapidly prototyped new materials to support our customers' process screening, validation, and optimization. These novel dopant materials, in combination with UpTime innovative packaging, offer the best suite of products and lowest cost-of-ownership solutions for ion-implant processes.

## Plasma Dicing

Plasma Dicing addresses the challenges of dicing smaller and thinner dies

- > Particle-Free

- > Damage-Free

- > Higher Chip Strength

- > Increased Yield / Active Area

Consider Plasma Dicing to achieve higher throughput, increased yield and lower costs per wafer.

Industry.panasonic.eu

#### ACM Research

### ACM Research is passionate about cleaning wafers

The critical importance of wafer cleaning grows with each new semiconductor node. As geometries shrink, even minute contaminants have outsized impacts. Particles that didn't effect performance at the 28nm node can become 'killers' at 10nm and below. ACM Research elevates wafer cleaning to new heights by not only reducing contaminants but also slashing waste, setting sights on building 'win-win' customer relationships in a highly competitive corner of the global IC process tool industry.

#### **BY: MARK ANDREWS, TECHNICAL EDITOR**

David Wang, CEO. ACM Research

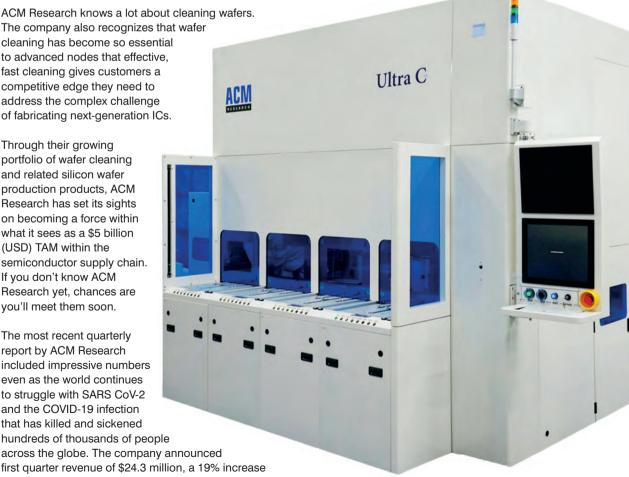

ACM Research knows a lot about cleaning wafers. The company also recognizes that wafer cleaning has become so essential to advanced nodes that effective, fast cleaning gives customers a competitive edge they need to address the complex challenge of fabricating next-generation ICs.

Through their growing portfolio of wafer cleaning and related silicon wafer production products, ACM Research has set its sights on becoming a force within what it sees as a \$5 billion (USD) TAM within the semiconductor supply chain. If you don't know ACM Research yet, chances are you'll meet them soon.

The most recent quarterly report by ACM Research included impressive numbers even as the world continues to struggle with SARS CoV-2 and the COVID-19 infection that has killed and sickened hundreds of thousands of people across the globe. The company announced

Right: ACM Research Ultra C Wet Bench

year-on-year, with \$12 million coming from equipment deliveries. While the \$12 million in new installations was \$2 million off its 2019 record, the fact that ACM moved forward while the COVID-19 pandemic began its rampage is telling about the company's continuing ability to excite new customers under the most challenging of circumstances.

ACM Research isn't exactly an 'overnight' success story – The company got its start in Fremont, California in 1998, where it is headquartered. ACM Research added a facility in Shanghai in 2006. By 2009, ACM was supporting memory giant SK Hynix after successfully demonstrating the effectiveness and yield improvements possible with its space alternated phase shift (SAPS) system and megasonic cleaning capabilities for both flat and patterned wafers.

The company's bubble oscillation system dubbed 'TEBO' followed, proving successful in effectively cleaning patterned wafers at advanced process nodes. Orders from SK Hynix continued to grow, and in 2015 the company achieved success with cleaning 3D structures; its customer base continued to grow in Korea, Taiwan and China. Following these successes, the company went public on the NASDAQ exchange in 2017, and added a second R&D and factory facility in Shanghai in 2018. Work continued on a new system that would be dubbed Ultra C Tahoe; ACM targeted deliveries to lead customers beginning in 2019.

As device geometries continue to shrink, heading towards 5nm and below, the complexity and sheer volume of process steps is also accelerating. Wafer cleaning, either using a dry process

or one of several wet processes, is generally believed to

generally believed to be repeated as many as 200 times for highly advanced structures.

Because IC and microcircuit recipes vary so widely across industry, there's no precise way to calculate exactly how many more cleaning steps are added at each new node, but one fact was immediately

clear to fab operators: what worked at 28nm wasn't going to cut-it at 10nm and below. Older cleaning methodologies such as wet bench systems in which wafers are essentially immersed in a bath of reused solvent and acid chemistries with water rinses were not up to the task of removing enough contaminants to ensure that today's 7-5nm devices could deliver acceptable lifetimes at profitable yields. As new cleaning technologies were being developed across the supply chain to meet the needs of advanced node devices, ACM Research was developing a unique approach in its Ultra C Tahoe system. From the viewpoint of company CEO, David Wang, some of the more advanced cleaning systems on the market were getting the job done, but at the expense of a sizeable uptick in the amount of sulfuric acid ( $H_2SO_4$ ) they consumed, creating waste treatment and disposal problems along the way. The company believed that some cleaning systems were wedded to technologies that either used too many 'consumables' or did a relatively poor job of removing defect-causing contaminants, or both.

"In a typical wet bench system, a batch of wafers is dunked in the bath statically, so that it cannot achieve the cleaning efficiency of a single wafer process, where the wafer is spinning with a very thin boundary chemical diffusion layer being applied to the wafer surface," Wang remarked.

"What's more, a standalone bench process cannot eliminate the problem of cleaning inefficiency from non-uniformity across the wafer. The wafer edge cleaning efficiency cannot be as good as the wafer center, due to the geometrical limitation of the tank, the wafer guides, etc. The wafer-to-wafer, batch-tobatch cleaning performance also cannot be controlled well. However, in a single wafer process, the cleaning method is more advanced because it spins each wafer while process chemicals are dispensed onto the wafer. Additionally, supplementary cleaning methods can be added to a single wafer process, such as N<sub>2</sub> spray DIW and megasonic cleaning," he said.

In December 2019 ACM Research formally announced the release of its Ultra C Tahoe cleaning system. It is designed to dramatically reduce the consumption of sulfuric acid and other industrial chemicals in HVM. The company said its new Ultra C Tahoe system is the world's first tool combining bench and single wafer cleaning through an integrated approach. The new tool supports photoresist stripping and postetch, post-implant and post-CMP cleans. The system delivers improved process performance, chemical cost savings and significantly reduced sulfuric acid waste generation that is accomplished by slashing acid consumption to approximately one-tenth that of legacy cleaning systems. Recent tests have confirmed that on average, using the Ultra C Tahoe can reduce sulfuric acid waste by 80 percent.

Wang said that his company has worked towards developing a complete system like the Ultra C Tahoe to offer customers a cost reduction strategy that addressed chemical waste issues as well as performance objectives. Waste disposal without harming the environment was a significant driving factor. The company noted that (global) government restrictions on semiconductor industry waste and awareness of environmental risks are driving increased demand for cleaning systems that can

#### ACM Research

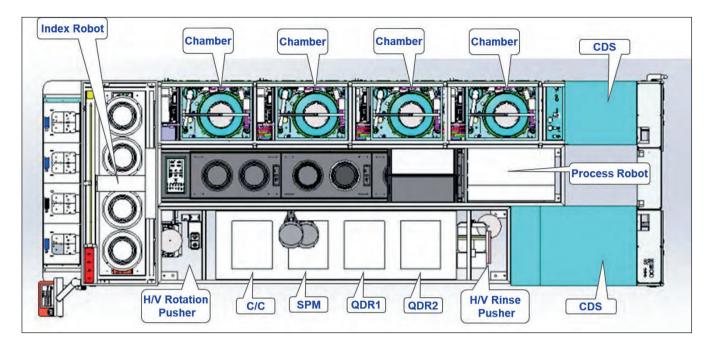

ACM Research Ultra C Tahoe (inside view from top)

reduce consumption of process chemicals without sacrificing performance. While handling, storing and dispensing hazardous acids present their own challenges, disposal methods for sulfuric acid are suboptimal.

Even though landfilling decontaminated waste remains an option in countries like the United States, it does not completely remove the risk of environmental contamination. In areas such as Korea, Taiwan and Shanghai that have limited or no landfill space available, the next waste disposal option is hightemperature purification, but this approach consumes a large amount of energy and contributes to additional greenhouse gas emissions.

The Ultra C Tahoe cleaning system combines two modules into a single wet-clean system. Sulfuric acidperoxide mixture (SPM) cleaning and quick dump rinsing (QDR) occur in the bench module, where the SPM process chemicals are recirculated as in a stand-alone bench system, which decreases sulfuric acid waste by at least 80% compared with single wafer SPM cleaning. After bench cleaning in the Tahoe, wafers are transferred to the single wafer module for advanced cleaning while still wet.

"Sulfuric acid waste treatment is a major challenge in advanced IC manufacturing. For example, semiconductor plants account for more than half of the total sulfuric acid used in Taiwan," said Wang. He noted that bench cleaning alone cannot achieve the required performance for 28nm nodes and below. Even as the industry has shifted to single wafer cleaning at advanced nodes to achieve improved performance, the shift dramatically increased sulfuric acid consumption and resulting waste disposal concerns. "We developed the proprietary Tahoe system to deliver the high cleaning performance and process flexibility that customers expect from single wafer cleaning, but with a fraction of the chemical consumption. We consider this a winning combination that will enable the industry to maintain its technology roadmap with an environmentally friendly solution that saves significant money on disposal costs," Wang explained.

The Ultra C Tahoe's single wafer chamber is flexible and can be configured for customer-specific needs such as dispensing standard clean (SC1), hydrofluoric acid (HF), ozonated deionized water (DI-O3), or other process chemicals. It can accommodate up to four arms with up to three process chemicals on each. Options include an  $N_2$  spray arm or megasonic cleaning with ACM Research's Smart Megasonix arm. The system also offers an isopropyl alcohol (IPA) drying function for patterned wafers.

The Ultra C Tahoe cleaning system has demonstrated low cross-contamination risk and excellent particleremoval performance rivaling state-of-the-art single wafer systems, all at a much lower consumption rate of SPM. When compared with a traditional SPM bench tool, data from an ACM Research customer's commercial production line demonstrated that the integrated Tahoe system can reduce particle counts from hundreds to around 10 per wafer at 30nm. A Tahoe system processing 2,000 wafers per day will consume less than 200 liters of sulfuric acid, eliminating more than 1,600 liters of sulfuric acid waste per day compared with single wafer hightemperature SPM cleaning systems.

Cross-contamination is another real issue for wafer cleaning as device geometries continue to shrink, Wang noted. In stand-alone bench systems, batches of wafers are processed in one tank, so particles, impurities or contaminants that are removed from

#### ACM Research

wafer surfaces stay in the tank and can redeposit on the wafers again. However, in a single wafer process system, the particles, impurities or contaminants that are removed from wafer surfaces are spun off by centrifugal force. Meanwhile, different process chemicals are dispensed onto the wafer surface and then spun off as well. In this way, the crosscontamination risk can be made minimal. "Because the Ultra C Tahoe combines bench and single wafer cleaning in an integrated, or hybrid system, we provide the best attributes of both," Wang remarked.

When ACM announced availability of Ultra C Tahoe, the system was already being evaluated by a lead customer. During first quarter 2020, that customer completed its evaluation, issuing 'first tool acceptance,' which bolstered quarterly revenue. Performance met or exceeded expectations; Wang announced during the company's earnings call that a second Ultra C Tahoe system had been ordered by their first Tahoe customer, and that a new North American sales vice president had been added; the company's staffing also increased in other major semiconductor markets.

In early May, the company announced that it was expanding its line of 'Ultra C' cleaning systems, with new tools targeting different and complementary portions of the wafer cleaning market. The three new Ultra C tools target advanced IC, power device, and advanced WLP markets for front and backside cleaning requirements.

ACM described its Ultra C b (backside) tool as a cost-effective cleaning system that provides good particle performance and etch uniformity control for three key applications: backside metal removal or RCA clean; backside silicon etching for wet wafer thinning, or wet through-silicon via (TSV) revealadditionally, it supports backside film removal on poly silicon, oxide and nitride layers for wafer recycling. With features that help mitigate high warpage, the system is especially well suited for processing 200mm or 300mm ultra-thin wafers and bonding wafers. The company said its new Ultra C wb (auto bench) tool performs batch cleaning of up to 50 wafers, utilizing the same advanced wet bench technology developed for ACM's Ultra C Tahoe tool. Key applications for the auto bench include pre-furnace clean, RCA clean, photoresist strip, oxide etch, silicon nitride removal, and removal of FEOL poly/oxide or BEOL metal for wafer recycling.

The tool is configured with different tanks of chemicals, such as sulfuric acid, phosphoric acid, hydrofluoric acid (HF), buffer oxide etchant (BOE), SC1 and SC2 for a specific application step. Wafers are successively dipped in the baths, rinsed with deionized (DI) water, and dried with an ATOMO dryer using vaporized isopropyl alcohol (IPA), leaving no watermark. ACM described its new Ultra C s (scrubber) as leveraging the company's proven scrubber capabilities for WLP and extends them to foundry IC processing. Its soft brush uses precise pressure control to remove particles following wafer frontside, bevel and backside cleans. The tool features an advanced dual-fluid (gas and liquid phase) spray cleaning technique; it can also be equipped with ACM's patented space alternated phase shift (SAPS) megasonic technology

for customers requiring further,

more intense cleaning to remove smaller particles. The modular system can be configured with eight chambers for 300mm IC applications – four each for frontside and backside cleaning. The scrubber is highly cost effective due to its flexibility, small footprint and high throughput.

When announcing its new cleaning systems, the company also stated that it was adding its Ultra Furnace to the product lineup. According to Wang, this tool is a 'broad platform' for ACM's entry into dry processing applications. "This opens another large market for ACM beyond wet processing. In our view, innovation in vertical furnace technology is required for the industry to progress to more advanced manufacturing nodes. That is why ACM entered the market. We have been hard at work on the furnace for more than two years. It is a joint development project of our world-class technology teams in China and Korea."

"The two teams developed a new hardware platform that combines our proven stable software and proprietary control system. The Ultra Furnace delivers reliable control of pressure, gas flow-rate and temperature; it is optimized to deliver high performance batch processing of up to 100, 12-inch wafers. It initially supports low-pressure chemical vapor deposition processes, or LPCVD. With additional development work, the furnace tool can be expanded to address oxidation, annealing processes, and future atomic layer deposition processes. We delivered our first Ultra Furnace demo tool to a key customer in the first quarter, and expect qualification by the end of this year," Wang noted.

Thanks to ongoing growth, the company broke ground 7 July on a new facility in the Lingang Special Area of the China (Shanghai) Pilot Free Trade Zone, about 30 miles from the company's China subsidiary headquarters. The new facility will consist of a 100,000 square meter factory with R&D facilities. The company has already begun construction, targeting a ramp to initial production in the second half of 2022.

ACM Research Ultra C Scrubber

### Implementing smart manufacturing in the sub-fab through operational excellence

Silicon Semiconductor recently explored methods for implementing smart manufacturing and Industry 4.0 concepts in the sub-fab through a webinar presented by Edwards Vacuum. Given the timeliness of the subject during the COVID-19 pandemic, Edwards was invited to capture essential webinar details in an article timed for SEMICON West 2020.

#### BY EDWARDS VACUUM

SILICON SEMICONDUCTOR recently hosted a webinar on the application of smart manufacturing and Industrie 4.0 concepts in the semiconductor manufacturing sub-fab. The webinar was presented by Edwards Vacuum; Silicon Semiconductor's technical editor, Mark Andrews, moderated a discussion among Edwards presenters: Alex Smith, vice president of field operations and safety; Alan Ifould, head of marketing and business transformation, and Neil Condon, head of digital solutions. The webinar followed a question and answer format with a central theme of exploring the ways smart manufacturing in the sub-fab enables smart manufacturing in the cleanroom. Edwards, a leading provider of vacuum and abatement systems for the semiconductor industry, describes their approach to implementing smart manufacturing in the sub, a program they call Operational Excellence. With over 100 years of rich heritage, Edwards has served the semiconductor industry since its birth and has installed over 100,000 vacuum pumps and 10,000 abatement systems. Following is a condensed version of the webinar content.

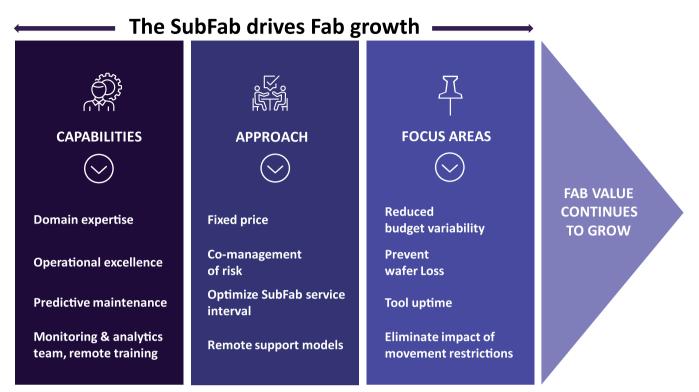

Figure 1: The SubFab can drive fab growth through domain expertise, operational excellence, and predictive maintenance combined with monitoring and analytics to yield many benefits including increased uptime and reduced overall costs.

#### Smart manufacturing/Industrie 4.0 MODERATOR: Is there more to smart manufacturing than simply collecting more data? What is Edwards approach?

**EDWARDS:** Smart manufacturing is about much more than simply collecting more data. It is about how the data is used. At Edwards we talk a lot about Operational Excellence – a term we use to describe our model for continuously improving our business operations. It is our way of effectively integrating people, machines, and processes to co-manage risk and deliver outcomes our customers care about. Data drives the process but is useless without domain expertise, the collective individual and institutional knowledge that transforms data into actionable insights. Domain expertise finds the solution.

Operational Excellence drives adoption – throughout our own and our customers' organizations. For example, we might collect more data about performance so that we can detect an underperforming system earlier and, with our customer, plan the right service intervention. That could be moving a pump exchange forward, to avoid unplanned-downtime on a critical tool; or refining a planned maintenance schedule to lengthen intervals and use fewer consumables and spare parts; or triggering an investigation to understand whether a different combination of product and service offerings would deliver better performance. We also use data about the performance of our service teams, and the procedures they use, to adjust procedures and drive training programs. We apply lean principles with a framework we call VTPS (vacuum technique production system) that tracks things like workplace organization, inventory management, adherence to well-designed work standards, and the idea of "Right from me", which underpins a culture of principle-driven leadership, safety and continuous improvement.

### MODERATOR: What market need does Edwards' technology, software & in-the-field service expertise address?

**EDWARDS:** A fab is an expensive tool, and down events are disruptive and costly. The impact of disruption is magnified when the supply chain is stressed, as it is now and is likely to remain for the foreseeable future. In spite of pandemic-induced stress on the supply chain and numerous other effects on operational efficiency and consumer demand, our customers have remained resilient. Recovery is underway for many, though variables within the crisis remain difficult to predict and heightened risk and uncertainty appear likely to persist.

In this context, anything we can do to reduce risks and uncertainty in the sub-fab that could affect the cleanroom is critically important. Any activity that reduces downtime, scheduled or unscheduled, can generate large savings. For instance, at one foundry customer we used our advanced data analytics to reduce the number of abatement PMs from 120 per year to 17 per year.

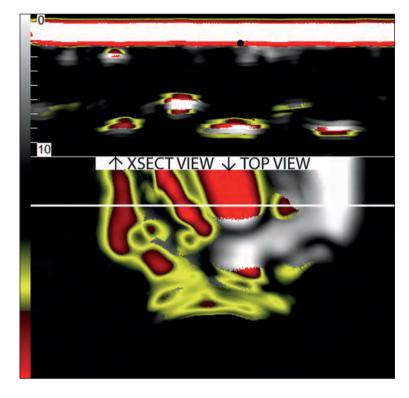

A vibration signal from a pump on an atomic layer deposition tool (left) and a photo of material deposited on internal components (right). Data analysis predicted the likelihood of a tool fault ahead of scheduled maintenance. After removal, a detailed analysis confirmed that the part was indeed about to fail; proactively replacing it prevented unscheduled process downtime and potential wafer scrap losses.

With each PM lasting 6-12 hours and consuming several thousand dollars' worth of spare parts, the cost of parts and lost production ran well over half a million dollars. This was just on one tool. There is much to gain by focussing on sub-fab equipment.

#### Sub-fab evolution

**MODERATOR:** How has the sub-fab evolved in recent years?

**EDWARDS:** As the number of processing steps required by leading edge processes grows, so does the need for vacuum and abatement. A fab that starts 40K wafers per month has thousands of process tools and supporting pumps and abatement systems. Processes have become harsher and more reliant on high quality vacuum. Environmental regulations continue to tighten, meaning the process cannot run without effective abatement.

Even fabs using legacy 200mm processes are changing. Many use a mix of refurbished 200mm tools and expensive hybrid solutions - 300mm tools adapted for 200mm wafers. The mix of old and new can introduce complexity into the sub-fab support infrastructure as well as the clean room. Against this backdrop, maintaining productivity through these strategic investments is essential to maximizing ROI and profitability. So overall, we see more costly consequences for safety excursions and unplanned vacuum and abatement down events across all sectors. The sub-fab is now regarded as a key opportunity for effectivity improvements. In response to these challenges, sub-fab equipment has evolved to be more sophisticated and tightly controlled while recruiting and retaining staff with the appropriate domain expertise has become more difficult. Within Edwards we recognized a clear need to develop a program to share and embed domain expertise, and ingrain cultural behaviours that assure safety, consistent performance, problem ownership, personal growth, and reward. This was the initial driver for developing our model for Operational Excellence, which focuses on creating teams, technologies and cultures that can continuously contribute to improved tool availability and reduced risks.

MODERATOR: What is the cost of failure when subfab systems suffer unplanned downtime? EDWARDS: It is hard to be specific about costs of failure as every fab has their own assessment and accounting methods. We base our models on assumptions that we test with customers in different sectors. Costs can vary widely. If a seal fails and toxic gases escape, the whole fab may be evacuated. An unplanned vacuum fault on a batch furnace can risk losing 125 wafers valued at several hundred thousand dollars. A faulty abatement system may cause a tool to be offline for several hours. Planning and anticipation are key. A vacuum pump fault can typically be rectified in around 4 hours, by swapping the pump. But if the tool is brought down in an uncontrolled manner, chamber components may be required, or even a complete requalification lasting up to 72 hours, plus all the costs of disrupting production.

#### Sub-fab systems approach

MODERATOR: Given the complexity of vacuum systems, how do major components interact, affecting uptime & fab performance?

**EDWARDS:** There are many examples of interdependencies among components of a vacuum process tool. Focus often falls on the pump itself where pressure can vary by several orders of magnitude and temperature can change by hundreds of degrees. But we also frequently see pumps that have stopped because a leak several meters upstream drove a chemical reaction in the pump.

Sometimes there seems to be a responsibility noman's land between the pump and the chamber,

which makes these issues hard to track down. To find the root-cause of a problem you need to examine the system as a whole, from the chamber through to the exit from the abatement system, and sometimes the supporting facilities as well. The key to progress here is collaboration. When all the stakeholders and domain experts work together, it is much easier to get to the root-cause, and implement a solution that delivers consistent performance and reliability.

In one case, a customer had a tool that was delivering only 10% of the productivity of peer tools. Our primary predictive analytics indicated the performance of the vacuum pump and supporting abatement systems degraded over an unusually short period of time, and at an increasing rate. This behaviour pointed to wider influences. Other signatures we saw in the data pointed to a fault upstream of the vacuum pump. When the customer provided critical contextual data from the wider fab, we identified a specific issue in the foreline that occurred around a maintenance activity owned by another team. This is a clear example of how a holistic approach to understanding the vacuum system is so important. The key here was being able to add context to what the data analytics showed. We get that context by drawing on our own domain expertise in how our equipment is known to behave. In the end we collaborated to create new maintenance procedures that assured a robust vacuum system and tool throughput returned to normal.

#### MODERATOR: Manufacturing ICs is complex; processes are tweaked, sometimes daily: How does Edwards determine what is useful for improving sub-fab performance?

**EDWARDS:** There are two sides to this. The first is the equipment itself. It needs to be configured and setup correctly. Edwards makes a lot of different product variants, and all of them can be tuned or configured through software. For example, our iXH dry pump for harsh CVD and ALD processes comes in 116 variants. The other consideration is the customer's process. Understanding how gases, vapours and by-products interact in the product is key to product selection and configuration. This is our domain expertise and it is the key ingredient that helps us measure and improve performance.

We do that by using Operational Excellence to continuously improve our best-known-methods (BKM) – documents and procedures that specify:

- the right combination of products for the process, *together*, as a system

- the best configuration of those products where do you put the knobs on those products?

- and the right service and maintenance regime, which is made "smart" by live data about performance.

These BKMs are a global view of what works, a view that we are uniquely qualified to provide by our broad experience with customers and processes across the Edwards makes a lot of different product variants, and all of them can be tuned or configured through software. For example, our iXH dry pump for harsh CVD and ALD processes comes in 116 variants

industry. They are getting more and more precise, and, as wafer processing becomes more complex, the relationship between process and BKM is becoming more and more critical.

#### Sub-fab optimization – Edwards role

MODERATOR: What differentiates Edwards' ability to help manufacturers optimize performance, reduce downtime, gain greater consistency, and reduce operational costs?

EDWARDS: When we examine the sub-fab space, we see many excellent companies offering some of the capabilities Edwards has. But we believe our framework for Operational Excellence and our broad domain expertise clearly stand out. We practice what we preach, finding confirmation for that belief in our own data. We have operations in locations around the world, each at a different stage in its journey toward Operational Excellence. When we compare performance metrics based on customer outcomes for each facility, we see a clear correlation between performance and the maturity of their journey. It is important to note that most of the improvement arises from effective use of all the disciplines in the Operational Excellence model, not just the use of data analytics. This is why we believe that, in the sub-fab, smart manufacturing must adopt a holistic approach to the effective interaction of people, machines and processes.

#### Safety

MODERATOR: Safety is a key metric for any fab operation. But how does continually collecting and analysing operational parameters improve safety while increasing uptime?

**EDWARDS:** We have all experienced the difference in being able to plan and make time for a task versus that feeling of being rushed to complete something against a deadline. Under pressure, methods may be improvised and risk-assessments rushed. Safety becomes reliant on the least reliable controls, i.e. personal protection equipment, procedures, and signs. These kinds of controls should be the last