# SILICONNECTING THE SILICON DUCTOR COMMUNITY

Bonding & dielectric materials deliver 5G, IoT device packaging solutions

VOLUME 43 ISSUE IV 2022

### INSIDE

News Review, Features News Analysis, Profiles Research Review and much more...

#### ELIMINATING EMI ENSURE ACCURATE TEST MEASURING

AN ANGEL BUSINESS COMMUNICATIONS PUBLICATION

Semiconductors shrink with each new generation, inspecting devices on-wafer or singulated die becomes more complex

#### EVOLVING SUBFAB VACUUM CHALLENGES

Semiconductor manufacturing no longer focused on Dennard scaling as a means to improve performance and reduce costs

SILICONSEMICONDUCTOR.NET

#### NEXT-GEN LOW-K FILMS ADDRESS FAB CHALLENGES

How tunable, low-k films deliver upgraded dielectric performance can have tremendous strategic leverage

www.EVGroup.com

# DIE-TO-WAFER (D2W) BONDING SOLUTIONS

Fusion and hybrid bonding for next-generation heterogeneous integration

Collective D2W bonding enabled by extensive knowledge in carrier preparation and die handling

Direct placement D2W activation and cleaning complete solution with EVG®320 D2W

Production-ready equipment solutions for successful integration of chiplets

Heterogeneous Integration Competence Center™ serving as leading-edge incubation center for customers and partners

VISIT US AT BOOTH #C1211

**GET IN TOUCH** to discuss your manufacturing needs **www.EVGroup.com**

EVG<sup>®</sup> 320 D2W

Õ

**VIEWPOINT** By Mark and rews Technical Editor

# Silicon sales continue growth through Q2, is a turnaround coming?

THE SEMI trade industry association announced in mid-September that Q2 equipment billings continued the breakneck pace that has set and broke records regularly since 2020. Silicon seems to have avoided the pandemic trauma that devastated humanity, but for how long?

As of this writing US President Joe Biden took a 'victory lap' after signing the so-called Chips Act into law that will channel more than \$50 billion into research and direct support for companies building fabs within US borders. The EU has its version. Can we expect equipment sales to continue booming for as long as the money flows? Time will tell.

With few signs of any serious headwinds other than global inflation running above 30-year highs and a population still pandemic weary, what could go wrong? Economists are already making cautionary statements and the US Federal Reserve will meet shortly; the Fed is expected to raise interest rates yet again to cool a steamy economy. How long can spend-spend outpace save-save-save?

Take a tip from someone who saw the Tech Bubble burst 22 years ago and who recalls when Apple stock sold for under \$10 a share: Nothing is forever.

In this issue of Silicon Semiconductor we look at some exciting new permanent bonding electronic materials advances from Brewer Science that in addition to delivering top performance without the extreme production demands of other solutions, is a photo imageable dielectric with unbeatable benefits for 5G and IoT applications, amongst many. Edwards Vacuum shares new insights into the rapidly evolving subfab equipment revolution, including the challenge vendors face when customers want improved performance, substantially increased capabilities and a form factor shrink up to 30 percent. Edwards believe collaboration is key to creating win-win solutions.

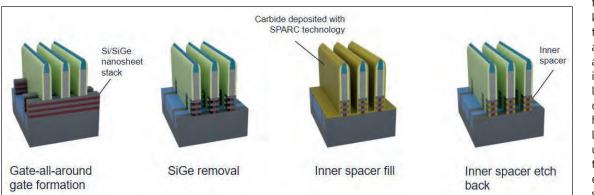

We also look to the experts at LAM Research who are unveiling their new SPARC technology that enables ever-shrinking transistors to fit into everdownsizing packages, all with substantially improved performance. And our friends at Onto Innovation detail how they have 'super-sized' their new JetStep X500 system that dramatically increases exposure fields up to 250x250mm, effectively slashing the number of exposures needed in FOPLP, along with a score of other money-saving benefits.

For your free weekly e-news roundup go to: WWW.SILICONSEMICONDUCTOR.NET

# CONTENTS

VOL 43 ISSUE IV 2022

# 16

## NEW BREWER SCIENCE BONDING & DIELECTRIC MATERIALS DELIVER PACKAGING SOLUTIONS FOR 5G, IOT DEVICES

Semiconductor IC packaging techniques include the utilization of 3D integration to increase chip density, maximize performance and reduce power consumption.

# 20 Evolving subfab vacuum challenges demand collaborative solutions

Semiconductor manufacturing is no longer focused on Dennard scaling as a principal means to improve performance and reduce costs.

#### 24 Onto Innovation's 'XL' fine resolution large field lithography dramatically cuts FOPLP pattern distortion

Heterogeneous integration enables multiple chips from varying Silicon processes to deliver superior performance.

#### 34 Next-generation low-k films can address present, future fabrication challenges

Smaller transistors packed more tightly into evershrinking packages are characteristic of new DRAM or logic devices.

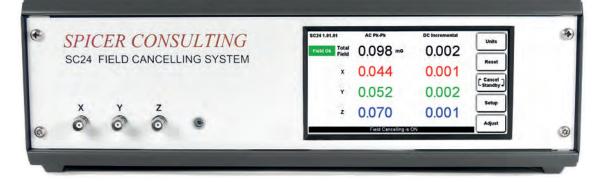

# 38 Eliminating EMI helps ensure accurate test, measurement

As semiconductors shrink with each new generation, inspecting devices on-wafer or as singulated die becomes increasingly complex thanks to environmental and co-located electronic sources of magnetic interference.

#### 42 How to mitigate the challenges of bulk gas purification & enhance industry innovation

There are several drivers for innovation in gas purification today, as the speed of technology continues to accelerate.

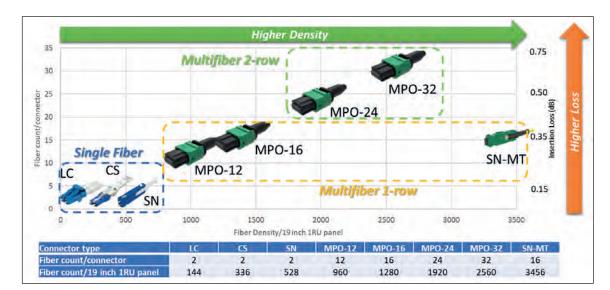

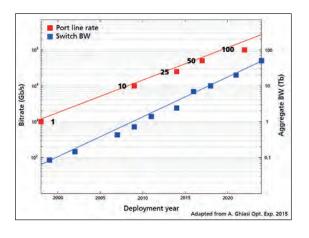

# 44 Co-packaged optics for hyperscale data centres

The continuing push for greater efficiency, smaller form factors and faster throughput is leading to the development of next-generation co-packaged optics for datacentres and related applications.

#### NEWS

- **06** Advantest to enable data analytics solutions

- 07 EV GROUP expands collaboration with ITRI

- **08** Intel signs agreement with Brookfield to jointly invest up to \$30 billion

- 10 Keysight enable system-on-a-chip makers with new test solutions

- 11 Park Systems acquires Accurion GmbH

- 12 EV Group revolutionizes 3D integration

- 14 Vedanta to set up semiconductors and display fab units in India

- 15 Global semiconductor sales increase by 7.3%

Publisher & Editor Jackie Cannon Technical Editor Mark Andrews Contributing Editor Richard Stevenson Sales & Marketing Manager Shehzad Munshi USA Representatives Tom Brun Media Janice Jenkins Director of Logistics Sharon Cowley Design & Production Manager Mitch Gaynor jackie.cannon@angelbc.com +44 (0)1923 690205 mark.andrews@angelbc.com richard.stevenson@angelbc.com +44 (0)1923 690215 tbrun@brunmedia.com +001 724 539-2404 jjenkins@brunmedia.com +001 724-929-3550 sharon.cowley@angelbc.com +44 (0)1923 690200 mitch.gaynon@angelbc.com +44 (0)1923 690214 Chairman Stephen Whitehurst Chief Executive Officer Sukhi Bhadal Chief Technical Officer Scott Adams Directors Jackie Cannon, Sharon Cowley stephen.whitehurst@angelbc.com sukhi.bhadal@angelbc.com scott.adams@angelbc.com

+44 (0)2476 718970 +44 (0)2476 718970 +44 (0)2476 718970

Published by Angel Business Communications Ltd, 6 Bow Court, Fletchworth Gate, Burnsall Road, Coventry CV5 6SP, UK. T: +44 (0)2476 718 970 E: info@angelbc.com

Silicon Semiconductor is published five times a year on a controlled circulation basis. Non-qualifying individuals can subscribe at: £50.00 per annum (UK), €60.00 per annum (Europe), \$90 per annum (air mail)(USA). Cover price £4.50. All information herein is believed to be correct at time of going to press. The publisher does not accept responsibility for any errors and omissions. The views expressed in this publication are not necessarily those of the publisher. Every effort has been made to obtain copyright permission for the material contained in this publication. Angel Business Communications Ltd © Copyright 2022. All rights reserved. Contents may not be reproduced in whole or part without the written consent of the publishers. The paper used within this magazine is produced by chain of custody certified manufacturers, guaranteeing sustainable sourcing. US mailing information: Silicon Semiconductor, ISSN 1096-598X, is published 5 times a year by Angel Business Communications Ltd, Unit 6, Bow Court, Fletchworth Gate, Burnsall Rd, Coventry CV5 6SP. UK. Airfreight and mailing in the USA by agent named World Container INC 150-15, 183rd St, Jamaica, NY 11413, USA.

We strive for accuracy in all we publish; readers and contributors are encouraged to contact us if they recognise an error or omission. Once a magazine edition is published [online, in print or both], we do not update previously published articles to align old company names, branding, marketing efforts, taglines, mission statements or other promotional verbiage, images, or logos to newly created or updated names, images, typographic renderings, logos (or similar) when such references/images were accurately stated, rendered or displayed at the time of the original publication. When companies change their names or the images/text used to represent the company, we invite organizations to provide Angel Business Communications with a news release detailing their new business objectives and/or other changes that could impact how customers/prospects might recognise the company, contact the organisation, or engage with them for future commercial enterprise. Printed by: The Manson Group. ISSN 2050-7798 (Print) ISSN 2050-7801 (Online) © Copyright 2022.

### Advantest to enable data analytics solutions

Semiconductor test equipment supplier Advantest Corporation has rolled out the Advantest ACS Solution Store, an advanced online platform that provides ease of access to ACS real-time data infrastructure solutions and software applications.

CUSTOMERS can conveniently discover, purchase and securely deploy all available ACS solutions from Advantest and a broad spectrum of analytics ecosystem partners across the semiconductor lifecycle process. In addition, the ACS Solution Store enables application developers from these partner firms to publish, promote, distribute and manage their Advantestcertified apps.

"The Advantest ACS Solution Store provides another key cornerstone for our ACS business model and strategy," said Michael Chang, vice president and general manager of ACS at Advantest.

"It will facilitate access to all ACS offerings for our customers, as well as give them and our partners the ability to develop and publish their own apps on our open ecosystem platform - ultimately, helping all participants in the ACS value chain to achieve transformational business results." Capabilities incorporated in the ACS Solution Store include browsing for available ACS solutions in an online catalog and discovering how the solutions help customers transform data into real-time production control, delivering significant ROI for the semiconductor manufacturing process.

In addition, automated software distribution is enabled via the ACS Container Hub for containerized apps, which ensures an easy, secure and reliable deployment of the apps in the test fleet. Key benefits of the ACS Solution store include:

- Purpose Built: enabling customers to buy and deploy Advantest-certified ACS apps from ecosystem partners with assured quality, verified security and guaranteed compatibility on Advantest test equipment.

- Optimized and Integrated: to provide customers with solutions tailored to deliver improved yield, quality, OEE and time to market.

- Convenient: a one-stop ecosystem portal where customers can seamlessly and securely deploy

ready-made or custom-built company and partner apps from a single, trusted source, maximizing the value they can realize from ACS Edge and ACS Nexus, the key building blocks of the ACS real-time data infrastructure.

• Versatile: open solution ecosystem enables third-party developers and customers to develop data analytics solutions powered by ACS real-time data infrastructure.

Advantest launched ACS as part of its Grand Design strategy to enhance edge and cloud infrastructure services, data analytics and Al/machine learning solutions as a means of helping customers accomplish data-driven workflows.

#### Mycronic receives order for three SLX mask writers

MYCRONIC AB has received an order for three SLX mask writers from an existing customer in Asia. The order value is in the range of USD 17-21 million. Two systems are planned for delivery during the fourth quarter of 2023, while the third system is planned for delivery during the first quarter of 2024.

The SLX laser mask writer meets rising demand for photomasks for

the semiconductor industry and a future need for replacement and modernization. Photomasks manufactured by laser mask writers are of high importance and account for 70-75 percent of all photomasks produced for semiconductor manufacturing. SLX is a new and modern mask writer based on the same technology as Mycronic's mask writers for displays.

"SLX's modern and flexible platform

is well suited to meet different customer needs, which in this case is manifested by a repeat SLX order from an existing customer. This time the order is for three systems in two different configurations", says Charlott Samuelsson, Sr VP Pattern Generators at Mycronic.

Mycronic provides mask writers for display manufacturing and production of semiconductors.

### EV Group expands collaboration with ITRI

EV Group (EVG), a supplier of wafer bonding and lithography equipment for the MEMS, nanotechnology and semiconductor markets, has announced that it has expanded its collaboration with the Industrial Technology Research Institute (ITRI).

ONE OF the world's leading applied technology research institutes based in Hsinchu, Taiwan, on developing advanced heterogeneous integration processes.

With the support of the Department of Industrial Technology (DoIT) of the Ministry of Economic Affairs (MOEA), Taiwan, ITRI established the Heterogeneous Integration Chiplet System Package Alliance (Hi-CHIP) to help create an ecosystem covering package design, testing and verification, and pilot production, to achieve the goal of supply chain localization and expand business opportunities. As a member of the Hi-CHIP Alliance, EVG has provided several of its most advanced wafer bonding and lithography systems, including the LITHOSCALE® maskless exposure lithography system, EVG®850 DB automated debonding system, and GEMINI®FB hybrid bonding system.

The installation of these high-volumemanufacturing platforms at ITRI's state-of-the-art facility will help enable EVG's and ITRI's shared customers to accelerate the development and transfer of new heterogeneous

integration processes from R&D to customers' fabs.

In semiconductor manufacturing, 3D vertical stacking and heterogeneous integration - the manufacturing, assembly and packaging of multiple different components and dies into a single device or package - are increasingly important for higher performance beyond transistor scaling. 3D and heterogeneous integration are enabling high-bandwidth interconnects in advanced packaging to achieve overall system performance gains, and thus have become a crucial driver for artificial intelligence (AI), autonomous driving and other high-performance computing applications. As a result, the MOEA is proactively following up and bridging the resources with nationalscale R&D projects such as "AI Chip Heterogeneous Integrated Module Advanced Manufacturing Platform" and "Programmable Heterogeneous 3D Integration".

According to Dr. Robert (Wei-Chung) Lo, Deputy General Director of Electronic and Optoelectronic System Research Laboratories at ITRI, "As part of ITRI's mission to drive industrial development,

create economic value, and enhance social well-being through technology R&D, we focused on developing new 3D and heterogeneous chip integration processes and forging close cooperation across the supply chain to enable continued development and growth of the semiconductor industry.

Having the same fully automated highvolume-manufacturing systems in our research facility that our customers have in their fabs, including these new wafer bonding and lithography solutions from EV Group, enables our customers to immediately transfer process recipes developed at ITRI to their own fabs - providing short rampup time from lab to fab."

WWW.SILICONSEMICONDUCTOR.NET | ISSUE IV 2022 7

**APRIL 2023**

SHERATON BRUSSELS

AIRPORT HOTEL BELGIUM

# Intel signs agreement with Brookfield to jointly invest up to \$30 billion

Intel Corporation has announced a first-of-its-kind Semiconductor Co-Investment Program (SCIP) that introduces a new funding model to the capital-intensive semiconductor industry.

AS PART OF its program, Intel has signed a definitive agreement with the infrastructure affiliate of Brookfield Asset Management, one of the largest global alternative asset managers, which will provide Intel with a new, expanded pool of capital for manufacturing build-outs.

SCIP is a key element of Intel's Smart Capital approach, which aims to provide innovative ways to fund growth while creating further financial flexibility to accelerate the company's IDM 2.0 strategy. Intel's agreement with Brookfield follows the two companies' memorandum of understanding announced in February 2022. Under the terms of the agreement, the companies will jointly invest up to \$30 billion in Intel's previously announced manufacturing expansion at its Ocotillo campus in Chandler, Arizona, with Intel funding 51% and Brookfield funding 49% of the total project cost. Intel will retain majority ownership and operating control of the two new leading-edge chip factories in Chandler, which will support long-term demand for Intel's products and provide capacity for Intel Foundry Services (IFS) customers. The transaction with Brookfield is expected to close by the end of 2022, subject to customary closing conditions.

"This landmark arrangement is an important step forward for Intel's Smart Capital approach and builds on the momentum from the recent passage of the CHIPS Act in the U.S.," said David Zinsner, Intel CFO. "Semiconductor manufacturing is among the most capital-intensive industries in the world, and Intel's bold IDM 2.0 strategy demands a unique funding approach. Our agreement with Brookfield is a first for our industry, and we expect it will allow us to increase flexibility while maintaining capacity on our balance sheet to create a more distributed and resilient supply chain."

Sam Pollock, CEO of Brookfield Infrastructure, said, "By combining Brookfield's access to large-scale capital with Intel's industry leadership, we are furthering the advancement of leading semiconductor production capabilities. Leveraging our partnership experience in other industries, we are pleased to come together with Intel in this important investment that will form part of the long-term digital backbone of the global economy."

#### **Benefits of the Transaction**

Intel's partnership with Brookfield is expected to enhance the company's strong balance sheet by allowing Intel to tap into a new pool of capital below its cost of equity while protecting its cash and debt capacity for future investments and continuing to fund a healthy and growing dividend. Over the next several years, the structure is expected to provide a \$15 billion cumulative benefit to Intel's adjusted free cash flow and is expected to be accretive to Intel's earnings per share during the construction and ramp phase. SCIP provides Intel the ability to replicate the co-investment model with other partners for other build-outs globally.

#### Intel's Smart Capital Approach

SCIP is an important component of Intel's overall Smart Capital approach, which is designed to allow the company to adjust quickly to opportunities in the market, while managing its margin structure and capital spending.

Through SCIP, Intel is accessing strategically aligned capital to increase its flexibility and help efficiently accelerate and scale its manufacturing build-outs. This type of co-investment also shows how private capital is unlocked and becomes a force multiplier for government incentives for semiconductor manufacturing expansion. In addition to SCIP, the other key elements of Smart Capital include:

#### Smart capacity investments:

Intel is aggressively building out relatively low-cost shell space, which gives the company flexibility in how and when it brings additional capacity online based on milestone triggers such as product readiness, market conditions and customer commitments. In 2021, approximately 35% of Intel's capital expenditures was spent on infrastructure.

#### **Government incentives:**

Intel is continuing to work with governments in the U.S. and Europe to advance incentives for domestic manufacturing capacity for leadingedge semiconductors. Considerable progress has been made over recent months, as President Biden signed into law the CHIPS and Science Act of 2022 that includes funding for \$52 billion in incentives for the U.S. semiconductor industry; the U.S. Congress is making strides with the FABS Act, which will establish a semiconductor investment tax credit in the U.S.; and the European Chips Act has added 15 billion euros to an existing 30 billion euros in public investments to build new infrastructure, among other advancements.

#### Customer commitments:

IFS is working closely with potential customers, and several have indicated willingness to make advance payments to secure capacity. This provides Intel with the advantage of committed volume, de-risking investments while providing capacity corridors for its foundry customers.

#### **External foundries:**

The company intends to continue its use of external foundries where their unique capabilities support Intel's leadership products.

# All Systems.

ClassOne

SOLSTICE

====

Your advanced microelectronics make the world go.

Our advanced manufacturing systems get you there.

#### SOLSTICE

Advanced Single-wafer Electroplating and Surface Preparation

**OUR FLAGSHIP SOLSTICE PLATFORM** delivers best-in-class performance at an unmatched price/performance ratio. Our highly flexible platform can be customized for a comprehensive range of semiconductor packaging applications for advanced device manufacturing including VCSELs, microLEDs, RF and power semiconductors.

#### **GO NOW, GO SOLSTICE**

- Advanced performance with maximum throughput and wafer uniformity

- Flexible, scalable platform for multiple applications on a single, compact system

- Elegant and simple design, easier to use, operate and maintain

- Engineered for reliability and uptime

- Unparalleled cost-efficiency and ROI

YOU SEEK WORLD-CLASS MANUFACTURING EQUIPMENT TO MAKE YOUR FAB GO. WE CREATED SOLSTICE TO MAKE YOUR DECISION EASY.

**REACH OUT - WE'RE READY.**

TEL: +1 406 407 7814 info@ClassOne.com

#### **INDUSTRY NEWS**

# Keysight enable system-on-a-chip makers with new test solutions

Keysight Technologies has announced that the company's new 224G Ethernet test solutions enables system-on-a-chip (SoC) makers to validate next generation electrical interface technology, accelerating 1.6 terabit per second (1.6T) transceiver design and pathfinding.

5G, ARTIFICIAL INTELLIGENCE (AI) and internet of things (IoT) applications are driving growth in data traffic, creating unprecedented bandwidth demands in networks and data centers. High-speed digital interfaces that support 224 Gbps per lane data connection speeds offer increased bandwidths and underpin 1.6 terabit per second (1.6T) high-speed interconnect technology.

Improved data throughput and efficiency in data center networks also reduce power consumption and cost. Keysight is the only provider of bit error ratio tester (BERT) solutions capable of generating and analyzing 224 gigabit per second (224 Gbps) signals.

"Keysight is pleased to enable Synopsys, and other semiconductor makers, capture early market opportunities associated with the transition from 800 gigabit per second (800G) to 1.6T," said Dr. Joachim Peerlings, vice president of Network and Data Center Solutions at Keysight Technologies. "Keysight's unique portfolio of high-speed digital interface test solutions enable Synopsys to validate the performance of 224G IP designs accelerating 1.6T design and pathfinding."

The M8050A BERT offers users a unique 224 Gbps test solution for electrical design and validation of transceiver SoCs used in data centers and networks for transferring large amounts of data at high speeds. Keysight's M8050A BERT provides signal integrity that enables accurate characterization of receivers used in next-generation data center networks and server interfaces. Synopsys used Keysight's M8050A BERT, M8199 Arbitrary Waveform Generator (AWG) and Infiniium UXR-Series Oscilloscope to develop and validate 224G serializer/ deserializer (SerDes) IP designs.

"High-performance computing systems depend on high-speed, low-latency interfaces to process massive amounts of data with minimal power," said John Koeter, senior vice president of marketing and strategy for the Solutions Group at Synopsys. "As a leading provider of high-speed Ethernet IP solutions, Synopsys utilizes Keysight's comprehensive digital interface test solutions to validate the performance of the PHY IP, enabling designers to meet their design and system-level requirements for highperformance computing, networking and AI SoCs."

At the European Conference on Optical Communication (ECOC) 2022 in Basel, Switzerland, Keysight and Synopsys will demonstrate the industry's first common electrical interface (CEI) SoC supporting 224Gbps.

Exhibition visitors can view the demonstration at the booth hosted by the Optical Internetworking Forum (OIF), an industry organization that promotes the development and deployment of interoperable networking solutions and services for optical networking products, network processing elements and component technologies.

### Park Systems acquires Accurion GmbH

Park Systems Corp. has announced that it has acquired Accurion GmbH, a privately held company that develops and manufactures imaging spectroscopic ellipsometers and active vibration isolations

THIS ACQUISITION adds to Park's portfolio of atomic force microscopy and white-light interferometric microscopy. Financial details of the transaction were not disclosed.

Headquartered in Goettingen, Germany, Accurion GmbH has pioneered the field of imaging spectroscopic ellipsometry. Originally a spin-off from the Max Planck Institute for biophysical chemistry, the company started out designing the Brewster angle microscope for the characterization of ultrathin films.

As these microscopes turned out to be sensitive to vibrations, the division of active vibration isolation followed.

Accurion's Imaging Ellipsometers combine the benefits of ellipsometry and optical microscopy in a single device. The unification of the two technologies creates a unique metrology tool that redefines the limits of both ellipsometric measurements and polarization-contrast microscopy.

The enhanced spatial resolution of imaging ellipsometers expands ellipsometry into new areas of microanalysis, microelectronics, and bio analytics.

"This is Park's very first business acquisition in the company's history, and we are very excited to add this storied, high-tech company to our business," said Dr. Sang-il Park, CEO of Park Systems. "

Accurion's imaging ellipsometers and active vibration isolation will have

wide range of product and business synergies with Park's existing line of atomic force microscopy that will benefit our customers and investors alike."

"We are honored to become a part of Park Systems," added Stephan Ferneding, co-founder and CEO of Accurion. "We are excited that Park's expertise and global sales and service reach in automated systems for industrial manufacturing will take the business to the next level.

We look back on 30 years of valuable experience enabling technological and scientific progress for customers around the world. We look forward to continuing the success together with a strong partner like Park Systems."

# Grow your profits...

With on-site hydrogen generation

A Nel Hydrogen electrolyser will help save money, streamline operations and increase your bottom line.

- Alkaline and PEM technologies

- Safe, clean and cost effective

- Consistent purity and pressure

- Eliminate hydrogen delivery

and storage

- Scale to match any application

nel•

Visit us on-line or call for a consult with one of our sales engineers today! +1.203.949.8697 www.nelhydrogen.com

### **EV Group revolutionizes 3D integration**

EV Group (EVG), a supplier of wafer bonding and lithography equipment for the MEMS, nanotechnology and semiconductor markets, has introduced NanoCleave<sup>™</sup>, a revolutionary layer release technology for silicon that enables ultra-thin layer stacking for front-end processing, including advanced logic, memory and power device formation, as well as semiconductor advanced packaging.

NANOCLEAVE is a fully front-endcompatible layer release technology that features an infrared (IR) laser that can pass through silicon, which is transparent to the IR laser wavelength. Coupled with the use of specially formulated inorganic layers, this technology enables an IR laser-initiated release of any ultra-thin film or layer from silicon carriers with nanometer precision.

As a result, NanoCleave enables silicon wafer carriers in advanced packaging processes such as Fan-out Waferlevel Packaging (FoWLP) using mold and reconstituted wafers as well as interposers for 3D Stacked ICs (3D SIC). At the same time, its compatibility with high-temperature processes enables completely novel process flows for 3D IC and 3D sequential integration applications – enabling hybrid and fusion bonding even of ultra-thin layers on silicon carriers, thereby revolutionizing 3D and heterogeneous integration as well as material transfer in next-generation scaled transistor designs. EV Group's revolutionary NanoCleave layer release technology uses an infrared (IR) laser that can pass through silicon and inorganic release materials to enable an IR laser-initiated release of any ultra-thin film or layer from silicon carriers with nanometer precision. Source: EV Group.

Company executives will be available to discuss this IR laser transfer technology breakthrough at SEMICON Taiwan, taking place at the Taipei Nangang Exhibition Center Hall 1 (TaiNEX 1) in Taipei, Taiwan, from September 14-16. Event attendees can visit EVG at Booth #L0316 (4th Floor) to learn more.

### Silicon Carriers Benefit 3D Stacking and Back-end Processing

In 3D integration, carrier technologies for thin-wafer processing are key to enabling higher performance systems with increasing interconnection bandwidth. Glass carriers have become an established method for building up device layers through temporary bonding with organic adhesives, using an ultraviolet (UV) wavelength laser to dissolve the adhesives and release the device layers, which are subsequently permanently bonded onto the final product wafer. However, glass substrates are difficult to process with semiconductor fab equipment that have been designed primarily around silicon, and that require costly upgrades to enable glass wafer processing. In addition, organic adhesives are generally limited to processing temperatures below 300°C, which limits their use to back-end processing.

Enabling silicon carriers with inorganic release layers avoids these temperature

and glass carrier compatibility issues. In addition, the nanometer precision of IR laserinitiated cleaving opens up the possibility of processing extremely thin device wafers without changing processes of record. Subsequent stacking of such thin device layers enables higher bandwidth interconnects and opens up new opportunities to design and segment dies for next-generation highperformance systems.

#### Next-generation Transistor Nodes Demand Novel Layer-transfer Proces

At the same time, transistor roadmaps for the sub-3-nm node are calling for new architectures and design innovations such as buried power rails, backside power delivery networks, complementary field-effect transistors (CFETs) and even 2D atomic channels, all of which will require layer transfer of extremely thin materials. Silicon carriers and inorganic release layers support process cleanliness, material compatibility and high processing temperature requirements for frontend manufacturing flows. However, until now, silicon carriers had to be completely removed using grinding, polishing and etching processes, which results in micron-range variations across the surface of the working device layer, making this method unsuitable for thinlayer stacking at advanced nodes.

EVG's new NanoCleave technology utilizes an IR laser and inorganic release materials to enable laser debonding on silicon with nanometer precision. This eliminates the need for glass substrates for advanced packaging, avoiding temperature and glass carrier compatibility issues, and enables the ability to transfer ultrathin (single micron and below) layers via carriers in front-end processing without changing the processes of record. The nanometer-precision of EVG's new process supports advanced semiconductor device roadmaps calling for thinner device layers and packages, increased heterogeneous integration, and reduced processing costs through thin-layer transfer and the elimination of glass substrates.

# **VACUUM SOLUTIONS FROM A SINGLE SOURCE**

Pfeiffer Vacuum stands for innovative and custom vacuum solutions worldwide, technological excellence, competent advice and reliable service. We are the leading supplier of vacuum technology that provides a complete product portfolio:

- Pumps for vacuum generation down to UHV

- Vacuum measurement and analysis equipment

- Leak detectors and integrity test systems

- System technology and contamination management solutions

- Chambers and components

Are you looking for a perfect vacuum solution? Please contact us: **Pfeiffer Vacuum, Inc.** · USA · T 800-248-8254 · F 603-578-6550 · contact@pfeiffer-vacuum.com · www.pfeiffer-vacuum.com

Clamp-On Sensor SEMIFLOW® CO.65

Highly Accurate Flow Meter for Rigid Plastic Tubing: Smallest Footprint | Increased Uptime | Maximum Yield

### Vedanta to set up semiconductors and display fab units in India

In a move that aims to put India on the global silicon map and make the country selfsufficient in the critical area of semiconductors and displays, Vedanta, the world's sixth largest diversified natural resources group, signed two Memorandum of Understanding (MoUs) with the Government of Gujarat to set up a semiconductor fab unit, a display fab unit and a semiconductor assembling and testing unit in the key industrial state, in line with Prime Minister Narendra Modi's vision to make the country a hub of futuristic technologies.

THE PROJECT, which will be taken up by the Vedanta-Foxconn JV announced earlier this year, envisages a total investment of USD 20 Billion and an employment potential of around 100,000 people. Vedanta will hold 60% of the equity in the JV while Foxconn will own 40%. The JV will look at setting up a semiconductor manufacturing plant in the next two years.

The MoU signing ceremony was attended by Union Minister Shri Ashwini Vaishnav, Gujarat Chief Minister Shri Bhupendrabhai Patel, Vedanta Group Chairman Anil Agarwal, Vedanta's Global Managing Director, Display and Semiconductors, Akarsh Hebbar, Mr. Brian Ho, VP. Foxconn Semiconductor Group and a host of other dignitaries. The project will attract electronics ecosystem players across the value chain entailing manufacturers of highly sophisticated and sensitive equipment, materials (high purity Gases, chemicals, wafers, photomasks), equipment service providers etc.

The proposed semiconductor manufacturing fab unit will operate on

the 28nm technology nodes and the display manufacturing unit will produce Generation 8 displays catering to small, medium and large applications.

On this occasion, Union Minister for Electronics and Information Technology, Shri Ashwini Vaishnav, said: "The project is in line with Hon. Prime Minister Shri Narendra Modi's vision for achieving self-reliance in the field of semiconductor manufacturing. I congratulate Vedanta and Foxconn for taking this initiative and bringing the semiconductor plant to India." Semiconductors and displays are critical to establishing India as an electronics hub and will help attract suppliers and device assemblers to setup base in India. The Indian semiconductor market was valued at \$27.2 billion in 2021 and is expected to grow at a healthy CAGR of nearly 19% to reach \$64 billion in 2026.

Speaking on the occasion, Vedanta Chairman Mr. Anil Agarwal, said: "We are delighted to announce that Gujarat will be the location for our display and semiconductor fab ventures. The state is well known globally for being a manufacturing hub and I hope that India's upcoming, cutting-edge electronics ecosystem will thrive, with every state benefitting to develop their electronic manufacturing hubs. We are privileged to take one step further in supporting Prime Minister Modi's vision of aatmanirbhar Bharat in this strategic sector."

The decision to set up the project in Gujarat comes after Vedanta and Foxconn announced in February that they will form a joint venture company in India. Vedanta has a presence in electronics and technology business through group companies Avanstrate Inc. and Sterlite Technologies.

Hon Hai Technology Group ("Foxconn") is the world's largest electronics manufacturer. Hon Hai is also the leading technology solution provider, and it continuously leverages its expertise in software and hardware to integrate its unique manufacturing systems with emerging technologies.

Mr. Brian Ho, VP, Foxconn

Semiconductor Group, said, "I am delighted that the semiconductor plant will come up in the industrial state of Gujarat. We applaud the efforts made by the Government of Gujarat, home of Prime Minister Narendra Modi. to attract semiconductor development and upgrade government efficiency. Gujarat is recognized for its industrial development, green energy, and smart cities. The improving infrastructure and the government's active and strong support increases confidence in setting up a semiconductor factory. We look forward to working with our partners and the Gujarat leadership to further enhance the infrastructure required to cater to the ambitious semiconductor project."

The broad plans for a semiconductor unit in India were announced after the COVID-19 pandemic upended global supplies of crucial electronic components used in everything from smartphones to cars. India has vowed to spend \$30 billion to overhaul its tech industry and build local chip supply chains to avoid being dependent on foreign producers.

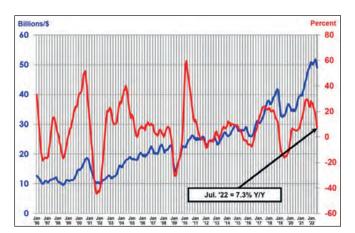

### Global semiconductor sales increase 7.3%

The Semiconductor Industry Association (SIA) has announced global semiconductor industry sales were \$49.0 billion in the month of July 2022, an increase of 7.3% over the July 2021 total of \$45.7 billion, but a decrease of 2.3% compared to the June 2022 total of \$50.2 billion

MONTHLY SALES are compiled by the World Semiconductor Trade Statistics (WSTS) organization and represent a threemonth moving average. SIA represents 99% of the U.S. semiconductor industry by revenue and nearly two-thirds of non-U.S. chip firms.

"Global semiconductor sales remained strong in July, easily topping the total from last July, but market growth has slowed substantially in recent months, with year-to-year sales increases dropping into the single digits for the first time since December 2020," said John Neuffer, SIA president and CEO. "Sales into the Americas market increased 20.9% year-to-year to lead all regions."

In addition to the Americas, year-to-year sales were up in the Europe (15.2%) and Japan (13.1%), and Asia Pacific/All Other (4.1%), but down in China (-1.8%). Month-to-month sales increased in Europe (2.7%) and Japan (0.6%), but decreased in the Americas (-2.3%), China (-3.5%), and Asia Pacific/All Other (-3.5%).

For comprehensive monthly semiconductor sales data and detailed WSTS forecasts, consider purchasing the WSTS Subscription Package. For detailed historical information about the global semiconductor industry and market, consider ordering the SIA Databook.

Semiconductor IC packaging techniques include the utilization of 3D integration to increase chip density, maximize performance and reduce power consumption. Brewer Science, a global technology leader in the development and manufacturing of innovative materials and processes, has introduced its latest packaging solutions utilizing a permanent bonding material and a photo-imageable dielectric for the fabrication of cutting-edge semiconductors as well as 5G and IoT microelectronic devices.

#### BY BARON HUANG, MEI DONG, AND ZIWEI LIU, BREWER SCIENCE

### Permanent Bonding Material with High Thermal Budget

BONDING TWO components together permanently is applied in many fields of advanced packaging to offer a z-axis direction of integration for the fabrication of three-dimensional integrated circuits (3D ICs). Such permanent bonding techniques include direct/fusion bonding, anodic bonding, soldering, and thermocompression. While fusion bonding is still the most frequently used permanent bonding technology in today's semiconductor industry, there is a fastgrowing trend for adhesive bonding.

Adhesive bonding, which develops a bond connecting one surface to another using a polymeric material as the intermediate layer, brings significant advantages including: 1) improved design flexibility; 2) good surface planarization and adaptability to surface topography; 3) lower bonding temperature for protecting sensitive components; and 4) better tolerance to particles. With all these merits, adhesive bonding has recently received much attention for microelectromechanical systems (MEMS) packaging and heterogeneous integration to assemble individual IC components such as logic chips, memory chips, and image sensor devices together into high-density, ultra-thin integrated packages. Such modules are needed for high-performance computing applications such as artificial intelligence (AI), data centers, 5G, and high-end mobile products.

Brewer Science previously introduced its first permanent bonding adhesive, the PermaSOL® family of materials, at the European 3D & Systems Summit.

#### COVER STORY | BONDING AND DIELECTRIC MATERIALS

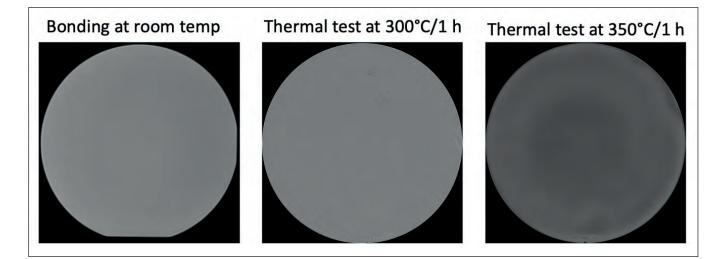

Figure 1. C-SAM images of next generation PBM after bonding at room temperature (left), after thermal testing at 300 °C for 1 hour (center), and after thermal testing at 350 °C for 1 hour (right)

PermaSOL materials were designed to address chip-level and wafer-level packaging requirements by providing reliable bonds with good thermal stability and with low moisture absorption. Brewer Science is now introducing its next generation of permanent bonding materials (PBM) with excellent thermal stability and an improved thermal budget up to 350°C. These materials further provide room temperature bonding with low pressure, low dielectric constant, high chemical resistance, and long shelf life.

In comparison to benzocyclobutene, a widely used bonding adhesive, the Brewer Science next generation PBM exhibits even lower curing temperature, smaller tensile strength and modulus, and larger CTE. These characteristics make the Brewer Science material a 'super low-stress resin' providing the benefits of low warpage, which brings up promising opportunities for applications on flexible substrates. Next generation PBM exhibits good thermal stability with a decomposition temperature above 470°C in a nitrogen atmosphere. The bonding can be achieved at 25°C, 2 kN, for 2 minutes, due to the intrinsic flexibility and fluidity of the material.

Figure 1 shows the bonding quality of the next generation PBM characterized by a SONIX Scanning Acoustic Microscope, demonstrating a void-free bondline. After bonding, the adhesive material is solidified via a thermal curing process. The material starts to cure at 160°C. Over 90 percent curing is realized when cured at 250°C for 3 minutes or 220°C for 30 minutes. A high temperature (300°C and 350°C) thermal test was also conducted on the cured material to further investigate its thermal stability. The C-SAM images in Figure 1 shows that next generation PBM has a good thermal budget: defect-free and low shrinkage after heat treatments at 300°C and 350°C for one hour.

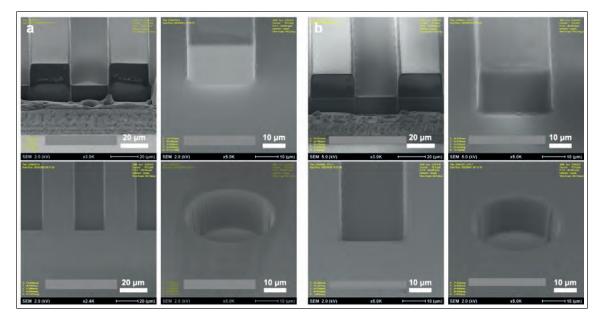

Figure 2. SEM/FIB images of (a) low-loss PID material on silicon substrate; (b) low-loss PID material on Ti/ Cu substrate

#### COVER STORY | BONDING AND DIELECTRIC MATERIALS

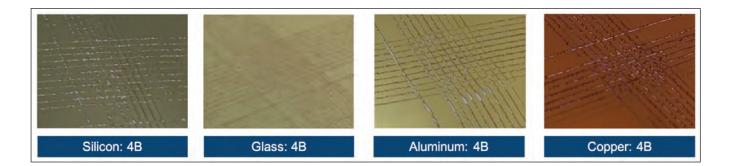

Figure 3. Cross hatch tape peel testing suggests good adhesion of low-loss PID material to various substrates, including Si, Glass, Al, and Ti/Cu surfaces

#### Low-loss photo-imageable dielectric

With the exploding demand for high-rate data connectivity, new spectrum for 5G mobile networks is being rapidly deployed worldwide. Since 2019, service providers have initiated a race for the 5G market—put another way: the fifth-generation technology standard for broadband cellular networks. Many network operators subsequently reported realizing the fascinating capabilities of 5G, including superior speeds and low latencies, which quickly expanded the number of use cases and further boosts the demand for data and performance.

In this 5G era, there is a growing demand for new materials and new packaging architectures to ensure low signal loss for high bandwidth millimeter wave (mmWave) RF transmission. Also needed is reliable measurements, especially in wafer level packaging, 3D integration, TSV filling, and stress-buffering applications. The 5G spectrum utilizes higher frequencies, which can lead to a greater risk of signal loss.

Photo-imageable dielectric (PID) with low-loss is now in the spotlight, especially for high-speed and high-frequency applications. Various polymeric dielectric materials have been evaluated as PID for packaging high-speed and high-frequency devices, including polybenzoxazole, polyimide, polysiloxane, and epoxy/phenol. However, most of them show a dielectric constant greater than three and with a dissipation factor of around 0.02, which might be fine for the existing applications with frequencies in the sub-6 GHz bands, but cannot meet the requirement and future challenges to be found with frequencies at 60 GHz or beyond for 5G mmWave communication.

> Table 1. Properties of Brewer Science's next generation PBM and low-loss PID materials

Herein, Brewer Science has developed a new lowloss PID material to meet the growing demand for 5G mmWave and IoT applications. The dielectric constant (Dk) for the Brewer Science low-loss PID material is measured to be 2.6 at 10 GHz and at 108 GHz, while the dissipation factor (Df) is 0.0016 at 10 GHz and 0.0041 at 108 GHz. Furthermore, the low-loss PID material can be patterned at low UV exposure dosages, around 300 mJ/cm2; it provides good line/space resolution with an aspect ratio around 1:1; patterned line/space, trench, and via features are shown in Figure 2. A steep sidewall angle close to 90 degrees that is free of footing/ rounding is also observed in SEM/FIB images of the low-loss PID material.

Besides the need for a low dielectric constant and loss tangent, additional requirements for the photo-imageable dielectric include strong adhesion, good thermal stability and reliability as well as low moisture uptake, high elongation, low shrinkage, and high photosensitivity. The adhesion quality for the Brewer Science low-loss PID material was examined by crosshatch tape peel testing.

Figure 3 shows the low-loss PID has a good adhesion (4B) to various substrates, including silicon, glass and aluminum as well as titanium and copper surfaces. Other properties of the low-loss PID material are summarized in table 1, which shows the material can meet or even exceed the demands for a wide range of applications for the packaging of high-speed and high-frequency devices.

#### Summary

This paper introduces a newly developed permanent bonding material (PBM) and a low-loss photo-imageable dielectric (low-loss PID) from Brewer Science. Its general material properties are summarized in Table 1. These materials offer many benefits including excellent thermal stability, low bonding temperature and pressure as well as low Dk and Df in addition to strong adhesion to various substrates. These many beneficial qualities make them attractive candidates to meet the growing demand for 5G and IoT device packaging where reliability, efficiency, and performance are critical to success.

| Material     | Electrical properties |                | Mecha                     | Thermal properties |                  |                  |            |            |                     |

|--------------|-----------------------|----------------|---------------------------|--------------------|------------------|------------------|------------|------------|---------------------|

|              | Dk<br>(10 GHz)        | Df<br>(10 GHz) | Tensile<br>strength (MPa) | Elongation<br>(%)  | Modulus<br>(GPa) | CTE<br>(ppm/ °C) | Tg<br>(°C) | Td<br>(°C) | Curing temp<br>(°C) |

| PBM          | 2.6                   | 0.0056         | 28.7                      | 90.9               | 0.71             | 113              | 35.7       | 470        | 150                 |

| Low-loss PID | 2.6                   | 0.0016         | 12.4                      | 112                | 0.17             | 157              | 85         | 350        | 180                 |

# SAVE THE DATE 18-19 APRIL 2023 SHERATON BRUSSELS

AIRPORT HOTEL BELGIUM

Talk to us about sponsorship NOW as it will be another full house Contact us at: info@angel-tech.net Or call us on +44 (0)2476 718970 and speak to Sukhi Bhadal

# Evolving subfab vacuum challenges demand collaborative solutions

Semiconductor manufacturing is no longer focused on Dennard scaling as a principal means to improve performance and reduce costs. Coordinated, lock-step efforts have given way to a sometimes-bewildering collection of new materials and technologies, often adding complexity in the form of new and different process tools, techniques and chemistries. This evolving IC production environment means manufacturers and suppliers need to collaborate in developing next-generation solutions that positively impact climate change, reduce costs and improve device performance.

#### BY MATT HALSEY, EDWARDS VACUUM

SEMICONDUCTOR MANUFACTURING technologies continue to diversify at all levels, from device architecture to multi-chip and chiplet integration schemes, through an expanding variety of advanced packaging technologies. Long gone are the days when device manufacturers advanced lock step down a road map focused almost exclusively on shrinking device sizes. Gone too is the luxury of developing a new process tool to meet a widely acknowledged, well defined set of requirements, with the assumption that there would be time to fine tune the design based on customer feedback after the product introduction.

In an environment with multiplying pathways to technical and commercial success, close collaboration between device manufacturers and equipment suppliers will acquire increasing importance as both seek to hasten development cycles, reduce time-to-market for new products, and target new products more precisely on key applications.

These same pressures apply in the subfab as well, where exist the essential systems that support the process tools above. Most semiconductor manufacturing processes require a vacuum; consequently, loss of that vacuum will take down a production line just as surely as a failure in the tool itself. Integrating new processes and materials into the production line must include careful consideration of the impacts on the vacuum systems tasked with removing excess gases and byproducts from the tools. Failure to do so will inevitably lead to more frequent maintenance, shorter service lifetimes and reduced reliability. In the worst case, it will result in unplanned down time with all its associated costs.

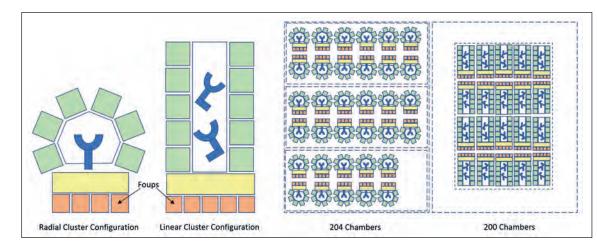

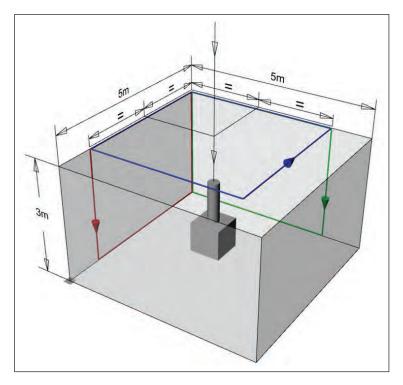

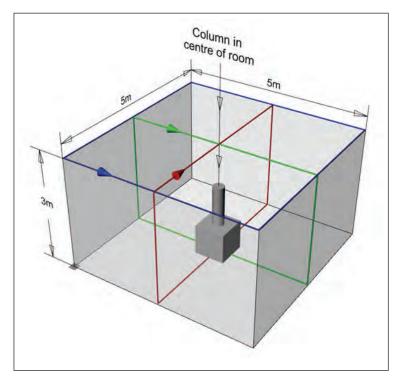

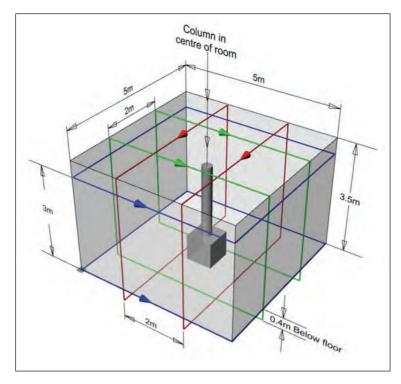

► Figure 1 shows how cluster tools might be reconfigured from the traditional radial layout to linear. The tools (and the pumps below) occupy less space, but the required pumping capacity remains the same.

#### SPOTLIGHT | SUBFAB VACUUM

In addition to changes in processes and materials, vacuum challenges in the subfab include shrinking space, increasing energy costs, and growing concern about the sustainability of the manufacturing process. Many of the design choices will require carefully balanced trade-offs among conflicting requirements.

#### **The Process**

The ever-increasing capital cost of new manufacturing capacity at advanced process nodes exerts relentless pressure on manufacturers to increase throughput in order to amortize higher fixed costs over a larger product output. For vacuum systems, higher throughput usually means higher flow rates and larger pumps.

Changes in process chemistry include the use of more aggressive reactions with harsher chemicals which require more resilient pumps. Pumps must incorporate materials and coatings that can withstand process gases and their by-products, as well as the corrosive chemicals used to clean process chambers.

Higher (and sometimes lower) temperatures for critical processes like atomic layer deposition and chemical vapor deposition require pumps that can handle the greater temperature range. Tolerances for rapidly spinning rotors are very tight and thermal expansion must be carefully managed. Materials used for seals at more conventional temperatures may not withstand higher temperatures. Often the temperature profile of the pump and associated piping must be carefully managed to avoid deposition of condensable materials.

#### Subfab space

Demands for higher throughput are leading manufacturers to put more smaller tools in less space in the fab. Following the convention that supporting systems must fit within the footprint of the process tool as projected down to the subfab, pumps and abatement must also fit in less space while handling increased flows. This can be especially challenging for pumps where the physical size of the pump has a direct relationship to its pumping capacity. Fab operators are currently looking for a 20-30% reduction in pump footprint, just to keep up with decreasing tool size. Stacking pumps in the subfab offers one solution, but there are limits related to safety and maintenance concerns.

Figure 1 shows how cluster tools might be reconfigured from the traditional radial layout to linear. The tools (and the pumps below) occupy less space, but the required pumping capacity remains the same.

#### Utility costs

Semiconductor manufacturing is energy intensive. The energy invested in a completed device can be

#### SPOTLIGHT | SUBFAB VACUUM

5.4 MJ (1.5 kWh) or more per square centimeter. Power is expensive and prices are increasing. Manufacturers are demanding more energy efficient systems, often for the simple reason that it reduces operating costs, with a sustainability aspect secondary to this.

Unfortunately, the desire for reduced energy consumption often conflicts with the need for increased pumping speed and pump temperature. Vacuum pumps do mechanical work, and, in the simplest analysis, more work takes more energy. The problem is exacerbated in harsh applications where additional power may be required to overcome resistance caused by material deposition within the pump or heavy particle loads in the process exhaust stream.

Implementation of idle mode technologies that reduce power consumption when the supported tool is not operating promise some relief; but again, harsh processes pose a specific challenge to vacuum systems where a halted pump may be difficult to restart reliably in the presence of deposition buildup and high particle loads.

The urgency of power concerns varies somewhat by region; power availability in Taiwan is severely restricted and energy efficiency is a high priority. In Europe, energy prices have soared recently, largely as a result of the war in Ukraine and the heavy reliance on natural gas as an energy source across the EU. Geopolitical tensions seem unlikely to diminish in the near term, adding additional pressure to demands for energy efficiency.

#### **Sustainability**

There is now a complete consensus within the scientific community that our environment is warming and that the warming is the result of human activity. Every industry, including semiconductor manufacturing, has an obligation to do everything possible to reduce the carbon emissions that are the primary cause of warming. Relative to some industries, semiconductor manufacturing is not a large direct emitter of greenhouse gases (GHG). But manufacturing ICs does consume vast amounts of energy, most of which currently comes from burning fossil fuels. The solution lies ultimately in the conversion of power generation to renewable sources, and as an industry with significant financial and political influence, we must advocate for that conversion.

However, the greatest potential for short-term reductions in GHG emissions lies in reducing our power consumption by improving our energy efficiency and minimizing the use of supporting utilities, all of which cost energy to produce.

Some of the trends we have mentioned work against reducing power consumption, such as the need for higher flow rates and temperatures. Fortunately, the most powerful influence – the always present drive to reduce costs – aligns directly with the environmental imperative to reduce power consumption. This powerful combination has driven broad commitment across the industry to embrace principles of environmental stewardship. As part of the Atlas Copco Group, Edwards Vacuum has signed on to the Science Based Target Initiative,

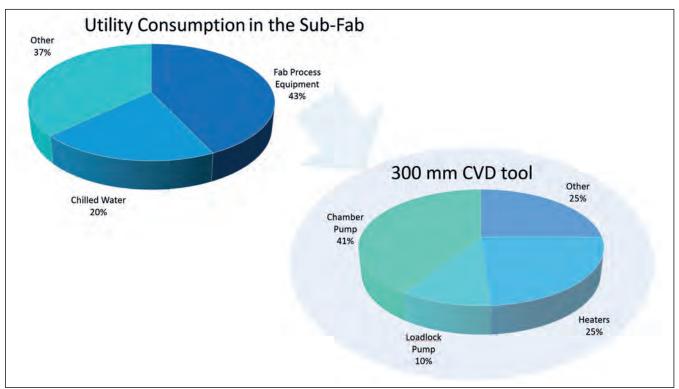

> Figure 2 In this example from an ISMI study, more than half of the power consumed by a CVD process tool is attributed to vacuum generation.

which commits participants to take all possible actions to limit global warming to less than 2°C. SEMI, our industry association, has updated its guidance (S23) to semiconductor manufacturers and equipment manufacturers to provide a basis for measuring energy consumption that will facilitate comparisons and encourage greater efficiency.

Vacuum requirements vary greatly from process to process. Some, like plating and chemical mechanical polishing, require no vacuum. Some, like EUV lithography and atomic layer deposition, require constant turnovers of chamber gases under vacuum conditions. Figure 2 shows an example taken from an ISMI Fab and Equipment Energy Study showing the power consumption attributed to a chemical vapor deposition (CVD) tool.

Most estimates allot something like 40% of overall fab power consumption to process equipment. In the case of CVD, over half of that power goes to creating and maintaining vacuum - 41% for chamber vacuum provided by dry pumps in the subfab and another 10% for the load lock pump on the tool itself. This is consistent with estimates that put power consumption for process vacuum at 20% of overall energy usage in semiconductor manufacturing. Clearly, improvements in the energy efficiency of vacuum systems can make a significant contribution to energy savings. Demands to take verifiable action to support sustainability goals is mounting throughout the supply chain and in capital markets. Downstream companies, especially consumer-facing companies, are under mounting pressure from customers to enhance their sustainability.

This ripples up the supply chain where subfab equipment can be a critical enabler. In an internal study at Edwards, we found that 97% of all GHG emissions (carbon dioxide equivalent) generated over the lifetime of a vacuum pump, including all inputs (power, water, cooling, nitrogen, etc.) from initial manufacture to final disposal, comes from energy consumed during use, which makes reductions in these emissions a primary target for equipment manufacturers.

#### Summary

Semiconductor manufacturers and their equipment suppliers face a constantly evolving array of often conflicting design and development priorities. Tightly coordinated advances toward the monolithic goal of smaller transistors has given way to a sometimes-bewildering collection of new materials and technologies.

In this environment it is more important than ever for equipment and device manufactures to collaborate closely in developing the next generation of solutions, working together to gain a better understanding of these evolving challenges from those who must live with them every day.

# Onto Innovation's 'XL' fine resolution large field lithography dramatically cuts FOPLP pattern distortion

Heterogeneous integration enables multiple chips from varying Silicon processes to deliver superior performance. In large panel packages, present day limits on exposure field size forces manufacturers to 'stitch' together multiple reticles, which slows throughput and increases costs. Onto Innovation's new JetStep® X500 system dramatically increases the exposure field up to 250 x 250 mm, slashing the number of exposures needed and cutting costs in FOPLP applications.

# BY JOHN CHANG, COREY SHAY, JAMES WEBB AND TIMOTHY CHANG, ONTO INNOVATION INC.

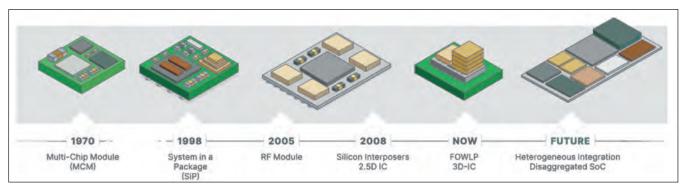

HIGH-PERFORMANCE compute, 5G, smartphones, data centers, automotive, artificial intelligence (AI) and the Internet of Things (IoT) – all rely on heterogeneous integration to achieve next-level performance gains. By combining multiple silicon nodes and designs inside one package, ranging in size from 75mm x 75mm to 150mm x 150mm, heterogeneous integration is one factor bringing us closer toward an era in which technology is beneficially embed into nearly all aspects of our lives whether it's in the smart factories where we work, the self-driving cars that navigate the cities in which we live, the mobile devices that connect us to each other and the wearable devices that help us live healthier lives.

Regardless of the speed to which we are approaching this promising new era, this transition comes with increasing challenges, ones that are constrained by increasingly stringent requirements. The next-generation of heterogeneous integration technologies, and the fan-out, panel-level packaging that often accompanies it, will demand even tighter overlay requirements to accommodate larger

> Figure 1. Heterogeneous integration enables next-generation device performance gains by combining multiple silicon nodes and designs inside one package, so the package size is expected to grow significantly. (Source: Cadence)

package sizes with fine-pitch chip interconnects on large-format, 510 mm x 515 mm flexible panels. (Fig 1)

As redistribution layers (RDL) are added, these processes may cause stresses to both the surface and inside of the substrate, stresses that may cause warpage and formation change. If the substrate suffers deformation from high pressure, high temperature or other process steps, the deformation can cause a pattern shift from the nominal position and affect the overlay results in the lithography process on large-format panels. If left uncorrected during the exposing process, these factors can result in serious overlay errors.

Adding to these challenges, advanced packages will soon require a resolution of 1 $\mu$ m, while advanced integrated circuit substrates (AICS) will require a resolution of 3 $\mu$ m. In addition, the budget for overlay is getting tighter due to the fine resolution process. In the case of AICS, the typical overlay yield is about 95% to 97% per layer.

How might an extremely large exposure field, fine-resolution lithography system deal with these heterogeneous integration challenges? To better understand the capabilities of such a tool, in this case Onto Innovation's JetStep® X500 system, we examined the use of metrology data from the lithography system, combined with overlay analysis algorithms, to identify the error terms and distortion components of the test vehicle and find a solution/ strategy to correct the errors. Designed specifically for the demands of high-volume manufacturing, this new lithography technology meets these challenges and successfully demonstrates how its users can achieve the stringent overlay requirements posed by heterogeneous integration.

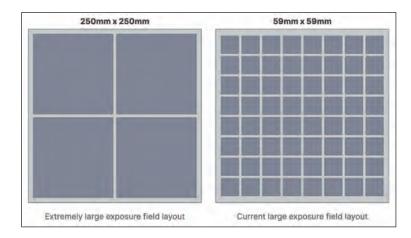

#### The Trouble with Stitching

Heterogeneous integration requires the integration of multiple chips into a single 75mm x 75mm or 150mm x 150mm package for increased functionality, a challenge for today's advanced packaging steppers, which have a limited exposure field of 59mm x 59mm. For most steppers, processing these two large package sizes requires the use of multiple exposure shots to complete a package because of the limited exposure field size. This method, known as "stitching," requires multiple reticles and has low throughput, which increases costs. However, increasing the stepper field size to sizes larger than 150mm x 150mm removes the need for stitching and increases throughput significantly.

While it takes 64 shots for current advanced packaging steppers with an exposure field of 59mm x 59mm, a stepper with an extremely large exposure field can expose a panel with just four (4) shots, an achievement that eliminates the need for image stitching and exceeds the overlay and critical uniformity requirements for these packages. (Fig 2)

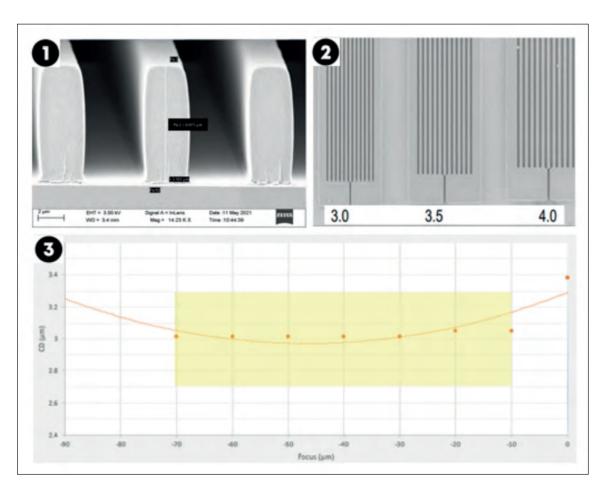

The 250mm x 250mm exposure field offered by the JetStep X500 system allows the user to process one or more large packages in a single shot and requires fewer shots to complete a substrate. This offers a significant throughput increase over regular exposure fields. This extremely large exposure field, fine-resolution lithography system is equipped with a 2.2x magnification projection lens, which enables

> Figure 2. The layout of an extremely large exposure field (250mm x 250mm) and a regular exposure field (59mm x 59mm) on a 510mm x 515mm panel. With the extremely large exposure field, a panel can be completed with just four (4) shots; with a current large exposure field, a panel requires 64 shots to complete.

Figure 3. Extremely large exposure field, fineresolution lithography system resolution performance: 1. Cross section copper seed wafer image of 3µm line/space with 10µm thick dry film resist, which is a 1:3.3 aspect ratio. 2. Isolated and dense area resolution results of 3µm, 3.5µm and 4µm line/ space. 3. Bossung curve of 3µm line/ space with a 10µm-thick dry film resist. The X axis is focus (µm), and the Yaxis is CD (µm). A 60µm depth of focus is observed in 3µm line/ space with 10µm-thick dry film resist.

exposure fields up to 250mm x 250mm, and offers  $3\mu$ m line/space resolution. In addition, the system has ±400ppm magnification compensation and ±100ppm anamorphic magnification compensation, with an overlay of < 1 $\mu$ m.

In order to demonstrate the resolution performance of this lithography system, we selected a copper clad laminate (CCL) and Ajinomoto build-up film (ABF) substrate with 10µm-thick dry film resist. As

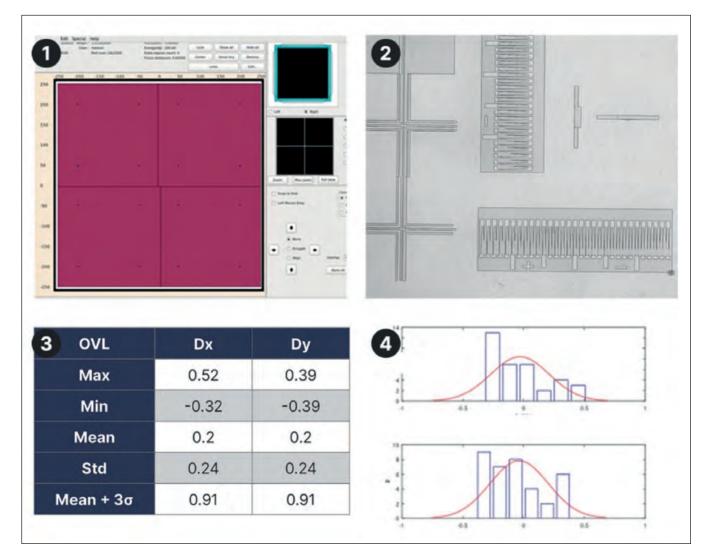

Each exposure field contains 3 x 3 measurement points, and 2 x 2 shots a panel were measured to determine the overlay performance of the lithography system. According to our overlay performance analysis, the extremely large exposure field, fine-resolution lithography system demonstrated a deviation X mean +3 sigma of 0.91µm and a deviation Y mean +3 sigma of 0.91µm seen in Fig 3, in only four shots the lithography system demonstrated a line/space resolution of  $3\mu$ m, while offering a depth of focus up to  $60\mu$ m, an indication that the extremely large exposure field, fine-resolution lithography system is suited for the high-volume manufacturing needs of larger package sizes with fine-pitch chip interconnects on large-format panels.

In order to test the overlay performance of the lithography system, we selected a 510mm x 515mm glass panel with  $1.4\mu$ m liquid resist. The test vehicle was run with a site-by-site correction method at four (4) shots per panel to build the second layer (Fig 4). We then checked the overlay error between layer 1 and layer 2 to determine its performance. The overlay error was determined by reading the location of overlapped verniers.

Each exposure field contains 3 x 3 measurement points, and 2 x 2 shots a panel were measured to determine the overlay performance of the lithography system. According to our overlay performance analysis, the extremely large exposure field, fine-resolution lithography system demonstrated a deviation X mean +3 sigma of 0.91µm and a deviation Y mean +3 sigma of 0.91µm. These numbers indicate an extremely large exposure field, fine-resolution lithography system can achieve the aggressive overlay number of less than 1µm that will be required for advanced packaging.

> Figure 4. The overlay performance of the extremely large exposure field fine-resolution lithography system: 1. Exposure layout for overlay demonstration, with four (4) shots per panel at 250mm x 250mm a shot. 2. Overlapped verniers built by the first layer and second layer: the overlay performance was determined by reading the verniers. 3. Overlay statistics table. 4. Dx and Dy distribution chart: the mean is close to center, and no peak distribution is observed.

#### **Correcting Overlay Errors**

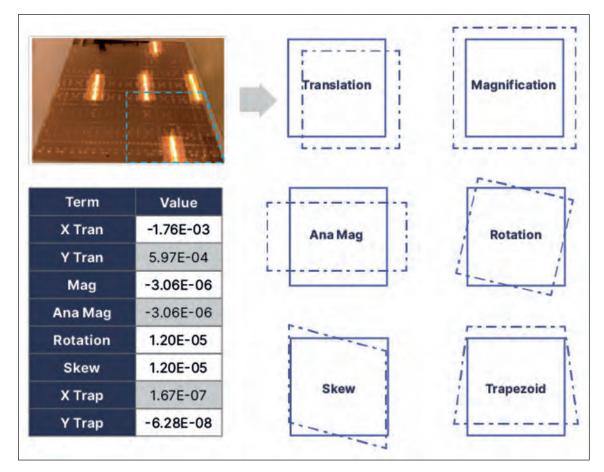

To demonstrate the ability of the extremely large exposure field, fine-resolution lithography system to correct errors on the substrate, we used the system's intra-field correction and global correction capabilities. The system's global correction capabilities offer translation, rotation, scale and orthogonality corrections, while the system's intrafield correction capabilities offer translation, rotation, magnification, radial distortion and trapezoid corrections. By combining global and intra-field correction capabilities, we were also able to test anamorphic magnification and skew corrections.

The stepper uses a reflective alignment system (RAS), which can recognize the alignment mark on the substrate, and grid stage information; which pairs with RAS to identify the pattern deviation of the substrate. The metrology data generated by the lithography system was combined with the following algorithms: a propriety algorithm and Dolana. These

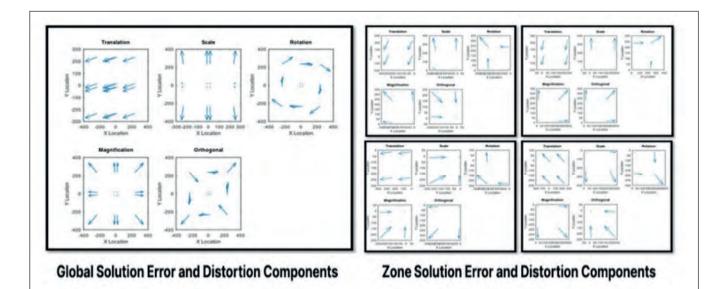

four exposure shots of the stepper then were analyzed for error terms and distortion components. With metrology data collected by the lithography system and analyzed by the Donala algorithm, we identified error terms and distortions in the test vehicles (Fig 5). In addition, we identified anamorphic pincushion and third radial distortion when describing errors in a full-panel model; however, the error terms change when fitting in a quadrant of the panel (lens field). The error terms change to include translation, magnification, anamorphic magnification, rotation, skew and trapezoid.

For each quadrant of the 510mm x 515mm panel, we found various error terms and distortion signatures, indicating that a global solution correction cannot fully correct test vehicle error and distortion; a unique correction is needed for each quadrant to correct the unique errors during exposure. By doing this, we were able to achieve successful overlay

► Figure 5. Error terms and distortion components are identified in a quadrant of a 510mm x 515mm test vehicle. The numbers in the table are the coefficients used in the equations of the algorithm that describe each term fit.

results. Fig 6 shows vector maps for global solution corrections and zone solution corrections; these two vector maps are from the same test vehicle. According to the vector maps, global solution translation corrections show that translation errors vector toward the down-left direction, but in the bottom-right quadrant of the zone correction solution, the translation errors vector toward the upper-right direction, which is the opposite direction of the global solution correction. Other correction components can be observed in different directions or trends in each quadrant.

The test vehicle was processed with liquid film. Using the lithography system, combined with a proprietary algorithm, corrections were generated for each quadrant of the test vehicle. The corrections were used during exposure, and then

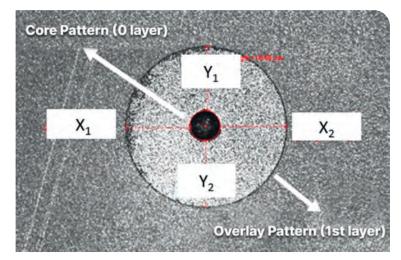

> Figure 6. Global solution correction vs. zone solution correction.

the test vehicle was taken to development. Overlay measurements were taken by optical microscope using measurement software, with six (6) measuring points per zone, four (4) zones per panel, totaling 24 measuring points per sampling. Four (4) measuring points were at the four (4) corners, the top-right, top-left, bottom-right and bottom-left corners. Two (2) measuring points were at the center of the zone. These measuring points were used to verify the overlay results of the entire area of the test vehicle. Fig 7 describes how the overlay deviation X, deviation Y and vector were defined.

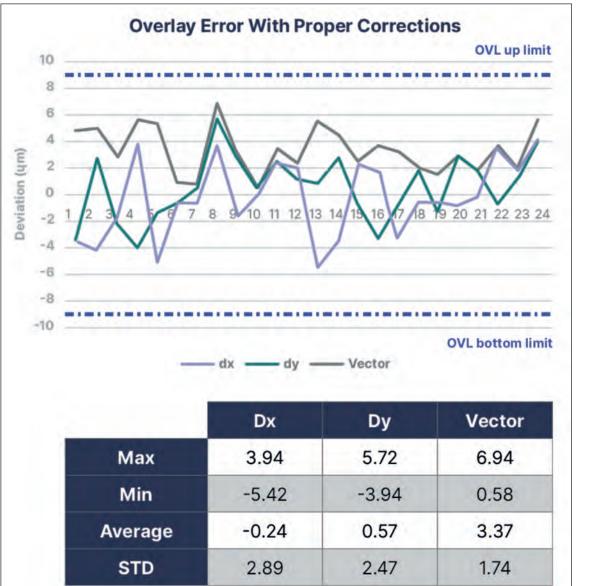

Fig 8 shows the overlay results of the test vehicle. The deviation X maximum is  $5.42\mu$ m and shifts right; the deviation Y maximum is  $5.72\mu$ m and shifts upward. Based on the substrate provider database, if the distortions and errors are recognized well and corrected properly, the final overlay error can be expected to be less than  $10\mu$ m. The final overlay error vector results are less than  $7\mu$ m, and dx and dy values are within  $\pm 6\mu$ m. This indicates that the errors

➤ Figure 7. Overlay measuring method to determine the overlay dx, dy and vector. Center black spot is core pattern, the bigger circle is of the overlay pattern, dx = X1-X2, dy = Y1-Y2 and error vector = (dx2+dy2).

Figure 8. Test overlay results with proper corrections and method. The unit of measurement is µm. Overlay pattern, dx = X1-X2, dy = Y1-Y2 and error vector = (dx2+dy2).

-5.47

6.46

Average

STD

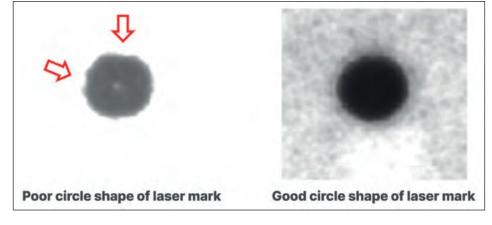

Figure 10. Alignment marks by laser drill system. The left figure has a poor shape compared to the right figure. This situation could result in alignment solution errors and affect final overlay. Alignment marks could contain one or multiple laser marks.

-0.95

11.26

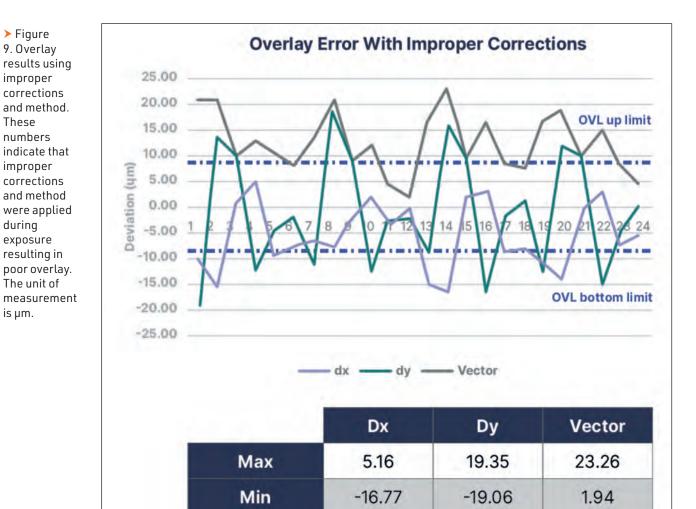

and distortions of the test vehicle were recognized correctly and corrected as expected. If the errors and distortions were not corrected properly, the overlay error vector could be  $20\mu$ m or higher. (Fig 9) We observed translation, rotation, scale, magnification, anamorphic magnification, skew, trapezoid and orthogonality errors in the test vehicle.

12.67

5.76

These errors needed to be corrected by a lithography tool to achieve better overlay results. In addition, we also observed various trending errors and distortion

signatures in each quadrant of the 510mm x 515mm panel. These observations indicate that a zone solution correction should be applied during exposure to enable better overlay results.

Analysis indicates that reasonable overlay results can be achieved by using proper corrections and zone solution corrections. However, better overlay numbers are to be expected when using yield predictions derived by the proprietary algorithm.

The 510mm x 515mm panel test vehicle was made using the AICS FOPLP process; the alignment marks on the test vehicle were created by a laser drill system (Fig 10). Due to the limitations of the laser drill system, we expected and observed lower accuracy and poor laser mark shape control, leading to an alignment solution error.

This alignment solution error can result in overlay errors, even though the lithography system or metrology system recognizes the alignment marks. Based on this finding, an additional offset may be needed to address this issue.

To address alignment solution errors, additional compensation by zone dimension is proposed. A proprietary algorithm was used for predicting the overlay results with additional compensation. The algorithm was used for analyzing the correctable terms based on current overlay errors.

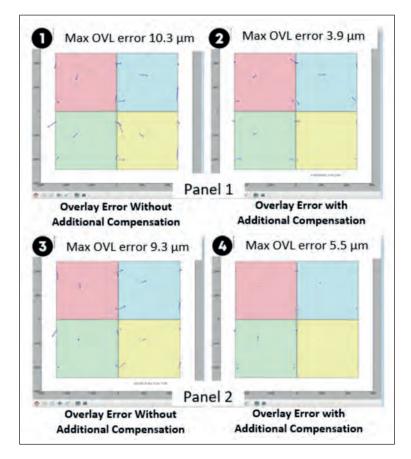

Following the removal of correctable errors, we predicted the final overlay results. Fig 11 shows the overlay results with and without additional compensation. Based on our predictions, overlay error can be reduced by  $4\mu m$  or more.

As a result of heterogeneous integration and highperformance requirements, resolution soon will be down to 1 $\mu$ m in advanced packaging and 3 $\mu$ m in AICS. In addition, the budget for overlay is getting tighter due to the fine resolution process. In AICS,

> Figure 11. The overlay error with and without additional zone compensation. The prediction results indicate additional compensation can reduce overlay error.

| d Threshold | 97%    |            | <b>Vield Threshold</b> | 98%    |            |         |                        |                     |                                       |

|-------------|--------|------------|------------------------|--------|------------|---------|------------------------|---------------------|---------------------------------------|

|             | Yield  | Yield Loss |                        | Yield  | Yield Loss |         | <b>Yield Increased</b> |                     |                                       |

| Layer1      | 97.00% | 3.00%      | Layer1                 | 98.00% | 2.00%      | Layer1  | 1.00%                  |                     |                                       |

| Layer2      | 94.09% | 5.91%      | Layer2                 | 96.04% | 3.96%      | Layer2  | 1.95%                  | and a second second | -                                     |

| Layer3      | 91.27% | 8.73%      | Layer3                 | 94.12% | 5.88%      | Layer3  | 2.85%                  |                     |                                       |

| Layer4      | 88.53% | 11.47%     | Layer4                 | 92.24% | 7.76%      | Layer4  | 3.71%                  |                     |                                       |

| Layer5      | 85.87% | 14.13%     | Layer5                 | 90.39% | 9.61%      | Layer5  | 4.52%                  |                     |                                       |