# **INSIDE**

News Review, Features News Analysis, Profiles Research Review and much more...

# NEW DEVELOPMENTS IN UNDERLAYERS

Extreme ultraviolet lithography is used to pattern the smallest features in advanced semiconductor devices

# ALL ROADS LEAD TO ARIZONA COMMERCE

ACA explain the long-term strategy that has led to Arizona becoming a premier location for the semiconductor industry

# ieloonoemioonbooron.iver

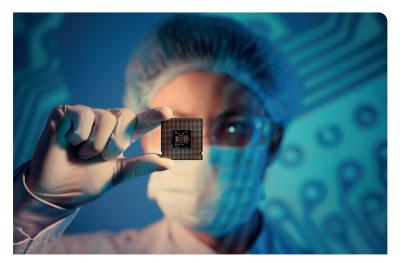

# X-RAY TECHNOLOGY FOR ADVANCED PACKAGING

New developments in micro-CT, sophisticated trajectories, and smart algorithms are delivering a non-destructive inspection method

# FUSION AND HYBRID BONDING FOR HETEROGENEOUS INTEGRATION

1

- Enabling advanced 3D device stacking and chiplet integration for CMOS image sensors, memory and 3D system-on-chip (SoC)

- High-volume production equipment and process technology for Wafer-to-Wafer (W2W) and Die-to-Wafer (D2W) hybrid bonding

- GEMINI® FB Automated Production Wafer Bonding System delivers industry leading alignment accuracy and bonding performance

- Heterogeneous Integration Competence Center™ serving as leadingedge innovation incubator for EVG customers and partners

**GET IN TOUCH** to discuss your manufacturing needs **www.EVGroup.com**

# **VIEWPOINT**

By Phil Alsop, Editor

# Optimism, pessimism and realism – where should the balance lie?

TALK to almost anyone in the semiconductor industry and there's not one voice that seems to dissent from the much heralded and much quoted \$1 trillion, 2030 market expansion roadmap. And yet, talk to anyone about one of the three Ss that cast a significant shadow over the industry right now – Supply Chain, Skills and Sustainability – and there's a little less confidence that the industry is on top of these challenges. Challenges which will have a direct impact on the achievement, or not, of the 2030 target. But only a little less.

Onshoring/reshoring and the various CHIPS Acts are apparently going to vanguish any supply chain problems that are a hangover from the pandemic or the result of ongoing geopolitical tensions – never mind the time and expense to build new fabs.

Hardly a day goes by without some skills or educationrelated news crossing my computer screen, and yet many of these programmes will not produce the semiconductor personnel required to fill the many vacancies which exist now, let alone the new jobs created by expansion, overnight. There are few shortcuts to learning a technology comprehensively – I've been involved in the storage networking industry for 20+ years, but would still not call myself an expert. And, yes, there are different skills required for different jobs within the semiconductor space, but I wonder just how much of a skills shortfall we might encounter between now and...2030. Although Al could just fill some of the gap.

As for sustainability, there's no doubt that technology and the environment can work together for mutual benefit, but to achieve such synchronicity, there does need to

be something of a revolution – we can't slowly, slowly evolve to address climate change. There will need to be step changes and some short-term disruption unless, of course, sustainability ambitions are allowed/continue to take second place to the digital imperative. This summer's weather extremes across the globe would suggest such an approach might be unwise.

In summary, rather than have the extremes of optimism and pessimism when it comes to the industry's future (and, let's face it extremes of any sort tend not work for the majority), maybe it's time for an era of realism? The glass is neither half full nor half empty, but contains just the right amount of liquid, so long as due consideration and balance is given to the three Ss and the impact they will undoubtedly have on the

industry's future.

# Greene Tweed: when it can't fail

For years, the world will tell stories about what happened when we ran out of semiconductors during the pandemic. But industry insiders will remember this time for one more reason. The crunch highlighted the vital importance of some inconspicuous but indispensable component makers that power the intricate machinery of chip manufacturing

18

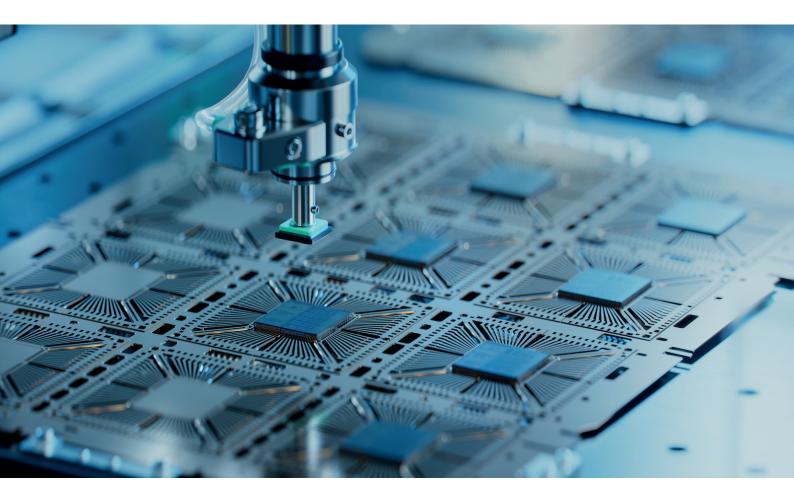

# 14 Industry on track for recovery, but near-term headwinds remain

With sequential IC sales declines beginning to moderate, the global semiconductor industry appears to be nearing the end of a downcycle and is expected to begin to recover in 2024

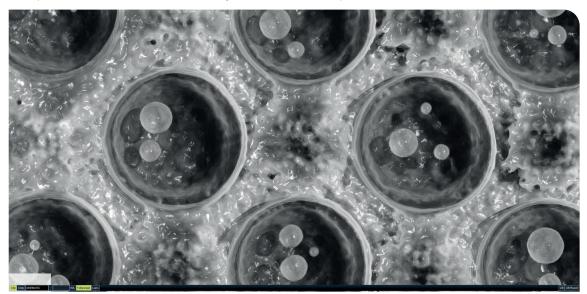

# 24 New developments in underlayers and their role in advancing EUV lithography

Extreme ultraviolet (EUV) lithography is used to pattern the smallest features in advanced semiconductor devices. The demand for smaller devices with more capabilities requires industry innovation in EUV processes and materials.

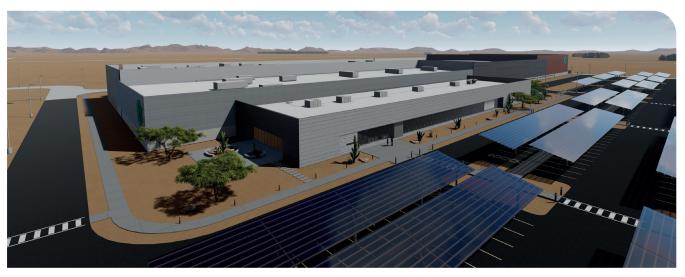

# 32 All roads lead to Arizona

Arizona Commerce Authority's President and CEO, Sandra Watson, explains the long-term strategy that has led to Arizona becoming a premier location for the global semiconductor industry

# 40 Time to celebrate and accelerate diversity, equity and inclusion

Laura Silverstein, Technology Development Integration Engineer at GlobalFoundries' Essex Junction, Vermont facility, was recently recognised as GF's DEI in Inventorship Champion – awarded for hard work in creating a new and more diverse generation of inventors

# 46 Advanced X-ray technology for advanced packaging

While X-ray technology in the semiconductor industry was considered too inaccurate, too slow, and too expensive, new developments in icro-CT, sophisticated trajectories, and smart algorithms are delivering a non-destructive inspection method

# 48 How does mass spectrometry support the demand for semiconductors?

The controlled use of various gases is an important aspect of semiconductor chip manufacturing, which helps to ensure high quality end products

# 50 UK semiconductor strategy: a patent attorney's perspective

The UK Government has published its National Semiconductor Strategy, announcing a 20-year initiative that seeks to establish the UK as a world-leader in semiconductor technologies

# 54 The move from project-centric design to IP-centric design

Geofencing IP must not hinder the effective collaboration of globally distributed teams. The management of project configurations should be carried out predictably and securely

# 58 How to get two-digit savings on the cost of semiconductor test, with device-oriented test architecture

The adoption of testing solutions that help increase throughput and lower the cost of testing is a key factor to keep competitiveness up in the semiconductor industry

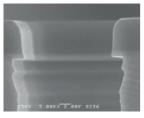

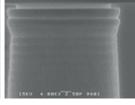

# 60 ULVAC ENVIRO™ plasma ashing systems

With over 40 years of ashing experience, Ulvac has ENVIRO plasma ashing tools for R&D, pilot production and high-volume manufacturing

# 62 Pfeiffer Vacuum HiPace Turbopumps combines high performance with reliability

The Pfeiffer Vacuum HiPace -I series turbo molecular vacuum pumps has been developed specially for the ion implantation processes with the goal to increase the lifetime at the harshest ion implantation process

# **NEWS**

- 06 Chips as currency

- 08 Semiconductor IP unleashes next-gen potential!

- 09 Embarking on a new growth cycle?

- 10 Catalyze Program promises decarbonisation

- 11 Applied Materials and Fraunhofer IPMS launch European Semiconductor-Metrology Technology Hub

- 12 TSMC, Bosch, Infineon, and NXP establish joint venture

Publisher Jackie Cannon Editor Phil Alsop Contributing Editor Richard Stevenson

Sales & Marketing Manager Shehzad Munshi Marketing & Logistics Executive Eve O'Sullivan USA Representatives Tom Brun Brun Media Janice Jenkins

Director of Logistics Sharon Cowley Design & Production Manager Mitch Gaynor jackie.cannon@angelbc.com phil.alsop@angelbc.com richard.stevenson@angelbc.com

shehzad.munshi@angelbc.com eve.osullivan@angelbc.com tbrun@brunmedia.com jjenkins@brunmedia.com

+001724-929-3550 +44 (0)1923 690200 sharon.cowley@angelbc.com +44 (0)1923 690214 mitch.gaynor@angelbc.com

+44 (0)1923 690205

+44 (0)1923 690215 +44 (0)2476 823123

+001724539-2404

Chief Executive Officer Sukhi Bhadal Chief Technical Officer Scott Adams Directors Jackie Cannon, Sharon Cowley sukhi.bhadal@angelbc.com scott.adams@angelbc.com

+44 (0)2476 718970 +44 (0)2476 718970

Published by Angel Business Communications Ltd.

6 Bow Court, Fletchworth Gate, Burnsall Road, Coventry CV5 6SP, UK T: +44 (0)2476 718 970 E: info@angelbc.com

Silicon Semiconductor is published five times a year on a controlled circulation basis. Non-qualifying individuals can subscribe at: \$50.00 per annum (UK), \$60.00 per annum (Europe), \$90 per annum (air mail)(USA). Cover price £4.50. All information herein is believed to be correct at time of going to press. The publisher does not accept responsibility for any errors and omissions. The views expressed in this publication are not necessarily those of the publisher. Every effort has been made to obtain copyright permission for the material contained in this publication. Angel Business Communications Ltd will be happy to acknowledge any copyright oversights in a subsequent issue of the publication. Angel Business Communications Ltd © Copyright 2023. All rights reserved. Contents may not be reproduced in whole or part without the written consent of the publishers. The paper used within this magazine is produced by chain of custody certified manufacturers, guaranteeing sustainable sourcing. US mailing information: Silicon Semiconductor, ISSN 1096-598X, is published 5 times a year by Angel Business Communications Ltd, Unit 6, Bow Court, Fletchworth Gate, Burnsall Rd, Coventry CV5 6SP. UK. Airfreight and mailing in the USA by agent named World Container INC 150-15, 183rd St, Jamaica, NY 11413, USA. Periodicals Postage Paid at Brooklyn, NY 11256. POSTMASTER: Send address changes to Silicon Semiconductor, Air Business Ltd, c/o World Container INC 150-15, 183rd St, Jamaica, NY 11413, USA.

We strive for accuracy in all we publish; readers and contributors are encouraged to contact us if they recognise an error or omission. Once a magazine edition is published [online, in print or both], we do not update previously published articles to align old company names, branding, marketing efforts, taglines, mission statements or other promotional verbiage, images, or logos to newly created or updated names, images, typographic renderings, logos (or similar) when such references/images were accurately stated, rendered or displayed at the time of the original publication. When companies change their names or the images/text used to represent the company, we invite organizations to provide Angel Business Communications with a news release detailing their new business objectives and/or other changes that could impact how customers/prospects might recognise the company, contact the organisation, or engage with them for future commercial enterprise.

Printed by: The Manson Group. ISSN 2050-7798 (Print) ISSN 2050-7801 (Online) © Copyright 2023.

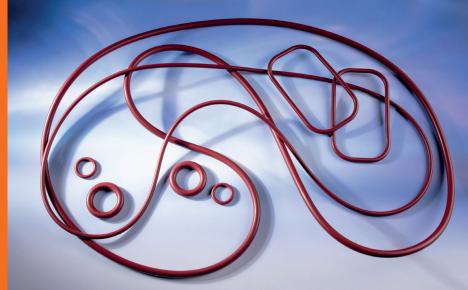

# Chips as currency

Leo Charlton, Technology Analyst at IDTechEx, discusses America, China, and the Al Race.

RUNNING in the background to the more visible, very real wars occurring around the world at present, there is another, economic and industrial in nature. This is a trade war between two principals: the USA and China. The potential consequences of this trade war are incredibly significant to global geopolitics, as how the interaction between the two parties is handled will determine a basis for any future cooperation between the two principals as well as their respective allies.

This trade war is over the production of semiconductor chips, those small pieces of (mainly) electronic circuitry that are found in many modernday devices, from smartphones to televisions, cars to computers. In IDTechEx's recent report "AI Chips 2023-2033", the market research company highlights the part that artificial intelligence (AI) plays in this trade war, where the race for AI supremacy has become a national concern.

# The Shortage, Where Demand Exceeds Supply

But before discussing the role of AI, it is more instructive to start at the beginning or thereabouts. This does not require going so far back in time - only five years, in fact, to 2018. From January of that year, under the presidency of Donald Trump formerly and now President Joe Biden, the US has enforced several layers of restrictions and barriers to trade on China where semiconductors are concerned, each successive layer aiming to plug a hole that the previous layer(s) had left. These restrictions are shown below.

The reasons for these restrictions are multiple, starting with simple economics (where the US wishes to halt China's growing market share in the semiconductor supply chain) before moving onto interwoven concerns such as risk exposure and the use of semiconductors for militaristic purposes.

With regards to geographic risk exposure, since 2020, there has been a global chip shortage, where demand for semiconductor chips has exceeded supply. This shortage exposed US design companies to the risk of relying upon South-East Asia manufacturing capabilities, as lead times elongated to upwards of 3 months by the beginning of the crisis.

A number of complementing factors caused the global chip shortage. Principle among them is the COVID-19 Pandemic, which saw a rise in demand (due to more people working from home and so in need of personal computers) and a fall in supply (due to lockdowns across Asia resulting in plants being shut down). Other factors include the rise of data mining (where GPUs are needed, thus once again increasing demand); a drought that hit Taiwan in 2021, resulting in problems with producing ultra-pure water to clean factories and wafers; fires at several fabrication facilities owned by Asahi Kaseri, Renesas and ASML: and difficulties procuring neon (used for lasers in chip manufacture) due to the Russia-Ukraine War, as Ukraine was responsible for providing more than 90% of the US semiconductor-grade neon.

These events combined would likely be enough for a country such as the US to consider investing in their own production capabilities (where the US Chips and Science Act of 2022 is discussed in more detail in the aforementioned IDTechEx report). But the level of spending on semiconductor imports by China, as well as the blurred line between commercial and military ventures in the country, has led the US to become wary of outfitting a rival economy with the tools to surpass them in key technology areas. This is where Al comes into play.

### Al as a Motivator

In addition to the restrictions presented above, on August 26th, 2022, the US government placed a ban on AMD and Nvidia from exporting chips that can be used to support Al workloads to China. According to an August SEC Filing made by Nvidia, this comes in the form of a license agreement, effective immediately, for any future export to China (including Hong Kong) and Russia of Nvidia's A100 and forthcoming H100 integrated circuits. Any systems that incorporate the A100 and H100 ICs are also covered by the new license requirement, as well as any future integrated circuits that are roughly as advanced as the A100. The filing asserts that the US government has indicated that the new license requirement will address the risk that the covered products may be used in a military capacity by China or Russia. In a similar fashion, a spokesperson for AMD - speaking with Reuters - said that the company had received new license requirements that effectively put a stop on exports of AMD's MI250 AI chips to China.

This information alludes to the fact that the restrictions imposed upon Chinese companies by the US government are not simply a matter of trying to take some control of the supply chain from the APAC region but also a matter of national security. The measures are an attempt by the US to arrest China's Al surge by preventing the type of advanced technologies that are needed for China to realize Al supremacy (a not unfounded concern, as by 2018, China had filed 2.5X more patents in Al technologies than the US). Such is the interwoven aspect of commercial and military endeavors in China that the Biden administration has effectively stopped trying to block military-affiliated exports while retaining commercial exports and the revenue that generates. As such, to quote the Center for Strategic & International Studies, "Highend Al chips can no longer be sold to any entity operating in China, whether that is the Chinese military, a Chinese tech company, or even a US company operating a data center in China".

Al not only promises to be one of the biggest drivers of economic advances within the next quarter century, but for China, Al mastery represents the ability to perfect a model of governance in keeping with existing architectures. The effectiveness of Al models comes largely down to the quality and breadth of the training data set provided. Given that China can collect significant volumes of citizen data, the country is poised to reap the benefits of widespread Al usage.

### **China's Response**

China has - until recently - been rather quiet in the face of these restrictions, although some displeasure was expressed when TSMC (a Taiwanese semiconductor fabricator that accounts for the vast majority of leading-edge node manufacture globally) announced plans to build new fabrication facilities in Arizona, USA, last year. But in July 2023, China struck back, with restrictions placed on the export of Gallium and Germanium, materials that are used in certain semiconductor chip manufacture.

Germanium is used in applications such as thermal imaging cameras, solar panels, and telecommunications, where germanium can be used in photodiodes to convert light signals to electrical ones. Gallium is often paired with arsenic to form gallium arsenide, a compound semiconductor that can operate at higher temperatures and frequencies than silicon. At present, China produces around 98% of the world's gallium and controls around 68% of global refined germanium production in various countries, according to the US Geological Survey. The impact that restrictions on these material exports have on the US and allied countries is not to be downplayed.

### **Outlook**

Both European and Asian delegates alike have warned against these ongoing restrictions by both principals, given that the onus on the shoring up of national interests currently involves punishing the other party concurrently. And the harder that the US pushes against China, the harder that China will lean into plugging money into their own domestic supply chain (and given that in 2021 China spent the equivalent of USD\$432 billion on imported microprocessors, money that they may no longer be able to be spend on imports, China is certainly not short of funding).

As with most countries, China has not looked to develop an isolated, front-to-back domestic semiconductor supply chain to date, as they have had the option to work with superior foreign partners rather than domestic firms that do not meet the same standards; design companies could work with established fabs in Taiwan rather than inferior domestic fabs, and Chinese fabs could buy foreign semiconductor manufacturing equipment (SME) with proven quality. Now that they are cut off from these possibilities, China must look to growing domestic capabilities.

In the short term, this will prove to be very difficult for China. While the country has been stockpiling chips and SMEs in anticipation of these imposed controls (the 7 nm chip produced by SMIC was produced using existing deep ultraviolet (DUV) machines), these resources will eventually run out, and so China must look to develop domestic capabilities if their semiconductor industry isn't to completely dry out, at least in terms of the more advanced node processes. It seems likely that, for

the next few years, China will have to rely on more mature node processes in the creation of new chips.

From a survey of 91 smartphones released from 2020 with Al coprocessing capabilities, the trend is for successively-released models to move to leading-edge nodes. Given that MediaTek, Qualcomm, and Apple are the industry leaders in the smartphone SoC space, it is unlikely that Chinese companies will be able to compete appreciably in this space any time soon. However, where leading-edge nodes are not as necessary to functioning edge devices - such as in matters of security and industrial settings - China may indeed be able to find more traction through the short-term focus on mature node technologies. Source: **IDTechEx**

This being said, it is unlikely that China will have no foreign support at all, at least in terms of SME and components supply. Companies that have a large stake in the Chinese market - such as Zeiss, a German company that supplies mirrors to ASML for their extreme ultraviolet (EUV) lithographic machines, and where China is their fastest growing market - may be unwilling to relinquish revenues generated from China. In an effort to abide by the US export controls, companies may engineer out the US inputs or components in their products such that they can sell these without repercussions in China.

In the longer term, there is cause for cautious optimism for China. Forced to work together in a way that they have not done previously, China's fabs, design companies, and SME firms may form an ecosystem that is not only stronger from the forced collaboration but also more thoroughly isolated from global supply chain disruptions than most other countries (and, in addition, free from US controls). This comes with significant hurdles, but these may be removed or - at the least - lessened should other countries feel the adverse economic effects of being unable to bolster their raw material supply.

The story is far from being finished, but with a projected growth of US\$257.6 billion by 2033 for Al chips alone, there is much to be gained and lost over the next ten years.

# Semiconductor IP unleashes next-gen potential!

Future Market Insight forecasts that the global semiconductor intellectual property (IP) market is poised to achieve a noteworthy milestone by 2033, surpassing a substantial valuation of US\$ 13.10 billion.

WITH A PROJECTED CAGR of 6.7%, this growth trajectory indicates a significant rise from its estimated worth of US\$ 6.83 billion in 2023.

The semiconductor IP market is experiencing growth due to the escalating demand for automation and the rapid adoption of IP Core products in the consumer electronics industry. There is an ever-growing demand for cutting-edge electronic devices, such as smartphones, tablets, and wearable gadgets. The utilization of semiconductor IPs is enhancing the capabilities of IoT products.

The industry is also expanding rapidly because of the increasing prevalence of internet access and the growing utilization of smart connected devices, which further contribute to market growth. Semiconductor IP provides pre-designed and verified components that help these companies accelerate their product development cycles. Semiconductor IP enables companies to cater to market demands swiftly by leveraging ready-made components. Developing semiconductor chips from scratch is a challenging process that requires significant time, effort, and investment. Companies strive to shorten their time-to-market and minimize development costs in today's fast-paced industry. Semiconductor IP addresses these challenges by offering pre-designed IP blocks and subsystems.

The semiconductor industry experiences constant advancements in manufacturing technologies, including smaller process nodes and enhanced integration capabilities. These technological breakthroughs present new design challenges that require specialized semiconductor IP solutions. To meet these demands, semiconductor IP providers develop and offer IP solutions optimized for the latest technological advancements. The semiconductor intellectual

property market thrives due to the growth of emerging markets like automotive electronics, industrial automation, robotics, and smart infrastructure. These emerging markets have unique requirements, such as functional safety, reliability, and power efficiency. Semiconductor IP providers meet these demands by offering application-specific IP solutions. The market growth is also supported by the increasing acceptance of wireless technology-driven devices and the substantial investments made by key players in the development of advanced wireless products.

Furthermore, prominent market players are actively investing in the global expansion of wireless technology devices to meet consumer demands. This surge in wireless technology development and investment creates a heightened demand for IP solutions, including silicon-based design IP, interface IP, and processor IP. The electronics industry is characterized by ever-evolving technology. The semiconductor sector is facing physical limitations in manufacturing existing materials. The detection of patented technology is increasingly challenging due to the integration of patented components within devices. Disentangling these components and determining the ownership of each patent has become difficult. The shrinking feature sizes in current semiconductor fabrication processes require more advanced analysis tools for circuit detection and extraction. This directly influences licensing activities and the value of companies' patent portfolios.

With the proliferation of connected devices and the ever-looming cyber threats, security has become a paramount concern in semiconductor design. Security IP, including encryption/decryption and hardware authentication, is witnessing a substantial surge in demand. IP vendors that prioritize and excel in securityrelated solutions can capitalize on the pressing need to safeguard data and protect systems.

Consolidation has become a prevailing trend in the semiconductor IP market, with larger companies acquiring smaller IP vendors to strengthen their portfolios and expand their market reach. This trend is expected to continue as companies strive to offer comprehensive solutions to their customers. Smaller IP vendors with unique and differentiated offerings present attractive acquisition targets, opening up lucrative opportunities.

### **Key Takeaways**

- The semiconductor intellectual property industry in the United Kingdom is anticipated to rise, exhibiting a CAGR of 5.4% through

- O The United States held a 15.4% share of the global semiconductor intellectual property industry in 2022.

- With a CAGR of 8.2% over the forecast period, India is predicted to develop rapidly in the semiconductor intellectual property industry.

- o In 2022, Japan had a 3.3% share of the semiconductor intellectual property industry globally.

- The semiconductor intellectual property industry in China is expected to flourish, registering a CAGR of 7.6% over the forecast period.

- Germany accounted for 8.1% of the global semiconductor intellectual property industry in 2022.

# **Competitive Landscape in the** Semiconductor Intellectual Property

Key players are engaged in various activities to maintain their competitiveness and drive innovation. They invest significantly in research and development to create advanced and cutting-edge semiconductor IP solutions.

# Embarking on a new growth cycle?

The trillion-dollar semiconductor industry is on the brink of a fresh phase of expansion, driven by advancements in AI, quantum computing, 5G, and specialized applications.

ACCORDING TO Yole Intelligence, semiconductor device revenue peaked in 2022 at US\$573 billion and is expected to retreat 7% to US\$534 billion in 2023. This industry plays a critical role in enabling technological advancements across various sectors, including mobile & consumer, infrastructure, automotive, industrial, and more.

In its new Overview of the Semiconductor Devices Industry 2023 report, the company, part of Yole Group, asserts that the industry has experienced a sustained 6.4% CAGR growth over the past few decades. This industry is driven hard by increasing demand for mobile & consumer electronics, the rise of internet usage such as social media, and the rapid digital transformation of all industries. Integrated circuits are becoming smaller, more powerful, and capable of handling complex tasks, paving the way for new technology advancements such as artificial intelligence, machine learning, and edge computing. This evolution presents numerous opportunities and challenges for leading companies, requiring them to invest massively in R&D and capital expenditure for new foundries to maintain significance in this fast-paced landscape.

Pierre CambouMSc, MBA, Principal Analyst, Yole Intelligence, explains: "The semiconductor device industry relies heavily on global ecosystems, making supply chain resilience and risk mitigation crucial for sustained success. Recent disruptions and geopolitical tensions have highlighted the vulnerabilities of the semiconductor supply chain."

The semiconductor industry is geographically concentrated in a few places, primarily the US, Taiwan, Korea, Japan, Europe, and mainland China. The dominance of US-based semiconductor device companies is

historical; in the last five years, they have maintained a 53% market share. "If we combine all types of semiconductor company business models, i.e., adding the open foundries, OSAT, equipment, and material companies, the market share of US companies drops to 41%", explains Pierre Cambou. "Then, if only the added value is considered, the US share becomes 32%, and this number has been diminishing at a rate of 1 percentage point per year in the last five years."

To go further, Yole Group shared its vision of the industry with ATREG, a company specialized in the disposition of infrastructure-rich advanced technology manufacturing assets, including semiconductor fabs and cleanrooms. Both companies reflected on the fortunes of the global semiconductor industry to date and discuss how the major players need to invest to secure their supply chain and chip capacity.

Indeed, over the last five years, there have been significant changes in the chip-making industry, such as Intel losing its crown to two relatively new contenders, Samsung and TSMC.

Stephen Rothrock, ATREG's CEO & Founder, and Pierre Cambou had the opportunity to debate the state of the global semiconductor industry landscape

and its evolution. In a wide-ranging discussion, they covered the market and its growth prospects, as well as the global ecosystem and how companies can optimize supply. Discover the first part of the discussion here, and the second part, centered around how to ensure chip supply amid growing geopolitical tensions and economic realities affecting semiconductor production, here.

Semiconductor technology trends are no longer single-threaded. At the center of competition is the More Moore node race in the manufacturing process, currently 7nm, 5nm, and 3nm, as well as upcoming smaller nodes. These cutting-edge processes allow for higher transistor density, improved performance, and energy efficiency, though they pose significant challenges regarding development costs, yield rates, and manufacturing complexity.

The semiconductor industry is, therefore, actively exploring innovative solutions through More-than-Moore approaches. And radical innovations are there. Therefore, advanced packaging, photonics integration, quantum computing, and neuromorphic computing will play their role in the expansion of the industry serving a growing diversity of semiconductor device types.

# Catalyze Program promises decarbonisation

Collaboration aims to accelerate the adoption of renewable energy and reduce carbon emissions throughout the global semiconductor value chain.

SCHNEIDER ELECTRIC has launched Catalyze, a new partnership program aimed at accelerating access to renewable energy across the global semiconductor value chain.

Unveiled during SEMICON West 2023, Catalyze is a 'first-of-its kind' program of collaboration among key semiconductor and technology industry leaders to address the supply chain emissions within their industry. The program joins other Schneider Electric supply chain partnership initiatives that seek to leverage the power of supply chain cohorts, including the Energize program for the pharmaceutical industry, and Walmart's Gigaton PPA program.

Intel, one of the world's leading semiconductor design and manufacturing companies, and Applied Materials, Inc., the world's largest semiconductor and display equipment company are the inaugural corporate sponsors of the Catalyze program. Together with Schneider Electric, the companies will encourage suppliers from throughout the semiconductor industry ecosystem to join the Catalyze program and help accelerate the value chain's transition to renewable energy and a low carbon future.

As the global demand for semiconductors in consumer and commercial products increases, the carbon footprint continues to grow, making it imperative for semiconductor industry leaders to collaborate to drive greater use of renewable energy and

achieve a more sustainable path to growth. The shared goal of the Catalyze participants will be to encourage the industry's thousands of suppliers to take bold climate action through decarbonization. This is a challenging task, due to the complexity of the value chain, data availability and reliability, and the difficulties in defining the boundaries of such emissions.

### **Catalyze Program Elements**

The Catalyze program strives to:

- Combine energy purchasing power across the semiconductor value chain to accelerate the deployment of renewable energy projects

- Provide suppliers who may not have the capability on their own – with the opportunity to participate in the market for utility-scale power purchase agreements (PPAs)

- Increase awareness of the availability of renewable energy in specific global regions where the semiconductor value chain is operational, to increase greater adoption

- Continue to assist suppliers who have made commitments to reduce their carbon emissions and/or sign on to this program

- Educate companies in the semiconductor value chain about the importance of developing operational models to use in their supply chain programs – to close net-zero ambition gaps

- Engage thousands of suppliers simultaneously through digital technology platforms, to drive swift and measurable actions in their supply chain decarbonization

- Lead the way for the industry to drive definitive next steps.

Sponsoring companies will collaborate on the development of the program – including identifying focus areas and suppliers – as well as encouraging other semiconductor companies to consider the program for their own value chains

"At Schneider Electric, our purpose is to empower companies to make the most of our energy and resources, bringing progress and sustainability together for everyone. Our mission is to be a digital partner for Sustainability and Efficiency, and the Catalyze partnership program is an excellent example of how companies in key global industries can collaborate to accelerate decarbonization," said Peter Herweck, CEO of Schneider Electric.

"Switching to renewable energy is an important step to reduce greenhouse gas emissions. Intel has achieved 93 per cent renewable electricity in our global operations and remains committed to reaching 100 per cent by 2030," said Intel's Keyvan Esfarjani, Chief Global Operations Officer. "Intel is proud to be a founding member of Catalyze to help remove barriers to choosing greener energy. Ultimately, we want our entire value chain to achieve net-zero as we continue to deliver leading technologies that power our digital world."

"Applied Materials has been working with our suppliers to instill sustainability best practices through our SuCCESS2030 initiative, and we are excited to build on our momentum with the Catalyze program," said Gary Dickerson, President and CEO, Applied Materials. "Promoting closer collaboration across the value chain is key to accelerating carbon emissions reduction. We look forward to working with our partners to drive higher output of clean energy for the global semiconductor industry."

The program will initially focus on suppliers with energy load in specific markets in the semiconductor value chain where renewable energy is currently available, with the intention to expand globally where specific interest and renewable energy market opportunities align.

# Applied Materials and Fraunhofer IPMS launch European Semiconductor- Metrology Tech Hub

New hub will provide state-of-the-art metrology systems to accelerate semiconductor research and enhance development projects with chipmakers and ecosystem partners across Europe, particularly in ICAPS market segments.

Applied Materials and the Fraunhofer Institute for Photonic Microsystems IPMS have revealed a landmark collaboration to create Europe's largest technology hub for semiconductor metrology and process analysis.

To be located at the Center Nanoelectronic Technologies (CNT) of Fraunhofer IPMS in Dresden, the technology hub is situated in the heart of Silicon Saxony, Europe's largest semiconductor cluster. The hub will be equipped with Applied Materials' state-of-the-art eBeam metrology equipment, including its VeritySEM® CD-SEM (critical dimension scanning electron microscope) systems, and staffed by Applied engineers and R&D experts.

"Fraunhofer IPMS and its partners will benefit from access to Applied's industry-leading eBeam metrology systems", said Dr. Benjamin Uhlig-Lilienthal, Head of Business Unit Next Generation Computing at Fraunhofer IPMS. "The new technology hub will offer advanced wafer-level metrology in our industrial CMOS environment with Fraunhofer IPMS's unique ability to loop wafers directly with semiconductor manufacturers."

"Our collaborative metrology hub will accelerate learning cycles and the development of new applications for the Fraunhofer Institute, Applied Materials and our customers and partners in Europe," said James Robson, Corporate Vice President for Applied Materials Europe. "This unique technology hub will have the capability to test and qualify processes on a variety of substrate materials and wafer thicknesses critical to applications across the diverse European semiconductor landscape."

Metrology is crucial in the production of microchips as it enables the accurate measurements needed to precisely monitor and control the quality of individual semiconductor manufacturing steps and sequences. Chipmakers use metrology equipment at critical points to help validate physical and electrical characteristics and maintain target yields.

# TSMC, Bosch, Infineon, and NXP establish joint venture

Plans to bring advanced semiconductor manufacturing to Europe.

TSMC, Robert Bosch GmbH, Infineon Technologies and NXP Semiconductors plan to jointly invest in European Semiconductor Manufacturing Company (ESMC) GmbH, in Dresden, Germany to provide advanced semiconductor manufacturing services. ESMC marks a significant step towards construction of a 300mm fab to support the future capacity needs of the fastgrowing automotive and industrial sectors, with the final investment decision pending confirmation of the level of public funding for this project.

The project is planned under the framework of the European Chips Act. The planned fab is expected to have a monthly production capacity of 40,000 300mm (12-inch) wafers on TSMC's 28/22 nanometer planar CMOS and 16/12 nanometer FinFET process technology, further strengthening Europe's semiconductor manufacturing ecosystem with advanced FinFET transistor technology and creating about 2,000 direct high-tech professional jobs. ESMC aims to begin construction of the fab in the second half of 2024 with production targeted to begin by the end of 2027.

The planned joint venture will be 70% owned by TSMC, with Bosch, Infineon, and NXP each holding 10% equity stake, subject to regulatory approvals and other conditions. Total investments are expected to exceed 10 billion euros consisting of equity injection, debt borrowing, and strong support from the European Union and German government. The fab will be operated by TSMC.

"This investment in Dresden demonstrates TSMC's commitment to serving our customers' strategic capacity and technology needs, and we are excited at this opportunity to deepen our long-standing partnership with Bosch, Infineon, and NXP," said Dr. CC Wei, Chief Executive Officer of TSMC. "Europe is a highly promising place for semiconductor innovation, particularly in the automotive and industrial fields, and we look forward to bringing those innovations to life on our advanced silicon technology with the talent in Europe."

Dr. Stefan Hartung, chairman of the Bosch board of management: "Semiconductors are not only a crucial success factor for Bosch. Their reliable availability is also of great importance for the success of the global automotive industry. Apart from continuously expanding our own manufacturing

facilities, we further secure our supply chains as an automotive supplier through close cooperation with our partners. With TSMC, we are pleased to gain a global innovation leader to strengthen the semiconductor ecosystem in the direct vicinity of our semiconductor plant in Dresden."

"Our joint investment is an important milestone to bolster the European semiconductor ecosystem. With this, Dresden is strengthening its position as one of the world's most important semiconductor hubs that is already home to Infineon's largest frontend site," said Jochen Hanebeck, CEO of Infineon Technologies.

"Infineon will use the new capacity to serve the growing demand particularly of its European customers, especially in automotive and IoT. The advanced capabilities will provide a basis for developing innovative technologies, products and solutions to address the global challenges of decarbonization and digitalisation."

"NXP is very committed to strengthening innovation and supply chain resilience in Europe," said Kurt Sievers, President and CEO of NXP Semiconductors.

# Dedicated webinars for the silicon semiconductor industry

Using our 30+ years' experience in B2B vertical technical markets, and as the publisher of Silicon Semiconductor, we offer effective webinars, ZOOM interview and virtual events. We help you get your message, to your desired audience, by marketing to over 55,000 silicon semiconductor professionals.

Find out how Angel Webinar can help you organise and run a webinar within the silicon semiconductor industry.

Reach Educate Influence

- Brand Awareness

- Lead Generation

- Thought Leadership

Contact: Jackie Cannon jackie.cannon@angelbc.com +44 (0)1923 690205

# **Connecting Semiconductors and Electronics**

### **About SEMI:**

SEMI connects more than 2,500 member companies and 1.3 million professionals worldwide to advance the technology and business of electronics design and manufacturing. The breadth and depth of our events, programs and services help members accelerate innovation and collaboration on the toughest challenges to growth.

WORKFORCE DEVELOPMENT

> **Global** ADVOCACY

> > Sustainability

1000+ STANDARDS

THOUGHT LEADERSHIP

**TECH**COMMUNITIES

**SEMI**UNIVERSITY

# Industry on track for recovery, but near-term headwinds remain

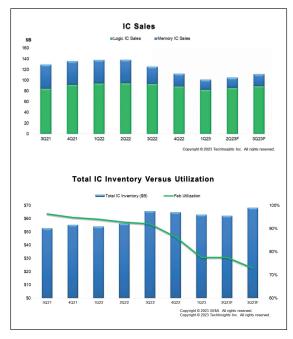

With sequential IC sales declines beginning to moderate, the global semiconductor industry appears to be nearing the end of a downcycle and is expected to begin to recover in 2024, SEMI, in partnership with TechInsights, reported in the Semiconductor Manufacturing Monitor.

In Q3 2023, electronics sales are projected to post healthy quarter-on-quarter growth of 10%, while memory IC sales are expected to log double-digit growth for the first time since the downturn started in Q3 2022. Logic IC sales are predicted to remain stable and improve as demand gradually recovers.

Headwinds will continue for the semiconductor manufacturing sector in the second half of the year, SEMI and TechInsights reported. Drawdowns of high inventory at integrated device manufacturer (IDM) and fabless companies will continue to suppress fab utilization rates to much lower levels than those in the first half of 2023. The weakness is projected to extend declines in capital equipment billings and silicon shipments for the rest of the

year despite stable results in the first half of 2023. Market indicators point to a semiconductor industry bottoming at the end of the first half of 2023, and the industry has since started a recovery, setting the stage for continued growth in 2024. All segments are projected to log year-over-year increases in 2024, with electronics sales surpassing its 2022 peak.

"The slower-than-expected demand recovery will delay the normalization of inventory until the end of 2023, later than we previously anticipated, leading to additional reductions in fab utilization rates in the short term," said Clark Tseng, Senior Director of Market Intelligence at SEMI. "However, recent trends suggest that the worst is over for ICs. We anticipate

> Sources: SEMI (www.semi.org) and TechInsights (www.techinsights.com), August 2023

semiconductor manufacturing will bottom in Q1 2024."

"While semiconductor markets have seen a sharp downturn the last four quarters, equipment sales and fab construction have been performing much better than expected," said Boris Metodiev, Director of Market Analysis at Techlnsights. "Government incentives have been driving new fab projects and strong backlogs have helped equipment sales." The Semiconductor Manufacturing Monitor (SMM) report provides end-to-end data on the worldwide semiconductor manufacturing industry. The report highlights key trends based on industry indicators including capital equipment, fab capacity, and semiconductor and electronics sales, and includes a capital equipment market forecast.

The SMM report also contains two years of quarterly data and a one-quarter outlook for the semiconductor manufacturing supply chain including leading IDM, fabless, foundry, and OSAT companies. An SMM subscription includes quarterly reports.

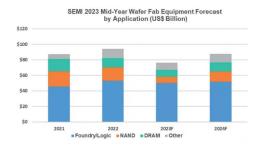

# Equipment sales to hit \$87 billion in 2023

Global sales of total semiconductor manufacturing equipment by original equipment manufacturers next year are forecast to bounce back from a projected contraction of 18.6% to \$87.4 billion in 2023 following the industry record of \$107.4 billion in 2022, SEMI announced today in its Mid-Year Total Semiconductor Equipment Forecast – OEM Perspective at SEMICON West 2023. The expected

2024 recovery – to \$100 billion – will be driven by both the front-end and back-end segments. "Despite current headwinds, the semiconductor equipment market is set to see a strong rebound in 2024 after an adjustment in 2023 following a historic multi-year run," said Ajit Manocha, SEMI president and CEO. "Projections for robust long-term growth driven by high-performance computing and ubiquitous connectivity remain intact."

Semiconductor Equipment Sales by Segment Sales of wafer fab equipment, which includes wafer processing, fab facilities and mask/reticle equipment, are projected to decrease 18.8% to \$76.4 billion in 2023 – more than the 16.8% decline predicted by SEMI in the 2022 year-end forecast. The wafer fab equipment segment is projected to account for the bulk of the recovery to \$100 billion in 2024, generating \$87.8 billion in sales, a 14.8% increase.

The 2022 decline in back-end equipment segment sales is expected to continue in 2023 due to challenging macroeconomic conditions and softening semiconductor demand. Semiconductor test equipment market sales are projected to contract by 15% to \$6.4 billion in 2023, while assembly and packaging equipment sales are expected to drop by 20.5% to \$4.6 billion in the same year. However, the test equipment and assembly and packaging equipment segments are expected to expand by 7.9% and 16.4%, respectively, in 2024.

➤ Source: SEMI July 2023, Equipment Market Data Subscription

> Source: **SEMI July** 2023, Equipment Market Data Subscription

#### Silicon Area Shipment Trends - Semiconductor Applications Only Millions of Square Inches 1Q 2022 2Q 2022 3Q 2022 4Q 2022 1Q 2023 2Q 2023 Total 3,679 3,704 3,741 3,589 3,265 3,331

Data cited in this release include polished silicon wafers, including those used as virgin test wafers, as well as epitaxial silicon wafers, and non-polished silicon wafers shipped by the wafer manufacturers to end users.

## Semiconductor equipment sales by application

Equipment sales for foundry and logic applications, accounting for more than half of total wafer fab equipment receipts, are expected to drop 6% yearover-year to \$50.1 billion in 2023, reflecting softer end-market conditions. Demand for leading-edge foundry and logic in 2023 is expected to remain stable, with a slight softening balanced out by a rise in spending on mature nodes. Foundry and logic investments are projected to increase 3% in 2024. DRAM equipment sales are expected to fall 28% to \$8.8 billion in 2023 due to continuing weak consumer and enterprise demand for memory and storage but rebound 31% to \$11.6 billion in 2024. NAND equipment sales are projected to decrease 51% to \$8.4 billion in 2023 and surge 59% to \$13.3 billion in 2024.

### Semiconductor equipment region sales

China, Taiwan and Korea are expected to remain the top three destinations for equipment spending in 2023 and 2024. While Taiwan is forecast to regain the lead in 2023, China is projected to return to the top position in 2024. Equipment spending for most regions tracked is expected to fall in 2023 before returning to growth in 2024. TThe SEMI forecast is based on collective input from top equipment suppliers, the SEMI Worldwide Semiconductor Equipment Market Statistics (WWSEMS) data collection program and the industry-recognized SEMI World Fab Forecast database. The Equipment Market Data Subscription (EMDS) from SEMI provides comprehensive market data for the global semiconductor equipment market.

### Worldwide silicon wafer shipments increase

Worldwide silicon wafer shipments increased 2.0% guarter-over-guarter to 3,331 million square inches in the second quarter of 2023, down 10.1% from the 3,704 million square inches recorded during the same quarter last year, the SEMI Silicon Manufacturers Group (SMG) reported in its quarterly analysis of the silicon wafer industry. "The semiconductor industry continues to work through excess inventory in various market segments, necessitating that fabs operate below full capacity," said Anna-Riikka Vuorikari-Antikainen, Chairman of

SEMI SMG and Chief Commercial Officer at Okmetic. "As a result, silicon wafer shipments are lagging their 2022 peak. Second-quarter wafer shipments held steady quarter-on-quarter with 300mm showing quarterly growth among all wafer sizes."

# Silicon area shipment trends – Semiconductor applications only

Silicon wafers are the fundamental building material for the majority of semiconductors, which are vital components of all electronic devices. The highly engineered thin disks are produced in diameters of up to 12 inches and serve as the substrate material on which most semiconductors are fabricated. The SMG is a sub-committee of the SEMI Electronic Materials Group (EMG) and is open to SEMI members involved in manufacturing polycrystalline silicon, monocrystalline silicon or silicon wafers (e.g., as cut, polished, epi). The SMG facilitates collective efforts on issues related to the silicon industry including the development of market information and statistics about the silicon industry and the semiconductor market.

### SEMICON West 2024 dates

SEMI has announced that SEMICON West 2024 at the Moscone Center in San Francisco will be held July 9-11.

SEMICON West is moving to Phoenix for a five-year annual rotation and shifting from its longstanding July event dates to October beginning in 2025. The exhibition and conference will be held again in Arizona in 2027 and 2029, with all three appearances at the Phoenix Convention Center. Phoenix will first host SEMICON West Oct. 7-9, 2025. The event will continue to be held at the Moscone Center in San Francisco on the alternating years and over the long term.

"We look forward to bringing the remarkable excitement pervasive at SEMICON West 2023 to next year's exhibition and conference," said Joe Stockunas, President of SEMI Americas. "Semiconductor industry growth, sustainability and talent will remain major themes at SEMICON West 2024 as we again provide a stage for critical insights and conversations key for the industry to flourish in the years to come."

# siconnex

GREEN GOALS.

YELLOW SOLUTIONS.

# TRANS VISION VIS

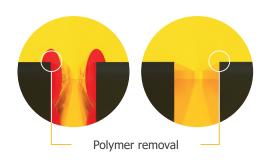

# PERC™ PROCESS FOR SUSTAINABLE POLYMER REMOVAL

perc<sup>™</sup> enables simple and flexible polymer removal. Due to its unique process flexibility, it is used to remove any kind of polymer residues after dry etching processes like metal-, oxide-, silicon- or VIA etching.

The perc<sup>™</sup> function is based on inline spiking technology. DI water applied with a very small quantity of acid/alkaline-based media is used to clean the wafer surface. Unique spiking and mixing technologies guarantee accurate concentration and flow for each wafer.

Polymer removal

Throughput increase

Reduction of chemical consumption

Reduction of waste treatment

Elimination of solvents

Reduction of costs per wafer

# Greene Tweed: When it can't fail

For years, the world will tell stories about what happened when we ran out of semiconductors during the pandemic. But industry insiders will remember this time for one more reason. The crunch highlighted the vital importance of some inconspicuous but indispensable component makers that power the intricate machinery of chip manufacturing.

By Nick McNeal, Director Semiconductor Strategy, Greene Tweed; Thyag Sadasiwan, Director Chemraz®, Greene Tweed; and Pragati Verma, Content Specialist, Greene Tweed

## Greene Tweed's Chemraz® FFKM seals: unsung heroes

GREENE TWEED is a remarkable example of such a company working behind the scenes to manufacture sealing solutions that outperform and outlast in the world's harshest semiconductor manufacturing applications. For 160 years, we've equipped critical sectors with materials and engineered components that deliver certainty for their crucial operations.

Our Perfluoroelastomer (FFKM) Chemraz® o-rings and sealing solutions, for instance, meet the critical demands of modern chip fabrication by preventing contamination while withstanding aggressive chemicals and extremely high temperatures.

For decades, we have been at the forefront of the complex FFKM production process. These highperformance materials need specific ingredients. So, disruptions can occur even if a single ingredient is in short supply. An unexpected and tumultuous industry-wide supply crunch gripped several FFKM ingredients due to several factors, including pandemic lockdowns and geopolitical events such as the Russia-Ukraine war.

The situation was exacerbated by an announcement from a major supplier that it will stop producing all fluoropolymers, fluorinated fluids, and certain additive products by the end of 2025. The disruption could not come at a worse time - It coincided with a global surge in demand for

chips. FFKM material was in short supply at the very moment when semiconductor manufacturers needed it to go into overdrive. Soon, the FFKM industry found itself caught in the middle of a perfect storm, where supply delays could cause serious impediments to semiconductor availability and the resultant economic recovery.

It's not hard to see how these disruptions have made chipmakers acutely aware of how dependent the semiconductor industry is on FFKM seals. What's more, the criticality of FFKM sealing solutions will only grow as chipmakers pack more

and tinier transistors in their chips and turn to more demanding processes that rely on ultraclean processing. Greene Tweed was the first sealing solutions company to use cleanroom manufacturing in the US and we intimately understand the significance of ultraclean operations in the semiconductor industry.

We understand that our FFKM Chemraz® sealing solutions are critical to perform in the harshest environments of modern semiconductor fabrication processes and improve uptime, reduce contamination, and boost wafer yield.

|          |                 | Plasma<br>Performance                              |                                    | Maximum         |          |

|----------|-----------------|----------------------------------------------------|------------------------------------|-----------------|----------|

| ©<br>N   | Greene<br>Tweed | O <sub>2</sub><br>Etch Rate<br>(% wt. loss, 90 min | O <sub>2</sub><br>Remote<br>Plasma | Temperature (C) | Cracking |

|          | E38             | direct exposure)                                   | % wt. loss)                        | 260             | +        |

| <u>a</u> | 629             | 1.739                                              | 0.074                              | 260             | +        |

| [        | 657             | 0.417                                              | 0.053                              | 280             | ++       |

| he       | XPE             | 0.570                                              | 0.026                              | 280             | +++      |

| Ö        | <b>G57</b>      | 0.670                                              | 0.089                              | 300             | ++       |

<sup>➤</sup> Chemraz® FFKM sealing solutions are known for their exceptional resistance to extreme temperatures, chemicals, and plasma environments.

# All your semiconductor sealing questions, answered

DO YOU need an elastomer o-ring or sealing solution built to withstand aggressive liquids, gases, and plasma at extreme temperatures found in the harshest semiconductor applications? Here are answers to the key sealing questions facing semiconductor manufacturers:

# What kind of seals work best for semiconductor manufacturing processes?

Perfluoroelastomer (or FFKM) sealing material, known for its exceptional resistance to aggressive chemicals, extreme temperatures, and plasma environments, is ideal for a manufacturing process as aggressive as semiconductor fabrication.

Greene Tweed offers Chemraz® sealing solutions, known for their exceptional resistance to extreme temperatures, chemicals, and plasma environments.

# What sets Greene Tweed's Chemraz® sealing solutions apart?

At Greene Tweed, we take pride in our Chemraz® sealing solutions that are engineered to outperform and outlast in the world's harshest environments. For 160 years, we've equipped critical sectors, including the semiconductor industry, with materials and engineered components that perform – no excuses, no exceptions.

With the broadest temperature range and unmatched chemical resistance among all elastomeric materials, Chemraz® is the prime choice for the most challenging semiconductor applications. Our superior quality, precision engineering and customizability result in less downtime, and higher wafer processing yields.

# What kind of semiconductor manufacturing processes benefit from Greene Tweed's Chemraz® sealing solutions?

Chemraz® FFKM sealing solutions are ideal for a wide range of semiconductor equipment such as:

- Conductor Etch

- O Dielectric Etch

- PECVD

- ALD

- RTP

- Wet Cleans

- Chamber Seals

- Slit Valve and BSVs

- Pendulum and Gate Valves

- Eseals

- Chemical Delivery

# Can Greene Tweed's sealing solutions withstand aggressive cleaning and etching chemistries?

Absolutely! Chemraz® exhibits exceptional chemical resistance, making it highly compatible with aggressive cleaning and etching chemistries used in semiconductor fabrication. It remains stable even when exposed to harsh plasma environments and reactive chemicals, ensuring optimal performance and longevity.

# Can Greene Tweed customize seals to suit specific semiconductor applications?

Yes, at Greene Tweed, we offer a range of sealing solutions that can be tailored to meet your specific requirements. Our engineering team works closely with semiconductor manufacturers to design custom seals that match equipment specifications and deliver optimized performance.

# I want to implement Greene Tweed's latest sealing solutions in my semiconductor application. How can I start the process?

To explore the benefits of FFKM sealing solutions tailored to your semiconductor equipment, reach out to our expert team at Greene Tweed. Our engineers are ready to talk about your specifications and provide technical guidance.

We'll keep working to iterate, improve, and deliver high-quality sealing solutions to elevate your semiconductor manufacturing process. As a global leader in seals based on FFKM elastomers, we at Greene Tweed know that second-best seals aren't good enough in an industry as complex and challenging as semiconductor manufacturing. So, we decided to take action to minimize the impact of future disruptions on our customers' ability to manufacture chips

# Where second best isn't good enough

Cut to 2023: While the semiconductor industry is currently experiencing a short-term cyclical downturn, the next year looks brighter with predictions pointing towards an upturn in the second half. These boomand-bust cycles are bound to intensify uncertainty and create demand-supply imbalances. In these uncertain times, even a downturn cannot eliminate the potential for supply disruptions leading to tightness and a resultant surge in demand. As a global leader in seals based on FFKM elastomers, we at Greene Tweed know that second-best seals aren't good enough in an industry as complex and challenging as semiconductor manufacturing. So, we decided to take action to minimize the impact of future disruptions on our customers' ability to manufacture chips. We realize that the dynamic landscape of the semiconductor industry demands strategic planning and foresight and are proactively

taking measures to create robust Business Continuity Plans (BCPs) and ensure a steady and uninterrupted supply. We began by conducting comprehensive risk assessments, identifying vulnerabilities, and developing contingency plans to mitigate potential disruptions. Following the deep exploration, Greene Tweed has rolled out four major initiatives to help us navigate this turbulent terrain, circumvent future disruptions, and secure a regular supply to help drive our semiconductor customers' continued growth and success:

### Secure FFKM polymer supply

Our first step at Greene Tweed was to build strategic stockpiles of critical raw materials to prepare for the anticipated upturn. Securing raw materials is very important, but it's just one aspect of our multifaceted approach to ensure supply. Greene Tweed scientists are innovating to develop new products and reformulate existing

# COVER STORY I GREENE TWEED

ones to prepare for the ever-evolving regulations and shifting market dynamics. We are proactively identifying risks from ingredients that are supply constrained and mitigating them with more readily available feedstock materials. At the same time, we are working with our supply chain partners to determine the potential impact of government reviews and supply crunch on their materials, chemicals, and production processes. Simultaneously, we are working with our customers to develop and validate alternate compounds with superior technologies and significant benefits.

### O Diversify supply chain

While reformulating and developing new products, we are taking proactive measures to diversify our supply chain and reduce the risk of overreliance on a single supplier or region. We realize that setting up multiple FFKM factories is too capital intensive and might not be feasible for our suppliers. That's why we are leveraging multiple suppliers to build a resilient and adaptable supply chain that is better equipped to navigate the challenges of an ever-evolving semiconductor landscape. To do this, we are developing equivalent products that serve as alternatives to the original ones. We carefully select compounds and source raw materials for two equivalent products from different suppliers located in separate countries. For example, we are augmenting our supply chain by adding Chemraz® G57 that is equivalent to Chemraz® 657 and provides excellent plasma resistance in a variety of aggressive chemical environments.

### Expand manufacturing operations

We are also spreading our manufacturing footprint, strategically setting up factories in new locations across the world to help bring supply chain stability to the semiconductor customers. The latest is our upcoming manufacturing facility in Cheongju-si, Chungcheongbuk-do, Korea. Expected to be ready by mid-next year, it will initially be dedicated to our highest-performing elastomer Chemraz® product line that was specifically formulated for semiconductor applications. The state-of-the-art factory will not only increase our production capacity but also enhance flexibility and resilience in our supply chains. By decentralizing production and sourcing, we will be better equipped to manage supply crunches, overcome production bottlenecks, and maintain consistent deliveries to customers.

### Boost operational capacity

In tandem with the expansion of manufacturing capacity, we have significantly stepped-up our inventory optimization by building the right inventory to meet future demand within industry leading lead times. Coupled with our new facility, this will help us grow our capacity and capability to better support the global demand for our products and bring enhanced supply chain stability to the semiconductor industry.

### Our lead times: back on track

The results of building supply resiliency are already evident. We have been able to restore standard pre-disruption level lead times that our customers saw before geopolitical and regulatory events cause unprecedented supply chain issues - it's a testament to our resilience, adaptability, and customer-centric approach.

As we continue to forge ahead on this transformative journey, we are committed to keeping customer satisfaction and supply chain stability at the core of everything we do. We understand that our high-performance Chemraz® seals do what other seals can't do and timely delivery of our products is essential for our customers' success. Together with our customers and partners, we will continue to shape a resilient future that thrives on innovation and a custom collaborative approach that delivers certainty for our customers' crucial operations.

We understand that our high-performance Chemraz® seals do what other seals can't do and timely delivery of our products is essential for our customers' success. Together with our customers and partners, we will continue to shape a resilient future that thrives on innovation and a custom collaborative approach that delivers certainty for our customers' crucial operations.

Not every discussion is a battle...

- Based around a hot topic for your company, this 60-minute recorded, moderated ZOOM roundtable would be a platform for debate and discussion

- Moderated by an editor, Phil Alsop, this can include 3 speakers

- Questions prepared and shared in advance

- There would be an opportunity to view and edit out any unflattering bloopers

# This event would be publicised for 4 weeks through all our mediums including:

- A banner on the Silicon Semiconductor homepage for 8 weeks

- 4x weekly dedicated HTMLs

- 4x news pieces which would also appear on the weekly e-newsletters

- Promoted through our social media platforms for 8 weeks (pre and post event)

- Available as an on-demand asset through all mediums

- All registered attendees' details would be made available to you

Cost: €5995

Contact: Jackie Cannon at jackie.cannon@angelbc.com

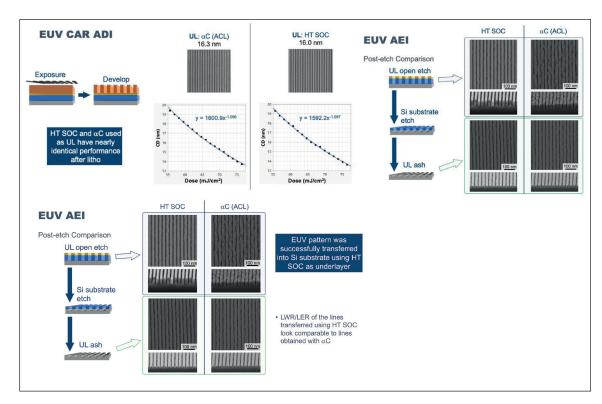

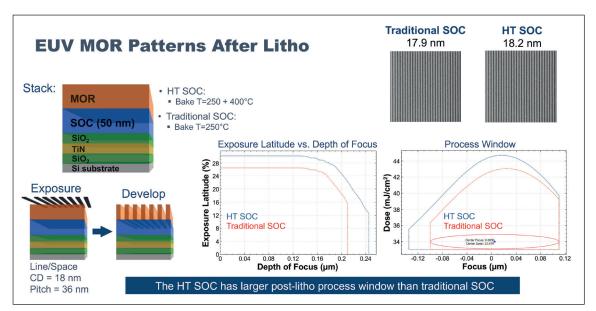

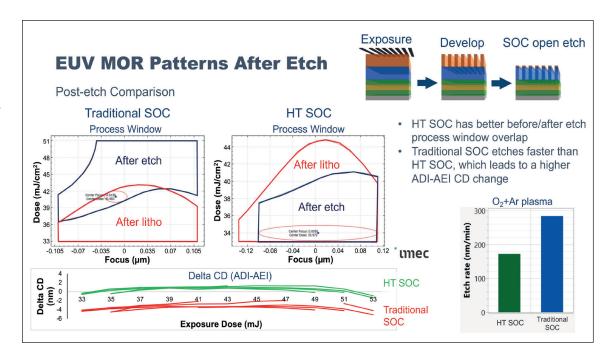

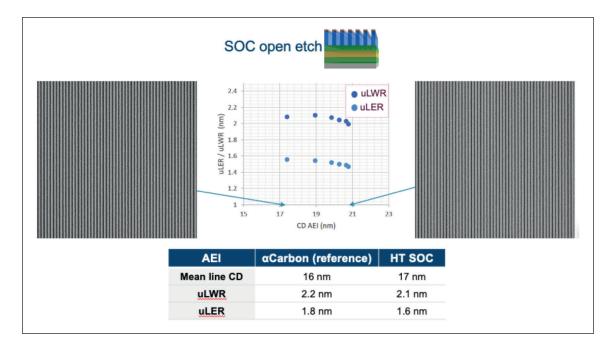

# New developments in underlayers and their role in advancing EUV lithography

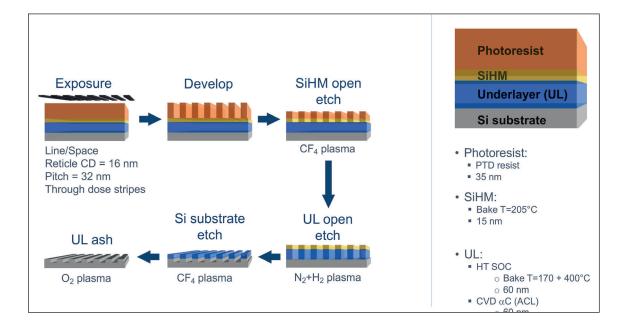

Extreme ultraviolet (EUV) lithography is used to pattern the smallest features in advanced semiconductor devices. The demand for smaller devices with more capabilities requires industry innovation in EUV processes and materials.

By Joyce Lowes, Director, Emerging Materials Technology, Corporate Research and Development, Brewer Scientific.

ADDITIONALLY, EUV plays a critical role in the evolution of technology and enables the continuous advancement of the semiconductor roadmap, as it provides the capabilities of higher processing power while using less energy and providing higher performance. However, one of the biggest challenges facing EUV lithography is material requirements, recognizing the critical role underlayers play in the patterning of EUV lithography.

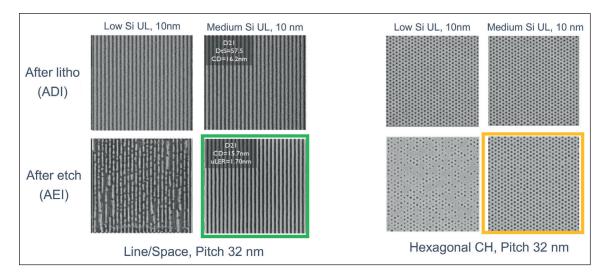

Unlike bottom antireflective coatings (BARCs), reflectivity control is no longer the driving mechanism for underlayers. Now, underlayers are necessary to support resist performance and to enable scaling of the process. Underlayers that offer optimum adhesion while ensuring minimization of pattern defects are key. Beyond just lithography performance, in cases where the underlayers also serve a dual purpose as an etch mask, they need to offer etch resistance beyond their predecessors and at a much reduced thickness.

Brewer Science introduced our first EUV underlayer material in 2010, E2Stack® AL412 material, which serves as the standard for EUV tool qualification and

resist screenings. This material delivers excellent adhesion and resist compatibility for lithography. Since then, Brewer Science has introduced a variety of material approaches that offer process and defectivity improvements for traditional EUV lithography schemes. These materials demonstrate improved process window, depth of focus, and LWR/CDU, and can be used across a variety of EUV patterning applications.

### **Underlayer Challenges for EUV**

With the adoption of EUV into more layers and the introduction of high-NA tools quickly approaching, the minimum pitch as defined in DRAM and Logic roadmaps requires photoresist thickness continue scaling down, reaching as thin as 15 nm in the next few years. As expected, the underlying film stack will need to scale as well, all while maintaining existing properties and often doing more.

The industry has already moved from traditional 30 - 80 nm deep UV (248 nm or 193 nm) BARC layers down to 5 - 20 nm EUV underlayers. This thinning-down trend will continue (likely towards 1 – 10 nm) as high NA becomes a reality. Meanwhile, to be able to print ever-shrinking defect-free EUV features

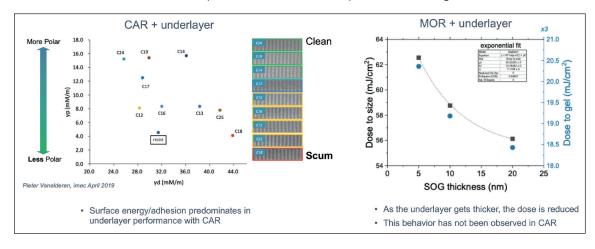

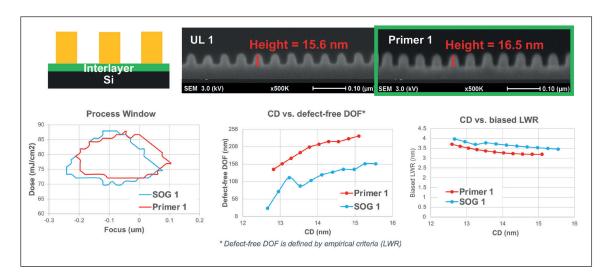

Figure 1.

Comparison

of underlayer

properties on

traditional CAR

and MOR.

with the lowest possible dose while maintaining reasonable process window, more functional demands are being added to the underlayer requirement list. Just to name a few, the underlayer needs to provide enough adhesion to prevent pattern collapse but not too much to cause scum, it needs to be as thin as possible but at the same time provide the required etch selectivity uniformly across a 12-inch wafer, and it is also called on to help reduce the dose but without too much chemical exchange with the resist. Overall, an optimum EUV underlayer design needs to have at least three main challenges in mind: enhancing the lithography performance with compatibility to a wide range of resist vendors and types, thickness and chemical homogeneity control to minimize both coating defects and stochastic impact to the imaging/ developing process, and the perfect etch selectivity for pattern transfer demanded by different resist types and integration schemes.

Obviously, lithography performance needs to be perfect. When films are at a normal thickness, bulk properties have large influence over performance. However, with thin films, those bulk properties are less significant, since there really is no bulk left and behavior at the interface is more important. All of the desired properties need to be packed at the interface. Adhesion to and interaction with the resist at the interface needs to be optimized to get the right balance. And, unlike traditional ArF or KrF resists, each EUV resist from each vendor has its own unique chemical designs and working mechanisms, so underlayers need to be adjusted for each different resist formulation. More preferably, the underlayer needs to be "universal" to be compatible with all the resists.

Reducing the thickness in itself is a critical challenge. At 5 nm, control of uniformity across the wafer is tricky, with the film sensitive to many factors in the tool, such as exhaust and hotplate uniformity. Compounding that as well are chemical effects, such as distribution of components and their effect on crosslinking rate. Even though the

thin films are at very low solids content, defectivity reduction does not get easier. Tiny defects that were previously tolerable or even ignorable compared to the rest of the bulk film now become dominant and problematic at the interface. These defects now may start becoming larger than the thickness of film or CD of the features and so become more impactful. Traditional methods that were used to remove larger defects are running into a wall in the EUV era where everything shrinks in size and thickness, requiring more sophisticated filtration and other techniques to purify the materials, and more innovative metrologies to even detect the defects.

Lastly, there is pattern transfer. These ultrathin underlayer films will need to deliver at the same but more likely at a better level of etch selectivity than their much thicker precedents. This applies to both silicon- and carbon-based films. Depending on the integration scheme and etch setup, faster or slower etch rates are prescribed for the EUV underlayers, but sometime the underlayer needs to be both faster and slower (under different etching gases), all at a thickness as thin as  $1-10\,\mathrm{nm}$ .

### Underlayer Effects on CAR and MOR

In figure 1, two examples illustrating the role the underlayers play in EUV with a traditional chemically amplified resist (CAR) and metal oxide resist (MOR) are shown. With CAR, one factor at play for performance is surface energy. With this combination, as seen on the left, underlayers with various polarities were screened. As the underlayer became more polar, this change leads to less scumming/cleaner profiles. At lower polarity, scumming became more evident, likely due to too much interaction of the exposed resist and the underlayer. But, too much of a good thing is sometimes bad, so there needs to be a balance to avoid too little adhesion and causing collapse.

With the MOR, surface energy is important, and the collapse/adhesion trends are similar to CAR. Some impact on thickness versus dose has been seen, which was not observed with CAR. When

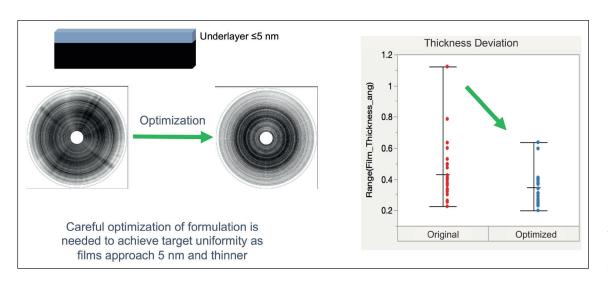

Figure 2. Thickness uniformity studies.

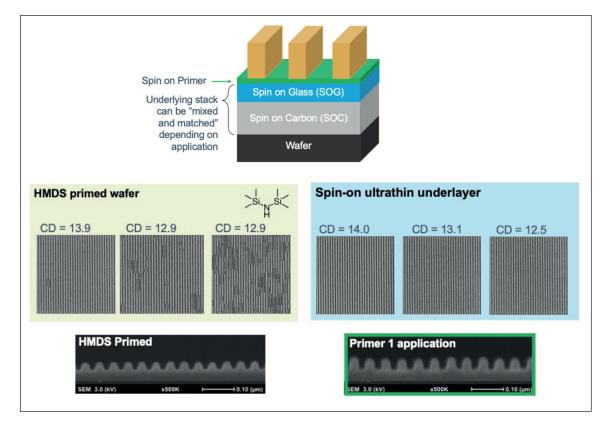

> Figure 3.

Primer

concept and

comparison of

HMDS priming

vs spin-on

primer film.

the underlayer became thinner, the resist required higher dose, which could be explained through some chemical interactions.

# Tackling Thickness Issues for Extreme Uniformity

Coating uniformity at EUV dimensions requires extreme uniformity. At a normal thickness, for an ArF underlayer, thickness variation targets can be as low as 5 angstroms. At 5 nm, that same variation is still expected. Unfortunately, it's not as simple as repurposing a 30-nm film by diluting it and have it perform the same. Striations as seen in Figure 2 with the radial striations in the haze image from an SP5 on the left, and thickness deviation from center to edge are common problems that occur when the film is thinned, causing process window errors,

CD mis-uniformity and other issues. To eliminate striations or to reduce thickness uniformity down to target, careful optimization of the formulation is necessary. And since all underlayers are not created equal, when the formulation changes for better adhesion, slower etch rate, or the need to replace or remove PFAS components such as surfactants, each material will need to go through another optimization step to fine tune its uniformity.

# Underlayers for Adhesion – How Thin Can We Go?

As films get thinner, a question arose: how thin can a traditional spin-on film actually coat before it starts to fail? Does a spin-coated polymer film actually coat consistently across the wafer when thinned down? Is there enough polymer for adequate coverage? A

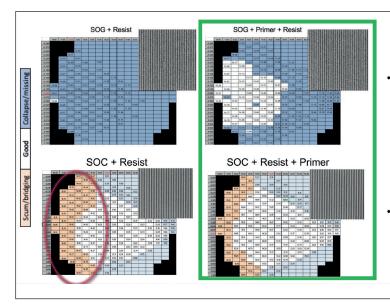

> Figure 4. Comparison of primer versus traditional crosslinked film.

Greatly improved litho performance after applying primer on SiHM

Reduced scumming is observed in low dose region after applying primer on traditional spin-on carbon ➤ Figure 5. Primer on top of problematic underlayers.

few methods can be used to characterize the film and coverage across the wafer. Of course, thickness , but also density, roughness via AFM, contact angle and surface energy are used. Using this data, it was found that high quality films can be obtained down to 4 nm and likely even thinner.

With those same thin films, evaluation with both CAR and MOR was conducted at 28-nm pitch. With CAR, no change in dose or best focus and CD were seen as thickness was decreased. Roughness values varied a little bit, but overall performance was very similar. But again, overall, thin films were proven to work as well as their thicker counterparts.

# Going Ultrathin – Spin-on Primer

So how much thinner can we go? If 4 nm works, why not 2 nm or even1 nm? One concept that has been borrowed from other areas may be a path to get the properties needed for performance but alleviate those issues seen with traditional crosslinked films. This spin-on primer concept can be used to functionalize a variety of surfaces including other spin-on films or CVD-deposited layers through just a simple grafting process. These types of materials have the ability to tune or adjust adhesive properties while allowing for truly ultrathin films.