# 半导体芯科技

## CHINA

ISSN 2523-1294

www.siscmag.com

2020年12月/2021年1月

用于IC制造的

## 半导体芯科技

### CHINA

《半导体芯科技》(Silicon Semiconductor China, SiSC)是面向中国半导体行业的专业媒体,获得全球知名权威杂志《Silicon Semiconductor》的独家授权。本刊根据中国半导体市场特点摘选出相关优秀文章翻译,并汇集编辑征稿、采编国内外半导体行业新闻、深度分析和权威评论等多方面内容,由香港雅时国际商讯以简体中文出版发行。

- ・内容覆盖半导体制造、先进封装、晶片生产、集成电路、 MEMS、平板显示器等。

- ·杂志服务于中国半导体产业,从IC设计、制造、封装到应用等方面。

- •双月刊,全国发行,每期10,000册,免费赠阅。并发行电子书,运营网站、微信公众号。

- · 主办CHIP China晶芯研讨会(线上/线下),搭建业界技术的有效交流平台。

- · 每月EDM发行25,000封, 定向推广行业新信息, 新产品发布。

#### 《半导体芯科技》杂志公开徵稿

- 1. 欢迎杂志读者、供应商以及相关科研单位,技术文章或是应用案例投稿。投稿文章经编辑部审核通过后会刊发在杂志或者网络及公号上,向将近25,000读者进行分享。

- 2. 稿件要求:中文字数(1500~3000),图片:300dpi。

- 3. 新产品投稿要求产品介绍简洁精准,中文字数300字左右,图片300dpi以上。

- 4. 联系邮箱: 赵雪芹主编 sunniez@actintl.com.hk。

免费索阅

微信公众号

半导芯客户服务微信号

### 半导体洁净室专用净化设备

## 高級金值粉 FI BEST FFU

### 特点

1.滤料:进口PTFE

2.效率: 99.99995%

3.节能:效能提升58%

4.控制:全自动智能控制

网址: www.zjnf.cn

深圳市中建南方环境股份有限公司

电话: 0755-26620315/4006699583

邮箱: zjnf@zjnf.cn 深圳市南山区西丽街道西丽工业区新光路15栋、8栋101、201、7栋101-3#

### 目录 CONTENTS

#### 专栏 Column

ChipChina:先进封装正挑起集成电路发展的重担 Advanced Packaging Is Taking the Charge of IC's Future - 贺贵鸿

#### 产品聚焦 Product Focus

- 10 PWG5™图案化晶圆几何系统 GAMMA GxT® 干式光刻胶剥离系统 Volta 180 测试头提升晶圆测试方案

- 11 XBS300 临时键合解决方案 EVG320 D2W 混合键合系统 PA53 MET 万能工业显微系统

- 12 新型 Dragonfly® G3 检测平台 CELLESTA™ SCD 单晶圆清洗系统 microVEGA xMR 选择性激光退火系统

#### 封面故事 Cover Story

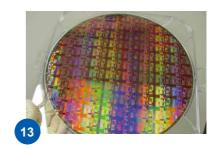

13 在 300mm 硅片上堆叠 GaN 和硅晶体管 Stacking GaN and Silicon Transistors on 300mm Silicon

- HAN WUI, 当时供职于 INTEL 公司

#### 技术 Technology

- 18 通过卓越运营, 在 sub-fab 实施智能制造 Implementing Smart Manufacturing in the Sub-Fab Through Operational Excellence

- Edwards Vacuum

#### 关于雅时国际商讯 (ACT International)

雅时国际商讯(ACT International)成立于1998年,为高速增长的中国市场中广大高技术行业服务。ACT通过它的一系列产品-包括杂志和网上出版物、培训、会议和活动-为跨国公 司及中国企业架设了拓展中国市场的桥梁。 ACT的产品包括多种技术杂志和相关的网站,以及各种技术会议,服务于机器视觉设计、电子制造、激光/光电子、射频/微波、化合物半导 体、半导体制造、洁净及污染控制、电磁兼容等领域的约二十多万专业读者及与会者。ACT 亦是若干世界领先技术出版社及展会的销售代表。ACT总部在香港,在北京、上海、深圳和 武汉设有联络外。www.actintl.com.hk

#### About ACT International Media Group

ACT International, established 1998, serves a wide range of high technology sectors in the high-growth China market. Through its range of products - including magazines and online publishing, training, conferences and events -- ACT delivers proven access to the China market for international marketing companies and local enterprises. ACT's portfolio includes multiple technical magazine titles and related websites plus a range of conferences serving more than 200,000 professional readers and audiences in fields of electronic manufacturing, machine vision system design, laser/photonics, RF/microwave, cleanroom and contamination control, compound semiconductor, semiconductor manufacturing and electromagnetic compatibility. ACT International is also the sales representative for a number of world leading technical publishers and event organizers. ACT is headquartered in Hong Kong and operates liaison offices in Beijing, Shanghai, Shenzhen and Wuhan

#### 关于《半导体芯科技》

《半导体芯科技》(原半导体科技)中国版(SiSC)是全球最重要和最权威的杂志Silicon Semiconductor的"姐妹"杂志,由香港雅时国际商讯出版,报道最新半导体产业新闻、深度分析和权威评论。为中 国半导体专业人士,提供他们需要的商业、技术和产品信息,帮助他们做出购买决策。《半导体芯科技》内容覆盖半导体制造、先进封装、晶片生产、集成电路、MEMS、平板显示器等。杂志服务于中国 半导体产业,包括IC设计、制造、封装及应用等。

#### **About Silicon Semiconductor China**

Silicon Semiconductor China is the 'sister' title to Silicon Semiconductor - the world most respected and authoritative publication, published by ACT International in Hong Kong (former SST China), reports the latest news, in-depth analysis, and authoritative commentary on the semiconductor industry. It provides for Chinese semiconductor professionals with the business and technology &product information they need to make informed purchasing decisions. Its editorial covers semiconductor manufacturing, advanced packaging, wafer fabrication, integrated circuits, MEMs, FPDs, etc. The publication serves Chinese semiconductor industry, from IC design, manufacture, package to application, etc

### **目录 CONTENTS**

22 借助虚拟工艺加速工艺优化

To Develop Process Optimization with Virtual Processes

- Joseph Ervin, 泛林集团半导体工艺整合总监

- 27 用于 IC 制造的非接触式测量技术

Contactless Metering for IC Manufacturers

- MARK ANDREWS, SiS 技术编辑

- 29 器件的 X 射线和声学 3D 成像

X-Ray and Acoustic 3D Imaging of Components

- TOM ADAMS, NORDSON SONOSCAN 公司顾问

- 31 适合大批量、自动化及可靠 3D 半导体焊点分析的最佳方案 The Perfect Solution for High-Volume, Automated and Reliable 3D Semiconductor Solder Joint Analysis

- YXLON 公司

- 33 快速的 DDR4 SDRAM 开创宇航新时代

Fast DDR4 SDRAM to Enable the New Space Age

- Rajan Bedi 博士, Spaceships 公司 CEO 及创始人

- 36 图神经网络加速器的 FPGA 解决方案

FPGA Solutions for GNN Accelerator

- 袁光, Achronix 公司资深现场应用工程师

#### 观点 Viewpoints

39 瑞萨电子将继续深入中国市场并深化与本地客户的合作 Renesas Is Dedicated to the China Market and Cooperate with Local Customers

- SiSC 编辑部

#### 40 广告索引 Ad Index

#### 《半导体芯科技》编委会 (排名不分先后)

刘胜 教授

武汉大学 工业科学研究院执行院长

郭一凡 博士

日月光集团工程副总经理

姚大平 博士

江苏中科智芯集成科技有限公司总经理

汤晖 教持

广东工业大学、精密电子制造 技术与装备国家重点实验室

于大全 教授

厦门云天半导体创始人

林挺宇 博士

广东芯华徽电子技术有限公司总经理

杨利华 院长

两江半导体研究院

王文利 教授

西安电子科技大学电子可靠性(深圳)研究

中心主任

雅时国际商讯顾问

张昭宇 教授

香港中文大学 (深圳) 理工学院 深圳半导体激光器重点实验室主任 刘功桂 教授级高工

中国电器科学研究院股份有限公司威凯

技术中心主任

云星 总经理

深圳安博电子有限公司

李光 常务副总裁 深圳雷曼光电股份有限公司

张弛 总裁

深圳贝特莱电子科技股份有限公司

乔旭东 博士

深创投集团投资发展研究中心总经理

### 半导体芯科技 SELICONDUCTOR · CHINA

#### 社长 Publisher

麦协林 Adonis Mak adonism@actintl.com.hk

#### 主编 Editor in Chief

赵雪芹 Sunnie Zhao sunniez@actintl.com.hk 贺贵鸿 Mizy He mizyh@actintl.com.hk

#### 出版社 Publishing House

雅时国际商讯 ACT International

香港九龙 B,13/F, Por Yen Bldg,

长沙湾青山道478号 478 Castle Peak Road,

百欣大厦 Cheung Sha Wan,

13楼B室 Kowloon, Hong Kong

Tel: (852) 2838 6298 Fax: (852) 2838 2766

#### 北京 Beijing

Tel/Fax: 86 10 64187252

上海 Shanghai

Tel: 86 21 62511200

Fax: 86 21 52410030

深圳 Shenzhen

Tel: 86 755 25988573 /25988567

Fax: 86 755 25988567

x. 00 100 200000

武汉 Wuhan

Tel: 86 27 59233884

#### **UK Office**

Angel Business

Communications Ltd.

6 Bow Court,

Fletchworth Gate.

Burnsall Road, Coventry,

CV56SP, UK

Tel: +44 (0)1923 690200

**Chief Operating Officer**

Stephen Whitehurst

stephen.whitehurst@angelbc.com

Tel: +44 (0)2476 718970

#### ChipChina:

### 先进封装正挑起集成电路发展的重担

半导体制造业犹如两架奔向不同方向的马车。一条是遵循摩尔定律走先进工艺路线,以CPU、逻辑、存储等高端芯片为主,为增强信息处理能力而提升芯片的集成能力。另一条是超越摩尔定律走特色工艺路线,芯片种类变得多样化,关注如何增加人与环境的互动,如模拟/射频、光电、功率、传感、生物等。新兴应用要求业界开发出高端芯片及配套的先进封装技术,因此更加高密度三维集成封装成为封测厂的优先选项。

马书英博士

深创投 史小梅博士

2021年1月21日,SiSC 第二届"晶芯"在线研讨会顺利召开,会议围绕"先进封装技术的发展趋势和应用挑战"这个主题,我们荣幸地邀请到四名业内专家演讲助阵,他们分别是华天科技昆山公司封装技术研究院院长马书英博士、SUSS MicroTec 总经理龚里博士、浙芯集成电路(浙江)有限公司总经理张黎博士、以及深圳市创新投资集团有限公司高级研究员史小梅博士。四位专家准备的演讲内容丰富、数据详实,非常具有参考价值,因此吸引了诸多听众上线听讲,大家获益匪浅。

#### IC产业现状

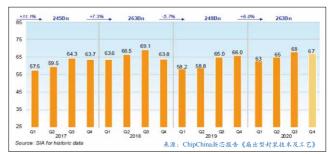

尽管全球受到新冠疫情的影响,2020年全球集成电路行业力改颓势、成为全球经济的亮点。尽管全球经济下滑2%左右,但IC的出货量预计有6%的增长。原因很明显,人们减少外出给家庭办公、家庭互联网创造了业务机会,于是数据中心、笔记本、桌面电脑、5G智能手机、游戏机等需要大数据处理及功能连接的IC业务大有作为。

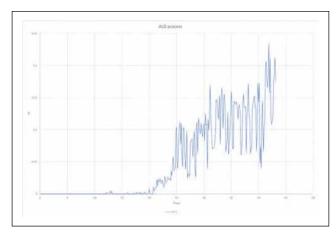

从 SIA 数据可以看出,2017年和2018年IC 行业的季度出货量表现很正常,即 Q1/2/3 呈上升态势、Q4 略微下滑、周而复始,2019年基于5G技术未来可期使得四个季度都处于上升阶段,2020年又恢复到常态,甚至Q4的IC 出货量逐年上升。这意味着,疫情并未给IC产业造成

实质的影响、只不过结构性调整 (图 1)。综合最新的报告,截止到 2020 年年底,半导体行业已从周期性的低迷中恢复,与此同时,芯片短缺状况已经从汽车行业蔓延到智能手机和其他电子设备领域。

图1.2020年全球IC出货量成为全球经济的亮点。

浙芯张博士在题为《扇出型封装技术及工艺》的报告开端就此给出了预警。由于天气转冷疫情又出现反复, 2021年的经济还存在着不确定因素,站在企业经营的角度,值得大家重视。

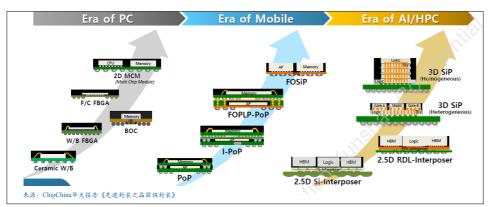

#### 终端应用驱动封装技术

随着智能化与信息化的到来,整个IC 市场的应用领域变得多元化和碎片化,如AI、IoT、5G将引领未来的应用。我们可以预测,三者经过任意结合后将会构成一个超级互联网,将成为自动驾驶、工业4.0、智慧医疗、智能安防等市场的引擎。

那么封装行业该如何满足上述要求?昆山华天马博士在题为《先进封装之晶圆级封装》的报告中详细展示了应用驱动封装技术的历史。首先在PC时代,当时的电子产品主要采用BGA、W/B、2D MCM 封装。迈入智能手机时代,封装进入系统领域、包括系统级封装(SiP.

作者: 贺贵鸿

图2. 应用驱动封装技术的趋势。

FOSiP)以及叠层封装(FOPLP-POP, I-POP, POP)封装;其中,智能手机中SiP 封装的份额在逐年上升。然而,我们正在迎接的AI/HPC时代,其显著特点是要实现高密度、高带宽的互联,所以业内普遍认为高集成度封装是未来封装技术的发展方向,包括同质或异构型3DSiP,以及基于RDL或硅的2.5D封装(图2)。这个趋势也是其他几位演讲嘉宾所认可的。

#### 长袖善舞的Fan-Out

先进封装是会议的主题。浙芯张博士先从封装的分类开始娓娓道来。他认为封装就是个搭积木的过程。按照结构划分,有 2D 与 3D 封装之分,另外还有基板(Lead Frame、塑料、陶瓷等)和无基板(WLCSP, WLFO等)之分。具体而言,基本类有 WB BGA, WB CSP, FC BGA, FC CSP等。高阶的封装如 2.5D interposer、3D 最终脱离不了基板,TSV 针对硅基板,另外还有形式多样的玻璃、陶瓷和 mold compound 等介质材料(TXV),因是腕带、智慧手表等便携式消费类电子产品越来越多,其中的电源模组和射频模组采用 SiP 方式,因此 SiP 封装将保持增量市场。而 bumping, Pillars, TSV, bumpless, embedded 等都是一些基本的互连方式。

扇出型封装(Fan-Out, 简称 FO)的概念起源于设计 领域,就是把线路部署出去。广义的 FO 是除 WLCSP(芯片与封装尺寸为 1:1)之外所有的封装形式,按照这个定义来划分,像 QFN、基板封装的 BGA、倒装芯片 (Flip-Chip,简称 FC)等,都应该归属于 FO。现在大家常说的 FO 封装是特指的狭义 FO,封装结构中没有基板,但是芯片面积要小于封装面积,比例视具体应用而定。

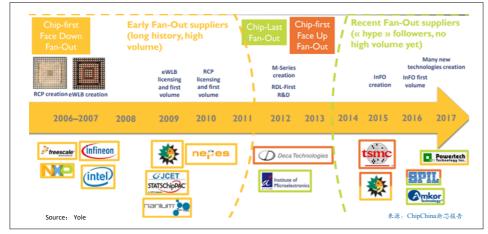

Yole Développement 曾对狭义 FO 做过阐述: 2010 年在英特尔与英飞凌 eWLB 工艺的驱动下 FO 开始实现 量产,产量小但增速较快; 2012~2015年为过渡期,在发 展初期业内因FO相对基板封 装的成本较大而引发争议,自 2016年起才开始实现快速增 长,InFO是主要助力之一。

自从台积电的InFO FOWLP (集成扇出型晶圆级封装)解决方案被用于iPhone的 A10/A11 处理器的封装,

FO 封装引起了市场的广泛关注。应用范围已经从移动智能终端逐渐蔓延至物联网、汽车电子、数据中心和医疗电子等领域。就应用领域而言,FO 具有最大的兼容性,与现有封装技术在每个领域都可形成可选择方案。不同应用产生不同的需求对应不同的封装特征,如密度和尺寸。总之,在后续发展中 FO 的产业规模将会越来越大并且产业接受度会不断攀升。

FO 的多样化与技术本身的灵活性有关,当然 FO 的发展史(授权、研发、企业并购)也是原因之一。最早的 FO 包括 eWLB 以及 RCP (Freescale 与 NXP 合作),2009年日月光、长电/星科金朋及 Nanium 被授权使用 eWLB,RCP 授权给韩国公司 NEPES,Deca 采用 die-up 方式做M-Series 扇出封装。到了2014年,台积电瞄准高端 AP推出 InFO,日月光 FOPOP 亦是为了部分替代2.5D 封装。总之,FO 变种较多,既可兼容传统的封装方式(低至几个引脚),也可面向高端高密度应用(图3)。

反观电子产品的走向,小型化、低功耗、高性能、高集成成为主流。这要求封装体的集成度更高,具体表现为:

1) SiP 转换为 FO-SiP 方式,2) 先前采用单颗封装的芯片可以从 MCM 转换到 FO-MCM。

谈到 FO 的技术优势,张博士认为 FO 其实是一个再布线的过程,其设计灵活性,可实现芯片与基板(包括 PCB 板)、芯片与芯片间的互连;此外,在对比 FO 封装与现有封装技术成本时,系统测算应包括晶圆制造、封装和测试的总成本,不能只考虑封装部分成本。与 WLCSP 相比,两者优点雷同:1) 连线短有利于电信号、功耗以及射频;2) 无基板模式可减小封装尺寸。在电性能方面,eWLB (FO) 的导电性能(高频/直流及电感)完胜传统 BGA;在封装热阻方面,FO 相对 BGA 热阻更小散热更快,当然热阻性能提升也与封装尺寸有

图3. Fan-Out封装发展历程。

图4. Fan-Out封装技术-eWLB (Face Down)。

关。在 MCM 结构中,在晶圆或者 Panel 平台上 FO 工艺可以将芯片间距压缩到最小,有助于提升芯片间互连性能。从供应链角度来看,传统基板类封装需要在 FAB、多个 OSAT 之间辗转往复,而 FOWLP 只需从 FAB 直接到 OSAT,更易形成一站式服务,因此 FO 有更短的物流供应链和交期。

#### 典型的FO技术

由于直播会议得到很多业内的老朋友的关注,张博士开宗明义,言明此次演讲主要与同仁分享对 FO 技术的看法,寻找机会在一些工艺上做进一步研究和探索,包括国内的一些材料厂商和设备厂商,有可能在哪些方面获得突破的机会。

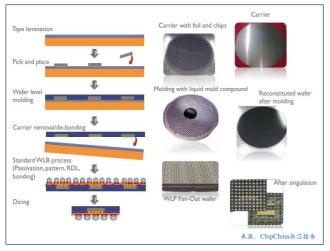

以业内出货量最大、面向中低引脚应用的 FO 封装形式 eWLB 来举例,张博士详细剖析 eWLB 工艺中遇到

的问题并解释每个工艺步骤前后可能影响的因素,有可能源自工艺材料,也可能来自机理及工艺本身,从 Carrier、贴片、Molding、RDL、PVD,可研究和提升的空间很多(图4)。概括下来,张博士认为eWLB存在的挑战和研究价值可能包括这几点:TRF的选择及特性、TRF Residual 去除方案、贴装对位及贴装后芯片位置精准测量、Multi-die 贴装对

位、molding 后芯片偏移的原理(Carrier/TRF/EMC···)、Molding 翘曲控制设计及优化、介电层(Repassivation)与 EMC 兼容工艺、重构晶圆工艺过程翘曲控制、PVD中的 Degas 等。之后,就 FO 几种典型的 FO 封装技术都做了详细的分解,包括 Face up 型(eSiFO、M-Serial、InFO)以及 Die-last FO 应用。

作为整条产业链相对薄弱环节,国产设备厂商备受产业关注;最近 1~2 年,受国际政治形势影响,国产化的呼声很高。通过对 bumping、WLCSP、WLFO、TSV 以及晶圆测试五个环节的归纳总结,我们可以看到:1) bumping和 TSV 技术的国产化推进较为突出,2) WLCSP、FO 以及晶圆测试尚有较大空间待突破(图 5)。

#### 市场多元化及延续摩尔定律驱使OSAT创新

随着 IDM、FAB、OSAT、模组厂、以及正在开发埋入式工艺的基板厂商和 PCB 厂商纷纷进入先进封装领域,封装行业成为整条半导体产业链关注的重点。通过投入大量的人力物力,2018~2024 年传统封装与先进封装分别以2.4% 及8.2%的 CAGR 增速发展,到2024 年两者有望平分秋色。

随着智能手机逐渐称霸市场,WLP 在其中的份额日渐提升。WLP 一般被定义为直接在晶圆上进行大多数或全部的封装制程,传统的 WLP 封装具有较小的封装尺寸及电性能,大多用于 I/O 数较少的消费类 IC (Fan-in);然而智能手机以及更多的中高端应用打破了这种桎梏,为了解决信号输出及 I/O 数受限的问题,WLP 与 Fan-Out 结合起来使用,并通过 RDL、bumping 等技术实现互连。因此,WLP 已成为封装中一个关键的技术平台。

早的 FSI 开发激光打孔做 MVP 封

装, 针对 Stacked BSI 开发直孔封

装技术, 针对 Triple Stack BSI 开

发 no cavity 技术, 等等。在开发

TSV工艺的过程中产生一些平台

性技术,包括12寸晶圆级减薄工

艺 (60μm)、TSV 刻 孔 技 术 (宽

30μm 深 150μm, 深宽比 10:1 的通

孔正在开发中)、低温 PECVD (解 决过程中的填充、膜干裂及应力问

题);针对超薄芯片及三维堆叠芯

片开发激光临时键合技术,包括

图5. 国产装备向封测厂推进的进展 (颜色代表国产化替代的状况, 绿、红分别代表1与0)。

昆山华天马博士认为, WLP 之所以得到广泛使用, 与其自身的特点分不开。首先是成本优势,由于封装尺寸 接近于1:1, 封装体积小因而成本较低, 且 WLP 封装器 件采用晶圆测试而非单颗测试, 因此测试成本大大降低。 再者, 电性能表现良好, 主要是互连距离更短, 无需打线 以及借助 FC 来提高电信号的传输性能。在散热性方面, WLP 主要采用塑封制程,这点适用于功率芯片,热管理 性能有保障。最后, WLP 结合 TSV 技术之后很容易实现 三维异质集成,包括SiP,3D和IPD。

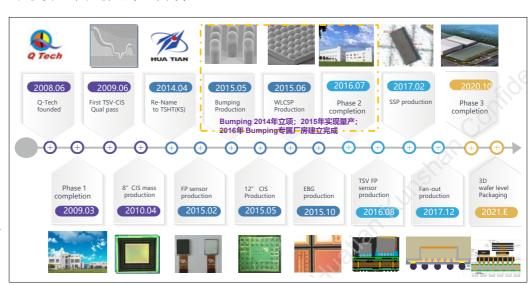

在昆山的三大厂区中,2#厂房在2016年兴建,先有 bumping 线后建 WLP, 目前可实现 bumping 月产能 4~5 万 片; bumping 线于 2020 年成为全球首家实现全自动化天车 生产的 OSAT。5# 厂房主营业务 8 寸 TSV, 月产能 2.5 万片。 6# 厂房是在1月6日搬迁,投资20亿元新建的一个汽车

电子封装线,主要做12 寸车载图像传感器以及 FC, 计划月产能 3 万片, 预计2021年开始生产 3D WLP。马博士自豪 地说,"华天昆山几乎 囊括了所有的先进封装 线 (图 6)"。

TSV是昆山华天 产量最大的产线,最 初生产8寸CIS,后再 扩建12寸线,针对不 同的晶圆开发不同的 封装结构,如针对最 图6. 华天的技术发展里程碑。 de-bonding 技术。

华天拥有知识产权的 eSiFO 扇出型封装有别于 eWLB, 采用硅基技术、超薄封装 (150μm), 适用于 多芯片的集成(目前最多做到5个不同且较小尺寸、不 同来源以及不能功能的芯片)。对大尺寸 eSiFO 研究表 现为良率管控及可靠性难度增大,因此华天做了测试单 元来验证其可靠性(包括 Daisy Chain、Gap 上端、漏

电流以及 Kelvin 测试单元), 已有 9x9mm, 20x20mm 及 30x40mm 三种样本。

硅基板相对 molding compound 的翘曲更好把控, 12 寸硅基扇出晶圆翘曲可以控制在 2mm 以内。另外与 eWLB 相比散热性能好,制程简单、成本较低,无需临 时键合以及 WL-molding (须另外投资产线)。最后采用 的回收硅片(挖空埋入 die 做标准 WLP 制程)更是大大

来源: ChipChina华天报告

7

图7. 混合键合应用-高密度互连。

节省原料成本,硅基与华天现有产线不发生交叉污染。eSiFO 技术与异质集成、再结合华天 TSV 技术很容易实现第三代半导体器件的三维堆叠集成。目前,eSiFO 蚀刻的均匀性可控制在 10μm 以内、最小线宽线间距可做到10/10μm,重构晶圆之后的工艺与 bumping 与 WLP 保持一致了,贴片精度可控制在 5μm 以内。

#### 全球领先的混合键合/解键合技术

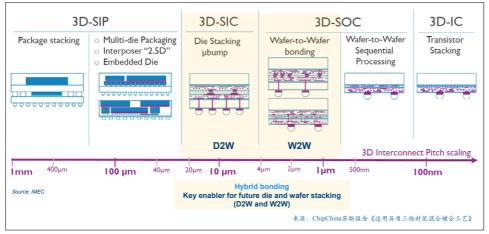

SUSS 作为全球领先的半导体设备厂商,可提供光刻、涂胶、显影、键合以及掩膜清洗设备。与前两位专家的着重点不同,SUSS 龚博士在题为《适用异质三维封装混合键合工艺》的报告中,更多地描述混合键合工艺并介绍键合机的功能。在先进封装领域,系统级封装需要用到基于不同工艺和材料产出的芯片,使得 3D 及 3D 异构封装(如 3D-SIC 及 3D-SOC)市场未来可期,混合键合又是 3D 封装的一种非常重要的方法。3D 封装通过使用各种方法将芯片堆叠在一起,有利于提高芯片系统的速度、性能以及降低工艺成本。

什么是混合键合?由于每次键合耗费时间很长,将Si-Si 键合与 Cu-Cu 键合放在一起,无论是预键合还是最终放入烤炉(Oven)及退火,两种工艺都可以同时同地进行,大大节省整体工艺时间。

如何实现三维封装的混合键合工艺? 龚博士认为,对Si-Si 键合进行键合前处理,即去除硅片表面的有机和无机沾污,对Si 表面做平整(控制在 0.5nm 以内)、去除颗粒(Si-Si 之间的 1μm 颗粒最终会形成 1cm 的空洞)。预键合的时间较短,因此可以将 Si-Si 和 Cu-Cu 键合放在一起做,然后同时进行烘烤(baking),上百对晶圆一起作业。

D2W 及 W2W 键合的主要市场包括 BI CMOS 图像传感 器、3D NAND 及 DRAM、MEMS 等。考虑到 Si-Si 与Cu-Cu 的热膨胀系数不同,在相同温度下(预键合时的温度范围须控制在 0.1 °C)烘烤,Cu-Cu 的延展相对较大。需要将原始的 Cu 稍稍腐蚀(Dishing),这对工艺的控制能力要求很高。

混合键合对于线宽和精度

的要求越来越低,Cu-Cu 键合节距可以做到 3μm,铜柱的直径在 1~1.5μm。选择性 D2W 被认为是未来最有前景的一种三维混合封装形式,尺寸最小、电性能最好(图7)。简单地说,就是提前挑拣出已知合格芯片(KGD)统一转移至载片(carrier wafer)上面——这个过程叫做Populated Carrier Preparation,将载片作为新的晶圆片与另一片晶圆按照标准工艺进行混合键合再剥离载片生成新的晶圆(上面附着 3D IC 成品或半成品),整个流程包括几道基本的工艺,如表面处理(去颗粒、去沾污、平整)、等离子处理、亲水性处理、涂胶、键合、烘烤、退火、解键合、载片剥离、去残胶或粘贴剂,以及晶圆级 die 转移。这个过程可以重复很多次,直至最终实现三维堆叠。目前,D2W 的 die bond 精度最高可达 3μm;而 W2W 的对准精度要求越来越高,苏斯的目标是控制在 0.1μm 以内。

站在量产型设备的角度, 苏斯 XBS300 设备的目标是 将对准精度控制在 40nm 水平, 而 60~80nm 的对准精度正 是存储器所要求的。

XBS300 混合键合设备采用模块化结构,包括等离子体模块 PL300,XBA 对准模块、AC300 清洗模块、LF300 键合腔体、MM300 测量模块(检测对准精度、X/Y 轴偏移、片子之间有无 Viods、方向性等)以及 TD300 Detach 中心,烘烤功能则由其他厂商配套提供。

#### 先进封装成为投行的目标

从全球视角来看半导体行业已经成熟,整体市场走向存量竞争的阶段。深创投史博士在《半导体产业投资新趋势》报告中指出,2019~2020年不仅是芯片行业的转折点,更是中国IC的崛起机遇。

|                            | 芯片类型               | 核心能力              | 市场特点         | 竞争策略            |

|----------------------------|--------------------|-------------------|--------------|-----------------|

| <b>克</b> 4 - 4 / 4 / 4 / 4 | CPU                |                   | + > 00 4 5 - | 高:技术壁垒          |

| 摩尔定律继续 主导的市场               | 存储芯片               | 技术、工艺             | 技术壁垒极高       | 带来的国产替代         |

| エバロバッツ                     | 手机基带芯片             |                   | 76 T 4X/0X/M | 红利              |

| 左是辛名主坛                     | 以功率半导体为代<br>表的模电芯片 | 产品:品控、功耗、<br>性价比  | 客户导向         | 深:成本优势、<br>定制化服 |

| 存量竞争市场                     | 汽车电子工业级芯片          | 服务:本地化能力、<br>服务能力 | 各厂分凹         | 务带来的国产替<br>代红利  |

|                            | 物联网芯片              |                   |              |                 |

|                            | AI芯片               | 产品定义能力            | 爆发式需求更新迭代快   |                 |

| 增量新兴市场                     | 智能汽车               | 本地化能力<br>服务能力     |              | 快:新市场带来的增量需求红利  |

|                            | 5G                 | ר אווי            |              | 山地主而水江州         |

|                            | 智能终端芯片             |                   |              |                 |

图8. 后摩尔时代国内半导体企业创业机会增加。

来源: ChipChina深创投报告《半导体产业投资新趋势》

中国的集成电路市场规模连续三年居于全球首位,长期保持两位数增长,2019年销售达7591.3亿元,比上年增长16.2%,产业起步晚但增速快。我国IC产品集中在低端领域,仍面临缺芯困扰,这点可以从中国海关总署提供的数据可以得出结论,2019年尽管国内产业规模不断扩大,集成电路进出口差额持续拉大,国产芯片的自给率仅10%。

随着去年 10 大项目的陆续暴雷,政府对于上马大项目尤其是 IC 制造等占地广、能源消耗大、重资产比重高、耗时长的项目审核将会变得更加谨慎,反之未来地方政府倾向于扶植本地的一些较成熟的企业。

随着国内几家头部半导体设备 厂商的陆续上市,史博士认为未来 深创投将更加关注设备的子系统、 关键零部件等。再者,由于先进封 装采用的工艺脱胎于晶圆厂,无论 是设备还是材料都有其传承性。因 此,关注先进封装的设备及原材料 也是个不错的选择。

史博士通篇以大量详实的数据、 图表并加以分析,启发听众换个角度 来观察和思考当下高烧不退的行业: 世界 IC 行业的格局,中国 IC 行业的痛点,国产化替代的进展,后摩尔时代 IC 产品的大方向,从资金注入以及市场导入两方面综合考量企业该如何寻找合适的投资机构(图 8)?单一化产品或者产品应用市场广泛的企业,是选择独立上市还是寻求并购的机会?这些都是问题!

#### 结语

本次晶芯在线研讨会得到诸多业内人士的关注,与四位演讲嘉宾自身的专业度以及在行业的影响力息息相关。由于笔者未在一线技术岗任职专业技术欠缺,以上仅挑选演讲中一些相对简单的内容进行报道,至于每道课题的精髓,如张博士对于eWLB的深入剖析与看法,龚博士对于国际最先进键合技术的理解,以及马博士对于华天为降低成本而自主开发各种工艺模块的窍门,我想只有那些多年从事生产管理和研发的技术人员亲临会场,才能获知其中的真正价值!

在此呼吁大家, 莫要错过第三期 ChipChina 晶芯在线研讨会, 2月24 日,"IC 制造光刻机:发展趋势和技术挑战"。◆

#### PWG5™图案化晶圆几何系统

为了制造 128 层或更多层级结构的 3D NAND 复杂的结构,需要经过沉积数百种不同材质的薄膜,然后通过刻蚀并填充几微米深、百分之一微米面积的导通孔结构来创建存储单元。随着这些薄膜堆叠的积累,它们会在晶圆上产生应力,最终使晶片的表面变形。这些翘曲的晶圆会影响下游工艺的均匀性以及图案成型的完整性,最终影响器件的性能和产品良率。

KLA 公司推出 PWG5™图案化 晶圆几何系统,专注解决先进的存 储器与逻辑集成电路制造中遇到的问题。PWG5量测系统具备前所未有的分辨率,能同时测量晶圆正面和背面的平面度偏差,以及晶圆几何

形貌的微小变形,从源头识别并修正 图案化晶圆的变形。而且,关键的晶 圆几何形状测量可配合在线生产的速 度,并在较大的翘曲范围内完成。

KLA 表示, PWG5 的在线测量

速度和分辨率还支持 先进的 DRAM 和逻 辑产品应用。结合 KLA 的 5D Analyzer<sup>®</sup> 数 据 分 析 系 统, PWG5 帮助客户制定 相应的决策,例如晶

圆返工、工艺设备的重新校准或提醒 光刻系统,并提供最佳的图案校正建 议。PWG5 用于制程控制,有助于提 高先进的存储器和逻辑产品良率、性 能和工厂盈利能力。

### GAMMA GxT® 干式光刻胶剥离系统

Lam Research 推 出 GAMMA GxT 干式光刻胶剥离系统,专门针对特色技术 8 吋晶圆的工艺挑战,包括射频滤波器、电源、读出磁头和数字打印等。相对 12 吋工艺,8 吋特色工艺更注重低温处理、薄厚抗蚀层、剥离替代材料和多种衬底材料的处理。

光刻胶剥离一直被认为是技术含量较低的工艺,然而剥离技术的应用贯穿整个工艺流程。随着 3D 架构、双重图形化技术、多层罩式掩膜和高剂量植入剥离 (HDIS) 等新技术的出现,光刻胶剥离工艺的复杂度也在不断提升。

GAMMA GxT 采用多工位顺序加工 (MSSP) 架构,可独立控制温度、射频功率和各种化学成分。得益于更强的源技术和更快的晶圆加热速度,GxT系统在块体和离子植入光阻剥离应用中都能实现零残留、高产能和低缺陷率。

在同一平台执行多个工艺步骤有助于最大限度地提升灵活性和生产率。

GxT 系统可在低温环境下去除残胶(最低 110 ℃),可用于半导体和高级硬盘应用领域的各种特种技术工艺,产能高达 350wph,占地面积小。

GxT 系统配备灵活的气体控制盘,可选配多种特气:1) 传统  $O_2/N_2$ ,适用于薄 DUV 光刻胶层 (i-line 光刻用超过  $10\mu m$  厚、无定形碳灰) 块体的剥离;2)  $CF_4$ 高剂量植入剥离和聚合物去除;3)  $H_2$ 或合成气 (FG),适用于 HDIS 以及低硅或残留物清理。

#### Volta 180测试头提升晶圆测试方案

Smiths Interconnect 全 新 的 Volta180 测试头可满足如下测试需求:最小引脚间距 180μm 的晶圆、 WLCSP 和已知合格芯片 (KGD)。

Volta180是一种增强型晶圆级别测试解决方案,可进行快速而可靠的测试以确保芯片性能是否符合要求,

性能优势包括:1) 在750,000 次寿命测试下仍保持低且稳定的电阻,从而提供高精度的测量;2) 针头共面性可满足64个工位,5000 根探针同时进行测试,以提高生产效率;3) 模组化的针头设计能确保快速更换,停机时间几乎为零;4) 全探针阵列设

计 允 许 现 场根据不同产品配置 探针位置,可测试多个产品。

该 司 总 裁 Paul Harris 表 示, Volta180 系列兼具高性能和高性价 比,帮助客户大大提升测试效率和测 试量率,从而增强市场竞争力。

#### XBS300临时键合解决方案

SUSS MicroTec 公司的 XBS300 是新一代用于批量生产的临时键合平台,可灵活配置。这款支持 8/12 吋晶圆的键合平台通过整合多个工艺模块,于独立设备中完成涂覆粘接层、剥离层和临时键合功能,并兼容晶圆厚度和厚度变化 (TTV) 的集成测量系统。XBS300 以低成本提供高度工艺灵活性。

XBS300 开放型临时键合平台兼容常见的涂覆粘材和工艺材料系统,此外通过与 Thin Materials、Brewer

Science、3M、Fujifilm等全球知名材料供应商深入合作,该系统将不断地鉴定更多材料,拓展可供选择的粘材,以满足不同客户的工艺需求。同时苏斯上海总经理龚里博士表示,愿意利用多年的半导体材料开发经验帮助国内材料供应商成长。

XBS300 临时键合平台为在减薄 前应预先置于晶圆载片上(与硅片或 玻璃载片兼容);针对相同或不同尺 寸的载片采用切边和中心对准;结合 GYRSET®技术可获得最佳的涂胶均

匀;内置无接触多点厚度的测量技术。

XBS300 临时键合仅用于覆剥离层(涂层或等离子体活化)、涂覆粘材、键合、热固化或紫外线固化等加工步骤;并在完成晶圆加工后解除键合。

#### EVG320 D2W混合键合系统

EVG320 D2W 是一个高度灵活 且独立运行的模块化平台,具有通用 的硬件/软件接口,可与第三方芯片 键合系统实现无缝集成;全球已装机 数百个。系统集成了 EVG 先进的清 洗技术和等离子活化技术、芯片对准 验证模块(AVM),可为系统直接反 馈关键工艺参数,包括芯片贴放精度、 芯片高度以及键合后的测量,用于改 进制程控制。

EVG320 D2W 具有灵活的基板

处理能力,可容纳任何类型的芯片载体或胶片框架 (film frame),这些载片支持等离子活化、混合和融熔键合的洁净标准和 SECS/ GEM 标准。EVG高级技术总监 Paul Lindner表示,已开始使用 D2W 晶圆键合机 EVG GEMINI® FB 系统的专用版来满足新兴 D2W 市场的需求。

EVG320 D2W 支持创新工艺解 决方案,有助于加快异构集成的部 署并支持新一代设备和系统,例如高

带宽存储器 (HBM)、逻辑存储器、Chiplets、分段式和三维式 SoC、以及 3D 堆叠式背面照明 CIS。

#### PA53 MET万能工业显微系统

Motic 推出的 PA53 MET 万能工业显微系统,代表了当今国内领先的显微光学设计和加工水准;在亚微米级显微领域媲美德日产的显微镜产品。它具备超大视野明视场、暗视场、高反差、偏振光、微分干涉观察方式;其模块化设计满足 4~12 吋晶圆和大面积 FPD 检查。

PA53 MET 具备 3D 超景深融合功能,采用 z-stack 多层堆栈技术,为目前工业领域纵向测量提供优秀的解决方案。PA53 MET 独特的智能显微镜设计,如ECO自动休眠功能及IL多物镜亮度记忆功能,保障厂内OP能够快速掌握操作高精密光学仪器,提升了生产安全与效率。PA53 MET

具有多物镜识别功能,完全避免了工 人使用软件测量时出现的测量失误。

### 新型Dragonfly® G3检测平台

Onto Innovation 的 Dragonfly G3 系统满足最近的 2D 和 3D 测量需求,新配置的亚微米分辨率光学系统大大提高了在亮场、暗场或 Clearfind®照明模式下的二维缺陷检测能力。对于要求 RDL 接近 1µm 设计规则的复杂封装设计而言,亚微米级分辨率至关重要,可满足在线式重复检测关键层上的低对比度缺陷,提高生产良率。除了拥有更高的灵敏度,系统的扫描速度比之前的平台快 30% 以上。

蜻蜓 G3 用于高端器件和系统的

生产厂商,目标产品包括下一代功率 器件、RF、滤波器、放大器、CIS 和 激光雷达传感器,特征尺寸的快速缩 减需要更灵敏的工具来提供可重复和 准确数据的制程控制设备,以检测出 更小及新型缺陷类型。

蜻蜓 G3 还采用了重新设计的 LT-200 的 3D 测量系统,创新的双 头设计将 3D 凹凸测量的出货率提高 50%。新的软件系统有别于 Discover® Defect 软件,为 5G、高性能计算和 复杂 DRAM 封装等更多复杂应用提

供实时过程控制套件。

蜻蜓 G3 升级的 Clearfind 技术可提高芯片可靠性;结合先进的图像处理算法,能以更快的速度在更大的范围内发现光刻胶残留和化学品残留。Clearfind 是 ONTO 独有技术,越来越多的 IDM、晶圆厂和 OSAT 用来控制扇出型和焊盘到焊盘的焊线工艺。

#### CELLESTA™ SCD单晶圆清洗系统

TEL 的 CELLESTA™ SCD 单晶圆清洗系统广泛用于半导体芯片的后清洗工艺,目标产品包括 Chiplets、复杂的逻辑芯片和 PC 或 NB 使用的DRAM 存储器。CELLESTA SCD 还集成专了用的干燥腔体。

在晶圆的清洗制程中, 通常使

用具有低表面张力的酒精。然而在晶圆干燥过程中,芯片微缩以及先进器件中采用的多层结构(类似3D叠层)会被液体表面张力破坏,从而导致晶圆的图案塌陷。为此TEL开发了一种使用超临界流体(表面张力很小)的无图案塌陷的干燥法,

并将该技术用在最先进的批量型生 产设备中。

#### microVEGA xMR选择性激光退火系统

3D-Micromac AG 的工业级选择性激光退火系统 microVEGA xMR,整合高度灵活的高通量工具配置和动态光斑与可变激光能量,可兼容巨磁阻(GMR)和隧道磁阻(TMR)传感器,并能轻松调整磁性方位、传感器位置和尺寸,能在单一晶圆上对传感器设置不同的参考磁化方向,适合生产磁性传感器。

相 较 于 传 统 退 火 技 术,microVEGA~xMR~的优势明显,包括加工精度为  $\pm 5\mu m$ ,支持加工较小的

磁性传感器结构,通量高达50万个/小时,出色的能量均匀性可提升传感器质量,适应最大12时晶圆,基于配方的灵活编程可控制所有系统参数,包括脉冲能量、传感器尺寸、传感器的间距、磁性方向和磁通量,无耗材或产品专用零件。

microVEGA xMR 系统可选择性加热各个传感器的钉扎层,以"压印"所需要的磁性方向。磁场强度和方向可由配方进行调整,而高温梯度能够确保低热冲击。这样传感器就可以

直接在读出电子器件旁边以及在更靠近的地方加工制造出体积更小的传感器,为晶圆腾出空间从而加工更多器件。最终可减少工艺步骤、简化生产流程、提高产量并实现更具成本效益的集成单片传感器封装工艺。

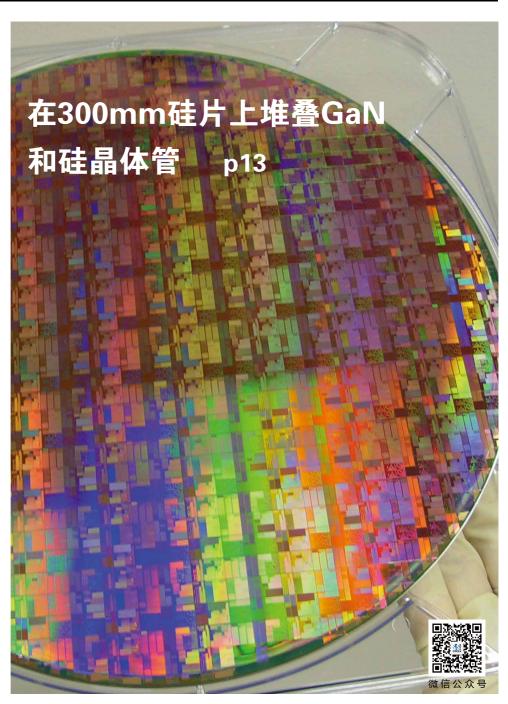

### 在300mm硅片上堆叠GaN和硅晶体管

通过在300mm晶圆上实现GaN和硅基CMOS的三维单片集成,可以为下一代移动设备、数据基础设施和通信网络有所助益。

界认为,向 5G 和之后的移动通信技术过渡,将推动联网移动设备的数量呈指数式增长。为它们供电的集成电路将需要具有更高的能量效率,并缩小自身的外形尺寸。因此,市场对于性能更强的晶体管以及在微芯片上集成越来越多的器件,有着巨大的需求。

满足上述要求绝不是一件简单的事,原因是现今的晶体管技术都不能满足与功率输出和 RF 前端设计相关的多样化需求。由于存在这个问题,电路设计人员采用了将许

多不同的独立芯片整合在一起的做法。这种做法并不太好, 会导致封装的体积较为庞大。

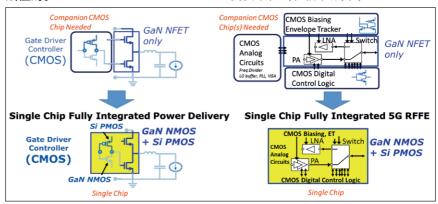

为了应对这个问题,我们设在 Intel 俄勒冈州技术开发小组器件研究部门的团队开发出首个三维单片式 GaN和硅晶体管堆叠技术。该技术能提供业界一流的性能和效率,同时允许在单颗芯片上集成多种不同的功能。

将硅和 GaN 整合是一个颇具吸引力的提议。对于电力电子器件和 RF 开关来说,硅是它们现在主流的半导体芯片

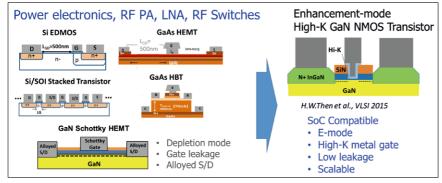

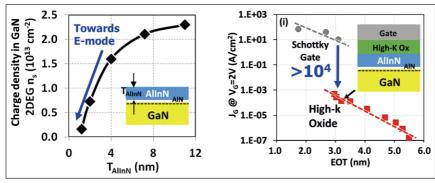

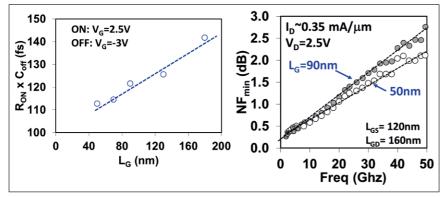

图1. 在目前的功率输出和RF前端解决方案中,不同的技术包含在多个有明显区别的独立芯片里,因而不得不让这些芯片在一个庞大的封装中配合工作。利用高 K 值电介质和金属栅极技术实现的增强模式GaN晶体管,首次实现将所有这些功能集成在单颗芯片上,从而成功打造片上系统(SOC)。

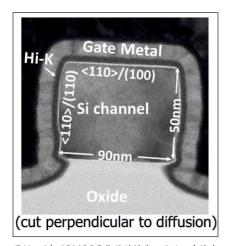

图2. 于自建的主流CMOS晶圆厂内, Intel在300mm Si (111) 晶圆上成功产出首 批GaN晶体管。该公司的研究人员运用了一种基于层转移的三维单片集成新技术,将硅PMOS晶体管堆叠在GaN NMOS晶体管之上,以实现CMOS功能,在 业界这是首创。

材料。然而,它在提供高频、高功率性能方面有点不堪重负,因此并不是RF 功率放大的上佳选择(图1)。就这项特定的任务而言,GaAs HBT、GaAs HEMT 和 GaN HEMT 处于领先地位。然而,这些技术并不是制备高效电力电子器件的理想选择:耗尽型 GaAs HEMT 和 GaN HEMT 不受青睐,原因在于它具有"始终保持接通"的特性;而 GaAs HBT 更加不合适的,因为它采用的是电流驱动,而不是场驱动。

幸运的是,有一种晶体管在各个方面都表现出色,它就是增强模

体管技术与硅 PMOS 的整合。得益于此,所有的功能皆可以集成在单颗芯片上,从而第一次形成了片上系统。

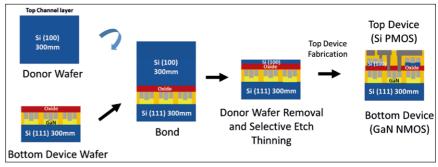

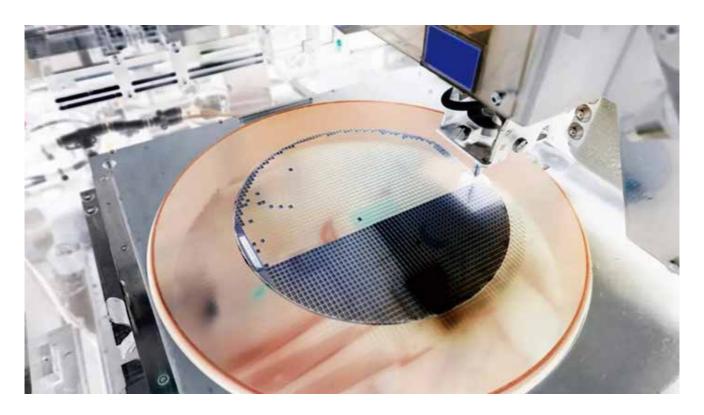

我们的努力取得了一些成就,即在 300mm Si (111) 晶圆片上成功制备了首批高性能 GaN 晶体管(图 2)。我们制备这些晶体管时,采用的是与主流 CMOS 晶圆厂相兼容的 300mm工艺技术。

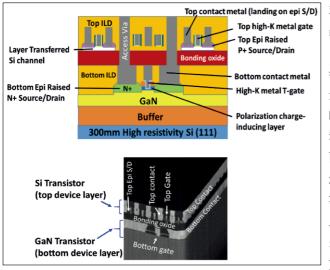

另一项成就是我们运用了一种新的三维单片集成技术,该技术基于层转移 (layer transfer)。借助这种方法,我们将硅 PMOS 晶体管堆叠在 GaN NMOS 晶体管之上,以实现 CMOS 功能,从而取得了新的突破。

对于能够以高效、纤巧的片上系 统来实现和集成的解决方案而言,这 项新技术显著地拓展了它们的领域。

我们有几家主要的 CMOS 晶圆 厂,用其中的一家在 300mm 硅晶圆 上加工自己的 GaN 晶体管,取得了 额外的回报,那就是它为所有最新的 工艺创新开启了大门。这些创新包括 高 κ 值技术、三维层转移、化学 - 机 械抛光、光刻技术和铜互连。此外, 由于采用了较便宜的 300mm 硅衬底, 并启动了大批量生产,因此显著降低 了成本,使得我们从中获益。

#### 利用尺寸较大的晶圆片

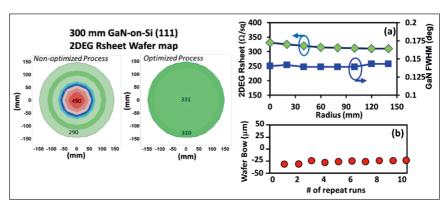

由于缺少同质衬底,几乎所有的 GaN 都是在异质衬底上生长的,如蓝

图3. 这是从Intel的一种适于生产的300mm GaN外延工艺获得的优化和一致数据。图中数据分布包括: 二维电子气体薄层电阻, GaN晶体质量(依据x射线衍射峰值的FWHM进行评估),以及300mm晶圆翘曲度。

图4. 高K值栅板电介质层在等比例缩放的等效氧化层厚度 (EOT) 上实现了超过4个数量级的栅极泄漏降幅,用以提高性能。

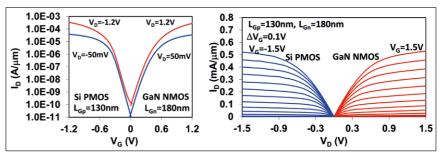

对我们在 300mm 硅衬底上制备的高 κ 值电介质增强模式 GaN NMOS 晶体管进行测量显示,它拥有优异的电特性,以及同类最优的功率输出和RF 性能。这些器件具有低漏极泄漏、高驱动漏极电流、低拐点/膝点电压和低导通电阻。这样的特性表明,高 κ 值电介质技术可使 GaN 晶体管集低泄漏和超卓性能于一身,就功率输出来说,其指标比业界标准的硅晶体管

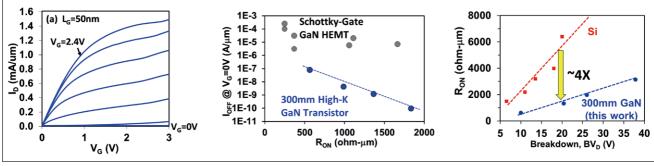

图5. 在300mm硅晶圆上制备的Intel增强模式高 $\kappa$ 值电介质GaN NMOS晶体管其ID-VD特性显示:接近1.5mA/ $\mu$ m的高驱动漏板电流、低膝点电压(低于1V),以及和导通电阻 $R_{ON}$ 仅有 $610\Omega_{-\mu}$ m。可以同时实现低漏极泄漏(在5V漏板电压下 $I_{OFF}$ 低至100pA/ $\mu$ m)和出色的 $R_{ON}$ 。与用于功率输出的硅晶体管相比,高 $\kappa$ 值增强模式GaN NMOS晶体管的性能高了4倍左右。

宝石、SiC 和硅。使用最普遍的平台是 3/4 英寸 SiC (这两者均相对昂贵),以及 4/6/8 英寸的 Si (111)。与此相反,我们采用的是具成本效益的 300mm Si (111) 衬底(图 3)。在该平台上,我们在自己的 300mm 晶圆厂内将 GaN与最先进的高 κ 值电介质金属栅极技术相结合。这支持增强模式操作和栅极堆叠微缩,并最终实现高性能和低泄漏,这是提高效率的关键。值得注意的是,这种泄漏的减少是很显著的,优于肖特基栅 GaN HEMT 的幅度可

图6. 在1~30GHz的频率范围内, Intel的高κ值增强 模式GaN NMOS晶体管的性能明显优于GaAs和Si/ SOI

达4个数量级以上(图4)。

增强模式 GaN 晶体管技术的另一个优点是它简化了电路架构。由于增强模式晶体管处于常闭状态,因此它不需要负电源。取而代之的是,该器件可以直接用电池供电驱动,从而节省了微芯片上宝贵的面积资源。

高出 4 倍左右(图 5)。

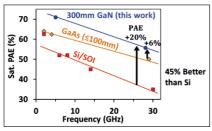

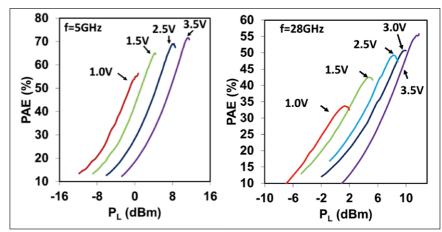

另外,我们的器件还具备出色的 RF 性能。在很宽的频率范围内(从 1~30GHz),我们的高 κ 值 GaN NMOS 晶体管的功率附加效率明显优于那些 基于 GaAs 和硅/SOI 的晶体管(图 6)。由于拥有优异的膝点电压和导通电阻,

图7. 在3.5V到低至1V的电源电压范围内呈现出高的功率附加效率。在远低于2V电压下的高效率PA运行超过了采用典型GaAs HBT可实现的最小截止电源电压,并突显了Intel高κ值GaN晶体管所具备的延长电池寿命和实现高效包络线跟踪RF功放的潜力。

图8. 高 $\kappa$ 值增强模式 $GaN\ NMOS$ 出色的开关品质因数( $R_{ON} imes C_{OFF}$ )及噪声性能 $NF_{min}$ 。

因此可以在低至 1V 的漏极电压条件下 实现高效的功放运行 (图 7)。

该数值远远低于典型 GaAs HBT 的最小截止电源电压,突显了高 κ 值 GaN NMOS 晶体管所具备的潜力,即:显著地延长电池寿命,并采用包络线跟踪 RF PA 架构提供无可比拟的效率。另外,高 κ 值 GaN NMOS 晶体管还可用于制作性能优良的 RF 开关和低噪声放大器。例如,它们具有卓越的品质因数(对于开关),以及仅仅110fs 的导通电阻与关闭电容乘积。最小噪声指数在 5GHz 和 28GHz 频率下分别为 0.4dB 和 1.36dB (图 8)。

将作为功率放大器、低噪声放大器、RF开关和功率晶体管的极佳性能加以组合,使得增强模式高 κ 值 GaN NMOS 晶体管技术能够将 RF 前端和功率输出系统的效率和性能提高,达到今天采用 GaAs 和硅技术所无法触及的水平。但这还不是全部,通过转向采用高 κ 值 GaN NMOS 晶体管技术,我们在单颗芯片上实现了多种功能的紧凑集成,从而节省了空间,并造就了无与伦比的小规格芯片。

#### 三维集成

在当今市场上,卖点之一是 CMOS模拟和数字逻辑/控制功能、 以及CMOS存储器的紧凑型片上集 成。目前,此类 CMOS 芯片是作为独立单元构建的,不过随着功能和复杂性的增加,将要采用单片式 SoC 解决方案,以提供更高的效率、更低的成本和更高的集成密度(图 9)。

然而,由于 GaN 中的空穴迁移 率低,而且难以在该材料中实现高的 p型掺杂浓度,因此实现基于单片式 互补型 GaN CMOS 的设计是极具挑 战性的。 好消息是,我们的团队与康奈尔 大学及 MIT 的研究小组之间的合作 正在取得进展。这项合作的目标是希 望实现 GaN PMOS 的宽带隙、高电 压操作。虽然此项工作尚处于起步阶 段,但寄予的希望是标准高 κ 值金属 栅极硅 PMOS 能够加入进来,目的是 为 GaN NMOS 提供绝佳的互补型 p 型沟道技术。因为它具有高的空穴迁 移率,并有可能为源极 - 漏极触点实 现非常高的 p 型掺杂浓度。

为了以单片式在单个硅衬底上 集成多种不同的半导体材料,我们运 用了层转移的方法。这让我们能够以 单片式将硅基 PMOS 晶体管堆叠在 GaN NMOS 晶体管之上。

利用这种形式的三维单片集成具 有许多优点,它允许对晶体管的每项 组成技术单独地进行构建和优化,以 提供最佳的性能和成本。

图9. 单芯片全集成型功率输出和RF前端单元,可利用Intel堆叠在GaN NMOS晶体管之上的三维单片集成型 硅PMOS技术实现。

图10. Intel的单片三维层转移工艺流程包含:在制备顶部硅PMOS晶体管之前,将一层单晶硅从一个300mm Si (100) donor晶圆转移到一个已完工的300mm硅基GaN (111) 晶圆上。

(这是由锂离子电池提供的), GaN

#### GaN的优点

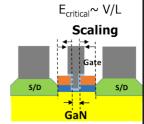

当与 GaAs 和硅相比时, GaN的 约翰逊 (Johnson)和巴利加 (Baliga)品质因数 (表1),处于绝对优势,这得益于它的宽带隙特性。这些优点使得 GaN 能够在高频和高功率下运行。

GaN 的一个优势源于这个材料家族所具备的自发和压电极化效应。因此,在 GaN 与一种相关三元合金的界面处的 GaN 沟道中产生二维电子气体,而不需要掺杂杂质。由此形成的 GaN 异质结构具有高的载流子浓度、还有高的电子迁移率,这是因为电子的有效质量低,而且没

有杂质散射。

GaN 还有另一个优点,就是其宽带隙特性使得临界击穿电场至少是GaAs 和硅的 10 倍。这允许将 GaN晶体管微缩到较小的长度,从而提高性能。例如,对于 3.7 V 的电源电压

|                                                                 | Si                | GaAs              | GaN               |

|-----------------------------------------------------------------|-------------------|-------------------|-------------------|

| 带隙 (eV)                                                         | 1.1               | 1.42              | 3.4               |

| 临界击穿电场,E <sub>crit</sub> (MV/cm)                                | 0.3               | 0.4               | 3.3               |

| 电子迁移率, μ (cm²/V/s)                                              | 1350              | 8500              | 2000              |

| 峰值速度,V <sub>peak</sub> (107cm/s)                                | 1                 | 2                 | 2.5               |

| N型沟道Baliga FOM与μE <sub>cri</sub> 2成正比 (归一化至硅)                   | 1                 | 11                | 179               |

| N型沟道Johnson FOM与V <sub>peak</sub> E <sub>crit</sub> 成正比 (归一化至硅) | 1                 | 2.7               | 27.5              |

| 空穴迁移率 (cm²/V/s)                                                 | <450              | <400              | <50               |

| 有源p型掺杂 (/cm³)                                                   | ~10 <sup>21</sup> | ~10 <sup>19</sup> | ~10 <sup>17</sup> |

| ,,                                                              |                   |                   |                   |

晶体管的长度可以较短,电阻较低,并提供较高的驱动电流。在当今以改善功率特性和 RF 性能为目标的生产中,像这样的一些优点已经使GaN 成为最佳的半导体材料。

Ecritical ~ V/L

表1. 硅、GaAs和GaN的本征半导体特性和品质因数 (FOM)。N型沟道GaN具有最高的Baliga FOM和Johnson FOM;但是P型沟道GaN仍有难度,因为它的有效p型掺杂浓度低,而且空穴迁移率低。硅PMOS晶体管具有一个经过验证的互补P型沟道,以及高的空穴迁移率和高的有效p型掺杂浓度。

图11. 顶部硅PMOS晶体管的横截面显示,它旨在提升空穴迁移率和性能的鳍型场效应晶体管架构、晶体取向和截流方向。这些硅晶体管设计和架构的选择可以独立于底部GaN晶体管的选择。

我们的三维层转移工艺的起点是 采用氧熔融胶合法将标准的 300mm 的 Si (111) donor 晶圆黏合到已完工的 300mm 硅基 GaN (111) 晶圆上面。在 这之后,我们去除该晶圆片,并制作 硅 PMOS 晶体管(图 10)。通过将鳍 型场效应晶体管对准一个可提高空穴 迁移率的方向,我们确保了高性能的

图12. 顶层沟道长度( $L_G$ =130nm)硅PMOS晶体管和底部沟道长度( $L_G$ =180nm)GaN NMOS晶体管的I-V特性。外形尺寸是独立选择的,以匹配驱动电流强度和断态漏电流。

硅 PMOS。它采用了一个方法达成目的:让侧壁上的晶体管沟道朝着一个特定的晶体平面和载流方向(图 11)。我们这个方法会获得很大的自由度。硅 PMOS 晶体管设计和架构的确立可独立于底部 GaN 晶体管的选择。例如,通过选择适当的沟道取向(针对硅 PMOS)和沟道长度(针对 GaN NMOS),可以使两个沟道的驱动电流和断态漏电流相匹配(图 12)。

我们制作的GaN NMOS与硅 PMOS晶体管的单片三维堆叠,为在 同一颗晶圆上集成两种不同的最先进 半导体技术提供了非常有效的方式, 并实现了最佳的性能、更高的集成密 度和更多的功能。

这项技术具有无限的潜力,因为它可能会产生全新的产品类别,且有能力改变现有的游戏规则。令人兴奋的是,许多契机即将来临,包括高效、高性能 RF 和功率输出与标准硅基处理器的全面集成。面向 5G 以及未来移动通信技术的下一代移动设备、数据基础设施和通信网络的需求,我们详细一种如此先进的技术是有潜力予以满足的。◆

### 通过卓越运营, 在sub-fab实施智能制造

近日,Edwards Vacuum举办了一场网络研讨会,Silicon Semiconductor于会上探讨了在sub-fab 实施智能制造和工业4.0概念的方法。鉴于新冠疫情仍在肆虐,市场对相关内容呼声较高,Edwards 应邀在SEMICON West 2020的一篇文章中分享了网络研讨会的重要内容。

Edwards Vacuum 供稿

If, Silicon Semiconductor 举办了一场关于在半导体制造 sub-fab 中应用智能制造和工业 4.0 概念的网络研讨会。本次网络研讨会由 Edwards Vacuum 主办;Silicon Semiconductor 的技术编辑 Mark Andrews 主持了Edwards 演讲者的讨论活动。演讲者包括现场运营和安全副总裁 Alex Smith、营销和业务转型负责人 Alan Ifould 和数字解决方案负责人 Neil Condon。

网络研讨会采用了问答的形式进行,重点探讨了利用 sub-fab 智能制造实现洁净室智能制造的方式。Edwards 公司是半导体行业真空和尾气处理系统的领先供应商,他们分享了在 sub-fab 中实施智能制造的方法,该项目被称为

"卓越运营"。Edwards 公司已成立 100 多年,自创立以来一直服务于半导体行业,并已为全球客户安装了 10 万多台真空泵和 1 万多套尾气处理系统。以下是网络研讨会的精华内容。

#### 智能制造/工业4.0

主持人:智能制造除了收集更多数据,还有其他用处吗? Edwards 的方法是什么?

EDWARDS:智能制造不仅仅是简单地收集更多的数据,它还能优化数据的使用方式。Edwards的同事们经常探讨"卓越运营"的话题——这个词能诠释我们持续改

进业务运营模式的行动。这样 我们就能有效整合人员、机器 和流程,共同管理风险,并提 供客户想要的结果。数据驱动 着整个流程不断发展,但如果 缺乏领域专业技术,也就是将 数据转化为实操见解的集体个 人和机构知识,那么数据就常 无用处。掌握了领域专业技术 后,就可以找到解决方案。

我们自己和公司客户都会 逐渐采用"卓越运营"的理念。 例如,我们可能会收集更多性 能数据,以便及早发现性能不

方法 专注领域 FAB价值 领域专业知识 固定价格 减少预算变动 持续走高 卓越运营 共同管理风险 防止晶圆损失 预测性维护 优化Sub-Fab服务 延长机台正常运行时间 时间间隔 监控和分析团队, 消除移动限制的影响 远程培训 远程支持模型

Sub-Fab带动Fab发展

图1. Sub-Fab可以利用领域专业知识、卓越运营、预测性维护以及监控和分析来推动fab发展,从而产生许多益处,如佳的系统,并与客户一起规划 增加正常运行时间、降低整体成本。

正确的服务干预。其中包括提前更换泵,以避免关键机台意外停机,或完善计划中的维护计划,以延长间隔时间并减少消耗品和备件的使用量,或启动调查,以了解其他产品和服务组合能否提升性能。我们还会利用服务团队的绩效数据,以及他们使用的程序来调整程序,并推动培训计划。

我们运用精益原则建立了一个名为 VTPS (真空技术 生产系统) 的框架,它能跟踪工作场所组织、库存管理、 精心设计的工作标准遵守情况,以及"从我做起"的理念。 这个框架为以原则为导向的领导力、安全和持续改进文化 提供了有力支撑。

### 主持人: Edwards 的技术、软件和现场服务专业知识解决了哪些市场需求?

EDWARDS: fab 造价不菲,停机事件既会影响生产,又会造成经济损失。供应链出现问题后,中断的影响就会进一步放大,现在是这样,未来预计也不会有变化。尽管疫情对供应链造成了压力,并对运营效率和消费者需求造成了许多影响,但我们的客户并没有被困难击垮。虽然疫情催生了很多变数,市场前景难以预测,风险和不确定性似乎仍会持续增加,但人们的信心正在不断恢复。

在这种情况下,我们必须采取行动,以减少可能影响 洁净室 sub-fab 的风险和不确定性。任何可以减少停机时间的计划内/计划外活动都能显著节省成本。例如,在一家代工厂客户那里,我们利用我们先进的数据分析技术,将尾气处理系统 PM 的数量从每年 120 个减少到了每年

17个。

由于每台 PM 持续 6-12 小时,并且会消耗价值数千美元的备件,因此零件成本和生产损失会超过 50 万美元。而且这还只是在一个机台上发生的损失。Sub-fab 的设备有很多用处。

#### Sub-fab的发展

#### 主持人: 近年来, sub-fab 有了哪些变化?

EDWARDS:前沿工艺所需的加工步骤数量逐渐增加,因此市场对真空和尾气处理系统的需求量也越来越大。一家每月生产4万片晶圆的 fab 拥有数千种加工机台以及配套的泵和尾气处理系统。工艺要求越来越高,越来越依赖高质量真空。环境法规越来越严,如果没有高效的尾气处理系统,生产就无法进行。

Fab 使用的传统 200mm 工艺也发生了变化。200mm 机台和昂贵的混合解决方案越来越受欢迎——使用 300mm 机台生产 200mm 晶圆。新旧混合会给 sub-fab 支持基础设施以及洁净室带来更多挑战。在这种背景下,为最大限度地提高投资回报率和盈利能力,通过这些战略投资来保持生产力非常重要。因此,我们认为,所有行业的安全探索、计划外真空和减排事件的代价会越来越高。目前来看,sub-fab 有望提高生产效率。为了应对这些挑战,sub-fab 设备也在不断升级,其复杂度和操作难度也在持续增加,而招聘和留住具备相应领域专业知识的员工则变得更加困难。Edwards 认为应该制定一项计划,以便分享

原子层沉积机台上的泵的振动信号(左)和附着有沉积物的内部组件照片(右)。数据分析预测了计划维护前机台故障的可能性。详细分析拆下的零件后,确 认零件的确即将失效;主动更换零件可防止计划外的工艺停机和潜在的晶圆废料损失。

和嵌入领域专业知识和根深蒂固的文化行为,确保企业能够安全生产、设有一致的绩效标准和问责机制,并为人才发展和获取回报保驾护航。

这是开发我们"卓越运营"模式的最初驱动力,该模式侧重于创建能够不断提高机台可用性和降低风险的团队、技术和文化。

主持人:当 sub-fab 系统遭受计划外停机时,发生故障的成本是多少?

EDWARDS:故障成本并不好确定,因为每个 fab 都有自己的评估和会计方法。我们将模型建立在假设的基础上,并对不同行业的客户进行测试。成本差异很大。如果密封失效,有毒气体逸出,那么整个 fab 的人员都需要疏散。分次式熔炉的非计划真空故障可能会导致 125 片总价值数十万美元的晶圆毁于一旦。尾气处理系统故障后,可能会导致机台离线数小时。计划和预期是关键。更换真空泵后,真空泵故障通常可以在大约 4 小时后排除。但如果机台突发性失效,则可能需要更换腔体部件,甚至需要进行长达72 小时的全面重新校准,而且生产中断也会产生成本。

#### Sub-fab的系统方法

主持人:鉴于真空系统较为复杂,主要组件是如何相 互作用,并进而影响正常运行时间和 fab 性能的?

EDWARDS:真空加工机台的组件彼此相互依赖,这类例子很多。我们都知道,泵本身的压力可以变化多个数量级,温度可以变化数百度。但有时泵的上游几米处发生泄漏后,会导致泵内发生化学反应,进而导致泵发生故障,此类故障同样屡见不鲜。

有时, 泵和腔室之间似乎有一片"真空地带", 这给

问题溯源带来了不少麻烦。如果想找出问题的根本原因,就要从腔室一路检查到尾气处理系统的出口,彻底排查整个系统,有时还需要检查配套设施。在这方面取得进展的关键是开展合作。当所有利益相关方和领域专家一起工作时,就更容易找到根本原因,并制定出一套能提供一致性能和可靠性的解决方案。

在一个案例中,一位客户拥有的机台的生产率仅为同类机台的10%。我们的初步预测分析表明,真空泵和辅助尾气处理系统的性能在极短时间内发生了退化,并且退化速度越来越快。这种方式还能用来判断其他问题。其他异常数据表明真空泵上游有故障。客户提供更多 fab 的关键上下文数据后,我们在进气管路发现了确切的问题,该问题发生在另一个团队负责的维护活动期间。这个例子清楚说明了理解真空系统的整体方法的重要性。这里的关键是能够为数据分析显示的内容添加上下文。我们利用我们掌握的领域专业知识来了解设备的工作方式。最后,我们合作创建了新的维护程序,以确保一套高负载的真空系统和机台能正常工作。

主持人:制造集成电路较为复杂,有时每天都要调整工艺。Edwards 如何确定哪些工艺能提高 sub-fab 的绩效呢?

EDWARDS:这要从两方面来看:首先是设备本身。我们要正确配置和设置设备。Edwards制造的产品种类很多,所有产品均可通过软件进行调整或配置。例如,我们的 iXH 干泵可用于要求严苛的 CVD 和 ALD 工艺,产品共有 116 种型号。另外,我们还要考虑客户的工艺。了解气体、蒸汽和副产品在产品中的相互作用原理是选择和配置产品的重要依据。这是我们擅长的领域,也是帮助我们衡量和提高绩效的关键因素。

因此,我们利用"卓越运营"不断改进我们的知名方法(best-known-methods, BKM)——文件和程序,具体描述如下:

- 针对工艺,系统性地拟定正确的产品组合

- 这些产品的最佳配置——您如何设置产品的运行?

- 以及正确的服务和维护制度,这是由有关性能的实时数据"智能化"的。

这些 BKM 是关于工作原理的全局视角,我们对客户和整个行业工艺非常了解,因此仅有我们可以提出这种方案。

它们的精度越来越高,并且,随着晶圆加工的复杂度逐渐升高,工艺和 BKM 之间的关系也变得更加重要。

#### Sub-Fab优化Edwards角色

主持人: Edwards 在帮助制造商优化性能、缩短停机时间、提高一致性和降低运营成本方面有哪些独到见解?

EDWARDS: 当我们检查 sub-fab 空间时,我们发现许多优秀的公司也同样拥有 Edwards 的技术。但我们相信,我们凭借"卓越运营"的框架和广泛的领域专业知识一定能脱颖而出。我们践行我们的承诺,用数据证实我们的信仰。我们的业务遍及世界各地,所有业务都处于迈向"卓越运营"的不同阶段。当我们根据各个设施的客户结果来比较性能指标时,我们可以看到性能和他们"卓越运营"的程度明显相关。值得注意的是,大多数改进都来自于有效利用"卓越运营"模式中的所有原则,而非仅仅利用数据分析。因此我们认为,在 sub-fab,智能制造必须采用一种整体的方法来使人、机器和工艺实现有效交互。

#### 安全

主持人:安全是任何 fab 运营的关键指标。但是,在增加正常运行时间的同时,持续收集和分析运行参数是如何提高安全性的呢?

EDWARDS:我们都有过这样的经历:能够为一项任务计划并腾出时间,避免赶在最后期限前完成某件事。受压力影响,方法可能是临时方法,风险评估也可能是匆忙做出的。安全依赖于最不可靠的控制,即个人防护用品、程序和标志。

这类控制应该是底牌,而不是优先采用的方法,因为 只有人员严格遵守,并且杜绝人为错误,此类方法才会生 效。依靠设计的解决方案能更好地降低风险。同样重要的 是,在紧急情况下使用临时方法执行的工作很难保证一致 EDWARDS制造的产品种类很多, 所有产品均可通过软件进行调整或 配置。例如,我们的iXH干泵可用于 要求严苛的CVD和ALD工艺,产品 共有116种型号。

性,并且最终会导致性能变化,延长停机时间。使用操作 参数来预测事件可为计划好的工作提供预警。

训练有素的人员可以使用能正确完成工作的安全工具,并遵循精心设计、经过风险评估的标准流程。这样一来,员工不仅能在已知风险得到控制的情况下进行安全的工作实践,而且可以提高结果的一致性,延长设备的正常运行时间。为此,我们会收集安全数据、维护数据和操作参数。这些信息为我们的设备、程序和工具的设计提供了信息。在早期设计阶段,我们使用数据评估任务的次数越多,我们就可以更好地设计特性,以降低风险并提高性能的一致性。我们的"卓越运营"安全文化贯穿了整个安全改进周期。

#### 全面整合

主持人:您能重新定义"卓越运营"模式及其角色吗? EDWARDS:我们的"卓越运营"模式是我们将智能制造引入 sub-fab 的方式:依靠数据分析和领域专业知识实施实操见解的最佳方式。我们的框架能确保人员、机器

和工艺高效协同工作,以实现客户所需的最佳性能和结果。

与所有操作模型一样,它是一个能有效收集和集成多种功能的框架。我们在这篇文章中已经谈到了很多相关内容。但要想正确界定"卓越运营"的作用,我们就必须牢记它的宗旨。"卓越运营"的作用是降低 sub-fab 的风险和不确定性,并通过降低 fab 的成本来增加 sub-fab 的价值。我们通过在结构化方法中应用功能来实现这一目标,以解决客户关注的问题。

仅靠 Edwards 或公司员工无法取得这些成就,这个模型需要全员参与。我们鼓励团队拥有自己的工作场所,并保障场所能够安全有效地运行。如前所述,许多问题需要跨职能部门沟通才能成功解决。我们与客户建立合作伙伴关系,共同管理风险。◆

### 借助虚拟工艺加速工艺优化

作者: Joseph Ervin, 泛林集团半导体工艺整合总监

多数芯片设计师需要基于现有制造工艺来开发新产品,但这些工艺本身也需要工程师来开发。工艺开发,相较于设计新的芯片,对于工程师以及他们的技能要求完全不同。工艺开发的目标在于创造新的半导体制造工艺,不仅要满足器件性能要求,也要保证高良率。

过去的开发人员需要准备多种测试晶圆来确定特定器件的最佳工艺需求。他们需要先制造一组晶圆并对其做分析,然后基于分析结果来改进下一轮的制造工艺步骤。随着特征尺寸的缩小,每次更新的工艺会对变量更加敏感。在测试时还必须考虑之前的开发中可能忽略的特征和寄生现象,

这进一步提高了测试的复杂性和数据量。在最终确定整个工艺流程之前要不断循环重复这一过程,由此带来的时间和成本会不断攀升,因此要将这样的方法用于最先进的技术节点几乎是不现实的。

#### 新结构迎来新挑战

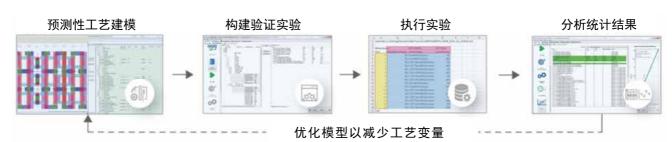

图2. 基于虚拟制造的统计实验。

2020年 12月/2021年 1月 半导体芯科技 www.siscmag.com

图3. 通过SEMulator3D展现的全包围栅极晶体管。

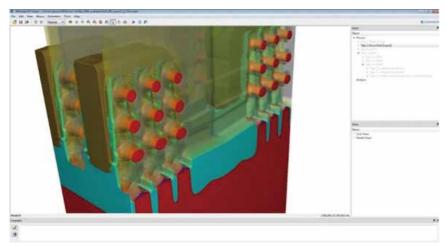

我们不断向先进的 CMOS 微缩和新存储技术转型,导致半导体器件结构日益复杂化。例如,在 3D NAND 内存中,容量的扩展通过垂直堆栈层数的增加来实现,在保持平面缩放比例恒定的情况下,这带来了更高深宽比图形刻蚀工艺上的挑战,同时将更多的阶梯连接出来也更加困难。人们通过独特的整合和图案设计方案来解决工艺微缩带来的挑战,引发了设计规则方面的难题。

二维(2D)设计规则检查(DRC)已不足以用来规范设计,也就达不成特定性能和良率目标。同时完全依赖实验设计(DOE)来进行工艺表征和优化,可操作性变得越发困难。以往工程师通过运用 DOE 实验来节省工艺研发的成本和时间,而现在他们需要进行数以百计的 DOE 才能达到目的,这需要消耗大量的时间和物料,包括晶圆片。此外,工艺步骤之间非直观的交互作用,以及狭窄的工艺窗口,这让通过利用第一性原理建模来实现性能提升和良率优化变得更加困难。因此,需要对复杂工艺流程进行三维建模理解。

#### 使用虚拟晶圆进行测试

如今,我们可以用虚拟制造来代替这种耗时且成本高昂的传统方法。虚拟制造是指用计算机模拟制造真实晶圆的工艺过程,并以可视化工艺流程帮助他们快速了解情况、调整工艺

配方和器件集成方案,并评估各项调整对电性能的影响。半导体工艺工程师可以用虚拟模型来测试制造设备的各种不同配置,其中的变量远超真实场景下的测试。通过模拟整个工艺流程,设计人员可以在几天(而非几个月)内完成数千片晶圆的虚拟制造。

#### 利用统计数据提高良率

基于大量数据的统计分析能够 让开发人员对选定的工艺设置更有信 心。虚拟制造的建模能纳入真实条件 下无法模拟的缺陷和随机变化,让开 发人员能够测试器件架构对工艺流程 中各种不可预测因素的灵敏度。

优化新存储器或逻辑制造流程的 工艺设置方式有数种,其中最简单的 就是选择一个变量并研究其影响。以 关键尺寸(CD)为例,CD标示能满

图4. 建立模型之后的电容器接触点结果,可进行电学分析,研究电容器的边缘效应。

图5. 虚拟测量步骤 (顶部) 可帮助测量结构,包括CD、刻蚀深度和薄膜厚度。结构搜索步骤 (底部) 可确定测量极值、并计算电网组件的数量、如识别网络短路或开路。

23

足电性能要求的器件特征尺寸。开发 人员可以先设定一个从低到高的特定 尺寸范围,然后测试该范围内不同尺 寸数值对器件性能(例如阈值电压) 的影响,他们还可以用这些建模来测 试交叉工序之间的相互作用。

然而,上述方法并不足以研究各 工艺步骤以及最终结构之间错综复杂 的相互作用。我们要用的第二种方法 是蒙特卡洛分析,即随机改变各种工 艺和器件参数,并计算得出最终器件 的几何形状和性能(图 2),这些数据 可以自动定义所需的工艺和设计参数 以满足特定良率和性能的要求。可以 说这是虚拟技术最主要的应用,非常 适用于测试众多不同工艺之间的相互 作用。

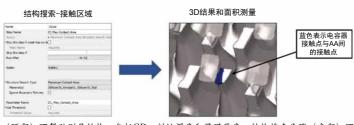

#### SEMulator3D虚拟制造建模

硬掩膜CD

頂部CD后的刻蚀 掩膜开口CD

硅潔度

Vsat

阁下斜丰

SEMulator3D 是 泛 林 集 团 旗 下 Coventor 公司开发的虚拟制造平台,可用于定义所有工艺步骤以及器件建模、指标数据收集、电性与器件分析、结果统计分析和基于图形动画的工艺流程可视化。如今很多半导体公司都在使用该平台来优化和扩展先进的工

顶部CD

结构量测

产生的电气特性

氧化物去除量深度 硅去除量深度

Id=1e-7 A处的Vt

Vt + 2V处的Id

Id=1e-9 A处的斜净

Id截距的Log, Vg=0V

图7. 研究标准模型的物理结构变化的影响 (左)。使用SEMulator3D进行的实验表明,氧化物深度和硅深度对CD变化的敏感性在20nm以上降低,而V<sub>sss</sub>敏感性在相同范围内增加 (右)。

| 节点名称   | 端口      | 初始电压(V) | 电压扫描(V)     |

|--------|---------|---------|-------------|

| 漏极节点   | Drain1  | 0       | 0- 1.1V     |

| 源极节点   | Source1 | 0       | 无,固定        |

| 個极节点   | NGate2  | 0       | 0 - 3V      |

| 村底     | Sub     | 0       | -0.8 - 0.4V |

| SS2    | Source2 | 0       | 无,固定        |

| NGate2 | NGate2  | -0.1    | 无,固定        |

DRAM示例偏置

图6. SEMulator3D可识别3D结构中的器件端口,并像TCAD中那样仿真电学性能,但不需要进行耗时的TCAD建模。

艺节点,开发像 GAA (环绕栅极晶体管) 这样先进的新技术(图 3)。

#### SEMulator3D能提供哪些功能?

SEMulator3D 可 从 一 系 列 标准单元工艺步骤中创建 3D 虚拟工艺整合模型,用来模拟工艺流程。 SEMulator3D 使用完全整合的工艺流程模型,可以预测工艺更改对下游工艺步骤的影响。与之对比,过去需要在晶圆厂中依靠"先制造和后测试"的循环来实现。 替换金属栅极(RMG)FinFET 进行 快速建模,该元件使用先沟槽金属硬 掩模(TFMHM)后段制程(BEOL) 与自对准通孔工艺(SAV)。工程师 在完成虚拟加工的 3D 模型之后,就 可以进行 2D 和 3D 的虚拟测量和电 学性能参数提取。

该软件的电学分析组件增加了电阻和电容提取功能,有助于理解工艺和设计的灵敏度。此外,软件还提供了3D建模和验证电学性能的快捷平台。SEMulator3D使用了具有预测性的工艺模型和能精确匹配实际晶圆的3D结构,比其它孤立解决方案中使用的理想化几何结构更能精确地表征器件,因此具有更高的精度。

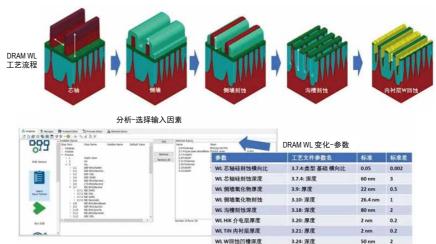

#### DRAM演示

SEMulator3D 是如何根据刻蚀设备的性能参数(如材料的刻蚀选择比和气流流向通量分布)的变化对器件电学性能进行建模的?这里有个简单的关于虚拟制造的 DRAM器件案例研究,它侧重于对栅极刻蚀行为和刻蚀特征的研究,通过对其做合理设定来满足预先设定的电学性能和良率目标。

0.457V

-13.76

7.22e-5A

该演示在虚拟制造中使用了典型的工作流程,包括四个步骤:

- 一个支持工艺校准的标准工艺流程的建立,生成具有预测性的3D结构模型:

- 添加量测参数,以评价器件结构 或电学行为。量测可能包括几何 尺寸测量、3D DRC(设计规则检 查)和电学参数测量;

- 使用 DOE (实验设计) 和校准;

- 数据分析,包括对工艺实现和/ 或设计变更的敏感性分析。

#### 标准工艺流程的建立

这是由 Coventor 开发的演示用 2X DRAM 流程实例,它根据公开数据开发的并未使用客户机密信息。DRAM 的有源区 (AA) 使用自对准四重图形技术 (SAQP) 和倾角 20°的光刻-刻蚀-光刻-刻蚀 (LELE)对多余的图形进行去除,其间距为28nm。掩埋字线使用自对准双重图形化技术 (SADP),间距为40nm,位线使用SADP,间距为44nm。工艺流程在电容器接触点(CC)处结束,这使得软件可以进行电学分析,并能够分析电容器中的边缘效应(图4)。

#### 添加重要度量

每个工艺步骤只需要几个易于理解和校准的几何和物理输入参数。工作流程的下一步是确定重要量工艺参数。就像在 Fab 一样,单元工艺参数如沉积一致性、刻蚀的各向异性和选择比,它们之间相互影响并与其它设计参数交互作用,最终以复杂的方式影响最终器件的结构。

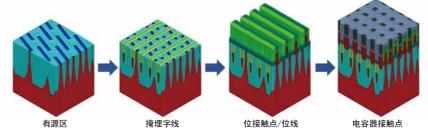

SEMulator3D 支持添加两种几何测量。第一种是虚拟测量,支持测量模型结构并验证结构是否符合预期尺

寸。第二种是结构搜索,相关步骤可以检查整个 3D 模型或某些部分,以确定测量极值,如膜厚度、线宽和接触面积的数值和位置。它还可以计算电网组件的数量,这有助于识别电网短路或开路(图 5)。

当几何偏差的位置随工艺的变化而变化时,对接触区域进行结构搜索显得特别有效。图 5显示了 CC 和AA 之间的接口最小面积。软件将高亮显示该位置,使之容易成为器件失效的故障点。

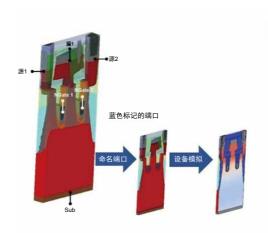

#### 器件电学性能模拟

器件的电学性能参数可以通过器件电学性能模拟来提取。通过使用与图 5 相同的模型,可以在SEMulator3D中进行器件电学仿真。

SEMulator3D 有助于识别 3D 结构中器件的端口和电极,并模拟器件的特性,如温度、带隙和电子/孔迁移率。该软件允许手动和自动识别节点(一个或多个连接在一起的引脚),初始电压或电流可以与选定节点的电压扫描一起设置。

图 6 中的电学仿真示例显示了两个栅极、两个源、一个漏和一个衬

底。工程师可以自由设置偏置电压或 初始电压以及电压扫描,如 DRAM 示例偏置电压表所示。

然后,工程师可以使用 SEMulator3D 自动提取重要电学性能指标,如一个电压点上的阈值电压  $(V_{th})$ 、亚阈值摆幅 (S)、漏致势垒下降 (DIBL) 和开启电流  $(I_{ON})$ 。这些功能无需耗时和严格的 TCAD 建模即可实现,同时可以体现 3D 工艺变化对电学性能的影响。

#### 物理结构变化的影响

工程师要对因物理结构改变而造成的影响进行研究,首先需要检查标准模型中参数的设定,包括硬掩模CD/顶部CD、硅深度和氧化物深度。SEMulator3D使用以上参数构建模型然后提取对应的器件电学参数,包括V<sub>1</sub>, I<sub>ON</sub>, I<sub>OF</sub>, 和亚阈值摆幅(图 7 左)。

本研究的目的是将图 4 中的硬掩模 CD 以 2nm 的增量从 12nm 变化至30nm,同时监测其他结构参数,包括硅深度和氧化物刻蚀。此变化是通过更改流程早期工艺步骤来实现的,并且下游工艺步骤对模型更改的响应符合预测。

图8. SEMulator3D利用数百甚至数十次DOE试验,使用回归分析来识别对特定指标有显著影响的关键工艺参数。

25

图 7(右)显示,硬掩模 CD 变化对栅极刻蚀具有非线性响应。氧化物深度和顶部硅深度对较小 CD 的顶部 CD 很敏感,但在较大 CD 上趋于饱和。另一方面,当 CD 高于 20nm标准值时, $V_{\text{tsat}}$  值显著增加。因此,SEMulator3D 的指标揭示了对单个物理结构变化的各种响应,有利于工程师研究物理结构变化对所选参数造成的影响。

#### 识别重要的工艺步骤

在 DOE 参数变化研究中,采用了蒙特卡洛分析法对 DRAM 字线(WL)深度进行演化分析,以确定重要的工艺步骤(图 8)。

WL工艺参数值是通过基于平均 值或标准值和标准差的高斯分布随机 设置的。演示中选择了50个实验。 然而,通常至少需要100个实验才能 获得有意义的数据。

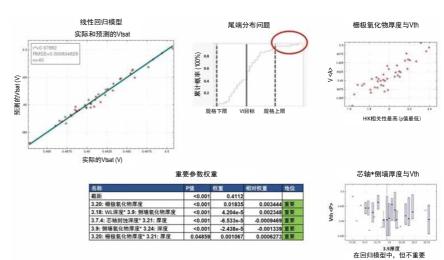

DOE 运 行 时, 阈 值 电 压 V<sub>t</sub> 在 0.4837~0.5031V 之 间 变 化。 SEMulator3D 的回归分析有助于识别 对阈值电压影响显著的 5 个参数,这 些参数的 p 值小于 0.5,不支持原假设(图 9)。需要注意的一点是第一个参数(截距)被排除在本讨论之外,因为它始终是列表的一部分。

基于上述量测结果,我们发现有待进一步研究的五个最重要的因素是:栅极介电层厚度(最重要的参数)、字线刻蚀深度和侧墙厚度的交叉项、芯轴刻蚀深度和栅极厚度的交叉项、间隔氧化物厚度和抛光深度的交叉项、栅极介电厚度和侧墙厚度的交叉项。

线性回归曲线的R方值为0.97882,说明模型与数据吻合较好。栅极氧化层厚度与V<sub>b</sub>图显示出很强

图9. 工程师可以在SEMulator3D中分析任何量测结果,以识别重要参数,极端情况如图中红圈标示。

的相关性,而芯棒间隔厚度与 $V_{th}$ 图则没有相关性,因此可以认为它不是一个重要参数。

DOE 的结果还可以帮助识别一些特殊情况,例如规格下限(LSL)到规格上限(USL)范围之外的 V<sub>h</sub>,工程师可以通过这两个 V<sub>h</sub> 值检查并找到造成这种结果的工艺条件。

#### 工艺优化

为了从不同的角度进行优化,我们可以将电学性能作为研究的目标,比方说使用电学性能参数目标值作为工艺步骤优化的目标。每个工艺步骤 参数都可以改变,以寻找满足电气性能的条件。

根据所使用的制造设备,在软件中定义了每个刻蚀行为的允许范围。因此,可以根据材料的刻蚀选择比、横向比、聚合/锥度、溅射和离子通量分布等参数来定义刻蚀行为。利用DOE确定的重要输入参数,输入电学性能指标。

SEMulator3D 采用直接优化的方法,以确定 WL 刻蚀工艺中最佳刻蚀 步骤行为的工艺参数,以满足电学性

能目标。校准工艺建议包括氧化层、 硅和氮化层的刻蚀选择比、氧化层和 硅的刻蚀角度和选择比等参数。

根据这些结果,可以通过工艺 研究验证是否存在满足条件的电学性 能,或者在此范围内是否无法实现特 定的电学性能。

#### 结语

由于工艺假设是在开发早期甚至 在硬件实现之前完成的,因此虚拟工 艺无需制造真正的晶圆来验证这些假 设,大大节省了器件开发时间和成本 投入。

DRAM 案例研究表明,通过在虚拟环境中执行大量的 DOE (实验设计)和工艺变化研究,可以消除不相关 DOE 路径的时间和成本,并快速实现性能和良率目标,从而加快产品上市时间。

这样的虚拟制造技术代表了半导体工艺开发的未来,能让新的工艺提前数月问世,并为领先的半导体公司带来高达数亿美元的市场机会。◆

### 用于IC制造的非接触式测量技术

SONOTEC利用其在制药和其他高可靠性市场上积累的数十年经验,为半导体制造商推出非接触式超声波传感器监测技术和产品,并提供高度准确的系统,此类系统专为增加正常运行时间和提高安全性、同时节约资源而设计。

满足全球对高质量微电子器件的需求方面,半导体制造商面临着许多共同的要求和挑战。尽管各个行业的技术、应用和工艺方法差异很大,但是,所有制造商都有一个共同的需求,那就是在将原始硅衬底转变为可靠成品所需完成的绝大多数生产工艺中,都需要进行高度准确且安全的工业化学品输送。

对半导体制造而言,对化学品流体进行精确、可重复和高效测量与控制是不可或缺的。实现这一目标面临着各种各样的挑战,因为工艺化学品和废弃副产品的管控、贮存、分配和移动会接触到通常是超纯且需要小心搬运的化合物,这些化合物有很多是有毒、有腐蚀性和磨蚀性(或粘附性)的,而且在多变的条件下还会易燃。工艺化学品虽然至关重要,但是,如果操作失误、发生泄漏或分配不当,那么也有可能被视为一种真正的"女巫佳酿(witch's brew)"式的潜在风险。

在处理工艺化学品的过程中,一项真正的挑战是,我们必须用这种方式进行测量:既不改变化学品流动或导致管道内气泡形成,测量过程又不会将易燃化合物暴露于潜在的火源之下。生产人员的生命和健康与此息息相关,更不用说那些价值数百万美元的工艺设备和正在制程中的晶圆片了。

在生产线的前前后后正确地测量、分配和管控化学品,有许多可选方案。就像所有设计用来与多种化合物一起使用的制程设备一样,每台设备都有其优点和局限性。理想情况下,化学监测系统应包括传感器,能在不阻碍化学流动的情况下进行准确的测量,即便在流速降至极低水平时也能继续完成准确的测量。为了保证拥有上述理想性能,传感器应当连续多年执行高度准确和可靠的操作,它们的价格应是可以承受的,并能提供灵活性以满足各种工艺设备的要求,而且,它们能无缝地融入工厂现有的制造监测

图1. 用于在硬管和管道上进行测量的SEMIFLOW非接触式超声波液体流量传感器,适合用在可能存在失火或爆炸风险的危险区域中(符合Zone 1、Group IIB标准)。

环境中,无需单单为了促成它们的使用而全部推到重来、 重新设计功能架构。SONOTEC 的传感器专家声称,其产 品系列之所以成功,植根的基础就在于满足了上述要求。

在其他高可靠性应用领域取得多年的成功之后, SONOTEC 开发了不断成长的半导体生产用流量传感器和 控制装置产品线。

SONOTEC 成立于 1991 年,该公司称其 SEMIFLOW 产品线是从创建非接触式超声波流量计过程中积累的经验 发展而来,此类流量计面向生物医药和医疗设备领域中的高度灵敏应用,像半导体制造一样,其运行必须遵守严格的规定,同时满足所有特定的安全要求。SONOTEC 设备能够提供高度准确、实时和高达 400L/min 的瞬时流量测量、流量总计,并支持多种标准工业接口。它所有的传感器皆基于该公司在应对各种管道特性和几何结构方面具备的渊博专业知识。

SONOTEC 公司国际战略和销售经理Anika Baumhauer认为, SONOTEC从2016年开始进入面向IC

作者: MARK ANDREWS, SiS 技术编辑

27

制造商的传感器领域,这是该公司在 其他传统行业中产生的自然产物,在 这些行业的大多数应用中,许多不同 化合物的测量和控制必须既准确、又 不是侵入式的。

她说:"在半导体行业严格的质量管理中,公司厂家越来越多地寻求用以优化其相关工艺制程的可选方案。非接触式流量计和气泡探测器能

图2. SONOCHECK ABD06气泡探测传感器能够精确地发现低至管道内径1/3的气泡,从而保护关键的工艺参数。

够监视和控制液体流动过程,并没有发生泄漏或污染的任何风险。直接通过管道或塑料管进行测量,而不接触具有磨蚀性、粘附性、腐蚀性和高纯度的液体,此做法所具有的优势大幅度地增加了对于这种测量设备的需求,而此类测量设备在 SONOTEC 的产品库中处于核心地位。"

SONOTEC 的高准确度非接触式传感器系统使该公司的在线式流量传感器 (inline sensor) 产品得到补充。Baumhauer 指出,这两种装置对于准确测量均很重要,但是它们的非接触式器件尤为引人注目,因为此类器件能以夹持的方式固定在现有的流入和流出管道上,从而加快安装和校准速度。

SEMIFLOW 传感器配有 4 个按 X 形图案排列的超声波换能器。这些换能器以一定的频率将脉冲超声波从一侧发射到另一侧,测量超声波顺着液体流向和逆着液体流向的飞行时间。两者最终的时间差与液体的平均流速成正比。Baumhauer 解释说:平均流速乘以管道横截面积可计算出流量结果。

采用渡越时间法测量流速既不会在管道中引起压力下降,也不会导致发生泄漏的风险。Baumhauer表示,一旦传感器得到了适当的校准,那么对于几乎所有的均质液体来说,无论其粘度、密度、色彩或电磁特性如何,其流速的高准确度测量都是能够做到的。SONOTEC 传感器不需要依据液体内的离子或微粒物质来计算测量的结果。

SONOTEC 向半导体市场的扩张始于亚洲,随后为该

公司开辟在欧洲和美国半导体行业的市场机会。自从该公司在亚洲启动市场之后,SONOTEC 现在与那里的主要半导体设备制造商开展了合作,并实现了其亚洲业务的两位数增长。

SEMIFLOW 传感器是经过业界验证的尖端测量仪器,它兼具坚固性和创新的钳形设计,可以避免产生污染和泄漏的任何风险,不会有系统故

障停机时间的烦扰。这些传感器具有紧凑小巧的外壳,纳 入了内置电子元器件和分析单元,还保持了堪比单个换能 器的细小占位面积,这些优势令人叹服。因此,它们能够 容易地整合到现有的工序链和流程架构中。

Baumhauer 指出, SEMIFLOW 系列产品提供不同尺寸的传感器和通道,适合各种各样的管道直径,它们非常适合可溶性聚四氟乙烯 (PFA)、聚四氟乙烯 (PTFE)及其他硬塑料管和管道。Baumhauer表示,鉴于需要准确测

量易燃化合物,因此 SONOTEC 的 新型 SEMIFLOW Ex1 Set 代表了一个专为满足这些要求而特别设计的新产品类别。这些本质上很安全的超声波流量

别。这些本质上很 图3. SONOFLOW IL.52流量传感器: 用于在充满液体 宏全的 招声 油 浴 县 的管道中进行超低流量测量的流量传感器。

传感器用在中小尺寸硬质塑料管上进行非接触式测量,可以在危险区域中确保操作安全。SEMIFLOW CO.66 PI Ex1 传感器符合 IIB 气体组标准,提供了因气体、蒸汽和液体引起的爆炸危险的保护(图 1)。按照 ATEX/IECEx 标准,对于在 Zone 1 中使用的设备,防护级别(EPL)为"Gb"。通过安放 SONOTEC 新颖的隔离盒 Barrier Box ST Ex1,安全性得到了保证。该隔离盒用于限制输送到传感器的能量,以避免发生着火危险,这符合 IEC 60079-11 下续来32页

一旦传感器得到了适当的校准,那么对于几乎所有的均质液体来说,无论 其粘度、密度、色彩或电磁特性如何,其流速的高准确度测量都是能够做 到的。SONOTEC传感器不需要依据液体内的离子或微粒物质来计算测量的 结果。

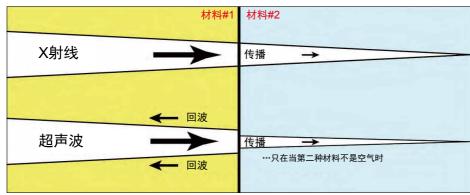

### 器件的X射线和声学3D成像

X射线和超声波均能以无损的方式对电子组件等固体物体的内部特征进行成像。由于两种方法为成像使用了不同形式的能量,因此运用这两种方法皆可极大地提高解决问题的能力和速度。大多数图像是二维的,但是上述两种方法也能够创建内部特征的三维图像,而且同样是以不同的方式完成。

X 射线通过某种特定的材料传播时,它会以材料独特的速率衰减。虽然超声波的传播机制与之有着很大的不同,与 X 射线表现的一样:通过特定的材料其能量也会以自己独特的速率衰减。

如果这两种类型的能量同时经过相同的材料(图1),并且在两种材料之间遇到相同的键合界面,那么X射线会径直穿过该界面并继续前进,尽管在第二种材料中它的衰减速率很可能有所不同。然而,超声波脉冲将部分反射回接收器,部分穿过界面继续传播。这两部分各自所占的比例由两种材料的特性决定,数值范围很宽。但是,倘若第二种材料是气体(比如空气),则几乎100%的脉冲都将被反射回来,而穿过界面向前传播的脉冲基本为零。

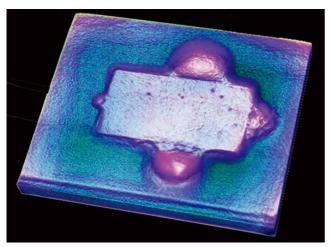

制作 3D X 射线图像与制作二维平面图像有着相当大的差异。三维图像依赖于从一个角度观察物体。为了制作 3D 图像,将光束(或物体)旋转到各种不同的角度,并从每个视图收集数据。然后采用软件以数字方式在 3D 中创建操作员想要的视图。这个过程有点类似于人体的 CAT (计算机辅助断层摄影术) 扫描,该扫描旨在获得人体骨骼和其他内部结构的 3D 图像。图 2是 TO-220 封装器件

裸晶片 (die) 区域的 3D X 射线图像。位于图中央的矩形 物品即为裸晶片。通过采用 Nordson DAGE Quadra 7 系统 完成成像。以下是一些观察结果:

- 裸晶片是平坦的,但是边缘提供了其垂直尺寸的某些暗示。

- 有两根导线连接至裸晶片的顶面,但是在这种分辨率下它们是不可见的,原因是它们非常薄,而且,相对于密封封装的总厚度来说,它在X射线束衰减中引起的变化微乎其微。

- 在裸晶片的4个侧面上都有明显的痕迹,它们是从裸晶片下方挤出的粘接材料。某些挤出区域的亮度并不表示更大的高度或反射的可见光,而是暗示构成裸晶片粘接材料的物料所产生的衰减小于模混合物(mold compound)或散热器,由此造成的结果是:穿过挤出物顶部的光束的衰减幅度要小于那些通过其他区域的光束。由于衰减较少,它们的成像因而更加明亮。

- 在裸晶片上大约有6个非常小的黑色特征,大多是在右侧。它们代表了密度足以使X射线束局部衰减的材料。它们肯定不是孔洞,因为孔洞看起来会比周围区

域更加明亮。它们也许是小的杂 质粒子,且很有可能位于裸晶片 的上方。

超声波以一种截然不同的方式创建 3D 图像。超声波传感器在样本上方来回扫描,每秒钟将几千个脉冲发送到样本中。从内部界面反射的回波直接返回到接收器。不过,如果某个表面与光束远非垂直,那么脉冲会以很大的

图1. X射线束 (上) 和超声波脉冲 (下) 在遇到介于两种固体之间的材料界面时所呈现的反应。

作者: TOM ADAMS, NORDSON SONOSCAN公司顾问

图2. TO-220封装的裸晶片区域的三维 X射线图像。

角度反射, 而回波将会丢失, 从而在图像中形成一个暗区。

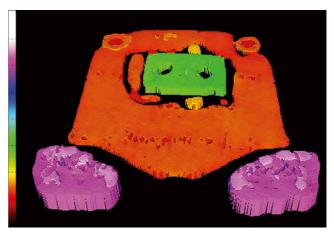

图 3 所示的 TO-220 封装与图 2 中成像的 TO-220 封装是相同的,不过是采用超声波进行成像的,并在图像的底部显示出引线。图 3 是用 Nordson SONOSCAN C-SAM®超声显微镜制作的飞行时间图像。在这种成像模式中,到达接收器的回波根据它所到达的时间被分配一种颜色。在图 3 左侧的垂直色图中,最高的特征(即引线)为粉红色,裸晶片为绿色,而散热器(最深部的界面)为橙色。

每个回波的传播时间被换算成距离。在样本(比如 TO-220 封装)的完整 3D 扫描之后,就得知了从器件顶面到所有成像内部界面上的每个 x-y 反射位置的距离。

整个器件封装的厚度为 6.4mm。"栅极"(回波被接受用于成像的垂直幅度)从略低于器件的顶面一直延伸到低于散热器的顶端。散热器的橙色表面比晶片的底部高约1mm、比顶部高2mm左右,而且比引线的顶端高很多(大约5mm),因而造成导线未能成像。

如果从正上方观察, TO-220 封装的 3D 超声图像看起来是平坦且多彩的。观察者可以推测每个特征的深度,但是不能直接看到深度。因此,超声 3D 图像通常是从一

图3. 相同封装的超声图像, 区别是它包含了引线在内。

#### 个倾斜角度观看的。

在图 3 中,位于中央的晶片是绿色的(几乎在色图的中间位置上),这是因为它高于散热器。图像中的晶片看似相当厚,但实际上很可能比看上去的要薄得多,3D软件为了实现 3D效果而夸大了厚度。在制作 3D图像时,超声波能看到特征的顶面,但是无法看到物体的垂直侧(如果有的话),于是它采用与特征顶部相同的颜色创建了一个直边。如果顶面不是平坦的,则侧壁可能具有多种颜色。

这幅图像显示,在晶片的顶面中没有可见的裂纹。晶片中的两个黑色斑点是连接导线的位置。导线的截面为圆形,当超声波脉冲击中导线时,它会向很多方向反射,基本上没有机会被返回给负责记录其距离的传感器。没有超声波通过导线传播至晶片表面。传感器"看到"的是一个没有返回信号的区域,于是将这个区域着色为黑,并让其具有彩色内壁。

靠近晶片的大部分区域也是黑色的,即"无返回信号"。在这些区域中,从晶片下方挤出了过多的晶片粘接材料,并形成了陡峭的隆起。由于这些隆起不是平坦的,因此来自传感器的超声波再次散射,且未接收到任何信号。在晶片左边的橙色"孤岛"差不多是平坦的,下珠\*32页

穿过靠近粉色引线的散热器水平布设的是一排相当直的模缝线。它们的排列形式和小尺寸表明,这不是散热器中的某种异常型缺陷,而更有可能是封装表面及穿透封装表面的字母数字的声影;也即:从散热器返回而被字母数字导致轻微变形的回波。

### 适合大批量、自动化及可靠3D半导体 焊点分析的最佳方案

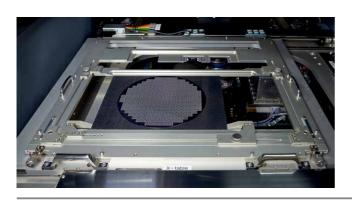

由于在晶圆、衬底、基材上或最终产品的组件中可能存在缺陷,因此在半导体制造中,需要进行自动化、高质量、可靠而快速的无损检测与分析,以实现最优生产。

**Y**XLON FF65 CL 是一款新型 X 射线检测系统,专门设计用于三维集成电路 (3D IC)、微机电系统 (MEMS) 和传感器,针对这些器件中最小且最苛刻的特征进行最佳的自动分析。结果是:测试和检测极其精确且具有可重复性,性能表现出色。

FF65 CL 采用 2D 和 3D X 射线技术,这些技术基于开放式纳米聚焦 X 射线源,经过验证且具有高功率 targets,最新一代优化型高分辨率 X 射线探测器,以及高精度的全自动化操作系统。总体来说,这些领先的组件使FF65 CL 成为凸焊、平坦的焊料连接和填充过孔自动分析的理想解决方案,它很容易发现不润湿的凸焊、空洞和错位,且具有可重复性。

有别于其他同类产品,YXLON FF65 CL 的独到之处在于它具有较大的检测面积 (510×610mm),且检测深度小于300nm,因而非常适合对凸焊和填充过孔进行自动和无损分析,如3D IC、倒装芯片和晶圆片中的硅通孔(TSV)。系统创新的真空机构在分析过程中能够安全而精确地保持样品,并抵消样品翘曲的影响。

FF65 CL 是全球分辨率最佳的 3D X 射线检测系统,

YXLON的根源要追溯到伦琴(W.C. Röntgen)于1895年发现的X射线,穆勒(C.H.F. Müller)于1896年吹制出第一根X射线管。YXLON成立于1998年,我们的名字代表着无损的质量保证,包括电子元件和组件、各类铸件和不同材料、增材制造、车轮和轮胎、焊缝,以及更多正在生产、研究和开发中的零部件。

用于 IC 封装缺陷的全自动化验证。它包括四项特性:高速 3D AXI、极其精确的缺陷尺寸测量、生产过程条件的可靠检查,以及可生成报告的全自动化检测解决方案。

FF65 CL 可以提供两种关键功能,包括 2D(自上而下) X 射线透视,以及 3D (CL 成像生成)自动化分析功能;分别由不同部件实现,前者是高性能平板检测器;后者是一个位于可倾斜旋转的独特操作组件内部的高分辨率图像增强器。最新一代纳米聚焦 X 射线管可生成能够显示和测量最小空洞和特征的 2D 和 3D 图像,使得 YXLON FF65 CL 能用于分析最苛刻的先进半导体难题。

图形用户界面(GUI)便于使用且直观,允许用户轻 松创建自动化、多点和多功能分析检测程序。通过自动、

YXLON供稿

连续地监测系统各个方面的背景校准测试,确保了随时间 变化的测量重复性。

在电子行业里,YXLON是数字X射线透视(DR)、计算机层析成像(CL)和计算机断层扫描(CT)检测系统的市场领导者,它不断地开展创新,并恰到好处地在用户需要的场合提供相应的解决方案。YXLON FF65 CL 秉承了这一传统,旨在确保为半导体行业应对当前和未来的制造挑战给予全面支持。我们相互关联的全球服务网络具有7个区域服务中心和50多家当地合作伙伴,做好准备为客户提供快速而高效的支持,以确保他们实现最高的产品质量和最少的故障停机时间。

YXLON 的根源要追溯到伦琴(W.C. Röntgen)于 1895 年发现的 X 射线, 穆勒(C.H.F. Müller)于 1896 年 吹制出第一根 X 射线管。YXLON 成立于 1998 年,我们 的名字代表着无损的质量保证,包括电子元件和组件、各 类铸件和不同材料、增材制造、车轮和轮胎、焊缝,以及 更多正在生产、研究和开发中的零部件。

在 SMT 和半导体领域中,我们的微聚焦 X 射线 (DR) 和 CT 系统均可满足电子、微电子和机电产品的安全性、可靠性和节约成本型测试的个性化要求。

对于检测裂缝、焊点或空腔开裂、测量孔隙及评估其分布来说, X 射线是最可靠的技术。检测可以采用手动、半自动或全自动的方式完成,并提供有关制造过程的有价值信息。作为一种附加的传感器,通过大量数据集的传输, X 射线系统被认为是现代智慧型工厂的一个重要组成部分。◆

上接第28页

标准。另外,此 Barrier Box 还给身处 Ex-Zone 之外的操作人员提供了所有必要的电源和数据接口,并让传感器在危险区域里可以安全地使用,这符合 Zone 1、Group IIB 国际标准。

#### 结论

跨产品线的半导体制造具有许多共同的要求,包括液体(化学品)流动须精确、可重复利用,高效测量与可控

制性好。实现这一目标面临着各种各样的挑战,因为工艺化学品和废弃副产品的管控、贮存、分配和移动会接触到通常是超纯且需要小心搬运的化合物,这些化合物有很多是有毒、有腐蚀性、有磨蚀性(或粘附性)的,而且其中不少也有可能是易燃的。SONOTEC 的 SEMIFLOW 传感器产品线是经过业界验证的尖端测量仪器,拥有稳健的可靠性;其创新的钳形设计是为消除产生污染和泄漏的任何风险而研发的,并不会受到系统故障停机时间的烦扰。◆

上接第30页

并代表了模混合物从散热器的分层剥离。在这个位置上的 薄分层与 X 射线图像是一致的, X 射线图像在这里没有 显示任何特征,原因是:分层对于 X 射线是不可见的。

在橙色散热器的远端是两个差不多呈圆形且橙色较浅的特征。它们是位于散热器正上方的模化合物中的模缝线 (mold mark)。穿过靠近粉色引线的散热器水平布设的是一排相当直的模缝线。它们的排列形式和小尺寸表明,这不是散热器中的某种异常型缺陷,而更有可能是封装表面及穿透封装表面的字母数字的声影;也即:从散热器返回而被字母数字导致轻微变形的回波。

TO-220 封装图像中最明显的特征是两条粉色引线。

它们是长而直的引线的末端,这些引线延伸到距离器件封 装相对较远的地方。与晶片和其他结构一样,软件采用顶 部高度报告的颜色来显示引线侧壁,它们实际上比在这里 看起来还要薄。

综上所述,这两幅 3D 图像让我们对 TO-220 封装有了大致的了解。超声波发现了有可能呈现的分层剥离,X 射线则发现了可疑的黑暗特征。另外,超声波和 X 射线都能以多个连续的水平切片来完成样本的成像:每个切片创建自己的图像,结果很像样本的幻灯片放映,一次播放一个用户定义层。与这里所示的 3D 图像一样,这两组图像完整详尽地展现了封装的内部结构。◆

### 快速的DDR4 SDRAM开创宇航新时代

了发掘宇航市场的潜力,卫星运营商正通过提供增值服务,如超高分辨率成像、流媒体视频直播和星上人工智能,提升星上处理的能力以减少下行链路的需求。从 2019 年到 2024 年,高吞吐量载荷的市场需求预计增长 12 倍,带宽增至 26,500Gbps。

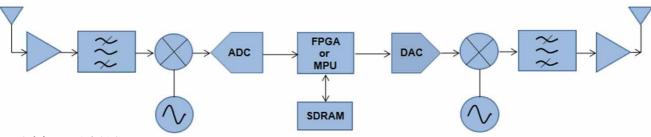

这些应用都和存储器的容量和速度密切相关,如FPGA、存储器、宽带 ADC 和 DAC。一个 12 位 1.5Gsps 采样率的 ADC 每秒产生 18Gb 的原始数据。一分钟的压缩 SAR 信息需要大约 70Gb 的存储容量。这对现有的宇航级存储器解决方案的 I/O 带宽、访问时间、功耗、物理尺寸和存储容量提出了很大的挑战。

和存储是必不可少的。然而,该如何找到一款合适的有足够容量、速度和可靠性的宇航级大容量存储器。

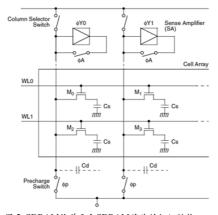

SDRAM (同步动态随机存取内存)是一种快速而大容量的半导体技术,它由单元的逻辑阵列和基本的存储元件组成,每个存储元件都包括一个电容和一个 FET 组成的控制门电路。每个单元存储一个比特,比如图 2 所示的简单 4 比特存储器来举例。每一行的电压控制晶体管的通断,并对相关的电容充电或放电。在每个所需的"字线"充电之后,列选择器选择对应的电容,准备接下来的读/写操作。由于自放电效应,这些单元必须周期性刷新,包括读和数据写回的操作。

图 1. 数字高吞吐量载荷的架构。

这是一个数字高吞吐量载荷的典型架构,它需要使用一个字航级 FPGA 或一个快速微处理器 (MCU) 进行星上处理 (图 1)。最新的 FPGA 基于超深亚微米工艺,一般包含大约 30Mb 的片上存储器,而 CPU 会更少。基于

这一架构的电信、地球观测和科学载荷多使用 Xilinx 的XQRKU060、Microchip 的RTPolarFire 或 NanoXplore 的宇航级 FPGA,需要额外的快速片外存储器来存储这些应用产生的大量数据。

下一代高吞吐量卫星服 务须具备怎样的数据处理能 力呢?据分析,实时处理, 结合大带宽数据的快速压缩 SDRAM 架构包含许多存储单元,这些存储单元组成行和列的二维阵列。要选择某一个比特,需首先确定对应的行,然后确定对应的列。当对应的行开启时,可以访问多个列,从而提高连续读/写的速度并降低延迟。

D3 4

D0 4

D1 /

图 2. SDRAW位于元和SDRAW总并以组织结构

作者: Rajan Bedi博士, Spaceships公司CEO及创始人

33

| 表 1 | SDR | $\Delta M$ | 掀制    | 直 | 估    | 表  |

|-----|-----|------------|-------|---|------|----|

| жı. | SUL |            | イ兄 市り |   | TEL. | Æ. |

| COMMAND                                                | cs | RAS | CAS | WE | ADDR        |

|--------------------------------------------------------|----|-----|-----|----|-------------|

| Command inhibit (NOP)                                  | Н  | Х   | Х   | Х  | X           |

| No operation (NOP)                                     | L  | Н   | Н   | Н  | Х           |

| Active (select bank and activate row)                  | L  | L   | Н   | Н  | Bank/row    |

| READ (select bank and column, and start READ burst)    | L  | Н   | L   | Н  | Bank/column |

| WRITE (select bank and column, and start WRITE burst)  | L  | Н   | L   | L  | Bank/column |

| PRECHARGE (deactivate row in bank or banks)            | L  | L   | Н   | L  | X           |

| AUTO REFRESH or SELF REFRESH (enter self refresh mode) | L  | L   | L   | Н  | Х           |

为了增加字容量,存储器使用多个阵列,这样当需要进行一次读/写操作时,存储器只需要寻址一次访问每个阵列中的1个比特。

为了增加存储器的整体容量,SDRAM 的内部结果还包含多个 bank,这些 bank 互相交织,进一步提高了性能,并可以独立寻址(图 2)。

当需要执行读或写操作时,首先存储器控制器发出 ACTIVE 命令,激活对应的行和 bank。操作执行完毕后, PRECHARGE 命令关闭一个或多个 bank 中的一个对应的 行。除非之前的行被关闭,否则无法打开新的行。

SDRAM 的操作通过如下的控制信号实现:片选(CS)、数据屏蔽(DQM)、写使能(WE)、行地址选通(RAS)和列地址选通(CAS)。后面的三个信号决定发出哪个命令,如表 1 所示:

从 1992 年至今, SDRAM 已发展了数代:最早的版本是单倍数据速率(SDR)型 SDRAM,其内部时钟频率和 I/O 速率相同。SDR型 SDRAM一个时钟周期只能读或写一次,在开始下个操作之前必须等待当前操作完成。

双倍数据率 (DDR) 型 SDRAM 通过在两个时钟边沿传送数据,在不提高时钟频率的情况下使 I/O 传送的速度加倍,从而实现了更大的带宽。这是采用一种 2n 预读取的架构,其内部数据路径是外部总线宽度的两倍,允许内部频率是外部传送速度的一半。对于每个读操作,可获

取 2 个外部字,而对于每个写操作,两个外部数据字在内部合并,并在一个周期内写入。DDR1 是一种真正的源同步设计,通过使用双向数据选通在一个时钟周期捕捉两次数据。

DDR2型 SDRAM 的外部总线速度是 DDR1的双倍 I/O 传送速度的两倍。它使用 4n 预读取的缓冲,内部的数据路径是外部数据总线宽度的四倍。DDR2的时钟频率可设置成 DDR1的一半,实现相同的传送速度;或相同的速率,实现双倍的信息带宽。

DDR3型 SDRAM 的外部总线速度是 DDR2 双倍 I/O 传送速率的两倍,使用 8n 预读取架构。它的内部数据路 径的宽度是 8 比特,而 DDR2 是 4 比特。DDR3 的时钟频率可设置成 DDR2 的一半,实现相同的传输速度;或相同的速率,实现双倍的信息带宽。

表 2 列出了当前卫星和航天器制造商可用的宇航级 SDRAM 的选项。

为了实现下一代高吞吐量卫星的服务,未来的载荷需要更快、更大容量、更小尺寸和更低功耗的星载存储器。 小卫星星座对尺寸和功耗有更严格的限制,而 OEM 厂商 也需要更大的存储带宽来实现实时应用。

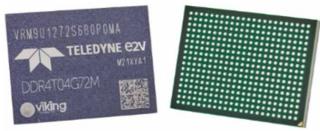

DDR4 SDRAM 是 Teledyne-e2v 首个面向宇航应用的耐辐射存储系列。DDR4T04G72是一款72比特4GB(32Gb)的存储器,目标 I/O 速度 2400MT/s,有效带宽 153.6Gbps

表 2. 当前的宇航SDRAM选项。

| SDRAM | Capacity<br>(Gb) | Data Bus<br>(bits) | Clock Frequency<br>(MHz) | Transfer Speed<br>(MT/s) | Bandwidth<br>(Gbps) |

|-------|------------------|--------------------|--------------------------|--------------------------|---------------------|

| SDR   | 0.5 to 4         | up to 72           | 133                      | 133                      | up to 9.6           |

| DDR   | 8                | up to 72           | 100 to 200               | 200 to 400               | up to 28.8          |

| DDR2  | 8                | up to 72           | 200 to 400               | 400 to 800               | up to 64            |

| DDR3  | 24               | up to 72           | 300 to 666               | 600 to 1,332             | up to 95.9          |

图 3. 耐辐射DDR4T04G72, 4 GB DDR4存储器。来源: www.e2v.cn/products/

(带 ECC)或 172.8Gbps(不带 ECC)。器件采用紧凑型封装, 15x20x1.92mm PBGA,包含391个焊球,间距 0.8mm(图 3)。 这款器件可提供 -55℃ ~+125℃和 -40℃ ~+105℃两种温度范围,其有铅的版本经过 NASA Level 1 和 ESCC class 1 的质量认证。将来公司计划发布 8GB (64Gb)的版本。

对于防辐射性能, DDR4T04G72 的 SEL 阈值超过 60.8 MeV.cm²/mg, SEU 和 SEFI 的阈值分别是 8.19 和 2.6 MeV.cm²/mg, 目标 100 krad (Si) TID 免疫。

4GB DDR4T04G72 是一款包含 5 个裸片的 MCM, 其中 4 个是 1 GB (8 Gb) 的存储容量,512Mb×16bits 结构,分为两个组,每个组有 4 个 bank。为了提高可靠性,器件采用了 72 比特的数据总线,包含 64 比特的数据和 8 比特的错误检测与纠正。这个 ECC 功能是通过第五个裸片实现的。器件使用内部的 8n 预读取缓冲,实现高速操作,提供可编程的读写操作和额外的延迟。

DDR4的供电电压的典型值是 1.2V。DDR4T04G72的物理尺寸和功耗与市面上的宇航级 SDRAM 的对比。功耗在很大程度上与下面几个因素相关:器件的架构、时钟频率、供电电压、执行的操作、器件的状态(如使能、预充电或读/写)、每个状态的持续时间、是否使用 bank 交织和 I/O 电路的实现(如终端电路)。SDRAM 在系统中的使用方式不同会对功耗产生很大的影响。对于系统设计,非常重要的一点是,您需要考虑存储器如何被访问、如何

被特定的 PDN 驱动以及如何设计散热方案。 DDR4 也支持 2.5V 的电压 V<sub>m</sub>, 其为器件提供字线加速以提升效率。

您可以从 Teledyne e2v 获取 DDR4T04G72 的 IBIS、SPICE、热模型和散热估算表。若您想把这款器件配合 Xilinx 的 XQRKU060 宇航级 FPGA 一起使用,Teledyne e2v 可以提供使用 Vivado® Design Suite 生成 DDR4 控制器 IP 的配置文件供您参考。

您也可以选择下图这款小型单基板 44x26mm 的模块, 包含 DDR4T04G72 DDR4 SDRAM 和一款耐辐射四核 64 比特 ARM® Cortex® A72 CPU, 其工作频率高达 1.8GHz。 对于这款宇航级模块,目前 Teledyne e2v 还未决定提供有 铅还是 RoHS 的封装。

图4. 耐辐射QLS1046-4GB quad ARM core和DDR4T04G72 DDR4存储器。

DDR4 将为宇航产业提供高吞吐量板上计算的方案,提高采集系统的性能,使诸如超高分辨率成像、流媒体视频直播和星上人工智能等新一代地球观测、宇航科学和电信应用变为可能。

DDR4T04G72 使卫星和航天器的制造商第一次可以使用大存储带宽技术,而类似的技术在商业领域已经使用了6年了。与市场上的经过认证的 DDR3 SDRAM 相比,DDR4T04G72 可与最新的宇航级 FPGA 和微处理器配合使用,存储器可实现如下特征参数:带宽增加62%、传输速度加倍、存储容量增加25%、物理尺寸缩小76%。◆

表 3. SDRAM的参数比较。

| SDRAM | Capacity<br>(Gb) | Transfer Speed<br>(MT/s) | Consumption (W) | Package                                   | Size<br>(mm)   | Supply<br>(V) |

|-------|------------------|--------------------------|-----------------|-------------------------------------------|----------------|---------------|

| SDR   | 4                | 133                      | 0.35            | SOP 54 to 88                              | 27.4×13.8×12.1 | 3.3           |

| DDR   | 8                | 200 to 400               | 0.4 to 1        | SOP 66 to 86, BGA239                      | 27.6×13.8×12.2 | 2.5           |

| DDR2  | 8                | 400 to 800               | 1 to 3          | SOP 74 to 88, BGA95 to 191<br>QFP144, CGA | Various        | 1.8           |

| DDR3  | 24               | 600 to 1,332             | 1 to 3          | BGA 95 to 259                             | 20×14×8.5      | 1.5           |

| DDR4  | 32               | 2,133 to 2,400           | 0.9 to 1.5      | PBGA 391                                  | 15×20×1.9      | 1.2           |

### 图神经网络加速器的FPGA解决方案

应用Achronix公司推出的Speedster7t系列高性能FPGA,可设计出高能效、可扩展的GNN加速器。

益于大数据的兴起以及算力的快速提升,机器学习技术在近年取得了革命性的发展。在图像分类、语音识别、自然语言处理等机器学习任务中,数据为大小维度确定且排列有序的欧氏(Euclidean)数据。然而,越来越多的现实场景中,数据是以图(Graph)这种复杂的非欧氏数据来表示的。Graph不但包含数据,也包含数据之间的依赖关系,比如社交网络、蛋白质分子结构、电商平台客户数据等等。数据复杂度的提升,对传统的机器学习算法设计以及其实现技术带来了严峻的挑战。在此背景之下,诸多基于 Graph 的新型机器学习算法—GNN(图神经网络),在学术界和产业界不断的涌现出来。

GNN 对算力和存储器的要求非常高,其算法的软件实现方式非常低效,所以业界对 GNN 的硬件加速有着非常迫切的需求。我们知道传统的 CNN(卷积神经网络网络)硬件加速方案已经有非常多的解决方案;但是,GNN 的硬件加速尚未得到充分的讨论和研究,在本文撰写之时,Google 和百度皆无法搜索到关于 GNN 硬件加速的中文研究。本文的撰写动机,旨在将国外最新的 GNN 算法、加速技术研究、以及笔者对 GNN 的 FPGA 加速技术的探讨相结合起来,以全景图的形式展现给读者。

#### GNN 简介

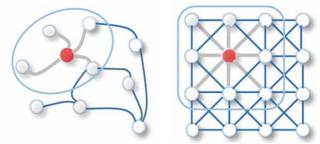

GNN 的架构在宏观层面有着很多与传统 CNN 类似的地方,比如卷积层、Polling、激活函数、机器学习处理器 (MLP) 和 FC 层等等模块,都会在 GNN 中得以应用。下图展示了一个比较简单的 GNN 架构。

图 1. 典型的GNN架构。来源: arXiv.org

但是, GNN 中的 Graph 数据卷积计算与传统 CNN 中的 2D 卷积计算是不同的。以图 2 为例, 针对红色目标节点的卷积计算, 其过程如下:

**Graph 卷积**:以邻居函数采样周边节点特征并计算 均值,其邻居节点数量不确定且无序(非欧氏数据);

**2D 卷积**:以卷积核采样周边节点特征并计算加权平均值,其邻居节点数量确定且有序(欧氏数据)。

图 2. Graph卷积和2D卷积。来源: arXiv.org

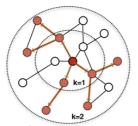

#### GraphSAGE算法

学术界已对 GNN 算法进行了非常多的研究讨论,并提出了数目可观的创新实现方式。其中,斯坦福大学在2017 年提出的 GraphSAGE 是一种用于预测大型图中动态新增未知节点类型的归纳式表征学习算法,特别针对节点数量巨大、且节点特征丰富的图做了优化。如下图所示,GraphSAGE 计算过程可分为三个主要步骤:

邻节点采样:用于降低复杂度,一般采样2层,每一 层采样若干节点:

聚合:用于生成目标节点的 embedding,即 graph 的 低维向量表征;

**预测**:将 embedding 作为全连接层的输入,预测目标节点 d 的标签。

为了在 FPGA 中实现 GraphSAGE 算法加速,我们需要知悉其数学模型,以便将算法映射到不同的逻辑模块中。这里暂不做详述。对于每一个待处理的目标节点 Xv,GraphSAGE 执行下列操作:

作者: 袁光 (Kevin Yuan) , Achronix资深现场应用工程师

from neighbors

3. Predict graph context and label using aggregated information

1. Sample neighborhood

图 3. GraphSAGE算法的视觉表述。来源: snap.stanford.edu

- 1) 通过邻居采样函数 N(v), 采样子图 (subgraph) 中的节点;

- 2) 聚合被采样的邻节点特征,聚合函数可以为 mean()、lstm() 或者 polling() 等;

- 3) 将聚合结果与上一次迭代的输出表征合并,并以 W<sup>k</sup> 做卷积;

- 4) 卷积结果做非线性处理;

- 5) 迭代若干次以结束当前第 k 层所有邻节点的处理;

- 6) 将第 k 层迭代结果做归一化处理;

- 7) 迭代若干次以结束所有 K 层采样深度的处理;

- 8) 最终迭代结果 Zv 即为输入节点 Xv 的嵌入。

#### GNN加速器设计挑战

GNN 的算法中涉及到大量的矩阵计算和内存访问操作,在传统的 x86 架构的服务器上运行此算法是非常低效的,表现在速度慢、能耗高等方面。

新型 GPU 的应用,可以为 GNN 的运算速度和能效 比带来显著收益。然而 GPU 内存扩展性的短板,使其无 法胜任海量节点 Graph 的处理, GPU 的指令执行方式, 也造成了计算延迟过大并且不可确定,无法胜任需要实

图5. Achronix的Speedster7t1500高性能FPGA架构。来源: Achronix.com

时计算 Graph 的场景。

述多的界可度 计内如由计在需支发、容易以并算存额,一持实巨量所,是是一个

带宽、以及在数据中心范围可扩展的 GNN 加速解决方案。

#### GNN加速器的FPGA设计方案

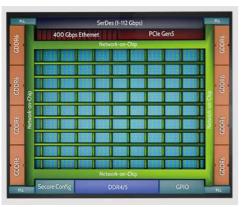

Speedster7t 系列高性能 FPGA,专门针对数据中心和机器学习工作负载进行了优化,消除了 CPU、GPU以及传统 FPGA 存在的若干性能瓶颈。

Speedster7t FPGA 基于台积电的 7nm FinFET 工艺, 其架构采用创新的 2D 片上网络 (NoC), 独创的机器学习处理器矩阵 (MLP), 并利用高带宽 GDDR6 控制器、400G 以太网和 PCI Express Gen5 接口, 在保障 ASIC 级别性能的同时, 为用户提供了灵活的硬件可编程能力(图 5)。

为此,针对IC设计工程师在GNN加速器设计中所面临的挑战,Achronix Speedster7t1500 FPGA器件为其提供了完美的解决方案。

表1. GNN设计挑战与Achronix的Speedster7t1500 FPGA解决方案。

| GNN设计挑战  | Speedster7t1500解决方案                   |

|----------|---------------------------------------|

| 高速矩阵运算   | MLP机器学习处理器矩阵                          |

| 高带宽低延迟存储 | LRAM+BRAM+GDDR6+DDR4                  |

| 高并发低延迟计算 | FPGA使用可编程逻辑电路,在硬件层面<br>确保低高并发延迟计算     |

| 内存扩展     | 基于4*400Gbps的RDMA,确保在数据中心范围以极低延迟扩展内存访问 |

| 算法不断演进   | FPGA使用可编程逻辑电路,在硬件层面<br>确保算法可升级重配      |

| 设计复杂     | 丰富的硬IP减少开发时间和复杂度,<br>NoC简化模块间互连并提高时序  |

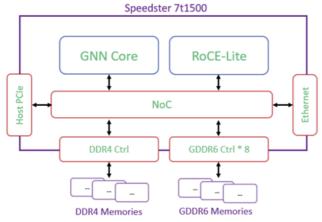

#### (1) GNN 加速器顶层架构

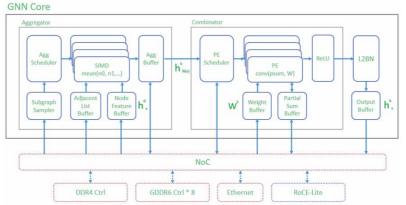

本 GNN 加速器针对 GraphSAGE 进行设计,但其架构具有一定的通用性,可以适用于其他类似的 GNN 算法加速,其顶层架构如图 6 所示。

图中 GNN Core 为算法实现的核心部分,其设计细节将在下文展开谈论;RoCE-Lite 为 RDMA 协议的轻量级版本,用于通过高速以太网进行远程内存访问,以支持海量节点的 Graph 计算,其设计细节将于后续文章中讨论;400GE 以太网控制器用来承载 RoCE-Lite 协议;GDDR6用于存放 GNN 处理过程中所需的高速访问数据;DDR4作为备用高容量内存,可以用于存储相对访问频度较低的数据,比如待预处理的 Graph;PCIe Gen5x16 提供高速主

图6. GNN加速器顶层架构。来源: Achronix

机接口,用于与服务器软件交互数据;上述所有模块,皆通过 NoC 片上网络来实现高速互联。

#### (2) GNN Core 微架构

在开始讨论 GNN Core 微架构之前,我们先回顾一下本文首页关于 GraphSAGE 算法的小结中,其内层循环的聚合以及合并(包含卷积)等两个操作占据了算法的绝大部分计算和存储器访问。通过研究,我们得到这两个步骤的特征如表 2 所示。

可以看出,聚合操作与合并操作,其对 计算和存储器访问的需求完全不同。聚合操 作中涉及到对邻节点的采样,然而 Graph 属 于非欧氏数据类型,其大小维度不确定且无 序,矩阵稀疏,节点位置随机,所以存储器 访问不规则并难以复用数据,在合并操作中,其输入数据

访问不规则开难以复用数据,在合并操作中,其输入数据 为聚合结果(节点的低维表征)以及权重矩阵,其大小维 度固定,存储位置规则线性,对存储器访问不存在挑战, 但是矩阵的计算量非常大。

基于以上分析, 我们决定在 GNN Core 加速器设计中

表2. GNN算法中聚合与合并操作对比。来源: arxiv.org

|         | 聚合操作<br>(Aggregation) | 合并操作<br>(Combination) |

|---------|-----------------------|-----------------------|

| 存储器访问模式 | 间接访问,不规则              | 直接访问,规则               |

| 数据复用    | 低                     | 高                     |

| 计算模式    | 动态,不规则                | 静态,规则                 |

| 计算量     | 低                     | 高                     |

| 性能瓶颈    | 存储                    | 计算                    |

用两种不同的硬件结构来处理聚合操作与合并操作,功能 框图如图 7。

聚合器(Aggregator): 通过 SIMD(单指令多数据处理器)阵列来对 Graph 进行邻居节点采样并进行聚合操作。其中的"单指令"可以预定义为 mean() 均值计算,或者其他适用的聚合函数;"多数据"则表示单次 mean() 均值计算中需要多个邻居节点的特征数据作为输入,而这些数据来自于子图采样器(Subgraph Sampler);SIMD 阵列通过调度器 Agg Scheduler 做负载均衡;子图采样器通过 NoC 从 GDDR6 或 DDR4 读回的邻接矩阵和节点特征数据  $h^0v$ ,分别缓存在 Adjacent List Buffer 和 Node Feature Buffer 之中;聚合的结果  $h^kN(v)$  存储在 Agg Buffer 之中。

**合并器(Combinator)**:通过脉动矩阵 PE 来执行聚合结果的卷积操作,卷积核为 W<sup>k</sup> 权重矩阵,卷积结果通过 ReLU 激活函数做非线性处理,同时也存储在 Partial

图7. GNN Core功能框图。来源: Achronix

Sum Buffer 中以方便下一轮迭代。

合并的结果通过 L2BN 归一化处理之后,即为最终的 节点表征  $h^k v$ 。

在比较典型的节点分类预测应用中,该节点表征 h<sup>k</sup>v 可以通过一个全连接层 (FC),以得到该节点的分类标签。此过程属于传统的机器学习处理方法之一,没有在GraphSAGE 论文中体现,此设计中也没有包含这个功能。

#### 结论

本文深人讨论了 GraphSAGE GNN 算法的数学原理, 并从多个维度分析了 GNN 加速器设计中的技术挑战。作 者通过分解问题并在架构层面逐一解决的方法,综合运用 Achronix Speedster7t1500 FPGA 所提供的竞争优势,创造 了一个性能极佳且高度可扩展的 GNN 加速解决方案。◆

### 瑞萨电子将继续深入中国市场 并深化与本地客户的合作

020 年对于全球所有人及企业而 ■情的爆发及蔓延对每一个普通人 的生活、企业以及行业来说都是一个 重大的挑战。在疫情带来诸多挑战的 同时,另一方面我们也看到正是由于 疫情的爆发扩散,促进了工业、基础 设施和物联网领域各类应用的发展。 其中, 比较典型的, 人们对网络带宽、 笔记本电脑、PC 和平板电脑以及用 于医疗保健、空气质量监测应用设备 的需求在不断增长。同时,5G也是 疫情之下我们所看到的增长领域之 一。监控和语音用户界面开始变得越 来越重要,因为当下人们变得越来越 敏感,希望通过减少各类触摸抑制病 毒的传播。

我们从瑞萨电子两大事业部来看 具体的 2021 年发展展望: 在非汽车 领域(物联网及基础设施事业本部, IIBU),数据和数据中心相关领域以 及对数据需求的爆炸式增长仍旧是 我们一大关注点。我们提供从网络核 心,从内存和接口、光学产品到低延 迟 HBM (一直到网络端点)的所有 解决方案。从面向消费者的消费类电 子、无线计算,到高性能计算,我们 的方案一应俱全。

正如集团 CEO 及 CFO 在我们的 战略会议上所公开的, 我们已经在这 一方面实现了盈利目标。而在汽车电 子领域(汽车电子解决方案事业本部, ABU), CASE (Connected Car 互 联 汽车, ADAS/自动驾驶, Mobility Service 移动服务, xEV 的统称)和 网关控制各个域以支持车辆 E/E 架构 的中央控制型已成为 OEM 及组件制 造商重点关注的领域。瑞萨电子将专 注于 ADAS/ 自动驾驶, xEV 和 E/E 架构 (网关+DCU)。立足于瑞萨电子 在车辆控制领域极具影响力的 MCU, 集成高端 ADAS/ 自动驾驶和网关的 SoC 业务。此外,我们还将扩展模拟 和电源产品到 xEV (BMIC/IGBT), ADAS/自动驾驶传感器(Lidar/ Radar) 领域,这一战略也已经通过 Intersil / IDT 的收购付诸实践。

中国显然是全球半导体产品最大 的消费国之一。我们不断努力与尽量 与众多本土公司进行深入合作,并希 望将中国长期视为我们的良好合作伙 伴, 使瑞萨电子成为客户可信赖的优 质产品及服务供应商。瑞萨电子本着 扎根中国、服务中国的原则, 一直致 力于推动我们在中国的本土化活动。 我们的研发和销售团队遍布全球,中 国也是其中一个重要据点。我们在北 京、上海、深圳、成都以及武汉(光 电子领域)拥有庞大的业务。我们在 支持客户需求方面非常多样化,包括 与中国本地公司的战略合作。

就在 2020 年 12 月 1 日, 瑞萨电

子刚宣布与中 国一汽集团在 中国长春成立 联合实验室, 展开深度合 作,助力中国 一汽打造其智 发平台, 共同 瑞萨电子中国董事长

能驾驶自主开 真凤朋光 (Tomomitsu Maoka) 瑞萨电子集团高级副总裁,

开发自动驾驶、智能座舱、动力总成、 车身控制等车载电控系统解决方案, 并将首先应用于一汽旗舰品牌红旗车

2020年,几乎整个行业都受到 新冠疫情的重大影响,包括工作和生 活方式的转变。目前,疫苗成功开发 的好消息已经传来, 但考虑到全球疫 情现状, 2021 年整体经济形势仍有很 大的不确定性。然而,于半导体产业 而言并非只有忧没有喜;实际上,世 界各地的人们通过利用 IT 工具不断 提高生产率,并且越来越关注"绿色" 环境。这些趋势将推动对高性能及高 效率半导体产品的需求,并将推动更 多的创新。中国政府已经通过抗疫过 程展示了如何使用这些技术来应对危 机。由于从危机中迅速复苏,中国经 济增长势头迅猛,预计该态势明年也 将得以持续。为顺应这一趋势, 瑞萨 电子将通过向中国客户提供最好的产 品和服务来继续专注于中国市场。◆

39

### 广告索引 Advertisers Index

| Advertiser         | 广告商名称 | 网址                                    | 页码  |

|--------------------|-------|---------------------------------------|-----|

| INNOLAS            |       | innolas-semiconductor.com             | 9   |

| SEMICON China 2021 |       | www.semiconchina.org www.fpdchina.org | IBC |

| 中建南方               |       | www.zjnf.cn                           | 1   |

#### 欢迎投稿

《半导体芯科技》(Silicon Semiconductor China, SiSC)是面向中国半导体行业的专业媒体,已获得全球知名权威杂志《Silicon Semiconductor》的独家授权。本刊针对中国半导体市场特点遴选相关优秀文章翻译,并汇集编辑征稿、采编国内外半导体行业新闻、深度分析和权威评论等多方面内容。本刊由香港雅时国际商讯(ACT International)以简体中文出版发行。

本刊内容覆盖半导体制造工艺技术、封装、设备、材料、测试、MEMS、mini/Micro-LED 等。文章重点关注以下内容:

#### FAB (Foundry, IDM, OSAT, R&D)

四个环节:晶圆制造(wafer 后道)、芯片制造、先进封装、洁净室;深入报道与之相关的制造工艺、材料分析,工艺材料、工艺设备、测试设备、辅助设备、系统工程、关键零备件,以及与 particle(颗粒度)及 contamination(沾污)控制等厂务知识。

#### FARI ESS

芯片设计方案、设计工具,以及与掩膜版内容和导入相关的资讯。

#### 半导体基础材料及其应用

III-V 族、II-VI 族等先进半导体材料的科学研究成果、以及未来热门应用。

《半导体芯科技》欢迎读者、供应商以及相关科研单位投稿,已甄选中文稿件将在印刷版杂志以及网上杂志刊登;IC 设计及应用等半导体相关内容将酌情予以网络发表(微信推送、杂志网站)。本刊优先刊登中文来稿(翻译稿请附上英文原稿)。

#### 技术文章要求

- 论点突出、论据充分:围绕主题展开话题,如工艺提升、技术改造、系统导入、新品应用,等等。

- 结构严谨、短小精悍:从发现问题到解决问题、经验总结,一目了然, 字数以3000字左右为宜。

- 3. 文章最好配有 2-4 幅与内容有关的插图或图表。插图、图表按图 1、图 2、表 1、表 2 等依次排序,编号与文中的图表编号一致。

- 4. 请注明作者姓名、职务及所在公司或机构名称。作者人数以四人为限。

- 5. 文章版权归著作者,请勿一稿多投。稿件一经发表如需转载需经本刊同意。

- 6. 请随稿件注明联系方式(电话、电子邮件)。

#### 新产品要求

- 1. 新产品必须是在中国市场新上市、可在中国销售的。

- 新产品稿件的内容应包含产品的名称、型号、功能、主要性能和特点、 用途等。

- 3. 新产品投稿要求短小精悍,中文字数 300~400 字左右。

- 4. 来稿请附产品照片,照片分辨率不低于 300dpi,最好是以单色作为背景。

- 5. 来稿请注明能提供进一步信息的人员姓名、电话、电子邮件。

电子邮箱: mizyH@actintl.com.hk, sunnieZ@actintl.com.hk

#### 行政及销售人员 Administration & Sales Offices

#### 行政人员 Administration

#### HK Head Office (香港总部)

#### ACT International (雅时国际商讯)

Unit B, 13/F, Por Yen Building,

No. 478 Castle Peak Road,

Cheung Sha Wan, Kowloon, Hong Kong

Tel: 852 28386298

Publishing Director ( 出版总监)

Adonis Mak (麦协林), adonism@actintl.com.hk

Editor-in-Chief (编辑)

Sunnie Zhao (赵雪芹), sunnieZ@actintl.com.hk Mizy He (贺贵鸿), mizyH@actintl.com.hk

Sales Director (销售总监)

Eva Liu (刘婷), evaL@actintl.com.hk

General Manager-China (中国区总经理)

Michael Tsui (徐旭升), michaelt@actintl.com.hk

#### **London Office**

Hannay House, 39 Clarendon Road Watford, Herts, WD17 1JA, UK. T: +44 (0)1923 690200

#### Coventry Office

Unit 6, Bow Court, Fletchworth Gate Burnsall Road, Coventry, CV5 6SP, UK. T: +44 (0)2476 718 970 Publisher & Editor-SiS English

Jackie Cannon, jackie.cannon@angelbc.com +44 (0)1923 690205

#### 销售人员 Sales Offices

#### China (中国)

#### Shenzhen (深圳)

Jenny Li (李文娟) jennyl@actintl.com.hk Gavin Hua (华北平), gavinH@actintl.com.hk Tel: 86 755 25988573 /25988567

#### Shanghai (上海)

Hatter Yao (姚丽莹), hattery@actintl.com.hk Helena Xu (许海燕), helenax@actintl.com.hk Amber Li (李歆), amberL@actintl.com.hk Tel: 86 21 6251 1200

#### Beijing (北京)

Cecily Bian (边团芳), cecilyB@actintl.com.hk Tel: 86 135 5262 1310

#### Wuhan (武汉)

Eva Liu (刘婷), evaL@actintl.com.hk Tel: 86 138 8603 3073

Sky Chen (陈燕), skyc@actintl.com.hk

Tel: 86 137 2373 9991

Grace Zhu (朱婉婷), graceZ@actintl.com.hk Tel: 86 159 1532 6267

#### Hong Kong (香港特别行政区)

Mark Mak (麦协和), markm@actintl.com.hk Tel: 852 2838 6298

#### Asia

#### Japan (日本)

Masaki Mori, masaki.mori@ex-press.jp Tel: 81 3 6721 9890

#### Korea (韩国)

Lucky Kim, semieri@semieri.co.kr Tel: 82 2 574 2466

#### Taiwan, Singapore, Malaysia (台湾,新加坡,马来西亚)

Regional Sales Director

Mark Mak (麦协和), markm@actintl.com.hk Tel: 852 2838 6298

#### US (美国)

Janice Jenkins, jjenkins@brunmedia.com Tel: 724 929 3550

Tom Brun, tbrun@brunmedia.com

#### Tel: 724 539 2404 Europe (欧洲)

Shehzad Munshi, Shehzad.Munshi@angelbc.com Tel: +44 (0)1923 690215

Jackie Cannon, Jackie.cannon@angelbc.com Tel: +44 (0) 1923 690205

# SEMICON® CHINA FPDCHINA 跨界全球·心芯相联

**CONNECT · COLLABORATE · INNOVATE**

2021年3月17-19日 上海新国际博览中心

预注册赢iWatch!

www.semiconchina.org www.fpdchina.org

## 半导体芯科技

### SILICON CHINA

从中国政府定立的长期目标,与及中国半导体行业的潜在规模,催化了《半导体芯科技》(Silicon Semiconductor China)中国版杂志的诞生。目前,中国的半导体消耗量达全世界的60%,但其中约 90%的半导体需要依靠进口。从更广阔的背景来看,中国已经启动了自己的工业4.0计划,以便与欧洲 和北美的制造能力相竞争。"中国制造2025"的目标之一是升级和增加包括信息技术、机器人和汽车业在 内的十个关键领域的国产零部件含量。

为了提升半导体制造能力,中国政府计划在未来10年至少投资1770亿美元,以建立中国自己的芯 片产业。目前,中国正在建设中的晶圆厂有24座。

多年来,面向全球的Silicon Semiconductor英文版杂志也一直为中国半导体行业的专业人士提供服 务,但现在是时候推出一本独立的《半导体芯科技》(Silicon Semiconductor China)中文版杂志了。