# SILICON SEMICONDUCTOR

VOLUME 46 ISSUE X 2025

AN ANGEL BUSINESS COMMUNICATIONS PUBLICATION

SILICONSEMICONDUCTOR.NET

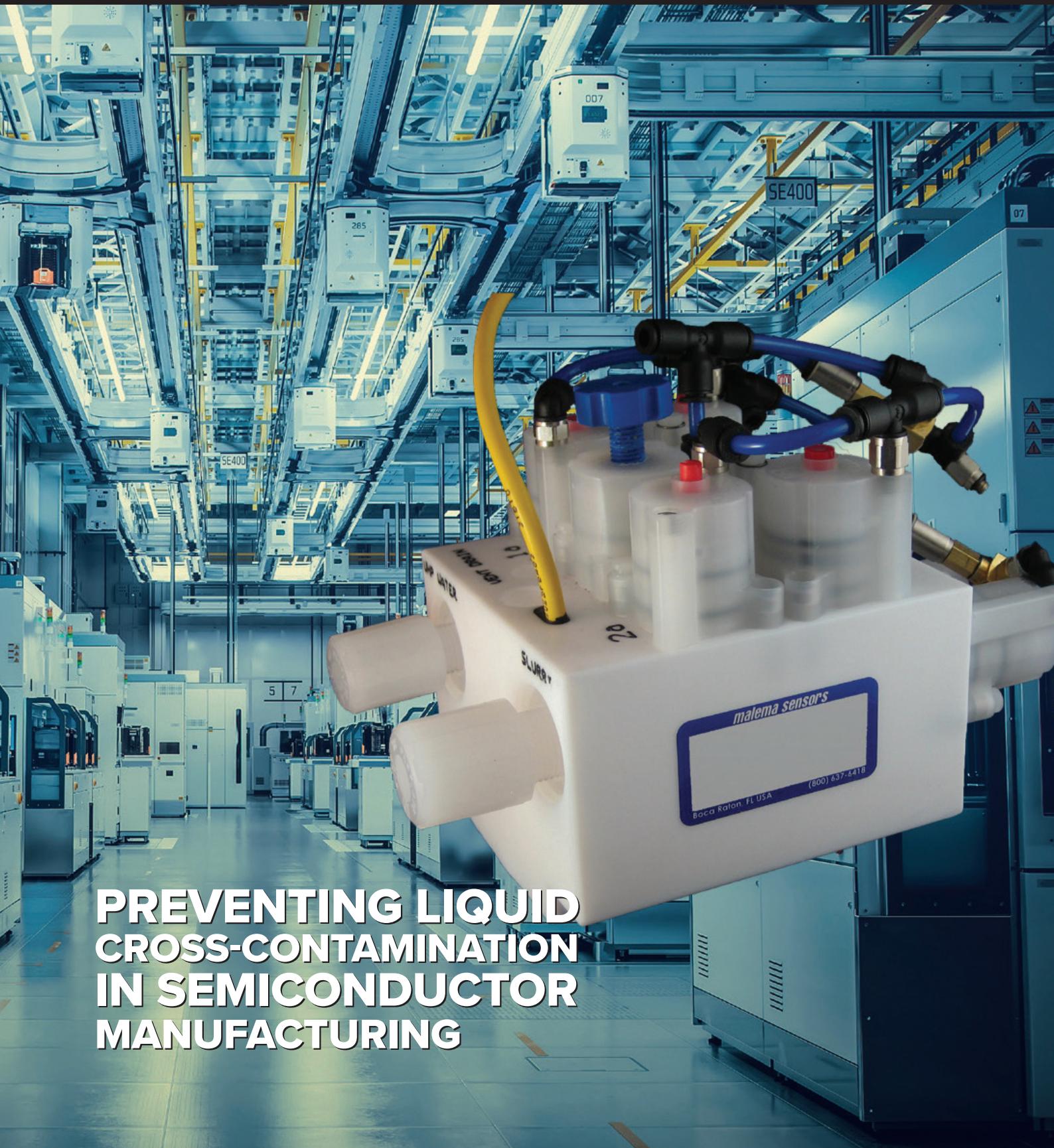

**PREVENTING LIQUID

CROSS-CONTAMINATION

IN SEMICONDUCTOR

MANUFACTURING**

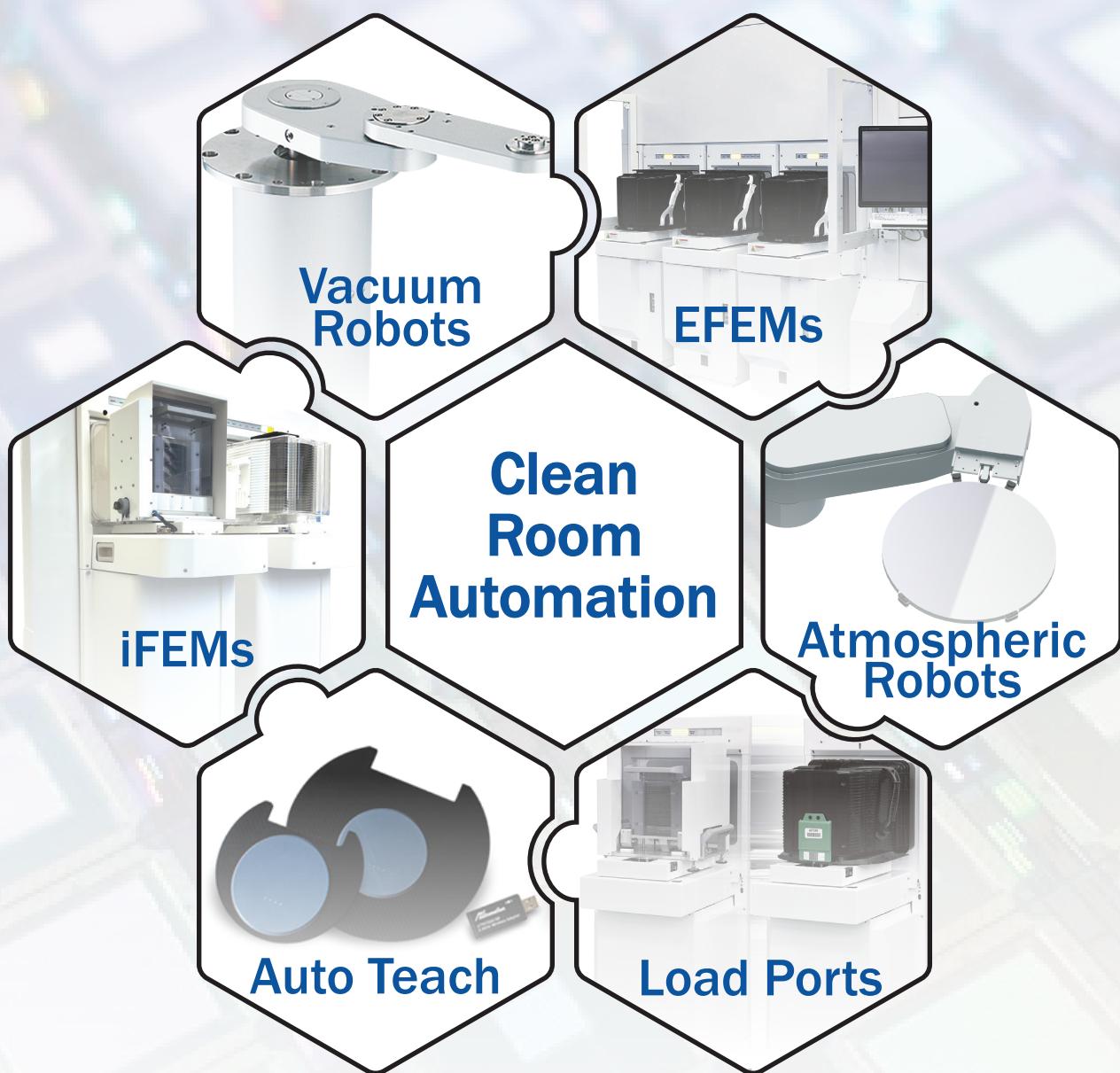

# AES motomation

Providing innovative and competitive solutions worldwide. From individual modules to entire platforms, for semiconductor and flat panel display industry as well as laboratory automation.

Visit us at Semicon Europa and Semicon West or

[www.motomation.com](http://www.motomation.com)

With our partners at :

**JEL**

JEL CORPORATION

**SINFONIA**

**Nidec**

## Looking ahead to 2026: scale, skills and the shape of silicon

AS the semiconductor industry looks toward 2026, the message from the data seems unambiguous: scale is back, complexity is accelerating, and the industry's future will be shaped as much by people and policy as by process technology. SEMI's latest forecasts, projecting equipment sales of \$145 billion in 2026 on the way to a record \$156 billion in 2027, confirm that this cycle is structurally different from those of the past. AI is not merely another demand driver; it is redefining how and where the industry invests.

In 2026, AI-driven capital expenditure will dominate the agenda. Leading-edge logic at 2nm, aggressive HBM ramps, and sustained DRAM and NAND upgrades will keep wafer fab equipment on a strong growth trajectory. Yet the real inflection point lies beyond the front end. Advanced packaging — from chip-to-substrate thermo-compression bonding to fan-out and panel-level processing — is rapidly becoming the industry's critical enabler. Recent wins by ASMPT and ACM Research underscore a broader truth: heterogeneous integration is no longer optional. It is the only viable path to scaling performance, yield and cost in an AI-centric world.

At the same time, back-end test and inspection are emerging as strategic bottlenecks. As devices grow larger, denser and more complex, the ability to validate performance, reliability and thermal behaviour at speed will be a defining competitive advantage in 2026. Software, AI-enabled automation and advanced metrology — exemplified by innovations in 3D image analysis and fab automation — will increasingly differentiate suppliers and manufacturers alike.

Another defining theme for 2026 is energy. AI's explosive compute demand is colliding with physical and

environmental limits, pushing power efficiency to the forefront of system and chip design. Silicon photonics is rapidly moving from promise to necessity. GlobalFoundries' expansion in photonics manufacturing and Europe's growing policy focus reflect a broader industry realisation: electrons alone cannot sustain AI's trajectory. Expect 2026 to be the year when photonics transitions decisively from infrastructure to integration, reshaping data centres, packaging architectures and foundry roadmaps.

Geopolitics and regionalisation will continue to influence investment patterns. China, Taiwan and Korea will remain the top equipment destinations, but Europe's role is evolving. The European Chips Act, its forthcoming 2.0 iteration, and initiatives such as Finland's 200 mm R&D upgrades signal a more determined push toward sovereignty — not just in fabs, but across materials, equipment, design and packaging. However, capital alone will not be enough.

Perhaps the most underestimated challenge heading into 2026 is talent. Europe's looming shortfall of skilled semiconductor workers highlights a global issue: advanced fabs, photonics lines and AI-driven manufacturing systems cannot run without a new generation of cross-disciplinary engineers. Skills in system design, AI-enabled hardware, cybersecurity and manufacturing automation will be as critical as lithography expertise.

Looking ahead, 2026 will not simply be about building more tools or fabs. It will be about building an ecosystem capable of sustaining unprecedented complexity — technologically, energetically and humanly.

For your free weekly e-news roundup go to: [siliconsemiconductor.net](http://siliconsemiconductor.net)

## COVER STORY

### Preventing liquid cross-contamination in semiconductor manufacturing

Producing high-purity wafers via the CMP process is a critical application and the halting of harmful slurry-DIW cross-contamination and back-flow can be optimised with the Malema™ Interconnect Interlock Device.

18

### 14 R&D advances for the FAMES Pilot Line

CEA-Leti, coordinator of the FAMES Pilot line, has a major milestone for next-generation chip stacking: fully functional 2.5 V SOI CMOS devices fabricated at 400 °C

### 16 Driving success for customers

Alan Maher, Business Development Manager, Greene Tweed, shares his thoughts on the industry's current buzz topics, as highlighted at SEMICON West, before outlining what is keeping the company busy, both now and into the future

### 22 Safety, purity and performance in semiconductor cleanroom environments

Advanced Almatec® AODD pumps play a vital role in next-generation semiconductor manufacturing

### 26 Maximising advanced packaging hinges on manufacturing process optimisation

Unlocking packaging's promise will require solving upstream manufacturing process bottlenecks and rethinking global semiconductor supply chain strategies

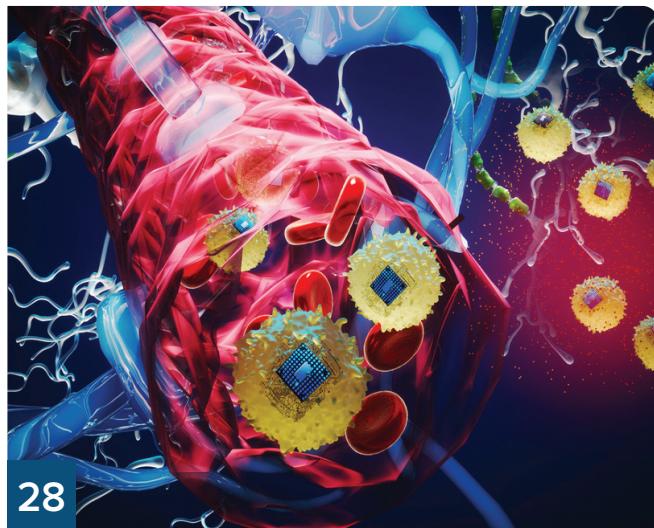

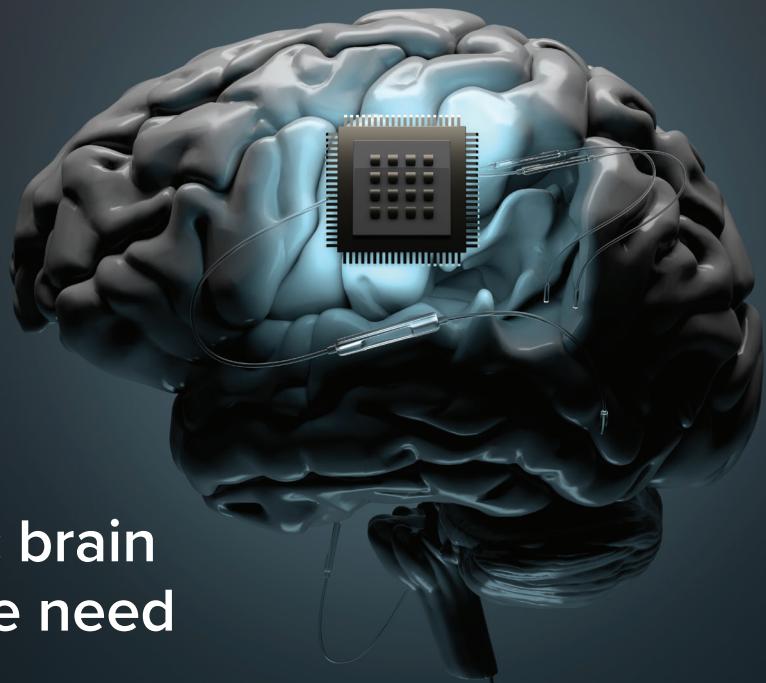

### 28 New therapeutic brain implants defy the need for surgery

MIT researchers created microscopic wireless electronic devices that travel through blood and implant in target brain regions, where they provide electrical stimulation.

### 30 Inspiring innovations address key industry challenges

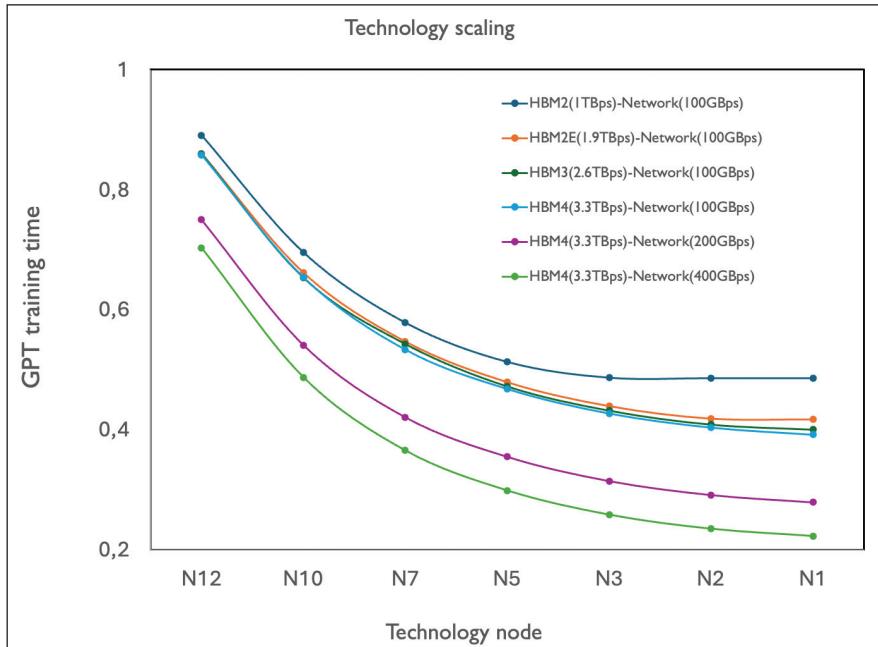

Imec has been busy in recent weeks, unveiling a tool for AI data centre design and optimization and presenting research results, including mitigating thermal bottleneck in 3D HBM-on-GPU architectures using a system-technology co-optimization approach

### 38 The secrets behind SCREEN's semiconductor success

Martin Hollfelder, VP for Service and Installation/Qualification and Technology at SCREEN SPE Germany, discusses the company's long track record in the semiconductor industry

34

28

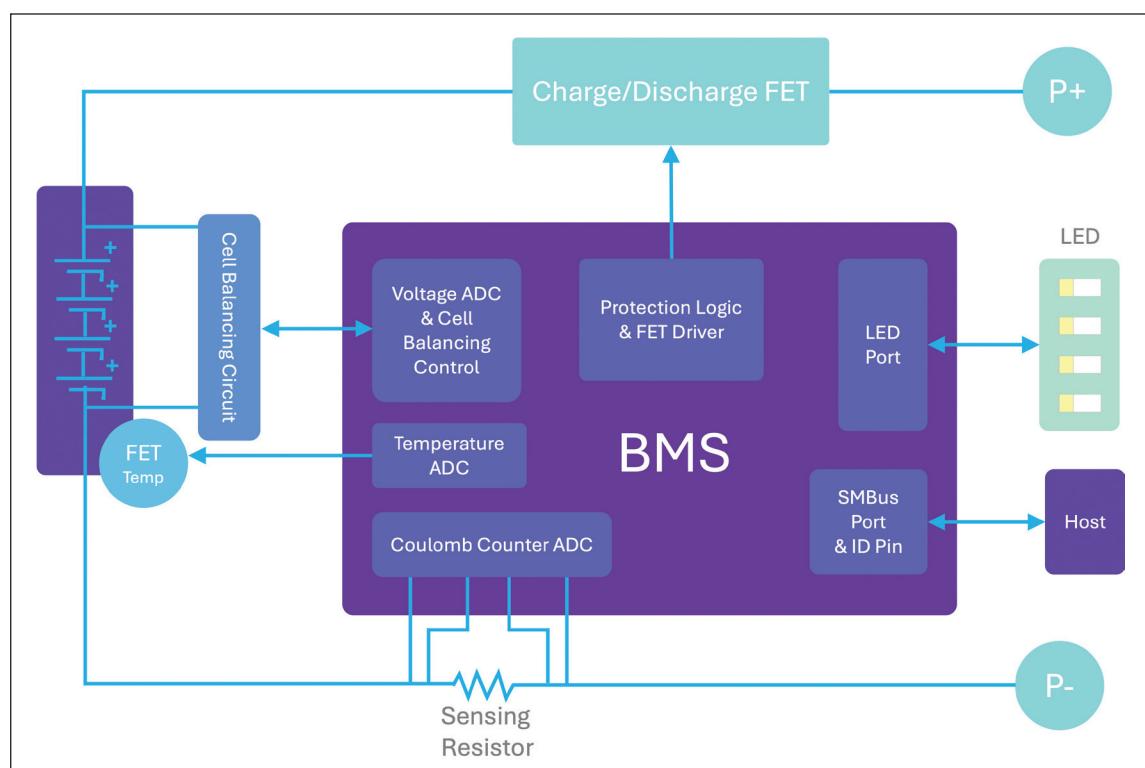

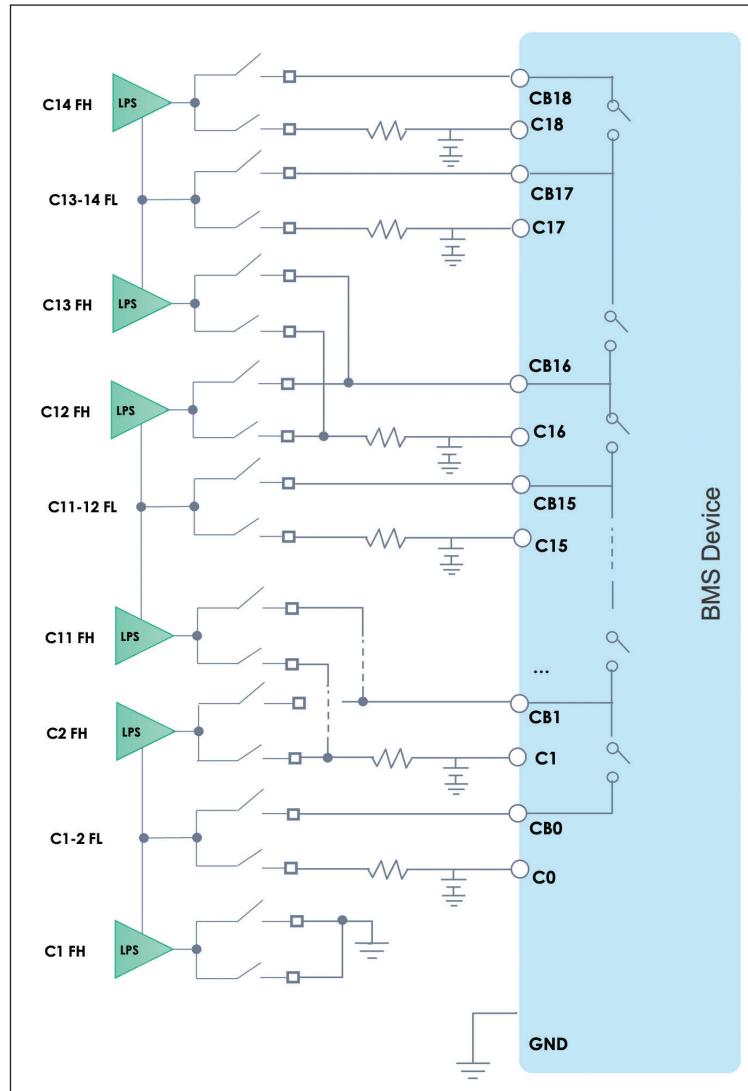

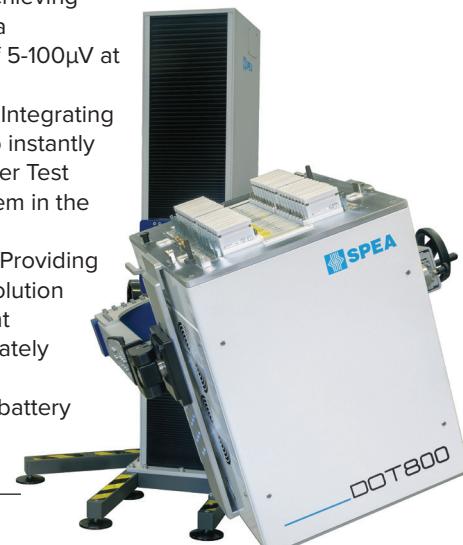

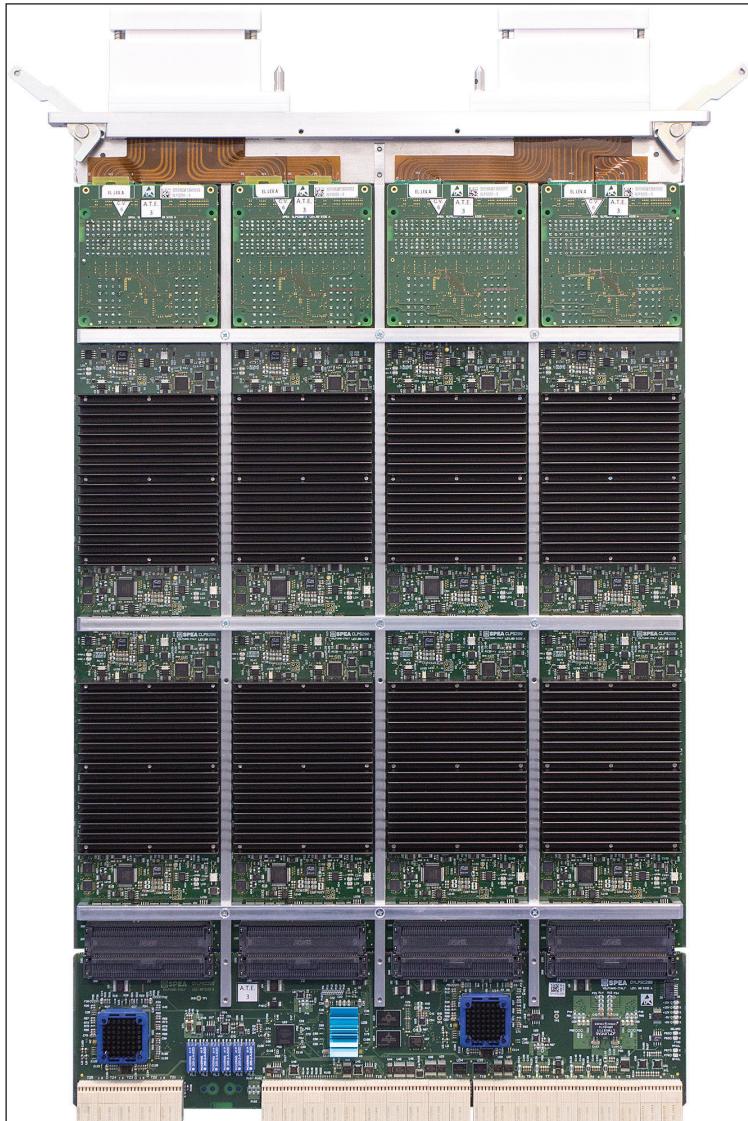

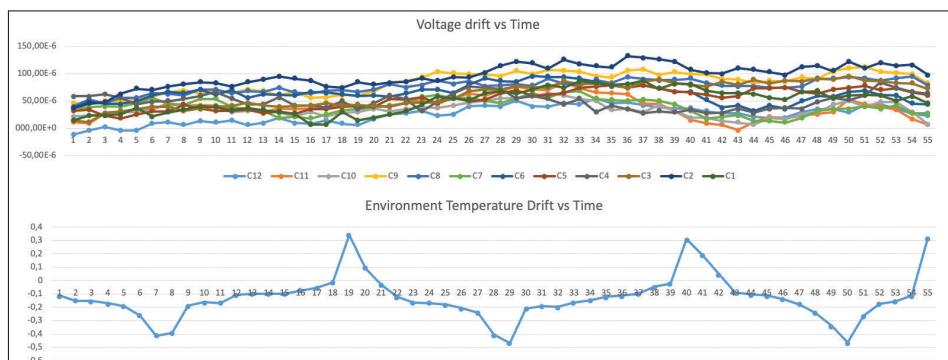

## 42 Securing the future of battery power: Precision testing challenges of next-generation BMS ICs

The rapid global transition toward electrification, driven by the booming Electric Vehicle (EV) and Energy Storage System (ESS) markets, has placed Battery Management System (BMS) Integrated Circuits (ICs) at the epicenter of system design

24

## NEWS

- 06 Global semiconductor equipment sales to reach \$156 billion in 2027

- 07 'Only photonics' can satisfy AI's insatiable appetite for compute power

- 08 Siemens and GlobalFoundries collaborate

- 09 One step towards European excellence in microelectronics

- 10 Dragonfly 3D World 2025 transforms 3D image analysis

- 11 Silicon Labs partners with Rimini Street

- 12 ACM Research delivers first horizontal panel electroplating tool

07

**Publisher** Jackie Cannon

**Editor** Phil Alsop

**Sales & Marketing Manager** Shehzad Munshi

**Director of Logistics** Sharon Cowley

**Design & Production Manager** Mitch Gaynor

**Chief Executive Officer** Sukhi Bhadal

**Chief Technical Officer** Scott Adams

jackie.cannon@angelbc.com

phil.alsop@angelbc.com

shehzad.munshi@angelbc.com

sharon.cowley@angelbc.com

mitch.gaynor@angelbc.com

sukhi.bhdal@angelbc.com

scott.adams@angelbc.com

+44 (0)1923 690205

+44 (0)1923 690215

+44 (0)1923 690200

+44 (0)1923 690214

+44 (0)2476 718970

+44 (0)2476 718970

**Directors** Jackie Cannon, Sharon Cowley

**Published by** Angel Business Communications Ltd,

6 Bow Court, Fletchworth Gate, Burnsall Road,

Coventry CV5 6SP, UK.

T: +44 (0)2476 718 970 E: info@angelbc.com

Angel  BUSINESS COMMUNICATIONS

**recycle**

When you have finished with

this magazine please Recycle it.

Silicon Semiconductor is published ten times (6x print and 4x video issues) a year on a controlled circulation basis. Non-qualifying individuals can subscribe at £50.00 per annum (UK), €60.00 per annum (Europe), \$90 per annum (air mail)(USA). Cover price £4.50. All information herein is believed to be correct at time of going to press. The publisher does not accept responsibility for any errors and omissions. The views expressed in this publication are not necessarily those of the publisher. Every effort has been made to obtain copyright permission for the material contained in this publication. Angel Business Communications Ltd © Copyright 2025. All rights reserved. Contents may not be reproduced in whole or part without the written consent of the publishers. The paper used within this magazine is produced by chain of custody certified manufacturers, guaranteeing sustainable sourcing. US mailing information: Silicon Semiconductor, ISSN 1096-598X, is published 5 times a year by Angel Business Communications Ltd, Unit 6, Bow Court, Fletchworth Gate, Burnsall Rd, Coventry CV5 6SP, UK. Airfreight and mailing in the USA by agent named World Container INC 150-15, 183rd St, Jamaica, NY 11413, USA. Periodicals Postage Paid at Brooklyn, NY 11256. POSTMASTER: Send address changes to Silicon Semiconductor, Air Business Ltd, c/o World Container INC 150-15, 183rd St, Jamaica, NY 11413, USA.

We strive for accuracy in all we publish; readers and contributors are encouraged to contact us if they recognise an error or omission. Once a magazine edition is published [online, in print or both], we do not update previously published articles to align old company names, branding, marketing efforts, taglines, mission statements or other promotional verbiage, images, or logos to newly created or updated names, images, typographic renderings, logos (or similar) when such references/images were accurately stated, rendered or displayed at the time of the original publication. When companies change their names or the images/text used to represent the company, we invite organizations to provide Angel Business Communications with a news release detailing their new business objectives and/or other changes that could impact how customers/prospects might recognise the company, contact the organisation, or engage with them for future commercial enterprise.

Printed by: The Mansen Group. ISSN 2050-7798 (Print) ISSN 2050-7801 (Online) © Copyright 2025.

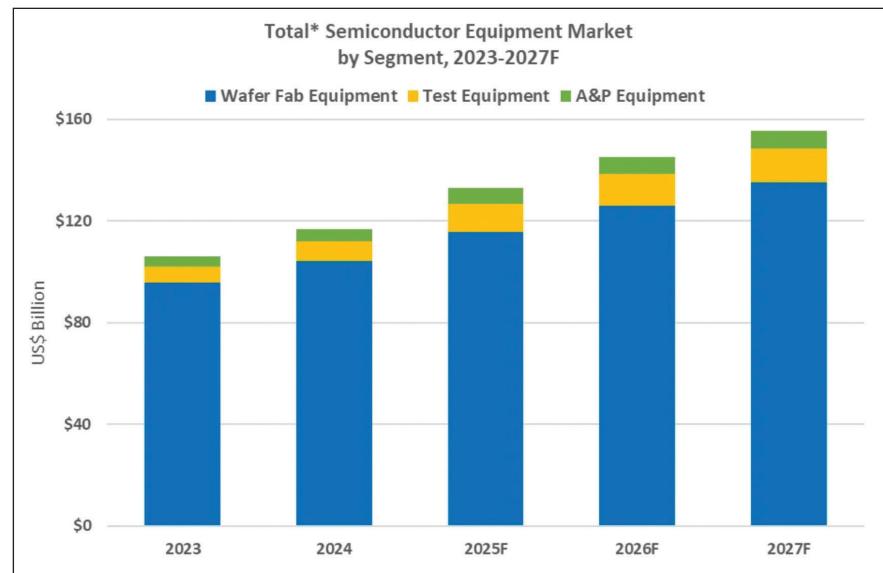

# Global semiconductor equipment sales to reach \$156 billion in 2027

Global sales of total semiconductor manufacturing equipment by original equipment manufacturers (OEMs) are forecast to reach a record high of \$133 billion in 2025, growing 13.7% year-on-year, SEMI announced its Year-End Total Semiconductor Equipment Forecast.

GROWTH in semiconductor manufacturing equipment sales is expected to continue in the two following years of the forecast period, with projections of \$145 billion in 2026 and \$156 billion in 2027. This growth will be driven primarily by investments related to AI, particularly in leading-edge logic, memory, and the adoption of advanced packaging technologies. "Global semiconductor equipment sales show robust momentum, with both the front-end and back-end segments projected to see three consecutive years of growth, culminating in total sales surpassing \$150 billion for the first time in 2027," said Ajit Manocha, SEMI president and CEO. "Investments to support AI demand have been stronger than anticipated since our midyear forecast, leading us to boost the outlook for all segments."

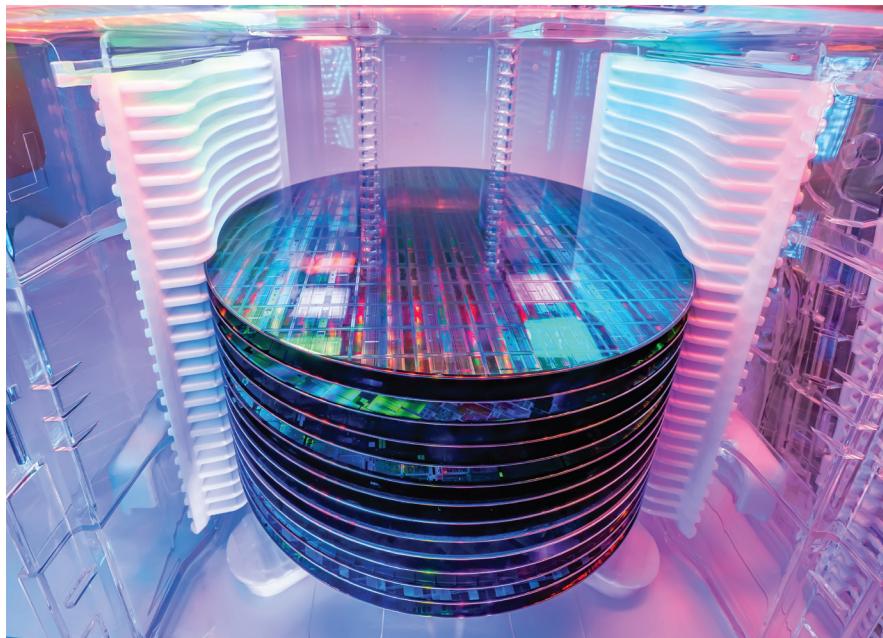

## Semiconductor equipment sales by segment

After registering a record \$104 billion in sales last year, the wafer fab equipment (WFE) segment, which includes wafer processing, mask/reticle, and fab facilities equipment, is projected to grow 11.0% to \$115.7 billion in 2025. This represents an upward revision from the previously forecast \$110.8 billion in the SEMI 2025 Mid-Year Equipment Forecast, reflecting stronger than expected investments in DRAM and high-bandwidth memory (HBM) to support AI computing. Continued capacity build-out in China is also contributing meaningfully to WFE demand. Looking ahead, WFE segment sales are projected to expand 9.0% in 2026 and 7.3% in 2027, reaching \$135.2 billion as device makers increase spending on advanced logic and memory technologies.

The back-end equipment segment is anticipated to continue its strong recovery that began in 2024. Sales of semiconductor test equipment are

projected to surge 48.1% to \$11.2 billion in 2025, while assembly and packaging (A&P) equipment sales are projected to rise 19.6% to \$6.4 billion. Back-end growth is expected to continue, with test equipment sales growing 12.0% in 2026 and 7.1% in 2027, and A&P sales are forecast to grow 9.2% in 2026 and 6.9% in 2027. This expansion is underpinned by the growing complexity of device architectures, accelerated adoption of advanced and heterogeneous packaging, and stringent performance requirements for AI and HBM semiconductors. These drivers are partly offset by ongoing softness in consumer, automotive and industrial demand, which continues to weigh on some mainstream test and packaging segments.

## Wafer fab equipment sales by application

WFE sales for foundry and logic applications are expected to show robust 9.8% year-over-year growth to \$66.6 billion in 2025, supported by resilient spending for advanced nodes. The segment is forecast to see 5.5% growth in 2026 and 6.9% increase to

\$75.2 billion in 2027 as chipmakers add capacity for AI accelerators, high-performance computing and premium mobile processors. Investments will increasingly target leading-edge technologies as the industry moves toward high-volume manufacturing at the 2nm gate-all-around (GAA) node.

Memory-related capital expenditures are projected to see significant expansion through 2027 powered by increasing demand for HBM to support AI deployment and ongoing technology migration. The NAND equipment market is expected to see growth of 45.4% to \$14.0 billion in 2025 and further increase 12.7% to \$15.7 billion in 2026 and 7.3% to \$16.9 billion in 2027, driven by advancements in 3D NAND stacking and capacity expansion at both leading and mainstream layers. DRAM equipment sales are projected to rise 15.4% to \$22.5 billion in 2025, followed by 15.1% and 7.8% year-on-year growth in 2026 and 2027, respectively, as memory suppliers ramp HBM and upgrade to more advanced process nodes to meet AI and data center requirements.

# 'Only photonics' can satisfy AI's insatiable appetite for compute power

As artificial intelligence expands, its soaring electricity use is putting unprecedented pressure on power grids, driving up costs and threatening to slow Europe's energy transition. But a new report shows that only light-based computing can keep AI's ever-expanding power demands at bay without triggering a surge in emissions.

The study, published by Photonics21 and compiled by market intelligence agency TEMATYS, finds that as electricity use from AI rises sharply, and conventional silicon chips struggle to keep pace with the twin pressures of ever-larger models and expanding data centres, Europe risks undermining its clean-energy goals and increasing reliance on fossil fuels.

Entitled "AI Desperately Needs Photonics," the report concludes that photonics, which uses light rather than electricity to move and process information, offers the only viable pathway to scale up AI computing while dramatically reducing energy consumption. The study reveals that integrating photonic technologies into data-centre and chip architectures can help AI growth remain compatible with Europe's climate commitments.

AI is scaling faster than the world's power grids can handle. Each new generation of larger, more complex models demands exponentially greater computing power, sending data-centre energy use soaring.

The International Energy Agency puts global consumption at roughly 415 TWh in 2024, and TEMATYS warns it could more than double by 2030 as AI workloads dominate digital infrastructure.

Sébastien Bigo, Nokia Bell Labs Fellow and Photonics21 Work Group Leader for Digital Infrastructure, said, "Photonics can provide the infrastructure that will determine whether AI becomes cleaner and more competitive or simply costlier and dirtier. Europe has the research base to lead; what it lacks is coordinated investment and industrial scale."

The report shows that bringing photons much closer to the compute (whether through co-packaged optics or other emerging photonic integration approaches) and using light to handle increasing parts of data movement or specific acceleration tasks can considerably improve the carbon and cost profile of AI. While photonics is not a replacement for CPUs or GPUs, it can become a critical complement that eases the pressure on them. If Europe wants sovereignty in future AI hardware and to meet its climate commitments, the report stresses that Europe's policy and investment decisions in the coming years will be decisive.

The report finds that photonics is already indispensable to the digital world. Fibre optics underpins today's internet and data-centre infrastructure, and the next step of integrating light directly into chip architectures through co-packaged optics is already underway. These advances, however, will not be enough on their own. Even with industry claims of 3.5 times greater power efficiency, TEMATYS concludes that these gains cannot fully offset the surge in energy demand driven by AI's rapid expansion.

The study also shows that optical

computing is no longer theoretical. Laboratory breakthroughs and start-up prototypes, including MIT's 2024 demonstration of an integrated photonic chip performing neural-network computations entirely with light, reveal a clear technical path towards fully photonic processors.

Finally, the report warns that Europe has the expertise but not yet the scale. World-class research and promising start-ups exist across the continent, but without faster investment, large-scale manufacturing, and workforce development, Europe risks surrendering this strategic market to competitors abroad.

The report urges European institutions, national governments and private investors to treat photonics as strategic infrastructure for AI. Recommended actions include: dedicated funding for pilot manufacturing, incentives to scale photonics start-ups, inclusion of photonics in Chips/AI/Green tech funding streams, and skills initiatives to build a manufacturing workforce. Without these steps, Europe risks ceding critical parts of the AI hardware value chain to overseas competitors while facing higher energy bills and emissions.

# Siemens and GlobalFoundries collaborate

Strategic collaboration to enhance performance of semiconductors and other advanced industries based on both companies' AI-based capabilities.

SIEMENS and GlobalFoundries (GF) have entered a new strategic collaboration to leverage each company's complementary AI-based capabilities to enhance performance of semiconductor manufacturing and advanced industries – making operations more efficient, secure and reliable. In their latest memorandum of understanding, the companies focus on automation technologies for semiconductor fabrication (fab automation), electrification, digital solutions and software ranging from chip development to product lifecycle management.

A key element of the new strategic collaboration is deployment of advanced AI-enabled software, sensors and real-time control systems in fab automation to meet the growing demand for reliable semiconductors and autonomous platforms. Through centralized automation and predictive maintenance, GF and Siemens aim to increase equipment availability and operational efficiency in chip production while building capabilities that can be extended to other advanced industries. The companies intend to develop and deploy new solutions within their own operations to deliver enhanced offerings.

This expanded collaboration comes at a time of unprecedented demand for essential semiconductors and autonomous platforms in critical areas such as artificial intelligence, defense, energy and connectivity. By teaming up and bringing new capabilities, Siemens and GF can support accelerated growth, better security and reliability and broaden their impact across the industry.

"Our economy runs on Silicon – one wafer at a time. Chips are critical for applications like robotics or connectivity and for bringing AI into the physical world and industry. We are collaborating to make global semiconductor supply

chains more resilient and to enable efficient localized manufacturing around the world," said Cedrik Neike, Member of the Managing Board of Siemens AG and CEO Digital Industries.

"Secure, locally manufactured semiconductors are at the core of the AI transition – from cloud to the physical world, bringing intelligence into devices we use every day and enabling applications we couldn't imagine a few years ago," said Tim Breen, CEO of GlobalFoundries. "Our unique collaboration with Siemens allows us to go faster – to build the technologies that make this possible – differentiated, energy-efficient,

**A key element of the new strategic collaboration is deployment of advanced AI-enabled software, sensors and real-time control systems in fab automation to meet the growing demand for reliable semiconductors and autonomous platforms**

connected and secure chips across a wide range of next-generation applications."

Siemens brings a comprehensive suite of industrial, energy & building automation and digitalization technologies including advanced software for chip design & manufacturing, fab automation, and product lifecycle management.

Utilizing Siemens' suite of solutions, GF and Siemens will enable seamless collaboration across the entire semiconductor lifecycle and deliver high performance and reliable semiconductor solutions at scale.

GF, together with MIPS, a GF company and global leader in RISC-V processor IP, brings unique process technology and design capabilities to accelerate the development and manufacturing of tailored solutions that support Siemens goal of enabling autonomous platforms and physical AI chips at scale. GF is one of the world's leading semiconductor foundries. The publicly listed U.S. company operates manufacturing facilities in the USA, Asia, and Europe. In Dresden, GlobalFoundries runs Europe's largest semiconductor production site with around 3,000 employees.

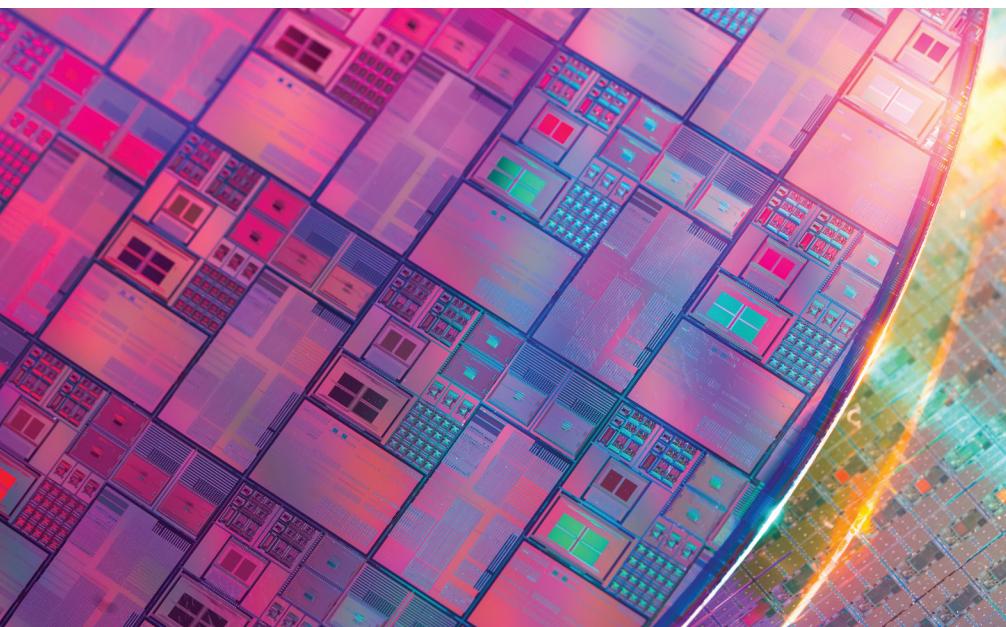

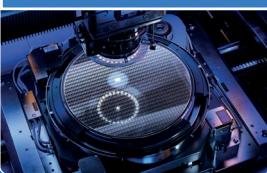

# One step towards European excellence in microelectronics

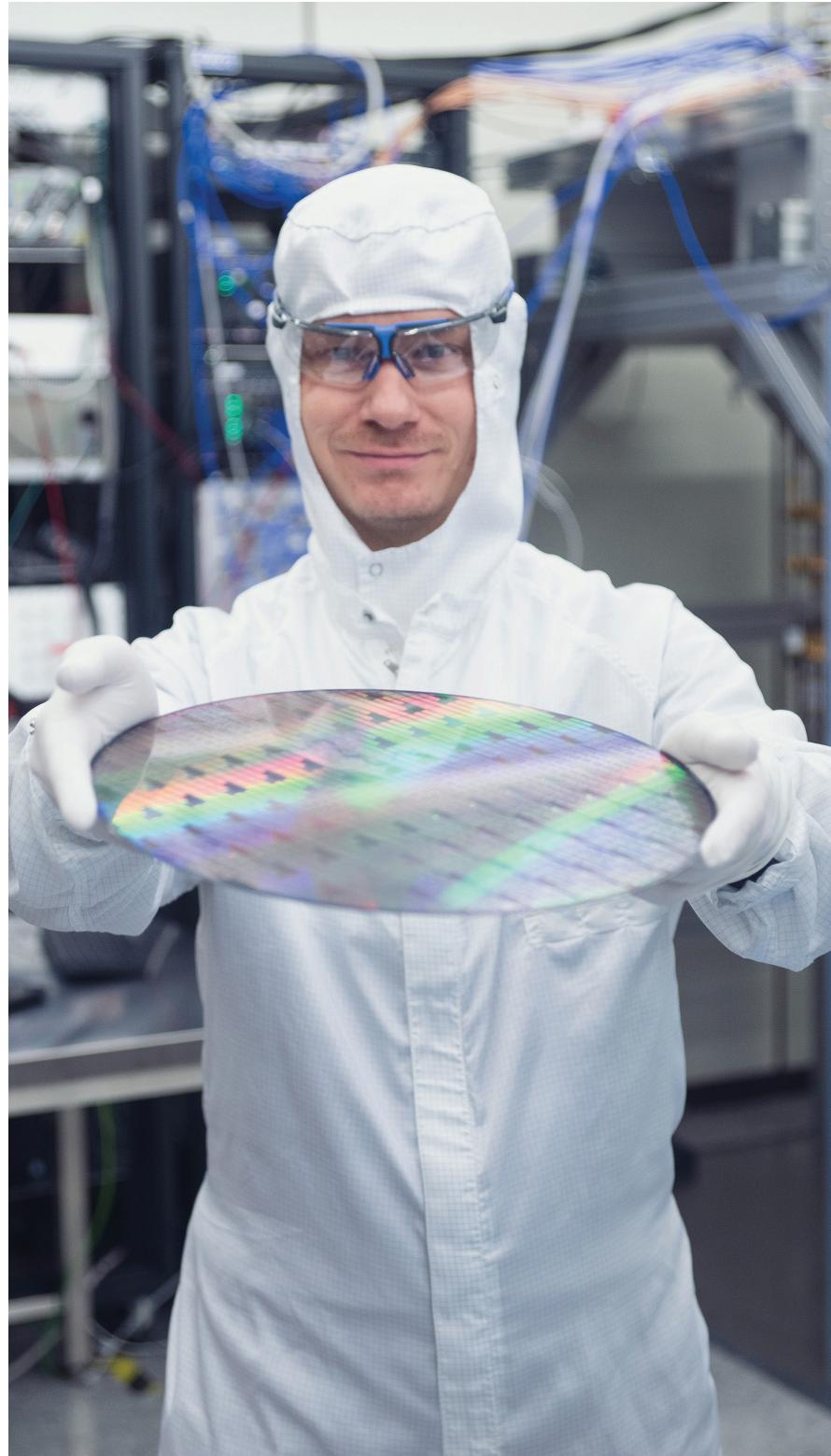

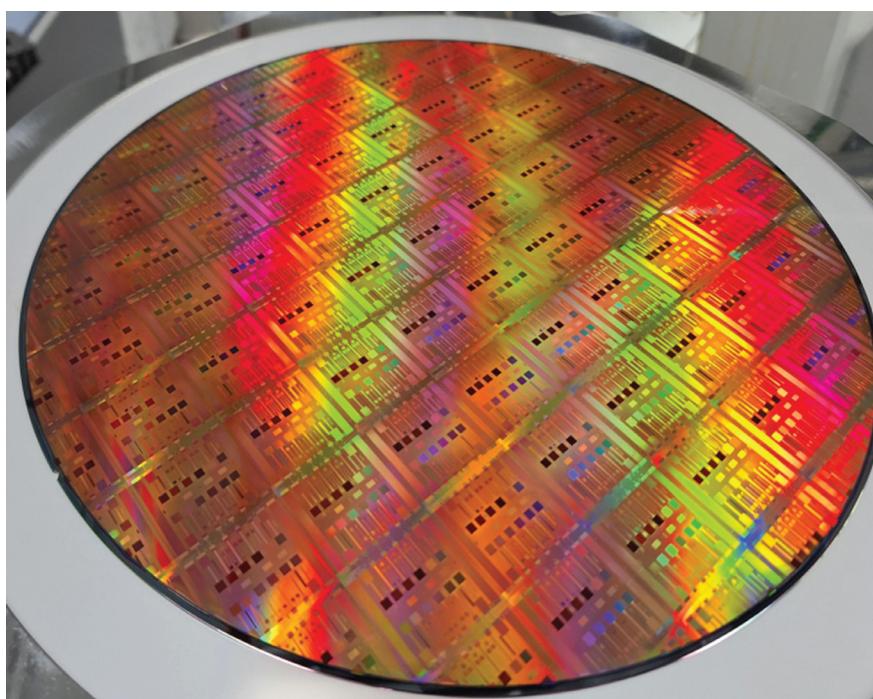

VTT completes 200 mm silicon wafer size conversion in its cleanroom.

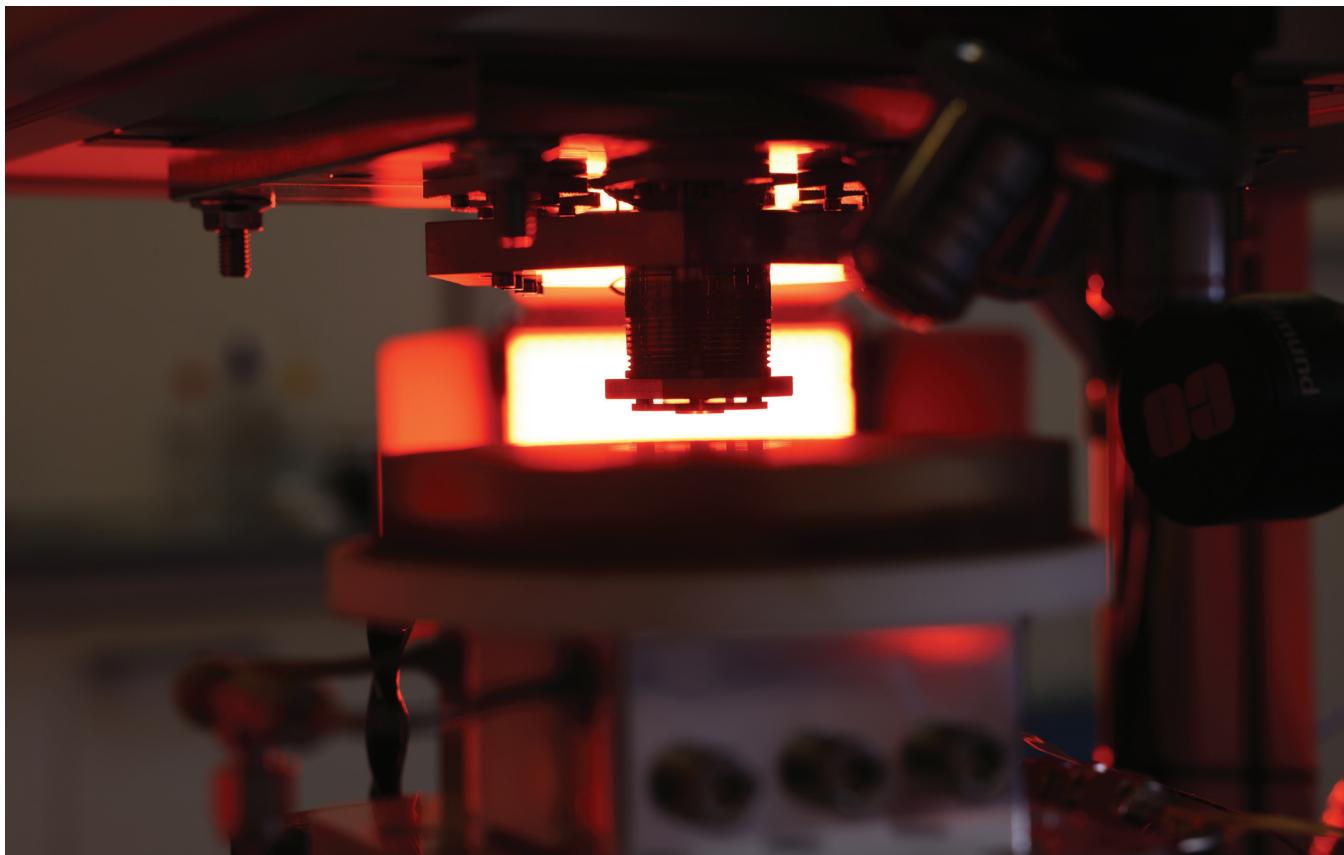

VTT completes the conversion of its cleanroom equipment in the Micronova cleanroom to 200 mm silicon wafer size. It has been a major project, during which the previous 150 mm semiconductor manufacturing equipment has either been converted or upgraded to support 200 mm wafers.

According to Piia Konstari, Director at VTT, the investment is part of Finland's goal to strengthen its leading role in the European specialised microelectronics ecosystem.

The investment strengthens Finland's position in specialised microelectronics development and supports Europe's strategic sovereignty in critical technologies. It also marks a significant step forward for Nordic semiconductor capabilities.

"This upgrade significantly enhances our toolset enabling us to efficiently process 200 mm sized wafers and benefit from the latest industrial technologies and processes.

With investments in front-end-of-line equipment as well as advanced back-end-of-line process equipment, we are strengthening our position in the forefront of microfabrication R&D and piloting," says Oliver Pabst, Head of Fab operations at VTT.

"Our goal is to build a leading European microelectronics R&D and piloting cleanroom and ecosystem, supporting research, development, innovation, piloting and industrialisation. Our customers and partners will widely benefit from VTT's new capabilities.

This investment is part of a broader strategy through which VTT and Finland strengthen their leading role in the European specialised microelectronics ecosystem," says Piia Konstari, Director, Microfabrication services at VTT.

The funding for this upgrade has come from Business Finland, the Research Council of Finland, the EU PREVAIL project, as well as VTT's own funds granted by the Ministry of Economic Affairs and Employment.

The project has spanned several years, beginning in 2019 and continuing through 2025, reflecting the scale, complexity and ambition of the transformation.

The rationale behind this conversion is rooted in the widespread adoption of 200 mm silicon wafers in the semiconductor industry and to the compatibility with other European cleanroom wafer sizes.

The 200 mm wafer size is a standard choice for fabrication in MEMS (micro-electromechanical systems), RF (radio frequency) devices, analogue integrated circuits, integrated photonic components and quantum circuits.

Transitioning to 200 mm wafers ensures seamless compatibility with key customers and research

partners, including several prominent EU institutions that have already standardised their processes around this wafer size.

The availability of cutting-edge processing equipment for 200 mm wafers is rapidly expanding, while support and equipment for the older 150 mm format is on the decline.

This demonstrates that the upgrade to 200 mm wafer size is not only strategic but necessary to remain competitive and relevant in the market.

Furthermore, the 200 mm wafer size offers access to a wide range of specialised wafer types, such as Silicon-on-Insulator (SOI), enabling advanced fabrication possibilities such as monolithic integration with CMOS technology, wafer-to-wafer bonding, and chip-to-wafer assembly processes.

These new capabilities lay the ground for future innovation, allowing VTT and the Finnish ecosystem to explore more complex system architectures and integrated solutions.

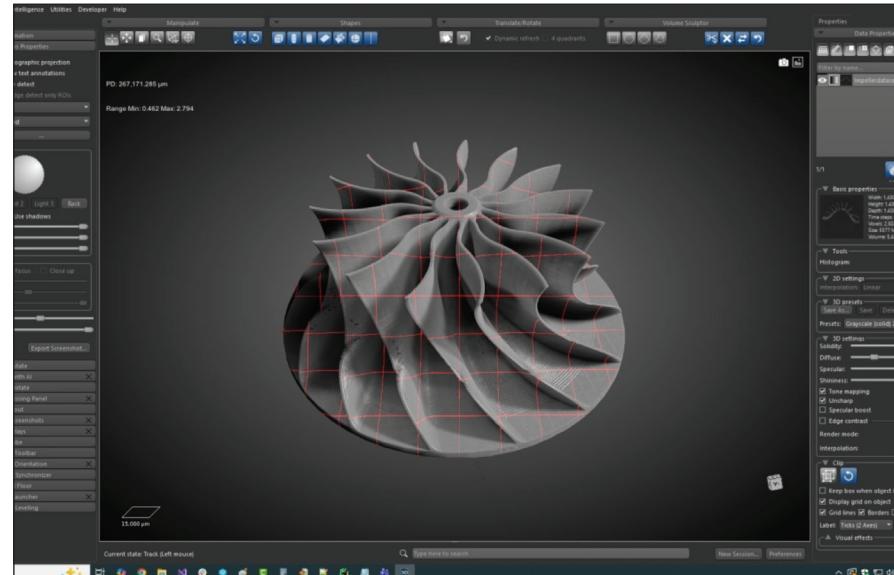

# Dragonfly 3D World 2025 transforms 3D image analysis

Comet Technologies Canada Inc. has launched Dragonfly 3D World 2025, a major software upgrade that redefines how scientists and engineers explore, analyze, and quantify complex 3D image data.

WITH its new high precision surface determination, faster GPU-accelerated performance, advanced one-click AI segmentation, and next-generation visualization tools, 3D World 2025 delivers a powerful combination of speed, precision, and usability for applications in materials science, life sciences, electronics, additive manufacturing, automotive, and beyond.

**Smarter segmentation. deeper insight**

Segmentation lies at the heart of image analysis and 3D World raises the standard once again. The newly integrated Meta AI's Segment Anything Model (SAM) brings one-click annotation to even the most complex objects, from microstructures to biological tissues. By adapting across imaging modalities, SAM enables users to identify and isolate meaningful features instantly, without manual thresholding or model training.

"This release marks a major leap forward in segmentation automation," says Joscha Malin, Director of Software Solutions at Comet. "Dragonfly 2025 helps our users spend less time preparing data and more time interpreting it — driving faster decisions and more accurate results."

## Precision that Reaches Beyond the Pixel

When it comes to quantitative measurement, accuracy starts at the surface. 3D World 2025 introduces a redesigned Surface Determination engine, now capable of sub-voxel precision. This advancement enables highly accurate surface and mesh extractions - a critical step for geometric metrology, roughness analysis, and dimensional validation.

Combined with new 3D rendering modes, users can visualize internal and

external structures with photorealistic clarity, making even the smallest details measurable, shareable, and ready for publication.

## Accelerated workflows for modern research and manufacturing

Whether analyzing thousands of CT slices or processing terabytes of microscopy data, performance defines productivity.

3D World 2025 introduces GPU-accelerated filtering, denoising, and skeletonization that deliver a performance improvement of as much as 100x over CPU processing. For instance, a Canny filter applied to a  $1024^3$  USHORT dataset is completed in under 1.4 seconds on an NVIDIA GeForce RTX 4090, compared to over 55 seconds on an Intel i7-13700K CPU. Together with macro automation and upcoming Auto Executor add-ins, this release empowers users to build fully reproducible, high-throughput pipelines that scale from single-lab experiments to industrial inspection lines.

This leap in efficiency helps both research teams and manufacturers

achieve faster validation cycles, improved quality control, and deeper data-driven understanding of materials and components.

## Setting the standard in 2D, 3D, and 4D image analysis worldwide

Dragonfly has long defined the benchmark for advanced image processing and quantitative analysis. Trusted by global leaders in X-ray CT and X-ray microscopy, the software is relied upon by industry innovators such as Comet Yxlon, Zeiss, Tescan, Rigaku, and Brucker, as well as by leading research institutions worldwide.

By powering inspection and visualization software for major OEMs, Dragonfly technology has become the analytical backbone of modern imaging - supporting applications in materials research, electronics, additive manufacturing, and life sciences. With the release of 3D World 2025, Dragonfly strengthens its leadership position, delivering tools that drive faster insight, greater precision, and smarter automation across the global imaging community.

# Silicon Labs partners with Rimini Street

Multi-year strategic partnership empowers Silicon Labs to maximize SAP ECC 6.0 value, accelerate transformation and avoid costly upgrades and disruption.

SILICON LABS has selected Rimini Street as its strategic partner to maximize the value of its SAP ECC 6.0 investment. This collaboration provides the U.S.-based semiconductor manufacturer with long-term SAP maintenance and professional services to accelerate modernization without costly upgrades or business disruption.

## Partnership reduces technical debt and accelerates modernization

Silicon Labs first engaged Rimini Street's professional services team, Rimini Consult™, to develop a strategic ERP roadmap leading to a multi-system project to align 12 SAP environments with modern operating system and database standards.

The project reduced Silicon Labs' technical debt by improving platform stability, strengthening its security and compliance posture and delivering faster, real-time reporting capabilities to support informed executive decision-making.

"Rimini Street not only delivered outstanding results for our SAP project, but we were also able to go live ahead of schedule, working side by side with our team to ensure success from start to finish," said Radhika Chennakeshavula, CIO and vice president of Silicon Labs. "Our current SAP ECC investment continues to provide value across our operations. As part of our innovation strategy, we are accelerating new capabilities built on and around our SAP core, modernizing where needed without the cost, risk and disruption of an unwanted move to RISE with SAP. I prefer to make impactful

investments of our people, time and money to harness the full power of the latest AI technology rather than a low-ROI platform upgrade".

## Outstanding results lead to expanded partnership

The success of the professional services engagement with Rimini Street became the catalyst for a five-year Rimini Support™ for SAP agreement generating an immediate savings of 50% on annual support costs, along with additional solutions such as Rimini Watch™, Rimini Street's change management alternative to SAP Solution Manager, allowing Silicon Labs to move quickly in its growth strategy.

"Rimini Street is more than a service provider. They are now a trusted, long-term partner that respects our strategic direction, aligns with our vision and delivers real value," said

Chennakeshavula. "Rimini Street frees up critical resources, fast-tracks innovation and provides expert support across our global operations, giving us the flexibility to modernize on our own terms and timeline." With deep confidence in Rimini Street's ERP expertise and capabilities, Silicon Labs is expanding its partnership to include new Agentic AI ERP innovations.

"We are proud to serve as a strategic partner to leading manufacturers such as Silicon Labs, helping to build a stronger, more secure operation that is agile in its ability to adopt the latest technology without lengthy migrations or replatforming," said Jeff Chenevey, Rimini Street's VP of manufacturing industry solutions. "Rimini Street's end-to-end approach means we look after the full scope of needs for our clients, expertly managing today's needs while accelerating tomorrow's capabilities."

We are proud to serve as a strategic partner to leading manufacturers such as Silicon Labs, helping to build a stronger, more secure operation that is agile in its ability to adopt the latest technology without lengthy migrations or replatforming

# ACM Research delivers first horizontal panel electroplating tool

ACM's Ultra ECP ap-p enables next generation device performance amid accelerating market demand for advanced packaging.

ACM RESEARCH has delivered the first panel electrochemical plating tool, the Ultra ECP ap-p, to an industry-leading panel fabrication customer.

This achievement underscores ACM's advancement in panel-level electroplating technology and reflects growing market demand for scalable, cost-efficient advanced packaging solutions to meet next generation device requirements.

The Ultra ECP ap-p is the first commercial panel-level copper deposition system for the large-panel market, supporting plating steps across pillar, bump, and redistribution layer (RDL) processes. The system achieves panel-processing performance - comparable to traditional round wafer processes, enabling manufacturers to meet demanding device requirements with greater efficiency.

"We are pleased to fulfill this order for our Ultra ECP ap-p," said Dr. David Wang, ACM's President and Chief Executive Officer. "This milestone demonstrates our ability to deliver high-performance horizontal panel electroplating solutions through our differentiated technology that help customers accelerate their fan-out panel-level packaging roadmaps while strengthening our role in the advanced packaging ecosystem. As demand grows for next-generation devices, panel-level packaging offers the scalability, throughput, and cost

advantages needed for high-volume production, which will achieve a seamless transition for the industry from 300-millimeter wafer packaging to panel-level packaging."

The system features ACM proprietary horizontal electroplating technology, and supports copper (Cu), nickel (Ni), tin-silver (SnAg) and a gold (Au) plating.

The Cu plating chambers incorporate high-speed plating paddles specifically designed for tall pillar applications, capable of achieving pillar heights exceeding 300 microns. The Ultra ECP ap-p features a four-sided sealing dry contact chuck for improved reliability, in-cell rinse functionality to minimize chemical cross-contamination between different plating cells, and a horizontal electroplating design synchronizing a rotating square electrical field with the rotating chuck for superior deposition uniformity.

## Qnity spins from DuPont

QNITY ELECTRONICS, INC. has completed its separation from DuPont de Nemours, Inc..

Jon Kemp has assumed the role of Chief Executive Officer of Qnity and continues as a member of Qnity's Board of Directors, as planned. Prior to this appointment, Kemp served as president of DuPont's Electronics & Industrial business, where he led major portfolio transformation and business growth.

"Today marks a pivotal milestone, built on decades of innovation, as Qnity begins its next chapter as a leading pure-play technology provider serving the semiconductor value chain," said Kemp. "Driven by strong customer partnerships, global reach, and a broad

portfolio of industry-leading materials and technologies, Qnity is making tomorrow's technologies possible. This includes the transition to advanced nodes, especially for AI applications, including chip manufacturing, advanced packaging, and thermal management."

Qnity has more than 10,000 employees serving customers in more than 80 countries and regions. Facilities include 39 manufacturing sites and 17 R&D facilities around the world. Two-thirds of Qnity's portfolio is tied directly to semiconductors, giving the company a total addressable market exceeding \$30 billion. The global semiconductor industry revenue is projected to surpass \$1 trillion<sup>1</sup> around the end of the decade.

At the company's Investor Day in September, Qnity's leadership outlined its financial strategy to achieve above-market growth and strong profitability through 2028.

"As a pure-play company focused on the evolving needs of the semiconductor industry, we're confident in our position to deliver sustained outperformance relative to peers and the market," said Matt Harbaugh, Chief Financial Officer of Qnity.

# Powerful inspection solutions for wafer and chip level packaging.

From root cause analysis in the lab, to fast process analysis in the fab, Comet's leading 2D and 3D X-ray technology provides powerful inspection solutions for wafer and chip level packaging, enhanced with incredible AI-based software.

|      | Height | Diameter |

|------|--------|----------|

| TSV  | 105 µm | 10 µm    |

| Void | 50 µm  | 6 µm     |

Visualization of 3D X-ray inspection results of TSV fills in a wafer. Wafer designed for Comet by Fraunhofer IZM\_ASSID, it contains voids for illustrative purposes.

Contact us to learn more, or explore our entire portfolio

comet

[yxlon.comet.tech](http://yxlon.comet.tech)

# R&D advances for the FAMES Pilot Line

400 °C CMOS breakthrough opens critical doors to 3D integration goals.

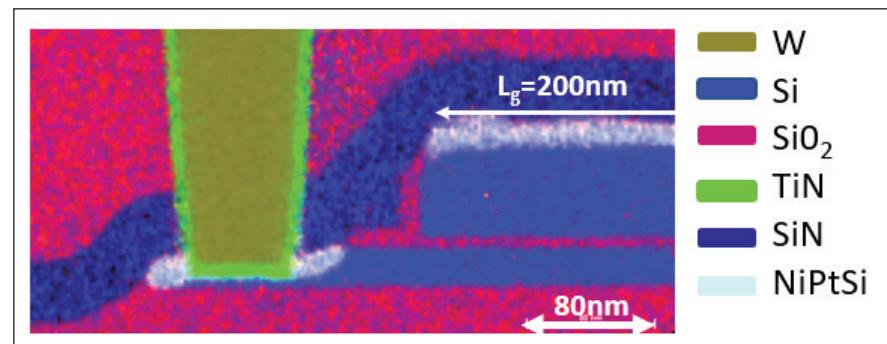

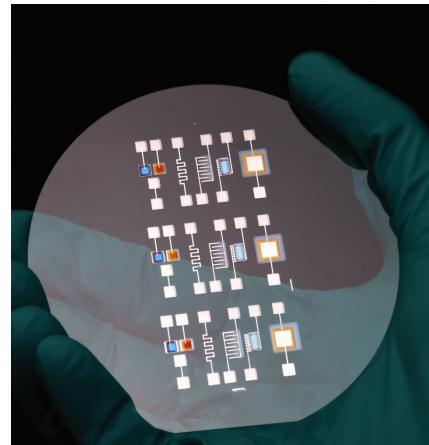

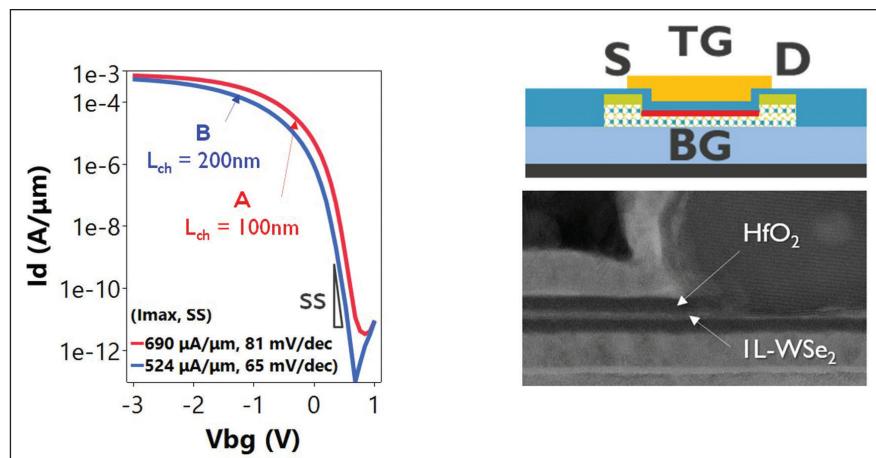

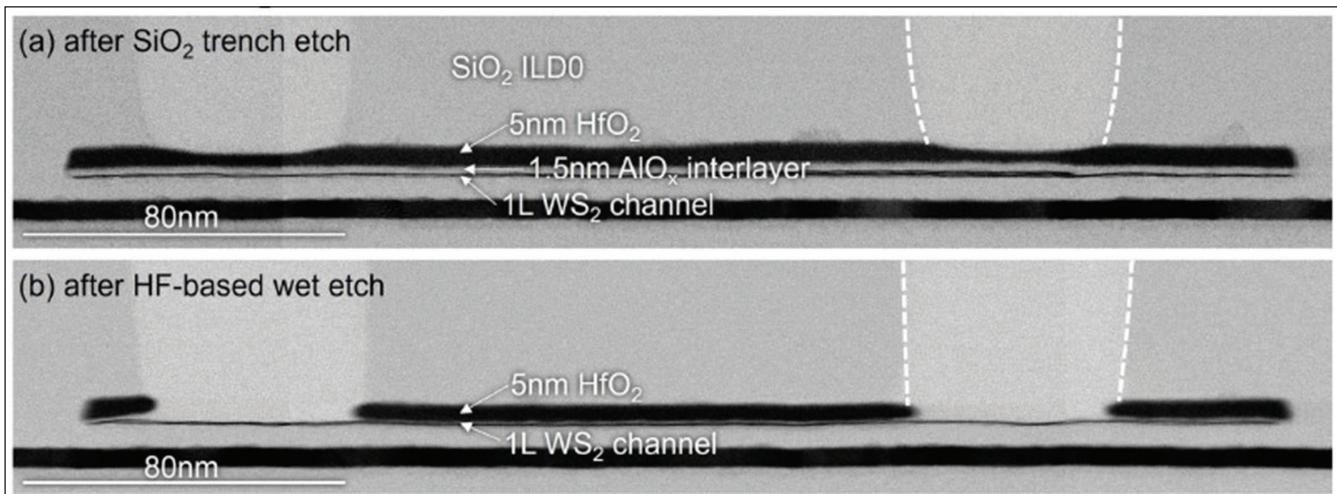

CEA-LETI, the coordinator of the FAMES Pilot line, has achieved a major milestone for next-generation chip stacking: fully functional 2.5 V SOI CMOS devices fabricated at 400 °C. The devices match electrical performance of devices fabricated at standard thermal budget ( $>1000$  °C), removing one of the last barriers to large-scale 3D sequential integration (3DSI) – a core objective of FAMES.

Enabled by advanced CEA-Leti expertise in low-temperature processes (nanosecond laser annealing (NLA) and solid-phase epitaxy regrowth (SPER)), this work offers true three-dimensional device stacking from the lab to fab. 3D sequential-integration interconnection density between tiers is the highest among 3D technologies, such as TSV and hybrid bonding. In this project, CEA-Leti demonstrated that Si CMOS is BEOL compatible, and thus can be stacked safely above BEOL, while transistor performance and maturity overtake largely the other technological options from the state-of-the-art, low-temperature solutions.

The achievement, presented today in a paper at IEDM 2025, titled, “High Performance 2.5 V n&p 400 °C SOI MOSFETs: A Breakthrough for Versatile 3D Sequential Integration,” is a key breakthrough for the FAMES Pilot Line, a European Union initiative launched in 2023 in response to the EU Chips Act strategy to strengthen sovereignty and competitiveness in semiconductor

technologies. By combining 3D heterogeneous and sequential integration on FD-SOI platforms, the consortium aims to enable a new generation of More-Than-Moore devices and applications.

## Enabling new chip architectures

“This breakthrough is a major milestone of the FAMES project as it enables innovative new chip architectures,” said Dominique Noguet, CEA-Leti vice president and coordinator of the FAMES Pilot Line. “Our low-temperature process could accelerate real-world demonstrations of multi-tier stacks combining advanced CMOS logic, with smart pixel or RF layers, to create new high-performance 3D chips.”

Concept of 3-tier  $\mu$ LED GaN pixel allowing an emissive array with strong pitch reduction thanks to 3DSI in combination with 3D hybrid bonding technology. CEA-Leti’s 400 °C CMOS process enables such top-tier integration without exceeding

the thermal limits of the active circuitry below. The team showed that SOI devices processed at 400 °C instead of the high temperature ( $>1000$  °C) industry standard and high-temperature industrial reference, performed equivalent to high-temperature devices.

“The 400 °C process enables 3D sequential stacking on any bottom tier,” Noguet said. “It’s a huge step forward because it’s far more mature—reliable and scalable – than current low-temperature solutions, such as polycrystalline films, oxide semiconductors or carbon nanotubes.”

## Protecting circuitry on bottom-tier layers

In their paper, CEA-Leti’s team demonstrated n- and p-type transistors matching the characteristics of conventional high-temperature CMOS devices, while staying within the  $\leq 400$  °C thermal budget required to preserve active circuitry in lower layers. The process relies on an optimized 400 °C LPCVD deposition for amorphous silicon followed by NLA in the melt regime for dopant activation and diffusion – producing polycrystalline, low-resistance gates with excellent interface quality. In addition, NLA-SPER mastering enables dopant activation without diffusion leading to access resistance within specifications.

“Our strength lies in mastering the cold process – especially nanosecond laser annealing – to achieve high-mobility, high-reliability CMOS at low temperature,” said Daphnée Bosch, lead author of the paper. “This laser expertise makes our approach unique.”

# MKS Advanced Packaging Handbook

## Semiconductor advanced packaging processes, technologies, and applications

Explore how advanced packaging is reshaping semiconductor integration – unlocking new possibilities through heterogeneous and system-level design.

As traditional transistor scaling approaches its physical limits, the semiconductor industry is turning to advanced packaging to maintain performance growth. This paradigm shift allows for the integration of multiple heterogeneous dies into a single package, unlocking new levels of functionality, bandwidth, and power efficiency.

Our process technologies in the Advanced Packaging Handbook are a comprehensive technical resource for anyone who wants to understand the latest advancements in semiconductor design and manufacturing.

To get the full Handbook, just scan the QR-Code

[www.atotech.com](http://www.atotech.com)

# Driving success for customers

**Alan Maher, Business Development Manager, Greene Tweed,** shares his thoughts on the industry's current buzz topics, as highlighted at SEMICON West, before outlining what is keeping the company busy, both now and into the future

**SIS:** If we can start with your overall feedback from the recent SEMICON West event – was it a success for Greene Tweed?

**AM:** Absolutely. Attendance was up significantly from last year, and you could feel the energy throughout the event. Having it in Arizona was also a nice change, especially with so many customers now based there. And locals turned up in numbers, which really helped.

Our booth was also buzzing with activity – customers, partners, analysts – it was a steady stream of meaningful conversations. The overall tone of the event, I would say, was optimistic.

**SIS:** There were a number of challenges discussed during the event – economics, supply chain and geopolitics, talent shortage and sustainability issues – what's the Greene Tweed take on these?

#### **AM: Supply chain**

The semiconductor industry is inherently cyclical, and supply chain challenges will always persist. We're focused on helping our customers navigate these complexities with innovative materials and solutions with our dual source model. On top of that, our global capacity

► Fusion® F07 FKM seal assembly used in semiconductor SubFab vacuum fittings and vacuum system lines operating up to 355°F (180°C).

investments ensure we're ready to support the next wave of growth. Our latest being our new manufacturing facility in Korea

#### **Talent shortage**

This is a critical issue for the industry. We ourselves are addressing it by fostering innovation and efficiency and making semiconductor careers more rewarding. Collaboration with partners and a focus on automation are key. Then there are great initiatives like the UK's Women in Tech Works that are focused on attracting and retaining more women in the industry.

#### **Sustainability**

We're committed to providing materials and solutions that perform at the highest level, while being mindful of their environmental impact. It's about balancing innovation with responsibility. We have two projects in the works where sustainability is the key driver that we hope to bring to the market in the near future.

**SIS:** There was also a great deal of positivity about the industry's numbers and future, with AI seen as the major opportunity right now?

**AM:** The numbers don't lie – AI is expected to make up nearly half of the semiconductor market by 2030.

That's huge. And we're already seeing how it's driving advancements in everything from high-performance

computing to advanced packaging. Greene Tweed is partnering with customers to tackle the unique challenges AI brings to manufacturing, in areas like particulation, electrostatic discharge, and adapting to new chemistries. It's exciting to be part of shaping AI.

**SIS:** Alongside the related topic of advanced packaging – 3D is here!?

3D is a new frontier. At SEMICON West, it was clear that hybrid bonding, substrate innovation, and other advanced packaging technologies are driving the industry forward. Greene Tweed is already making an impact in this space. Our Chemraz solutions are helping customers tackle the challenges of advanced packaging, from yield improvement to process reliability.

As the industry continues to push the boundaries of 3D integration, we're excited to extend our collaborations and help drive this innovation forward.

**SIS:** If not already covered, it would be great to understand Greene Tweed's role when it comes to supplying technology solutions to help the development of AI and advanced packaging technologies?

**AM:** Greene Tweed aims to be at the forefront of enabling the next generation of semiconductor technologies. For AI, we're delivering solutions that address critical manufacturing challenges, ensuring our customers can meet the demands of this rapidly growing market. In advanced packaging, we partner with customers to design materials that support the precision and reliability required for cutting-edge processes,

like hybrid bonding and 3D integration.

**SIS:** A couple of other takeaways from the event – the need for cost-effective innovation?

**AM:** Cost-effective innovation is a cornerstone of Greene Tweed's approach. We understand that our customers need solutions that deliver exceptional performance without compromising on value.

We remain committed to providing a well-balanced portfolio of options, including Chemraz, Fusion, and ONX materials, designed to strike a balance between performance and cost of ownership. For example, our Fusion F07 line exemplifies how we address specific process challenges while keeping cost-effectiveness in mind. Similar is our recently launched Chemraz G-Series range.

**SIS:** And the acknowledgement that no one organisation can 'do it all' – why is collaboration important?

**AM:** No single organization can tackle every challenge alone, especially in an industry as complex as the semiconductor ecosystem. To overcome the biggest hurdles, we need to work together.

Greene Tweed prioritizes close collaboration with Fabs, OEMs, and other industry leaders, as well as industry trade bodies. By working together, we co-develop innovative solutions to complex problems more effectively. I, myself, am part of a collective, grouping the critical needs of Fabs and OEMs in the USA and UK, and

forming tactical task forces to address these needs. The "collective" is the key to success.

**SIS:** How would you characterise Greene Tweed's profile in the semiconductor industry as of now – what have been the successes?

**AM:** Greene Tweed has been a trusted partner and innovator in the industry for over 35 years. Our materials and solutions are integral to critical processes across etch, dep and now advanced packaging, and we keep pace with changing needs.

You will find us on everything from 30-year-old legacy tools to the latest, most advanced tools in the world's leading Fabs.

Our success comes from a relentless focus on quality, innovation, and collaboration. However, the main driver of our success has been providing technology-enabling solutions to our customers' problems. By staying true to that approach, I believe we will continue to lead our field for years to come.

**SIS:** And how are you looking to further develop your presence in the sector – any plans you can share as to technology innovations coming down the line, different ways of working with partners and the like?

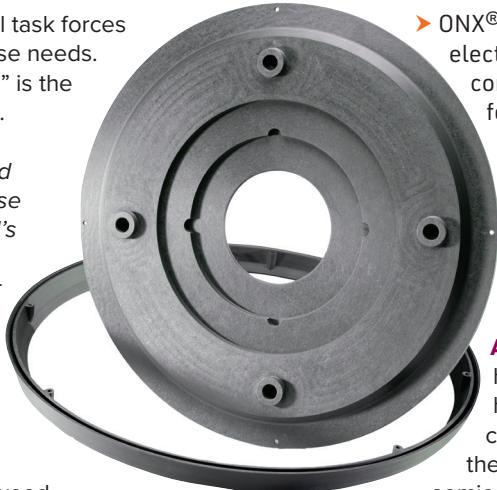

► ONX® 600 lightweight, electrically conductive composite components for semiconductor wafer handling and cleaning systems, stable up to 260°C (500°F).

**AM:** Greene Tweed has invested heavily in our global capacity to support the next growth in semiconductors, as well as

the research and development to create new materials and solutions for critical processes like etch, deposition, lithography, etc.

We're also strengthening our collaborations with OEM equipment providers and exploring new opportunities in advanced packaging and AI, so Greene Tweed can stay ahead of the curve and help our customers do the same.

**SIS:** Greene Tweed solutions cover a great many applications within the semiconductor industry – how to build on this success?

**AM:** We need to continue to innovate, deepen our partnerships with OEMs, Fabs, and academia, and deliver solutions that address our customers' evolving needs.

Whether that's through new materials or advanced manufacturing techniques, we're committed to driving success for our customers.

## Dedicated webinars for the silicon semiconductor industry

Using our 30+ years' experience in B2B vertical technical markets, and as the publisher of Silicon Semiconductor, we offer effective webinars, ZOOM interview and virtual events. We help you get your message, to your desired audience, by marketing to over 55,000 silicon semiconductor professionals.

Find out how Angel Webinar can help you organise and run a webinar within the silicon semiconductor industry.

### Reach Educate Influence

- Brand Awareness

- Lead Generation

- Thought Leadership

**SS SILICON**

SEMICONDUCTOR

Contact: Jackie Cannon

jackie.cannon@angelbc.com

+44 (0)1923 690205

# Preventing liquid cross-contamination in semiconductor manufacturing

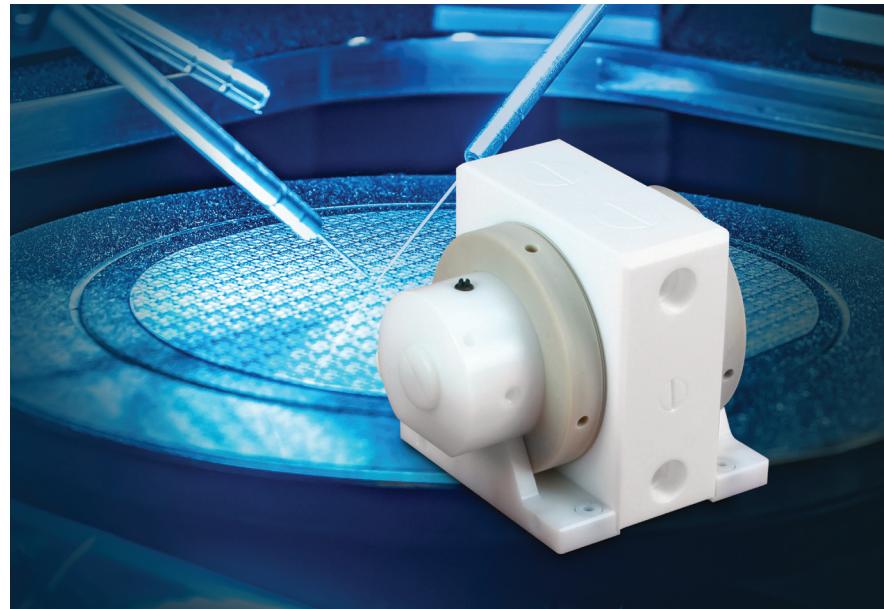

Producing high-purity wafers via the CMP process is a critical application and the halting of harmful slurry-DIW cross-contamination and back-flow can be optimised with the Malema Interconnect Interlock Device.

BY JAY RAJAGOPALAN, MALEMA

CHEMICAL MECHANICAL PLANARIZATION, or CMP, also known by some of its practitioners as Chemical Mechanical Polishing, is a stage in the semiconductor-manufacturing process where the surfaces of an integrated circuit – otherwise called a “wafer”

– are smoothed and flattened via chemical and mechanical forces.

The CMP process requires the use of a colloidal chemical slurry that contains nano-sized abrasive powders. The slurry is pumped over the surface

of the wafer with a polishing tool, which removes excess material and imperfections from the wafer’s exterior, resulting in a uniformly smooth and ultra-flat, or planar, finish. In the final stage of the CMP process, deionized (DI) water is sent through the polishing

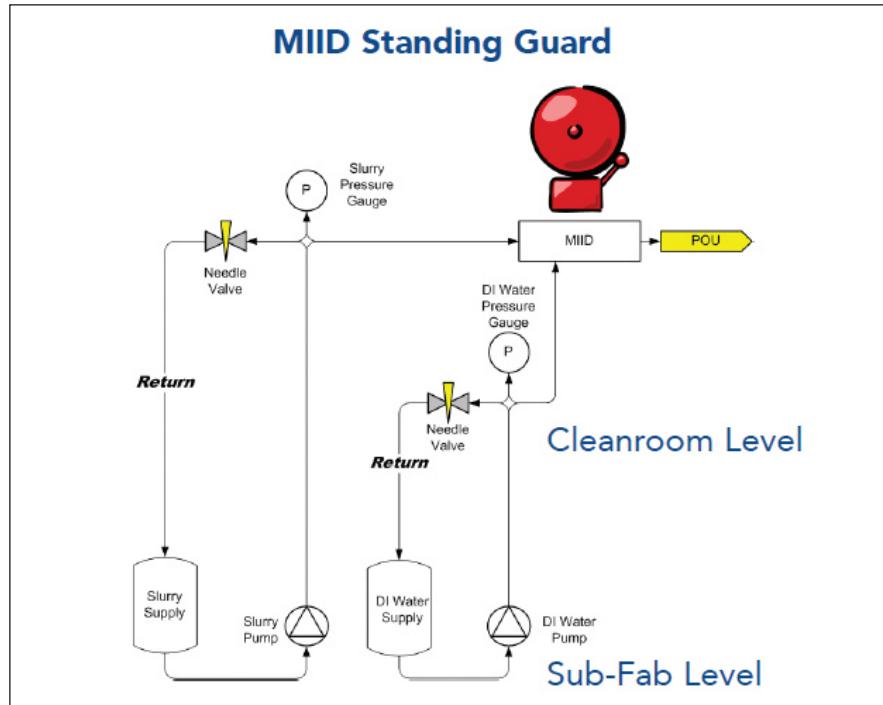

► Chemical Mechanical Planarization (CMP) is a critical stage in the manufacture of integrated circuits (wafers) for use with semiconductors. As such, it is imperative that the colloidal chemical slurry and deionized (DI) water that are used in the process do not commingle, with any cross-contamination compromising the slurry’s ability to deliver the required level of smoothness to the wafer’s surface. The Malema™ Interconnect Interlock Device (MIID-1000) overcomes this challenge through a design and method of operation that specifically prevent cross-contamination of the slurry and DI water, resulting in an optimized CMP process.

tool in order to wash away any remaining chemical slurry from the wafer's surface before the next wafer in the production line is treated.

To optimize the CMP process, it is imperative that the dedicated supplies of chemical slurry and DI water not be allowed to commingle; allowing this to happen will adversely affect the slurry's ability to deliver the demanded level of smoothness to the wafer's surface. However, some semiconductor manufacturers noticed slurry contamination with DI water within their CMP systems, which led to lost wafers, overall reduced yields and unwanted repair, replacement and cleanup costs.

This article will illustrate how this phenomenon was confronted and, eventually, solved through the creation of a breakthrough technology: the Malema™ Interconnect Interlock Device (MIID-1000), which has been designed to specifically prevent cross-contamination of the CMP slurry and DI water.

### The challenge

As mentioned, the overarching challenge of the CMP process comes from the aggressive nature of the chemicals that are used, as well as the abrasiveness of the very-fine grinding particles found in the polishing medium. This makes the flushing away of the used chemical slurry with DI water critical to the success of the CMP operation.

At the beginning of the process, however, the chemical slurry must not be contaminated by any other type of liquid. If this occurred, its ability and effectiveness in producing the ultrasmooth and ultra-flat wafer surface would be compromised.

The prevention of this unwanted occurrence has traditionally been achieved by using a three-way diverting valve designed to alternately deliver the chemical slurry and DI water for the CMP process. Operators were discovering, though, that there were times when the polishing tool requested slurry that DI water was delivered instead and vice versa.

An investigation into what was causing this problem also revealed that DI water was diluting the chemical supply and,

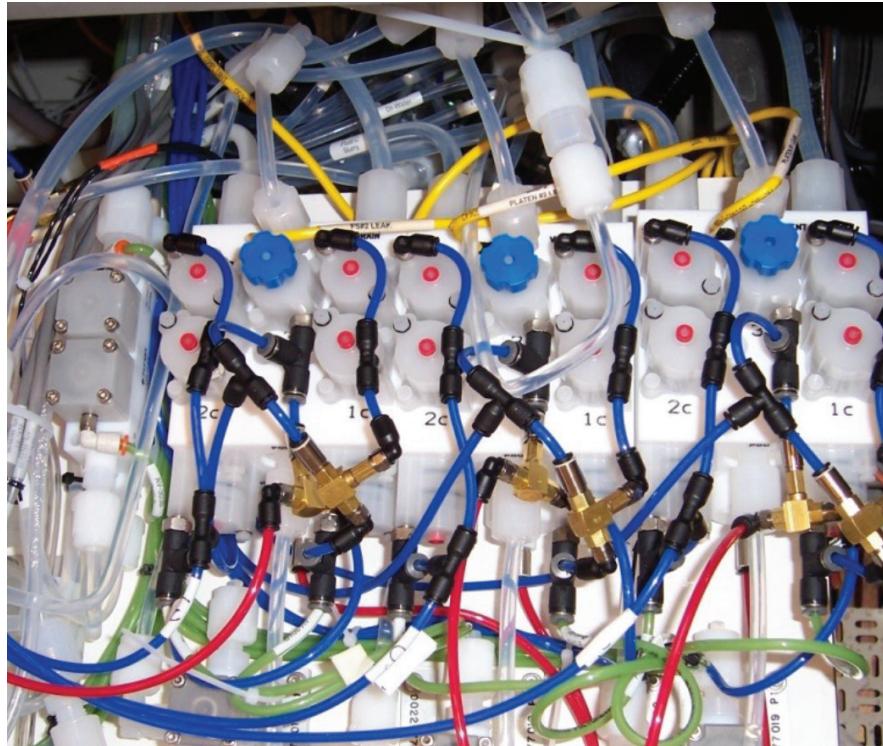

► One of the differentiating advantages of the Malema MIID-1000 is that it can be retrofitted onto existing CMP polishers as a drop-in replacement for the existing slurry-supply manifold. Malema streamlines this retrofit process by including all of the needed parts in a replacement kit with a single part number.

again, vice versa. At this point, the entire semiconductor-manufacturing system would need to be shut down for cleaning.

A thorough, top-to-bottom examination and review of the CMP system revealed that the root cause of the slurry/DI water cross-contamination was unexpected and intermittent reverse liquid back-flow or internal bypass leaks in the three-way valve that were occurring during certain operating conditions experienced by the polishing tool. Finding this hiccup in the CMP process was difficult because while the valves were indeed malfunctioning, they were not actually being damaged at the same time, so they would often times return to normal function for a period of time before malfunctioning again.

Identifying the problem was also made more problematic by the simple mechanical fact that, to some degree, all valves will leak. The job for the user is to determine what is an acceptable leak rate for the application in which the valves will be used. Further complicating the problem is the volume

of slurry or DI water that was lost during back-flow or reverse bypass-leak conditions could be less than 5 milliliters per minute (0.17 ounces per minute), a minuscule amount that can be extremely difficult to detect, yet one that still possesses the ability to contaminate or dilute the CMP processes' cross-connected liquids.

This cross-contamination via back-flow and bypass leaks can be prohibitively costly for the semiconductor manufacturer since it will typically result in the cessation of the production process and long periods of downtime.

These unplanned shutdowns to repair or replace leaking components and clean up contaminated plumbing systems will both adversely affect the operation's overall financial performance and make meeting tight delivery schedules virtually impossible.

All of this meant that a solution to the problem would have to satisfy two things: 1) detect when a back-flow or a reverse-bypass leak was occurring in the three-way valve and 2) prevent these events from happening.

### The solution

Recognizing the urgent need for a solution to the leaking three-way valve quandary, Malema, Boca Raton, FL, USA, a brand of PSG®, Oakbrook Terrace, IL, USA, a Dover company, began searching for ways to either prevent the leaks from occurring or develop a next-generation solution to the conundrum.

With over 20 years of experience supplying ultrasonic- and Coriolis-based flow measurement and control solutions to major semiconductor equipment manufacturers, the engineering team at Malema understood the industry's exacting requirements for cleanliness and reliability.

In the search for a leak-halting solution, Malema engineers tested a variety of methods that could potentially prevent the leaking-valve condition.

These included the incorporation of low-flow uni- and bi-directional flow switches, flow meters, and pH and conductivity meters. While these pieces of equipment were able to detect back-flow and bypass leaks in the three-way valves, they were only able to do so after the slurry or DI water supplies became contaminated, which compromised the CMP process.

The "eureka" moment for the Malema research team came when they determined that a "double block-and-bleed" (DB&B) valve arrangement would prevent reverse bypass leaks. DB&B is a piping configuration that anticipates leaking valves, but provides absolute protection against their precariousness by placing dedicated isolation valves upstream and downstream of a third vent valve on both the CMP slurry and DI water lines.

**“** The "eureka" moment for the Malema research team came when they determined that a "double block-and-bleed" (DB&B) valve arrangement would prevent reverse bypass leaks. DB&B is a piping configuration that anticipates leaking valves, but provides absolute protection against their precariousness by placing dedicated isolation valves upstream and downstream of a third vent valve on both the CMP slurry and DI water lines **”**

► A built-in leak sensor in the Malema MIID-1000 enables it to prevent cross-contamination from occurring by sounding a warning when a potential back-flow event that will mix the CMP slurry with DI water could be imminent.

This double containment between the two liquid-supply lines ensures that no amount of back-flow or bypass leaks will bleed through to the other side of the valve block. Instead, any CMP slurry or DI water that does leak is vented out of the polishing tool before it reaches the point of use (POU). In laboratory tests where all of the valves were actually forced to leak, the DB&B configuration prevented any of the leaked liquid from working its way downstream to the POU or back upstream to the supply lines.

These features were incorporated into the patented Malema Interconnect Interlock Device (MIID-1000) By-Pass

Leak Detection and Prevention System, which has been designed specifically to protect against liquid back-flow and internal bypass leaks. This capability is created via a manifold of pneumatically actuated valves that operate in a coordinated fashion in order to ensure that CMP-liquid supplies cannot be contaminated before use or during the actual CMP process.

#### Key features of the MIID-1000 include:

- All wetted components are constructed of high-purity PTFE (modified) and PFA

- Non-wetted surfaces of PFA and PVDF

- Other materials used: FKM seals, ECTFE-coated stainless steel, polypropylene, nylon and acetyl

- Media-pressure range from 0 to 80 psig (0-5.5 bar)

- Pneumatic-actuation pressure range of 60 to 120 psig (4.1-8.3 bar)

- Media-temperature range of 0°F to 265°F (-17.7°C-130°C), excluding phase changes

#### MIID standing guard cleanroom level sub

- Ambient-temperature range from 0°F to 150°F (17.7°C-130°C), with no frozen liquids allowed • Critical Value characteristic: Cv = 0.8

- Field-configurable inlet connections – with either 1/4- or 3/8-inch flare nipples – that allow for simplified retrofit installation and reduced inventories

- Minimal lead loss

- Built-in leak detection and monitoring

- Built-in optical valve-position sensing

- Valve components tested to more than 10 million cycles for DI water and more than 2 million cycles for SS-12 slurry

To simplify the incorporation of the MIID-1000 into a CMP system, Malema integrated the supply lines for the CMP slurry and DI water into a single block. This combines the leak-detection and drain-management features of two DB&Bs in one easy-to-handle and install console.

Additionally, Malema has created MIID-1000 retrofit kits – which can be installed by an experienced technician in as little as two hours – that include all components needed to upgrade an existing CMP system.

The retrofit kits place the MIID-1000

into a watertight programmable logic controller (PLC) enclosure. This allows the system's existing plumbing and pneumatic signals to be repurposed to manage the MIID-1000's functions.

Since this process makes the operation of the MIID-1000 completely transparent to the system's host-tool controller, no adjustment to the host tool's software is needed. Finally, all of the electrical connections between the MIID-1000 and the PLC are fully connected. This enables any leak-warning signals generated by the MIID-1000 PLC to be communicated to the existing user-input channels on the CMP polishing tool.

### Conclusion

The use of three-way valves in CMP systems in semiconductor manufacturing had been accepted, as had the fact that, at some undetermined point, those valves would experience liquid back-flow or internal bypass-leak conditions. The problem with this habitual "cost of doing business" with three-way valves was unpredictable

cross-contamination of the chemical slurry and DI water that are the lifeblood of the CMP process.

The results when this happens are not pleasant or profitable: shutdown of the semiconductor-manufacturing process; excessive downtime to rectify the problem; and the accumulation of ancillary repair, replace and cleanup costs that will have a deleterious effect on the operation's bottom line.

To put an end to this untenable situation, Malema worked to find a solution, achieving it with the creation of the Malema Interconnect Interlock Device. This innovative device allows semiconductor manufacturers to replace their OEM-supplied and mis-performing three-way valves with a DB&B-based solution that completely eliminates liquid back-flow and internal bypass leaks.

The ultimate result is optimized wafer production that can be a boon to the semiconductor-manufacturing operation's bottom line.

**Meet Hiro,

Your Fluid System

Reliability Resource**

*Access fluid system expertise wherever you are in the world. Connect with our global network of semiconductor industry specialists and get the local support you need.*

**[www.swagelok.com/Global](http://www.swagelok.com/Global)**

All service marks and trademarks shown are owned and registered by Swagelok Company. © 2025 Swagelok Company. [swagelok.com](http://swagelok.com)

**Swagelok®**

# Safety, purity and performance in semiconductor cleanroom environments

Advanced Almatec AODD pumps play a vital role in next-generation semiconductor manufacturing

BY JESSE OWEN AND DANIEL CZEKAJ, ALMATEC

THE semiconductor industry is growing at an unprecedented pace, fueled by the demand for advanced electronics, 5G infrastructure, AI processing power and IoT integration. As chip geometries shrink and production volumes increase, even the smallest impurities or equipment failures can result in costly yield losses. This environment demands not only cutting-edge fabrication tools but also auxiliary equipment, like pumps, that can maintain strict purity, safety and uptime requirements throughout production.

Because semiconductor manufacturing continues to evolve in scale and

sophistication, pump technologies must meet increasingly stringent demands. Whether it's transferring solvents, handling waste streams, or maintaining safety in environments with explosion risks, cleanroom-compatible pumping systems must deliver uncompromising performance without contaminating delicate processes.

One technology stands out for its ability to meet these challenges: air-operated double-diaphragm (AODD) pumps. Offering a unique combination of metal-free construction, chemical resistance, self-priming capability and ATEX compliance,

AODD pumps are increasingly being adopted in semiconductor cleanroom environments, especially for niche applications involving aggressive or explosive fluids.

This article explores how AODD pumps, specifically those designed for conductive, solvent-handling applications, can help semiconductor manufacturers maintain safety, reliability and operational uptime while navigating the complex requirements of modern cleanroom processing.

## Understanding the cleanroom pumping challenge

Cleanrooms in semiconductor facilities are tightly controlled environments. Even the most microscopic contaminants can destroy wafers or compromise yields. This puts extraordinary pressure on the materials and design of process equipment, including pumps.

In addition to purity, specific applications – such as solvent transfer, waste stream handling, or alcohol pumping – introduce an added layer of risk: flammability. In these cases, any electrostatic discharge or metal-on-metal contact within the pump could result in ignition. This is where the ability to provide explosion protection becomes vital.

► Every Almatec FUTUR Series component is repeatedly cleaned and assembled in ISO-class cleanrooms to ensure contamination-free performance.

**EDWARDS**

[ enabling environments where innovation thrives ]

**Ganymede**

Performance without compromise

Semiconductor fabrication facilities, commonly known as fabs, are required to follow global explosion protection standards, such as ATEX (ATmosphères EXplosibles) certification, for equipment operating in potentially explosive environments. Finding pumps that can meet both the cleanroom-grade purity and explosion-proof safety standards is no easy feat – yet it's where AODD technology excels.

Moreover, the pumping systems in these settings must operate reliably under fluctuating chemical conditions and temperatures, often in confined or enclosed cabinets. Maintenance opportunities are limited, so pumps must not only be durable but also easy to inspect or service with minimal disruption. At the same time, safety cannot be compromised. This combination of factors makes it critical for semiconductor fabs to specify pump technologies that are purpose-built for the unique operational and safety demands of cleanroom environments, particularly in niche or hazardous applications.

### The case for AODD pumps in semiconductor applications

AODD pumps have long been used in demanding industries due to their exceptional versatility, chemical compatibility and self-priming abilities. In semiconductor applications, AODD pumps offer a range of benefits over mechanical or centrifugal pumps:

**1. Metal-free, contamination-free operation:** Semiconductor-grade AODD pumps are often crafted entirely from high-grade plastics or PTFE-based materials. This design eliminates the risk of trace metal contamination, a crucial factor when handling ultrapure fluids or solvents in fabrication processes.

**2. Conductivity and electrostatic discharge control:** Specialized AODD pumps designed from conductive plastics, such as carbon-filled conductive ultra-high molecular weight polyethylene (UHMW-PE), enable safe fluid transfer in explosive or flammable environments. These materials allow for electrostatic dissipation while avoiding the use of metals altogether.

**3. ATEX certification:** Leading AODD pump models meet ATEX Zone 2 compliance requirements, making them

► Built from high-grade, non-metallic materials, Almatec FUTUR Series pumps are engineered for ultra-pure chemical supply and circulation in semiconductor manufacturing. Designed for long-term reliability, these pumps have become a trusted standard in fabs worldwide, helping manufacturers maintain the highest levels of safety, purity and process performance.

suitable for solvent handling, alcohol transfer, or chemical disposal tasks in explosion-prone areas of the facility.

#### 4. One-piece PTFE diaphragms:

Modern AODD pump diaphragms are machined from solid PTFE for maximum durability and minimal delamination risk. These diaphragms offer a long service life and ensure that aggressive fluids don't compromise pump integrity or performance.

**5. Straight-through flow paths and minimal bends:** In some AODD designs, the liquid path is engineered for minimal bends and surfaces, reducing particle generation and improving chemical compatibility.

**6. Self-priming, low-shear and maintenance-free:** AODD pumps are self-priming and capable of dry running. They are low-shear by design, protecting sensitive fluids, and they often incorporate maintenance-free air control systems, which require no external lubrication or electronics.

**7. Cost effectiveness:** AODD pumps are often more cost-effective over the long term compared to other pump types. Their robust construction, minimal maintenance requirements and compatibility with a wide range of chemicals help reduce downtime and

simplify spare parts inventory. These factors contribute to a lower total cost of ownership, making them a wise investment for fabs focused on long-term operational efficiency.

### Alcohols, solvents and waste streams

While most semiconductor-grade AODD pumps are used in ultra-pure chemical loops, a specific subset of applications presents a different challenge – safely transferring potentially explosive or aggressive media in cleanroom environments.

#### These include:

- Alcohol transfer for cleaning and rinsing processes

- Solvent and stripper circulation in lithography and etching steps

- Chemical waste and solvent recovery systems

- Tank or cabinet venting and draining in explosive atmospheres

In many of these applications, the implementation of ATEX-compliant pumping systems is not just a safety best practice; it's a regulatory and insurance requirement. Yet, meeting these standards without compromising cleanroom compatibility can be difficult.

The availability of a fully non-metallic, conductive and ATEX-approved AODD

pump bridges this gap, enabling facilities to adhere to explosion protection standards without sacrificing chemical purity or uptime. FUTUR Series AODD pumps from Almatec, a product brand of PSG, a Dover company, are designed precisely for such environments.

### Conductive, ATEX-certified FUTUR AODD pumps

The development of the Almatec FUTUR Series was directly driven by requests from semiconductor customers. These users wanted the proven benefits of the Almatec non-conductive FUTUR pumps, particularly the one-piece PTFE diaphragm. Still, they needed a version that could be safely deployed in ATEX-regulated environments. The result was the Almatec FUTUR: a carbon-filled pump combining cleanroom compatibility with explosion protection.

Available in different sizes, the Almatec FUTUR is one of the only pumps on the market offering the rare combination of ATEX certification, fully metal-free construction and a machined, one-piece PTFE diaphragm. This makes it particularly valuable in fab processes where contamination, sparking, or chemical degradation simply cannot be tolerated. Its conductive plastic construction eliminates the risk of static discharge without relying on any metallic components, aligning with the most stringent cleanroom safety protocols. Additionally, its straightforward installation and proven long-life design make it a reliable solution for operations that cannot afford downtime or maintenance interruptions. The Almatec PERSWING

P® air control system, which requires no lubrication or maintenance, adds an extra layer of operational efficiency.

Optional accessories such as stroke counters and membrane break sensors add further value, enabling real-time monitoring and predictive maintenance capabilities that help fabs stay one step ahead of unexpected failures or costly disruptions.

As a testament to the trust that semiconductor manufacturers place in the reliability of Almatec AODD pumps, more than 400 units have already been successfully installed at companies throughout Germany's Dresden region – widely known as "Silicon Saxony." This region has emerged as Europe's leading hub for semiconductor manufacturing and microelectronics, where global players operate alongside a robust network of medium-sized companies and cutting-edge research institutes.

With its unique ecosystem of suppliers, universities and applied research centers, Dresden seamlessly blends industrial strength with scientific expertise to drive breakthroughs in chip design and production. The strong presence of Almatec in this innovation-rich environment underscores its reputation as a trusted partner for high-performance, reliable pumping technology.

► Applications involving solvents, the Almatec FUTUR 100F is made from electrically conductive ultra-high molecular weight polyethylene (UHMW-PE), offering outstanding chemical resistance, abrasion resistance and conductivity.

### Conclusion

In a semiconductor industry defined by precision, purity and safety, selecting the right pumping technology for niche applications is critical. AODD pumps, especially those engineered with conductive, non-metallic materials and certified to ATEX standards like Almatec FUTUR pumps, offer fabs the ability to transfer aggressive or flammable media without compromising cleanroom integrity.

As fabs strive to scale production, minimize contamination risks and comply with stringent safety standards, advanced AODD pumps are poised to become more than just a utility. They will serve as a critical enabler, driving the next generation of semiconductor manufacturing with precision and reliability.

As the industry continues to evolve, the role of versatile, safe and contamination-free pumping technologies will only grow more critical. By choosing the Almatec FUTUR today, fabs secure unmatched reliability and the confidence to meet tomorrow's technological and regulatory challenges without compromise.

## Dedicated webinars for the silicon semiconductor industry

Using our 30+ years' experience in B2B vertical technical markets, and as the publisher of Silicon Semiconductor, we offer effective webinars, ZOOM interview and virtual events. We help you get your message, to your desired audience, by marketing to over 55,000 silicon semiconductor professionals.

Find out how Angel Webinar can help you organise and run a webinar within the silicon semiconductor industry.

### Reach Educate Influence

- Brand Awareness

- Lead Generation

- Thought Leadership

**SS SILICON**

SEMICONDUCTOR

Contact: Jackie Cannon

jackie.cannon@angelbc.com

+44 (0)1923 690205

## Maximising advanced packaging hinges on manufacturing process optimisation

Unlocking packaging's promise will require solving upstream manufacturing process bottlenecks and rethinking global semiconductor supply chain strategies.

BY DR. MAKSYM PLAKHOTNYUK, CEO AND FOUNDER, ATLANT 3D

AI CHIP revenue is soaring, driven by breakthrough models and unprecedented demand across the GPU and ASIC segments.

This rapid growth benefits semiconductor manufacturers, as each new AI generation requires ever-larger quantities of leading-edge silicon to deliver improved cost, performance, and efficiency per operation.

To keep pace with this demand – and transcend the physical limits of classic transistor scaling—advanced packaging technologies, especially 3D stacking and chiplet architectures, have become a vital frontier. These techniques integrate multiple chips and

components (such as CPUs, GPUs, memory, and high-speed interconnects) in a single heterogeneous package.

By minimizing the physical distance between elements, advanced packaging improves data transmission rates and energy efficiency, a key factor in the escalating technological rivalry between the U.S. and China.

Leading foundries and outsourced semiconductor assembly and test (OSAT) players are responding. Notably, TSMC has announced a \$100 billion U.S. investment plan – including a next-generation advanced packaging facility in Arizona – while Intel recently

expanded its advanced packaging operations in New Mexico, aiming for domestic supply chain resilience.

Such moves are further catalyzed by policy incentives and tariff structures designed to onshore semiconductor manufacturing capacity.

Despite these advances, challenges remain. Advanced packaging is highly complex, involving tightly integrated stacks of diverse materials and structures – such as interposers, redistribution layers (RDLs), and multiple active and passive chips.

Conventional thin-film approaches like atomic layer deposition (ALD)