# SILICONNECTING THE SILICON SEMICONDUCTOR COMMUNITY

## ClassOne simplifies metallization while improving On-Wafer performance

VOLUME 43 ISSUE I 2022

AN ANGEL BUSINESS COMMUNICATIONS PUBLICATION

#### INSIDE

News Review, Features News Analysis, Profiles Research Review and much more...

#### SUB-FAB SEALS AND COMPLEX CHEMISTRIES

The quest for higher performance has steadily increased the complexity of semiconductor manufacturing

#### UTILIZING BACKSIDE 3D SOC INTERCONNECTS

Significant performance gains are possible by utilizing new backside interconnects in 3D SOC circuits

#### SILICONSEMICONDUCTOR.NET

#### IMPROVE DESIGN FLOW THROUGH IP MANAGEMENT

IP reuse has become a necessity since circuits and systems are almost always built on content from preceding generations

## Perfect ALD

Fast batch manufacturing for 300 mm wafers

#### A REVOLUTION IN ALD MASS PRODUCTION FOR 300 MM WAFER MARKETS

The PICOSUN<sup>®</sup> Sprinter ALD system is designed to disrupt batch ALD production on 300 mm manufacturing lines in the semiconductor (emerging memory, transistor, capacitor), display, and IoT component industries. Barrier, high-*k* oxide, and conductive films are deposited in the PICOSUN<sup>®</sup> Sprinter with perfect ALD in mass production volumes.

#### SINGLE-WAFER FILM QUALITY SCALED TO HIGH VOLUME, WITH PERFECT ALD

Fully automated, SEMI S2/S8-certified PICOSUN<sup>®</sup> Sprinter combines the leading single-wafer film quality and uniformity with fast processing, high throughput, and uncompromising reliability.

Fast process times make Sprinter's thermal budget lower than typical vertical furnace reactors commonly used in batch ALD manufacturing. Fully laminar precursor flows in the reaction chamber guarantee perfect ALD deposition without unwanted CVD growth, minimizing the need for system maintenance.

Sprinter operates fully automated with Picosun's own, proprietary, SEMI-compliant PicoOS™ operating system and process control software. PicoOS™ combines individual ALD process module, wafer handling and transfer system, and instrumentation control under one common HMI for easy, intuitive and user-friendly operating of the whole Sprinter cluster.

## VIEWPOINT By Mark and rews Technical Editor

## Strong 2021 semiconductor sales set pace for 2022 growth

Looking back at 2021 we see a year that underscored the vital role semiconductor manufacturing plays in geopolitics and a universe of end-use products. In a January report, IC Insights said 2021 chip sales grew 25 percent; researchers forecast sales in 2022 will likely drop to a 'meager' 11 percent, which would have been considered 'outstanding' five years ago.

How is 2022 progressing? The Semiconductor Industry Association (SIA) reported in March that global IC sales increased 26.8 percent year-on-year this January, the second highest first quarter start in history.

While the global supply chain is still a tangled mess, there are signs that a gradual return to normal is unfolding. But as we have seen since 2020, what is predicted one month is not always realized the next.

When auto industry and consumer electronics manufacturing executives assembled in January for the JP Morgan Tech/Auto Forum, opinions about achieving a 'new normal' varied. For Nvidia Corporation, chips are still hard to find, with sales falling short largely due to unavailable key components, delivery delays and other headwinds; CFO Colette Kress said she expects constraints to ease mid-year.

Like many OEMs looking to balance demand, supply and internal post pandemic challenges, company after company has reported 2021 profits were held back by a slowly recovering global economy. Apple joined the chorus, reporting it could not realize up to \$6 billion in sales thanks to component shortages.

Sales outlooks for the balance of 2022 remain positive. Although the world is anxiously watching the war in

Ukraine that began when Russia invaded, it is too soon to tell how the conflict may affect the region or Europe as a whole.

In this edition of Silicon Semiconductor we explore a unique new approach to electroplating courtesy of ClassOne Technology. The company's new Solstice GoldPro system can dramatically simplify metallization, benefitting manufacturers pursuing

a 'More than More' strategy for enhancing performance.

We also look at major industrial trends that characterized 2021; the latest in technology for ensuring the integrity of vacuum and abatement seals from Greene Tweed; research updates from imec and tactics for managing IP resources by Perforce Software.

For your free weekly e-news roundup go to: SILICONSEMICONDUCTOR.NET

### CONTENTS

VOL 43 ISSUE I 2022

## 16

## ClassOne simplifies metallization while improving On-Wafer performance

Reducing transistor size to increase performance has driven semiconductor manufacturing since Moore's Law was first articulated. Only a handful of companies still pursue this; many others look to new device types and architectures that do not depend on shrinking transistors or increasingly complex and expensive equipment

#### 22 Imec demonstrates significant performance gains utilizing backside 3D SOC interconnects

Principal researchers at imec, working with Cadence EDA programmers, have demonstrated significant performance gains are possible by utilizing new backside interconnects in 3D SOC circuits.

#### 26 Top semiconductor manufacturers improve design flow through IP management

Intellectual property reuse has become a necessity since complex circuits and systems are almost always built on content from preceding generations.

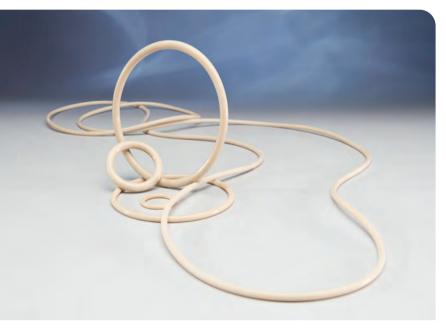

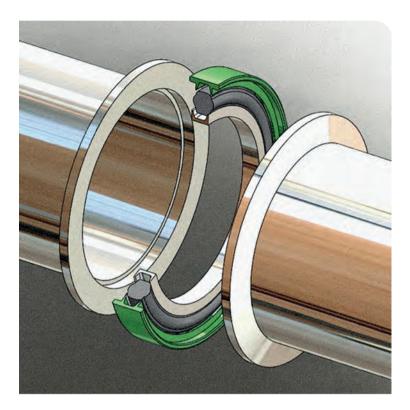

#### 30 Sub-fab seals critical in handling complex chemistries at higher temperatures

The quest for higher performance has steadily increased the complexity of semiconductor manufacturing

#### 34 Pandemic lessons learned will shape IC manufacturing well beyond 2022

From the first days of the pandemic to the recovery now taking hold, the semiconductor industry has retained its role as both a pain point and as a balm to speed a much needed global economic reset

#### NEWS

- 06 Surging automotive semiconductor industry to grow

- 07 Lam Research introduces suite of selective etch tools

- 08 Corning Laser Technologies announces new technology for glass wafer dicing

- 09 Picosun delivers powder MEMS technology platform

- 10 Siemens joins Intel Foundry Services' EDA Alliance program

- 11 EV Group and Teramount Collaborate

- **12** Particle measuring systems celebrates 50 years

- 14 Imec, KU Leuven and PragmatIC Semiconductor demonstrate fast 8-bit flexible microprocessor

Publisher & Editor Jackie Cannon Technical Editor Mark Andrews Contributing Editor Richard Stevenson Sales & Marketing Manager Shehzad Munshi USA Representatives Tom Brun Brun Media Janice Jenkins

Director of Logistics Sharon Cowley Design & Production Manager Mitch Gaynor jackie.cannon@angelbc.com mark.andrews@angelbc.com richard.stevenson@angelbc.com shehzad.munshi@angelbc.com tbrun@brunmedia.com jjenkins@brunmedia.com sharon.cowley@angelbc.com mitch.qaynor@angelbc.com Chairman Stephen Whitehurst Chief Executive Officer Sukhi Bhadal Chief Technical Officer Scott Adams stephen.whitehurst@angelbc.com sukhi.bhadal@angelbc.com scott.adams@angelbc.com

+44 (0)2476 718970 +44 (0)2476 718970 +44 (0)2476 718970

+44 (0)1923 690215 Direc +001 724 539-2404 +001 724-929-3550 Publ +44 (0)1923 690200 6 Bo +44 (0)1923 690214 Cove

+44 (0)1923 690205

Chief Technical Officer Scott Adams Directors Jackie Cannon, Sharon Cowley Published by Angel Business Communications Ltd,

6 Bow Court, Fletchworth Gate, Burnsall Road, Coventry CV5 6SP, UK. T: +44 (0)2476 718 970 E: info@angelbc.com

Silicon Semiconductor is published five times a year on a controlled circulation basis. Non-qualifying individuals can subscribe at: £50.00/e60.00 pa (UK & Europe), £70.00 pa (air mail), \$90.00 pa (USA). Cover price £4.50. All information herein is believed to be correct at time of going to press. The publisher does not accept responsibility for any errors and omissions. The views expressed in this publication are not necessarily those of the publisher. Every effort has been made to obtain copyright permission for the material contained in this publication. Angel Business Communications Ltd © Copyright 2022. All rights reserved. Contents may not be reproduced in whole or part without the written consent of the publishers. The paper used within this magazine is produced by chain of custody certified manufacturers, guaranteeing sustainable sourcing. US mailing information: Silicon Semiconductor, ISSN 1096-598X, is published 4 times a year, Jan/Feb, March, April/May, June, July, August/September, October, November/ December by Angel Business Communications Ltd Unit 6, Bow Court, Fletchworth Gate, Burnsall Rd, Coventry CVS 6SP. UK. The 2022 US annual subscription price is \$90.00. Airfreight and mailing in the USA by agent named World Container Inc, 150-15, 183rd Street, Jamaica, NY 11413, USA. Periodicals postage paid at Brooklyn, NY 11256. US Postmaster: Send address changes to Silicon Semiconductor, Air Business Ltd, c/o WN Shipping USA, 156-15, 146th Avenue, 2nd Floor, Jamaica, NY 11434, USA. Printed by: The Manson Group. ISSN 2050-7798 (Print) ISSN 2050-7801 (Online) © Copyright 2022. We strive for accuracy in all we publisher and resistions is published for inspublished articles to align old company names, branding, marketing efforts, taglines, mission statements or other promotional verbiage, im-ages, or logos to newly created or update previously published articles to align (or similar) when such references/images were accurately stated, rendered or displayed at the time of the original publication. When com

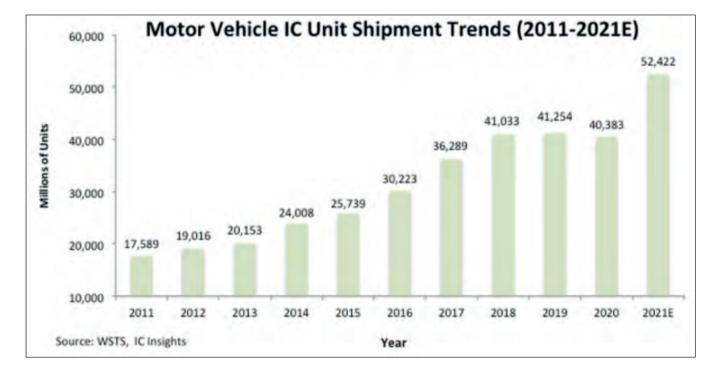

## Surging automotive semiconductor industry to grow

THE AUTOMOTIVE SEMICONDUCTOR industry is set to surge at a compound annual growth rate (CAGR) of 12.3% through 2025 on the heels of a strong comeback from the pandemic, according to a new report from Omdia.

Semiconductor content in automobiles has been increasing steadily for the past decade, but several recent trendlines have combined to accelerate automotive semiconductor revenues, Omdia notes in its new report Automotive Semiconductor Market Tracker - 2H21 Analysis. Those trends include rising sales of battery electric vehicles (BEVs) and growing demand for advanced driver assist systems (ADAS) and infotainment & telematics (I&T) systems, according to Sang Oh, Senior Research Analyst for automotive semiconductors at Omdia and author of the market tracker report.

"The average BEV creates 2.9 times more semiconductor revenue than a vehicle with a traditional internal combustion engine," Oh said. "In addition, ADAS applications like camera modules for park assistance and collision warning, plus I&T applications like the transition from analog or hybrid instrument clusters to digital clusters, are also driving increased semiconductor content."

#### Bouncing back from pandemic

COVID-19 dealt a significant blow to the global automotive semiconductor industry in the first half of 2020 as global vehicle production ground to a halt during the early days of the pandemic. But the industry posted a strong rebound beginning in 3Q20.

The sector's recovery accelerated in 2021, with total annual revenues hitting a projected \$51.6 billion, up 28.6% from the prior year.

This came at a time when the automotive supply chain overall continued to experience disruption, and global vehicle production grew a relatively small 2.5% in 2021 against the prior year.

"The much stronger recovery in the automotive semiconductor market than we see in the industry as a whole can be attributed to the dramatic increase in average selling prices for auto semis as supplies became constrained, as well as the trend for electronics manufacturers to pre-order and increase their inventories and safety stocks," explained Oh.

The Automotive Semiconductor Market Tracker summarizes the auto semis industry and provides information to help industry players better understand and forecast upcoming trends.

The report covers 30 separate semiconductor device types used across more than 49 different primary vehicle electronic applications. The tracker is built using vehicle production and electronic module fitment projections.

## Lam Research introduces suite of selective etch tools

LAM RESEARCH has announced a new suite of selective etch products that apply breakthrough wafer fabrication techniques and novel chemistries to support chipmakers in the development of gate-all-around (GAA) transistor structures. Composed of three new products – Argos<sup>®</sup>, Prevos<sup>™</sup> and Selis<sup>®</sup> – Lam's selective etch portfolio provides a powerful advantage in the design and manufacture of advanced logic and memory semiconductor solutions.

As modern technologies and devices continue to evolve, the need for greater device density for improved performance and efficiency increases. To keep pace with Moore's Law, chipmakers are now developing transistor structures vertically – an exceptionally complex process that requires ultra-high selectivity, precision etching and uniform isotropic removal of material without modifying or causing damage to other critical material layers.

Lam's selective etch solutions provide the ultra-high, tunable selectivity and damage-free material removal required to support advanced logic nanosheet or nanowire formation, enabling chipmakers to make the next evolutionary leap from planar to threedimensional structures for DRAM as it reaches its planar scaling limit.

Developed in collaboration with the world's most innovative logic and foundry chipmakers, Lam's selective etch products are already being used in the fabs of industry leaders like Samsung Electronics to support nearly a dozen critical steps in the advanced logic wafer development process.

"The semiconductor industry is continuously driven toward more powerful and faster device capability. As the density and complexity of the devices have been increasing significantly, selective etch technology is critical to manufacturing our most advanced logic device," said Dr. Keun Hee Bai, Master of Semiconductor R&D Center at Samsung. The Lam selective etch portfolio is composed of three new tools:

Argos, with revolutionary MARS<sup>™</sup> (Metastable Activated Radical Source) technology, selectively modifies and decontaminates wafer surfaces. Its groundbreaking treatment and conditioning capabilities enable chipmakers to treat wafer surfaces precisely, optimizing them for peak performance.

- Prevos enables atomic layer precision, ultra-high selectivity etching for oxide, silicon, and metal by combining novel chemistries and innovative vapor technology with agile temperature control. Prevos leverages a new proprietary chemical technology solution developed by Lam; additional chemistries can be added to support chipmakers' production needs.

- Selis uniquely employs both radical and thermal etch capabilities to enable ultra-high selective etching with uniform top to bottom process control without causing damage to the wafer structure.

- Prevos and Selis can also be delivered as a single, integrated tool to provide unique multi-layer selective etching, improved queuetime control, and maximum production flexibility.

#### Infineon names Rutger Wijburg as new COO

Rutger Wijburg will join Infineon's management board as new chief operations officer in April 2022. He will succeed Jochen Hanebeck, who will take over from Reinhard Ploss as the new CEO, according to plan.

"We are very pleased that Rutger Wijburg, an internationally experienced industry expert with intimate knowledge of both semiconductor manufacturing and the silicon foundry world is joining the Management Board team," says Wolfgang Eder, chairman of the supervisory board of Infineon. "He will bring valuable additional perspectives to the board as the chief operations officer."

"Electrification and digitalisation are major trends of the coming decade. Infineon is investing decisively in its manufacturing capacities in order to satisfy the long-term demand for semiconductor solutions," says Jochen Hanebeck, current COO at Infineon. "Rutger Wijburg has both the knowledge and the vision to develop Infineon's operations in the years to come.."

"Based on our structural growth drivers, Infineon is ready to invest in its manufacturing capacity and to extend partnerships in order to deliver to our customers what they need, when they need it," says Rutger Wijburg. "Infineon creates a competitive advantage through quality, innovation and cost performance. It will be my priority to further expand our lead over the competition by harnessing our technological leadership, while always keeping an eye on profitable growth."

Wijburg joined Infineon in 2018. As MD of Infineon Dresden, he was responsible for the successful rampup of highly automated 300-millimeter production. After taking over as head of frontend in the beginning of 2021, Wijburg has focused on expanding wide bandgap capacities and was instrumental in establishing the concept of the 300-millimeter "One Virtual Fab" cluster. He has more than 30 years of international experience in the semiconductor industry.

## Corning Laser Technologies announces new technology for glass wafer dicing

CORNING INCORPORATED today announced the launch of a dicing technology that will allow the company's Corning Laser Technologies (CLT) business to enter the semiconductor application space to further focus on microfabrication processes.

CLT advanced its patented nanoPerforation process and paired it with a well-established breaking technology from Dynatex International, an industry leader in mechanical breaking of crystalline wafers, to create a new glass wafer dicing technology.

The new technology will allow customers to drive lower cost through significantly higher throughput as well as achieve lower, near-zero kerf loss and high edge strength through an inherently clean process that will eliminate subsequent cleaning steps. Additionally, the glass wafer dicing technology for up to 300 mm diameter glass wafers achieves superior results on yield, enabling unprecedented die aspect ratios and a side-wall quality that meets the highest demands of the semiconductor industry. The innovation was developed for use in industries such as micro-fluidics and micro-optics. It can also be applied for meta-surfaces on glass and other glass wafer-based semiconductor applications, as well as dicing of other brittle and transparent materials.

"We are looking forward to leveraging our 20-plus years of experience in precision laser machining along with Dynatex's expertise in breaking tools and supporting equipment," said Michael Mueller, business director, Precision Glass Solutions and Corning Laser Technologies. "This novel wafer dicing method will help Corning continue to grow in the semiconductor industry and innovate to meet current and future demands."

With decreasing die sizes and increasing wafer diameters, material utilization becomes significantly more important for high-yield semiconductor applications. When comparing to a kerf-removing technology such as blade dicing (calculated with a kerf loss of 0.2 mm), CLT's new laser dicing method can increase utilization of a wafer with small dies of 5x5 mm by 8% and even smaller dies of 2x2 mm by 17%. Enabled by the near-zero kerf loss, a fully populated 300 mm diameter and 0.7 mm thick wafer can provide a wafer utilization of 96% calculated with an edge exclusion of 5 mm.

Small dies on large glass wafers require a high-quality and high-speed dicing process. With the die size of 5x5 mm, a 300 mm wafer can be fully diced in less than 10 minutes – significantly faster than classical blade dicing, which requires multiple hours to cut.

Additionally, when using Corning® HPFS® Fused Silica (HPFS), a semiconductor-ready wafer material known for its high transparency, results demonstrate the exceptional performance for chipping and edge quality. HPFS wafers allow for low chipping that is better than 50 µm with very precise edges and die corners.

#### Income and revenue up for Veeco

VEECO INSTRUMENTS has announced financial results for its fourth quarter and fiscal year ended December 31, 2021. Revenues were \$153.0 million, compared with \$138.9 million in the same period last year. GAAP net income was \$8.2 million, or \$0.15 per diluted share, compared with a net loss of \$0.1 million, or \$(0.00) per diluted share in the same period last year. Non-GAAP net income was \$22.6 million, or \$0.43 per diluted share, compared with \$15.0 million, or \$0.30 per diluted share in the same period last year.

For the full year, Veeco reports revenues of \$583.3 million, compared with \$454.2 million last year. GAAP net income was \$26.0 million, or \$0.49 per diluted share, compared with a net loss of \$8.4 million, or \$(0.17) per diluted share last year. Non-GAAP net income of \$73.6 million, or \$1.43 per diluted share, compared with \$42.3 million, or \$0.86 per diluted share last year.

"I am proud of our many accomplishments in 2021," commented Bill Miller, Veeco's CEO. "We successfully advanced our product innovation and penetrated new customers, enhanced our service capabilities, increased our manufacturing capacity, improved our capital structure, solidified our governance and commitment to corporate responsibility, and strengthened the Veeco United culture. In September, we announced long-term financial targets and made immediate progress toward those targets with significant revenue and EPS growth in 2021." We had solid results in the fourth quarter with revenue and EPS exceeding the midpoint of our guidance," continued Miller. "Demand in our semiconductor and compound semiconductor markets is exceptionally strong and we exited 2021 with order momentum, increased backlog and exciting opportunities that will support our growth strategy."

Veeco has given the following guidance for the first quarter 2022.

Revenue is expected in the range of \$145 million to \$165 million, GAAP diluted earnings per share are expected in the range of \$0.15 to \$0.32, and non-GAAP diluted earnings per share are expected in the range of \$0.28 to \$0.44. The guidance takes into account the impact of the adoption of ASU 2020-06, effective January 1, 2022.

#### **INDUSTRY NEWS**

## Picosun delivers powder MEMS platform

FRAUNHOFER INSTITUTE for Silicon Technology (ISIT) has taken PICOSUN P-300B ALD system into use as their powder MEMS technology platform.

Fraunhofer ISIT PowderMEMS is a new innovative technology for creating three-dimensional microstructures from a multitude of materials on wafer level.

The technology is based on bonding together µm-sized powder particles in a cavity with Atomic Layer Deposition (ALD). It has many advantages compared to other manufacturing techniques as it allows using much lower process temperatures compared to a traditional sintering process.

The bonded porous structures are thermally and chemically resistant thus enabling their extensive postprocessing in a clean room.

"The technology can be used for various applications, such as microelectronics, MEMS sensors, MEMS actuators and microfluidics.

For example, it enables the integration of porous and magnetic 3D microstructures on wafer level", explains Dr. Björn Gojdka, Group Leader at Fraunhofer ISIT.

"We were looking for a solution for conformal high surface area coating of powder located in trenches. Picosun solution is a perfect fit for this need as we are also looking into scaling up the technology. We are especially happy about the tool's hot wall reactor, versatile precursor sources and its easy maintenance", states Dr. Thomas Lisec, Chief Scientist at Fraunhofer ISIT.

"We are excited over this new technology coming to life and all the opportunities it will bring. I am especially impressed by the potential applications for the Fraunhofer ISIT PowderMEMS as they are exceptionally diverse. I'm looking forward to continuing working closely with Fraunhofer ISIT on bringing the technology up to industrial production", says Dr. Christoph Hossbach, General Manager of Picosun Europe GmbH.

## Grow your profits...

With on-site hydrogen generation

A Nel Hydrogen electrolyser will help save money, streamline operations and increase your bottom line.

- Alkaline and PEM technologies

- · Safe, clean and cost effective

- Consistent purity and pressure

Eliminate hydrogen delivery and storage

- Scale to match any application

nel•

Visit us on-line or call for a consult with one of our sales engineers today! +1.203.949.8697 www.nelhydrogen.com

#### **INDUSTRY NEWS**

## Siemens joins Intel Foundry Services' EDA Alliance program

SIEMENS Digital Industries Software has announced it has become a charter member of the Intel Foundry Services (IFS) Accelerator - EDA Alliance, a program committed to establishing an ecosystem for the design and fabrication of next generation Systemon-Chip (SoCs) manufactured on IFS' leading-edge process technologies.

The initiative promotes collaboration between IFS and its ecosystem partners, with a focus on reducing risk and tackling design barriers while accelerating time-to-market for mutual customers' products. IFS Accelerator - EDA Alliance partners receive early access to Intel process and packaging technologies, allowing them to cooptimize and enhance tools and flows to best realize Intel's technology capabilities.

"We are excited to announce the IFS Ecosystem Alliance as a major step forward for Intel's foundry ambitions," said Rahul Goyal, vice president and general manager for Intel Product & Design Ecosystem Enablement. "We are pleased that Siemens EDA has joined the program. The combination of Siemens' world-class EDA offerings and IFS' leading-edge process technologies will provide design teams across the industry with the solutions needed

to deliver in today's competitive IC markets."

As part of the alliance, Siemens plans to collaborate closely with IFS to optimize best-in-class IC design tools, flows and methodologies for Intel's world-class processes. The initial Siemens EDA product lines certified by IFS include the industry-leading Calibre® nm platform, as well as the Analog FastSPICE (AFS) platform for leading-edge circuit verification targeting nanometer analog, radio frequency (RF), mixed-signal, memory and custom digital circuits. "With the increasing importance of semiconductors in the global economy, Intel's commitment to the foundry market through IFS is an important new source of innovative capacity for advanced products," said Joe Sawicki, executive vice president, IC-EDA for Siemens Digital Industries Software. "Siemens is proud to collaborate with IFS to help provide software solutions that are tuned to allow mutual customers to get the most out of Intel process and packaging technologies."

### Expertise: Moderators, Markets, 30 Years + Pedigree

Reach: Specialist vertical databases

**Branding:** Message delivery to high level influencers via various in house established magazines, websites, events and social media

#### For more information contact:

Jackie Cannon T: 01923 690205 E: jackie@angelwebinar.co.uk W: www.angelwebinar.co.uk T: +44 (0)2476 718 970 E: info@angelbc.com W: www.angelbc.com

## EV Group and Teramount collaborate

EV Group (EVG), a supplier of wafer bonding and lithography equipment for the MEMS, nanotechnology and semiconductor markets, and Teramount, a supplier of scalable solutions for connecting optical fibers to silicon chips, announce a collaboration on implementing wafer-level optics to solve a major obstacle of silicon photonics, namely fiber chip packaging. The collaboration will leverage EVG's nanoimprint lithography (NIL) technology, expertise and services with Teramount's PhotonicPlug technology.

Under this collaboration, standard CMOS wafers that implement silicon photonics chips will be post processed using EVG's NIL technology to implement optical elements such as mirrors and lenses for Teramount's unique "self-aligning optics". This enables flexible beam extraction from the chips and easy connection to a large number of optical fibers. Furthermore, it enables wafer-level optical inspection capabilities for enhancing silicon photonics wafer manufacturing.

The collaboration is being carried out within EVG's NILPhotonics Competence Center at its headquarters in St. Florian, Austria. The NILPhotonics Competence Center provides an open access innovation incubator for customers and partners across the NIL supply chain to collaborate to shorten development cycles and time to market for innovative photonic devices and applications. Through the collaboration with Teramount, EVG provides process development and production services, as well as expertise in both CMOS and photonics manufacturing, thus accelerating the commercialization of Teramount's PhotonicPlug technology.

The need for high-speed data transfers in data centers, telecom networks, sensors and emerging applications in advanced computing for artificial intelligence (AI) is growing exponentially. This in turn is driving the importance of developing solutions that can cost-effectively scale up production of silicon photonics, which enable ultra-high bandwidth performance. The collaboration between EVG and Teramount aims to solve this problem.

"Our joint work with EVG has been very successful in producing this innovative synergy between wafer-level optics and silicon photonics wafer manufacturing," said Hesham Taha, CEO of Teramount. "By offering this capability to the industry, Teramount solves one of the major hurdles to further adoption of optical connectivity, which is critical for so many applications that require high-speed data transfers and low power consumption. Teramount's PhotonicPlug silicon photonics packaging technology is a truly novel approach to improving optical performance, and we are excited to be a partner in helping to bring it to the market," stated Markus Wimplinger, Corporate Technology Development and IP Director at EV Group.

#### **PTIM**WAFER SERVICES

OPTIM Wafer Services is pleased to announce the installation of an automated ALPSITEC MECAPOL E550 CMP tool at its site in Greasque France.

The system will allow OPTIM to offer for following new or improved services.

- Oxide CMP Planarisation

- Oxide Roughness Improvement

- Metal CMP

- Poly CMP

This additional capability enhances OPTIM's already large portfolio of services that include:

- Wafer thinning by grinding

- Individual Die thinning

- Taiko Grinding

- Single/Double side Polishing

- SOI Processing

- Edge Trimming

- Wafer Dicing

- Dice Before Grinding

- Wafer Cleaning

- Process development services, combining any of the above capabilities.

For detailed technical discussions please contact either Mr. Mark Wells or Mr. Georges Peyre using the contact details below or visit our website.

#### www.Optimwaferservices.com

Mark Wells Tel - +44 1743 891 820 Email – MWells@optimws.com

Georges Peyre Tel - +33 442 126 158 Email – GPeyre@optimws.com

#### **INDUSTRY NEWS**

## Particle measuring systems celebrates 50 years

PARTICLE MEASURING SYSTEMS (PMS) has celebrated the 50th Anniversary of its inception. Started in 1972 as a cloud microphysics company, PMS has grown into a solutions and thought leader for contamination monitoring and control within clean manufacturing facilities at facilities around the globe.

PMS was founded in 1972 in Boulder, Colorado, USA by Dr. Robert G. Knollenberg who invented the laser

Particle Measuring Systems Presidents (Lto R) Paul Kelly, John Mitchell, Dr Robert Knollenberg (founder), the late Dr Don Veal (not pictured) particle counter to count and measure the sizes of particles in air. In 1978 PMS sent the first particle spectrometer into space on the Pioneer Venus Probe. In 1985 it incorporated its portfolio of particle monitors into full Facility Monitoring Systems. In 1996 PMS was acquired by Spectris, whose focus is to equip their customers with the ability to reduce time to market, improve processes, quality and yield.

PMS has since developed into the industry leader in monitoring sensitivity and is the only complete contamination monitoring solution provider. PMS delivers not only micro contamination instruments, but also expert consultants, data management software, and training and education to our global customers.

As thought leaders and industry experts, the PMS teams have trained contamination monitoring professionals around the world using their inhouse "Particle College" curriculum. PMS employees are recognized as authorities in the field and are frequently asked to present at industry events and write technical papers for publications. PMS maintains an extensive knowledge center to educate and support contamination control specialists.

"It has been gratifying to see this business, that started with me designing and building instruments in my basement while juggling my full-time work in academia, grow into the industry leader for contamination monitoring in controlled environments", said Dr. Robert Knollenberg, founder, Particle Measuring Systems. This sentiment was supported by John Mitchell, 4th President of PMS, who followed, "The key to our success is having employees who embrace our values of Aim High, Be True, and Own It. I'm immensely proud to have been part of this growth while being a company with a purpose: making the world cleaner, healthier, and more productive. I look forward to what we will accomplish for our customers, employees, and the world far into the future."

### Edwards invests in New Arizona facility

Edwards, supplier of vacuum and abatement services and solutions to the semiconductor industry, has announced its investment in a new state-of-the-art manufacturing facility in Chandler, Arizona, North America.

The new 200,000-square-foot facility will use the latest manufacturing and digital technologies to support the fastgrowing North American semiconductor market with services and solutions for the efficient and environmentally sustainable production of chips.

"Unprecedented growth in the semiconductor market to meet the world's growing consumer demand has resulted in extraordinary growth in demand for Edwards' products and services," said Troy Metcalf, president of Edwards Semiconductor Service. "Looking ahead, this growth is set to continue, with our customers in the USA investing billions of dollars in additional manufacturing capacity. At Edwards, we have a long tradition of supporting our customers with local service and manufacturing capabilities, and our investment in the Chandler facility continues that tradition. With the utilisation of the latest in smart manufacturing techniques and advanced automation, this new facility will be instrumental in supporting the safe, productive and environmentally sustainable manufacturing of semiconductors in North America."

The Chandler facility will also feature warehousing facilities, factory areas, meeting rooms, and a dedicated training centre. It is anticipated that the new facility will create approximately 200 new jobs in the local area, with scope to grow along with the market.

Construction of the new site in Chandler is underway and from the third quarter of this year, the facility will commence the remanufacturing and assembly of equipment essential to meet the demand for new semiconductor fab requirements. It will use advanced automation and data solutions to disassemble, clean, inspect, repair, replace and reassemble vacuum pumps. Reduced transportation through close customer proximity, along with water recycling and the use of renewable energy will all contribute to more sustainable manufacturing operations.

## **SEMI AMERICAS EVENTS**

## **Technology Leadership Series** of the Americas Events

JULY 12-14, 2022 SAN FRANCISCO, CA

JULY 12-14, 2022 SAN FRANCISCO, CA

The **Technology Leadership Series** of the Americas is a collection of eight major events representing the various technology communities in our industry. These programs connect 2,400+ member companies and over 1.3 million global professionals to advance the technology and business of electronics manufacturing and the design-supply chain.

There are numerous ways for you to participate in these events to connect with the industry and grow vour business.

#### ATTEND | PRESENT | SPONSOR | EXHIBIT

### SAVE THE DATES FOR THESE 2022 EVENTS

Explore these upcoming programs and fill out the Interest Form on each website to get connected for the latest event updates.

#### www.semi.org/semi-americas

## Imec, KU Leuven and PragmatIC Semiconductor demonstrate fast 8-bit flexible microprocessor

AT THE 2022 International Solid-State Circuits Conference (2022 ISSCC), imec, a research and innovation hub in nanoelectronics and digital technologies, KU Leuven, and PragmatIC Semiconductor, presented the fastest 8-bit microprocessor in 0.8 µm metal-oxide flexible technology capable of running real-time complex assembly code.

The microprocessor was implemented with a unique digital design flow that allowed the creation of a new standard cell library for metal-oxide thin-film technologies – relevant for designing a broad range of IoT applications.

The robust thin-film technology offered by imec's foundry partner PragmatIC Semiconductor was key to integrate the approximately ~16,000 metal-oxide thinfilm transistors on a 24.9mm2 flexible chip.

Flexible electronics based on thinfilm transistor technology is preferred over Si CMOS-based electronics for applications requiring low-cost, thin, flexible and/or conformable devices. The technology already made inroads in, e.g., health-patch sensors and RFID labels, and as a driver for flat panel displays. The missing piece is a flexible microprocessor to perform more complex signal processing calculations – as such adding compute functionality to a broad range of IoT applications.

Imec has designed a flexible 8-bit microprocessor in 0.8 μm indiumgallium-zinc-oxide (IGZO)-transistor technology, able to perform such complex computations. Kris Myny, Principal Scientist at imec:

"Our flexible microprocessor shows excellent characteristics for IoT applications, including high speed (71.4kHz max operating speed), Iow power consumption (11.6 mW when running at 10kHz, 134.9 mW at max operating speed), and high transistor integration density ("16,000 transistors with 0,8 µm gate length in a 24.9mm2 chip).

"Moreover, at ISSCC 2022, we will showcase real-time correct operation of our circuit by running the complex assembly code of the popular Snake game."

With the new microprocessor, imec addressed major challenges related to the design of unipolar systems. Kris Myny: "Metal-oxide thin-film transistors based on IGZO are inherently n-type.

This results in circuits with a higher (static) power consumption compared to complementary technologies. To address this, we created our own design flow starting from the open-source file of the MOS6502 microprocessor – one of the most influential microprocessors ever designed.

We engineered the number of cells and logic gates to obtain the most optimal design for our flexible6502 microprocessor in terms of area, power, and speed – using pseudo-CMOS as our logic family. This unique design flow allowed us to create a new standard cell library for metal-oxide thin-film technology that can be used to innovate applications based on metal-oxide thin-film technology. As such, this work nicely wraps up my ERC Starting Grant which aimed at opening up new horizons in the field of thin-film transistor technology."

To fabricate the flexible microprocessor, imec teamed up with foundry partner PragmatIC, whose unique FlexIC Foundry offers rapid prototyping and high-yield volume manufacturing of flexible integrated circuits. Brian Cobb, VP Product Development at PragmatIC: "Until recently, there was no mature and robust technology available for integrating such a large number of thin-film transistors with sufficient yield.

Our pioneering FlexLogIC fab now enables the rapid turnaround of such complex new designs at an ultra-low cost, delivering ICs on thin and flexible wafers. Our FlexIC Foundry service continues to be instrumental in enabling design teams like the one at imec to expand the range of design and use cases for flexible electronics."

This research was performed in the framework of the ERC starting grant FLICs under grant agreement No 716426 under the European Union's Horizon 2020 research and innovation programme.

## **3 EVENTS 2 DAYS 1 TICKET**

One ticket gives you access to a 2 DAY EVENT which will see 3 GROUPS of device makers gathered under one roof.

Hear over 100

PRESENTATIONS

covering the entire spectrum of the compound semiconductor, integrated photonics and global sensor supply chain.

Connecting, informing and inspiring the compound semiconductor industry

csinternational.net

picinternational.net

28-29 June 2022

Sheraton Brussels Airport Hotel Belgium Sensor Solutions: Market opportunities

sensorsinternational.net

For speaking & sponsorship opportunities call: +44 (0)2476 718970

Register NOW and secure your place Registration allows access to: CS INTERNATIONAL PIC INTERNATIONAL & SSI INTERNATIONAL

https://angel-tech.net/register

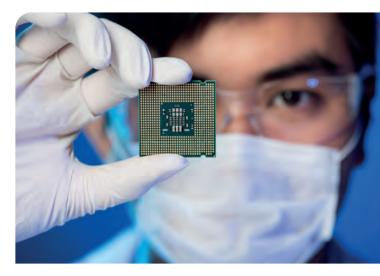

## ClassOne simplifies metallization while improving On-Wafer performance

Reducing transistor size to increase performance has driven semiconductor manufacturing since Moore's Law was first articulated. Only a handful of companies still pursue this; many others look to new device types and architectures that do not depend on shrinking transistors or increasingly complex and expensive equipment. ClassOne Technology is a leader in the anti-complexity revolution that champions high performance and cost-effective throughput.

#### BY JOHN GHEKIERE, VICE PRESIDENT, PRODUCT AND TECHNOLOGY, AND CODY CARTER, PRODUCT ENGINEER, CLASSONE TECHNOLOGY

THE WITHERING MARCH of relentless device scaling described by Moore's Law has left a mere handful of device manufacturers in that race, with TSMC clearly in the technology lead. When the cost per transistor inflected to become more expensive with each generation, somewhere between 26 and 22 nm nodes, it drove even many of the larger and more powerful manufacturers to alternate paths of innovation and new means of bringing value; GlobalFoundries pivoted boldly into FD-SOI; STMicroelectronics into SiC. The broad expansion of new device types - in short, the ubiquitous adoption of microelectronic devices into almost every aspect of our daily lives - has brought about the More Than

#### COVER STORY I CLASSONE TECHNOLOGY

Moore era, where feature scaling is no longer the sole means of device innovation.

This sea change in device innovations has essentially occurred in the wake of feature scaling, in a space of free-mindedness around device architecture and the applicability of manufacturing steps defined by that ceaseless grind. The industry, in a sense, has been able to take a breath, and we now see clearly, perhaps surprisingly, that the pace of Moore drove into unit processes and capital equipment certain complexities that may add little or no value. Whereas More Moore brought an almost exponential increase in complexity to unit processes, More Than Moore, while retaining expectations around on-wafer performance, has kicked wide the door to reducing complexity.

The shift is not only timely; it is critically necessary in very practical ways. As the global race for semiconductor leadership continues to escalate, thousands of new semiconductor jobs are being opened with thousands more to come. It is an expansion not previously seen and its impact is the rapid dilution of experience in the workforce. Now, the complexities of setting up, operating and optimizing unit process equipment becomes a costly, and for many More Than Moore manufacturers, a debilitating challenge. Device manufacturers need the same performance from their equipment, but they need it to be simpler to use.

The truth of the impacts of Moore on complexity was made clear to me, in a previous role, during a visit to a major advanced memory manufacturer to discuss process equipment technology. I had traveled to share some recent development results, aiming to place equipment within a new R&D location within the fab. The senior technology director was pressing me on a particularly nuanced capability that our competitor had and we did not. Adding the capability meant introducing a complicated mechanical system submerged in a concentrated wet chemistry. From an engineering perspective, such a system was not only expensive, but it introduced a dozen new potential failure modes. I explained to him that we had studied that function and its effects in depth and could find no indication of any kind that it provided any benefit. I asked for clarity of its on-wafer benefit. He said, "John, you don't understand. If I can measure it, then you must control it."

It became clear. The pace of Moore means that there is simply not sufficient time to investigate everything to complete understanding. Perception of risk is risk, thus, complexity is driven in, even if, in certain cases, that complexity serves as largely an insurance policy against factors that may or may not be important. Better to have the complexity (and cost) than the question.

The More Than Moore crowd are rising in the wake of Moore, where heightened complexity no longer

offers assurances. It offers higher cost and more unwieldy process steps; and if it doesn't bring measurable benefit, then it simply isn't needed. The opportunities are fruitful. This article will focus on the simplification of electrochemical deposition (we'll simply say plating), which when compared to the entirety of semiconductor unit processes, already lies somewhere in the middle in terms of complexity. Plating is also broadly and deeply captured by a great host of patents. As a basic technology, plating is already more than 200 years old; yet, as we will show, even its fundamentals are ripe for innovations that simplify operation while not only maintaining on-wafer performance, but improving it.

Plating remains an enabling, cost effective and highly-flexible option for metallization. The means of producing high quality plating and excellent onwafer results are well established. The principles behind great performance are no longer the domain of one or two providers.

Uniform deposition by plating requires careful sculpting of two key factors: the electric field profile and the fluid motion profile.

As it turns out, the electric field is actually the easier of the two to perfect. Computational Fluid Dynamic modeling (CFD) provides an exceptionally accurate and predictive model around the electric field and its ultimate effects on on-wafer performance, namely film deposition rate. The need here is to deliver a zero-gradient potential at the wafer surface. The electric field wants to be zero-gradient so this aspect of reactor engineering has a lot to do with developing hardware that "stays out of the way." In terms of the actual state of reactor hardware in the industry, however, the scaling race resulted in over-engineering of plating chambers for most More Than Moore applications and, arguably, many

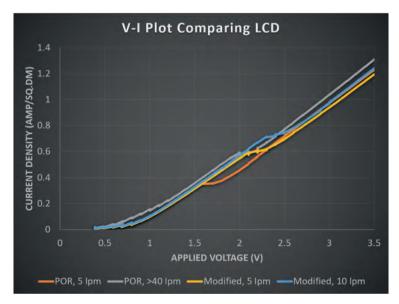

Figure 1: V-I plot comparing LCD of POR condition against modified condition

#### COVER STORY | CLASSONE TECHNOLOGY

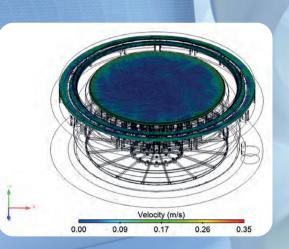

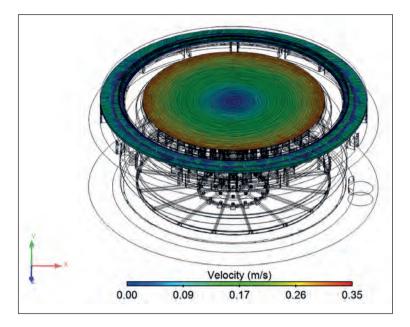

➤ Figure 2: CFD image of electrolyte at wafer surface applications at >32nm node.

Anode elevators, mechanically actuated irises and multiple independently controlled anodes provide very clever and interesting control knobs (as an engineer who worked extensively with such systems, I also found them extremely fun to play with). But these features add complexity and hardware costs that provide little to no benefit except in the most extreme use cases. For example, multiple independently controlled anodes do allow for radial tuning of the electric field. But so do physical diffusers made of natural polypropylene. The difference is not in the ability to deposit uniformly - both do. The difference lies in the need (or lack thereof) to adjust dynamically insitu.

Electric field dynamic tuning is very cool. But patently unnecessary for seed thickness above about 100A. A careful reader of this article will note that a uniform potential at the wafer surface does not necessarily mean a uniform current density across that surface. However, looking more closely at the reality of the situation, we find that until scaling drives a sufficiently thin seed material, one that results in a significant potential gradient across the wafer itself, a uniform potential does result in a uniform current density. The multiple independent anodes, as well as mechanically actuated irises, really only find their use in the dynamic condition where a very thin and resistive seed rapidly, typical of the most advanced logic and memory devices, thickens with plating, changing the curve to a flat one. The vast majority of MtM applications, as well as damascene applications at 32nm and above, are applied to wafers with a flat potential profile. It's notable, if you believe the patent landscape, that only one major plating manufacturer engineered multiple anodes into its system, and more notably that the provider with the larger market share was not that one.

So we see that shaping the electric field is readily done and without complexities that bring challenging setup procedures as well as expanding modes of potential failure.

The more challenging factor is the fluid motion profile. The fluid motion profile relates entirely to cation availability. Plating processes result in beautiful, shiny high purity metal films in large part because those processes are run in an "electronpoor" regime. This regime is crippled when the concentration of target cations available at the surface of the wafer is drawn down to become similar to the "concentration" of electrons. In such areas on the wafer where this depletion occurs, the resistance rises, and since the plating system is driving a potential while tuning by an ammeter, the localized current density is lowered and plating slows locally.

The key to ensuring abundant cation supply is to make uniform the time required, at each location, for the target cation to cross the diffusion layer. This can be done by simply slowing the process. But, as a rule, device manufacturers do not like to slow down processes. Again, the inherently risk-averse drive of Moore resulted in a large number of complexities aimed to eliminate questions of cation availability with brute force as opposed to system efficiency.

There is an interesting difference between e-field and fluid motion profile in that the e-field reaches the wafer and "sinks in". The fluid motion profile, by contrast, has to get out of its own way. The fluid that reaches the wafer must turn and go away from the wafer, and it must move past other fluid in order to do so. The challenge here, in terms of supporting the highest possible plating rates, is to sculpt the fluid motion profile in such a way that no bias of motion is produced. A bias in fluid motion vector creates localized and stable differences in diffusion layer thickness, which translate to slightly different times for cations to diffuse. As the current density is increased in order to drive the fastest possible process, so is the consumption of those precious cations.

The limitation is reached wherever that supply becomes sparse and starts to impose higher potential, thus lower current density, thus slower localized plating, and an impact to uniformity. The most prevalent solution to combat this in the industry has been the inclusion of a submerged paddle. While simple in concept, paddles do add to complexity of a chamber. They introduce more moving parts and therefore things that require setup and which have certain modes of failure. They also, obviously, add to the cost of building the reactor, both in terms of materials, machining steps and labor of assembly. In cases where a technician needs to access the interior of the chamber, for whatever reason, there is now the need to get the paddle out of the way of hands and tools. In short, chambers must be disassembled for even relatively

#### COVER STORY | CLASSONE TECHNOLOGY

minor maintenance tasks.

Interestingly, as noted earlier in this article, whereas we said that forming the profile of the electric field was easy and amounted to setting it up and then staying out of the way, with paddles, there is something literally placed in its way.

In actuality, the electric field is not manipulated by the motion of the electrolyte. But it is manipulated by the hardware that produces the motion of the electrolyte. Put another way, one can independently model the electric field and the fluid motion profile. And the results of the models accurately predict on-wafer behavior. The two factors really do function independently from one another. This means, in theory, it should be possible to tune them separately. And yet, reactor designs historically bind the two together. After all, the fluid passes through and across the same hardware that the electric field does. The result has been the proliferation of highly complicated reactors driven by the dual constraint of field sculpting and fluid motion formation. Theoretically then, if one can fully segregate optimization of the electric field from optimization of the fluid motion profile, then both can be tuned to best possible state without "getting in the way". And this, it turns out, can be done with a reduction in complexity as opposed to an increase.

The thickness of the diffusion layer cannot be directly measured of course. But a very descriptive proxy is available by use of an V-I graph, which plots voltage as an input and current as the output. Ohm's Law of course states that, for an electrical circuit with a given resistance, current rises linearly with voltage. This is true of electrochemical systems as well, yet with one notable influence. Electrochemical cells involve electrochemical reactions, meaning the electrons are "consumed" in the formation of reaction products, namely deposited metal. When cations begin to become scarce, the resistance of the system begins to rise and the curve starts to flatten out, as shown in Figure 1. This flat region is called the Limiting Current Density (LCD) and it serves as a practical limitation to how fast one can drive a plating system. Approaching this region leads to poor uniformity and ultimately poor deposition.

The LCD of a given system thus serves as a means to compare cation availability between systems. If a modification of a given system results in the LCD being moved to a higher potential, that means the supply of cations has been improved. It further means that the system can be run at a higher current density while still depositing high-quality films.

ClassOne Technology, with MtM manufacturers as its target customer base, has adhered since inception to a design ethic whereby no complexity is added to its Solstice plating system unless actual value is realized. And even having started from this mission of design elegance, continues to uncover new means of advancing on-wafer results while maintaining or even reducing complexity. In revisiting the principles summarized above, we understood that our paddle-free GoldPro reactor, which already competes with all major plating systems globally for on-wafer performance and feature uniformity, could be improved further in terms of the simplicity in delivering perfectly uniform features across the entire wafer.

Typical adjustments that raise LCD include increasing agitation or increasing temperature. Typically, increasing electrolyte temperature causes certain undesirable side effects and is not a practical option. This leaves agitation and also explains the reason that paddles have been so prevalent in reactor design. Other means of enhancing agitation involve higher wafer rotation rates and higher fluid flow rates. Wafer rotation rate is constrained by two factors: one, it produces radial effects in terms of localized variations in cation availability, thus there is going to be an optimal rotational speed above which uniformity becomes worse again. Secondly, a too-high wafer rotation can establish stable and directional fluid motion, i.e. bias, that results in localized non-uniform plating and lopsided features. Thus wafer rotation rate is not really a viable process knob for substantially increased plating rates.

Sheer fluid flow rate is viable as a process parameter though it bears practical limitations related to pump size as well as fluid evacuation (remember, the fluid has to get out of its own way). If the aim is simplification, which it is, then inclusion of a paddle is not taking things the preferred direction. All of this apparently leaving few options for raising LCD and making room for higher plating rates. ClassOne, through a focused effort aided by CFD modeling, investigated certain passive means of fluid manipulation within its reactor, aimed at producing ample fluid motion in a non-directional

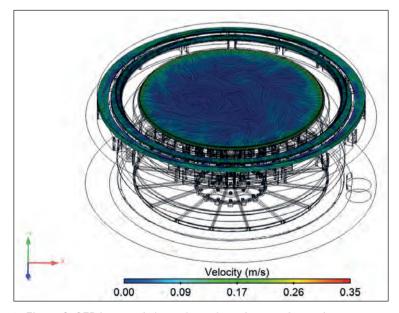

Figure 3: CFD image of electrolyte <1mm from wafer surface showing randomized motion

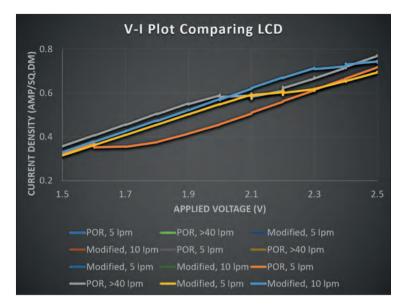

Figure 4: V-I plot zoomed in to highlight increase in LCD using modified condition

manner. Considered more closely, our aim was to transform the observed motion of fluid from the circular motion of liquid attached to the spinning wafer to a random pattern, and to do so as close to the wafer as possible. CFD modeling of various reactor concepts directed the design team to a specific concept that manipulates fluid motion in a passive way (i.e. no paddles or moving parts).

As the model shows, the electrolyte at the wafer surface (d=0) is clearly attached and moving rotationally with the wafer. Yet at a distance much less than a millimeter, the fluid motion is already largely random, leaving no effective bias. (See Fig 2 and 3) Further, the concept increases cation availability, as evidenced by a significant shift upward of the LCD. The LCD is found by initiating a plating sequence in voltage control mode and then periodically raising the voltage setting while recording the current that results.

Using this method, the LCD was found for POR condition which uses a flow rate of >40 lpm. Combined with a specific wafer rotation rate, this POR produces cross-wafer uniformity in gold of <2.5% 3-sigma and a feature uniformity of <1% (maxmin / max+min). We then used the same method to find LCD at lower flow rates, including as low as 5 Ipm through the system. The lower flow rate on the standard system produces a very low LCD, so low as to be debilitating. In short, this is a process of very low productivity.

Next, by implementing some targeted changes to fluid motion through the reactor, still employing a passive system, we determined that the LCD at 5 Ipm flow rate, could be raised again to the level of LCD for the POR at >40 lpm. The conclusion is that, with the targeted modifications to the reactor, we are able to maintain very high cation availability at the wafer surface while decreasing the flow rate by more than 87%! This opens the process window significantly without high flow rates. As a last confirmation of the new approach, we then increased flow to 10 lpm (still a quite low flow rate) and we see that the LCD is actually improved to a value higher than the original POR. (See Figure 4) The conclusion is that greater performance is achieved using a simpler process.

The specifics of this design, while they cannot be disclosed in this publication, also ensure that the manipulation of the fluid motion profile does not interfere at all with the formation and shaping of the electric field. The chamber stays out of its own way. Taking altogether, we confirmed that exceptionally high cation availability is possible at significantly low flow rate using a passive means of fluid motion control, i.e. no paddle or other submerged moving parts. Further, we demonstrated we were able to achieve this profile without interference to the electric field distribution.

The work shows that there is ample room, particularly among More Than Moore device manufacturers, to not only maintain competitive on-wafer performance, but to improve on it, while simultaneously eliminating complexities in the process system. This results in lower costs on equipment, lower costs on maintenance, and a far simpler system to operate at a time when the industry is experiencing rapid dilution of experienced workforce.

And this is just the beginning.

For additional information, please visit: https:// classone.com/reactor-and-platform-innovationsadvancing-our-plating-technology/#GoldPro

Talk to us about sponsorship NOW as it will be another full house Contact us at: info@angel-tech.net Or call us on +44 (0)2476 718970 and speak to Sukhi Bhadal or Stephen Whitehurst

Non-Contact Flow Meter SEMIFLOW® CO.65 Highly Accurate Flow Meter for Rigid Plastic Tubes & Pipes

Merck

We are the Electronics business of Merck.

Our semiconductor materials are at the heart of electronics, and enable the transformation of communications, mobility and healthcare.

We unlock the potential for smaller, faster and more energy-efficient devices.

For more information, please visit **bit.ly/SemiconductorMaterials**

The Electronics business of Merck KGaA, Darmstadt Germany, operates as EMD Electronics in the U.S. and Canada.

#### 3D | SOC DESIGN

## Imec demonstrates significant performance gains utilizing backside 3D SOC interconnects

Principal researchers at imec, working with Cadence EDA programmers, have demonstrated significant performance gains are possible by utilizing new backside interconnects in 3D SOC circuits.

#### BY DRAGOMIR MILOJEVIC, GEERT VAN DER PLAS AND ERIC BEYNE, IMEC

IMEC RESEARCHERS Dragomir Milojevic, Geert Van der Plas and Eric Beyne delve into highlights of their work to improve SOC performance through a novel approach utilizing backside interconnects. According to imec, researchers have shown the following key results with the promising approaches studied so far:

• 3D system-on-chip (3D SOC), enabled by electronic design automation (EDA) and 3D process technologies, is an attractive heterogeneous integration approach for addressing the memory wall in highperformance systems.

- Further performance gains at the system level can be achieved when the backside of one of the integrated wafers is exploited for either power delivery, signal routing or both.

- The benefits of 3D-SOC design and of backside interconnects in specific circuits are highlighted in two papers presented at the 2021 IEEE International Electron Devices Meeting (IEDM).

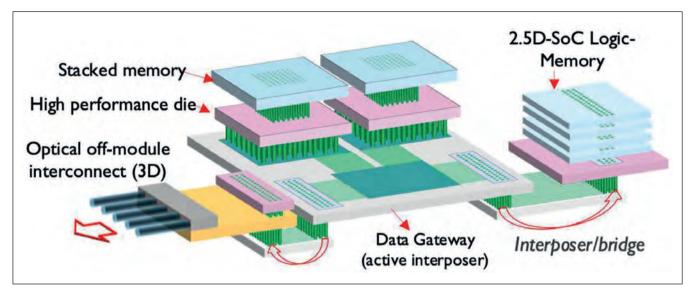

➤ Figure 1: Abstracted view of a possible future high-performance system. High-performance die with 3D-SOC stacked memory are implemented on an active interposer chip which acts as a data gateway and connects in a '2.5' fashion with local high bandwidth memories and optical transceiver modules (as presented at 2021 IEDM).

### Promises of a 3D-SOC design approach

Data-intensive high-performance systems intended for advanced computation, data server or deeplearning applications increasingly suffer from the so-called 'memory wall' – the challenge of accessing data quickly enough. An interesting approach to tear down this memory wall is 3D system-on-chip (3D SOC) integration. Following this heterogeneous integration approach, the system is automatically partitioned into separate chips that are concurrently designed and interconnected in the third dimension.

In their invited 2021 IEDM paper '3D-SOC integration, beyond 2.5D chiplets', the authors explain how this 3D-SOC concept goes beyond today's popular chiplet approaches for realizing multi-chip heterogeneous system integration. Eric Beyne, senior fellow, VP R&D and program director 3D system integration at imec said, "Chiplets involve separately designed and processed chiplet dies.

A well-known example are high-bandwidth memories (HBMs) – stacks of dynamic random access memory (DRAM) chips. This memory stack connects to a processor chip through interface buses, which limit their use to latency-tolerant applications. As such, the chiplet concept will never allow for fast access between logic and fast, first and intermediate level cache memories."

With 3D-SOC integration, memory-logic partitions can be realized using direct and shorter interconnects - resulting in significant performance improvements. In their invited paper, the authors showed an optimized implementation of a 3D-SOC design with memory macros in the top die and remaining logic in the bottom die – resulting in a 40 percent higher operating frequency compared to a 2D design. The authors also discuss the key challenges of realizing fully functional 3D SOCs. Dragomir Milojevic, principal scientist at imec and professor at Université libre de Bruxelles remarked, "On the design side, a 3D-SOC co-design strategy is needed for both logic and memory partitions. This requires dedicated electronic design automation (EDA) tools that can handle both designs simultaneously, using automated tools for system partitioning and 3D critical path optimization during place-androute. Through our collaboration with Cadence, we have access to these highly advanced tools." On the technology side, progress in wafer-to-wafer hybrid bonding solutions will allow for very high chip-to-chip interconnect densities, mandatory for partitioning of first and intermediate level cache memories.

### The next step: exploiting the wafer's backside

A possible partitioning of high-performance 3D-SOC systems involves some or all memory

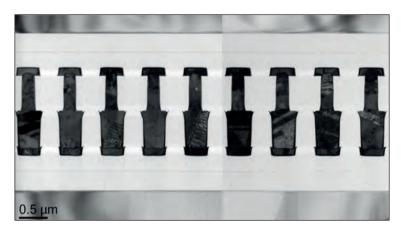

Figure 2: Wafer-to-wafer hybrid bonding at 700nm pitch (as presented at 2021 IEDM).

#### 3D | SOC DESIGN

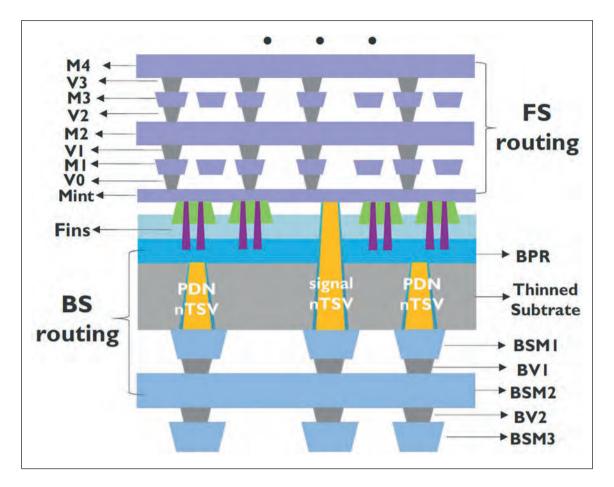

> Figure 3: Schematic of conventional frontside (FS) BEOL and backside (BS) metals for PDN and signal routing. The BS metals for PDN routing use nTSVs to connect BS metals to buried power rail while BS metals for signal routing use nTSVs to connect BS metals to FS metals (as presented at 2021 IEDM).

Dragomir Milojevic

Geert Van der Plas

Eric Beyne

macros to be placed in the top die, while the logic is placed in the bottom die. On the technology side, this can be realized by bonding the active frontside of the 'logic wafer' to the active frontside of the 'memory wafer' by using a low-temperature waferto-wafer bonding technique. In this configuration, the original backsides of both wafers now reside on the outside of the 3D-SOC system.

Eric Beyne said, "We can now think of exploiting the 'free' backside of these wafers for signal routing or for directly powering the transistors in the 'logic wafer'. Traditionally, signal routing and power delivery happens in the wafer's frontside, where they compete for space in a complex scheme of back-end-of-line interconnects. In these designs, the wafer's backside only serves as a carrier.

In 2019, simulations by Arm for the first time showed the beneficial impact of using a backside power delivery network (BSPDN) in the design of a central processing unit (CPU) that implemented a 3nm process as developed by imec. In this design, the interconnect metals residing in the wafer's thinned backside connected to 3nm transistors in the wafer's frontside using through-silicon vias (TSVs) landing on buried power rails. Simulations revealed that this BSPDN was seven times more efficient than the traditional frontside PDN."

Additional performance gains can therefore be expected when BSPDNs are implemented to supply the power-hungry core logic circuits that reside in the bottom of a 'memory-on-logic' 3D-SOC. One could also think of alternative 3D-SOC partitions where part of the memory tiles (e.g. the L1-level caches static random access memory (SRAM)) reside in the bottom die as well, also powered from the backside.

Besides extending the possibilities for 3D-SOC designs, BSPDNs have also been proposed for monolithic single-chip logic and SRAM systems-onchip (SOC), where they can assist further device and IC scaling. Geert Van der Plas, program manager at imec said, "Moving the power delivery network to the chip's backside has proven an interesting approach to address the back-end-of-line (BEOL) routing congestion challenge and reduce the IRdrop. A main difference with the 3D-SOC approach is that a dummy wafer is now bonded to the target wafer to allow for backside wafer thinning and metallization." One of imec's partners recently announced to implement such a BSPDN concept in one of its future node chips.

## Backside interconnects to further improve SRAM macro and logic performance

While the benefits of a BSPDN could already be demonstrated in specific designs, additional gains can be expected from using the wafer's backside for global signal routing. Imec, in collaboration with Cadence, has for the first time assessed and optimized SRAM macro and logic circuit designs that

#### 3D | SOC DESIGN

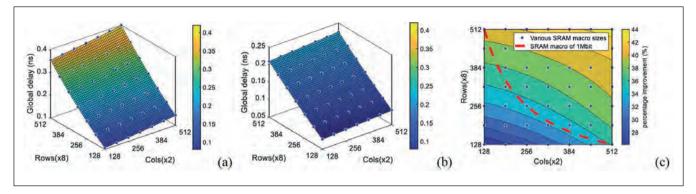

Figure 4: Global routing delay (read access) of SRAM macro at various macro rows and columns. (a) FS; (b) BS and (c) from FS to BS improvement. The macro size ranges from 128\*128\*16=256kbit to 515\*512\*16=4Mbit (as presented at 2021 IEDM).

are partly routed from the backside. An SRAM macro not only involves the memory bit cell arrays but also the peripheral circuitry (like address decoders, control block, etc.) that are relevant for processor design.

For both SRAM macro and logic, up to three backside metal layers were used for signal routing, while nano-TSVs (nTSVs) connect the backside metallization to the frontside. The SRAM macros implemented 2nm nanosheet transistors in their design. In these macros, only the global routings for the peripheral circuit were designed with backside metallization.

For logic, a ring oscillator framework was used to assess the impact of backside signal routing. The design implemented forksheets of the 2nm technology node in the logic standard cells. A physical implementation of a 64-bit ARMTM CPU using the same 2nm forksheet process design kit (PDK) is used to ensure the meaningfulness of the ring oscillator simulation results.

Geert Van der Plas said, "Compared to frontside routing, backside routing turned out significantly more beneficial in improving delay and power efficiency for long interconnect signal routing. For the SRAM macros, we demonstrated up to 44 percent performance improvement and up to 30 percent power efficiency improvement compared to frontside routing. For logic cells, backside routing enabled 2.5x speed improvement and 60 percent energy efficiency increase." The results are described in the 2021 IEDM paper 'Design and optimization of SRAM macro and logic using backside interconnects at 2nm node' by R. Chen et al.

Assessment of the circuits' performance and power efficiency was enabled through a combination of experiments and modelling. Dragomir Milojevic explained the process: "Experiments involved an optimization of nTSV processing in terms of capacitance and resistance to ensure a good electrical connection between the frontside and the backside metals. These parameters were fed into a model, used to perform the simulations.

Finally, our team performed a design-technology co-optimization (DTCO)-driven routing optimization which showed a path for further improvements. We demonstrated an additional 20 percent performance improvement by reducing the capacitance of the backside metals."

#### Conclusion

The heterogeneous 3D-SOC approach – enabled by system architecture re-design and 3D integration technologies – has proven an attractive way of improving system performance. Additional performance gains can be achieved by exploiting the backside of the bottom wafer for power delivery and/or signal routing. Imec has for the first time shown the beneficial impact of using backside interconnects in SRAM macros and logic circuits. These backside interconnects can bring performance improvements for high-performance 3D-SOCs as well as for monolithic single-chip SOCs.

#### FURTHER READING

- 'Imec demonstrates critical building blocks for a backside power delivery network', imec reading room;

- Cadence accelerates system innovation with breakthrough integrity 3D-IC platform', press release;

- 'Next-gen chips will be powered from below', IEEE Spectrum, August 2021.

#### More details can be found in the 2021 IEDM papers:

- '3D SOC integration, beyond 2.5D chiplets', invited paper by Eric Beyne et al.

- 'Design and optimization of SRAM macro and logic using backside interconnects at 2nm node' by R. Chen et al.

## Top semiconductor manufacturers improve design flow through IP management

Intellectual property (IP) is used and reused as semiconductor designs evolve from one generation to the next. IP reuse has become a necessity since complex circuits and systems are almost always built on content from preceding generations. IP management tools are the most efficient way to track origins and changes, which translates into far less time spent researching IP. Perforce Software explains how IP management tools are already shortening design cycles while helping ensure security.

#### BY SIMON BUTLER, GENERAL MANAGER, METHODICS BUSINESS UNIT, PERFORCE SOFTWARE

AS IS SEEN EACH DAY, the semiconductor industry is going through a period of rapid evolution, with growing demand being counter-balanced by some considerable challenges. At the end of 2021, Perforce Software asked close to 100 industry professionals worldwide about current concerns, working methodologies, and emerging trends around design and development. While Perforce does not claim this to be an exhaustive list, the results provide valuable insight into some of the main factors shaping semiconductor design and development right now.

The largest categories of respondents were engineering management and design engineering (approximately a third each), followed by CAD management, executive management, and others. Company size ranged from under \$500 million annual revenue to over \$5 billion. While these organizations do vary, there are some strong areas of commonality.

#### The biggest industry issues

When asked about design imperatives, responding organizations' two most important issues were time-to-market (55%) and IP reuse (45%). These point out that semiconductors are becoming commoditized, with fierce competition and slim margins in most categories. Keep in mind that even when considering more expensive application specific integrated circuits (ASICs), these designs almost always reuse at least some IP just like their commoditized cousins. Reusing some components from of a previous design — also known as IP reuse — has become a priority for many.

functional safety (35%) and IP security (23%). In a sense this comes as no surprise, given that chips are often used in safety-critical, sensitive or highly regulated environments. Over 70% of respondents are required to meet compliance or functional safety standards, such as ISO 26262, ITAR and others, yet 70% are still using manual processes for compliance management. This may be fine for smaller teams, but this can become untenable as organizations scale. However, almost half of respondents also have some element of automated compliance management, even if it is not being used for everything.

A majority of the survey's global respondents (76%) were also concerned about the drop in the US share of global manufacturing capacity. The hope is that the US government's efforts to find new ways to drive more in-country manufacturing and gain more control over the semiconductor supply chain will work.

#### Key trends

Nearly two-thirds of respondents develop embedded software as part of their product portfolios, reflecting that the global embedded system market is predicted to grow 6.3% to \$137.31 billion by 2027, according to a report published by Fior Markets<sup>1</sup>. Bundling hardware and software together creates new challenges; designs become more complex, creating a greater need for developers and designers to collaborate and manage design lifecycles in a coherent, unified way. Perforce also asked about analog designs for SoCs, and almost half stated that there is 40% or more custom-IC design on a die in a typical chip in their organizations. In addition, 76% of respondents said that more than half of their jobs requires IP integration. The survey also found that 2.5D (interposer) designs are being considered or implemented by 36%. While that number may sound low, it does indicate that 2.5D is no longer being used only for expensive, high-end chips. Importantly, usage is trending upwards.

#### IP reuse and management are hard

While IP reuse may be a priority, many find it difficult. More than half of the respondees do not have access to a centralized IP catalog, which inhibits the design reuse discovery process. In practice, this means that people are searching through various projects or asking colleagues for recommendations. This approach is inefficient: nearly 40% report that discovering candidate IP for their designs is time-consuming and burdensome.

Furthermore, for more than a third reported that trying to determine the status of IPs after making an initial discovery is a challenge, and nearly 75% reported difficulty in determining the context of an IP and its quality.

Clearly, with IP-centric design and IP reuse continuing to grow, these issues need to be addressed. Understanding the context of IPs for reuse has historically required advocates from the original project. Having a better process for identifying IP for inclusion in a project helps companies make better use of their existing assets and avoid reinventing the wheel for each new project.

Bundling hardware and software together creates new challenges; designs become more complex, creating a greater need for developers and designers to collaborate and manage design lifecycles in a coherent, unified way