### **INSIDE**

News Review, Features News Analysis, Profiles Research Review and much more...

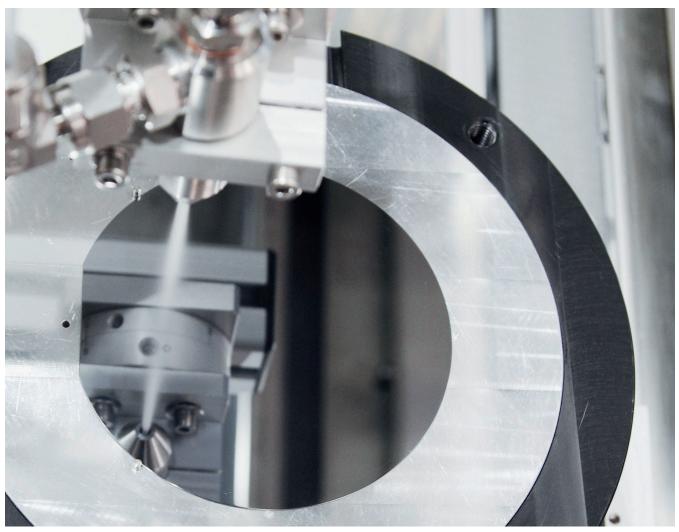

# Dry cleaning process for optimum cleaning

Whether energy, mobility or industry - electronic systems and components play a key role towards climate neutrality

# Microprocessor architecture choice in the age of Ai

In the age of AI, the microprocessor selection for anchoring an AI solution is especially important

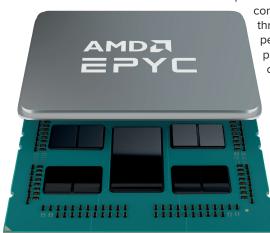

# STMicroelectronics boosts chip design speed

Europe's largest semiconductor company optimised performance, cost, and energy consumption by choosing AMD EPYC CPUs

# NANOCLEAVE™ LAYER TRANSFER REVOLUTIONIZES ADVANCED PACKAGING AND LOGIC SCALING

- IR laser cleave technology enables ultra-thin-layer transfer from silicon carriers

- Nanometer-precision release of bonded, deposited or grown layers

- Front-end compatibility through silicon carriers and inorganic release materials

- Supporting future roadmaps in advanced packaging and transistor scaling

# **VIEWPOINT**

By Phil Alsop, Editor

# Promise of a better year ahead, geopolitics permitting

The good news seems to be that, no matter which forecast(s) you subscribe to, the industry is predicted to enjoy some significant growth this year, which might not quite make up for the 2023 downturn numbers, but is nonetheless very welcome. All things Al seem to be fuelling this growth – with the data centre and related high performance computing sectors seeing the lion's share of the resulting increased semiconductor demand. There is some suggestion that Al will also begin to make inroads into the personal device market as well.

2.5/3D packaging is another area highlighted by IDC as enjoying a good increase in numbers over the next few years – something confirmed by Allied Market Research's '3D Semiconductor Packaging Market' research report. As the Ansys interview in this issue highlights, the main challenge for this market right now seems to be that a range of companies are coming at the problem/ opportunity from different perspectives and, as yet, there seems to be no agreement as to the development of any kind of standards. So, for now at least, a dynamic space, with plenty of investment and innovation, but also a fair amount of uncertainty as to the exact 2.5D/3D packaging roadmap.

Elsewhere in the news, the ongoing skills shortage and the somewhat linked continuing on-/reshoring trend are front and centre. In no particular order, the Semiconductor Research Corporation (SRC) has unveiled the Microelectronics and Advanced Packaging (MAPT) Roadmap, described as 'the first industry-wide 3D semiconductor roadmap to guide the forthcoming microelectronic revolution' (there's 3D cropping up again!); the European Commission has officially inaugurated the Chips Joint Undertaking (Chips JU), designed to 'reinforce the European semiconductor ecosystem and Europe's technological leadership' – it will do this by bridging the gap between research, innovation and production; and, 'in response to the critical shortage of skilled engineers in semiconductor IC design and layout', a new initiative has been launched by Professor Patrick Reynaert of KU Leuven, working alongside several semiconductor companies in Flanders.

I will resist the urge to bring up the three Ss once more(!), but maybe introduce a fourth for the new year – security. Sadly, no matter where one looks in the world right now, a combination of human-made and natural chaos continues to threaten long-held certainties in so many ways. From the US where it seems, no matter the result of the forthcoming presidential election, some kind of subsequent instability seems unavoidable, through the Middle East's regular disruption, to the ongoing tension in Asia, and not forgetting the war in Europe...security is under scrutiny in so any ways.

Let us hope that the geopolitical events of 2024 do not derail the semiconductor industry's growth to any great extent. I write more in hope than expectation.

For your free weekly e-news roundup go to: siliconsemiconductor.net

## 14 Global capacity to reach record30 million wafers per month

Global semiconductor capacity is expected to increase 6.4% in 2024 to top the 30 million wafers per month mark for the first time after rising 5.5% to 29.6 in 2023, SEMI announced recently in its latest quarterly World Fab Forecast report

# 28 Dry cleaning process for optimum results in electronics production

Whether energy, mobility or industry - electronic components and systems play a key role in the transformation towards climate neutrality

# 32 STMicroelectronics boosts chip design speed and enhances sustainability

Europe's largest semiconductor company optimised the performance, cost, and energy consumption in its R&D data centre by choosing AMD EPYC CPUs

### 36 Filling the metrology void

Nearfield Instruments B.V. recently launched AUDIRA – said to be the industry's first and only in-line, non-destructive subsurface metrology system for advanced semiconductor manufacturing

### 40 Microprocessor architecture choice in the age of AI: exploring ARM and RISC-V

In a world where the everyday devices we use are based on programmable silicon, choosing the right microprocessor architecture is key to delivering a successful product

### 44 Semiconductor market to recover in 2024

IDC reveals eight key trends for the global semiconductor market in 2024

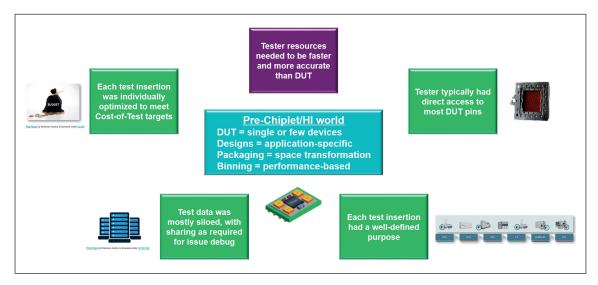

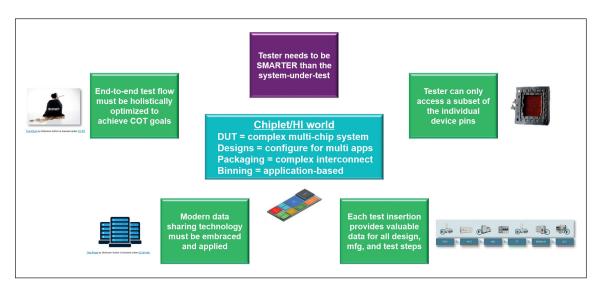

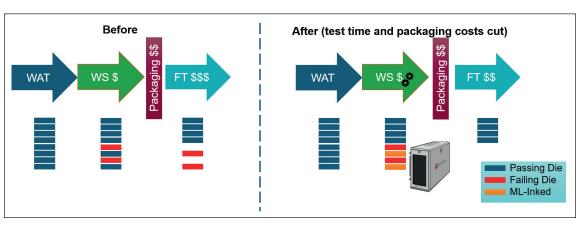

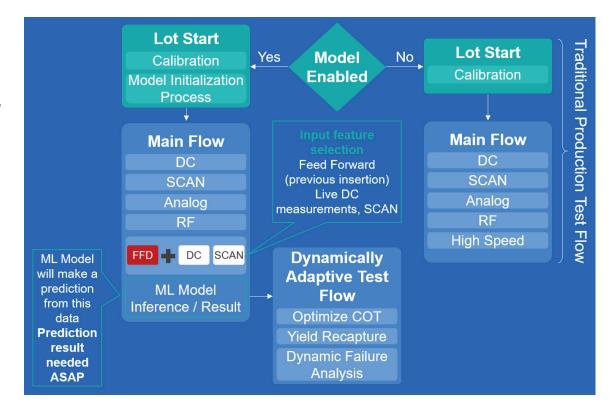

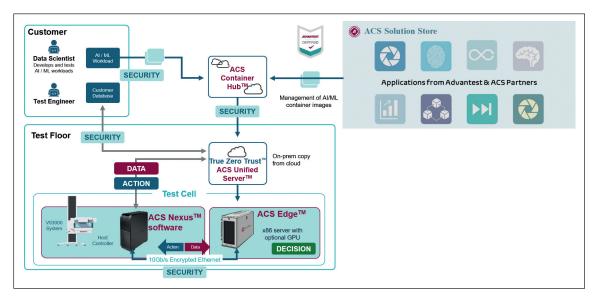

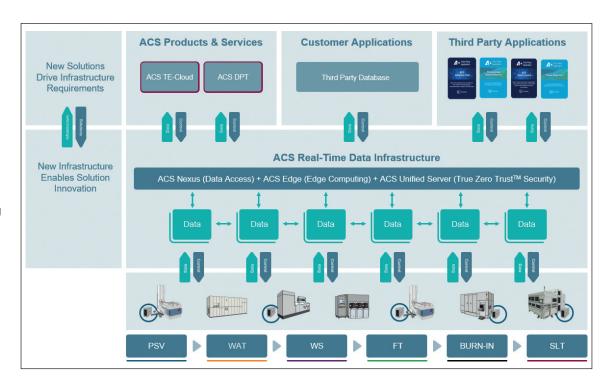

### 46 Leveraging AI to efficiently test Al chips

The semiconductor devices that bring artificial intelligence (AI) and machine learning (ML) to the cloud as well as to the edge present significant test challenges

### **NEWS**

- 06 Photonic pursues silicon-based approach to quantum computing

- 07 China and US bolster semiconductor independence

- 08 Breakthroughs and opportunities in 3D packaging

- **09** Bridging the talent gap in Flanders' Semiconductor Industry

- 10 Worldwide semiconductor revenue to grow 17% in 2024

- 11 Commission launch chips joint undertaking under the European Chips Act

- 12 Al demand leads semiconductor revenue growth

Publisher Jackie Cannon Editor Phil Alsop

Sales & Marketing Manager Shehzad Munshi Marketing & Logistics Executive Eve O'Sullivan USA Representatives Tom Brun Brun Media Janice Jenkins

Director of Logistics Sharon Cowley

Design & Production Manager Mitch Gaynor

jackie.cannon@angelbc.com phil.alsop@angelbc.com shehzad.munshi@angelbc.com eve.osullivan@angelbc.com

tbrun@brunmedia.com iienkins@brunmedia.com

sharon.cowlev@angelbc.com mitch.gaynor@angelbc.com

+44 (0)1923 690205

+44 (0)1923 690215 +44 (0)2476 823123 +001 724 539-2404

+001724-929-3550 +44 (0)1923 690200

+44 (0)1923 690214

Chief Executive Officer Sukhi Bhadal Chief Technical Officer Scott Adams sukhi.bhadal@angelbc.com scott.adams@angelbc.com +44 (0)2476 718970 +44 (0)2476 718970

Published by Angel Business Communications Ltd, 6 Bow Court, Fletchworth Gate, Burnsall Road, Coventry CV5 6SP. UK. T: +44 (0)2476 718 970 E: info@angelbc.com

Silicon Semiconductor is published ten times (6x print and 4x video issues) a year on a controlled circulation basis. Non-qualifying individuals can subscribe at: £50.00 per annum (UK), €60.00 per annum ( Europe), \$90 per annum (air mail)(USA). Cover price £4.50. All information herein is believed to be correct at time of going to press. The publisher does not accept responsibility for any errors and omissions The views expressed in this publication are not necessarily those of the publisher. Every effort has been made to obtain copyright permission for the material contained in this publication. Angel Business Communications Ltd will be happy to acknowledge any copyright oversights in a subsequent issue of the publication. Angel Business Communications Ltd © Copyright 2024. All rights reserved. Contents may not be reproduced in whole or

part without the written consent of the publishers. The paper used within this magazine is produced by chain of custody certified manufacturers, guaranteeing sustainable sourcing. US mailing information Silicon Semiconductor, ISSN 1096-598X, is published 5 times a year by Angel Business Communications Ltd, Unit 6, Bow Court, Fletchworth Gate, Burnsall Rd, Coventry CV5 6SP. UK. Airfreight and mailing in the USA by agent named World Container INC 150-15, 183rd St, Jamaica, NY 11413, USA. Periodicals Postage Paid at Brooklyn, NY 11256. POSTMASTER: Send address changes to Silicon Semiconductor, Air Business Ltd. c/o World Container INC 150-15, 183rd St. Jamaica, NY 11413, USA

We strive for accuracy in all we publish: readers and contributors are encouraged to contact us if they recognise an error or omission. Once a magazine edition is published (online, in print or both), we do not update previously published articles to align old company names, branding, marketing efforts, taglines, mission statements or other promotional verbiage, images, or logos to newly created or updated names images, typographic renderings, logos (or similar) when such references/images were accurately stated, rendered or displayed at the time of the original publication. When companies change their names or the images/text used to represent the company, we invite organizations to provide Angel Business Communications with a news release detailing their new business objectives and/or other changes that could impact how customers/prospects might recognise the company, contact the organisation, or engage with them for future commercial enterprise Printed by: The Manson Group. ISSN 2050-7798 (Print) ISSN 2050-7801 (Online) © Copyright 2024.

# Photonic pursues silicon-based approach to quantum computing

Photonic Inc., a company building one of the world's first scalable, fault-tolerant, and unified quantum computing and networking platforms based on photonically linked silicon spin qubits, has introduced its quantum architecture.

PHOTONIC'S unique approach to quantum computing stands to accelerate innovation across the quantum ecosystem.

"Quantum computing is real, and we believe that—within five years, significantly sooner than the widely accepted timeframe—we will be the first quantum computing company to offer a scalable, distributed, and fault-tolerant solution," said Dr. Stephanie Simmons, Founder and Chief Quantum Officer of Photonic and Co-chair of Canada's National Quantum Strategy Advisory Board. "These are the capabilities that must be delivered for quantum computing to be a relied upon across industries, and we believe that we have correctly identified the silicon T centre as the missing component needed to finally unlock the first credible path to impactful commercial quantum computing."

Photonic specializes in spinphoton interfaces in silicon, silicon integrated photonics, and quantum optics. Photonic has committed to silicon—the chemical element serving as the backbone of modern telecommunications and computation – as the dominant enabling design in quantum computing.

Leveraging colour centers and telecom photons, Photonic's patented technology provides computing (with spin qubits), networking (via photons), and memory. Photonic links in silicon deliver quantum entanglement not only between gubits on the same chip but also among multiple quantum chips. Silicon-based qubits enjoy substantially greater microelectronic-style scalability than other types of qubits. Indeed, Photonic's architecture achieves horizontal scaling. Photonic's highly connected qubit architecture also enables use of efficient quantum error correction codes, such as quantum

LDPC (Low Density Parity Check) codes. These codes are known for extremely low physical to logical qubit overheads and fast and efficient hardware implementation.

Such attributes will prove increasingly crucial as quantum computing drives more applications. For example, Photonic's technology can deliver unparalleled security to global digital communications, offering a solution to the cybersecurity threat posed by the development of quantum computing. Beyond internet cybersecurity, quantum computing promises transformative capabilities for modelling and simulation of complex systems and processes in areas such as climate modelling, materials development, and creation of life-saving pharmaceuticals.

"Ultimately, the breadth of problems to which quantum computing can offer a solution means it will have a tangible, meaningful impact on people all around the world," said Dr. Paul Terry, Photonic Chief Executive Officer. "We're moving to large-scale, accessible quantum computers networked together to provide access to quantum services that will enable companies and governments to suddenly tackle problems that are, right now, beyond our capabilities because of the inescapable constraints of classical computing. It's incredibly thrilling to be on the cusp of this inflection point in quantum computing and, more broadly, physics history."

Photonic, which has built one of the world's largest teams of quantum silicon experts, has raised a total of \$140 million USD in funding to date, and benefits from leveraging the globally mature manufacturing ecosystem for semiconductors and telecoms. The company is led by innovators with deep expertise in delivering disruptive

technologies. Dr. Simmons is a Tier 2 Canada research chair in silicon quantum technologies and a Canadian Institute for Advanced Research fellow in quantum information science. She is an associate professor in the physics department at Simon Fraser University in Burnaby, British Columbia, who has twice been accorded a Physics World Top 10 Breakthrough of the Year (2013 and 2015) for her work in silicon quantum technologies.

Dr. Terry is a seasoned executive, entrepreneur, engineer, and angel investor who has founded or has been one of the founding employees at six successful companies in areas from big data systems to supercomputing, to IP services and telecom networking.

In related news, Photonic also announced today Photonic Collaborating with Microsoft to Power Global Quantum Ecosystem, and Photonic Raises \$100 Million USD for Quantum Technology from BCI, Microsoft, and Other Investors.

In addition, a Photonic technical paper, Scalable Fault-Tolerant Quantum Technologies with Silicon Colour Centres, details the company's novel architecture, and a Microsoft blog post, Microsoft and Photonic join forces on the path to quantum at scale, offers more perspective on that company's collaboration with Photonic. offers more perspective on that company's collaboration with Photonic.

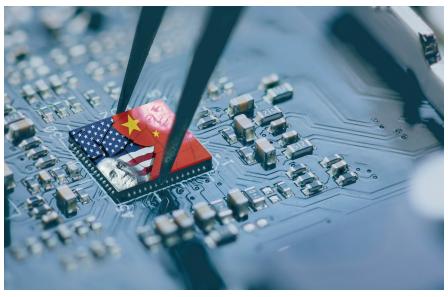

### China and US bolster semiconductor independence

TrendForce's latest findings reveal that as of 2023, Taiwan holds approximately 46% of global semiconductor foundry capacity, followed by China (26%), South Korea (12%), the US (6%), and Japan (2%).

DUE to government incentives and subsidies promoting local production in countries like China and the US, the semiconductor production capacities of Taiwan and South Korea are projected to decrease to 41% and 10%, respectively, by 2027.

Taiwan to concentrate 60% of advanced manufacturing processes by 2027, retaining a hold on key technologies In advanced manufacturing processes (including 16/14nm and more advanced technologies), Taiwan leads with a 68% global capacity share in 2023, followed by the US (12%), South Korea (11%), and China (8%). Meanwhile, Taiwan holds nearly 80% when it comes to EUV generation processes (such as 7nm and beyond).

In response to the concentration of semiconductor manufacturing capacity in Taiwan, the US, which has a high demand for advanced processes, is actively encouraging and supporting major companies such as TSMC, Samsung, and Intel. 2027, the US's share of advanced process capacity is expected to increase to 17%, although TSMC and Samsung will still account for over half of this capacity.

Japan is also planning a return to semiconductor manufacturing, actively supporting local company Rapidus with a goal of reaching the most advanced 2 nm process. They aim to create a semiconductor cluster in Hokkaido and are offering subsidies to foreign companies, including Japan Advanced Semiconductor Manufacturing (JASM) and PSMC's Sendai plant (JSMC). China's mature process capacity is set to grow to 39% as Taiwanese firms actively cultivate unique technological advantages

China is focusing aggressively on mature process technologies (28nm and older), particularly in response to export controls on advanced equipment by the US, Japan, and the Netherlands.

By 2027, China's share in mature process capacity is expected to reach 39%, with room for further growth if equipment procurement proceeds smoothly.

However, as Chinese manufacturers rapidly expand their mature process capacities—backed by government subsidies—this could lead to intense price competition in products like CIS, DDI, PMIC, and power discrete, impacting Taiwan-based foundries like UMC, PSMC, and Vanguard. Vanguard is expected to be most affected due to its product line including LDDI, SDDI, PMIC, and power discrete. Other companies like UMC and PSMC will maintain their advantages in the 28/22nm OLED DDI and memory sectors.

In response to chip shortages and geopolitical influences, fabless customers are diversifying risk by working with multiple foundries, potentially leading to increased IC costs and concerns over duplicate orders. Customers are also requiring global validation of production lines, even with long-term foundry partners, to enable flexible capacity adjustments. Consequently, foundries must navigate

larger scale capacity and price competition while needing to maintain profitability, flexibility in capacity adjustments, new capacity depreciation pressures, and technological leadership.

China is focusing aggressively on mature process technologies (28nm and older), particularly in response to export controls on advanced equipment by the US, Japan, and the Netherlands. By 2027, China's share in mature process capacity is expected to reach 39%, with room for further growth

### Breakthroughs and opportunities in 3D packaging

Increase in trend of miniaturization in portable electronic industry and rise in dependency on these devices worldwide is shifting device manufacturers toward finding new methods of size reduction.

GLOBAL 3D semiconductor packaging market size is estimated to reach \$8.9 billion by 2022, growing at a CAGR of 15.7 % from 2016 to 2022 according to the Allied Market Research Titled "3D Semiconductor Packaging Market".

The report includes a detailed analysis of the dynamic factors such as drivers, restraints, challenges, and opportunities. The drivers and opportunities help to comprehend the rapidly changing industry trends and how they can impact the growth of the market. Moreover, the challenges and restraints analyzed in the report help recognize profitable market investments. The global 3D Semiconductor Packaging report provides quantitative and qualitative analysis of the market from 2021 to 2030.

The qualitative study focuses on the value chain analysis, key regulations, and pain point analysis. The global 3D Semiconductor Packaging market report includes an overview of the market and highlights market definition and scope along with major factors that shape the 3D Semiconductor Packaging market. The study outlines the major market trends and driving factors that boost the growth of the 3D Semiconductor Packaging market. The report includes an in-depth study of sales, market size, sales analysis, and prime drivers, challenges, and opportunities.

Some of the prime drivers of the 3D Semiconductor Packaging industry are surge in penetration of the aging infrastructure is further anticipated to drive the 3D Semiconductor Packaging market growth. The market for 3D Semiconductor Packaging would be driven by investing in new technology aimed at increasing system life. Another key factor driving the growth of the 3D Semiconductor Packaging market is the increased focus on infrastructure throughout the world.

3D Semiconductor Packaging provides monitoring technology to alert maintenance workers when outdated and overused equipment is about to fail, allowing them to make better decisions by providing real-time data on problems and possibilities for improvement.

Aside from the limits listed above, there are others, such as environmental factors such as temperature and humidity, as well as groundwater seepage, which can have an influence on the operation of switchgear electrical networks, particularly those situated outside. The changing times necessitate changes in the fundamentals as well. In this situation, even small and medium-sized organizations (SMEs) are taking advantage of collocation data hubs' immense potential and the internet's enormous capacity.

The market study further promotes a sustainable market scenario on the basis of key product offerings. On the other hand, Porter's five forces analysis highlights the potency of buyers and suppliers to enable stakeholders make profit-oriented business decisions and strengthen their supplier-buyer network. The report provides an explicit global market breakdown and exemplifies how the opposition will take shape in the new few years to come. Rendering the top ten industry players functional in the market, the study emphasizes on

the policies & approaches integrated by them to retain their foothold in the industry.

The analysis highlights the highest revenue generating and fastest growing segments. These insights are helpful in devising strategies and achieving a sustainable growth. The 3D Semiconductor Packaging market is studied on the basis of different segments including type, applications, and region. This makes the study well organized and resourceful along with promoting easy understanding. The report a comprehensive data based on each segment of the 3D Semiconductor Packaging market.

The 3D Semiconductor Packaging market is analyzed on the basis of geographical penetration along with a study of market influence in the various regions such as North America (United States, Canada, and Mexico), Europe (Germany, France, UK, Russia, and Italy), Asia-Pacific (China, Japan, Korea, India, and Southeast Asia), South America (Brazil, Argentina, Colombia), Middle East and Africa (Saudi Arabia, UAE, Egypt, Nigeria, and South Africa).

The global 3D Semiconductor

Packaging market offers a detailed

overview of the industry based on the

main parameters including market

extent, probable deals, sales analysis,

and essential drivers. The market report

is summarized enfolding the operations

of an array of different organizations

in the sector from different regions.

The study is a perfect consolidation of

quantitative and qualitative information

accentuating on the key industry

developments and challenges that the

market is facing along with the lucrative

opportunities available in the sector.

The 3D Semiconductor Packaging market report also showcases the factual data throughout the forecast period and brings about an estimate till 2031.

# Bridging the talent gap in Flanders' Semiconductor Industry

Sofics supports initiative and donates time and resources for the course on analog layout.

IN RESPONSE to the critical shortage of skilled engineers in semiconductor Integrated Circuit (IC) design and layout, a new initiative has been launched by Professor Patrick Reynaert of KU Leuven in collaboration with several leading semiconductor companies in Flanders, Belgium, including Sofics. Flanders, renowned for the prestigious research center imec, boasts a myriad of commercial enterprises at the forefront of cutting-edge technology. These companies play pivotal roles in various electronic applications, spanning automotive, medical, industrial, consumer, data center, optical, and space industries. Despite their ambitious growth plans, the semiconductor industry, also in Flanders, faces a significant hurdle - a shortage of qualified engineers in IC design and layout.

To address this challenge head-on, Professor Reynaert's recent initiative introduces three comprehensive courses designed to coach individuals into proficient 'chip designers'. This program provides students with specialized skills essential for semiconductor industry roles.

Crucially, the courses are not just

theoretically driven; they are developed and taught by seasoned experts from Flanders' leading semiconductor companies. Participating firms include BelGan, Caeleste, Cyient, easics, iCana, ICsense, imec, Melexis, Omnivision, and Sofics. This collaboration ensures that students gain practical insights, real-world perspectives, and industry-specific knowledge directly from those shaping the landscape.

"We are excited to be part of this collaborative effort to cultivate the next

generation of chip designers," said Koen Verhaege, CEO of Sofics. "It can help to bridge the skills gap, enabling semiconductor companies in Flanders to thrive and achieve their growth aspirations."

Prospective students are encouraged to enroll and embark on a journey towards becoming the future leaders of semiconductor design. For more information about the courses and enrollment details, please visit https://www.esat.kuleuven.be/mc\_chips.

# Dedicated webinars for the silicon semiconductor industry

Using our 30+ years' experience in B2B vertical technical markets, and as the publisher of Silicon Semiconductor, we offer effective webinars, ZOOM interview and virtual events. We help you get your message, to your desired audience, by marketing to over 55,000 silicon semiconductor professionals.

Find out how Angel Webinar can help you organise and run a webinar within the silicon semiconductor industry.

Reach Educate Influence

- Brand Awareness

- Lead Generation

- Thought Leadership

Contact: Jackie Cannon jackie.cannon@angelbc.com +44 (0)1923 690205

# Worldwide semiconductor revenue to grow 17% in 2024

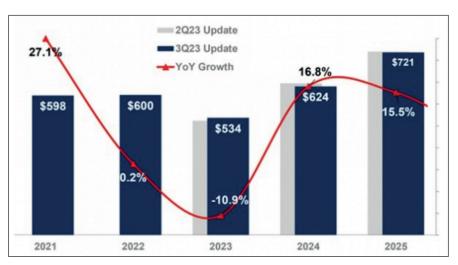

Global semiconductor revenue is projected to grow 16.8% in 2024 to total \$624 billion, according to the latest forecast from Gartner, Inc. In 2023, the market is forecast to decline 10.9% and reach \$534 billion.

"We are at the end of 2023 and strong demand for chips to support artificial intelligence (AI) workloads, such as graphics processing units (GPUs), is not going to be enough to save the semiconductor industry from double-digit decline in 2023," said Alan Priestley, VP Analyst at Gartner. "Reduced demand from smartphones and PC customers coupled with weakness in data centre/hyperscaler spending are influencing the decline in revenue this year."

However, 2024 is forecast to be a bounce-back year where revenue for all chip types will grow (see Figure 1), driven by double-digit growth in the memory market. Memory Revenue to Rebound in 2024 After Double-Digit Decline

The worldwide memory market is forecast to record a 38.8% decline in 2023 and will rebound in 2024 by growing 66.3%.

Anaemic demand and declining pricing due to massive oversupply will lead NAND flash revenue to decline 38.8%

and fall to \$35.4 billion in revenue in 2023. Over the next 3-6 months, NAND industry pricing will hit bottom, and conditions will improve for vendors. Gartner analysts forecast a robust recovery in 2024, with revenue growing to \$53 billion, up 49.6% year-over-year. Due to high oversupply level and lack of demand, DRAM vendors are chasing the market price down to reduce inventory. Through the fourth quarter of 2023, DRAM market's oversupply will continue which will trigger a pricing

rebound. However, the full effect of pricing increases will only be seen in 2024, when DRAM revenue is expected to increase 88% to total \$87.4 billion. Developments in generative AI (GenAI) and large language models are driving demand for deployment of high-performance GPU-based servers and accelerator cards in data centres. This is creating a need for workload accelerators to be deployed in data centre servers to support both training and inference of AI workloads.

# Commission launches chips joint undertaking under the European Chips Act

The European Commission has officially inaugurated the Chips Joint Undertaking (Chips JU), designed to reinforce the European semiconductor ecosystem and Europe's technological leadership.

IT WILL BRIDGE the gap between research, innovation and production thereby facilitating the commercialisation of innovative ideas. The Chips JU will, among others, deploy pilot lines for which the Commission announced today the first call with €1.67 billion of EU funding. This is expected to be matched by funds from Member States to reach €3.3 billion, plus additional private funds.

In addition, the European

Semiconductor Board held its

first meeting recently. The Board

brings together Member States to

provide advice to the Commission

on the consistent implementation

of the European Chips Act and

on international collaboration in

semiconductors. It will be the key

platform for coordination between

the Commission, Member States, and

stakeholders to address issues relating

to the resilience of the supply chain and

possible crisis responses.

### The Chips Joint Undertaking

The Chips JU is the main implementer of the Chips for Europe Initiative (expected total budget €15.8 billion until 2030). The Chips JU aims at strengthening Europe's semiconductor ecosystem and economic security by managing an expected budget of nearly €11 billion by 2030, provided by the EU and participating states.

### The Chips JU will:

- Set up pre-commercial, innovative pilot lines, providing industry state-of-the-art facilities to test, experiment and validate semiconductor technologies and system design concepts;

- Deploy a cloud-based Design

### Platform for design companies across the EU:

Support the development of

- advanced technology and engineering capacities for quantum chips;

- Establish a network of competence centres and promote skills development.

The work of the Chips JU reinforces Europe's technological leadership by facilitating the transfer of knowledge from the lab to the fab, bridging the gap between research, innovation and industrial activities, and by promoting the commercialisation of innovative technologies by European industry including start-ups and SMEs.

First calls for funding Chips pilot lines To launch its first calls for innovative pilot lines, the Chips JU will make €1.67 billion in EU funding available. The calls are open to organisations that wish to establish pilot lines in Member States, typically research and technology organisations, calling for proposals on:

• Fully Depleted Silicon on Insulator, towards 7 nm: This transistor architecture is a European innovation and has distinct advantages for highspeed and energy-efficient applications. A roadmap towards 7 nm will provide a path towards the next generation of high-performance, low-power semiconductor devices. O Leading-edge nodes below 2 nm:

This pilot line will focus on developing cutting-edge technology for advanced semiconductors at the size of 2 nanometres and below, which will play essential roles in a variety of applications, from computing to communication devices, transport systems and critical infrastructure.

- Heterogeneous system integration and assembly: Heterogeneous integration is an increasingly attractive technology for innovation and increased performance. It refers to the use of advanced packaging technologies and novel techniques to combine semiconductor materials, circuits or components into one compact system.

- O Wide Bandgap semiconductors:

The focus will be on materials that allow electronic devices to operate at much higher voltage, frequency and temperature than standard silicon-based devices. Wide bandgap and ultra-wide bandgap semiconductors are necessary to develop highly efficient power, lighter weight, lower costs and radiofrequency electronics.

The deadline for the calls for these pilot lines is in early March 2024.

### Al demand leads semiconductor revenue growth

Led by continued demand for AI, the total semiconductor industry grew 8.4% in 3Q23 from 2Q23 hitting \$139bn according to Omdia's latest Competitive Landscape Tracker.

THE INDUSTRY has now grown for a second straight quarter, after previously declining for five consecutive quarters. "The increase in the semiconductor industry wasn't solely due to Al demand, as growth spread throughout other semiconductor segments," said Omdia Principal Analyst Cliff Leimbach. "Fourteen of the top fifteen companies experienced a quarterly increase in semiconductor revenue in 3Q23, and 80 of the 126 companies (63%) tracked grew revenue in the third quarter." Al continues to drive the market, but improvements observed throughout the industry

Demand for Al continued to be a major theme for the semiconductor industry in 3Q23. Two firms that have benefited from AI, NVIDIA, and SK Hynix, continued to record large semiconductor revenue increases. NVIDIA, which makes GPUs that are used for data-intensive AI, increased semiconductor revenue 18% to \$12bn. NVIDIA's semiconductor revenues are up \$7.3bn from a year ago when 3Q22 revenues were \$4.6bn. SK Hynix, which is dominant in the high bandwidth memory (HBM) used in AI applications, increased semiconductor revenue 26% to \$6.7bn.

Since the memory market was at the lowest in 1Q23, SK Hynix's revenue has increased by \$2.9bn. The rise of AI has significantly improved revenues for firms with a large presence in this area. However, other areas of the semiconductor market also increased in 3Q23. The wireless segment also progressed along with the release of new smartphone models and better inventory dynamics than previous quarters. Growth was lower in the automotive sector, up 4.3% in 3Q23, but this segment has been reliably steady, having last declined in 3Q20 and currently representing 13.5% of all semiconductor revenue. The consumer segment also improved,

up 7.9% from 2Q23, showing the breadth of the increased revenue in the semiconductor market.

Memory market continues improvement The memory segment was the hardest hit segment during the semiconductor market decline which started in 2022, declining from \$43.6bn in 1Q22 to \$19.3bn in 1Q23. From the low point in 1Q23, the market bounced back going from \$19.3bn to \$24.5bn in 3Q23. Four of the top five memory makers increased memory IC revenue by double-digit percentage points in 3Q23 from 2Q23. Al demand is a large part, but other applications are increasing in demand as well. NVIDIA has risen the ranks and has become the second largest semiconductor firm by revenue. This has split up the long-time pair at the top of the semiconductor market shares of Intel and Samsung Electronics. These two firms have traded the position of number one and number two over the years.

### A plan to 'revitalise' the semiconductor industry

SEMICONDUCTOR RESEARCH CORPORATION (SRC) has unveiled the Microelectronics and Advanced Packaging (MAPT) Roadmap, crafted through the collective effort of approximately 300 individuals representing 112 organizations from industry, academia, and government.

The MAPT Roadmap defines critical research priorities and technology challenges that must be addressed to support the seismic shifts outlined in the Decadal Plan for Semiconductors released in January of 2021. The MAPT Roadmap, available at https:// srcmapt.org/, is the first industry-wide 3D semiconductor roadmap to guide the forthcoming microelectronics revolution.

Funded by the U.S. Department of Commerce's National Institute of Standards and Technology (NIST) in April 2022, SRC was selected to head this effort based on a strong history of thought leadership and forging innovation. SRC Chief Scientist and Director of the MAPT Roadmap, Dr. Victor Zhirnov, commented, "The commitment demonstrated by such a wide array of scientists, engineers, and researchers to the development and production of the MAPT Roadmap indicates the importance of such an effort."

Every day, people across the planet interact with dozens of semiconductor devices without a second thought. There is a crisis at hand, however. The ever-shrinking components are facing fundamental physical limits, and nextgen breakthroughs are unachievable without major advancements. The 2030 Decadal Plan for Semiconductors, released by SRC and Semiconductor Industry Association (SIA) identified five seismic shifts in the industry related to

smart sensing, memory and storage, communication, security, and energy efficient computing. The Decadal Plan is, by design, agnostic on specific solutions; it identifies what is needed, rather than how it will be accomplished.

The MAPT Roadmap continues the spirit of the Decadal Plan and discusses how to achieve its system-level goals, outlining the implementation plan for semiconductor industry. The fundamental research that will transform these obstacles is focused on advanced packaging, 3D integration, electronic design automation, nanoscale manufacturing, new materials, and energy-efficient computing. The MAPT Roadmap is framed around fundamental and practical limits of information and communications technology sustainability: energy sustainability, environmental sustainability, and workforce sustainability.

OUR NEW BATCH TOOL FOR HIGH THROUGHPUT WET PROCESSING

- Compact design

for optimal use of the clean room

- Fast processes

through high process temperature

of up to 170°C

- Via warehouse with up to 75 storage locations and automated loading connected to the transport system

- Reduction of particle generation & contamination

by improved access and optimized extraction of the process chamber

### WE ARE YOUR PARTNER FOR WET PROCESS EQUIPMENT

# Global capacity to reach record 30 million wafers per month

Global semiconductor capacity is expected to increase 6.4% in 2024 to top the 30 million wafers per month (wpm) mark for the first time after rising 5.5% to 29.6 wpm in 2023, SEMI announced recently in its latest quarterly World Fab Forecast report.

THE 2024 growth will be driven by capacity increases in leading-edge logic and foundry, applications including generative AI and high-performance computing (HPC), and the recovery in end-demand for chips. The capacity expansion slowed in 2023 due to softening semiconductor market demand and the resulting inventory correction.

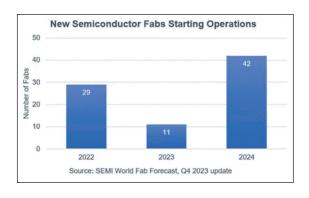

"Resurgent market demand and increased government incentives worldwide are powering an upsurge in fab investments in key chipmaking regions and the projected 6.4% rise in global capacity for 2024," said Ajit Manocha, SEMI President and CEO. "The heightened global attention on the strategic importance of semiconductor manufacturing to national and economic security is a key catalyst of these trends." Covering 2022 to 2024, the World Fab Forecast report shows that the global semiconductor industry plans to begin operation of 82 new volume fabs, including 11 projects in 2023 and 42 projects in 2024 spanning wafer sizes ranging from 300mm to 100mm.

### China leads semiconductor industry expansion

Boosted by government funding and other incentives, China is expected to increase its share of global semiconductor production. Chinese chip manufacturers are forecast to start operations of 18 projects in 2024, with 12% YoY capacity growth to 7.6 million wpm in 2023 and 13% YoY capacity growth to 8.6 million wpm in 2024.

Taiwan is projected to remain the second-largest region in semiconductor capacity, increasing capacity 5.6% to 5.4 million wpm in 2023 and posting 4.2% growth to 5.7 million wpm in 2024. The region is poised to begin operations of five fabs in 2024.

Korea ranks third in chip capacity at 4.9 million wpm in 2023 and 5.1 million wpm in 2024, a 5.4% increase as one fab comes online. Japan is expected to place fourth at 4.6 million wpm in 2023 and 4.7 million wpm in 2024, a capacity increase of 2% as it starts operations of four fabs in 2024.

The World Fab Forecast shows the Americas increasing chip capacity by 6% YoY to 3.1 million wpm with six new fabs in 2024. Europe & Mideast is projected to up capacity 3.6% to 2.7 million wpm in 2024 as it launches operations of four new fabs.

Southeast Asia is poised to increase capacity 4% to 1.7 million wpm in 2024 with the start of four new fab projects.

### Foundry segment continues strong capacity growth

Foundry suppliers are forecast to rank as the top semiconductor equipment buyers, increasing capacity to 9.3 million wpm in 2023 and a record 10.2 million wpm in 2024.

The memory segment slowed expansion of capacity in 2023 due to weak demand in consumer electronics including PCs and smartphones. The DRAM segment is expected to increase capacity 2% to 3.8 million wpm in 2023 and 5% to 4 million wpm in 2024. Installed capacity for 3D NAND is projected to remain flat at 3.6 million in 2023 and rise 2% to 3.7 million wpm next year.

In the discrete and analog segments, vehicle electrification remains the key driver of capacity expansion. Discrete capacity is forecast to grow 10% to 4.1 million wpm in 2023 and 7% to 4.4 million wpm in 2024, while Analog capacity is projected to grow 11% to 2.1 million wpm in 2023 and 10% to 2.4 million wpm in 2024.

The latest update of the SEMI World Fab Forecast report, published in December, lists 1,500 facilities and lines globally, including 177 volume facilities and lines with various probabilities expected to start operation in 2023 or later.

### Global equipment sales to reach \$124 billion in 2025

Global sales of total semiconductor manufacturing equipment by original equipment manufacturers are forecast to reach \$100 billion in 2023, a contraction of 6.1% from the industry record of \$107.4 billion

posted in 2022, SEMI announced in its Year-End Total Semiconductor Equipment Forecast – OEM.

Semiconductor manufacturing equipment growth is expected to resume in 2024, with sales forecast to reach a new high of \$124 billion in 2025, supported by both the front-end and back-end segments. "We anticipate a temporary contraction in 2023 due to the cyclical nature of the semiconductor market," said Ajit Manocha, SEMI President and CEO. "2024 will be a transition year. We then expect a strong rebound in 2025, driven by capacity expansion, new fab projects, and high demand for advanced technologies and solutions across the front-end and back-end segments."

### Semiconductor equipment sales by segment

After registering a record \$94 billion in sales last year, the wafer fab equipment segment, which includes wafer processing, fab facilities and mask/ reticle equipment, is projected to slip 3.7% to \$90.6 billion in 2023. This contraction marks a significant improvement from the 18.8% decline forecast by SEMI in its Mid-Year Total Semiconductor Equipment Forecast – OEM Perspective. The upward revision is primarily due to strong equipment spending by China. Wafer fab equipment segment sales are projected to grow at a modest 3% in 2024 from the revised 2023 base due to limited memory capacity addition and the pause of mature capacity expansion. A growth path with a further 18% expansion in 2025 is expected as new fab projects, capacity expansion and technology migrations drive investments to nearly \$110 billion.

The decline in back-end equipment segment sales started in 2022 and continued in 2023 due to challenging macroeconomic conditions and softening semiconductor demand. Semiconductor test equipment market sales are projected to contract by 15.9% to \$6.3 billion in 2023, while assembly and packaging equipment sales are expected to drop by 31% to \$4.0 billion in the same year. The test equipment and assembly and packaging equipment segments are forecast to expand by 13.9% and 24.3%, respectively, next year. Back-end segment growth is expected to continue in 2025, with test equipment sales rising 17% and assembly and packaging sales increasing 20%.

### Semiconductor equipment sales by application

Equipment sales for foundry and logic applications, accounting for more than half of total wafer fab equipment receipts, are expected to log a 6% increase year-over-year to \$56.3 billion in 2023 despite softer end-market conditions. The application segment is forecast to contract 2% in 2024 as mature technology expansion slows and spending on leading-edge technology improves.

Foundry and logic equipment investments are projected to increase 15% in 2025 to \$63.3 billion, driven by increased capacity expansion purchases and the introduction of new device architectures.

As anticipated, memory-related capital expenditures will see the sharpest decline in 2023. NAND equipment sales are predicted to drop by 49% to \$8.8 billion in 2023 but will surge 21% to \$10.7 billion in 2024 and rise another 51% to \$16.2 billion in 2025. DRAM equipment sales are expected to remain stable, growing by 1% and 3% in 2023 and 2024, respectively. Supported by continuous technology migration and expanding demand for high-bandwidth memory (HBM), DRAM equipment segment sales are expected to increase an additional 20% to \$15.5 billion in 2025.

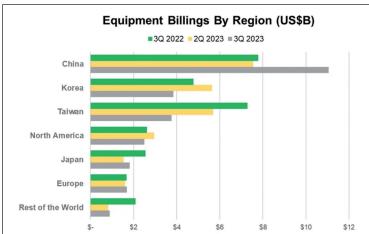

### Semiconductor equipment sales by region

China, Taiwan and Korea are expected to remain the top three destinations for equipment spending through 2025. China is projected to maintain the top position over the forecast period as the region's equipment billings continue to soar. Equipment shipments to China are projected to surpass a record \$30 billion in 2023, widening its lead with other regions. While equipment spending for most tracked regions is expected to fall in 2023 before resuming growth in 2024, China is expected to see a mild contraction in 2024 after heavy investments in 2023.

### SEMI recognises Edwards

SEMI Europe and the SEMI European Advisory Council for Diversity and Inclusion have announced Edwards as the recipient of the 2023 SEMI Industry Leader in Diversity and Inclusion Award. Christine Pelissier, General Manager, Customer Center EMEA of Semiconductor at Edwards accepted the award Source:

SEMI

December

2023,

Equipment

Market Data

Subscription

at SEMICON Europa 2023 during the Future of Work session.

"I'm proud of the work that we've done at Edwards to promote diversity and embed a positive culture of inclusion," Pelissier said. "We started our journey in 2019 and we still have work to do. This award is a recognition of the organization's commitment to not just set targets but to do the work required to deliver on them."

"The semiconductor industry's capacity to innovate and sustain competitiveness in Europe relies significantly on a diverse and skilled workforce," said Laith Altimime, President of SEMI Europe. "Over the past five years, Edwards has continuously focused on improving the diversity and inclusion of its workforce through innovative and progressive programs."

Established in 2019, the SEMI Industry Leader in Diversity and Inclusion Award recognizes European semiconductor companies that exhibit outstanding leadership and make strategic contributions to fostering diversity, equity, and inclusion. The award celebrates their practices that advance both their workforces and the chip industry at large.

### Edwards promotes culture-first mindset

Edwards' leaders have placed a strong emphasis on diversity and inclusion in the European semiconductor industry, establishing the company as a pioneer with recent measures to promote worker wellbeing, mental health and inclusivity. Edwards takes a holistic approach to cultivating an inclusive workplace with corporate policies that support inclusive language, trans colleagues, and Fusion, a network for the Edwards LGBTQ+ community. Edwards also offers employee education programs to raise awareness of issues such as unconscious bias and menopause.

SEMI Europe welcomes nominations for the 2024 award for companies that have inspired the industry through their exemplary leadership and execution,

volunteerism, sponsorship, and innovation in diversity, equity, and inclusion. Prior award recipients hailed from companies including Soitec, Melexis, and SPTS Technologies, a KLA company.

SEMI honours sustainability leaders

SEMI has announced recipients of the 2023

SEMI Sustainability Excellence Award. SEMI

SEMI Sustainability Excellence Award. SEMI President and CEO Ajit Manocha selected the award recipients based on their inspirational leadership and innovative approaches to expanding sustainability practices at their companies and in the semiconductor industry in order to meet aggressive net zero emission goals.

The leaders were also recognized for their contributions to the Path to Net Zero session during the SEMICON West 2023 CEO Summit keynote program. The honorees will be commemorated on the SEMI Wall of Fame at the association's headquarters in Milpitas.

### 2023 SEMI Sustainability Excellence Award honorees:

- Gary Dickerson, President and CEO, Applied Materials

- Keyvan Esfarjani, Executive VP, Chief Global Operations Officer, GM of Manufacturing, Supply Chain and Operations, Intel Corporation

- Mukesh Khare, General Manager of IBM Semiconductors and VP of Hybrid Cloud Research, IBM

- Aamir Paul, President, North America, Schneider Electric

"The drive toward net zero is a challenge that requires intense collaboration across international borders and supply chains," said Manocha. "SEMI is pleased to honor Gary, Keyvan, Mukesh and Aamir for their tremendous inspiration as the semiconductor industry works to achieve its emissions goals. Their leadership and passion are strong drivers for their companies adopting leading-edge sustainability practices, and their actions are a powerful motivator for the entire industry supply chain to follow suit."

The recipients were selected based on their alignment with principles of the SEMI Sustainability Initiative and its focus on Environment, Social and Governance (ESG) issues.

### **Recipient accomplishments**

Gary Dickerson is a longtime sustainability leader and a major contributor to the semiconductor industry's net zero pathway. His passion for making a positive impact is reflected in Applied Materials' vision to Make Possible a Better Future. Dickerson champions Applied's ESG leadership initiatives, including the company's "3x30" program, which is aimed at reducing the environmental impact of its products, and Applied's Net Zero 2040 Playbook, a bold framework for reducing the industry's carbon emissions through close collaboration with Applied's customers and suppliers.

The semiconductor industry's capacity to innovate and sustain competitiveness in Europe relies significantly on a diverse and skilled workforce," said Laith Altimime, President of SEMI Europe. "Over the past five years, Edwards has continuously focused on improving the diversity and inclusion of its workforce through innovative and progressive programs.

Keyvan Esfarjani leads Intel's ambitious sustainability efforts, which include achieving 100% renewable energy, net positive water and zero waste to landfill by 2030, reaching net zero Scope 1 and 2 GHG emissions by 2040, and collaborating with suppliers to meaningfully reduce Scope 3 emissions and achieve net-zero upstream GHG emissions by 2050. He is a consistent force in reducing Intel's environmental footprint while driving global capacity expansion plans and calling for the semiconductor industry to accelerate its timeline in meeting climate goals.

Dr. Mukesh Khare leads a global IBM team that is redefining the future of computing for products such as generative artificial intelligence (AI) and high-performance computing, two energy-intensive technologies. He leads teams of researchers devising new methods to process data more efficiently and accelerate the pace of progress towards sustainable quantum, AI and hybrid cloud infrastructure while advancing the industry's drive to net zero emissions.

Aamir Paul led Schneider Electric's partnership with Applied Materials and Intel to launch the pioneering Catalyze program. Unveiled at SEMICON West 2023, the Catalyze program promotes the adoption of a renewable and low-carbon energy roadmap for the chip sector and provides global partners in the semiconductor value chain with better access to renewable energy solutions and comprehensive decarbonization assistance. By collaboratively digitalizing energy for efficiency and sustainability, the Catalyze program's partners allow energy transition to be advantageous for businesses and environmentally beneficial for all.

### Leadership accelerator launch

SEMI has introduced the SEMI Leadership Accelerator to foster industry growth by assisting organizations in cultivating the next generation of leaders. This initiative will support semiconductor supply chain organizations in evaluating high-potential employees, offering personalized leadership coaching, and delivering tailored training for individual and team development. Developed in a collaboration between SEMI Europe and Mercuri Urval, the SEMI Leadership Accelerator provides science-based, ISO-certified programs, empowering senior leaders, executives, and board members to navigate global challenges, drive business transformation, and achieve sustained growth in the semiconductor sector.

With Europe projected to need 350,000 new workers in the semiconductor industry by 2030, Laith Altimime, President of SEMI Europe, emphasized the imperative for cultivating leaders capable of navigating the complexities of the semiconductor industry. "The semiconductor industry must further develop diverse leaders who can reshape businesses in a complex and fast-changing world of uncertainty. The growing number

of job vacancies in Europe's semiconductor sector risks undercutting its growth potential as companies expand manufacturing capacities. It is essential for leaders in the industry to unlearn outdated approaches and prepare for unforeseen challenges. The SEMI Leadership Accelerator will facilitate this transformative process."

Mercuri Urval, is a global leadership advisory firm with over 50 years of experience, an extensive global presence, and specialized knowledge across industry sectors. Methodically crafted, semiconductor industry-specific programs tailored by Mercuri Urval and leveraging SEMI's extensive industry insights and network, will enable the SEMI Leadership Accelerator to address leadership development needs, empowering companies to identify and nurture leaders internally.

### Equipment billings drop 11%

Global semiconductor equipment billings contracted 11% year-over-year to US\$25.6 billion in the third quarter of 2023, while quarter-over-quarter billings slipped 1% during the same period, SEMI announced today in its Worldwide Semiconductor Equipment Market Statistics (WWSEMS) Report.

"The Q3 2023 dip in equipment billings was due to softening chip demand," said Ajit Manocha, SEMI President and CEO. "However, China has shown strong demand and spending power for mature-node technologies, a sign of the industry's resilience and growth potential in the long run."

Source: SEMI (www.semi.org) and SEAJ (www.seaj.or.jp), November 2023

| Region            | 3Q 2023 | 2Q 2023 | 3Q 2022 | 3Q (QoQ) | 3Q (YoY) |

|-------------------|---------|---------|---------|----------|----------|

| China             | \$11.06 | \$7.55  | \$7.78  | 46%      | 42%      |

| Korea             | \$3.85  | \$5.65  | \$4.78  | -32%     | -19%     |

| Taiwan            | \$3.77  | \$5.69  | \$7.28  | -34%     | -48%     |

| North America     | \$2.50  | \$2.95  | \$2.61  | -15%     | -5%      |

| Japan             | \$1.82  | \$1.54  | \$2.55  | 19%      | -29%     |

| Europe            | \$1.70  | \$1.61  | \$1.67  | 5%       | 2%       |

| Rest of the World | \$0.89  | \$0.83  | \$2.08  | 8%       | -57%     |

| Total             | \$25.59 | \$25.81 | \$28.75 | -1%      | -11%     |

Sources: SEMI (www.semi.org) and SEAJ (www.seaj.or.jp), November 2023 Note: Summed subtotals may not equal the total due to rounding.

Compiled from data submitted by members of SEMI and the Semiconductor Equipment Association of Japan (SEAJ), the WWSEMS Report is a summary of the monthly billings figures for the global semiconductor equipment industry. Following are quarterly billings data in billions of U.S. dollars with quarter-over-quarter and year-over-year changes by region:

### New energy collaborative

Aiming to reduce global semiconductor ecosystem carbon emissions, SEMI and the Semiconductor Climate Consortium (SCC) have created the Energy Collaborative (EC) to understand and clear roadblocks to the installation of low-carbon energy sources in the Asia-Pacific region. The EC, a collective of industry leaders, will provide a consolidated view of priorities for low-carbon energy in the region.

"Sharing resources to start this foundational semiconductor industry sustainability work now is important to enable wider access to low-carbon energy in the next five to ten years," stated Young Bae, SCC Governing Council member and sponsor for the SCC Scope 2 Working Group, and Global Business Director, Advanced Cleans Technologies at DuPont. "One of the key action areas the SCC has identified is the lack of low-carbon energy plans and actions in the Asia-Pacific region. The EC will help the SCC by accelerating investments to broaden access."

The EC sponsoring companies will anchor the collective's work to engage in roundtables and factfinding sessions.

McKinsey & Company is a Knowledge Partner to the initiative, providing fact-based analysis and support.

"The semiconductor value chain and its downstream partners and customers have a pivotal role to play in the acceleration of low-carbon energy installations, due to their scale in high-priority markets and the extent to which they will drive growth in future energy demands," stated Ajit Manocha, President and CEO of SEMI. "To reach the emissions reductions goals of the sector, a step function change in ambition and action is required. The EC is focused on that goal – increasing the pace and scaling of access to low-carbon energy."

A recent SCC report found that the semiconductor value chain is a significant consumer of energy in almost all key Asian markets. Additionally, a recent analysis by McKinsey & Company shows that even with major semiconductor companies' latest commitments, which are more stringent than past measures, the industry is not on track to limit emissions to the extent required under the 2015 Paris Agreement. The analysis finds that both individual and collective actions by semiconductor players can help the entire industry increase its sustainability effort and meet the 1.5°C challenge.

### Two new international board members

SEMI has announced the election of two new members to the SEMI International Board: Kai Beckmann, Member of the Executive Board and CEO of the Electronics business sector of Merck KGaA, Darmstadt, Germany, and Benjamin Loh, Chair of the Management Board and President and CEO of ASM. The tenure of the new board members begins immediately.

"We congratulate the newly elected International Board members. Kai Beckmann and Benjamin Loh. and thank them for their commitment to guide SEMI in representing the global electronics manufacturing and design supply chain," said SEMI President and CEO Ajit Manocha. "Kai and Benjamin add to the breadth and depth of knowledge on our Board of Directors and will help us to ensure that SEMI programs continue to advance semiconductor industry growth, address top concerns, and deliver exceptional member value."

SEMI's 18 independent voting directors and 11 emeritus directors represent companies from Europe, China, Japan, Korea, North America, and Taiwan, reflecting the global scope of the association's activities. SEMI directors are elected by the general membership as voting members of the Board and can serve a total of five three-year terms. Kai Beckmann joined the Executive Board of Merck KGaA, Darmstadt, Germany in April 2011. He has served as CEO of the Electronics business sector since September 2017. Under his leadership the business successfully transformed into a leading player in the global electronics materials market. Beyond Merck, he has several external mandates such as President of the German Federation of Chemical Employers' Associations and Chairman of the Advisory Board of Fraunhofer Institute for Computer Graphics Research.

Benjamin Loh was appointed Chair of the Management Board and President and CEO of ASM in May 2020. He is a non-executive director of ASMPT and in the past held positions as nonexecutive director at Schneeberger, Schweiter Technologies AG, and Liteq BV. Loh was a SEMI China regional advisory board member while employed with Unaxis Corporation and living in China from 2002 to 2005.

### siconnex

# SOLUTION FOR CHEMICALS SHORTAGE

Ongoing supply chain disruptions impact the industry, leading to anticipated shortages and rising prices in cleaning chemicals, as forecasted by researchers like TECHCET. Smart utilization of ozone, along with the usage of minimal amounts of ammonia

BATCHSPRAY® SicOzone

sicOzone

and acids, result in significant cost savings. This approach can

replicate traditional cleaning steps and enhance organic clean-

ing efficiency in SC1, SC2, and DHF processes, with precise

control by using inline spiking technology.

MORE INFO

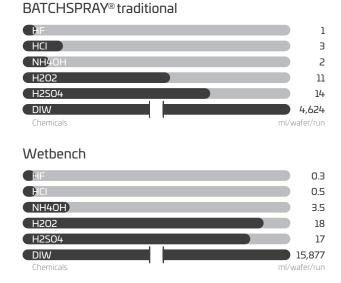

### Chemical consumption: SicOzone vs. conventional cleaning applications

0.2

###

Marc Swinnen, Product Marketing Director at Ansys, discusses recent collaboration with TSMC and Microsoft to develop a joint solution which provides a high-capacity cloud solution for analysing the mechanical stresses in 2.5D/3D-IC multi-die systems, which lets joint customers avoid field failures and extends product lifetime and reliability.

### PHILIP ALSOP, EDITOR asks the questions

PA: Ansys has been collaborating with TSMC and Microsoft, focusing on analysing mechanical stresses in multi-die 3D integrated circuit systems. The obvious place to start would be to understand how did the collaboration come about?

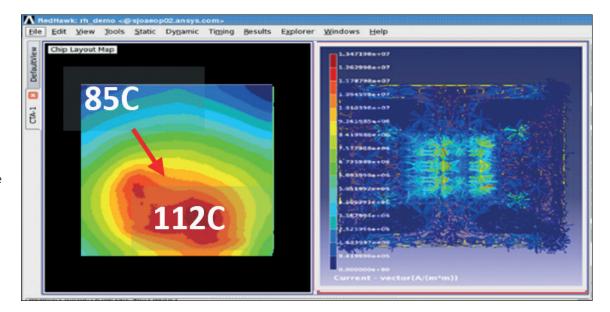

MS: Our collaboration with TSMC has been going on for decades. That's based largely on the fact that Ansys sells and produces the RedHawk-SC™ product, which is an electronic design automation (EDA) software tool used by chip designers to verify the power integrity of their chip. Basically, every chip has a power and ground network on it. Every single transistor has to be connected to power and has to be connected to ground, like any electronic device. If you have 50 billion transistors on your chip, that means you must design two electrical

networks, each with 50 billion endpoints. So, these are incredibly large and complicated on-chip networks that are vital to the proper functioning of the chip. They need to be checked because there is always voltage drop on the power lines. And these days, to save power, the voltage is so low that you really can't afford to lose even 100 millivolts going from the package pin to the actual transistor. Hence everything has to be very carefully analysed to make sure your power integrity, or voltage drop, is properly accounted for and will meet your spec.

And that's a very big, tough problem. And that's what RedHawk-SC does. It does the final sign off for manufacturing, saying, yes, this will work. Of course, this all relies critically on the manufacturing rules. We work very closely with all of the major foundries, including TSMC. TSMC and Ansys have a longstanding collaborative association to get this golden sign off tool out to the industry - the large majority of all the chips in the world are signed off for their power integrity using Ansys Redhawk-SC. That is the foundation of our deep and ongoing collaboration with TSMC.

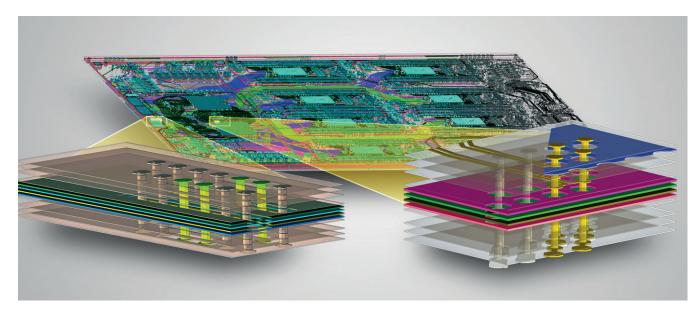

Which brings us to the topic under discussion. Traditionally, a chip, or integrated circuit (IC), is a monolithic piece of silicon - it's all one thing. You cut it out of the wafer and it's one little chip of silicon which gets embedded in a package. But now, for multiple reasons, it is no longer possible to build the big systems you want today on just a single

chip. So, they've started making multiple chips and putting them together into a system we call 3D IC - where you stack several chips on top of each other or, more commonly, you put them right next to each other, which we call two-and-a-half D. I'll just call all of these configurations 3DIC - all these different ways of stacking or putting them right next to each other. The idea of a 3DIC is that it contains multiple dice. So bare dice, not packaged dice, that are placed right next to each other. Usually they're placed on top of another chip, called an interposer, which connects them all together. All highperformance computing is going there today.

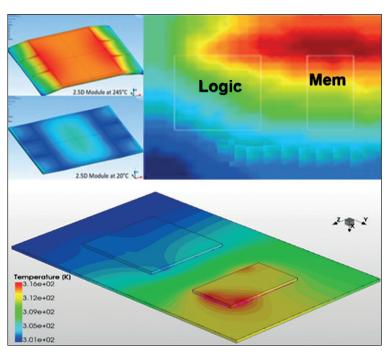

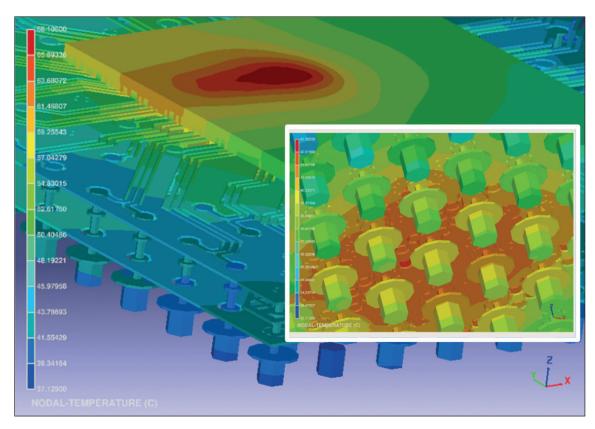

Now, some of these dice get hot and some of them get less hot and so you have differential thermal expansion. The dice are connected to each other with micro bumps. These are tiny, tiny bumps - up to a thousand per square millimetre - and they can't stand very much shear stress. If your assembly starts expanding and contracting differentially and cycling through these thermal cycles, you're going to get mechanical deformation, warping and stresses in this 3D assembly. And that is something radically new for chip designers. I mean, someone always had to worry about thermal expansion at some point. Usually a system or package designer way down the line, after the chip was assembled on a board and the board was put in the system and the system was in the heatsink - at that point, somebody did some mechanical analysis. But now it's come crashing down onto the chip, designers who now have to worry right out of the gate, how is this thing

➤ Display of thermal and warpage results from RedHawk-SC Electrothermal<sup>™</sup> for a multi-die 2.5D assembly of a logic chip and memory chip on an interposer.

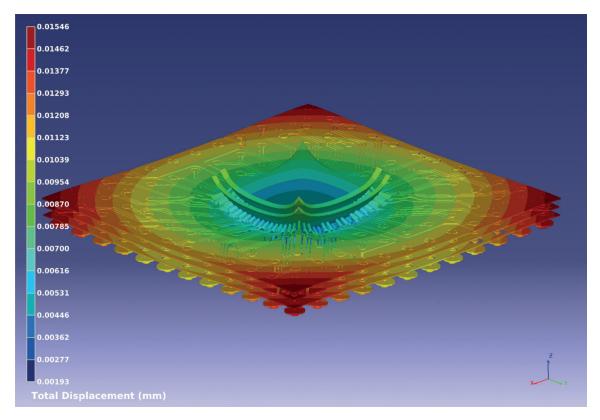

➤ 3DIC stack showing thermal induced warping and stresses from Ansys RedHawk-SC Electrothermal<sup>TM</sup>. Colors indicate displacement (exaggerated in Z-axis for easy visibility).

### TECHNOLOGY | SIMULATION

going to deform and warp? And if I use the wrong materials or use the wrong floor plan, my design will have much lower reliability than if it's done properly. Hence, they need to do mechanical simulations early on, and predict thermo-mechanical behaviour.

Ansys has a rich history in this area - beyond the semiconductor division we have many other simulation tools. We have computational fluid dynamics, we have mechanical, we have safety, we have optics, we have electromagnetics - many, many fields. But mechanical is one of our specialties where we are industry leading. It was natural for us to take those algorithms and apply them to our semiconductor problem.

TSMC worked with us to solve some of the issues they've seen in their own production and design side of things. They saw this as a problem which they needed solving. It's a tough computational problem so they pulled in Microsoft Azure to give the cloud computing capabilities required to really solve this in the required timeframe.

With cloud computing from Microsoft, the mechanical/thermal simulation from Ansys, and the manufacturing capability from TSMC, together we came up with a solution flow that worked and has been proven to work.

PA: And the objective of the project, I believe it's to provide added confidence to address novel multi-physics requirements that improve the functional reliability and increase product lifetimes of advanced 3D fabric designs?

MS: So, there's two points to that. One is novel, and the other one's reliability. So why is this novel? Mechanical simulation is not novel in itself, but for semiconductor designers, it is. As I already mentioned, this was something monolithic designers never had to worry about. But 3D assemblies - and I use 3D as a catch-all name for all those different architectures that the foundries supply with chip-on-chip and chip-next-to-chip - there's lots of ways of arranging these chips. I'll just call them all 3D-IC.

➤ Temperature gradient on a chip based on current distribution analysis from Ansys RedHawk-SC™. Chips have very specific rules about tolerance to bending. For example, a chip, is allowed to bend to a certain amount in the concave way - only so much. And by the way, it's not only heating that causes it to bend, but also during assembly, when they're actually mounting these chips on top of each other, you press the chips down and that bends them a little bit

So that is novel for chip designers that they now have to think at the floor planning stage: Okay, which of these chips is going to get hot, which is going to stay cooler? If I put two hot chips right next to each other, is that going to be a thermal problem that I can't fix? Or especially if two chips get hot in the same activity mode, like in streaming mode while you're playing video, both these chips get really hot in this corner. That could doom my project right from the get go.

Thermal is the number-one limitation on achievable integration density today. You can very easily stack chips several layers deep. You can design that. You can manufacture that. All that is not a problem. The problem is you can't cool it! It'll get too hot, and it'll melt. So how close and how compact you can make a system is determined, number one, far and away, by power dissipation. How do I control and manage my heat dissipation? So, when you're assembling these large systems, multiple chips together - and we're talking up to a dozen chips - how do I manage my power?

With heat comes thermal expansion, temperature cycling, and differential expansion of multiple materials. Monolithic chips are made out of one thing, silicon. Now suddenly you have systems that may include silicon chips together with silicon carbide chips and organic substrates. The individual chips are usually placed on an interconnection substrate called an interposer. The interposer is often made of silicon, like a giant chip made with an old process, like 35 nanometre or something.

But interposers can be made of organic resin as well. It can also be glass. There are foundries working with glass substrates. So, there's multiple materials in this stack-up and they all expand differentially. This mechanical concern is novel to most chip designers today. They may have expertise in the company somewhere that deals with thermal issues in electronic systems, but it's not in the chip design group. As a result, they may have to reorganise how the company is set up so that this mechanical expert is involved right from the get go. So that's novel to them.

Ansys is taking our multiphysics simulation capabilities and making them available in a way that works with semiconductor data formats in a semiconductor flow. That is what we believe to be the answer. We have a tool called RedHawk-SC

Electrothermal™, which takes care of integrating these. On the reliability side, the fundamental benefit is that thermal expansion is something that will, over time, degrade the chip. As I said, these chips are connected through little solder bumps that connect when you press the chips together.

They're about 10 micrometres apart, which gives you a very high density of interconnect. But if these chips start bending, warping or twisting and you get shear stresses between them, it's very easy for these micro bumps to shear, to break or to deform slightly so that their contact point becomes diminished. Which means that the power density or current density through that bump becomes higher and the chance of them melting becomes higher.

We did a 3D-IC assembly recently, with 400,000 micro bumps in the system, and you can have millions of micro bumps. If any one of them fails, you could have a system failure. It really behoves you to very carefully consider how your multi-die system warps as it heats up and cools down over time. That will give you a reliability problem if not properly managed.

Chips have very specific rules about tolerance to bending. For example, a chip, is allowed to bend to a certain amount in the concave way - only so much. And by the way, it's not only heating that causes it to bend, but also during assembly, when they're actually mounting these chips on top of each other, you press the chips down and that bends them a little bit. So that needs to be taken into account, too. Concave bending is allowed to a certain degree, but convex bending is absolutely not allowed. Apparently, there's very low tolerances on that. One way of bending is allowed, the other one isn't. These are some of the reliability issues that come up and there's trade-offs to be made there.

PA: If I understand you correctly, the issue is, because this is a completely novel process, there needs to be a lot of learning to take place. Once they have understood how all you've described happens, they will then find out the optimum way to make these 3D systems. But until they do, they have to carry out multiple tests under all different loads and conditions. And if they do things in exactly the same way each time, they will get the same results? Or are there variations, what we might call random variations, even in identical conditions?

> 3D thermal analysis results from Ansys RedHawk-SC Electrothermal™ for a chip on a package substrate, with pin-by-pin thermal resolution.

MS: Yes, so that is the beauty of simulation. People might say, well, I prefer working on a real system that doesn't predict what it's going to do, but actually you can measure on the test bench. Yes, there's a benefit to measuring reality, but the problem is you're measuring a specific instance of reality. You're measuring this particular device with this particular set of parameters. As an example, imagine measuring the parameters of something like steel bolts. How strong is a steel bolt? Well, some will be a little stronger than others. Batches of steel vary. There's a range there. You can test a particular bolt and that might be a strong one or it might be a weak one, but it doesn't tell you what the range of possibilities are when I'm going to build thousands of these things into a bridge. So too, when you take a chip under test or 3D assembly, you can put it on the test bench and test it, but you're testing a particular device. But there's so many different parameters in thickness variation, material property variation. Also temperature or thermal is due to activity, right? If the chip isn't doing anything, it doesn't get hot, it's only when it's actually active that it starts to get hot.

So what activity are you going to give it? And that's a problem because there's many, many thousands, millions of possible activity combinations. Simulation allows you to test across a variety of parameters, a variety of conditions, a variety of environmental, ambient conditions, too, and do all this with a variety of material combinations and verify that the system

will work across this entire envelope of possibilities. So that's the power of simulation in general. That is what RedHawk-SC Electrothermal allows you to do as well. You can identify problems and then decide what you're going to do about fixing these or how to prevent them. For example, one of the trade-offs you have to consider is this silicon interposer. It's much bigger than a standard chip, we're talking three inches by three inches or so. This interposer, if you make it thick, then it will not warp as much. It'll be stiffer, it won't deform as much, which is good, but that means that you get much higher thermal stresses. The differential expansion wants to be there but it can't bend, so the stresses will be very high, but it won't deform as much. But if you make the interposer much thinner, it'll deform much more, but the stresses will be lower. Like everything in engineering, it's a trade-off.

Also, there are holes drilled through that punch through the silicon interposers to connect from one side to the other. These holes are called throughsilicon vias (TSVs) and they're typically copper pillars. They're tiny, but for a chip size they're actually quite big. Even though they're electrical conductors meant to connect signal wires, they also serve a good purpose of dissipating the heat down through the silicon. There are different ways you can arrange these, not just for the electrical functionality, but also for the heat functionality. This is another way in which you can even-out the heat to reduce the amount of differential expansion, which will

reduce the stresses. Getting an optimal pattern of TSVs is another way you could optimise your design. There are a lot of angles to look at to see if the design can be improved.

PA: What you're describing, the main challenge is scaling up what you might call computationally demanding stress simulations, but crucially, at the same time, maintaining the predictive accuracy alongside. How big is that challenge?

MS: These thermal simulations can be very accurate and rely on meshing. You break the design down into a finite element mesh, which means you break down the whole pattern into millions of tiny little triangles that model the design geometry and can be analysed as a small local problem. A fine mesh gives you high accuracy but takes a long time to solve. And we're talking days to weeks of computation on hundreds of CPUs, and so that can become prohibitively expensive.

There are two ways to address the huge computational demands of these simulations. One is to improve your algorithms, and that's Ansys's job. We have things like adaptive meshing, where you check if the mesh really needs to be that fine everywhere. Some places have a lot of thermal gradient, and yes, I have to model that with a fine mesh to capture those curves. But a lot of the chip, the cooler parts, have a pretty even temperature across them. I don't need a fine mesh to model that. I can do a much faster, coarser mesh and still get accurate results. So, you have adaptive meshing which is fine, where it needs to be, and it can be coarser where it doesn't need to be, and that really brings the computation time down. That's the algorithmic side.