# SILICON SEMICONDUCTOR

Connecting the Silicon Semiconductor Community

Volume 42 ISSUE II 2021

@siliconsemi

www.siliconsemiconductor.net

Benefits of plasma dicing technology

For die in a package, it's always about the bond

Paradigm shift for device manufacturers

News Review, News Analysis, Features, Research Review, and much more...

Free Weekly E News round up go to: www.siliconsemiconductor.net

# editor's view

By Mark Andrews, Technical Editor

# Post-COVID IC manufacturing sees surging wafer, materials & equipment sales

EVEN AS THE WORLD STRUGGLES to regain its pre-pandemic footing, leading semiconductor indicators point towards a strong post-COVID economy driven by a thirst for tech-enabled products and services. Shortages persist across many IC categories while stronger demand affecting nearly every supply chain sector has fueled concerns that consumer spending may also drive inflation.

Consumers are paying more for just about everything in these post-pandemic times. Anyone who has recently shopped for pantry staples, consumer electronics, vehicles, or even a home, the chances are that prices seen today are higher than three months ago. Answering the 'why' question is straightforward — demand

continues to outstrip supply. In a world where almost everyone has been told for months to stay at home, avoid crowds, mask, and be vaccinated, factory output is lagging behind the spending of consumers anxious to trade the 'new normal' of 2020 for a taste of pre-pandemic freedoms.

The SEMI trade group reported that as of May, first guarter silicon wafer shipments easily surged past historic 1Q seasonal benchmarks. Materials makers are also enjoying robust sales as digitization (in part pandemic driven,) continues to surge more deeply into daily life. SEMI also attributes the rise in materials sales to an outgrowth of 5G buildouts and new interest in this supply chain sector by global investors. Unsurprisingly, semiconductor equipment makers are also on track for another bonanza year, so much so that legacy gear (process tools for wafers under 300mm) is enjoying a resurgence. Refurbished equipment sales are also climbing thanks to

> lower costs and an experienced workforce that got its start with 200mm tech.

In this edition of Silicon Semiconductor we look at how advanced electronic materials are playing an increasingly important role in IC manufacturing, Merck KGaA continues to expand its capabilities

> with materials that help reduce defects while offering the ability to assess performance in unique ways, providing customers a new competitive edge.

We also look at new bonding solutions from Palomar Technologies that put a fresh spin on 'multi-tasking' and Edwards Vacuum's continuing evolution of sub-fab maintenance designed to ensure uptime while lowering overall costs.

Publisher & Editor Jackie Cannon Technical Editor Mark Andrews Sales & Marketing Manager Shehzad Munshi

USA Representatives Tom Brun Brun Media Janice Jenkins Director of Logistics Sharon Cowley Design & Production Manager Mitch Gaynor

Circulation Director Scott Adams Chairman Stephen Whitehurst

jackie.cannon@angelbc.com +44 (0)1923 690205 mark.andrews@angelbc.com shehzad.munshi@angelbc.com +44 (0)1923 690215 tbrun@brunmedia.com +001 724 539-2404 +001 724-929-3550 iienkins@brunmedia.com sharon.cowley@angelbc.com +44 (0)1923 690200 mitch.gaynor@angelbc.com +44 (0)1923 690214 scott.adams@angelbc.com +44 (0)2476 718970

stephen.whitehurst@angelbc.com +44 (0)2476 718970

Chief Executive Officer Sukhi Bhadal Chief Technical Officer Scott Adams Directors Jackie Cannon, Sharon Cowley sukhi.bhadal@angelbc.com scott.adams@angelbc.com

+44 (0)2476 718970 +44 (0)2476 718970

Published by Angel Business Communications Ltd, Unit 6, Bow Court, Fletchworth Gate, Burnsall Road, Coventry CV5 6SP, UK. T: +44 (0)2476 718 970 F: +44 (0)2476 718 971 E: info@angelbc.com

Silicon Semiconductor is published four times a year on a controlled circulation basis. Non-qualifying individuals can subscribe at: £50.00/e60.00 pa (UK & Europe). £70.00 pa (air mail). \$90.00 pa (USA). Cover price £4.50. All Silicon Semiconductor is published four times a year on a controlled circulation basis. Non-qualitying individuals can subscribe at: \$50.00/e60.00 pa (UK & Europe), £70.00 pa (air mail), \$90.00 pa (USA). Cover price \$4.90. A information herein is believed to be correct at time of going to press. The publisher does not accept responsibility for any errors and omissions. The views expressed in this publication are not necessarily those of the publishe Every effort has been made to obtain copyright permission for the material contained in this publication. Angel Business Communications Ltd will be happy to acknowledge any copyright oversights in a subsequent issue of the publishers. The paper used within this magazin is produced by chain of custody certified manufacturers, guaranteeing sustainable sourcing. US mailing information: Silicon Semiconductor, ISSN 1096-598X, is published 4 times a year, Jan/Feb, March, April/May, June, July, August/September, October, November/ December by Angel Business Communications Ltd, Unit 6, Bow Court, Fletchworth Gate, Burnsall Rd, Coventry CV5 6SP. UK. The 2021 US annual subscription price is \$90.00. Affreight and mailing in the USA by agent named World Container Inc, 150-15, 1887d Street, Jamaica, NY 114134, USA. Periodicals postage paid at Brooklyn, NY 11256. US Postmaster: Send address changes to Compound Semiconductor, Air Business Ltd, c/o WN Shipping USA, 156-15, 146th Avenue, 2nd Floor, Jamaica, NY 11434, USA. Printed by: The Manson Group. ISSN 2050-7798 (Print) ISSN 2050-7801 (Online) © Copyright 2021.

We strive for accuracy in all we publish; readers and contributors are encouraged to contact us if they recognise an error or omission. Once a magazine edition is published [online, in print or both], we do not update previously published articles to align old company names, branding, marketing efforts, taglines, mission statements or other promotional verbiage, im-ages, or logos to newly created or updated names, images, typographic renderings, logos (or similar) when such references/images were accurately stated, rendered or displayed at the time of the original publication. When companies change their names or the images/text used to represent the company, the invite organizations to provide Angel Business Communications with a news release detailing their new business objectives and/or other changes that could impact how customers/prospects might recognise the company, contact the organisa-tion, or engage with them for future commercial enterprise.

# CONTENTS

## 12 COVER STORY

Merck meets

demanding customer

requirements

through revolutionary

materials science

The continuing evolution of semiconductor devices has challenged materials suppliers to take a more active role in defect elimination and yield enhancement as IC manufacturing grows increasingly complex

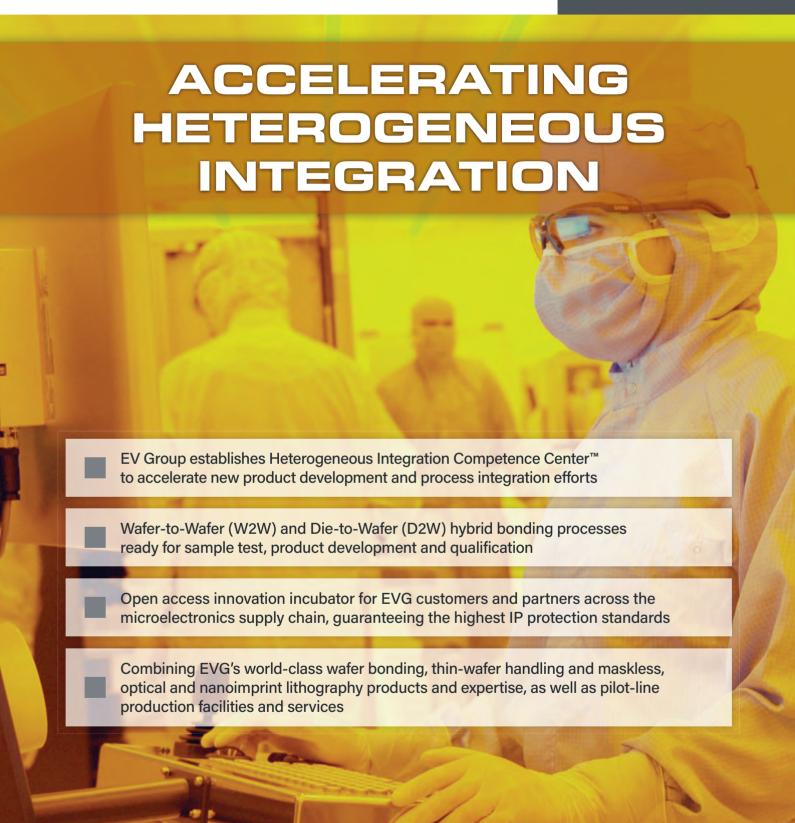

# 16 For die in a package it's always about the bond

Manufacturers constantly seek to reduce costs and improve performance. As advanced node devices continually shrink, process complexity, cost and risk also multiply.

# 20 Ensuring the reliability of electronic devices

Non-destructive advanced scanning acoustic microscopy detects flaws in specialty metals, materials, and packaging of semiconductor devices.

# 22 Benefits of plasma dicing technology

Plasma dicing addresses the challenges of dicing smaller and thinner dies; enables higher throughput and increased yield per wafer.

# 30 System level test enables a paradigm shift

Research conducted by AEM Singapore says the semiconductor industry needs continuous improved faults coverage while reducing the overall costs of test and measurement operations.

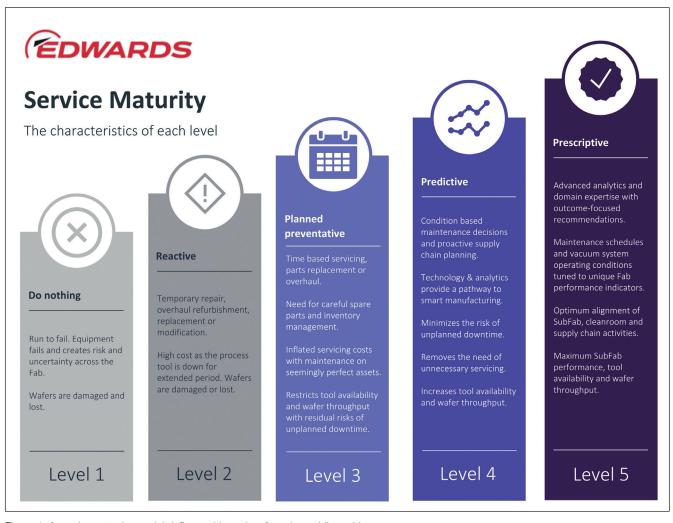

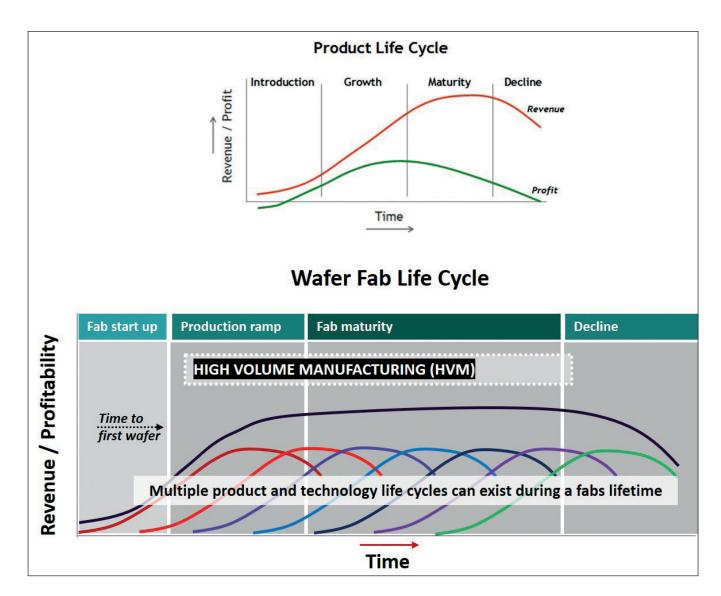

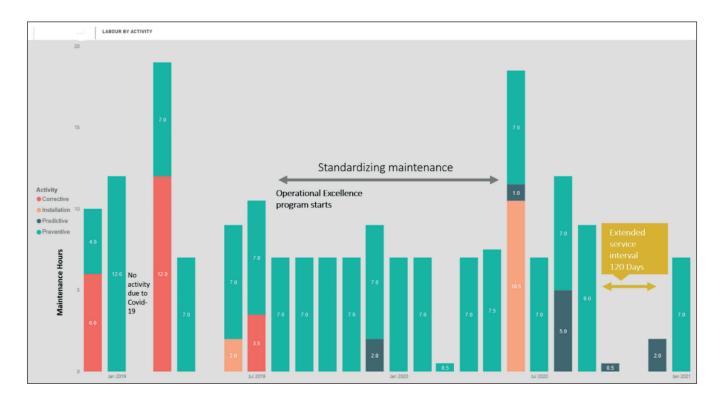

# 34 Evaluating the Fab Lifecycle and SubFab service maturity model

Many plant managers view subfab maintenance as an unavoidable cost rather than an opportunity to lower overall expenses while increasing uptime.

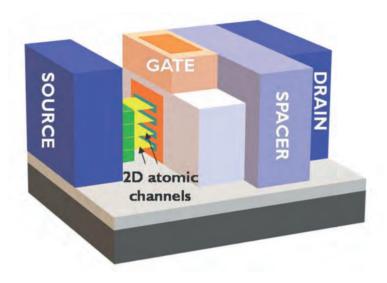

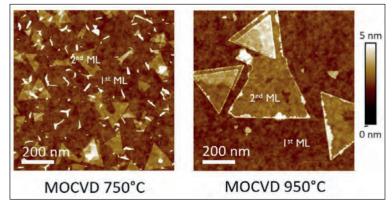

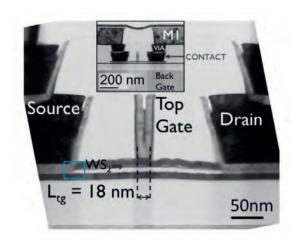

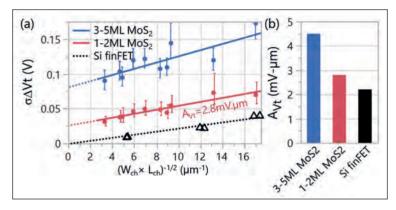

# 42 2D transistors to extend the logic roadmap

Development of WS2 2D transistors in a 300 mm CMOS fab provides a promising pathway for scaling the transistor

### news

- 06 Quantum Computing breakthrough shows blueprint for scalable future

- 07 Brewer Science expands capabilities

- 08 EU Project to mimic multi-timescale processing of Biological Neural Systems

- 09 Park Systems hits 1 Trillion KRW mark at KOSDAQ

- 10 Reno launches Series of integrated RF power systems at 7nm or below

- TESCAN new delayering capability for unattended, automated failure analysis

# Quantum Computing breakthrough shows blueprint for scalable future

QUANTUM MOTION, a UK-based quantum computing startup led by academics from UCL and Oxford University, has made a breakthrough that radically advances the viability and production of quantum computers. Quantum Motion has been able to demonstrate state of the art quantum capabilities using industrial-grade silicon chips, helping to set a blueprint for how quantum chips can be manufactured at scale using existing manufacturing processes. The discovery has been peer reviewed in the scientific journal PRX Quantum

The discovery changes the dynamics in the development of quantum computing, showing that it is possible to build devices at scale using established processes and fabrication plants. This contrasts with other industry approaches that are looking at totally new manufacturing processes or even newly discovered particles. This potentially makes quantum computing development quicker and more cost effective.

A quantum computer harnesses some of the deepest laws of physics, normally seen only at the atomic and subatomic level, giving it unique powers to model the natural world. Quantum computers could be more powerful than today's super computers and capable of performing complex calculations that are otherwise practically impossible. While the applications of quantum computing differ from traditional computers, they will enable us to be more accurate and faster in hugely challenging areas such as drug development and tackling climate change, as well as more everyday problems that have huge numbers of variables - just as in nature - such as transport and logistics.

"We're hacking the process of creating gubits, so the same kind of technology that makes the chip in a smartphone can be used to build quantum computers," said John Morton, Professor of Nanoelectronics at UCL and co-founder of Quantum Motion. "It has taken 70 years for transistor development to

reach where we are today in computing and we can't spend another 70 years trying to invent new manufacturing processes to build quantum computers. We need millions of gubits and an ultrascalable architecture for building them, our discovery gives us the blueprint to shortcut our way to industrial scale quantum chip production."

The peer reviewed paper demonstrates that Quantum Motion has been able to isolate and measure the quantum state of a single electron for a period of nine seconds on a CMOS chip. The chips were manufactured at CEA Leti, a large microelectronics facility in Grenoble, France. Qubits, the building blocks of quantum computers, are often realised using exotic technologies such as superconductors or individually trapped atoms. The big breakthrough is the proof that it is possible to create a stable qubit on a standard silicon chip, like those found in any smartphone, rather than one specially created in a lab environment. Combined this creates the potential for stable and scalable quantum computing.

The experiments were performed by Virginia Ciriano Tejel, a PhD student

working in a low-temperature laboratory at UCL, and co-workers. During operation, the chips are kept in a refrigerated state, cooled to a fraction of a degree above absolute zero (-273 degrees Celsius).

Virginia described the eureka moment, "Every physics student learns in textbooks that electrons behave like tiny magnets with weird quantum properties, but nothing prepares you for the feeling of wonder in the lab, being able to watch this 'spin' of a single electron with your own eyes, sometimes pointing up, sometimes down. It's thrilling to be a scientist trying to understand the world and at the same time be part of the development of quantum computers."

Quantum Motion was founded in 2017 and has raised £8million in series A funding, led by INKEF capital, a Dutch based venture capital company. The round was supported by new investors Octopus Ventures and the National Security Strategic Investment Fund (NSSIF) as well as existing investors Oxford Sciences Innovation, Parkwalk Advisors and IP Group plc.

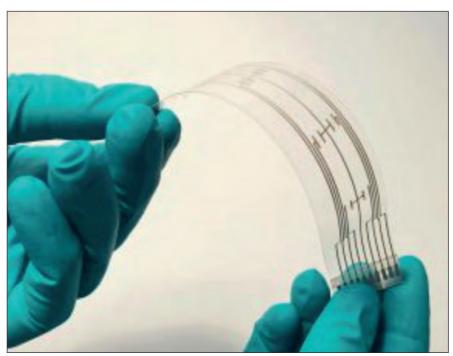

# **Brewer Science expands** capabilities: smart devices & printed electronics foundry

BREWER SCIENCE has announced that its division formerly known as "Printed Electronics" has expanded and is now its "Smart Devices & Printed Electronics Foundry." Brewer Science combines materials science expertise, printed flexible electronics technology, and firmware development capabilities to deliver flexible hybrid electronic (FHE) products that deliver actionable data required for today's sophisticated IIoT environments.

The expanded Smart Devices & Printed Electronics Foundry now offers a full range of electronics platforms, including sensors and systems, that are easily integrated into existing processes and products, such as foundry services, printed temperature sensors, water quality sensors, and condition-monitoring sensors.

The complete end-to-end services range from small-scale prototyping and sensor manufacturing to user interface design, security protocols, as well as data-to-cloud capabilities.

"Brewer Science continues to push the boundaries of what is possible. Cuttingedge materials science and innovative process development are at the core of the company's 40-year history.

By expanding into smart devices and printed electronics, we are leveraging our knowledge and experience in microelectronics to deliver smart sensor systems and real-time data to our customers," said Dr. Adam Scotch, Director of R&D, Smart Devices and PE Foundry.

Showcasing its cutting-edge technology, Brewer Science exhibited its FHE capabilities at the FLEX 2021 Virtual Conference February 22 through 26, and will exhibit at the LOPEC International tradeshow in Messe Munchen, Germany. 23 - 25 March. Rvan Moss. Director of New Business Development at Brewer Science, and Jonathan Fury, Director of Printed Electronics at Brewer Science, will be presenting their research, "Enabling IIOT Applications in Water Sensing.'

### PICOSUN Sprinter demonstrates record-breaking batch film quality

PICOSUN GROUP has further optimized its PICOSUN Sprinter ALD system processes successfully for semiconductor, display and IoT component manufacturing lines. PICOSUN Sprinter ALD system Al2O3 process results showed excellent thickness uniformity even at low 90 °C deposition temperature.

At 300 °C temperature the results were at recordbreaking level (<0.2% 1sigma) when measured within wafer. Furthermore. the team has continued to improve

also other parts of the process performance. The production capacity has more than doubled in the last two months when the process cycle time has been reduced to 8 seconds, without any uniformity degradations.

Other examples include the SiO2 process results, which showed uniform films for backend-of-the-line compatible thermal SiO2 ALD process at 300-390 °C.

More information on these and other process improvements are available on request. Al2O3 is one of the most common deposited films for applications such as moisture barrier for image sensors and displays. SiO2 thin film is widely used in the manufacturing process of for example logic chips as spacer or multipattern applications. Sensitive substrates can require low deposition temperature or low thermal budget without compromising the film quality, which is one of the challenges the company wanted to address with PICOSUN Sprinter.

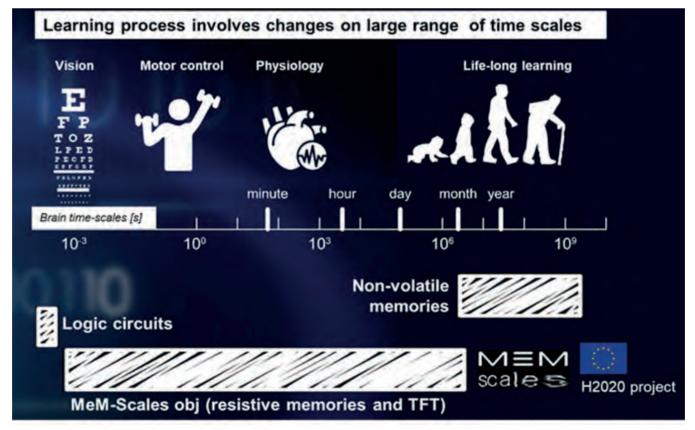

# EU Project to mimic multi-timescale processing of **Biological Neural Systems**

CEA-LETI has announced the launch of an EU project to develop a novel class of algorithms, devices and circuits that reproduce multi-timescale processing of biological neural systems. The results will be used to build neuromorphic computing systems that can process efficiently real-world sensory signals and natural time-series data in real-time and to demonstrate this with a practical laboratory prototype.

The technology developed in the MeM-Scales project will enable novel solutions for the Internet of Thinas (IoT). In the future IoT, much computing volume will be offloaded from central servers and delegated to small controllers and intelligent sensors directly where their services are needed. These IoT systems must be able to work reliably, without interruptions and with very low energy demands. The project also will develop edge-computing processing systems for applications that do not require connectivity to the cloud. Multi-timescale processing is inspired by neural

processing in the nervous system, which occurs naturally over time scales ranging from milliseconds (axonal transmission) to seconds (spoken phrases) and much longer intervals (motor learning).

"The MeM-Scales project aims at lifting neuromorphic computing in analog spiking microprocessors to an entirely new level of performance," said Elisa Vianello, manager of CEA-Leti's AI program and the coordinator of the MeM-Scales project. "Our work is based on a dedicated commitment that novel hardware and novel computational concepts must co-evolve in a close interaction between nano-electronic device engineering, circuit-andmicroprocessor design, fabrication technology and computing science: machine learning and nonlinear modeling."

For physical substrates, novel memory and device technologies will be fabricated to support on-chip learning over multiple timescales for both

synapses and neurons. Multi-timescale resistive memory technologies as well as thin-film transistor (TFT) technology will be used to enable timescales spanning up to nine orders of magnitude. On the side of computational theory, autonomous learning algorithms and architectures supporting computation over this wide range of timescales will be developed. These computational methods will be specifically tailored to cope with the low numerical precision, parameter drift, stochasticity and device mismatch that are inherent in analog nanoscale devices.

The project brings together European specialists in neuromorphic engineering, an emerging interdisciplinary field that takes inspiration from biology, physics, mathematics, computer science, and engineering to design hardware/ physical models of neural and sensory systems. The project's name is short for Memory technologies with Multi-Scale time constants for neuromorphic architectures.

# Park Systems hits 1 Trillion KRW mark at KOSDAQ

PARK SYSTEMS, manufacturer of Atomic Force Microscopes announced the company stock valuation exceeded 1 Trillion KRW (almost \$1 Billion USD) at the end of KOSDAQ on April 20, 2021. Park Systems issued 1 million shares for its initial public offering on December 17th, 2015 at KOSDAQ, a

NASDAQ equivalent in Korea. Since the IPO, the company has progressed as a global leader in Atomic Force Microscopy. with a commanding lead in semiconductor advanced automated AFM systems and bringing AFM technology into the mainstream as the premier tool for nanoscale metrology.

"Park Systems has received successive purchase orders by all the world's top semiconductor and data storage manufacturers," states Dr. Sang-il Park, CEO and founder of Park Systems, who worked as an integral part of the group at Stanford University that first developed AFM technology, and created the first commercial AFM in 1988. "We have continued to grow at an accelerated rate of over 20% compounded growth, even during the turbulent pandemic year." The valuation at KOSDAQ, close to \$1 Billion USD brought attention from foreign investors who have made active purchases. increasing the company's holding from 11% (Jan) to 18% (March). Recently Park was recognized by Forbes Asia Best Under a Billion list for 2020, received the KOSDAQ Grand Prize. and listed on the FTSE small-cap index.

In 2020, Park Systems signed a joint development project with IMEC to address the current metrological challenges of continuously downscaling the geometrical dimensions of devices and 3D stacking assembly. Earlier this year, Park Systems made an equity investment in Molecular Vista, that produces tools to probe and understand matter at the molecular level through quantitative visualization using InfraRed Photo-induced Force Microscopy. Park Systems is headquartered in Suwon, South Korea. With its rapid global expansion, it has become the premier supplier of Atomic Force Microscopy (AFM) tools for industrial, research and academic nanoscale research. Research at the extensive Park Applications Technology locations worldwide have led to the development of many leading AFM technologies including True Non-Contact<sup>™</sup> technology, SmartScan<sup>™</sup> operating software, PinPoint™ mode, which can be applied for nano-mechanical analysis and electrical modes; and most recently, the Smart Litho™ for nanoscale lithography. Park Systems was the first company to revolutionize AFM technology with its flexure-based scanner system that brought new levels of accuracy, resolution, and sample handling to the technology. In 2024, Park Systems will move into a new expanded headquarters, and later this year, it will introduce a new fully automated AFM with Al and robotic intelligence for both scientific and industry labs.

**OPTIM Wafer Services is pleased** to announce the installation of an automated ALPSITEC MECAPOL E550 CMP tool at its site in Greasque France.

The system will allow OPTIM to offer for following new or improved services.

- Oxide CMP Planarisation

- Oxide Roughness Improvement

- Metal CMP

- Poly CMP

This additional capability enhances OPTIM's already large portfolio of services that include:

- Wafer thinning by grinding

- Individual Die thinning

- Taiko Grinding

- Single/Double side Polishing

- SOI Processing

- Edge Trimming

- Wafer Dicing

- Dice Before Grinding

- Wafer Cleaning

- Process development services, combining any of the above capabilities.

For detailed technical discussions please contact either Mr. Mark Wells or Mr. Georges Peyre using the contact details below or visit our website.

### www.Optimwaferservices.com

### Mark Wells

Tel - +44 1743 891 820 **Email** – MWells@optimws.com

### **Georges Peyre**

**Tel** - +33 442 126 158 **Email** – GPeyre@optimws.com

# Reno launches Series of integrated RF power systems at 7nm or below

RENO SUB-SYSTEMS (Reno), a developer of high performance radio frequency (RF) matching networks for nanoscale semiconductor manufacturing, has introduced its new GenMatch Series that integrates the company's proven solid-state Electronic Variable Capacitor (EVC) RF match and Precis generator technologies into a single unit. The systems have a footprint similar to a match alone, saving space on the process tool, and are faster, more repeatable and more reliable, with lower cost of ownership. GenMatch systems are ideal for leading-edge etch and deposition applications in semiconductor manufacturing, where level-to-level pulsing and short RF on-times are critical to meet performance requirements at the most advanced nodes.

"Reno has a strong track record of bringing novel RF match technology to market, and the GenMatch™ is no exception," said John Voltz, senior vice president of business development at Reno. "The high reliability of our EVC all-solid-state match equals RF generator reliability, making it now economical to put both in the same package. The GenMatch is a true RF power system that delivers plug-and-play performance, a first for plasma processing in advanced

semiconductor manufacturing."

The GenMatch platform covers powers from 500W to 10kW and frequencies from 400kHz to 60MHz. The generator supports level-to-level pulsing, while the RF matching network matches impedance on each pulse, meaning every wafer sees the same frequency, unlike frequency sweep. Al and machine learning using the matching network's extensive sensor and sampling capability further enhance system performance.

Benefits offered by the GenMatch Series include:

- O Detection of fast transients at the output of the RF matching network. These transients may represent micro-arcing in the plasma chamber that the etch or deposition tool would never identify. Reno's RF generator can then control the power to the chamber to eliminate the micro-arcing.

- The option to fully tune the plasma impedance, compared to standard frequency tuning approaches that can only tune limited plasma impedances, and then only the reactive part of the plasma impedance.

- The ability to provide additional tuning options, such as sequential tuning, where the frequency tuning and

**EVCTM** tunina are done sequentially for faster, repeatable and more stable tuning of

- The generator can be set to sweep the frequency to tune the reactive portion of the plasma impedance, for which the EVCTM-based matching network adjusts the capacitance values to tune the resistive portion of the plasma impedance.

- Proprietary, dual-stage heterodyne circuitry that enables a faster slew rate response from the detector stages of the control circuit. This provides a considerably more accurate measurement of pulsed RF signals.

With match and generator about the same size as Reno match alone, the combined unit saves valuable space on the process tool. Additional cost savings are achieved, as only one location is required to facilitize power, water, etc. All-digital units allow for multiple communication protocols, Ethernet, EtherCAT and DeviceNet.

### Brewer Science recognized as certified B corporation

BREWER SCIENCE, a global technology company has announced it is now a Certified B Corporation. As a B Corp, Brewer Science is committed to achieving the highest standards of corporate, social, and environmental performance, along with transparency and accountability.

The rigorous certification process recognizes for-profit companies who utilize business as a force for good through exacting standards for social and environmental performance. Brewer Science is the first company in the semiconductor industry to earn this certification and the seventh in the state of Missouri. Brewer Science joins a worldwide network of almost 4,000

Certified B Corps to date, from more than 60.000 applicants across 150 different industries and 74 countries, with one unifying goal: to redefine business success.

Brewer Science completed a meticulous assessment process conducted by B Lab, the governing body of B Corps, which examined over 170 factors while reviewing Brewer Science's customers and vendors, record of inclusion, community involvement, corporate governance and environmental impact. Key elements such as average employee tenure, charitable giving, energy savings plan, recycling policies, employee volunteer service and employee upward mobility are also analyzed. Brewer

Science will hold B Corp certification for three years before submitting to a renewal process.

Environmental impact is one of the highest factors Brewer Science scored. valuing the company's efforts in its environmentally innovative manufacturing processes. "Brewer Science remains committed to protecting the environment, conserving resources, and providing a healthy, safe and secure workplace. Environmental responsibility is an ongoing priority at Brewer Science and we are targeting a carbon-neutral footprint by 2030," said Dan Brewer, Chief Resources Officer at Brewer Science.

# TESCAN new delayering capability for unattended,

# automated failure analysis

TESCAN ORSAY HOLDING a.s. has announced the release of the new TESCAN Delayering Module that enables automated gas-assisted top-down delayering using TESCAN SOLARIS X and AMBER X Plasma focused ion beam (FIB) instruments. TESCAN Delayering supports physical failure analysis through the combination of inert Xe plasma FIB ions and unique, proprietary gas chemistries that have been developed specifically for today's advanced technology nodes, creating artifact-free, site-specific trenches—with maximum planarity and homogeneity and without altering a device's electrical propertiesfor rapid access to deeply buried features or defects.

"Efficiently delayering today's devices requires solutions that are different from the standard gas chemistries or traditional gallium (Ga) FIB technologies that have been used in the past for this application," states Lukáš Hladík, product manager for FIB-SEM in TESCAN's Semiconductor market segment. "With

TESCAN Delayering. we have developed a state-of-the-art solution for technology nodes below 10nm, and which also provide the ability for users to customize parameters for their own devices. Predictable. automated and unattended delayering can help with allocating and deploying

lab resources. Users can be confident that the delayering process will terminate at the designated laver so they don't need to spend a lot of time monitoring the process."

TESCAN Delayering uses a step-by-step guided wizard to set-up the required delayering process. Factory-defined templates assure consistent application of all delayering parameters. The templates also can provide the starting point for users to develop their own recipes customized to their specific devices. Once the job is set-up, the

TESCAN Delayering module executes the process automatically, with the plasma FIB providing rapid material removal, without Ga implantation or beam damage. At any time during the delayering process, users may monitor the progress by using signal peak recognition in the end-pointdetection curve. TESCAN Delayering module is supported by a team of skilled applications scientists who can assist with process development and customizations for users who want to further streamline their delayering processes.

### Luvata announces €34M investment in Finland hot extrusion line

LUVATA in Pori, Finland has announced a €4M investment in a new hot extrusion line and facility on its premises in the Pori Copper Industrial Complex. This new 5237-square metre facility will be home to a 130-metre long by 30-metre wide, 55 meganewton (MN) hot extrusion press that includes the latest in robotics and automation.

Construction of the new building includes over 1000 concrete and steel piles to support the 1000-ton hot extrusion press, roughly 5X the weight of a Boeing 747. The building's infrastructure and equipment will enable improved efficiencies in terms of productivity, quality, safety and energy efficiency. The complex installation involves components from Germany, Spain, Czech Republic, and Italy coming to Finland in over twenty truckloads at prescribed times and in designated sequences. "This extremely complex project reflects the technical competence

and confidence we have in our employees and suppliers," indicates Jyrki Rantanen, Managing Director of Luvata Pori Oy. "It also reflects Luvata's longterm commitment in meeting the growing needs of our customers."

Luvata Pori Ov produces a wide variety of oxygen-free high-conductivity copper and copper-alloy products including hollow conductors, tubes, wires, strip and other specialty profiles that serve the automotive, electronics, healthcare, mining, power generation and distribution and renewable energy markets. The new extrusion press will double Pori's current capacity and expand available billet sizes, wire sizes and alloys to meet the company's growing demand for high-quality copper-alloy products and solutions.

Construction of the new building is now underway with production estimated to begin in Q2 2022. The new extrusion press will eventually replace Pori's nearly 60-year old 25-meganewton press currently in operation.

# Merck meets demanding customer requirements through revolutionary materials science

The continuing evolution of semiconductor devices has challenged materials suppliers to take a more active role in defect elimination and yield enhancement as IC manufacturing grows increasingly complex. MERCK, a science and technology company headquartered in Darmstadt, Germany, offers insights into how the company has redefined material science to speed up production, increase yields and provide customers a competitive edge.

> **DEMANDING PRODUCTION requirements for** advanced node semiconductors continue to make the world's most complex manufacturing processes all the more challenging. Flaws that were inconsequential two or three device generations ago today are 'killer' defects in devices at 10nm and below.

As a consequence of ever more stringent process requirements, manufactures and their supporting supply chain members are seeking ways to make the production of advanced node devices as fool-proof as possible. One way to minimize defects requires greater materials purity and precisely controlled formulations that essentially create materials with carefully documented 'fingerprints' for each compound so that batches can be more readily sourced, stored, and tracked from the point that they enter the manufacturing process stream to the very last back end of line steps.

No compound is exempt from constantly improving quality control demands since manufacturers appreciate that the more control they exert over every aspect of a material's composition, the less likely it is that one of those materials might accidentally inject defect-inducing qualities. At stake is billions of euros in microelectronic devices and trillions in end-use products that will succeed or fail based on their semiconductor content.

The continual advancement of materials science has created unique opportunities for suppliers and

process chemical manufacturers that already have stringent standards and exemplary quality controls. Such companies are ideally positioned to meet the growing needs of semiconductor device makers. Somewhat like semiconductor manufacturing, the development and formulation of pharmaceutical and life science products require extreme precision and rigorous quality control. So it should come as no surprise that a company known for quality and advanced technology such as Merck would continually invest in its advanced electronics materials division.

Today, Merck has emerged as one of the largest international players supplying high-purity/high-quality semiconductor process chemical formulations to a growing list of global IC manufacturers.

Merck isn't satisfied to rest on its laurels or expect its more than 300 years of industrial excellence to meet every requirement in an ever-changing 21st-century global marketplace. Since 2007, Merck has made acquisitions and divestments totaling around €40 billion - in the process, Merck has transformed itself into a leading science and technology company supporting semiconductor manufacturers in addition to its prominence in healthcare and life science industries.

Recent acquisitions by Merck include bringing Versum Materials into its family of companies in October 2019. In September that same year, Merck completed

# COVER STORY MERCK NDUCTOR | ISSUE II 2021 WWW.SILICONSEMICO. D. TOR.NET 13

### **COVER STORY MERCK**

its acquisition of Intermolecular, a California-based company focused on advanced materials innovation. Both acquisitions added products, processes, and a wealth of experience to Merck's already deep well of high-performance materials expertise.

Following completion of the Versum acquisition, former Chairman of the Executive Board and former CEO of Merck, Stefan Oschmann remarked. "By acquiring Versum, we will be optimally positioned to capitalize on long-term growth trends in the electronic materials industry. At the same time, we are broadening our commitment to electronic materials. balancing our portfolio with three strong business sectors and sharpening our strategic focus on innovation-driven technologies."

Echoing those remarks, Kai Beckmann, Executive Board member of Merck and CEO of Electronics said, "We are very pleased to welcome Versum to our team. After the most recent acquisition of Intermolecular, this closing marks another major milestone on our Bright Future transformation journey to become a leading player in the electronic materials market. The expertise of our combined business will enable us to offer customers in the electronics industry cutting-edge technology innovations."

In all its acquisitions, Merck has sought to add strategic advantages that complement its existing global portfolio. Amongst key benefits of its 2019 acquisition of Intermolecular was an opportunity to relocate the Merck Silicon Valley Innovation Hub team in Menlo Park to Intermolecular's 150,000 square foot facility located in San Jose, California. Much more than just a consolidation, the move to San Jose allowed Merck to take advantage of Intermolecular's 30,000 square feet of cleanroom, chemical laboratories, offices, meeting and event spaces in a way that not only benefitted Merck, but also created a unique space to empower collaboration with startup

companies focused on advanced materials and support services for semiconductor manufacturing.

"The mission of the Silicon Valley Innovation Hub is to identify and explore untapped innovation and business opportunities for Merck. In this context, the intersection of life science and material science is becoming increasingly important and opens new areas of innovation. Having the Silicon Valley Innovation Hub and Intermolecular under one roof now will allow us and our cooperation partners to develop and test new materials for biological applications. We are very excited about these new opportunities," stated Thomas Herget, head of the Silicon Valley Innovation Hub, on the occasion of the move by Merck staffers to San Jose in March 2021.

Materials science can and does play a decisive role in the fabrication of next-generation semiconductors. Products and processes that may have previously been considered secondary to the success of a new wafer production step have now proven critical. Equally important is the need for manufacturers to understand and appreciate exactly what constitutes a successful new material or process compared to legacy approaches.

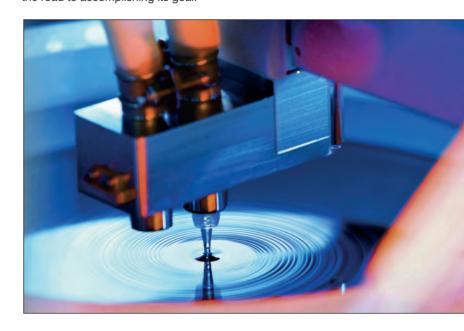

One area in which Merck continues to excel and set new standards involves delivering superior materials as well as better performance data compared to competing approaches. A ready example can be found in the chemical mechanical planarization (CMP) technologies that are utilized throughout the transformation of a bare silicon wafer into a substrate bearing finished devices at high yield with high performance. Amongst its many functionalities in device manufacturing, CMP plays a critical role in producing finished copper interconnects. In production, sheet resistance (Rs) of copper interconnects are measured after the barrier layer is removed by copper/barrier CMP.

### COVER STORY MERCK

But generally speaking, this analysis is not available in the laboratories of consumable CMP suppliers.

A combination approach to measuring the effectiveness of CMP on copper interconnects is to examine dishing and erosion following planarization completion. Ordinarily, only dishing is analyzed in part due to the challenges of measuring both qualities.

Merck has found that as feature sizes become even smaller, traditional CMP metrology becomes more time consuming, noisy and challenging. Hence, electrical testing provides the most comprehensive, accurate, and reliable dataset. Merck performs back end of line (BEOL) copper and copper-barrier CMP slurry testing on an electrically capable test vehicle. The test vehicle is then sent to the company's inhouse electrical characterization laboratory.

An automated high-throughput program can be used to probe the test vehicle. For example, 16 features across 32 dies can be measured in four hours, whereas by physical methods (AFM, profilometer), only 11 features across three dies can be measured, which typically takes double the time, (i.e., 8 hours.)

Merck can provide such data to customers upon their request; other CMP suppliers do not have access to such electrical characterization, and typically lack expertise in electrical data analysis. Merck's approach was developed in concert with customers to ensure that the data made available is not only useful, but provides the manufacturer with an 'edge' compared to other approaches to characterizing post-CMP effectiveness.

One company that has partnered with Merck is UMC Fab12i (Singapore.) Fab Director Steven Hsiao shared his opinion that the accelerated success of a recent wafer run could be tied not only to the support of his internal engineering team and production technicians, but also the direct support of Merck in assessing the performance of their CMP copper planarization processes. "We believe that anything is possible if we work together, and we look forward to working with Merck again on our next project," said Hsiao.

For BEOL copper bulk slurries, Merck products offer the following advantages:

- Residue-free & 100 percent copper clearing due to low additives

- Tunable profile and dishing to meet customer's technical requirements, low step-height to large step-height

- Low abrasives to provide low defects

- No pad stains

- High selectivity

- Slurry in corrosion-free regime of the Pourbaix diagram

- Newtonian and Prestonian behavior for predictability across consumable sets

For BEOL copper barrier slurries, Merck products offer the following advantages:

- Customized tunable selectivity, working with customer-specific requirements

- Low defectivity

- Superb topography control

- More concentrated formulations

- Compatible with novel liner schemes

"Merck is pushing boundaries to create nextgeneration CMP slurries which revolutionize the semiconductor industry. The integration of Merck and Intermolecular provides more value to customers and enables us to partner with customers to solve current and future integration challenges. For example, Merck developed its new, innovative CMP slurries and can provide dishing/erosion (physical) data of materials as well as electrical data to measure CMP slurry performance. This preview of electrical data minimizes risk, maximizes vield and shortens cycle time for our customers, which also demonstrates Merck to be a total solutions provider. At Merck, we are striving to respond quickly to industry challenges. We aim to deliver the total solution, and strive to be the preferred partner for our customer's future needs," said Laura Matz, the Chief Science and Technology Officer at Merck.

In an effort to continually improve its already industryleading approach to combining high-performance materials with actionable performance data, Merck is also examining the development of novel abrasives and the ability to modify the surface of abrasive constituents so that materials are effectively customized to a manufacturer's unique needs and requirements. This is a key element of topography and defect control that will continue to grow in importance as the industry moves from one device generation to the next. Merck has set its sights on leading the semiconductor materials industry; Merck is well down the road to accomplishing its goal.

### PALOMAR TECHNOLOGIES

For die in a package

# it's always about the bond

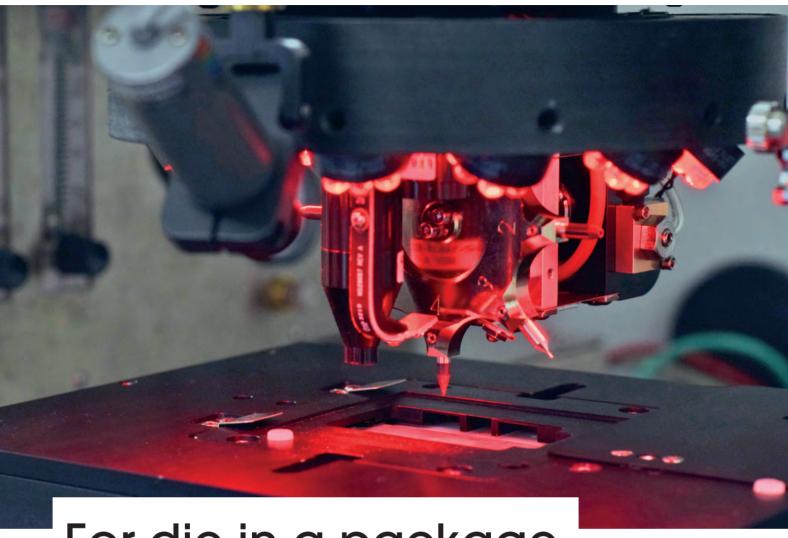

Semiconductor production is so complex that manufacturers constantly seek to reduce costs and improve performance. As advanced node devices continually shrink, process complexity, cost and risk also multiply. Silicon Semiconductor spoke with the experts at Palomar Technologies to learn how die bonding continues to evolve and play a central role in II-VI, III-V, photonic and hybrid module manufacturing.

THE UNIVERSALITY of some semiconductor processes points to their essential nature across technological platforms. Even as device form factors, lithographic innovations, defect management and performance enhancement techniques come and go, there remain some steps that are always needed including the requirement to place finished die

inside a receptacle that will protect it and enable its functionality.

As nodes advance to smaller feature dimensions, manufacturers are keenly aware of the growing importance of finely tuning process steps and material formulations to aid in defect elimination and quality

### PALOMAR TECHNOLOGIES

control while improving product lifetimes / adding value. This attention to details pays dividends that include enhanced profit margins, faster time to market and reduced cost, not to mention overall customer satisfaction.

Die bonding is a prime example of how a technology that has been a part of semiconductor production predating the advent of widespread automation has continued to evolve and bring value to complex manufacturing systems. In a recent conversation with Palomar Technologies' Kyle Schaefer, product marketing manager, Silicon Semiconductor technical editor Mark Andrews spoke about ways that die bonding has evolved, and how advances in the field can contribute to balancing the need for high throughput along with process control. This versatility benefits very diverse products that can range from filters to power amplifiers to photonic assemblies.

Schaefer noted that one measure of how die bonding continues to evolve can be found in the RF power amplifier market, which is expected to increase substantially in the next five years. This expectation is rooted in the need to support 5G service rollouts that depend heavily on new power amplifier assemblies in base stations. The estimated CAGR for the general RF power amplifier market is 5-6 percent from 2020-2025. This anticipated demand translates into a need for manufacturers to increase their production capacity. But unlike previous generations, 5G technology is different than the more evolutionary transitions seen as 2G became 3G, which begat 4G; a simple production ramp will not address all 5G needs since volumetric growth carries with it new challenges as well as new processes that need to be developed and refined

5G vendors must simultaneously churn out considerably more devices while dealing with design, material, and process faults. There is also a great deal at stake in terms of long-term supply chain relationships-5G technology is the foundation of new, wide-ranging commercial initiatives including the opportunity to use wireless networks to fill gaps in wireline networks or supplant fixed broadband access. In the mix are new amplifier designs at higher frequencies and new technologies along with all the usual pressures to ramp-up volumes. A misstep during the early stages of a build-out expected to take a decade or more could freeze-out a manufacturer from future business. Poor execution in terms of yield, quality, or product reliability could indeed prove quite costly if future business tenders fail to convert into design wins.

RF power amplifiers are worth examining in the context of die bonding due to the mixed technologies being utilized. While not as different as requirements for photonic assemblies, there are substantial differences between amplifier types, principally divided between die utilizing LDMOS technology and

components based upon newer technologies such as gallium nitride (GaN) on silicon carbide (SiC). While LDMOS is considered mature, GaN on SiC has been a mainstream product for a fraction of the LDMOS tenure. GaN-based amplifiers also serve a substantially different frequency range (3.5 GHz and above), and due to its significantly greater power density, the most important metric for assessing a successful bond for GaN amplifier die comes down to thermal management.

"Ensuring high thermal conductivity of the bond between the chips and the transistor package is paramount to the longevity and performance of the device. Beyond that, the build requirements vary based on assembly approach and materials used," Schaefer noted. In addition to the thermal management requirements, GaN devices are also more fragile and come at a higher cost than similarly sized LDMOS devices. Due to their fragility and susceptibility to surface damage, pick-place-bond sequences for GaN die need greater care during handling and bonding.

In addition to very significant differences between LDMOS and GaN that affect handling and die attach methodologies, the second most important division concerns the actual assembly and die attach material options. There are a host of choices available, each designed to deliver voidless bonds with high strength and longevity appropriate to the underlying die technology. An important related aspect of die bonding is the vision system used to not only ensure highly accurate and consistent placement, but also help maintain quality while collecting data to ensure damage-free placement of each die. Using Palomar Technologies 3880 Die Bonder as a reference, Schaefer explained ways that industry's latest bonding systems deliver performance that was previously not possible.

### PALOMAR TECHNOLOGIES

### Often a simple active process control step consisting of a single reference can be enough to prevent repeated misplacement or consecutive component damage

"For preventing component damage in general, or even simply just monitoring die placement, the die bonder vision system can be used to great effect. Often a simple active process control step consisting of a single reference can be enough to prevent repeated misplacement or consecutive component damage. This can be achieved by using a unique feature of the VisionPilot® referencing system referred to as the ability to 'score clutter'. Essentially, the pattern recognition algorithms can use excess data (i.e. clutter) which comes from debris, chips, and scratches, to lower the given 'score' for a reference. This allows rejection of die based on damage or cleanliness."

"Using this technique before beginning any assembly allows for die sorting during the actual build process to prevent any waste of material. It is also possible to use this same 'chip damage check' after placement to avoid any instances where damage was done through any debris collected on the vacuum tool – a situation that, when left unchecked, could result in consecutive device destruction until noticed much later down the line. This control step can also simultaneously check for die placement repeatability in terms of X, Y, and Theta, further adding to the complete control options available," Schaefer explained.

While some process tools come and go depending on the die generation, others evolve since the need to perform a given function like wafer manipulation remain even as wafer diameters change, die grow

smaller, or substrate materials vary in crystalline structure, thickness and fragility. Yet the underlying need to move wafers along a processing line remains even as other factors change. The same could be said with die bonding, hence the favored approach of building a process tool that evolves rather than enters production with only a limited lifetime.

The idea of flexible evolution was central to the development of Palomar Technologies 3880 Die Bonder. Schaefer explained some of the highlights of the system's enduring and wide-ranging appeal.

"Flexibility is key to providing a strong ROI across many business models from academia, SME's, CM's, to full scale manufacturing giants like Lumentum & II-VI. Typically, Palomar customers keep Palomar bonders for many years, so longevity of support and the ease of reconfiguration as products and processes mature and change is a major consideration for engineers and procurement professionals when investing in bonding solutions."

"Specifically, flexibility is one of the core design philosophies of the Palomar 3880. The flexibility of the system is unique in that it offers the capability to easily change from one process or configuration to another while also remaining effective in its performance for all potential applications."

"It is not just the 8-position, bi-directional tool turret, which only takes 250ms to change tools on the fly, that makes the 3880 extremely flexible. It is the extralarge work envelop where many configurations of bonding hardware, material presentation options and automation options can be utilized. In addition, the changeover is rapid and effortless which supports any company's need for high mix."

"Essentially, the robust abilities of the software and hardware are the core functionality that make the flexibility of the 3880 so impactful, in that it is not just great in one area and good in many others, but it is great in all areas. The 3880 is an R&D, NPI and volume production machine all in one," Schaefer stated.

As semiconductor processes and manufacturing goals change with succeeding device generations, some needs remain constant, like the requirement to pick and place die, then create a permanent, robust bond between the device and its package. The Palomar 3880 remains a centerpiece of both research and all manner of production environments. Sometimes, the best products just keep getting better.

# Micromachining Excellence

Whether standard system or special solution:

# High-Performance & Reliable Laser Micromachining Solutions for

- » Roll-to-roll laser processing of flexible substrates

- » Laser drilling, cutting, structuring, modification, ...

- » Almost any application and substrate

Contact us now!

3D-Micromac AG

Tel: +49 371 40043-222

sales@3d-micromac.com

# Ensuring the reliability of electronic devices through non-destructive testing of specialty metals & materials

Non-destructive advanced scanning acoustic microscopy detects flaws in specialty metals, materials, and packaging of semiconductor devices

> MANUFACTURERS of high-end semiconductor electronic products used in consumer, industrial, and military applications have long relied on precise testing methodologies to identify the location of defects such as voids, cracks, and the delamination of different layers within a microelectronic device, also known as a Chip.

Manufacturers employ a range of other techniques: scanning acoustic microscopy (SAM), a non-invasive and non-destructive ultrasonic testing method, has become an industry standard to detect and analyze flaws during various chip production steps and in the final quality inspection after packaging.

In addition, SAM is often utilized as a Failure Analysis method when needed to identify a specific root cause failure mechanism when a device fails during use.

Beyond semiconductor components themselves, today's electronics products contain various specialty metals, alloys, plastics, and glass components. All semiconductor components need to be enclosed and packaged in consumer usable formfactors. As a result. SAM equipment has evolved and is now being used to detect subsurface flaws, dis-bonds, cracks, and other irregularities in these types of materials that constitute "packaging" of semiconductor components.

With the same rigor of failure analysis and quality testing used for semiconductors now being applied to metals and alloys, both the production yield and overall reliability of electronic devices have improved significantly. In doing so, projects are completed in less time while eliminating potential points of failure in the field.

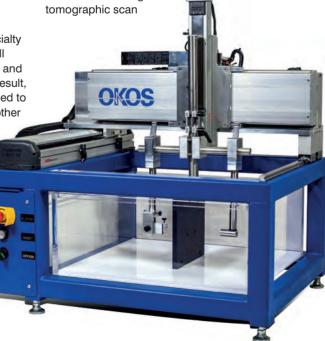

"The reality is that a failure in an electronic product package or a non-semiconductor component can be just as catastrophic as a failure with the semiconductor," said Hari Polu, President of OKOS, a Virginia-based manufacturer of SAM and industrial ultrasonic non-destructive (NDT) systems. The company serves the electronics manufacturing, aerospace, and metal/alloy/composite manufacturers, and end-user markets.

### Detecting Flaws with SAM

without the need

for time-consuming

SAM is a powerful non-invasive and non-destructive method for inspecting internal structures in optically opaque materials. Depth-specific information can be extracted and applied to create two- and threedimensional images

procedures and more costly X-rays. SAM works by directing focused ultrahigh frequency sound from a transducer at a tiny point on a target object. The sound as it passes through the material is either scattered, absorbed, reflected, or transmitted.

Detection of the direction of scattered pulses and measuring the TOF "time of flight," the presence of a boundary or object is determined and its distance. Three-dimensional images are created by scanning point by point and line by line on an object. Scan data is digitally captured and processed by special imaging software and filters to resolve a specific area of focus in either single or multiple layers.

According to Polu, the industrial sector has traditionally utilized other methods considered inferior compared to what is being used in today's semiconductor industry. However, with SAM equipment, specialty materials manufacturers can achieve the same level of failure testing to the companies that make metals, alloys, composites, and titanium plates used in electronic devices.

"OKOS has leveraged the lessons and the tight specifications from the semiconductor world and adapted our SAM scanning systems for various form factors and provide unique solutions for specialty crystalline, metals, and other material for our customers in the industrial markets," said Polu. "With this type of testing, we can inspect materials at a level one to two orders of magnitude better to discover flaws that were previously undetected."

Today, much of the SAM equipment can inspect various items with unique product geometries or sizes, from crystal ingots, wafers, and electronics packages to miniature physical packaging, metal bar/rods/ billets, turbine blades, etc. However, as important as the physical and mechanical aspects of conducting a scan, the software is the key to analyzing the information to produce detailed scans.

For this reason, "OKOS decided early on to deliver a software-driven, ecosystem-based solution," said Polu. The company's ODIS Acoustic Microscopy software supports a wide range of transducer frequencies from 2.25 to 230 MHz. Multi-axis scan options enable A, B, and C-scans, contour following, off-line analysis, and virtual rescanning for composites, metals, and alloys, which result in highly accurate internal and external inspection for defects and thickness measurement via the inspection software.

Polu estimates that their software-driven model enables them to drive down the costs of SAM testing

"Every company will eventually move towards this level of failure analysis because of the level of detection and precision required for specialty metals and materials," says Polu. "The cost advantages and time savings of Industrial SAM equipment make this possible."

SAM systems have an integral role in semiconductor device manufacturing based on their precision, usability, and time-saving advantages compared to other NDT options. Extending this testing methodology beyond semiconductor components to specialty metals and materials throughout a semiconductor device can provide more robust failure detection capability for manufacturers of consumer, industrial and military electronic devices.

# Benefits of plasma dicing technology

Plasma dicing addresses the challenges of dicing smaller and thinner dies; enables higher throughput and increased vield per wafer.

### BY SHOGO OKITA, NORIYUKI MATSUBARA, ATSUSHI HARIKAI, AND JAMES WEBER, PANASONIC CORPORATION

IT COULD BE ARGUED that the defining feature of the Electronics Industry is the ability to miniaturize. Every person with a passing interest in electronics has heard of Moore's Law: the processing power of affordable CPUs - or the number of transistors on a chip - will roughly double every two years. It is credit to both Gordon Moore's foresight, and the technical and engineering teams around the world who continue to innovate, that the 'Law' is still even being discussed today. Part of the reason for chip size reduction lies in the shrinking of technology nodes (process

geometries). Currently the smallest node that is being manufactured in mass volume is 7nm, and even the smaller size is under development in the industry. The increase in processing power and speed and the miniaturisation and integration of electronic functions that continue to result from such technological advances lie at the heart of the pervasiveness of electronics in our everyday lives: the smart phones that we rely on; the uptake of artificial intelligence in smart homes and cities; driverless vehicles; remote medical home diagnostics – there is not one aspect of life that electronic products and systems have not penetrated.

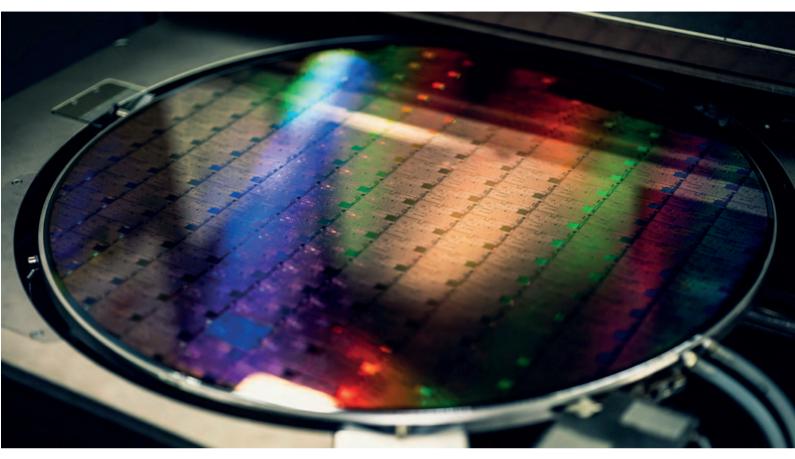

But for this to continue, it is not only in the area of photolithographic processing that technology needs to keep innovating. Once a wafer has been created it must be singulated into individual dies, and as dies are becoming smaller and thinner, many products are facing difficulties caused by the singulation or dicing process. New challenges include: increasing material loss due to the width of the dicing street; mechanical damage such as chipping; and increasing processing time. Now, Panasonic has developed a plasma dicing process that in certain circumstances can replace mechanical dicing, which addresses these issues.

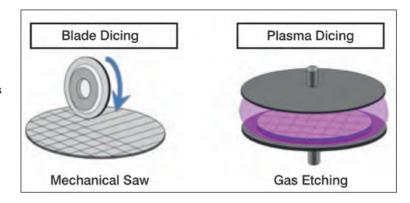

### Types of Dicing Process

Traditionally, two dicing technologies have been used: scribing and breaking, and mechanical cutting using a dicing saw ("blade dicing"). Scribing and breaking causes stresses on the wafer and die and results in chipping and yield inefficiencies. Blade dicing also introduces stresses and contaminants which are more problematic as the die size and process geometries shrink. Laser dicing is another method which is faster than using a saw, but can also cause cracking and damage to the chip.

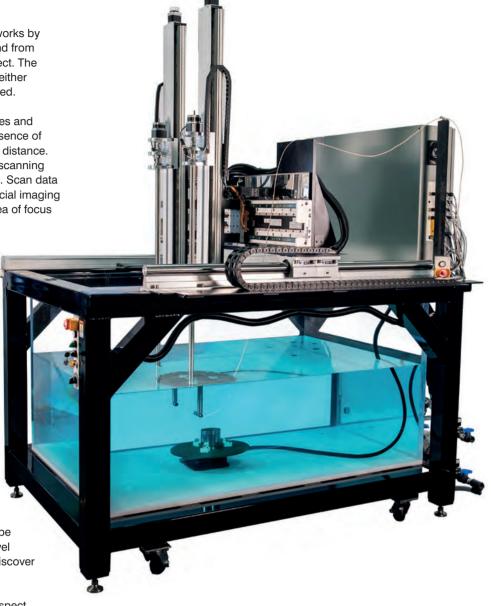

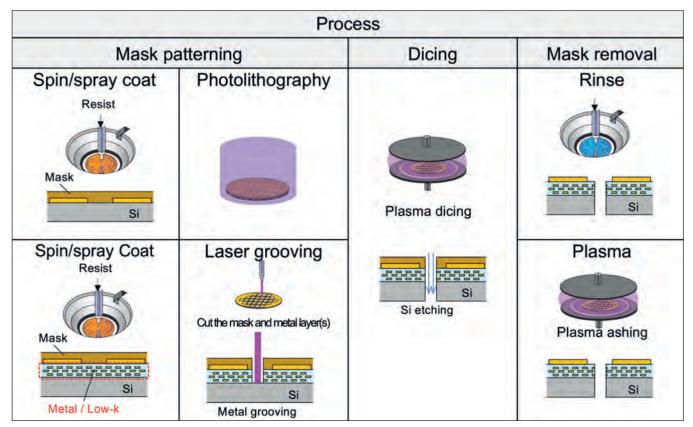

Now, a new dicing process has been introduced which uses a plasma chemical etching process, where all the 'cuts' are achieved in a single batch process, with no die stressing, no contamination, and an increase in wafer dicing throughput. Also, more chips can be designed onto the wafer as narrower dicing 'streets' can be used due to mask patterning. In addition, the

APX300 Plasma Dicer

### PLASMA DICING PANASONIC

mask pattern enables flexibility in the choice of chip sizes, shapes, positioning. The two approaches are shown in Figure 1.

Figure 2 shows Panasonic's plasma dicing process which uses a dicing mask. The plasma process etches the streets by chemical reaction. Plasma dicing uses pulsed or time-multiplexed etching, with the process cycling repeatedly between two phases: a nearisotropic plasma etch where ions attack the wafer in a near-vertical direction; followed by the deposition of a chemically inert passivation layer which protects the entire substrate from further chemical attack. During etching, the vertically-directed ions attack the passivation layer only at the bottom of the trench (not along the walls), exposing the substrate to the chemical etch. This two-phase process results in sidewalls that increase and decrease with an amplitude of between 100 and 500nm. The cycle time is adjustable: short cycles yield smooth walls; longer cycles yield a higher etch rate.

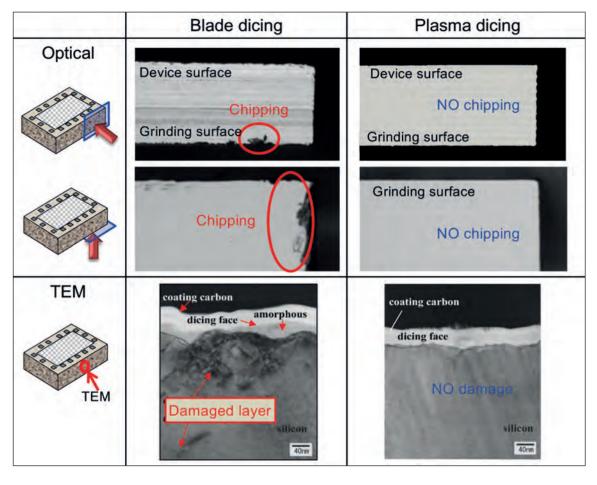

### Advantages of the plasma process over mechanical dicing

The action of the saw blade during the dicing process causes mechanical damage and affects inner layers of the die. Figure 3 demonstrates damage and chipping at the edge and of the inner layers. By contrast, the micro-photographs show no damage when the individual dies are separated using the plasma dicing process. Also, unlike blade dicing which causes micro particles of the wafer (e.g. silicon) to be freed up,

potentially causing devices to fail, by using plasma etching, no contaminating particles are released.

### Greater chip strength

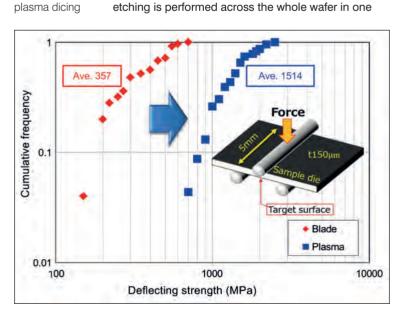

Chip breakage tests show the typical range of fracture strength for silicon chips to be in the range of 100MPa up to 3000MPa. Dies from several positions on a 150µm thick wafer were sampled and a Weibull plot was used to compare the statistical data for chip strengths of lots using blade and plasma dicing preparation methods. Figure 4 shows that the plasma dicing process results in chips that are about five times stronger than those which underwent blade dicing. With a fracture stress pressure of 600MPa, all samples of chips that had been processed using blade dicing broke due to internal micro-cracks, whereas all of the plasma diced chips shattered at a pressure close to the breaking-strength of silicon.

Figure 1. Blade Dicing & Plasma Dicing Processing

Figure 2. Panasonic's chemical etch dicing process

### PLASMA DICING PANASONIC

Figure 3. Damage evident on chip samples using blade dicing (left); none present when plasma dicing is used

Therefore the plasma dicing process is proven to result in dramatically higher chip strength, especially if thin wafers are being processed.

### Higher throughput and yield

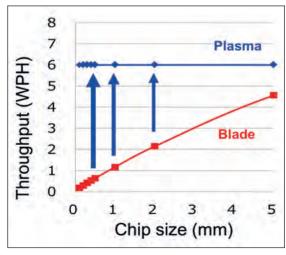

The processing time of blade dicing depends on the number of dicing lines. If the die size is small, longer dicing processing time is required and throughput is reduced. However, with the plasma dicing process, etching is performed across the whole wafer in one

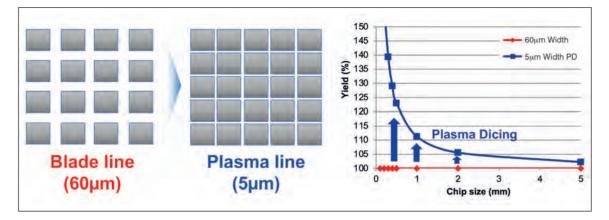

pass, so throughput remains constant, no matter how many dicing streets are required (see Figure 5). In addition, the plasma dicing process uses a narrower dicing street design. With blade dicing, there is always a minimum cutting street width, due to the thickness of the blade. A simulation prepared by Panasonic shows that for a 0.5mm<sup>2</sup> chip size, reducing the dicing street width from 60μm to 5 μm, yield will be increased by 23% using the new plasma process. (See Figure 6).

Figure 5. Productivity curves show increasing benefits with

Figure 4.

prove the

benefits of

Strength tests

WE MAKE

SURE POLICY

MAKERS

HEAR IT.

Learn how SEMI Advocacy represents the industry with governments worldwide.

We amplify the voices of individual members and transform them into policy positions. To explore the ways we advance the health and prosperity of the global electronics design and manufacturing supply chain, visit **semi.org/semiismore**.

**SEMIIS MORE**

### PLASMA DICING PANASONIC

Figure 6. reduced street widths result in more chips/ wafer

But how to avoid chips to contact others when handling wafer with 5 um dicing street width needs to be considered.

### Suitability for different wafer processes

The Panasonic plasma dicing process can be applied to wafer dicing with mask patterning either performed by photolithography or laser patterning methods. The appropriate process flow should be selected to fit the wafer design (Figure 7).

Plasma dicing is a high quality innovation which offers different benefits depending on the end application, as shown in Figure 8. In small chips, for example, RF ID tags, IoT devices or MEMS sensors, the ability to obtain a higher number of chips per wafer, plus the reduction in process time is paramount. For

devices such as image sensors, the elimination of contaminating particles is essential, and the smoother, damage-free sidewalls, with no heat-affected zones or cracking, allows an increase in the active area. For makers of memory ICs, the elimination of damage is most significant.

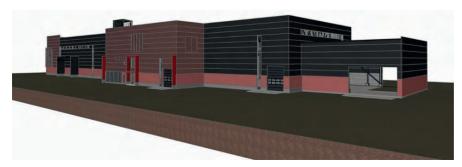

### Panasonic Demo Centre

In order to demonstrate the plasma dicing process, Panasonic has built a customer demonstration centre in Osaka, Japan. This Class 1000 facility is capable of processing 200mm and 300mm diameter wafers with a minimum thickness of 25µm. It is fully-equipped including two APX300 plasma dicing machines, laser patterning equipment, polish grinder, lithography and measurement equipment, enabling customers to quickly and thoroughly evaluate different products and materials.

| Appli-               | Chip            | Wafer Structure               | Process                   |                           |        |

|----------------------|-----------------|-------------------------------|---------------------------|---------------------------|--------|

| cation               | size            | vvaler Structure              | Mask formation            |                           | Dicing |

| loT<br>Small<br>Chip | Small<br>(~3mm) | Plasma Dicing                 | Photolith  Coat/Expo.     | Develop.                  | Plasma |

| Image<br>sensor      |                 | Mask Patterning  Metal/ Low-k | Mask<br>Coating<br>Resist | Laser                     | Plasma |

| lemory<br>/Logic     | Large<br>(3mm~) | Plasma Dicing                 | Spin or spray coating     | Cut mask &<br>Metal layer | Dicing |

Figure 7. Panasonic plasma dicing process Applications

# **ONLINE ROUNDTABLE**

- Based around a hot topic for your company, this 60-minute recorded, moderated zoom roundtable would be a platform for debate and discussion

- Moderated by an editor, this can include 3 speakers

- Questions would be prepared and shared in advance

- There would be an opportunity to view and edit out any unflattering bloopers

This event would be publicised for 4 weeks through all our mediums including:

- A banner on the Silicon Semiconductor homepage for 8 weeks 4x weekly dedicated HTMLs

- 4x news pieces which would also appear on the weekly e-newsletters

- Promoted through our social media platforms for 8 weeks (pre and post event)

- Available as an on-demand asset through all mediums

- All registered attendees' details would be made available to you

Contact: Jackie Cannon jackie.cannon@angelbc.com

Cost: £4995

| Target Application                                  | Blade Dicing<br>Issues  Wider dicing lane (W 60µm) | Benefits of using Plasma Dicing                            |                                 |                                                |

|-----------------------------------------------------|----------------------------------------------------|------------------------------------------------------------|---------------------------------|------------------------------------------------|

| 0.1 mm                                              |                                                    | Narrower lane<br>(W 5µm)<br>→ More chips<br>from a wafer   | Blade<br>\$\int_{60\text{pm}}\$ | Plasma                                         |

| IoT Small chip •RF-ID tag •Chip component •MEMS etc | Longer process<br>time in smaller<br>dies          | Shorter process time →lower COO                            | Line-by-line                    | Whole wafer                                    |

| Image Sensor                                        | Particle from<br>blading,<br>less yield            | Particle free<br>→improve yield                            | Blade NG chip                   | Plasma                                         |

| Memory CPU Memory                                   | Chipping/die<br>breakage<br>due to damage          | Damage free chip<br>obtained<br>→new value for<br>end user | Blade                           | Plasma  resting earlies  Along free  No damage |

Figure 8. Benefits of Plasma Dicing

### Conclusion

Panasonic's plasma dicing process achieves damagefree and particle-free dicing, resulting in inherently stronger chips and increased yield. Throughput is increased and production costs reduced. Figure 9 summarises the different dicing processes and the advantages of the plasma dicing process.

All the data in this white paper have been verified in Panasonic's Plasma Dicing Demo Centre in the company's Smart Factory Solutions facility in Osaka, Japan, using the APX300 plasma dicer. Panasonic are continuing to develop the plasma dicing process for other materials such as silicon carbide, gallium arsenide and gallium nitride as well as silicon dioxide.

### **Product Information**

Panasonic can provide a plasma dicing total solution to achieve a damage-free, particle free, higher throughput and lower overall cost of production.

Panasonic Industry Europe GmbH Caroline-Herschel-Strasse 100 85521 Ottobrunn, Germany

Tel. +49 89 45354-1000

microelectronics.sales@eu.panasonic.com http://pfse.panasonic.eu

|                                             | Blade               | Laser                    | Plasma                        |  |

|---------------------------------------------|---------------------|--------------------------|-------------------------------|--|

| Dicing method                               |                     |                          |                               |  |

| Processing time<br>(8"wafer, t 100µm, □1mm) | (32 min / wafer)    | (13 min / wafer)         | √ Shortest<br>(7 min / wafer) |  |

| Chip strength                               | (Mechanical damage) | √<br>(Mechanical damage) | ✓ Highest (Damage-free)       |  |

| Low-k etching                               | (Wet process)       | (Dry process)            | (Dry process)                 |  |

Figure 9. Summary comparison of dicing processes

**BUSINESS COMMUNICATIONS**

Specialists with 30 year+ pedigree and in-depth knowledge in these overlapping sectors:

Expertise: Moderators, Markets, 30 Years + Pedigree

**Reach:** Specialist vertical databases

**Branding:** Message delivery to high level influencers

via various in house established magazines,

web sites, events and social media

Power Electronics World

**Future Mobility**

Publications include: TaaS Technology, TaaS News

### **Data Centres**

Publications include: DCS Europe, DCS UK, SNS International

### SmartSolar UK & Ireland

**Publications include:** Solar and Power Management, Solar UK and Ireland

Publications include: Sensor Solutions Magazine, Sensor Solutions International

Publications include: Digitalisation World, Information Security Solutions, Managed Services

Publications include: PIC Magazine, PIC Conference

### **Expert Moderators**

Dedicated technical and time-served experts/editors

### **MARK ANDREWS**

Mark Andrews is technical editor of Silicon Semiconductor. PIC Magazine, Solar+Power Management, and Power Electronics World. His experience focuses on RF and photonic solutions for infrastructure, mobile device, aerospace, aviation and defence industries

### **JACKIE CANNON**

Director of Solar/IC Publishing, with over 15 years experience of Solar, Silicon and Power Electronics, Jackie can help moderate your webinar, field questions and make the overal experience very professional

### DR RICHARD STEVENSON

Dr Richard Stevenson is a seasoned science and technology journalist with valuable experience in industry and academia. For almost a decade, he has been the editor of Compound Semiconductor magazine, as well as the programme manager for the CS International Conference

### PHIL ALSOP

Journalist and editor in the business to business publishing sector for more than 30 years currently focusing on intelligent automation, DevOps, Big Data and analytics, alongside the IT staples of computing, networks and storage

### For more information contact:

6 Bow Court, Burnsall Road, Coventry, CV5 6SP. UK

### AEM HOLDINGS SINGAPORE

# System level test enables a paradigm shift for device manufacturers

According to research conducted by AEM Singapore, the semiconductor industry needs continuously improved faults coverage while reducing the overall costs of test and measurement operations to enable better, more efficient defects detection while improving quality and overall vield. BY STUART PEARCE. **AEM HOLDINGS, SINGAPORE**

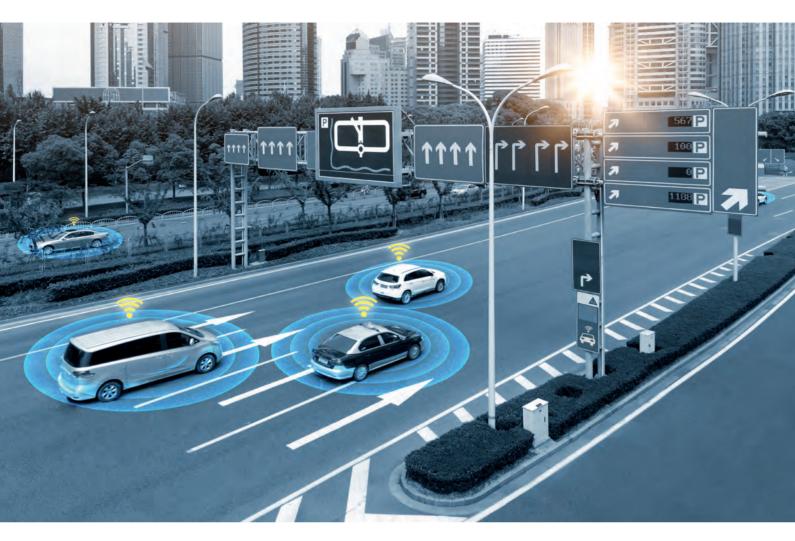

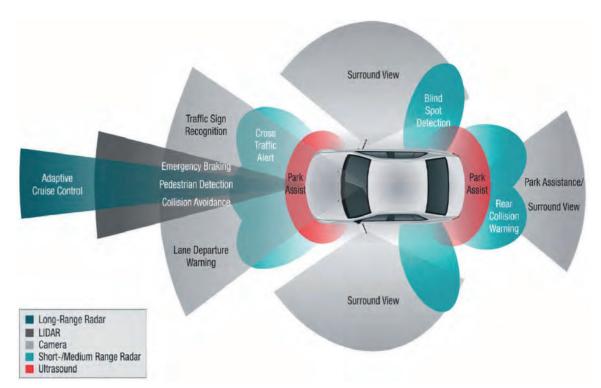

FAULTS COVERAGE is becoming more problematic as systems are getting more complex, heterogeneous and applications are more demanding. Applications such as self-driving cars, cloud servers, AI, industrial IOT or medical devices are now mission critical to many end use sectors, driving the need for low parts per billion (PPB) defect levels.

### Advanced Driver Assistance Systems (ADAS) and infotainment applications

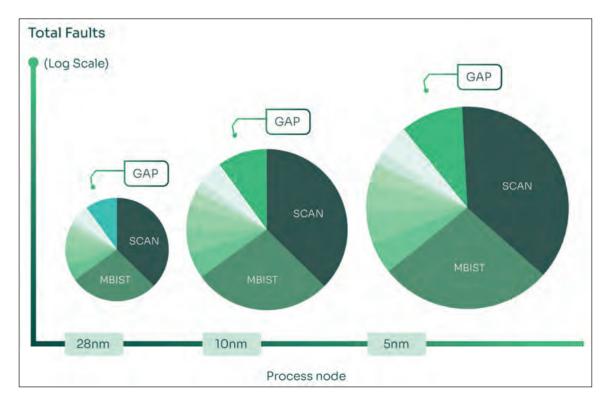

Semiconductors continue to follow Moore's Law regarding the doubling of transistors at every process node. While these leaps occurred previously in 18-24 month periods, the complexity of advanced nodes has made progress more challenging and time between nodes greater. As these new process nodes come to market, higher numbers of smaller transistors will

### **AEM HOLDINGS SINGAPORE**

Figure 1: As on-board automotive systems rely more heavily on semiconductor based system, the requirement for fast, accurate and costeffective testing increases

make it more difficult to catch defects, and will make test coverage more demanding.

For example, test coverage of 99.4% of an advanced node 300mm wafer still leaves 15 million transistors untested on a 2.5 billion transistor device. Time to market and time to revenue drives the need for shorter cycle time with increased faults coverage. System

level test in the customer application environment provides the ability to solve these challenges while providing an opportunity to significantly reduce overall cost of test.

### A New System Level Test Solution (AMPS)

AEM Singapore has developed a new system level test solution (AMPS) that leverages the knowledge

Figure 2: As transistor sizes decrease, more devices are squeezed into each wafer, creating complex test environments. Source: Qualcomm Mike Campbell

### AEM HOLDINGS SINGAPORE

Figure 3: Example of a testing scenario

and experience gained over the last decade in system level device handling for leading semiconductor companies. AMPS stands for Asynchronous, Modular Parallel and Smart as key parameters for system level testina.