VOLUME 44 ISSUE II 2023

AN ANGEL BUSINESS COMMUNICATIONS PUBLICATION

SILICONSEMICONDUCTOR.NET

#### **INSIDE**

News Review, Features News Analysis, Profiles Research Review and much more...

#### imec focuses on footprint reductions

imec, discusses the sustainability challenge facing the semiconductor industry with their Virtual Fab

#### Why 'silicon proven' is not what you think

The complexity of integrated circuit design has expanded a billion-fold since the invention of the first transistor

#### The perfect partner for wet process equipment?

AP&S International, discusses the company's batch processing, single wafer processing and support equipment technologies

# ACCELERATING HETEROGENEOUS INTEGRATION

- EV Group's Heterogeneous Integration Competence Center™ accelerates new product development fueled by heterogeneous integration and advanced packaging

- Wafer-to-Wafer (W2W) and Die-to-Wafer (D2W) hybrid bonding processes ready for sample test, product development and qualification

- Open access innovation incubator for EVG customers and partners across the microelectronics supply chain, guaranteeing the highest IP protection standards

- Combining EVG's world-class wafer bonding, thin-wafer handling and maskless, optical and nanoimprint lithography products and expertise, as well as pilot-line production facilities and services

## **VIEWPOINT**

By Phil Alsop, Editor

#### Short term pain, long term gain?

FOLLOWING ON from the optimism contained within the KPMG LLP and Global Semiconductor Alliance 19th annual global semiconductor industry survey, which I commented on in the last issue, we have a slightly less cheerful market assessment, courtesy of Gartner, which predicts an 11% decline in worldwide semiconductor revenue this year. In actual figures, this means that 2022's virtually \$600 billion USD total will shrink to \$532 billion in 2023. However, according to Gartner, 2024 promises to be quite some year revenue-wise, with a predicted 18.5% rise to a high of \$630.9 billion.

The cause of this revenue volatility? Chip over-supply resulting in price declines and, as Gartner puts it: "The past decades of high volume, high-dollar content market drivers are coming to an end, notably in the PC, tablet and smartphone markets where technology innovation is lacking."

Oh, and there's the small issue of techno nationalism to be addressed. Most obviously, this is manifested in the ongoing tension between China and the US, but plenty of countries (and the whole EU region) across the globe have decided that the business of semiconductors (and many other key manufacturing activities) is too important to be outsourced, hence the current major onshoring focus.

Whether or not the semiconductor supply chain is quite so enamoured of the geopolitics which puts pressure on who they can or cannot supply or what technology they may or may not supply, is less certain. After all, individual and even company to company relations tend to exist beneath the nationalist radar.

On the plus side, the need for the semiconductor supply chain to be much more flexible and responsive to changing market conditions means that, come 2024, it should be in a good place to meet what Gartner believes will be the twin positives of revenue recovery in the memory sector and growth in a whole range of smaller (compared to the PC, tablet and

smartphone one) end markets. These include the automotive, industrial, IoT and military and aerospace sectors. No mention is made of the quantum computing opportunity, but one presumes that this will begin to make an impact over the next few years.

Richard Gordon, Practice Vice President at Gartner, concludes: "End-market demand will be less exposed to consumer discretionary spending and more exposed to business capital spending. Supply chains will be more complex with many more intermediaries involved and varied channels to market, and to satisfy different end-market requirements, different types of capacity will be required."

In the same way that a small, but significant, pandemic silver lining was the way in which many businesses accelerated their digital transformation journeys, and the flexible, hybrid workplace became a reality (and a benefit) for many, so it just might be that the current semiconductor industry volatility and uncertainty leads to the emergence of a leaner, fitter, more flexible sector over the next few years.

I'll leave you with my favourite quote:

"In Italy for thirty years under the Borgias, they had

warfare, terror, murder, and bloodshed, but they

produced Michelangelo, Leonardo da Vinci, and the

Renaissance. In Switzerland, they had brotherly love,

they had five hundred years of democracy and peace,

and what did that produce? The cuckoo clock."

(To be fair to the Swiss, they also produced a banking industry of some note!).

#### 18 Virtual fab focuses on real carbon footprint reductions

Emily Gallagher, at imec, discusses the sustainability challenge facing the semiconductor industry and explains how imec's recently launched Virtual Fab is playing an important role in helping to improve both the understanding and development of environmentally friendly, patterning-related process solutions

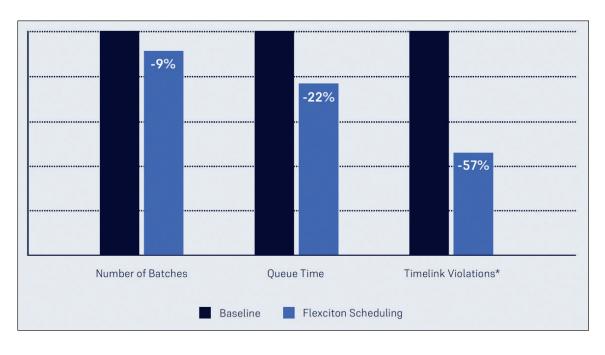

### 26 Fab scheduling is now so complex that it needs next-generation intelligent software

There are literally billions of possible ways to schedule all the work through a fab, so finding the best way is an immense challenge

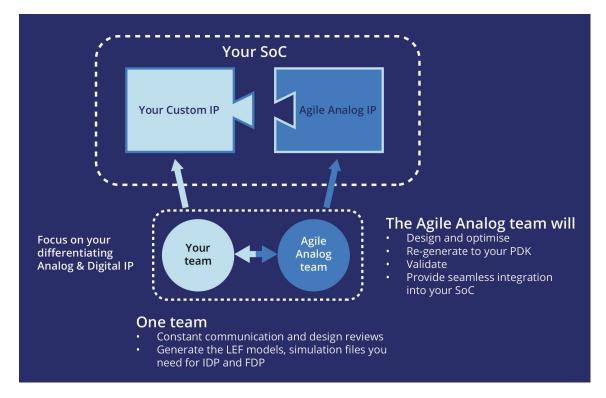

#### 36 Why 'silicon proven' is not what you think

Agile Analog's approach to analog IP design and quality

#### 30 New centre for semiconductor research in Dresden

With the establishment of the Center for Advanced CMOS & Heterointegration Saxony, the Fraunhofer Institute for Photonic Microsystems IPMS and the "All Silicon System Integration Dresden - ASSID "branch of Fraunhofer IZM are pooling their expertise in semiconductor research

#### 40 The perfect partner for wet process equipment?

Tobias Bausch, CMO & CTO at AP&S International, discusses the company's batch processing, single wafer processing and support equipment technologies, with the emphasis very much on continuous innovation to deliver cost-saving, operationally-optimised and sustainable customer solutions

#### **NEWS**

- **06** Hybrid approach best for chip innovation?

- 07 Gordon Moore, Intel Co-Founder, dies at 94

- **08** Top 10 foundry revenue falls by 4.7%

- 10 UMC circular economy & recycling innovation center breaks ground

- 11 New signs of price stability and improved availability

#### SEMI NEWS UPDATE

12 Industry hits record sales

Editor Phil Alsop Contributing Editor Richard Stevenson Sales & Marketing Manager Shehzad Munshi USA Representatives Tom Brun Brun Media

Publisher Jackie Cannon

Janice Jenkins Director of Logistics Sharon Cowley

Design & Production Manager Mitch Gaynor

jackie.cannon@angelbc.com phil.alsop@angelbc.com richard.stevenson@angelbc.com

shehzad.munshi@angelbc.com tbrun@brunmedia.com jjenkins@brunmedia.com sharon.cowley@angelbc.com

mitch.gaynor@angelbc.com

+44 (0)1923 690215 +001724539-2404 +001 724-929-3550 +44 (0)1923 690200 +44 (0)1923 690214

+44 (0)1923 690205

Chairman Stephen Whitehurst Chief Executive Officer Sukhi Bhadal Chief Technical Officer Scott Adams Directors Jackie Cannon, Sharon Cowley

E: info@angelbc.com

Published by Angel Business Communications Ltd. 6 Bow Court, Fletchworth Gate, Burnsall Road, Coventry CV5 6SP, UK T: +44 (0)2476 718 970

Angel 🔼

stephen.whitehurst@angelbc.com

sukhi.bhadal@angelbc.com

scott.adams@angelbc.com

+44 (0)2476 718970

+44 (0)2476 718970

+44 (0)2476 718970

Silicon Semiconductor is published five times a year on a controlled circulation basis. Non-qualifying individuals can subscribe at: £50.00 per annum (UK), €60.00 per annum ( Europe), \$90 per annum (air mail)(USA). Cover price £4.50. All information herein is believed to be correct at time of going to press. The publisher does not accept responsibility for any errors and omissions. The views expressed in this publication are not necessarily those of the publisher. Every effort has been made to obtain copyright permission for the material contained in this publication. Angel Business Communications Ltd will be happy to acknowledge any copyright oversights in a subsequent issue of the publication. Angel Business Communications Ltd © Copyright 2023. All rights reserved. Contents may not be reproduced in whole or part without the written consent of the publishers. The paper used within this magazine is produced by chain of custody certified manufacturers, guaranteeing sustainable sourcing. US mailing information: Silicon Semiconductor, ISSN 1096-598X, is published 5 times a year by Angel Business Communications Ltd, Unit 6, Bow Court, Fletchworth Gate, Burnsall Rd, Coventry CV5 6SP. UK. Airfreight and mailing in the USA by agent named World Container INC 150-15, 183rd St, Jamaica, NY 11413, USA. Periodicals Postage Paid at Brooklyn, NY 11256. POSTMASTER: Send address changes to Silicon Semiconductor, Air Business Ltd, c/o World Container INC 150-15, 183rd St, Jamaica, NY 11413, USA.

We strive for accuracy in all we publish; readers and contributors are encouraged to contact us if they recognise an error or omission. Once a magazine edition is published [online, in print or both], we do not update previously published articles to align old company names, branding, marketing efforts, taglines, mission statements or other promotional verbiage, images, or logos to newly created or updated names, images, typographic renderings, logos (or similar) when such references/images were accurately stated, rendered or displayed at the time of the original publication. When companies change their names or the images/text used to represent the company, we invite organizations to provide Angel Business Communications with a news release detailing their new business objectives and/or other changes that could impact how customers/prospects might recognise the company, contact the organisation, or engage with them for future commercial enterprise. Printed by: The Manson Group, ISSN 2050-7798 (Print) ISSN 2050-7801 (Online) © Copyright 2023

#### Hybrid approach best for chip innovation?

A ground-breaking Lam study featured in the journal Nature proves a human-machine hybrid model can cut the cost of process development by 50 percent and accelerate time-to-market

IN A NEW STUDY, Lam Research Corp. examined the potential for the use of artificial intelligence (AI) in process development for chip fabrication, today a human-driven step that is essential for the mass production of every new advanced semiconductor in the world.

As the semiconductor market progresses towards \$1 trillion in annual revenue by 20301 according to experts, the study, recently published in the journal Nature, identifies an opportunity to address two grand challenges facing the industry: reducing development costs and accelerating the pace of innovation to meet the increasing demand for next-generation chips. The study found that a "human first, computer last" approach can reach process engineering targets dramatically faster and at half the cost compared to today's approach.

"New approaches in innovation are needed to enable the industry to scale fast enough to meet the data-driven world's evolving demand for nextgeneration chips," said Tim Archer, president and chief executive officer at Lam Research. "The opportunity for greater collaboration between talented engineers and machines in process engineering highlighted in Lam's study in Nature is a potential game-changer for our customers and our industry at large. This research is a testament to Lam's more than 40-year heritage of industry leadership and semiconductor manufacturing innovation. I congratulate the Lam team on this exciting work."

The rising complexity of nextgeneration chips continues to drive process development to be more challenging and expensive. Seeking a more efficient approach, researchers at Lam put talented process engineers head-to-head against Al-enabled computer algorithms in the study. To manufacture every chip or transistor designed, experienced and skilled engineers must first create a

specialized recipe that outlines the specific parameters and permutations needed for each process step.

Hundreds of steps are required to build these nanometer-sized devices on a silicon wafer. Process steps typically include multiple instances of depositing thin layers of materials onto silicon wafers and etching away excess material with atomic-scale precision. This essential phase of semiconductor development is currently done by human engineers, largely using their intuition and a "trial and error" approach. With every recipe unique to the chip design and more than 100 trillion possible options to incorporate, process development can be laborious, time-intensive, and costly - increasingly slowing down the time needed to achieve the next technology breakthrough.

In the Lam study, machine and human participants competed to create a targeted process development recipe at the lowest cost, weighing a variety of factors associated with test batches, metrology and overhead expenses. The study concluded that while humans excelled in solving challenging and out-of-the-box problems, a hybrid human first, computer last strategy can help address the tedious aspects of process development and, ultimately, speed up

process engineering innovation.

"Although critical to the creation of each and every chip produced, the plasma physics of process engineering has been for decades rooted in the same scientific approach that Thomas Edison used: trial and error," said Rick Gottscho, executive vice president and strategic advisor to the CEO – Innovation Ecosystem at Lam Research and co-author of the study. "Our research showed that while engineering talent remains essential to innovation, process engineering costs can be reduced by 50 percent by integrating AI at the right stage and with the right data. The study provides a prescriptive approach for bringing together the best of human-led engineering and the best of what data science and machines offer to create a combination that performs better than either one alone. If realized, this hybrid approach can lead to significant savings in both dollars and engineering time for the industry."

Lam is currently incorporating the key learnings from the study into its development operations. The Lam study provides initial guidance on how to successfully integrate human knowledge, skill and experience with Al's ability to rapidly assess numerous possible combinations in process engineering.

#### Gordon Moore, Intel Co-Founder, dies at 94

Moore, who set the course for the future of the semiconductor industry, devoted his later years to philanthropy

INTEL and the Gordon and Betty Moore Foundation have announced that company co-founder Gordon Moore has passed away at the age of 94. The foundation reported he died peacefully on Friday, March 24, 2023, surrounded by family at his home in Hawaii.

Moore and his longtime colleague Robert Noyce founded Intel in July 1968. Moore initially served as executive vice president until 1975, when he became president. In 1979, Moore was named chairman of the board and chief executive officer, posts he held until 1987, when he gave up the CEO position and continued as chairman. In 1997, Moore became chairman emeritus, stepping down in 2006.

During his lifetime, Moore also dedicated his focus and energy to philanthropy, particularly environmental conservation, science and patient care improvements. Along with his wife of 72 years, he established the Gordon and Betty Moore Foundation, which has donated more than \$5.1 billion to charitable causes since its founding in 2000.

"Those of us who have met and worked with Gordon will forever be inspired by his wisdom, humility and generosity," reflected foundation president Harvey Fineberg. "Though he never aspired to be a household name, Gordon's vision and his life's work enabled the phenomenal innovation and technological developments that shape our everyday lives. Yet those historic achievements are only part of his legacy. His and Betty's generosity as philanthropists will shape the world for generations to come."

Pat Gelsinger, Intel CEO, said, "Gordon Moore defined the technology industry through his insight and vision. He was instrumental in revealing the power of transistors, and inspired technologists

and entrepreneurs across the decades. We at Intel remain inspired by Moore's Law, and intend to pursue it until the periodic table is exhausted. Gordon's vision lives on as our true north as we use the power of technology to improve the lives of every person on Earth. My career and much of my life took shape within the possibilities fueled by Gordon's leadership at the helm of Intel, and I am humbled by the honor and responsibility to carry his legacy forward."

Frank D. Yeary, chairman of Intel's board of directors, said, "Gordon was a brilliant scientist and one of America's leading entrepreneurs and business leaders. It is impossible to imagine the world we live in today, with computing so essential to our lives, without the contributions of Gordon Moore. He will always be an inspiration to our Intel family and his thinking at the core of our innovation culture."

Andy Bryant, former chairman of Intel's board of directors, said, "I will remember Gordon as a brilliant scientist, a straight-talker and an astute businessperson who sought to make the world better and always do the right thing. It was a privilege to know him, and I am grateful that his legacy lives on

in the culture of the company he helped to create."

Prior to establishing Intel, Moore and Noyce participated in the founding of Fairchild Semiconductor, where they played central roles in the first commercial production of diffused silicon transistors and later the world's first commercially viable integrated circuits.

The two had previously worked together under William Shockley, the co-inventor of the transistor and founder of Shockley Semiconductor, which was the first semiconductor company established in what would become Silicon Valley. Upon striking out on their own, Moore and Noyce hired future Intel CEO Andy Grove as the third employee, and the three of them built Intel into one of the world's great companies. Together they became known as the "Intel Trinity," and their legacy continues today.

In addition to Moore's seminal role in founding two of the world's pioneering technology companies, he famously forecast in 1965 that the number of transistors on an integrated circuit would double every year – a prediction that came to be known as Moore's Law. "All I was trying to do was get that message across, that by putting more and more stuff on a chip we were going to make all electronics cheaper," Moore said in a 2008 interview.

With his 1965 prediction proven correct, in 1975 Moore revised his estimate to the doubling of transistors on an integrated circuit every two years for the next 10 years. Regardless, the idea of chip technology growing at an exponential rate, continually making electronics faster, smaller and cheaper, became the driving force behind the semiconductor industry and paved the way for the ubiquitous use of chips in millions of everyday products.

#### Top 10 foundry revenue falls by 4.7%

According to TrendForce's latest survey of the global foundry market, electronics brands began adjusting their inventories in 2Q22, but foundries were unable to rapidly adapt to this development because they reside in the more upper portion of the supply chain

MOREOVER, revising procurement quantities of long-term foundry contracts takes time as well. Hence, only some tier-2 and -3 foundries were able to immediately respond to the changes in their clients' demand. Also, among them, 8-inch wafer foundries made a more pronounced reduction in their capacity utilization rates.

As for the remaining foundries, the downward corrections that they made to their capacity utilization rates did not become noticeable until 4Q22. Hence, in 4Q22, the quarterly total revenue of the global top 10 foundries registered a QoQ decline for the first time after 13 consecutive quarters of positive growth. The quarterly total revenue of the top 10 foundries came to US\$33,530 million, reflecting a drop of 4.7% from 3Q22. Moving into 1Q23, TrendForce projects that the quarterly total revenue of the top 10 will show an even steeper drop on account of seasonality and the uncertain macroeconomic situation.

Although TSMC and GlobalFoundries actually managed to raise revenue market share in 4q22, top five foundries all inevitably faced massive reduction in orders.

In 4Q22, foundries' revenues were affected by an underwhelming peak season and their customers' inventory corrections. Even with stock-up activities related to new iPhones and Android smartphones, TSMC still posted a QoQ drop of 1.0% in revenue to reach US\$19,962 million. However, TSMC's revenue market share climbed to almost

60% mainly because tier-2 and -3 foundries took a heavier hit with respect to customers' inventory corrections. Competitors' weaker performances thus allowed TSMC to gain market share. Regarding the revenues from TSMC's process technologies, the decline in the revenues from the 7/6nm nodes was mostly offset by the rise in the revenues from the 5/4nm nodes. The share of the ≤7nm nodes in TSMC's overall revenue remained stable at 54%.

Turning to Samsung, it experienced a drop in orders for advanced processes and a general demand contraction as its customers were concentrating on inventory reduction. However, the demand drop associated with these factors was marginally offset by stock-up activities related to the components for the new iPhones and Android smartphones. All in all, Samsung posted a QoQ drop of 3.5% in foundry revenue to reach US\$5,391 million for 4Q22. TrendForce also points out that Samsung has lost a significant amount of demand for its ≤7nm nodes as Qualcomm and NVIDIA made the decision to reallocate orders for chips used in flagship hardware products.

Currently, there are no new major customers that can effectively address the idling production capacity caused by the order reallocation. Therefore, the utilization rates of Samsung's advanced processes are projected to remain at a low level of around 60% through 2023. In sum, Samsung lacks the momentum to achieve a positive YoY revenue growth for this year.

Regarding other the major foundries, UMC saw a drop in both capacity utilization rate and wafer shipments in 4Q22, so its revenue fell by 12.7% QoQ to US\$2,165 million. In the aspect of wafer size and process technology, UMC saw a QoQ revenue decline for both 12- and 8-inch wafer foundry services, and its 0.35/0.25µm nodes

had the worse revenue performance with a QoQ decline coming to 47%. Conversely, in the case of GlobalFoundries, its revenue actually rose by 1.3% QoQ to US\$2,101 million thanks to the optimization in its ASP and product mixes, as well as an increase in revenue from its non-wafer business. GlobalFoundries was the only one among the top 10 to record a positive QoQ growth, and its revenue market share also climbed to 6.2%. Turning to SMIC, it also saw a drop in both wafer shipments and wafer ASP. As a result, its revenue slid by 15.0% QoQ to US\$1,621 million. Looking at SMIC's revenue by application or production category, the sharpest drops were experienced by chips related to smart home and consumer electronics. To get its customers to raise wafer input, SMIC has been offering price concessions.

However, this aggressive pricing strategy has not been particularly effective as customers are concerned about the risks associated with the US-China trade dispute. Therefore, SMIC's capacity utilization rate and revenue are expected to shrink further in 1Q23.

TrendForce notes that the extent of the impact from order cuts varied for individual foundries in 4Q22. Consequently, there were two notable changes in the quarterly revenue ranking from sixth to 10th place. First, Nexchip fell out of the top 10 group and will unlikely return in the short term. DB Hitek filled in the 10th place vacated by Nexchip in 4Q22. However, its capacity utilization rate dropped to 80-85% due to the recent market downturn. DB Hitek posted a QoQ drop of around 12.4% in revenue to reach US\$292 million. Second, Tower, which was in ninth place in the 3Q22 ranking, benefited from the stable demand for chips based on specialty process technologies and a relatively steady flow of orders from European clients during 4Q22.

# All Systems.

**OUR FLAGSHIP SOLSTICE PLATFORM** delivers best-in-class performance at an unmatched price/performance ratio. Our highly flexible platform can be customized for a comprehensive range of semiconductor packaging applications for advanced device manufacturing including VCSELs, microLEDs, RF and power semiconductors.

#### GO NOW, GO SOLSTICE

- Advanced performance with maximum throughput and wafer uniformity

- Flexible, scalable platform for multiple applications on a single, compact system

- Elegant and simple design, easier to use, operate and maintain

- · Engineered for reliability and uptime

- Unparalleled cost-efficiency and ROI

YOU SEEK WORLD-CLASS

MANUFACTURING EQUIPMENT

TO MAKE YOUR FAB GO. WE

CREATED SOLSTICE TO MAKE

YOUR DECISION EASY.

REACH OUT - WE'RE READY.

TEL: +1 406 407 7814 info@ClassOne.com

## UMC circular economy & recycling innovation center breaks ground

The first R&D center for waste recycling in the Southern Taiwan Science Park

UNITED MICROELECTRONICS CORPORATION recently held a groundbreaking ceremony for its Circular Economy & Recycling Innovation Center, which will be established at its Fab 12A in Tainan, Taiwan.

The NT\$1.8 billion (US\$58.8 million) facility will be the first waste recycling R&D center in the Southern Taiwan Science Park, serving as an important contributor for sustainable circular economy in Taiwan. After the center begins operating in 2025, it is expected to reduce 15,000 metric tons of semiconductor manufacturing waste annually.

"UMC has invested in Taiwan for more than four decades, including in our flagship Fab 12A, the manufacturing and R&D hub for our specialty process technologies. While we have continued to pursue capacity expansions and enhance our R&D capabilities, UMC is also deeply committed to our corporate sustainability goals. The Circular Economy & Recycling Innovation Center will serve as the center of our efforts to maximize resource recovery and minimize waste," said SC Chien, UMC's Co-President and Chief Sustainability Officer. "Working hand in hand with our value chain partners, we believe we can raise the bar for circularity in Taiwan, and enhance our industry's competitiveness through sustainable practices."

In the first phase, UMC's Circular Economy & Recycling Innovation Center will process waste produced during IC manufacturing processes into products that can be reused or sold, such as turning liquid waste and sludge into industrial-grade products. As for waste solvents that cannot be purified, the thermal cracking process will be applied to produce fuel gas to be

reused within the facility. In the second phase, the Center will further develop thermal cracking technology that can directly convert waste solvents and plastics into energy supply.

Once operational, the facility is expected to reduce waste from UMC's Taiwan fabs by one-third, and create around NT\$100 million worth of value-added products.

UMC has invested in a number of circular economy initiatives over the years, such as decreasing outsourced waste disposal by promoting resource reuse within its fabs.

Estimated to lower carbon emissions by around 5,000 tons per year, this program reduces the need for waste transportation and raw material mining, while also mitigating the risks of transporting waste to external facilities.

In addition, Fab 12A has introduced an electrolysis process to convert

copper sulfate liquid waste into copper tubes with re-sale value, expected to generate more than NT\$13 million of revenue per year. Anther initiative in progress is the recycling of used photomasks, which are cleaned on-site to remove patterning and resold as quartz substrates for optical products.

With a total floor area of around 9,000 square meters, the Circular Economy & Recycling Innovation Center is designed in compliance with green building codes, and will also act as an education center to promote circular economy and environmental protection to the young generation.

Using this center as a base, UMC will work closely with waste management service providers and raw material suppliers to develop innovative recycling methods and projects, contributing to a better, more sustainable future through collaborations together with value chain partners.

#### Signs of price stability and improved availability

Complexity, uncertainty, and unevenness persist, driving need for the power of intelligence

SUPPLYFRAME'S latest Commodity IQ insights reveal positive signs for a normalized supply-demand balance and reduced pricing and availability challenges as we advance into the new year. Excluding memory devices, 85% of semiconductor pricing dimensions will be stable and the remainder will move squarely in favor of buyers for the second half of 2023. But Supplyframe Commodity IQ indicates that extended lead times for semiconductors, including programmable logic devices and passive components like automotivespecific resistors, will continue into the second half of the year.

"New Commodity IQ insights, the resilience of world economies to inflation and threats of recession, and China's reopening economy in the second half suggest there is reason to be optimistic. Commodity IQ indicates that component availability has largely improved, and prices across many commodities and sub-commodities have stabilized," said Supplyframe CEO and founder Steve Flagg. "But electronic component lead times remain longer than historical norms. Component lead times are improving faster than prices as demand in some markets deteriorates. And in this age of macroeconomic uncertainty, where it is becoming increasingly difficult to forecast demand amid mixed end-market signals, further intensification of the Russia-Ukraine war, continuing COVID-19 challenges in China or any number of other disruptions could emerge."

Supplyframe Commodity IQ is a transformed approach to electronics supply chain sourcing and analysis that provides unique, predictive, and prescriptive intelligence for electronic components, systems, and associated commodities based on operational analytics. This always-on software-as-aservice solution from Supplyframe pairs expert analysis and context with global

electronics design, demand, pricing, lead time, and inventory indices to help companies connect the dots.

For the first quarter of 2023,

Commodity IQ forecasts indicate

the global market will experience

an 8% decline in the number of

rising lead times and commodities

with part allocations for active and

passive components. According to

the Commodity IQ Price Index for Q1,

the number of component pricing

dimensions will decrease by 14%. And

global electronic component demand

and sourcing activities quarter-onquarter in the first quarter

of this year are

expected to be down by 2%, while engineering design will be off by 20% – further evidence of demand erosion.

While there are bloated inventories for components like memory and small case-size ceramic capacitors, automotive-grade microcontrollers, and FPGAs remain far below the Commodity IQ Inventory Index baseline. And analog integrated circuits (ICs), microcontrollers, and discrete ICs (especially power MOSFETs) will remain constrained and costly in the first quarter and beyond.

In the third quarter of 2023, global lead times for all electronic components will ebb dramatically as compared to the third quarter of 2022. Commodity IQ projects that nearly 60% of lead time dimensions will decrease in the third quarter versus 1% in the third quarter of 2022, with none expected to increase in the third quarter compared to a massive 73% in the same quarter of 2022. But Commodity IQ expects extended lead times to endure into

the second half for semiconductors, including programmable logic devices and passive components like automotive-specific resistors.

Despite inventory reductions that will likely be complete by the end of the first half, IC orders, wafer starts, and capacity utilization will begin to rise and memory pricing will reach its bottom in the second half of this year. The company forecasts that DRAM prices will commence recovery in the third quarter, and NAND pricing will follow in the fourth quarter or early in 2024.

Following seasonal trends, global

demand activities increased by 7% monthover-month

in January, with all

regions rising except Asia, which declined by 14% from December to January on general economic weakness and the Chinese Lunar Holiday. In the Europe/Middle East/ Africa region, growth was driven by significant sourcing action increases in Germany (44%), France (37%), Italy (32%), Israel (15%), and the United Kingdom (55%). Month-over-month through January in these countries, transistors, including constrained IGBTs, rose sharply by 68%, microcontrollers and microprocessors climbed by 34%,

The Commodity IQ global electronic component demand forecast is for a weaker first half in 2023, compared to 2022, with Q1 anticipated to grow just 1% versus Q4 2022. Given automotive and industrial component order optimism and a resilient macroeconomic outlook, Supplyframe projects an overall demand rebound commencing in the second half of the year.

capacitors expanded by 30%, and diodes were up by nearly 40%.

#### Industry hits record sales

Worldwide sales of semiconductor manufacturing equipment increased 5% from \$102.6 billion in 2021 to an all-time record of \$107.6 billion last year, SEMI has reported. The data is now available in the Worldwide Semiconductor Equipment Market Statistics (WWSEMS) Report.

FOR THE THIRD consecutive year, China remained the largest semiconductor equipment market in 2022 despite a 5% slowdown in the pace of investments in the region year over year, accounting for \$28.3 billion in billings. Taiwan, the second-largest destination for equipment spending, recorded an increase of 8% to \$26.8 billion, marking the fourth straight year of growth for the region. Equipment sales to Korea contracted 14% to \$21.5 billion.

Annual semiconductor equipment investments in Europe surged 93%, while North America logged a 38% increase. Sales to the Rest of World and Japan increased 34% and 7% year over year, respectively.

"The record high for semiconductor manufacturing equipment sales in 2022 stems from the industry's drive to add the fab capacity required to support long-term growth and innovations in key end markets including high-performance computing and automotive," said Ajit Manocha, SEMI president and CEO. "Additionally, the results reflect investments and

determination across regions to avoid future semiconductor supply chain constraints like those that surfaced during the pandemic."

Global sales of wafer processing equipment rose 8% in 2022, while other front-end segment billings grew 11%. After robust growth in 2021, assembly and packaging equipment sales decreased 19% last year while total test equipment billings contracted 4% year over year.

Compiled from data submitted by members of SEMI and the Semiconductor Equipment Association of Japan (SEAJ), the WWSEMS Report is a summary of the monthly billings figures for the global semiconductor equipment industry.

#### Fab equipment spending on track for 2024 recovery

Global fab equipment spending for front-end facilities is expected to decrease 22% year-over-year (YoY) to US\$76 billion in 2023 from a record high of US\$98 billion in 2022 before rising 21% YoY to US\$92 billion in 2024 to reclaim lost ground, SEMI announced

in its latest quarterly World Fab Forecast report.

The 2023 decline will stem from weakening chip demand and higher inventory of consumer and mobile devices. Next year's fab equipment spending recovery will be driven in part by the end of the semiconductor inventory correction in 2023 and strengthening demand for semiconductors in the high-performance computing (HPC) and automotive segments.

"This quarter's SEMI World Fab Forecast update offers our first look ahead to 2024, highlighting the steady global expansion of fab capacity to support future semiconductor industry growth driven by the automotive and computing segments and a host of emerging applications," said Ajit Manocha, SEMI president and CEO. "The report points to a healthy 21% uptick in equipment investment next year."

Taiwan is expected to retain the global lead in fab equipment spending in 2024 with US\$24.9 billion in investments, a 4.2% YoY increase, followed by Korea at US\$21 billion, a YoY 41.5% jump. While China is forecast to place third in equipment spending worldwide in 2024, U.S. export controls are expected to limit the region's spending to US\$16 billion, comparable to the region's investments in 2023. The Americas is expected to remain the fourth largest region in spending with a record US\$11 billion in investments in 2024, a 23.9% YoY increase. Europe & Mideast is also forecast to log record investments next year, increasing spending by 36% to US\$8.2 billion. Fab equipment spending in Japan and Southeast Asia is expected to increase to US\$7.0 billion and US\$3.0 billion, respectively, in

#### Foundry Segment Continues to Lead Semiconductor Industry Expansion

Covering 2022 to 2024, the SEMI World Fab Forecast report shows the global semiconductor industry increasing capacity by 4.8% this year after a 7.2% rise in 2022. Capacity growth is expected to continue in 2024, rising 5.6%.

With more suppliers providing foundry services to increase global capacity, the foundry segment is expected to lead the semiconductor expansion in 2023 with US\$43.4 billion in investments, a 12.1% YoY decline, and US\$48.8 billion, a 12.4% increase, in 2024. Memory is forecast to place second in global spending in 2023 despite a 44.4% YoY decline to US\$17.1 billion, with investments rising to US\$28.2 billion next year.

Unlike other segments, analog and power will see a steady expansion with a forecast spending increase of 1.3% to US\$9.7 billion in 2023 on the strength of stable growth in the automotive market. Investments by the segment are expected to remain flat next year.

The latest update of the SEMI World Fab Forecast report, published in March, lists 1,470 facilities and lines globally, including 142 volume facilities and lines with various probabilities that are expected to start production in 2023 or later.

#### SEMI wins skills funding

SEMI Europe, as the lead of a new 18-partner consortium, has won up to €4 million in funding to develop the European Chips Skills Academy, an initiative to help tackle the skills and talent shortages in Europe's electronics industry and propel its long-term growth.

The initiative is backed by more than 30 partner research organizations, vocational and education training providers, certification agencies and industry stakeholders.

The European Chips Skills Academy will expand on the Microelectronics Pact for Skills and the EU Chips Act to support the microelectronics ecosystem in Europe to attract new talent. The academy will deliver

#### Annual Billings by Region in Billions of U.S. Dollars with Year-Over-Year Change Rates

#### **Region 2022 2021 % Change**

| Total         | 107.64 | 102.64 | 5%   |

|---------------|--------|--------|------|

| Rest of World | 5.95   | 4.44   | 34%  |

| Europe        | 6.28   | 3.25   | 93%  |

| Japan         | 8.35   | 7.80   | 7%   |

| North America | 10.48  | 7.61   | 38%  |

| Korea         | 21.51  | 24.98  | -14% |

| Taiwan        | 26.82  | 24.94  | 8%   |

| China         | 28.27  | 29.62  | -5%  |

Sources: SEMI (www.semi.org) and SEAJ (www.seaj.or.jp), April 2023

Note: Summed subtotals may not equal the total due to rounding.

targeted European-wide training in key microelectronics fields such as automotive and additive manufacturing.

The grant, provided by the European Commission's Erasmus+ Programme, will fund the academy for four years. The European Chips Skills Academy is the second phase of the Microelectronics Training, Industry and Skills (METIS) consortium. Both initiatives are designed to foster microelectronics industry collaboration with key education, training and certification providers to address the skills shortage and European competitiveness.

"The pan-European alliance guiding the European Chips Skills Academy will leverage the diverse and considerable strengths of its many partners from across the microelectronics' ecosystem and industrial value chain," said Ajit Manocha, president and CEO of SEMI. "The project aims to bring greater strategic foresight to the evolution of professions and skills in the industry by applying evidence-based, datadriven success metrics to workforce development."

"Rapid semiconductor industry growth in Europe and around the globe in the years ahead necessitates that we quickly scale up the region's training efforts and drive greater cohesion of skills strategies across Europe to meet demand for the qualified workers required to sustain innovation and growth," said Laith Altimime, president of SEMI Europe. "The European

Chips Skills Academy will be the first decentralized microelectronics skills provider in Europe to help overcome this critical workforce development challenge."

Expected to begin work in autumn 2023, the European Chips Skills Academy consortium consists of the following organizations:

- Asociación Nacional de Centros con Certificados de Profesionalidad (ANCCP) - Spain

- Association for European NanoElectronics Activities (AENEAS)

France

- Budapest University of Technology & Economics (BME) - Hungary

- O DECISION Etudes & Conseil France

- Dresden University of Technology (TU Dresden) - Germany

- Graz University of Technology (TU Graz) - Austria

- Infineon Technologies Austria

- Information Centre on Academic Mobility and Equivalence (CIMEA) -Italy

- Innovazione Apprendimento Lavoro Friuli Venezia Giulia (IAL-FVG) - Italy

- Interuniversity Microelectronics

Centre (imec) Belgium

- O Knolyx Romania

- O Melexis Belgium

- Okmetic Finland

- Platform Talent voor Technologie (PTVT) / European STEM coalition -Netherlands

- SEMI Europe Germany

- Silicon Saxony Germany

- Technical University of Ostrava (VSB)Czechia

- Tyndall National Institute Ireland.

# Government support for the microchip industry – a perspective from Flanders

Over many decades the US, EU and UK have all been reliant on microchips from Taiwan and China. In that time technology has made the product as critical to our daily lives as oil has been since the 1950s. More recently there have been increasing concerns about that reliance and a growing belief that the west should be self-sufficient.

BY JAN WAUTERS, SCIENCE AND TECHNOLOGY COUNSELOR AT FLANDERS INVESTMENT & TRADE (AN OFFICIAL BODY OF THE GOVERNMENT OF FLANDERS).

IN RESPONSE, the U.S. and EU have announced multibillion-dollar packages aimed at boosting domestic chip production, but that's not happening in the UK. Many in the industry are pleading with the Government for subsidies amid fears that some chip firms will be forced to move overseas due to the innate lack of competitiveness of the UK industry. Do subsidies work? What is the long-term impact of subsidies? What other factors influence their success?

Flanders is a leading destination for the development of next-generation semiconductors. The region is home to three major strategic research centres and a further five research institutes with dedicated microelectronics, nanotech and semiconductors departments. The region is cultivating a vibrant ecosystem supporting semiconductor innovation. On the private innovation side, four semiconductor startups have raised six rounds of investment between them in the last 18 months.

This is underpinned by a substantial public budget for research and innovation. Of all EU member states, Belgium gives the highest net subsidies to support the business world in terms of innovation, employment and more. The Flemish government made an initial investment of €62m to help found Imec in 1984 and continues to support research centres to this day. Imec has since become a global leader in R&D, and in the translation of that innovation into industry. How has that happened? What has been the role of the public subsidies in this?

#### Background - The history

It is useful to first explain the context to how and why Flanders made the decisions they did. In the 1980s, Belgium introduced major constitutional reforms which gave Flanders, the northern region, far greater autonomy and with it the ability to promote itself as an industrial, entrepreneurial, and technological powerhouse.

The Flemish government took this opportunity to develop a clear vision, which became known as the 'DIRV' program or Third Industrial Revolution. The aim was for Flanders to be a pioneer in the European knowledge society and economy. A key part of the strategy was to boost the region's ability to innovate, develop its knowledge base and focus on its strengths. It made major strategic investments in a number of key sectors with a focus on renewal and re-enforcement of industrial ecosystems in new materials and micro-electronics.

One unique aspect of this is that, despite many changes of government in the last 40 years, the focus has never changed. The grants have been reviewed every five years, and each time the funding has been maintained. In 2022 the Government of Flanders committed to putting innovation at the centre of its strategy for recovery following the pandemic and allocated an additional €100 million from the recovery provision for companies' R&D projects. An additional €60 million from the recovery provision will be used to strengthen the research field and accelerate R&D.

#### R&D in Flanders – An overview

Gross domestic expenditure on R&D is comparatively high in Flanders. The equivalent of 3.3% of the region's GDP is invested in R&D (2019), which makes the region an outlier in the EU and a reputed knowledge hub in Europe.

In 1984, the University of Leuven (KU Leuven), wanted to launch a microelectronics research and development (R&D) 'superlab' in order to enter, what was then, a new chip-based industrial revolution. However, the funding required to pay for the advanced equipment needed was challenging for the university to manage alone. They needed significant investment. That came from the Flemish Government. In 1984, as part of their new vision, the Government made an initial investment of €62m to help found imec, as a spin-off from KU Leuven.

Imec brought R&D in advanced microelectronics technologies into one center, creating a central hub, where the level of investment needed for state-of-the-art cleanrooms could be concentrated.

Imec is now Europe's largest independent research and training centre and boasts highly-specialised expertise in microelectronics and nanotechnology for applications in the ICT, automotive, health, food and materials sectors – and beyond. Its nanotech R&D activities include:

- nano-CMOS and novel devices for nanoelectronics, micro- and nanoelectromechanical systems (MEMS and NEMS);

- o nanomaterials and nanopatterning;

- nanoprobes, surface functionalization and selfassembly;

- molecular interconnects for molecular electronics and bioelectronic circuits.

120 unique spin-offs have been established from imec. A recent example is Azalea Vision, which has produced a smart artificial lens for the human eye. In addition to the creation of imec, we also have the Strategic Research Center for Life Sciences and Biotechnology (VIB), with headquarters in Ghent. VIB works closely with Flanders' universities to unite the strengths of various research teams into a single institute for life sciences and biotechnology. VIB and imec set up the Neuro-Electronics Convergence laboratory together. Located at imec, this unique R&D facility is home to multidisciplinary tools for:

- semiconductor processing;

- nanotechnologies;

- biosensor fabrication:

- o cell culture:

- molecular biology;

- electrophysiology;

- o and more.

Between 1984 and 1999, international technology fairs were organised by the newly established Flanders Technology. The aim of these fairs was to position Flanders as a national and international innovation hub. They promoted innovation, entrepreneurship and economic growth by supporting the development and commercialisation of new technologies. Flanders also has a minority stake in imec.xpand, the independently managed investment fund of approx. €117 million that takes participations in promising nanotech companies. The Flemish Government committed €30 million in capital to a second xpand fund.

#### The ecosystem

Flanders leveraged imec and maximized the economic development benefits coming from its research by creating an ecosystem that fosters collaboration between academia, industry, and government. This has been done through initiatives such as:

O Spin-off companies: imec has created numerous

#### REPORTING I **GEOPOLITICS**

- spin-off companies that are commercialising the research and technology developed at the center. They have created a dynamic ecosystem in Leuven and Flanders together with universities (Leuven, Ghent, Antwerp and Hasselt) that thrives on talent, serial entrepreneurs, mentors, venture capitalists, etc.

- Industry platform: imec's model is largely based on joint R&D programmes, with the industry, that deliver new pre-competitive technologies to be used in future generations of semiconductor products. This joint collaboration model accelerates innovation, by pooling resources and alleviating the everincreasing development costs of new technologies. Today, imec is one of the largest R&D industry platforms of its kind in the world.

- Incubation and acceleration programmes: Flanders established incubation and acceleration programs to support start-ups and young companies, leveraging the knowledge and technology generated by imec. E.g. Over the years, imec has created a fund, imec.xpand, to invest in spinoffs and other startups/scaleups to increase the fabric of high-tech in the region. It is based on imec's unique semiconductor expertise and infrastructure. The business accelerator imec.istart, another example, targets promising startups and supports them in their growth process.

- Concentration of research infrastructure and talent: The government has invested in research infrastructure and provided funding for imec's research programs, helping to create a supportive environment for innovation and entrepreneurship.

- Attracting foreign direct investment: Flanders Investment & Trade has been very successful in leveraging the reputation of the Flemish research centers, such as imec and VIB, and its worldleading universities, to attract foreign investment, particularly in the fields of nanoelectronics and life sciences. imec is a key partner for many foreign companies to develop new technologies.

- Collaboration with universities: Partnerships have been established between imec, universities and research centers, promoting collaboration between researchers and students and increasing the transfer of knowledge between academia and industry. imec has collaboration agreements with over 200 universities worldwide, and many more that involve nonformal collaborations through a network of scientists, engineers and PhD students. One of the legacies of this is that Universities in Flanders consistently score well in the international rankings: Thomson-Reuters has ranked KU Leuven as Europe's most innovative university several years in a row.

#### Beyond subsidies

Flanders has taken a comprehensive and integrated approach to creating a knowledge-based innovation ecosystem. However, government subsidies alone

would not have delivered the results we've seen in Flanders. There are many other crucial factors that are key to the success. The top two are:

- O Tax incentives: The Government of Flanders actively supports business innovation through R&D tax incentives. Flanders gives an 85% corporation tax saving on profits that are the result of a company's own innovations. This is one of the most advantageous in Europe. This allows companies to recover part of their innovation investments.

- Longstanding joint efforts by knowledge institutions, companies and governmental organizations. It is rare for successive governments to maintain the consistency of focus that has been experienced in Flanders. The European Innovation Scoreboard (EIS), released by the European Commission, ranks Flanders/ Belgium among the 5 innovation leaders.

There are a number of unique factors that have substantially contributed to delivering the original vision, some within the control of policy makers and some are cultural. These include:

- O The concentration in a very small territory of top scientists and engineers (both from Flanders and international companies) and R&D centers, and the availability of state-of-the-art infrastructure

- A focus on interdisciplinary research in sectors at the interface of new technologies, such as nanotech and biotech. There have been a number of cross-disciplinary initiatives, such as NERF (Neuro-Electronics Research Flanders), which is a collaboration between Imec, VIB and KU Leuven.

- An open and international mindset, written in our

- O Talent attraction and retention: Flanders works hard to attract and retain talented individuals through programmes such as internships, research fellowships, and entrepreneurship support. This helps to build a pool of skilled professionals that can contribute to the growth of the innovation ecosystem.

- Open innovation: Flanders has adopted an "open innovation" approach, encouraging collaboration between different stakeholders and promoting the sharing of ideas and knowledge between businesses, academia, and government.

- Focus on key industries: The region has focused its efforts on key industries such as life sciences, clean technology, and microelectronics, helping to create a strong ecosystem in these areas and attract investment.

- International partnerships: Flanders has established partnerships with other regions and countries, promoting the exchange of knowledge and ideas and providing opportunities for collaboration on research projects and technology development.

- High levels of success in attracting foreign investment, led by Flanders Investment & Trade. This was partly due to factors such as proximity

to other markets and the strength of our transport infrastructure, including our world famous ports. Building on the success of foreign investments and exports, Flanders Investment & Trade substantially enlarged its foreign network with 10 Science & Technology Offices (New York, Palo Alto, Paris, London, Copenhagen, Munich, Mumbai, Singapore, Guangzhou and Tokyo), focussing on Digital Tech, Health Tech and/or Climate Tech).

Extensive study work and analysis in place to boost the opportunities for growth in Flanders' technology niches.

#### The impact

Over the last 40 years, Flanders has become a global leader in R&D, and in the translation of that innovation into industry. Through its support of its strategic R&D centers such as Imec and VIB, the Government of Flanders ensures that the long-term IP needs of industry are met across the key sectors first identified in the 1980s.

Imec has become one of the world's most important independent electronics R&D centres. Thousands of world leading researchers are based there, and its pilot production line is home to around €4bn complex semiconductor-making equipment. Imec is at the centre of an ecosystem of companies that, over the years, have leveraged their partnership with the centre to develop world-leading technologies. They include ASML, the only company in the world that owns the technology to produce microchips out of silicon wafers. Their machines are used by every major advanced semiconductor producer.

Imec's business and financing model means that it is able to be a non-commercial, or neutral, provider of R&D services in the semiconductor industry which is recognised as intensely competitive.

Financial support from the Government of Flanders initially accounted for the majority of imec's budget. Today the annual government grant,

though increased, accounts for less than 15% of its budget. Most of imec's income now comes from local and international contract research with industry. According to the most recent figures, companies, governmental organisations and knowledge institutions in Flanders collectively spent 3.60% of the region's GDP on R&D. This is more than any other region in Europe. FDI (secured by Flanders Investment & Trade) also plays a major role in enriching the ecosystem in Flanders. 1 in 4 new jobs created through FDI in 2022 is related to R&D. Government support has been crucial to the success of the original vision. Imec would not have been established without that support. And without imec Flanders would not have been able to establish itself in the way it has and delivered on its strategic objectives.

#### What next?

In October 2022, the Government of Flanders launched a new project and a promotional campaign called "Flanders Technology & Innovation". It was inspired by the success of "Flanders Technology". The initiative breathes new life into the concept of technology fairs, which are to be held in 2024. Through "Flanders Technology & Innovation", the region will present itself as a world leading technology laboratory.

In 2019 76% of R&D in Flanders was funded by the business enterprise sector (BERD of 2.40%). However, innovation efforts are still largely concentrated in certain industrial sectors and large companies. Industry does not typically invest in long-term foundation IP for pre-competitive enabling technologies. It is challenging to convince Finance Directors and shareholders of the benefits. Through its continued financial support of imec, the Government of Flanders ensures that the long-term IP needs of industry are met and it enables imec to:

- Carry out groundbreaking technology research in joint R&D programs with industrial partners and

- Keep its position as the world's most advanced independent nanoelectronics R&D platform for industry, with state-of-the art infrastructure.

#### Virtual fab focuses on real carbon footprint reductions

EMILY GALLAGHER, A PRINCIPAL MEMBER OF THE TECHNICAL STAFF AT IMEC, discusses with Philip Alsop, SiS Editor, the sustainability challenge facing the semiconductor industry and explains how imec's recently launched Virtual Fab is playing an important role in helping to improve both the understanding and development of environmentally friendly, patterning-related process solutions.

> PA: CO<sub>2</sub> emissions associated with integrated circuit manufacturing, I think they're expected to quadruple over the next decade. Why is that? Simply because of the massive explosion in digital infrastructure, an explosion that is not sustainable?

> EG: There are two factors to that quadrupling number. It's really sort of doubling twice. One time, because of complexity, so going to more advanced nodes, having more process steps involved, that creates a growth. And then the other thing that creates a growth is the volume, so the market itself is getting larger. So those two things together add to the quadrupling. And I agree it's not sustainable. There are some low hanging fruit things we can do. One of them is move to greener energy and another one is improved abatement. Those are in the works,

planned, but even with those two, we still are about two and a half x off where we need to be to meet the Paris agreement - reducing by 50% over the next decade.

PA: I think the semiconductor industry, or certainly the majority of companies, have committed to the carbon neutral and net zero targets by. It's debatable how much activity is maybe being done right now to get there. But I know in this context, Imec has launched the Sustainable Semiconductor Technology and System programme. The idea behind this is, I think, to help the supply chain with these changes?

EG: First, on the horizon for the targets, there are some companies who are more aggressive and they have net zero goals for more like 2030. The problem for these companies is very real and one of the big gaps in the industry was, well, how do we measure, how do we measure over a full process what the emissions impact is?

And that's where Imec netzero was launched to provide a way of measuring the impact of creating fabricating an IC device from cradle to grave. We work on the fabrication piece so that obviously there's a whole value stream, but everyone in that value stream is going to have to become involved. But our main focus, at least initially, has been on the fabrication piece. So, from the silicon coming in, to a chip leaving.

PA: And expanding on what you just said, I think that you're taking a bottom-up approach. You're looking to provide insight, actual data in terms of environmental impact assessment and that's to do with what you call the process flow. So, that's before people even start the manufacturing process, it's to understand the impact of what they're planning to do, is that correct?

**EG:** The application can be used either way. Either you could really just have a methodology for assessing what's already done today, or you could look towards the future and say, I know I have these process steps, calibrated, I know what an etch step costs environmentally, I know the same for a resist. Apply step costs, and you can basically string them together with a different process, flow forward, looking into the future, and make decisions based on minimising the emissions for those future processes.

I think it can be used multiple ways, really, with this bottom-up approach. It's like putting lego together - you have your building blocks, which are the process steps. You can link them however you want to assess a given semiconductor flow.

PA: In terms of that already, if I understand correctly, you have a physical fab where you can explore the idea behind various environmentally friendly process solutions. What's being done with this, is it just available for hire, or do you do your own research and then also offer it to semiconductor vendors - how does that work?

**EG:** We have a lot of fab space, over 12,000 metres squared of fab space, and it's 200 millimetre, 300 millimetre, and also some specialty fabrication areas. And those are used multiple ways, but it is a functioning fab.

One of the ways that Imec netzero is used is we can run a process flow, identify what the big contributors to emissions are and then specifically target what we like to call improve projects on those sectors. For example, if it's a fluorinated gas etch, we can specifically target projects that look at replacing the fluorinated gases (with their high global warming

potential) for less impactful options. So that's one of the tangible ways Imec netzero plays with the fab space we have at Imec.

PA: And you use that for your internal research, or do you also have outside organisations ask to use it and you work with them on anything they're looking at?

**EG:** Both. I mean, Imec is a research institute and there are a huge number of partners as part of our ecosystem. So it's definitely both some internally owned systems and projects, but a lot of them are collaborative because ultimately our mission isn't just to identify a solution and keep it to ourselves. Our goal is to identify a solution and propagate it throughout the industry so that we can all reduce our emissions.

PA: One of the main reasons we're having this discussion is that you've fairly recently developed a virtual fab as part of your Imec netzero modelling platform. It would be good to understand where that idea came from and what is the objective?

Either you could really just have a methodology for assessing what's already done today, or you could look towards the future and say, I know I have these process steps, calibrated, I know what an etch step costs environmentally, I know the same for a resist

EG: That is the netzero virtual fab. You can almost use them interchangeably, so it's really just a question of how you put the software together. I mean, it all relies on these calibrated models with a combination of supplier input and measured input to identify the emissions associated with a certain process step, and then strung together, they become part of a whole fab. In the virtual fab, of course, we have to add things like timing, idle time yield, a lot of complexity can get added on, and the software is pretty flexible in terms of being able to choose what you include or don't include, even abatement options. There are different ways that people deal with emission output from tools like gases and those models can be changed. Also, there's a lot of flexibility within this system so that if we have a partner as part of the programme, who wants to run their own use case, they know certain things about their yield and die size fab timing, they can modify it at as they choose.

PA: And using this modelling platform/virtual fab tool, IMEC and partners have been able to quantify the 'environmental impact of patterning-related

#### INDUSTRY I **SUSTAINABILITY**

process steps for various logic technology nodes'? Or is there more to it than that?

EG: There are logic nodes, but we can do NAND, we can do DRAM, you can do multiple different types of devices, so it's not just logic. A lot of the same background is there if you think about it, it's a virtual fab that can make different things and you just have to modify the flows in order to get there.

PA: In terms of what you've been able to do with the virtual fab tool so far, what have you discovered, for example, to do with lithography and etch carbon footprint? You've got some interesting results, is that right?

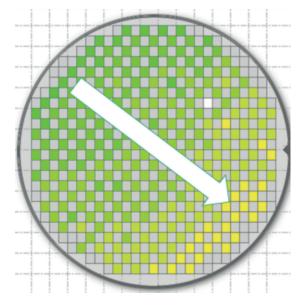

EG: Yeah. So I'm from the patterning area, that's my technical background most recently. I am part of the sustainability team but definitely targeting to improve different processes within patterning. If for example we focus on a future node, you can see that I think for an N3 Wafer, it's almost 40% of the influence comes from just patterning alone.

So, etch and lithography. We really targeted that area. In terms of lithography, the types of things you can do, we wanted to know. For example, if you go from DPV multiple patterning approaches to introducing EUV, which if you look and just compare DPV tool and an EUV tool, the EUV tool uses a tremendous amount of energy. It's a complex source with relatively low efficiency to get the EUV light. And there was a lot of concern about introduction of EUV and manufacturing and what that would do with two emissions. So we did that comparison. But what we find is, for example, if you use N7 with and without EUV, the version with EUV eliminates a lot of extra process steps that are related to using multiple patterning approaches. So yes, you introduce this really high emission system but you eliminate a lot of etch steps, a lot of clean steps, a lot of deposition steps and in the end you actually have a lower emission fabrication process.

So that was one good example. We'll be doing that sort of activity again when we talk about

moving towards High-NA, which is even a different throughput model and something else we'll have to look at for etch, there are other things to look at. For example, what can we do to optimise the etch stack in order to minimise the etch processes or to optimise there's a lot of detailed process work that can be done on etch. And it was really helpful for us to identify it as a big contributor. Especially the high GWP gases are something that needs to be addressed in order to get the etch impact lowered.

PA: You described there the overall net benefit of the EUV process. But I think you've also done some fab experiments around lowering the dose of EUV as well. What results have you got with that?

EG: Yeah, so for example, you can just run a curve that shows what the impact of changing dose does. And there are a lot of different ways to address dose. And reducing dose also reduces cost. You have a certain tool with a given throughput and if you just lower the dose your throughput during the process time is going to increase linearly with that. So it's a pretty obvious knob to work on and one that helps cost as well as emissions very easily. But it's not so simple to get equal performance at a lower dose point. So some of the kinds of things you can do is use different resists, different bakes. So we look at all of those things and what we're doing now is we basically have a calculator that we can apply to different projects just to see what the benefit is when you change dose, for example.

PA: Okay, so the ultimate there, you'll produce, as you say, some kind of table or best practises so people can understand all the variables. Obviously, you need to produce a product - that's important, but also vou want to minimise or optimise vour environmental footprint. So, it's helping people understand the consequences of what they do or don't do during the manufactured process?

EG: Right. So for a long time we've talked about PPAC, right. Power, performance, area, and cost, those have been things the whole industry has optimised around. What we'd like to do is add E for environment to that. So PPACE, and just like you said, just being sure that during the development phase we're optimising for emissions as well as everything else. It's an innovative industry, we can do this, but we have to know what we're measuring.

PA: And in terms of the partners, I believe you're able to share, for example, you've been doing some work with Edwards, so it'd be good to understand how you've been working with them and what sort of area helping them, collaborating with them?

EG: Yeah. Edwards is a great example of sort of an improved project. One of the consumables on the scanner for the EUV scanner is hydrogen. It's used as a gas to keep the source clean, to keep the reticle environment, mini environment (RME) clean because it keeps carbon build up so that your mirror If you really look critically at an etch recipe, there a lot of knobs that can be turned to minimise either the power consumption or what's more important for etching is what we call the scope one emissions that are associated with the GWP gases

reflection stays as high as you need it to. So again, helping throughput. It also keeps particles away from critical areas in the source. So there's really a tremendous flow of hydrogen through the system. And what Edwards has developed, they're a vacuum and abatement company, and they have developed a system that actually reuses the hydrogen.

So rather than just consume it and then abate it with a common way suchas burning with methane, which is a high GWP gas and a pretty consumptive process, instead they're recovering. And we had the first demonstration of that system in fourth quarter of last year at Imec and demonstrated a 70% recycling of the hydrogen. And going forward, we anticipate as much as 80%. Some changes are being made now to look at that. So, a really nice example of an abatement improvement that can really reduce the emissions associated with using EUV.

PA: Is there anything to add on the load? Because I know you are doing lots of work on the low dose solutions for EUV Lithography. Again, is that with partners or is that more of your internal research?

**EG**: A lot of the dose reduction projects are actually together with ASML. They're one of our big partners there, but then almost every resist supplier is aware of this challenge and there are different formulations looking at that. So, I would say a lot of those dose reduction work is together with partners, various kinds.

PA: And I also believe the work you've been doing, you've identified etch directions for improved sustainability. Can you explain how that works as well?

**EG:** Yeah, so I think I touched on a few of them, but maybe just to say them all at the same time. So you can do things like optimise your recipe for having less power, more efficiency in terms of the use of the gases that you use, optimising stabilisation steps. If you really look critically at an etch recipe, there a lot of knobs that can be turned to minimise either the power consumption or what's more important for etching is what we call the scope one emissions that are associated with the GWP gases. Those are, I guess, the biggest things.

One of our big thrusts this year is working on various ways to have what we call reducing the fluorinated content of the gases that are used in etch. So that's basically reducing the GWP. There's an output

side of that which is working on abatement too. And that'll obviously be considered with any etch process that we change. Etch is complicated, so there are a lot of pieces that come into it. And of course, we need to maintain performance at the same time as making all these other changes. But there are some good examples of effective work in the industry and we're trying to bring more of those, optimise them and bring them to people's attention. But we're not alone in working on this. There are a lot of companies both material suppliers and edge tool suppliers that are also working in this area, which is good because it's a high impact area.

PA: To characterise it, is it very much trial and error? You tinker with a certain parameter, do you then anticipate a result and it tends to come as you expected, or is it often unexpected? So, it is very much you're a bit in the dark, trying bit by bit all these different recipes, if you like, or do you have a fairly good idea of what you think will work and then you use the virtual lab to just say, yes, what you thought was indeed correct?

EG: The virtual lab is helpful to a point here, but we do need to make measurements as well, because the input gases, you could understand right away what the embodied carbon of making a certain type of gas is and how much it leaks and guess at what the output would be after etch. But in fact, you really need to measure. So this is one of those cases where you might have a relatively good idea, but measuring the by-products after etch are really important because some processes are very efficient consumers of the greenhouse gases.

And if that's the case, it's much, much less of a problem than if they're actually being released into the atmosphere. And also, I should mention, my background was not etch until recently. I've been focusing on it more because of the sustainability work. So to me, plasmas are a little bit of a black box. I think that's the way most people look at them. But perhaps if you had someone who grew up in plasmas, they wouldn't think about it quite that way.

PA: And the overall objective is that you can get to the point where you can produce a semiconductor process flow with the sustainability angle, very much part of it. Do you have a time frame for that and how is your work going towards that overall goal?

**EG:** Our initial goal was to create this virtual fab or Imec netzero platform, so that you could actually

#### INDUSTRY I **SUSTAINABILITY**

measure and assess where you are today and then work from that. On terms of being able to move the needle of HVM manufacturing that relies on adoption and changes within the industry.

So our big goal there is really just to collaborate and partner as much as we can. For example, we are part of some larger organisations as well, such as SEMI's SCC, the Semiconductor Climate Consortium. We're heavily involved there and with other groups like IRDS, because I think climate is one of those things, no one's going to be able to do it alone. And what we can do is try and look for the biggest gaps in the industry and try and fill them and sort of act as a way to propel everybody to a state where we're using less and emitting less. But Imec could have a perfect process and if it's only at Imec, it doesn't help anybody.

PA: Just to restate, the fundamental issue is you're trying to maintain and develop patterning processes for the industry moving forward, but at the same time reducing CO<sub>2</sub>. So to a certain extent they might appear, on the face of it, sort of incompatible goals. But your idea is obviously to make sure that the industry progresses, but it also reduces its carbon footprint – achieves much more in terms of sustainability.

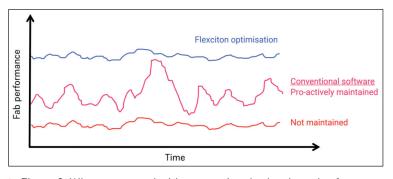

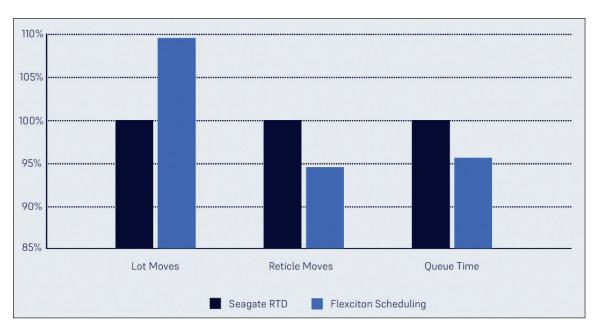

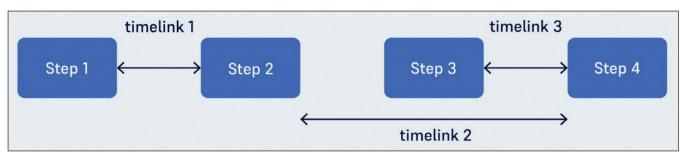

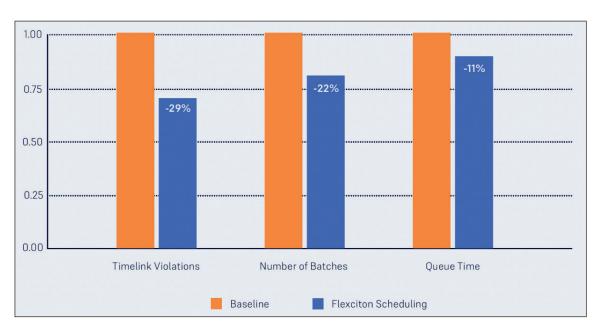

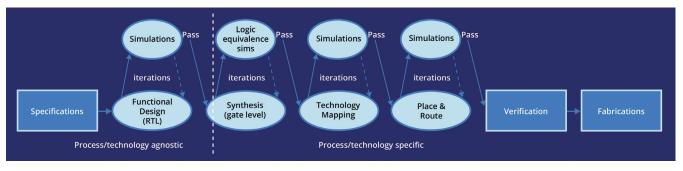

EG: Exactly. I don't think the industry would accept a process that wasn't at a high level. They wouldn't accept, for example, higher line edge roughness or lower EPE just because you reduced emissions. They want everything. But I think if we do this at the early stages, that's possible.