# SEMICONDUCTOR

VOLUME 46 ISSUE II 2025

C

$\bigcirc$

AN ANGEL BUSINESS COMMUNICATIONS PUBLICATION

SILICONSEMICONDUCTOR.NET

# EUROPE'S SEMICONDUCTOR INDUSTRY FOCUSES ON SUSTAINABLE GROWTH

# FUSION AND HYBRID BONDING FOR HETEROGENEOUS INTEGRATION

Enabling advanced 3D device stacking and chiplet integration for CMOS image sensors, memory and 3D system-on-chip (SoC)

High-volume production equipment and process technology for Wafer-to-Wafer (W2W) and Die-to-Wafer (D2W) hybrid bonding

GEMINI<sup>®</sup> FB Automated Production Wafer Bonding System delivers industry leading alignment accuracy and bonding performance

Heterogeneous Integration Competence Center<sup>™</sup> serving as leadingedge innovation incubator for EVG customers and partners

GET IN TOUCH to discuss your manufacturing needs www.EVGroup.com

# EVPOINT BY PHIL ALSOP

### The race for resilience

WITH ELON MUSK at his side, one imagines that the US president is all too aware that the current focus on AI chips is nothing to do with his favourite fast-food choices, and everything to do with the ongoing geopolitical tension whereby China looms large over Taiwan. In a recent podcast, Musk spelt out the threat guite simply - if China were to invade Taiwan, the rest of the world would be cut off from advanced AI chips, as 100% of advanced AI chips are currently made in Taiwan.

With my storage and data centre hats on, where resilience and business continuity and disaster recovery (BC/DR) plans are so crucial, I might ask how such a situation has been allowed to occur within the semiconductor industry. Hindsight is a wonderful thing of course. Until fairly recently, the concentration of AI chip manufacturing in Taiwan made complete commercial sense. Ah, but even then, did no one even think of the risks of concentrating this manufacturing activity in one location?

In the storage and data centre industries, offsite backups, mirroring, disaster recovery sites and the like are all taken for granted. Even more so, as cybersecurity threats have heightened the awareness of the imperative of cyber resilience. Of course, every organisation makes its own decisions around the cost of such resilience - hence BC/DR plans can vary greatly – with the main decision being the relative cost of protecting crucial business assets (data, infrastructure etc.) versus the possible cost of doing nothing - anything from minor disruption through to the business shutting down.

For the semiconductor industry, the billions involved in building and operating fabs means that the idea of having some empty fabs in a different geographical location sitting idle against the day when they might be needed is a nonstarter. Nevertheless, the 'putting all of your eggs in one basket' approach that seems to have been adopted when it comes to AI chips was maybe less smart than it might once have appeared.

To use another cliché – there's no use crying over spilt milk. As the business folks like to say: 'We are where we are'. Hence, not before time, countries and regions far away from Taiwan are looking to ensure that some level of resilience is now being built into the semiconductor supply chain, from the construction of new fabs onwards.

Regrettably, what has yet to play out is just how local and insular these supply chains need to be. Not only do we have the uncertainty over Taiwan's future, but we are also faced with an absence of any certainties when it comes to whether or not the rest of the world can continue to operate as one unified, all be it competitive, supply chain, or whether geopolitics will mean further fragmentation is likely.

Historically, there's always been a balance to be struck between the success of individual

country economies and more collaborative, mutual economic success across multiple countries and regions. It will be fascinating to see how such different points of view do, or do not, impact the semiconductor industry into the future.

For your free weekly e-news roundup go to: siliconsemiconductor.net

### CONTENTS

**VOL 46 ISSUE II 2025**

# 14 Smarter by design: how AI is reshaping manufacturing in 2025

Al is at the heart of the manufacturing revolution, driving efficiency, sustainability, and precision as we head into 2025

#### 16 Biometric ID drives semiconductor manufacturing security and efficiency

The wrist-worn Nymi Band using biometric ID is expediting secure, hands-free authentication across semiconductor fabs, dramatically increasing productivity.

#### 18 The geopolitics of the semiconductor industry: navigating a global power struggle

Nations are racing to control the semiconductor technologies that power everything from consumer gadgets to defence systems

#### 22 Innovative approaches to scaling network-on-chip architectures

Co-integration of NoC routing channels alongside the backside power delivery network as a cost-effective scaling path

### 30 Fiber computer allows apparel to run apps and "understand" the wearer

MIT researchers developed a fiber computer and networked several of them into a garment that learns to identify physical activities

### 34 Vacuum systems: a guide to turnkey projects

When it comes to implementing vacuum systems in industrial settings, the route you take can significantly impact the efficiency, cost, and success of your project

## 36 Drip by drip: semiconductor water management innovations

IDTechEx forecasts water usage in semiconductor manufacturing to double by 2035

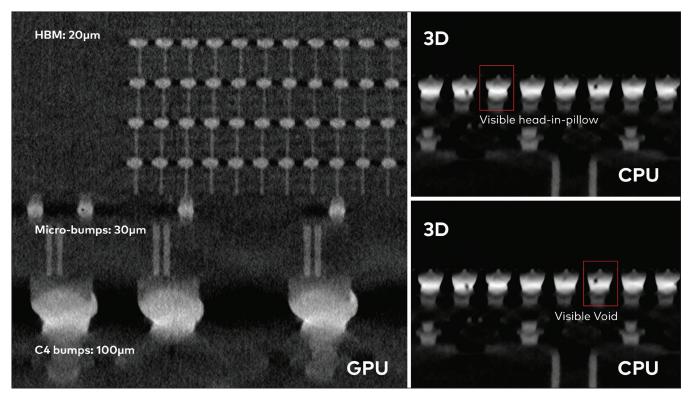

# 38 From lab to fab. Solving systematic yield issues with next generation3D X-ray

With the increasing adoption of 2.5D and 3D ICs in semiconductor manufacturing, the sophistication of packaging design is on the rise, highlighting the importance of robust quality assurance practices in bringing these complex architectures to market

#### 40 Synopsys teams up with SEMI Foundation

Synopsys, Inc. and the SEMI Foundation have signed a Memorandum of Understanding (MoU) at Synopsys' corporate headquarters in Sunnyvale, California to dvance workforce development within the semiconductor chip design sector

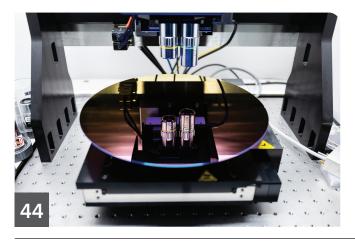

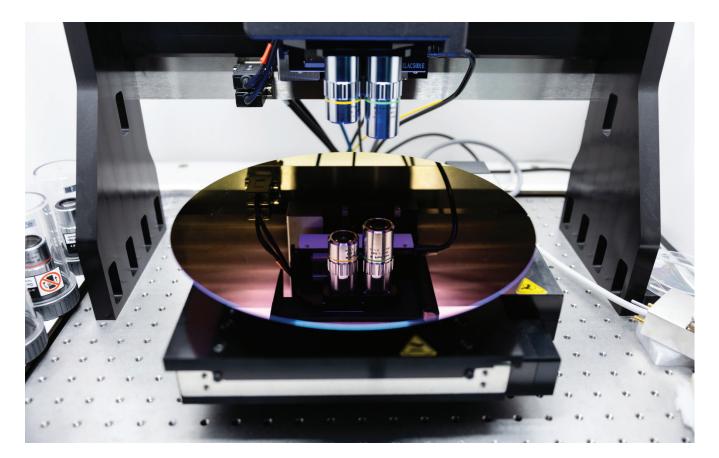

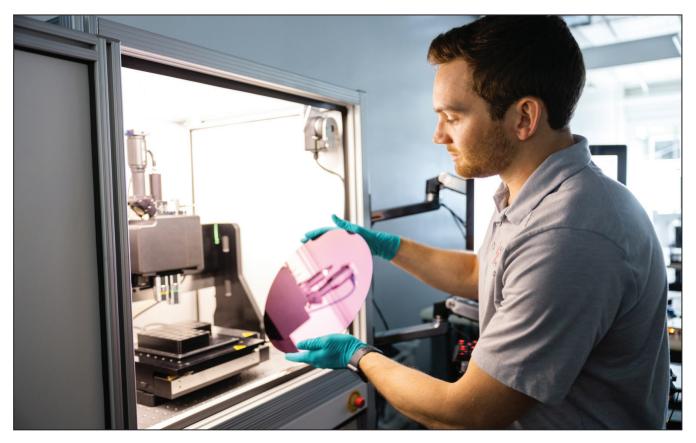

### 44 Thin film thermal metrology and its implications for electronic devices

How a new technology addresses the limitations of traditional measurement methods

#### Publisher Jackie Cannon Editor Phil Alsop Sales & Marketing Manager Shehzad Munshi

Marketing & Logistics Executive Eve O'Sullivan USA Representatives Tom Brun Brun Media Janice Jenkins

Director of Logistics Sharon Cowley Design & Production Manager Mitch Gaynor jackie.cannon@angelbc.com +44 (0)1923 690205 phil.alsop@angelbc.com +44 (0)1923 690215 eve.osullivan@angelbc.com +44 (0)2476 823123 tbrun@brunmedia.com +001 724 539-2404 jjenkins@brunmedia.com +001 724-929-3550 sharon.cowley@angelbc.com +44 (0)1923 690210 mitch.gaynor@angelbc.com +44 (0)1923 690214

#### NEWS

- 06 Water usage in semiconductor manufacturing to double by 2035

- **07** 3D Semiconductor Packaging market to reach US\$ 43.6 billion by 2034

- 08 Commission approves €920 million German State aid measure to support Infineon

- **09** EU funding boosts Europe's semiconductor production

- 10 Worldwide semiconductor revenue grew 18% in 2024

- 11 NVIDIA continues to dominate global semiconductor sector

- 12 ASML and imec sign strategic partnership agreement

Chief Executive Officer Sukhi Bhadal Chief Technical Officer Scott Adams Directors Jackie Cannon, Sharon Cowley sukhi.bhadal@angelbc.com +44 (0)2476 718970 scott.adams@angelbc.com +44 (0)2476 718970

Published by Angel Business Communications Ltd, 6 Bow Court, Fletchworth Gate, Burnsall Road, Coventry CV5 6SP, UK T: +44 (0)2476 718 970 E: info@angelbc.com

Silicon Semiconductor is published ten times (6x print and 4x video issues) a year on a controlled circulation basis. Non-qualifying individuals can subscribe at: £50.00 per annum (UK), €60.00 per annum ( Europe), \$90 per annum (air mail)(USA). Cover price £4.50. All information herein is believed to be correct at time of going to press. The publisher does not accept responsibility for any errors and omissions. The views expressed in this publication are not necessarily those of the publisher. Every effort has been made to obtain copyright permission for the material contained in this publication. Angel Business Communications Ltd will be happy to acknowledge any copyright oversights in a subsequent issue of the publication. Angel Business Communications Ltd © Copyright 2024. All rights reserved. Contents may not be reproduced in whole or part without the written consent of the publishers. The paper used within this magazine is produced by chain of custody certified manufacturers, guaranteeing sustainable sourcing. US mailing information: Silicon Semiconductor, ISSN 1096-598X, is published 5 times a year by Angel Business Communications Ltd, Unit 6, Bow Court, Fletchworth Gate, Burnsall Rd, Coventry CV5 6SP. UK. Airfreight and mailing in the USA by agent named World Container INC 150-15, 183rd St, Jamaica, NY 11413, USA. Periodicals Postage Paid at Brooklyn, NY 11256. POSTMASTER: Send address changes to Silicon Semiconductor, Air Business Ltd, *c/o* World Container INC 150-15, 183rd St, Jamaica, NY 11413, USA.

We strive for accuracy in all we publish; readers and contributors are encouraged to contact us if they recognise an error or omission. Once a magazine edition is published [online, in print or both], we do not update previously published articles to align old company names, branding, marketing efforts, taglines, mission statements or other promotional verbiage, images, or logos to newly created or updated names, images, typographic renderings, logos (or similar) when such references/images we accurately stated, rendered or displayed at the time of the original publication. When companies change their names or the images/text used to represent the company, we invite organizations to provide Angel Business Communications with a news release detailing their new business objectives and/or other changes that could impact how customers/prospects might recognise the company, contact the organisation, or engage with them for future commercial enterprise. Printed by: The Manson Group. ISSN 2050-7798 (Print) ISSN 2050-7801 (Online) © Copyright 2024.

#### **INDUSTRY NEWS**

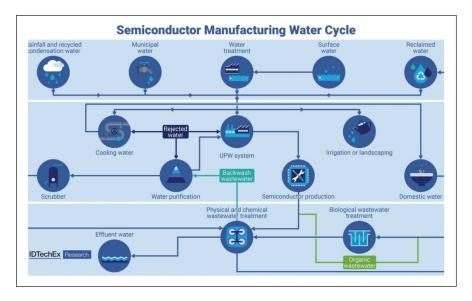

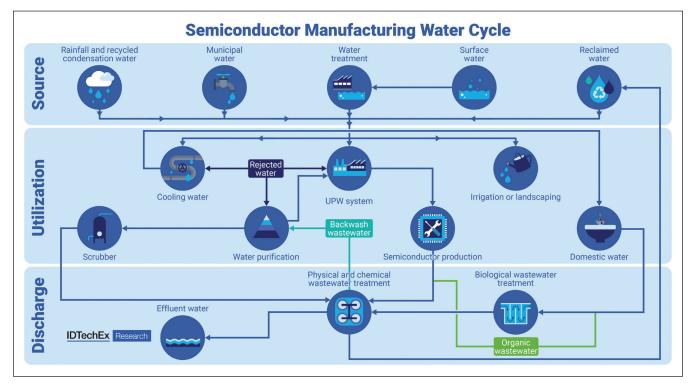

# Water usage in semiconductor manufacturing to double by 2035

Not only does semiconductor manufacturing require large volumes of energy, chemicals, and silicon wafers, it also requires vast volumes of water.

IDTECHEX'S latest report, "Sustainable Electronics and Semiconductor Manufacturing 2025-2035: Players, Markets, Forecasts", (courtesy of Thomas Bithell, Technology Analyst at IDTechEx) forecasts water usage across semiconductor manufacturing to double by 2035, as demand for integrated circuits continues to rise. In 2023 alone, semiconductor giant TSMC reported consumption of a staggering 101 million m3 of water, highlighting the scale of thirst in this fast-growing sector.

Furthermore, as node technology advances, so do the number of manufacturing process steps, and the usage of single wafer tools instead of batch tools, making the task of reducing water usage both challenging and even more critical. With many semiconductor fabs located in areas of high-water scarcity, such as Taiwan and Arizona, it is vital that semiconductor manufacturers take action to mitigate this huge consumption as part of the wider search for sustainable electronics. Water management for semiconductor manufacturers is complex, propagated by the extreme purity requirements for the water used in manufacturing, giving it the name Ultra-Pure Water (UPW). However, water management techniques being implemented have the potential to mitigate water scarcity fears whilst also reducing operational costs.

Increasing volumes of reused water Most semiconductor manufacturers now recycle or reuse water in some capacity, with annual targets to increase current levels of water reuse and combat increasing water withdrawal rates. Many companies such as NXP, Onsemi, and TI now reuse wastewater in their cooling towers. Reprocessing wastewater back into UPW is more difficult, but implementing new water treatment systems will be necessary to achieve sustainability in water use in

semiconductor manufacturing. SK Hynix increased its volume of reused water by 51% between 2020 and 2023, partly motivated by water stress classification of 3 fabs as 'High' or 'Medium-high'. This is expected to also reduce operational costs through reduced municipal water consumption.

#### Efficiency of water use

Process optimization can also reduce water usage. Many semiconductor manufacturers have cited a reduction in water per wafer as a key target for sustainability and to negate the risk of water shortages. This has been an issue for some, as the increased demand and complexity of wafers required has increased water use per wafer for companies such as SMIC. Reducing consumption per wafer becomes increasingly difficult with advancing node technologies, which often require increasing numbers of process steps.

However, simply reducing rinse times can result in large savings. GlobalFoundries reduced their rinse time from 10 minutes to 5 minutes after etching, resulting in an annual water saving of 10,000 m<sup>3</sup>, and there are many more examples in the report. Diversification of water sources Negation of water scarcity risk can come through diversification of water sources. Installing facilities such as rainwater collection may reduce operational costs due to a decreased requirement for municipal water.

Tower Semiconductor has utilized the dehumidification of air required for the dry indoor environment in their factory in Texas. SMIC have also utilized condensate from air conditioning alongside rainwater collection to reduce municipal water consumption and associated costs.

These techniques may only recover a small fraction of total water usage but could still be invaluable. Larger usage could be obtained from seawater, with desalination employed in the Hsinchu TSMC plant. Where fabs are located close to the coast, utilization of onsite desalination could solve many fears surrounding sustainable water usage, although this would require high energy consumption.

# 3D Semiconductor packaging market to reach US\$ 43.6 billion by 2034

According to Fact.MR, a market research and competitive intelligence provider, the 3D Semiconductor Packaging Market is valued at US\$ 10 billion in 2024 and is expected to grow at a CAGR of 15.9% during the forecast period of (2024 to 2034).

PRESENT market trends show that the rising demand for compact, quicker, and more efficient electronic devices drives the expansion of 3D semiconductor packaging. This technology stacks and integrates multiple chips in one package to enhance performance while reducing latency and power consumption. Fan-out wafer-level packaging development and throughsilicon via are also aiding in delivering high performance interconnects and signal integrity. As the semiconductor industry proceeds with development, 3D packaging has become one of the major enablers for innovating autonomous driving, 5G connectivity, and nextgeneration consumer electronics that are further driving market growth.

#### Key takeaways from 3D semiconductor packaging market study

The global 3D semiconductor packaging market is projected to grow at 15.9% CAGR and reach US\$ 43.6 billion by 2034 The market created an absolute \$ opportunity of US\$ 33.6 billion growing at a CAGR of 15.9% between 2024 to 2034.

North America is a prominent region that is estimated to hold a market share of 30.5% in 2034. Predominating market players include TSMC (Taiwan Semiconductor Manufacturing Company), Amkor Technology, GlobalFoundries, Infineon Technologies, Qualcomm Incorporated, among others. Through-Silicon Via (TSV) under technology are estimated to grow at a CAGR of 16.9% creating an absolute \$ opportunity of US\$ 7.9 billion between 2024 and 2034. North America and East Asia are expected to create an absolute \$ opportunity of US\$ 29.5 billion collectively.

"North America and Asia Will Drive The 3D Semiconductor Packaging Market Due To Strong Demand from Technology, Automotive and Al-Driven Sectors" says Fact.MR analyst.

#### Leading players driving innovation in the 3D semiconductor packaging market

The Key Players in the Infant 3D Semiconductor Packaging Industry include Amkor Technology; ASE Group (Advanced Semiconductor Engineering); Broadcom Inc.; GlobalFoundries; Infineon Technologies; Intel Corporation; Jiangsu Changjiang Electronics Technology Co.; Lattice Semiconductor Corporation; Marvell Technology Group; Micron Technology; NXP Semiconductors; ON Semiconductor; Qualcomm Incorporated; Renesas Electronics Corporation; Samsung Electronics; Siliconware Precision Industries Co., Ltd. (SPIL); Sony Corporation; STMicroelectronics; Texas Instruments; TSMC (Taiwan Semiconductor Manufacturing Company); Other Market Players.

#### **Country-wise insights:**

Why is the US one of North America's top markets for 3D semiconductor packaging?

The US market is expected to reach US\$2 billion in 2024 and grow at a compound annual growth rate (CAGR) of 16% until 2034. From 2024 to 2034, this market is expected to create an absolute potential worth US\$6.7 billion. Advanced electronic equipment, like as sensors, artificial intelligence (AI) processors, and potent computers, are essential to an autonomous car and require tiny, high-performance chips. Multiple chips can be stacked vertically thanks to 3D semiconductor packaging, which boosts processing power while taking up less physical space in these devices. 3D packaging is essential for integrating many functionalities, increasing energy efficiency, and

speeding up data transfer rates as AV technology advances and demands smaller sizes and more processing power.

This partnership between 3D semiconductor packaging and autonomous vehicle integration strengthens the US market's position as a leader by meeting the growing demand for reliable yet small solutions that are necessary for cutting-edge autonomous driving advancements.

#### What is the current state of demand in China for 3D semiconductor packaging?

At a compound annual growth rate (CAGR) of 16.2%, the Chinese market is projected to reach US\$ 11.4 billion in 2034. From 2024 to 2034, this market is expected to create an absolute potential worth US\$ 8.9 billion.

China's rapid adoption of 5G technology and drive to provide ultra-fast internet connections are driving increasing demand for 3D semiconductor packaging in the nation. Building up 5G networks is part of this expansion of digital infrastructure, and China has been actively working to meet the demand for faster data rates and more processing power with the use of 3D semiconductor packaging.

As cloud computing, smart cities, and the Internet of Things become more integrated, 3D packaging helps dataintensive applications that require low latency and high-speed communication.

#### **INDUSTRY NEWS**

# Commission approves €920 million German State aid measure to support Infineon

The European Commission has approved, under EU State aid rules, a €920 million German aid measure for the construction of a new semiconductor manufacturing plant in Dresden.

THE MEASURE will allow Infineon to complete the MEGAFAB-DD project which will be able to produce a wide range of different types of chips. This new manufacturing plant will bring flexible production capacity to the EU and thereby strengthen Europe's security of supply, resilience and technological autonomy in

semiconductor technologies, in line with the objectives set out in the European Chips Act Communication and the Political Guidelines for the European Commission 2024-2029.

#### The German measure

Germany notified the Commission of its plan to support Infineon's project to set up a new semiconductor manufacturing facility in Dresden, Germany. The plant will produce two technology families: (i) discrete power technologies used for power switching, management and control in electronic systems, and (ii) analog/mixed-signal integrated circuits that are crucial for bridging the gap between the analog and digital worlds. The produced semiconductors will be used in industrial, automotive and consumer applications.

The new facility will be the first one in Europe that will be able to rapidly switch its production between the two technology families while maintaining its high output capacity. It will be a frontend facility, covering wafer processing, testing and separation. The plant will reach its full capacity in 2031.

The aid will take the form of a direct grant of up to  $\notin$ 920 million to Infineon

to support its investment amounting to  $\in$ 3.5 billion. Under the measure, Infineon agreed to:

ensure that the project will bring wider positive effects to the EU semiconductor value chain; invest in the research and development of the next generation of chips in Europe:

contribute to crisis preparedness by committing to implement priority-rated orders in the case of a supply shortage in line with the European Chips Act Regulation; and

provide access to its new facility to SMEs and research organisations for testing and prototyping.

#### The Commission assessment

The Commission assessed the German measure under EU State aid rules, in particular Article 107(3)(c) of the Treaty on the Functioning of the EU ('TFEU'), which enables Member States to grant aid to facilitate the development of certain economic activities subject to certain conditions, and based on the principles set out in the European Chips Act Communication.

The Commission found that: The measure facilitates the development of certain economic activities, by enabling the establishment of a new semiconductor manufacturing facility in Europe.

The facility is a firstof-a-kind in Europe, as there is currently no semiconductor manufacturing facility that would be able to flexibly change its output between discrete power and analog-mixed signal technologies in a

comparable manner.

The aid has an 'incentive effect', as the beneficiary would not carry out this investment in Europe without public support. The measure has a limited impact on competition and trade within the EU. The measure is necessary and appropriate to ensure the resilience of Europe's semiconductor supply chain. In addition, the aid is proportionate and limited to the minimum necessary based on a proven funding gap (i.e. the aid amount necessary to attract the investment that otherwise would not take place in Europe). Infineon has agreed to share with Germany potential additional profits going beyond current expectations.

The measure has wider positive effects for the European semiconductor ecosystem and contributes to strengthening Europe's security of supply. The Commission also took note that Infineon will apply to be recognised as an integrated production facility under the EU Chips Act Regulation and will comply with all obligations linked to this status. On this basis, the Commission approved the German measure under EU State aid rules.

# EU funding boosts Europe's semiconductor production

The Public Authorities Board of the Chips Joint Undertaking (EU Chips Act) has awarded funding to the APECS pilot line project.

THE PROJECT is part of a major effort to develop European semiconductor production. The project focuses on developing and providing new packaging and integration solutions for the industry. VTT is also involved in the following pilot line projects aiming at semiconductor production: FAMES, NanoIC and PIXEurope.

The APECS (Advanced Packaging and Heterogeneous Integration for Electronic Components and Systems) pilot line, as part of the EU Chips Act programme, will promote European semiconductor manufacturing capability and chip innovation. The pilot line will focus on the development of reliable packaging solutions for microchips and innovative combinations of semiconductor materials and technologies, as well as chiplet integration. As its name suggests, the APECS pilot line will provide technologies to help others develop technology and innovation and will be coordinated by Fraunhofer.

"In the APECS project, VTT will focus in particular on the radio frequency technologies required for the 6G network and on the development and demonstration of optical microsystems and chip packaging methods," says Tauno Vähä-Heikkilä, Vice President, Microelectronics and Quantum Technologies at VTT.

VTT is involved in other European pilot projects: The FAMES and NanolC pilot lines are run by CEA-Leti of France and imec of Belgium. In October, we published news about our collaboration on the EU-funded CEA-Let and imec FAMES and NanolC pilot projects. Through the pilot lines, Finland is strongly involved in the European semiconductor ecosystem. The pilot lines provide services to companies to develop products and scale them up for production. Technologies under development include the latest transistor and RF technologies, new memory technologies and packaging technologies.

VTT's activities in the European APECS, FAMES and NanoIC pilot lines will be located in Kvanttinova for which the Finnish government has granted EUR 79 million in funding to build shared pilot lines. Kvanttinova is an RDI Hub in microelectronics and quantum technology, jointly developed by VTT, Aalto University and the City of Espoo.

VTT's shared-use cleanroom enables domestic companies to develop and pilot microelectronics components, systems and innovation and scale them up for production. The first semiconductor processes in Finland will start up towards the end of 2026.

Furthermore, the European Commission has announced the creation of PIXEurope, a new pilot line for photonic chips. It is coordinated by ICFO, the Institute of Photonic Sciences in Barcelona. VTT is among the participants of the PIXEurope consortium. Financial and technical negotiations are currently underway. VTT develops low-loss thick-SOI integrated photonics for the pilot line's offering.

The EUR 29 million funding from the EU and the Finnish government for the APECS pilot line will focus on VTT's shared-use cleanroom facilities and the development of semiconductor manufacturing processes.

"Taken together, these four pilot lines, APECS, FAMES, NanoIC and PIXEurope, will support the growth of the Finnish and European semiconductor industry and help Finnish industry to connect to European value chains," says VTT's Research Manager Pekka Pursula.

The recent funding decisions made through the Chips Act and the equipment acquisitions enabled by them will support the strong areas of expertise of the Finnish semiconductor industry, in particular new materials, ALD technology for memory applications and RF technology.

#### **INDUSTRY NEWS**

# Worldwide semiconductor revenue grew 18% in 2024

Worldwide semiconductor revenue in 2024 totalled \$626 billion, an increase of 18.1% from 2024, according to preliminary results by Gartner, Inc. Revenue is projected to total \$705 billion in 2025.

"GRAPHICS PROCESSING units (GPUs) and AI processors used in data centre applications (servers and accelerator cards) were the key drivers for the chip sector in 2024," said George Brocklehurst, VP Analyst at Gartner. "The rising demand for AI and generative AI (GenAI) workloads led data centres to become the secondlargest market for semiconductors in 2024, behind smartphones. Data centre semiconductor revenue totalled \$112 billion in 2024, up from \$64.8 billion in 2023."

The positive performance of the overall market impacted the ranking of several semiconductor vendors. Eleven vendors experienced double-digit growth and only 8 of the top 25 semiconductor vendors posted revenue decline in 2024.

#### Samsung Electronics Regained No. 1 Spot in 2024

With 9 out of the top 10 semiconductor vendors recording revenue growth in 2024, the ranking of the top 10 semiconductor vendors changed yearover-year.

Samsung Electronics reclaimed the No.1 spot from Intel and extended its lead over the company in 2024 driven

by a strong rebound in memory device prices. Samsung Electronics revenue totalled \$66.5 billion in 2024.

Intel moved to the No. 2 position as its product set — AI PCs and the Core Ultra chipset — was insufficient to offset the limited success of its AI accelerator offering and the modest growth in its x86 business. Intel's semiconductor revenue was flat at 0.1% growth in 2024.

Nvidia continued to perform exceptionally well, increasing its semiconductor revenue by 84% in 2024, to total \$46 billion. It moved up two spots to secure the No. 3 position thanks to the strength of its AI business. HBM to Represent 19.2% of DRAM Revenue in 2025, Up from 13.6% in 2024

Memory revenue recorded 71.8% revenue growth in 2024. Memory's share as a percentage of total semiconductor sales increased to 25.2% in 2024. DRAM revenue improved 75.4% in 2024 while NAND revenue increased 75.7% year-overyear. High-bandwidth memory (HBM) production contributed significantly to the revenue for DRAM vendors. HBM revenue represented 13.6% of total DRAM revenue in 2024.

Expertise: Moderators, Markets, 30 Years + Pedigree

Reach: Specialist vertical databases

**Branding:** Message delivery to high level influencers via various in house established magazines, websites, events and social media

knowledge in overlapping sectors

Specialists with 30 year+ pedigree and in-depth

#### For more information contact:

Jackie Cannon T: 01923 690205 E: jackie@angelwebinar.co.uk W: www.angelwebinar.co.uk T: +44 (0)2476 718 970 E: info@angelbc.com W: www.angelbc.com

PIC PHOTONIC

# NVIDIA continues to dominate the global semiconductor sector

Brand Finance data reveals strong growth for world's top semiconductor companies despite ongoing supply chain challenges and geopolitical tensions.

NVIDIA has retained its position as the world's most valuable semiconductor brand, according to a new report from Brand Finance, the world's leading brand valuation consultancy. With a 98% increase in brand value to USD87.9 billion, NVIDIA's brand value is now more than two and a half times that of TSMC, the second-most valuable brand in the sector.

This growth propelled NVIDIA into the top 10 most valuable global brands list for the first time since it was valued in 2014, when it ranked 424th in the US 500. Last year, NVIDIA was the fastest growing brand in the world.

With a Brand Strength Index (BSI) score of 88.9 out of 100, NVIDIA has also become the world's strongest semiconductor brand in 2025. This puts NVIDIA more than seven points ahead of Intel, whose BSI now stands at 81.4 out of 100 – a notable shift from Intel's former position as the sector's strongest brand in 2024.

Lorenzo Coruzzi, Valuation Director at Brand Finance, commented, "Artificial intelligence remains a hotbed of controversy, investment, and innovation, drawing significant interest from VCs and big tech firms.

This Al-driven momentum continues to bolster semiconductor brand equity, with Brand Finance research confirming NVIDIA's dominance. Brand Finance data also highlights NVIDIA's strong 'positive contribution' score, reflecting widespread consumer

trust and a strong market reputation. This enduring brand strength not only cements NVIDIA's leadership in the semiconductor industry but also positions it for sustained growth in an increasingly competitive market.

Looking ahead, a key question for the industry is sustainability—whether brands can maintain their value over time amid rapid advancements, including the recent launch of Deepseek."

NVIDIA CEO Jensen Huang also retains his position as the third-ranked CEO globally in the 2025 Brand Guardianship Index, securing the top spot in the semiconductor sector. Under Huang's visionary leadership, NVIDIA has not only advanced in Al but has also made significant strides in digital biology, climate science, autonomous vehicles, and robotics—sectors poised to reshape the future. According to Brand Finance data, Huang excels in familiarity, reputation, and is also recognised for his exceptional 'strategy and vision.'

The Brand Finance Semiconductors 2025 ranking has expanded from 20 to 30 brands, reflecting the intensifying competition and rising influence of emerging players in the semiconductor industry, particularly in Europe. This expansion highlights the sector's dynamic evolution, with new entrants such as UK-based Arm (brand value USD1.5 billion) and Dutch brand ASM (brand value USD837 million) making their mark.

Artificial intelligence remains a hotbed of controversy, investment, and innovation, drawing significant interest from VCs and big tech firms. This Al-driven momentum continues to bolster semiconductor brand equity, with Brand Finance research confirming NVIDIA's dominance

#### **INDUSTRY NEWS**

# ASML and imec sign strategic partnership agreement

ASML Holding N.V. and imec have signed a new strategic partnership agreement, focusing on research and sustainability.

THE AGREEMENT has a duration of five years and aims to deliver valuable solutions in two areas by bringing together ASML's and imec's respective knowledge and expertise. First, to develop solutions that advance the semiconductor industry and second, to develop initiatives focused on sustainable innovation.

The collaboration incorporates ASML's whole product portfolio, with a focus on developing high-end nodes, using ASML systems including 0.55 NA EUV, 0.33 NA EUV. DUV immersion. YieldStar optical metrology and HMI single- and multi-beam technologies. These tools will be installed in imec's state-of-theart pilot line and incorporated in the EU- and Flemish-funded NanolC pilot line, providing the most advanced infrastructure for sub-2nm R&D to the international semiconductor ecosystem. Focus areas for R&D will also include silicon photonics, memory and advanced packaging, offering full stack innovation for future semiconductorbased AI applications in diverse markets.

A new area in the collaboration consists of a significant contribution to fund innovative ideas and activities in imec's research funnel that bring environmental and societal benefits. ASML's president and CEO Christophe Fouquet comments: "This agreement marks the next step in the longstanding co-operation between ASML and imec. It signals our joint ambitions to develop solutions for the semiconductor industry and fits our strategy of investing in technology and innovation that will benefit society at large."

"We are excited to continue our longstanding unique partnership with ASML, offering the industry access to the most advanced patterning solutions for over 30 years," states Luc Van den

hove, President and CEO at imec, "The inclusion of ASML's full product portfolio will allow us to expand and further mature the capabilities of our pilot line, providing the entire semiconductor ecosystem with the most advanced R&D to tackle the challenges of Aldriven technological advancements. Since imec has a strong focus on sustainable innovation, having this explicitly included in our partnership is a great addition."

The ASML investment in the partnership is complemented with funding made available by the Chips Joint Undertaking and the Flemish government (for the realization of the EU Chips Act NanolC pilot line), and by the Dutch government (as an Important Project of Common European Interest). The acquisition and operation of the NanolC pilot line are jointly funded by the Chips Joint Undertaking, through the European Union's Digital Europe (101183266) and Horizon Europe programs (101183277), as well as by the participating states Belgium (Flanders), France, Germany, Finland, Ireland and Romania. For more information, visit nanoic-project.eu.

Making 0.55 NA technology available at imec was part of the Next Gen-7A project (IPCEI22201) funded by the Dutch government as an Important Project for Common European Interest (IPCEI).

The inclusion of ASML's full product portfolio will allow us to expand and further mature the capabilities of our pilot line, providing the entire semiconductor ecosystem with the most advanced R&D to tackle the challenges of Al-driven technological advancements. Since imec has a strong focus on sustainable innovation

# Don't carry defects through your processes.

Bump shift

Find systematic yield issues fabulously fast.

With our new smart 3D X-ray solution for the fab.

Head-inpillow

Bump tílt

yxlon.comet.tech

#### TECHNOLOGY I AI

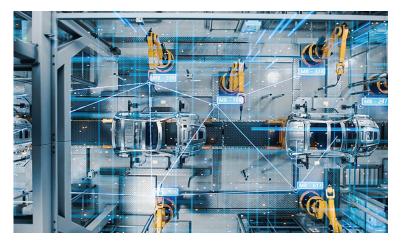

# Smarter by design: how AI is reshaping manufacturing in 2025

Al is at the heart of the manufacturing revolution, driving efficiency, sustainability, and precision as we head into 2025.

#### BY DIGANT SHAH, CHIEF REVENUE OFFICER (CRO) BOSCH SDS

ACCORDING TO a recent PwC report, AI adoption in manufacturing is expected to contribute \$4.6 trillion to the global economy by 2030, illustrating its huge potential. As CES 2025 prepares to spotlight the latest AI innovations, it's clear that AI-driven tools like robotics, predictive analytics, and digital twins are no longer optional but essential ingredients to the industry's future.

But integrating the technology isn't without its hurdles. Al-powered solutions that tackle critical challenges - from minimising waste to optimising energy consumption and enhancing decision-making - require significant levels of operationalisation to achieve their goals.

#### Al on the assembly line

The manufacturing sector is witnessing a revolution on the factory floor, driven by the integration of AI and robotics.

A McKinsey study highlights that AI can boost manufacturing productivity by up to 20% by improving processes and reducing downtime. Predictive maintenance plays a pivotal role here. By analysing real-time machine data, AI tools can anticipate equipment failures before they occur, enabling proactive repairs that save both time and money while keeping production lines running smoothly.

It's no surprise, then, that the impact of robotics automation is accelerating. The market is projected to grow at a 10% compound annual growth rate (CAGR) through 2025.

Assembly lines, once defined by manual labour, are one area in particular which is benefiting from the precision and efficiency of Al-powered robotics. These advancements are not only boosting speed and accuracy but also reducing the likelihood of costly errors.

As these technologies advance, assembly lines are evolving into centres of innovation, setting new benchmarks for precision, speed, and competitiveness in production. But they're not the only area in which innovation is accelerating.

### AI & Digital twins – doubling down on smarter decisions

Digital twins-digital replicas of physical

objects—are experiencing rapid adoption. In the manufacturing sector, 89% of organisations adopting digital twin technology have done so within the past two years, with 19% adopting it within the past six months.

Digital twins are being used to simulate and optimise factory workflows in real time, allowing manufacturers to test scenarios and refine operations before implementing changes on the ground. Al-based data analysis has also helped reduce cycle times during production ramp-ups by 15%, while new algorithms have streamlined component-testing processes, significantly enhancing efficiency. These advancements demonstrate how Al models and digital twins mirroring production lines can reduce energy usage and enhance production outputs without overextending resources.

By combining advanced simulations with realtime insights, digital twins are not only improving operational performance but also laying the groundwork for more sustainable manufacturing practices.

#### Efficiency meets responsibility

Sustainability remains a key priority for manufacturers, with the industry responsible for one-fifth of the world's carbon emissions.

Al can help manufacturers track and optimise energy consumption across every area of operation. By identifying inefficiencies and suggesting Aldriven adjustments, manufacturers can significantly cut emissions and costs.

Supply chain sustainability is another huge focus area. Al-powered tools enable predictive inventory management, reducing overproduction and minimising waste. A recent Capgemini report found that Al could cut supply chain emissions by 5-10%, in line with growing corporate ESG commitments.

As such, AI is enabling manufacturers to create leaner, greener supply chains, reducing waste and helping meet ambitious ESG targets without compromising operational performance.

#### Filling the (skills) gap

It's no secret that the manufacturing sector faces a widening skills gap, with over 2.1 million jobs expected to go unfilled by 2030, according to Deloitte. This shortfall not only threatens productivity but also risks slowing innovation in an industry that is rapidly evolving with the adoption of advanced technologies.

One solution lies in leveraging Al-enabled workforce strategies. By automating repetitive or routine tasks, manufacturers can free up human workers to focus on more complex, value-added roles. Beyond automation, Al also supports upskilling initiatives, helping employees adapt to new technologies and work collaboratively with AI systems. This dual approach empowers workers, enhances efficiency, and builds a future-ready workforce.

#### Keeping AI in check

Ethical AI implementation is equally critical to manufacturing's future. Transparency, privacy, and worker safety must remain at the core of any AI strategy.

Crucially, the building blocks for Ethical AI in manufacturing hinges on five key things. Transparency, fairness, privacy, accountability and human oversight. Bosch SDS prioritises these principles, ensuring AI adoption respects ethical standards and aligns with initiatives like the World Economic Forum's advocacy for "ethical AI governance."

We use our Sure.Al framework, which merges Al innovation with ethical governance standards. We also use Computer Vision based solutions to ensure worker safety and these algorithms are tested continuously to ensure that there are no biases developed over time. Such efforts not only mitigate potential risks but also build trust among employees and stakeholders, fostering greater acceptance of Al in manufacturing.

### Al: the blueprint for smarter manufacturing

To begin integrating AI and driving smarter, more sustainable operations, manufacturers should launch small pilot projects to test their solutions before scaling up. Investing in employee training also ensures teams are equipped to collaborate effectively with AI systems. Al-literate employees who can leverage real-time insights are the key to agile, data-driven decision-making that enhances efficiency.

As we approach 2025, the opportunity to transform operations for the better is at hand. By embracing AI and building partnerships with technology providers, manufacturers can streamline processes, improve decision-making, and drive sustainability—paving the way for a smarter, greener, and more efficient future.

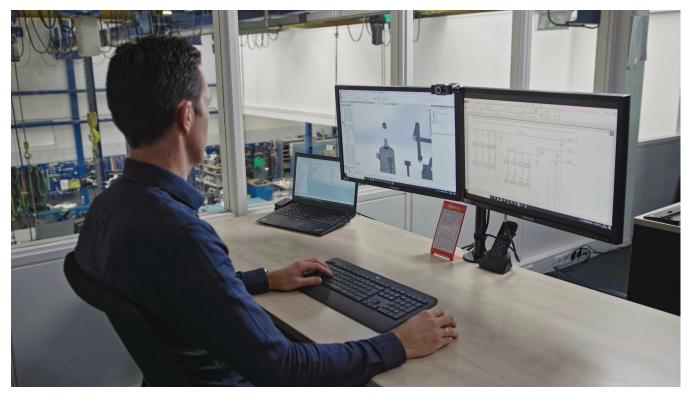

### Biometric ID drives semiconductor manufacturing security and efficiency

The wrist-worn Nymi Band using biometric ID is expediting secure, hands-free authentication across semiconductor fabs, dramatically increasing productivity.

#### BY ARISTA BIOMETRICS

SEMICONDUCTOR manufacturers have traditionally been hindered by the need to authenticate operator identity across a complex patchwork of access points, workstations, and tools. Using badges, passwords, and other means of authentication has been slow, requiring the use of gloved hands, and could always be utilized independent of the intended operator, an inherent security flaw.

Wafer fabrication is a highly intricate process that demands precise execution, stringent control, and strong security protocols to safeguard intellectual property, protect sensitive information, and adhere to industry regulations. Conventional authentication approaches, such as passwords and hardware tokens, are often inadequate, inefficient, and insecure, particularly for deskless workers. This challenge is especially pronounced in

> semiconductor fabs, where employees are required to wear gloves and full-body suits while working in cleanroom conditions.

> > In response, semiconductor manufacturers are increasingly turning to wearable biometric ID products like wristworn Nymi Bands to securely speed authentication in a hands-free manner.

These innovative, wearable wristbands blend biometrics, security, and privacy, digitally empowering employees with passwordless, contactless workflow across applications, systems, and networks. Employees simply wear their Nymi Band, authenticate as little as once per day, and work until they want to disconnect, according to the OEM's solutions brief "Connected Workers in a Passwordless World."

When used to facilitate employee entry to access points, tools, and equipment, wearable biometric identity products are significantly increasing security and productivity.

Now, computing solutions providers are providing scanners that can instantly read biometric wearables such as bands. When used with equipment such as mobile workstations, the combination is enabling seamless identification and authentication of authorized users throughout semiconductor fabs, further enhancing safety and efficiency.

"Using unique biometric ID wearables like Nymi bands is not only more secure than utilizing credentials [such as passwords] that can be compromised, but also enables much faster access to a wide range of tools. When utilized with equipment such as mobile workstations or handheld devices that require authorization to use, the combination unlocks greater productivity," says Paul Shu of ARISTA Corporation, a leading provider of computing platforms and visualization display products for semiconductor manufacturing environments.

"Ultimately, the wearable bands provide much greater security to semiconductor fabs. Employees cannot take someone else's band and log into a computer since each band corresponds with the operator's specific biometric data," adds Shu.

#### Streamlining connectivity

Semiconductor fabs often consist of hundreds of systems and applications that require proper user identification to access and use. Traditionally, the burden of providing and managing separate identification credentials has fallen on the employee, which has resulted in increased stress and decreased productivity.

Mobile workstations are now available with an optional NFC reader that can be used throughout semiconductor manufacturing facilities with biometric wearables and other forms of identification.

The wafer fabrication process in semiconductor manufacturing takes place in an ultraclean environment where high-precision equipment is used, necessitating strict trackability and traceability.

Deskless operators in these facilities move between multiple machines, systems, and terminals throughout their shifts. Depending on the task, they may use devices such as desktop computers, tablets, or human-machine interfaces (HMIs). This frequent movement, coupled with the need to switch between various systems, makes conventional authentication methods like password entry or USB keys inconvenient, prone to errors, and inefficient.

Additionally, the use of PPE garments designed to minimize contamination from the operator further complicates traditional authentication processes like typing passwords or using hardware tokens.

Today, a new approach is enabling identity to be authenticated once per person while allowing the platform to facilitate connections to the required systems. Employees no longer assume the burden of manually authenticating their identity at each access point.

An example of this more streamlined, integrated approach to identification and access is the increased adoption of the Nymi Band at semiconductor fabs. The biometric wristband works in conjunction with the Nymi Connected Worker Platform, which creates an intermediary layer between employees and their employer's complicated IT infrastructure. The Platform establishes the biometric security and privacy of its users and allows them to inter-operate between disparate technologies.

Employees authenticate to their Nymi Band as little as once per day through their fingerprint, which takes less than a second. The device's on-body detection capability enables an assigned employee to use it continually throughout all of their integrated applications. Employees simply take off their Nymi Band to deactivate and disconnect from their workplace, according to the OEM's solutions brief.

To enhance security, the Nymi Band is authenticated via fingerprint and verified against a mathematical template created at enrollment. Biometric images are never stored, and templates are secured locally in the band.

Employees can use their wearable band to efficiently gain hands-free access to terminals, email, applications, doors, and Biometric ID wearables like Nymi Bands are much more secure than any other NFC device, so are ideal for logging into a wide range of devices at semiconductor fabs. When used with equipment such as mobile workstations, the combination can further promote productivity, allowing the work to occur where needed

elevators throughout a facility, as required for their official duties. Access can be custom set according to the user's role, to appropriately protect sensitive information and areas.

Paul Shu of ARISTA Corporation notes that biometric wearables pair with short-range wireless Near Field Communication (NFC) technology to expedite identification, authorized access, and communication. This is the case, for example, with ARISTA's mobile workstations, which are now available with an optional NFC reader that can be used throughout semiconductor fabs with biometric wearables and other forms of identification. NFC readers and related technologies are widely employed across industries for tasks such as asset management, inventory control, equipment monitoring, and enhancing security.

> While other mobile workstations must be plugged into the wall to function. ARISTA's Mobile Operator Workstation can move from place to place while in operation free of wires due to its powerful lithiumion battery. Wi-Fi capability is built into the workstation to allow for uninterrupted wireless communication in all corners of the cleanroom and fab. In addition, most advanced semiconductor fabs today have Wi-Fi-based system backbones connected to legacy subsystems, meaning the workstation can communicate directly with the fab's server.

"Biometric ID wearables like Nymi Bands are much more secure than any other NFC device, so are ideal for logging into a wide range of devices at semiconductor fabs. When used with equipment such as mobile workstations, the combination can further promote productivity, allowing the work to occur where needed. The technology provides greater security, convenience, and efficiency, so we expect its use to grow in the industry and beyond," concludes Shu.

> Mobile workstations with NFC readers enable biometric wearables to provide seamless identification and authentication of authorized users throughout semiconductor fahs

# The geopolitics of the semiconductor industry: navigating a global power struggle

Nations are racing to control the semiconductor technologies that power everything from consumer gadgets to defence systems. With supply chain issues, national security concerns, and economic goals all at play, the competition to lead this sector has never been more intense.

#### BY DUNSTAN POWER, DIRECTOR OF EMBEDDED DESIGN CONSULTANCY BYTESNAP DESIGN

HERE we explore the dynamics shaping the semiconductor industry, from the intensifying US-China rivalry and Taiwan's pivotal role to the global push for supply chain resilience, the rise of AI and EVs, and the challenges faced by regions like Europe and India in carving out a foothold in the sector.

US-China tensions and the semiconductor race At the centre of semiconductor geopolitics lies the rivalry between the United States and China. While Washington seeks to maintain its technical and economic dominance, Beijing is rapidly growing its semiconductor capabilities. Allegations of intellectual property theft and questionable practices are further fuelling tensions. While US sanctions, which block China's access to advanced manufacturing equipment, have slowed its progress, they have not dented its long-term goal of becoming a global leader in chip production. Despite its efforts, China remains 5–10 years behind in the most advanced semiconductor technologies. The gap between its global market share in semiconductor equipment supply (3.2%) and its share of demand (34.4%) further underscores the significant challenge it faces in achieving self-sufficiency.

To counter China's semiconductor ambitions, the US enacted the CHIPS Act, a key initiative aimed at boosting domestic production and restricting China's access to advanced manufacturing equipment. However, the future of the legislation is uncertain following President Donald Trump's sharp criticism during his campaign, which has raised doubts about the continuity of projects funded by the Act. This includes a £6.29 billion grant finalised by the Biden administration for Intel's semiconductor plant in Ohio, which some GOP lawmakers are keen to protect despite broader Republican support for cost-cutting measures.

#### INDUSTRY I SUPPLY CHAIN

Taiwan plays a pivotal role in the semiconductor industry, with TSMC producing over 50% of the world's chips. This dominance has raised concerns from governments and businesses like Apple about geopolitical risks from potential conflict with China. In response, TSMC is diversifying its operations by constructing new fabs in Arizona and Japan, though these facilities will contribute only about 10% of its total silicon output. Despite these initiatives, the majority of production will remain in Taiwan, highlighting the challenges of reducing reliance on a single region – a process that will take years to fully materialise.

The Netherlands has also been drawn into this geopolitical struggle, with its leading lithography equipment company, ASML, facing pressure to limit exports to China. These lithography machines, especially those using extreme ultraviolet (EUV) technology, are critical to advanced chip production and represent a linchpin in the semiconductor ecosystem. Although the Dutch government has taken steps to align with US sanctions, questions remain about the extent of its compliance.

Supply chain challenges and the road to recovery The COVID-19 pandemic laid bare the fragility of global semiconductor supply chains. A surge in demand for electronics and automotive components created an acute shortage, with lead times stretching beyond a year. During this crisis, China absorbed a significant share of global demand. However, as the pandemic's supply chain pressures eased in early 2023, the industry faced a new problem: overproduction and excess inventories. Companies, having overordered during the crisis, found themselves saddled with surplus chips, dampening innovation and creating market instability.

Despite the challenges, the semiconductor industry is rebounding, largely driven by the surging demand for artificial intelligence (AI) applications. Al-specific chips, such as those produced by Nvidia, have experienced explosive growth, marking a significant shift in market priorities. The AI chip market, valued at £49.1 billion in 2023, is projected to grow at a compound annual rate of 29.4%, reaching £496.9 billion by 2032.

Another key driver is the rising integration of semiconductors in electric vehicles (EVs). Globally, 15.2 million EVs were sold in 2024, reflecting a 25% year-to-date increase, according to Rho Motion. China leads the charge, setting a record with 1.3 million units sold in November 2024 alone, almost entirely from battery electric vehicles (BEVs). Brands like Geely, Tesla, and Changan were among the top sellers, further cementing China's dominance in the EV market.

China's high EV sales have profound geopolitical implications for the semiconductor industry, as EVs rely heavily on advanced chips for critical systems. By leading global EV adoption, China is solidifying its influence in the semiconductor sector, even as it remains dependent on foreign technology. This dynamic heightens competition with the US and Europe, driving their efforts to secure supply chains and reduce reliance on Taiwan for chips and China for EV technologies. At the same time, China's integration of domestic semiconductor development into its booming EV industry strengthens its position in the global tech race, making semiconductors a focal point of both economic strategy and geopolitical power conflicts.

Europe's struggles in the semiconductor landscape Europe, while home to significant players like NXP and STMicroelectronics, has long been overshadowed by its US and Asian counterparts. The region faces several challenges, including a lack of large-scale investment and a struggling automotive sector. Germany, the largest electronics market in Europe, exemplifies these difficulties, with its car manufacturers grappling with the transition to EVs. Meanwhile, China is taking the lead in EV technology, putting further pressure on Europe's traditional industries.

In response, the European Union has pledged billions in subsidies to bolster its semiconductor sector. For instance, Germany recently announced  $a \in 2$  billion investment aimed at strengthening chip manufacturing. While this is a step in the right direction, the scale of investment pales in comparison to the costs of building state-of-the-art fabs. There is, however, a need for greater financial commitments to reduce reliance on non-European manufacturers and foster more innovation. Europe's progress is, however, hampered by bureaucratic red tape and political vacillation.

Unlike the US, which has adopted a more aggressive approach to reshoring manufacturing, Europe appears to be on the sidelines of this global competition. The UK, in particular, has little influence, with limited government investment and a reliance on allies for strategic direction. Efforts to block Chinese acquisitions, such as the attempted purchase of a fab in Wales, highlight the UK's

#### INDUSTRY I SUPPLY CHAIN

defensive posture but do little to address its lack of domestic manufacturing capability.

Global trends reshaping the semiconductor industry The semiconductor industry is navigating a critical period of transformation. Diversification of manufacturing, while necessary to mitigate risks tied to Taiwan's dominance, highlights the sheer complexity and cost of redistributing global supply chains. The strategic investments in fabs across the US, Japan, and Europe signal progress, but achieving meaningful independence will require years of sustained effort and collaboration.

Al and electric vehicles are reshaping semiconductor design and production, driving demand for specialised chips that power these transformative technologies. This shift creates opportunities for regions like India, with its £12 billion investment in chip-packaging plants and its first modern chip fab, and Europe to carve out niches. However, realising this potential will also require solutions to critical talent shortages. The expertise required for semiconductor design and manufacturing is concentrated in regions like Taiwan and South Korea, where decades of focused development have cultivated a highly skilled workforce. New entrants to the industry, such as India, face significant challenges in building this specialised talent pool, with red tape and bureaucratic hurdles adding further delays. Even with AI assisting in aspects of chip design, the deep, specialised knowledge needed for tasks such as coding, placement, and fabrication remains irreplaceable by automation.

At the heart of these trends is a renewed emphasis on resilience. Nations and corporations are beginning to view semiconductors as strategic assets, integral to both economic stability and national security. This recalibration is fostering an ecosystem where long-term innovation and crossborder collaboration may ultimately outweigh competition. If governments and industries align their priorities effectively, the semiconductor sector could emerge not only stronger but also more decentralised and inclusive, offering a more secure foundation for future technological growth.

SMART MOBILITY ഫ

SMART MEDTECH

Connecting Semiconductors and **Electronics**

About SEMI:

SEMI connects more than 2,500 member companies and 1.3 million professionals worldwide to advance the technology and business of electronics design and manufacturing. The breadth and depth of our events, programs and services help members accelerate innovation and collaboration on the toughest challenges to growth.

SMART DATA-AI

᠈ᢑᡏ

WORKFORCE DEVELOPMENT

> Global ADVOCACY

> > Sustainability

MARKET INTELLIGENCE

1000+ **STANDARDS**

THOUGHT LEADERSHIP

SEMICON

TECH COMMUNITIES

SEMI UNIVERSITY

Cyber Security

# Innovative approaches to scaling network-on-chip architectures

The evolution of cloud computing has sparked a pressing need for advanced solutions that maximize computational efficiency while minimizing physical and energy constraints. Modern data centers depend heavily on multi-core processors, often packing over 100 cores into a single chip.

# BY MORITZ BRUNION, RESEARCHER DESIGN-TECHNOLOGY CO-OPTIMIZATION AND JAMES MYERS, PROGRAM DIRECTOR SYSTEM TECHNOLOGY CO-OPTIMIZATION, BOTH AT IMEC.

THESE PROCESSORS are designed to handle the growing demands of cloud-based applications by sharing network, memory, and storage resources, transforming each core into a rentable unit of processing power.

However, as processors grow more powerful, the network-on-chip (NoC) has emerged as a critical

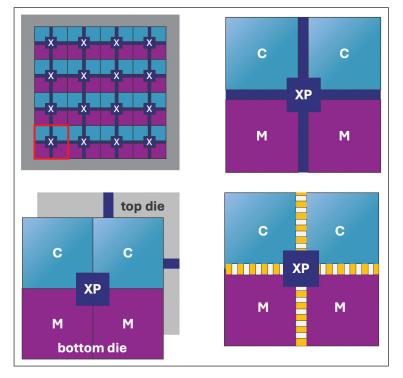

> Figure 1. 2D reference system (top left) and tile (top right) with NoC channel routes and logic within a single FEOL and BEOL stack. In the bottom are the two new approaches depicted: (left) 3D stacking design, showing the separation of NoC channel routes into a dedicated routing die bonded to the A10 logic die, and (right) the backside integration approach, showing NoC channel routes integrated into the backside metal layers of the BSPDN. bottleneck in scaling. The NoC, tasked with routing data among CPU cores and memory, relies on metal interconnects that present unique challenges when scaled down. Higher resistance in these interconnects increases power consumption and necessitates additional signal repeaters to maintain performance over long distances.

Adding to this, the increasing core count and HD logic scaling, while maintaining the same NoC dimensions, drive a significant rise in NoC area. These factors add complexity and compromises the goal of achieving smaller and more efficient designs.

Addressing these challenges has led to a variety of innovative solutions, though none without tradeoffs. 2D mesh topologies, while straightforward and scalable, struggle with communication latency as the number of cores increases.

Other approaches, such as routerless configurations or workload-specific optimizations, can improve performance but are often impractical for generalpurpose systems like those used in cloud computing. While scaling the NoC link throughput by an increase in the number of signals per channel can increase the throughput, it often results in higher costs and resource demands, further complicating the NoC landscape.

In response to these constraints, imec researchers have pioneered two transformative approaches: relocating NoC channels to a dedicated die and integrating them with the backside power delivery network (BSPDN). These strategies, guided by system-technology co-optimization (STCO) principles, aim to overcome scaling limitations while balancing cost and performance. Of these, the cointegration of NoC channels with the BSPDN offers particularly promising results for future design of such high core-count systems.

#### TECHNOLOGY I RESEARCH

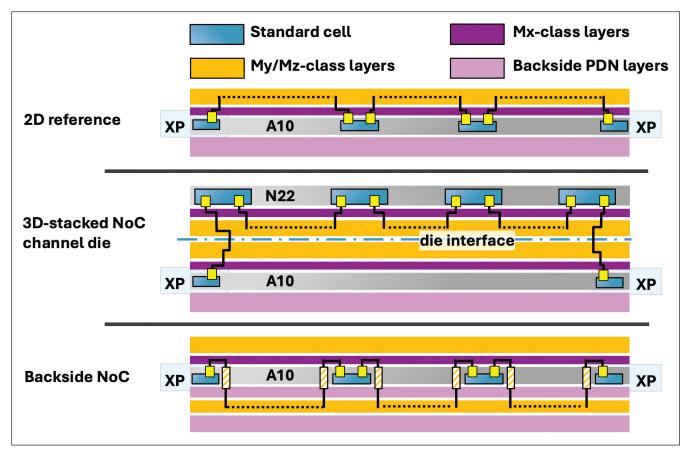

> Figure 2. (Top) The technology stack cross-section for the 2D reference shows both NoC channels and crosspoints (XP) in the A10 logic frontend. (Middle) The NoC routing is entirely offloaded to a dedicated die freeing up placement and routing resources on the main logic die. In this case, channels in the separate die are manufactured in older technology while the crosspoints reside in the A10 logic. (Bottom) The NoC channels sharing routing resources with the power delivery network and repeaters located on the logic die front-end. NoC buffer islands occupy 1-2% of a high-performance CPU core (compared to up to 10% of the silicon area being dedicated to the NoC in the 2D reference), with the addition of two dedicated backside metal layers for NoC channels.

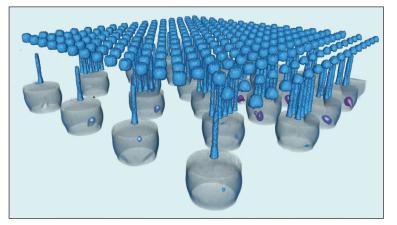

### Dedicated NoC routing on a separate die

One novel approach proposed by imec involves offloading the NoC channel routes to a dedicated die, independent of the main logic layers. Using wafer-to-wafer face-to-face hybrid bonding, this architecture can leverage the high-bandwidth data transfer in the vertical direction with minimal energy usage per bit. The NoC die can be fabricated using a less advanced manufacturing process, such as N22, significantly reducing production costs.

This design also simplifies the back-end-of-line (BEOL) configuration by using fewer metal layers, thereby optimizing functional integration efficiency. The NoC routers, which make real-time routing decisions, remain on the main logic die, ensuring that latency is kept to a minimum.

This design, however, is not without its challenges. Power distribution becomes more complicated, as the additional die requires its own power infrastructure. Physical design experiments also revealed an 8% increase in propagation delay and a 15% rise in energy per bit transferred across a channel link compared to conventional 2D NoC systems.

#### Backside integration with the BSPDN

A second solution involves co-integrating NoC channels with the BSPDN on the backside of the wafer. The BSPDN's existing metal layers, optimized for power delivery with wider pitches and lower resistance, provide an ideal foundation for routing NoC channels over long distances at high clock speeds. This integration takes advantage of the relaxed design constraints of backside interconnects to achieve efficient signal transmission.

To implement this approach, the researchers made several design adjustments. First, they devised a bidirectional wiring scheme, enabling both horizontal and vertical NoC channels to share the same metal layer. This reduces the total number of required layers, lowering both costs and the overall chip footprint. Second, since BSPDN currently doesn't support active devices on the backside, signal repeaters were placed as compact "islands"

on the main logic die. These repeaters ensure robust signal strength at a small area overhead, while freeing up the channel routing footprint in the main logic die for other logic components. Finally, integrating NoC channels with the BSPDN required addressing the shared routing resources between data and power delivery, which increases the risk of IR drop and can affect performance. To mitigate these challenges, the researchers traded-off the PDN pitches and IR drop against the area overhead of the repeater islands, maintaining the benefits of the BSPDN and ensuring stable voltage levels, while also supporting reliable data transmission across the NoC.

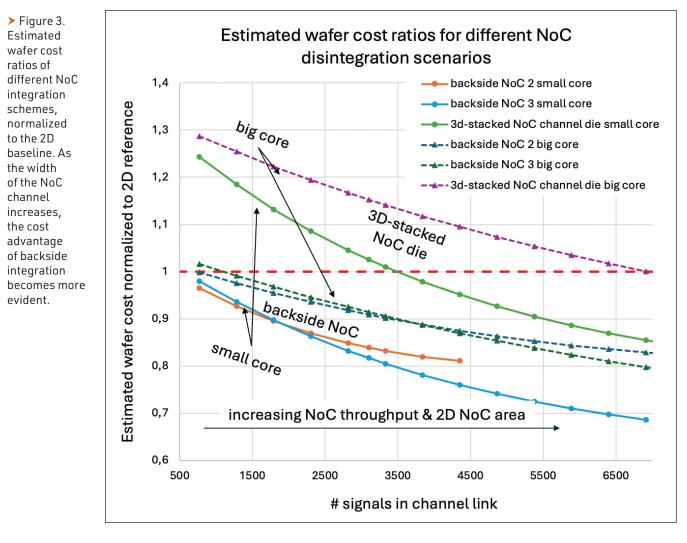

### Cost-benefit analysis favours NoC backside integration

When comparing the two approaches, not only their technical trade-offs but also cost-effectiveness is important to identify the best solution for growing

demands. The dedicated die method offers greater flexibility and customization options but incurs higher manufacturing costs due to the need for an additional fully processed wafer. By contrast, integrating NoC channels with the BSPDN reuses existing infrastructure, adding only a few extra metal layers. This significantly reduces costs and optimizes the use of front-side silicon, making it an attractive option for applications requiring high core densities, such as cloud server CPUs.

Backside integration also excels in scalability. As core counts per processor continue to rise, the demand for wider NoC channels increases. By leveraging the backside metal layers, this approach minimizes congestion and enables higher data throughput without substantially increasing the silicon footprint. These attributes make it a compelling solution for next-generation chip architectures.

To mitigate these challenges, the researchers traded-off the PDN pitches and IR drop against the area overhead of the repeater islands, maintaining the benefits of the BSPDN and ensuring stable voltage levels

### Broader implications and future directions

While backside NoC integration is highly applicable for cloud server CPUs, its relevance to other applications, such as GPUs and accelerators with coarse-grained, regular topologies, is still being explored. However, widespread adoption of this technology depends on advancements in Electronic Design Automation (EDA) tools. Currently, implementing backside NoC channels requires specialized workflows, which can be labor-intensive and costly. As EDA tools evolve, they are expected to streamline the design process, making backside integration more accessible and practical for a variety of use cases.

In conclusion, the integration of NoC channels with the BSPDN represents a significant breakthrough in chip design. By addressing routing and power delivery challenges simultaneously, this approach exemplifies the power of STCO principles. As the demand for scalable, high-performance architectures continues to grow, innovations like backside NoC integration will play a pivotal role in shaping the future of semiconductor technology and driving the next wave of computational advancements.

# W F M

#### Moritz Brunion

**Researcher Design-Technology Co-optimization** Moritz Brunion received the M.Sc. degree in electrical and computer engineering from the University of Bremen, Germany, in 2022. He is

currently a researcher at imec, Leuven, Belgium, and his research focuses on design-technology co-optimization for finegrained 3D systems.

#### James Myers

Program Director System Technology Cooptimisation

James Myers holds a MEng degree in Electrical and Electronic Engineering from Imperial College in

London. He spent 15 years at Arm, leading research from low power circuits and systems, through printed electronics, to DTCO activities. He joined imec in 2022 to lead the System Technology Co-optimisation program, with the aim of building upon established DTCO practices to overcome the numerous scaling challenges foreseen for future systems. James holds 60 US patents, has taped out 20 SoCs, has presented at ISSCC and VLSI Symposium, and has published in IEDM and Nature.

### perc

High cost savings

### Get rid of your solvents.

Cut costs by eliminating solvents while achieving 100% polymer removal. perc<sup>™</sup> offers flexible solutions for removing residues after dry etching, including metal, oxide, silicon, or VIA etching.

siconnex

siconnex.com

#### INTERVIEW I SEMIEUROPE

# Europe's semiconductor industry focuses on sustainable growth

Laith Altimime, President of SEMI Europe, discusses the challenges and opportunities facing the European semiconductor industry. Laith talks sustainability, collaboration, technology innovation, skills and geopolitics, sharing his excitement for the industry's future as it underpins the ongoing development of our digital world.

> **SIS:** The theme of last year's Semicon Europa, towards the end of 2024, was, innovation collaboration, powering sustainable and exponential growth. It would be good to understand what was the thinking behind this focus, as well as how did the event go?

> LA: Th event went exceedingly well. I think the feedback was tremendously positive. Semicon Europa is and will always be a pivotal event, and an exciting opportunity for the European semiconductor ecosystem, providing a platform for collaboration, innovation, and knowledge sharing.

The focus on innovation and collaboration is powering sustainable, exponential growth. It's very much the statement of the industry, which is the goal for a holistic, forward-thinking approach. And it recognises that the pace and scope of growth required to meet the global demands cannot be achieved through isolated efforts. It very much calls for leveraging cutting edge technologies alongside collaborative efforts across industries, borders, and across sectors to create sustainable, scalable digital future.

Ultimately, the thinking behind the theme underscores that the future must be built on technological advancement, cooperation, collaboration, and sustainability, all working together to generate exponential progress in a way that respects both the planet and humanity, which is really the key contribution of the semiconductor industry.

**SIS:** Perhaps we can drill down into a little more detail, starting with sustainability. It's clearly a major focus for the industry. And it'd be good to understand how you would perhaps characterise the work that's been done so far, and maybe contrasting it with what more remains to be done?

LA: Sustainability is part of the industry's exponential growth, the target to reach or even exceed \$1 trillion global industry revenue by 2030. Sustainability has become a critical focus across industries, particularly in the semiconductor and tech sectors, as they play a central role in global carbon emissions, resource consumption, and electronic waste. It's key to state that that the semiconductor industry has made substantial strides towards sustainability, particularly in the areas like energy efficiency, material recycling, and renewable energy adoptions. These are fundamental, you know, in terms of enabling the industry to transition and to contribute. However, achieving Net Zero, requires the addressing of the broader environmental impacts associated with the entire supply chain, e-waste, carbon emissions from the semiconductor manufacturing and product usage. Ultimately, the semiconductor industry's path to Net Zero will depend very much on continued innovation and collaboration and a willingness to adopt circular economy principles, from design and manufacturing to end of life disposal.

Although this journey is complex, with really concentrated efforts, the industry can play a pivotal role in a sustainable Net Zero future.

**SIS:** Collaboration has been mentioned a couple of times - there does seem to be a growing, even a final recognition that, in many cases, the challenges and the opportunities for the sector are just too complex, sizeable and expensive to be tackled by individual organisations. There is a growing need for collaborative partnerships, whether that's research to commercial or commercial organisations working each other. How would you characterise this necessity and how it is working in practise?

LA: Yes. You you're absolutely right. The semiconductor sector, like many other high-tech and industrial sectors, is facing challenges and opportunities that are increasingly too complex as the industry continues to growth. And one needs to keep in mind that the industry growth or doubling by 2030 is basically doubling what it has taken to reach today's figure – just over \$600 billion over five decades.

Within the next five to seven years, the challenges of complexity and the speed of innovation required cannot be tackled by a single CEO, single country or single company. There needs to be a global collaborative effort, and SEMI has provided these platforms. They've grown in recognition that collaborative partnerships, whether between commercial organisations, research institutions, or even public/private entities are key for tackling the complex, large scale, unprecedented challenges of the semiconductor industry. The demand for innovation in areas like AI, quantum computing and sustainability is vast.

By leveraging collective expertise, shared resources, and joint development - collaboration - the semiconductor industry can address these unprecedented challenges. SEMI has the necessary global footprint and has launched the SEMI International Policy Summit, to bring together the industry, academia, and the policy makers to educate all on generating the new policies required to help the industry advance towards the 2030 target.

**SIS:** Slightly opposed to this collaboration, or at least not necessarily fully in line, there is this growing trend towards reshoring or onshoring. Do you think that is specifically anti-collaboration? And what impact is it having on the industry overall – is it weakening or strengthening it?

LA: It's right to highlight the growing trends towards reshoring and onshoring, it's very much in the spotlight today. It's driven by several factors, including geopolitical tensions. This is really very high on the agenda today. Along with the supply chain, which can also experience geopolitically induced disruptions. National security concerns are

#### INTERVIEW I SEMIEUROPE

very high on the agenda. There is a desire to reduce dependence on foreign sources.

The solution it to think global, act regional - by integrating into a broader strategy of collaboration, both within Europe and globally, we can achieve the best of both worlds - stronger regional capabilities while still participating in global ecosystems when it comes to innovation, research, commerce. It's key to keep in mind that the industry's future hinges on this delicate balancing act, with geopolitical tensions the overriding issue.

**SIS:** In terms of innovation within the industry, advanced packaging and fab production management are near the top of the industry's priority list. It would be good to understand how excited you are about work in this area and any other innovations that you might want to highlight?