# **SEBUCION SEMICONDUCTOR COMMUNITY**

# THE CHALLENGE OF DECARBONISING THE SEMICONDUCTOR INDUSTRY AND FULFILLING CHIP DEMAND

AN ANGEL BUSINESS COMMUNICATIONS PUBLICATION

O DECARBON I

#### VOLUME 45 ISSUE III 2024

#### INSIDE

News Review, Features News Analysis, Profiles Research Review and much more...

#### Wafer-level integration of ALD for 2D Materials

Meeting the challenges of advanced process development for the integration of ALD grown 2D materials at wafer level

#### Chasing the swarm: the new challenge for chip manufacturers

From the geopolitical sparring of China and the US to the global supply chain upon which we all depend

#### SILICONSEMICONDUCTOR.NET

#### Lasers: a sustainable wafer heating solution

Lasers, in particular diode lasers, are an attractive and sustainable option for future chipmaking needs WINNER OF THE PRODUCTRONICA INNOVATION AWARD

OUR NEW BATCH TOOL FOR HIGH THROUGHPUT WET PROCESSING

**Compact design** for optimal use of the clean room

Fast processes through high process temperature of up to 170°C

**Uninterrupted production flow** via warehouse with up to 75 storage locations and automated loading connected to the transport system

# Reduction of particle generation & contamination

by improved access and optimized extraction of the process chamber

# WE ARE YOUR PARTNER FOR WET PROCESS EQUIPMENT

AP&S International GmbH . Obere Wiesen 9 . 78166 Donaueschingen . Germany . 0771 8983 0 . sales@ap-s.de . www.ap-s.de

# VIEWPOINT

By Phil Alsop, Editor

# Collaboration - the way forward

IN PREPARING the potential news stories for this issue of SiS, I was struck by the sheer quantity of stories on our website which highlight some of the many initiatives which individual countries, and both smaller and wider regions, are undertaking in pursuit of what seems to be the major focus on onshoring or reshoring.

In no particular order, I read stories referencing EU, Swiss, Japanese, Indian, German, UK and US projects, designed to increase the semiconductor industry footprint in each location.

So, much more local activity, but on a global scale.

I guess the major choice facing any local, national or regional government is what is possible, practical and, ultimately, affordable, in terms of encouraging the development of a semiconductor industry 'closer to home'. Key to making this decision is a good understanding of who is doing what, where and how. In other words, there are several options which can be pursued when it comes to playing in this space.

At the highest level, there's the possibility to create a complete, large scale, end-to-end semiconductor manufacturing supply chain. Such a strategy comes with an incredibly high price tag, but maybe one worth paying in terms of the security it provides, as well as the potential commercial return over the medium to long term. For most locations, the investment required for such an approach is prohibitive. This then leaves the

decision of what area(s) in which to specialise and/or how to collaborate with other like-minded and nearby locations to develop a semiconductor focus which promises to deliver a level of specialist knowledge and expertise which can compete with the end-to-end approach in one or more part of the semiconductor industry supply chain.

It's fascinating to hear and read about all of the many partnerships and initiatives which are a part of the industry's evolution right now. Theoretically, there's room for everyone to share in the industry's predicted expansion and success, heading towards the \$1 trillion/2030 objective. And sharing would seem to be the name of the game. Working with others – government at all levels, academic bodies, other vendors and, importantly, potential and actual customers – gives the best possible chance of success. I look

forward to more and more examples of industry collaboration bringing huge benefits to many over the coming months.

For your free weekly e-news roundup go to: siliconsemiconductor.net

# CONTENTS

#### VOL 45 ISSUE III 2024

### The challenge of 14 decarbonising the semiconductor industry and fulfilling chip demand

The semiconductor sector is an essential part of our increasingly digital environment. There can't be a future without semiconductors, but their widespread use also presents growing environmental challenges

#### 18 Effective hermetic sealing for next-generation packaging

A perfectly sealed electronic package can fulfill its intended function without disruption, error or a significant reduction in performance for decades

#### 26 Lasers – a sustainable wafer heating solution

Lasers, in particular diode lasers, are an attractive and sustainable option for future chipmaking needs

#### 28 Chip, Chip, Hooray! Addressing connected semiconductor and chip growing pains

The rise of the Internet of Things (IoT), artificial intelligence (AI), and 5G has ushered in an era of unprecedented connectivity and automation

# **30** Wafer-level integration changes of ALD for 2D materials

Meeting the challenges of advanced process development for the integration of ALD grown two-dimensional (2D) materials at wafer level

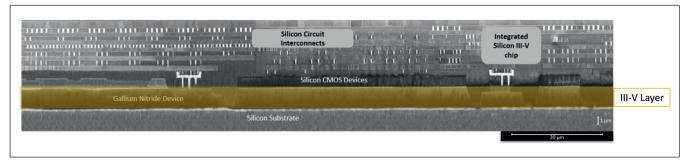

#### 34 How to integrate silicon and III-Vs

To draw on all the traditional benefits that come from scaling, silicon and the III-Vs must be united via epitaxy and processing in silicon foundries

# 40 Chasing the swarm: the new challenge for chip manufacturers

From the geopolitical sparring of China and the US to the global supply chain upon which we all depend, those watching the worldwide semiconductor market will be witnessing an ever-changing environment – and one that's now never far from the news

#### 42 Waging a war on wastewater

Next-level water utilization and recycling for increased capacity means adopting newer technologies

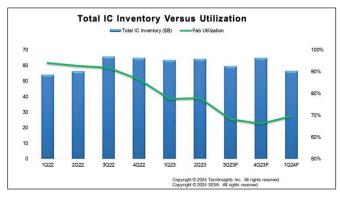

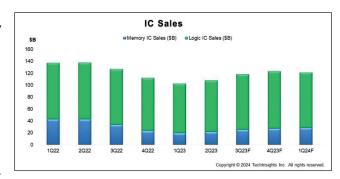

#### 45 Industry poised for 2024 recovery

The global semiconductor manufacturing industry recovery is taking hold with electronics and IC sales increasing in the final quarter of 2023 and more growth projected for 2024

#### NEWS

- **06** EU Consortium accepting Edge-AI design proposals

- **07** Intel launches Systems Foundry designed for the AI era

- **08** Saxony-Anhalt embraces change as an opportunity

- 09 Taalas emerges from stealth

- 10 Rolls-Royce supplies mtu Kinetic PowerPacks for X-FAB Sarawak

- 11 SemiQon ships silicon-based quantum chip and transistors

- 12 Tata Group to build India's first indigenous facility in Assam

- 12 £35m boost for British semiconductor scientists and businesses

Publisher Jackie Cannon Editor Phil Alsop Sales & Marketing Manger Shehzad Munshi Marketing & Logistics Executive Eve O'Sullivan USA Representatives Tom Brun Brun Media Janice Jenkins

Director of Logistics Sharon Cowley Design & Production Manager Mitch Gaynor jackie.cannon@angelbc.com +44 (0)1923 690205 phil.alsop@angelbc.com +44 (0)1923 690215 eve.osullivan@angelbc.com +44 (0)2476 823123 tbrun@brunmedia.com +001 724 539-2404 jjenkins@brunmedia.com +001 724-929-3550 sharon.cowley@angelbc.com +44 (0)1923 690200 mitch.gaynor@angelbc.com +44 (0)1923 690214 Chief Executive Officer Sukhi Bhadal Chief Technical Officer Scott Adams Directors Jackie Cannon, Sharon Cowley sukhi.bhadal@angelbc.com scott.adams@angelbc.com +44 (0)2476 718970 +44 (0)2476 718970

Published by Angel Business Communications Ltd, 6 Bow Court, Fletchworth Gate, Burnsall Road, Coventry CV5 6SP, UK. T: +44 (0)2476 718 970 E: info@angelbc.com

Silicon Semiconductor is published ten times (6x print and 4x video issues) a year on a controlled circulation basis. Non-qualifying individuals can subscribe at: £50.00 per annum (UK), €60.00 per annum ( Europe), \$90 per annum (air mail)(USA). Cover price £4.50. All information herein is believed to be correct at time of going to press. The publisher does not accept responsibility for any errors and omissions. The views expressed in this publication are not necessarily those of the publisher. Every effort has been made to obtain copyright permission for the material contained in this publication. Angel Business Communications Ltd will be happy to acknowledge any copyright oversights in a subsequent issue of the publication. Angel Business Communications Ltd © Copyright 2024. All rights reserved. Contents may not be reproduced in whole or

part without the written consent of the publishers. The paper used within this magazine is produced by chain of custody certified manufacturers, guaranteeing sustainable sourcing. US mailing information: Silicon Semiconductor, ISSN 1096-598X, is published 5 times a year by Angel Business Communications Ltd, Unit 6, Bow Court, Fletchworth Gate, Burnsall Rd, Coventry CV5 6SP. UK. Airfreight and mailing in the USA by agent named World Container INC 150-15, 183rd St, Jamaica, NY 11413, USA. Business Ltd, *c/o* World Container INC 150-15, 183rd St, Jamaica, NY 11413, USA.

We strive for accuracy in all we publish; readers and contributors are encouraged to contact us if they recognise an error or omission. Once a magazine edition is published [online, in print or both], we do not update previously published articles to align old company names, branding, marketing efforts, taglines, mission statements or other promotional verbiage, images, or logos to newly created or updated names, images, typographic renderings, logos (or similar) when such references/images were accurately stated, rendered or displayed at the time of the original publication. When companies change their names or the images/text used to represent the company, we invite organizations to provide Angel Business Communications with a news release detailing their new business objectives and/or other changes that could impact how customers/prospects might recognise the company, contact the organisation, or engage with them for future commercial enterprise. Printed by: The Manson Group. ISSN 2050-7798 (Print) ISSN 2050-7801 (Online) © Copyright 2024.

#### **INDUSTRY NEWS**

# EU Consortium accepting Edge-AI design proposals

A new European Union consortium created to accelerate the development of nextgeneration, edge-AI technologies is installing cleanroom tools and gearing up to design, evaluate, test and fabricate new circuits from across Europe.

COORDINATED by the EU's four leading research and technology organizations (RTOs), France's CEA-Leti, Germany's Fraunhofer-Gesellschaft, Belgiumheadquartered imec and Finland's VTT, the PREVAIL project is a networked, multi-hub platform providing prototype chip fabrication capability in advanced artificial technology to EU stakeholders. In most cases, the technology offer will be based on commercial foundry processes, and advanced technology modules will be enhanced in the cleanrooms of the project partners.

"The PREVAIL project's ultimate goal is to position Europe with an easyaccess, advanced manufacturing infrastructure enabling users to make early research samples of innovative and trustworthy products and accelerate their commercialization," said Sergio Nicoletti, CEA-Leti business development manager and PREVAIL project manager. "And while bringing their cutting-edge technologies to a higher maturity level and giving users the possibility to fabricate and test AI prototypes based on these technologies, the RTOs are reaping the benefits of technological crossfertilization."

"In addition to providing highperformance, low-power edge components and technologies to support the massive data-processing requirements of AI, the project will help energize the EU's digital transformation, a precursor to the goals of the European Chips Act," he said.

Launched at the end of 2022, the project is leveraging the RTOs' advanced 300 mm fabrication, design and test facilities and related expertise to create the Testing and Experimentation Facility for Edge-AI Hardware (TEF Edge AI HW). This

network will validate new highperformance, low-power, edge-Al components and support an infrastructure capable of fabricating early research prototype samples for testing in innovative edge-Al applications.

Nicoletti said the consortium is working with selected SMEs, the RTOs' industrial partners and academic labs to prepare early designs that will be used to test fabrication equipment in the RTOs' facilities. The project plans to open access widely for EU designers by May 2026.

While 80 percent of the project's budget targets equipment suited for design, testing and fabrication of edge-AI devices, the project also will dramatically reinforce the readiness of the RTOs to equip their new pilot lines for developing 3D technologies, which also are envisioned in the chips act.

#### Key project components

In addition to fabricating advanced edge-AI applications and creating the platform's TEF Edge AI HW, the consortium will provide process design kits (PDKs) compatible with standard commercial CAD tools and all the elements necessary for full chip design. A user-interface team will manage relationships among the developers of next-generation, edge-AI solutions and the consortium.

PREVAIL is the EU's first step to link the RTO's different infrastructures and synchronize and coordinate their investments to minimize duplication, and to jointly increase the technology readiness levels (TRLs) of tools in development. The nearly €156 million (\$169.3 million) cost of the 42-month project will be shared by the RTOs' countries and the European Commission. Approximately 80 percent of this funding is CAPEX invested in new tools suited for edge-AI devices.

PREVAIL's founding members CEA CEA-Leti Fraunhofer-Gesellschaft Imec VTT Technical Research Centre of Finland Ltd

# Intel launches new foundry designed for the AI era

Intel announces expanded process roadmap, customers and ecosystem partners to deliver on ambition to be the No. 2 foundry by 2030.

INTEL has launched Intel Foundry as a more sustainable systems foundry business designed for the AI era and announced an expanded process roadmap designed to establish leadership into the latter part of this decade. The company also highlighted customer momentum and support from ecosystem partners – including Synopsys, Cadonaco Sigments and Apsys

Cadence, Siemens and Ansys – who outlined their readiness to accelerate Intel Foundry customers' chip designs with tools, design flows and IP portfolios validated for Intel's advanced packaging and Intel 18A process technologies.

The announcements were made at Intel's first foundry event, Intel Foundry Direct Connect, where the company gathered customers, ecosystem companies and leaders from across the industry. Among the participants and speakers were U.S. Secretary of Commerce Gina Raimondo, Arm CEO Rene Haas, Microsoft CEO Satya Nadella, OpenAI CEO Sam Altman and others.

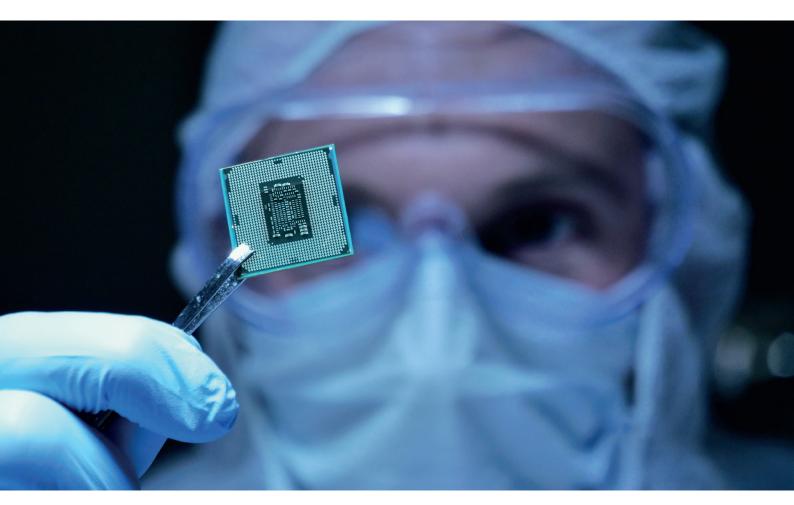

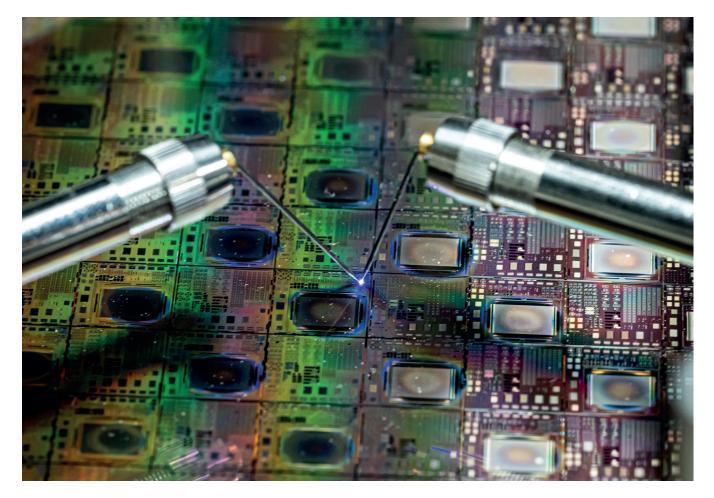

An Intel factory employee holds a wafer with 3D stacked Foveros technology at an Intel fab in Hillsboro, Oregon, in December 2023. In February 2024, Intel Corporation launched Intel Foundry as the world's first systems foundry for the AI era, delivering leadership in technology, resiliency and sustainability. (Credit: Intel Corporation) "Al is profoundly transforming the world and how we think about technology and the silicon that powers it," said Intel CEO Pat Gelsinger. "This is creating an unprecedented opportunity for the world's most innovative chip designers and for Intel Foundry, the world's first systems foundry for the AI era. Together, we can create new markets and revolutionize how the world uses technology to improve people's lives."

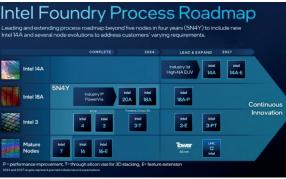

### Process roadmap expands beyond 5N4Y

Intel's extended process technology roadmap adds Intel 14A to the company's leading-edge node plan, in addition to several specialized node evolutions. Intel also affirmed that its ambitious five-nodes-in-four-years (5N4Y) process roadmap remains on track and will deliver the industry's first backside power solution. Company leaders expect Intel will regain process leadership with Intel 18A in 2025.

The new roadmap includes evolutions for Intel 3. Intel 18A and Intel 14A process technologies. It includes Intel 3-T, which is optimized with through-silicon vias for 3D advanced packaging designs and will soon reach manufacturing readiness. Also highlighted are mature process nodes, including new 12 nanometer nodes expected through the joint development with UMC announced last month. These evolutions are designed to enable customers to develop and deliver products tailored to their specific needs. Intel Foundry plans a new node every two years and node evolutions along the way, giving customers a path to continuously evolve their offerings on Intel's leading process technology.

Intel also announced the addition of Intel Foundry FCBGA 2D+ to its comprehensive suite of ASAT offerings, which already include FCBGA 2D, EMIB, Foveros and Foveros Direct.

#### Microsoft design on Intel 18A headlines customer momentum

Customers are supporting Intel's long-term systems foundry approach. During Pat Gelsinger's keynote, Microsoft Chairman and CEO Satya Nadella stated that Microsoft has chosen a chip design it plans to produce on the Intel 18A process.

"We are in the midst of a very exciting platform shift that will fundamentally transform productivity for every individual organization and the entire industry," Nadella said. "To achieve this vision, we need a reliable supply of the most advanced, high-performance and high-quality semiconductors. That's why we are so excited to work with Intel Foundry, and why we have chosen a chip design that we plan to produce on Intel 18A process."

Intel Foundry has design wins across foundry process generations, including Intel 18A, Intel 16 and Intel 3, along with significant customer volume on Intel Foundry ASAT capabilities, including advanced packaging.

In total, across wafer and advanced packaging, Intel Foundry's expected lifetime deal value is greater than \$15 billion.

#### IP and EDA vendors declare readiness for Intel process and packaging designs

Intellectual property and electronic design automation (EDA) partners Synopsys, Cadence, Siemens, Ansys, Lorentz and Keysight disclosed tool qualification and IP readiness to enable foundry customers to accelerate advanced chip designs on Intel 18A, which offers the foundry industry's first backside power solution. These companies also affirmed EDA and IP enablement across Intel node families.

#### **INDUSTRY NEWS**

## Saxony-Anhalt embraces change as an opportunity

#### Billions invested in key transformation industries.

THE LARGEST investment project not only in Saxony-Anhalt but in all of Europe is Intel's establishment in Magdeburg. Approximately 30 billion euros are set to be invested in the construction of multiple chip factories. The company has initiated collaborations with six universities in Saxony-Anhalt and is actively recruiting its initial workforce. Approval processes commenced in February, paving the way for the production of the world's most advanced chips in the two factories starting from 2027.

### Saxony-Anhalt – HERE is the place for big plans

In addition to Intel, numerous other semiconductor companies are also making substantial investments. Sioux Technologies, a globally recognized technology accelerator with around 1,100 employees, is developing strategic high-tech solutions for various markets such as semiconductors, laboratory and medical technology, mechatronics, imaging, mobility, and clean energy. In Barleben, Sioux plans to invest around 20 million euros in a research and development center, gradually creating three hundred highly qualified permanent jobs.

Meanwhile, in Bernburg, a large high-performance distribution center for semiconductors and electronic components is taking shape. The topping-out ceremony for Avnet's Electronics Distribution Center was celebrated in November 2023, with an investment volume exceeding 225 million euros. Over the next eight years, around 700 jobs are expected to be created in Bernburg.

Sven Schulze, Minister for Economic Affairs, Tourism, Agriculture, and Forestry of the State of Saxony-Anhalt, emphasizes the economic dynamism of the region against the backdrop of these examples: "Saxony-Anhalt is on the fast track. High-profile fast-track approvals, a central location in Europe, close collaboration with educational institutions, and attractive conditions such as affordable rents and sufficient childcare spaces make investments and living here exceptionally appealing." Life Sciences Take Pioneering Role in Saxony-Anhalt's Future

Saxony-Anhalt is establishing itself as a leader in the field of Life Sciences, showcasing the state's future resilience. The mRNA Center in Halle (Saale) is taking shape, with the Wacker Chemie AG demonstrating serious ambitions in this cutting-edge technology through a substantial investment exceeding 100 million euros. The new facility is expected to host around 200 employees. Additionally, the Magdeburg-based medical technology company Neoscan Solutions recently secured a contract to build the world's most powerful 14 Tesla MRI magnet for human examinations.

Chemical parks in Saxony-Anhalt are undergoing expansion and sustainable transformation, with Germany's largest Chemical Park Leuna, being one of the nation's largest construction sites. Over 100 companies from eleven nations are investing 1.3 billion euros in research and green chemistry. The expansion is set to create up to 250 direct and 750 indirect jobs, primarily in the sustainable chemistry sector. AMG Lithium has chosen the Chemical Park Bitterfeld-Wolfen for a 140-million-euro investment to purify lithium hydroxide, transforming it into a battery-grade raw material – a unique endeavor in Europe.

### Innovations in renewables and storage technologies

NexWafe, a US-based company, is investing 30 million euros in Bitterfeld-Wolfen to establish a factory for producing solar wafers, a crucial material for the photovoltaic industry. In Bitterfeld, the German company Silicon Products, in collaboration with a French partner, aims to produce high-purity silicon carbide, a vital resource for nearly all semiconductor manufacturers.

TESVOLT AG, a leading technology company in commercial and industrial energy storage, plans to construct a new Gigafactory in Lutherstadt Wittenberg, investing around 60 million euros. The long-term goal is to create over 400 new jobs, particularly in research and development.

The automotive and logistics sectors are also experiencing rapid development from international players. LMG Manufacturing, an aluminum diecasting specialist, inaugurated its new manufacturing hall in Hoym/Seeland after just ten months of construction.

Daimler Truck's largest logistics project commenced with the official groundbreaking in Halberstadt in September 2023. The Global Parts Center in Halberstadt/Harz aims to deliver spare parts worldwide starting in 2025, generating approximately 450 jobs with an investment of nearly 500 million euros.

Dr. Robert Franke, Managing Director of the Investment and Marketing Corporation Saxony-Anhalt mbH, emphasizes, "Saxony-Anhalt is an attractive and sought-after location for settlement. We are witnessing significant investments not only in the chip industry but also in various other sectors such as pharmaceuticals, medical technology, and the automotive industry. This underscores why Saxony-Anhalt has gained considerable international visibility."

### Taalas emerges from stealth

#### \$50 million in funding and a 'groundbreaking' silicon AI technology.

TAALAS INC., an innovator in AI and silicon, has exited stealth mode and raised \$50 million dollars over two rounds of funding led by Pierre Lamond and Quiet Capital.

Over the last year, Al has undergone a large scale productization and has already begun reshaping the world. Concurrently, deep learning models have become the world's most demanding computational workload, unsustainably capital intensive, power hungry, and GPU constrained.

"Artificial intelligence is like electrical power – an essential good that will need to be made available to all.

Commoditizing AI requires a 1000x improvement in computational

power and efficiency, a goal that is unattainable via the current incremental approaches.

The path forward is to realize that we should not be simulating intelligence on general purpose computers, but casting intelligence directly into silicon. Implementing deep learning models in silicon is the straightest path to sustainable AI," said Ljubisa Bajic, Taalas' CEO.

Taalas is developing an automated flow for rapidly implementing all types of deep learning models (Transformers, SSMs, Diffusers, MoEs, etc.) in silicon.

Proprietary innovations enable one of its chips to hold an entire large Al model without requiring external memory. The efficiency of hardwired computation enables a single chip to outperform a small GPU data center, opening the way to a 1000x improvement in the cost of AI.

"We believe the Taalas 'direct-to-silicon' foundry unlocks three fundamental breakthroughs: dramatically resetting the cost structure of Al today, viably enabling the next 10-100x growth in model size, and efficiently running powerful models locally on any consumer device.

This is perhaps the most important mission in computing today for the future scalability of Al. And we are proud to support this remarkable n-of-1 team as they do it," said Matt Humphrey, Partner at Quiet Capital.

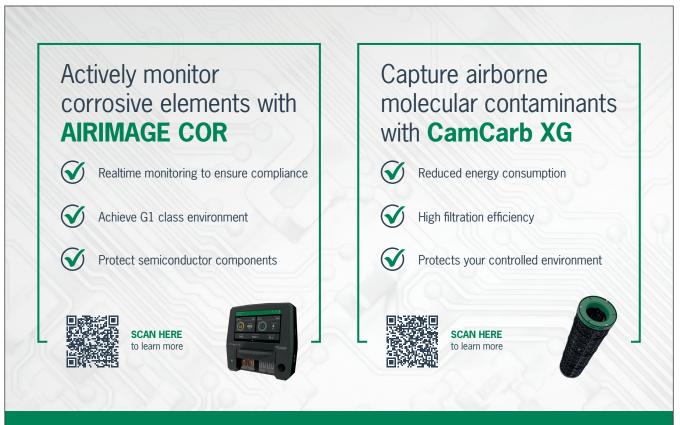

www.camfil.com

₹camfil

#### **INDUSTRY NEWS**

# Rolls-Royce supplies mtu Kinetic PowerPacks for semiconductor manufacturer X-FAB Sarawak

Four uninterruptible power supply units secure critical power load for semiconductor operations in Malaysia.

ROLLS-ROYCE has supplied and commissioned four of its mtu Kinetic PowerPacks to X-FAB Sarawak, the Malaysian division of X-FAB, the world's leading foundry group for specialty semiconductor applications.

The dynamic uninterruptible power supply (DUPS) units secure the critical power load for operations at the company's manufacturing site located in Kuching, Sarawak, Malaysia.

mtu Kinetic PowerPacks are engineered to perform seamlessly under the most demanding power supply challenges. They provide immediate, high-quality power through the use of kinetic energy. The units eliminate the need for batteries as in a standard UPS configuration, offer a much smaller footprint and are environmentallyfriendly due to their 20+ year equipment life and their ability to run on sustainable fuels such as HVO.

Bryan Foo, Project Manager, Rolls-Royce Solutions Asia Pte. Ltd. said: "Being secure in the knowledge that your power supply is reliable and of the highest quality, even during times of grid instability or interruption, is important for any business but is especially vital for a company such as X-FAB Sarawak that has a consistent, high-level output of critical products and that supports many employees and corporate functions." The X-FAB site in Kuching manufactures semiconductor wafers for automotive, industrial and medical applications and has more than 1,400 employees and a wide array of operations such as finance and procurement.

The four installed mtu Kinetic PowerPacks feature a medium voltage, parallel system configuration offering 2000 kVA (1600kW). They replace older, existing DUPS units from a different manufacturer that were experiencing ongoing issues with dropping critical load from the mains. In normal operation, when the public power supply is working, the mtu Kinetic PowerPacks use a choke - a heavy, rotating electromagnetic coil - to compensate for short-term current and voltage fluctuations in the power grid. The Kinetic PowerPacks also come with an mtu ValueCare service agreement, which provides preventative maintenance at regular intervals and technical support to ensure maximum performance.

Elvenrey Rios, Project Engineer, Rolls-Royce Solutions Asia Pte. Ltd. said: "Our project team upheld X-FAB's strong safety culture, product quality and user-friendly equipment during the entire process. The reliable critical load support provided by the current mtu Kinetic PowerPacks has also resulted in the customer engaging Rolls-Royce for an additional unit."

#### Kioxia and Western Digital's Joint venture

THE SUBSIDY will be granted under a designated government program aimed at facilitating corporate investment in cuttingedge semiconductor production facilities and securing stable production of semiconductors in Japan. This marks the second time that Kioxia's and Western Digital's joint venture manufacturing facilities are receiving this subsidy from the Japanese government.

Previously, the joint venture manufacturing facility at Yokkaichi was approved to receive up to 92.9 billion yen subsidy from the Japanese government in 2022.

Leveraging an over 20-year joint venture partnership, Kioxia and Western Digital will continue to enhance the development and production capabilities of cuttingedge flash memory at the Yokkaichi and Kitakami plants in Japan. In addition, the two companies will contribut e to the development of semiconductor-related industries and talent.

"We appreciate the support of the Japanese government and will continue to produce cuttingedge flash memory, which is indispensable for technologies that underpin the expanding digital transformation of society. With this subsidy, we will continue to contribute to the advancement of the semiconductor industry and the development of local and domestic economies," said Nobuo Hayasaka, President and CEO of Kioxia.

David Goeckeler, CEO of Western Digital said, "We thank the Japanese government for their ongoing and unwavering commitment to our joint venture flash memory manufacturing facilities in Japan and our long track record of innovations in the NAND flash industry."

# SemiQon ships silicon-based quantum chip and transistors

Research groups around the world are now using these first-generation silicon-based chips helping the industry step faster to the million qubit level of quantum computing.

SEMIQON, a Finland-based startup specializing in silicon-based quantum processors, has successfully manufactured and pre-tested a 4-qubit quantum dot array from the first production run at its manufacturing facility in Espoo, Finland. The new chips are now shipping to strategic partners around the world as a toolkit for further research and development. The aim is to help make building stable logical qubits easier and faster to accelerate the use of quantum computing for complex problems.

First-generation quantum computers have already achieved impressive computational feats. However, solving highly specific problems related to pharmaceuticals, logistics, space, and material design will require increased computational power. As researchers, ecosystems, and companies around the globe lay out their ambitious visions for quantum computing, the computing power must still be scaled efficiently to address these challenges. Current methods do not make this possible. "We are gradually moving towards the million qubit era and the contribution of hardware is becoming more and more essential," says Dr. Himadri Majumdar, CEO and Co-founder of SemiQon. "Our solution builds on the technological development and know-how of semiconductors and benefits from existing infrastructure and industry. Utilizing such infrastructure effectively and efficiently has allowed us to accomplish one of our first goals within a short period of time. The challenge is getting to guantum supremacy in a sustainable, scalable, and affordable manner. These new chips are our first step in a long journey to making quantum dreams a reality."

SemiQon's strategic path of combining classical and quantum elements at cryogenic temperatures also took a big

leap forward through the demonstration of very low noise and better control over the channel using record low subthreshold swing in the manufactured fully-depleted silicon-on-insulator metal-on-semiconductor (FDSOI-MOS) transistors. These transistors will be the backbone of realizing a cryogenic integrated circuit (IC), ultimately leading to quantum IC for scalable, efficient, and affordable quantum computers. The results will be communicated through a peer-reviewed international scientific article, which is currently under review.

### SwissChips Initiative to boost Swiss chip industry

BY FOSTERING collaboration between academia and industry, the initiative aims to drive innovation and economic growth.

The SwissChips Initiative is a collaborative effort launched by CSEM, EPFL, and ETH Zurich, with support from various Swiss and European research entities, semiconductor associations, and industrial partners. This initiative is supported by the Swiss State Secretariat for Education, Research and Innovation (SERI).

Inspired by the US and European Chips Acts, this act aims to enhance the Swiss semiconductor sector by promoting cutting-edge research in integrated circuit (IC) design. The initiative covers a wide range of domains such as: Computing System on Chips (SoCs), 6G Communications, Space Electronics and Photonics, SoCs for Autonomous IoT Devices, Chips for EDGE AI, Biomedical Circuits and Systems, and Devices and Sensors. ETH Zurich coordinates the program, with all three founding institutions taking leading roles in their respective research areas.

These efforts are designed to bolster microelectronics and IC design research, innovation, development, and businesses, ensuring Swiss academic institutions have access to cutting-edge manufacturing and design technologies. Additionally, the initiative aims to foster the Swiss semiconductor, microelectronics, and IC design ecosystem, developing robust synergies among research institutions.

### Enhance the semiconductor sector in Switzerland

The program involves PhD and Postdoc researchers, as well as the existing engineering and research staff of the participating institutions, who will push the boundaries of IC design. This concerted effort will not only enhance Switzerland's influence in the semiconductor industry during the post-Global Chip Shortage era of 2020-2023 but also ensure the development of infrastructure and technologies that benefit all scientific domains.

This includes making advancements accessible to Swiss universities and universities of applied sciences, thereby nurturing a holistic growth in the semiconductor, microelectronics, and IC design sectors.

#### **INDUSTRY NEWS**

# Tata Group to build India's first indigenous facility in Assam

INR 27,000 crore investment in a greenfield facility in Assam for assembly and testing of semiconductor chips for applications across automotive, mobile devices, artificial intelligence (AI), and other key segments to serve customers globally.

IN A SIGNIFICANT step towards creating an end-to-end semiconductor manufacturing ecosystem in India, Government of India has approved a proposal by Tata Electronics to build a state-of-the-art, greenfield semiconductor assembly and test facility in Jagiroad, Assam. The facility will be built with an investment outlay of INR 27,000 crore and is expected to generate over 27,000 direct and indirect jobs in the region.

Tata Electronics Pvt Ltd (wholly owned subsidiary of Tata Sons Pvt Ltd) will build this facility focusing on three key platform technologies - Wire Bond, Flip Chip, and a differentiated offering called Integrated Systems Packaging (ISP), with plans of expanding the roadmap to advanced packaging technologies in the future. These technologies are extremely critical for key applications in India – like automotive (especially electric vehicles), communications, network infrastructure and others.

Tata Electronics has already made significant investments in indigenous technology development for all these platforms and has put together a very credible team with over 1,000+ years of global domain experience to drive this project. The proposed facility will serve the growing global demands across key market segments like AI, industrial, and consumer electronics.

The construction of the facility is scheduled to start this year with the first phase of the facility becoming operational by mid-2025 and will provide an immense boost to industrialization in North-East India. The project is envisioned under the Government of India's Semiconductor policy being driven by the India Semiconductor Mission and the Government of Assam's Electronics policy.

Semiconductor assembly and test is a

critical part of the semiconductor value chain where wafers manufactured by semiconductor fabs are assembled or packaged and then tested before they are finally used in the desired product. Innovations in semiconductor assembly and test are driving increased performance, reduced form factor, and reduced costs of semiconductor chips.

Commenting on the announcement, N Chandrasekaran, Chairman, Tata Sons said, "We are in a unique time for the electronics manufacturing market alobally and the world is seeking a more secure and resilient electronics supply chain. With our announcement of the semiconductor fab and this strategic project in semiconductor assembly and test, we will be enabling our global customers to base a key part of their semiconductor value chain in India. Alongside mitigating global supply chain risks, I am confident that this project will have a transformational impact towards technology led industrialization and job creation in the Northeast in particular.

Under the decisive leadership of Hon'ble Prime Minister Shri Narendra Modi, the Government of India has developed a comprehensive central and state semiconductor policy. This along with support from Ministry of Electronics and Information Technology, India Semiconductor Mission and the Government of Assam has made this announcement possible."

Dr Randhir Thakur, CEO & MD, Tata Electronics said, "The strategy of serving across the semiconductor value chain is our differentiator and will enable Tata Electronics to deliver complete system offerings to customers. We have a critical window of opportunity where we see tremendous customer pull from global players for manufacturing in India and we

plan to capitalize on this opportunity and leapfrog through technology innovation. This investment will go a long way in putting India on the map of global semiconductor manufacturing and in spurring a complete domestic ecosystem for high technology manufacturing while being an enabler for the indigenous product ecosystem."

The proposed facility in Jagiroad is strategically located with access to abundant water and green power – a key sustainability consideration for the Tata group and its customers globally. Assam is also closer to the current semiconductor packaging & test hubs in countries like Taiwan, Malaysia, Vietnam, and Singapore. Assam has technical and engineering workforce available from the entire North-East India, providing a stable talent pool for this project as well as the ecosystem development that this project will seed.

This new initiative from Tata Electronics will bring to India a portfolio of cuttingedge semiconductor technologies, advanced skill set and talent, and a network of semiconductor manufacturing suppliers and ecosystem partners, resulting in foundational development of indigenous semiconductor ecosystem in India.

This Assembly & Test facility will be able to directly ship semiconductor chips to end-users and OEMs (Original Equipment Manufacturers) in India and the world.

# £35m boost for British semiconductor scientists and businesses

Semiconductor sector to benefit from up to £35m, plus European funds, in a boost to British leadership in research of cutting-edge chip technology.

BRITISH SEMICONDUCTOR researchers and businesses now have enhanced access to research funding backed by the UK Government and Horizon Europe, now the UK has joined the EU's 'Chips Joint Undertaking'.

The move provides the UK semiconductor sector enhanced access to a  $\leq$ 1.3 billion pot of funds set aside from Horizon Europe to support research in semiconductor technologies up to 2027. Access to the one of the Chips Joint Undertaking's funds is being backed by an initial £5 million this year from the Department for Science, Innovation and Technology, and delivered by Innovate UK. An additional £30 million is due to support UK participation in further research between 2025 and 2027.

By joining the fund and contributing in the same way as all other countries who take part, the UK sector has enhanced access to bid for funding support from the €1.3 billion pot, funded by Horizon Europe. Announcing the move at a conference of global semiconductor leaders in London, Technology Minister Saqib Bhatti said: "Our membership of the Chips Joint Undertaking will boost Britain's strengths in semiconductor science and research to secure our position in the global chip supply chain.

"This underscores our unwavering commitment to pushing the boundaries of technology and cements our important role in shaping the future of semiconductor technologies around the world."

This follows the UK joining Horizon Europe through a bespoke new agreement with the EU last year. The programme is giving UK companies and research institutions unrivalled opportunities to lead global work to develop new technologies and research

projects, in areas from health to Al. Tens of thousands of UK companies are now eligible for Horizon Europe grants, which are worth £450,000 to a business on average. UK firms already benefitting from Horizon funding include Nova Innovation, whose consortium won over £17 million to develop tidal energy in Orkney, and South Yorkshire tech firm The Floow who are part of a project awarded just under £3 million, looking into road safety.

Jari Kinaret, Chips JU Executive Director, said: "We are very happy to welcome the UK to the Chips Joint Undertaking as a participating state. We are looking forward to working with the UK partners to develop the European industrial ecosystem in microelectronics and its applications, contributing to the continent's scientific excellence and innovation leadership in semiconductor technologies and related fields."

This year, the Chips Joint Undertaking fund is well aligned to UK research expertise. In 2024, it includes two focussed calls for funding bids on semiconductors for cars and other vehicles as well as RISC-V, an opensource architecture that aims to accelerate semiconductor innovation by lowering the cost of chip design. It also provides more open opportunities for scientists and firms to bid for research support. Sean Redmond, Managing Partner at SiliconCatalyst, added: "UK Semiconductor startups have a rich history of collaboration with the European Union. Our semiconductor

research base is the fourth largest in the world.

"Commercialising these inventions with the help of the EU Chips Joint Undertaking will significantly increase their probability of success, mitigating risks by local collaborations that provide a clear path from lab to fab."

Jalal Bagherli, Chairman, PTSL, Chair, Williams Advanced Engineering and Co-Chair of UK Semiconductor Advisory Panel, commented: "As the UK Semiconductor Strategy ramps up its implementation phase in support of a thriving industry, I believe this initiative is the next major step enabling engagement with our global partners to advance the state of the art in chip development and innovative packaging technologies in the UK".

The UK has joined the initiative as a "Participating State", allowing the country to collaborate more closely with European partners on semiconductor innovation. As a Participating State, the UK will have a role in setting research priorities and funding decisions as the fund evolves in the years ahead. This includes the opportunity for the UK to be a part of a new funding opportunity with the Republic of Korea to research ways to combine semiconductor chips to improve performance through advanced packaging – which the UK-Republic of Korea Semiconductor Framework. signed in November last year.

British research has elsewhere led global efforts to push semiconductor technology forward in fields like "silicon photonics", which creates faster chips by using light instead of electricity, and compound semiconductors, which enable improved performance over silicon in key applications such as power transmission and radiofrequency communications.

#### TECHNOLOGY | SUSTAINABILITY

# The challenge of decarbonising the semiconductor industry and fulfilling chip demand

The semiconductor sector is an essential part of our increasingly digital environment. Its technologies, which include cell phones and computers we use for communication, the vehicles and aircraft that allow us to transport, the medical equipment that aids in disease diagnosis and treatment, and the grid systems that power our cities, are essential to everyday life. There can't be a future without semiconductors, but their widespread use also presents growing environmental challenges.

#### BY HENRI BERTHE, SEMICONDUCTOR VICE PRESIDENT, SCHNEIDER ELECTRIC

THE ENVIRONMENTAL COST of semiconductors To meet demand, semiconductor players are building new fabrication plants (FABS), which can use as much as 100 megawatt-hours of power each hour—more than many automotive plants or oil refinery. This massive amount of electricity consumption will result in significant waste generation, greenhouse gas emissions and large carbon footprint In 2020, the industry emitted an astounding 41 million tonnes[VT2] of CO<sub>2</sub>, the equivalent of 5 million houses> annual emissions. And by 2030, semiconductor manufacturing is projected to consume 237 TWh of electricity globally, around equal to Australia's total 2021 electrical consumption.

As electronics grow in importance, manufacturers must navigate concerns around energy consumption and sustainability. Recent McKinsey research finds that major semiconductor companies' latest commitments are still falling short of what is required under the 2016 Paris Agreement. As a result, businesses that fail to make their operations more environmentally friendly may face stronger restrictions and sanctions from future governments, as well as decreasing orders from increasingly environmentally sensitive customers.

Conversely, those who optimise their energy efficiency early will unlock considerable resource savings and huge opportunities for growth.

To protect their businesses' futures, it is essential for manufacturers to start establishing sustainable practices today.

#### Upholding sustainability with resilience

Aside from environmental problems, many manufacturers are still dealing with the fallout from the global semiconductor crisis. A 'perfect storm' of global events almost brought production to a standstill throughout the pandemic: COVID-19's lockdowns both accelerated demand for consumer electronics and closed the factories producing the required components. Meanwhile, the China– United States trade war, Russia–Ukraine war, severe weather events, production facility fires, and a general reliance on semiconductor imports, rather than domestic manufacturing, also contributed to the sustained scarcity.

At the height of the chip shortage, research indicated that up to 169 businesses were affected globally. The consumer electronics and automotive industries took the brunt of the damage. PlayStation 5 consoles became akin to gold dust and Apple slashed its iPhone manufacturing targets, while Toyota reduced car manufacturing by 40% and General Motors paused vehicle production across North American plants.

Overall, the shortage cost the auto industry as much as \$210 billion in revenue in 2021. And though manufacturers have now adapted to a constrained supply, increasingly complex products, such as electric vehicles with advanced safety and autonomy systems, will continue to accelerate semiconductor demand and spark a significant change in the manufacturing landscape.

As semiconductor production has been concentrated in Asia for the past 10 years, organisations and countries are now looking to create more diverse, resilient supply chains. In October 2022, the US government administered export control rules to constrain China's production of the world's most advanced chips.

Meanwhile, the EU also intends to become a significant player through the European Chips Act. As investments shift from APAC to North America and Europe, manufacturers must be ready to offer low-carbon services to stand out from their competitors.

# The three-step plan for resilience and sustainability

Determining an environmental baseline is a 'must' when decarbonizing the chip industry. At Schneider Electric, we've identified three key steps that help semiconductor organizations of all types and sizes to turn sustainable, net-zero ambitions into action. The first step, called 'Strategize', involves measuring a manufacturer's current energy performance and carbon footprint, and then crafting a net-zero plan that delivers tangible results. In reality, this involves establishing a baseline for carbon emissions, examining digital technologies to identify gaps and inform future roadmaps, assessing technical and economic feasibility to prioritize actions, and modelling building retrofit scenarios to develop a roadmap and timeline. The use of electrical digital twins when designing and simulating new FABS power systems in particular will improve their designs and optimise the network to meet local requirements and standards.

The second step is 'Digitize'. This means creating a digital hub that can monitor and visualize a semiconductor organization's energy and resource usage, enabling leaders to make data-driven sustainability decisions and report on progress towards set goals. This single source of truth aids in the tracking of embedded carbon, including building information modelling, as well as the measurement of energy and carbon, including centralizing energy supply and utility data and implementing cloudbased, Al-powered analysis.

Finally, the third step is 'Decarbonize'. This is where the true action takes place, in which semiconductor manufacturers must leverage insights from their Strategize and Decarbonize steps to make genuine sustainability improvements. Exact upgrades will depend on their findings, but examples include the electrification of fleet vehicles, the installation of renewable energy generators, the purchase of low or no-carbon products, and the use of AI to optimize on-site energy consumption in real-time.

#### TECHNOLOGY | SUSTAINABILITY

# Collaborating with dependable advisors and specialised partners

Alongside the three-step Strategize, Digitize, Decarbonize process, collaboration and partnerships are pivotal to achieving sustainability success in the semiconductor industry. With long-term sustainability requiring disparate areas of specialization and support, manufacturers must realize that no single company can accomplish it alone. Instead, semiconductor producers and vendors must work together and leverage external expertise and technology.

Schneider Electric has long been instrumental in assisting semiconductor companies in addressing sustainability and decarbonization challenges. For example, it recently partnered with Intel, one of the world's leading semiconductor design and manufacturing companies, and Applied Materials, Inc., the world's largest semiconductor and display equipment company, to launch Catalyze: a new partnership program aimed at accelerating access to renewable energy across the global semiconductor value chain. With the assistance of the Catalyze program, semiconductor leaders will be able to achieve a number of sustainability and resilience goals, including:

- Combine energy purchasing power across the semiconductor value chain to accelerate the deployment of renewable energy projects

- Participate in the market for utility-scale power purchase agreements (PPAs)

- Develop operational models to be used in supply chain programs to close net-zero ambition gaps

- Increase awareness of the availability of renewable energy in specific global regions where the semiconductor value chain is operational

- Lead the way for the industry to drive definitive next steps

# Sustainable power in the manufacturing of semiconductors

Ultimately, embracing sustainability measures not only aligns with global environmental goals, but also makes sense for semiconductor fabrication plants' bottom lines.

Studies indicate that implementing sustainability strategies can reduce costs and positively impact operating profit by up to 60%. Moreover, adopting sustainability practices mitigates long-term risks and opens opportunities in new markets. Now that we've seemingly progressed from the semiconductor crisis , manufacturers have potential for enormous growth through long-term improvements. They can produce large savings as well as unlock enormous untouched energy efficiency possibilities. And the best part? The tools to achieve this are right in front of us.

With the help of a knowledgeable network of partners, organisations must learn to decarbonize, digitize, and strategize today.

DOPROC

# NEXT-GENERATION SEMICONDUCTOR TESTING

# **DOT Test Platform**

SPEA

The test performance you need to test your devices, reducing complexity and operations.

Discover how to save **up to 90%** on your Cost of Test www.spea.com/savewithDOT

# NANOCLEAVE™ LAYER TRANSFER REVOLUTIONIZES ADVANCED PACKAGING AND LOGIC SCALING

IR laser cleave technology enables ultra-thin-layer transfer from silicon carriers

Nanometer-precision release of bonded, deposited or grown layers

Front-end compatibility through silicon carriers and inorganic release materials

Supporting future roadmaps in advanced packaging and transistor scaling

GET IN TOUCH to discuss your manufacturing needs www.EVGroup.com

EVG<sup>®</sup>850 NanoCleave<sup>™</sup>

1DD

# Effective hermetic sealing for next-generation microelectronic packaging

A perfectly sealed electronic package can fulfill its intended function without disruption, error or a significant reduction in performance for decades. However, design and field engineers can only achieve this level of performance by applying the right materials and sealants, and employing the correct tools, equipment and process steps to build semiconductor-driven electronic packages for the next generation. The confidence engendered by a well-sealed package inevitably leads to the development of better chips with more features.

#### BY RAMESH KOTHANDAPANI, TECHNICAL DIRECTOR, MICROELECTRONIC PACKAGING, MATERION CORPORATION

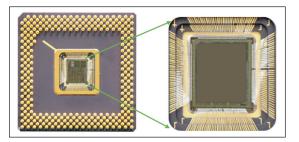

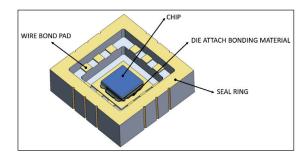

HERMETIC SEALING is an important process for packaging semiconductor chips. The word "hermetic," in this case, suggests leak-safe sealing. A semiconductor chip goes through several process steps, starting as a wafer before being cut into individual chips and eventually ending up in a discrete package. Such chips are strongly bonded to die pads with a die-attach epoxy or eutectic solders. They are then electrically connected to the ceramic package bond pads with very fine wires.

The ceramic package – in effect a "chip carrier" – is generally multi-layered with electrical feedthroughs within its ceramic body. These layers are internally connected to the bottom or sides of the package to be mounted onto printed circuit boards along with other electrical components. An array of packages is available for chip bonding, including leaded chip

> The ceramic package with semiconductor chip attached via bonding materials. The image on the right shows the fine wire bonds to the bond pads. Each bond pad is internally connected to the pins surrounding the package.

carrier (LCC); ceramic, quad, flatpack (CQFP), and quad-flat package (QFP), among others.

The ceramic package containing the chip with wire bonds must eventually be hermetically sealed to prevent the entry of contaminants such as moisture or loose particles.

The hermetic sealing process is vital to determining the viability of the assembly in operation. Illustration 1 shows the semiconductor chip and its hundreds of very fine wire bonds. These chips range in size from a few millimeters to tens of millimeters. Smaller chips may have fewer wire bonds, while larger chips can have hundreds. These bonds are thinner than a human hair, with diameters as small as 0.0007 inch (17.78 microns).

Discrete chips contain micro-electromechanical systems (MEMS) with super-fine gears, clocks and moving actuators that cannot be seen with the naked eye. Any particles that deposit on these chips are likely to interfere with their performance. Equally, with the bonded fine wires so close to each other, conductive particles or moisture between the wires could cause a malfunction. This makes proper hermetic sealing of the assembled packages even more important.

Before focusing on the sealing process, it's important to know about materials which are used for sealings, its limitations, the design guidelines, storage, and handling processes.

#### TECHNOLOGY | ADVANCED PACKAGING

There are, for example, several types of ceramic packages:

- Surface mount ceramic packages

- Ceramic pin grid array packages

- Ceramic quad flat packages

- Ceramic hybrid packages

- Fiber-optic communication packages

- The bonding materials or solders

- The components which have to be attached to the package such as dies, die attach materials, wires and etc.

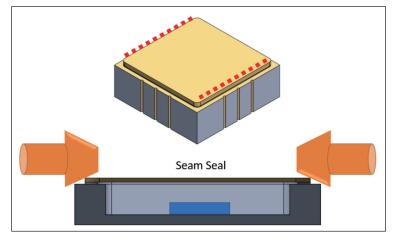

Depending on the level of hermeticity required, packages undergo one or two sealing processes: seam-sealed with a metal lid, or solder-sealed with a plated metal lid.

#### SEAM-SEALED WITH METAL LID:

This is a reliable hermetic sealing process in which a pair of round electrodes run around the edge of the lid, melting and fusing it to the package's seal ring area. Seam sealing is useful when:

- The semiconductor chip cannot accept high levels of heat. Seam seal offers localized edge heating.

- The user may not have oven reflow capability.

- The end application is RF-related with a low level of hermeticity required (i.e., RF packaging).

#### SOLDER-SEALED WITH PLATED METAL LID:

This process can also achieve high levels of reliable, airtight sealing. Several post-seal tests are available to confirm its effectiveness.

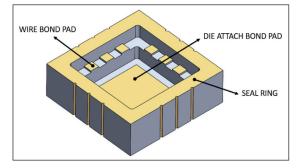

Some factors are common to all package types, including the use of die-bond pads, wire bond pads and seal rings. Illustration 3 shows some key features of the ceramic package.

**DIE-ATTACH PAD:** This is the area where the semiconductor chip is attached with the aid of eutectic solder alloy or epoxy materials. Epoxy-based die-attach adhesives typically comprise a resin and a hardener, which must be well mixed before being applied to the die pad. The chip is then put into place and scrubbed with pressure to initiate wetting and release any trapped gasses in the bonding materials. The assembly is cured at high temperatures to harden it, a potentially tricky process that must be properly controlled.

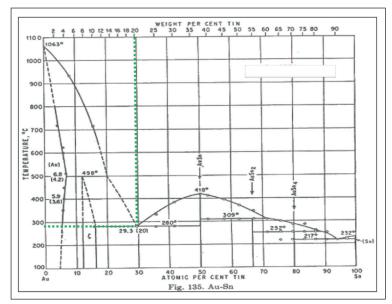

Both 88Au12Ge and 80Au20Sn can be used as eutectic bonding materials. They melt at 361°C and 280°C, respectively. After considering the heat loss into the fixtures and other components, the set temperature is usually higher. Both types of eutectic solders are pure alloys without any binders or bonding agents.

The selection of the die-attachment bonding material is subject to the coefficient of thermal expansion (CTE) of the chip and other neighboring materials with which the bonding agent may come

> The ceramic package is seam-sealed with two electrodes running parallel to melt the lid and seal it to the ceramic or metal package.

> The ceramic package with seal ring and wire and diebond pads.

➤ The ceramic package with chip attachment.

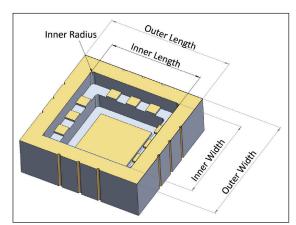

> Ceramic package with seal ring dimensions.

#### TECHNOLOGY | ADVANCED PACKAGING

> Design guidelines for package lid and solder.

≻ Gold-Tin phase diagram.

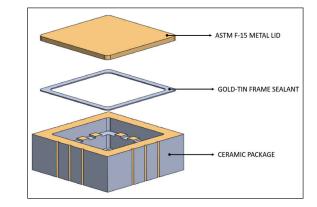

> Exploded view of ceramic package, solder frame and plated metal lid. into contact. Melting and curing temperatures and conditions must also be determined.

#### CHIP ATTACH POST-SEAL CONDITIONS:

It is important to validate secure bonding and ensure the release of trapped gasses. Suppliers will generally provide curing instructions and process steps to remove organics and binders. Otherwise, hydrogen-saturated hydrocarbons or moisture could release during the solder hermetic sealing process. Trapped gases within the package will negatively affect its overall electrical performance and lifespan.

Consequently, a well-controlled die-attach process is important for achieving void-free bonding. Unfortunately, post-seal validation can be costly and may produce irregular or misleading results. Close attention must be paid, then, to storage conditions, expiry date, mixing ratio, duration of use, and volume required per unit per shift. There is also the looming possibility of moisture absorbed from the environment.

#### **SEAL RING:**

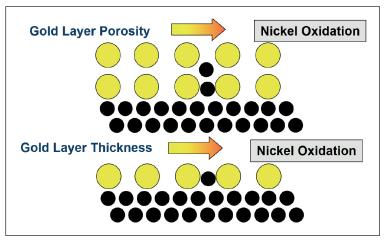

This is one of the most important components in the ceramic package when it comes to hermetic sealing. As is the case with die and wire bond pads, nearly the full surface of the seal ring is used in the soldering process. The seal ring surface is generally porous and plated with nickel and gold, which could lead to nickel migration to the seal ring at elevated temperatures. This in turn may result in pin holes and solder voids. Thus, careful handling and temperature control are essential.

### Effective hermetic sealing: Step-by-step

Successful hermetic sealing is dependent upon several factors, including:

- Design guidelines for the package seal ring

- Sealant and lid material selection

- Sealing methods and process controls

- Post-hermetic sealing tests and troubleshooting

- Next-generation packaging material options

### DESIGN GUIDELINES OF THE PACKAGE SEAL RING:

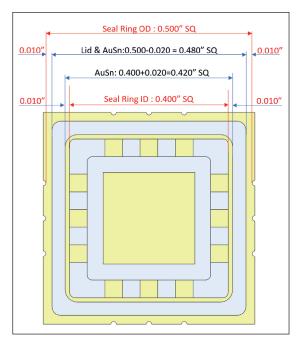

Consider the size of the hermetic cover lid and its solder. The outer seal ring, the metal lid, and the gold-tin frame are key design elements. For example, if the package seal ring outer length and width is 0.500" square, the lid should 0.500 inch -0.010" - 0.010", or 0.480" square.

Next is to determine the gold-tin solder inner dimensions. For this, both inner and outer dimensions must be considered. If the seal ring inner dimensions are 0.400" square, then the gold-tin solder inner dimensions should be 0.400" + 0.010" + 0.010", or 0.420" square. The inner and outer radii are also important for the overall design, as is the thickness of the solder and lid. These dimensions will be based upon the size of the final package.

#### TECHNOLOGY I ADVANCED PACKAGING

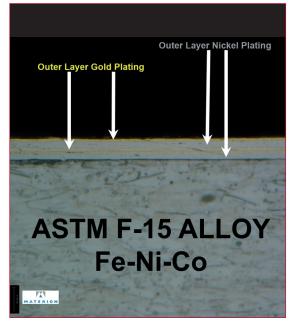

> Cross section image of four layers plated sequentially with nickel and gold.

The 0.010" clearance relies on the availability of space for the seal ring. It can be as low as 0.002" for the outer gap, and almost as low for the inner seal ring if the ring is narrow.

#### SEALANT MATERIAL SELECTION:

There is a variety of suitable solder alloys and eutectic solders for leak-safe hermetic joints. Gold-tin has been proven particularly effective for bonding metal lids to ceramic or metal packages. The 80% gold/20% tin solder melts at 280°C and holds up well when subjected to temperature cycle testing.

The 80% gold/20% tin alloy must be manufactured with very few impurities and must be within its nominal weight percentage to achieve a good bond.

Nickel migration process.

Frame lid assembly.

Tack weld points at corners.

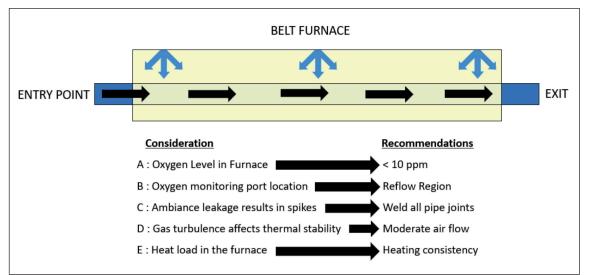

<sup>&</sup>gt; Critical parameter controls and recommendations for effective hermetic sealing using a belt furnace.

#### TECHNOLOGY | ADVANCED PACKAGING

> Vacuum furnace inner chamber.

- Gold-tin purity: Decrease in heat conductivity

Gold-tin contamination: Oxides, organics

- Oold-tin interfacial contact area

#### **COVER LID MATERIAL SELECTION:**

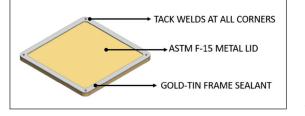

The metal lid is an alloy of iron, nickel and cobalt, also known as ASTM F-15. In order for the gold-tin solder to bond well with the package, the metal lid must be well prepared. A lid composed of more than 50% iron (Fe) elements could oxidize over time. A bare lid will not allow gold-tin solder wetting. Reliable gold plating is therefore essential.

The lid is electroplated with 100 to 350 microinches of nickel, followed by gold at a thickness of 50 microinches. Additional nickel and gold are plated for high-reliability applications, though the sum of

Gold-tin reflow profile.

both nickel films cannot exceed 450 microinches, while the sum of the gold-plated films must be at least 50 microinches. The idea is to prevent excess build-up at the edges. which could eventually have a negative effect on the hermetic seal. The following illustration shows a cross-section of the four-layer plated lid.

#### **EFFECTIVE PLATING:**

The plating process is extremely critical. Edge buildup, for example, must be avoided. The electroplate bath and chemistry maintenance are both important. It should be noted that this plating is not cosmetic in nature, but is rather designed for high-quality hermetic sealing, which also entails good solder bonding. Poor maintenance plating could trap unwanted gases.

Post-plate tests are available to check the quality of the plating, particularly to quantify hydrogen content in the plated films.

Plating bath maintenance and bath chemistry checks should be performed periodically for preventative reasons. Post-plate bakeouts are also sometimes performed following last-stage plating at lower temperatures (between 120°C to 150°C) for 8 to 12 hours.

High-temperature bakeouts for longer durations could cause the inner layer of nickel to migrate to the gold layer and interfere with solder wetting. The gold-tin solder alloy will not wet with nickel. Nickel migration may also occur if the plated layer is too thin or demonstrates high porosity on the plated surface.

#### Sealing methods and process controls

• Tack Welding or Spot Welding: The gold-tin solder must be attached to the plated lid by spot or tack welding. This process is crucial to avoiding misalignment and other defects that could eventually affect seal yield. It also creates additional benefits for end users who must assemble the frame and lid as a single component before final sealing. Tack welding requires very small portions of the eutectic goldtin solder at all four corners to melt and adhere to the plated lid.

• Reflow equipment and process controls: It's important to select the proper reflow equipment prior to sealing. Hermetic sealing with gold-tin or other solders requires an inert environment; otherwise, oxidation might affect the integrity of the seal. If a belt furnace is used, the maintenance and seal profiles must be well monitored. Oxygen content within the reflow chamber should be tracked and controlled. Similar monitoring is required if a vacuum seal furnace is chosen, with the additional benefit of removing unwanted gasses. In both cases, equipment performance will ultimately determine the quality of the hermetic seal.

WINNER OF THE PRODUCTRONICA INNOVATION AWARD

OUR NEW BATCH TOOL FOR HIGH THROUGHPUT WET PROCESSING

**Compact design** for optimal use of the clean room

Fast processes through high process temperature of up to 170°C

**Uninterrupted production flow** via warehouse with up to 75 storage locations and automated loading connected to the transport system

# Reduction of particle generation & contamination

by improved access and optimized extraction of the process chamber

# WE ARE YOUR PARTNER FOR WET PROCESS EQUIPMENT

AP&S International GmbH . Obere Wiesen 9 . 78166 Donaueschingen . Germany . 0771 8983 0 . sales@ap-s.de . www.ap-s.de

#### TECHNOLOGY | ADVANCED PACKAGING

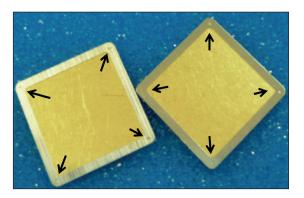

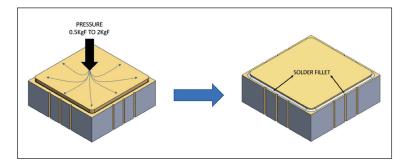

Ilustration 16: Left, assembly with pressure applied. Right, postseal with solder fillet.

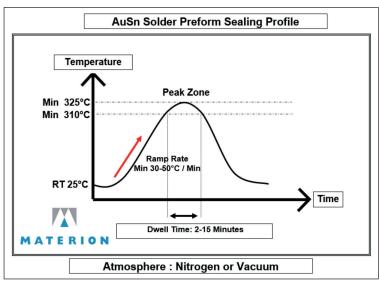

- The gold-tin seal profile: Following are key considerations for the gold-tin seal profile:

- Rise rate: The rise rate must be gradual and slow. This helps to release gasses from the various components without promoting nickel migration. Such migration may result from a quicker ramp-up, especially with porousplated layers. Vacuum furnaces will evacuate any outgasses, while a belt furnace with nitrogen pressure should do the same.

- Peak temperature: Eutectic gold-tin solder melting temperature is 280°C. In addition to the sealing components, fixtures, clips and other materials can also pull in heat. Once the solder and lid reach peak temperature, the goal should be the complete removal of gases, complete solder flowing, solder fillet formation, and the elimination of pin holes or void removal. Duration of exposure to peak temperature is very subjective and depends on product size, ssembly tools and conditions. Reducing this duration while critical processes are in progress can uncover failure modes, which can be observed visually, through leak tests or under X-ray.

- Ramp down from peak zone: Product cooling must also be done gradually, as sudden cooling or ejection of the product from the oven can be quite harmful.

• Adequate pressure should be applied to gold-tin solder to achieve a good hermetic joint. Interestingly, though, only about 0.5 to 4 kilogram-force is required. In all cases the pressure is transferred from the lid down to the gold-tin sealant (see Illustration 16). As mentioned, this pressure is very helpful during the peak temperature phase to press the lids and squeeze out molten solder to form a fillet.

#### **SEAL CLIPS:**

There are many different types of readily procurable clips. Depending on the type of package and production volume, pressure clips can be customized and fabricated. The aligning fixture should also be considered if increased production volume is desired.

#### **POST-SEAL RELIABILITY TEST:**

Post-seal reliability tests validate process and material selection. Several different levels of tests are performed one after another. Details of all listed tests can be found in standard Mil-883 guidebooks.

#### NEXT-GENERAL PACKAGING MATERIAL OPTIONS:

These tests are intended to confirm successful hermetic sealing. Similarly, an effective packaging process can significantly prolong the life of the package in field.

Many applications, such as a board-level module installed in a satellite or space vehicle, are not reachable for replacement or repair. Thus, they are made to last even in the most adverse conditions.

A variety of new materials and processes are coming into the market. For next-generation hermetic sealing applications, for example, a range of innovative cover lids are now available. These include hermetic covers or Visi-Lids for optical communications, non-magnetic Combo Lids for electromagnetic nose controls, and Getter Combo Lids to contain the release of hydrogen from the package.

| No | Reliability Tests                     | Purpose                                            |

|----|---------------------------------------|----------------------------------------------------|

| 1  | Gross leak test or die penetrate test | Hermeticity, identify leaks                        |

| 2  | Fine leak test (with helium bombing)  | Hermeticity, identify leaks                        |

| 3  | Optical leak test                     | Hermeticity, identify leaks (mass scale)           |

| 4  | Krypton leak test                     | Hermeticity, Identify leaks (quicker than helium)  |

| 5  | Electrical test                       | Assembled unit performance                         |

| 6  | Temperature cycle test                | Accelerated test for field performance             |

| 7  | X-ray imaging                         | Solder joint integrity                             |

| 8  | Salt Atmospheric Test (SAT)           | Accelerated test for field performance             |

| 9  | PIND Test                             | Sealed unit internal particle identification       |

| 10 | Visual inspection                     | Visual assurance of sealed unit, solder flow, etc. |

Various reliability tests.

# High-temperature insulation for semiconductor process tube up to 1.600 °C

**UltraVac:** PCW vacuum-formed 3-dimensional insulation shapes

- Cylinders

- Rings

- Vestibule blocks for e.g. CVD-, hydrogen-, oxygen- or diffusion-furnaces

M.E. SCHUPP Industriekeramik GmbH | Aachen/Germany | info@schupp-ceramics.com | www.schupp-ceramics.com

# **Lasers:** a sustainable wafer heating solution

Lasers, in particular diode lasers, are an attractive and sustainable option for future chipmaking needs.

#### BY IURII MARKUSHOV, KAZUNARI MIYATA AND HARLON O. NEUMANN AND TOBY STRITE, IPG PHOTONICS CORPORATION

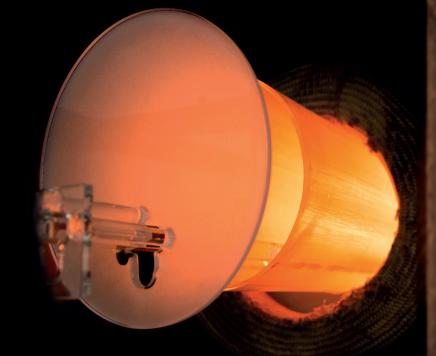

THE JOURNEY to a sustainable fab requires closer examination of how silicon wafers are heated during chip making. Elevated wafer temperature is required for annealing, epitaxial and etch processes. A sustainable heating solution must minimize energy consumption and consumables, while providing excellent temperature uniformity and competitive thermal rise time. Heating by infrared laser has proven itself in other industries to be just such a silver bullet. Here we describe heating experiments on a 200 mm silicon wafer utilizing a commercially available 975 nm diode laser. An empirical thermal model enables extrapolation to 300 mm wafer heating scenarios. The experimental and theoretical findings coupled with the mature state of diode laser technology suggest that heating silicon wafers by laser is an attractive path forward.

Our experimental apparatus (Figure 1) projects an 11kW near infrared (975 nm) diode laser over a thermally isolated 200 mm polished silicon wafer in regular atmosphere. The projection optics uniformly illuminate a ~213 mm square fully covering the wafer surface with minimal energy overspill onto the heatsink beneath. Wafer temperature is measured using a Chino model IP-CZPOJL pyrometer

Figure 1. Experimental configuration showing the 11kW laser (right) and experimental chamber (left)

positioned about one meter above the wafer. Our experiments operate the laser at constant output power until steady state temperature is reached. After laser power is shut off, the cooling curve is also recorded.

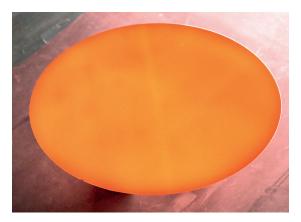

Maximum available 11 kW laser power heats the wafer quickly. Our experiment achieves 800°C in below 9 seconds. Steady state laser power of ~8.1 kW is sufficient to maintain that temperature. Figure 2 shows the heated wafer at 800°C. The color attests to the uniform nature of the laser heating across the wafer diameter.

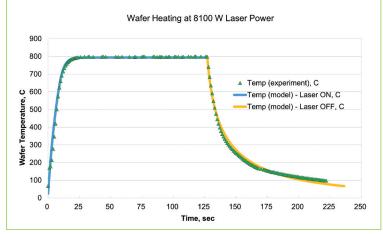

Data were collected at six laser settings ranging from 0.86 kW to 8.1 kW constant power, enabling us to develop an empirical model covering a wide range of energy input, temperature and wafer diameters. The thermodynamic model incorporates absorptive heating from the laser, the wafer's radiative and convective losses, and the heat capacity of silicon, each as a function of temperature.

Figure 3 shows an example of fitting curves (blue – heating rise and steady-state and yellow - cooling) which accurately match experimental observations at 8.1 kW laser power. Similarly excellent fits were generated at the five other settings to create our temperature dependent empirical model.

Discussions with prospective customers suggest both the short rise times and low steady state power requirements demonstrated by the laser heater are highly attractive compared with infrared lamp alternatives. Fast rise times increase tool throughput. These are possible because up to 80% of the laser optical energy is absorbed by the silicon wafer. Low overall power requirements are a byproduct of the strong absorption, along with the high directivity of laser, meaning little energy is wasted heating the chamber atmosphere or enclosure. In contrast, infrared lamps operate hot, emit energy in all directions, and produce significant energy output at longer wavelengths where silicon is not highly absorbing.

#### TECHNOLOGY | WAFER HEATING

➤ Figure 2. Visible light image of 200 mm silicon wafer heated to 800°C by laser. Click here to view a video clip

Figure 4 shows the calculated laser requirements to heat 300 mm silicon wafers to a variety of temperatures. The calculated values are modeled using a regular hexagonal illumination pattern such that 91.5% of the laser output hits the wafer surface. The first column provides the laser power required to heat the wafer to target temperature within a 10 second rise time constraint. Less power is required to hold a 300 mm wafer at the target temperature. The range of values required for steady state is given in the second column. The empirical model incorporates a temperature dependent absorption coefficient for silicon to match experimental data. At 400°C, we observe 62% of the laser energy is absorbed by the wafer, while at 800°C the absorbed percentage rises to 80%.

Commercially available diode lasers, such as the DLS-ECO series from IPG Photonics Corporation, are attractive options for the sustainable wafer fab. Silicon is absorptive at 975 nm, so up to 80% of the laser optical energy contributes to wafer heating. A diode laser converts 55+% of electrical power input to usable optical energy. Laser output is homogenized for uniform energy distribution, while its shape is tailored to match the wafer dimensions. Little energy is wasted heating the susceptor, chamber atmosphere or enclosure.

High component redundancy ensures diode lasers provide uninterrupted, service-free operation over

seven years without any consumables. Fiber delivery cables 15 meters or longer enable laser light to be conveniently delivered to the tool, while all heat dissipation and electrical utilities remain outside the clean room. Because the laser operates at a single mid-infrared wavelength, pyrometry is effective in the absence of heater source interference.