# SLICON SEMICONDUCTOR CONNECTING THE SILICON SEMICONDUCTOR COMMUNITY

# 5G, AI & IoT devices benefit from latest dual-layer materials

### VOLUME 42 ISSUE IV 2021

### INSIDE

News Review, Features, News Analysis, Profiles, **Research Review** and much more...

### 🄰 @siliconsemi

### **MES CAPABILITIES CAN** EXTENDS FAB LIFETIMES

Current global microelectronics shortage demonstrates that IC fabs are not created to pivot guickly as much as they are to produce high quality products at low cost

### www.siliconsemiconductor.net

### **ADDING ML TO APC** MANUFACTURING SYSTEMS

n) SEM 2.0 (kV)

advanced packaging interconnects. (Left) baseline process (Right)

Brewer Science Dual-Layer materials enable damage-free

after optimization with Brewer Science materials

With the continual buzz around artificial intelligence (AI) and machine learning (ML), one might think it relatively easy to improve output by adding a 'bit' of AI/ML to one's IC recipe

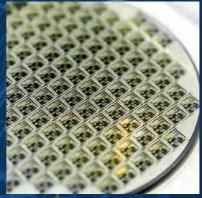

# DIE-TO-WAFER (D2W) BONDING SOLUTIONS

Fusion and hybrid bonding for next-generation heterogeneous integration

Collective D2W bonding enabled by extensive knowledge in carrier preparation and die handling

Direct placement D2W activation and cleaning complete solution with EVG®320 D2W

Production-ready equipment solutions for successful integration of chiplets

Heterogeneous Integration Competence Center™ serving as leading-edge incubation center for customers and partners

GET IN TOUCH to discuss your manufacturing needs www.EVGroup.com

EVG<sup>®</sup> 320 D2W

# **VIEWPOINT** By Mark and rews Technical Editor

# Ending the semiconductor shortage will take time, diligence

Anyone working in the semiconductor supply chain cannot miss the mass media drumbeat of oh-so-simple yet often unrealistic solutions for ending the chip shortage. Rarely does mainstream media manage to offer accurate insights into our complicated industry in a package fitting neatly into 60-second news bites.

Some commentators outside of industry almost make it sound as if solutions should be as simple as tossing another log on a fire. Add capacity? Sure—there's an idea. But those working in IC manufacturing know fabs only cost around a billion euros; they take three or more years to build, another year to qualify equipment and 'around' 6-18 months for profitable yields. The same applies to onshoring production or squeezing more from fabs already operating 24/7. The plain and simple truth won't grab headlines, but you and I know this is going to take time and diligence amongst the myriad suppliers that support manufacturers.

The shortage has at least focused attention on the need for supply chain resilience. Everyone is getting busy. The US wants to on-shore IC manufacturing, yet Intel needs a year-plus to complete its newest Southwest fab. TSMC's US project is not yet 'shovel ready.' The EU is in the game with its European Chips Act, but like other solutions, this will take time. China is pushing its aggressive fab building programmes, but they are also encountering headwinds. Easy and quick? Hardly.

In positive news reported as 2Q ended, SEMI researchers forecast manufacturing equipment

sales will crest \$100 billion by year's end. SEMI later reported that wafer shipments will post record growth through 2024; GlobalFoundries is going public and Apple announced its latest 'home grown' processor chips continue to set new performance standards.

In this Silicon Semiconductor edition we look at advanced 3D device materials including those that will be highlighted at SEMICON Europa in November.

Our cover story profiles Brewer Science and its Dual-Layer materials that play a critical role in temporary wafer bonding that facilitates optimized thermal compression bonds. We also explore the benefits of an advanced MES for future-proofing industrial automation and new research innovations.

For your free weekly e-news roundup go to: WWW.SILICONSEMICONDUCTOR.NET

# CONTENTS

### VOL: 42 ISSUE IV 2021

## 5G, AI & IOT DEVICES BENEFIT FROM LATEST DUAL-LAYER MATERIALS

Wafer-level packaging (WLP) has become the norm for a growing number of 5G, Artificial Intelligence (AI) and Internet of Things (IoT) system components

## FEATURES

24 Tignis simplifies ML to advanced process control manufacturing systems

> With the continual buzz around artificial intelligence (AI) and machine learning (ML), one might think it relatively easy to improve manufacturing output by adding a 'bit' of AI/ML to one's IC recipe

### 26 Advanced MES apabilities can extend semiconductor fab lifetimes

As the current global microelectronics shortage demonstrates, semiconductor manufacturing is not a simple

34 How do we protect discoveries without closing the door on innovation and industry growth? Patents can create more favourable environments for companies to thrive provided they have a suitable IP strategy for their size

### 38 Outsourced SAM testing provides a cost-effective solution for testing nd failure analysis

Ultrasonic-based Scanning Acoustic Microscopy (SAM) has long been the method of choice for quality testing and failure analysis of silicon ingots, wafers, integrated circuits, MEMS, and other electronic packages

### 42 Today's digital transformation demands better bulk gas delivery

Today's digital transformations are happening faster than ever. And as technology evolves, so should the systems and solutions that support it

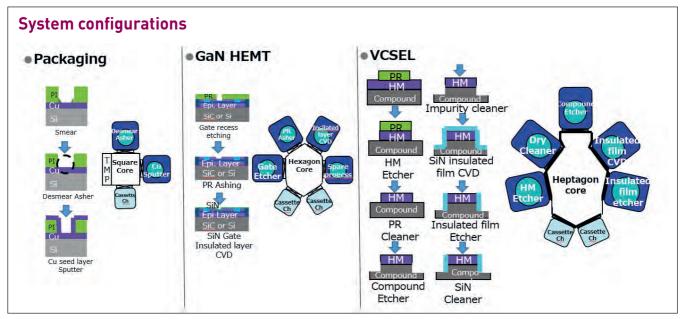

### 44 ULVAC uGmni **Cluster System** for Advanced **Microelectronics**

The ULVAC uGmni, all-in-one tool provides different process modules such as sputtering, etching and others on the same transfer core

## **NEWS**

- 06 Edwards opens new flagship Service Technology Centre in Dublin

- 07 Advantest Introduces evolutionary V93000 EXA Scale SoC test system

- 08 SkyWater signs technology transfer and license agreement with Deca

- 09 Sivers Semiconductors' Japanese customer takes step towards mass production

- 10 Applied Materials unveils eBeam metrology system

- 11 PragmatIC Semiconductor secures \$80 million funding

- 12 JNano Dimension Acquires Essemtec

### RESEARCH

18 NUS researchers develop brain-inspired memory device that can revolutionise semiconductor design

tbrun@brunmedia.com

Publisher & Editor Jackie Cannon Technical Editor Mark Andrews Contributing Editor Richard Stevenson Sales & Marketing Manager Shehzad Munshi USA Representatives Tom Brun Brun Media Janice Jenkins

Director of Logistics Sharon Cowley Design & Production Manager Mitch Gaynor jackie.cannon@angelbc.com +44 (0)1923 690205 mark.andrews@angelbc.com richard.stevenson@angelbc.com

shehzad.munshi@angelbc.com +44 (0)1923 690215 +001 724 539-2404 jjenkins@brunmedia.com +001 724-929-3550 sharon.cowley@angelbc.com +44 (0)1923 690200 mitch.gaynor@angelbc.com +44 (0)1923 690214

Chairman Stephen Whitehurst Chief Executive Officer Sukhi Bhadal Chief Technical Officer Scott Adams Directors Jackie Cannon, Sharon Cowley stephen.whitehurst@angelbc.com +44 (0)2476 718970 sukhi.bhadal@angelbc.com +44 (0)2476 718970 +44 (0)2476 718970 scott.adams@angelbc.com

Published by Angel Business Communications Ltd, Unit 6, Bow Court, Fletchworth Gate, Burnsall Road, Coventry CV5 6SP, UK T: +44 (0)2476 718 970 E: info@angelbc.com

Silicon Semiconductor is published five times a year on a controlled circulation basis. Non-qualifying individuals can subscribe at: £50.00/e60.00 pa (UK & Europe), £70.00 pa (air mail), \$90.00 pa (USA). Cover price £4.50. All information herein is believed to be correct at time of going to press. The publisher does not accept responsibility for any errors and omissions. The views expressed in this publication are not necessarily those of the publisher. Every effort has been made to obtain copyright permission for the material contained in this publication. Angel Business Communications Ltd will be happy to acknowledge any copyright oversights in a subsequent issue of the publication. Angel Business Communications Ltd © Copyright 2021. All rights reserved. Contents may not be reproduced in whole or part without the written consent of the publishers. The paper used within this magazine is produced by chain of custody certified manufacturers, guaranteeing sustainable sourcing. US mailing information: Silicon Semiconductor, ISSN 1096-598X, is published 4 times a year, Jan/Feb, March, April/May, June, July, August/September, October, November/ December by Angel Business Communications Ltd, Unit 6, Bow Court, Fletchworth Gate, Burnsall Rd, Coventry CV5 6SP. UK. The 2021 US annual subscription price is \$90.00. Airfreight and mailing in the USA by agent named World Container Inc, 150-15, 183rd Street, Jamaica, NY 11413, USA. Periodicals postage paid at Brooklyn, NY 11256. US Postmaster: Send address changes to Silicon Semiconductor, Air Business Ltd, c/o WN Shipping USA 156-15, 146th Avenue, 2nd Floor, Jamaica, NY 11434, USA. Printed by: The Manson Group. ISSN 2050-7798 (Print) ISSN 2050-7801 (Online) © Copyright 2021. We strive for accuracy in all we publish; readers and contributors are encouraged to contact us if they recognise an error or omission. Once a magazine edition is published [online, in print or both], we do not update previously published articles to align old company names, branding, marketing efforts, taglines, mission statements or other promotional verbiage, im-ages, or logos to newly created or updated names, images, typographic render-ings, logos (or similar) when such references/images were accurately stated, rendered or displayed at the time of the original publication. When companies change their names or the images/text used to represent the company, we invite organizations to provide Angel Business Communications with a news release detailing their new business objectives and/or other changes that could impact how customers/prospects might recognise the company, contact the organisa-tion, or engage with them for future com nercial enterprise.

### **INDUSTRY NEWS**

# Edwards officially opens new flagship Service Technology Centre in Dublin

EDWARDS, supplier of vacuum and abatement services and solutions to the global semiconductor industry, has opened its new flagship Service Technology Centre (STC) in Blanchardstown, Dublin.

The new site and associated field service operations have so far employed a diverse workforce of around 100 people, 90% of whom are engineers, and this is expected to rise to around 120 by the end of the year. The STC, which will help support the semiconductor manufacturing industry in Ireland, represents an investment in the region of US\$7.5 million.

Semiconductor manufacturing is essential to supporting developments in the technology, electronics, transport, scientific and healthcare sectors – all of which have been classed as critical industries during the Covid-19 pandemic.

Edwards is the world leader in supplying the vacuum and abatement technology, along with the equipment and services, necessary to support the efficient and environmentally sustainable production of semiconductors.

The new 4,000m<sup>2</sup> facility uses advanced automation and data solutions to disassemble, clean, inspect, repair, replace and reassemble vacuum pumps and abatement equipment. On-site manufacturing will improve responsiveness to customers' needs.

State-of-the-art technology in the new data driven facility brings together innovations developed by the expertise of our STCs around the world, including the automated cleaning system, smart tooling, automated guided vehicles, and a digital pump tracking system which enables Edwards to track progress of products through the STC and provides data to improve planning abilities, while keeping the customer informed.

These new technologies, including the use of a mobile app for employees, significantly remove the amount of paper

needed and thus reduce the facility's carbon footprint.

Edwards is supported by IDA Ireland through the Department of Enterprise, Trade and Employment. Tánaiste and Minister for Enterprise, Trade and Employment Leo Varadkar TD said, "Today is a big day for Edwards and I'd like to congratulate all staff on the opening of this flagship centre. I'm sure you will all find a very warm home in Blanchardstown. Today's opening reaffirms Ireland's position as a global leader in the semiconductor industry. I wish Edwards every success in the future."

Troy Metcalf, President of Edwards' Semiconductor Service division formally opened the new facility and welcomed the new employees. Troy commented, "I am delighted to be opening our new Dublin Service Technology Centre, the latest in our global network of STCs that enables us to best support our customers in the safe, productive and environmentally sustainable manufacturing of semiconductors in Ireland and across Europe.

I want to extend my sincere gratitude to everyone involved in helping to facilitate the new site for their enthusiasm and hard work, despite the significant challenges posed during the pandemic.

"I would also like to thank IDA Ireland on behalf of Edwards for the continued valuable support they have provided us in this exciting new venture."

Congratulating Edwards on its official opening, Martin Shanahan, CEO, IDA Ireland said "Despite the challenge of this past year, Edwards has already onboarded 100 new members of staff and opened its new flagship Service Technology Centre (STC) in Dublin. This is a very welcome investment and I wish Edwards continued support and ongoing success with this operation."

Edwards is continuing to recruit for the new Dublin facility. Learn more about the company and emerging roles or send your details to edwardsvac@ collinsmcnicholas.ie

# Advantest introduces evolutionary V93000 EXA scale SoC test system

SEMICONDUCTOR test equipment supplier Advantest Corporation has announced its next-generation V93000 testers targeted at advanced digital ICs up to the exascale performance class. The systems' new test heads incorporate Xtreme Link technology, and the EXA Scale universal digital and power supply cards that enable new test methodologies, lower cost-of-test and faster time-to-market.

Today's most advanced semiconductor processes allow for technology transformations that enable real-time integration of data from a countless number of sources such as IoT and handheld devices, automobiles and large servers to name a few. As mobile processors, high-performance computing (HPC) and artificial intelligence (AI) ICs evolve, the amount of data being processed continues to grow exponentially. Along with these advancements, new testing challenges, including very high scan-data volumes, extreme power requirements, fast yield-learning, and high-multisite configurations, need to be addressed.

Advantest's new V93000 EXA Scale generation addresses these challenges with innovative advancements on the proven V93000 architecture. All EXA Scale cards are designed with the latest generation of Advantest's test processors with 8 cores per chip, featuring unique capabilities to speed up and simplify test execution. Furthermore, the V93000 EXA Scale system employs Advantest's patented Xtreme Link technology, a communication network designed specifically for automatic test equipment (ATE). The technology provides high-speed data connections, embedded computing power, and instant card-to-card communication.

The system's new Pin Scale 5000 digital card is designed to address the explosion of scan data volumes which are inherent to large digital designs. The Pin Scale 5000 is setting a new standard for scan test with 5Gbit/s speed, providing the deepest vector memory available on the market and using the Xtreme Link technology for the industry's fastest processing of results. With this technology, customers can choose the most efficient scan methodology for their device.

Very high current requirements up to several 1000A at supply voltages below 1V make power delivery capabilities of ATE a differentiating factor. The XPS256 power supply is another industry innovation, covering all power requirements with a single DPS card: fine-granular power, unlimited and flexible ganging and exceptional static and dynamic performance.

With 256 channels on the Pin Scale 5000 digital card and XPS256 power supply card, the density is doubled,

while maintaining the industry-leading V93000 highly integrated form factor. High-multisite configurations can be implemented in smaller physical systems, reducing infrastructure cost and floor-space requirements.

Scalable solutions extend across test heads of different sizes, including the ability to test a mix of device functions, like digital, RF, analog and power on one test system.

The V93000 EXA Scale generation renews Advantest's commitment to platform compatibility. Existing V93000 load boards and Smart Scale cards are compatible, supporting a smooth transition to the V93000 EXA Scale generation and best asset utilization. With the continued use of the proven SmarTest software, customers benefit from the installed base software infrastructure and tooling.

Advantest has already shipped dozens of the V93000 EXA Scale systems to multiple industry-leading customers.

# SkyWater signs technology transfer and license agreement with Deca

SkyWater Technology, technology realization partner and Deca Technologies (Deca), a provider of advanced electronic interconnect technology, has announced an agreement for Deca's second generation M-Series fan-out wafer-level packaging (FOWLP) technology with Adaptive Patterning within SkyWater's advanced packaging facility in Florida. The companies are endeavoring to establish the first high volume FOWLP capability in the U.S. to bring proven solutions for single and multi-die packaging and advanced heterogeneous integration capability for chiplets through 2.5D and 3D implementations.

Deca's first generation technology changed the game with high volume production for leading mobile applications and is well-known for enabling exceptional board-level reliability, end-customer quality and electrical performance.Deca's unique Adaptive Patterning with mask-less laser direct imaging delivers high-density design rules and high production yields in a cost-effective miniaturized format. Deca's second generation FOWLP technology includes 2 µm RDL features

combined with industry-benchmark 20  $\mu$ m bond pad pitch and targets advanced mobile devices, high-performance computing (HPC), high-end networking, artificial intelligence (AI), and edge computing as well as high density 3D integration technology in medical and defense applications.

Cliff Sandstrom, Deca's vice president of technology development, stated, "This is an exciting time for the industry as SkyWater invests in Deca's Gen 2, delivering a cutting-edge packaging technology which is competitive with current industry leaders including advanced silicon interposers. With multiple customers designing into Gen 2, we look forward to working closely with SkyWater to successfully bring these new products to market."

Dr. Brad Ferguson, SkyWater Florida senior vice president and general manager, added, "Through this collaborative work with Deca, we look forward to reaching another milestone in the realization of our vision for state-ofthe-art domestic advanced packaging foundry services. We're proud to lead the onshoring of this key technology and expect it to serve customer demand in numerous markets. Deca's powerful integration platform nicely complements our Technology as a ServiceSM model for customers driving leading-edge device architectures that require advanced electronic interconnect solutions.'

## SEMI applauds European Chips Act

SEMI, the global industry association has applauded the proposed European Chips Act legislation aimed at strengthening semiconductor research, development, and manufacturing in Europe.

Proposed by European Commission President Ursula von der Leyen in her State of the Union speech on September 15, the European Chips Act is part of the Commission's policies to achieve the digital transformation of the region's economy by 2030 under its Digital Decade plan.

"SEMI supports incentives for semiconductor manufacturing and supply chain investments such as those proposed to be included in the European Chips Act," said Ajit Manocha, SEMI president and CEO. "Transparent implementation of such initiatives allows industry participants the opportunity to efficiently strengthen the resilience of the global semiconductor industry and create a more robust supply chain. The current chip shortage has exacerbated backlogs and lead times for semiconductor manufacturing equipment and materials. Given the vital importance of these elements to expanding semiconductor production capacity, incentives should extend to investments in both new and existing semiconductor manufacturing equipment and materials facilities."

Citing the current shortages and Europe's dependency on the global chip ecosystem in a recent blog post, Thierry Breton, the European Commissioner for Internal Market, emphasized the Chips Act must ensure the resilience of the semiconductor supply chain across design, production, packaging and equipment. Breton calls for the legislation to strengthen Europe's ability to develop mega fabs capable of high-volume production of advanced and energy-efficient semiconductors. Additionally, he recommends the Chips Act include strategies for extending the research ambitions of Europe, tightening coordination of chip production among EU member states, and providing a framework for international cooperation and partnerships.

# Sivers Semiconductors' Japanese customer takes step towards mass production

SIVERS SEMICONDUCTORS AB has announces that its Japanese lead customer Fujikura, after several successful customer trials, is now preparing the start of full-scale, highquality volume production of their 60 GHz communication module.

Sivers Semiconductors and Fujikura have worked closely together for several years in a joint effort to offer this competitive 60 GHz communication module. Fujikura has developed a compact communication module including a baseband wireless modem function and an antenna with an included RF front end RFIC from Sivers Semiconductors (TRX BF/01). This module developed by Fujikura is built on their own low loss liquid crystal polymer (LCP) material and Fujikura antenna design. Kiyoshi Kobayashi, Product Owner of the 60 GHz communication module at Fujikura explains: "We have been working very tightly with Sivers Semiconductors for several years and they have provided excellent guidance and support during the development and integration of our new 60 GHz module. Over the last year we have had great success in several trials and pilot projects we have been involved in and now we are taking the next important step to secure our capabilities to provide high volumes and good quality products to the market."

Anders Storm, Group CEO of Sivers Semiconductors says: "Fujikura is a well-known company with many capabilities, and it is an honor to work with their 60 GHz team in this project. With thoroughness and very high-quality standards, they have taken steps to reach a point where they now will take the final leap to commercially pursue the many new opportunities in the 60 GHz communications market. We are very happy to see that they now are entering this phase."

As part of this project, Sivers Semiconductors and Fujikura are now also starting commercial negotiations to reach a long-term volume purchasing agreement, which is expected to be finalized during the autumn.

### **PTIM**WAFER SERVICES

OPTIM Wafer Services is pleased to announce the installation of an automated ALPSITEC MECAPOL E550 CMP tool at its site in Greasque France.

The system will allow OPTIM to offer for following new or improved services.

- Oxide CMP Planarisation

- Oxide Roughness Improvement

- Metal CMP

- Poly CMP

This additional capability enhances OPTIM's already large portfolio of services that include:

- Wafer thinning by grinding

- Individual Die thinning

- Taiko Grinding

- Single/Double side Polishing

- SOI Processing

- Edge Trimming

- Wafer Dicing

- Dice Before Grinding

- Wafer Cleaning

- Process development services, combining any of the above capabilities.

For detailed technical discussions please contact either Mr. Mark Wells or Mr. Georges Peyre using the contact details below or visit our website.

### www.Optimwaferservices.com

Mark Wells Tel - +44 1743 891 820 Email – MWells@optimws.com

### **Georges Peyre**

**Tel** - +33 442 126 158 **Email** – GPeyre@optimws.com

### **INDUSTRY NEWS**

# Applied Materials unveils eBeam metrology system

APPLIED MATERIALS has unveiled a unique eBeam metrology system that enables a new playbook for patterning control based on massive on-device, across-wafer and through-layer measurements.

Advanced chips are built one layer at a time, and each of billions of individual features must be perfectly patterned and aligned to create working transistors and interconnects with optimal electrical characteristics. As the industry increasingly moves from simple 2D designs to more aggressive multipatterning and 3D designs, a commensurate breakthrough in metrology is needed to perfect each critical layer and enable the best performance, power, area-cost and time to market (PPACt).

Traditionally, patterning control has been achieved using optical overlay tools that help align die patterns with "proxy targets" which are guide marks printed into the spaces between die that are removed from the wafer during die singulation. Proxy target approximation has been complemented with statistical sampling of a small number of die patterns from across the wafer. However, after successive generations of feature shrinking, broader adoption of multipatterning, and the introduction

of 3D designs that cause interlayer distortions, the traditional approach is leading to measurement deficiencies - or "blind spots" - that are making it more difficult for engineers to correlate intended patterns with on-die results. With the arrival of new eBeam system technology that can directly measure semiconductor device structures across the wafer and through layers at high speed, customers are moving to a new patterning control playbook based on big data. Applied's latest eBeam metrology innovation - the PROVision 3E system - is especially designed for this new playbook.

"As the leader in eBeam technology, Applied Materials is giving our customers a new playbook for patterning control that is optimized for the most advanced logic and memory chips," said Keith Wells, Group Vice President and General Manager, Imaging and Process Control at Applied Materials. "The resolution and speed of the PROVision 3E system allows it to see beyond the blind spots of optical metrology, performing accurate measurements across the wafer and between the many layers of a chip. This provides chipmakers with the multidimensional data sets they need to improve PPAC and accelerate the time to market of new process technologies and chips.'

Kanthal LPCVD technology opens new deposition opportunities in optical, power and microLED applications

YES (Yield Engineering Systems), a manufacturer of process equipment for semiconductor packaging, life sciences and 'More-than-Moore' applications, has purchased the semiconductor equipment business of Swedish heating technology provider Kanthal.

Under the terms of the agreement, which was signed on October 6th, YES will take ownership of Kanthal's semiconductor-related capital equipment portfolio, system-related upgrades, and service needs. The acquisition will add Kanthal's hightemperature (>800°C) furnace technology as well as Low Pressure Chemical Vapour Deposition (LPCVD) processes to YES's growing capabilities in the thermal processing area.

"We aim to be the semiconductor industry's provider of choice for surface modification, material enhancement, and high-quality deposition," said Rezwan Lateef, president of YES. "With this acquisition of equipment and technical expertise from a leader in industrial heating, we look forward to supporting our global customer base with new high-temperature annealing and bonding systems that leverage Kanthal heating equipment.

"In addition, we feel that the Kanthal LPCVD technology has potential to open exciting deposition opportunities for YES beyond our current monolayer coating systems, particularly in the areas of optical, power and microLED."

## **PragmatIC Semiconductor secures funding**

PRAGMATIC Semiconductor has announced that it has secured \$80 million of Series C funding. This scaleup investment will be used to build a second FlexLogIC fab in the North East of England, to meet the growing demand for ultra-low-cost flexible integrated circuits (FlexICs) for the Internet of Everything, and strengthening the position of the UK in its ambition to be a leading designer and manufacturer of next generation semiconductors.

"This successful Series C round is a testament to the potential for our technology to enable trillions of smart items and address key UN sustainable development goals," said Scott White, CEO of PragmatlC Semiconductor.

"Our FlexLogIC-002 fab will deliver significantly higher capacity than our first line, whilst still maintaining our signature ultra-low capex, fast production cycle time and minimal carbon footprint. In addition to supporting our continued commercial ramp, it provides a template for rolling out a distributed global network of FlexLogIC systems, offering a Fab-as-a-Service (FaaS) for dedicated production on major customer sites to enable efficient and secure semiconductor supply chains."

Erik Langaker, independent Chair of the Board, added: "This capital raise is a fantastic recognition of the achievements of Scott White, Richard Price and their team. The round has been subscribed by a highly qualified select group of industrial and individual investors with significant experience in the semiconductor industry.

Their backing will enable the team to more than double in size over the next 12 months and expand capacity to fulfil the rapidly growing demand for electronics in everyday objects. PragmatlC's development over the past few years has seen the launch of its flagship ConnectIC® product line of ultra-low-cost RFID FlexICs, as well as its FlexIC Foundry® service enabling innovative designers to create more pioneering products and advance them rapidly from concept to reality.

This year it has demonstrated an order-of-magnitude improvement in complexity and compute capability for non-silicon chips by producing flexible microprocessors. These include the iconic 6502 and PlasticArm, an ultraminimalist Arm® Cortex®-M0 based system-on-a-chip which is 12 times more complex than previous state-of-the-art flexible electronics.

PlasticArm is the result of many years of collaboration between the two companies, a partnership that is set to continue long into the future with semiconductor IP leader Arm participating in this funding round.

SENICON BURDON B

Non-Contact Flow Meter SEMIFLOW® CO.65 Highly Accurate Flow Meter for Rigid Plastic Tubes & Pipes

# Nano Dimension acquires Essemtec

Nano Dimension, an industry leader in Additively Manufactured Electronics (AME) / 3D-Printed Electronics (PE), and Micro Additive Manufacturing (Micro-AM), has announced that it has signed and closed a definitive agreement to acquire Essemtec AG based in Lucerne Canton, Switzerland.

ESSEMTEC's product portfolio is comprised of production equipment for placing and assembling electronic components on printed circuit boards (PCBs). They are a leader in adaptive highly flexible surface mount technology (SMT) pick-and-place equipment, sophisticated dispenser suitable for both high-speed and micro-dispensing, and intelligent production material storage and logistic system. Its products are equipped with a sophisticated software package which makes extensive and efficient material management possible.

ESSEMTEC's equipment and software have been having impact with customers since their first machine was introduced. As their high-tech solution can be adjusted quickly and easily to meet wide ranging requirements, they are able to respond to all manner of customer needs, particularly in high-mix-lowvolume production environment. Their portfolio of products will continue to be available to the thousands of organizations that have called themselves a customer of ESSEMTEC, while also being part of the AME revolution that Nano Dimension is driving with its existing technology.

## Wuppertal University chooses Tektronix to develop advanced 6G technology

WUPPERTAL UNIVERSITY in Germany has chosen Tektronix instrumentation to help it develop innovative and capable new technologies that will underpin 6G networks. The project will develop components that allow higher data throughputs for 6G, while also cutting the latency of networks to allow applications, such as autonomous driving and remote surgery, with haptic feedback.

Led by Prof. Dr. Ullrich Pfeiffer, the project team was looking for instrumentation that could demonstrate the best vertical resolution, the best residual Error Vector Magnitude (EVM), a large memory and the ability to synchronize multiple instruments. After careful consideration of vendors, Prof. Dr. Pfeiffer and his team settled on Tektronix.

The scope of supply encompassed six DPO77001SX 70GHz Oscilloscopes, six AWG70001B 50 GSa/s Arbitrary Waveform Generators, three AWG Synch Hubs, three SignalVuPC Vector Signal Analysis Software, three SourceXpress Waveform Generation Software, and two water cooled 19" Racks supplied by system integrator ATV (Automatisierungstechnik Voigt GmbH) to reduce acoustic noise and improve thermal stability.

The Tektronix solutions offer synchronization between instruments and the ability to add new capabilities through their modular construction. As well as equipment, Tektronix was also chosen for the engineering support it could offer through its engineers. "We were pleased to have found Tektronix, as access to their technical experts made our team feel safe and supported. Particularly the possibility to scale up the system by synchronizing multiple instruments is crucial for the research on THz MIMO communication" savs Professor Dr. Pfeiffer. "Working with the global team of Tektronix engineers in this cooperative way, we feel we can really unlock the 'magic' in Tektronix solutions. We expect the cooperation with Tektronix to produce many breakthrough results" he added.

Maria Heriz, Vice President Commercial Operations EMEAI, commented,

### Jenoptik intends to acquire Berliner Glas Medical and SwissOptic

JENOPTIK AG is set to acquire from Berliner Glas GmbH, a 100 percent subsidiary of ASML Holding N.V.

Overall, Berliner Glas Medical and SwissOptic currently employ around 500 people worldwide. The transaction is still subject to approval from the German antitrust authorities. Closing is expected in December 2021.

"With this strategic acquisition we will strengthen our global and fastgrowing photonics business thus significantly expanding our already strong semiconductor equipment business, and, in particular, our highly attractive medical technology business," says Stefan Traeger, President & CEO of Jenoptik AG.

"We are pleased to have reached this agreement whereby Jenoptik will acquire the Medical Applications and SwissOptic business of Berliner Glas (part of ASML)," says Andreas Nitze, CEO of the Berliner Glas Group. "We are convinced that the combined businesses are well positioned to realize the potential we see for the business and will offer the best environment for its employees."

"Engineering the Future is Tektronix's motto and every day we enable our customers to develop new technology. With the University of Wuppertal, we take pride to support and enable Prof. Dr. Pfeiffer and his team to develop advanced 6G technology, that will touch every part of our society – socially and commercially; may it be autonomous driving, remote rescue and medical applications, which require the highest resolution 360° video transmission, IoT devices with much quicker data throughput, or smart cities.."

# **CARRIER TAPE ON-DEMAND** The new normal in semi-packing

Produce component carrier tape in-house as and when you need it, removing the need to store pre-formed reels. *Re-flex II* produces both standard and custom tape pockets either directly on to a tape and reel system in-line "On-Demand" or output to reel.

Best of all, the reduction in tape cost returns your investment within months, and ensures control over your own carrier tape supply and pocket quality.

Visit http://reflex-odt.com/semi/ to find out more

re-flex'

# 5G, AI & IoT devices benefit from the latest dual-layer materials

Wafer-level packaging (WLP) has become the norm for a growing number of 5G, Artificial Intelligence (AI) and Internet of Things (IoT) system components. Advanced applications require high-performance integrated circuits (ICs) built on substrates that require extreme thinning. The manufacturing of these devices requires minimal total thickness variation (TTV), little to no warpage, and high temperature survivability during downstream processing. The materials experts at Brewer Science explain how their BrewerBOND® Dual-Layer materials and process gives manufacturers the edge they need to lower costs, enhance performance capabilities and increase production throughput.

SUCCESS in creating next-generation electronic devices demands a sound foundation. While the largest IC makers are pushing CMOS scaling to 5 nm and below, other advanced circuit manufacturers are taking different routes to high performance, including the adoption of 2.5D/3D architectures that reduce footprints while increasing processing speed and functionality.

Manufacturers have succeeded in dramatically reducing TTV and warpage while containing costs even as they maintain high throughput. A variety of wafer thinning techniques and material technologies have been developed to enable the support of advanced packaging platforms. One common process is wafer-level chip-scale packaging (WLCSP) that delivers high performance at low cost. But since it utilizes a 'substrateless' package, applications can be limited due to die size. As dies continue to shrink, manufacturers are already seeking alternatives. Fan-out wafer-level packaging (FOWLP) technology is seeing continual development since input/ output (I/O) density can be increased by fanning out interconnects to external pad locations – this enables a smaller form factor with decreased power consumption.

An important aspect of advanced wafer-level packaging involves the use of temporary wafer bonding (TWB) materials and processes that enable partially processed wafers to withstand various subsequent steps even at very high temperatures and with high vacuum. If asked to describe their 'ideal' TWB materials solution that can save time and money while maintaining top performance, many manufacturers would ask for materials that can be applied and bonded at room temperature and can deliver protection when thinned wafers are manipulated as part of thermal compression bonding (TCB) steps. The materials should also be sufficiently flexible to support different cure options while preserving device feature integrity. At the same time, materials should enable the debonding of thinned wafers from carriers using a variety of separation technologies.

"Brewer Science is constantly working to improve its materials that are already seeing widespread adoption. A good example is our Dual-Layer materials that continue to see refinements that make them even more adaptable. We are seeing particular interest from manufacturers developing devices and systems for 5G, AI and IoT applications. Since the intial introduction, Brewer Science Dual-Layer materials have demonstrated protection during thin wafer handling in TCB processing. We continue to improve TTV performance in production environments and we have seen Dual-Layer materials successfully support wafers thinned to 10 µm. They can also be applied at room temperature with any of the industry's most commonly utilized dispense equipment," said John Massey, Principal Field Applications Engineer.

Handling thinned wafers is a major challenge within semiconductor manufacturing. Silicon wafers thinner than 50  $\mu$ m or those with redistribution layers (RDLs) created using a RDL-first process are delicate and expensive to manufacture. Safe handling necessitates the use of support substrates and processing steps that employ temporary bonding and debonding (TBDB) materials designed to enable complex packaging architectures.

Materials created using high-viscosity, low-T<sub>g</sub> thermoplastic polymers are commonly used in TBDB processes. When paired with a supportive carrier, these materials offer thermo-mechanical stability and easier handling of thin device substrates. While the extensive selection of TBDB materials offered by Brewer Science supports many bonding/debonding techniques (predominantly: mechanical, laser, and thermal slide), the introduction of higher-temperature steps can cause traditional adhesive materials to behave more like a liquid; as a result, temporarily bonded wafers lose mechanical stability as melt viscosity decreases. This allows some material to soften, weakening bond-line stability. Deformation and delamination of the device wafer can occur at higher temperatures, which leads to downstream processing issues. Brewer Science has developed advanced

materials and processes, providing customers a TBDB system that eliminates common material failure points.

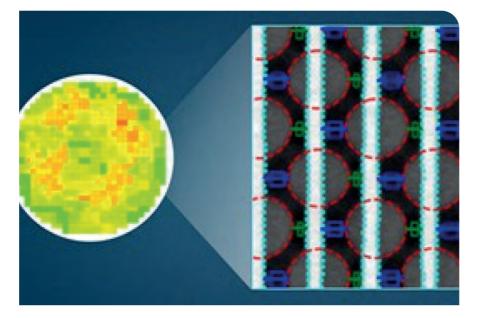

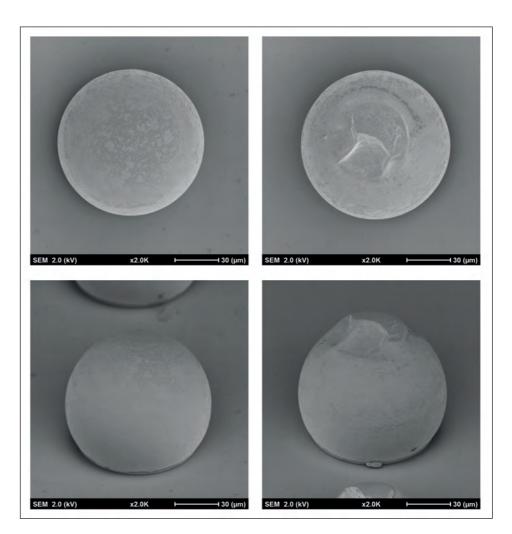

## BrewerBOND® Dual-Layer materials for TBDB

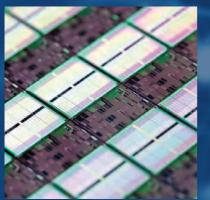

The latest Brewer Science Dual-Layer materials deliver next-generation bonding system performance for high throughput and thermal stability. The materials also provide room-temperature bonding and debonding for both wafer-level and panel-level processing. Dual-Layer materials support wide-ranging manufacturing requirements, enabling more uniform post-grind device thicknesses of < 50  $\mu$ m while also enabling device structures (and the temporary bond) to survive high-temperature treatments under vacuum. Figure 2 shows a scanning electron microscope (SEM) image of damage-free device features enabled by Brewer Science Dual-Layer materials and process optimization (left). The same size features using the baseline process are shown on the right.

According to Kim Yess, Brewer Science Executive Director for Wafer-Level Packaging Materials, the Dual-Layer approach of BrewerBOND materials has key advantages compared to the previous solutions offered to the industry.

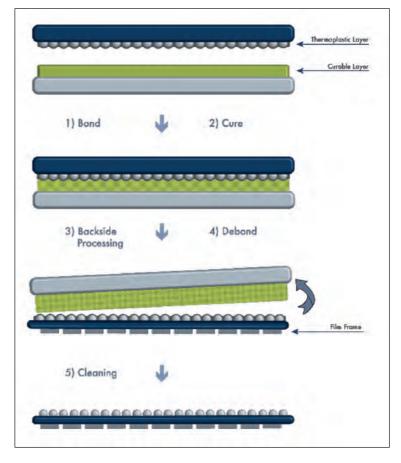

"The BrewerBOND T1100 series materials are designed to conformally coat the device structures before bonding; the materials have specific rheology attributes for exceptional conformal coating for protection of device structures. The BrewerBOND C1300 material is a curable thermoset layer used in Figure 1: The Brewer Science TBDB process flow using Dual-Layer materials.

Figure 2: Scanning electron microscope images showing damage-free device features enabled by Brewer Science Dual-Layer materials and process optimization (left) and defects found in the samesized features (right) that were made using the baseline process.

conjunction with the T1100 series material, which remains malleable until final cure. This will enable the bonded pair to have very low TTV and also survive downstream processes approaching  $400^{\circ}$ C," she said. Yess explained that the Dual-Layer system includes a low-glass-transition-temperature (low-T<sub>o</sub>) thermoset

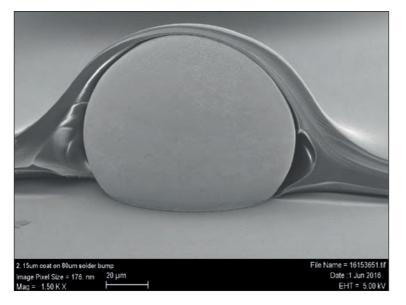

Figure 3: The BrewerBOND T1100 material delivers highly conformal coating and adhesion preperties.

material (BrewerBOND C1300) applied to a carrier. This assembly is then bonded to the device wafer that has been processed with the corresponding higher-T<sub>9</sub> bonding material (BrewerBOND T1100) that coats device structures. After bonding and processing at room temperature, the pair can then either be UV exposed or hotplate baked to cure the thermoset material. When processed below 350°C, the BrewerBOND T1100 series material remains solvent-soluble with little to no melt flow up to 300°C. When coated, this material is highly conformal and can cover severe topography even when applied thinly. Figure 3 shows a scanning electron microscope (SEM) cross-section of a 2.15  $\mu$ m film of BrewerBOND T1100 series material processed over 80- $\mu$ m solder bumps.

Yess explained that the exceptional performance achieved by their Dual-Layer approach was developed by Brewer Science to optimize the coatings' most essential qualities while making various application steps fit into typical process flows at high throughput levels. (See Table 1 for key materials properties.)

"The BrewerBOND T1100 and C1300 materials need each other to perform to their optimal potential. The BrewerBOND T1100 material is thinner, relatively speaking, and more conformal, which manufacturers need to address ever-shrinking device geometries. It also enables easier downstream cleaning of

| Droportu              | Curable Material                    | Thermoplastic Materials |                      |                                  |  |  |  |  |

|-----------------------|-------------------------------------|-------------------------|----------------------|----------------------------------|--|--|--|--|

| Property              | BrewerBOND <sup>®</sup><br>C1301-50 | BrewerBOND®<br>T1107    | BrewerBOND®<br>T1105 | BrewerBOND <sup>®</sup><br>T1101 |  |  |  |  |

| Solution<br>viscosity | 4675 cP at 24.5°C                   | 160 cP at 24.5°C        | 100 cP at 24.5°C     | 75 cP at 24.5°C                  |  |  |  |  |

| Target thickness      | 25-60 μm                            | 2 µm                    | 2 µm                 | 2 µm                             |  |  |  |  |

| Young's modulus       | 3.3 MPa                             | 2500 MPa                | 2500 MPa             | 2550 MPa                         |  |  |  |  |

| CTE                   | 394 ppm/°C                          | 63 ppm/°C               | 63 ppm/°C            | 53 ppm/°C                        |  |  |  |  |

| Td                    | 420°C                               | 465°C                   | 465°C                | 375°C                            |  |  |  |  |

| Tg                    | <-50°C                              | 328°C                   | 328°C                | 82°C                             |  |  |  |  |

the device. Our BrewerBOND C1300 material creates better stability during higher-temperature processes, which reduces warpage and helps ensure post-processing functionality of the devices being packaged," she said, noting that using the BrewerBOND C1300 material by itself is only one piece of the process and that the thermoplastic is required for the mechanical debond processes.

"Creation of new device structures and their extreme requirements are stretching the limits of the techniques and materials used up to this point. This is why Brewer Science is focusing on developing better materials and processes to enable device manufacturers to achieve the stability and temperature resistance they need for downstream processing, but still retain the ability to remove the coatings as needed simply by using industry-standard cleaning processes and chemicals. By using the right coatings, semiconductor manufacturers can achieve the stability and temperature resistance they need at nano-scale while still retaining the ability to remove coatings as needed," she explained.

### Summary

Brewer Science brings leading-edge materials expertise to advanced packaging that is paving the way for innovation through the use of new temporary

9-10 November 2021- Brussels

700 delegates csinternational.net

bonding/debonding materials that uniquely support FOWLP technology requirements. When combined into a system, Brewer Science Dual-Layer materials impart improved mechanical stability that reduces the hazards of handling thinned bonded wafers that need to undergo high-vacuum or high-temperature processing. The materials' conformal nature, roomtemperature bonding/debonding characteristics and chemical resistance provide added value and improved performance while reducing cost of ownership.

Dual-Layer materials from Brewer Science also facilitate low-energy laser debond processes that deliver improved protection for the device wafer with low carbon residues, and can also facilitate other debonding methods. As packaging techniques continue to evolve and device geometries shrink even further, Dual-Layer materials have evolved as well, enabling processing wafers thinned to 10 µm. They also protect 3D device structures that are capturing an increasingly large share of overall semiconductor production. Brewer Science continues to develop and deliver advances in temporary bonding and debonding materials to facilitate manufacturers' requirements while formulating new materials to support emerging device packaging technologies now under development.

Table 1: Properties of **BrewerBOND** advanced materials

WWW.SILICONSEMICONDUCTOR.NET | ISSUE IV 2021 17

Picture Credit: National University of Singapore

NUS researchers develop brain-inspired memory device that can revolutionise semiconductor design

Reconfigurable device can simplify semiconductor circuit design and enhance computational power and speed

MANY ELECTRONIC DEVICES TODAY are dependent on semiconductor logic circuits based on switches hard-wired to perform predefined logic functions. Physicists from the National University of Singapore (NUS), together with an international team of researchers, have developed a novel molecular memristor, or an electronic memory device, that has exceptional memory reconfigurability.

Unlike hard-wired standard circuits, the molecular device can be reconfigured using voltage to embed different computational tasks. The energy-efficient new technology, which is capable of enhanced computational power and speed, can potentially be used in edge computing, as well as handheld devices and applications with limited power resource.

"This work is a significant breakthrough in our quest to design low-energy computing. The idea of using multiple switching in a single element draws inspiration from how the brain works and fundamentally reimagines the design strategy of a logic circuit," said Associate Professor Ariando from the NUS Department of Physics who led the research.

The research was first published in the journal Nature on 1 September 2021, and carried out in collaboration with the Indian Association for the Cultivation of Science, Hewlett Packard Enterprise, the University of Limerick, the University of Oklahoma, and Texas A&M University.

### Brain-inspired technology

"This new discovery can contribute to developments in edge computing as a sophisticated in-memory computing approach to overcome the von Neumann bottleneck, a delay in computational processing seen in many digital technologies due to the physical separation of memory storage from a device's processor," said Assoc Prof Ariando. The new molecular device also has the potential to contribute to designing next generation

### **RESEARCH I** MEMORY DEVICES

Left: The novel memory device is based on a molecular system that can transition between on and off states at several discrete sequential voltages.

processing chips with enhanced computational power and speed.

"Similar to the flexibility and adaptability of connections in the human brain, our memory device can be reconfigured on the fly for different computational tasks by simply changing applied voltages. Furthermore, like how nerve cells can store memories, the same device can also retain information for future retrieval and processing," said first author Dr Sreetosh Goswami, Research Fellow from the Department of Physics at NUS.

Research team member Dr Sreebrata Goswami, who was a Senior Research Scientist at NUS and previously Professor at the Indian Association for the Cultivation of Science, conceptualised and designed a molecular system belonging to the chemical family of phenyl azo pyridines that have a central metal atom bound to organic molecules called ligands. "These molecules are like electron sponges that can offer as many as six electron transfers resulting in five different molecular states. The interconnectivity between these states is the key behind the device's reconfigurability," explained Dr Sreebrata Goswami.

Dr Sreetosh Goswami created a tiny electrical circuit consisting a 40-nanometer layer of molecular film sandwiched between a top layer of gold, and a bottom layer of gold-infused nanodisc and indium tin oxide. He observed an unprecedented current-voltage profile upon applying a negative voltage to the device. Unlike conventional metal-oxide memristors that are switched on and off at only one fixed voltage, these organic molecular devices could switch between on-off states at several discrete sequential voltages.

Using an imaging technique called Raman spectroscopy, spectral signatures in the vibrational motion of the organic molecule were observed to explain the multiple transitions. Dr Sreebrata Goswami explained, "Sweeping the negative voltage triggered the ligands on the molecule to undergo a series of reduction, or electron-gaining which caused the molecule to transition between off and on states." The researchers described the behavior of the molecules using a decision tree algorithm with "ifthen-else" statements, which is used in the coding of several computer programs, particularly digital games, as compared to the conventional approach of using basic physics-based equations.

## New possibilities for energy-efficient devices

Building on their research, the team used the molecular memory devices to run programs for different real-world computational tasks. As a proof of

concept, the team demonstrated that their technology could perform complex computations in a single step, and could be reprogrammed to perform another task in the next instant.

An individual molecular memory device could perform the same computational functions as thousands of transistors, making the technology a more powerful and energy-efficient memory option.

"The technology might first be used in handheld devices, like cell phones and sensors, and other applications where power is limited," added Assoc Prof Ariando.

The team in the midst of building new electronic devices incorporating their innovation, and working with collaborators to conduct simulation and benchmarking relating to existing technologies. Other contributors to the research paper include Abhijeet Patra and Santi Prasad Rath from NUS, Rajib Pramanick from the Indian Association for the Cultivation of Science, Martin Foltin from Hewlett Packard Enterprise, Damien Thompson from the University of Limerick, T. Venkatesan from the University of Oklahoma, and R. Stanley Williams from Texas A&M University.

# Developments in the high-end inertial sensor market for harsh environments

The rise of inertial systems used in industrial applications during the last years is driven by the possibility of integrating new functionality at low cost and good performance, mostly thanks to the recent developments in MEMS accelerometer and gyroscope technology.

### BY DIMITRIOS DAMIANOS, PHD, SENIOR ANALYST, YOLE DÉVELOPPEMENT

HIGH PERFORMANCE motion sensing is useful in many industries considered to have harsh environments. In the military & aerospace areas, the use of Inertial Measurement Units (IMU), Inertial Navigation Systems (INS) and other systems based on high-performance accelerometers & gyroscopes has been widespread for critical navigation, flight control or stabilization functions for decades, especially in cases where GNSS and GPS signals are lost or not available. In the naval area, navigation through gyrocompassing is a historical application of gyro assemblies. The rise of inertial systems used in industrial applications during the last years is driven by the possibility of integrating new functionality at low cost and good performance, mostly thanks to the recent developments in MEMS accelerometer and gyroscope technology.

To name a few, structural and machine health monitoring, train tilting and vibration monitoring, autonomous cars and robots, are all benefiting and will continue to do so in the future, as less human intervention is driving innovations.

### SENSORS I ENERTIAL SYSTEMS

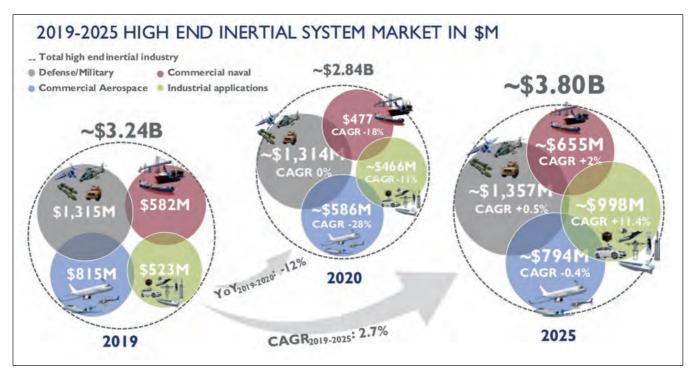

The market for accelerometers, gyroscopes, IMU, INS is still a very fragmented market, with many applications, as seen in Figure 1 that can be categorized in four big groups: industrial, commercial aerospace, commercial naval and defense applications. The high-end inertial system market is estimated to be ~\$3.2B in 2019, dominated by defense and aerospace applications. In 2020 the market suffered due to the negative impact of covid-19 on cruise ships and logistics ships (tankers, etc), the paralysis of civil aviation and also supply chain problems, causing delays in deliveries across all markets. Commercial aerospace has been the hardest hit, with aircraft orders getting slashed, and with an outlook that doesn't look as bright as before.

Recovery is not expected before 2024. Yole sees the global high-end inertial market growing at a 2.7% annual growth rate, reaching \$3.8B in 2025 (Figure 2). Industrial applications will be the most dynamic with more than 11% yearly growth, while the defense and commercial aerospace markets will be pretty much stable, with commercial naval applications growing at a 2% CAGR in the same period (2019-2025). Besides that, rising geopolitical risks could impact the defense market mostly through changes in military spending, however the need for resilient and assured position, navigation and timing (A-PNT) will create opportunities for inertial sensors, as more systems go autonomous.

The industrial market, on the other hand could really rejuvenate the high-end inertial business. In the long term, the market could be pushed by long-awaited industrial applications that have already made their first baby steps: robotic cars, autonomous robots, industrial IoT and and new space applications. During 2020 and 2021, there were a lot of investments and M&A's related to all kind of robotics companies (last-mile delivery, AGV & warehouse logistics, automation, autonomous vehicles, etc) and space companies (launchers, nano-satellites, services, etc). New actors in these domains are coming from various backgrounds who are ready to adopt inertial technologies. In these high-volume applications, integrators will be probably technology-agnostic which could prove beneficial for inertial systems that can achieve a good C-SWAP.

It is key for the companies involved in those markets to invest in the right technologies and partners, depending on the end-markets which are targeted. Different strategies are observed: some companies carefully invest in select technologies like the market leader Honeywell, while others love all inertial technologies, like Northrop Grumman and Safran. Most companies though follow the example of Honeywell, having product lines of a single technology supplying carefully selected integrators. Still, all technologies have a long lifetime and no abrupt shift from one technology to the others is expected, required that players keep their technology up to date.

Several gyro and IMU technologies are currently on the market, with Ring Laser Gyroscope (RLG) and Fiber Optic Gyroscope (FOG) based systems being the most widespread and still benefiting from advances in photonics. FOG has a great reach in various tactical and navigation-grade applications (missile guidance, antenna and platform stabilization, etc), as well as some industrial-grade applications (agriculture, pipeline monitoring, borehole drilling, etc). Integrated solutions are underway, driven by the need for smaller form factor in industrial and tactical grade applications. Such examples are an integrated photonic FOG by KVH or a resonator FOG with integrated Silicon Photonics laser Figure 1: Application space for high-end inertial systems

Figure 2: Market forecast for high-end inertial systems by applications for the 2019-2025 period.

sources by Honeywell & TeraXion. RLG is still the legacy technology (and the biggest market) for aerospace and other high-end navigation or strategic applications. Hemispheric Resonator Gyroscope (HRG) was traditionally fabricated by Safran and Northrop Grumman for very high-end and space applications such as satellite guidance.

Now, the technology has potentially experienced a breakthrough on the market, with Safran bringing industrialized manufacturing of the HRG, thus lowering the cost, which is expected to increase the outreach of HRG in the coming years. Finally, MEMS technology is dominating the industrial applications and keeps improving, having the largest impact on the market landscape and on the competition.

Many traditional players try to ride the upcoming MEMS wave, such as Honeywell, Northrop Grumman, Safran, UTC, etc who are already using Si-MEMS technologies. It is not illogical to see a couple of the smaller companies in the domain getting acquired by bigger ones, that need access to specific technology, geographies and clients While traditionally originating from consumer and other low-end commercial applications, Si-MEMS with a low C-SWAP is continuously improving and pushing FOG out of many industrial and some tactical applications that are considered high-end, at 1-10°/h in-run bias instability performance.

However, Si-MEMS gyros are still immature to expand in other applications that require bias instability below 1°/h. Many traditional players try to ride the upcoming MEMS wave, such as Honeywell, Northrop Grumman, Safran, UTC, etc who are already using Si-MEMS technologies. It is not illogical to see a couple of the smaller companies in the domain getting acquired by bigger ones, that need access to specific technology, geographies and clients. The moment is ripe for bigger companies to buy smaller actors at a good price, that are more flexible in their product and technology development. These strategic decisions could enable the bigger companies have a foot in emerging markets, all the while keeping the strengths in their traditional markets.

High-end inertial sensors are the backbone of new space, autonomous vehicles for commercial or and defense markets (air, land, sea), as well as industrial robots.

Eventually, one should closely monitor the technology side. MEMS will keep improving and increasing their performances, HRG high-volume manufacturing that could make it spread to many applications and finally photonic integrated FOGs could bring extra value to applications that are dominated by legacy technologies.

# ELECTRONICS STARTS WITH US

### We are the Electronics business of Merck.

Our semiconductor materials are at the heart of electronics, and enable the transformation of communications, mobility and healthcare.

We unlock the potential for smaller, faster and more energy-efficient devices.

For more information, please visit **bit.ly/SemiconductorMaterials**

AQ6380 Optical Spectrum Analyzer

Next generation optical performance

DISCOVER IT HERE:

**Precision Making**

www.tmi.yokogawa.com

# Tignis simplifies adding ML to advanced process control manufacturing systems

With the continual buzz around artificial intelligence (AI) and machine learning (ML), one might think it relatively easy to improve manufacturing output by adding a 'bit' of AI/ML to one's IC recipe. But the reality has been far more complicated. Enter the AI process control experts at Tignis who believe they have a new solution that could make ML-driven APC much more accessible and cost-effective.

> IMAGINE a small semiconductor manufacturer that wants to add a machine learning-aided application to improve its fabrication process flow. The company is about to discover that besides their process engineer, adding ML capabilities is a multidisciplinary approach with no off-the-shelf solutions that are fast, highly adaptable or easy to implement. According to Tignis, a Seattle-based Al-powered process control company, that paradigm is about to shift.

Tignis announced today its new Al/machine learning analytics tool set that it calls PAICe, which it describes as a solution for companies to add the benefits of Al/ML APC without the substantial investments of time and money that has previously been the norm. Company co-founder and CEO Jon Herlocker told Silicon Semiconductor in a prerelease interview

that PAICe is designed to put the power of machine learning into the hands of non-data scientists. This next-generation technology helps manufacturers achieve process improvements not

previously possible with today's advanced process control (APC) approaches including the ability to utilize surrogate machine learning models created by Tignis that are more accurate and up to one million times faster than physics-based simulations. This performance enhancement can directly lead to faster production, better quality control and faster time to market.

"In creating PAICe the basic idea is to empower the process engineer. This is the opposite approach that some solutions providers offer today that essentially take a 'magic black box' approach that does what you want, but you have no idea what goes on inside the box and as a customer, you are totally dependent on another company's technology; you give up control. Our approach—using what we call our digital twin query language, or DTQL, is to be able in minutes to build models without even one course in data programming. The basic system is ideal for at least 80 percent of use cases, and we can offer our own programmers for unique situations that need further optimization," he explained.

According to Tignis, their new DTQL is the first language designed specifically to build machine analytics on digital twins. Through DTQL, Tignis says its PAICe product suite significantly removes the obstacles that have prevented engineers from leveraging all the historical data they have collected to help

data they have collected to help them make better decisions; the new solution enables process and reliability engineers to convert their deep subject matter knowledge into hundreds

of machine learning based predictive models that are easily managed across thousands of diverse physical assets – all without having to become a data-scientist.

The PAICe product suite accelerates the ability to build, validate and deploy machine learning enabled solutions in manufacturing and process industries, with an initial focus on semiconductor manufacturing, oil and gas processing, and energy. It is the latest venture by Jon Herlocker, a serial entrepreneur and deep technologist with a track record of founding and building successful startups, as well as a former VP and CTO at VMware, a \$12 billion dollar a year virtual infrastructure management company. Tignis is funded and advised by industry leaders such as software executive Paul Maritz, who is an investor and member of Tignis' board of directors. Maritz was CEO at VMWare, and at Microsoft he was a member of the top executive management team. Harel Kodesh, former CTO of GE Digital, is also an investor.

"The PAICe product suite puts machine learning in the hands of people that have never been able to use it before," said Herlocker. "This is important because machine learning-based control algorithms not only outperform classic feedback or feedforward advanced process control applications, they continuously learn from new process data, reducing the need to retune controls and improve over time. With the PAICe product suite, many more manufacturers will now be able to take advantage of the benefits of machine learning in modern manufacturing and process control by increasing process quality, throughput and yield." The PAICe product suite enables machine learning for more than just predictive maintenance - it enables it for process optimization and its implementation directly into process control loops. It is able to run machine learning-based simulations one million times

faster than legacy physics-based simulations, allowing manufacturers to have real time feedback control in places that were not possible in the past such as realtime optimization. Key features of the suite include:

PAICe Builder, a machine learning analytics tool easy enough for anyone to use. It provides simple connectivity to OSIsoft PI data historian and other data sources, and is available in both downloadable or cloud versions, allowing users to do analytics anywhere.

PAICe Monitor, which allows customers to easily deploy their analytics to private or public cloud infrastructure and thousands of assets with one click (including web APIs to ingest and send data to and from data historians). It offers a scalable cloud infrastructure to build analytics as needed; the Tignis managed infrastructure means customers only pay for the resources they need.

PAICe Maker, which deploys and manages machine learning based control algorithms that improve over time with more data. Machine learning models can compute control variables at speeds up to one million times faster than legacy physics-based simulations, allowing real time computation of control. Hybrid on premise and cloud architecture ensures low latency for control but the best possible model training and learning in the cloud.

Through the company's extensive beta test program prior to launch, the PAICe product suite is in use by a number industrial clients spanning the oil and gas, semiconductor and energy industries. Some notable users of the product suite include Tokyo Electron (TEL), Synopsys, Etairon, and Optimum Energy. The product suite is now available directly from Tignis; visit www.tignis.com for details.

# Advanced MES capabilities can extend semiconductor fab lifetimes

As the current global microelectronics shortage demonstrates, semiconductor manufacturing is not a simple. IC fabs are not created to pivot quickly as much as they are to produce high quality products at low cost. The experts from Critical Manufacturing outline ways advanced manufacturing execution systems (MES) can help fabs maximize output while also extending their serviceable lifetime.

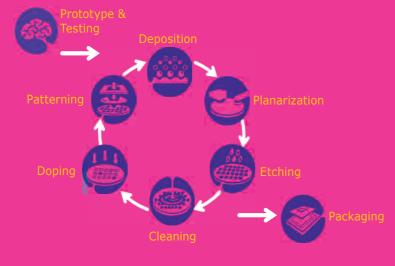

### BY CRITICAL MANUFACTURING

SEMICONDUCTOR MANUFACTURING is unquestionably one of the most complex and sensitive manufacturing processes in the world. Creating line widths on silicon wafers down to five nanometers or less with billions of transistors means that even the smallest vibration or misalignment during fabrication will cause issues. Alongside the sophisticated processes required to manufacture, the industry is further challenged with very short product lifecycles involving millions of devices, or, the need for small batches of niche products to be produced over decades. Only a few semiconductor companies in the world can afford to invest in building new, large capacity fabs with the latest equipment and technologies. Incredibly expensive equipment such as extreme ultraviolet (EUV) scanners costing over \$125 million each combined with the need for costly clean room real estate truly makes IC manufacturing one of the most challenging business environments.

For the last two decades, increasing wafer size and performance in front-end chip processing has been an industry focus, with manufacturers looking to more expensive 300mm wafer technology to meet demands for quality, high volume products. But as chips are made and used in an increasing number and variety of products, it has become apparent that not every chip needs to be produced at the millions of unit's level using the latest technology. A substantial portion of the ICs

> made today – even those in advanced products – can still be produced, efficiently and profitably, in smaller 150mm and 200mm fabs, which are experiencing a surprising

renaissance in recent years. Many of these smaller fabs started life in the 1990s or even the 1980s; a lot of the equipment dates

ALL DE LE DE

| () JF_CS2 (InApproval) / New stat | e / 06/14/2021 02:51 PM | Λ                          |     |                  |     |

|-----------------------------------|-------------------------|----------------------------|-----|------------------|-----|

| Approvals                         |                         |                            | + 🛍 |                  |     |

| APPROVALS                         |                         | NEW STATE 2                |     | State:           |     |

| New state                         | >                       | Services user<br>observer  |     | New state 2      |     |

| New state 2                       | >                       | Administrators<br>Approver | Ű   | Reviewer Type:   |     |

| New state 1                       |                         |                            |     | C Employee       |     |

| New state 3                       |                         |                            |     | *Role:           |     |

|                                   |                         |                            |     | Administrators   | × • |

|                                   |                         |                            |     | * Approval Type: |     |

|                                   |                         |                            |     | Approver         |     |

|                                   |                         |                            |     | Observer         |     |

|                                   |                         |                            |     |                  |     |

|                                   |                         |                            |     |                  |     |

|                                   |                         |                            |     |                  |     |

| Comments:                         |                         |                            |     |                  |     |

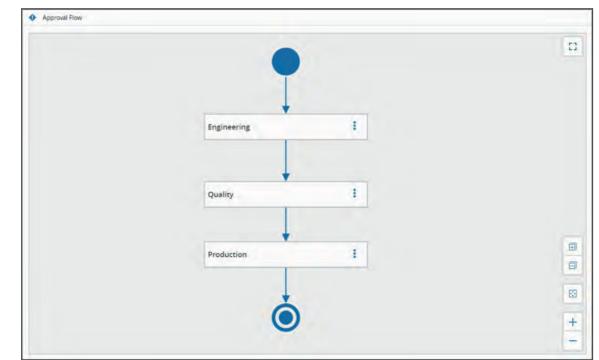

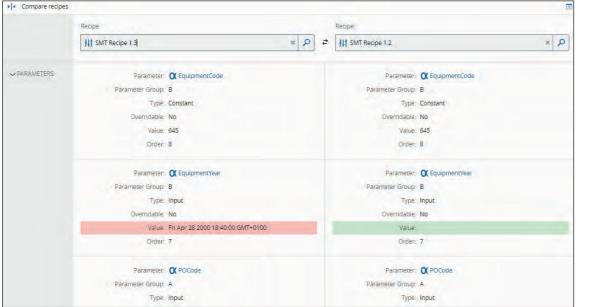

One hallmark of a good MES designed to support advanced semiconductor manufacturing is a simple interface; ideally the interface should be: intuitive; support multiple production sites; offer multi-lingual options and provide easy navigation.

back to the last century, but still adhere to industry manufacturing standards. This equipment has what some might consider surprising longevity thanks to frequent upgrades, readily available replacement parts and the addition of more sophisticated robots and sensors combined with comprehensive maintenance programmes.

Smart manufacturing is establishing a foothold in the semiconductor industry and Industry 4.0 technologies are breathing new life into aging process tools to make them run even more cost efficiently. By employing modern manufacturing execution systems (MES), the life of aging semiconductor production facilities can be extended, and advanced capabilities can be added to provide a pathway to the future for the industry.

A future-ready MES provides manufacturers with solutions to many challenges. It can add production capacity and throughput by driving efficiency without increasing expensive clean room space. It can enhance production consistency and reduce costly processing errors, reduce time-to-market for new products, and provide solutions to enable the latest, most advanced production steps. Some or all of these benefits may not only be critical for profitability, but may actually be the key to the survival of a company.

### Why and which MES

The cost and changing landscape of semiconductor manufacturing needs an MES solution that can adapt for the future. Data is more important than ever and offers manufacturers a way to better monitor and control processes as well as providing deeper insights to help resolve production challenges and support decision making.

As volumes of data continue to increase at a tremendous rate, first and foremost, a future-ready MES needs to incorporate a fully scalable Industrial Internet of Things (IIoT) data platform for ingesting, processing and analyzing the vast volumes of data points that, if contextualized and analyzed correctly, can increase the speed of learning to help drive production efficiency and deliver continuous process improvements.

New fabs and equipment have the capability to be highly automated, but the cost is very high. For older fabs, a modern MES solution presents a way to extend the life of facilities and tools without spending billions of dollars needed to build and equip a new fab. But success requires a highly versatile system that can integrate new IoT devices and legacy equipment to provide full visibility of plant operations. By providing greater control and tighter processing tolerances, the right MES solution can increase production capacity,

In documenting the flow of information and automating such tasks as step change approvals, a simple graphic depiction of hierarchy and process flow (seen here) aids guick comprehension of the task at hand.

efficiency and throughput, presenting significant advantages to producers, especially with the current shortage of chips available in the market.

Older facilities usually have a legacy MES combined with a patchwork of disparate systems that operators have used over the course of years. Long-term operation within a given environment may build confidence, but it is a fact the maintenance of such older systems that consume a great deal of specialized resources since technology upgrades and additional applications have been added over the years.