# ADDRESSING THE CHALLENGES OF ADVANCED ALD PROCESSES

VOLUME 45 ISSUE V 2024

# INSIDE

News Review, Features News Analysis, Profiles Research Review and much more...

## Silicon-based quantum computing processors

AN ANGEL BUSINESS COMMUNICATIONS PUBLICATION

Contrary to popular belief, simply demonstrating quantum advantage is not the ultimate goal of quantum computing

# Exploiting the new wave of semiconductors

Navigating the semiconductor revolution and identifies opportunities for growth

### SILICONSEMICONDUCTOR.NET

## The challenges of advanced ALD processes

Addressing the potential problems of pump failure, process downtime and slow processing speeds

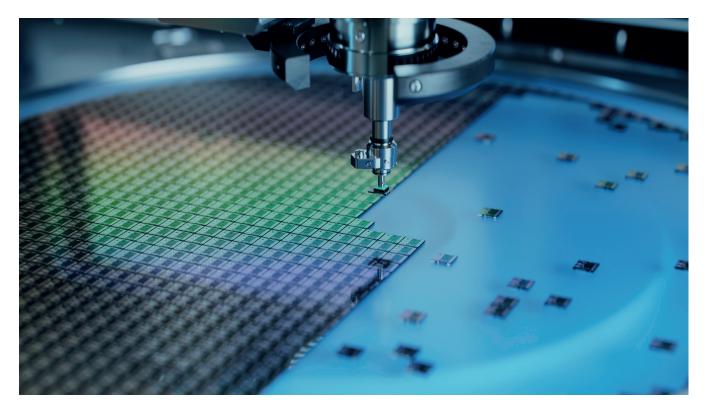

# FUSION AND HYBRID BONDING FOR HETEROGENEOUS INTEGRATION

Enabling advanced 3D device stacking and chiplet integration for CMOS image sensors, memory and 3D system-on-chip (SoC)

High-volume production equipment and process technology for Wafer-to-Wafer (W2W) and Die-to-Wafer (D2W) hybrid bonding

GEMINI<sup>®</sup> FB Automated Production Wafer Bonding System delivers industry leading alignment accuracy and bonding performance

Heterogeneous Integration Competence Center<sup>™</sup> serving as leadingedge innovation incubator for EVG customers and partners

GET IN TOUCH to discuss your manufacturing needs www.EVGroup.com

# VIEWPOINT

By Phil Alsop, Editor

# When does a shortage become a crisis?

A COMMON THEME running across the three industry sectors in which I work – data centres, semiconductors and water – is the very real concern that there is a shortage of skilled individuals joining these industry sectors, as a significant quantity of the incumbent workforce are nearing retirement. A great deal of experience is leaving these important industries and it is not being replaced at anything near the required rate – especially when one considers the time it will take new recruits to themselves become 'experienced professionals'.

So far, the talk around this impending...well, what seems to be a crisis, but almost everyone I speak to across these three sectors goes out of their way not to use such a word, is very measured and calm. The talk is about all of the initiatives being introduced by individual organisations and the collective industries to develop tomorrow's workforce in the right numbers and with the right skills. Mention of the projects that have been delayed because there are not enough suitably qualified people to build a data centre, or to operate a semiconductor fab, is kept to a minimum.

Now, I am sure we can all sign up to the power of positive thinking, but, at some stage, such positivity does also have to take on board a healthy dose of realism. A workforce that is neither large enough nor skilled enough to help sustain the digital expansion predicted over the next few years is a serious problem. And, more to the point, something of a self-inflicted one. Historians might argue that we were due a major global health disaster, and point out that global peace and stability is noted more by its absence than its observance, but few could have predicted the problems brought about by the pandemic or the war in Ukraine. However, the skills shortage has bee obvious for quite some time.

While AI sceptics might not lament the predicted shortage of AI chips in the near future at least, this potential bottleneck, with the guarantee of price volatility and some major winners and losers long the way, is not especially healthy. And there could be a knock on effect as all of the attention goes to expanding AI chip capacity, to the detriment of other chip types.

All of which leads me to the conclusion that, as far as is possible, the industry needs to go further and faster in terms of addressing the supply chain issues which it can control. The various Chips acts, and the expansion of national and regional semiconductor industries across many parts of the world, is an exciting development. Let's hope that industry is not putting all of its trust in a 'build it and they will come' belief.

Rather, we should hope to see the industry pushing at what is largely an open door. The financial incentives being offered by so many governments to the semiconductor industry demonstrates that the people in charge understand the importance of the sector. Not too difficult then to persuade them that an accompanying re-focusing of the education system is as equally important as the money?

For your free weekly e-news roundup go to: siliconsemiconductor.net

# CONTENTS

## VOL 45ISSUE V 2024

14

# High-speed, high-temperature pumps address the challenges of advanced ALD processes

Addressing the potential problems of pump failure, process downtime and slow processing speeds when it comes to atomic layer deposition

# 18 Exploiting the new wave of semiconductors: AI, Trust & information overload

Mobica navigates the semiconductor revolution and identifies opportunities for growth

## 24 Semiconductors in a world without PFAS

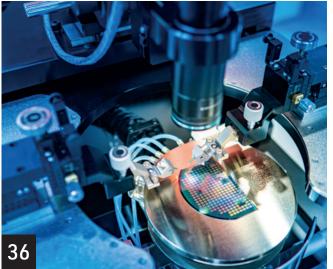

At the end of the day, the world's reliance on semiconductors isn't going away, but semiconductor manufacturers likely won't get to avoid PFAS requirements, even if their products are vital

# 26 The crucial role of ADCs and DACs in scaling quantum computing

In recent years there has been a surge in interest surrounding the topic of quantum computing and heightened anticipation about its potential to revolutionise the technology world

## 30 Silicon's dual role

Fueling AI's need for computation and connectivity

## 34 Sparking change in silicon semiconductor manufacturing with green energy

In the ever-evolving tech landscape, few industries rival the energy demands of silicon semiconductor manufacturing. These energy-intensive businesses are the backbone of modern electronics, powering everything from smartphones to supercomputers

## 36 A sustainable semiconductor industry needs smarter water management

As the industry expands exponentially, so does its needs for water

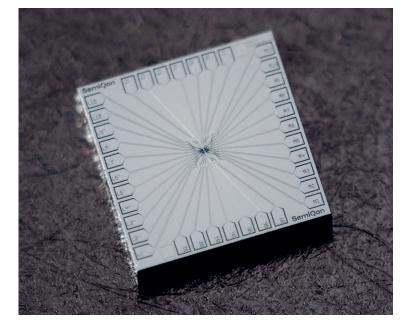

# 40 The future of computing runs on silicon-based quantum computing processors

Contrary to popular belief, simply demonstrating quantum advantage is not the ultimate goal of quantum computing. It would be an amazing feat of science and engineering, but it is not sufficient to reach the goal of making quantum computing mainstream

# 44 SEMI focuses on skills initiatives

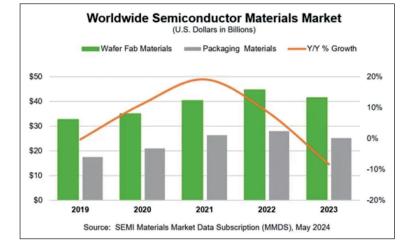

Skills, sustainability and market numbers are all covered in this SEMI news update

Publisher Jackie Cannon Editor Phil Alsop Sales & Marketing Manager Shehzad Munshi Marketing & Logistics Executive Eve O'Sullivan USA Representatives Tom Brun Brun Media Janice Jenkins

Director of Logistics Sharon Cowley Design & Production Manager Mitch Gaynor

| jackie.cannon@angelbc.com<br>phil.alsop@angelbc.com | +44 (0)1923 690205 |

|-----------------------------------------------------|--------------------|

| shehzad.munshi@angelbc.com                          | +44 (0)1923 690215 |

| eve.osullivan@angelbc.com                           | +44 (0)2476 823123 |

| tbrun@brunmedia.com                                 | +001 724 539-2404  |

| jjenkins@brunmedia.com                              | +001724-929-3550   |

| sharon.cowley@angelbc.com                           | +44 (0)1923 690200 |

| mitch.gaynor@angelbc.com                            | +44 (0)1923 690214 |

# **NEWS**

- 06 Hyperscalers forge ahead with in-house semiconductor solutions

- 07 CHIPS for America announces \$285 million funding opportunity

- 08 Imec.xpand launches EUR 300m fund

- **09** Semiconductor giants add \$1.1 trillion to stock values

- 10 Infineon reveals roadmap for energy-efficient power supply units in Al data centres

- 11 Rapidus and Esperanto Technologies sign memorandum of cooperation

- 12 £3m grant for Glasgow chip research

Chief Executive Officer Sukhi Bhadal Chief Technical Officer Scott Adams Directors Jackie Cannon, Sharon Cowley

sukhi.bhadal@angelbc.com scott.adams@angelbc.com

Published by Angel Business Communications Ltd, 6 Bow Court, Fletchworth Gate, Burnsall Road, Coventry CV5 6SP, UK. T: +44 (0)2476 718 970 E: info@angelbc.com

+44 (0)2476 718970

+44 (0)2476 718970

Silicon Semiconductor is published ten times (6x print and 4x video issues) a year on a controlled circulation basis. Non-qualifying individuals can subscribe at: £50.00 per annum (UK), €60.00 per annum ( Europe), \$90 per annum (air mail)(USA). Cover price £4.50. All information herein is believed to be correct at time of going to press. The publisher does not accept responsibility for any errors and omission: The views expressed in this publication are not necessarily those of the publisher. Every effort has been made to obtain copyright permission for the material contained in this publication. Angel Business Communications Ltd will be happy to acknowledge any copyright oversights in a subsequent issue of the publication. Angel Business Communications Ltd will be happy to acknowledge any copyright oversights in a subsequent issue of the publication. Angel Business not be reproduced in whole or

part without the written consent of the publishers. The paper used within this magazine is produced by chain of custody certified manufacturers, guaranteeing sustainable sourcing. US mailing information. Silicon Semiconductor, ISSN 1096-598X, is published 5 times a year by Angel Business Communications Ltd, Unit 6, Bow Court, Fletchworth Gate, Burnsall Rd, Coventry CV5 6SP. UK. Airfreight and mailing in the USA by agent named World Container INC 150-15, 183rd St, Jamaica, NY 11413, USA. Periodicals Postage Paid at Brooklyn, NY 11256. POSTMASTER: Send address changes to Silicon Semiconductor, Air Business Ltd, c/o World Container INC 150-15, 183rd St, Jamaica, NY 11413, USA

We strive for accuracy in all we publish; readers and contributors are encouraged to contact us if they recognise an error or omission. Once a magazine edition is published [online, in print or both], we do not update previously published articles to align old company names, branding, marketing efforts, taglines, mission statements or other promotional verbiage, images, or logos to newly created or updated names, images, typographic renderings, logos (or similar) when such references/images were accurately stated, rendered or displayed at the time of the original publication. When companies change their names or the images/text used to represent the company, we invite organizations to provide Angel Business Communications with a news release detailing their new business objectives and/or other changes that could impact how customers/prospects might recognise the company, contact the organisation, or engage with them for future commercial enterprise Printed by: The Manson Group. ISSN 2050-7798 (Print) ISSN 2050-7801 (Online) © Copyright 2024.

## **INDUSTRY NEWS**

# Hyperscalers forge ahead with in-house semiconductor solutions

Hyperscalers such as Meta, Microsoft, Google, and Amazon are strategically shifting towards developing proprietary semiconductor technologies in response to the soaring demand for Nvidia's GPUs in the burgeoning generative AI (GenAI) market

THIS STRATEGIC MOVE is aimed at reducing dependency on Nvidia while fostering innovation and facilitating global expansion. Within this dynamic landscape, significant investments in Al technologies and strategic partnerships underscore the intense competition within the GenAl space, says GlobalData, a leading data and analysis company.

Nvidia, which sells graphic processing unit (GPU) semiconductors particularly suited to AI-specific workloads, has emerged as one of the clear winners in the nascent GenAI market as demand for its GPUs explodes. However, providers of GenAI services such as big cloud computing companies have been impacted by the massive financial burden of acquiring the expensive chips.

Beatriz Valle, Senior Enterprise Technology and Services Analyst at GlobalData, comments: "There is a significant imbalance between supply and demand when it comes to GPU processors, because GenAl models in general, and especially multimodal systems that produce images and videos, greatly benefit from the parallel processing capabilities of GPUs. As a result, the chips are expensive and in short supply.

"To counteract this trend, GenAl companies are coming to market with their own proprietary technologies to run these workloads. Google has its tensor processing unit (TPU) semiconductors and Amazon has its Inferentia and Trainium architectures.

Meta, the social media company behind Facebook and Instagram, recently announced the next generation of custom-made chips to help power Aldriven rankings and recommendation ads on social media platforms."

GlobalData analysis notes that money continues to flow in the lucrative GenAl space as hyperscalers jockey for position. Leading GenAl companies are ramping up investment in strategic partnerships across the world to remain competitive. Microsoft, now vying for a global presence to offer Al services across Microsoft Azure's infrastructure, has recently invested \$1.5 billion in new technology group G24, an Abu Dhabi (UAE) Al consortium. AWS is completing its final round of \$4 billion in funding to partner Anthropic, striving to gain a foothold following Microsoft's mega OpenAl investment.

Charlotte Dunlap, Research Director of Enterprise Technology and Services at GlobalData, comments: "Microsoft's investment signals the start of a much larger AI technology role for the UAE. G24 is targeting various sectors for its AI solutions, including healthcare and energy. The deal is not without its complications. In return for the mega investment by Microsoft, G42 severed ties to China by eliminating hardware provisioning by Huawei systems, among other efforts in recent months to appease US concerns."

To counteract this trend, GenAl companies are coming to market with their own proprietary technologies to run these workloads. Google has its tensor processing unit (TPU) semiconductors and Amazon has its Inferentia and Trainium architectures

# CHIPS for America announces \$285 million funding opportunity

The Biden-Harris Administration has issued a Notice of Funding Opportunity (NOFO) seeking proposals from eligible applicants for activities to establish and operate a CHIPS Manufacturing USA institute focused on digital twins for the semiconductor industry

DIGITAL TWINS are virtual models that mimic the structure, context, and behavior of a physical counterpart. The CHIPS for America Program anticipates up to approximately \$285 million for a first-of-its-kind institute focused on the development, validation, and use of digital twins for semiconductor manufacturing, advanced packaging, assembly, and test processes. The CHIPS Manufacturing USA institute is the first Manufacturing USA institute launched by the Department of Commerce under the Biden Administration.

Unlike traditional, physical research models, digital twins can exist in the cloud, which enables collaborative design and process development by engineers and researchers across the country, creating new opportunities for participation, speeding innovation, and reducing costs of research and development.

Digital twin-based research can also leverage emerging technology like artificial intelligence to help accelerate the design of new U.S. chip development and manufacturing concepts and significantly reduce costs by improving capacity planning, production optimization, facility upgrades, and real-time process adjustments.

"Digital twin technology can help to spark innovation in research, development, and manufacturing of semiconductors across the country – but only if we invest in America's understanding and ability of this new technology," said Secretary of Commerce Gina Raimondo. "This new Manufacturing USA institute will not only help to make America a leader in developing this new technology for the semiconductor industry, it will also help train the next generation of American workers and researchers to use digital twins for future advances in R&D and production of chips."

"Under President Biden's leadership, we're writing a new chapter in semiconductor manufacturing in America," said Arati Prabhakar, Assistant to the President for Science and Technology and Director of the White House Office of Science and Technology Policy. "CHIPS R&D is about making sure American manufacturers can continue to succeed and thrive. Digital twin technology can accelerate the costly and timeconsuming work to develop the next generation of robust manufacturing for this extraordinarily complicated product."

Funded activities are expected to include, but not necessarily be limited to operational activities to run the Institute; basic and applied research related to semiconductor digital twin development; establishing and supporting shared physical and digital facilities; industry-relevant demonstration projects; and digital twin-related workforce training.

"Digital twin technology will help transform the semiconductor industry," said Under Secretary of Commerce for Standards and Technology and National Institute of Standards and Technology (NIST) Director Laurie E. Locascio. "This historic investment in the CHIPS Manufacturing USA institute will help unite the semiconductor industry to unlock the enormous potential of digital twin technology for breakthrough discoveries. This is a prime example of how CHIPS for America is bringing research institutions and industry partners together in public private partnership to enable rapid adoption of innovations that will enhance domestic competitiveness for decades to come."

# Imec.xpand launches EUR 300m fund

Imec.xpand, an independent global venture capital fund, has launched a new EUR 300 million fund aimed at accelerating the growth of transformative semiconductor and nanotechnology innovations

ESTABLISHED as a collaborative effort with imec, the world-leading R&D and innovation hub in nanoelectronics, the fund will invest in startups that have the potential to be globally disruptive within their target domains. The fund is designed to fuel semiconductor innovation beyond traditional applications and drive the nextgeneration technologies that are 10 years ahead of their time.

Imec.xpand invests globally across all stages, transforming semiconductor and nanotechnology innovations into market-ready solutions. Focused on leveraging imec's expertise, the fund targets breakthrough technologies including artificial intelligence (AI), machine learning (ML), augmented reality/virtual reality (AR/VR) and photonics. In life sciences, imec. xpand is looking for opportunities to advance cell therapy, sequencing, neuromodulation and other applications that will revolutionize medical diagnostics and treatments. "Imec.xpand is not just about funding startups, it's about building companies that can lead the next wave of technological transformation," said Tom Vanhoutte, partner at imec.xpand. "With this fund, we are dedicated to advancing the semiconductor industry by empowering startups to bring innovative technologies to market faster. The combination of our venture capital and international network helps unicorns grow amid the global race for semiconductor supremacy."

The first imec.xpand fund was launched in 2017 with the strong support of imec. Since then, imec.xpand has attracted a loyal base of international financial and strategic investors. Over the years, imec.xpand has built a strong track record of investing in game-changing companies.

The fund's unique positioning among the global venture capital community, and also in the U.S., is instrumental in attracting potential co-investors for its portfolio companies. Imec.xpand's stamp of approval often acts as a financial catalyst that enables startups to raise additional funding from other investors. To date, imec.xpand has invested in 23 companies that, so far, have raised nearly EUR 1.5 billion in financing and includes two unicorns.

Imec.xpand portfolio companies are developing cutting-edge, differentiated technologies that give them a global competitive advantage in their respective markets. Noteworthy imec. xpand portfolio companies include Celestial AI, a Palo Alto-based company that recently raised \$175 million USD to advance its optical compute and memory fabric solution for AI infrastructure; PsiQuantum, a frontrunner in the race to develop the first practical quantum computer; and Swave Photonics, developing a unique holographic extended reality chip technology designed to disrupt 3D holographic imaging and spatial computing.

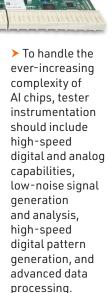

# AI chip market to become a \$300 billion industry

THE GLOBAL AI renaissance, which started last year, only fuelled the market growth, helping it to reach a staggering value in the following years. According to data presented by AltIndex.com, the global AI chip market is expected to grow 10 times in the next ten years and become a \$300 billion industry.

Al chips are specialized semiconductor devices that perform complex calculations and tasks required for artificial intelligence applications. They are designed to accelerate Al algorithms and processes, enabling higher performance, lower power consumption, and improved costeffectiveness. Today, Al chips are used across industries, from healthcare and finance to automotive and manufacturing, and the global demand for these devices is expected to skyrocket in the following years. According to Statista and Market.us data, the global AI chip market will gross \$30 billion in 2024, or \$7 billion more than last year. Over the next three years, the market revenue will more than double and hit \$67 billion by 2027. Still, that is nothing compared to growth projections in the years after that. By 2029, the entire market is expected to hit a massive milestone and become a \$100 billion industry. Three years later, that \$100 billion will grow into \$260 billion, or eight times the expected revenue in 2024. Statistics show the global AI chip market will continue surging in 2033, with revenues rising to a whopping \$341 billion, or 1,000% more than this year.

Although Nvidia is the absolute king in the AI chip industry with a massive

80% market share, both large and small businesses are searching for alternatives to diversify their Al chip options. That caused intense competition in the market, with both semiconductor giants and emerging startups heavily investing in Al chip research and development to gain a competitive edge. The surging need for Al chips has also created a huge space for VC investors, who have poured tens of billions of dollars into these startups.

# Semiconductor giants add \$1.1 trillion to stock values

After a challenging year in 2023, the global semiconductor industry is back on track for recovery, fuelled by a surging AI chip sale, especially in the generative AI field

GLOBAL SEMICONDUCTOR sales are expected to hit \$588 billion in 2024, 13% more than last year and 2.5% higher than 2022's record industry revenues of \$574 billion. This positive trend has also helped the largest players in the market add hundreds of billions of dollars to their stock values.

According to data presented by AltIndex.com, the five largest semiconductor companies have collectively increased their stock values by over \$1.1 trillion year-to-date.

The surge in generative AI use continues fuelling global AI chip sales and rising stock prices of the biggest semiconductor companies. In January, the combined market cap of Nvidia, Taiwan Semiconductor Manufacturing, Broadcom, Samsung, and ASML Holding, the five largest semiconductor manufacturers globally, amounted to \$2.99 trillion. Since then, this figure has jumped by an impressive \$1.1 trillion and hit \$4.1 trillion last week. And while most of these tech giants added tens and even hundreds of billions of dollars to their market cap over the past four months, none is even close to Nvidia (NVDA).

The world's third-largest tech company and the biggest semiconductor company by market cap is having another fantastic year. After ending 2023 as the best S&P 500 performer with a 236% gain, the Nvidia added more than one trillion dollars to its stock value in the first three months of the year, or 15% more than in the entire 2023.

In January, Nvidia's market cap amounted to \$1.2 trillion. By the end of March, this figure soared to \$2.3 trillion, showing an impressive 90% growth in just three months. Although the company's market cap dropped by 10% since then and hit \$2.06 trillion last week, Nvidia still added a whopping \$833 billion to its stock value year-todate, the biggest increase among the semiconductor giants.

Semiconductor Manufacturing (TSM) jumped by almost \$170 billion, or 31%, in this period, the second-highest increase in this group. In January, the market cap of the Taiwanese tech giant stood at \$539 billion; now, it's over \$708 billion. Statistics show the US semiconductor manufacturer, Broadcom, added \$77 billion to its market cap year-to-date and hit a market cap of almost 600 billion last week. The Duch-based ASML Holding follows with a \$58 billion increase and \$356 billion in stock value as of last week.

## INDUSTRY NEWS

# Rapidus and Esperanto Technologies sign memorandum of cooperation

Promote development and manufacture of more energy-efficient semiconductors for artificial intelligence and other high-performance datacenter applications

RAPIDUS has signed a Memorandum of Cooperation with Esperanto Technologies Inc, a leader in energyefficient RISC-V based computing solutions. With the conclusion of the MOC, the two companies intend to promote the development and manufacture of low-power consumption AI semiconductors for datacenters, which will be indispensable in the coming full-fledged AI era.

Esperanto develops high-performance, energy-efficient computing solutions for artificial intelligence/machine learning based on the open standard RISC-V instruction set architecture. The company has semiconductor design technology that achieves high energy efficiency in the fields of generative AI and high-performance computing (HPC).

Last September, Rapidus began construction of IIM (Innovative Integration for Manufacturing) in Chitose City, Hokkaido. This will be Japan's first facility for the production of state-of-the-art logic semiconductors at 2-nanometers (nm) and beyond. At the same time, Rapidus has been dispatching researchers to the Albany Nanotech Complex in New York, USA, one of the world's most advanced semiconductor research centers, to work with IBM to develop technologies for the production of 2nm logic semiconductors. The company is also planning to acquire EUV lithography technology, which is essential for the production of cutting-edge semiconductors, from imec. Utilizing these technologies, the company plans to start operation of a pilot production line at IIM-1 in April 2025, and begin mass production in 2027.

As society enters the full-fledged Al era represented by generative Al, power consumption in data centers is

increasing. According to International Energy Agency, data centers are significant drivers of growth in electricity demand in many regions. After globally consuming an estimated 460 terawatthours (TWh) in 2022, data centers' total electricity consumption could reach more than 1.000 TWh in 2026. This demand is roughly equivalent to the entire electricity consumption of Japan. Updated regulations and technological improvements, including on energy efficiency, will be crucial to moderate the surge in energy consumption from data centers. (Source: "Electricity 2024" ©International Energy Agency)

The 2nm node semiconductors that Rapidus aims to manufacture will be more advanced than conventional semiconductors, enabling not only improved processing performance but also dramatically reduced power consumption. Esperanto, meanwhile, has been developing products with superior energy efficiency for generative AI, HPC and edge devices.

By collaborating early on the cooptimization between design and manufacturing of next-generation semiconductors, the two companies aim to better enable the development of energy-efficient products for the Al era.

"The strategic partnership with Rapidus plays a key role in our expansion plans for Japan," said Art Swift, CEO of Esperanto Technologies Inc. "Rapidus represents a new approach to leading-edge semiconductor manufacturing, and we are very impressed with the direction and speed at which they are operating. Along with our other partners in Japan, we hope our new relationship with Rapidus will extend the benefits of our energy efficient technology to a broader set of SoC designers."

"As part of our corporate philosophy, we will commit ourselves to further innovating toward a truly green society," said Dr. Atsuyoshi Koike, president and CEO of Rapidus Corporation. "As we enter the age of full-fledged AI, it is imperative to design and manufacture semiconductors with superior energysaving performance, and we believe that this collaboration with Esperanto is a major step toward solving this issue."

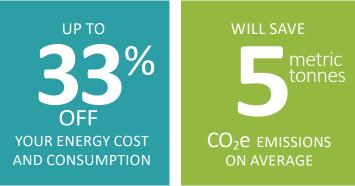

# Infineon reveals roadmap for energy-efficient power supply units in AI data centres

## Artificial intelligence leads to increasing energy demand of data centres worldwide

THE INFLUENCE of artificial intelligence (AI) is driving up the energy demand of data centers across the globe. This growing demand underscores the need for efficient and reliable energy supply for servers. Infineon Technologies opens a new chapter in the energy supply domain for AI systems and unveils a roadmap of energy efficient power supply units (PSU) specifically designed to address the current and future energy need of AI data centers.

By introducing unprecedented PSU performance classes, Infineon enables cloud data center and AI server operators to reduce their energy consumption for system cooling. The innovative PSUs reduce power consumption and CO 2 emissions, resulting in lower lifetime operating costs. The powerful PSUs are not only used in future data centers but can also replace existing power supply units in servers and increase efficiency. In addition to the current PSUs with an output of 3 kW and 3.3 kW available today, the new 8 kW and 12 kW PSUs will contribute to further increasing energy efficiency in future AI data centers. With the 12 kW reference board, Infineon will offer the world's first power supply unit that achieves this level of performance and supplies future data centers with power.

"At Infineon, we power AI. We are addressing a critical question of our era – how to efficiently meet the escalating energy demands of data centers," says Adam White, Division President Power & Sensor Systems at Infineon. "It's a development that was only possible by Infineon's expertise in integrating the three semiconductor materials silicon (Si), silicon carbide (SiC), and gallium nitride (GaN) into a single module. Our PSU portfolio is therefore not only an example of Infineon's innovative strength, which leads to first-class results in terms of performance, efficiency and reliability for data centers and the AI ecosystem. It also reinforces Infineon's market leadership in power semiconductors."

Infineon is responding to the requirements of data center operators for higher system efficiency and lower downtimes. The growth of server and data center applications has led to an increase in power requirements, necessitating the development of power supplies with higher power ratings from 800 W up to 5.5 kW and beyond. This increase is driven by the growing power requirements of Graphic Process Units (GPU) on which Al applications are computed.

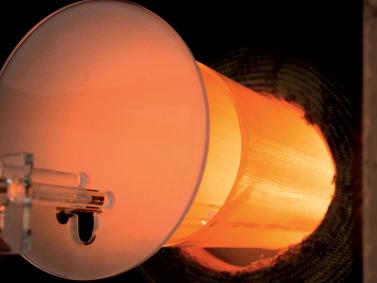

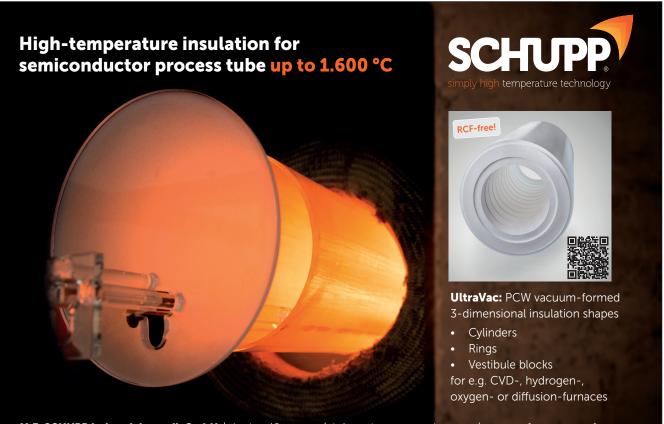

# High-temperature insulation for semiconductor process tube up to 1.600 °C

RCF-free!

high temperature technology

**UltraVac:** PCW vacuum-formed 3-dimensional insulation shapes

- Cylinders

- Rings

- Vestibule blocks

- for e.g. CVD-, hydrogen-,

oxygen- or diffusion-furnaces

M.E. SCHUPP Industriekeramik GmbH | Aachen/Germany | info@schupp-ceramics.com | www.schupp-ceramics.com

## **INDUSTRY NEWS**

# £3m grant for Glasgow chip research

A major new grant will allow the University of Glasgow to build one of the UK's most advanced research facilities for silicon chip integration and packaging

A MAJOR new grant will allow the University of Glasgow to build one of the UK's most advanced research facilities for silicon chip integration and packaging.

The Engineering and Physical Sciences Research Council's Strategic Equipment Grant scheme will provide £3m to help the University establish ANALOGUE – the Automated Nano AnaLysing, characterisatiOn and additive packaGing sUitE.

Clockwise from top left: Prof David Flynn, Prof Hadi Heidari, Dr Mahmoud Wagih and Prof Jeff Kettle of the James Watt School of Engineering

ANALOGUE will enable the rapid prototyping and characterisation of a wide range of semiconductor devices. New developments prototyped at ANALOGUE could find applications in biomedical implants, sustainable and biodegradable sensors, and quantum computing interfaces.

The facility, which will be based at the University's Mazumdar-Shaw Advanced Research Centre (ARC), brings together researchers from the University's James Watt School of Engineering with a strategic network of partners from industry, national semiconductor facilities, and academia, aligned with fast tracking disruptive new technologies into applications.

It aims to support the UK government's semiconductor strategy by providing access to new technologies to boost cutting-edge research and development. It will also play a role in expanding the country's semiconductor skills base through industry-led events and partnerships with Centres for Doctoral Training across the UK.

The suite will house chip probing equipment, advanced packaging capabilities, and additive electronics

manufacturing using state-of-theart tools. The equipment will be automated as a single suite, making it the UK's first machine-driven integrated assembly and characterisation line for semiconductor devices. ANALOGUE's advanced automation will allow users to use the suite remotely, with support from on-site experts, helping to streamline the research process.

ANALOGUE will also provide support for ongoing efforts to decarbonise the electronics supply chain by helping researchers gather data on their product's environmental impact.

ANALOGUE will be open to academia and industry working on lowvolume and high-value research and development projects, helping them to rapidly prototype advanced nanoelectronic devices.

Professor Hadi Heidari, Head of the University of Glasgow's Electronics and Nanoscale Engineering Research Division, is the project's principal investigator.

He said: "This grant is a significant milestone for semiconductor research in the UK, which is a key part of the country's economy. The electronics sector as a whole supports more than a million jobs in the country, and the UK government has ambitious plans to grow the sector in the years to come.

"The establishment of ANALOGUE represents a substantial advance in

the UK's semiconductor research infrastructure for heterogeneous integration and advanced packaging.

"This initiative will help spark new innovations across the tech sector and cultivate valuable partnerships between academia and industry, helping to support breakthrough research which can drive economic expansion."

The suite is supported by 27 external project partners including national facilities such as the Manufacturing Technology Centre (MTC) and the National Physical Laboratory (NPL), academic networks (EPSRC eFutures and E-Textiles), and top research universities.

A team of 23 academics and more than 100 researchers and students will make regular use of the facility. ANALOGUE's industrial partners include Arm, PragmatIC, Inseto, Nano-Dimension, Vector Photonics, Touchlab, Printed Electronics, Kelvin Nanotechnology, Denchi Power, SeeQC, Quantum Science, Labman, Scotland 5G Centre, and CENSIS.

This multidisciplinary project is strongly supported by other colleagues at the James Watt School of Engineering from different areas of Quantum Technologies, Medical Implantables, Wearables and Diagnostics, Ultrasound Systems, and Sustainable Electronics including Prof Jeff Kettle, Prof David Flynn, Dr Mahmoud Wagih, Prof Martin Weides, Prof Muhammad Imran, Prof Edward Wasige, Prof Marc Sorel, Dr Chong II, Dr Kaveh Delfanazari, Dr Andrew Feeney, Prof Sandy Cochran, Dr John Mercer, Dr Daniel Mulvihill, Prof Margaret Lucas, Prof S Kumar, Prof David Cumming, Prof Manuel Salmeron-Sanchez, Prof Qammer Abbasi, Dr Morteza Amjadi, Prof Julien Reboud, Prof Jonathan Cooper, Dr Qingshen Jing, Dr Kwok Ho Lam and Dr Rair Macedo.

SMART MOBILITY ഫ

SMART MEDTECH

Connecting Semiconductors and **Electronics**

About SEMI:

SEMI connects more than 2,500 member companies and 1.3 million professionals worldwide to advance the technology and business of electronics design and manufacturing. The breadth and depth of our events, programs and services help members accelerate innovation and collaboration on the toughest challenges to growth.

SMART DATA-AI

᠈ᢑᡏ

WORKFORCE DEVELOPMENT

> Global ADVOCACY

> > Sustainability

MARKET INTELLIGENCE

1000+ **STANDARDS**

THOUGHT LEADERSHIP

SEMICON

TECH COMMUNITIES

SEMI UNIVERSITY

Cyber Security

# High-speed, high-temperature pumps address the challenges of advanced ALD processes

Addressing the potential problems of pump failure, process downtime and slow processing speeds when it comes to atomic layer deposition.

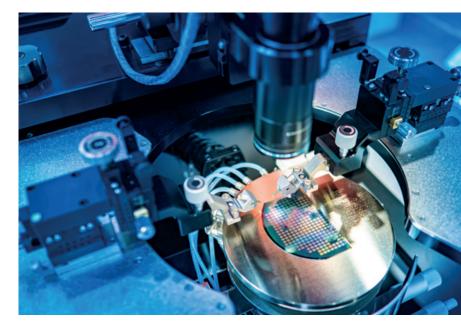

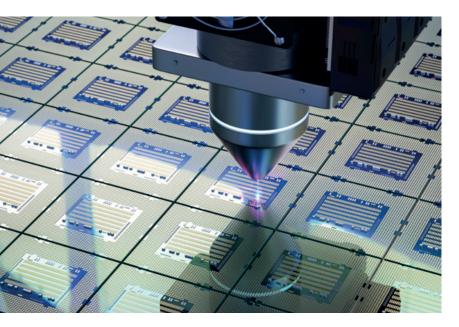

## BY ALLISTER WATSON AND YOUNG CHUNG, EDWARDS VACUUM

SEMICONDUCTOR DEVICE designs are going vertical. Some of the most exciting new devices use many-layered film stacks and incorporate high aspect-ratio (HAR) features that are themselves complex multilayered structures deposited with atomic layer deposition (ALD) processes. Some ALD processes generate condensable by-products that can accumulate in vacuum pumps.

If not addressed, the deposits can lead to pump failure and process downtime. Even when managed appropriately, these accumulations require periodic maintenance that increases cost-of-ownership and reduces productivity. While ALD is exquisitely precise, it is also inherently slow, limited to a large extent by the vacuum system's ability to cycle between precursor and reactant gases in the process chamber. Together, these considerations are driving the development of higher temperature, higher speed pumps to extend maintenance intervals and shorten ALD process cycles.

## HAR structures

HAR features are becoming more common, and their aspect-ratios continue to increase. In some cases, such as the capacitors in DRAM, the increasing ratio results from pressure to pack more capacitors within a given footprint. In other cases, the pressure is in the vertical direction, as in 3D NAND, where increasing memory capacity means

## TECHNOLOGY | PUMPS

more layers and longer channels. In both cases, tall, narrow, cylindrical cavities etched in the substrate are filled by concentric layers of various materials to create the functioning device.

### **ALD** processes

Most conventional deposition processes were developed to deposit uniform films over shallow features. The processes are relatively fast, and the deposition continues as long as the surface is exposed to the process.

The thickness of the film is thus a function of the time the deposition time. These processes are not good at maintaining uniformly thick films in the presence of significant topography, especially the extreme topography of HAR features where the deposition process has restricted access to the internal vertical walls and deeply recessed bottoms of the features.

ALD offers an elegant solution for depositing highly conformal, precisely controlled thin films on complex, deeply recessed surfaces. The deposits accumulate one atomic layer at a time as the surface is exposed to a repeating cycle of precursor and reactant gases. In the first phase, the precursor reacts with specific sites on the surface.

The reaction is self-limiting – once all sites have been occupied by a precursor molecule, the reaction stops. Next, the precursor gas is removed, and a reactant gas is introduced. The reactant interacts with the previously deposited precursor, again in a self-limited way, to complete the deposition and recreate the original surface chemistry. The newly deposited monolayer is ready for another ALD cycle.

Because both reactions are self-limiting, film thickness is a function of the number of cycles, not exposure time. This gives process engineers the luxury of allowing each cycle of the process to continue as long as needed to be sure all surfaces are completely and uniformly covered.

The biggest drawback of ALD is its slow speed. It is best suited to the deposition of very thin films that require fewer deposition cycles. Wafer throughput is determined primarily by the time it takes to remove one gas from the process chamber and replace it with the other, which puts a premium on high pumping speed in the vacuum system. Condensable Process Gases and By-Products

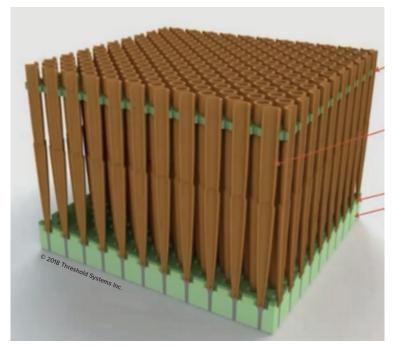

> Figure 1: The tube-shaped capacitors comprise concentric cylindrical TiN plates separated by dielectric materials. ALD of TiN from TiCl4 creates NH4Cl, a condensable by-product. TiCl<sub>4</sub> flows will increase as the capacitors grow taller and narrower. Reference: Threshold.

Some process gases and by-products condense on cooler surfaces. In extreme cases, accumulations can completely block vacuum lines and cause pumps to seize. Avoiding unwanted deposition is most critical in the pump itself where rapidly rotating parts must maintain very tight mechanical tolerances. Condensation can be reduced or prevented by maintaining sufficiently high temperatures within the vacuum system. The challenge is best addressed by specially designed high-temperature pumps and by heating the foreline and exhaust line.

DRAM capacitors (Fig 1) are getting taller and thinner to increase their aerial density. The half-pitch of the capacitor array is projected to decrease by half over the next decade. Inside each capacitor, concentric tubular plates are separated by a complex structure of layered dielectric materials. ALD is essential for depositing the TiN electrodes of the capacitors. It is produced by the reaction of TiCl4 and NH3. The reaction deposits TiN but generates NH4Cl, a condensable by-product. A carefully controlled, high-temperature profile throughout the vacuum

| DRAM                | 2022    | 2025    | 2028    | 2031    | 2034    |

|---------------------|---------|---------|---------|---------|---------|

| Min Half Pitch (nm) | 15.5    | 13      | 14      | 11.5    | 10      |

| Cell Size (µm²)     | 0.00165 | 0.00118 | 0.00085 | 0.00062 | 0.00044 |

> Table 1. The cell size and half pitch of DRAM capacitor arrays are expected to shrink substantially in the next 10 years. (source: IRDS 2022)

Edwards' latest generation of high-speed, high-temperature pump (iXH6520HTXS+) was developed in collaboration with major semiconductor equipment suppliers to address the challenges presented by advanced ALD process

system, but especially in the pump, reduces unwanted deposition and the risk of pump seizure. As aspect ratios increase, so will TiCl4 flows.

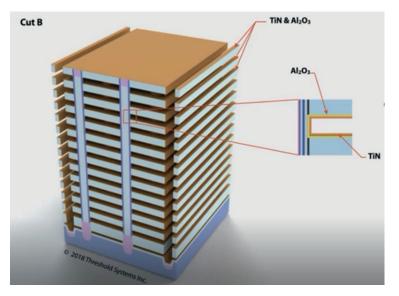

Current generation 3D NAND devices have nearly 200 pairs of alternating oxide/nitride dielectric layers. Vertical memory strings are created along channels that penetrate these layers. The number of layers determines the number of memory cells along each channel and thus the memory density and capacity of the device.

The number of layers for multi-tiered devices will likely increase to 500 or more this decade. To create the memory cells, the channels are lined with an oxide/nitride (ONON) sandwich. The nitride layers become the charge traps that store information. The outermost oxide layer is needed to block a

Figure 2. The number of layers in 3D NAND memory is predicted to double or more by 2031, requiring longer, higher aspect ratio channels. The ONON sandwich that lines each channel is deposited with ALD from HCDS. The nitride phase of the deposition creates condensable NH4Cl. The HCDS can also condense to a polymeric gel. (Source: Threshold Systems 2021) subsequent nitride etch that removes nitride from between the oxide layers of the original ONON stack.

ALD processes are used to deposit the ONON sandwich within the channels. Both the oxide (SiO2) and the nitride (SiN) are generated from hexachlorodisilane (HCDS). For nitride layers, HCDS + NH3 deposits SiN but also generates condensable NH4Cl as a by-product, requiring a hot pump to prevent unwanted condensation within the pump.

For oxide layers, HCDS + oxidant deposits the oxide without creating the NH4Cl by-product. However, the HCDS molecule itself may polymerize to form a condensable gel. Thus, a hot pump is needed to prevent NH4Cl in the nitride case and HCDS gel condensation in both cases. As the number of layers increases, so will the flows of HCDS and the need for hotter pumps.

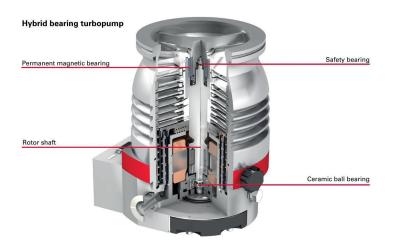

## The pump

Edwards' latest generation of high-speed, hightemperature pump (iXH6520HTXS+) was developed in collaboration with major semiconductor equipment suppliers to address the challenges presented by advanced ALD process. It incorporates several new critical high-temperature technologies that allow it to operate at surface temperatures as high as 260°C. High-temperature operation reduces by-product condensation on critical pump surfaces, significantly extending recommended service intervals. Compared to its predecessor this new pump also benefits from a 30% increase in peak pumping speed, up to 96,000 l/min; a 34% lowering in power consumption; and better achievable ultimate vacuum pressure performance (important for high cleanliness between ALD steps).

For advanced ALD processes where condensable by-products are a concern then less frequent maintenance, faster process cycles, and lower power consumption can offer substantial bottomline returns by lowering cost of ownership and increasing productivity.

| 3D NAND                 | 2022    | 2025    | 2028    | 2031    | 2034     |

|-------------------------|---------|---------|---------|---------|----------|

| Number of Memory Layers | 128-192 | 256-384 | 384-576 | 576-768 | 768-1024 |

| Number of Tiers         | 2       | 2       | 3       | 3       | 4        |

| Bits/mm <sup>2</sup>    | 2Т      | 5.2T    | 8T      | 12T     | 16T      |

➤ Table 2. 3D NAND Layers, tiers and storage density will all increase substantially over the next ten years. (Source: IRDS 2022)

#### Your added value

- Good combination between pumping speed and compression ratio

- Maximum reliability through the use of hybrid bearings

- High pumping speeds for both light and heavy gases

- Highest process capability, resistant to particles

# PFEIFFER VACUUM

Your Success. Our Passion.

# Exploiting the new wave of Semiconductors:

Al, trust & information overload

# **ROBERT MCKENZIE, VP OF SILICON SECTOR AT GLOBAL SOFTWARE SERVICES COMPANY, MOBICA** navigates the semiconductor revolution and identifies opportunities for growth.

THE GLOBAL SEMICONDUCTOR INDUSTRY is experiencing huge growth and predicted to become a trillion dollar industry by 2030. That growth is being accompanied by an ongoing rediscovery of application approaches and step changes in design and development. It is not an understatement to say that we are seeing momentous changes happening at an unprecedented pace.

In this article we take a look at what's driving those changes, their adoption and the technology underlying this momentous change.

## The scale of change

A keynote at Embedded World conference, March 2023, provided the following eye popping statistics about the level of growth in Internet of Things (IoT) business and installations:

- By 2030, the IoT could enable \$5.5 trillion to \$12.6 trillion in value globally

- In 2023 11.5bn connected devices will ship, bringing the installed base to 40bn units - 1.5bn home automation, 0.75bn inventory and asset tracking, 600m for lighting, 300m health and fitness

Thanks to the rapid adoption of AI, embedded solutions and the IoT, there is a new wave of chips

coming along that can serve a broader range of applications. They can do so because of the increased capability to support security, safety, identity and privacy, all areas where the new architecture and semiconductor chip features add value.

Originally computers were designed for a particular purpose, for example, breaking cryptographic ciphers. The arrival of the first commercially available general purpose computer, the Ferranti Mark 1, led to general purpose applications for government, business and scientific challenges. But there was still an opportunity for 'application specific integrated chips' (ASICS). Companies such as LSI Logic played a significant role in changing the semiconductor market during the 1980s and 90s, with their ASICS for calculators etc.

# Building on the foundations laid over the past 50 years

Today's industry builds on previous inventions to deliver a wide range of architectures and technologies that deliver the new applications. As well as the general purpose 'central processing units' (CPUs), those technologies include:

• ASICS for handling, amongst other things, compression, encryption and with features

like VRAN boost in Intel XEON based SmartNICS accelerating networking needs.

- FPGAs fully programmable gate arrays enabling feature updates on the semiconductor itself, making them as upgradeable as a software package

- GPUs graphics processing units accelerating graphics processing by enabling single instructions to operate in parallel on multiple data

- xPUs the processing unit designed for a particular application

The 'system on chip' (SOC) approach brings together semiconductor designs to deal with I/O, power management, telecoms, including the iterations of mobile protocols 3-5g, WAN and Bluetooth.

We should mention the concept of the xPU: this is a catch-all for the 'processing unit', designed for a particular application e.g. most SOCs now include an NPU, or neural processing unit, designed for efficiently calculating the mathematics of neural networks, which feature in new products from Intel, Apple and Qualcomm. A further example is the VPU, or 'visual process unit', used in cameras, and designed for image processing.

# Scaling up: trends and new developments

As well as being able to design all the systems on one chip, standardisation around 'chiplets' will increase the possibility and market for new semiconductor development.

The UCle specification for the 'Universal Chiplet Interconnect Express' is focussed on building an open ecosystem of chiplets for on-package innovations. This market will take a decade to develop, but is part of the new wave of semiconductor innovation.

Before moving onto AI, trust and information overload, it's worth providing two more examples of scale. At the data centre end, Nvidia's GPU Technology Conference in 2022, Stephen Jones ran through the phenomenal increase in performance that has occurred at the high-end of silicon technology.

The A100 GPU, or Ampere architecture, used in the data-centres, runs at 9.7 TFLOP/s double precision performance. To put this in perspective, the world's leading supercomputer in 2001 was the Lawrence Livermore National Laboratory in the USA's ASCI White, had 7.9 TFLOPS/s. So the A100 chip has more than the equivalent performance.

At the recent GTC, Jensen Huang - Nvidia's CEO - announced its new Blackwell architecture to be released in 2024. Whilst double precision (FP16) performance figures weren't presented, the new chip does deliver 20k TFLOPS at FP4, or 1000x increase over the past 8 years.

At the edge, the microcontroller (MCU) is becoming increasingly sophisticated and able to deliver more. Traditionally it has a few components such as RAM, ROM, and programmable I/O ports primarily designed to control and drive other electronic equipment. MCUs are designed to be embedded, often in a highly restrictive environment. They usually consume very little power, may run relatively slow, and typically execute individual task-specific programs. But now they are increasingly including features to ensure security and provide AI services.

TinyML is one movement that is enabling machine learning on these tiny devices. According to the TinyML foundation, it is broadly defined as a fast growing field of machine learning technologies and applications including hardware, algorithms and software capable of performing on-device sensor data analytics at extremely low power, typically in the mW range and below, which enables a variety of always-on uses for battery operated devices.

The NXP MCX N Advanced Series Microcontrollers, includes intelligent peripherals and on-chip accelerators. To balance performance and power efficiency, they incorporate NXP's elQ Neutron neural processing unit (NPU) specifically for machine learning applications.

Similar devices are being produced by Infineon, STMicro, Sony, Espressif, often combining off the shelf IP CPU cores licensed from ARM and then adding these new features in order to support new applications. Whereas the latest data centre chips and boards cost tens of thousands of dollars, microcontrollers can be bought in quantity for under fifteen dollars - or less.

Further new innovations coming down the line will increase the performance and reduce the power consumption even further. A good example of this is being developed by EnchargeAI. They are designing a hybrid of analogue and digital chip technology due to ship at the end of 2024. Benchmarks demonstrate a 150 TOPS/W, which is 20x current market leader in power usage efficiency.

# TECHNOLOGY I SOFTWARE

## Inference: use cases and applications

Initial use cases for the EnchargeAI product will be in inference, not for training the Deep Neural Nets (DNN) and Large Language Models that Nvidia and newer entrants such as Tenstorrent and Cerebras are aiming at. The inference work will use these trained models for natural language processing and image recognition support. The product is likely to become integrated in SOCs for the phone, or battery powered devices. Currently, security systems are often wired in because the components won't operate for multi-year periods on batteries. These new technologies bring the promise that they will not only be able to operate for long periods of time, but that they will also be able to make decisions based on better training.

At the moment, standard commercial or domestic security systems will recognise intruders, capture the image and, if armed, inform the owner. With new features at an improved price point, it's a short step to having the system recognise that it's you, or someone else who lives or works at the premises, and disarm and open the door.

For the first time, the ability to get inferencing and then decision making right at the edge is becoming a reality. Perhaps more significantly, it is also becoming economically viable.

So much so that a number of companies such as Google's advanced projects and Levi and Nike have been championing the use of wearable technology. For Nike, this is in the sporting field, where its value in assessing fitness and performance is married with the far more important need to understand the longterm health of athletes, especially in contact sports.

Mobica has worked on SOLI for gesture recognition (radar) and Jacquard (gyro) for motion. Jacquard technology used by Levi's and Nike, Soli technology features in the Pixel phone. Semiconductors form the bedrock for these applications but need the software and firmware above it in order to put an ecosystem in place that makes it a usable solution.

The two fundamental technological areas of artificial intelligence (AI) and trust, which is more typically referred to as security, have driven the demand for new semiconductor design and performance. The software and firmware part of the journey is also vital.

# Connecting the hardware to the software

The capability of connecting the hardware to the software is at the core of Mobica - a Cognizant company - services. When a device needs a driver, whether it be GPU or Ethernet adapter, Mobica is often asked to assist and we cover all other aspects of connecting the hardware by developing and optimising systems software and firmware.

Our customers included industry leaders such as BMW, Jaguar Land Rover, Cariad in the automotive industry and ARM, Imagination Technologies as well as Samsung in the semiconductor industry.

The customers of these customers are demanding smarter products, which now means using AI and products they can trust, which means better security technology.

# The new wave of chips - privacy, security and trust

This new wave of chips supports trust in new products and services, but includes well understood cryptographic theory as features in the chip set or SOC. The algorithm was initially devised by mathematician Clifford Cocks who, in the early 1970s, while working at the United Kingdom Government Communications Headquarters (GCHQ), developed public key cryptography (PKC). It was developed into a solution known as public key encryption (PKE), by Rivest, Shamir and Adleman (RSA) who established a company to commercialise it.

This algorithm and digital certificates infrastructure has been widely used since the 1990's - but it has been implemented at the network, (the IP layer) to deliver 'virtual private networks' (VPNs) with IPSec protocol and at the Transport layer, via the TLS implementation, to deliver security to web browsers, text messages and email for example. The problem is that neither of these prevents interception or 'man in the middle' attacks at the physical media level that is the processor.

Mobica has worked on SOLI for gesture recognition (radar) and Jacquard (gyro) for motion. Jacquard technology used by Levi's and Nike, Soli technology features in the Pixel phone

## TECHNOLOGY | SOFTWARE

Consequently semiconductor industry participants have developed frameworks and IP to ensure that customer information and data can remain private, not only when 'at rest' i.e in a storage medium, or when 'in flight' i.e. over communication protocols such as HTTP, but now when 'in use'. The expression 'secure, at rest, in flight and in use' has become commonplace over the last 3-5 years.

Two companies that have introduced semiconductor technology to support this are Intel and ARM. Intel is most famously associated with the PC and data centre, whereas ARM licences technology to companies such as Apple, Qualcomm and Samsung and, between these two ecosystems, the cloud to edge security is covered.

Intel delivered the Intel Trust Authority, offering a unified independent assessment of its Trusted Platform Module. TPM came from the Trusted Computing consortium and provides circuitry to implement PKI down to the processor level in both the PC and data centre. The Trust Authority provides a framework for independent attestation that nothing has touched, read, or in any way interfered with your data.

The key point is that the TA services will give users confidence that confidential information placed in the cloud remains secret, even from those that operate the cloud. There is nothing that they can do, at the container, hypervisor or OS level that gives them the privileges to access this. This is vitally important for many industries e.g. banking, pharmaceutical, for its drug research data chemical industries, for product recipes.

ARM provides its Platform Security Architecture (PSA) as a common industry framework for IoT devices. PSA helps developers define a consistent level of security by providing principles and deliverables, including threat models, architecture specifications and open source firmware.

For its Cortex A architecture, the heart of most mobile phone SOCs, it has created Trust Zone, which is commonly used to run trusted boot and trusted OS to create a Trusted Execution Environment (TEE). Typical use cases include the protection of authentication mechanisms, cryptography, mobile device management, payment, key material, and digital rights management (DRM).

These two frameworks add the semiconductor integrity to well understood trust algorithms, providing the integrity required for customer trust of the product. Naturally, even though these foundations are in place, it requires excellent and experienced software and firmware engineering to implement an error free solution. Mobica works with chip manufacturers and smart product manufacturers to ensure that the implementation includes all valid specifications and verifies that the specifications are implemented accurately.

To the consumer, they can have confidence that these products and services will prevent unauthorised access to property or theft of vehicles. If used for monitoring services - and if the provider transfers sole access and data to the consumer then the same technology can be used to prevent 'big brother' scenarios, whether from government or organisations.

#### The future functions of AI PC

The AI features in the new semiconductor solutions work in tandem with trust features to combat information overload. The vast majority of work activity today requires handling large amounts of information and data.

Recently at Mobile World Congress (MWC) in Barcelona, a partner discussion posited a few examples of where AI assistants either help, or may help, reduce overload. The first example was for office productivity where the new AI PC - which was being promoted - would feature applications that could summarise and prioritise emails and the coming week's meetings, in conversation with the PC. This might be possible, but there is a lot of software engineering and LLM training and application development to be done before this would work faster and more accurately than doing it yourself.

As the diversity of document and file types and stores proliferate, this capability will be much needed - particularly thanks to phones, drives (Apple, Gdrive, Onedrive) mail (Gmail, Outlook, Thunderbird, Apple), messaging apps (Slack, WhatsApp, Messenger) and social media (Snapchat, Facebook, Instagram, TikTok).

This is particularly the case since the AI PC is taking the workload off the CPU, resulting in a more responsive and power efficient PC. For example, tests show that blurring the background for video conferencing (an AI task) takes up to 20% of CPU

# TECHNOLOGY I SOFTWARE

cycles. This goes down to 1% with the AI NPU offload and gives a 38% power saving when tested with ZOOM. Further examples included translating sign-language to english in real-time which was not possible with earlier PC generations but is now a possibility, using CPU, GPU and NPU in the AI PC to deliver this.

Microsoft has co-opted the term 'Co-pilot' for embedding AI technology into OS's and applications. It's a good term, better than 'digital twin' as it confers the notion of assistance. As Mobica is a software and firmware solution provider, benefits from assistance in writing both are appreciated, but it's not a panacea, even for programming, where logic and algorithms are documented in Open Source repositories such as GitHub and GitLab.

The best illustration of the journey still to be taken was presented by Fireship - a popular technology YouTube channel. It's worth looking at 'Devin' - a product from Cognition AI labs - which accesses a terminal, browser, coder editor like a SW engineer and is designed to work like an SW engineering expert. It iterates, through from requirement, to code fragments similar to the issue and generates code, runs it, tests it and more, until the requirement is met.

As a product, it is comparable to AutoGPT, where LLM is also the base technology, but Devin gets the ability to perform actions and react to the feedback from those actions.

They demonstrated the product using the "SW Engineering Benchmark", which is closer to real SW engineering challenges, than what is commonly used for demonstrating other 'co-pilot' type products.

The benchmark provides an evaluation framework

including 2,294 software engineering problems drawn from real GitHub issues and corresponding pull requests across 12 popular Python repositories. Given a codebase along with a description of an issue to be resolved, a language model is tasked with editing the codebase to address the issue.

The table below shows the results:

Whilst 13.85% is a step change compared to previous LLM products benchmark results, it is not the end of software and firmware engineering as a career. In fact the need for experienced engineers is likely to continue to grow.

# The ongoing importance of software engineering

The new performant semiconductor products provide the foundation for these new solutions, both in the cloud (large scale) and at the edge (small scale), but engineering the complete stack requires skilled software engineering services.

It is imperative that we continue to train and develop engineers that understand the performance parameters, strengths and characteristics of new and developing software, whether that's AI technologies (LLMs, SLMs, DNN RNNs), cryptographic, compression or performance accelerators, which is something Mobica, and its parent Cognizant delivers.

| Tool          | % Issue Resolved |

|---------------|------------------|

| Claude2       | 4.8%             |

| SWE Llama 13B | 3.97%            |

| SWE Llama 7B  | 3.01%            |

| GPT-4         | 1.74%            |

| ChatGPT-3.5   | 0.52%            |

| DEVIN         | 13.85%           |

- Based around a hot topic for your company, this 60-minute recorded, moderated zoom roundtable would be a platform for debate and discussion

- Moderated by editor, Phil Alsop, this can include 3 speakers

- Questions prepared and shared in advance

Cost: €5995

Contact: Jackie Cannon jackie.com

# siconnex

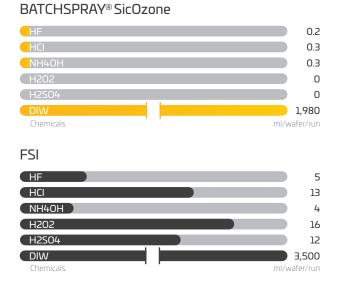

# SOLUTION FOR CHEMICALS SHORTAGE

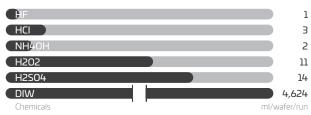

# ELIMINATE H<sub>2</sub>SO<sub>4</sub> AND H<sub>2</sub>O<sub>2</sub> WITH OUR TECHNOLOGY

Ongoing supply chain disruptions impact the industry, leading to anticipated shortages and rising prices in cleaning chemicals, as forecasted by researchers like TECHCET. Smart utilization of ozone, along with the usage of minimal amounts of ammonia

ing efficiency in SC1, SC2, and DHF processes, with precise control by using inline spiking technology.

$\nabla$

HCI

Reduce

sicOzone

$\nabla$

DIW

Reduce

and acids, result in significant cost savings. This approach can

replicate traditional cleaning steps and enhance organic clean-

$\bigcirc$

NH, OF

Reduce

MORE INFO

# Chemical consumption: SicOzone vs. conventional cleaning applications

## BATCHSPRAY® traditional

Wetbench

# Semiconductors in a world without PFAS

At the end of the day, the world's reliance on semiconductors isn't going away, but semiconductor manufacturers likely won't get to avoid PFAS requirements, even if their products are vital. They almost assuredly need to act now to avoid disruptions in their supply chain as PFAS restrictions tighten

## BY NEIL SMITH, A REGULATORY AND SUSTAINABILITY EXPERT FOR ASSENT.

FROM THEIR USE in our smartphones and laptops, and video game systems and chips for our appliances and vehicles, semiconductors play a vital role in our economy and everyday lives. The increasing demand for semiconductors around the globe has a profound impact on both business and geopolitics, with manufacturers and governments positioning to protect their supply of these important materials.

One complication to future semiconductor production is the current and upcoming changes to legislation surrounding the use of perfluoroalkyl and polyfluoroalkyl substances (PFAS), particularly in North America and the EU. These changes will result in restrictions on PFAS, potentially creating supply issues for companies in the semiconductor industry. Procurement professionals are working vigorously to ensure they have a sustainable stockpile of semiconductors to keep their operations running smoothly and avoid supply chain disruptions.

Why would the regulation of PFAS have such a profound impact on semiconductors? The

equipment and technology used to manufacture semiconductors are often reliant on PFAS, and there are no suitable alternatives readily available in the marketplace. The reality is that as PFAS restrictions continue to tighten, they will create severe disruptions for manufacturers in the areas of intellectual property and confidentiality; machine obsolescence, redesign, and derogation/exemption determinations; equipment maintenance and repair; and management of end-of-life e-waste.

## Confidentiality & intellectual property

The importance of semiconductors is not lost on governments and NGOs. The EU's REACH Annex XVII PFAS restriction proposal initially suggested exemption periods (derogations) of five and 12 years, based on risk and socioeconomic assessments. Semiconductor manufacturing was a commonly referenced example of why such a process was necessary.

Although the U.S. Environmental Protection Agency's Toxic Substances Control Act (TSCA) PFAS reporting rule does not currently exempt

semiconductor manufacturers, state-level PFAS restrictions in Maine and Minnesota allow exemptions for unavoidable use.

Even in cases where exemptions exist, it's not likely the derogation/exemption period will give industry enough time to adjust without significant pain and disruption. This is due to the sheer volume of data that needs to be collected from the supply chain concerning PFAS use, and the long lead time involved in product redesigns if they are necessary. To put it simply, if companies want to get ahead of their requirements, the time to map PFAS use in the semiconductor manufacturing process is now.

Even if an extended use period is granted, it doesn't mean companies are exempt from submitting data on PFAS usage. Product-level reporting requirements have created new challenges for the semiconductor industry as well. Historically, downstream manufacturers that requested PFAS information from semiconductor manufacturers were denied on the basis that the data was confidential business information (CBI) or intellectual property (IP). Now, there is a growing understanding that these inquiries are based on regulatory pressures and reporting obligations associated with PFAS. This has resulted in a shift in the way these types of inquiries are handled. Companies that encounter true IP roadblocks may need to do joint filings with their suppliers, or the suppliers will need to work with customers so they can meet their obligations in a manner that protects supplier IP/CBI.

# Machine obsolescence, redesign & derogation

Staying ahead of upcoming regulatory changes also means taking a hard look at the semiconductor manufacturing equipment that relies on PFAS.

Even if a company receives a 12-year derogation, there is a strong possibility that these machines will have a decades-long service life that stretches beyond the regulatory obsolescence period. As such, the company may face significant challenges if they have to routinely re-supply parts or other materials that contain PFAS as part of maintenance and repair. The machine may become a victim of unplanned obsolescence much sooner than intended.

A derogation/exemption could allow for continued PFAS use for maintenance and repair of equipment already on the market. But there is still a risk that the manufacturers of maintenance repair and operations (MRO) parts and materials see the market dry up because they are now only supplying pre-existing machines — a small amount of the market. That, coupled with heightened regulatory scrutiny and increased liability burdens, could easily lead them to significantly raise prices or, in a worst-case scenario, exit the market completely. In that worst case, their customer would then have an unplanned, non-regulatory supply chain obsolescence. In many cases, this will be the reality more so than the regulatory obsolescence. Companies have so many different moving parts to consider in a world where PFAS is restricted. Even if they're allowed to use those substances, will they still have access to them?

It is worth noting that the packaging side of semiconductor manufacturing could also be profoundly affected. Some of the semiconductor manufacturers use PFAS-containing protective coatings like films for shipping purposes, which would add another layer to their production challenges and potential supply chain disruptions.

#### End of life/e-waste

The EU is very committed to a green circular economy, including end of life. Many other jurisdictions globally also have e-waste extended producer responsibility programs in place. In the future, companies may have the challenge of figuring out a way to extract PFAS or "forever chemicals" from e-waste at end of life, which raises the question of how to treat and properly dispose of substances when there are no easy treatment technologies currently available. This derivative problem has to be solved, but it's not even being considered as an overhang yet.

Manufacturing engineers will be asking, "How do I know where PFAS are in my products and manufacturing operations?"

Product engineers will ask, "How do I remove those PFAS and what do I do with them after?"

Everyone reading this is asking, "How did I find myself in this PFAS disaster?"

At the end of the day, the world's reliance on semiconductors isn't going away, but semiconductor manufacturers have a lot of hurdles to overcome in the transition to a PFAS-regulated and PFASrestricted world. They will need to collaborate effectively with their customers and suppliers, and rely on deep visibility into their supply chains to keep their operations running smoothly.

# TECHNOLOGY I QUANTUM COMPUTING

# The crucial role of ADCs and DACs in scaling quantum computing

In recent years there has been a surge in interest surrounding the topic of quantum computing and heightened anticipation about its potential to revolutionise the technology world. However, its future relies heavily on the complex interplay with a broader set of factors. While qubits may steal the spotlight, the Analog-to-Digital Converters (ADCs) and Digital-to-Analog Converters (DACs) operating behind the scenes play a vital role.

## BY CHRIS MORRISON, DIRECTOR OF PRODUCT MARKETING, AGILE ANALOG

FIRSTLY, let's give a brief overview of what's involved with quantum computing. At the heart of quantum computing lies the quantum elements such as qubits and gates.

Qubits are the fundamental units of quantum information. Unlike the classical bits we use in conventional computers, which can only exist in a binary state of 0 or 1 at a given moment, qubits can simultaneously occupy states of 0, 1, or even a combination of the two, thanks to a quantum phenomenon known as superposition. This unique property of superposition allows qubits to perform parallel calculations, offering ground-breaking potential for quantum computing applications. Whereas classical bits can only represent one state at a time, qubits can exploit the richness of quantum mechanics to process a multitude of information simultaneously, offering exciting prospects for solving complex problems.

A quantum gate (or quantum logic gate) is a basic quantum circuit operating on a small number of qubits. Quantum logic gates are the building blocks of quantum circuits, like classical logic gates are for conventional digital circuits. They manipulate qubits to perform quantum operations.

Below is a short description of different types of quantum computer.

Superconducting quantum computers use superconducting circuits to create qubits. In order to preserve their quantum characteristics, the circuits are cooled to incredibly low temperatures. Superconducting quantum computers are comparatively advanced and capable of carrying out a large number of computations. However, they are highly sensitive to their environment and can be difficult to scale to larger sizes.

Trapped ion quantum computers use trapped ions to produce qubits. Ions are atoms that have lost or gained electrons, and they can be trapped in an electromagnetic field. Though complex to construct and operate, trapped ion quantum computers are nonetheless a relatively mature technology.

Photonic quantum computers use photons (particles of light) to form qubits. These are still in the early stages of development but are thought to be scalable because photons can be easily delivered over great distances with the use of optical fibres. In addition to being challenging to build, photonic quantum computers require specialized hardware.

Neutral atom quantum computers use neutral atoms (atoms that have not lost or gained electrons) to create qubits. These too are in the early phases of development and have the potential to be highly scalable. This is due to the ease with which lasers may be used to trap neutral atoms. Neutral atom quantum computers are also complex to build and need specialized hardware.

## Why are ADCs and DACs needed?

The control and measurement of qubits often involve converting between analog and digital signals. This is where ADCs and DACs come into play.

# Role of Analog-to-Digital Converters (ADCs)

ADCs are instrumental in quantum control, converting analog signals from the measured qubits into digital data that can be processed by standard control systems. Advances in ADC technology have led to the development of high-resolution converters capable of accurately capturing quantum signals with minimal noise and distortion. These ADCs also enable precise measurement of quantum states, providing the feedback necessary for real-time control and error correction in quantum systems.

## ADCs for sensitive readout